## Planification de la production à capacité finie dans un contexte à forte variabilité, application à l'industrie des semi-conducteurs

Emna Mhiri

#### ▶ To cite this version:

Emna Mhiri. Planification de la production à capacité finie dans un contexte à forte variabilité, application à l'industrie des semi-conducteurs. Automatique / Robotique. Université Grenoble Alpes, 2016. Français. NNT: 2016GREAT066 . tel-01485148

#### HAL Id: tel-01485148 https://theses.hal.science/tel-01485148

Submitted on 8 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Automatique Productique

Arrêté ministériel : 25 mai 2016

Présentée par

#### **Emna MHIRI**

Thèse dirigée par Mireille JACOMINO et coencadrée par Fabien MANGIONE

préparée au sein du Laboratoire G-SCOP dans l'École Doctorale EEATS

# Planification de la production à capacité finie dans un contexte à forte variabilité, application à l'industrie des semi-conducteurs

Thèse soutenue publiquement le **13 décembre 2016**, devant le jury composé de :

#### Mme. Olga BATTAÏA

Professeur, Institut supérieur de l'aéronautique et de l'espace de Toulouse, Rapporteur

#### **Mme. Nathalie SAUER**

Professeur, Université de Lorraine, Rapporteur

#### M. André ROSSI

Professeur, Université d'Angers, Examinateur

#### M. Lyes BENYOUCEF

Professeur, Université d'Aix Marseille, Président

#### M. Philippe VIALLETELLE

Ingénieur, STMicroelectronics de Crolles, Examinateur

#### **Mme. Mireille JACOMINO**

Professeur, Grenoble INP, Directrice de thèse

#### M. Fabien MANGIONE

Maître de conférences, Grenoble INP, Encadrant de thèse

#### M. Guillaume LEPELLETIER

Ingénieur, STMicroelectronics de Crolles, Invité

Emna Mhiri : Planification de la production à capacité finie dans un contexte à forte variabilité, application à l'industrie des semi-conducteurs. Thèse de doctorat, 13 décembre 2016

#### Remerciements

Cette thèse est l'aboutissement de plusieurs années de travail et n'aurait jamais pu voir le jour sans le soutien et l'aide de nombreuses personnes qui m'ont accompagnée tout au long de cette épopée! Je tiens donc ici à les remercier et leur témoigner de ma reconnaissance.

Mes premiers remerciements vont tout naturellement à mes encadrants qui ont suivi de près ces travaux. J'exprime mes plus profonds remerciements à ma directrice de thèse, Mireille Jacomino, pour l'intérêt qu'elle a porté à ce travail, sa disponibilité malgré les fonctions qui lui incombent, sa gentillesse et ses directives si précieuses. Je remercie également mon co-encadrant de thèse Fabien Mangione pour sa patience, ses nombreux conseils, ses idées, ses nombreuses relectures, et ses remarques qui m'ont permis d'affiner mon propos. Un grand merci pour cet encadrement de qualité intellectuellement et humainement.

Mes sincères remerciements vont également aux membres de jury qui ont accepté d'évaluer ce travail de thèse : Lyes Benyoucef, qui m'a fait l'honneur de présider le jury ; Olga Battaïa et Nathalie Sauer qui ont accepté d'être rapporteurs de ce mémoire, merci pour l'intérêt qu'elles ont porté à cette thèse. Merci à André Rossi qui a accepté d'examiner ma thèse. Merci pour ses remarques judicieuses et les améliorations qu'il a suggérées.

Cette thèse est le fruit d'une collaboration étroite avec l'entreprise STMicroelectonics, précisément le site de Crolles. Je tiens tout particulièrement à adresser mes remerciements à Philippe Vialletelle et Guillaume Lepelletier, des ingénieurs à STMicroelectronics de Crolles, pour leur disponibilité, leur suivi régulier et la richesse de nos échanges, sans lesquels je n'aurais pu collecter les données suffisantes qui ont enrichi ce travail de thèse et acquérir une vision synthétique du système de production à étudier.

Je remercie aussi tous les enseignants et les chercheurs du laboratoire G-SCOP. Ces trois années à G-SCOP m'ont donné l'occasion de passer de l'autre côté du miroir en travaillant avec ceux qui étaient auparavant mes enseignants. Je remercie particulièrement Yannick Frein, Khaled Hadj-Hamou, Michel Tollenaere, Pierre David, Hadrien Cambazard, Maria Di Mascolo, Gülgün Alpan, Lilia Gzara et tous les autres avec qui j'ai eu l'occasion de travailler dans le cadre de mes missions d'enseignement à Grenoble INP génie industriel.

Je souhaite aussi saluer l'ensemble des ingénieurs, stagiaires et doctorants du laboratoire G-SCOP, sans qui ces quelques années auraient paru bien plus mornes. Je pense spécialement à Widad, Khadija, Wafa, Amine, Ahmed, Hassan, Hussein, Khalil, Kléber, Rami. Je remercie également mes co-bureaux Anis et Asma. Merci pour cette ambiance exceptionnelle au laboratoire et pour les bons moments passés ensemble. Merci aussi pour leur soutien et leur aide précieuse. Merci à tous qui sont passés de collègues à vrais amis.

Enfin, je remercie mes amis et ma famille qui ont largement contribué à l'aboutissement de ce projet de thèse. Merci à Afef, Maroua, Fatma d'avoir partagé aussi bien les bons que les durs moments de la thèse. Merci à mes chers parents, qui me témoignent depuis toujours une confiance sans faille. Sans leur enthousiasme, leurs encouragements infaillibles et leur soutien indéfectible, tout ceci n'aurait pas pu être possible. Merci aussi à mes deux petits frères et ma chère grand-mère.

J'adresse une pensée particulière à Riadh. Avec sa patience et son soutien, j'ai pu mener à bien la phase finale de ces travaux avec confiance et sérénité.

Une page se tourne, une autre s'ouvre, merci à tous ceux et celles qui y ont contribué et m'ont amené à faire les bons choix.

$\grave{A}$  ma famille.

$\grave{A}$  mes amis.

$\grave{A}$  mes rencontres de la vie, d'aujourd'hui et d'hier. . .

$\grave{A}$  tous ceux qui m'aiment!

À tous ceux que j'aime.

$\grave{A}$  la vie qui me porte.

## Table des matières

| Ta                        | Table des figures    |         | ix                                                                            |       |

|---------------------------|----------------------|---------|-------------------------------------------------------------------------------|-------|

| $\mathbf{L}_{\mathbf{i}}$ | iste d               | les tab | oleaux                                                                        | xiii  |

| In                        | ntroduction générale |         |                                                                               | 1     |

| 1                         | Cor                  | ntexte  | industriel et problématique                                                   | 5     |

|                           | 1.1                  | Introd  | $\operatorname{luction} \ldots \ldots \ldots \ldots \ldots \ldots \ldots$     | . 7   |

|                           | 1.2                  | Proces  | ssus de fabrication des circuits intégrés                                     | . 8   |

|                           |                      | 1.2.1   | Description générique du processus de fabrication                             | . 8   |

|                           |                      | 1.2.2   | Entités de base de la fabrication des semi-conducteurs                        | . 10  |

|                           |                      | 1.2.3   | Classification du système de production des semi-conducteurs                  | . 11  |

|                           |                      | 1.2.4   | Complexité de la production dans le secteur de la microélectronique           | ue 12 |

|                           | 1.3                  | Planif  | fication de la production dans l'industrie des semi-conducteurs $\ \ . \ \ .$ | . 17  |

|                           |                      | 1.3.1   | Niveaux de la planification de la production                                  | . 18  |

|                           |                      | 1.3.2   | Objectifs de la planification de la production                                | . 19  |

|                           |                      | 1.3.3   | Caractéristiques des problèmes de planification de la production              | 1     |

|                           |                      |         | dans l'industrie des semi-conducteurs                                         | . 20  |

|                           |                      |         | 1.3.3.1 Contraintes                                                           | . 20  |

|                           |                      |         | 1.3.3.2 Indicateurs de performance                                            | . 21  |

|                           |                      | 1.3.4   | Techniques de planification de la production dans l'industrie des             | 3     |

|                           |                      |         | semi-conducteurs                                                              | . 22  |

|                           |                      |         | 1.3.4.1 Les techniques classiques                                             | . 22  |

|                           |                      |         | 1.3.4.2 Les modèles analytiques                                               | . 25  |

|                           |                      |         | 1.3.4.3 Les modèles de simulation                                             | . 26  |

|                           |                      |         | 1.3.4.4 Les techniques heuristiques                                           | . 28  |

|          |     | 1.3.4.5 Les techniques d'intelligence artificielle                 | 30 |

|----------|-----|--------------------------------------------------------------------|----|

|          |     | 1.3.4.6 Autres classifications des techniques de planification     | 31 |

|          |     | 1.3.5 Systèmes de planification de la production                   | 31 |

|          | 1.4 | Problématique                                                      | 34 |

|          | 1.5 | Conclusion                                                         | 35 |

| <b>2</b> | Pla | nification de la fabrication des semi-conducteurs : État de l'art  | 37 |

|          | 2.1 | Introduction                                                       | 39 |

|          | 2.2 | Méthodologie et classification des problèmes                       | 39 |

|          | 2.3 | Techniques de planification existantes et leurs limites            | 45 |

|          |     | 2.3.1 Planification stratégique                                    | 45 |

|          |     | 2.3.2 Planification tactique et opérationnelle                     | 46 |

|          |     | 2.3.2.1 Techniques basées sur l'optimisation                       | 46 |

|          |     | 2.3.2.2 Techniques basées sur la simulation                        | 50 |

|          |     | 2.3.2.3 Techniques basées sur la théorie des files d'attente       | 50 |

|          | 2.4 | Positionnement de notre problématique                              | 51 |

|          | 2.5 | Conclusion                                                         | 52 |

| 3        | Rés | solution analytique du problème de planification à capacité finie  | 55 |

|          | 3.1 | Introduction                                                       | 57 |

|          | 3.2 | Description du problème                                            | 57 |

|          |     | 3.2.1 Contraintes                                                  | 58 |

|          |     | 3.2.2 Hypothèses                                                   | 59 |

|          |     | 3.2.3 Enjeux                                                       | 60 |

|          |     | 3.2.4 Questions de recherche                                       | 61 |

|          | 3.3 | Notations                                                          | 61 |

|          | 3.4 | Formulation mathématique du problème : MIP                         | 62 |

|          | 3.5 | Complexité                                                         | 64 |

|          | 3.6 | Résolution du problème                                             | 65 |

|          | 3.7 | Méthodes de résolution alternatives                                | 66 |

|          |     | 3.7.1 Procédure d'agrégation                                       | 67 |

|          |     | 3.7.2 Heuristique de décomposition                                 | 67 |

|          |     | 3.7.3 Relaxation lagrangienne                                      | 69 |

|          |     | 3.7.3.1 Principe de la relaxation lagrangienne                     | 69 |

|          |     | 3.7.3.2 Application de la relaxation lagrangienne à notre problème | 71 |

|          | 3.8 | Résultats expérimentaux                                            | 75 |

|          | 3.9 | Conclusion                                                         | 79 |

| 4 | Rés   | solution | approchée du problème de planification à capacité finie 8             |

|---|-------|----------|-----------------------------------------------------------------------|

|   | 4.1   | Introd   | uction                                                                |

|   | 4.2   | Projec   | tion du $\mathit{WIP}$ à capacité infinie                             |

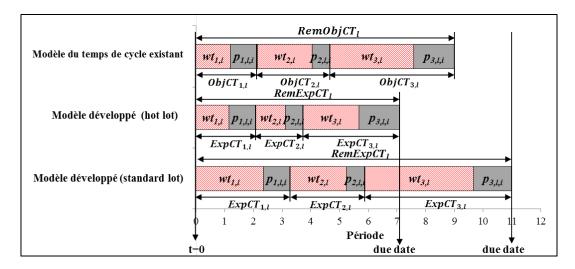

|   |       | 4.2.1    | Modèle du temps de cycle                                              |

|   |       |          | 4.2.1.1 Modèle du temps de cycle développé 8                          |

|   |       | 4.2.2    | Principe de la projection du WIP à capacité infinie                   |

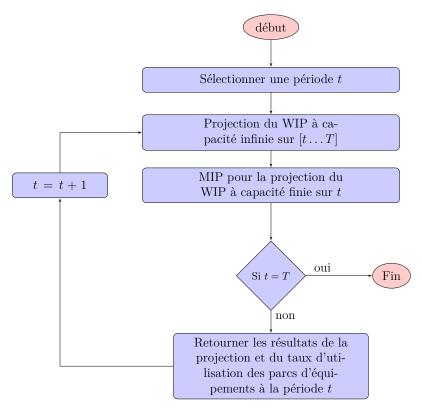

|   | 4.3   | Heuris   | tique de décomposition à base de $MIP$                                |

|   | 4.4   | Heuris   | tique de décomposition à base d'algorithmes                           |

|   |       | 4.4.1    | Calcul de la charge accumulée                                         |

|   |       | 4.4.2    | Equilibrage de la charge et la capacité                               |

|   | 4.5   | Résult   | ats et discussion                                                     |

|   |       | 4.5.1    | Génération des instances aléatoires                                   |

|   |       | 4.5.2    | Evaluation des algorithmes heuristiques proposés en comparaison à     |

|   |       |          | une solution optimale                                                 |

|   |       |          | 4.5.2.1 Comparaison entre la solution optimale et l'heuristique à     |

|   |       |          | base de MIP                                                           |

|   |       |          | 4.5.2.2 Comparaison entre la solution optimale et l'heuristique à     |

|   |       |          | base d'algorithmes                                                    |

|   |       | 4.5.3    | Comparaison entre le processus réel et les résultats de l'heuristique |

|   |       |          | à base d'algorithmes pour des instances industrielles                 |

|   |       |          | 4.5.3.1 Analyse basée sur la mesure de la performance : nombre        |

|   |       |          | de $moves$ par usage                                                  |

|   | 4.6   | Conclu   | asion                                                                 |

| 5 | Mis   | se en œ  | euvre industrielle 11                                                 |

|   | 5.1   | Introd   | uction                                                                |

|   | 5.2   | Préser   | ntation du cas industriel                                             |

|   |       | 5.2.1    | Particularités du cas industriel                                      |

|   |       | 5.2.2    | Description de la planification de la production chez ST Crolles 12   |

|   | 5.3   | Descri   | ption de la plateforme développée                                     |

|   |       | 5.3.1    | Vue d'ensemble                                                        |

|   |       | 5.3.2    | Conséquences de la mise en œuvre du système de planification à        |

|   |       |          | capacité finie                                                        |

|   | 5.4   | Conclu   | asion                                                                 |

| C | onclu | ısion g  | énérale et perspectives 12                                            |

| D | áfána | noos b   | ibliographiques 13                                                    |

|   | SICIE |          | 101102170111011C3                                                     |

| Annex | e A    |                                         | 149                                    |

|-------|--------|-----------------------------------------|----------------------------------------|

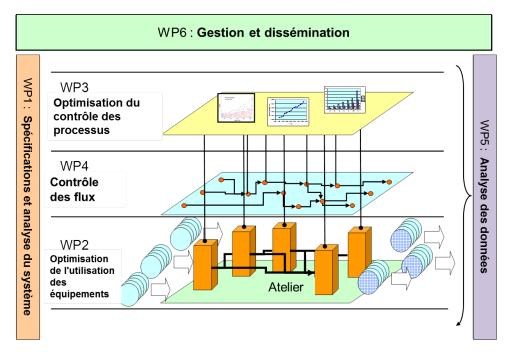

| A     | Le pro | ojet européen <i>INTEGRATE</i>          |                                        |

|       | A.1    | Introduction                            |                                        |

|       | A.2    | WP2 : Optimisation de l'utilisation des | $\acute{e}$ quipements 150             |

|       |        | A.2.1 WP2.1 : Ajustement dynamiqu       | e des recettes d'équipement 151        |

|       |        | A.2.2 WP2.2 : Gestion de l'équipemen    | it liée à l'état de l'équipement $151$ |

|       |        | A.2.3 WP2.3 : Performance de l'équip    | pement / fabrication visuelle $151$    |

|       |        | A.2.4 WP2.4 : Mise en œuvre pilote      |                                        |

|       | A.3    | WP4 : Contrôle des flux de production   |                                        |

|       |        | A.3.1 WP4.1 : Planification et métho    | des de répartition $\dots 152$         |

|       |        | A.3.2 WP4.2 : Des outils de simulation  | on et de validation $\dots 152$        |

|       |        | A.3.3 WP4.3 : Implémentations pilot     | es                                     |

|       | A.4    | WP5 : Analyse des données               |                                        |

| Annex | е В    |                                         | 155                                    |

| В     | Preuv  | e de complexité                         |                                        |

## Table des figures

| 1.1  | Utilisation quotidienne des circuits intégrés                                   | 7  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Chiffre d'affaires annuel et taux de croissance cumulé du marché des            |    |

|      | semi-conducteurs                                                                | 8  |

| 1.3  | Processus de fabrication d'un circuit intégré                                   | 9  |

| 1.4  | Exemple d'une route                                                             | 11 |

| 1.5  | Modèle simplifié d'un flux réentrant                                            | 14 |

| 1.6  | Un lot de 25 plaquettes dans un FOUP                                            | 15 |

| 1.7  | Flux d'information dans un système de fabrication                               | 20 |

| 1.8  | Classification des techniques industrielles de planification de la production.  | 23 |

| 1.9  | Relation entre les approches de planification de la production                  | 23 |

| 1.10 | Phases de la simulation                                                         | 27 |

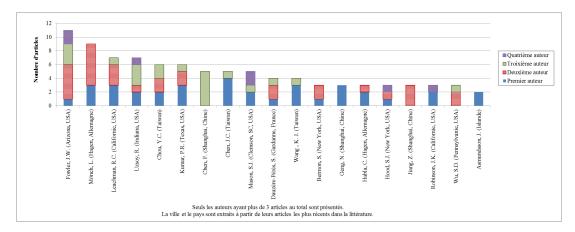

| 2.1  | Principaux auteurs                                                              | 40 |

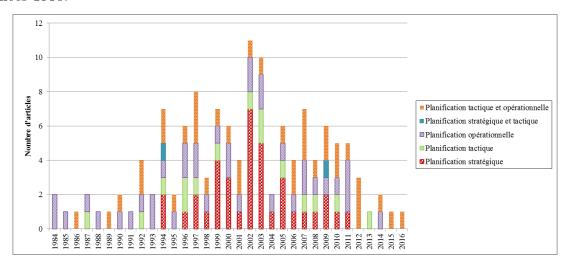

| 2.2  | Nombre d'articles par année classés selon le niveau de décision de la           |    |

|      | planification.                                                                  | 41 |

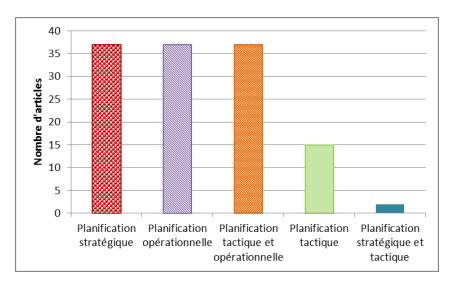

| 2.3  | Répartition des articles selon les niveaux de décision                          | 42 |

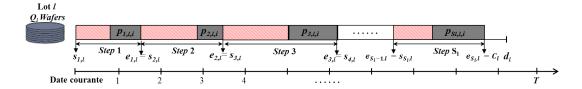

| 3.1  | Paramètres et variables de décision du problème                                 | 62 |

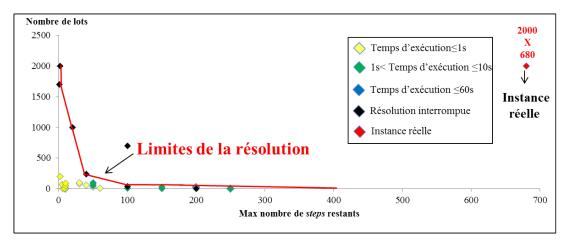

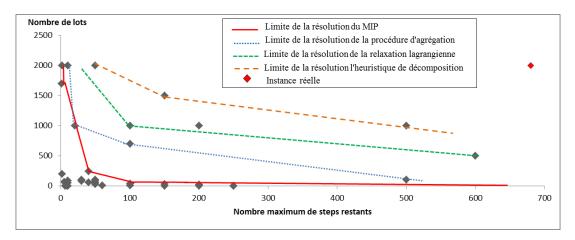

| 3.2  | Limites de résolution du MIP                                                    | 66 |

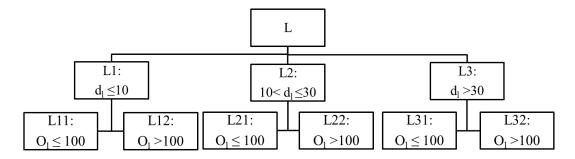

| 3.3  | Principe de décomposition                                                       | 68 |

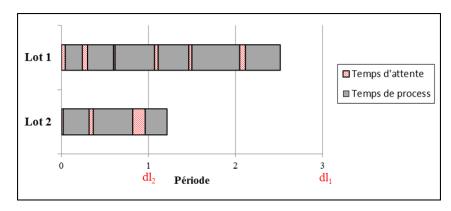

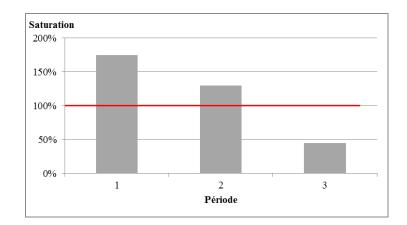

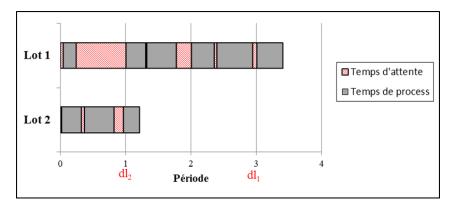

| 3.4  | Planning de production de l'instance                                            | 75 |

| 3.5  | Saturation du parc d'équipements par période.                                   | 75 |

| 3.6  | Résultat de l'heuristique : Planning de production                              | 75 |

| 3.7  | Résultat de l'heuristique : Saturation du parc d'équipements par période.       | 76 |

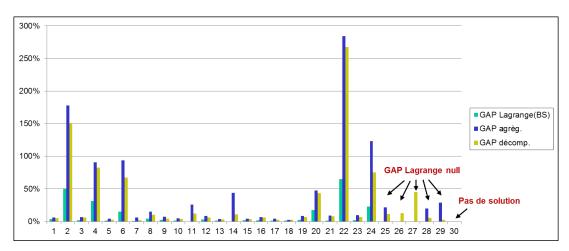

| 3.8  | Limites de résolution du $\emph{MIP},$ la procédure d'agrégation, l'heuristique |    |

|      | de décomposition et la relaxation lagrangienne                                  | 77 |

| 3.9  | Qualité de la solution de la procédure d'agrégation, l'heuristique de dé-<br>composition et l'heuristique post-lagrangienne |

|------|-----------------------------------------------------------------------------------------------------------------------------|

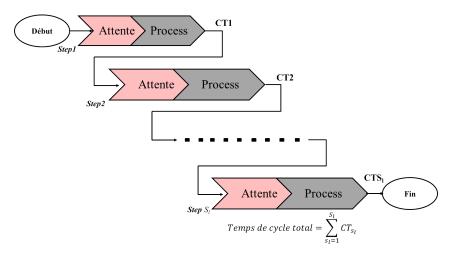

| 4.1  | Évaluation du temps de cycle total                                                                                          |

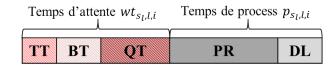

| 4.2  | Composants du temps de cycle total                                                                                          |

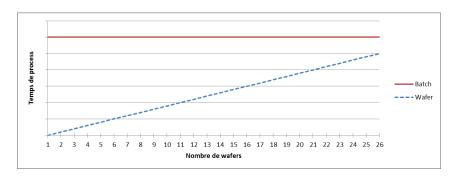

| 4.3  | Variabilité du temps de process en fonction du type de traitement de                                                        |

|      | l'équipement                                                                                                                |

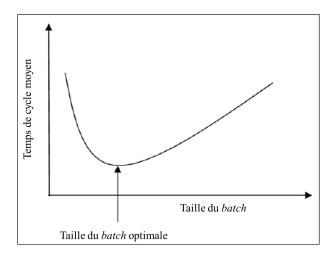

| 4.4  | Variabilité du temps de cycle en fonction de la taille du batch 90                                                          |

| 4.5  | Principe du calcul du temps de cycle des steps                                                                              |

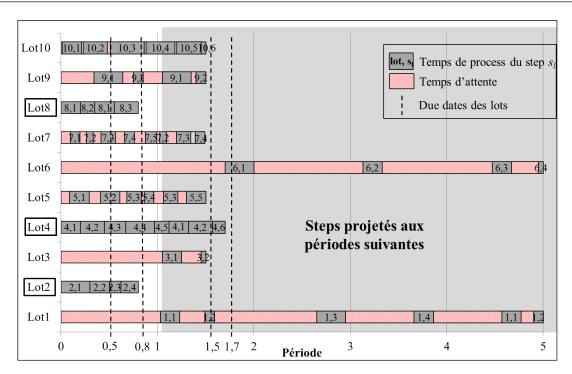

| 4.6  | Simple instance : planning de production à capacité infinie                                                                 |

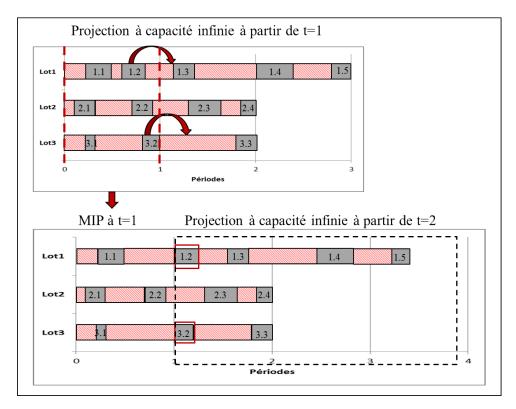

| 4.7  | Algorigramme de l'heuristique à base de MIP                                                                                 |

| 4.8  | Instance simple expliquant le principe de l'heuristique à base de $MIP$ 98                                                  |

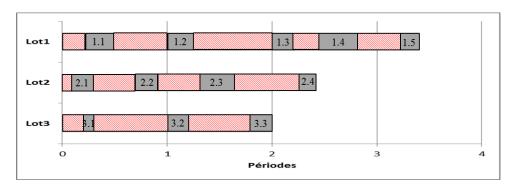

| 4.9  | Planning obtenu à la fin du test de l'heuristique                                                                           |

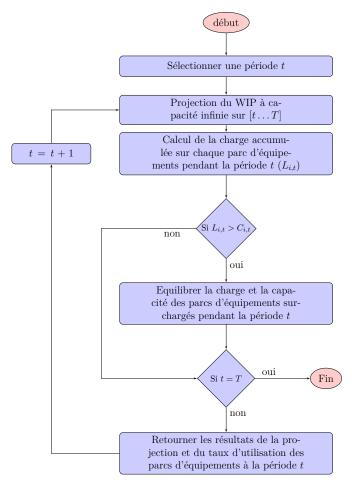

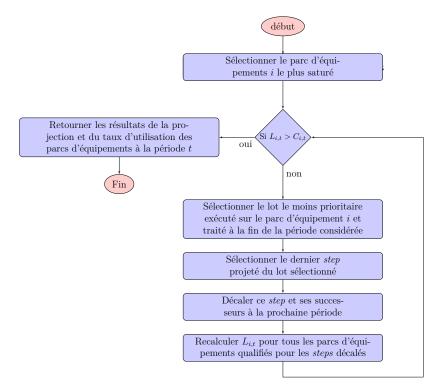

| 4.10 | Algorigramme de l'heuristique à base d'algorithmes                                                                          |

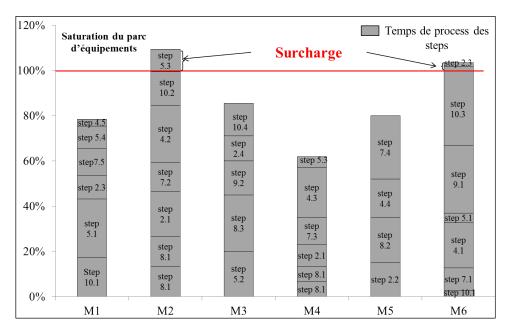

| 4.11 | Calcul de la charge à capacité infinie                                                                                      |

| 4.12 | Algorigramme de l'équilibrage de la charge                                                                                  |

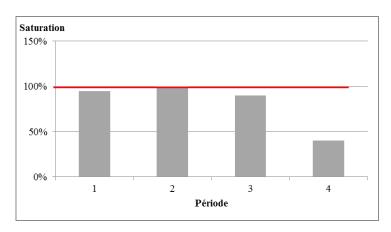

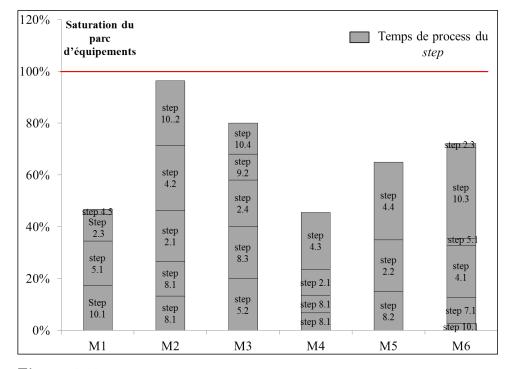

| 4.13 | Saturation des parcs d'équipements après équilibrage de la charge $107$                                                     |

| 4.14 | Le planning de l'instance obtenu en utilisant l'heuristique à base d'algo-                                                  |

|      | rithmes                                                                                                                     |

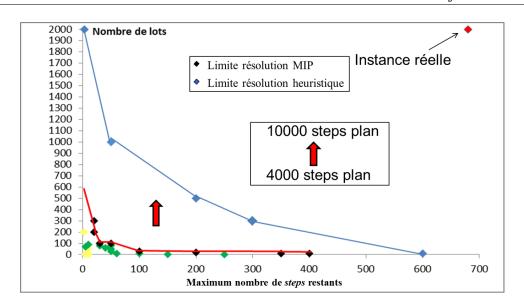

| 4.15 | Limite de la résolution de l'heuristique en comparaison avec celle du MIP $110$                                             |

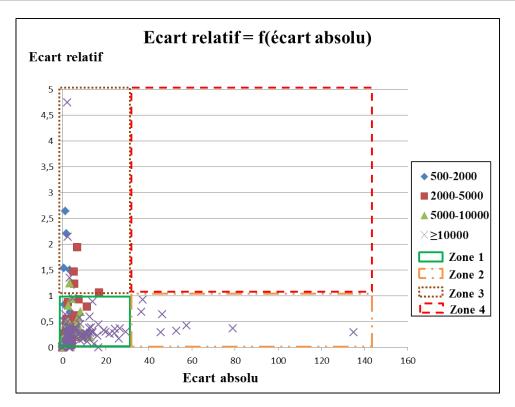

| 4.16 | Comparaison entre la solution optimale et l'heuristique à base d'algo-                                                      |

|      | rithmes                                                                                                                     |

| 4.17 | Saturation hebdomadaire d'un parc d'équipements de photo-lithographie                                                       |

|      | à capacité infinie et finie                                                                                                 |

| 4.18 | Comparaison du nombre de <i>moves</i> réel vs. estimé                                                                       |

| 4.19 | Comparaison entre le nombre total de moves traités par l'usage de pho-                                                      |

|      | tolithographie réel vs. estimé                                                                                              |

| 4.20 | Comparaison entre le nombre total de moves traités par l'usage de gra-                                                      |

|      | vure réel vs. estimé                                                                                                        |

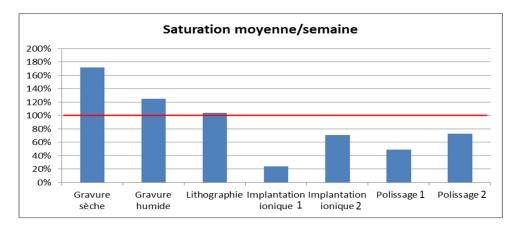

| 5.1  | Résultats de saturation des parcs d'équipements                                                                             |

| 5.2  | Écarts entre la quantité prévue à livrer et la quantité livrée réellement                                                   |

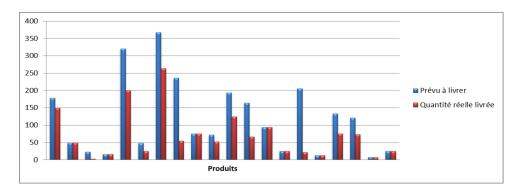

|      | pour une vingtaine de produits                                                                                              |

| 5.3  | Écarts entre la date de livraison réelle et la date de livraison prévue pour                                                |

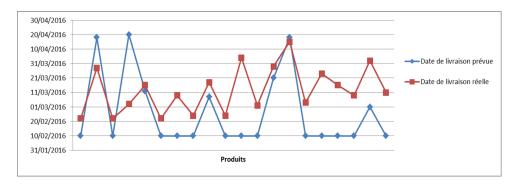

|      | une vingtaine de produits                                                                                                   |

| 5.4  | Vue d'ensemble du logiciel développé                                                                                        |

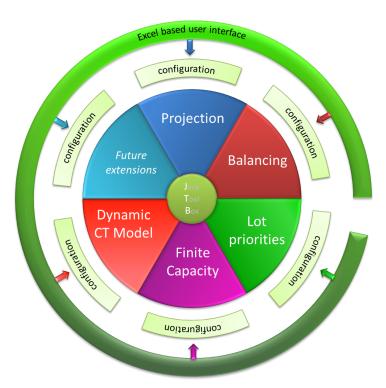

| 5.5  | Interface graphique du logiciel développé                                                                                   |

| 5.6  | Entrées et sorties de chaque module du logiciel développé                                                                   |

| 5.7 | Évolution de l'indicateur juste à temps à ST Crolles 300 |

|-----|----------------------------------------------------------|

| 5.8 | Saturation des parcs d'équipements                       |

| A.1 | Les work packages du projet INTEGRATE                    |

| B.1 | Instance du problème d'ordonnancement                    |

## Liste des tableaux

| 1.1 | Classification des systèmes de production                                        | 13  |

|-----|----------------------------------------------------------------------------------|-----|

| 1.2 | Niveaux de planification de la production selon l'horizon de planification       | 18  |

| 1.3 | Principales approches de la méthode $MRP$                                        | 25  |

| 2.1 | Type de la source pour les différents articles de la revue de littérature        | 39  |

| 2.2 | Source des articles de revues                                                    | 40  |

| 2.3 | Classification des articles selon la méthode de résolution                       | 44  |

| 2.4 | Taxonomie des approches de planification de la production à capacité             |     |

|     | finie appliquée à l'industrie des semi-conducteurs, extraites de la littérature. | 53  |

| 3.1 | Notations du problème                                                            | 63  |

| 3.2 | Synthèse des paramètres des tests réalisés                                       | 65  |

| 3.3 | Valeurs des nouveaux paramètres                                                  | 68  |

| 3.4 | Pourcentage des lots pour chaque sous-problème pour des instances réelles        | 69  |

| 3.5 | Données relatives aux lots pour une instance simple                              | 74  |

| 3.6 | Pour<br>centages des problèmes résolus en moins de $5min~(\%)$                   | 76  |

| 3.7 | Résultats expérimentaux : Comparaison de la qualité de la solution des           |     |

|     | trois méthodes pour résoudre le problème de planification à capacité finie       | 79  |

| 3.8 | Résultats expérimentaux : Comparaison du temps de résolution des trois           |     |

|     | méthodes pour résoudre le problème de planification à capacité finie             | 80  |

| 4.1 | Données d'une simple instance                                                    | 93  |

| 4.2 | Notations pour le $MIP$ mono-période                                             | 96  |

| 4.3 | Paramètres de l'exemple                                                          | 97  |

| 4.4 | Notations pour le (PL.3)                                                         | .01 |

| 4.5 | Ordre des lots traités par $M2$ selon $rankingCoeff_l$                           | .07 |

#### Table des matières

| 4.6 | Les paramètres du $\mathit{WIP}$ au début de la seconde période | 107 |

|-----|-----------------------------------------------------------------|-----|

| 4.7 | Paramètres des tests                                            | 109 |

| 4.8 | Comparaison MIP vs. heuristique                                 | 110 |

| 4.9 | Comparaison du TWT réel versus estimé                           | 115 |

## Introduction générale

L'industrie des semi-conducteurs, et la micro-électronique de façon générale, est l'épine dorsale des innovations qui permettent la fabrication de nombreux nouveaux produits allant des produits de consommation jusqu'aux applications industrielles, aux domaines de l'automobile, des télécommunications, de la médecine, de la bureautique et bien d'autres. Cette industrie consiste à la fabrication d'un circuit intégré. Le processus de fabrication d'un circuit intégré se décompose principalement en deux grandes phases :

- la phase de fabrication des plaques ou wafers en anglais, appelée front-end.

- la phase d'encapsulation et d'assemblage du produit, qu'on appelle back-end.

La phase front-end est la phase la plus longue et la plus coûteuse dans le processus de fabrication. En effet, le coût d'une nouvelle usine de fabrication de wafers peut atteindre environ 4 milliards de dollars et il faut entre 4 et 6 semaines pour obtenir une plaque avec tous ses circuits intégrés [70]. Une opération aussi critique mérite qu'on s'y attarde et c'est ce à quoi nous nous sommes intéressés dans ces travaux de thèse.

Le processus de fabrication est considéré comme l'un des processus de fabrication les plus complexes [125]. L'usine de fabrication des semi-conducteurs ou le "wafer fab" est caractérisée par une production de forte variabilité et faible volume (High Mix Low Volume ou HMLV): il y a des centaines de produits et le même équipement peut être partagé par de nombreux produits de diverses technologies, c'est-à-dire nécessitant différents réglages et temps de process.

En outre, le processus de fabrication des wafers est composé des centaines d'étapes élémentaires appelées "steps". Le nombre important des steps est dû au fait que les processus dans les installations de fabrication de semi-conducteurs sont de type ré-entrant, i.e. les wafers sont traités par les mêmes équipements à plusieurs reprises. Pour chaque step, le wafer doit être traité par divers types d'équipements selon une recette bien définie. La recette contient les instructions détaillées à utiliser au niveau de l'équipement

afin de procéder à des transformations physiques ou des mesures prévues. L'identification des équipements candidats à utiliser est effectuée par la qualification des recettes sur les équipements. Cependant, dans les wafer fabs HMLV, en raison de multiples différences dans des configurations matérielles et logicielles, d'où la variété des recettes à utiliser, il est impossible de qualifier toutes les recettes sur chaque équipement. La qualification est l'une des caractéristiques de la fabrication des semi-conducteurs HMLV. Différents parcs d'équipements (i.e. ensemble d'équipements parallèles et identiques) peuvent être qualifiés pour la même recette et de multiples recettes peuvent être réalisées sur le même parc d'équipements. Alors, le processus de chaque step sur un parc d'équipements spécifique dépend de sa qualification. Ceci est connu par la contrainte des qualifications du processus de fabrication. En outre, chaque parc d'équipements a une capacité identifiée qui se réfère à sa charge limite.

Toutes ces caractéristiques et contraintes rencontrées dans l'environnement de fabrication des semi-conducteurs rendent la planification de la production dans cette industrie très complexe.

En effet, pour établir un planning de production réalisable sur un horizon de planification à moyen terme, il faut donc considérer en plus des caractéristiques du processus de fabrication, les contraintes de capacité et de qualifications des équipements.

En plus, comme pour d'autres industries, les installations de fabrication des semiconducteurs doivent respecter leurs engagements de livraison aux clients et tenir compte

des due dates des lots de production pour survivre dans un environnement commercial

concurrentiel. En effet, ne pas répondre aux dates d'échéance peut entraîner des pénalités

à cause des retards de livraison et éventuellement la perte de futurs clients. Pour mesurer

la qualité d'un planning au point de vue livraison à temps, plusieurs critères ont été utilisés

dans la littérature, tels que la minimisation du retard total pondéré, la minimisation de

la somme des avances (pondérés) et des retards (pondérés), la minimisation du nombre

de lots en retard, etc. Pour les fabs HMLV, le temps de cycle des steps est très variable

en raison de nombreuses sources telles que l'hétérogénéité des modes de fonctionnement

des équipements, les priorités des produits, les qualifications des steps, etc. Il est alors

crucial de considérer également des temps de cycle variables en définissant un plan de

production. Dans la pratique, les données historiques de la fab et diverses applications de

la théorie des files d'attente sont souvent utilisées.

Ainsi, l'objectif de cette étude est de proposer des outils d'aide à la décision pour la planification de la production tout en tenant compte des contraintes de capacité et des qualifications des équipements, des priorités des lots, de la variabilité des temps de cycle et plusieurs caractéristiques du processus de fabrication des semi-conducteurs d'où l'obtention d'un plan de production réalisable.

Le projet, réalisé tout au long de cette thèse, est présenté dans ce rapport réparti en cinq chapitres.

Dans un premier chapitre introductif, nous présentons le contexte industriel de cette étude et nous posons la problématique traitée. Dans le chapitre 2, un état de l'art est réalisé, qui vise à présenter les différents problèmes et techniques de planification présents dans la littérature. L'objectif de cette partie est non seulement de retracer l'état de l'art des techniques existantes, mais aussi d'identifier les écarts entre les différents travaux et de bien positionner notre étude par rapport à la littérature existante. Des méthodes de résolution analytique sont présentées au chapitre 3 et des algorithmes approchés au chapitre 4. La mise en œuvre de ce travail à travers une plateforme de planification de la production pour une entreprise fera l'objet du chapitre 5.

Enfin, nous clôturons ce rapport par une conclusion générale contenant une synthèse du travail effectué et les perspectives éventuelles qui ouvrent les horizons sur d'autres sujets pouvant être abordés à la suite de cette étude.

1

### Contexte industriel et problématique

Résumé: Cette thèse a été effectuée dans le cadre d'un projet européen impliquant des industriels des semi-conducteurs. Pour cela, ce chapitre présente ce secteur industriel et les spécificités de son processus de fabrication. À partir des caractéristiques de cet environnement industriel, nous déterminons plusieurs facteurs qui rendent la planification de la production extrêmement difficile et complexe. Nous nous intéressons, par la suite, aux différents techniques et systèmes de planification de la production existants, employés au sein de cet environnement industriel, en précisant leurs avantages et leurs limites. Enfin, la problématique traitée dans ce travail est présentée en détaillant les thèmes de réflexion qui en découlent.

#### Chapitre 1. Contexte industriel et problématique

#### Sommaire

| 1.1 | $\mathbf{Intr}$ | oduction                                                                    | 7         |

|-----|-----------------|-----------------------------------------------------------------------------|-----------|

| 1.2 | Pro             | cessus de fabrication des circuits intégrés                                 | 8         |

|     | 1.2.1           | Description générique du processus de fabrication                           | 8         |

|     | 1.2.2           | Entités de base de la fabrication des semi-conducteurs                      | 10        |

|     | 1.2.3           | Classification du système de production des semi-conducteurs                | 11        |

|     | 1.2.4           | Complexité de la production dans le secteur de la microélectronique         | 12        |

| 1.3 | Plan            | dification de la production dans l'industrie des semi-conducteurs           | 17        |

|     | 1.3.1           | Niveaux de la planification de la production                                | 18        |

|     | 1.3.2           | Objectifs de la planification de la production                              | 19        |

|     | 1.3.3           | Caractéristiques des problèmes de planification de la production dans l'in- |           |

|     |                 | dustrie des semi-conducteurs $\dots$                                        | 20        |

|     | 1.3.4           | Techniques de planification de la production dans l'industrie des semi-     |           |

|     |                 | conducteurs                                                                 | 22        |

|     | 1.3.5           | Systèmes de planification de la production                                  | 31        |

| 1.4 | Prol            | olématique                                                                  | <b>34</b> |

| 1.5 | Con             | clusion                                                                     | <b>35</b> |

#### 1.1 Introduction

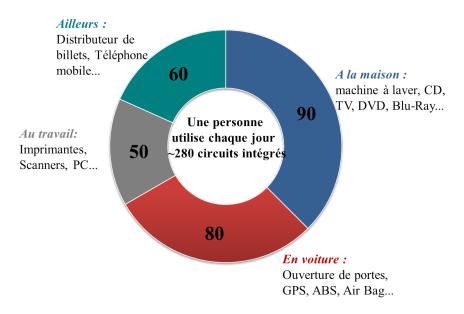

Les circuits intégrés <sup>1</sup> sont de plus en plus utilisés dans tous les domaines de la vie quotidienne. En moyenne, en 2014, une personne utilise plus de 280 puces et 6 milliards de transistors par jour. Ces puces sont installées dans presque tous les équipements qui nous entourent allant des lave-vaisselles, fours, micro-ondes, écrans plats aux téléphones et équipements de bureau [51]. La figure 1.1 illustre l'utilisation moyenne des puces électroniques dans les différentes activités de la vie quotidienne.

Figure 1.1 – Utilisation quotidienne des circuits intégrés

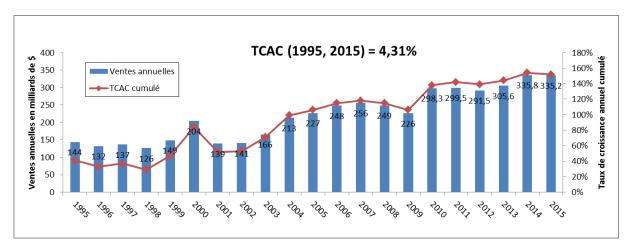

La demande en circuits intégrés est en forte croissance dans tous les domaines (automobile, communication, divertissement, multimédia, soin médical,...). Le revenu annuel de l'industrie des semi-conducteurs a atteint 335 milliards de dollars en 2015. Durant ces vingt dernières années, son taux de croissance annuel composé (TCAC) atteint 4.31% [1]. La figure 1.2 illustre l'évolution des revenus annuels et du taux de croissance cumulé du marché des semi-conducteurs dans le monde de 1995 à 2015. Cette augmentation de la demande a conduit à une concurrence accrue sur le marché. Par conséquent, les industriels des semi-conducteurs ne doivent pas limiter leur intérêt à la conception du produit mais doivent aussi accorder plus d'attention à la capacité de fabrication afin d'assurer un coût raisonnable et une livraison à temps du produit. En effet, une bonne compréhension de la capacité est essentielle pour maintenir la rentabilité au fil du temps. Dans de nombreux cas, la demande d'un produit est supérieure à la capacité de l'entreprise pour satisfaire

<sup>1.</sup> Circuit intégré (aussi appelé puce électronique) : composant électronique reproduisant une ou plusieurs fonctions électroniques plus ou moins complexes dans un volume réduit.

Figure 1.2 — Chiffre d'affaires annuel en milliards de dollars et taux de croissance cumulé du marché des semi-conducteurs dans le monde entier [1].

cette demande. Cela implique une pénalité importante, en termes de pertes de revenus, afin que le chargement de l'usine soit à un niveau inférieur au maximum qu'elle peut gérer. D'autre part, des conséquences négatives importantes peuvent provenir lors d'une surcharge de l'usine. Ces résultats incluent les longs temps de cycle, les dates de livraison manquées, des stocks excessifs, et les rendements éventuellement faibles. Par conséquent, il est essentiel que les fabricants de semi-conducteurs utilisent des méthodes précises pour la planification de leur capacité.

#### 1.2 Processus de fabrication des circuits intégrés

#### 1.2.1 Description générique du processus de fabrication

Les circuits intégrés sont constitués de deux parties : la plaquette (appelée aussi plaque ou « wafer » en anglais), partie active en silicium, et le boîtier qui protège la plaquette de son environnement externe et en facilite le montage dans les systèmes électroniques.

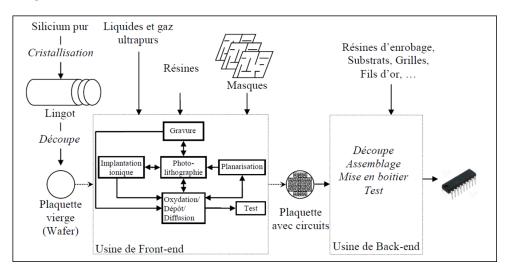

La fabrication d'un circuit intégré est effectuée par l'association de plusieurs composants électroniques élémentaires interconnectés (transistors, résistances, etc.) qui sont réalisés sur une même plaquette d'un matériau semi-conducteur (généralement du silicium). La figure 1.3 résume le processus de fabrication. Tout d'abord, les plaquettes brutes sont fabriquées en découpant des lingots de silicium monocristallin. En parallèle, les différents masques sont conçus et réalisés pour chacun des produits. Ensuite, les plaques rentrent dans la première phase de fabrication appelée « Front End ». Dans cette phase, on trouve une succession d'opérations d'élaboration des composants et de leurs connexions ainsi qu'un test électrique de validation. Les flux physiques (lots de plaquettes) entre les différents ateliers de l'usine sont schématisés par des flèches sur la figure 1.3. Ensuite, les

plaquettes passent à l'usine de « Back End » où elles sont découpées pour obtenir des circuits individuels. Ces derniers sont assemblés, mis en boitier et testés pour obtenir les circuits intégrés.

Figure 1.3 – Processus de fabrication d'un circuit intégré [16].

Cette thèse porte sur la planification de production pour la phase de *front end* et plus précisément la fabrication des plaques électroniques. Cette phase correspond à la partie la plus coûteuse (le coût d'une wafer fab peut atteindre jusqu'à 5 milliards de dollars [125]), la plus complexe et la plus longue dans le processus de fabrication par rapport aux autres phases de fabrication. Une description détaillée du processus de fabrication est présentée dans la suite de cette section.

Les plaquettes de silicium vierges subissent des centaines d'opérations de fabrication suivant une gamme spécifique à chaque produit appelée « route » <sup>3</sup>. Ces opérations sont répétées pour chaque couche du circuit sur la plaquette et elles peuvent être classées en six catégories :

**L'oxydation**: Il s'agit de la formation d'une couche de silice  $(SiO_2)$  à la surface du wafer de silicium par l'oxydation dans un four à haute température. Une couche de résine photosensible est ensuite déposée sur la couche d'oxyde.

La photolithographie : Elle consiste à imprimer des motifs d'un masque sur la couche photosensible déposée sur la plaquette par projection de lumière.

La gravure : C'est une élimination des zones générées par le masque (gravure sèche) ou suppression des éléments indésirables du matériau photosensible (gravure humide).

<sup>3.</sup> Gamme opératoire pour un produit donné

L'implantation ionique ou dopage : Après la gravure, les surfaces exposées peuvent être chargées électriquement en utilisant un faisceau d'ions de haute intensité.

La déposition chimique : Il s'agit de déposer une couche isolante sur la plaquette pour en aplanir la surface et en isoler les couches de métal.

La création des interconnexions : Cette étape permet de créer des connexions entre les différents composants de la puce par dépôt des couches conductrices sur la plaquette.

#### 1.2.2 Entités de base de la fabrication des semi-conducteurs

Dans cette section, les entités impliquées dans le processus de fabrication des semiconducteurs sont introduites tout en présentant les relations et les interactions entre elles.

Dans ce contexte industriel, on trouve un mélange entre les termes extraits de l'industrie et ceux utilisés dans la littérature. Par conséquent, nous introduisons des définitions spécifiques et précises afin d'avoir une analyse claire lors de cette étude.

- Plaque, plaquette ou « wafer » : Les plaques non traitées sont la matière première du processus de fabrication des semi-conducteurs et les plaques traitées correspondent au produit final. Ce sont des disques circulaires de silicium constituant le support des circuits intégrés.

- *Produit*: Un produit spécifie le circuit intégré fabriqué. En général, des centaines à des milliers d'unités du même produit sont fabriqués simultanément l'un près de l'autre sur une plaque.

- Lot : Un lot se réfère à un ensemble de plaques qui suivent une route ensemble. Toutes les plaques dans un lot correspondent à un même produit. Dans notre cas d'étude, un lot est composé de 25 plaques.

- Route: Une route décrit le flux de processus de fabrication d'un lot. Elle se compose d'un ensemble d'opérations depuis le lancement du lot jusqu'à sa livraison.

- Opération : Une opération est une étape dans une route. Elle est composée d'un ensemble de tâches élémentaires appelées « steps ». On trouve des opérations de process et des opérations de métrologie i.e. de contrôle du processus de fabrication. Dans cette étude, seules les opérations de process sont considérées.

- Step : Un step caractérise une étape élémentaire du processus de fabrication correspondant au passage d'un lot d'une machine à une autre. Il est associé à une recette et un parc d'équipements.

- Equipement : Les équipements ou « tools » en anglais correspondent aux machines de traitement des différentes opérations du processus de fabrication.

- Parc d'équipements: Un parc d'équipements ou « toolset » en anglais est un ensemble d'un ou plusieurs équipements ayant des caractéristiques similaires.

- *Usage* : Un regroupement de parcs d'équipements selon leur utilisation *i.e.* un niveau plus agrégé qu'un parc d'équipements.

- Recette : Une recette est l'ensemble des instructions nécessaires pour effectuer un step du processus de fabrication sur un parc d'équipements. On trouve plusieurs parcs d'équipements pouvant effectuer la même recette. On dit qu'ils sont qualifiés pour la recette.

La relation et l'interaction entre les différentes entités présentées sont illustrées dans la figure 1.4. Cette figure montre l'exemple d'une route composée de n opérations. Chaque opération comporte un certain nombre de steps par exemple l'opération 1 se compose de 4 steps. Chaque step est associé à une recette et un parc d'équipements. Chaque parc d'équipements est qualifié pour différentes recettes par exemple le parc d'équipements  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  et  $Station\ B$  est qualifié pour les recettes  $Station\ B$  est  $Station\ B$  est qualifié pour les recettes  $Station\ B$  est qualifié po

| Opération        | Step     | Parc d'équipements | Recette |

|------------------|----------|--------------------|---------|

| Lancement du lot |          |                    |         |

| Opération 1      | Step 1.1 | Station A          | Rec. A1 |

|                  | Step 1.2 | Station B          | Rec. B1 |

|                  | Step 1.3 | Station C          | Rec. C1 |

|                  | Step 1.4 | Station D          | Rec. D1 |

| Opération 2      | Step 2.1 | Station B          | Rec. B2 |

|                  | Step 2.2 | Station C          | Rec. C1 |

| Opération 3      | Step 3.1 | Station E          | Rec. E1 |

|                  | Step 3.2 | Station B          | Rec. B3 |

|                  | Step 3.3 | Station D          | Rec. D2 |

|                  |          |                    |         |

| Opération n      | Step n.1 | Station C          | Rec. C2 |

|                  | Step n.2 | Station A          | Rec. A2 |

| Livraison du lot |          |                    |         |

Figure 1.4 – Exemple d'une route.

#### 1.2.3 Classification du système de production des semi-conducteurs

Les systèmes de production peuvent être classés selon différents critères. Ils peuvent être regroupés dans des classes en fonction du type de production, volume de produc-

#### Chapitre 1. Contexte industriel et problématique

tion, flux de production et niveau d'automatisation. Le tableau 1.1 résume les principales classifications des systèmes de production en se basant sur la revue de la littérature (par exemple Groover [69], Zarembra et al. [184]). L'environnement industriel, auquel nous sommes intéressés dans cette étude, fait partie de la classe des systèmes de production caractérisée par une forte variabilité (High mix en anglais), un faible volume, des ateliers job shop, des flux ré-entrants et de très haut niveau d'automatisation. Ces caractéristiques sont mises en évidence en gras et italique dans le tableau 1.1.

#### 1.2.4 Complexité de la production dans le secteur de la microélectronique

Dans une unité de fabrication de semi-conducteurs (ou « wafer fab » 4 en anglais), il y a plusieurs facteurs qui en font un environnement particulièrement difficile à gérer (cf. [37], [70], [124], [125], [167], [168]).

#### Des flux ré-entrants

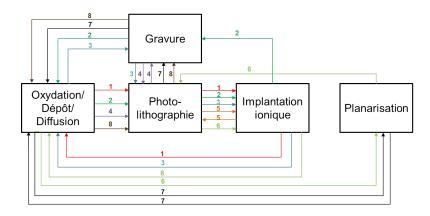

Dans le système de fabrication des semi-conducteurs, le produit est réalisé par des traitements sur des couches successives. La réalisation de chaque couche nécessite l'exécution de plusieurs steps individuels (photolithographie, gravure, etc.). De plus, plusieurs de ces steps sont répétés plusieurs fois. Les équipements utilisés pour les exécuter sont coûteux et ne sont donc pas multipliés dans les ateliers. Ainsi, les lots doivent passer plusieurs fois sur le même équipement au cours de son processus de fabrication. Les systèmes de fabrication dans lesquels les lots doivent visiter à plusieurs reprises les mêmes équipements à des étapes différentes de la gamme opératoire sont appelés lignes ré-entrantes [99]. Un exemple de flux ré-entrant est présenté en figure 1.4. On remarque que le parc d'équipements Station B est utilisé plusieurs fois. Ce dernier a traité les steps 1.2, 2.1 et 3.2. Un diagramme des flux illustrant une séquence typique du processus de fabrication des semi-conducteurs est schématisé dans la figure 1.5. Les chiffres sur les arcs représentent le numéro du flux parcouru par une plaque. Dans cet exemple particulier, l'oxydation est répétée six fois (flux 1, 2, 3, 6, 7 et 8) et la photolithographie quatre fois (flux 3, 4, 5 et 6).

La principale conséquence du caractère ré-entrant est que des wafers à différents stades du processus de fabrication sont en compétition pour le même équipement. Par conséquent, les plaques passent une grande partie de leur temps soit en attente d'un équipement, soit dans une activité de transport entre deux opérations, au lieu d'être effective-

<sup>4.</sup> Usine de fabrication des plaques électroniques.

**Tableau 1.1** — Classification des systèmes de production

| Critère de classification | Types                                                     | Caractéristiques                                                                                                                                             |

|---------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ıction                    | Production à faible volume                                | Gamme de production (1 à 100 unités/an), des ateliers de type $Job\ shop$                                                                                    |

| Volume de production      | Production à moyen volume                                 | Gamme de production (100 à 10000 unités/an), la complexité augmente avec l'augmentation du $mix$ produit                                                     |

|                           | Production à volume élevé                                 | Gamme de production (10000 à des millions d'unités/an), production de masse                                                                                  |

|                           | Job Shop                                                  | Différents $jobs$ réalisés sur différents équipements, la séquence des $jobs$ est prédéfinie                                                                 |

| uo                        | $egin{array}{ll} Production & par \\ batch & \end{array}$ | La variété des produits est très importante, des batches pour chaque type de produit, et la plupart du temps des ordres répétés                              |

| Flux de production        | Production de masse / Flow shop                           | Volume élevé de produits, conception stable et demande exigée des produits, ordre de passage unique pour tous les <i>jobs</i> sur les différents équipements |

|                           | Production à forte variabilité (High mix)                 | Mix produit élevé, système de production flexible, production à la commande                                                                                  |

|                           | Flux ré-entrants                                          | La séquence des opérations est répétée plusieurs<br>fois durant le processus de fabrication                                                                  |

| Niveau d'automatisation   | Manuel                                                    | Toutes les tâches sont effectuées par des opérateurs                                                                                                         |

|                           | Semi-automatisé                                           | Combinaison entre des tâches manuelles et des<br>tâches automatisées, par exemple les lignes d'as-<br>semblage                                               |

|                           | $Automatis \'e$                                           | Manutention robotisée (Automatic Material Handling Systems), transfert inter-cellulaire automatisé                                                           |

${\bf Figure} \ \ {\bf 1.5} - {\rm Mod\`{e}le \ simplifi\'e \ d'un \ flux \ r\'e-entrant \ dans \ l'industrie \ des \ semi-conducteurs. }$

ment traitées sur un équipement. Cette caractéristique principale engendre des problèmes de planification difficiles à gérer dans la pratique et intraitables sur le plan théorique [99].

#### Diversité des produits

Les fabs peuvent être classées en low-mix ou high-mix selon le nombre de produits différents. Dans les fabs low-mix, les équipements peuvent être dédiés aux produits, tan-dis que dans les fabs high-mix, le même équipement doit être partagé par de nombreux produits de diverses technologies, c'est-à-dire nécessitant une configuration et des temps de process différents.

Dans cette étude, nous nous intéressons aux fabs high-mix où la planification de production est plus complexe.

#### Multiplicité des opérations

Le processus de fabrication des semi-conducteurs est composé d'environ 250 opérations par produit. Chaque opération comporte entre 400 et 800 *steps* (nettoyage, processus, mesure).

#### Hétérogénéité des opérations

Dans une usine de fabrication de semi-conducteurs typique, il y a des dizaines de flux de production pour lesquels le « mix »  $^5$  produit évolue au fil du temps [125]. En outre, selon la nature des opérations, le temps de process des steps varie de manière significative. Certains steps de processus nécessitent 15 minutes ou moins pour traiter un lot tandis que d'autres demandent plus de 12 heures de temps de process. Les longs steps, représentant le tiers des opérations dans la fab, se réalisent par batch où plusieurs lots sont traités

simultanément.

#### Différents modes opératoires

Certains steps sont effectués sur des plaques individuelles, d'autres sur des groupes de plaques (lots), et d'autres encore sur des groupes de lots (batches). Un lot est composé généralement de 25 plaques, tandis qu'un batch typique contient jusqu'à six lots. Dans tous les cas, les plaquettes sont transportées par lot dans des caissons de protection en plastique appelés « FOUP » (Front-Opening Unified Pod) pouvant contenir jusqu'à 25 plaquettes (cf. figure 1.6). Le transfert des FOUPs entre les différents ateliers est réalisé manuellement ou avec des systèmes automatisés appelés « AMHS » (Automatic Material Handling Systems).

Figure 1.6 – Un lot de 25 plaquettes dans un FOUP.

#### Longueur du temps de cycle

Le temps de cycle est le temps écoulé entre le moment où un lot de wafers entre à l'usine de fabrication et le moment où il sort. En général, le temps de cycle de fabrication d'un lot est de l'ordre de 7 à 8 semaines. Il est composé d'un temps d'attente devant les équipements et d'un temps de process.

#### Variabilité du processus de fabrication

Le processus de fabrication des semi-conducteurs est caractérisé par une forte variabilité due à plusieurs facteurs, parmi lesquels on cite :

• Les arrêts des équipements, prévus et imprévus, conduisant à une faible disponibilité des équipements en comparaison avec les autres industries de production de masse.

<sup>5.</sup> Mot anglais utilisé dans le secteur de microélectronique exprimant la complexité de l'en-cours de production liée à la variété des produits et des technologies et la demande du marché.

#### Chapitre 1. Contexte industriel et problématique

- La réentrance des flux aboutissant à une grande variabilité dans les arrivées des lots aux parcs d'équipements.

- Le fonctionnement par *batch* qui résulte en une augmentation de la variabilité des temps d'inter-arrivées des lots aux parcs d'équipements traitant les opérations ultérieures.

- Le mix produit dû à la diversité des routes et des processus de fabrication.

Les quatre facteurs présentés contribuent ensemble à une variation importante des temps d'inter-arrivées et des temps opératoires des lots. Ainsi, le processus de fabrication des circuits intégrés est caractérisé par une variabilité du temps de cycle.

#### Diversité des caractéristiques des équipements

Une wafer fab est composée de plus d'une centaine d'équipements organisés en ateliers de fabrication. Chaque atelier est composé de groupements d'équipements identiques, parallèles et qui exécutent des opérations similaires, formant un parc d'équipements. Chaque parc d'équipements possède généralement ses propres caractéristiques selon le débit de production, le temps de processus ou de réglage, la taille de lot, la configuration, etc. Certains équipements ont d'importants temps de setup dépendant de la séquence telles que les implanteurs ioniques, tandis que d'autres n'en ont pas.

Selon le mode opératoire, les parcs d'équipements peuvent se diviser en deux types, ceux fonctionnant en série et d'autres fonctionnant par *batch*. Les équipements fonctionnant en série traitent les plaques une par une, alors que ceux fonctionnant par *batch*, utilisés pour les opérations de gravure et de traitement thermique, traitent plusieurs lots simultanément.

Le coût d'un équipement de fabrication des semi-conducteurs atteint 75% des coûts globaux d'investissement de l'usine [70]. Cela est dû principalement à la haute précision des équipements tels que les scanners pour la photolithographie qui valent jusqu'à 70 millions d'euros l'unité. Par conséquent, les équipements ne sont pas multipliés dans les ateliers de fabrication. Ainsi, l'utilisation des équipements présente une contrainte importante lors de la planification de production des semi-conducteurs.

#### Qualifications recette-équipement

La contrainte de qualification définit l'éligibilité d'un équipement à traiter un produit. La réalisation d'un process sur un équipement nécessite la qualification de la recette sur l'équipement considéré. À cause des caractéristiques matérielles et informatiques, les opérations ne peuvent pas être effectuées sur tous les équipements. Autrement dit, une

recette ne peut être appliquée que sur certains parcs d'équipements.

#### Multiple priorités des lots

Afin de maintenir la compétitivité et satisfaire les commandes clients urgentes, les industriels des semi-conducteurs définissent plusieurs niveaux de priorité des ordres de fabrication. Les priorités de production peuvent être divisées en trois niveaux selon l'urgence de livraison : haut, moyen et faible. Le traitement opérationnel doit respecter les ordres de priorité identifiés à priori.

#### Délais de livraison à respecter

Comme toute autre industrie, l'industrie des semi-conducteurs a pour objectif de répondre à l'une des attentes les plus importantes des clients : maximiser la livraison à temps *i.e.* minimiser les retards de livraison. En effet, si le fabricant ne peut pas répondre aux dates d'échéance de livraison prédéfinies, il pourrait être confronté à de fortes pénalités et éventuellement perdre ses clients. Afin d'évaluer la qualité d'un planning en termes de respect des dates d'échéance de livraison, plusieurs critères ont été utilisés tels que minimiser la somme des retards pondérés, minimiser le retard moyen, minimiser le nombre de tâches en retard, etc.

## 1.3 Planification de la production dans l'industrie des semi-conducteurs

La planification de la production est un processus de prise de décision qui joue un rôle important dans la plupart des industries manufacturières et de services. La fonction de planification vise à prévoir l'utilisation des ressources et l'exécution des *jobs* pour atteindre des objectifs déterminés. Les ressources peuvent être matérielles telles que les machines ou la matière première ou humaines *i.e.* le personnel du centre de travail. Les *jobs* peuvent être des opérations dans l'atelier ou des tâches (de maintenance ou de process) à effectuer. Chaque job peut avoir un niveau de priorité, une date de début au plus tôt et une date d'échéance de livraison. Les objectifs d'optimisation sont nombreux tels que la réduction du temps de cycle des *jobs*, la minimisation des retards, la maximisation de l'utilisation des ressources,... Le processus de planification prend en considération le contexte et les contraintes internes et externes connues actuellement ou prévisibles dans le futur.

Le rôle de la planification dans un environnement de fabrication est crucial. Les commandes des clients sont converties en *jobs* avec des dates d'échéance associées. Ces *jobs*

#### Chapitre 1. Contexte industriel et problématique

doivent souvent être réalisés sur les machines d'un centre de travail selon une séquence donnée. Le traitement des *jobs* peut être retardé si certaines machines sont occupées. Des événements imprévus, tels que les pannes de machines ou des temps de process plus longs que prévu, doivent également être pris en compte, car ils peuvent avoir un impact majeur sur le planning.

### 1.3.1 Niveaux de la planification de la production

Dès 1965, Anthony [2] a distingué trois niveaux de planification de la production selon la longueur de l'horizon de planification : le long terme (planification stratégique), le moyen terme (planification tactique) et le court terme (planification opérationnelle). La dimension temporelle diffère d'une industrie à une autre [170].

Le tableau 1.2 présente une description de chaque niveau de planification selon l'horizon temporel.

Tableau 1.2 – Niveaux de planification de la production selon l'horizon de planification

| Niveau de<br>planification  | Exemples                                                                                                                                                                                                                                                                           | Horizon           |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Long terme<br>(stratégique) | <ul> <li>Recherche de nouveaux partenaires industriels,</li> <li>Sélection des fournisseurs et sous-traitants,</li> <li>Ouverture, fermeture ou délocalisation des sites de production,</li> <li>Développement d'un nouveau produit,</li> <li>Configuration de l'usine,</li> </ul> | de 1 à 5 ans      |

| Moyen terme (tactique)      | Programme directeur de production, équilibrage de la charge des ressources                                                                                                                                                                                                         | de 3 à 6 mois     |

| Court terme (opérationnel)  | Ordonnancement, suivi des ateliers, règles de répartition                                                                                                                                                                                                                          | de 1 à 6 semaines |

Au niveau stratégique, les décisions prises se traduisent par une formulation à long terme de la politique de l'entreprise (vision sur plusieurs années). Ces décisions concernent la mise au point des installations de production (par exemple, la taille et l'emplacement de nouvelles usines, l'acquisition de nouveaux équipements ...) ou du processus de fabrication (développement d'un nouveau produit ou d'une nouvelle gamme de production ...). Le niveau stratégique fixe un cadre au niveau tactique.

Les décisions tactiques concernent l'organisation des produits et des ressources en fonction des prévisions commerciales et correspondent à un ensemble de décisions à moyen terme. À ce niveau, on retrouve notamment la planification de la production qui vise à

calculer un plan de production. Dans ce plan, les quantités à produire par période sont calculées de façon à répondre aux demandes au moindre coût. Ces décisions tactiques sont des directives pour la production détaillée et la planification au niveau opérationnel.

À court terme, les décisions opérationnelles consistent à gérer le fonctionnement quotidien des ateliers de fabrication. À ce niveau, les décisions opérationnelles concernent les volumes de production et les dates de passage par produit ou lot, l'utilisation détaillée de la capacité par parc d'équipements, etc.

Dans cette étude, nous nous intéressons à la planification de la production à moyen et court terme impliquant des décisions plus tactiques sur des périodes mensuelles ou hebdomadaires. Nous considérons la planification de la capacité de production qui consiste à estimer la capacité de production nécessaire pour satisfaire les commandes clients.

### 1.3.2 Objectifs de la planification de la production

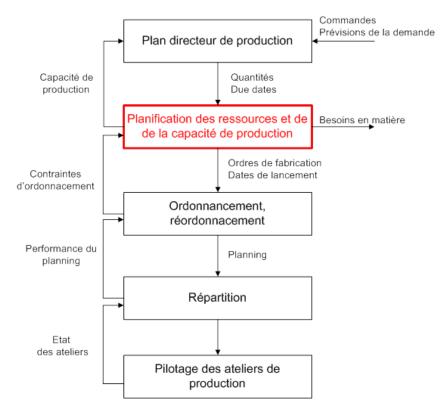

Planifier les activités et les ressources de production, en tenant compte de l'état des encours de production, les prévisions de la demande, et la capacité des ressources, est un objectif principal de la planification sur le niveau tactique. Les décisions, prises à ce propos, ont une incidence directe sur le processus de planification. La planification de la capacité de production est l'un des niveaux les plus critiques de la planification, car elle est le lien entre la planification stratégique et la planification opérationnelle. Elle est conduite, comme le montre la figure 1.7, par des décisions prises à moyen et court terme.

Les activités principales, à ce niveau de planification, sont la détermination des dates de début et de fin des tâches à exécuter et le calcul de la charge des ressources. La planification de la capacité de production doit interagir avec d'autres procédures de prise de décision utilisées dans l'usine. La figure 1.8 représente, de façon générale, le flux d'informations dans un système de fabrication [135].

A ce niveau de décision, il est courant de planifier dans les grandes lignes c'est-à- dire de ne pas prendre en compte certains détails qui complexifient trop la prise de décision. Ainsi, un ensemble de variables possédant des caractéristiques communes sont remplacées par une variable agrégée. Par exemple, les produits sont agrégés par familles, les ressources en grandes catégories . . . . L'agrégation des décisions permet de simplifier considérablement la formulation et la résolution des problèmes. Le plan de production ainsi obtenu est appelé plan agrégé. Cependant, ce plan doit être calculé de manière à être réalisable.

Généralement, parmi les objectifs des systèmes de planification de la production, on trouve la livraison à temps, la minimisation des encours de production, la réduction des temps de cycle et l'utilisation maximale des ressources. Cependant, ces objectifs peuvent être divergents, par exemple la satisfaction des délais de livraison peut être inconciliable avec la réduction des stocks ou le respect des contraintes de capacité. Le but de la pla-

Figure 1.7 – Flux d'information dans un système de fabrication [135].

nification de la capacité est de trouver un équilibre profitable entre ces objectifs contradictoires [80]. Il s'agit d'établir un planning de production réalisable respectant simultanément les capacités disponibles et les dates d'échéance de livraison en utilisant les équipements au plus près de leur charge maximale.

Les problèmes de planification ont été et sont encore largement rencontrés dans l'industrie des semi-conducteurs. Une attention particulière est portée sur les problèmes de planification de la capacité de production qui visent à déterminer un équilibrage entre la charge et la capacité de production. Nous allons donc présenter les caractéristiques des problèmes de planification ainsi que les techniques de planification utilisées pour les résoudre dans la suite de ce chapitre.

# 1.3.3 Caractéristiques des problèmes de planification de la production dans l'industrie des semi-conducteurs

#### 1.3.3.1 Contraintes

Comme mentionné ci-dessus, il s'avère que le processus de fabrication des semi- conducteurs est très complexe impliquant une grande variété de produits, un grand nombre d'opérations, un long temps de cycle, de multiples contraintes liées aux équipements, une

#### 1.1.3 Planification de la production dans l'industrie des semi-conducteurs

forte variabilité du processus de fabrication et une pénalité élevée en cas des retards de livraison. Ces caractéristiques rendent la planification de la production, au sein de cet environnement complexe, très difficile. En plus des contraintes issues du processus de fabrication des semi-conducteurs, on trouve les contraintes de capacité et la forte variabilité des temps de cycle.

#### 1.3.3.2 Indicateurs de performance

Un indicateur permet de mesurer de façon objective l'efficacité d'un dispositif mis en place : c'est un outil décisionnel synthétique, c'est-à-dire facile à établir et pratique à utiliser, facilitant le dialogue entre les utilisateurs ayant des cultures et des préoccupations différentes. Dans les *fabs* de semi-conducteurs, plusieurs indicateurs sont utilisés pour mesurer la performance. Le lecteur intéressé peut se référer à Montoya-Torres [126] pour plus de détails. Parmi les indicateurs de performance de la planification de la production les plus importants et les plus employés dans cette industrie, on cite :

#### Temps de cycle

Le temps de cycle de production, encore appelé temps de séjour ou délai de fabrication, est la durée totale nécessaire pour fabriquer un lot de *wafers*. Il mesure le temps écoulé entre le moment où le lot entre dans l'unité de fabrication et le moment où il sort.

Le temps de cycle inclut le temps opératoire, le temps de transfert entre les opérations, le temps d'attente devant les équipements et le temps d'attente pour les transferts. Dans la plupart des wafer fabs, un lot de wafers peut passer entre 50% et 90% de son temps de cycle en attente d'un équipement ou d'un transfert [126]. Le temps de cycle est une mesure de la capacité requise par la fab pour délivrer ses produits à temps. Généralement, une réduction du temps de cycle implique une augmentation de la satisfaction des clients. Les entreprises, dont la fabrication s'effectue avec des temps de cycle courts, sont capables de lancer souvent de nouveaux produits, de pénétrer plus rapidement de nouveaux marchés, de réagir plus efficacement aux changements de la demande et de délivrer à temps leurs produits.

Dans l'industrie des semi-conducteurs, le *X-factor*, représentant le rapport entre temps de cycle total et le temps total de process [114], est plus employé que le temps de cycle comme indicateur de performance. Avec cet indicateur, l'objectif recherché est d'avoir un X-factor le plus proche possible de l'unité. Cela impose une diminution de la moyenne et de la variance du temps de cycle.

#### Chapitre 1. Contexte industriel et problématique

#### Niveau d'encours de production

Le niveau d'encours (Work-In-Progress, WIP) est défini comme le nombre de wafers de production se trouvant dans la fab à un instant donné. Le nombre de wafers pris en compte est aussi bien sur une activité de production que sur une activité de non-production (transport et attente des lots). Les encours représentent du capital immobilisé dans les ateliers, donc trop d'encours diminue la trésorerie disponible.

#### Débit du système ou throughput rate

Le débit du système, appelé « throughput rate », est défini comme le nombre de wafers finis qui sortent de la fab par période. Cet indicateur indique le niveau de saturation ou d'utilisation du système i.e. il permet de savoir si le système est stable, c'est-à-dire s'il n'y a pas d'accumulation de produits à certaines positions dans le système.

#### Niveau de service

Dans le cadre de la fabrication des *wafers*, des indicateurs de performance importants sont des objectifs liés aux dates d'échéance de livraison pour mesurer le niveau de service offert au client (interne ou externe).

# 1.3.4 Techniques de planification de la production dans l'industrie des semi-conducteurs

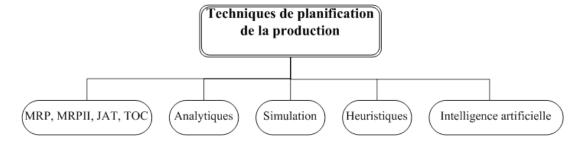

Les techniques industrielles de planification de la production peuvent être réparties en : (cf. figure 1.8)

- Techniques classiques : MRP, MRPII, JIT et TOC

- Modèles analytiques

- Modèles de simulation

- Heuristiques

- Techniques basées sur l'intelligence artificielle

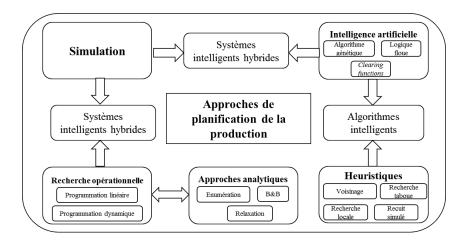

Souvent, ces techniques de résolution sont combinées pour fournir des solutions plus complètes, voir figure 1.9.

#### 1.3.4.1 Les techniques classiques

Parmi les techniques industrielles de planification de la production les plus classiques et les plus répandues, on trouve la technique Material Requirement Planning (MRP) introduite par Orlicky en 1975 [130] qui permet de calculer les besoins en composants sans

Figure 1.8 – Classification des techniques industrielles de planification de la production.

Figure 1.9 – Relation entre les approches de planification de la production.

capacité et son évolution, la technique Manufacturing Resource Planning (MRPII) développée par Wight en 1981 [176] qui intègre un système ajustant les niveaux de capacité. Ces techniques permettent de générer des plans de production sur la base des commandes d'entrée au système. Le concept principal de la méthode MRP, dans la génération de ces plans, est de considérer un temps de cycle fixe (ou lead time en anglais) et une capacité infinie des machines.

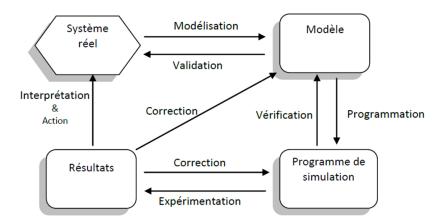

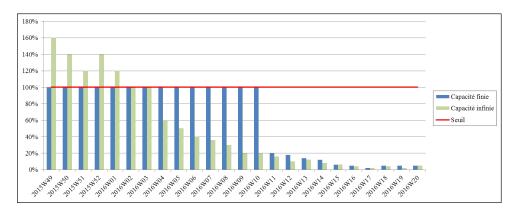

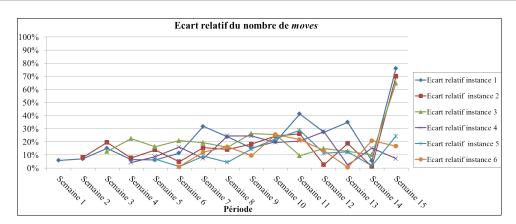

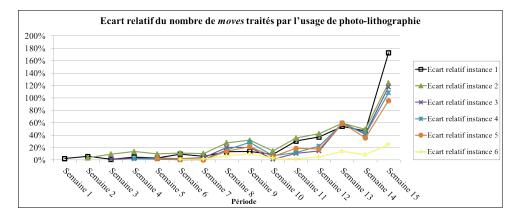

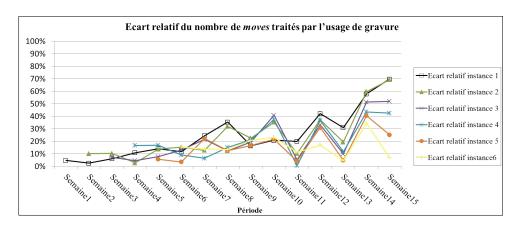

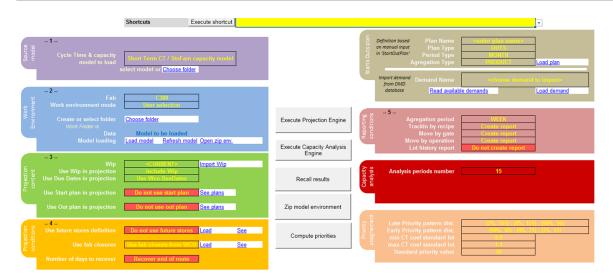

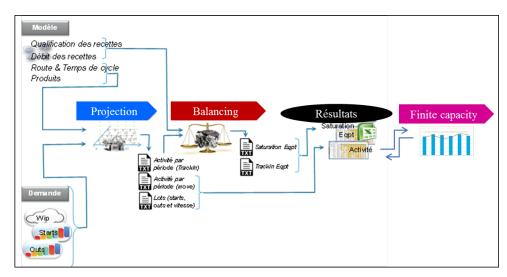

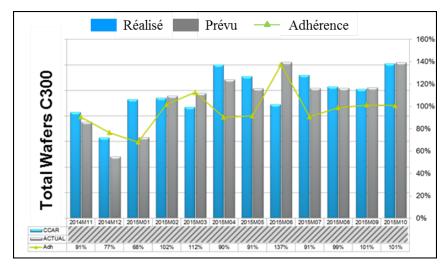

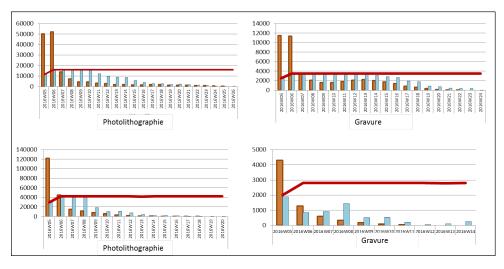

L'application de ces techniques traditionnelles pour la planification des capacités dans l'industrie des semi-conducteurs présente ainsi certaines limitations. En effet, il est prouvé que la méthode MRP est inefficace. Elle peut provoquer des problèmes de types retards de livraison ou stocks d'en-cours et produire des plannings de production irréalisables lors-qu'elle est appliquée à l'industrie des semi-conducteurs vu qu'elle ne tient pas compte des contraintes de capacité et suppose que les temps de cycle sont fixés [17, 161]. Cependant, dans les installations de semi-conducteurs, les temps de cycle dépendent de nombreux facteurs, tels que le taux d'utilisation des équipements, la taille du lot, les volumes de stock et les règles de répartition, et sont donc variables.