# Design characterization and implementation of an integrated CMOS driver circuit for GaN components

Van-Sang Nguyen

#### ▶ To cite this version:

Van-Sang Nguyen. Design characterization and implementation of an integrated CMOS driver circuit for GaN components. Electric power. Université Grenoble Alpes, 2016. English. NNT: 2016GREAT067. tel-01485856

### HAL Id: tel-01485856 https://theses.hal.science/tel-01485856

Submitted on 9 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Génie Electrique

Arrêté ministériel: 7 août 2006

Présentée par

#### Van-Sang NGUYEN

Thèse dirigée par Jean-Christophe CRÉBIER et

Co-encadrant par Pierre LEFRANC

préparée au sein du Laboratoire de Génie Electrique de Grenoble (G2ELab)

dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal (EEATS)

## Conception, caractérisation et mise en œuvre d'un circuit intégré type driver en CMOS pour composants GaN

Thèse soutenue publiquement le **«08/12/2016»**, devant le jury composé de :

M. Bruno ALLARD

Professeur à l'INSA de Lyon, Président

M. Eric LABOURÉ

Professeur à l'Université Paris Sud, Rapporteur

M. Stéphane LEFEBVRE

Professeur au CNAM, Rapporteur

Mme. Radoslava MITOVA

Ingénieure Recherche, Schneider-Electric, Examinatrice

M. Pierre LEFRANC

Maitre de conférences à Grenoble-INP, Co-Encadrant

M. Jean-Christophe CRÉBIER

Directeur de recherche au CNRS, Directeur de thèse

#### Ph.D THESIS

To acquire the degree of

#### DOCTOR AT THE UNIVERSITY OF GRENOBLE ALPES

Major: Electrical Engineering

Ministerial law from: August 7th 2006

Presented by

#### Van-Sang NGUYEN

Thesis supervised by **Jean-Christophe CRÉBIER** and Co-supervised by **Pierre LEFRANC**

Prepared at **Grenoble Electrical Engineering Laboratory** (G2ELab)

Under the **Doctoral School of Electronics**, **Electrical Engineering**, **Automatics and Signal Treatment (EEATS)**

# Design, characterization and implementation of an integrated CMOS gate driver circuit for GaN components

#### M. Bruno ALLARD

Professor at INSA-Lyon, President

#### M. Eric LABOURÉ

Professor at Paris-Sud University, Reviewer

#### M. Stéphane LEFEBVRE

Professor at CNAM, Reviewer

#### **Mme. Radoslava MITOVA**

Researcher at Schneider-Electric, Member

#### M. Pierre LEFRANC

Associate Professor at Grenoble-INP, Co-supervisor

#### M. Jean-Christophe CRÉBIER

Senior Scientist at CNRS, Supervisor

#### Acknowledgements

#### (Remerciements)

Finalement, Je suis très honoré d'avoir pu aboutir à la fin de mes travaux de thèse (financé par BPI France et OSEO – Projet MEGaN), ont été réalisée au sein du laboratoire G2ELab, Université Grenoble Alpes.

Tout d'abord, Je tiens à remercier le premier lieu Monsieur Stéphane LEFEBVRE et Monsieur Éric LABOURE pour avoir accepté d'être rapporteur de ma thèse. Je vous remercie pour le temps que vous avez passé sur ce manuscrit et aussi pour les commentaires, les remarques constructives que vous avez portées à amélioration mes travaux de thèse.

Un grand merci à Monsieur Bruno ALLARD qui m'a fait l'honneur d'être le président de mon jury. Je remercie également Madame Radoslava MITOVA d'avoir participé au jury en tant qu'invité industriel. Merci pour vos questions, vos échanges et vos propositions pour améliorer notre travail dans le cadre du projet MEGaN.

Un grand merci à Pierre LEFRANC de m'avoir beaucoup aidé pendant tous ces 3 ans de thèse. Sans toi, Je n'aurais certainement pas pu arriver à la fin de cette thèse. C'est toujours agréable et c'est toujours un grand plaisir de travailler avec toi.

Un merci tout particulier à Jean-Christophe CREBIER. Je te remercie tout d'abord de m'avoir proposé venir en France pour faire un post-master ensuit la thèse. Tes qualités scientifiques, tes passions pour la recherche m'ont beaucoup inspiré dans ma vie de recherche. Je suis très fier d'être ton dixième doctorant vietnamien, peut-être c'est le dernier, malheureusement. Tu es toujours très spécial dans nos sentiments des anciens élèves vietnamiens du G2ELab.

Je voudrais adresser mes remerciements aux doctorants de l'équipe électronique de puissance du G2ELab qui ont travaillé avec moi dans les projets collaboratifs comme Duc, Long, Farshid et Davy. Un grand merci à Nicolas ROUGER pour m'avoir aidé dans la troisième année de thèse pour la suite du travail de Duc TO. Je remercie aussi les partenaires du projet MEGaN, en particulier les personnels du WP3 : ID-MOS, CEA-LETI, Laboratoire AMPERE.

Je souhaite ensuite remercier la direction ainsi que le personnel administratif, technique, financière et informatique du G2ELab qui m'a réglé des problèmes divers.

Un merci sincère à tout personnel du CIME-Nanotech que J'ai eu la chance de travailler avec. Merci Alejandro CHAGOYA, Irène PHENG pour m'avoir aidé pendant les périodes de dimensionnements et caractérisations des circuits intégrés.

Je voudrais aussi remercier mes collègues du laboratoire, et mes amis internationaux, français, vietnamiens d'avoir partagé avec moi des moments de convivialité et d'amitié dans la vie professionnel et aussi dans la vie quotidien pendant tous ces années.

Un merci particulier à ma famille pour m'avoir soutenu tout au long de ces années d'études en France, merci à ma mère et ma belle-mère. J'ai une pensée très forte pour mon père, qui a décédé depuis 7 ans mais son esprit est toujours avec moi et me renforce dans tous moments.

Pour finir, Merci Lory et Quynh, elles illuminent ma vie quotidienne.

Merci encore à vous pour tout!

## **Contents**

| Contents                                                                                           | i    |

|----------------------------------------------------------------------------------------------------|------|

| List of Acronyms                                                                                   | vii  |

| List of Figures                                                                                    | ix   |

| List of Tables                                                                                     | xvii |

| General Introduction                                                                               | 1    |

| Chapter I                                                                                          | 3    |

| Gate driver circuit for high speed power devices with improved EMI management environment:         |      |

| Introduction and motivations                                                                       | 3    |

| Abstract                                                                                           | 5    |

| I.1 The sate-of-art of the wide-band gap power components and the challenges for drivers           | _    |

| I.1.a New specifications of the wide-band gap devices                                              | 6    |

| I.1.b Challenges for the design of the gate drivers in the context of GaN power devices.           | 9    |

| I.1.c MEGaN (Module Electronique GaN) Project                                                      | 11   |

| I.2 The need of EMI management on the driver circuitry with the evolution of high spe              | _    |

| I.2.a The EMI problems on the driver circuit                                                       | 12   |

| I.2.a-i EMI in general: source, propagation and reception                                          | 12   |

| I.2.a-ii How does the conducted EMI in common-mode impact on the driver circuit? .                 | 16   |

| I.2.a-iii Conducted EMI problems with high speed power devices                                     | 18   |

| I.2.b Solutions for the conducted EMI problems on the gate driver circuit                          | 21   |

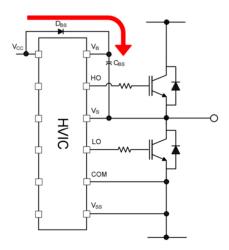

| I.2.b-i At system level for a low side – high side configuration                                   | 22   |

| I.2.b-ii At component level                                                                        | 24   |

| I.2.b-iii Perspective for the complex configurations                                               | 24   |

| I.2.c Side issues                                                                                  | 25   |

| I.2.c-i Thermal considerations of the proposed architecture                                        | 25   |

| I.2.c-ii The need of redesign the elements of the new architecture gate driver for h power devices | •    |

| I.3 Gate driver for high speed power devices with improved EMI management environments             |      |

| I.3.a Today solutions of the gate driver for WBG devices                                           | 27   |

| I 3 b Driver circuit elements of a novel gate driver for high speed devices                        | 32   |

| I.4 General research orientation – Thesis overview                                                 | 34 |

|----------------------------------------------------------------------------------------------------|----|

| Chapter II                                                                                         | 37 |

| Gate Driver Architectures                                                                          | 37 |

| Abstract                                                                                           | 39 |

| II.1 Introduction to gate driver architectures                                                     | 40 |

| II.1.a Gate driver architecture for a high side – low side configuration: a reminder               | 40 |

| II.1.b Power devices in series connection: expectation on the gate driver circuitry was management |    |

| II.2 Design and analysis of an innovative gate driver architecture                                 | 42 |

| II.2.a Proposed gate driver architecture from the conducted EMI point-of-view                      | 42 |

| II.2.b High frequency equivalent circuit of gate driver architectures                              | 43 |

| II.2.c Simulation comparisons of the conventional and the proposed architectures                   | 48 |

| II.2.d Improved proposed gate driver architecture for the EMI management                           | 53 |

| II.2.e Compromised solution                                                                        | 54 |

| II.3 Experimental validations of a high side – low side configuration's gate driver                | 55 |

| II.3.a Set-up for measuring the conducted EMI common mode current                                  | 55 |

| II.3.b Experimental Results                                                                        | 57 |

| II.3.c Comparison of the switching speed of the power devices                                      | 61 |

| II.4 Recommendations for the design of HF power modules with high dv/dt and in environment         |    |

| II.4.a Recommendations for the locations of the elements of the gate driver circuitry              | 62 |

| II.4.b Two options for the high side power supply of the gate driver circuit                       | 63 |

| II.5 Expectations on the gate driver architectures for the power devices in series co-             |    |

| II.5.a High voltage and high speed system with WBG devices in series                               | 64 |

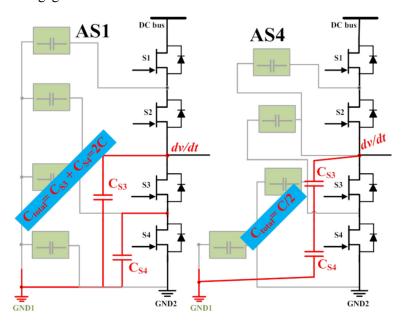

| II.5.b The architectures of the gate driver (AS1 - AS2 - AS3 - AS4)                                | 65 |

| II.5.b-i The conventional gate driver architecture (AS1)                                           | 65 |

| II.5.b-ii The proposed solutions of the gate driver architecture (AS2 – AS3 – AS4)                 | 65 |

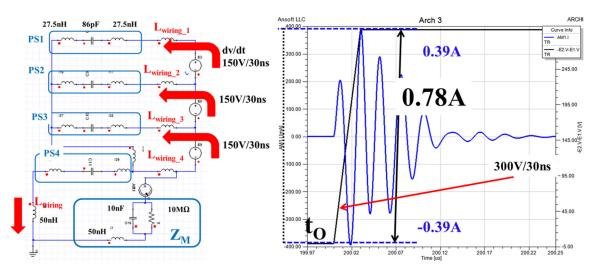

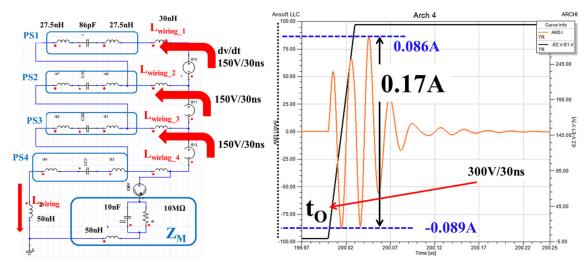

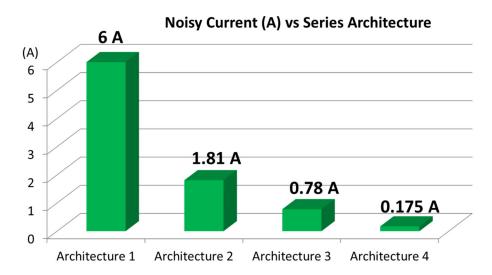

| II.5.c Simulation comparison for 4 architectures (AS1 - AS2 - AS3 - AS4)                           | 69 |

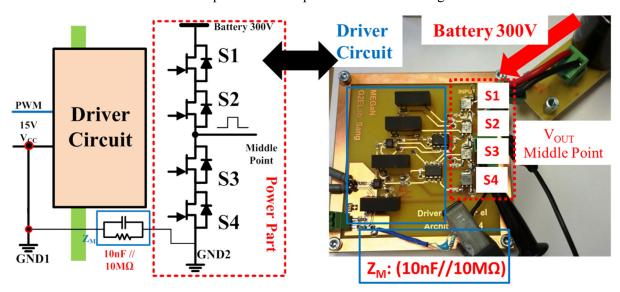

| II.5.d Experimental results for 2 extreme architectures: AS1 and AS4                               | 72 |

| II.5.e Comparison the switching speeds of the power devices in AS1 and AS4                         | 74 |

| II.6 Conclusions and perspectives                                                                  | 76 |

| Chapter III                                                                                        | 77 |

| Redesign The Elements                                                                              | 77 |

| Of Gate Driver Circuitry:                                                                      | 77  |

|------------------------------------------------------------------------------------------------|-----|

| High Temperature ASICs For High dv/dt                                                          | 77  |

| Abstract                                                                                       | 80  |

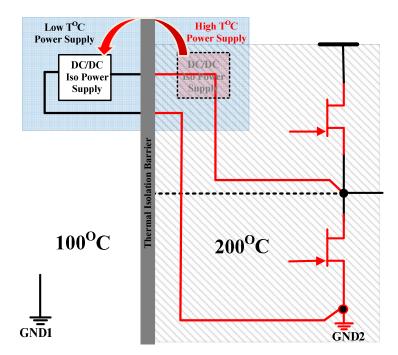

| III.1 Introduction of the high side power supply of the gate driver                            | 81  |

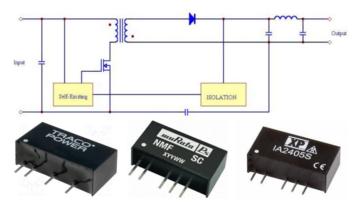

| III.1.a Solutions for the high side power supply of the gate driver                            | 81  |

| III.1.b Specifications of the isolated high side power supply of the gate driver               | 85  |

| III.1.c DC-DC isolated converter as the most suitable technique                                | 86  |

| III.2 DC-DC isolated converter topologies for the high side power supply                       | 87  |

| III.2.a Criteria for the topology's selection                                                  | 87  |

| III.2.b A brief comparison of the isolated topologies                                          | 88  |

| III.2.b-i Isolated flyback converter                                                           | 88  |

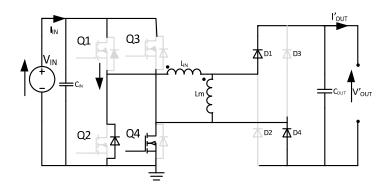

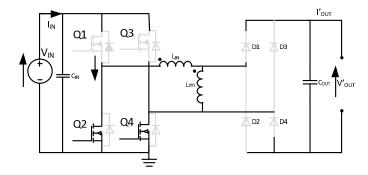

| III.2.b-ii Half Bridge and Full Bridge converters                                              | 89  |

| III.2.b-iii LLC resonant half bridge converter                                                 | 90  |

| III.2.b-iv Dual Active Bridge converter (DAB)                                                  | 91  |

| III.2.b-v Single Active Bridge converter (SAB).                                                | 92  |

| III.2.c The selected topology: the SAB converter (SAB)                                         | 94  |

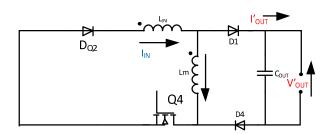

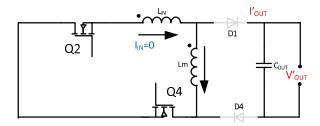

| III.2.c-i Operating principle of SAB                                                           | 94  |

| III.2.c-ii Design calculations                                                                 | 97  |

| III.2.d Validation of SAB converter                                                            | 101 |

| III.2.d-i Simulations                                                                          | 101 |

| III.2.d-ii Experiments                                                                         | 103 |

| III.3 Integrated high side power supply for high temperature                                   | 106 |

| III.3.a High temperature technology for the active elements of the power supply                | 107 |

| III.3.b Design of the integrated H-bridge of the SAB converter                                 | 108 |

| III.3.c Design the integrated rectifier.                                                       | 112 |

| III.3.c-i The intrinsic-diode rectifier                                                        | 112 |

| III.3.c-ii The synchronous rectifier                                                           | 113 |

| III.3.d Characterization of the active part of the SAB converter                               | 118 |

| III.4 Isolated signal transfer unit for very high switching speed and high temperature devices | _   |

| III.4.a Approach towards the integrated circuit complying with application constraints         |     |

| III.4.b Integration approach of the isolated signal transfer unit                              |     |

| III.4.b-i Integrated coreless transformer                                                      |     |

| III 4 b-ii Current source level-shifter and ontical transmissions                              | 128 |

| III.4.c Comparison between the three techniques                                                 | 128 |

|-------------------------------------------------------------------------------------------------|-----|

| III.5 Conclusions and perspectives                                                              | 129 |

| Chapter IV                                                                                      | 131 |

| Implement An Integrated Gate Driver                                                             | 131 |

| Work Package 3 – MEGaN Project                                                                  | 131 |

| Abstract                                                                                        | 133 |

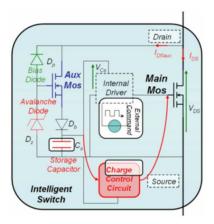

| IV.1 Generic Blocks of Gate Driver                                                              | 134 |

| IV.1.a Gate Driver Tasks                                                                        | 134 |

| IV.1.b The specifications of the gate driver                                                    | 134 |

| IV.1.c Configuration of the generic integrated blocks.                                          | 136 |

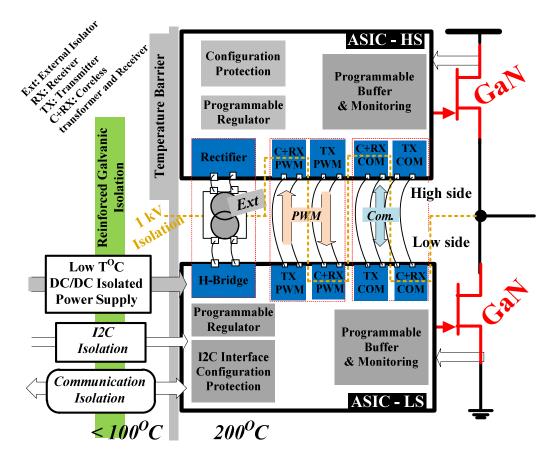

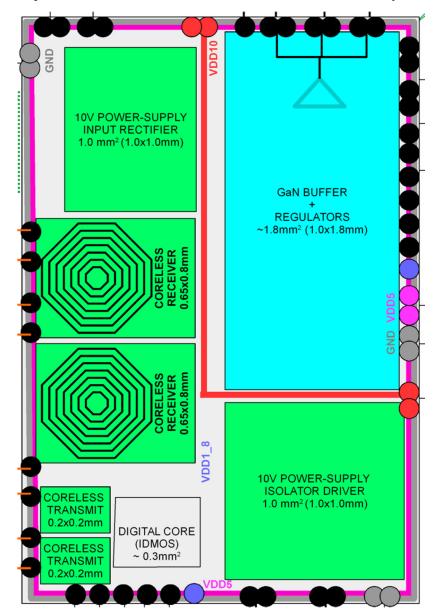

| IV.2 Final ASIC                                                                                 | 137 |

| IV.2.a Main features of the ASIC                                                                | 137 |

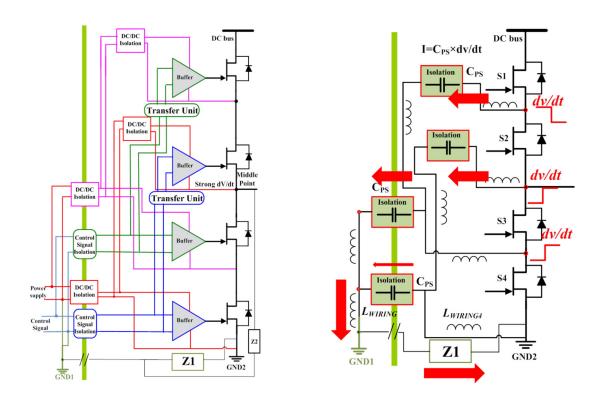

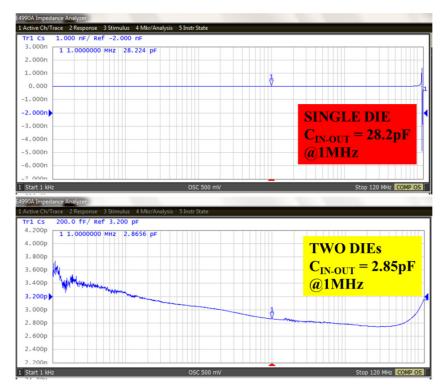

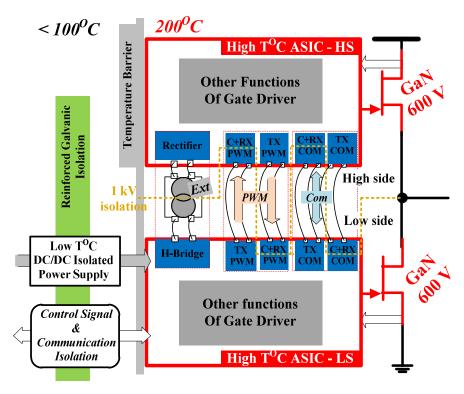

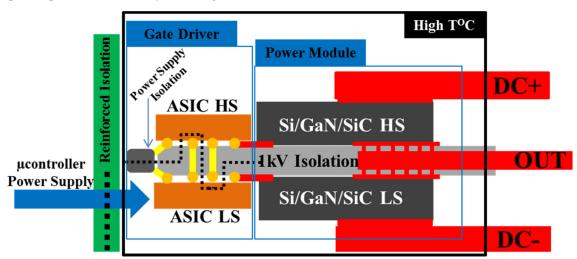

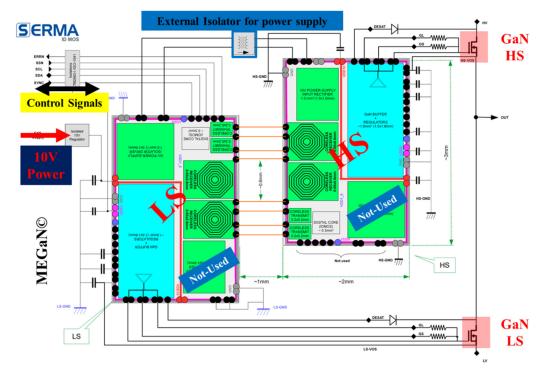

| IV.2.b Gate driver architecture with ASICs                                                      | 140 |

| IV.3 Conclusion and perspectives                                                                | 142 |

| General Conclusions and Perspectives                                                            | 145 |

| Chapter V                                                                                       | 151 |

| Résumé en français                                                                              | 151 |

| V.1 Introduction et motivations: circuit de pilotage pour les composants avec forte commutation |     |

| V.1.a Etat de l'art et objectifs du projet                                                      | 153 |

| V.1.b Deux approches proposées                                                                  | 154 |

| V.2 Architectures du gate driver pour un bras d'onduleur                                        | 155 |

| V.2.a Architecture classique                                                                    | 155 |

| V.2.b Architecture proposée                                                                     | 156 |

| V.2.c Validations                                                                               | 156 |

| V.2.d Recommandations de la conception du gate driver pour composant GaN                        | 157 |

| V.3 Dimensionnements des nouveaux circuits du gate driver                                       | 158 |

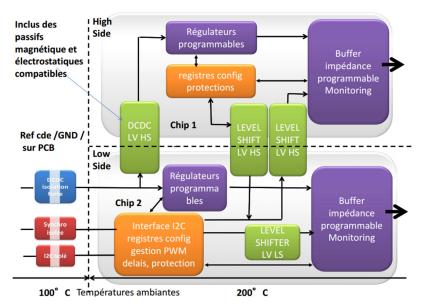

| V.3.a Synoptique du gate driver MEGaN                                                           | 158 |

| V.3.b Validations expérimentales des puces de test                                              | 158 |

| V.4 Mise en œuvre d'un gate driver intégré sous la forme d'un ASIC                              | 159 |

| V.5 Conclusions                                                                                 |     |

| Publications                                                                                    |     |

|                                                                                                 |     |

| References                                                                                      | 163 |

| Appendix A: Design the gate driver circuit of integrated H-Bridge of the SAB converter b |

|------------------------------------------------------------------------------------------|

| Appendix B: The calculations of synchronous rectifier of the SAB converter               |

| Appendix C: Signal transfer units: current source level-shifter and optical transmission |

## **List of Acronyms**

Si Silicon

WBG Wide Band Gap

GaN Gallium Nitride

GaN HEMT Gallium Nitride High-Electron-Mobility Transistor

SiC Silicon Carbide

MOSFET Metal Oxide Semiconductor Filed Effect Transistor

IGBT Insulated Gate Bipolar Transistor

BJT Bipolar Junction Transistor

SCR Silicon Controlled Rectifier

GTO Gate Turn-Off Transistor

IEGT Injection Enhanced Gate Transistor

UPS Uninterruptible Power Supply

HVDC High-Voltage Direct Current

FACT Flexible Alternating Current Transmission

SMPS Switching Mode Power Supply

EMI Electro-Magnetic Interference

EMC Electro-Magnetic Compatibility

CMTI Common Mode Transient Immunity

LS Low Side

HS High Side

HT High Temperature

HF High Frequency

HEV / EV Hybrid Electric Vehicle / Electric Vehicle

EMRC Electro Magnetic Resonance Coupler

DAB Dual Active Bridge

SAB Single Active Bridge

MMC Modular Multi-Level Converter

PDK Process Design Kit

LTH Low-to-High (delay)

HTL High-to-Low (delay)

I2C Inter-Integrated Circuit (communication protocol)

TX Transmitter

RX Receiver

C+RX Coreless Transformer+ Receiver

Ext External Isolator (of the power supply)

COM Communication

PWM Pulse Width Modulation

AZS Auto-Zero-Skew

MEGaN Module Electronique GaN (Project)

## **List of Figures**

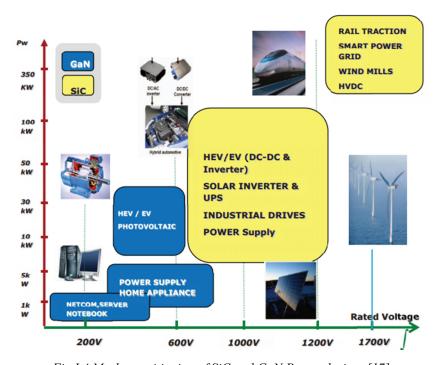

| Fig.I.1 Application areas of classical discrete power semiconductors [6]                                       | 6  |

|----------------------------------------------------------------------------------------------------------------|----|

| Fig.I.2 Simplified energy band of the semiconductor [8]                                                        | 7  |

| Fig.I.3 Overview of WBG devices in 2015 [16]                                                                   | 8  |

| Fig.I.4 Market positioning of SiC and GaN Power devices [17]                                                   | 8  |

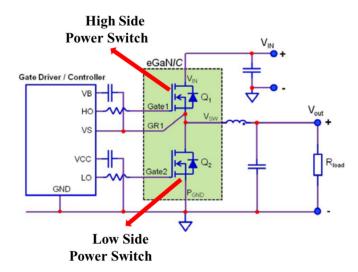

| Fig.I.5 A low side high side switching cells configuration, GaN EPC 2140 [19]                                  | 9  |

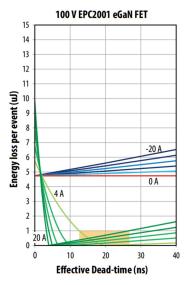

| Fig.I.6 Critical dead-time management of GaN EPC – 100V EPC2001 eGaN FET [20]                                  | 10 |

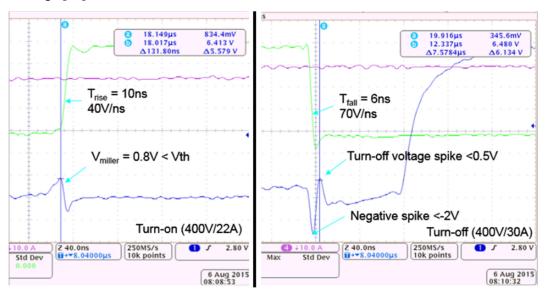

| Fig.I.7 Pulse test switching waveforms turn-on and turn-off of GaN-System evaluation board [21].               | 10 |

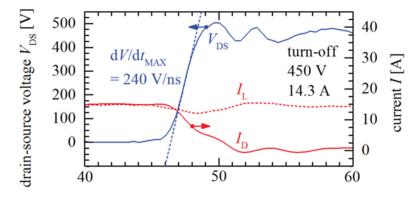

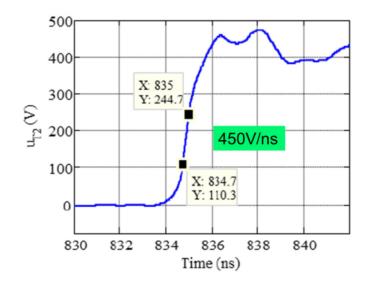

| Fig.I.8 Inductive-load turn-off transition at 450 V, 14.3 A [22]                                               | 11 |

| Fig.I.9 600V IFX Normally-Off GaN GIT with dv/dt up to 450V/ns [23]                                            | 11 |

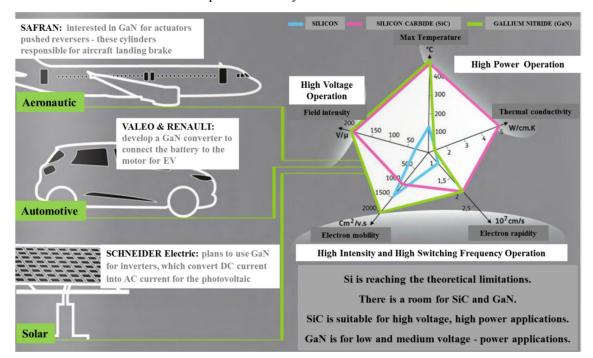

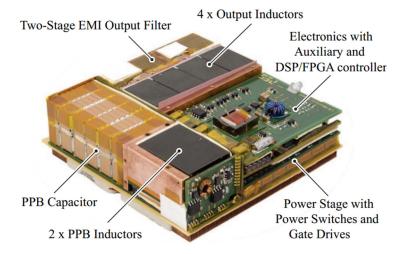

| Fig.I.10 Initial context of MEGaN project, 2012 [24]                                                           | 12 |

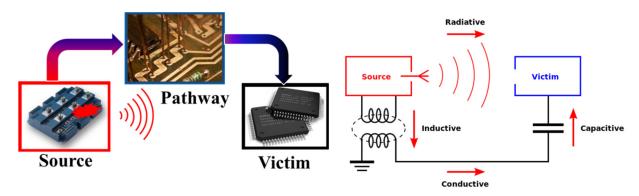

| Fig.I.11 EMI from source through pathway to victim [28]                                                        | 13 |

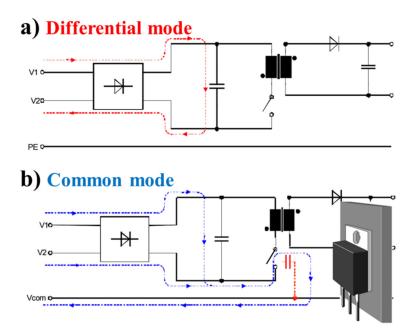

| Fig.I.12 Example of the interference currents, a) Differential mode current b) Common mode cur [32]            |    |

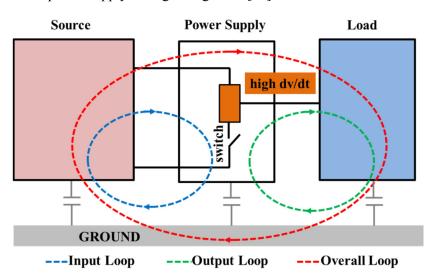

| Fig.I.13 Three common mode current loops [33]                                                                  | 14 |

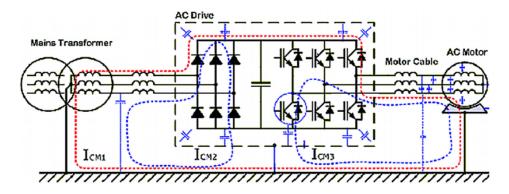

| Fig.I.14 Example for common mode current paths in an adjustable speed AC motor drive applica [34]              |    |

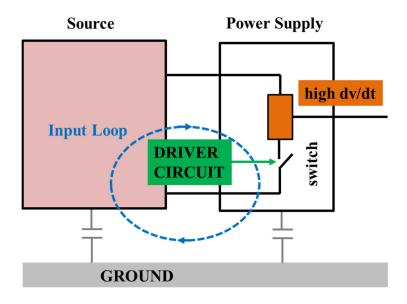

| Fig.I.15 Driver within the input loop                                                                          | 15 |

| Fig.I.16 Power converter all-in-one of 2kW with the power density of 200W/in <sup>3</sup> [35]                 | 16 |

| Fig.I.17 Left, gate driver circuit. Right, the switching cells of the power converter in Fig.I.6 [23]          | 16 |

| Fig.I.18 Principle driver circuit in power electronics system, adapted in a half-bridge [36]                   | 17 |

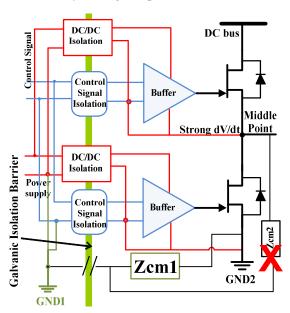

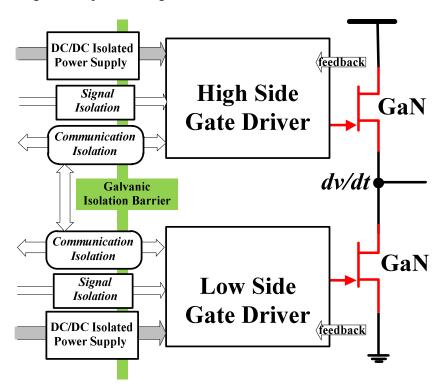

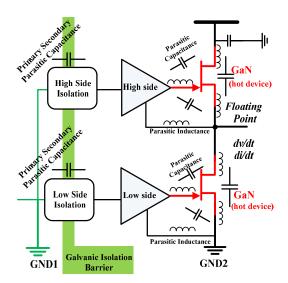

| Fig.I.19 Conventional architecture of a gate driver circuit for a high side – low side devices [37]            | 17 |

| Fig. I. 20. Gate driver circuit with power devices and common mode impedances                                  | 18 |

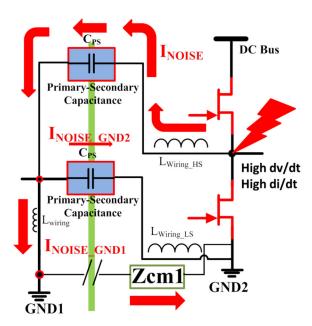

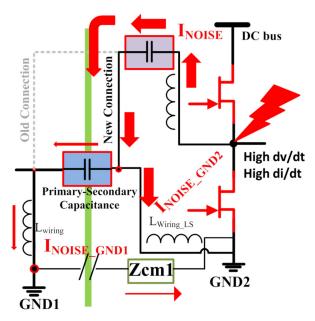

| Fig.I.21. Simplified gate driver circuit with the primary-secondary capacitance of the convention architecture |    |

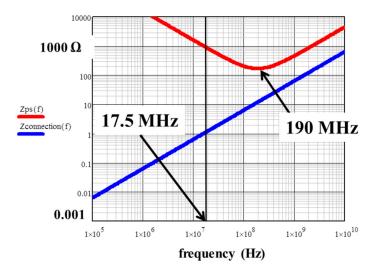

| Fig.I.22. Impedances Z <sub>PS</sub> and Z <sub>CONNECTION</sub> versus transient frequency                    | 20 |

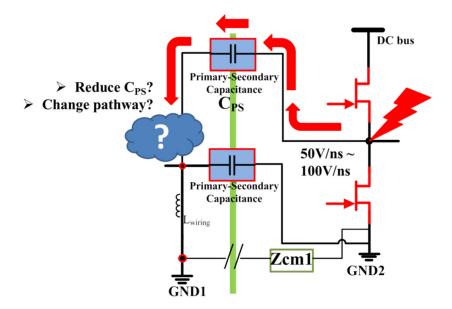

| Fig.I.23. Which ways to reduce the conducted EMI perturbation?!                                                | 22 |

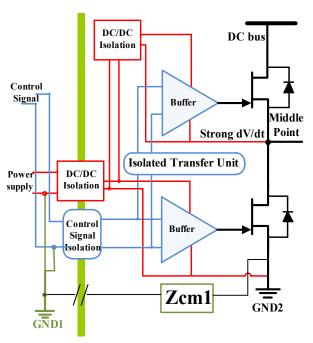

| Fig.I.24. Proposed gate driver architecture solution at the system level                                       | 22 |

| Fig.I.25. Simplified gate driver circuit with the primary-secondary capacitance of the proper architecture     |    |

| Fig.I.26 Parasitic elements of the conventional gate driver circuit and power devices                          | 25 |

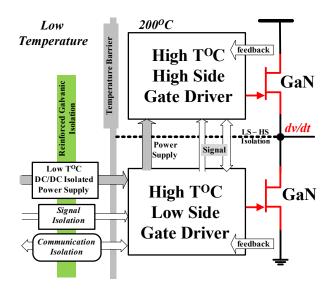

| Fig.I.27 "Hot box" with the power devices and the driver circuit, all-in-one [45]                              | 26 |

| Fig.I.28 Conventional gate driver circuitry of the half-bridge system overview                                 | 27 |

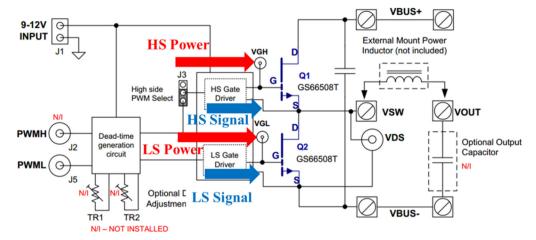

| Fig.I.29 GS66508T-EVBHB Evaluation Board Block Diagram from GaN-System with conventional gate driver architecture                                                      |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

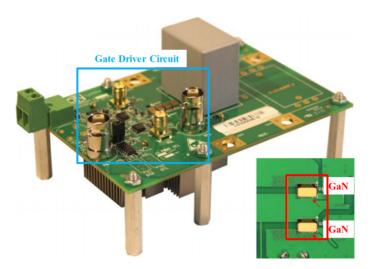

| Fig.I.30 GaN E-HEMT Half Bridge Evaluation Board using SI8261BAC-C-IS driver                                                                                           | 28    |

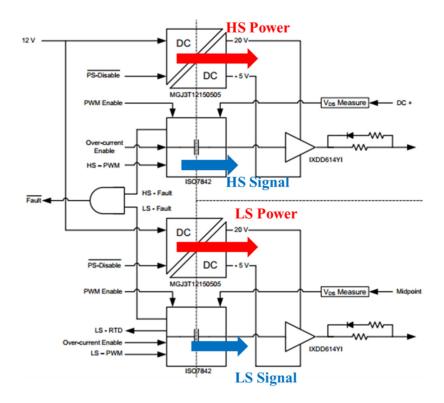

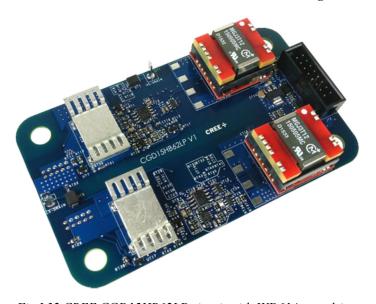

| Fig.I.31 CREE CGD15HB62LP schematic circuit with the conventional gate driver architecture                                                                             | 29    |

| Fig.I.32 CREE CGD15HB62LP circuit with IXD614 gate driver                                                                                                              | 29    |

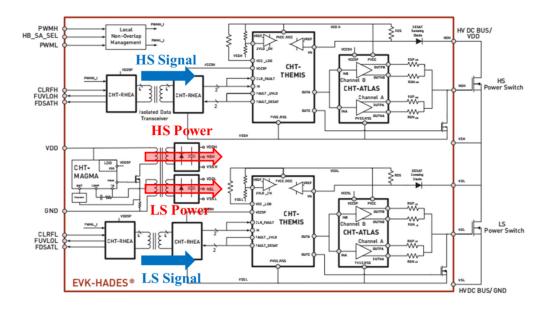

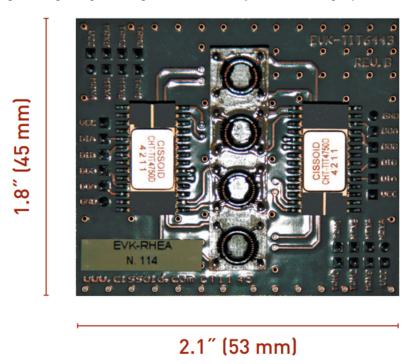

| Fig.I.33 High temperature gate driver RHEA of CISSOID Company schematic                                                                                                | 30    |

| Fig.I.34 High temperature gate driver RHEA board overview                                                                                                              | 30    |

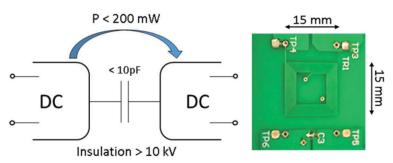

| Fig.I.35 Left, gate driver power supply basic specification. Right, PCB coreless transformer of [52]                                                                   | ]. 31 |

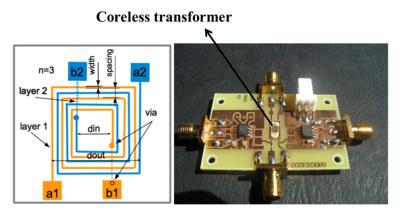

| Fig.I.36 Left, Simplified top view of the coreless transformer for the control signal isolation. Right tests boards developed for the coreless transformers chips [55] | -     |

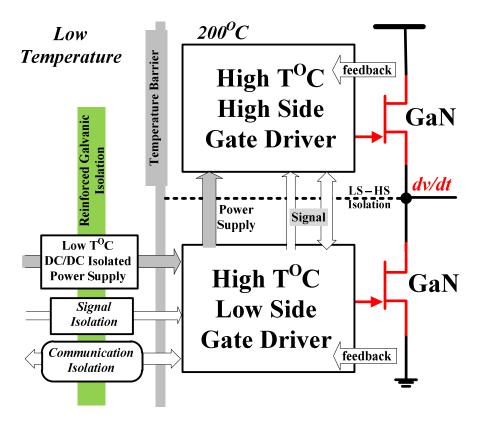

| Fig.I.37 Gate driver with 2 temperature zones for thermal and EMI managements                                                                                          | 32    |

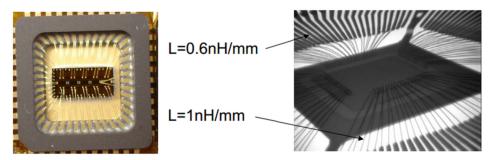

| Fig.I.38 Left, photo of CQFP 44 packaging. Right, the estimation of the parasitic inductances [63]                                                                     |       |

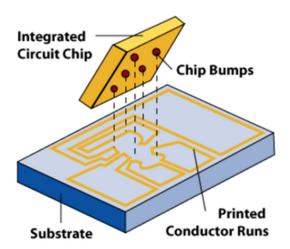

| Fig.I.39 A flip chip and substrate, shown with the bumped active face of the die to be placed down upon the matching substrate [64]                                    |       |

| Fig.I.40 Solder bumps on the pads of the CMOS circuit [62]                                                                                                             | 34    |

| Fig.I.41 Proposed high temperature gate driver overview                                                                                                                | 35    |

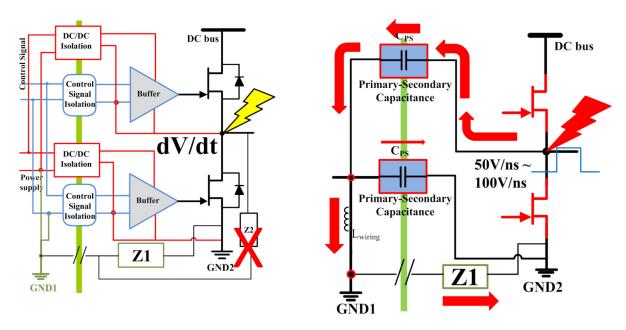

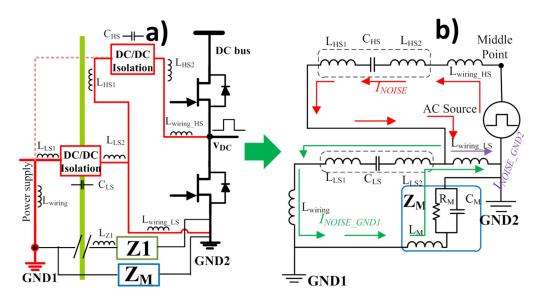

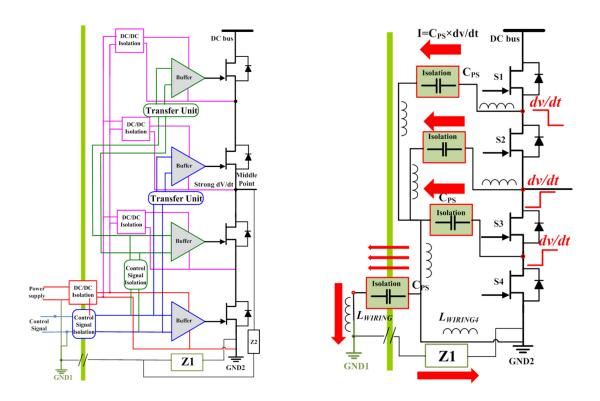

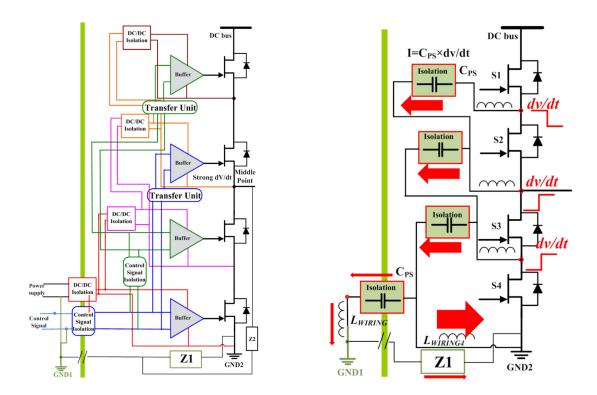

| Fig.II.1. Gate driver circuit with conventional architecture. Left, schematic bloc diagram. R pathways for the conducted EMI perturbations.                            | •     |

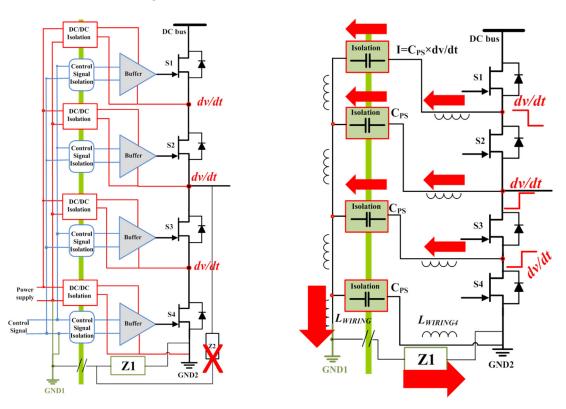

| Fig.II.2. Left, conventional gate driver architecture of a series-connection of transistor. Right conducted EMI perturbations pathways in common mode                  |       |

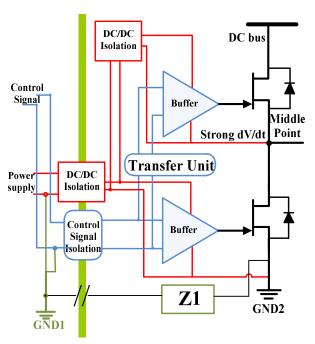

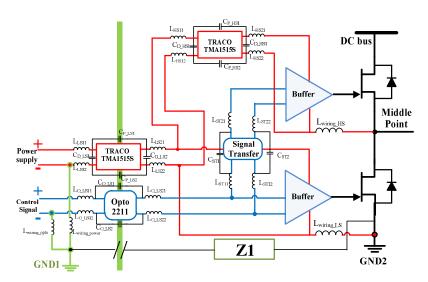

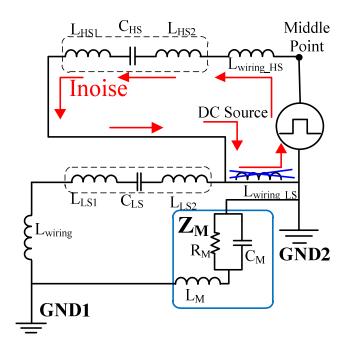

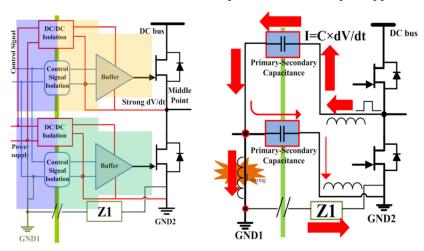

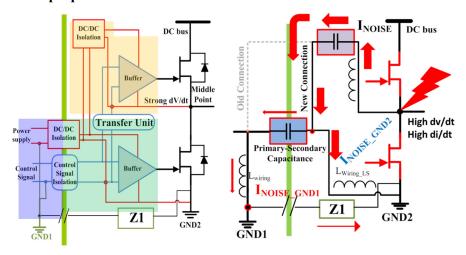

| Fig.II.3. Proposed architecture of the gate driver circuitry                                                                                                           | 42    |

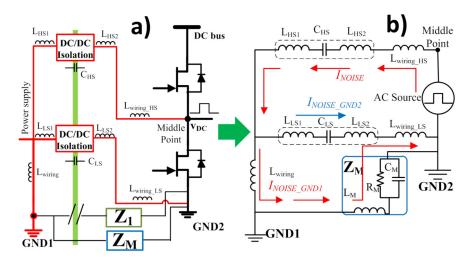

| Fig.II.4. Parasitic elements around the power supplies and the control signal insulators conventional architecture                                                     |       |

| Fig.II.5. Parasitic elements around the power supplies and the control signal insulators in the proparchitecture                                                       |       |

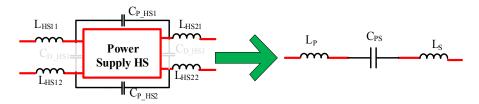

| Fig.II.6. High frequency equivalent circuit of an isolated DC – DC power supply                                                                                        | 45    |

| Fig.II.7. Left, high frequency equivalent circuit of the conventional architecture. Right, driver circuit with the power supplies                                      |       |

| Fig.II.8. Left, high frequency equivalent circuit of the proposed architecture. Right, driver circuit only power supplies                                              |       |

| Fig.II.9. High frequency equivalent circuit of the proposed architecture with improvement                                                                              | 48    |

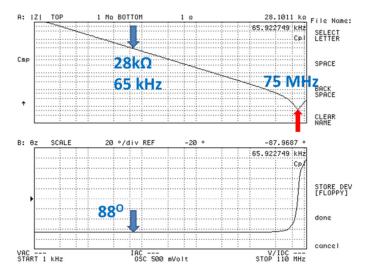

| Fig.II.10. Primary – secondary impedance of the power supply TRACO TMA1515S.                                                                                           | 49    |

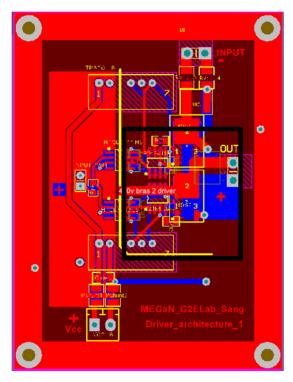

| Fig.II.11. PCB layout of the conventional gate driver architecture                                                                                                     | 49    |

| Fig.II.12. Simplified conductors between the GND2 and output of the low side power supply                                                                              | 50    |

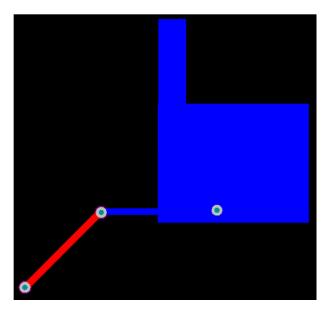

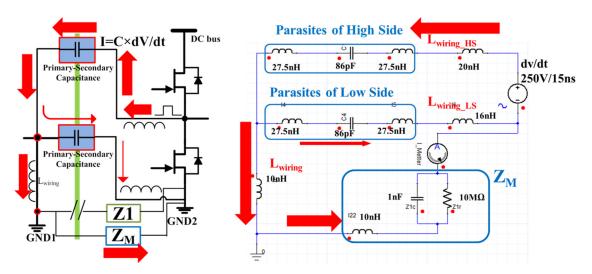

| Fig.II.13. Modeled geometry in InCa3D                                                                                                                                  | 50    |

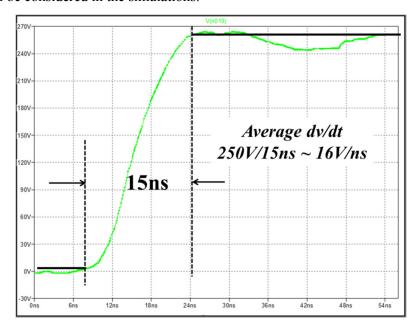

| Fig.II.14. Screen shot of the power side middle point voltage rising.                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

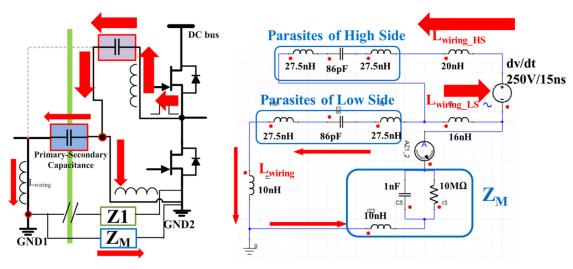

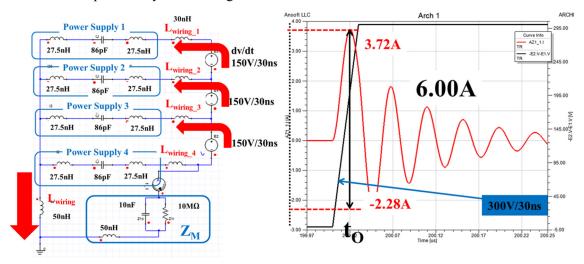

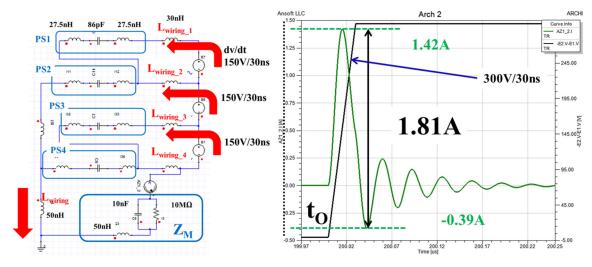

| Fig.II.15. Conventional architecture: Left, schematic circuit. Right, SIMPLORER circuit                                                                          |

| Fig.II.16. Proposed architecture: Left, schematic circuit. Right, SIMPLORER circuit                                                                              |

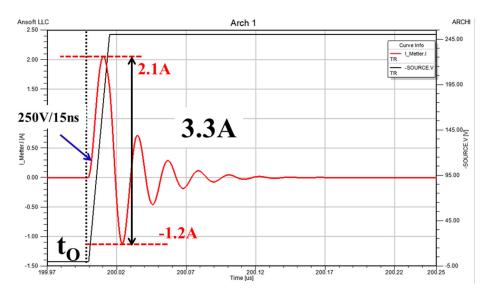

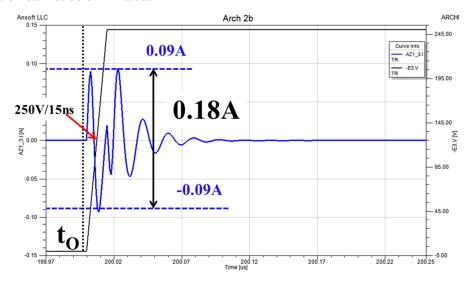

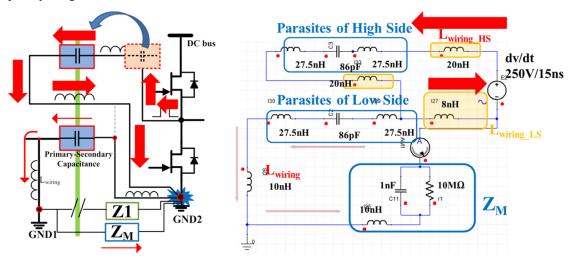

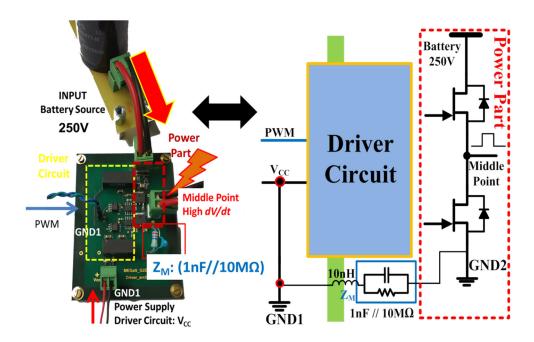

| Fig.II.17. Noisy current in $Z_M$ for the conventional architecture, simulation results                                                                          |

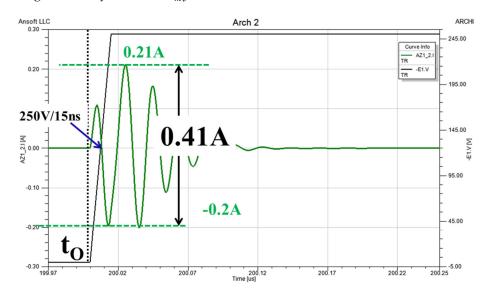

| Fig.II.18. Noisy current in $Z_M$ for the proposed architecture, simulation results                                                                              |

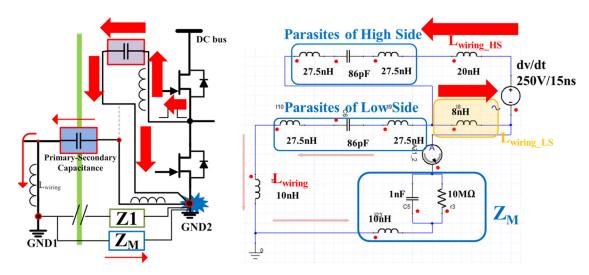

| Fig.II.19. Proposed architecture with the improved routing: Left, schematic circuit. Right SIMPLORER circuit                                                     |

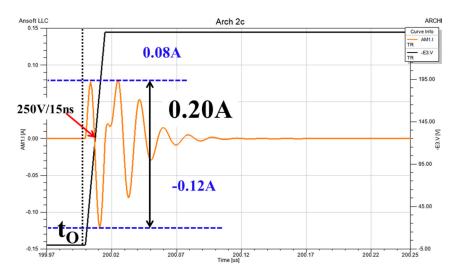

| Fig.II.20. Noisy current in $Z_M$ of the proposed architecture with improved wire routing, simulation results                                                    |

| Fig.II.21. Left, schematic circuit. Right, SIMPLORER circuit of compromised solution of th proposed architecture                                                 |

| Fig.II.22. Noisy current in $Z_M$ of compromised solution, simulation results                                                                                    |

| Fig.II.23. Experimental setup to separate physically GND1 and GND2                                                                                               |

| Fig.II.24. Experimental circuit with conventional gate driver architecture                                                                                       |

| Fig.II.25. Noisy current between GND1 and GND2 in conventional architecture, test circuit and experimental results                                               |

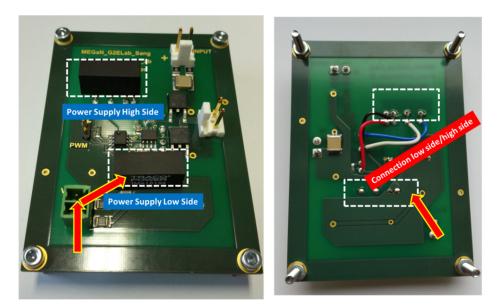

| Fig.II.26. Circuit with proposed gate driver architecture                                                                                                        |

| Fig.II.27. Noisy current between GND1 and GND2 in the proposed architecture                                                                                      |

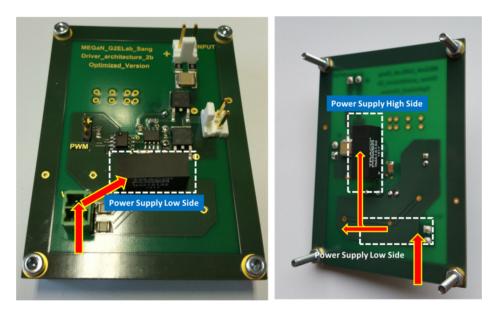

| Fig.II.28. PCB circuit with top view and bottom view of the proposed architecture with improved wir routing,                                                     |

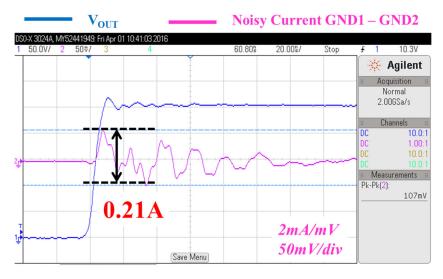

| Fig.II.29. Experimental result of the noisy current between GND1 and GND2 in the propose architecture with improved wire routing                                 |

| Fig.II.30. Compromised architecture circuit                                                                                                                      |

| Fig.II.31. Noisy current between GND1 and GND2 in the compromised solution of the propose architecture gate driver                                               |

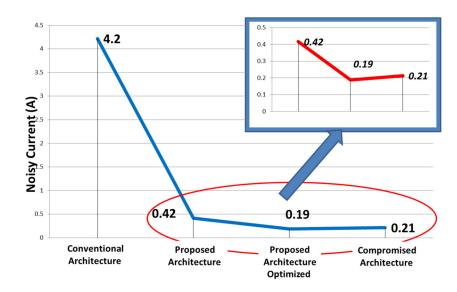

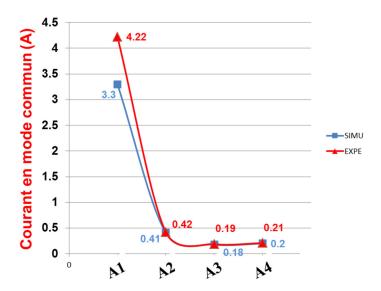

| Fig.II.32. Noisy currents in the 4 different cases, experimental results                                                                                         |

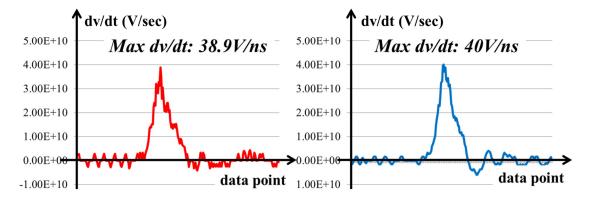

| Fig.II.33 dv/dt on each point of the rising voltage of the conventional architecture (left) and the proposed architecture (right)                                |

| Fig.II.34. Circuit diagram of the gate driver for the proposed architecture                                                                                      |

| Fig.II.35. Two options for the high side DC-DC isolated power supply                                                                                             |

| Fig.II.36. Left, first proposed gate driver architecture for series-connection of transistors, named AS2 Right, the conducted EMI perturbations in common mode   |

| Fig.II.37. Left, second proposed gate driver architecture for a series-connection of transistors name AS3. Right, the conducted EMI perturbations in common mode |

| Fig.II.38. Left, conventional gate driver architecture for series-connection of transistors named AS4 Right, the conducted EMI perturbations in common mode      |

| Fig.II.39. Experimental dv/dt captures across a pair of power devices in the experiment                                                                          |

| Fig.II.40. Simulation of the conventional architecture AS1: Left, schematic circuit. Right, simulation results                                                 |            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Fig.II.41. Simulation of the proposed architecture AS2: Left, schematic circuit AS2. Right, simulation result                                                  |            |

| Fig.II.42. Simulation of the proposed architecture AS3: Left, schematic circuit AS3. Right, simulation result                                                  |            |

| Fig.II.43. Simulation of the proposed architecture AS4: Left, schematic circuit AS4. Right, simulation result                                                  |            |

| Fig.II.44. Noisy currents peak to peak maximum amplitude for the 4 different gate driver supplied architectures, simulation results                            |            |

| Fig.II.45. Experimental setup with physically separated GND1 and GND2                                                                                          | '2         |

| Fig.II.46. Conventional gate driver architecture (AS1) with 2 power devices in series connection Right, Picture of the PCB circuit. Left, experimental results |            |

| Fig.II.47. Proposed gate driver architecture (AS4 – fourth case): Right, Picture of the PCB circuit Left, experimental results                                 |            |

| Fig.II.48 Rising voltages of AS1 and AS4 without the gate resistors of transistors                                                                             | <b>'</b> 4 |

| Fig.II.49 Switching speeds of AS1 and AS4, the dv/dt                                                                                                           | ′4         |

| Fig.II.50 Parasitic capacitances in power circuit of 2 architectures: AS1 and AS4                                                                              | 15         |

| Fig.III.1 Commercial power supplies based on the flyback topology [77] [78] [79]                                                                               | 31         |

| Fig.III.2 Bootstrap supply in IRS2330 gate driver[80] [81]                                                                                                     | 32         |

| Fig.III.3 Self-powering circuit for high side transistor [59]                                                                                                  | 32         |

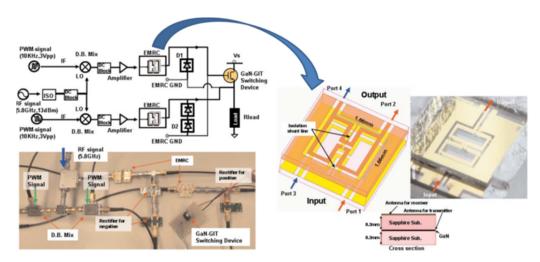

| Fig.III.4 Direct gate driver supply using Electro Magnetic Resonance Coupler [82]                                                                              | 3          |

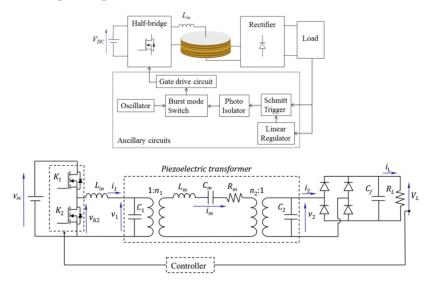

| Fig.III.5 System block diagram and circuit topology of piezoelectric transformer based DC/D converter with burst-mode control [83]                             |            |

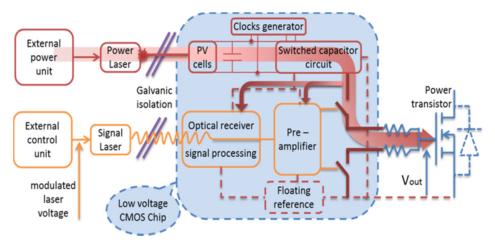

| Fig.III.6 Optical supply chain [86]                                                                                                                            | 34         |

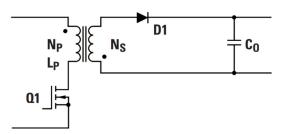

| Fig.III.7 Conventional flyback converter topology [93]                                                                                                         | 8          |

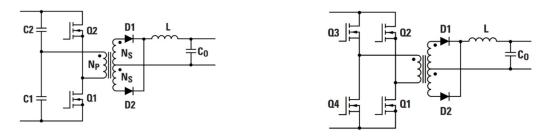

| Fig.III.8 Left, Half-Bridge converter. Right, Full-Bridge converter [93]                                                                                       | 39         |

| Fig.III.9 LLC resonant converter [97]                                                                                                                          | 0          |

| Fig.III.10 Operation of LLC at f <sub>0</sub> [97]                                                                                                             | 0          |

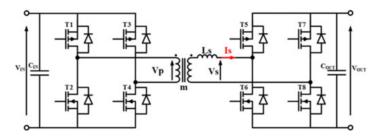

| Fig.III.11 DAB topology [102]                                                                                                                                  | 1          |

| Fig.III.12 Current and voltage waveforms of DAB converter [102]                                                                                                | 1          |

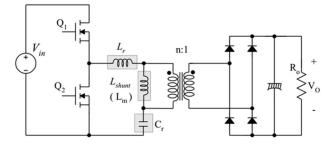

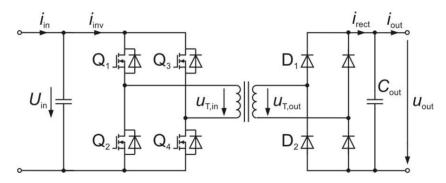

| Fig.III.13 Topology of SAB converter[103]                                                                                                                      | 2          |

| Fig.III.14 Transformer input voltage and the input current of SAB converter[103]                                                                               | 13         |

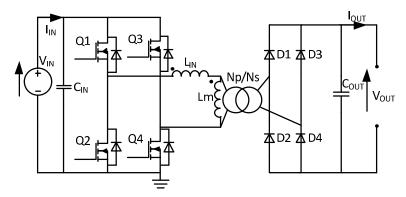

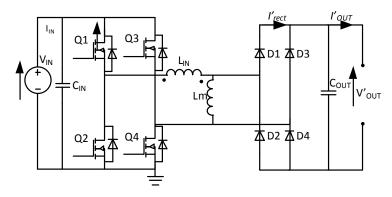

| Fig.III.15 Equivalent circuit of SAB                                                                                                                           | )4         |

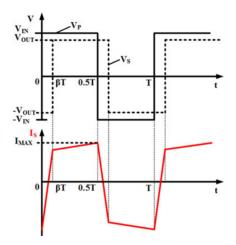

| Fig.III.16 SAB topology without the idealized transformation ratio                                                                                             | )5         |

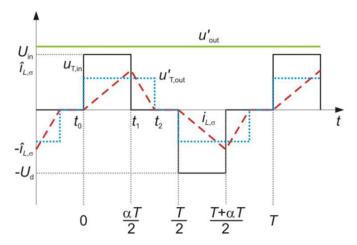

| Fig III 17 PWM wave forms of the H-bridge                                                                                                                      | )5         |

| Fig.III.18 Waveforms of SAB converter: the input voltage of the transformer and the output vo                                                                                                                                   | _       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Fig.III.19 Simple equivalent circuit of SAB during MODE 1                                                                                                                                                                       | 97      |

| Fig.III.20 Simplified circuit during MODE 1                                                                                                                                                                                     |         |

| Fig.III.21 Simple equivalent circuit of SAB during MODE 2                                                                                                                                                                       | 98      |

| Fig.III.22 Simplified circuit during MODE 2                                                                                                                                                                                     | 98      |

| Fig.III.23 Simple equivalent circuit of SAB during MODE 3                                                                                                                                                                       | 99      |

| Fig.III.24 Simplified circuit during MODE 3                                                                                                                                                                                     | 99      |

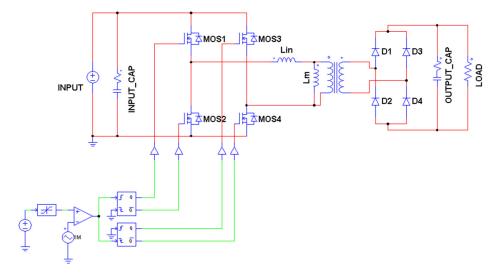

| Fig.III.25 An idealized PSIM simulation of a SAB converter                                                                                                                                                                      | 101     |

| Fig.III.26 SAB waveforms of the idealized simulation with Lin = $2\mu$ H, Lm= $72.8\mu$ H, f = 1 MH = $0.5$                                                                                                                     |         |

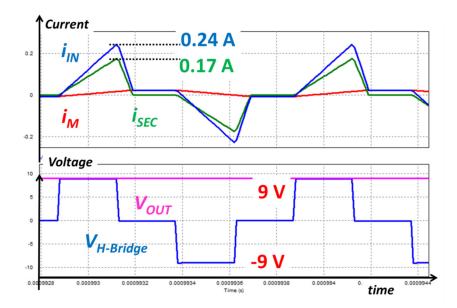

| Fig.III.27 Comparison of the output voltage versus the output load between the idealized ar calculation and the idealized PSIM simulation, Lin = 2 $\mu$ H, Lm=72.8 $\mu$ H, f=1 MHz and $\alpha$ = 0.5                         | -       |

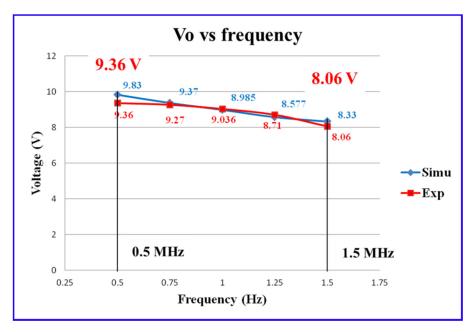

| Fig.III.28 Comparison of output voltage versus frequency from 0.5 MHz to 1.5 MHz with Lin Lm=72.8 $\mu$ H, the resistive load R <sub>out</sub> =162 $\Omega$ and $\alpha$ = 0.5                                                 | •       |

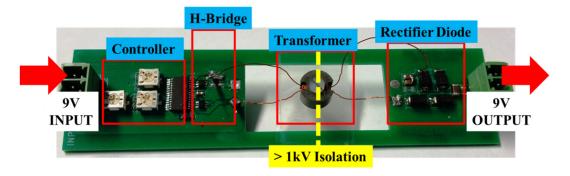

| Fig.III.29 SAB converter prototype on a PCB implemented with discrete components                                                                                                                                                | 104     |

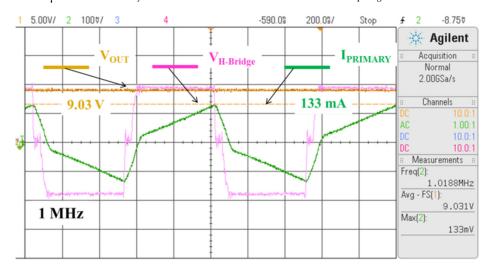

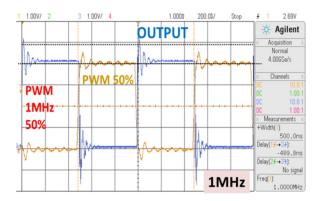

| Fig.III.30 Waveforms of the SAB converter, experimental results: output voltage, H-Bridge and primary current with Lin=8.8 $\mu$ H, Lm=133 $\mu$ H, N <sub>P</sub> /N <sub>S</sub> =22/30, $\alpha$ =0.95 and Rout=162 $\Omega$ | •       |

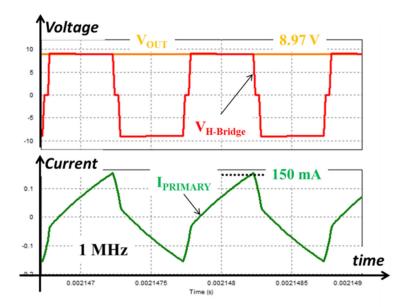

| Fig.III.31 Waveforms of the SAB converter, simulation results with realistic parameters                                                                                                                                         | 105     |

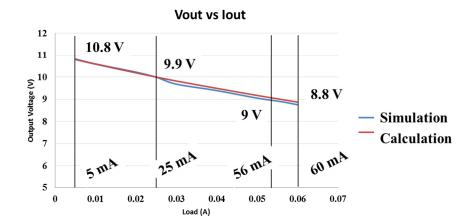

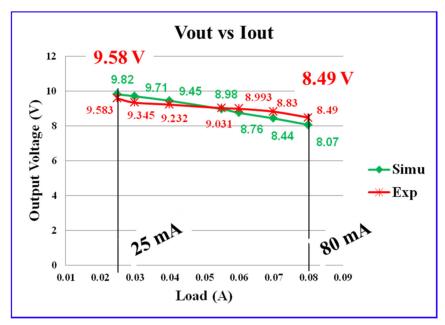

| Fig.III.32 Output voltage as a function of the output load from 25mA to 80mA with the frequent load, simulation and experimental results                                                                                        | -       |

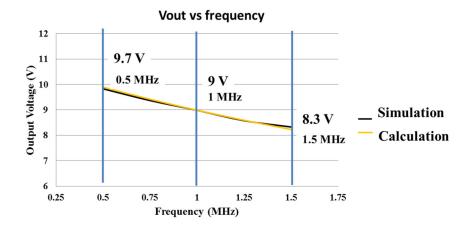

| Fig.III.33 Output voltage as a function of the switching frequency from 0.5 MHz to 1.5 MHz output resistive load of 165 $\Omega$ , simulation and experimental results                                                          |         |

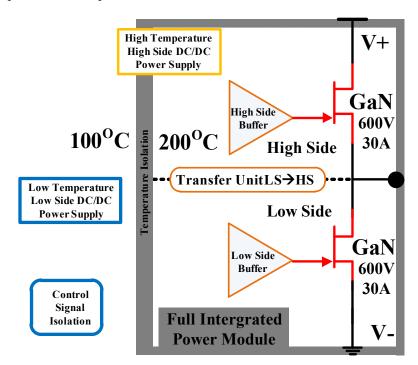

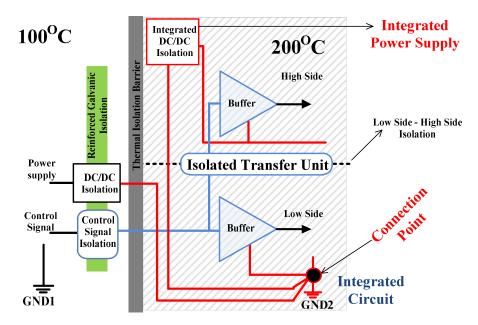

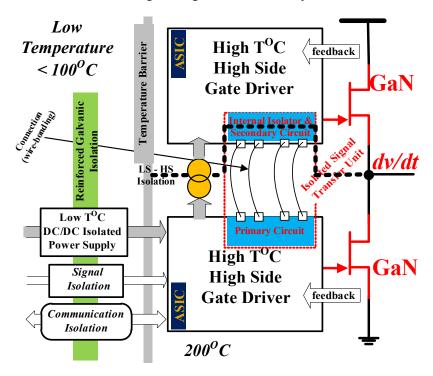

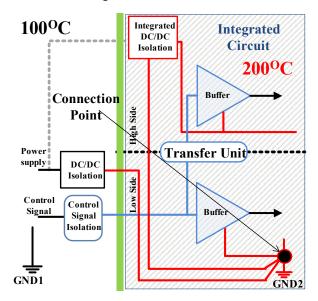

| Fig.III.34 Gate driver architecture with the high temperature power supply                                                                                                                                                      | 107     |

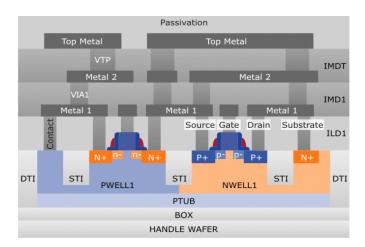

| Fig.III.35 Devices schematic cross section of XFAB XT018[106]                                                                                                                                                                   | 108     |

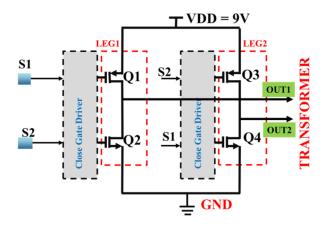

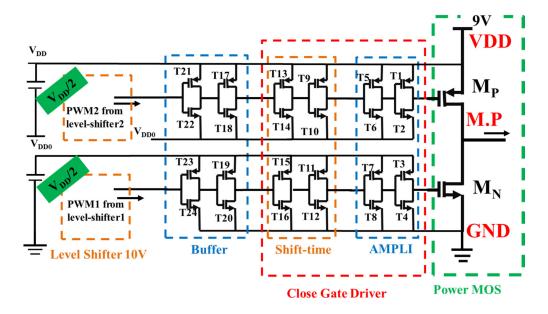

| Fig.III.36 H-Bridge of the SAB converter                                                                                                                                                                                        | 108     |

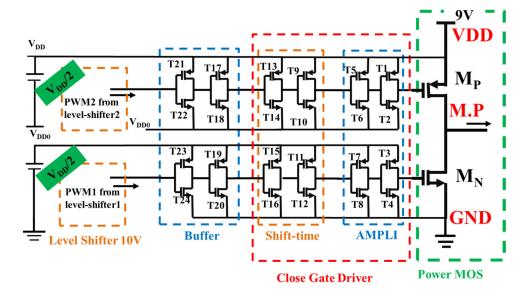

| Fig.III.37 Schematic of the inverter leg with level shifters and buffers [89], [108], [109]                                                                                                                                     | 108     |

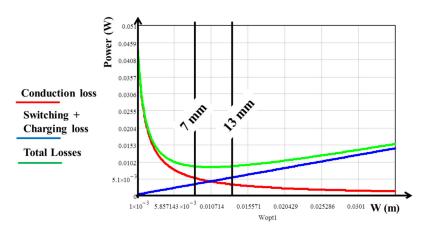

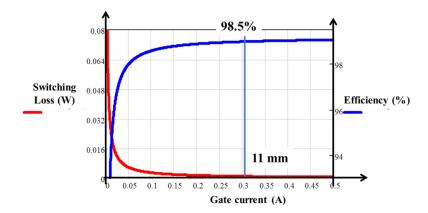

| Fig.III.38 Losses and the N-channel width (Technology XFAB XT018, $V_{DD}=10 \text{ V}$ , $I=0.1 \text{ A}$ )                                                                                                                   | 109     |

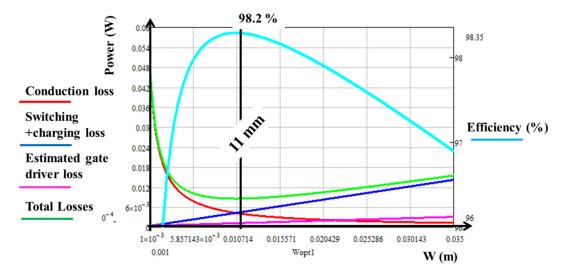

| Fig.III.39 Theoretical efficiency with the estimated charging loss and the optimal N-channel wi                                                                                                                                 | dth 110 |

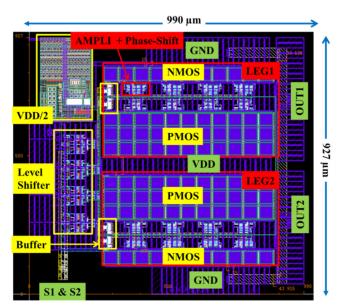

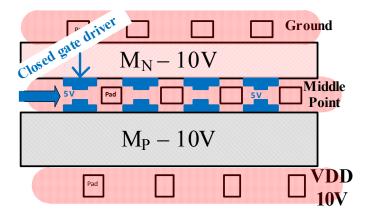

| Fig.III.40 Layout of the H-bridge with gate driver 990 μm x 927μm                                                                                                                                                               | 111     |

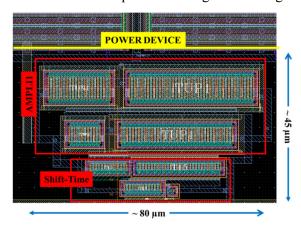

| Fig.III.41 Layout of the amplification stage circuit with AMPLI1 and Shift-Time blocs                                                                                                                                           | 112     |

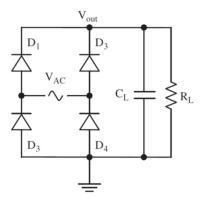

| Fig.III.42 Schematic of a diode rectifier                                                                                                                                                                                       | 112     |

| Fig.III.43 Options of the rectifier diodes in technology XFAB XT018                                                                                                                                                             | 112     |

| Fig.III.44 Schematic [112] [113] of the intrinsic body -diodes rectifier by connecting the gates sources                                                                                                                        |         |

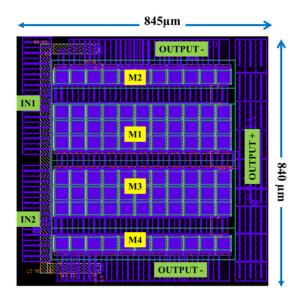

| Fig III 45 Layout of the intrinsic-body diodes rectifier in XFAB XT018 845 um x 840 um                                                                                                                                          | 113     |

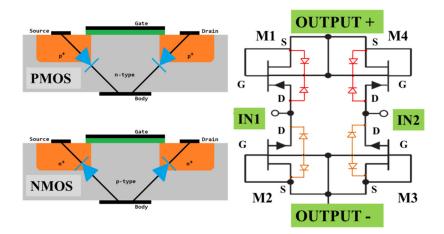

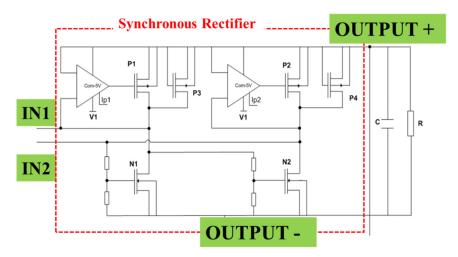

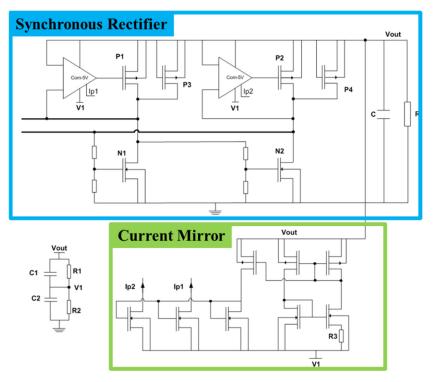

| Fig.III.46 Schematic of the synchronous rectifier studied in this work                                                                                            | 114  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

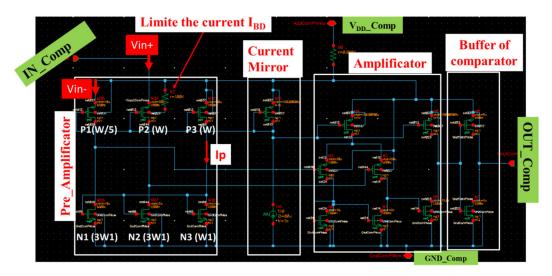

| Fig.III.47 CADENCE schematic circuit of a PMOS comparator with its stages                                                                                         | 116  |

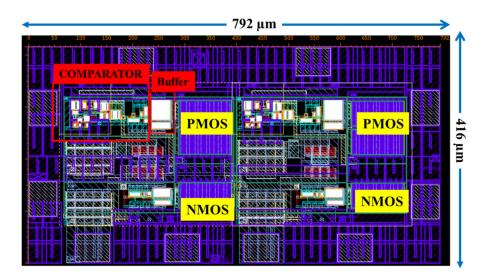

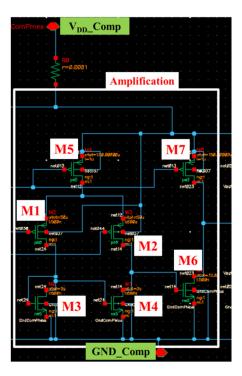

| Fig.III.48 Layout of the synchronous rectifier, 792 μm x 416μm                                                                                                    | 117  |

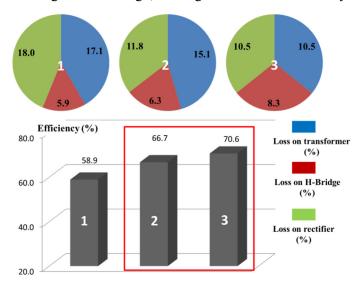

| Fig.III.49 Comparison of the efficiencies and the losses' distributions of the SAB converter with different rectifiers (case 1, case 2 and case 3)                |      |

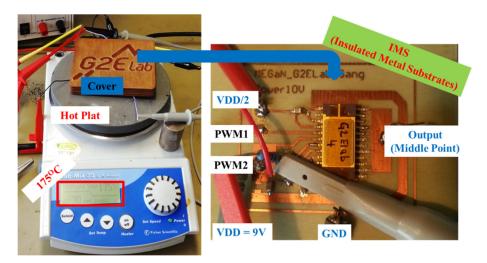

| Fig.III.50 Test chip XFAB XT018 under high temperature tests                                                                                                      | 119  |

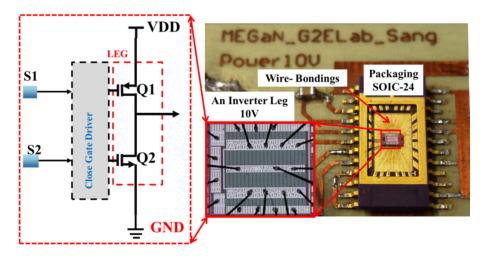

| Fig.III.51 Test-chip - an inverter leg 10: schematic and pictures                                                                                                 | 119  |

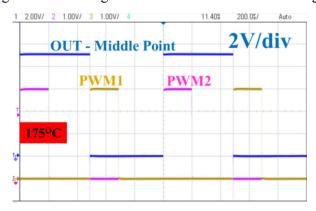

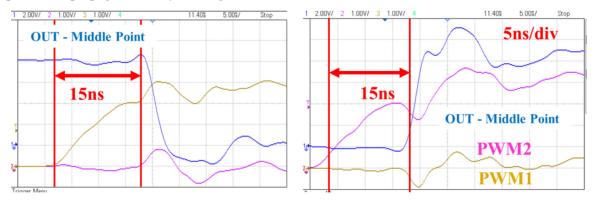

| Fig.III.52 Output signal of the inverter leg with the control signals                                                                                             | 119  |

| Fig.III.53 Delay times during rise time and fall time of the output voltage                                                                                       | 120  |

| Fig.III.54 Gate driver architecture with the signal transfer unit as the gate driver by using co transformer                                                      |      |

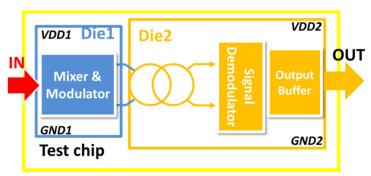

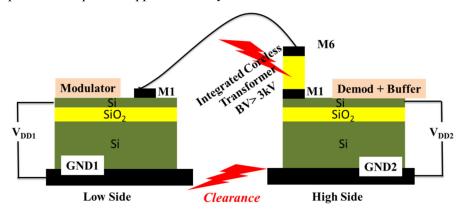

| Fig.III.55. Schematic of the coreless gate driver signal transfer unit                                                                                            | 122  |

| Fig.III.56. Low side – high side ICs [121]                                                                                                                        | 123  |

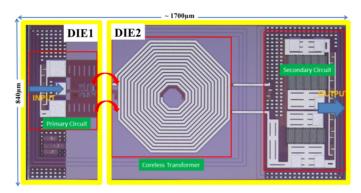

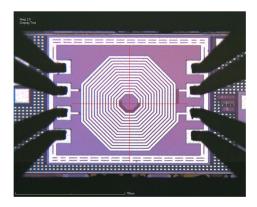

| Fig.III.57 Microscope photo of XFAB XT018 gate signal transfer unit with coreless transformer .                                                                   | 123  |

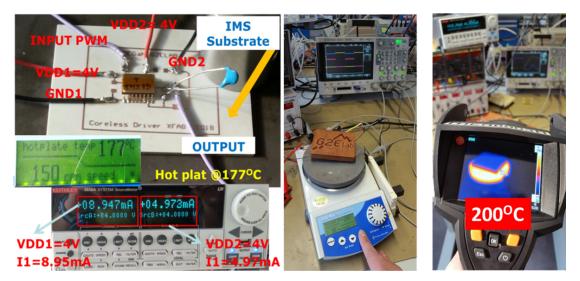

| Fig.III.58 Set-up for tests at high temperatures                                                                                                                  | 124  |

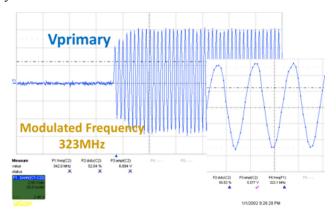

| Fig.III.59 Input and output signals of the gate signal transfer unit with coreless transformer at 1 under 175°C                                                   |      |

| Fig.III.60 Primary voltage appled to the coreless transformer (+ Zoom of the waveform)                                                                            | 124  |

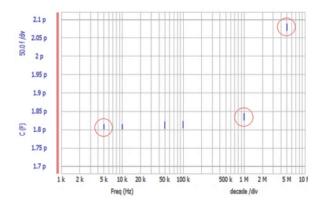

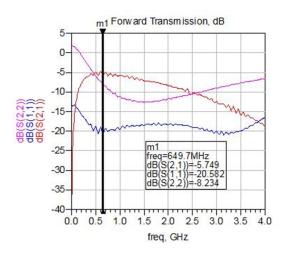

| Fig.III.61 Primary-secondary windings parasitic capacitance with respect to frequency                                                                             | 125  |

| Fig.III.62 Microscope picture of the transformer under tips for the S-parameters characterism (70MHz to 20GHz)                                                    |      |

| Fig.III.63. Measurement of S-parameters of the transformer                                                                                                        | 125  |

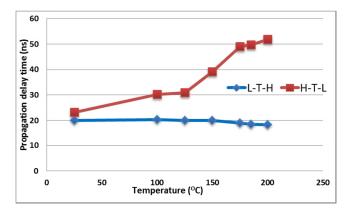

| Fig.III.64 Propagation delay evolution of the coreless signal transmission unit as a function operating temperature                                               |      |

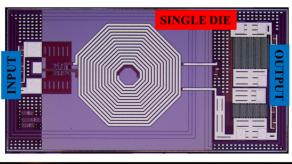

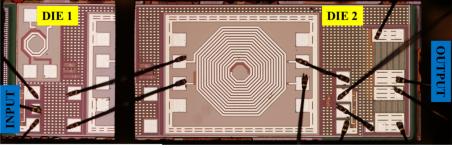

| Fig.III.66 Microscope pictures of a single die prototype and a prototype with two separated dies                                                                  | 127  |

| Fig.III.67 Input - output parasitic capacitance of two prototypes                                                                                                 | 127  |

| Fig.IV.1 Configuration of the block diagram for a low side-high side implementation                                                                               | 137  |

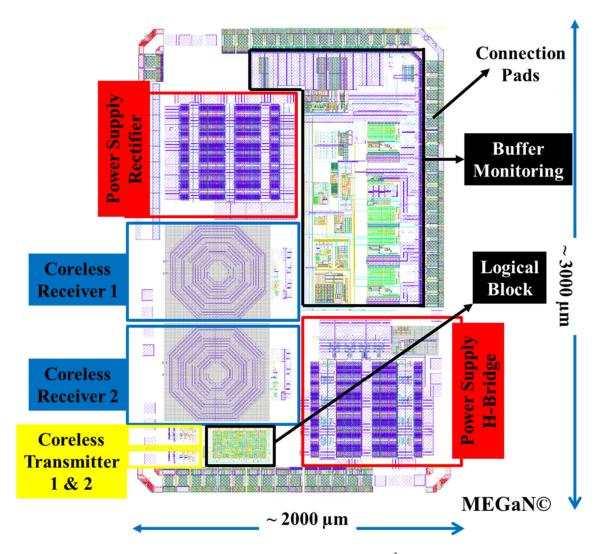

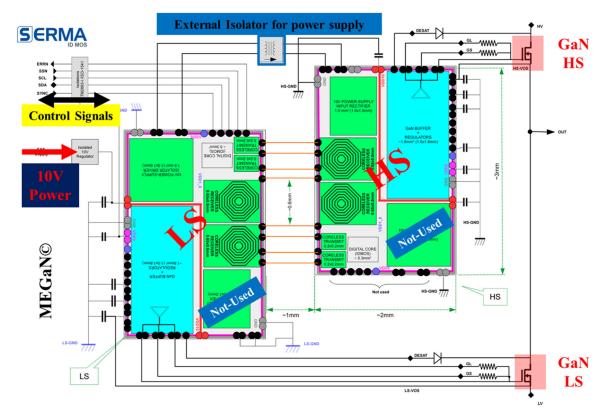

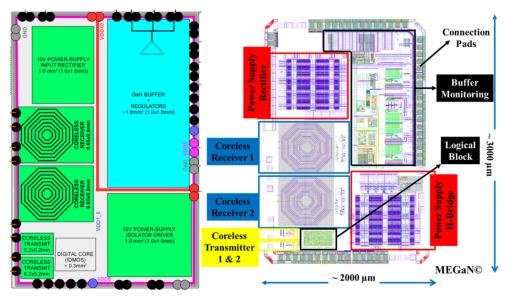

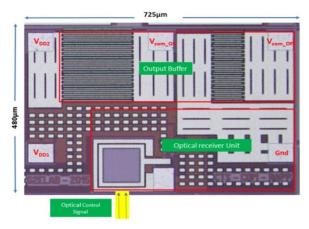

| Fig.IV.2 Blocks and functions of a single ASIC (MEGaN©)                                                                                                           | 139  |

| Fig.IV.3 ASIC layout in XFAB XT018, 2 x 3 mm <sup>2</sup> (MEGaN©)                                                                                                | 140  |

| Fig.IV.4 Schematic of the proposed gate driver (MEGaN©).                                                                                                          | 141  |

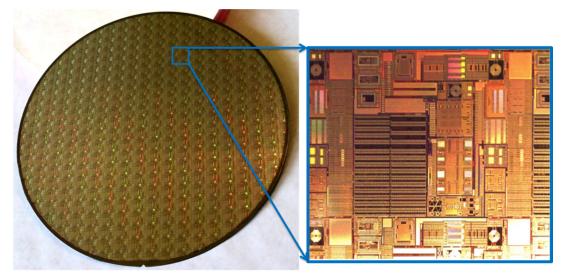

| Fig.GCP.1 Left, 8 inches wafer of the ASICs XFAB XT018. Right, the 1 <sup>st</sup> version test-chips of functions                                                |      |

| Fig.GCP.2 Configuration of the proposed gate driver architecture with the high temperature ASIG 600V GaN components (Blue function blocks are designed by G2ELab) |      |

| Fig.GCP.3 Cross-section of perspectives of gate driver circuit and 600V GaN power modules advance packaging technology                                            | with |

| Fig.V.1 Gauche, positionnements du marché du composants GaN et SiC. Droite, contexte du projet MEGaN                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.V.2 Défis du gate driver d'un bras d'onduleur                                                                                                                                          |

| Fig.V.3 Proposition du gate driver au niveau système                                                                                                                                       |

| Fig.V.4 Architecture classique et son circuit simplifié                                                                                                                                    |

| Fig.V.5 Architecture proposée et son circuit simplifié                                                                                                                                     |

| Fig.V.6 Validations des architectures sur le courant en mode commun. Résultats de simulation et résultats expérimentaux                                                                    |

| Fig.V.7. Recommandations de la conception du gate driver                                                                                                                                   |

| Fig.V.8 Synoptique du gate driver MEGaN                                                                                                                                                    |

| Fig.V.9 Gauche, fonctionnalités de l'ASIC. Droite, le layout final de l'ASIC                                                                                                               |

| Fig.V.10 Schématique du gate driver pour les composants GaN                                                                                                                                |

| Fig.A.1 Schematic of the inverter leg with level shifters and buffers                                                                                                                      |

| Fig.A.2 An inverter leg: the closed control circuit between two power components                                                                                                           |

| Fig.A.3 switching loss and efficiency of first stage of AMPLI                                                                                                                              |

| Fig.A.4 Input and output dynamic of second stage of the closed control circuit in the low side channel (for low side power transistor) [108]                                               |

| Fig.A.5 Design of the 2 <sup>nd</sup> stage                                                                                                                                                |

| Fig.A.6 Shift-time circuit to manage the dead-time                                                                                                                                         |

| Fig.A.7 Supplementary buffer between two power components (green), layout of the inverter leg g                                                                                            |

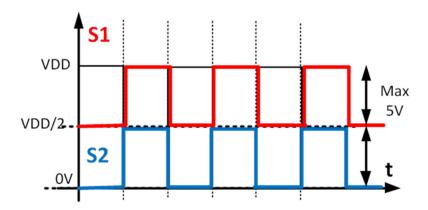

| Fig.A.8 S1 is the control signal for the high side, S2 is the control signal for the low side                                                                                              |

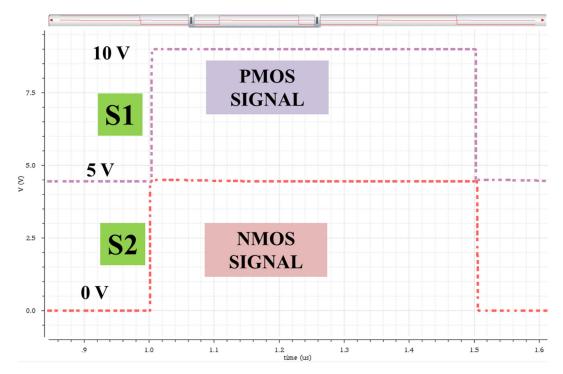

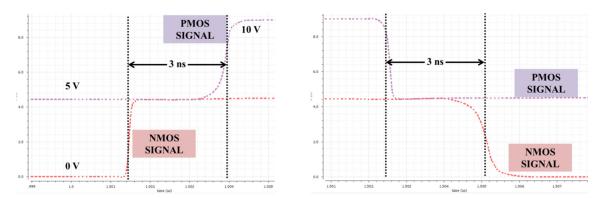

| Fig.A.9 Low side and high side control signal after the dead-time stage, CADENCE simulation results                                                                                        |

| Fig.A.10 3ns of the dead-time between the low side and the high side control signals, CADENCE simulation results (zoom-in)                                                                 |

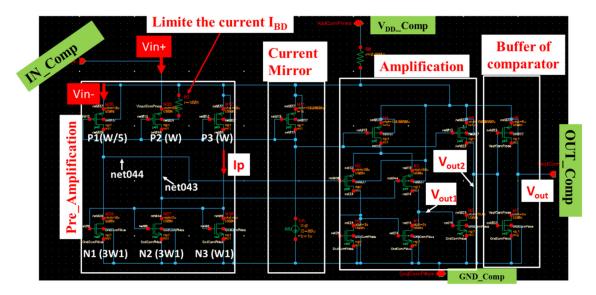

| Fig.B.1 Schematic of the comparator of the synchronous rectifieri                                                                                                                          |

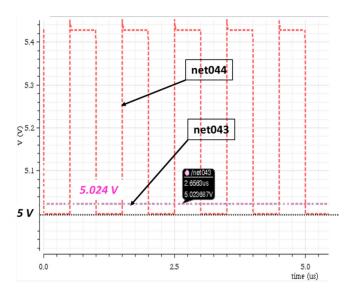

| Fig.B.2 Voltage on the transistor of the pre-amplification stage: VDS_P1 (net 44) and VDS_N1 (net 43)j                                                                                     |

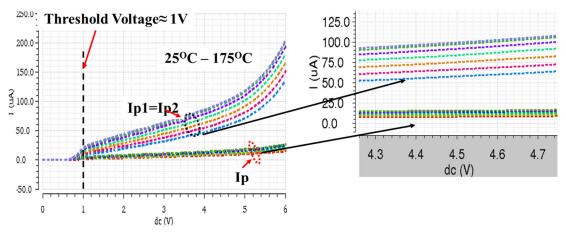

| Fig.B.3 Mirror current of the synchronous rectifier                                                                                                                                        |

| Fig.B.4 Current of the mirror current and current Ip of the pre-amplification stage with different supplied voltage $V_{DC}$ (in the complete circuit, $V_{DC}$ is Vout and GND is Vout/2) |

| Fig.B.5 Amplification stage with its transistors                                                                                                                                           |

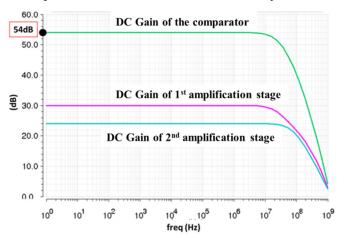

| Fig.B.6 Gain of the different stages of the amplification stage, AC simulation results                                                                                                     |

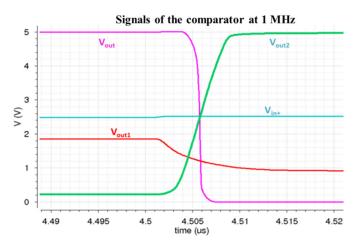

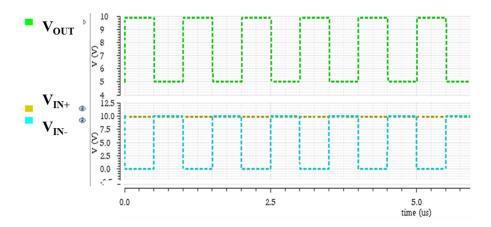

| Fig.B.7 Signals of the comparator at 1 MHz, transient simulations results: Vin+ of the pre-<br>amplification stage. Vout1 and Vout2 of the amplification stage and Vout of the comparator  |

| Fig.B.8 Input signals of the pre-amplification stage and the output signal of the comparator (for PMOS transistor)                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

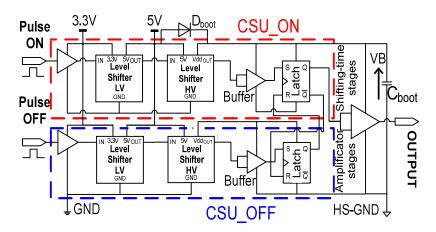

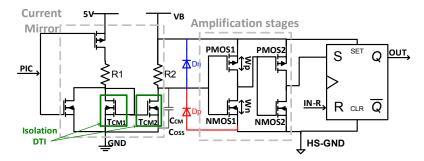

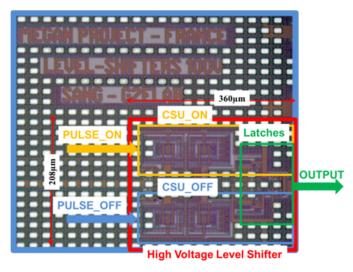

| Fig.C.1 High voltage level shifter with CSUs                                                                                                                               |

| Fig.C.2 High Voltage Level Shifter topology proposedp                                                                                                                      |

| Fig.C.3 Microscope photo of XFAB XT018 level shifter                                                                                                                       |

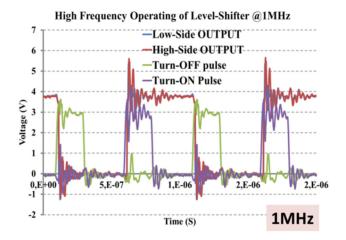

| Fig.C.4 Pulsed signals for control and the output of the level shifter for a low side – high side implementation                                                           |

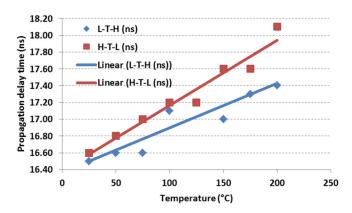

| Fig.C.5 Propagation delay of turn-on and turn-off signals at differences temperatures                                                                                      |

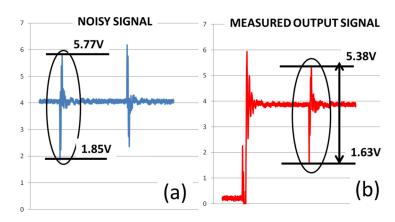

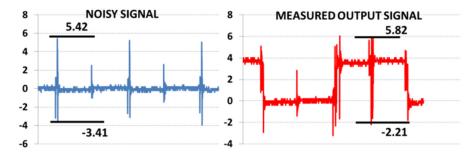

| Fig.C.6 Output signals of the pulsed level shifter with dv/dt: a) No input signal, noisy signal at output b) With input signal, measured output signal including the noise |

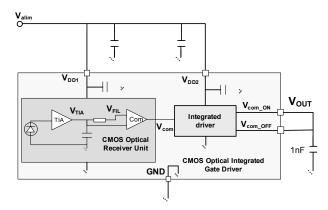

| Fig.C.7 IC optical gate driver structure (Integrated photo-detector + signal process circuit + a gate driver)                                                              |

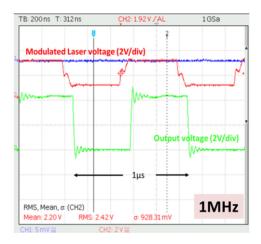

| Fig.C.8 Optical microscope picture of the fabricated chip XFAB XT018                                                                                                       |

| Fig.C.9 Optical microscope picture of the fabricated chip XFAB XT018                                                                                                       |

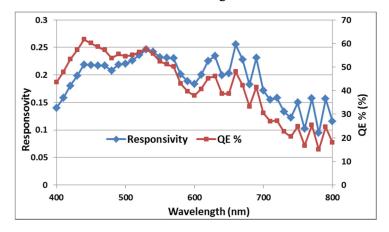

| Fig.C.10 Measured spectral responsivity and QE%                                                                                                                            |

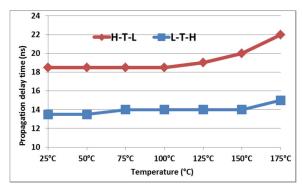

| Fig.C.11 Measured turn-on and turn-off propagation delay times as a function of temperatures                                                                               |

## **List of Tables**

| Table.I.1 Comparison between Si and WBG                                                                    | 7   |

|------------------------------------------------------------------------------------------------------------|-----|

| Table.I.2 Comparison of the commercial gate drivers                                                        | 31  |

| Table.II.1 The elements of the high frequency equivalent circuits in Fig.II.4 and Fig.II.5                 | 44  |

| Table.II.2 Elements of the simplified high frequency equivalent circuit in, Fig.II.6, Fig.II.7             | 46  |

| Table.II.3 Estimate parasitic inductances of the connections                                               | 51  |

| Table.II.3 Elements of experiments                                                                         | 56  |

| Table.III.1. Supplied techniques of the high side switching cell                                           | 84  |

| Table.III.2. Specifications of the isolated high side power supply                                         | 86  |

| Table.III.3 Parameters of idealized PSIM simulations.                                                      | 101 |

| Table.III.4 Parameters of realistic PSIM simulations                                                       | 104 |

| Table.III.5 Parameters of the power transistors.                                                           | 110 |

| Table.III.6 Losses in the inverter leg                                                                     | 110 |

| Table.III.7 Parameters of the power transistors of the synchronous rectifier                               | 115 |

| Table.III.8 The sizes of the primary circuit (H-Bridge) and the secondary circuit (rectifier) of converter |     |

| Table.III.9 Three cases of the efficiencies                                                                | 117 |

| Table.III.10 Comparison 3 integrated assessment of drivers                                                 | 128 |

| Table.IV.1 Main features of the ASIC (Source: ID-MOS)                                                      | 138 |

| Table.A.1 Input parameter of the inverter leg and XFAB XT018 for calculations                              | b   |

| Table B.1 Specification of the comparator                                                                  | k   |

| Table.B.2 The designs of the amplification stage by the estimations in simulation and the sir results.     |     |

#### **General Introduction**

Recently, the 21<sup>st</sup> yearly session of Conference of the Parties (COP 21, December 2015, in Paris) have made a decision on the limiting of the global warming less than 2 degree Celsius (2<sup>o</sup>C) compared to pre-industrial level. Eventually, the parties will also effort to limit the increase to 1.5 °C. The 1.5 °C goal will require zero emissions sometime between 2030 and 2050 [1], [2]. In this context, many researchers have been engaged to pursue the efficient energy use; the low-carbon energy and the renewable energy are the key points on this transition.

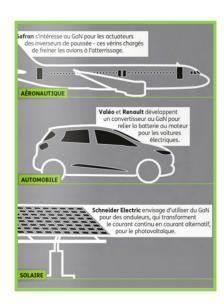

In the renewable energy systems, the power electronics systems are considered critical elements. Similarly, the aeronautic applications, more electric aircrafts are intended to reduce on board weight and increase the efficiency to actuators, saving important quantities of energy. Also, in the automotive applications, the introduction of electrical appliance must be balanced by extremely efficient operations. In general, the power electronics systems are always required to be faster, more robust and more compact, operating in harsh environments, EMI and/or temperature dependent. Several researches are deployed to achieve these requirements which deal with design, control, integration and semiconductor materials.

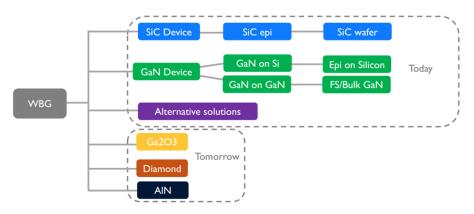

Today, the conventional power electronics semiconductor counter parts based on Si reach their theoretical limitations. Working on the new generation of the semiconductor materials is more essential than ever. The novel components based on GaN, SiC and even coming up Diamond materials are becoming the key factor for the future of the power electronics breakthrough. Because, these semiconductor devices are faster, can perform at higher temperatures and under a better surface R<sub>DSon</sub> tradeoff ratio, because there are a lot of improvements of these WBG components during last decade which make them more and more implemented in advanced power electronics systems.

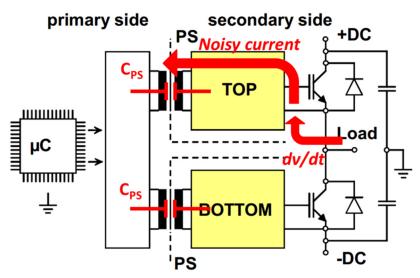

However, high speed power components introduce fast dv/dt and high di/dt voltage and current transients when these devices switch. These are the origins of most of the EMI perturbations in the upper frequency range, from several MHz up to ten and even hundreds of MHz.

As a part of MEGaN project, this research focuses on the gate driver design and optimization for the WBG components, especially for implementation in a low side high side GaN power components configuration in order to optimize the EMI management in harsh environment. In Chapter I, the negative effects of the high dv/dt through the gate driver circuit as the conducted EMI perturbations are detailed and then the potential solutions are described. In this chapter, we understand that the problems of the gate driver circuit are not only located at the system level but also at the component level. Hereby, the proposed solutions are stretched out from the conceptual requirements of the gate driver system to the requirements of the new components of the gate driver. In the next chapters, the solutions are detailed with the validations to overcome the problems of the gate driver side-by-side.

Chapter II shows how the conducted EMI propagation paths are redefined by working on the system level. In this chapter, a novel architecture is depicted for optimizing the conducted EMI perturbation flowing from the power parts to the gate driver circuit when high dv/dt occurs. This chapter pushes also to the extreme optimization of the system by improving the interconnections of the circuit. Moreover, to minimize the negative impacts of the parasitic elements between the gate driver and the component to drive, the devices of the gate driver must be brought close to the WBG power

## Design, characterization and implementation of an integrated CMOS gate driver circuit for GaN components

General Introduction

components where the temperature is critical and to be taken into account; the recommendations talk about which devices should be interconnected close to the power devices and "where".

Also, in this chapter, the driver circuitry conducted EMI problems in more complex systems as the power electronics system with power transistors in series connection or MMC systems are investigated. In order to validate the solution at the system level, simulations and experiments are implemented, results are reported and analyzed.

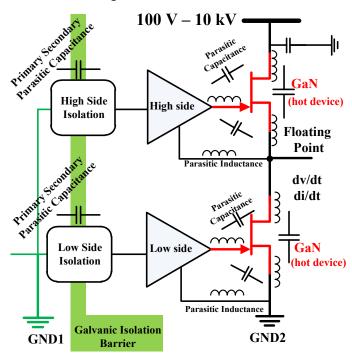

To tackle the recommendations of Chapter II, the works of Chapter III at the components' level are presented in order to minimize the conducted EMI propagation paths at their sources by optimizing the parasitic capacitances of the devices. The temperature becomes critical when the gate driver is implemented as close as possible to the WBG power devices to minimize the parasitic elements. This is an important motivation to design new components for the proposed gate driver circuit implementation, adapted to the constraints of GaN components.

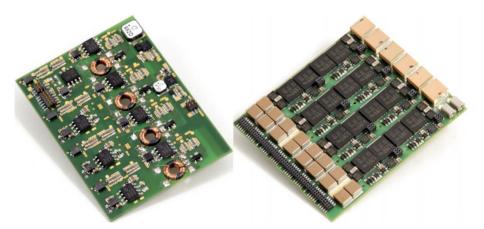

In this thesis, the high temperature integrated power supply of the gate driver is designed after the studies of several power supply techniques and DC/DC converter topologies. At G2ELab, three techniques of the signal transfer units from the low side to the high side of the gate driver are also developed by our team in order to fulfill the requirements of the CMTI and the high temperature operation constraint. The high temperature integrated technology XFAB XT018 PDK is made available by MEGaN project for designing these elements.

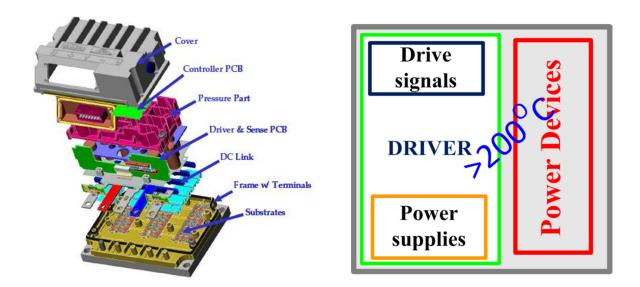

Finally, Chapter IV shows a panorama of the proposed gate driver architecture with the high temperature components. In this chapter, WP3 partners (Work Package 3) introduce a dedicated work on the gate driver circuitry adapted to answer new constraints of GaN components implementations. The final ambition of WP3 is to implement the final version of a "fully" integrated gate driver and associated circuitry allowing to perform and to drive in the best manner advanced power device under strong dv/dt (50V/ns for instance) and under high temperature (up to 250°C at best). Chapter IV describes the specifications and depicts the schematic for implementation of the gate driver.

## **Chapter I**

Gate driver circuit for high speed power devices with improved EMI management in harsh environment:

**Introduction and motivations**

## **Contents of this chapter**

| Chapter I                                                                                                               | 3   |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Gate driver circuit for high speed power devices with improved EMI management environment: Introduction and motivations |     |

| Abstract                                                                                                                | 5   |

| I.1 The sate-of-art of the wide-band gap power components and the challenges for drivers                                | _   |

| I.1.a New specifications of the wide-band gap devices                                                                   | 6   |

| I.1.b Challenges for the design of the gate drivers in the context of GaN power devices                                 | 9   |

| I.1.c MEGaN (Module Electronique GaN) Project                                                                           | 11  |

| I.2 The need of EMI management on the driver circuitry with the evolution of high spec                                  | -   |

| I.2.a The EMI problems on the driver circuit                                                                            | 12  |

| I.2.a-i EMI in general: source, propagation and reception                                                               | 12  |

| I.2.a-ii How does the conducted EMI in common-mode impact on the driver circuit                                         | 16  |

| I.2.a-iii Conducted EMI problems with high speed power devices                                                          | 18  |

| I.2.b Solutions for the conducted EMI problems on the gate driver circuit                                               | 21  |

| I.2.b-i At system level for a low side – high side configuration                                                        | 22  |

| I.2.b-ii At component level                                                                                             | 24  |

| I.2.b-iii Perspective for the complex configurations                                                                    | 24  |

| I.2.c Side issues                                                                                                       | 25  |

| I.2.c-i Thermal considerations of the proposed architecture                                                             | 25  |

| I.2.c-ii The need of redesign the elements of the new architecture gate driver for hi power device                      | _ 1 |

| I.3 Gate driver for high speed power devices with improved EMI management in environments                               |     |

| I.3.a Today solutions of the gate driver for WBG devices                                                                | 27  |

| I.3.b Driver circuit elements of a novel gate driver for high speed devices                                             | 32  |

| I A Canaral research arientation Thesis everyion                                                                        | 3.1 |

#### **Abstract**

In order to present a gate driver circuit for the high speed power devices with EMI management in harsh environment, the beginning point of this research is to present the problems of the high speed power devices – the conducted perturbations on the driver circuit.

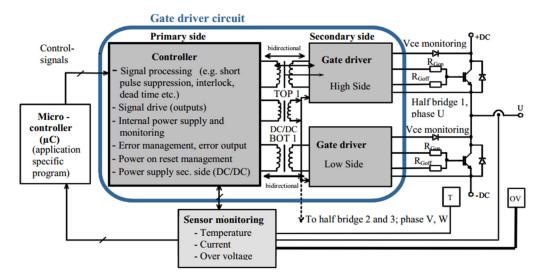

In this chapter, a general introduction on EMI (Electro-Magnetic Interference) is presented. Hence this thesis focuses is on a specific gate driver for a high side – low side switching cell implementation. The gate driver circuit is dedicated for high speed power devices as wide band-gap components. The harsh environment issue is considered as the high temperature and the common mode transient immunity for strong dv/dt.

The sequence of the works is from the conceptual requirements of the system to the component specifications. Finally, the ending point is to show a fully integrated power module in order to overcome the conducted EMI problems which are presented as the orientations of this work.

#### I.1 The sate-of-art of the wide-band gap power components and the challenges for the gate drivers

#### I.1.a New specifications of the wide-band gap devices

Today, the power electronics system takes one of the most important roles in the renewable energy systems. The power electronics conversion circuits are the main pathways for the renewable energies to reach the loads, they are so-called the power electronics energy transfer systems.

Power semiconductor devices are used widely in power electronics energy transfer systems, especially in the renewable energy systems. An impressive development has been made on the technology of power semiconductors since the 1970s [3],[4], [5].

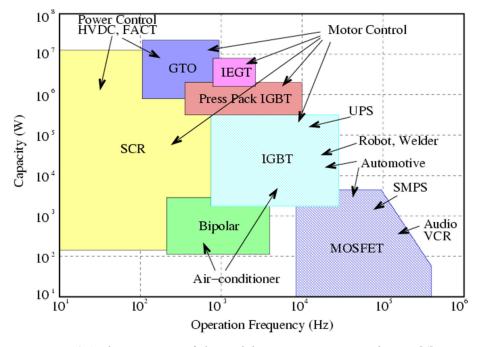

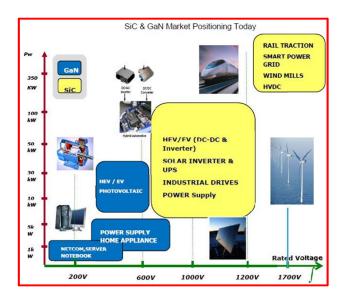

Fig.I.1 shows the application areas of classical Si power semiconductor devices. MOSFETs (Metal-Oxide Semiconductor Field-Effect Transistor) are used for high-frequency applications up to 1 MHz but at low power, less than 10kW. IGBTs (Insulated Gate Bipolar Transistor) are operated at lower switching frequencies but higher power, up to 1MW. And SCRs (Silicon Controlled Rectifier) and GTOs (Gate Turn-Off Thyristor) are mainly used for high-power applications up to 100MW. For medium-power applications such as uninterruptible power supply (UPS), automotive, and robots, IGBT or MOSFET power modules, are constructed with series and parallel connection of power devices inside a package.

Fig.I.1 Application areas of classical discrete power semiconductors [6]

Concurrently, the classic silicon (Si) power components have reached their theoretical physical limitations, especially in terms of  $R_{DS}$ on/cm² and temperature [7]. The wide band-gap (WBG) semiconductors such as the Gallium Nitride (GaN), the Silicon Carbide (SiC), and the Diamond are excellent candidates to replace the Si-based counterparts in the coming years.

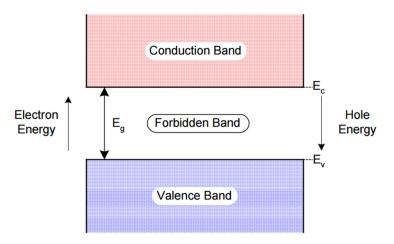

"Wide-band-gap" refers to "high-different-energy-level" which makes the electrons of the semiconductor switch between the two energy levels as in Fig.I.2. There are two bands: the conduction band and the valence band. Between these two bands, the electrons do not exist, it is called the forbidden band.

In the valence band, the electrons have low energy of Ev and are not able to participate to current conduction. If they are excited externally, they can move to the conduction band, where the electrons are able to participate to current conduction. For an electron to move to the conduction band, it needs an amount of energy Eg=Ev-Ec, where Eg is so-called the band-gap.

Fig.I.2 Simplified energy band of the semiconductor [8]

Silicon has a band-gap of  $E_{g\_Si}$ =1.12 eV, this amount of energy is fairly small which is interesting to lower the energy needs to make the material conductive, but can also occur naturally when the material is heated up or heats up for example. This limit for Si-based devices is the reason why the operational maximum temperature is between 125°C and 250°C, depending mainly on material doping levels. Above this temperature, the electrons will switch between the energy levels without any controlled action. WBG materials typically have band-gaps on the order of 3 to 5.5 eV ( $E_{g\_SiC}$ =3.26 eV,  $E_{g\_GaN}$ =3.45 eV,  $E_{g\_SiC}$ =5.45 eV ), allowing them to operate at higher temperatures typical above 300°C [9], [10], [11], [12]. In addition, most of them also have a much higher critical electrical field, in the order of ten times of silicon material (even 30 times for the Diamond), with comparable electron mobility. These very attractive properties enable to size down the drift region of the devices while increasing the doping levels which in turn decreases drastically the  $R_{DSon}$ /cm² of the components. Nowadays, researchers are trying to combine these properties in order to produce devices able to operate at higher voltage and current ratings, making them highly suitable for high power, high power density applications such as portable electrical system, electrical mobility (EV, Train, buses and others), and more electrical aircraft.

Table.I.1 shows the main physical characteristics of Si and WBG materials [8], [13], [14], [15].

| Property                                                                    | Si   | 4H - SiC | GaN  | Diamond |

|-----------------------------------------------------------------------------|------|----------|------|---------|

| Ban-gap, Eg (eV)                                                            | 1.12 | 3.26     | 3.45 | 5.45    |

| Dielectric constant                                                         | 11.9 | 10.1     | 9    | 5.5     |

| Electric breakdown field (kV/cm)                                            | 300  | 2200     | 2000 | 10000   |

| Electron mobility (cm <sup>2</sup> /V.s)                                    | 1500 | 1000     | 1250 | 2200    |

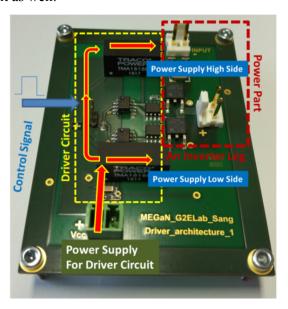

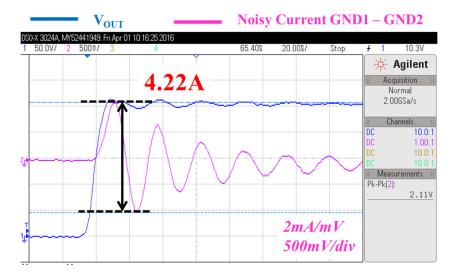

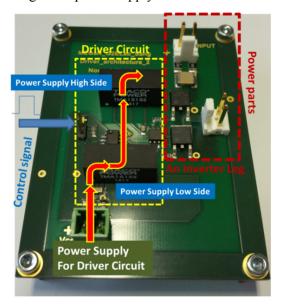

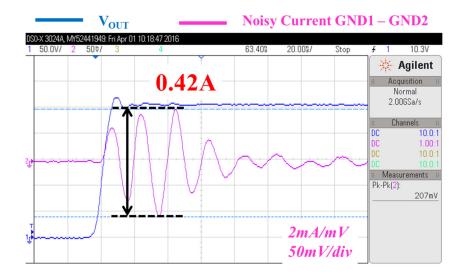

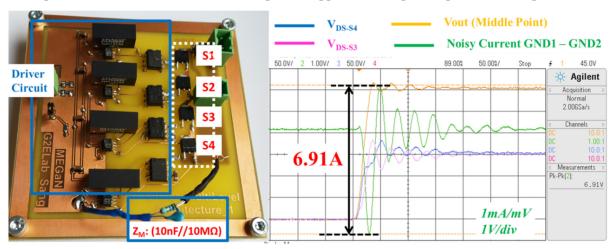

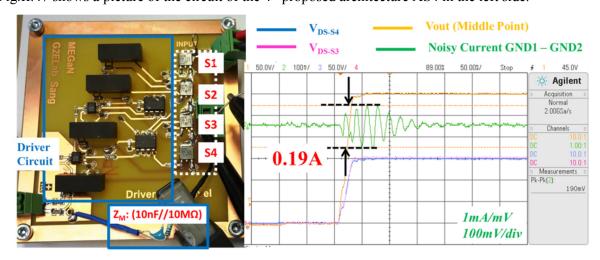

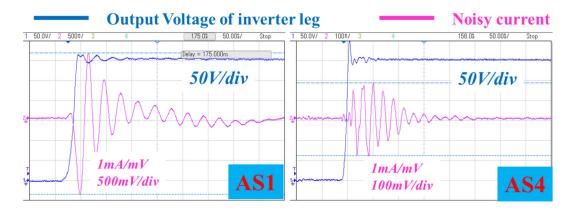

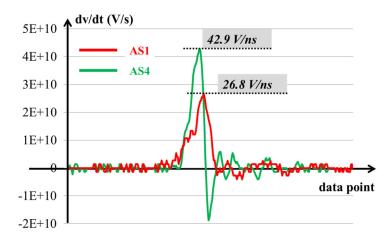

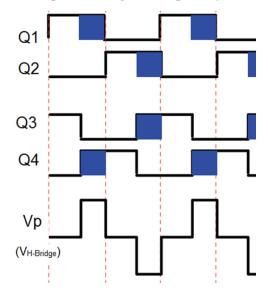

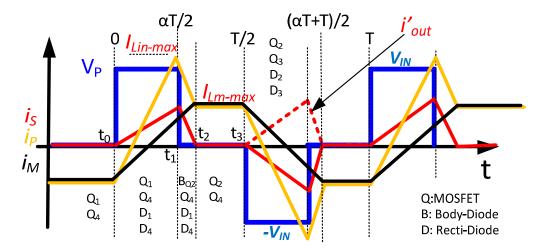

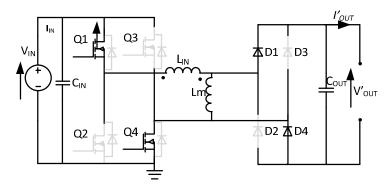

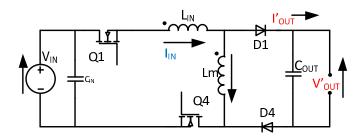

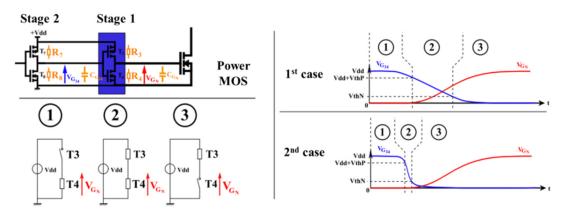

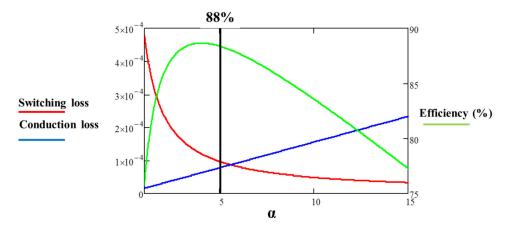

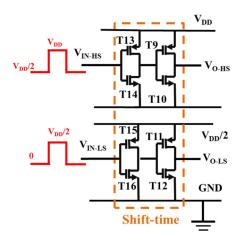

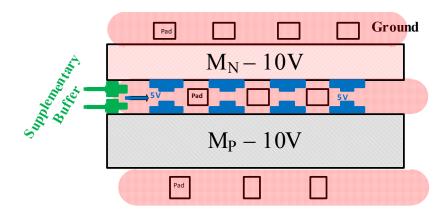

| Hole mobility (cm <sup>2</sup> /V.s)                                        | 600  | 115      | 850  | 850     |