## Analysing and Supporting the Reliability Decision-making Process in Computing Systems with a Reliability Evaluation Framework

Maha Kooli

#### ▶ To cite this version:

Maha Kooli. Analysing and Supporting the Reliability Decision-making Process in Computing Systems with a Reliability Evaluation Framework. Micro and nanotechnologies/Microelectronics. Université Montpellier II, 2016. English. NNT: . tel-01489288

## HAL Id: tel-01489288 https://theses.hal.science/tel-01489288v1

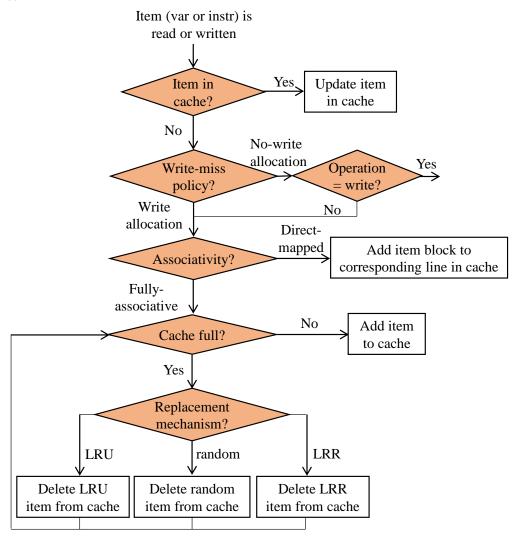

Submitted on 14 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE Pour obtenir le grade de Docteur

Délivré par l'Université de Montpellier

Préparée au sein de l'école doctorale **I2S** Et de l'unité de recherche **LIRMM-CNRS**

Spécialité: Systèmes Automatiques et Microélectroniques

Présentée par Maha KOOLI

Analysing and Supporting the Reliability Decision-making Process in Computing Systems with a Reliability Evaluation Framework

Soutenue le 01/12/2016 devant le jury composé de

Régis LEVEUGLE

Paolo PRINETTO

RAMON CANAL

Mohamed KAÂNICHE

Giorgio DI NATALE

Alberto Bosio

Lionel Torres

Pascal Benoit

Professeur

Professeur Associé

Directeur de recherche

Directeur de recherche

MCf-HDR

Professeur

MCf-HDR

Univ. Grenoble Alpes

Politecnico di Torino

Politècnica de Catalunya

LAAS-CNRS Toulouse

LIRMM-CNRS

LIRMM-UM

LIRMM-UM

LIRMM-UM

Rapporteur

Rapporteur

Examinateur

Examinateur, Président

Directeur de Thèse

Co-encadrant de Thèse

Co-directeur de Thèse

Examinateur

À Firas À ma mère Henda, mon père Nejib

## **Contents**

| Acknow                          | vledgment                                                                                                       | 4                                |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|

| Abstrac                         | et                                                                                                              | 5                                |

| Resume                          | ž                                                                                                               | 6                                |

| I Ov                            | rerview                                                                                                         | 7                                |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | r 1 Introduction  Context and Objectives  CLERECO Project  Contributions  Author Publications  Thesis Structure | 8<br>8<br>10<br>10<br>11<br>12   |

| 2.1<br>2.2<br>2.3               | T 2 Background  Dependability                                                                                   | 13<br>13<br>15<br>16             |

| II R                            | eliability Evaluation via Fault Injection                                                                       | 18                               |

| Introdu                         | action                                                                                                          | 19                               |

| Chapte                          |                                                                                                                 | 20                               |

| 3.1                             | Fault Injection                                                                                                 | 20<br>21<br>23<br>25<br>26<br>27 |

| 3.3                             | 3.2.2 Mutation Testing for Hardware Verification                                                                | 27<br>28                         |

| Chapte                          | r 4 Proposed Fault Injection Methods                                                                            | 30                               |

Contents

| 4.1     | Introduction                                              | 31        |

|---------|-----------------------------------------------------------|-----------|

| 4.2     | LLVM-based Fault Injection                                | 31        |

|         | 4.2.1 Overview                                            | 31        |

|         | 4.2.2 Fault Models                                        | 32        |

|         | 4.2.3 Fault Classification                                | 34        |

|         | 4.2.4 Fault Injection                                     | 35        |

| 4.3     | C-based Fault Injection                                   | 42        |

|         | 4.3.1 Overview                                            | 42        |

|         | 4.3.2 Fault Classification                                | 43        |

|         | 4.3.3 Fault Injection                                     | 43        |

| 4.4     | Comparison                                                | 45        |

| 4.5     | Validation                                                | 46        |

|         | 4.5.1 Simulation-based Fault Injection on Intel Processor | 46        |

|         | 4.5.2 FPGA-based Fault Injection on LEON3 Processor       | 47        |

|         | 4.5.3 Experiments' Setup                                  | 47        |

|         | 4.5.4 Results and Discussion                              | 49        |

| 4.6     | Conclusion                                                | 51        |

| Chapte  | r 5 Memory Subsystem Emulator                             | 53        |

| 5.1     | Introduction                                              | 53        |

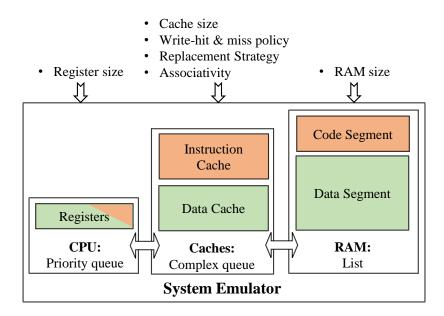

| 5.2     | Subsystem Emulator                                        | 54        |

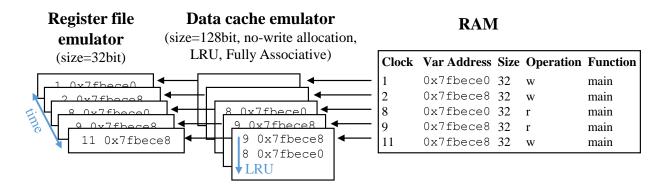

|         | 5.2.1 RAM Emulator                                        | 56        |

|         | 5.2.2 Cache Emulator                                      | 56        |

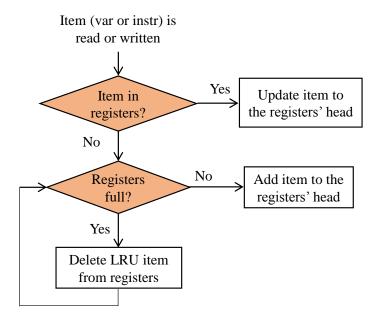

|         | 5.2.3 Register Files Emulator                             | 58        |

| 5.3     | Validation through Memory Emulator                        | 60        |

|         | 5.3.1 Emulators' Integration to Fault Injection           | 60        |

|         | 5.3.2 Experimental Results                                | 62        |

| 5.4     | Conclusions                                               | 66        |

|         |                                                           |           |

| III F   | Reliability Evaluation through Lifetime Analysis          | 68        |

|         | ·                                                         |           |

| Introdu | action                                                    | 69        |

| Chapte  | r 6 State of the Art                                      | <b>70</b> |

| 6.1     | Analytical Reliability Evaluation                         | 70        |

|         | 6.1.1 AVF Computation                                     | 70        |

|         | 6.1.2 Program Analysis                                    | 72        |

| 6.2     | Cache Design Space Exploration                            | 73        |

|         | 6.2.1 DSE for Performance                                 | 74        |

|         | 6.2.2 DSE for Reliability                                 | 74        |

| 6.3     | Conclusion                                                | 75        |

| Chapte  | r 7 Analytical Reliability Evaluation                     | 76        |

| 7.1     | Introduction                                              | 77        |

| 7.1     | Lifetime Analysis                                         | 78        |

|         | 7.2.1 Variable Lifetime                                   | 78        |

|         |                                                           |           |

Contents

|           | 7.2.2 Instruction Lifetime                | 79  |

|-----------|-------------------------------------------|-----|

|           | 7.2.3 Fault Classification                | 81  |

|           | 7.2.4 Lifetime Validation                 | 82  |

| 7.3       | Fault Analysis                            | 83  |

|           | 7.3.1 Faults in Data                      | 83  |

|           | 7.3.2 Faults in Instructions              | 85  |

| 7.4       | Validation                                | 86  |

| 7.5       | Industrial Case Study                     | 87  |

|           | 7.5.1 Flight Management System            | 88  |

|           | 7.5.2 Application Analysis                | 88  |

| 7.6       | Conclusions                               | 91  |

| Chapte    | r 8 Memory-aware Design Space Exploration | 92  |

| 8.1       | Introduction                              | 92  |

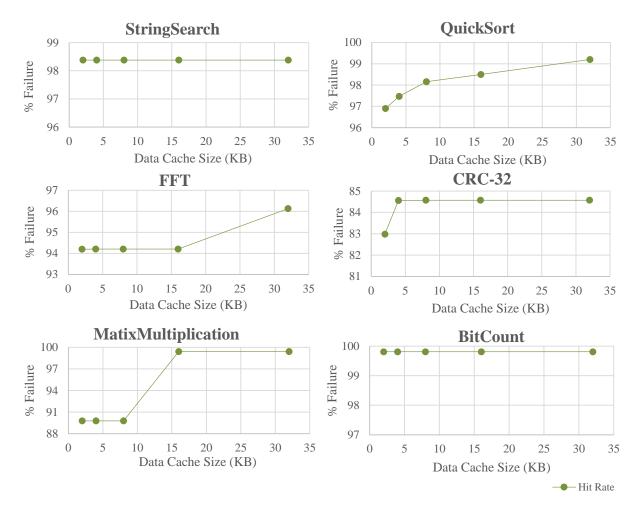

| 8.2       | Cache Characterizations                   | 93  |

| 8.3       | Fault Evaluation                          | 94  |

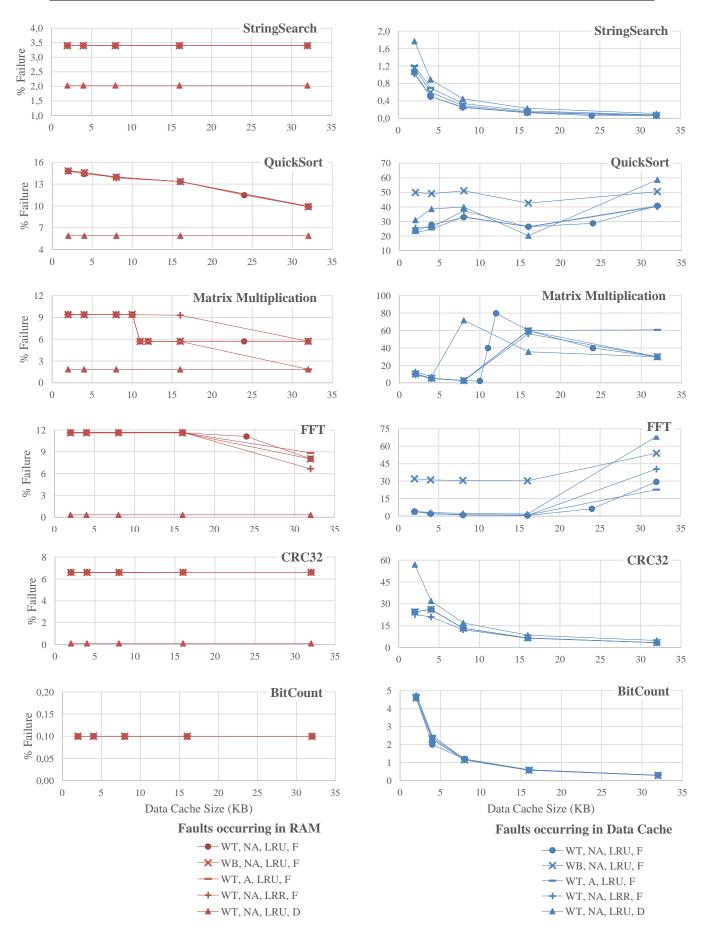

|           | 8.3.1 Faults occurring in Data            | 94  |

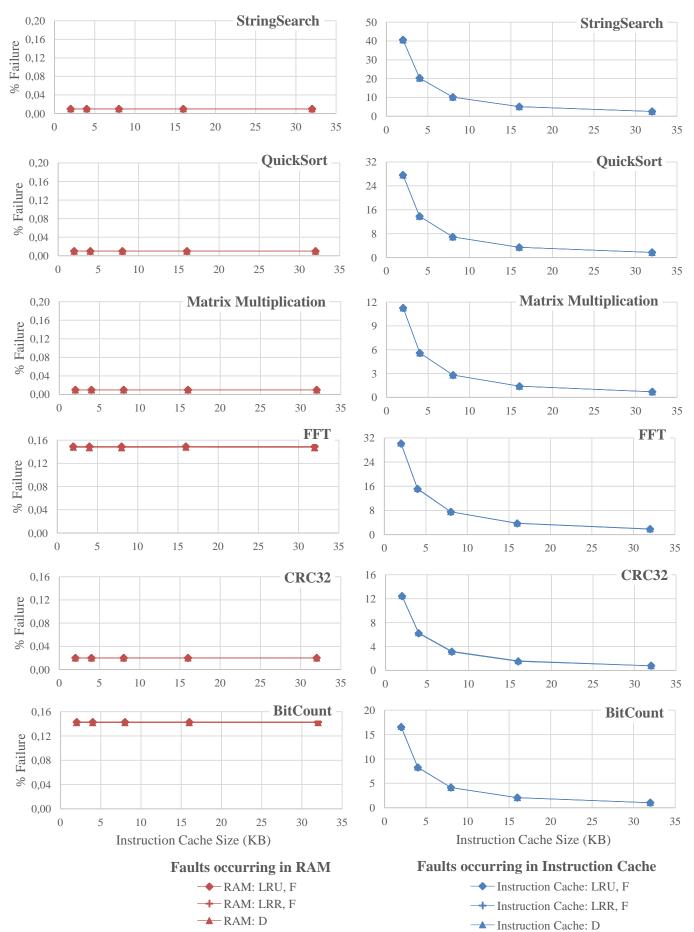

|           | 8.3.2 Faults occurring in Instructions    | 98  |

| 8.4       | Conclusion                                | 100 |

| Chapte    | r 9 Conclusion                            | 101 |

| 9.1       | Summary and Conclusion                    | 101 |

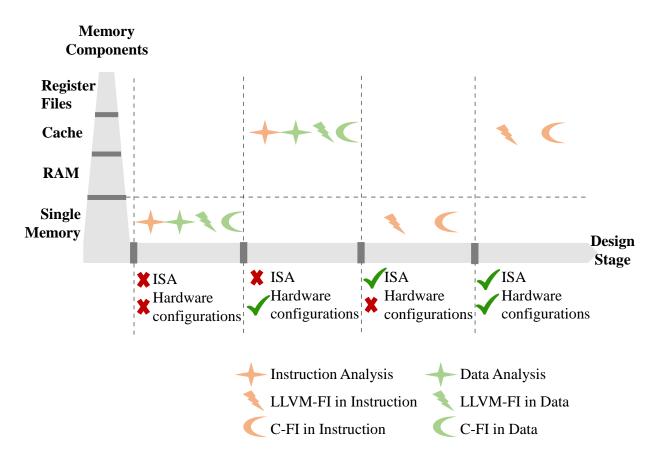

| 9.2       | Application in CLERECO Project            | 103 |

| 9.3       | Future Work                               | 104 |

| Glossar   | ${f y}$                                   | 105 |

| List of 1 | Figures                                   | 106 |

| List of   | Tables                                    | 107 |

| Append    | lix                                       | 108 |

| Bibliog   | raphy                                     | 110 |

## Acknowledgment

J'adresse mes sincères remerciements à ceux qui ont contribué à l'élaboration de cette thèse. Je tiens tout particulièrement à remercier mon directeur de thèse Giorgio Di Natale, qui m'a encadré et soutenu durant ces trois années. Avec son expérience pronfonde, ses conseils bien pertinentes et sa motivation, il m'a aprit le métier de chercheur. Je remercie également mon co-encadrant de thèse Alberto Bosio pour son aide, ses encouragements et sa confiance. Je remercie aussi Pascal Benoit et Lionel Torres qui ont collaboré dans ce projet. Je les remercies pour leur commentaires et encouragements.

Je tiens à remercier mes amis et collègues que j'ai recontré à Montpellier. J'ai partagé avec eux des moments marquants dans cette expérience. Je remercie également mes chers amis partout dans le monde pour leur soutiens et encouragements.

Un remerciement spécial à mon cher mari Firas qui m'a supporté et encouragé avec son amour, ses mots douces et sa patience. Il m'a aidé également sur le plan professionel avec ses idées originales et son expérience.

Enfin, je suis très contente de remercier ma jolie famille, qui était source de force et d'amour dans tous les moments de mon parcours. Je remercie mes très chers parents pour leur tendresse et confiance. Je remercie mes beaux parents pour leur encouragements. Je remercie ma chère soeur Nihel, mon cher frère Achraf et mon beau-frère Nabil. Je vous aime tous très fort.

## **Abstract**

Reliability has become an important design aspect for computing systems due to the aggressive technology miniaturization and the increase of the non interrupted performance that introduce a large set of failure sources for hardware components. The hardware system can be affected by faults caused by physical manufacturing defects or environmental perturbations such as electromagnetic interference, external radiations, or high-energy neutrons from cosmic rays and alpha particles. For embedded systems and systems used in safety critical fields such as avionic, aerospace and transportation, the presence of these faults can damage their components and can lead to catastrophic failures. Investigating new methods to evaluate the system reliability helps designers to understand the effect of faults on the system, and thus to develop reliable and dependable products. Depending on the design phase of the system, the development of reliability evaluation methods can save the design costs and efforts, and will positively impact product time to-market.

The main objective of this thesis is to develop new techniques to evaluate the reliability of complex computing system running a software. The evaluation targets faults leading to soft errors. These faults can propagate through the different layers composing the full system. They can be masked during this propagation either at the technological or at the architectural level. When a fault reaches the software layer of the system, it can corrupt its data, its instructions or the control flow. These errors may impact the correct software execution by producing erroneous results or preventing the application execution and leading to abnormal termination or application hang.

In this thesis, the reliability of the different software components is analyzed at different levels of the system (depending on the design phase), emphasizing the role that the interaction between hardware and software plays in the overall system. Then, the reliability of the system is evaluated via a flexible, fast and accurate evaluation framework. Finally, the reliability decision-making process in computing systems is comprehensively supported with the developed framework (methodologies and tools).

## Resumé

La fiabilité est un aspect important de conception des systèmes informatiques suite à la miniaturisation agressive de la technologie ainsi que le fonctionnement non interrompu qui introduisent un grand nombre de sources de défaillance des composantes matérielles. Le système matériel peut être affecté par des fautes causées par des défauts de fabrication ou de perturbations environnementales telles que les interférences électromagnétiques, les radiations externes ou les neutrons de haute énergie des rayons cosmiques et des particules alpha. Pour les systèmes embarqués et systèmes utilisés dans les domaines critiques pour la sécurité tels que l'avionique, l'aérospatiale et le transport, la présence de ces fautes peut endommager leurs composantes et conduire à des défaillances catastrophiques du systèmes. L'étude de nouvelles méthodes pour évaluer la fiabilité du système permet d'aider les concepteurs à comprendre les effets des fautes sur le système, et donc de développer des produits fiables et sûrs. En fonction de la phase de conception du système, le développement de méthodes d'évaluation de la fiabilité peut réduire les coûts et les efforts de conception. Ainsi, il aura un impact positif sur le temps de mise en marché du produit.

L'objectif principal de cette thèse est de développer de nouvelles techniques pour évaluer la fiabilité globale du système informatique complexe. L'évaluation vise les fautes conduisant à des erreurs dites "soft". Ces fautes peuvent se propager à travers les différentes structures qui composent le système jusqu'à provoquer une défaillance du logiciel. Elles peuvent être masquées lors de cette propagation soit au niveau technologique ou architectural. Quand la faute atteint la partie logicielle du système, elle peut endommager ses données, ses instructions ou le contrôle de flux. Ces erreurs peuvent avoir un impact sur l'exécution correcte du logiciel en produisant des résultats erronés ou empêchant l'exécution de l'application.

Dans cette thèse, la fiabilité des différentes composantes logiciels est analysée à différents niveaux du système (en fonction de la phase de conception), mettant l'accent sur le rôle que l'interaction entre le matériel et le logiciel joue dans le système global. Ensuite, la fiabilité du système est évaluée grâce à des méthodologies d'évaluation flexible, rapide et précise. Enfin, le processus de prise de décision pour la fiabilité des systèmes informatiques est pris en charge avec les méthodes et les outils développés.

## Part I Overview

## Chapter 1

## Introduction

## **Contents**

| 1.1 | Context and Objectives |

|-----|------------------------|

| 1.2 | CLERECO Project        |

| 1.3 | Contributions          |

| 1.4 | Author Publications    |

| 1.5 | Thesis Structure       |

## 1.1 Context and Objectives

Reliability is a main concern while designing electronic systems that are specially used in safety critical fields such as avionics, aerospace, military, and transportation. Reliability is defined as the probability that a component in the system performs continuously in a predictable way without failures. However, the increase of the non interrupted performance and the progressive miniaturization of microelectronic devices used inside these types of system introduce a large set of failure sources for hardware components. The hardware system can be affected by faults caused by physical manufacturing defects or environmental perturbations such as electromagnetic interference, external radiations, or high-energy neutrons from cosmic rays and alpha particles. These faults can damage the system components and lead to catastrophic failures.

Investigating new methods to evaluate the system reliability helps the designers to understand the effects of faults on the system, and thus to develop reliable and dependable products. Depending on the design phase of the system, the development of reliability evaluation methods can save the design cost and effort, and will positively impact the product time to-market.

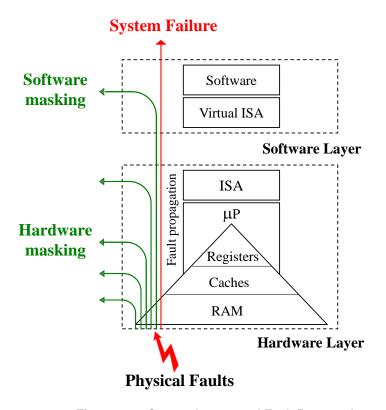

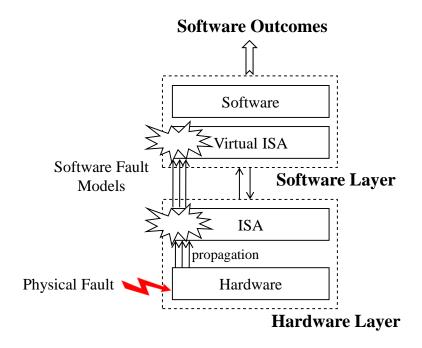

For computing system, the development of methods to evaluate the reliability is a challenging task. Nowadays computing systems are based on complex architectures with multiple micro-processors, memories, external devices and several layers of software (operating system, device drives, user applications) running on the system. The hardware and software layers interact in a way that the fault affecting the hardware and leading to soft errors may propagate through the different system layers, as presented in Figure 1.1. The fault propagates through the

different hardware structures composing the full system. However, they can be masked during this propagation either at the technological or at architectural level. When a fault reaches the software layer of the system, it can corrupt its data, its instructions or the control flow. These errors may impact the correct software execution by producing erroneous results or preventing the execution of the application and leading to abnormal termination or application hang. The software stack can play an important role in masking errors, which enables the improvement of the system reliability.

Figure 1.1: System Layers and Fault Propagation

This thesis aims to propose fast, flexible and accurate methods to evaluate complex computing system when affected by faults that manifest in the underlying hardware layer. We consider computing systems the system that are based on microprocessor and that are running software. The work proposed in this thesis is applied to microprocessor with a single core on a chip and that is running a single thread at one time. The evaluation targets faults leading to soft errors. We focus on studying the software layer role to evaluate the system reliability in different design stages of the system. At advanced design stage, the Instruction Set Architecture (ISA) is known and therefore can be used to perform simulations to analyze how faults propagate through the system components. However, at early design stage of the system when the hardware architecture is possibly not fully defined, the ISA might be unknown and cannot be used to study the effect of faults on the system behavior. The accurate reliability evaluation at this stage is a challenging task.

In this thesis, the reliability of the different software components is analyzed at different levels of the system (depending on the design phase), emphasizing the role that the interaction between hardware and software plays in the overall system. Then, the reliability of the

system is evaluated via a flexible, fast, and accurate evaluation framework. Finally, the reliability decision-making process in computing systems is comprehensively supported with the developed framework (methodologies and tools).

## 1.2 CLERECO Project

This thesis is proposed in the context of the joint FP7 Collaboration European CLERECO Project (Grant No. 611404). CLERECO research project recognizes early accurate reliability evaluation as one of the most important and challenging task throughout the design cycle of the computing systems across all domains. In order to continue harvesting the performance and the functionality offered by technology scaling, current methodologies to evaluate the reliability of the system should be dramatically improved. CLERECO addresses early reliability evaluation with a cross-layer approach considering different computing disciplines, computing system layers and computing market segments to address reliability for the emerging computing continuum. CLERECO methodology considers low-level information such as raw failure rates as well as the entire set of hardware and software components of the system that eventually determine the reliability delivered to the end users. The CLERECO project methodology for early reliability evaluation is comprehensively assessed and validated in advanced designs from different applications provided by the industrial partners for the full stack of hardware and software layers.

This thesis focuses on the tasks of the Work-Package number 4 of the project. The main objective of this work-package is to evaluate the impact that hardware failures may have on the overall system reliability regarding the software stack executed on the platform. In fact, this requires understanding the sensitivity of the software activities to errors generated by hardware faults, and therefore to understand its intrinsic capability of masking these errors. It is important to emphasize that CLERECO focuses only on effects of hardware faults in the software stack. Software reliability engineering including software-testing techniques that target the detection of the software design bugs is not considered in this project.

## 1.3 Contributions

The main contributions of this thesis are:

- Developing new fault injection approaches that aim to evaluate the effect of hardware faults at different level of the system. These approaches allow to evaluate the reliability at different design stage of the system. Depending on the evaluation level, the approaches offer gain in the simulation time and the hardware cost.

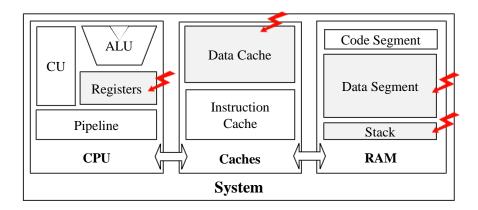

- 2. Proposing a memory subsystem emulator that is able to emulate, at software-level, the behavior of the RAM, the caches, and the register files without the presence of the fully defined hardware. The structure of each unit is designed in a way to be as close as possible to the real system behavior, and as generic as possible to support different characteristics of different microprocessors.

- 3. Introducing a novel analytical methodology that analyzes the effect of hardware faults on the system behavior. The proposed method is accurate, fast, and flexible. It allows

to evaluate the reliability of the different system components. Furthermore, it is used to study a memory-aware design space exploration.

## 1.4 Author Publications

The contributions and results of this thesis have been published and presented in international conferences, journals and workshops.

- A. Vallero, S. Tselonis, N. Foutris, M. Kalioraki, M. Kooli, A. Savino, G. Politano, A. Bosio, G. Di Natale, D. Gizopoulos, S. Di Carlo. Cross-layer reliability evaluation, moving from the hardware architecture to the system level: A CLERECO EU project overview. In Microprocessors and Microsystems Embedded Hardware Design 39(8): 1204-1214, June 2015.

- Maha Kooli, Giorgio Di Natale, Alberto Bosio. Cache Design Space Exploration in Computing Systems for Reliability Improvements. Submitted to IEEE Transactions on Dependable and Secure Computing.

- M. Kooli, G. Di Natale, A. Bosio, P. Benoit, L. Torres. Computing Reliability: On the Differences between Software Testing and Software Fault Injection Techniques. Submitted to Microprocessors and Microsystems.

- A. Vallero, A. Savino, G. M. M. Politano, S. Di Carlo, A. Chatzidimitriou, S. Tselonis, M. Kaliorakis, D. Gizopoulos, M. R. Villanueva, R. Canal, A. Gonzalez, M. Kooli, A. Bosio and G. Di Natale. Cross-Layer System Reliability Assessment Against Hardware Faults. In IEEE International Test Conference (ITC) 2016.

- M. Kooli, G. D. Natale, and A. Bosio. Cache-aware reliability evaluation through LLVM-based analysis and fault injection. In 22nd IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS), Sant Feliu de Guixols, Catalunya, Spain, July 4-6, 2016.

- M. Kooli, F. Kaddachi, G. D. Natale, and A. Bosio. Cache- and register-aware system reliability evaluation based on data lifetime analysis. In 34th IEEE VLSI Test Symposium (VTS), Las Vegas, NV, USA, April 25-27, 2016, pp. 1–6.

- F. Kaddachi, M. Kooli, G. Di Natale, A. Bosio, M. Ebrahimi, M. Tahoori. System-level Reliability Evaluation through Cache-aware Software-based Fault Injection. In Proceedings of the 19th IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Kosice, Slovakia, April 20-22, 2016.

- M. Kooli, A. Bosio, P. Benoit, and L. Torres. Software testing and software fault injection. In 10th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Napoli, Italy, April 21-23, 2015.

- M. Kooli, P. Benoit, G. Di Natale, L. Torres, and V. Sieh. Fault injection tools based on virtual machines. In 9th International Symposium on Reconfigurable and Communication-Centric Systems-on-Chip (ReCoSoC), Montpellier, France, May 26-28, 2014.

- M. Kooli and G. Di Natale. A survey on simulation-based fault injection tools for complex systems. In Proceedings of the 9th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Santorini, Greece, May 6-8, 2014.

- A. Vallero, A. Savino, G. Politano, S. Di Carlo, A. Chatzidimitriou, S. Tselonis, M. Kaliorakis, D. Gizopoulos, M. Riera, R. Canal, A. Gonzalez, M. Kooli, A. Bosio, and G. Di Natale. Early component-based system reliability analysis for approximate computing systems. In 2nd Workshop On Approximate Computing (WAPCO), Prague, January, 18-20, 2016.

- M. Kooli, G. Di Natale. Evaluation of System Reliability at High Level. In GDR SoC-SiP, 2014.

#### 1.5 Thesis Structure

The rest of this thesis is structured as follows.

Part I proceeds by Chapter 2, which presents preliminary definitions and backgrounds relevant for the thesis.

Part II is related to the reliability evaluation via fault injection. Chapter 3 discusses existing works in the literature based on fault injection and mutation testing techniques. Chapter 4 proposes new fault injection environments that are virtual-level and source-code-level. The validation of the proposed methods is discussed through comparisons to hardware-based fault injections. Chapter 5 introduces a novel memory subsystem emulator and provides a validation of the proposed fault injection environments in term of accuracy and simulation time.

Part III is related to the reliability evaluation via lifetime analysis. Chapter 6 explores the state-of-the-art of analytical reliability evaluation techniques and cache design space exploration. Chapter 7 proposes new analytical reliability evaluation technique and validates its accuracy through comparisons to hardware-based fault injections. Chapter 8 provides a memory-aware design space exploration using the proposed analytical approach.

Chapter 9 concludes the thesis, presents the application of the proposed methodologies in the CLERECO project, and discusses different perspectives.

## Chapter 2

## **Background**

#### **Contents**

| 2.1 | Dependability | 13 |

|-----|---------------|----|

| 2.2 | Soft Errors   | 15 |

| 2.3 | LLVM          | 16 |

In this chapter, we provide background and technical definitions related to this thesis, and we present the virtual instruction set architecture used in our works.

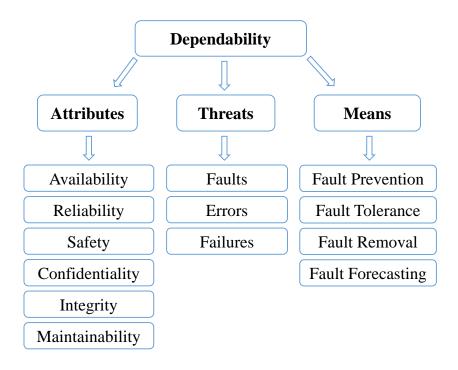

## 2.1 Dependability

Dependability [1] is a key decision factor in today's global business environment. It is first introduced as a global concept that subsumes the usual attributes of reliability, availability, safety, integrity, maintainability, and security [2]. It represents the ability to avoid service failures that can happen to the system more frequently and severely than acceptable. In other words, dependability is the ability to deliver products that can be trusted. Fig. 2.1 presents the schema of the complete taxonomy of dependability. It could also be defined as a measure of the system availability, reliability, and maintainability. Dependability can be determined and measured through three elements: attributes, threats, and means.

The attributes represent the way to measure the dependability. They are represented by the following elements:

- Availability: It represents the probability that the system is available to operate correctly at a given instant of time. A highly available system is a system that will most likely be working at a given instant in time.

- *Reliability:* It represents the probability that a component in the system performs continuously in a predictable way without failure, *i.e.*, for a prescribed time and under exact environmental conditions. A highly reliable system is a system that most likely continues to work without interruption during relatively long period of time.

Reliability is defined over an interval of time rather than an instant in time, which is the case for availability.

Figure 2.1: The Dependability Tree [1]

- Safety: It represents the probability that the system either operates correctly or interrupts its functions in a way that nothing catastrophic happens to the user or the environment.

- *Maintainability:* It represents the measure of how easily the system can be fixed in case of failure. A highly maintainable system is a system that shows high degree of availability when failures can be detected and repaired automatically.

- Confidentiality: It represents the absence of unauthorized disclosure of information.

- *Integrity*: It represents the absence of improper system and data modifications.

- Security: It is a composite of confidentiality, integrity, and authenticity attributes.

Regarding these definitions, most of the attributes are subjective and could not be measured. Only availability and reliability are quantifiable by direct measurements. For example, reliability can be measured as the failure over time, while safety is a subjective evaluation that needs judgmental information in order to have the required level of confidence. This is the reason why techniques developed to evaluate the dependability represent in reality the techniques developed to measure the availability and the reliability.

The threats represent the effects that can touch the dependability of the system. They are undesired and unexpected events possible leading to the non-dependability of the system. They represent the following elements:

• Fault: It is physical defect or imperfection that happens in the hardware, software or human components of the system. A fault can be the cause of specification mistakes, implementation mistakes, external disturbances, physical hardware component defects or

misuses. A fault can be permanent, intermittent or transient depending on its persistence time.

- *Error*: It is the deviation of the system internal state from the right service state. It can also be defined as contradiction between the experimental (or observed) behavior, and the theoretically (or expected) behavior of a component in the system. Errors can be observed during the test session or using special mechanisms such as System Error Detection Mechanism (*e.g.*, hardware exceptions handling, software checks).

- *Failure*: It is the result of the delivered service deviation from the correct service. A failure is also defined as an instance in time when the resulting behavior of the system does not correspond to the required specification.

The relationship between faults, errors, and failures is represented by "the chain of threats" [1]. In fact, an error is the result of the activation of a fault, and a failure occurs when an error propagates to the service interface and becomes the reason of incorrect service. The system component failure may be the cause of permanent or transient fault in the system containing this component.

The means are the techniques and methods that are able to increase the dependability of the system. They include the following techniques:

- Fault Prevention: It deals with avoiding the fault to occur on the system. It could be achieved by integrating development methodologies and good implementation techniques, such as design rules, modularization, use of hardened hardware, use of strongly-typed programming languages.

- Fault Tolerance: It means to prevent failures when faults are present in the system. The system remains working in an expected manner, according to its specifications in the presence of faults. Several studies in the literature present different methods and techniques for fault tolerance, such as control flow checking [3], Algorithm Based Fault Tolerance (ABFT) [4] and Redundancy (space redundancy, time redundancy, information redundancy).

- Fault Removal: It means to decrease the severity and the number of faults in the system. During the development phase, it consists on three steps: the verification, the diagnosis, and the correction. During the use of the system, fault removal is corrective or preventive maintenance. Corrective maintenance aims to remove faults that produced one or more errors, while preventive maintenance aims to uncover and remove faults before causing errors.

- Fault Forecasting: It is conducted by performing an evaluation of the system behavior with respect to fault occurrence or activation. The evaluation has two aspects: qualitative evaluation and quantitative evaluation.

## 2.2 Soft Errors

The size and complexity of the systems used in the safety-critical field lead to significant increase in the number of transient, permanent and intermittent faults in processors. Permanent

faults are defined as faults that exist indefinitely in an element if no corrective action is taken. Thus, they model permanent hardware failures such as an ALU that stops working or a cache line that has a stuck-at fault. Transient faults are defined as faults that can appear and disappear within a given period of time during computation. They are caused by events such as cosmic rays, alpha particle strikes or marginal circuit operation caused by noise for instance. Intermittent faults are malfunctions of a device or system that occur at intervals, usually irregular, in a device or system that functions normally at other times.

In electronics and computing systems, a soft error is the type of error where the signal or the data is altered to a wrong value. Soft errors can be caused by electromagnetic interference, by external radiations, such as high-energy neutrons from cosmic rays and alpha particles. For example, when a particle strikes a sensitive region of the memory cell, the charge that accumulates could exceed the minimum charge needed to flip the value stored in the cell, thus resulting in a soft error.

Soft errors are reversible and can be recovered by a reset, a power cycle or simply a rewrite of the information, which is not the case for hard errors [5] that are caused by irreversible physical changes in a chip during the manufacturing process or by aging phenomena. Soft errors can propagate through the different hardware structures composing the full system, or they can be masked during this propagation either at the technological or at architectural level [6] [7] [8]. If not masked, they can reach the software layer of the system. In computer-based systems, when a soft error reaches the software layer, it can corrupt either the data, the instructions or the control flow of the program. These errors may impact the correct software execution by producing erroneous results or preventing the execution of the application leading to abnormal termination or application hang.

Soft errors arise from Single Event Upset (SEU), Multiple Bit Upset (MBU) and Multi-Cell Upset (MCU) due to ionizing particle (ions, electrons, photons...) striking a sensitive node in a micro-electronic device. The non interrupted performance and the progressive miniaturization of microelectronic devices in the systems make them more susceptible to be affected by such errors [9].

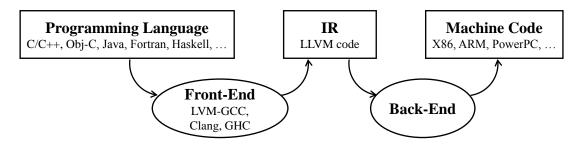

#### **2.3** LLVM

The main goal of this thesis is to develop methods to evaluate the reliability at early design stage of the system. Thus, we need to investigate tools that analyze the software independently from the target hardware architecture. At early design stage, the target Instruction Set Architecture (ISA), which defines the interface between the hardware and the software, might be unknown and therefore cannot be used to evaluate the reliability of the system. The solution is to resort to virtualization techniques that allow to abstract the ISA. The concept of software virtualization ensures the possibility to make analysis without previous knowladge of the actual ISA.

Different alternatives of virtualization environment implementing Virtual Instruction Set Architecture (VISA) are available in the literature [10] [11] [12] [13]. Java is widely used in web-based applications. It has the disadvantage of not being really suitable for both HPC and embedded applications. The JVM is restricted to the Java programming language, thus limiting the spectrum of software that can be analyzed. The .NET framework consists of a virtual machine able to run code in Common Languages Infrastructure (CLI), an object-oriented VISA

that is the lowest level of the framework. LLVM (Low Level Virtual Machine) [13] is a compiler framework that uses virtualization with virtual instruction sets to perform complex analysis of software applications on different architectures. LLVM provides high-level information to compiler transformations at compile-time, link-time, run-time, and idle-time between runs. LLVM uses the Intermediate Representation (IR) as a form to represent code in the compiler. It symbolizes the most important aspect of the framework, because it is designed to host mid-level analysis and transformations found in the optimizer section of the compiler. The LLVM IR is independent from the source language and the target machine.

Figure 2.2: The LLVM Compiler

In this thesis, most of our contributions are based on LLVM. The advantage is the support of different programming languages, and different machine codes. In figure 2.2, we provide the LLVM compiler. As source code front ends, the LLVM compiler supports several programming languages, such as C, C++, Objective-C, Fortran, Python. As machine code back-ends, it supports many instruction set, such as ARM, MIPS, PowerPC, SPARC, x86/x86-64. This means that LLVM permits to define an abstraction layer to make the information obtained at software level and the information obtained at hardware level, compatible and easily exchangeable. In addition to the full tool chain required for software design (*e.g.*, compiler, optimizer), LLVM provides a set of additional tools explicitly devoted to perform investigation of different software properties.

# Part II Reliability Evaluation via Fault Injection

## Introduction

A powerful and useful technique to evaluate the system reliability is the fault injection. It allows to assess the behavior of the system when affected by faults. The fault injection can be performed at different levels of the system. Hardware-based fault injection techniques directly inject faults in the internal processor components using manufactured processor prototype, simulation of the processor architecture or implementation of the processor on FPGA board. These techniques provide accurate evaluation of the system reliability. However, they can not be used at early design stage of the system. Software-based fault injections provide cheaper solution to evaluate the system reliability by modeling the fault injection at abstract level. Nevertheless, they are inaccurate and can not target faults in different system components.

In this part, we propose new fault injection environments that bridge the gap between software- and hardware-based fault injections. Similar to software-based fault injection, the proposed methodologies are fast, cheap and usable at early design stage. Furthermore, they are accurate and target memory system components similar to hardware-based fault injection. We introduce a virtual-level fault injection based on the LLVM virtual ISA, and a source-code-level fault injection based on the C programming language. The proposed methods target faults in both the data and instructions of the software application, and study the effect of these faults on the output of the system that is running this software. In order to target faults occurring in the system components such as the RAM and the caches, we propose a memory subsystem emulator that emulates, at software-level, the behavior of the RAM, the caches, and the register files without requiring fully defined hardware.

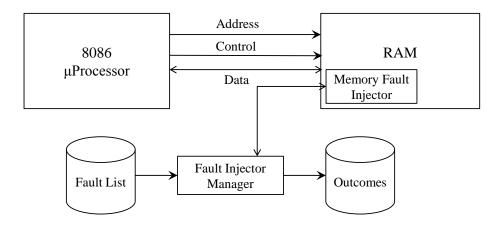

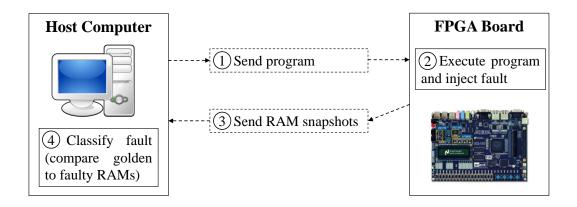

In order to validate the accuracy of the proposed approaches, we perform comparisons to hardware-based fault injections: simulation-based fault injection on the Intel©8086 processor and FPGA-based fault injection on the LEON3 processor. The experimental results prove the accuracy of our approaches with gain in the execution time.

The reminder of this part is structured as follows. Chapter 3 discusses the state-of-the-art on different categories of fault injection techniques, and mutation testing. Chapter 4 introduces the proposed fault injection environments. Chapter 5 presents the implementation of the memory subsystem emulator, explains the integration of this emulator within the proposed fault injection techniques, and provides experimental results to validate the proposed methods.

## Chapter 3

## State of the Art

| Contents |

|----------|

|----------|

| 3.1 | Fault Inj | ection                                     | 20 |

|-----|-----------|--------------------------------------------|----|

|     | 3.1.1     | Hardware-based Fault Injection             | 21 |

|     | 3.1.2     | Software-based Fault Injection             | 23 |

|     | 3.1.3     | Comparison                                 | 25 |

| 3.2 | Mutation  | n Testing                                  | 26 |

|     | 3.2.1     | Mutation Testing for Software Reliability  | 27 |

|     | 3.2.2     | Mutation Testing for Hardware Verification | 27 |

| 3.3 | Discussi  | on 2                                       | 28 |

|     |           |                                            |    |

In this chapter, we discuss the state-of-the-art on the reliability evaluation methodologies based on fault simulation. The fault injection technique is a reliability evaluation technique that targets hardware faults (*e.g.*, soft errors and hard errors). Mutation testing is also a reliability evaluation technique but targets software errors occurring during the design or the implementation stage. It is also used for hardware verification.

Section 3.1 introduces the different categories of the fault injection existing in the literature. Section 3.2 presents mutation testing with its different applications on software and hardware reliability. Finally, Section 3.3 provides comparison between the two methodologies and explains their limitations regarding the goal of this thesis.

## 3.1 Fault Injection

Fault injection is a powerful and useful technique to evaluate the reliability of the systems under faults [14], and in particular to assess the behavior of the system when a fault affects a part of it. Fault injection is based on the realization of controlled experiments in order to evaluate the behavior of the computing systems in presence of faults. This technique can speed up the occurrence and the propagation of faults in the system to observe their effects on the system.

Fault injection is widely studied in the three last decades. Two main classifications of fault injection techniques exist in the literature: hardware-based techniques that directly inject faults

in the target hardware, and software-based techniques that model the fault injection at abstract level.

### 3.1.1 Hardware-based Fault Injection

Hardware-based fault injection allows to inject physical faults (e.g., bit flip, stuck at fault) in the target system. It uses either manufactured processor prototype, or simulation of the processor architecture, or an implementation of the processor on FPGA board. The main advantage of these techniques is the fact that they are performed in realistic conditions which enables to provide accurate results [14].

#### 3.1.1.1 Physical Fault Injection

The physical fault injection techniques are based on the application of external perturbations on the circuits under evaluation to assess their reliability [5]. Particle radiations, laser beams or pin forcing can be used to create realistic faults:

- Radiation Methods: These methods test the device in its real environment and expose it to the particle radiation [15] [16]. The device is put in realistic conditions, but it is quite hard to control where the fault is injected and to set the appropriate energy of particles up.

- FIST [17] is a fault injection tool that uses heavy ion radiation to create transient faults at random locations inside the chip and generates single or multiple bit-flips. FIST directly injects faults inside a chip, which cannot be done with pin-level injections.

- Laser Methods: The laser beams generate a photon-material interaction instead of a particle-material interaction. These methods can better control where the fault is injected. Radiation-based and laser-based methods provide correlation in term of fault evaluation results [18].

- Several studies in the literature use this method to inject faults. In [19], the authors use laser based equipment to inject faults at circuit level. The target faults are random spot defects that may result in discrete faults such as line breaks and short circuits. These faults could therefore contribute significantly to yield losses in stable fabrication lines of VLSI integrated circuits. In [20], the authors describe the use of a pulsed laser for studying radiation-induced single-event transients in integrated circuits. They present the basic failure mechanisms and the fundamentals of the laser testing method, and they illustrate the benefits of using a pulsed laser for studying single-event transients.

- **Pin Forcing:** The values at input/output pins of the device are directly modified to cause the same effect of radiation and laser methods [21]. This solution is cheaper, but it is only applied on simple circuits.

- RIFLE [22] is a pin-level fault injection system for dependability validation. It can be adapted to a wide range of systems, where faults are mainly injected in the processor pins. Different types of faults can be injected. The tool is able to detect whether the injected fault has produced an error or not without requiring of feedback circuits.

MESSALINE [23] is a pin-level fault forcing system. It uses both active probes and sockets to conduct pin-level fault injection. It can inject stuck-at, open, bridging, and complex logical faults. It can also control the lifetime of the fault and its frequency.

Physical fault injection techniques can access locations that are not easy to access by other techniques. They provide accurate evaluation of the system reliability. However they introduce a high risk to damage the system under test and thus a high hardware cost.

#### 3.1.1.2 Simulation-based Fault Injection

The simulation-based fault injections do not operate on the physical device under evaluation, but they target a model of the hardware described using a simulation language, such as VHDL [24] [25] or Verilog [26]. They inject faults in the VHDL models either at run-time or at compile-time. Compared to the physical fault-injections, the simulation-based fault-injection techniques are cheaper in term of set-ups and involved hardware, and can better control the fault location. However, their application creates a computational overhead depending on the complexity of the system design[27].

VERIFY [28] is a VHDL-based fault injection technique that efficiently evaluates the effect of faults on the system reliability. The tool describes the behavior of hardware components in case of faults by extending the VHDL language with fault injection signals together with their rate of occurrence.

LIFTING [26] [29] is a simulator able to perform fault simulations for stuck-at faults and SEU on digital circuits described in Verilog. It is based on an event-driven logic simulation engine to perform the fault injection. LIFTING is different from other fault injection tools, because it provides many features for the analysis of the fault simulation results, which is meaningful for research purposes. In addition, it enables to simulate faults in complex microprocessor-based systems by describing the hardware system components (including the memory). It models the software stored in the memory, and injects faults in all elements of the hardware model.

#### 3.1.1.3 FPGA-based Fault Injection

The FPGA-based fault injections implement the device under evaluation on an FPGA board and perform fault injection campaigns on different system components. These techniques can precisely control where the fault is injected. FPGA-based fault injection methods have recently become more popular since they provide high speed in fault injection experiments compared to simulation- and physical-based fault injection [30]. The fault injection process applies one of the following mechanisms:

- **Reconfiguration Mechanism:** The bits of the FPGA board are reconfigured to inject the fault in the specified location [31] [32] [33] [34]. The fault injection takes place either at run-time or at compile-time. However, the reconfiguration process creates a time overhead [35].

- **Instrumentation Mechanism:** Additional circuit elements in the different processor components are built to inject the fault in the target location, called *Saboteurs* [36] [37] [38]. The activation of these elements generates the required fault. The instrumentation mechanism is therefore faster than the reconfiguration mechanism.

SCFIT [27] [39] is an FPGA-based fault injection technique that is flexible and easy-to-develop. This technique utilizes debugging facilities of Altera [40] FPGAs in order to inject SEU and MBU fault models in both flip-flops and memory units. As this technique uses FPGA built-in facilities, it imposes negligible performance and area overheads on the system.

## 3.1.2 Software-based Fault Injection

The software-based fault injections provide cheaper solution to evaluate the system reliability. They involve modifications in the software state of the system under analysis in order to model hardware faults. The first drawback of these methods is the inability to inject faults into some locations that are not accessible by the software, such as faults occurring in the logic-level. However, these techniques are able to target applications and operating systems, which are not easy to simulate using the hardware-based fault injection. Software-based techniques model the fault injection at abstract levels, such as the operating system, the source code or the virtual machine. The fault is modeled either at compile-time or at run-time. At compile-time, the fault is injected by modifying the software executed by the system (e.g., the source code). At run-time, the fault is injected during the simulation or the execution of the software.

#### 3.1.2.1 Operating-System-level Fault Injection

The operating system presents complex and critical part of the software stack in computerbased systems. Fault injection techniques performed at the operating system level target faults in the system calls and the kernel data structure.

FERRARI [41] is an operating system fault injection technique. It uses traps and system calls in order to modify the execution state of the target application in UNIX system. The fault injection mechanism is based on the interaction between two parallel processes: the fault injection and the target program process. The first process allows to configure the fault injection environment by specifying the target program, the fault number and the fault location. Then, the *fork* system call is used to create the target program process and the *wait* system call is used to wait until the target program completes. In order to perform memory-level faults, the task memory image of the target program is modified before the execution. The target program process allows to execute the *ptrace* system call and the *execv* system call to start target program execution.

XCEPTION [42] is an operating system fault injection technique that uses advanced debugging and performance monitoring features of the actual processor in order to perform fault injections as realistically as possible. It targets the major internal processor units: the *Integer Unit*, the *Floating Point Unit*, the *Memory Management Unit*, the *Internal Data Bus*, the *Internal Address Bus*, the *General Purpose Registers* and the *Branch Processing Unit*.

#### 3.1.2.2 Virtual-level Fault Injection

Fault injections based on virtual machine target hardware faults at the software level, and allow observing complex computer-based systems with operating system and user applications. They allow to simulate the computer system without having the real hardware thanks to the use of virtual machine.

FAUMachine [43] [44] is a virtual machine that permits to install a full operating system, such as Linux, WindowsOpenBSD or Mac OS X, and run them as an independent computers.

As microprocessors, it supports CPUs 80286, 80386, pentium, pentium II and AMD64. FAU-Machine is similar in many aspect to standard virtual machines like QEMU [45] or VirtualBox [46]. The property that distinguishes FAUMachine from the other virtual machines is its ability to support fault injection functionality. The tool targets faults in memory such as transient bit flips, permanent struck-at faults, and permanent coupling faults; in disk CD/DVD drive such as transient or permanent block faults, and transient or permanent whole disk faults; in network such as transient, intermittent, and permanent send or receive faults. Compared to existing fault injection tools, FAUMachine is able to inject faults and observe the whole operating system and software applications. Thanks to the concept of virtual system, this tool provides a high simulation speed for both complex hardware and software systems [44].

Based on the Low Level Virtual Machine (LLVM) [13] [47] [48], the compiler framework that uses virtual instruction sets to perform complex analysis of software applications on different hardware architectures presented in Section 2.3 of Chapter 2, two fault injection techniques are proposed in the literature: LLFI [49] [50] and KULFI [51]. Injecting faults at the virtual instruction set architecture of the application allows to be completely independent from the source code language and the target hardware architecture.

LLFI allows to inject faults into the LLVM intermediate level of the application source code. It performs fault injections at specific program points and data types. The tool is typically used to map fault outcomes back to the source code, and understand the relationship between program characteristics and the various types of fault outcomes. The goal behind LLFI is to build source level heuristics permitting to identify optimal locations for high coverage detections of faults. Regarding the considered fault model, LLFI targets transient hardware faults affecting the processor's computation units. However, the tool does not consider faults in the memory components, the control logic of the processor and the instructions.

KULFI allows to inject random single bit flips into the instructions as well as in the data and the address registers. It permits to simulate faults occurring within the CPU state elements, providing a finer control over the fault injection process compared to LLFI. It enables the user to define some relevant options, such as the fault-occurrence probability, the byte position in which the fault will be injected, and the possibility to choose whether the fault is injected into the pointer register or the data register. KULFI considers the injection of both dynamic faults and static faults. Dynamic faults represent the transient faults and are injected randomly in time during program execution. Static faults represent the permanent faults and are injected randomly before the program execution.

#### 3.1.2.3 Code-level Fault Injection

Fault injection techniques that perform faults at code level require the presence of the source code of the software under test. The fault injection can be either in the original source code or in the binary code of the application. The fault injection is performed by changing the code to model hardware faults.

Jaca [52] [53] is a fault injection tool that is able to inject fault in object-oriented systems. Additional Java classes are defined to generate faults in the attributes, the method return values and their parameters. The use of Javassist toolkit allows to be as independent as possible from the source code and to easily manipulate the byte-code of the loaded classes at run-time. However, this technique does not target faults affecting the instructions.

J-SWFIT [54] is a byte-code-level fault-injection technique. It directly targets the byte-

codes of the compiled Java applications. The architecture of the tool was proposed at abstract level in order to be easily understood and extended. J-SWFIT is based on a set of predefined Java operators. It consists of analyzing the byte codes of compiled Java files, finding locations where specific faults can exist and can be injected each one independently. J-SWFIT allows to evaluate the system behavior in the presence of each fault.

## 3.1.3 Comparison

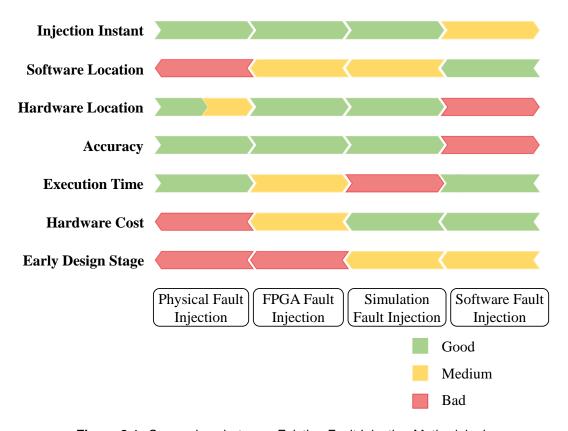

Figure 3.1: Comparison between Existing Fault Injection Methodologies

Fault injection is a powerful method to evaluate the system reliability. A comparison between the hardware- and the software-based fault injections reveals many advantages and drawbacks for both of them [55]. Based on the following criteria, we present in Figure 3.1 a comparison between the previously discussed methods:

• Hardware Cost: To perform fault evaluation, the hardware-based techniques require extra special hardware with different cost levels depending on the adopted method. The physical techniques are the most expensive because they present a serious risk to damage the hardware under test. However, the simulation-based and the software-based fault injection techniques do not make use of additional hardware since they consider the source code either of the simulated processor or of the software application. Thus they are cheaper in term of hardware cost.

- Execution Time: The software-based fault injection techniques offer an important gain in the time of the fault evaluation experiments. For the hardware-based fault injections, the physical techniques require fast fault evaluation. However, the simulation-based techniques require long simulation time. Furthermore, hardware-based techniques have less computational overhead, because they do not insert modifications at software level.

- Fault Evaluation Accuracy: In the literature, the main disadvantage of the software-based fault injection techniques is the lack of accuracy in terms of fault evaluation results [56]. The hardware-based techniques are considered more accurate since they perform fault injections in realistic conditions.

- Fault Location: The software-based methods offer better visibility of the software components, which allows better understanding of the fault effects on the software level. They enable to know exactly which variables or instructions are the most vulnerable to the injected faults. This enhances the development of reliability improvement techniques such as Software Implemented Hardware Fault Tolerance (SIHFT) [57] [4] [58]. However, the hardware-based methods offer better visibility of the internal hardware components, which allows a design space exploration of the target system by changing the characteristics of these components in order to observe the impact on the reliability. Design space exploration is a powerful methodology that helps designers to develop reliable and dependable systems.

- **Injection Instant:** For different hardware-based fault injection techniques, the fault injection instant is controlled in term of clock cycles. Thus, they provide a good precision and help to know which interval of time during the system execution is the most vulnerable to faults.

- Early Design Stage: The physical and the FPGA-based fault injections require fully designed, implemented and constructed hardware architecture. Thus, they can not be used at early design stage of the system. However, the simulation- and software-based fault injections, which simulate the processor under evaluation, require the definition of the ISA of the processor without needing the fully implementation and construction of the hardware.

## 3.2 Mutation Testing

Mutation testing is a technique for software quality improvement used during the software development phase. Its goal is to improve the ability of test cases to detect faults. While mutation testing was first introduced to target software errors (*i.g.*, bugs, design errors), lately it has been applied on hardware verification to target errors introduced during the hardware design. However, mutation testing has not been applied to target soft errors. Since in this thesis we aim to have an evaluation of the system reliability at software level, we present the technique of mutation testing in order to study the possibility to use it to target soft errors.

## 3.2.1 Mutation Testing for Software Reliability

Software reliability is defined as the probability of the correct software performance for a specific period and in a specified environment [59]. It is related to the field of software development, and consists on testing and modeling the ability of the software to behave correctly without failures. The software failures are caused by software faults, which mainly represent errors and bugs caused by effect such as incorrect logic, incorrect statements, incorrect input data, or misinterpretation of the specification that the software is supposed to satisfy in the design. The software reliability is evaluated in the literature through software fault injection and mutation testing [60].

Mutation testing [61] [62] [63] is a software testing technique used to assess the adequacy of test set in terms of its ability to detect software faults. The main idea consists in modifying the original program in order to obtain a faulty program behavior. Mutation testing uses supporting tools to seed artificial faults in the original code of the software in order to generate faulty programs that are supposed to produce incorrect outputs. The faults targeted by mutation analysis represent mistakes that the programmer makes during the implementation or the specification of the program.

Mutation testing is mainly applied in the field of software testing. It is used for the black box and the white box testing [61]. On the one hand, the black box testing is a validation technique for the design level. It permits to test if the program responds to customer requirements when the source code may not be available. At the software design level, mutations are generated to target faults that the programmer may introduce in the program specifications. On the other hand, the white box testing is a validation technique for the software implementation level to test the program source code. It targets the faults that the programmer may introduce in the source code such as coding errors or bugs [61]. At the software implementation level, program mutation is applied on both unit and integration testing [64]. Unit testing is a software testing method where individual units of source code are tested to determine whether they are correct for use or not[65]. Integration testing is the phase in software testing where individual software modules are combined and tested as a group [66]. This step occurs after the unit testing and before the validation testing.

Program mutation is applied on imperative programming language [63] (*e.g.*, C and Fortran), object-oriented programming language [67] [68] (*e.g.*, Java, C++ and C#), and aspect-oriented programming language [69].

As example, for imperative languages, many mutation operators have been explored by researchers, such as statement deletion, statement duplication or insertion, replacement of boolean expressions with true and false, replacement of arithmetic operations with others, e.g. + with \*, replacement of variables with others from the same scope (variable types must be compatible).

## 3.2.2 Mutation Testing for Hardware Verification

Hardware reliability is defined as the ability of hardware components inside the system to perform in a predictable way, for a specific period of time under given environmental conditions, without failures [1]. A system is considered highly reliable when it continues to work without interruption during a relatively long period of time.

During the last decades, mutation testing has acquired consensus as an efficient technique to measure the software quality. In recent works, the effectiveness of mutation analysis in

hardware verification has also been proved in different levels of abstraction [70]. The purpose of the hardware verification is to detect and correct errors (*i.e.*, bugs) introduced during the hardware design. These errors can be incorrect logic, incorrect statements, or misinterpretation of the specification that the hardware is supposed to satisfy.

Mutation testing has been applied on Hardware Description Languages (HDLs), such as Verilog and VHDL. In [71], the authors use mutation analysis to study the ability of the test cases to detect errors, and improve the functional verification process of VHDL description. In [72], the authors reuse transaction level modeling mutation analysis at Register Transfer Level (RTL). They demonstrate how this can help designers to optimize the time of simulation at RTL on the one hand, and to improve the RTL test-bench quality on the other hand.

Mutation testing has also been applied to language modeling and verification for system level hardware, such as SystemC [73] [74]. In [75], the authors propose to assess the verification quality for concurrent SystemC programs. They introduce a novel mutation analysis based on coverage metrics. In [76], the authors propose a C/C++/SystemC error and mutation injection tool to facilitate the development on high-level coverage metric and diagnosis. In [77], the authors present an automatic fault localization approach for SystemC transaction level modeling designs. They target typical transaction level modeling faults, such as accidentally swapped blocking and non blocking transactions, erroneous event notification, or incorrect transaction data.

### 3.3 Discussion

| Fault Injection           |                                                                                                             | Mutation Testing                                                              |

|---------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Faults                    | Physical faults leading to soft and hard errors                                                             | Software faults occurring in the design or the implementation of the software |

| Fault Location            | The ISA of the microprocessor, the real hardware system, the virtual system, the source/bite-code code, ect | The software source code                                                      |

| Cost                      | High execution time and hardware cost                                                                       | High computational cost                                                       |

| Automation                | Automatic output analysis                                                                                   | Manual Analysis of equivalent mutants                                         |

| Reliability<br>Evaluation | Accurate system reliability evaluation for hardware-based fault injection                                   | Good assessment of the test set quality                                       |

Table 3.1: Fault Injection versus Mutation Testing

In this chapter, we presented fault injection and mutation testing as useful techniques to evaluate the reliability of different system layers (*i.e.*, software and hardware systems). In Table 3.1, we present a comparison between the two methodologies. Even if their targets and objectives are different, mutation testing and fault injection are both based on introducing artificial faults into the system under evaluation and observing their impact on its performance.

Mutation testing evaluates the quality of software test set. It quantifies the test set ability to detect faults occurring during software implementation. It has been also applied on hardware verification. However, it does not target soft errors that may occur in the hardware layer

either at run-time or at standstill, which are the main target of the reliability evaluation in this thesis. Hardware-based fault injection techniques target this type of faults, but the evaluation is hardware-dependent. They require to have the fully designed hardware architecture, which could not be available at early design stage of the system. In addition, the fault evaluation is costly in terms of execution time. Existing software-based fault injections also target soft errors, but their main disadvantage is the inaccuracy of the fault evaluation.

The goal of the next chapter is to evaluate soft errors at software level trying to be, at some points, as independent as possible from the target hardware architecture. We aim to bridge the gap between the software and hardware reliability evaluation techniques. We propose new fault injection environments that evaluate hardware faults at different software levels. We couple (i) mutation analysis to have a software-level evaluation, and (ii) fault injection to target hardware faults.

## **Chapter 4**

## **Proposed Fault Injection Methods**

| Contents |                                                           |

|----------|-----------------------------------------------------------|

| 4.1      | Introduction                                              |

| 4.2      | LLVM-based Fault Injection                                |

|          | 4.2.1 Overview                                            |

|          | 4.2.2 Fault Models                                        |

|          | 4.2.3 Fault Classification                                |

|          | 4.2.4 Fault Injection                                     |

| 4.3      | C-based Fault Injection                                   |

|          | 4.3.1 Overview                                            |

|          | 4.3.2 Fault Classification                                |

|          | 4.3.3 Fault Injection                                     |

| 4.4      | Comparison                                                |

| 4.5      | Validation                                                |

|          | 4.5.1 Simulation-based Fault Injection on Intel Processor |

|          | 4.5.2 FPGA-based Fault Injection on LEON3 Processor       |

|          | 4.5.3 Experiments' Setup                                  |

|          | 4.5.4 Results and Discussion                              |

| 4.6      | Conclusion                                                |

In this chapter, we propose new fault injection environments: a virtual-level approach and a source-code-level approach. The validation of the proposed methods is discussed through comparisons with hardware-based fault injections.

Section 4.1 discusses the goal of the proposed methodologies and the advantages compared to related work. Section 4.2 introduces the LLVM-based fault injection. Section 4.3 presents the C-based fault injection. Section 4.4 provides a comparison between the two techniques. Section 4.5 exposes experimental results to validate the proposed approaches. Finally, Section 4.6 concludes the chapter.

#### 4.1 Introduction

One of the goals of this thesis is to evaluate, at early design stage, the reliability of computing systems that are running software. At this stage of the system design, the hardware architecture is not yet fully defined. Thus, it is a challenging task to develop methods that accurately evaluate the system reliability. Based of fault injection, as one of the most used technique to evaluate the reliability, we present in this chapter the first contribution of this thesis. In particular, we propose two fault injection environments: a virtual-level fault injection environment based on LLVM, and a source-code-level fault injection environment based on the C programming language. Both methods allow to evaluate the behavior of the system against soft errors at software level and at different stages of the system design.

Compared to fault injection techniques existing in the literature, the proposed fault injection environments present several outcomes. In comparison with the hardware-based fault injection, the main advantage consists in the absence of the hardware under test. This makes the reliability evaluation less expensive in terms of hardware cost and execution time. In addition, while the hardware-based techniques are dependent to the target hardware architecture, the proposed approaches can be easily applied on different hardware architectures. Furthermore, the proposed fault injection environments offer a better observation of the software components, in particular the fault location in terms of space (i.e. which data or instruction is affected by the fault). This allows a better understanding of the fault effects at software level and enhances the development of reliability improvement techniques. In comparison with existing software-based fault injection, the main contribution of the proposed approaches consists in the good accuracy of the fault evaluation. Existing software-based methods are inaccurate, as discussed in Subsection 3.1.2, because they do not perform fault injection in realistic conditions. In addition, they do not target the evaluation of faults in the different system memory components such as the RAM or the caches, which is performed using the proposed methods. Furthermore, our approaches offer a better visibility of the system memory units, which allows to explore the design space of the target system by easily changing the configurations of its components in order to observe the impact on the reliability.

All the discussed advantages of the proposed fault injection environments will be proved by experimental results in Chapter 5.

## 4.2 LLVM-based Fault Injection

In this section, we propose new fault injection environment based on the virtual ISA of LLVM. It provides reliability evaluation of the computing system by injecting a set of fault models that represent the effect of soft errors on the software.

#### 4.2.1 Overview

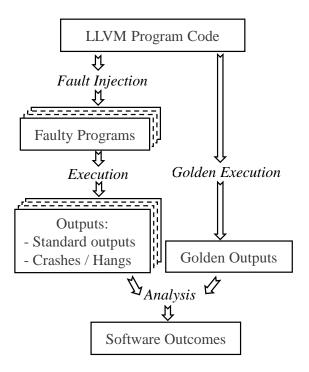

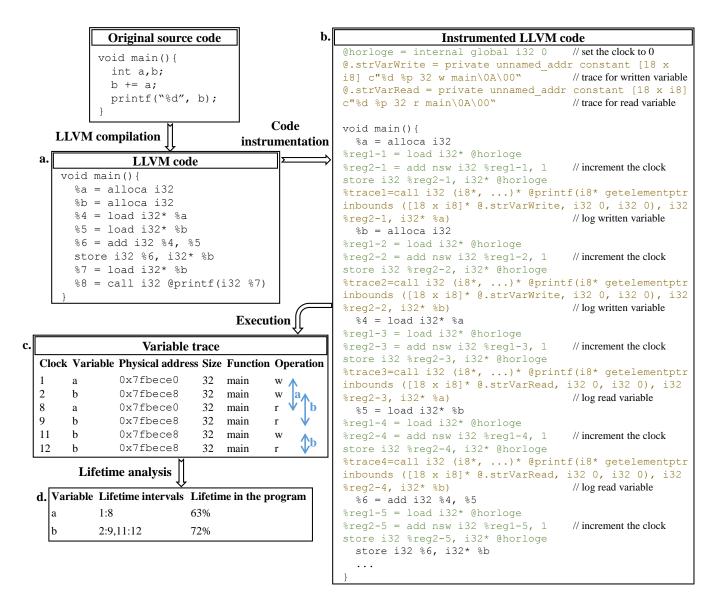

The proposed fault injection environment is based on LLVM and is able to collect data about the software reliability without resorting to predefined hardware platform. The proposed tool permits to inject a set of software fault models into the LLVM intermediate code level of the application, and to observe the outcomes on the software layer.

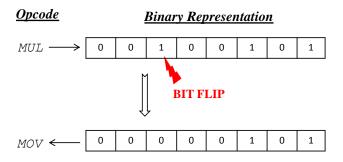

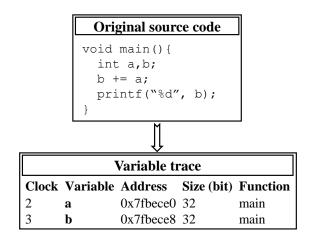

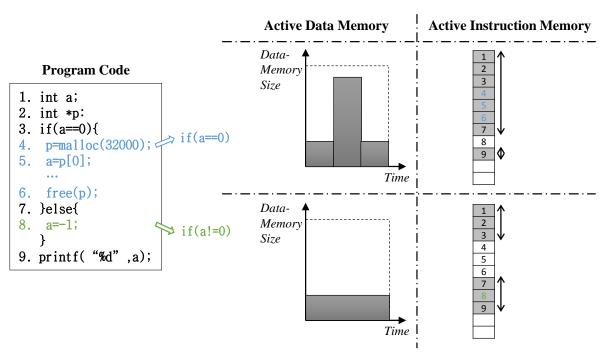

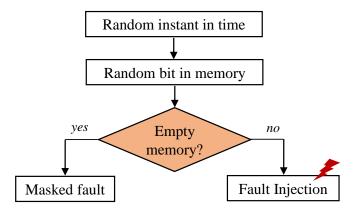

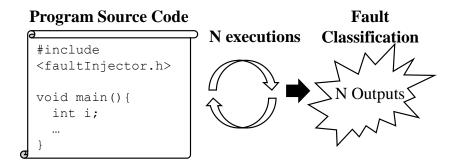

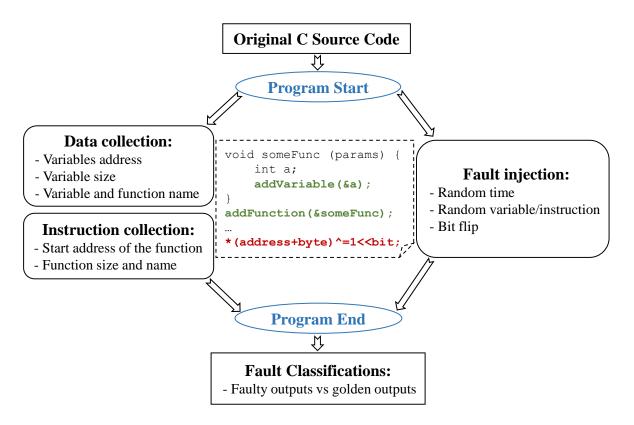

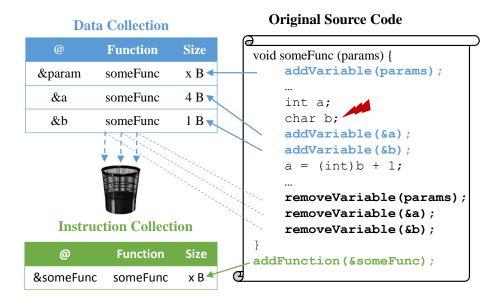

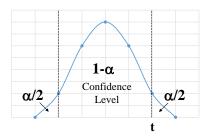

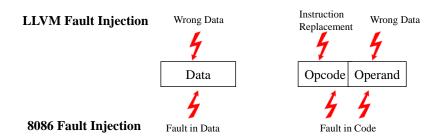

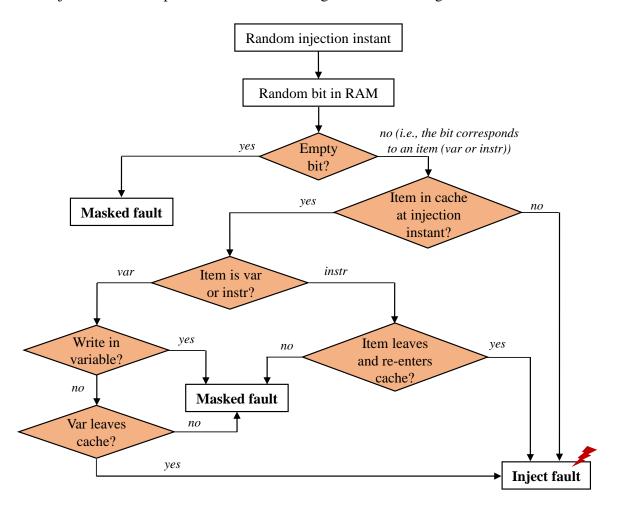

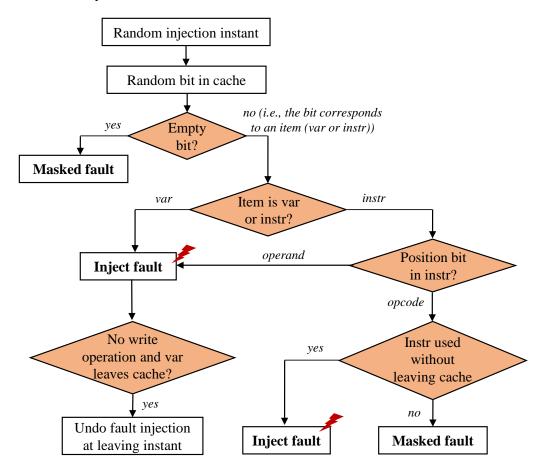

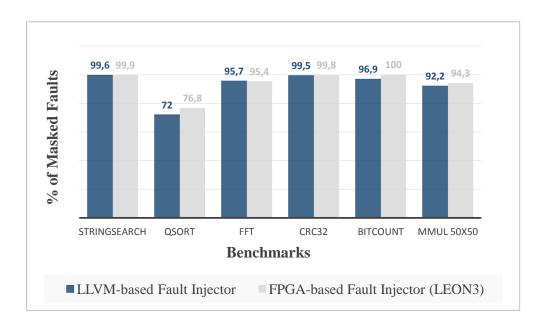

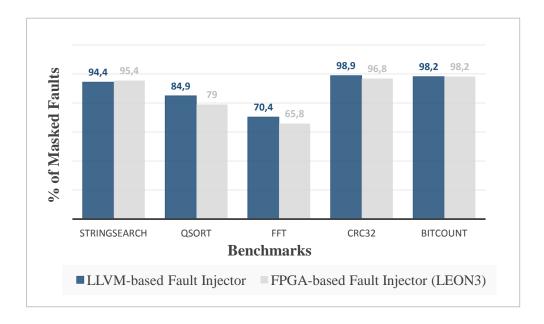

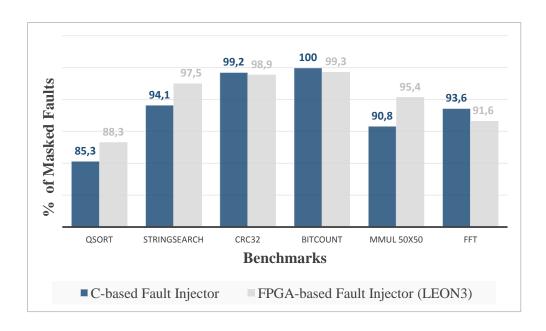

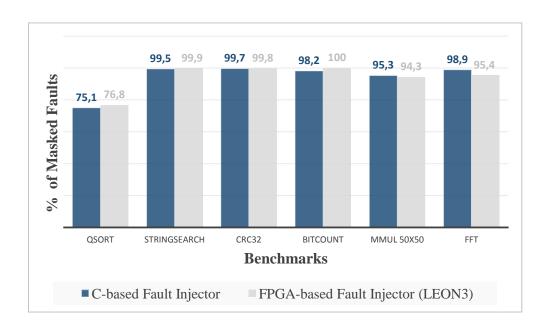

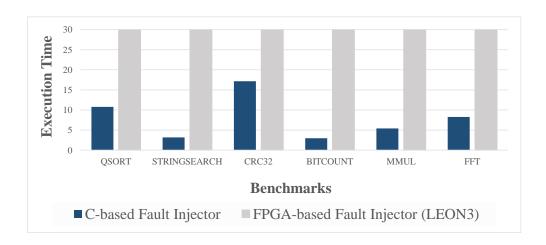

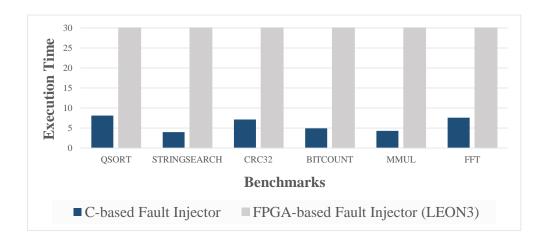

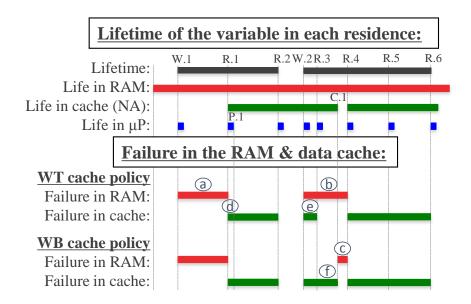

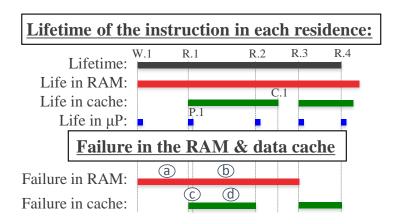

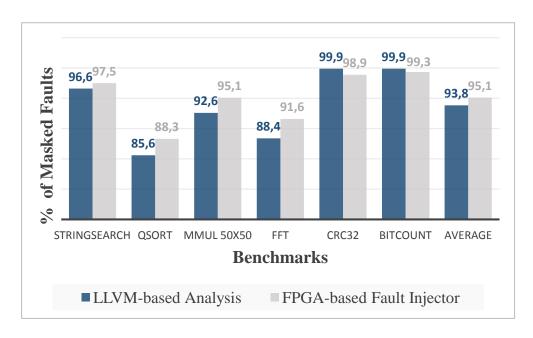

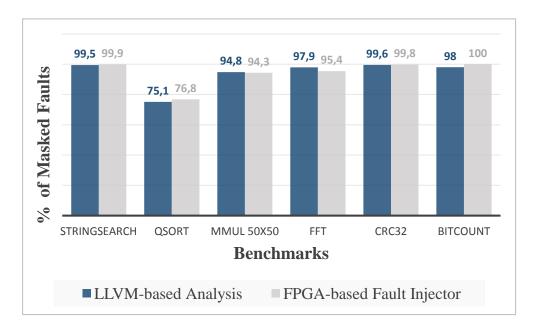

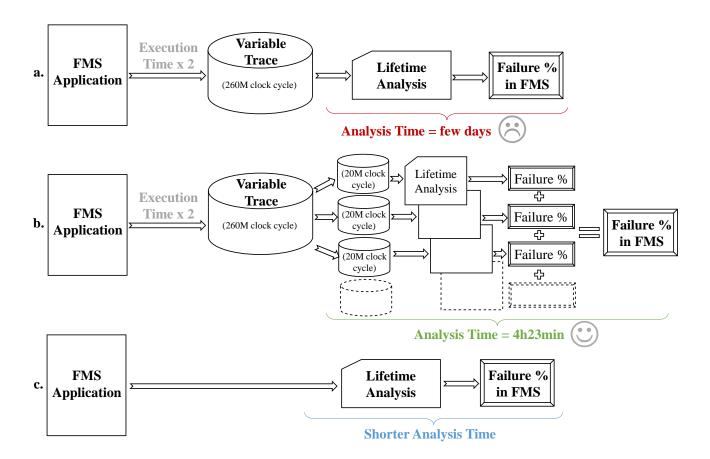

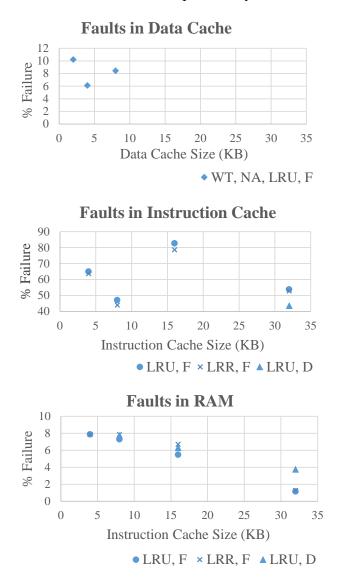

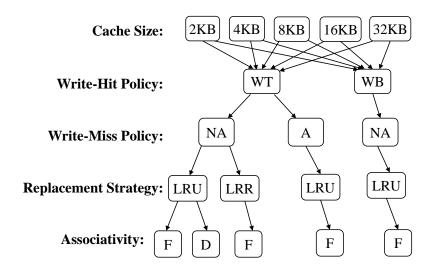

The main advantages of this approach are: (i) achieving speed up of the simulation time compared to hardware-based fault injection techniques, (ii) targeting faults in both the data and the instructions with only considering the software layer, (iii) targeting faults affecting hardware components such as the cache without requiring a fully designed hardware architecture, (iv) having accurate results and precisions in the fault location in space and time, which could enhance the development of reliability improvement methods.