## Automatic synthesis of hardware accelerator from high-level specifications of physical layers for flexible radio

Ganda Stéphane Ouedraogo

#### ▶ To cite this version:

Ganda Stéphane Ouedraogo. Automatic synthesis of hardware accelerator from high-level specifications of physical layers for flexible radio. Networking and Internet Architecture [cs.NI]. Université de Rennes, 2014. English. NNT: 2014REN1S183. tel-01492963

#### HAL Id: tel-01492963 https://theses.hal.science/tel-01492963

Submitted on 20 Mar 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Traitement du signal et télécommunications

Ecole doctorale Matisse

présentée par

## Ganda Stéphane OUEDRAOGO

préparée à l'unité de recherche IRISA (UMR 6074) Institut de Recherche en Informatique et Systèmes Aléatoires École Nationale Supérieure des Sciences Appliquées et de Technologie

Automatic Synthesis

of Hardware Accelerators

from High-Level

Specifications of Physical

Layers for

Flexible Radio

Thèse soutenue à Lannion le 10 décembre 2014

devant le jury composé de :

Tanguy RISSET

Professeur, INSA de Lyon / rapporteur

Renaud PACALET

Directeur d'études, Institut Mines-Télécom / Télécom ParisTech / rapporteur

Christophe MOY

Professeur, Supelec Rennes / examinateur

Dominique NOGUET

Ingénieur recherche, CEA-LETI / examinateur

Olivier SENTIEYS

DR INRIA / directeur de thèse

Matthieu GAUTIER

MCF, Université de Rennes 1 / co-directeur de thèse

#### Remerciements

À mes parents, à ma famille, à mes amis.

$\grave{\mathbf{A}}$  mes encadrants.

Aux membres de l'équipe CAIRN.

## Contents

| 1 | Intr                        | roduction                                                 | 13 |

|---|-----------------------------|-----------------------------------------------------------|----|

|   | 1.1                         | Internet of Things (IoT) and Software-Defined Radio       |    |

|   |                             | (SDR)                                                     | 13 |

|   | 1.2                         | Design Methodologies                                      | 13 |

|   | 1.3                         | The Proposed Methodology and the Main Contributions       | 15 |

|   | 1.4                         | The Outline                                               | 15 |

|   |                             |                                                           |    |

| Ι | $\mathbf{R}$                | ACKGROUND                                                 | 17 |

| • | Dı                          | TOTAL OT THE                                              | Τ. |

| 2 | $\mathbf{Dig}$              | ital Radio and Software-Defined Radio                     | 19 |

|   | 2.1                         | Introduction                                              | 20 |

|   | 2.2                         | Introduction to Digital Communication                     | 21 |

|   |                             | 2.2.1 Symbol Mapping                                      | 21 |

|   |                             | 2.2.2 Channel Access Techniques                           | 24 |

|   |                             | 2.2.3 Pulse Shaping                                       | 25 |

|   | 2.3                         | Digital Communication Technologies                        | 27 |

|   |                             | 2.3.1 DSP Software Platforms and Programming Environment  | 27 |

|   |                             | 2.3.2 DSP Hardware Platforms and Programming Environment  | 28 |

|   | 2.4                         | Flexible Radios                                           | 29 |

|   |                             | 2.4.1 Cognitive Radios                                    | 30 |

|   |                             | 2.4.2 Adaptive Coding and Modulation (ACM) Technique      | 31 |

|   | 2.5                         | Software-Defined Radios                                   | 31 |

|   |                             | 2.5.1 Motivations and Main Features                       | 32 |

|   |                             | 2.5.2 Survey of SDR Platforms                             | 33 |

|   |                             | 2.5.3 SDR Design Methodologies                            | 35 |

|   | 2.6                         | FPGA Platforms for SDR                                    | 37 |

|   | 2.7                         | Conclusion                                                | 38 |

| 3 | $\operatorname{Th}\epsilon$ | e Waveforms of Interest                                   | 39 |

|   | 3.1                         | Introduction                                              | 40 |

|   | 3.2                         | The IEEE 802.15.4 Standard                                | 40 |

|   |                             | 3.2.1 ZigBee Generalities                                 | 40 |

|   |                             | 3.2.2 The IEEE 802.15.4 PHY                               | 40 |

|   |                             | 3.2.3 State of the art of IEEE 802.15.4 SDR transceivers  | 43 |

|   | 3.3                         | The IEEE 802.11 Standards                                 | 45 |

|   |                             | 3.3.1 Generalities                                        | 45 |

|   |                             | 3.3.2 The IEEE 802.11a Physical Layers (PHYs)             | 45 |

|   |                             | 3.3.3 State-of-the-art of IEEE 802.11a/p SDR transceivers | 48 |

|   | 3.4                         | Conclusion                                                | 49 |

4 CONTENTS

| 4 | $\mathbf{Hig}$ | h-Level Designing of Physical Layers (PHYs)                        | 51 |

|---|----------------|--------------------------------------------------------------------|----|

|   | 4.1            | Introduction                                                       | 52 |

|   | 4.2            | Model-Driven Engineering                                           | 52 |

|   |                | 4.2.1 Generalities                                                 | 52 |

|   |                | 4.2.2 Domain Specific Languages (DSLs)                             | 52 |

|   |                | 4.2.3 Eclipse Modeling Framework (EMF) and Xtext/Xtend             | 53 |

|   |                | 4.2.4 Some relevant MDE-based technologies for embedded systems    | 55 |

|   | 4.3            | High-Level Synthesis (HLS)                                         | 56 |

|   |                | 4.3.1 A bit of history                                             | 56 |

|   |                | 4.3.2 High-Level Synthesis Fundamentals                            | 57 |

|   |                | 4.3.3 Advantages of HLS                                            | 58 |

|   |                | 4.3.4 Examples of mature HLS Tools                                 | 60 |

|   | 4.4            | Bringing together HLS and MDE for FPGA-SDR                         | 61 |

|   |                | 4.4.1 Dataflow Model of Computation (MoC)                          | 61 |

|   |                | 4.4.2 SDR Control Requirements                                     | 62 |

|   | 4.5            | In a Nutshell                                                      | 62 |

|   | 4.6            | Conclusion                                                         | 63 |

|   | 1.0            | Conclusion                                                         | 00 |

|   |                |                                                                    |    |

| Π | $\mathbf{C}$   | ONTRIBUTIONS                                                       | 65 |

|   |                | · · · · · · · · · · · · · · · · · · ·                              |    |

| 5 |                | Domain-Specific Language (DSL) for FPGA-Based SDRs                 | 67 |

|   | 5.1            | Introduction                                                       | 68 |

|   | 5.2            | The Proposed Design Flow                                           | 68 |

|   |                | 5.2.1 Waveform Modeling                                            | 68 |

|   |                | 5.2.2 Waveform Compiling                                           | 69 |

|   |                | 5.2.3 Verification and Validation $(V\&V)$                         | 69 |

|   |                | 5.2.4 Platform Integration                                         | 70 |

|   | 5.3            | Conceptual aspects of the proposed DSL                             | 70 |

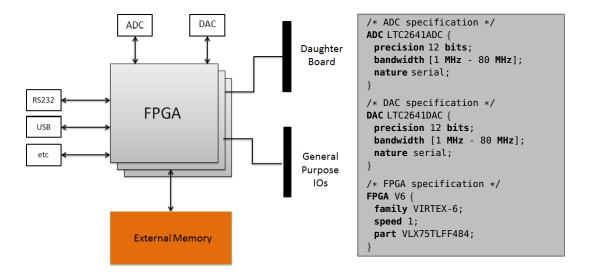

|   |                | 5.3.1 Platform Modeling                                            | 70 |

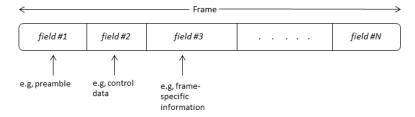

|   |                | 5.3.2 DSL-Based Data-Frame Modeling                                | 71 |

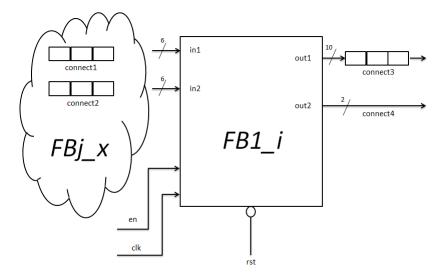

|   |                | 5.3.3 DSL-Based Dataflow Modeling                                  | 73 |

|   | 5.4            | Frame-Based Control Unit                                           | 76 |

|   |                | 5.4.1 A Hierarchical FSM (HFSM) for FPGA-based Dataflow Control    | 76 |

|   |                | 5.4.2 Frame-based Control Algorithm                                | 77 |

|   |                | 5.4.3 Simulation of the proposed HFSM on the StateFlow Environment | 80 |

|   | 5.5            | Library of HLS/RTL-based Functional Blocks                         | 81 |

|   | 5.6            | Conclusion                                                         | 82 |

|   |                |                                                                    |    |

| 6 |                | e DSL-Compiling Framework                                          | 83 |

|   | 6.1            | Introduction                                                       | 84 |

|   | 6.2            | DSL Implementation                                                 | 84 |

|   |                | 6.2.1 Parsing                                                      | 84 |

|   |                | 6.2.2 Abstract Syntax Tree (AST)                                   | 85 |

|   | 6.3            | DSL Compiler Flow                                                  | 85 |

|   |                | 6.3.1 AST Verification                                             | 85 |

|   |                | 6.3.2 Waveform Generation                                          | 87 |

|   | 6.4            | Platform Programming                                               | 90 |

|   | 6.5            | Conclusion                                                         | 91 |

|   |                |                                                                    |    |

| 7 |                | Case Study: DSL-based Specification and Implementation of PHYs     | 93 |

|   | 7.1            | Introduction                                                       | 94 |

|   | 7.2            | Testbed Description                                                | 94 |

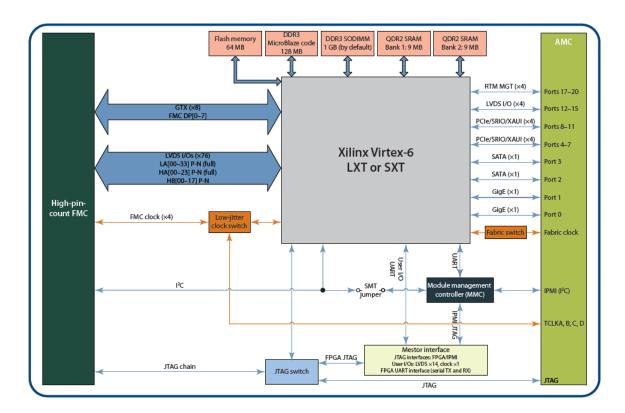

|   |                | 7.2.1 Nutaq Perseus 6010 Motherboard                               | 95 |

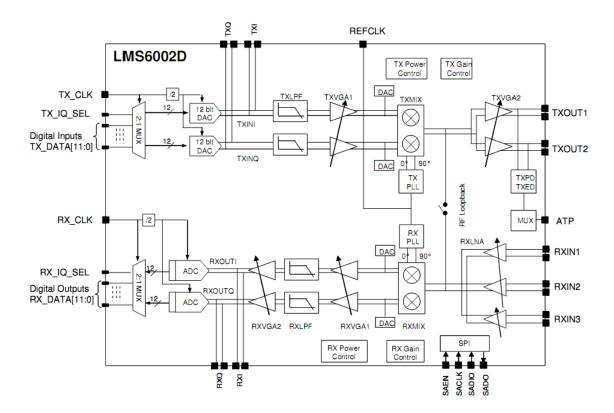

|   |                | 7.2.2 Radio420X Radio Front-end Daughterboard                      | 95 |

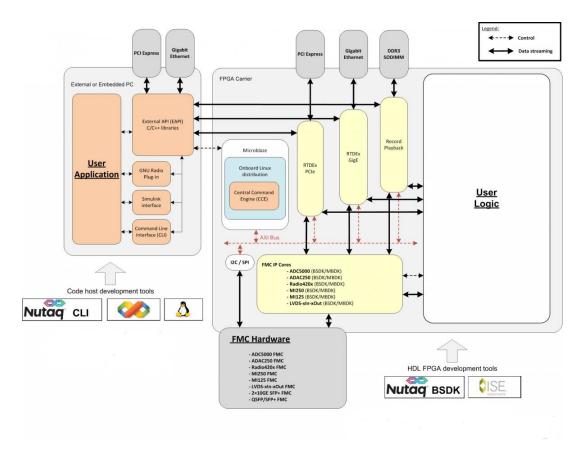

|   |                | 7.2.3 Perseus 6010 Software Development Tools                      | 95 |

CONTENTS 5

|                           | 7.3               | DSL-based Platform Modeling                                                  | 98                                     |

|---------------------------|-------------------|------------------------------------------------------------------------------|----------------------------------------|

|                           | 7.4               | DSL-based IEEE 802.15.4 PHY                                                  | 99                                     |

|                           |                   | 7.4.1 IEEE 802.15.4 PHY Data-Frame Modeling                                  | 99                                     |

|                           |                   | 7.4.2 IEEE 802.15.4 PHY Transceiver Modeling                                 | 100                                    |

|                           | 7.5               | DSL-based IEEE 802.11a PHY                                                   | 103                                    |

|                           |                   | 7.5.1 IEEE 802.11a PHY Data-Frame Modeling                                   | 104                                    |

|                           |                   | 7.5.2 IEEE 802.11a PHY Transceiver Modeling                                  | 105                                    |

|                           | 7.6               | The "adaptive" keyword                                                       | 108                                    |

|                           | 7.7               | Validation and Synthesis Results                                             | 109                                    |

|                           | 7.8               | A few remarks regarding the development time                                 | 111                                    |

|                           | 7.9               | Conclusion                                                                   | 112                                    |

|                           |                   |                                                                              |                                        |

| 0                         | Con               | activities and Danas actives                                                 | 115                                    |

| 8                         | Con               | nclusion and Perspectives                                                    | 115                                    |

|                           |                   | •                                                                            | 115<br>121                             |

|                           |                   | nclusion and Perspectives adices                                             |                                        |

| $\mathbf{A}_{\mathbf{j}}$ | ppen              | •                                                                            |                                        |

| $\mathbf{A}_{]}$          | ppen<br>Rés       | adices<br>sumé en français                                                   | 121<br>123                             |

| $\mathbf{A}_{]}$          | ppen<br>Rés<br>HL | ndices sumé en français S Specifications                                     | 121<br>123<br>131                      |

| $\mathbf{A}_{]}$          | ppen<br>Rés<br>HL | adices sumé en français S Specifications IEEE 802.15.4 PHY HLS specification | 121<br>123<br>131<br>131               |

| $\mathbf{A}_{]}$          | ppen<br>Rés<br>HL | adices sumé en français S Specifications IEEE 802.15.4 PHY HLS specification | 121<br>123<br>131                      |

| $\mathbf{A}_{]}$          | Rés<br>HLS<br>B.1 | adices sumé en français S Specifications IEEE 802.15.4 PHY HLS specification | 121<br>123<br>131<br>131<br>131<br>131 |

6 CONTENTS

## List of Figures

| 2.1  |                                                                            | 20             |

|------|----------------------------------------------------------------------------|----------------|

| 2.2  | The OSI Model                                                              | 21             |

| 2.3  | BPSK, QPSK, and 16-QAM                                                     | 23             |

| 2.4  |                                                                            | 27             |

| 2.5  | Harvard Architecture                                                       | 28             |

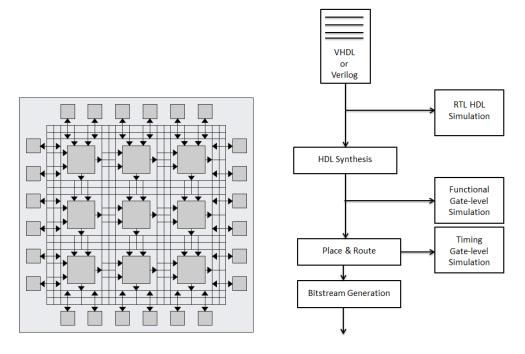

| 2.6  | Abstract FPGA representation (left) and a typical FPGA design flow (right) | 29             |

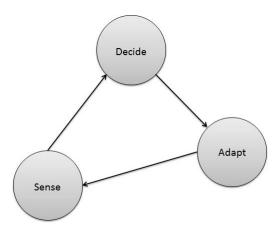

| 2.7  | Cognitive cycle composed of three major states                             | 30             |

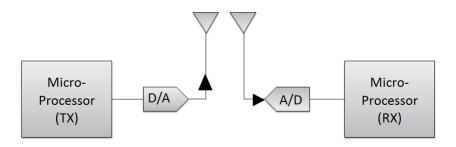

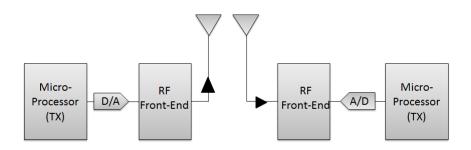

| 2.8  | Ideal Software-Defined Radio (SDR)                                         | 32             |

| 2.9  |                                                                            | 33             |

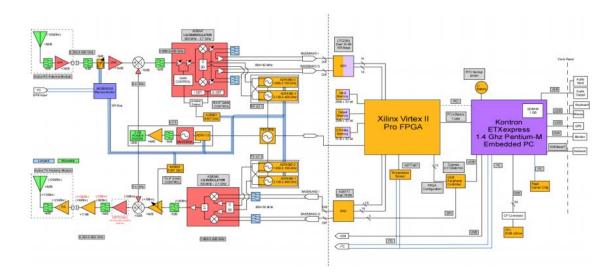

| 2.10 | KUAR System Diagram                                                        | 34             |

| 2.11 |                                                                            | 37             |

|      |                                                                            |                |

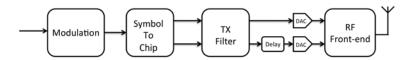

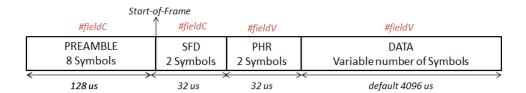

| 3.1  |                                                                            | 42             |

| 3.2  |                                                                            | 44             |

| 3.3  |                                                                            | 44             |

| 3.4  |                                                                            | 45             |

| 3.5  | IEEE 802.11a PPDU format.                                                  | 45             |

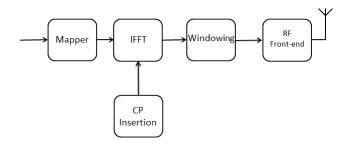

| 3.6  |                                                                            | 47             |

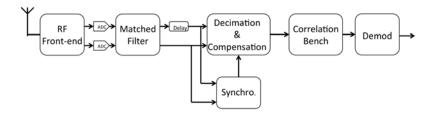

| 3.7  | PHY IEEE 802.11a receiver                                                  | 47             |

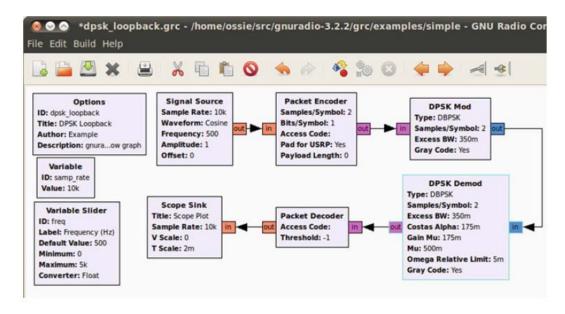

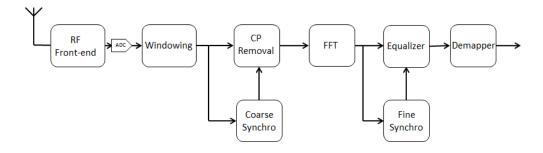

| 3.8  | GNURadio PHY IEEE 802.11p receiver                                         | 48             |

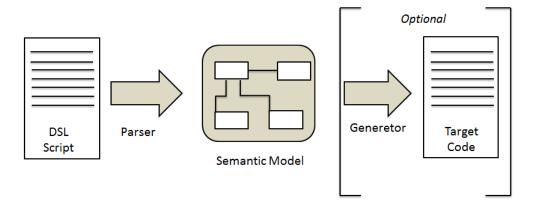

| 4.1  | Generic architecture of DSL processing                                     | 53             |

|      |                                                                            | ออ<br>54       |

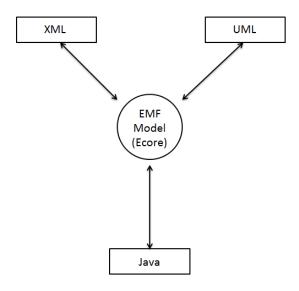

| 4.2  | 1 , , , ,                                                                  |                |

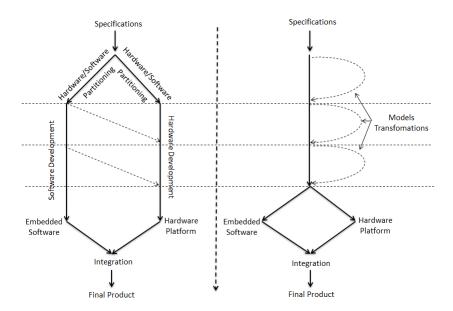

| 4.3  | 9                                                                          | 55             |

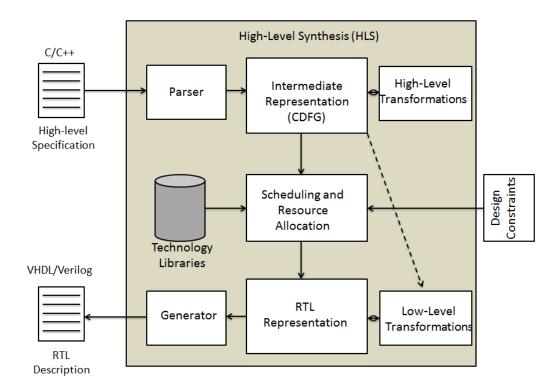

| 4.4  |                                                                            | 57             |

| 4.5  | 1 1                                                                        | 59             |

| 4.6  | 0 1                                                                        | 62             |

| 4.7  | An SDF signal flow graph (left) and its possible implementation (right)    | 63             |

| 5.1  | Proposed Design Flow                                                       | 69             |

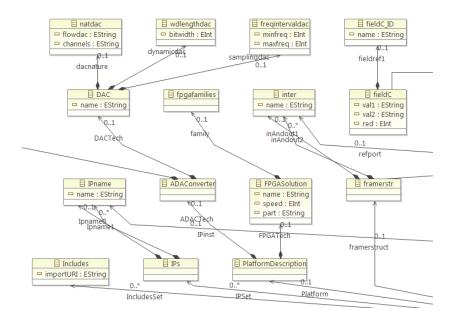

| 5.2  |                                                                            | 71             |

| 5.3  |                                                                            | 71             |

| 5.4  |                                                                            | 72             |

| 5.5  | 1 0                                                                        | -<br>74        |

| 5.6  |                                                                            | $\frac{1}{74}$ |

| 5.7  | •                                                                          | 75             |

| 5.8  |                                                                            | . 5<br>77      |

| 5.9  |                                                                            | 79             |

|      |                                                                            | 79             |

| 5.10 |                                                                            | 80             |

|      |                                                                            | 81             |

|      |                                                                            | 82             |

| 0.10 | 11111 002.19.4 transceiver materied inter specification in Catapute        | 2              |

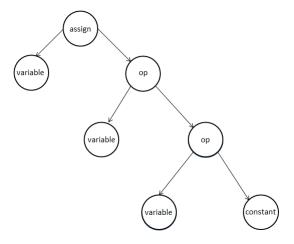

| 6.1  | Generic AST representation                                                 | 84             |

8 LIST OF FIGURES

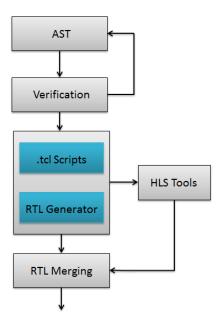

| 6.2  | DSL-compiling framework                                                   | 6 |

|------|---------------------------------------------------------------------------|---|

| 6.3  | Zoom into the actual AST representation                                   | 6 |

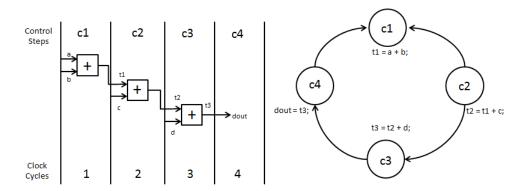

| 6.4  | Scheduled Design and Datapath Sate Diagram at the block-level             | 7 |

| 6.5  | Example of tcl script generating RTL code with loop constraints           | 9 |

| 6.6  | Hierarchical view of generated RTL for a given FB                         | 0 |

| 6.7  | Waveform assembly view                                                    | 0 |

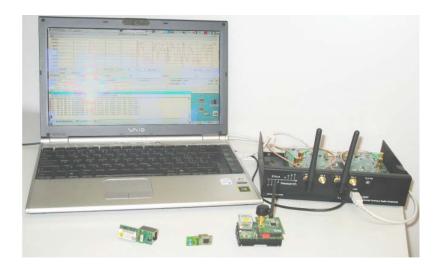

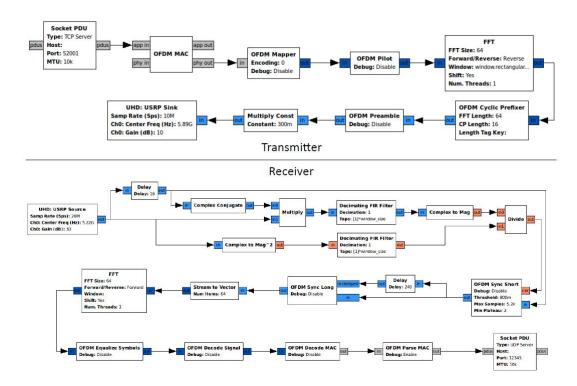

| 7.1  | Testbed Description                                                       | 4 |

| 7.2  | Validation and Testing Environment                                        | 5 |

| 7.3  | Perseus block diagram                                                     | 6 |

| 7.4  | LMS6002D transceiver block diagram                                        | 7 |

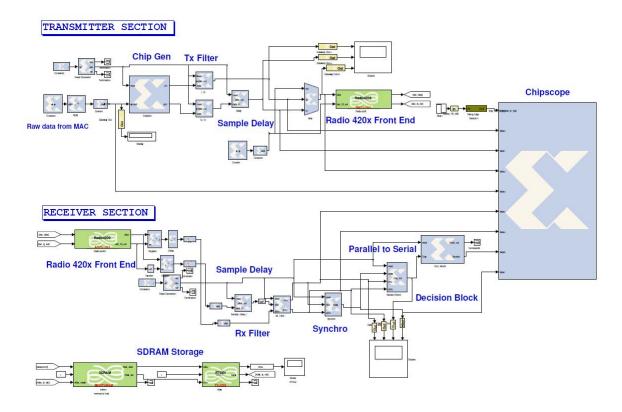

| 7.5  | MBDK-based hand-coded ZigBee transceiver design                           | 8 |

| 7.6  | MBDK-based hand-coded ZigBee transceiver design                           | 9 |

| 7.7  | DSL-based Perseus 6010 platform description                               | 0 |

| 7.8  | DSL-based IEEE 802.15.4 PHY data frame representation                     | 0 |

| 7.9  | DSL-based IEEE 802.15.4 PHY data frame description                        | 1 |

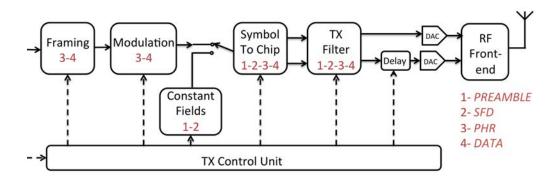

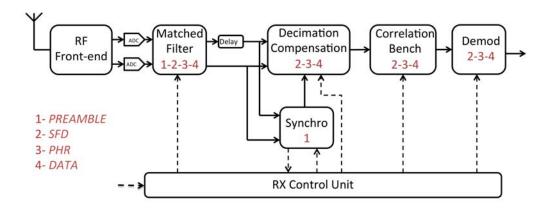

| 7.10 | DSL-based IEEE 802.15.4 PHY transmitter description                       | 2 |

| 7.11 | DSL-based IEEE 802.15.4 PHY transmitter implementation                    | 3 |

| 7.12 | DSL-based IEEE 802.15.4 PHY receiver implementation                       | 4 |

| 7.13 | DSL-based IEEE 802.15.4 PHY receiver description                          | 5 |

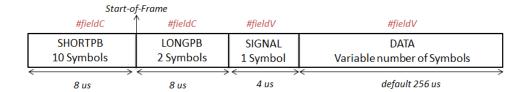

| 7.14 | DSL-based IEEE 802.11a PHY data frame representation                      | 6 |

|      | DSL-based IEEE 802.11a PHY data frame description                         | 6 |

| 7.16 | DSL-based IEEE 802.11a PHY receiver description                           | 7 |

| 7.17 | DSL-based IEEE 802.11a PHY transmitter implementation                     | 8 |

|      | DSL-based IEEE 802.11a PHY receiver implementation                        | 8 |

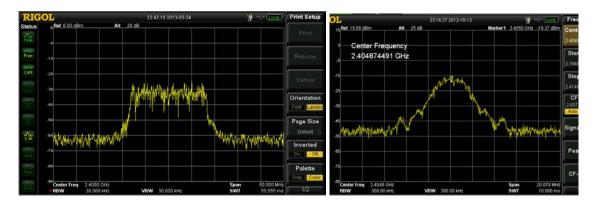

| 7.19 | Transmitted (left) and received (right) IEEE 802.15.4 baseband signals 10 | 9 |

|      | Decoding the transmitted IEEE 802.15.4 signal with VSA                    | 0 |

|      | OFDM (left) and ZigBee (right) spectrum                                   | 1 |

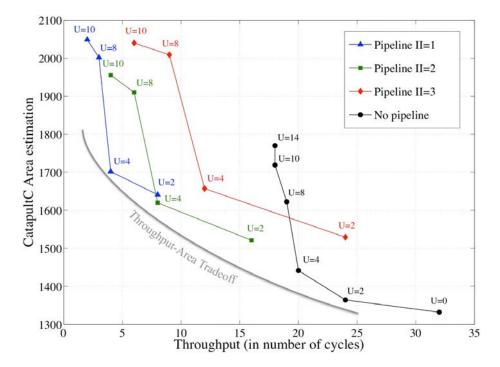

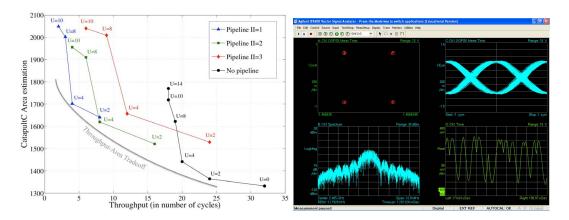

| 7.22 | Throughput/Area trade-off of the CorrBench FB                             | 2 |

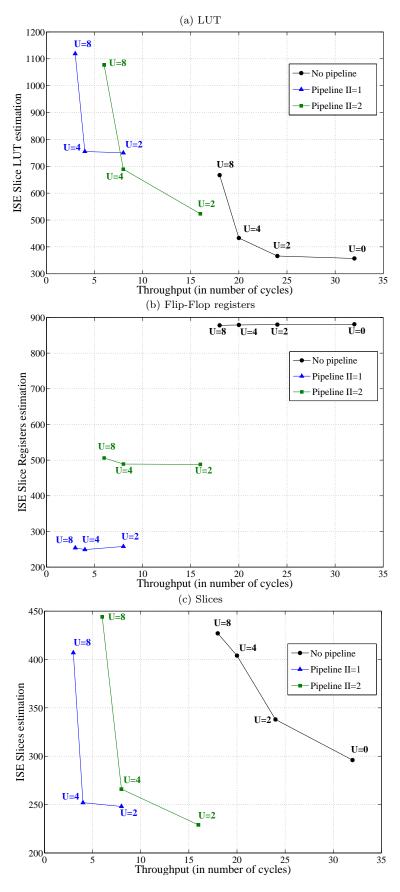

|      | Fine estimation: throughput/area tradeoff of the $CorrBench$ block        | 3 |

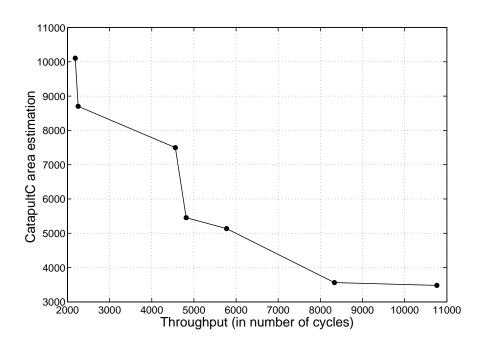

| 7.24 | Resource estimation for the FFT FB                                        | 4 |

## List of Tables

| 2.1        | Summary of state-of-the-art SDR languages                             | 38       |

|------------|-----------------------------------------------------------------------|----------|

| 3.2<br>3.3 | Frequency bands and data rates                                        | 42<br>43 |

| 4.1        | A comparative study between different HLS tools                       | 60       |

| 7.1        | Resource estimation for the IEEE 802.15.4 and IEEE 802.11a receivers. | 111      |

10 LIST OF TABLES

## Acronyms and Abbreviations

ACM Adaptive Coding and Modulation

ADC Digital to Analog Converter

ASIC Application Specific Integrated Circuit

AST Abstract Syntax Tree

AWGN Additive White Gaussian Noise

**BER** Bit Error Rate

**BNF** Backus-Naur Form

BPSK Binary Phase Shift Keying

**BSDK** Board Software Development Kit

CISC Complex Instruction Set Computer

CP Cyclic Prefix

CPU Central Processing Unit

CR Cognitive Radio

**DAC** Digital to Analog Converter

${\bf DSE}$  Design Space Exploration

**DSL** Domain Specific Language

**DSSS** Direct Sequence Spread Spectrum

**DSP** Digital Signal Processing

FB Functional Block

FDM Frequency Division Multiplexing

**FFT** Fast Fourier Transform

${\bf FHSS}$  Frequency Hopping Spread Spectrum

FIR Finite Impulse Response

FMC FPGA Mezzanine Card

FPGA Field Programmable Gate Array

FSM Finite State Machine

**GPL** General Purpose Language

**GPP** General Purpose Processor

$\mathbf{HDL}$  Hardware Description Language

**HFSM** Hierarchical Finite State Machine

**HLL** High-Level Language

**HLS** High-Level Synthesis

ICI Inter-Channel Interference

**IDE** Integrated Development Environment

IFFT Inverse Fast Fourier Transform

IIR Infinite Impulse Response

IoT Internet of Things

**ISI** Inter-Symbol Interference

ISM Industrial Scientific and Medical

MBDK Model Based Design kit

MAC Medium Access Control

MDE Model Driven Engineering

MoC Model of Computation

OFDM Orthogonal Frequency Division Multiplexing

OQPSK Offset Quadrature Phase Shift Keying

**OSI** Open System Interconnection

PER Packet Error Rate

PHY Physical Layer

**QAM** Quadrature Amplitude Modulation

QoS Quality of Service

QPSK Quadrature Phase Shift Keying

RF Radio Frequency

RISC Reduced Instruction Set Computer

RTL Register Transfer Level

RX Digital Receiver

SCA Software Communication Architecture

${f SDF}$  Synchronous Data Flow

SDR Software-Defined Radio

SNR Signal to Noise Ratio

TRX Digital Transceiver

$\mathbf{TX}$  Digital Transmitter

UML Unified Modeling Language

USRP Universal Software Radio Peripheral

VHDL VHSIC Hardware Description Language

XPS Xilinx Platform Studio

## Chapter 1

## Introduction

## 1.1 Internet of Things (IoT) and Software-Defined Radio (SDR)

The Internet of Things (IoT) [1][2] is a promising concept which purpose is to connect billions of communicating devices (the things) through an internet-like network. Such things are expected to range from simple RFID tags to powerful smartphones interacting with various types of nodes or even with human beings themselves. Further to this, the IoT is intended to be implemented through wireless links without any predefined standards or infrastructures. However, such technology would require multiple communicating devices to coexist in a spectrum limited environment. To tackle this issue, diverse approaches have been proposed in the literature. Thus, solutions like the Cognitive Radio (CR) [3][4][5], the Cooperative Radio [6][7][8] or the Green Radio [9] are presented as the enabling technologies to implement the IoT.

Traditional radios have shown some limitations regarding the implementation of such brand new technologies. Indeed, they often consist of a set of dedicated hardware which usually implements a single function at a time. However, the cognitive radio, the cooperative radio or the green radio technologies foster flexible architectures that can adapt to their environmental conditions. A promising alternative which is also presented as a key enabling technology for these concepts is the Software-Defined Radio (SDR)[10][11]. SDR fosters the implementation of most of the processing stages in digital form by using programmable devices. Hence, this architecture is much more flexible than using dedicated hardware while requiring fewer components. It also enables to change the functionality of the radio at any time by simply using software updates. However, the SDR approach comes with some drawbacks which are related to the reliability and the security of the software. Moreover, the encountered SDR solutions require more power than dedicated-hardware based solutions.

Whilst, these concepts have come to a certain maturity, the underlying methodologies or tools which support their implementation still represent an open research topic. Indeed, it is important to point out the fact that an efficient toolset would allow to achieve better productivity by considerably shortening the time-to-market.

#### 1.2 Design Methodologies

Methodologies for implementing digital systems often referred to as design flows, have motivated a lot of research work throughout the decades. As a result, the level of abstraction was raised from the transistor-level up to the system-level all the way through gate-level and function-level. Each of these breakthroughs was welcome with a lot of skepticism with respect to the achievable performance even though their main purpose was to allow the designers to focus more on the functionality rather than its implementation. To this aim, several steps within the design process were automated thanks to some tailored algorithms as well as mechanisms for source code or other artifacts generation. Such automation processes is generally supported by a dedicated compiler.

The design methodologies can be split up into two categories. On the one hand, some tools support the development of digital applications on software-based technologies such as microprocessors or DSP microprocessors. Their entry point consists of a high-level description of the intended application written in a high-level language such as C/C++. Afterwards, this description is compiled to a machine language which consists entirely of numbers (bits) that are understood by the target processor (machine). The assembly language is often used for intermediate representation however, it consists of variables and names which are relatively easy to interpret by human beings unlike machine language. On the other hand, some tools support the development of digital systems on hardware-based technologies like Field Programmable Gate Arrays (FPGAs) or Application Specific Integrated Circuits (ASICs). These technologies allow the designer to build customized circuit architectures which are tailored to the application's needs. However, FPGAs provide more flexibility compared to their ASICs counterparts. Indeed, FPGAs enable to program a customized circuit architecture through a configuration file. It can be reprogrammed to implement a different functionality unlike ASICs whose circuits are hardwired. Their underlying design tools usually consider as entry point a description of the application in form of a Hardware Description Language (HDL) such as VHDL or Verilog. The description which is usually performed at the Register Transfer Level (RTL) is first synthesized into a netlist which is the equivalent description at the gate-level in HDL. Following this step, the netlist is further processed and placed and routed afterwards. The placement and routing tool generates the layout or the configuration files which are not in HDL. Such files are used either to program the FPGA or for ASIC manufacturing.

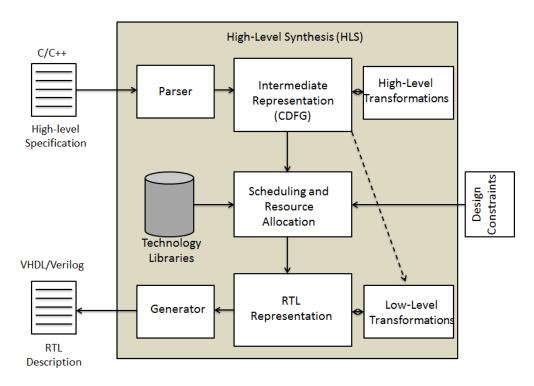

An emerging approach consists in raising the level of abstraction while considering FPGA or ASIC based designs. Referred to as High-Level Synthesis (HLS), it fosters the use of high-level languages as entry point in both FPGA and ASIC design flows. Thus, an application can be first specified in C/C++ for instance and then directly compiled to a configuration file for the target FPGAs or ASICs. Once again, the approach allows the designers to focus on the functionality of the application rather than the underlying hardware. The HLS is supported by a set of academic and industrial tools such as Catapult from Calypto and Vivado HLS from Xilinx. In summary, HLS flows can be used for rapid prototyping when hardware fabrics are being considered in a digital system implementation process. However, they emphasize more on datapath designing rather than control path. Hence, the control aspects should be handled separately whenever complex control schemes are required. Indeed, HLS was first thought as a processor generator employing native sequential languages such as C/C++. The related compilers have succeeded in extracting some parallelism in the specified applications so as to build an efficient datapath. Control path on the other hand is handled at function-level rather than system-level. For instance, HLS did not properly address the specification of state machines, which are the mainstream structure for defining the control logic of an application at the system-level.

In the context of SDR, the design tools must support the specification as well as the implementation of any applications while being independent of the underlying hardware, which could ensure the *portability* of the solution on different platforms. Furthermore, the tools entry point should be a high-level language for *programmability* purpose and finally, such tools must address the *reconfigurability* of the application at a higher level of abstraction. To this aim, different proposals can be found in the literature and a state of the art of the design methodologies for SDR implementation is provided in this document.

The FPGA technology is often used as a simple hardware accelerator in a typical SDR platform. Paradoxically, it is also presented as a key enabling technology for SDR since it trades-off between design throughput and power consumption while offering reconfigurability capabilities. In effect, the main reason why FPGA platforms have not encountered a lot of success within the SDR community is essentially because of their programming model which relies on HDLs. This programming model requires a deep knowledge in hardware design, which contrasts with the stated goal of SDR that is to say a software intensive platform. To remedy this issue, we believe that the HLS technology can be leveraged so as to define an FPGA-based SDR design flow.

In essence, the design methodologies for implementing digital radios are broadly addressed in the literature. However, the SDR technology has come with some new challenges which require rethinking the development process by integrating some relevant features that could tackle the domain issues.

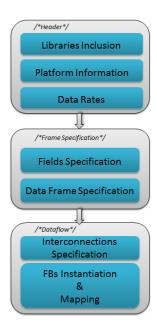

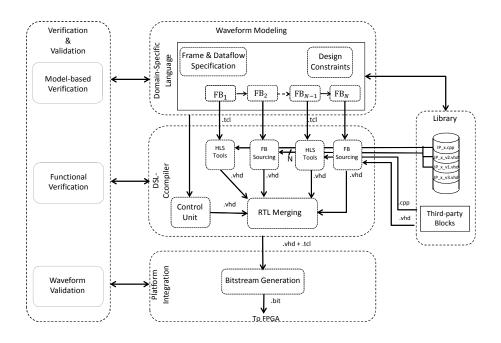

#### 1.3 The Proposed Methodology and the Main Contributions

Our proposal consists of a design flow for SDR specification and implementation on FPGA-based platforms. It leverages the HLS principle which allows rapid prototyping on FPGA fabrics while addressing the control requirements at the system-level. The entry point of the proposal is a Domain Specific Language (DSL) which is a customized language tailored to a domain's needs. The DSL was entirely developed with the Xtext/Xtend framework which is an Eclipse plugin. It coarsely allows the designers to capture different parts of an SDR waveform, *i.e.* the frame model and the dataflow structure, at a higher level of abstraction while instantiating HLS-based Functional Blocks (FBs). The DSL is featured with a compiler which purpose is to automate as many steps as possible in the implementation process. The compiler further analyzes the description of the waveform made with the DSL and then produces a set of artifacts such as synthesis script and source code. Finally, the proposed flow has been validated on two well-known waveforms, namely the IEEE 802.15.4 PHY and the IEEE 802.11a PHY transceivers which implement the radio communication protocol of the ZigBee and the WiFi technologies respectively.

In sum, our contributions can be listed in the following way:

- A Domain Specific Language (DSL) which provides the primitives to rapidly prototype the dataflow applications meant for SDR. The DSL is combined to HLS tools so as to take advantage of their offerings.

- A frame-based algorithm to automatically generate an appropriate control path capable of handling the reconfiguration requirements of a multi-rate complex dataflow specification.

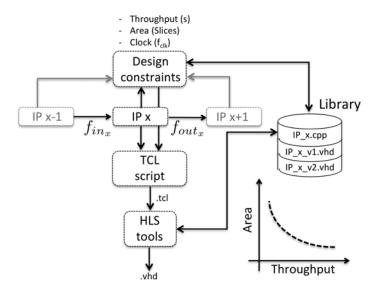

- A design space exploration scenario which enables the appropriate selection of the blocks composing the final design. Such scenario was made possible by the usage of HLS for rapid prototyping.

- A compiler which implements the proposed algorithms by further analyzing the DSL-based descriptions and generating the required artifacts such as synthesis scripts as well as source code.

- A library of functional blocks specified in HLS and compatible with *Catapult* or *Vivado HLS*. The library includes some blocks which are part of either the IEEE 802.15.4 PHY or the IEEE 802.11a PHY.

#### 1.4 The Outline

This document is basically divided into two major parts. The first part, Chapters 2 to 4, entitled *Background* provides a comprehensive overview of the SDR throughout the different notions involved. The second part, Chapters 5 to 7, entitled *Contributions* covers the details of our proposal which consists of a design flow for implementing FPGA-based SDRs. More detailed descriptions of the chapters follow.

- Chapter 2 discusses some digital radio principles as well as the underlying technologies. Furthermore, the chapter presents the "big picture" of SDR including platforms and design methodologies.

- Chapter 3 provides the details of two PHYs that we have considered in this work for validation purpose. The two PHYs are the IEEE 802.15.4 PHY and the IEEE 802.11a PHY which implement the radio communication protocols of the ZigBee and the WiFi technologies respectively.

- Chapter 4 covers the methodologies which purpose is to raise the level of abstraction for PHY designing. It introduces some concepts such as the Model Driven Engineering (MDE) or the HLS.

- Chapter 5 provides an overview of our proposal. The chapter discusses the conceptual aspects of the DSL through generic examples. In addition, a discussion on the automatically generated control logic is provided.

- Chapter 6 details the features of the associated compiler. To this aim, it provides more information on the intermediate representation of a DSL-based SDR waveform description and then discusses the mechanisms that we have developed to produce the final waveform.

- Chapter 7 discusses the specification and the implementation of the two aforementioned

- waveforms with the proposed flow. The ensuing results are interpreted and some conclusions are drawn.

- Chapter 8 first summarizes the entire work depicted in this document and discusses the perspectives afterwards.

A appendix chapter is provided at the end of the document. It includes HLS specifications, which are intended to illustrate a typical description of a PHY with HLS tools.

# Part I BACKGROUND

## Chapter 2

## Digital Radio and Software-Defined Radio

| Contents   |                 |                                                    |           |

|------------|-----------------|----------------------------------------------------|-----------|

| 2.1        | Intr            | oduction                                           | 20        |

| 2.2        | $\mathbf{Intr}$ | oduction to Digital Communication                  | <b>21</b> |

|            | 2.2.1           | Symbol Mapping                                     | 21        |

|            | 2.2.2           | Channel Access Techniques                          | 24        |

|            | 2.2.3           | Pulse Shaping                                      | 25        |

| 2.3        | Digi            | tal Communication Technologies                     | 27        |

|            | 2.3.1           | DSP Software Platforms and Programming Environment | 27        |

|            | 2.3.2           | DSP Hardware Platforms and Programming Environment | 28        |

| <b>2.4</b> | Flex            | tible Radios                                       | <b>29</b> |

|            | 2.4.1           | Cognitive Radios                                   | 30        |

|            | 2.4.2           | Adaptive Coding and Modulation (ACM) Technique     | 31        |

| <b>2.5</b> | Soft            | ware-Defined Radios                                | 31        |

|            | 2.5.1           | Motivations and Main Features                      | 32        |

|            | 2.5.2           | Survey of SDR Platforms                            | 33        |

|            | 2.5.3           | SDR Design Methodologies                           | 35        |

| 2.6        | FPC             | GA Platforms for SDR                               | <b>37</b> |

| 2.7        | Con             | clusion                                            | 38        |

#### 2.1 Introduction

Digital radio systems [12][13][14][15] resulted from an increasing demand in terms of efficiency and control over the electronic applications. Indeed, analog designs which physically operated the signal turned out to be less efficient when high data rates and low power consumption were required. In addition, pure analog systems gave uncertain performance in production in the sense that they did not guarantee accuracy and perfect reproducibility of the designs [16].

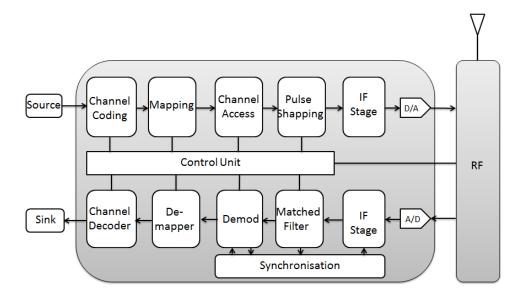

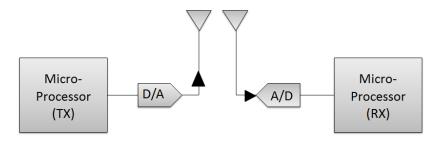

The advent of the transistor and the limitations of the analog systems have led the designers to rethink the overall electronic designing processes by introducing some new concepts. Thus, electronic systems have evolved from analog devices to hybrid fabrics composed of both analog and digital components as illustrated in Figure 2.1. Figure 2.1 shows the architecture of a current digital radio transceiver which comprises a baseband processing module to perform the digital processing and a front-end module to modulate a signal on a career frequency. An antenna transmits/receives the signal into/from the propagation channel. A mainstream approach consists now in designing flexible radio transceivers which are capable to adapt to the environmental conditions. Such transceivers are intended to improve the usage of the spectral resource which tends to be more and more scarce owing to an under optimized utilization. Moreover, the evolution of the digital platforms has enabled to reach a certain flexibility at the price of a lesser efficiency in terms of power consumption. Software-Defined Radio (SDR) [10][11] can be presented as a potential implementation of a flexible radio. In addition to the flexibility, the SDRs also address the programmability and the portability of a waveform. In this chapter, we will first emphasize on the baseband transceivers architectures which are mainly ruled by some signal processing principles. Flexible radios and SDRs will be discussed afterwards.

Section 2.2 and 2.3 introduce the digital communication principles and the underlying technologies respectively. In Section 2.4, the concept of flexible radio is discussed and illustrated throughout some examples. Section 2.5 introduces the SDR concept while Section 2.6 discusses the usage of the Field Programmable Gate Array (FPGA) fabrics as physical hardware for SDR development. Conclusions are drawn in Section 2.7.

Figure 2.1 – Digital transceiver consisting of digital and analog components.

#### 2.2 Introduction to Digital Communication

Generally speaking, a radio transceiver can be defined as any device that is used to exchange an information signal from point A to point B through wired or wireless channels. It is usually referred to as the Physical Layer (PHY) which is composed of hardware transmission technologies and represents the lowest layer in the OSI model. The OSI model, shown in Figure 2.2, characterizes the internal functions of a communication system. The PHY layer plays an important role within the OSI model since it provides a medium access to the higher layers. The information theory introduced by Claude Shannon [17], partly introduced the concept of digital communication by defining some of its major principles. Indeed, the document teaches us the theoretical capacity of a channel as well as the performance which can be expected. For instance, by considering an Additive White Gaussian Noise (AWGN) channel and a passband transmission, it was shown that the maximum capacity achievable, also known as the channel capacity, is given by

$$C = W \log_2(1 + SNR), \tag{2.1}$$

where C is the bit rate (in bits per second), W the width of the spectral band in which the signal is transmitted and SNR, the Signal to Noise Ratio in this band. These results later guided the research toward source coding, channel coding and algorithmic complexity theories.

The communication theory [18][19] on the other side focuses on how the information transits from point A to B under the constraints dictated by the information theory. In other words, it deals with how to condition the signal so as to ensure its integrity throughout the channel. It is usually well-specified by telecommunication standards [20][21][22][23][24].

Our research work emphasizes on PHY specifications and implementations and therefore, the following sections provide some discussions over the main aspects of a PHY from a baseband perspective namely, the symbol mapping, the channel access techniques and the pulse shaping or signal conditioning. The following equations are taken from [12].

#### 2.2.1 Symbol Mapping

Symbol mapping is usually the starting stage of a PHY definition depending on whether a channel coding scheme is required or not. It literally takes a sequence of streaming bits and

| OSI Layers     | Physical Components          |  |

|----------------|------------------------------|--|

| 7-Application  | Application Software         |  |

|                | Network Applications         |  |

| 6-Presentation | Data Conversion<br>Utilities |  |

| 5-Session      |                              |  |

| 4-Transport    | Network Operating<br>System  |  |

| 3-Network      |                              |  |

| 2-Data Link    | Network                      |  |

| 1-Physical     |                              |  |

Figure 2.2 – The OSI Model.

converts (maps) them into a set of symbols predefined in an alphabet of symbols. The symbols can be either real or complex. Complex symbols are composed of two components, namely an in phase (I) component and a quadrature phase (Q) component. The choice of a symbol mapping scheme for a given standard depends on its requirements in terms of bit rate and probability of error. Thereby, several symbol mapping techniques have been proposed and each of them allows achieving some theoretical data rate and Bit Error Rate (BER). In the following paragraphs, we will discuss some of the most encountered symbol mapping techniques by highlighting their mathematical formalization together with the associated theoretical error rates.

#### M-ary Pulse Amplitude Modulation (M-PAM)

The M-PAM modulation consists in mapping the input set of bits into a sequence of symbols according to an M-ary alphabet or constellation. Thus, the number of possible transmitted symbols is equal to M and a unique symbol represents a set of  $\log_2(M)$  bits. The alphabet is composed of the symbols  $s_m$  given by (2.2), where  $E_g$  is the energy per symbol.

$$s_m = \sqrt{E_g}(2m - 1 - M), \qquad m = 1, 2, ..., M,$$

(2.2)

One can note from (2.2) that the distance between two consecutive symbols is  $2\sqrt{E_g}$ . This distance impacts the distinction of the symbols at the receiver since the metric that is used to differentiate them is based on setting a threshold between neighboring symbols. In the context of an AWGN channel, it leads to a theoretical probability of error at the symbol-level given by (2.3).

$$P_{SER} = \frac{2(M-1)}{M} Q(\sqrt{\frac{6P_{av}T_s}{(M^2-1)N_0}}), \tag{2.3}$$

where  $P_{av}$  is the average power,  $N_0$  the spectral density of the noise  $T_s$  the symbol period and Q(.) the Gaussian density function given by

$$Q(x) = \frac{1}{\sigma\sqrt{2\pi}}e^{-(x-\mu)^2/2\sigma^2},$$

where  $\mu$  is the mean and  $\sigma^2$  the variance of the function.

#### M-ary Phase Shift Keying (M-PSK)

The M-PSK modulation is a slightly different approach in the sense that in this symbol mapping technique, the information is embedded in the phase component of a signal with constant amplitude. It contrasts with the M-PAM modulation where the amplitudes vary with a constant phase. An M-PSK constellation fits onto the circumference of a circle where the symbols lay at equal angular distances. Thereby, the symbols are the phase information whose values are given by

$$\theta_m = \frac{2\pi m}{M} + \frac{\pi}{M}, \qquad m = 0, 1, ..., M - 1,$$

(2.4)

where M is the number of symbols.

The Quadrature Phase Shift Keying (QPSK) is a particular case of an M-PSK modulation, where M=4, that has found several applications in wireless communication such as in the IEEE 802.11a standard. The Offset Quadrature Phase Shift Keying (OQPSK) is a slightly modified version of the QPSK which introduced a delay of half a symbol in order to prevent fluctuations in the constant envelop of QPSK. It was employed in the definition of the PHY of the Zigbee technology [20]. For the QPSK modulation and its variant OQPSK, the distinction of the symbols at the receiver is performed by assigning a region of decision around each symbol of the alphabet. It leads to a theoretical expression of the probability of symbol error, in the context of an AWGN channel, given by

$$P_{SER} = 2Q(\sqrt{\frac{E_g}{N_0}}) - Q^2(\sqrt{\frac{E_g}{N_0}}),$$

(2.5)

where  $\frac{E_g}{N_0}$  is the symbol SNR.

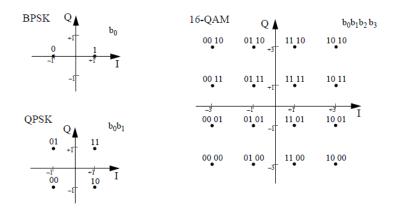

Figure 2.3 – BPSK, QPSK, and 16-QAM.

#### M-ary Quadrature Amplitude Modulation (M-QAM)

The M-QAM modulation is a combination of the two aforementioned modulation techniques. Indeed, it modulates the information signal into both phase and amplitude information. Doing so, the two dimensions are simultaneously exploited, which enables to achieve higher data rates. It is formalized through a complex mathematical representation that exhibits both the amplitude and the phase information. Equation (2.6) gives the complex representation of an M-QAM modulation where the amplitude corresponds to an M-PAM modulation and the phase corresponds to an M-PSK modulation. The probability of error is given in (2.7) where  $E_b$  is the energy per bit. Figure 2.3, which is taken from [21], shows the constellation for M=2, 4 and 16 respectively. One can notice that for M=4 it results in the QPSK modulation that was discussed in the previous paragraph.

$$s_m = \sqrt{E_g}(2m - 1 - M)e^{j(\frac{2\pi m}{M} + \frac{\pi}{M})}, \qquad m = 0, 1, ..., M - 1,$$

(2.6)

$$P_{BER} = 4\left(\frac{\sqrt{M} - 1}{\sqrt{M}}\right)\left(\frac{1}{\log_2 M}\right) \sum_{i=0}^{\frac{\sqrt{M}}{2} - 1} Q((2i + 1)\sqrt{\frac{E_b}{N_0}} \frac{3\log_2 M}{M - 1}),\tag{2.7}$$

#### M-ary Frequency Shift Keying (M-FSK)

The M-FSK is a frequency modulation that turns a set of  $K = \log_2(M)$  input bits into a frequency information. The set of possible frequencies is given by (2.8), where  $\Delta f$  is the frequency separation between two consecutive frequency symbols.

$$f_m = (2m - 1 - M)\frac{\Delta f}{2},$$

(2.8)

Other symbol mapping techniques have been developed and deployed throughout the decades. Among them, one can mention the Minimum Shift Keying whose variant, the Gaussian-MSK[12] has been employed in the GSM [25] telecommunication standard. Remembering that the choice of a given mapping technique depends on the expectation in terms of data rate and probability of error, accurate simulations must be carried out in order to find the appropriate symbol mapping technique. These simulations must include the distortions of the expected channel which can vary in the context of wired, wireless, satellites or underwater communication.

In addition to information signal modulation, it is important to decide how the allocated bandwidth resource will be utilized by the modulated symbols. This is known as channel access techniques that are developed in the next section.

#### 2.2.2 Channel Access Techniques

The channel access techniques have been developed to optimize the usage of the allocated spectral bandwidth under certain conditions. Indeed, the spectral resource is quite a scarce and costly resource that is generally managed by the local authorities and at some point coveted by the other applications. Thus, several techniques have been proposed to increase the overall communication performance given both a spectral resource and a propagation condition, while ensuring the signal integrity. Each of these techniques has some relevant advantages however they may exhibit some shortcomings deeply related to the properties of the channel.

In this section, we will essentially discuss two of those techniques namely, the spread spectrum and the Orthogonal Frequency Division Multiplexing (OFDM) techniques that have been employed in many of nowadays applications. They are also relevant for the PHY waveforms that we will use to validate our approach.

#### **Spread Spectrum Systems**

Spread spectrum is a channel access technique in which the information signal is transformed to a signal of a higher bandwidth before transmission. It is declined in two variants namely, the Direct Sequence Spread Spectrum (DSSS) and the Frequency Hopping Spread Spectrum (FHSS). In DSSS systems, the spreading is performed by multiplying the information signal by a known code while in FHSS this code indicates the carrier frequency on which the information signal is modulated. These two techniques both result in a wider signal bandwidth that protects the signal from narrowband interference. Moreover, these techniques show some improvements in the context of multipath transmission.

Equations 2.9 and 2.10 formalize the information signal S(t) and the spread signal respectively (in the context of the DSSS). The spread signals are commonly called chip sequences and should include some properties (e.g. orthogonality) that enable to efficiently differentiate them at the receiver. Indeed, at the receiver, the transmitted symbols are recovered by a synchronization, which implies a multiplication by the synchronized spreading code and detection. Finally, performance vary depending on the channel under consideration.

$$S(t) = \sum_{m=-\infty}^{+\infty} s_m g_T(t - nT_s), \qquad (2.9)$$

where  $s_m$  is the transmitted symbol sequence and  $g_T(t)$  the modulation pulse of period  $T_s$ .

$$S(t)s_C(t) = \sum s_n g_T(t - nT_s) \sum c_{PN}(n) p(t - nT_c), \qquad (2.10)$$

where U(t) is the information signal and  $c_{PN}(n)$  takes the values  $\pm 1$  of the desired code.  $T_c$  is the duration of a chip and p(t) represents the unit pulse.

On the other hand, FHSS operates by loading the information signal S(t) onto a carrier, the frequency of which is indicated by the spreading code. The transmitted signal remains in such a way at a specific carrier frequency for a period of  $T_f$ . Thus, the hopping process can be mathematically formalized through (2.11). At the reception, the signal is de-hopped by combining mixing operation and bandpass filtering.

$$f(t) = f_m, \quad mT_f \le t \le (m+1)T_f.$$

(2.11)

To conclude, it is important to note that the spread spectrum technique has been employed in well-known telecommunication protocols and also for many other ad hoc networks. For instance, the IEEE 802.15.4 radio protocol [20] uses the DSSS within one of its PHY definitions that will be further discussed in this document. Furthermore, both the Bluetooth protocol and the UMTS standard leverage FHSS and DSSS respectively.

#### Orthogonal Frequency Division Multiplexing (OFDM)

Some classes of modulation techniques operate by dividing the allocated bandwidth into a set of subchannels that are modulated independently. This approach is called Frequency Division

Multiplexing (FDM) and results in a lower data rate per subchannel. However, it was shown that this technique reduces the effect of the impulse response of the channel but requires being further improved so as to reduce the Inter-Channel Interference (ICI). In fact, it was also shown that by selecting orthogonal subchannels the ICI effect can be considerably reduced. Thus, the Orthogonal FDM (OFDM) has become a mainstream channel access technique in which the orthogonality of the subchannels is achieved by making all subcarriers be an integer multiple of a fundamental frequency.

In practice, the OFDM is achieved by splitting the incoming complex data symbols (issued from a symbol mapping function) into N parallel streams corresponding to the subcarriers. Then, for each parallel stream, the complex symbols are modulated by complex sinusoids with frequencies corresponding to the subcarriers. The modulated symbols are then added to form an OFDM symbol. In the digital domain, this operation is known as the Digital Fourier Transform (DFT) whose equation is given by (2.12) and the inverse operation is known as the Inverse Digital Fourier Transform (IDFT) given by (2.13). It was shown that this operation can be digitally realized with a Fast Fourier Transform (FFT) or an Inverse Fast Fourier Transform (IFFT) which are two faster (reduced complexity) implementation of the DFT and the IDFT respectively.

$$s_k = \frac{1}{N} \sum_{k=0}^{N-1} S_n e^{j(\frac{2\pi kn}{N})}, \tag{2.12}$$

$$S_n = \sum_{k=0}^{N-1} s_k e^{-j(\frac{2\pi kn}{N})}, \tag{2.13}$$

Several telecommunication standards employ the OFDM channel access technique. Coarsely, at the transmitter the IFFT is used to convert the complex symbol in time domain as aforementioned. Furthermore, a Cyclic Prefix (CP) is appended to each OFDM symbol before transmission. It was shown that the CP enables to protect the signal from the channel impairments. Signal windowing is also part of the transmitter as it enables to squeeze the signal into the spectral recommendation. The receiver consists essentially in synchronization and symbol recovery through a DFT calculation. Many other challenges are encountered at the receiver making it a burden in OFDM design.

OFDM systems will be further depicted through an example later in this document where an OFDM-based telecommunication standard will be discussed. Finally, OFDM has encountered a lot of success and it has been employed in many standards such as the Digital Audio Broadcasting (DAB) [23], the Digital Video Broadcasting (DVB) [24], the Long Term Evolution (LTE) [26] and many others.

#### 2.2.3 Pulse Shaping

The pulse shaping technique has been developed to counter the Inter-Symbol Interference (ISI) damaging effects. Indeed, pioneers transmission systems have faced severe interference effects. These interference were due to the leakage of the energy of the previously transmitted symbols into the current symbol. It ended up with strong distortions which made it very complex to decode the current symbol. To tackle this issue, a first solution has been to decrease considerably the symbol rate so as to tell the received symbols apart. This solution was not sustainable since the trend was fostering to move toward the opposite way, *i.e.* to increase the transmission rate.

As a result, pulse shaping techniques have been proposed to strengthen the information signal prior to the transmission. Say, g(t) is a pulse shape function,  $g^*(-t)$  its transform conjugate and c(t) the impulse response of the channel. The received pulse, formalized as  $p(t) = g(t) * c(t) * g^*(-t)$  should satisfy the Nyquist criterion which states that p(t) must be equal to zero at optimal sampling times. In the next paragraphs, three useful pulse shaping techniques are discussed.

#### Rectangular Pulse

Rectangular pulse shaping consists in shaping the incoming symbols with a time-domain rectangular filter. It is quite an intuitive shape that unfortunately leads to some important shortcomings in practice. Indeed, the rectangular pulse is difficult to create in time domain because of its rise

time and its decay time. In addition, its frequency response is a sinc function  $(\sin(x)/x)$  that has a zero amplitude at integer multiples of the symbol rate. Furthermore, the sinc frequency response goes on forever and might interfere with others, which is not allowed by the frequency regulators. It exhibits some second lobes that are only 13 dB lower than the main one. Equation 2.14 gives the time domain rectangular pulse function where  $T_s$  is the symbol period.

$$g(t) = \sqrt{\frac{2}{T_s}}, 0 \le t < T_s, \tag{2.14}$$

From then on, one can argue that a filter with a rectangular frequency response could solve this problem since both second lobes and going forever issues would have been tackled in such a way. Such a filter corresponds to a sinc function in time domain that is unfortunately no more possible to build than a rectangular pulse. Thus, alternative solutions have been proposed to trade-off between these two classes of filters.

#### Cosine Pulse

Cosine pulse shaping presents some interesting spectral gain as compare to the rectangular pulse. For instance, it has some 10 dB lower side lobes in comparison, with a constant amplitude. Equation 2.15 gives the time domain expression of the pulse.

$$g(t) = \sin(\frac{\pi t}{T_s}), 0 \le t < T_s,$$

(2.15)

#### Raised Cosine Pulse

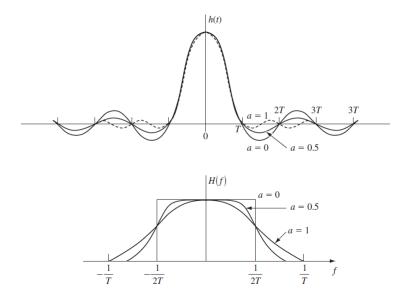

The raised cosine filters came up as a modification of the sinc pulse. They have an adjustable bandwidth that can be adapted through a parameter called the roll-off factor. Equation 2.16 gives the time domain representation of the raised cosine pulse where the roll-off factor a ranges from 0 to 1. This equation shows that the filter ranges from a pure sinc function (a=0) to a rectangular function (a=1) depending on the value of a. The most encountered values given to the parameter a are 0.2, 0.4 and 0.6. Figure 2.4 gives both the impulse response and the frequency response of a raised cosine pulse for different values of the roll-off factor a. In practice, the raised cosine filter is implemented as a Finite Impulse Response (FIR) filter. In addition, it requires a minimum number of taps since the filter get better as the number of taps increases.

$$g(t) = \frac{\sin(\frac{\pi t}{T_s})}{\frac{\pi t}{T_s}} \frac{\cos(\frac{\alpha \pi t}{T_s})}{1 - \frac{4r^2t^2}{T^2}}, 0 \le t < T_s,$$

(2.16)

Further Digital Signal Processing (DSP) blocks/algorithms can be involved in the definition of a digital transceiver, however covering all these blocks features is out of the scope of this document. For instance, the channel coding and decoding techniques are relevant mechanisms for ensuring the integrity of the transmitted information signal throughout a noisy channel. They are declined into block codes [27] and convolutional codes [28]. The former submit k bits in their inputs and forward n bits in their outputs. The latter induces the notion of memory by considering the preceding bits for computing the ongoing code. Both techniques are usually characterized by a coding rate (r) which denotes the redundancy induced by the coding technique. In addition to channel coding, one can mention the synchronization blocks which purpose is to lock the receiver components with the appropriate processing parameters. They are employed in coherent receivers which are opposed to non-coherent receiver where a blind reception is performed. Synchronization has actually a crucial importance on a given transceiver architecture since its performance can limit the request for data re-transmission in the network. Channel estimation is optionally implemented on receivers. It aims at estimating the channel's distortions by using blind techniques or known sequences that are inserted in the transmitted data.

In the next section, the technologies that are proposed to support these algorithms are discussed. Their choice can have a significant impact on the final product, so it is important to have an idea of the expected performance when considering a given technology.

Figure 2.4 – Impulse response and frequency response of raised cosine pulse.

#### 2.3 Digital Communication Technologies

The advent of the digital communication has started a new era for communication systems in general. This paradigm has been supported by the proposal of a set of technologies which purpose is to increase the overall productivity in digital systems designing. In the signal processing domain, these technologies allow implementing most of the algorithms discussed in the previous section and they are often referred to as the baseband technology. As the complexity of the communication systems increases, technologies turn out to be rapidly obsolete and may require to be further enhanced so as to support more complex algorithm implementations. As a result, a bunch of technologies, most of them issued from research programs, for digital systems designing have appeared throughout the decades. These technologies can be classified into two main groups namely, the software technologies and the hardware technologies. They both enable implementing digital systems and are supported by specific design flows.

In this section we briefly review the technologies that are involved into digital signal processing systems, which essentially consist in design flows and running platforms. Designs flows, on the one hand, are generally composed of textual or graphical programming languages and their associated compilers. The platforms on the other hand, represent the physical device on which the application is run. In DSP, the choice of the underlying platform is governed by the target performance. Those performance are diverse, in the sense that they can be estimated in terms of processing speed, platform area, power consumption or flexibility. Further to this, DSP applications are described as computationally intensive, data independent, exhibiting a high level of parallelism and requiring low arithmetic architectures. As a result, different types of platforms have been proposed, some of which tending to be more software-oriented in contrast to the hardware-oriented platforms. Coarsely, software-oriented platforms emphasize on the programmability issues whereas the hardware-oriented platforms focus more on the resulting circuit architecture. Each of these two platforms is depicted in the following two paragraphs.

#### 2.3.1 DSP Software Platforms and Programming Environment

Microprocessors are generally characterized by their Instruction Set Architecture whose instructions are sequentially evaluated on a fixed hardware. They are declined into two types namely, the Complex Instruction Set Computer (CISC) [29] machines that have some complex instruction formats and the Reduced Instruction Set Computer (RISC) [29] machines with regular and simple instruction formats. Microprocessors are widespread electronic components that are employed in

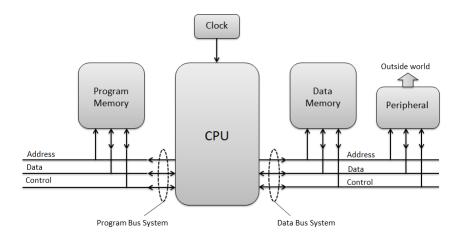

Figure 2.5 – Harvard Architecture.

many industrial fields such as the automotive, the aerospace, the home/building automation or the telecommunication industry. However, their sequential nature can make them unsuitable for an efficient implementation of computationally intensive DSP applications.

These limitations have led in the 80s to the proposal of microprocessors that are optimized for DSP, those DSP microprocessors [30] are capable to perform multiplication and accumulation operations by consuming less power. They rely on the Harvard architecture [30] which separates the data memory and the program memory as shown in Figure 2.5. Indeed, a common data and program memory leads to a memory bottleneck that limits the performance of microprocessors. DSP microprocessors have been enhanced with dedicated complex functions and also with some of the fixed-point operators that are often required in most of DSP applications.

Furthermore, parallelism has been also addressed in DSP microprocessors by introducing instruction level parallelism through instruction pipelining or  $Very\ Long\ Instruction\ Word\ (VLIW)$  [31] architecture for instance. Thus, DSP microprocessors have become an interesting alternative for implementing DSP applications and they are usually associated with General Purpose Processors (GPPs) or other type of general microprocessors, such as the Advanced RISC Machine (ARM) microprocessors, to implement the rest of the network stack.

As mentioned before, software platforms offer a good trade-off between programmability and performance. Thereby, DSP microprocessors and general purpose microprocessors are supported by software tools that enable specifying and implementing an application from a high-level of abstraction with an a priori knowledge of the underlying architecture. Those tools usually consider a C-based specification of the application and rely on a compiling framework to produce a runtime code that is optimized for the microprocessor architecture. Moreover, some of these compilers are featured with some *intrinsic* functions that are used to optimally target, from the C-based description, a dedicated resource.

#### 2.3.2 DSP Hardware Platforms and Programming Environment

Whilst DSP microprocessors have enabled achieving certain performance in terms of application throughput, they still restrict the application designers to a pre-defined architecture. This restriction limits the achievable level of parallelism, which makes DSP microprocessors unsuitable for several high data rate DSP applications. FPGA and ASIC technologies enable customizing circuit architecture for a given application. From a DSP point of view, these platforms allow defining the architecture that are tailored to an application, thereby optimized in terms of processing speed, resource area and power consumption. FPGAs can be coarsely presented as a set of programmable logic components, interconnections and input/output (I/O) pins at their outer edge as shown in Figure 2.6. Nowadays, they are featured with large memory and data processing resources. Logic

Figure 2.6 – Abstract FPGA representation (left) and a typical FPGA design flow (right).

components can be programmed to implement simple or complex DSP functions while the interconnection is used to program a desired functionality. FPGAs are declined into different types based on the way they are configured. Actually, FPGAs are programmed via configuration files stored into memories. Thus, SRAM-based FPGAs, FLASH-based FPGAs or antifuse-based FPGAs can be found. However, this programmability at the architectural level implies an overhead in terms of power consumption and speed as compared to ASICs fabrics.

ASICs are fully customized architectures that are generally employed for large market technologies. They consist in providing a hardware that is suitable for a given DSP application. By doing so, the provided hardware (referred to as an ASIC) can be optimized to meet all the requirements regarding processing speed, resource area and power consumption. As a result, ASICs are not flexible fabrics and they are usually associated with microprocessors to perform some others task such as control.

The design methodologies employed to prototype an FPGA-based or an ASIC-based DSP application usually relies on Hardware Description Languages (HDLs). Those languages such as Verilog or VHDL are the main entry points for most of the available FPGA and ASIC synthesis tools. HDLs are programming languages that allow an accurate description of circuit architecture at the RTL-level for instance. In the context of FPGA, a HDL description is compiled down to a bitstream which is used to program the FPGA as shown in the design flow illustrated in Figure 2.6. An ASIC development methodology is quite similar to the FPGA ones, however it requires additional steps for the final circuit manufacturing.

#### 2.4 Flexible Radios

In the previous section we have introduced the DSP concept by discussing some of its core principles together with its underlying technologies. A high degree of flexibility is now expected in DSP applications since communication protocols must support multiple modes and transceiver must support multiple communication protocols. Flexible radios are then employed when it comes to incorporate adaptive capabilities. Such radios must be capable for instance to switch between different configurations so as to take advantage of their operating environment. This approach aims at increasing the spectral efficiency or can be used to save the overall energy. Indeed, the

Figure 2.7 – Cognitive cycle composed of three major states.

spectral resource which is managed by the local authorities tends to be scarce because of all the operating radios. One way to tackle this issue is to undertake a cognitive usage of the spectrum by these radios.

#### 2.4.1 Cognitive Radios

Cognitive Radios (CRs) [5] can be defined as radios that are aware of the context in which they are being operated. They observe a set of environmental parameters before selecting the optimal communication scheme. The cognition refers to the fact that cognitive radios monitor their operating environment in order to improve their performance. A cognition cycle as shown in Figure 2.7 is usually employed so as to illustrate the main features of a cognitive radio. It is composed of three major states, namely the *Sense* state where the system monitors a set of metrics, the *Decide* state where the system makes up a decision on which configuration to select and the *Adapt* where the system is reconfigured into the selected configuration. In the following two paragraphs, we will discuss two implementations of a cognitive radio that are the Spectrum-Aware radios and the Multi-Standard radios.

#### Spectrum Aware Systems

The research on cognitive systems has been essentially oriented toward spectrum aware radios. As spectrum turns out to be quite a scarce resource, there has been a growing need for spectrum management techniques so as to take advantage of the underutilized allocated spectrum. Such opportunistic systems aim at achieving better performance from a clever usage of the spectrum. For instance, the white space in the TV band (470 to 790 MHz in Europe) has gathered a lot of interest in the community and an important part of the research in cognitive systems focuses on how to exploit these spectral bands without disturbing the incumbents. The detection of an incumbent is performed by using different signal processing methods that can be found in the literature [32][33][34]. Among those methods, one can mention the energy detector [32] which typically detects the presence of an incumbent by thresholding the energy that is sensed in the channel. A relevant detection technique that is also discussed in the literature is the cyclostationnarity detector [33][34][35] which detects digital modulations through their cyclostionnarity properties. Indeed, most of the digital modulations imply cyclic frequencies in the transmitted signal due to the periodical digital computations performed over random source data. Thus, the cyclostationnarity detector aims at finding a periodicity within the mean and the autocorrelation function of a signal x(t). Equations (2.17) and (2.18) give the mean and the autocorrelation functions of a signal x(t) and (2.19) gives the periodicity of these functions.

$$m_x(t) = E[x(t)] (2.17)$$

$$r_{xx}(t) = E[x(t - \frac{\delta}{2})x^*(t + \frac{\delta}{2})]$$

(2.18)

$$m_x(t+T_0) = m_x(t)$$

$r_{xx}(t+T_0,\delta) = r_{xx}(t+T_0).$  (2.19)

#### **Multi-Standard Systems**

Multi-Standard systems [36][37] can also be viewed as another type of cognitive systems where the cognition is related to the capability to operate with different telecommunication standards. Indeed, several telecommunication standards were released in order to fulfill the increasing demand in terms of data rate. However, given an application (voice, data, video...), the required data rate may vary in the sense that a high data rate standard may not be appropriate to transmit low data rate signal such as voice. It would be more efficient in such cases to switch to a lower data rate standard before initiating the communication. Furthermore, owing to the limited coverage that is offered by the telecommunication operators, multi-standard systems enable, given a geographical region, virtualizing global network coverage. An example of such scenario that we often face is the switching between mobile standards operated by most of the current mobile phones in order to ensure a permanent network access to the users. From an implementation perspective, this is currently achieved by integrating a dedicated chip for each standard and then using a software control to switch at run-time between standards. Some mechanisms are provided to handle the handover between the standards as well. This approach implies a duplication of radio chips, which is not economically sustainable in the long term.

#### 2.4.2 Adaptive Coding and Modulation (ACM) Technique

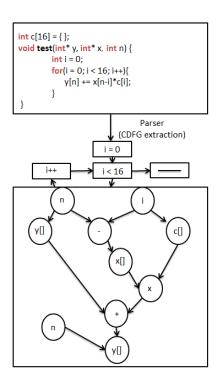

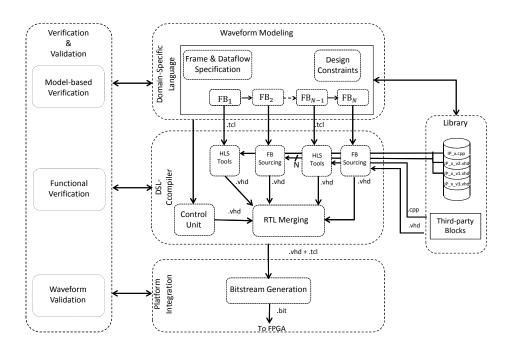

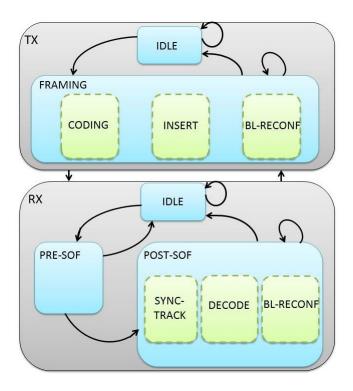

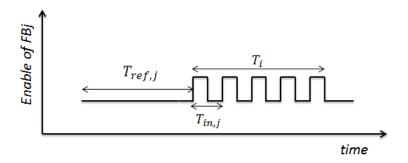

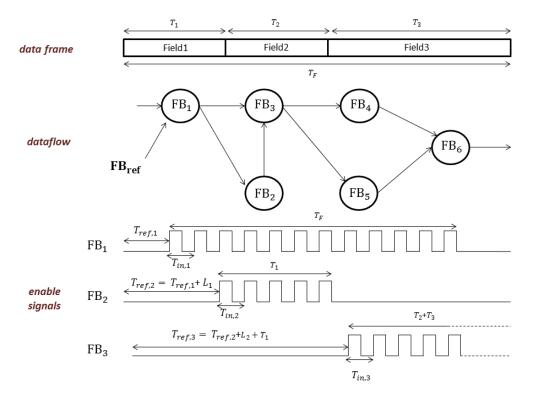

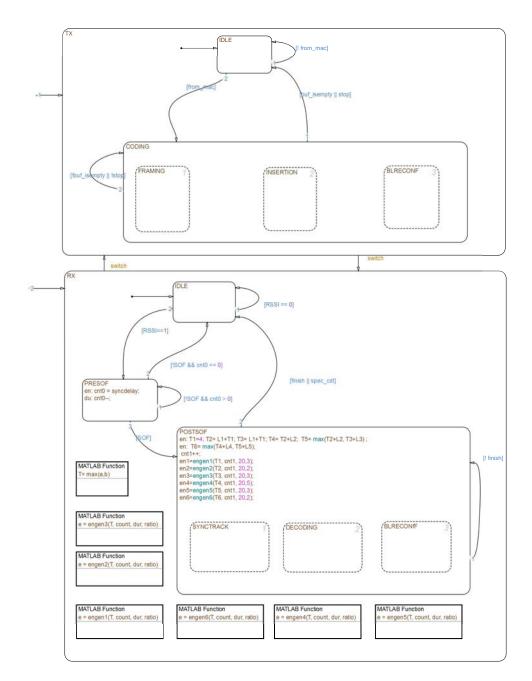

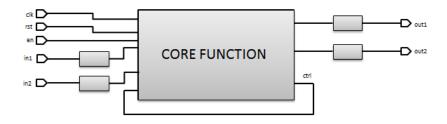

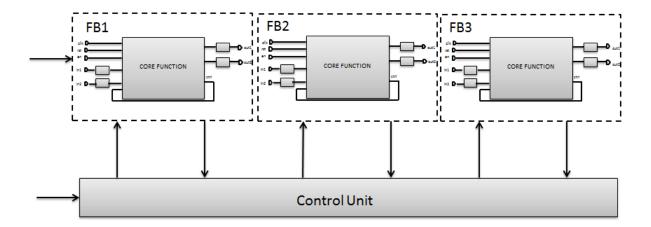

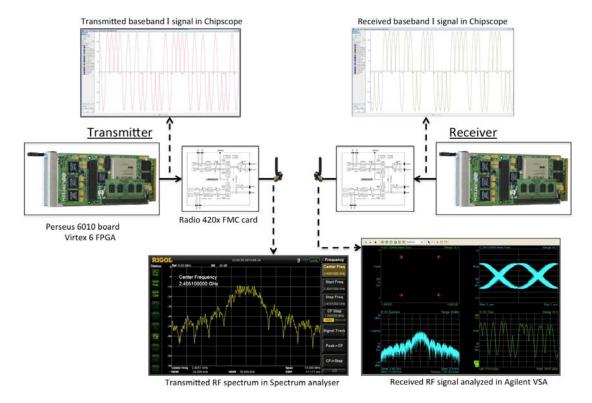

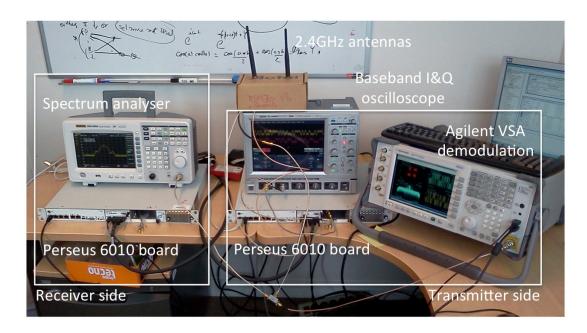

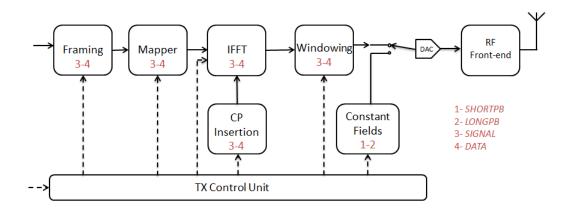

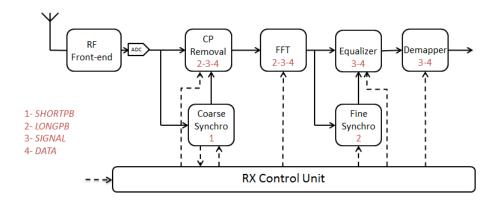

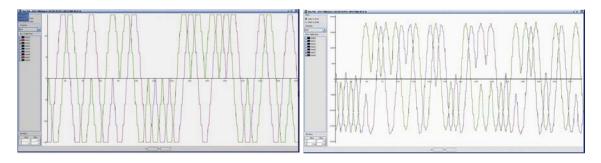

The Adaptive Coding and Modulation (ACM) [38] technique is used in many of the recent radio protocol. Its main purpose is to dynamically improve the overall spectral efficiency, *i.e.* increasing the number of bit per second in a given spectral band. This technique employs some cognition to tailor both the coding and the modulation schemes to the environmental conditions. Thus, depending on the value of the SNR, the system can select which coding or modulation technique to employ. As a result, such a system would be capable to higher the data rate when SNR is high and lower it when SNR is low.