# Security of micro-controllers: From smart cards to mobile devices

Tiana Razafindralambo

# ▶ To cite this version:

Tiana Razafindralambo. Security of micro-controllers : From smart cards to mobile devices. Embedded Systems. Université de Limoges, 2016. English. NNT : 2016LIMO0087 . tel-01492971

# HAL Id: tel-01492971 https://theses.hal.science/tel-01492971

Submitted on 20 Mar 2017  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# On the Security of Microcontrollers: from Smart Cards to Mobile Devices

# THÈSE

présentée et soutenue publiquement le 24-11-2016

pour l'obtention du

# Doctorat de l'Université de Limoges

( spécialité informatique )

par

# Tiana RAZAFINDRALAMBO

### Composition du jury

| Rapporteurs :  | André Seznec, Professeur, IRISA/INRIA, Rennes<br>David Naccache, Professeur, Ecole Nationale Supérieure, Paris                                                                                                                    |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Examinateurs : | Benoit Feix, Responsable Sécurité Cryptographique, UL<br>Jean-Pierre Seifert, Professeur, Université Technique de Berlin<br>Guillaume Bouffard, Ingénieur de Recherche, ANSSI<br>Eric Vetillard, Architecte Sécurité, Prove & Run |

| Directeur :    | Professeurs Christophe Clavier et Jean-Louis Lanet                                                                                                                                                                                |

### Laboratoire de recherche XLIM UMR CNRS 7252

Mis en page avec la classe thesul.

$\dot{A}\ ma$  famille, mes amis et à tous les passionnés.

ii

### Remerciements

Je remercie tout d'abord Christophe Clavier et Jean-Louis Lanet qui m'ont beaucoup inspiré depuis la License et qui m'ont permis de sortir de la routine scolaire de la FAC, grâce à des projets et des sujets de discussion passionnantes et stimulantes. La curiosité, l'envie de comprendre, et la persévérance ont été les meilleurs enseignements qu'ils m'ont inculqué, et qui ne se trouvent dans aucun manuel scolaire. Un grand merci à eux deux d'avoir accepté d'être mes directeurs de thèse.

Je suis très reconnaissant envers les professeurs André Seznec et David Naccache pour avoir accepté de rapporter mes travaux. Je les remercie pour le temps qu'ils ont consacré à la relecture de ce mémoire, ainsi que pour leur présence dans mon jury. Un grand merci en particulier à David Naccache pour avoir accepté de présider ce jury de thèse.

Un très grand et chaleureux merci à Jean-Pierre Seifert, Guillaume Bouffard, Benoît Feix et Eric Vétillard d'avoir accepté de faire parti du jury.

Merci sincèrement Benoît de m'avoir si bien accueilli à UL et de m'avoir communiqué, inspiré et transmis, sans que tu ne le saches, la passion pour notre métier si particulier, même si nous n'avions pas forcément les mêmes domaines d'expertise.

Merci Guillaume d'avoir joué le rôle du grand frère, et de m'avoir guidé de la FAC à Michard, des cartes à puce au Docteur. Un gros bisous à Anne qui m'a aussi beaucoup supporté et encouragé.

Je remercie aussi très chaleureusement, Hugues Thiebeauld, Georges Gagnerot, Lionel Rivière, Antoine Wurcker et Pierre Carru, patrons et collègues passionnés, qui m'ont supporté, écouté, lu et conseillé jusqu'au bout.

Sur une note un peu plus personnelle, j'aimerais beaucoup remercier affectueusement mes parents et mon frère qui m'ont toujours poussé à persévérer, et qui m'ont toujours soutenu quels qu'eussent été les épreuves de la vie, et surtout pendant ces 3/4 dernières années. Bà mamy be!

Finalement, je te remercie infiniment Jenny pour m'avoir accompagné pendant tout ce temps et de m'avoir fais confiance jusque là et d'avoir affronté sur la ligne de front tous les hauts et les bas de la dernière année. Promis, j'aurais un peu plus de temps cette fois-ci <3... iv

# Contents

| Remerciements iii |         |                                                                           |   |

|-------------------|---------|---------------------------------------------------------------------------|---|

| Chapte            | er 1 In | troduction                                                                | 1 |

| 1.1               | What    | makes Smarpthones so "smart"?                                             | 1 |

|                   | 1.1.1   | From an Actual Phone to a Multi-Purpose Device                            | 1 |

|                   | 1.1.2   | The Operating Systems that Make the Magic Happen $\ . \ . \ . \ .$ .      | 2 |

| 1.2               | Motiva  | ation                                                                     | 4 |

|                   | 1.2.1   | Study of the Attack Surface and the Attacks Implementations $\ . \ . \ .$ | 4 |

|                   |         | 1.2.1.1 Software Attacks                                                  | 4 |

|                   |         | 1.2.1.2 Physical Attacks                                                  | 4 |

|                   | 1.2.2   | Hardware and Software Security of Microcontrollers in the Context of      |   |

|                   |         | Mobile Devices                                                            | 5 |

| 1.3               | Contri  | ibutions and Outline                                                      | 6 |

|                   |         |                                                                           |   |

# Partie I Software Security of Java Card-based Secure Elements

-

| Chapte | er 2 Se      | ecurity C | oncepts behind Java Card-based Secure Elements                 | 11 |

|--------|--------------|-----------|----------------------------------------------------------------|----|

| 2.1    | Introduction |           |                                                                | 12 |

|        | 2.1.1        | What is   | a Smart Card?                                                  | 12 |

|        | 2.1.2        | What is   | a Secure Element?                                              | 12 |

|        |              | 2.1.2.1   | A Tamper Resistant Microcontroller                             | 12 |

|        |              | 2.1.2.2   | A Smarter Contact and Contactless Smart Card $\ . \ . \ . \ .$ | 12 |

| 2.2    | Java (       | Card Tech | nology                                                         | 13 |

# Contents

|     | 2.2.1  | Java Card Architecture                                                    | 13 |

|-----|--------|---------------------------------------------------------------------------|----|

|     | 2.2.2  | Java Card Virtual Machine                                                 | 14 |

|     | 2.2.3  | Java Card Runtime Environment                                             | 14 |

| 2.3 | Securi | ty Concepts in a Multi-Application Environment                            | 15 |

|     | 2.3.1  | Application Verification                                                  | 15 |

|     | 2.3.2  | Application Loading                                                       | 15 |

|     | 2.3.3  | Application Isolation                                                     | 15 |

|     |        | 2.3.3.1 The Firewall                                                      | 15 |

|     |        | 2.3.3.2 The Security Domains                                              | 16 |

|     | 2.3.4  | Operation Atomicity                                                       | 16 |

| 2.4 | Summ   | ary                                                                       | 16 |

|     |        |                                                                           |    |

| -   |        | troduction to Software Attacks on Java Card Platforms                     | 19 |

| 3.1 |        | ty Risks of Java Cards                                                    | 21 |

|     | 3.1.1  | Invasive attacks                                                          | 21 |

|     | 3.1.2  | Semi-Invasive attacks                                                     | 21 |

|     | 3.1.3  | Non-Invasive attacks                                                      | 21 |

|     |        | 3.1.3.1 Side-channel attacks                                              | 21 |

|     |        | 3.1.3.2 Software Attacks                                                  | 22 |

| 3.2 |        | Techniques through Malevolent Applications                                | 23 |

|     | 3.2.1  | Concepts of Well-formed and Ill-formed Applications                       | 23 |

|     | 3.2.2  | Malicious Well-formed Application based Attacks                           | 23 |

|     |        | 3.2.2.1 Abuse of the Java Card Firewall                                   | 23 |

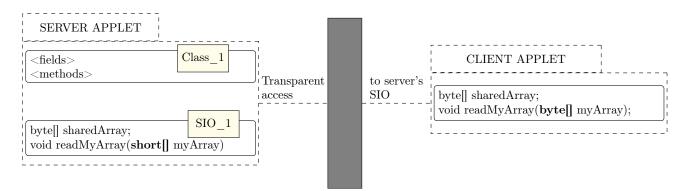

|     |        | Abusing Shareable Interface Objects –                                     | 24 |

|     |        | 3.2.2.2 Transaction Mechanism Abuse                                       | 24 |

|     | 3.2.3  | Ill-formed application based attacks                                      | 26 |

|     |        | 3.2.3.1 Type Confusion attacks (TC)                                       | 26 |

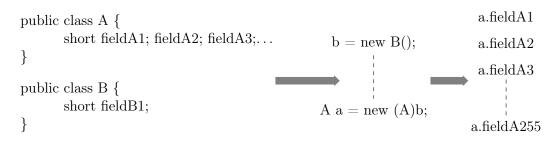

|     |        | Reference-to-Primitive Type Confusion (RPTC)                              | 27 |

|     |        | Primitive-to-Reference Type Confusion (PRTC)                              | 28 |

|     |        | Reference-to-Reference Type Confusion (RRTC)                              | 28 |

|     |        | 3.2.3.2 Stack Overflow/Underflow Attacks                                  | 30 |

|     |        | 3.2.3.3 Static Links based attacks (SLA)                                  | 32 |

|     |        | 3.2.3.4 Control Flow Modification based Attacks (CFTA)                    | 33 |

|     |        | Return Address Modification                                               | 33 |

|     |        | Jump Subroutine (JSR) Exploitation                                        | 33 |

| 3.3 | Our G  | eneric Framework for Evaluating Java Card Platforms and Applets $\ . \ .$ | 34 |

|     | 3.3.1  | Testing Tools Categories                                                  | 34 |

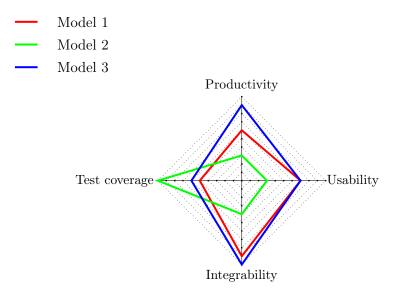

|        |        | 3.3.1.1                                                                      | Model 1: Static One-to-One approach                  | 35                               |

|--------|--------|------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------|

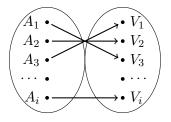

|        |        | 3.3.1.2                                                                      | Model 2: Automated One-to-Many approach              | 36                               |

|        |        | 3.3.1.3                                                                      | Model 3: Semi-Automatic One-to-Many approach         | 36                               |

|        | 3.3.2  | Constrai                                                                     | nts                                                  | 37                               |

|        | 3.3.3  | Approac                                                                      | hes comparison                                       | 37                               |

|        | 3.3.4  | A Frame                                                                      | ework for Designing Attack Scenarios                 | 37                               |

|        | 3.3.5  | A Frame                                                                      | ework for Performing Static Code Analysis            | 38                               |

|        | 3.3.6  | Example                                                                      | e of Usage                                           | 38                               |

| 3.4    | Summ   | nary                                                                         |                                                      | 42                               |

| ~1 /   | 4 7 4  |                                                                              |                                                      |                                  |

| -      |        |                                                                              | Frame Creation to Exploit Stack Underflow Attacks on |                                  |

| lava C | Card P | latform                                                                      |                                                      | 43                               |

| 4.1    | Proble | em analys                                                                    | is                                                   | 45                               |

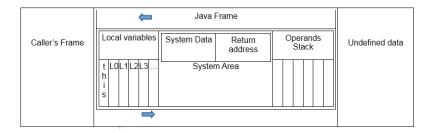

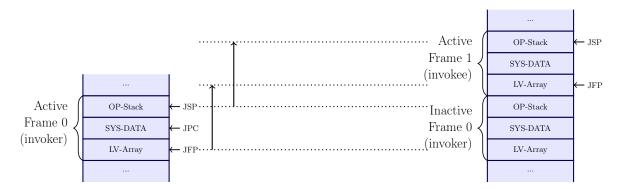

|        | 4.1.1  | The Java                                                                     | a Virtual Machine stack                              | 45                               |

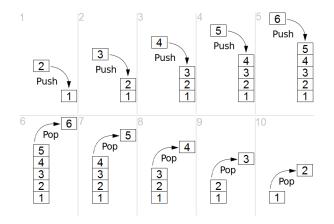

|        |        | 4.1.1.1                                                                      | Basic Stacks Implementations                         | 45                               |

|        |        | 1.1.1.1                                                                      |                                                      |                                  |

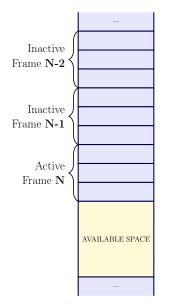

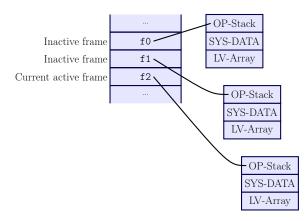

|        |        | 4.1.1.2                                                                      | Stack Structure                                      | 45                               |

|        |        |                                                                              | -                                                    | $\frac{45}{47}$                  |

|        | 4.1.2  | 4.1.1.2<br>4.1.1.3                                                           | Stack Structure                                      |                                  |

|        | 4.1.2  | 4.1.1.2<br>4.1.1.3                                                           | Stack Structure                                      | 47                               |

|        | 4.1.2  | 4.1.1.2<br>4.1.1.3<br>Compile                                                | Stack Structure                                      | 47<br>47                         |

|        | 4.1.2  | 4.1.1.2<br>4.1.1.3<br>Compile<br>4.1.2.1                                     | Stack Structure                                      | 47<br>47<br>47                   |

| 4.2    |        | 4.1.1.2<br>4.1.1.3<br>Compile<br>4.1.2.1<br>4.1.2.2<br>4.1.2.3               | Stack Structure                                      | 47<br>47<br>47<br>48             |

| 4.2    |        | 4.1.1.2<br>4.1.1.3<br>Compile<br>4.1.2.1<br>4.1.2.2<br>4.1.2.3<br>ption of n | Stack Structure                                      | 47<br>47<br>47<br>48<br>48       |

| 4.2    | Corru  | 4.1.1.2<br>4.1.1.3<br>Compile<br>4.1.2.1<br>4.1.2.2<br>4.1.2.3<br>ption of n | Stack Structure                                      | 47<br>47<br>47<br>48<br>48<br>48 |

|     |        | 4.2.1.2    | Method's reference modification                                                        | 52 |

|-----|--------|------------|----------------------------------------------------------------------------------------|----|

|     |        | 4.2.1.3    | Token modification on <i>invokeinterface</i>                                           | 53 |

|     |        | 4.2.1.4    | The export file modification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 54 |

| 4.3 | Attack | ks scenari | os for Java Card                                                                       | 54 |

|     | 4.3.1  | Underflo   | ow on sensitive buffers                                                                | 54 |

|     | 4.3.2  | Underflo   | ow on Runtime Data                                                                     | 54 |

|     |        | 4.3.2.1    | Frame Exploitation on JSP                                                              | 54 |

|     |        | 4.3.2.2    | Frame Exploitation on JFP                                                              | 55 |

|     |        | 4.3.2.3    | Frame Exploitation on JPC                                                              | 55 |

|     |        | 4.3.2.4    | Frame Exploitation on Execution Context                                                | 55 |

|     |        | 4.3.2.5    | Frame Exploitation on call-return structure                                            | 56 |

| 4.4 | Attack | k assumpt  | tions                                                                                  | 56 |

|     | 4.4.1  | Reliance   | e on secret of other entities                                                          | 56 |

|     |        |            |                                                                                        |    |

| Contents |

|----------|

|----------|

\_\_\_\_

|        | 4.4.2   | The bytecode verification                                                                                                                | 57 |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|        | 4.4.3   | New edition, new vulnerabilities                                                                                                         | 57 |

| 4.5    | Concl   | $\operatorname{sion}$                                                                                                                    | 58 |

| Chapte | er 5 V  | sual Forensic Analysis of a Java Card Raw Memory Dump and                                                                                |    |

| Autom  | natic C | ode Extraction 5                                                                                                                         | 59 |

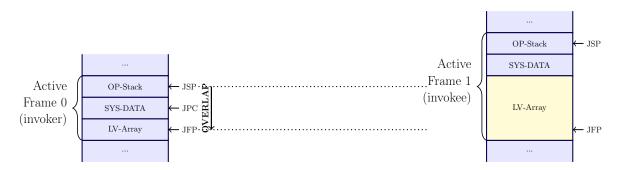

| 5.1    | Proble  | m Analysis                                                                                                                               | 61 |

|        | 5.1.1   | Memory Forensics of a Java Card Dump                                                                                                     | 61 |

|        | 5.1.2   | Understanding the Index of Coincidence Computation                                                                                       | 62 |

|        |         | 5.1.2.1 Index of Coincidence of a Language                                                                                               | 63 |

|        |         | 5.1.2.2 Index of Coincidence for measuring the roughness of a text 6                                                                     | 63 |

|        |         | 5.1.2.3 Approximating the I.C measure                                                                                                    | 64 |

|        | 5.1.3   | Analysis of unknown Binary file                                                                                                          | 64 |

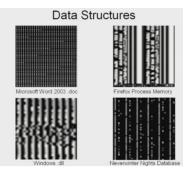

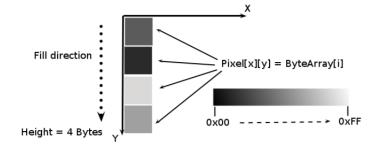

|        | 5.1.4   | Visual Reverse Engineering of Binary and Data Files                                                                                      | 65 |

|        | 5.1.5   | Experiments                                                                                                                              | 66 |

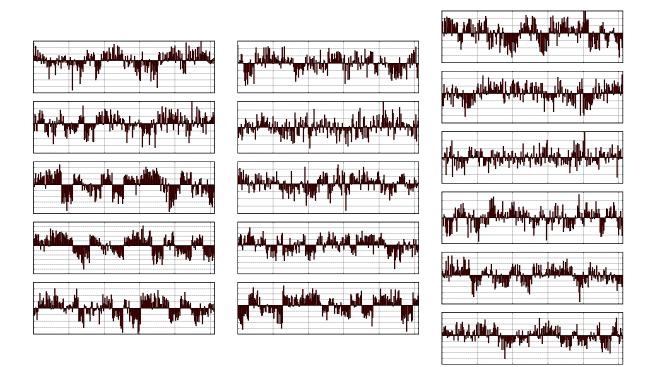

|        |         | 5.1.5.1 Visual Signature of a Java Card Application                                                                                      | 66 |

|        |         | 5.1.5.2 CAP components extraction $\ldots \ldots \ldots$           | 66 |

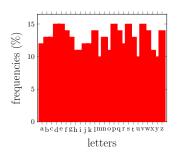

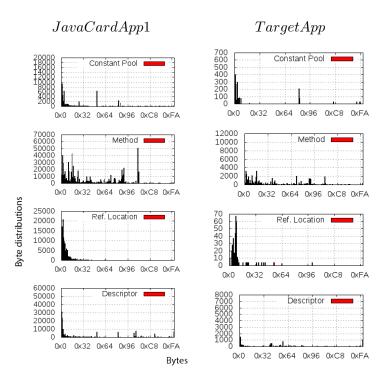

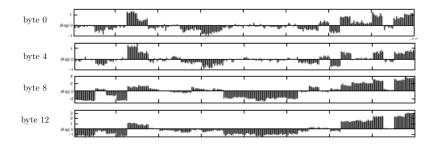

|        |         | 5.1.5.3 Byte distribution analysis and characterization $\theta$                                                                         | 67 |

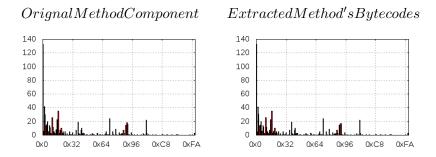

|        |         | Byte distribution –                                                                                                                      | 67 |

|        |         | Statistical tests for comparing two sets of byte distribution – $\ . \ \ 0$                                                              | 68 |

|        |         | Analysis of the byte distribution of a Java Card Memory Dump $\theta$                                                                    | 69 |

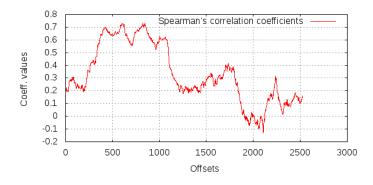

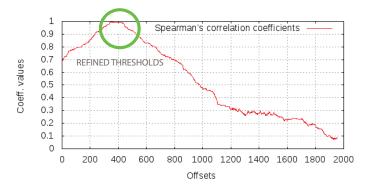

|        |         | $Correlation tests - \ldots \dots \dots$ | 69 |

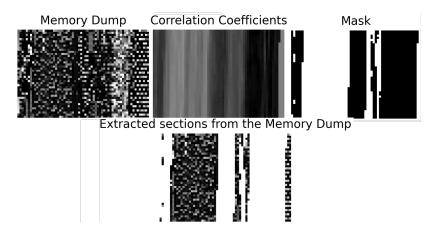

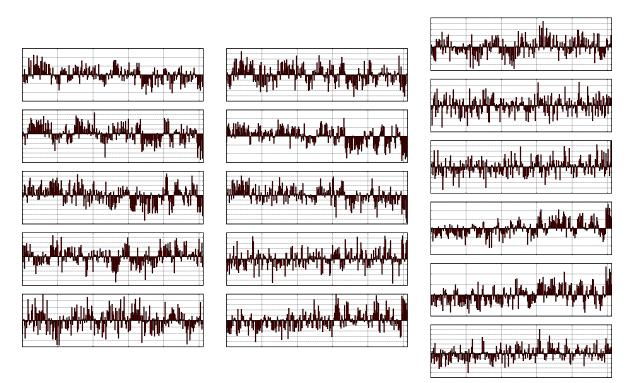

| 5.2    | Auton   | ated Java Card Application Code Detection                                                                                                | 71 |

|        | 5.2.1   | The Running Correlation Coefficient Computation Trace (RCCT) $~$ $~$                                                                     | 71 |

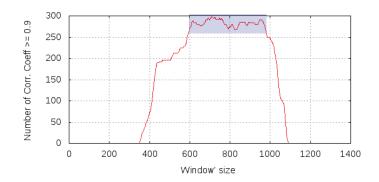

|        | 5.2.2   | Data Extraction                                                                                                                          | 72 |

| 5.3    | Count   | ermeasures                                                                                                                               | 74 |

|        | 5.3.1   | Instructions Scrambling                                                                                                                  | 74 |

|        | 5.3.2   | Improved Instructions Scrambling                                                                                                         | 74 |

| 5.4    | Concl   | $\operatorname{sion}$                                                                                                                    | 75 |

|        |         |                                                                                                                                          |    |

# Partie II Security of Baseband Processors

\_

-

| Chapter 6 Attack Surface | e Analysis of Baseband P | rocessors and Related Work 79 |

|--------------------------|--------------------------|-------------------------------|

|--------------------------|--------------------------|-------------------------------|

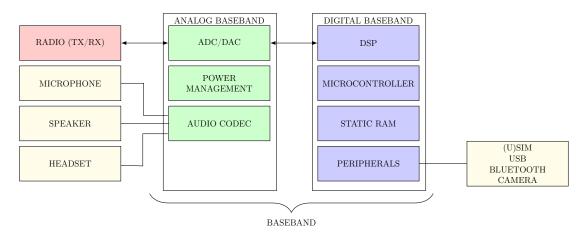

| 6.1 | Introd | uction to the Baseband Processor                                                                     | 81  |

|-----|--------|------------------------------------------------------------------------------------------------------|-----|

|     | 6.1.1  | Baseband Architecture Overview                                                                       | 81  |

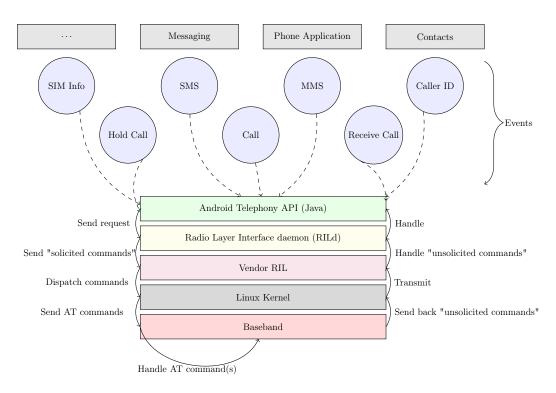

|     | 6.1.2  | Communication between the Baseband and the Application Processors                                    | 81  |

|     | 6.1.3  | The Baseband Operating System                                                                        | 82  |

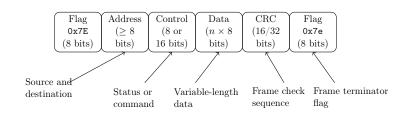

|     | 6.1.4  | Communicating with a baseband                                                                        | 82  |

|     |        | 6.1.4.1 The Radio Layer Interface                                                                    | 82  |

|     |        | 6.1.4.2 Hayes commands for communicating with a baseband                                             | 82  |

| 6.2 | Relate | d Work                                                                                               | 84  |

|     | 6.2.1  | Local Attacks                                                                                        | 84  |

|     |        | 6.2.1.1 Software unlock                                                                              | 84  |

|     |        | 6.2.1.2 Hardware unlock                                                                              | 84  |

|     |        | $6.2.1.3  \text{Bootloader unlock} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                           | 85  |

|     | 6.2.2  | Attack Through USB Connection                                                                        | 85  |

|     | 6.2.3  | Remote Attacks                                                                                       | 86  |

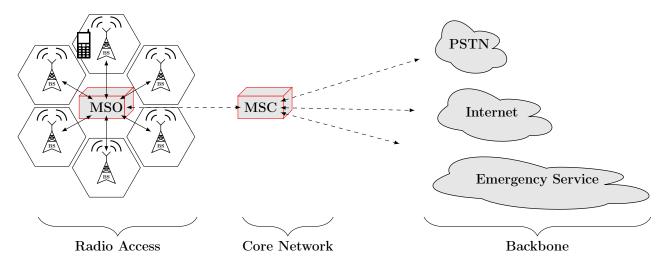

|     |        | 6.2.3.1 Basics on Cellular Network                                                                   | 86  |

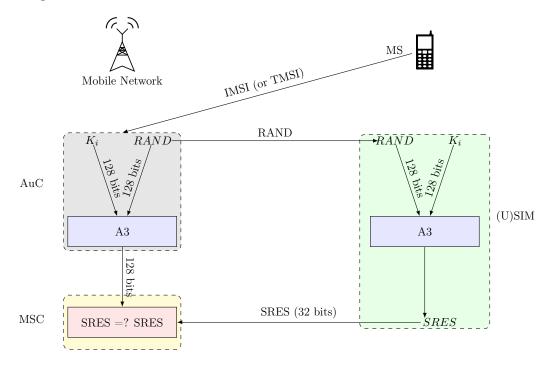

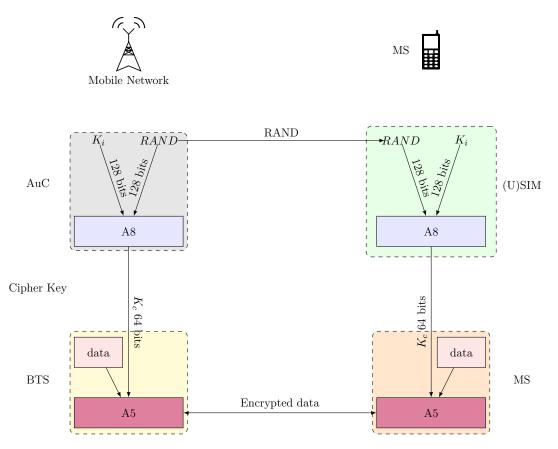

|     |        | 6.2.3.2 Overview of GSM Security Features                                                            | 86  |

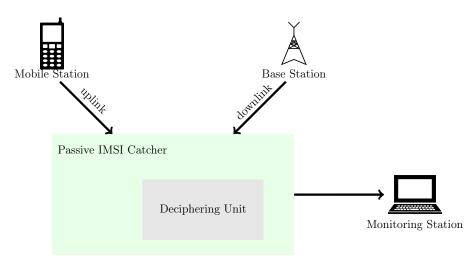

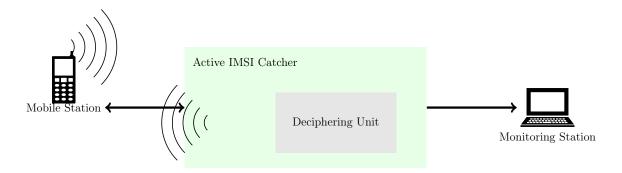

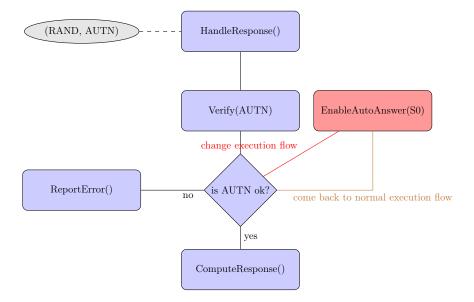

|     |        | 6.2.3.3 Remote attack through the GSM/UMTS network $\hdots$                                          | 88  |

|     |        | 6.2.3.4 $$ Remote attack through the CDMA/3G and 4G networks $$                                      | 90  |

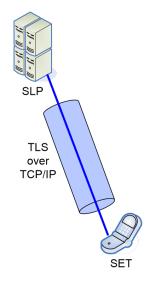

|     |        | 6.2.3.5 Remote Attack against Localisation-Based Services $\ldots$ .                                 | 90  |

|     |        | 6.2.3.6 Global Remote Code Execution Through OTA Device Man-                                         |     |

|     |        | agement Protocols                                                                                    | 92  |

| 6.3 | Findir | ng Bugs in a Baseband Processor                                                                      | 92  |

|     | 6.3.1  | Fuzzing the baseband                                                                                 | 92  |

|     | 6.3.2  | Source Code Review and/or Static Analysis of the Baseband Firmware's                                 |     |

|     |        | Binary                                                                                               | 94  |

|     | 6.3.3  | Debugging the Baseband Firmware                                                                      | 98  |

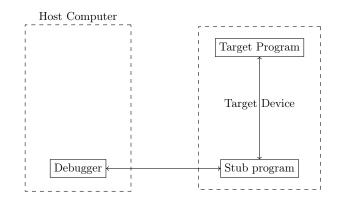

|     |        | 6.3.3.1 Debugging through simulation                                                                 | 98  |

|     |        | 6.3.3.2 Software-only solution                                                                       | 98  |

|     |        | 6.3.3.3 Hardware-assisted solution                                                                   | 99  |

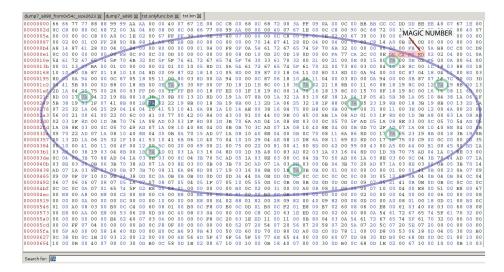

|     | 6.3.4  | Static Analysis of a Raw Memory Dump of the Baseband at Runtime                                      | 100 |

|     | 6.3.5  | Dynamic Analysis of an Embedded Firmware                                                             | 102 |

| 6.4 | Analy  | sis of the REX micro-kernel                                                                          | 103 |

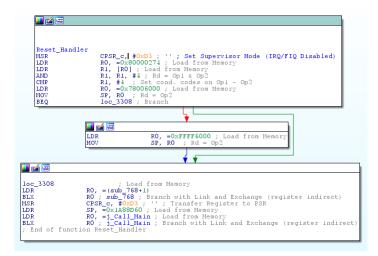

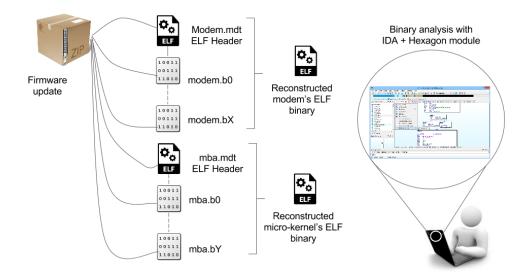

|     | 6.4.1  | Methodology                                                                                          | 104 |

|     | 6.4.2  | From the Boot Sequence to the SIM Interface Implementation $\ . \ . \ .$                             | 104 |

|     |        | $6.4.2.1  \text{The Boot Sequence}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 104 |

\_

\_\_\_\_\_

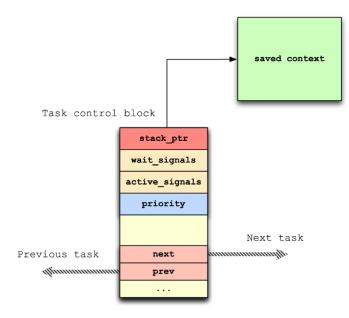

|     | 6.4.2.2         | REX's Tasks                                                    | 105 |

|-----|-----------------|----------------------------------------------------------------|-----|

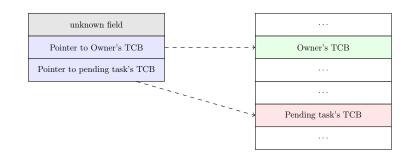

|     | 6.4.2.3         | REX's Dynamic Memory Management                                | 107 |

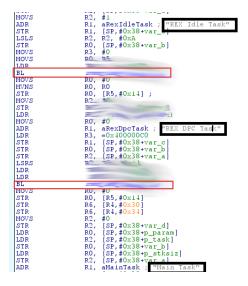

|     | 6.4.2.4         | REX's primary tasks                                            | 107 |

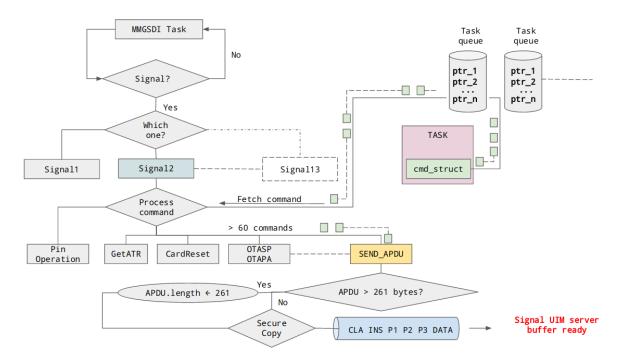

|     | 6.4.2.5         | Analysis of the SIM Interface Implementation $\ . \ . \ . \ .$ | 108 |

| 6.5 | Analysis of the | SIM interface implementation on an actual mobile device $\ $   | 111 |

| 6.6 | Conclusion and  | Future Investigations                                          | 113 |

## Partie III Practical Time-Driven Cache Attack on a Mobile Device

# Chapter 7 Introduction to ARM Processors and Their Multi-Level Cache Memories 117

| 7.1 | Generalities on Advanced RISC Machine (ARM) Processor |                                                                                                                          |  |  |

|-----|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| 7.2 | The P                                                 | rinciple of Locality                                                                                                     |  |  |

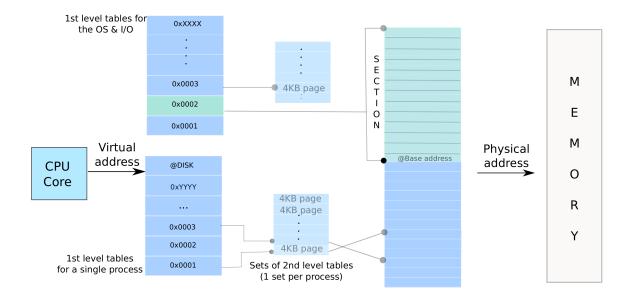

| 7.3 | Paging                                                | g Systems                                                                                                                |  |  |

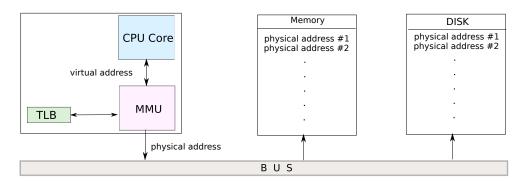

|     | 7.3.1                                                 | The Table Lookaside Buffer (TLB)                                                                                         |  |  |

|     |                                                       | 7.3.1.1 Notions about TLB misses                                                                                         |  |  |

| 7.4 | The C                                                 | Cache Memory                                                                                                             |  |  |

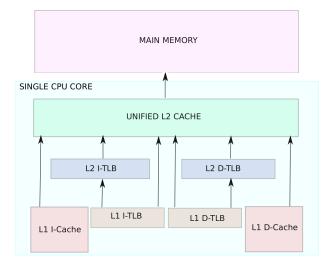

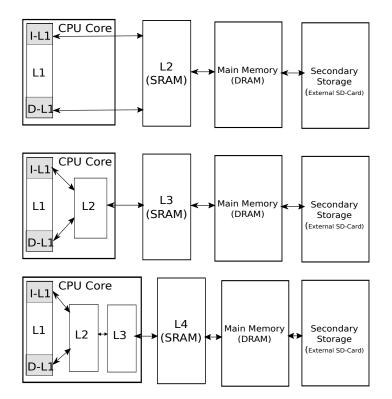

|     | 7.4.1                                                 | Cache Levels                                                                                                             |  |  |

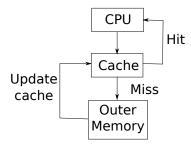

|     | 7.4.2                                                 | Cache Hits and Cache Misses                                                                                              |  |  |

|     | 7.4.3                                                 | Types of Cache Misses                                                                                                    |  |  |

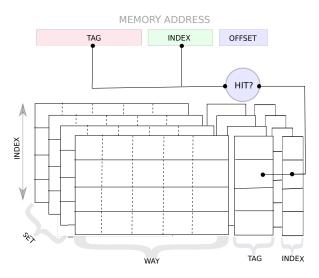

|     | 7.4.4                                                 | The Cache Associativity                                                                                                  |  |  |

|     | 7.4.5                                                 | Locating Data in The Cache                                                                                               |  |  |

|     | 7.4.6                                                 | Replacement Policy                                                                                                       |  |  |

|     | 7.4.7                                                 | Cache Writing Policies                                                                                                   |  |  |

|     | 7.4.8                                                 | Cache Allocation Policy on a Cache Miss                                                                                  |  |  |

|     | 7.4.9                                                 | Inclusive versus Exclusive Multi-level Cache                                                                             |  |  |

| 7.5 | Summ                                                  | $nary \dots \dots$ |  |  |

| 8.1    | Introd  | uction and Related Work                                                                                   |

|--------|---------|-----------------------------------------------------------------------------------------------------------|

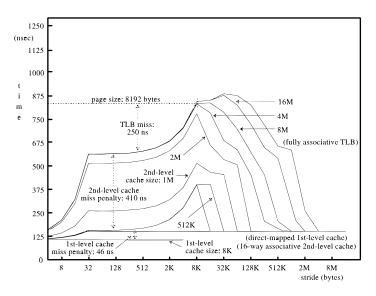

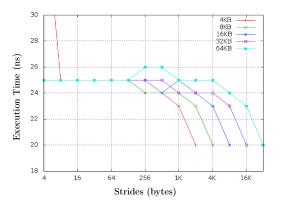

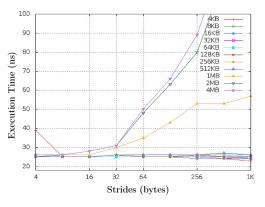

| 8.2    | On the  | e Characterization of the Cache Parameters                                                                |

|        | 8.2.1   | Strided Memory Accesses                                                                                   |

|        | 8.2.2   | Sequential and Random Memory Accesses                                                                     |

|        | 8.2.3   | Dealing with Noise                                                                                        |

| 8.3    | Measu   | rement of Cache Effects on an ARM Processor                                                               |

|        | 8.3.1   | Resulting Traces                                                                                          |

|        | 8.3.2   | Observations and Analysis                                                                                 |

| 8.4    | Summ    | ary                                                                                                       |

| Chapte | er 9 In | troduction to micro architectural Attacks 139                                                             |

| 9.1    |         | architectural Attacks                                                                                     |

|        | 9.1.1   | Data Cache Timing Attack (DCTA)                                                                           |

|        | 9.1.2   | Instruction Cache Analysis Attack (ICAA)                                                                  |

|        | 9.1.3   | Branch Prediction Analysis                                                                                |

|        | 9.1.4   | Shared Function Units Attack (SFUA)                                                                       |

| 9.2    | Cache   | -based Attacks                                                                                            |

|        | 9.2.1   | Time-Driven Cache Attacks                                                                                 |

|        | 9.2.2   | Trace-Driven Cache Attacks                                                                                |

|        | 9.2.3   | Access-Driven Cache Attacks                                                                               |

| 9.3    | Inform  | action Extraction Through Cache Attacks                                                                   |

|        | 9.3.1   | Cache information Extraction Techniques                                                                   |

|        |         | 9.3.1.1 Evict+Time                                                                                        |

|        |         | 9.3.1.2 Prime+Probe                                                                                       |

|        |         | 9.3.1.3 Flush+Reload                                                                                      |

|        |         | 9.3.1.4 $Prime+Trigger+Probe \dots 144$                                                                   |

|        |         | 9.3.1.5 Evict + Reload $\ldots \ldots 145$ |

|        |         | 9.3.1.6 S\$A Attack                                                                                       |

|        |         | 9.3.1.7 Flush + Flush                                                                                     |

|        | 9.3.2   | Cache Attacks Applied to ARM platforms                                                                    |

| 9.4    | Summ    | ary                                                                                                       |

| Chapte | er 10 I | Experimenting Time-Driven Cache Attack on Real Mobile De-                                                 |

| vices  |         | 147                                                                                                       |

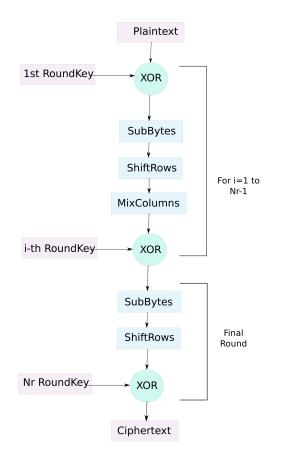

| 10.1   | Introd  | uction to AES                                                                                             |

|        |         |                                                                                                           |

# Contents

| 10.2            | Typical Time-Driven Cache Attack Flow                                                                                    | 149 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| 10.3            | Attack Scenarios                                                                                                         | 150 |

| 10.4            | The Threat Model                                                                                                         | 150 |

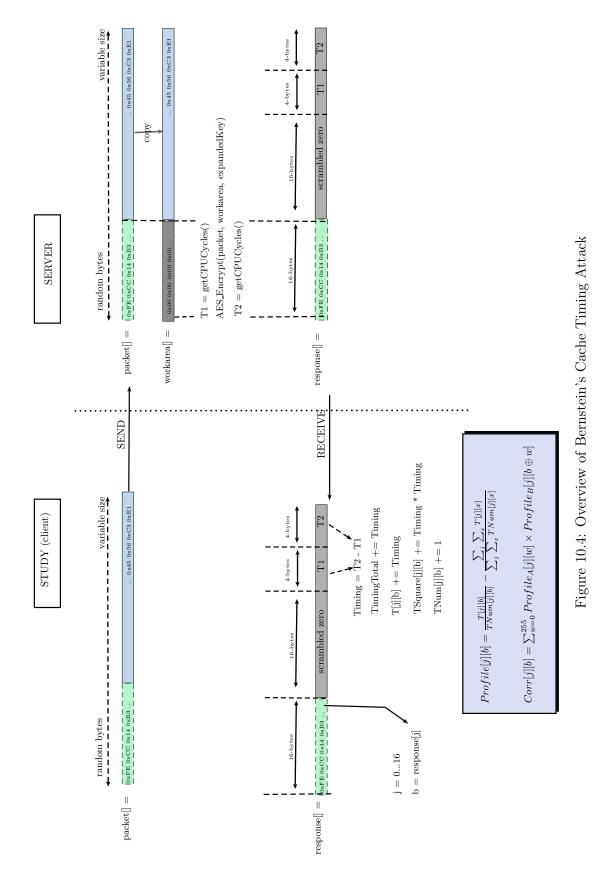

| 10.5            | Overview of Bernstein's Time-Driven Cache Attack                                                                         | 151 |

|                 | 10.5.1 Learning phase                                                                                                    | 151 |

|                 | 10.5.2 Attack phase                                                                                                      | 152 |

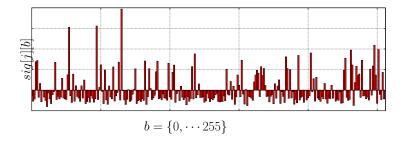

|                 | 10.5.3 Correlation phase $\ldots$       | 153 |

|                 | 10.5.3.1 Filtering Out Key Byte Candidates by Means of a Deviation                                                       |     |

|                 | Threshold $\ldots$                      | 153 |

|                 | 10.5.4 Full key recovery phase $\ldots$ | 154 |

|                 | 10.5.5 Identification of the Right Key Byte Candidates $\ldots \ldots \ldots \ldots \ldots$                              | 156 |

| 10.6            | Differences and Improvements                                                                                             | 156 |

|                 | 10.6.1 Local Attack Scenario                                                                                             | 156 |

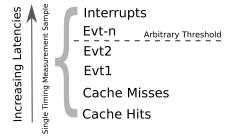

|                 | 10.6.2 Threshold Determination to Minimize the Noise                                                                     | 157 |

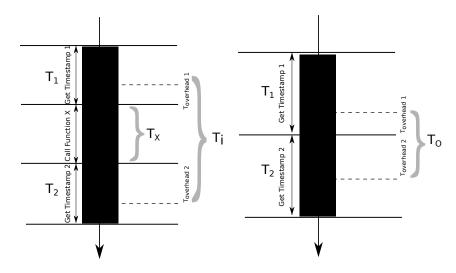

|                 | 10.6.3 Timing Measurement on ARM processor                                                                               | 158 |

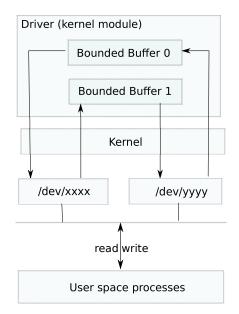

|                 | 10.6.3.1 Timing Measurement From the Kernel Space                                                                        | 159 |

|                 | 10.6.3.2 Timing Measurement From the User Space $\ldots$ $\ldots$ $\ldots$                                               | 160 |

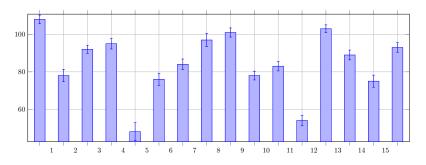

| 10.7            | Practical Experiments                                                                                                    | 161 |

|                 | 10.7.1 Profiling                                                                                                         | 161 |

|                 | 10.7.2 Learning and Attack phase set up                                                                                  | 161 |

|                 | 10.7.3 The Correlation Phase Results $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 163 |

|                 | 10.7.4 Observations $\ldots$            | 163 |

| 10.8            | Results Summary                                                                                                          | 166 |

| 10.9            | Future Investigations                                                                                                    | 167 |

|                 | 10.9.1 Performance Counters Inaccuracy                                                                                   | 167 |

|                 | 10.9.2 On the Quantification of System Noise $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                          | 167 |

|                 | 10.9.3 On a More Robust Key-Search Complexity Evaluation                                                                 | 167 |

|                 | 10.9.3.1 Choosing The Relevant Combination Functions $\ldots \ldots \ldots$                                              | 167 |

|                 | 10.9.3.2 Using Artificial Neural Networks                                                                                | 168 |

| 10.10           | Conclusion                                                                                                               | 168 |

| Conclusion      | and Future Work                                                                                                          | 171 |

| Publication     | 15                                                                                                                       | 175 |

| Bibliograph     | ıy                                                                                                                       | 177 |

| List of Figures |                                                                                                                          |     |

# Chapter 1

# Introduction

## 1.1 What makes Smarpthones so "smart"?

### 1.1.1 From an Actual Phone to a Multi-Purpose Device

Moore's law<sup>1</sup> states that the number of transistors on an affordable CPU (Central Processing Unit) would double every two years. This implies the fact that the more transistors we have, the faster a processor can be. But somehow, more transistors also means more space. For 50 years, following Moore's law, continual shrinking of transistors has helped make computers and any electronic device more powerful, compact, and energy-efficient. Although Moore's empirical observation is now considered as obsolete [Man00], it has helped in bringing powerful Internet services, breakthroughs in fields such as artificial intelligence and genetics and smartphones.

Initially, so-called GSM (Global System for Mobile) phones were actual phones that provided the necessary for performing voice calls and SIM (Subscriber Identity Module) phone book editing features. Hereafter, Personal Digital Assitants (PDA) appeared and introduced touch screen user interfaces and a set of application programs (calendar, scientific calculators, etc.). Basically, PDAs were mobile electronic devices that function as a personal information manager. Afterwards, PDA's functionalities were slowly added to phones. Those phones were called "feature phones".

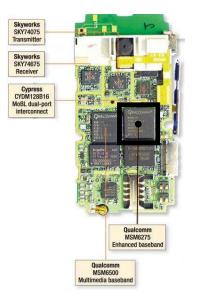

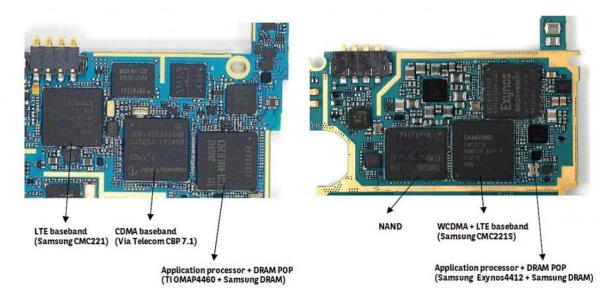

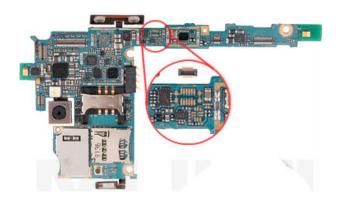

Nowadays mobile devices are called "smartphones". A very common definition that enables to differentiate between both is given by Welte [Wel10]. On one hand, a feature phone is basically a phone that contains a single application processor (AP) that is also called the baseband processor (BP). The latter is the only one responsible of running the software that handle the GSM protocol, managing the user interface and running the applications. On the other hand, a smartphone is a more evolved phone that may embed two main microcontrollers<sup>2</sup> that are physically separated from each other: the baseband processor that remains the one, amongst other radio-related functions, that handles the GSM protocol and the AP (generally multi-core) that is a general purpose one, and manages the user interface and applications.

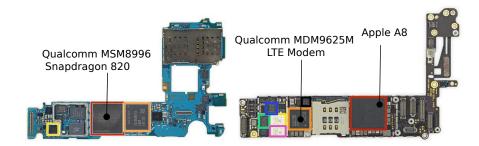

However modern smartphones do not always implement such kind of design where the AP and BP are physically separated. As illustrated by the Figure 1.3, on the left we have the Samsung Galaxy S7 (SGS7) and on the right we have the iPhone 6. The latter has the AP (Apple A8) and the BP (Qualcomm MDM9625M) that are physically separated from each other, where the

<sup>&</sup>lt;sup>1</sup>http://www.mooreslaw.org/

<sup>&</sup>lt;sup>2</sup>A microcontroller contains the actual CPU and memories (RAM, ROM, flash) with different peripherals, while a microprocessor only contains the CPU.

Figure 1.1: Inside a feature phone that embeds the MSM6275 Qualcomm's baseband processor (src: http://eetimes.com) that packages the application processor and the modem.

Figure 1.2: Example of two devices where the application and baseband processors are physically separated (src: http://www.semiwiki.com).

SGS7 has both integrated within a single chipset, the Qualcomm MSM8996 Snapdragon which is also referred to as a System-on-Chip (SoC).

### 1.1.2 The Operating Systems that Make the Magic Happen

Smartphones are now so much more than phones or personal organizers. They are mobile web browsers, video and music players, cameras, electronic wallets and more. They are small computers and as we have seen, they feature more than a single microcontroller to make all the magic happen. What exactly differentiate the main CPU with other sub-processors (*e.g.* video (e.g. v))

Figure 1.3: Design comparison between the Smasung Galaxy S7 and the iPhone 6 (src: http://www.ifixit.com)

encoders/decoders, audio playback, etc.) is that it has an Operating System (OS), the software responsible of providing the base management of the whole device (*e.g.* setting the device while booting, managing the underlying hardware and so on). There are many different mobile operating systems but the most popular ones are *Android* (Google Inc.), iOS (Apple) and Windows Phone (Microsoft).

Nevertheless, the AP is not the only hardware unit that has an OS. Nowadays, we can at least count two other microcontrollers that are controlled by other OSs that can run independently from the main one. We have already seen the first one, the baseband processor, and it is controlled by a proprietary real-time baseband OS such as for example QuRT (Qualcomm) or ThreadX (Apple). The second one is the secure element (SE) which is a tamper resistant integrated circuit (IC) capable of running smart card applications and is also controlled by a proprietary OS. One of the most popular OS for SEs is Java Card that provides platform interoperability and post-issuance application management.

SEs can have different form factors where the most known one is the SIM (Subscriber Identity Module) card that can mainly run GSM-related applications. With the advent of more services, a major evolution of the SIM card has been the introduction of the UICC (Universal Integrated Circuit Card) which is actually a secure smart card – also known as chip card – that provides a more secure storage, advanced 4G/LTE mobile network capabilities, more storage space and particularly more secure cryptographic capabilities. The other form factors are the eSE (embedded Secure Element) a tamper-proof chip, and the microSD (Secure Digital) card that provides a flash memory combined with a dedicated eSE.

Figure 1.4: Illustration of the different form factors of a Secure Element within a mobile device (src: http://www.applus.com)

## 1.2 Motivation

### 1.2.1 Study of the Attack Surface and the Attacks Implementations

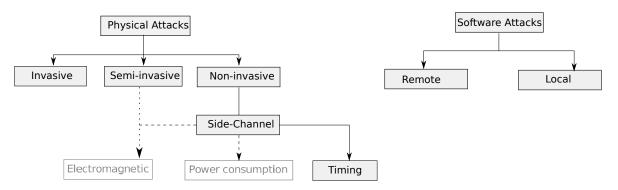

The attack surface on mobile devices is amazingly large due to the numerous attack vectors that exist. Those attack vectors can also be referred to the entry points from where an attack can be carried out. Those entry points mainly depends on the different high level features (Messaging, Voice calls, etc.) provided by the software, and the low-level features provided by the hardware (cache mechanism, hardware implementation of a cryptographic operation, hardware protection, etc.) that the device provides. Considering those attack vectors, we can define two categories of attacks. *Software* and *Physical Attacks*.

#### 1.2.1.1 Software Attacks

They are also known as Logical Attacks and can be divided into two sub-groups of attacks: Remote Attacks and Local Attacks.

On the one hand, remote attacks refer to attacks that do not require to touch the device. Different wireless technologies can be considered to carry out such kind of attack (e.g. Wi-Fi, GSM, GPS, NFC, Bluetooth, etc.). They are the most attractive as in some cases, the adversary does not need to be physically near the victim, or at least in other cases, within a certain distance range.

On the other hand, local attacks require the adversary to have the device at his disposal in order to perform them. During our experimental research we mainly performed local attacks. They are useful for learning the target platform and improving the attack techniques, however, in some cases, considering a more sophisticated scenario, it is possible to turn a local attack into a remote one.

#### 1.2.1.2 Physical Attacks

They consist of any attacks that involve any invasive or semi-invasive modification of a given hardware component or any passive observation of the behavior of the latter.

**Invasive attacks** – Firstly, an invasive or semi-invasive attack both involve physical alteration of a part of the microcontroller. The difference between both resides in whether after the physical alteration the package of the SoC remains intact or not. For example, so-called microprobing attacks exist and require to directly access the chip surface in order to observe, manipulate and interfere with the integrated circuit. Be it a SE, an AP or a BP, according to the type of packaging of the microcontroller, if the chip surface is not directly accessible due to some layers of some types (plastic, resins, metal) some techniques could be used to get access to the latter such as using wet chemical etching, drilling and so on. Any invasive attacks are quite complicated and require highly qualified specialists and a proper budget. The microcontrollers may remain functional, however such kind of attack definitely destroy the package.

**Semi-Invasive attacks** – Secondly, any attack that consists of modifying hardware to perform a function, either not originally conceived for, or initially hidden in one way or another.

Different entry points can be considered in such kind of attacks such as for example, the CPU

itself, the serial ports, any debug ports (if available, e.g. JTAG<sup>3</sup>, Serial Wire Debug<sup>4</sup>), the flash memories, and more. Such kind of attack may be destructive because of the limited physical access to some hardware components which also may requires to remove a or to add hardware.

**Non-Invasive attacks** – Finally, physical attacks can also be non-invasive such as the adversary still exploits the specificities of a target hardware implementation, but without any physical access. A very well-known attack technique in the area of cryptography that correctly defines such kind of attacks is called *Side-Channel Analysis* (SCA). Basically, it consists of measurement-based inference techniques to highlight the behavior of a given hardware component such as the main CPU, and to recover information and data manipulated by a targeted algorithm. Examples of techniques can be the measurement of the power consumption, the analysis of the electromagnetic emanation, or the measurement of the execution time of a part of an algorithm or a whole program.

### 1.2.2 Hardware and Software Security of Microcontrollers in the Context of Mobile Devices

This thesis is concerned with the security of the three main microcontrollers that are managed by independent OSs within mobile devices; the SE, the baseband processor and the application processor, *i.e* the main CPU. Their security depends on the hardware and the software implementation of the numerous features that they provide.

First of all, SEs implements various techniques to implement tamper resistance to prevent from extracting information from it. It is considered as a digital vault as it provides a very secure storage. Furthermore, it generally provides a co-processor with cryptographic computation capabilities. The specification [Ora15] defines its implementation. However, this does not ensure that the actual implementation strictly respects it. Consequently, it is likely that some platforms may embed vulnerabilities due to the specificities of their implementation.

Secondly, one of the key components that has directly access to the SEs is the baseband processor. If we take as an example an open source mobile device's OS like Android, the baseband OS is one of the few close-source software that run on the device. No public documentation is available (unless leaked). Having control over the baseband side allows an attacker to perform different attacks related to the "phone" part of a device. Therefore it is worth to be aware of the security impacts of this companion processor over the whole system.

Finally, the security of software that is run by the application processor and the sensitive assets that are manipulated may also depend on the hardware implementation of the latter. In cryptography, a very well-known technique for passively extracting information from a system without any knowledge of the internal workings is called Side-Channel Analysis. The most popular techniques involve inferring information by measuring the power consumption, or the electromagnetic emanation during the execution of a sensitive operation. However, other techniques that do not require physical measurements also exist and can be used to gather and analyse information.

To summarize, the Figure 1.5 illustrates the major topics that are studied throughout the dissertation. The dotted arrows refer to topics that have not been considered at all.

<sup>&</sup>lt;sup>3</sup>Joint Test Action Group

Figure 1.5: Approximate taxonomy of the studied major topics

# 1.3 Contributions and Outline

Major contributions of the PhD studies research work summarized in this dissertation are as follows:

**Software attack on Java Card Platform:** The chapter 4 is a proposal of a new software attack technique on the Java Card platform that exploits the Java frame creation mechanism to perform a stack underflow attack. More particularly, our technique is not dependent on the Java stack implementation which may be totally different from one platform to another one.

**Memory forensics of a raw Java Card memory dump:** The chapter 5 is a proposal of a new heuristic to identify the code of a Java Card application within a raw memory dump that has been obtained after a successful attack. The clear objective in this experimental analysis is to improve memory forensics and reverse engineering capabilities while studying a secure microcontroller.

Security of the main CPU against Cache Timing Attacks: The chapter 10 studies the applicability of Bernstein's time-driven cache attack [Ber05] on real mobile devices. We particularly focus on highlighting the behavior of the main CPU while performing the attack through practical experiments and various adaptations of the original attack. Furthermore, while nobody in the literature explicitly shares the specific configuration within which their experiments have been performed, we particularly describe the different parameters that we have used to carry out our experiments.

The remainder of this dissertation is structured as follows: The next chapter (chapter 2) provides the reader the knowledge about the Java Card platform and an overview of the security of the latter. The chapter 3 introduces, explains and classifies the software attacks that are known in the literature. The Part II of the dissertation summarizes our investigations to answer the following question: what is the attack surface on a baseband processor from a local to a remote attack perspective? What are the means to perform security assessment of a baseband processor? How is the (U)SIM card managed by the baseband OS?

The Part III concerns our investigations regarding the applicability of so-called time-driven cache attacks on actual mobile devices. We provide an introduction to ARM processors and their multi-level cache memories in chapter 7. The chapter 8 summarizes our empirical analysis of the cache memories effects on a mobile device. The chapter 9 summarizes our findings regarding all

### 1.3. Contributions and Outline

the known so-called micro architectural attacks that exploit the behavior of the CPU due to the implementation of specific hardware mechanisms. In that chapter, we also particularly try to identify the different techniques that are used up to now in the area of cache attacks to extract information used to carry out further analysis.

Finally, the chapter 10 summarizes our experiments related to the application of Bernstein's time-driven cache attack[Ber05] on an actual mobile device.

# Part I

# Software Security of Java Card-based Secure Elements

# Chapter 2

# Security Concepts behind Java Card-based Secure Elements

### Contents

| 2.1 Intro | oduction                                             | 12        |

|-----------|------------------------------------------------------|-----------|

| 2.1.1     | What is a Smart Card?                                | 12        |

| 2.1.2     | What is a Secure Element?                            | 12        |

|           | 2.1.2.1 A Tamper Resistant Microcontroller           | 12        |

|           | 2.1.2.2 A Smarter Contact and Contactless Smart Card | 12        |

| 2.2 Java  | Card Technology                                      | <b>13</b> |

| 2.2.1     | Java Card Architecture                               | 13        |

| 2.2.2     | Java Card Virtual Machine                            | 14        |

| 2.2.3     | Java Card Runtime Environment                        | 14        |

| 2.3 Secu  | rity Concepts in a Multi-Application Environment     | 15        |

| 2.3.1     | Application Verification                             | 15        |

| 2.3.2     | Application Loading                                  | 15        |

| 2.3.3     | Application Isolation                                | 15        |

|           | 2.3.3.1 The Firewall                                 | 15        |

|           | 2.3.3.2 The Security Domains                         | 16        |

| 2.3.4     | Operation Atomicity                                  | 16        |

| 2.4 Sum   | mary                                                 | 16        |

In this chapter, we define the main aspects of the Java Card technology and basic knowledge regarding the security of the platform, and the main risks it faces. In the section 2.2, we provide the reader with a general understanding of the platform under study. The section 2.3 aims at introducing fundamental security concepts that gives a general picture of the security mechanisms that are involved in the Java Card technology. The final section 3.1 introduces the different categories of attacks that a Java Card paltform must withstand.

### 2.1 Introduction

### 2.1.1 What is a Smart Card?

The most known form factor of smart cards is the traditional credit-card which is a piece of plastic with fixed dimensions housing a small microcontroller at a fixed exact location defined by international standards<sup>5</sup>. Additionally, the contacts and positioning of the input and output (I/O) interfaces are closely specified and fully disclosed in the IS07816 standard<sup>6</sup>. Smart cards offer a secure storage and a secure computing environment. It is managed by an operating system whose sophistication varies between the most rudimentary data access or update operation, to controlling the loading and the execution of applications with full security management.

The second major use of smart cards is within mobile devices. Inside every phone resides a very small smart card which is commonly known as the SIM card. The SIM card is used to store a secret SIM key that is used in a challenge/response protocol (see Part II, section 6.2.3.2) to authenticate the SIM to the mobile network. However, SIM cards are not the only form factor of secure elements within a mobile device.

### 2.1.2 What is a Secure Element?

#### 2.1.2.1 A Tamper Resistant Microcontroller

A secure element is a tamper resistant smart card chip that provides the ability to run smart card applications, to securely store data and to execute cryptographic functions by means of coprocessors that implement common algorithms such as RSA, DES, AES. Smart Cards use various hardware and software techniques to implement tamper resistance, making hard the analysis of the chip to extract data by means of either physical attacks (see section 1.2.1.2) or software attacks (see section 1.2.1.1). They are generally pre-programmed with a multi-application OS, namely an OS that enables to load and execute multiple applications. The memory protection features provided by the platform (hardware + software) ensures the segregation of each application and their data.

#### 2.1.2.2 A Smarter Contact and Contactless Smart Card

Typical smart card has contacts set aside to enable the communication between the chip and a card reader. However, smart cards can also be contactless and they do not need to be physically connected to a reader. The delivery of power and the transmission of data to and from the card are achieved at a distance by means of different technologies: close-coupling (ISO/IEC 10536), remote-coupling (ISO/IEC 14443 and ISO/IEC 15633) or NFC (Near Field Communication) that uses contactless identification according to the ISO/IEC 14443 standard and operates over the air interface according to the ISO/IEC 18000-3 standard.

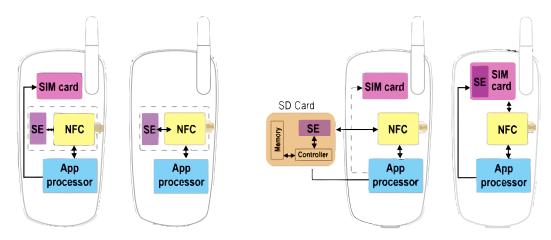

Nowadays, modern smartphones also support NFC technology. In this case, the secure element is connected to a NFC chip making the wireless communication with the SE possible. An illustration of the possible layouts of the NFC Chip, the SIM Card and the secure element within a mobile device is illustrated by the Figure 2.1.

The secure element has at least equivalent capabilities to that of a smart card. It also can have superior capabilities since it can host multiple applications, it enables to manage within a

<sup>&</sup>lt;sup>5</sup>http://www.iso.org/iso/catalogue\_detail?csnumber=31432

<sup>&</sup>lt;sup>6</sup>http://www.cardwerk.com/smartcards/smartcard standard ISO7816.aspx

Figure 2.1: Secure Element Solutions (src: http://smartcardalliance.org/)

single device many different types of cards or security tokens (access cards, loyalty cards, One Time Password generators, Public Key Infrastructure credential storage, and so on).

# 2.2 Java Card Technology

### 2.2.1 Java Card Architecture

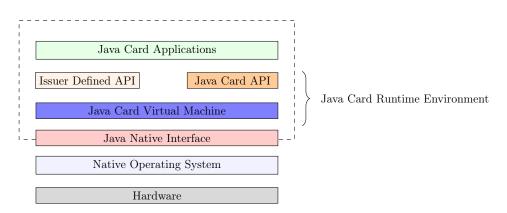

Java Card is a multi-application platform that enables programs written in Java to run Java bytecode on smart cards. It supports only a carefully chosen and customized subset of the features of the Java platform. Therefore smart card manufacturers can design their own Java Card technology-based implementations. It defines a runtime environment, the Java Card Runtime Environment (JCRE). The latter is on top of the hardware, the native operating system and the Java Card Virtual Machine (JCVM). The JCRE is paired with a high level standard interface to Java Card applications, the Java Card API (JCAPI). As a result, it enables for rapid application development. A card issuer may also provide its own API on top of the JCAPI.

Figure 2.2: Java Card Architecture overview

### 2.2.2 Java Card Virtual Machine

The Java Card Virtual Machine mainly consists of two separate components: the *converter* and the *interpreter*.

**The** converter is the off-card component of the JCVM and runs on a host computer. As any other Java program, Java Card applets are first compiled and translated into a binary form that respects the CLASS file format. The converter is then in charge of converting the latter into a Converted APplet (CAP) file that suits better the Java Card platform and the underlying hardware. The converter takes as an input two files, CLASS files and an EXPORT file. For the sake of memory constraints, all the public information needed for linking every classes and methods within the CAP file, are stored within the EXPORT file and are never stored on the device.

**The** *interpreter* runs on the Java Card device, and is responsible for executing the code of the application, and enforcing the runtime security.

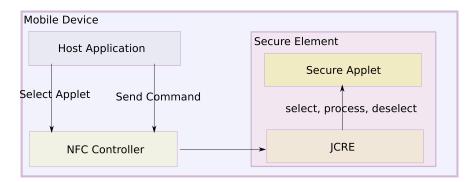

### 2.2.3 Java Card Runtime Environment

The JCRE is a masterpiece in the Java Card architecture and can be considered as the device's operating system, as it manages the resource management, I/O communication, the general security model enforcement and the applet life cycle. The JCRE is initialized at card initialization time and takes care of instantiating the applets. It is also responsible of handling the commands sent from the external world that are also called Application Protocol Data Unit (APDU) commands as defined by the standard IS07816-4<sup>7</sup>. As many applets can be installed on the device, one of the main step to perform is to request the JCRE for selecting a specific applet thanks to its Application ID (AID). The JCRE forwards the APDU packet to the select method of the applet and tells the JCRE if the applet is ready or not for processing other commands. In case the applet is ready, it takes the control and passes the received command to its process method that will handle the command.

Figure 2.3: Communication between a host application and a secure applet installed on a secure element embedded within a mobile device

#### 14

$<sup>^{7}</sup> http://www.cardwerk.com/smartcards/smartcard\_standard\_ISO7816-4\_5\_basic\_organizations.aspx$

# 2.3 Security Concepts in a Multi-Application Environment

### 2.3.1 Application Verification

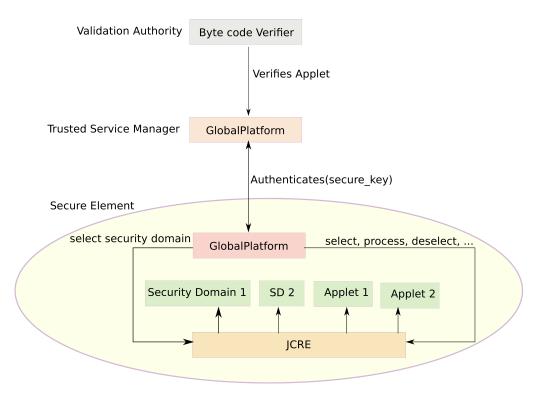

To preserve the Java Card platform from being attacked with tampered applications, a very important component of the JCVM, called the Byte Code Verifier (BCV), is run for statically verifying the correctness of the internal structure of the application. While in the regular Java Virtual Machine (JVM), this piece of software is completely integrated within the VM itself, on Java Card platform, due to memory and performance constraints, it is common to retrieve the BCV as an off-card piece. However, there is no doubt that in a near future, all the devices will be able to run such resource-consuming process.

### 2.3.2 Application Loading

Another corner stone of the Java Card platform security is the application loading process. In case it is not secured, it would give the freedom to arbitrarily install applications. Therefore, for security purpose, a code loading mechanism is generally implemented for enforcing the integrity and authenticity of the application through public key or symmetric key cryptography. Consequently, one has the notion of "loading keys" that may be owned either by the card issuer, or by a third party. In the second case, the loading keys are derived from a master key that is also either only owned by the card issuer or shared among different third parties. They are required for installing an application on the device. For instance, practically all SIMs used today implement GlobalPlatform card specification<sup>8</sup> so applet can be installed by authenticating first to a pre-loaded applet called the Card Manager, also called the Issuer Security Domain (see section 2.3.3.2). The latter has to be used for uploading and installing new applets by issuing LOAD and INSTALL commands after selecting it and performing an optional authentication.

An important difference SIM cards have compared to regular smart cards is that it supports Over-The-Air (OTA) updates via binary SMS (Short Message Service) or over TCP/IP (Transmission Control Protocol/Internet Protocol) through the mobile network (GPRS/3G etc.). For Java Card-based SIM cards, they are pre-personalized by the network operator with an "OTA profile" that enables them to retrieve and execute OTA commands. Hence, file management and more particularly applet management can be performed remotely by network operators on the SIM card.

### 2.3.3 Application Isolation

### 2.3.3.1 The Firewall

The Firewall is a mechanism that provides a means to guarantee the segregation between applets' data on the device. It mainly prevents an arbitrary applet from unwanted interference from another applet. To each application is assigned a security context, or also called, execution context. Furthermore, to several applications can be assigned the same security context. Subsequently, all objects belong to some security context. The latter defines the access rules that protect a given object (field access, method call, etc.), and thus, it can only be accessed by the current running security context. Any attempt to illegally perform an access may result in a SecurityException. Only the JCRE is able to bypass those rules, as it is the one that has the highest privileges.

$<sup>^{8}</sup> http://www.globalplatform.org/specificationscard.asp$

To enable data exchange, the shareable interface mechanism is provided for giving the ability of two applets to communicate through a shareable interface object (SIO). The SIO is the only interface that a client applet must request to a server applet for getting access to the functions exposed by the SIO.

### 2.3.3.2 The Security Domains

Security domains are privileged applications that manage their own cryptographic keys. They enable the coexistence of multiple applications on the same device without violating the privacy and integrity of each application provider. Security domains are grouped in 3 types:

- 1. the issuer security domain: represents the on-card representative of the card administrator

- 2. the application providers security domain: consist of representatives of application providers, or card issuer

- 3. the controlling authorities security domains, which are optional and offer further confidential personalization services to authenticated application providers

### 2.3.4 Operation Atomicity

For the sake of data consistency and integrity, it is critical to ensure that the data that are manipulated at runtime are protected against external events that would abruptly stop an ongoing operation due to a power loss. Thus, while such events occur, the platform must implement a mechanism that should be able to recover the previous state of the data. The platform provides the ability to protect critical data by means of a Transaction Mechanism, that mainly keeps track of the data state before the transaction begins until it ends.

## 2.4 Summary

We have provided the reader an overview of various security concepts around Java Card platform. The latter can benefit from a layered security to provide a very secure storage and computing environment. From the lowest level to the highest one we have:

- a multi-application environment that can run and segregate multiple secure applets thanks to hardware and software protections

- a semi-open platform that enables to perform post-issuance applet loading only on condition one has the right keys to authenticate to a given security domain that ensure that one has the right to load and install a given apple

- a split virtual machine architecture that provides an off-card applet verifier that could be run by a third-party validation authority to ensure that the applet is structurally and semantically correct

From this layered architecture, one can ask the corresponding questions:

• is the current Java Card platform implementation fully bullet-proof, and what a malicious applet can do from the inside?

Figure 2.4: Java Card: a layered security with different actors

- how much can we trust our "business partners" that may also be present in the same secure element, can we fully trust the security domains implementations that provide the powerful ability to perform post-issuance applet loading and installation?

- how much can we trust to the so-called validation authority that has to verify applets that have to be installed in the same secure element as ours?

To answer these questions, the next chapter provides the reader the knowledge about software attacks applied to Java Card platforms following a basic assumption that defines our adversary: regardless how a malicious applet has been uploaded onto the secure element, it may potentially embed malicious code that may threaten other applications or the whole platform.

# Chapter 3

# Introduction to Software Attacks on Java Card Platforms

### Contents

| 3.1        | Secu           | rity Risks of Java Cards                                                                                      | <b>21</b> |

|------------|----------------|---------------------------------------------------------------------------------------------------------------|-----------|

|            | 3.1.1          | Invasive attacks                                                                                              | 21        |

|            | 3.1.2          | Semi-Invasive attacks                                                                                         | 21        |

|            | 3.1.3          | Non-Invasive attacks                                                                                          | 21        |

|            |                | 3.1.3.1 Side-channel attacks $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21        |

|            |                | 3.1.3.2 Software Attacks                                                                                      | 22        |

| <b>3.2</b> | Atta           | ck Techniques through Malevolent Applications                                                                 | <b>23</b> |

|            | 3.2.1          | Concepts of Well-formed and Ill-formed Applications $\ . \ . \ . \ .$                                         | 23        |

|            | 3.2.2          | Malicious Well-formed Application based Attacks                                                               | 23        |

|            |                | 3.2.2.1 Abuse of the Java Card Firewall                                                                       | 23        |

|            |                | 3.2.2.2 Transaction Mechanism Abuse                                                                           | 24        |

|            | 3.2.3          | Ill-formed application based attacks                                                                          | 26        |

|            |                | 3.2.3.1 Type Confusion attacks (TC) $\ldots \ldots \ldots \ldots \ldots$                                      | 26        |

|            |                | 3.2.3.2 Stack Overflow/Underflow Attacks $\ldots \ldots \ldots \ldots$                                        | 30        |

|            |                | 3.2.3.3 Static Links based attacks (SLA)                                                                      | 32        |

|            |                | 3.2.3.4 Control Flow Modification based Attacks (CFTA) $\ldots$                                               | 33        |

| <b>3.3</b> |                | Generic Framework for Evaluating Java Card Platforms                                                          |           |

|            |                |                                                                                                               | <b>34</b> |

|            | 3.3.1          | Testing Tools Categories                                                                                      | 34        |

|            |                | 3.3.1.1 Model 1: Static One-to-One approach                                                                   | 35        |

|            |                | 3.3.1.2 Model 2: Automated One-to-Many approach                                                               | 36        |

|            |                | 3.3.1.3 Model 3: Semi-Automatic One-to-Many approach                                                          | 36        |

|            | 3.3.2          | Constraints                                                                                                   | 37        |

|            | 3.3.3          | Approaches comparison                                                                                         | 37        |

|            | 3.3.4          | A Framework for Designing Attack Scenarios                                                                    | 37        |

|            | 3.3.5          | A Framework for Performing Static Code Analysis                                                               | 38        |

|            | 3.3.6          | Example of Usage                                                                                              | 38        |

| <b>3.4</b> | $\mathbf{Sum}$ | mary                                                                                                          | <b>42</b> |

This chapter presents the related work regarding pure software attacks on the Java Card platform. This topic is crucial for the reader, in order to give thorough insights regarding the possible attack techniques that exist on the platform. Therefore the section 3.2 will mainly focus on the study of the different attack techniques that are presented in the current literature applied to the Java Card platform. The section 3.3 briefly presents our generic framework that enables to test both the platform implementation and the applet that has to be executed on the latter. But first, we provide a brief overview of the security risks of Java Cards in the section 3.1.

## 3.1 Security Risks of Java Cards

Java Card devices are prone to various attacks, however, we will only focus on a given type of attacks. Furthermore, in order to give the reader an overview of the large attack surface in this field, a brief description of the different possible attacks are given in the next sections.

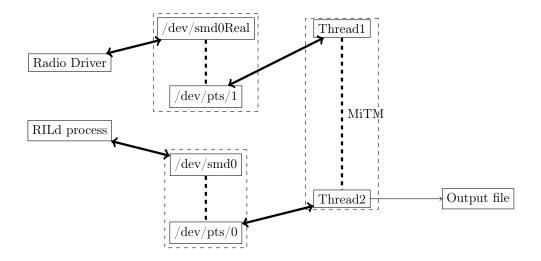

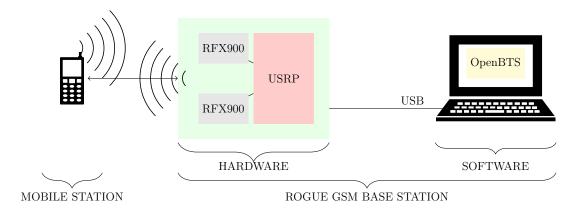

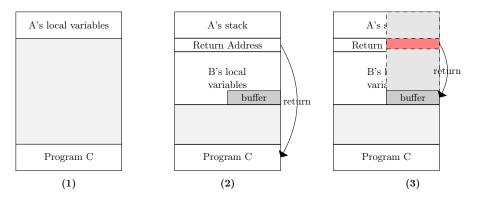

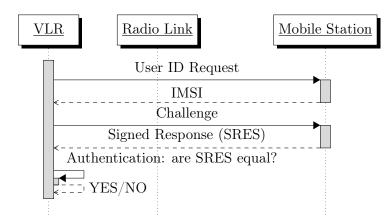

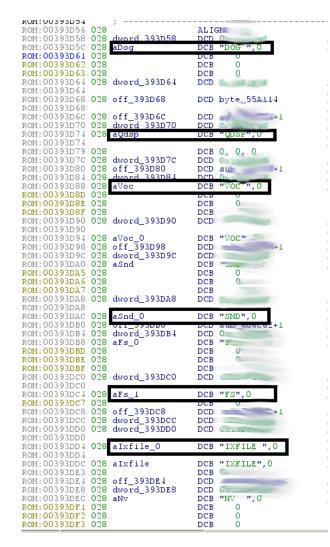

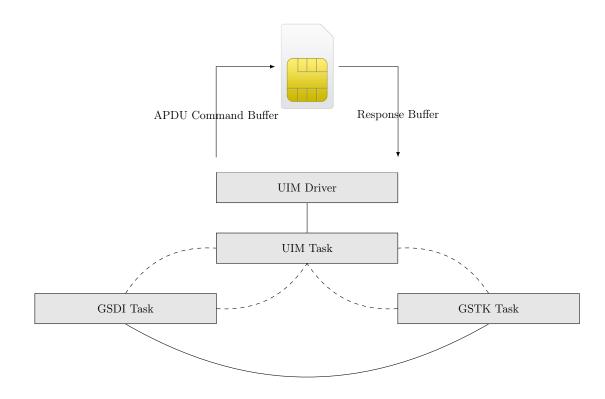

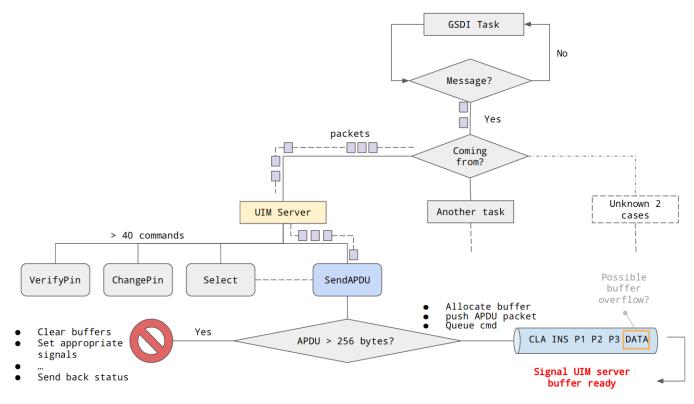

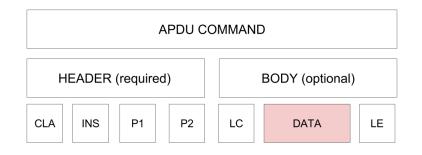

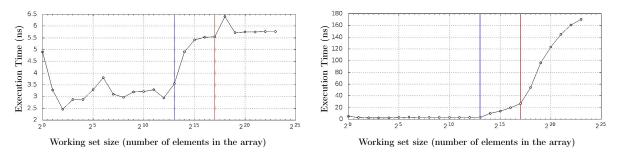

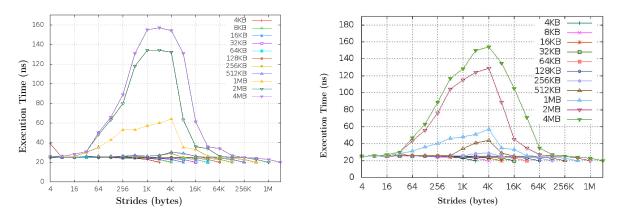

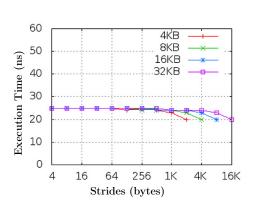

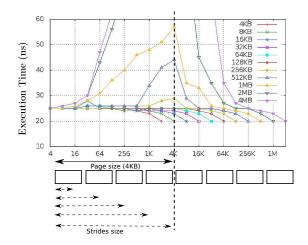

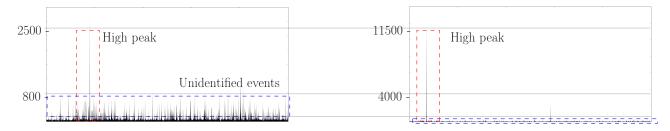

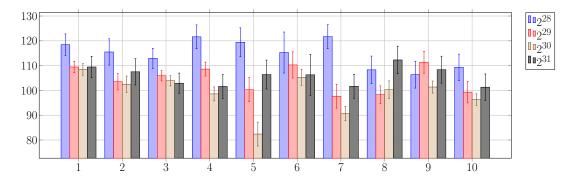

### 3.1.1 Invasive attacks