# A synchronous approach to quasi-periodic systems

Guillaume Baudart

#### ▶ To cite this version:

Guillaume Baudart. A synchronous approach to quasi-periodic systems. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Paris sciences et lettres, 2017. English. NNT: 2017PSLEE007. tel-01507595v2

## HAL Id: tel-01507595 https://theses.hal.science/tel-01507595v2

Submitted on 22 Jun 2017

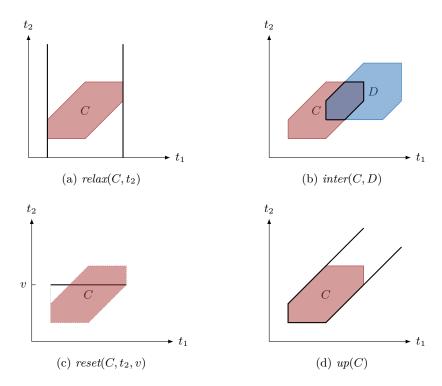

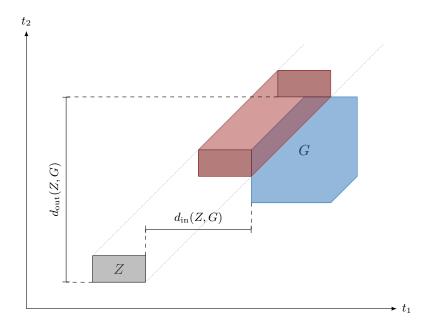

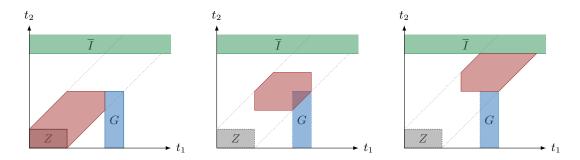

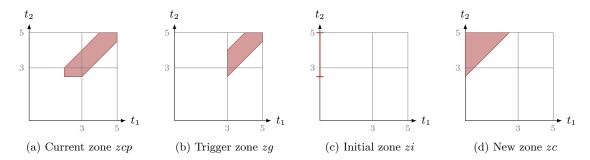

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences Lettres PSL Research University

# Préparée à l'École normale supérieure

## A Synchronous Approach to Quasi-Periodic Systems

Une Approche Synchrone des Systèmes Quasi-Périodiques

**ED 386** SCIENCES MATHÉMATIQUES DE PARIS CENTRE **Spécialité** INFORMATIQUE

Dirigée par Marc Pouzet

Soutenue le 13 Mars 2017

par Guillaume Baudart

#### COMPOSITION DU JURY:

M. Albert Benveniste Inria Rennes Co-encadrant

M. Timothy Bourke Inria Paris Encadrant

M. Nicolas Halbwachs Vérimag Rapporteur

M. Marc Pouzet École normale supérieure et UPMC Directeur de thèse

M. Xavier Rival Inria Paris Examinateur

M. Alberto Sangiovanni-Vincentelli University of California Berkeley Examinateur

M. Cesare Tinelli University of Iowa Rapporteur

Pour Lucile, la plus belle personne du monde.

# Merci!

I would like to warmly thank Nicolas Halbwachs and Cesare Tinelli. I admire their work, and it is a great honor for me that they both accepted to review this manuscript. I am also very grateful to Xavier Rival and Alberto Sangiovanni-Vincentelli for their participation to my committee.

Je voudrais remercier Marc Pouzet qui m'a accueilli en stage de master sur un sujet étrange, un peu en dehors des thématiques habituelles de l'équipe. Cette rencontre m'a permis de découvrir dans un cadre idéal les langages synchrones qui me fascinent encore aujourd'hui. J'ai ensuite eu la chance de pouvoir poursuivre en thèse sous sa direction pendant trois années incroyablement enrichissantes. L'élégance et l'originalité de ses travaux ont été une grande source d'inspiration pour les développements présentés dans cette thèse. Je voudrais également le remercier pour sa disponibilité et ses conseils. J'ai beaucoup apprécié nos longues séances de travail qu'il arrivait à inclure dans son agenda chargé.

Timothy Bourke a été un encadrant exceptionnel. Il a su admirablement composer avec mon caractère riche et contrasté tout au long de ma thèse. J'ai adoré nos séances de rédaction à quatre mains où nous avons pu débattre pendant des heures de la place d'un mot, d'une virgule, ou même d'un simple espace. Merci Tim pour ton incroyable disponibilité. Merci d'avoir toujours été à l'écoute pendant ces trois années. J'espère que nous aurons encore de nombreuses occasions de nous disputer.

Au début de ma thèse, j'ai contacté Albert Benveniste pour discuter d'un de ses articles paru des années plus tôt. Cette discussion a été le point de départ d'une collaboration à qui je dois tous les développements sur les LTTAs. Grâce à Albert, j'ai également eu la chance d'entrer en contact avec des industriels qui ont grandement contribué à éclaircir ma vision (jusqu'alors un peu théorique) des systèmes embarqués. Je voudrais le remercier pour ses conseils, sa bienveillance, son ouverture d'esprit, et son impressionnante créativité.

À la fin de ma thèse j'ai eu la chance de pouvoir effectuer un stage à IBM Research. Merci à toute l'équipe du projet CloudLens: Louis Mandel, Olivier Tardieu, et Mandana Vaziri. J'ai adoré ces quelques mois de stage et vous y êtes pour beaucoup. Merci Louis pour tous ces bons moments passé à New-York. Merci Jérôme pour Harlem et les chats.

Merci à tous les membres de l'équipe Parkas pour tous ces repas et pauses cafés partagés. Merci aux vénérables anciens Léonard Gérard, Adrien Guatto<sup>1</sup>, et Cédric Pasteur. Merci

<sup>&</sup>lt;sup>1</sup>Adrien a été un énorme soutien sur le plan scientifique et humain tout au long de ma thèse. Je lui dois beaucoup et j'espère que nous aurons encore de nombreuses occasions de discuter d'obscurs points techniques à la terrasse de cafés, d'un côté ou de l'autre de l'océan.

Louis pour ReactiveML et tout ce qui va avec. Merci Ulysse, co-bureau exemplaire, pour les ravioles.

J'ai eu la chance de travailler avec un personnel administratif aussi redoutablement efficace que sympathique. Merci à Anna Bednarik, Lise-Marie Bivard, Isabelle Delais, Joëlle Isnard, Sophie Jaudon, Valérie Mongiat, et Assia Saadi.

Merci à tous mes amis: Thibault qui a trop souvent subi mes divagations, Pierre (Félicitation!) qui est toujours là après tant d'années, Antoine le nouveau Prince de Mineapolis, Mathilde et ses cailloux, Benjamin la fripouille, Paulin et Anaïs et leur bonne humeur communicative, Xavier colloc légendaire, les atiamiens Camille et Quentin, Élise et Tanguy (et Sandro), Morgan et Salomé (et Andréa), Agathe et Clément, Maxence, Marguerite et Paul, Agnès. J'espère tous vous revoir bientôt de l'autre côté de l'atlantique.

J'ai une pensée spéciale pour mes parents, Pôpa et Môman, et mes frères Clément, Nicolas, Vincent, et Joseph, qui me soutiennent depuis toujours (même quand je leur ai annoncé que je ferais de l'informatique). Merci aussi à toute la famille Nême/Debray qui m'a si gentiment adopté il y a maintenant quelques années.

Enfin merci Lucile de rendre la vie si agréable, amusante, et fascinante.

#### Abstract

In this thesis we study embedded controllers implemented as sets of unsynchronized periodic processes. Each process activates quasi-periodically, that is, periodically with bounded jitter, and communicates with bounded transmission delays. Such reactive systems, termed *quasi-periodic*, exist as soon as two periodic processes are connected together. In the distributed systems literature they are also known as synchronous real-time models. We focus on techniques for the design and analysis of such systems without imposing a global clock synchronization.

Synchronous languages were introduced as domain specific languages for the design of reactive systems. They offer an ideal framework to program, analyze, and verify quasi-periodic systems. Based on a synchronous approach, this thesis makes contributions to the treatment of quasi-periodic systems along three themes: verification, implementation, and simulation.

Verification: The *quasi-synchronous abstraction* is a discrete abstraction proposed by Paul Caspi for model checking safety properties of quasi-periodic systems. We show that this abstraction is not sound in general and give necessary and sufficient conditions on both the static communication graph of the application and the real-time characteristics of the architecture to recover soundness. We then generalize these results to multirate systems.

Implementation: Loosely time-triggered architectures are protocols designed to ensure the correct execution of an application running on a quasi-periodic system. We propose a unified framework that encompasses both the application and the protocol controllers. This framework allows us to simplify existing protocols, propose optimized versions, and give new correctness proofs. We instantiate our framework with a protocol based on clock synchronization to compare the performance of the two approaches.

Simulation: Quasi-periodic systems are but one example of timed systems involving real-time characteristics and tolerances. For such nondeterministic models, we propose a *symbolic simulation* scheme inspired by model checking techniques for timed automata. We show how to compile a model mixing nondeterministic continuous-time and discrete-time dynamics into a discrete program manipulating sets of possible values. Each trace of the resulting program captures a set of possible executions of the source program.

**Keywords** Embedded systems; Synchronous real-time distributed systems; Synchronous languages; Quasi-synchronous abstraction; Loosely time-triggered architectures; Symbolic simulation.

#### Résumé

Cette thèse traite de systèmes embarqués contrôlés par un ensemble de processus périodiques non synchronisés. Chaque processus est activé quasi-périodiquement, c'est-à-dire périodiquement avec une gigue bornée. Les délais de communication sont également bornés. De tels systèmes réactifs, appelés quasi-périodiques, apparaissent dès que l'on branche ensemble deux processus périodiques. Dans la littérature, ils sont parfois qualifiés de systèmes distribués temps-réels synchrones. Nous nous intéressons aux techniques de conception et d'analyse de ces systèmes qui n'imposent pas de synchronisation globale.

Les langages synchrones ont été introduits pour faciliter la conception des systèmes réactifs. Ils offrent un cadre privilégié pour programmer, analyser, et vérifier des systèmes quasi-périodiques. En s'appuyant sur une approche synchrone, les contributions de cette thèse s'organisent selon trois thématiques: vérification, implémentation, et simulation des systèmes quasi-périodiques.

Vérification: L'abstraction quasi-synchrone est une abstraction discrète proposée par Paul Caspi pour vérifier des propriétés de sûreté des systèmes quasi-périodiques. Nous démontrons que cette abstraction est en général incorrecte et nous donnons des conditions nécessaires et suffisantes sur le graphe de communication et les caractéristiques temps-réels de l'architecture pour assurer sa correction. Ces résultats sont ensuite généralisés aux systèmes multi-périodiques.

Implémentation: Les *LTTAs* sont des protocoles conçus pour assurer l'exécution correcte d'une application sur un système quasi-périodique. Nous proposons d'étudier les LTTA dans un cadre synchrone unifié qui englobe l'application et les contrôleurs introduits par les protocoles. Cette approche nous permet de simplifier les protocoles existants, de proposer des versions optimisées, et de donner de nouvelles preuves de correction. Nous présentons également dans le même cadre un protocole fondé sur une synchronisation d'horloge pour comparer les performances des deux approches.

Simulation: Un système quasi-périodique est un exemple de modèle faisant intervenir des caractéristiques temps-réels et des tolérances. Pour ce type de modèle non déterministe, nous proposons une *simulation symbolique*, inspirée des techniques de vérification des automates temporisés. Nous montrons comment compiler un modèle mêlant des composantes temps-réels non déterministes et des contrôleurs discrets en un programme discret qui manipule des ensembles de valeurs. Chaque trace du programme résultant capture un ensemble d'exécutions possibles du programme source.

**Mot-clés** Systèmes embarqués; Systèmes distribués temps-réels synchrones; Langages synchrones; Abstraction quasi-synchrone; Architectures LTTA; Simulation symbolique.

# **Contents**

| C | onter        | nts                                 | 10 |

|---|--------------|-------------------------------------|----|

| 1 | Intr         | roduction                           | 13 |

|   | 1.1          | Quasi-periodic systems              | 14 |

|   | 1.2          | A synchronous approach              |    |

|   | 1.3          | Contributions                       | 16 |

|   | 1.4          | Organization                        |    |

| 2 | A E          | Brief Introduction to Zélus         | 23 |

|   | 2.1          | A synchronous language              | 24 |

|   | 2.2          | extended with continuous time       | 26 |

|   | 2.3          | A complete example: the Zélus clock | 28 |

|   | 2.4          | Conclusion                          | 31 |

| 3 | Qua          | asi-Periodic Architectures          | 33 |

|   | 3.1          | Definition                          | 34 |

|   | 3.2          | Communication by Sampling           | 35 |

|   | 3.3          | Discrete model                      |    |

|   | 3.4          | Real-time model                     |    |

|   | 3.5          | Other modeling tools                |    |

|   | 3.6          | Bibliographic notes                 |    |

|   | 3.7          | Conclusion                          |    |

| 4 | $Th\epsilon$ | e Quasi-Synchronous Abstraction     | 51 |

|   | 4.1          | A discrete abstraction              | 52 |

|   | 4.2          | Traces and causality                | 56 |

|   | 4.3          | Unitary discretization              |    |

|   | 4.4          | Quasi-synchronous systems           |    |

|   | 4.5          | Multirate systems                   |    |

|   | 4.6          | Bibliographic notes                 |    |

|   | 4.7          | Conclusion                          |    |

| 5  | Loo    | sely Time-Triggered Architectures | 33 |

|----|--------|-----------------------------------|----|

|    | 5.1    | Synchronous applications          | 84 |

|    | 5.2    |                                   | 87 |

|    | 5.3    |                                   | 90 |

|    | 5.4    | •                                 | 92 |

|    | 5.5    | Round-based LTTA                  | 96 |

|    | 5.6    | Clock synchronization             |    |

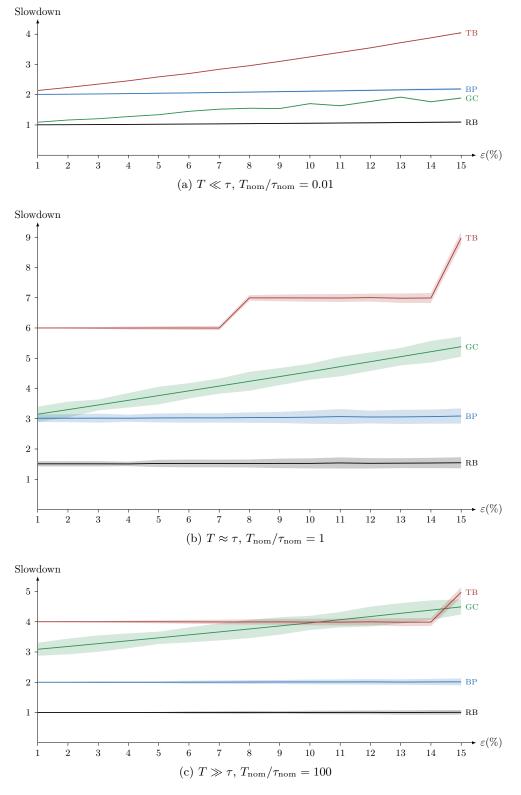

|    | 5.7    | Comparative evaluation            |    |

|    | 5.8    | Conclusion                        |    |

| 6  | Syn    | abolic Simulation 10              | 09 |

|    | 6.1    | Motivation                        | 10 |

|    | 6.2    | Related work                      | 13 |

|    | 6.3    | Difference-Bound Matrices         | 15 |

|    | 6.4    | ZSy: an extended subset of Zélus  | 20 |

|    | 6.5    | Static typing                     | 22 |

|    | 6.6    | Compilation                       |    |

|    | 6.7    | Extensions                        | 35 |

|    | 6.8    | Conclusion                        | 39 |

| 7  | Cor    | aclusion 1                        | 41 |

|    | 7.1    | Summary                           | 41 |

|    | 7.2    | Open questions                    | 44 |

|    | 7.3    | Concluding remark                 | 45 |

| Bi | ibliog | graphy 1                          | 47 |

| Li | st of  | Figures 1                         | 56 |

| In | dex    | 1                                 | 59 |

# Introduction

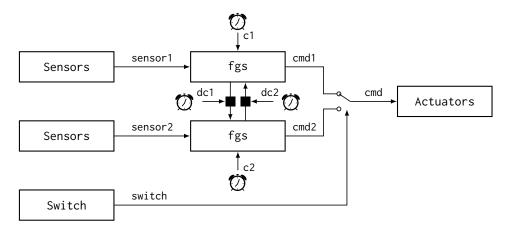

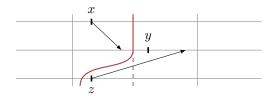

A quasi-periodic system exists as soon as two periodic processes are connected together. They are everywhere: flight control systems in aircraft, control loops in factories or power plants, and distributed control in vehicles. Figure 1.1 illustrates a two-node quasi-periodic system and the code of the control loop executed by each process.

Each process  $P_k$  is triggered by a periodic clock  $c_k$ . The code of the process is executed inside an infinite loop. A new iteration starts at each tick of the clock  $c_k$ . Before the loop, the internal state  $s_k$  is initialized. At each iteration of the loop, a process reads the inputs  $i_k$  from the environment and the output  $o_{1-k}$  of the other process to update its state and produce the output  $o_k$ . The function step is a placeholder for the body of the code executed by the process. This function is typically compiled from specifications written in high-level languages.

Since a process is triggered by local clocks, it only has a local notion of time. Without explicit synchronization their intercommunication is subject to sampling artifacts. One possibility for avoiding them is to rely on a clock synchronization protocol as in the Time-Triggered Architecture (TTA) [KB03]. It is then possible to treat a quasi-periodic system as if all the processes were triggered by a single global clock. Perhaps surprisingly, it is also possible to design and analyze such systems without imposing a global synchronization.

This approach originates in the work of Paul Caspi who noticed, while consulting at Airbus, that for historical reasons, 'in the domain of critical control systems, the use of clock synchronization is not so frequent' [Cas00, §1]. Instead, Airbus engineers relied on

Figure 1.1: A two-node quasi-periodic system. The two processes are triggered by their local clocks and execute the control loop shown on the right.

a set of design *good practices* that Paul Caspi started to formalize in what he called the *quasi-synchronous approach to distributed systems*. As already noted by Caspi in the original report, the so called 'cooking book' [Cas00]:

This raises the question of the techniques used in these systems for simulating, validating, and implementing fault tolerance without clock synchronization, and for the well-foundedness of these techniques which equip, up to now, some of the most safety critical control systems ever designed.

The work in this thesis began in an attempt to precisely understand Caspi's report. It led us to consider quasi-synchronous systems from three related points of view:

- **Verification:** How to precisely model and verify safety properties, that is, checking that nothing bad ever happens, of a system implemented as a set of unsynchronized processes?

- Implementation: How to ensure the correct execution of an embedded application running on a quasi-periodic system despite the absence of synchronization?

- **Simulation:** How to capture the possible behaviors of the system with simulations before implementation?

### 1.1 Quasi-periodic systems

Designing controllers running on distributed architectures is notoriously difficult. The quasisynchronous approach thus focuses on particular architectures characterized by the following assumptions.

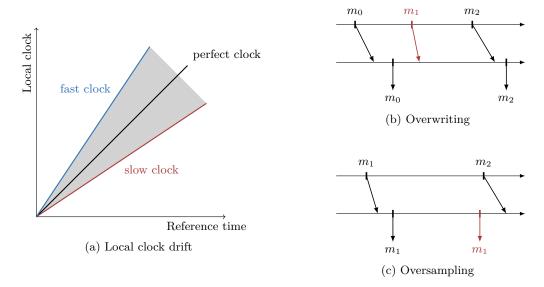

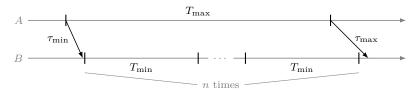

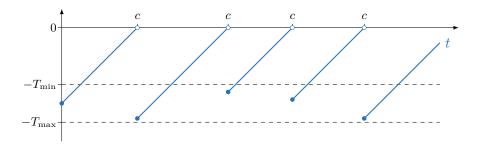

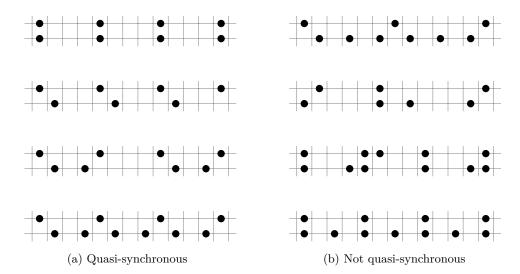

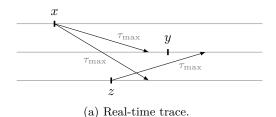

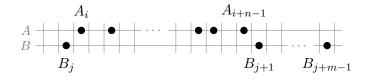

Quasi-periodicity Each process is periodically activated by its own local clock. These clocks are imperfect—subject to jitter—and unsynchronized. However, in the context of embedded systems the system must be predictable. This is especially the case for critical embedded systems, for instance, the fly-by-wire system found in aircraft We thus assume that each process executes quasi-periodically, that is, the delay between two successive activations is bounded by known constants. As shown in figure 1.2a, this assumption does not prevent clock values from drifting arbitrarily apart during execution. For instance, one process can always execute as quickly as possible while another executes as slowly as possible.

**Reliable transmissions** For the same reasons, we focus on systems with a reliable communication network: transmission delays are always bounded with known constants and there is no loss or reordering of messages during transmission.

**Blackboard communication** Since processes are not synchronized, it is almost never the case that a message is received by a process precisely when it activates. Processes thus communicate using *blackboards*: messages are stored in local memories that are only sampled when the receiver activates, no message queues are allowed and a message written in the memory remains there until it is overwritten by a newer one. This communication scheme is often used as a robust alternative to bounded buffers which require control mechanisms

Figure 1.2: Quasi-periodic systems. During execution local clock may drift apart (a). Blackboard communications are subject to loss (b) or duplication of data (c) depending on the last received value when a process is activated.

ensuring that buffer overflows cannot occur. Blackboards avoid these control dependencies between processes at the cost of introducing sampling artifacts. For instance, data may be lost—a value can be overwritten before being read (figure 1.2b)—or duplicated—a process may twice sample the same value (figure 1.2c).

These assumptions are very general and not difficult to satisfy. They thus potentially apply to many systems. Embedded controllers implemented on these *quasi-periodic* architectures are termed *quasi-periodic systems* and are the central focus of this thesis.

### 1.2 A synchronous approach

Synchronous languages [BCE<sup>+</sup>03] were introduced in the late 80s as *domain specific languages* for the design of reactive systems. A synchronous program executes in a succession of discrete steps. A programmer writes high level specifications in the form of stream functions specifying variable values at each step. This approach is reminiscent of block diagrams, a popular notation to describe control systems.

Specific compilation techniques for synchronous languages exist to generate efficient code for embedded controllers. Compilers produce imperative code that can be executed in a control loop like the one presented in figure 1.1. In addition, dedicated formal verification tools have been developed to check program properties. One example is the language Lustre [CPHP87] which is the backbone of the industrial language and compiler Scade. Scade is now routinely used to program embedded controllers in many critical applications.

www.esterel-technologies.com/products/scade-suite

In this thesis, we focus on quasi-periodic systems where multiple synchronous programs (one for each process) execute in parallel but are not synchronized. We propose to reason about the entire system in a synchronous framework. We can thus benefit from the mathematically precise semantics offered by synchronous languages to reason about the global system, and rely on well-understood compilation techniques to generate the embedded code of processes. Compared to other modeling techniques, this approach reduces the gap between the model and the executable code.

The main question is then: How to model the asynchronous behavior of quasi-periodic systems in a synchronous framework? In particular, when modeling and simulating a complete quasi-periodic system, the timing constraints of the underlying architecture are of paramount importance. We thus look for extensions of the synchronous approach that allow the inclusion of real-time characteristics in the model.

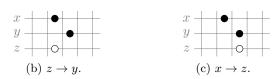

Abstracting real-time specifications as discrete predicates A classic solution consists in abstracting from the real-time behavior of the architecture using discrete-time predicates like: 'A process never activates twice between two activations of another'. Both the discrete-time controllers and the predicates capturing their real-time behavior can be expressed as synchronous programs. This allows the use of the existing verification tools for synchronous programs to check safety properties of the model. For instance, we can check that the system never reaches an *alarm* state.

The main limitation of this approach is that we must ensure that the discrete-time abstraction captures all possible behaviors of the real-time system. Otherwise, one cannot assume that safety properties that hold for the discrete model also hold for the real system. Designing sound discrete abstractions is complex and error prone.

Models mixing continuous and discrete time Another approach is to rely on tools that allow the modeling of systems with complex interactions between discrete-time and continuous-time dynamics. For instance, Simulink/Stateflow<sup>2</sup> or Ptolemy.<sup>3</sup>

In this thesis, we choose to model systems using Zélus,<sup>4</sup> a synchronous language extended with continuous time that is developed in our team. Zélus is a conservative extension of a Lustre-like synchronous language to which it adds the ability to define continuous-time dynamics by means of ordinary differential equations and state events. In Zélus it is possible to design and implement discrete-time controllers and model their physical environment in the very same language.

#### 1.3 Contributions

This thesis makes contributions to the treatment of quasi-periodic systems along three themes: verification, implementation, and simulation. In each, using a synchronous approach, we clarify existing work and propose new developments.

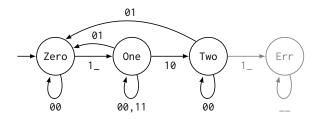

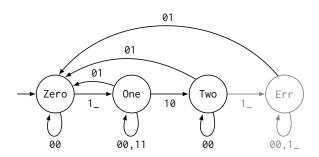

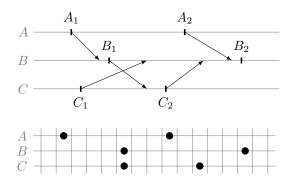

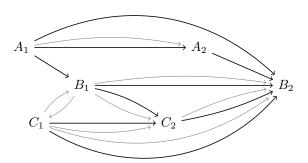

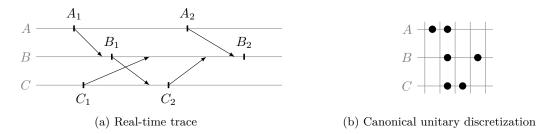

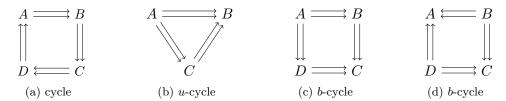

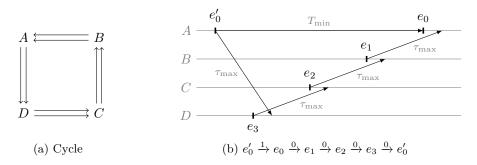

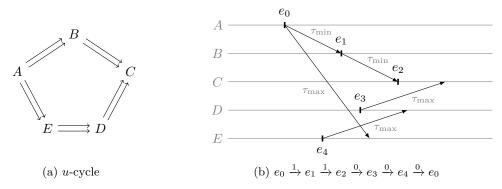

**Verification** The quasi-synchronous abstraction [Cas00] is a discrete abstraction proposed by Paul Caspi for model-checking the safety properties of quasi-periodic systems. Logical steps

<sup>&</sup>lt;sup>2</sup>http://mathworks.com/products/simulink.html

<sup>3</sup>http://ptolemy.eecs.berkeley.edu/

<sup>4</sup>http://zelus.di.ens.fr/

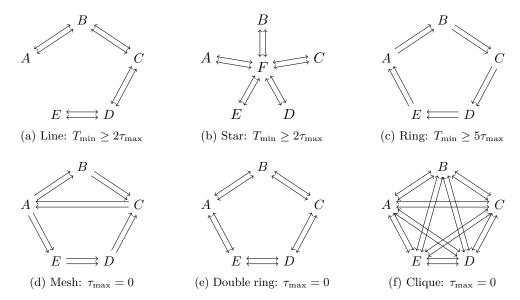

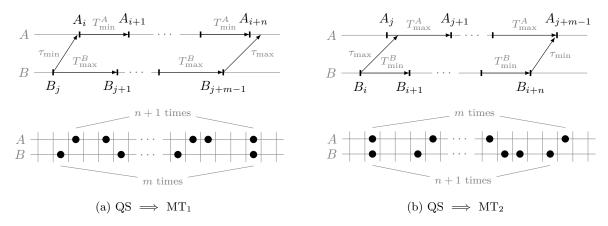

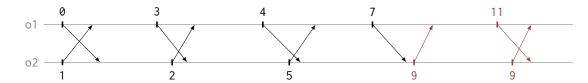

account for transmission delays and the quasi-periodic behavior of processes is captured by the following condition: no process may be activated more than twice between two successive activations of any other. We show that the abstraction is not sound for general systems of more than two nodes. Interestingly, the main difficulty comes from the modeling of transmissions as unit delays, that is, as single logical steps of the discrete model. We introduce the notion of unitary discretization that characterizes traces for which transmission delays can be safely abstracted as unit delays. This notion links the causality induced by communications in the real-time traces with the causalities expressible in the discrete model. We are then able to give necessary and sufficient conditions on both the static communication graph of the application and the real-time characteristics of the architecture to recover soundness. These results generalize naturally to multirate systems where each process is characterized by its own activation period. The quasi-synchronous abstraction thus becomes n/m-quasi-synchrony which states that a process cannot activate more than n times between m activations of another.

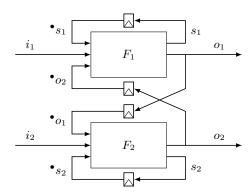

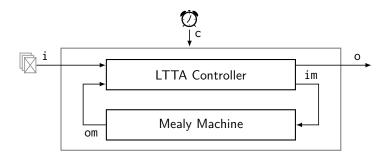

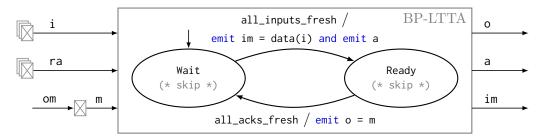

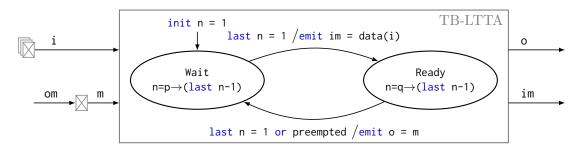

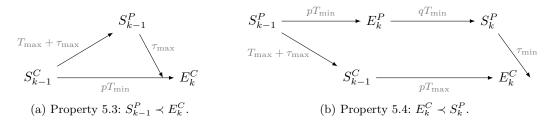

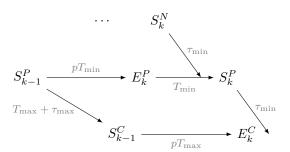

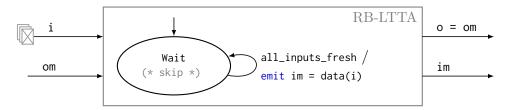

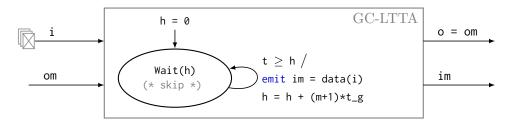

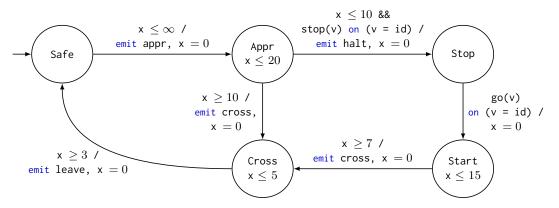

Implementation Introduced in 2002 [BCLG<sup>+</sup>02], Loosely Time-Triggered Architectures or LTTAs are protocols designed to ensure the correct execution of an application running on a quasi-periodic architecture despite the sampling artifacts introduced by communications between unsynchronized processes. Noticing that protocol controllers are also synchronous programs that can be compiled together with application code, we propose a unified synchronous framework that encompasses both the application and the protocol controllers. This framework can be instantiated with any of the LTTA protocols: back-pressure [TPB+08] and timebased [CB08]. We thereby give executable specifications of the protocols written in the kind of languages typically used to program embedded controllers. We show that both of these protocols can be expressed as two-state automata. Additionally, we present new correctness proofs of the protocols, give a simpler version of the time-based protocol and show that it requires broadcast communication. Based on this remark, we propose optimized protocols for system using broadcast communication. Finally, we instantiate our framework with a simple protocol based on clock synchronization to compare its performance with the LTTA approach. This shows that there is no gain in performance when using the LTTA protocols. However, the LTTA protocols are simple to implement and remain a lightweight alternative to clock synchronization. They add the minimum amount of control to ensure the correct execution of an embedded application.

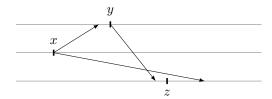

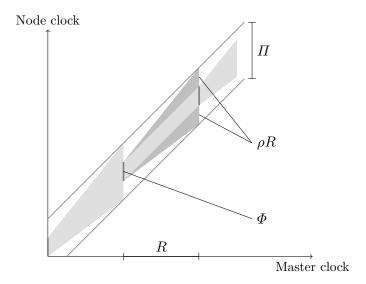

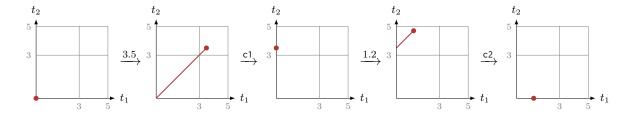

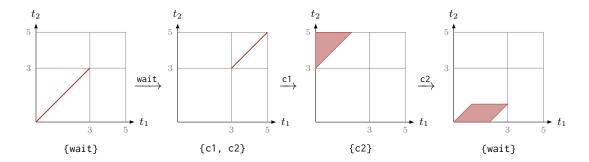

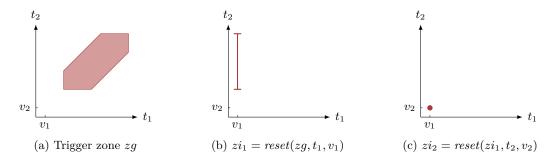

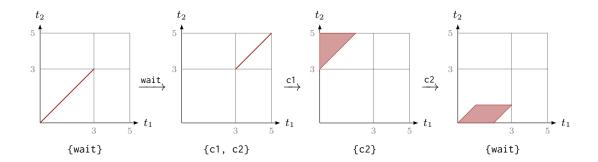

Simulation The specifications of quasi-periodic systems involve real-time characteristics and tolerances: the bounds on the activation periods and the transmission delays. The continuous dynamics of such systems are limited to *timers* that measure time elapsing but also involve nondeterminism. For this kind of system we propose a symbolic simulation scheme—inspired by model checking techniques for timed automata [AD94]—where multiple executions are captured in a single discrete trace and nondeterminism is controlled by the user. Each step is characterized by a set of possible values for the timers and a set of enabled actions. Simulation advances when the user chooses a transition. Starting from a small synchronous language extended with timers and nondeterministic constructs, we show how to adapt typing and modular compilation techniques developed for Zélus to generate discrete synchronous code for symbolic simulation.

### 1.4 Organization

The body of this thesis comprises two introductory chapters and three distinct technical chapters. Related work is described and discussed throughout.

Chapter 2 The first chapter is a brief introduction to Zélus, a synchronous language reminiscent of Lustre [CPHP87] extended with continuous time. The chapter aims to familiarize the reader with the syntax and key features of the language that is used in the rest of the thesis. In particular we show how discrete components activate on the emissions of signals produced by continuous components modeling a physical environment. As an illustration of the modeling possibilities offered by Zélus, this chapter concludes with a complete model of an old fashioned clock.

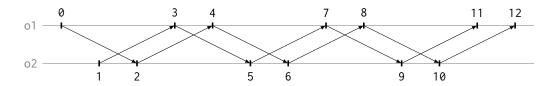

Chapter 3 The second chapter introduces quasi-periodic architectures. We precisely define these architectures and describe the sampling artifacts introduced by communications between unsynchronized nodes. Then we present a synchronous model of quasi-periodic architectures written in the discrete part of Zélus. The link between discrete and real time is realized through input signals for the clocks of the nodes and their delayed versions that model non-instantaneous transmissions. Using the continuous part of Zélus we then show how to implement continuous components producing these signals according to the real-time characteristics of the architecture. This gives a complete executable specification for quasi-periodic systems that can be used for testing and simulation. Our modeling approach is not specific to Zélus and we show how to adapt it to other modeling languages.

Chapter 4 The first technical chapter focuses on the quasi-synchronous abstraction proposed by Paul Caspi. We first show how this abstraction allows the models presented in chapter 3 to be simplified. Then, we prove that the abstraction is not sound in general and give necessary and sufficient conditions to recover soundness. Finally, we extend our results to multirate systems. This chapter is based on the article [BBP16].

Chapter 5 The second technical chapter is dedicated to loosely time-triggered architectures. We first show how the model of chapter 3 can be refined to capture *middleware* that ensures the correct execution of the embedded application. This synchronous framework is instantiated with the two historical LTTA protocols (back-pressure and time-based) an optimized protocol for systems using broadcast communication, and a simple protocol based on clock synchronization. For each of these protocols we give a correctness proof and its theoretical worst-case performance. Using the Zélus model described in chapter 3, we simulate all protocols under various parameter values to compare their performance. This chapter is based on the articles [BBB15] and [BBB16].

Chapter 6 The last technical chapter presents a symbolic simulation scheme for systems involving nondeterministic real-time specifications. We motivate our approach with the example of a simple quasi-periodic system. Then we present a kernel synchronous language extended with *timers* to measure time elapsing and nondeterministic constructs and show how to adapt the typing and compilation of Zélus to generate discrete code for symbolic simulation.

**Chapter 7** The last chapter concludes this thesis with a summary of our results and presents possibilities for future research.

The source code presented throughout the thesis can be compiled and executed in version 1.2.3 of Zélus.<sup>5</sup> This code can be downloaded from:

http://guillaume.baudart.eu/thesis.

<sup>5</sup>http://zelus.di.ens.fr/download.html

# Related publications

- [BBP16] Guillaume Baudart, Timothy Bourke, and Marc Pouzet. Soundness of the quasi-synchronous abstraction. In *International Conference on Formal Methods in Computer-Aided Design (FMCAD)*, pages 9–16, USA, October 2016

- [BBB16] Guillaume Baudart, Albert Benveniste, and Timothy Bourke. Loosely Time-Triggered Architectures: Improvements and comparison. *Transactions on Embedded Computing Systems*, 15(4):71:1–71:26, August 2016 Extended journal version of [BBB15]

- [BBB15] Guillaume Baudart, Albert Benveniste, and Timothy Bourke. Loosely Time-Triggered Architectures: Improvements and comparisons. In *International Conference on Embedded Software (EMSOFT)*, pages 85–94, The Netherlands, October 2015. Best paper nominee

- [BBBC14] Guillaume Baudart, Albert Benveniste, Anne Bouillard, and Paul Caspi. A unifying view of Loosely Time-Triggered Architectures. Technical Report RR-8494, INRIA, March 2014. Corrected version of [BBC10]

# A Brief Introduction to Zélus

In this thesis, we make a significant effort to illustrate our contributions with actual code. This discipline forces a high degree of precision in the models. Additionally, this approach gives both formal models and executable specifications that can be simulated.

Although the main contributions of this thesis are not specific to any programming language, we present all the examples in a single language developed in our team: Zélus [BP13]. We choose Zélus for three main reasons:

- 1. Zélus is a synchronous language in the spirit of Lustre [CPHP87] and Scade. We can thus program the quasi-periodic processes in the kind of programming language typically used to implement embedded applications.

- 2. The language provides constructs to mix discrete controllers and continuous-time dynamics expressed as Ordinary Differential Equations (ODE). We are thus able in chapter 3 to precisely model the real-time specifications of a quasi-periodic system and program the discrete processes in a single, precisely defined, and executable language.

- 3. Compilation of the continuous components is based on source-to-source translations into discrete functions with additional inputs and outputs to handle continuous computations. We show in chapter 6 how to adapt this compilation technique to the symbolic simulation of nondeterministic real-time systems.

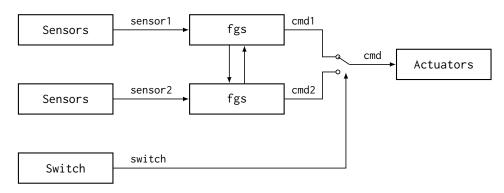

The compilation of a Zélus program mixing discrete and continuous components produces code that must be executed in interaction with a numeric solver. During the simulation, the solver computes an approximation of the continuous-time expressions defined with ODEs. Compared to the control loop presented in figure 1.1 where discrete steps are triggered by an external clock, in Zélus discrete computations are triggered when the solver detects particular events: zero-crossings of continuous-time expressions.

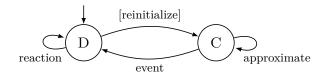

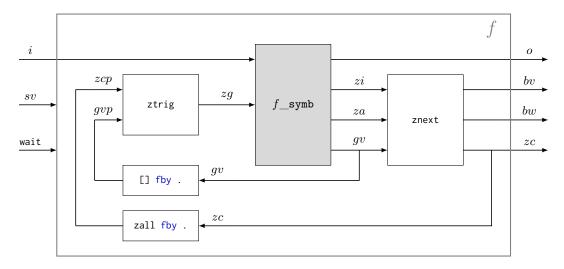

Figure 2.1: [BP13] The basic structure of a Zélus simulation.

As illustrated in figure 2.1, a simulation alternates between two phases. In phase D, discrete components are executed and physical time does not progress. When the computation terminates, the program enters phase C and integration in the numeric solver begins. In phase C, the numeric solver approximates the evolution of continuous-time variables to detect and locate zero-crossing events. The integration stops when such an event has been detected. The program then returns to phase D and the next discrete step is triggered.

A Zélus program is compiled to statically scheduled sequential OCaml<sup>1</sup> code. The semantics of the language, based on non-standard analysis, is described in [BBCP12]. Details on the compilation process can be found in [BBCP11a, BBCP11b, BCP+15].

**Outline** This chapter is a *Zélus survival kit.*<sup>2</sup> It aims to familiarize the reader with the basic syntax and the key features of the language that we use in the following chapters. We illustrate in section 2.1 the discrete part of the language inherited from Lustre. Then in section 2.2 we show how to express continuous dynamics using ODEs, and how to activate discrete components on events generated by continuous ones. Finally in section 2.3 we illustrate this hybrid modeling approach on a complete example: a model of an old-fashioned clock.

### 2.1 A synchronous language ...

Zélus is a synchronous language reminiscent of Lustre [CPHP87] and borrows constructs from Lucid Synchrone [Pou06]. A program is a set of equation defining *streams* of values. Time proceeds by discrete logical steps, and at each step, a program computes the value of each stream depending on its inputs and possibly previously computed values.

For instance, the following function returns the stream of natural numbers starting from an initial value v:

```

let node nat(v) = cpt where

rec cpt = v → pre (cpt + 1)

```

The keyword node indicates a discrete stream function. The only equation uses the initialization operator  $\rightarrow$  and the non initialized *unit delay* pre. It defines the variable cpt as follows:  $\forall n \in \mathbb{N}$ ,

$$cpt_n = (v \to \mathsf{pre}\ (cpt+1))_n$$

(Definition)

$= if\ n = 0\ then\ v_0\ else\ (cpt+1)_n$  (Initialization)

$= if\ n = 0\ then\ v_0\ else\ (cpt+1)_{n-1}$  (Unit delay)

$= if\ n = 0\ then\ v_0\ else\ cpt_{n-1} + 1$  (Simplification)

The execution of a program can be represented as a timeline, called a *chronogram*, showing the sequence of values taken by its streams at each step. For instance, applying the nat function to the constant stream of 10's yields the execution:

http://ocaml.org

<sup>&</sup>lt;sup>2</sup>More details can be found at http://zelus.di.ens.fr.

The delay operator pre has an unspecified value (denoted nil) at the first instant. The compiler performs an *initialization check* to ensure that the behavior of a program never depends on the value nil. Alternatively, the initialized delay operator fby combines initialization and delay operators: x fby  $y = x \rightarrow pre y$ .

When given nat, the Zélus compiler returns the following type signature:

```

val nat: int \xrightarrow{D} int

```

The  $\stackrel{\text{o}}{\longrightarrow}$  indicates a discrete stream function. The compiler infers that nat produces values of type *int* from an input of type *int*.

Operators—like +,  $\star$ , or the logical and—and constants—like 1, true, or 4.2—are lifted to streams of values.

For some functions, like arithmetic operators, the output at an instant only depends on the inputs at the same instant. These functions are termed *combinatorial*.

```

let average(x, y) = (x + y) / 2

val average: int \times int \xrightarrow{A} int

```

The ' $\xrightarrow{A}$ ' in the type signature stands for *any* and indicates a combinatorial function. Such functions can be used in any context: discrete or continuous (see section 2.2).

Valued signals Compared to Lustre, Signal [GGBM91], or Lucid Synchrone, Zélus does not have explicit *clocks* to indicate the presence or absence of a value. Instead, the language has *valued signals*, built and accessed through the constructions emit and present, to model sporadic activations. Consider, for instance, the following program:

```

let node positive(i) = s where rec present i(v) \rightarrow do emit s = (v > 0) done val positive: int signal \xrightarrow{D} bool signal

```

Whenever signal i is present, its value is bound to v and signal s is emitted with value (v > 0). A signal is absent if not explicitly emitted.

**Memories** A signal can be used to update a *memory*, declared by the keyword init. The value of a memory is maintained between two updates. The following example returns the sum of the values received on signal i.

```

let node cumul(i) = o where rec init o = 0 and present i(v) \rightarrow do o = last o + v done val cumul: int signal \xrightarrow{D} int

```

The operator last(.) refers to the value of a memory at the last update.

| i      |   |   | 10 |    | 2  |    |    | 30 |  |

|--------|---|---|----|----|----|----|----|----|--|

| last o | 0 | 0 | 0  | 10 | 10 | 12 | 12 | 12 |  |

| o      | 0 | 0 | 10 | 10 | 12 | 12 | 12 | 42 |  |

**Automaton** Complicated behaviors are often best described as automata whose defining equations at an instant are mode-dependent. An automaton is a collection of states and transitions. There are two kinds of transitions: *weak* (until) and *strong* (unless).

Consider the following example.

```

let node edge_strong(x) = o where rec automaton

| Wait \rightarrow do o = false unless (x = 0) then Found

| Found \rightarrow do o = true done

val edge_strong: int \xrightarrow{D} bool

```

Starting in state Wait, the output o is defined by the equation o = false while the condition (x = 0) is false. At the instant that this condition is true, Found becomes the active state and the output is thereafter defined by the equation o = true.

Weak transitions introduce a delay between the instant when a transition guard becomes true and the instant when the mode changes. Consider the same automaton written with weak transitions.

```

let node edge_weak(x) = o where rec automaton

| Wait \rightarrow do o = false until (x = 0) then Found

| Found \rightarrow do o = true done

val edge_weak: int \stackrel{\rm D}{\rightarrow} bool

```

Applied to the same input stream, we get:

#### 2.2 ... extended with continuous time

Zélus combines two models of time: discrete and continuous. Continuous-time functions are introduced by the keyword hybrid and continuous dynamics are expressed with ordinary differential equations.

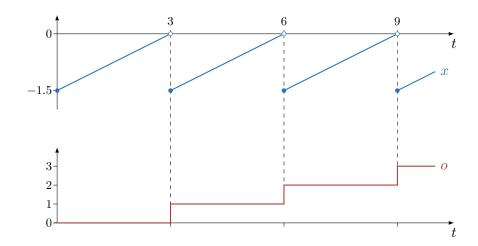

Figure 2.2: Simulation trace of the function sawtooth(0.5, -1.5).

Consider the following Zélus program that implements the initial value problem shown on the right. The continuous-time variable x is defined by an ODE and an initial condition.

```

let hybrid affine(a, b) = x where  \text{rec der x = a init b} \qquad \qquad \begin{cases} \dot{x}(t) = a \\ x(0) = b \end{cases}  val affine: float \times float

```

The  $\stackrel{\cdot}{\longrightarrow}$  in the type signature indicates a continuous time function. The keyword der defines x by its derivative and initial value. The ideal value of x produced by affine is:

$$x(t) = b + \int_0^t a \, dx$$

During execution this value is approximated by a numeric solver.

**Zero-crossings** Discrete computations are triggered when the solver detects particular events: zero-crossings of continuous-time variables. In Zélus, (rising) zero-crossings are monitored using the up operator. For instance, the following program triggers the nat function of section 2.1 on the zero-crossings of a sawtooth signal.

```

let hybrid sawtooth(a, b) = o where rec init o = 0 and der x = a init b reset z \rightarrow b and z = up(x) and present z \rightarrow do o = nat(1) done val sawtooth: float \times float \xrightarrow{C} int

```

A memory o is initialized with value 0. At zero-crossing instants—when the value of x computed by the numeric solver passes through zero from a negative value to a positive one—x is reset to b and the new value of o is computed. Otherwise the last computed value is maintained. Figure 2.2 shows a simulation trace of this program.

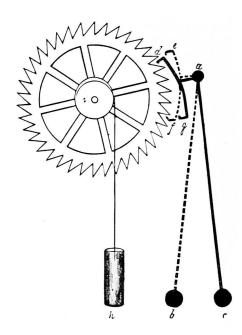

Figure 2.3: [Mat86] Gravity clock escapement mechanism aided by weight.

### 2.3 A complete example: the Zélus clock

In this section we present a complete example: the Zélus clock. First we show how to implement a physical model of an old-fashioned pendulum clock in Zélus. The clock generates a regular signal tick that we use to trigger a discrete stopwatch. This example illustrates how to mix the continuous dynamic of the pendulum clock with the discrete control of the stopwatch.

#### A pendulum clock

Figure 2.3 illustrate the simplest form of clock work or *movement*. A cog-wheel turns on a pin by the force of the suspended weight. The position of the weight h is a function of its initial position  $h_0$ , and, without any additional control, follows a simple ODE.

where g is the acceleration of gravity ( $g \approx 9.8 \, m.s^{-2}$  on Earth) and +., -., \*., /. denote floating-point operations. The hands of the clock are attached to the wheel (or, more probably, another wheel coupled with the main one) and move with the weight.

The escapement mechanism controls the fall of the weight. It comprises two elements: a pendulum and an anchor attached to the pendulum and swinging with it. Assume that the pendulum starts in the position r (marked in black) in figure 2.3. In this position, the anchor blocks the wheel. When the pendulum starts swinging to the position b (marked by the dotted line), the anchor moves, releasing the wheel which is then dragged down by the weight. But before it moves too far, the anchor catches the wheel and stops the movement of the weight.

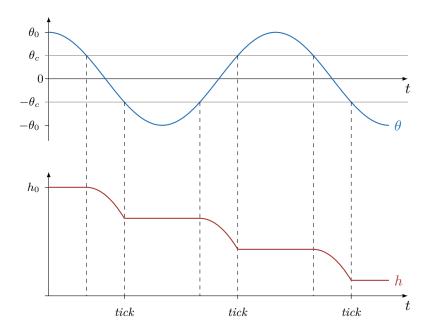

Figure 2.4: Simulation trace of the function clock.

The discontinuous movement of the wheel produces a regular signal that can be used to measure time elapsing (the ticks of the clock). In other words, the escapement mechanism discretizes the continuous fall of the weight. In an old-fashioned watch, the weight is replaced by a circular spring, and the pendulum by a small oscillating spring-mass system, but the principle is the same.

The position of the pendulum is a function of its (constant) length l and initial angle  $\theta_0$ , following the well-known pendulum equation.

```

let hybrid pendulum(theta0) = theta where rec der td = -. (g /. 1) *. sin (theta) init 0.0 and der theta = td init theta0 \begin{cases} \ddot{\theta}(t) = -(g/l)\sin(\theta(t)) \\ \dot{\theta}(0) = 0 \\ \theta(0) = \theta_0 \end{cases} val pendulum: float \overset{\text{C}}{\to} float

```

The escapement mechanism blocks the movement of the weight when the absolute value of the angle  $|\theta|$  is greater than a value  $\theta_c$ , characteristic of the anchor. This behavior is implemented in Zélus by the following two-state automaton.

```

let hybrid clock(h0, theta0) = tick where

rec theta = pendulum(l, theta0)

and automaton

| Block(hi) → do h = hi

until up(thetac -. abs(theta)) then Move(h)

| Move(hi) → do h = weight(hi)

until up(abs(theta) -. thetac) then do emit tick in Block(h)

init Block(h0)

val clock: float × float → unit signal

```

The state Block is parametrized by the position of the weight. This position is maintained until  $|\theta|$  (abs(theta)) crosses the value  $\theta_c$ . Then the escapement frees the weight and the clock enters state Move. The state Move is also parametrized by the initial position of the weight. In this state, the wheel is free and the movement of the weight is controlled by the function weight. When  $|\theta|$  (abs(theta)) crosses the value  $\theta_c$  the escapement blocks the wheel (producing the characteristic *tick* sound of the clock). The clock emits a signal tick and goes back to state Block with the current position of the weight h (do emit tick in Block(h)). This is a simple example of actions triggered on the transitions of an automaton. The automaton starts in state Block (init Block(h0)) with the initial position of the weight  $h_0$ . Figure 2.4 shows a simulation trace of this program.

#### A discrete stopwatch

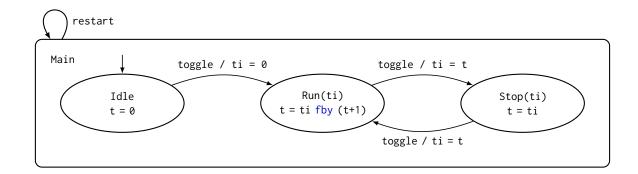

A simple stopwatch can be implemented with the hierarchical automaton illustrated in figure 2.5. The user controls the stopwatch with two buttons: toggle to start and stop the stopwatch, and restart to reinitialize the controller. The output is the number of clock ticks emitted when the stopwatch is running. The automaton of figure 2.5 is readily programmed in Zélus.

```

let node stopwatch(toggle, restart) = t where rec automaton  | \mbox{ Main } \rightarrow \mbox{ do automaton } \\ | \mbox{ Idle } \rightarrow \mbox{ do } t = 0 \\ | \mbox{ until toggle() then } \mbox{Run(0)} \\ | \mbox{ Run(ti) } \rightarrow \mbox{ do } t = ti \mbox{ fby } (t+1) \\ | \mbox{ until toggle() then } \mbox{ Stop(t)} \\ | \mbox{ Stop(ti) } \rightarrow \mbox{ do } t = ti \\ | \mbox{ until toggle() then } \mbox{ Run(t)} \\ | \mbox{ end} \\ | \mbox{ until restart() then } \mbox{ Main} \\ | \mbox{ val stopwatch : unit signal } \times \mbox{ unit signal } \xrightarrow{D} \mbox{ int} \\ | \mbox{ intil toggle() then } \mbox{ Stopwatch : unit signal } \times \mbox{ unit signal } \xrightarrow{D} \mbox{ int } \\ | \mbox{ intil toggle() then } \mbox{ Stopwatch : unit signal } \times \mbox{ unit signal } \xrightarrow{D} \mbox{ int } \\ | \mbox{ intil toggle() then } \mbox{ intil toggle() then } \\ | \mbox{ unit loggle() then } \mbox{ intil toggle() then } \\ | \mbox{ unit loggle() then } \mbox{ unit loggle() then } \\ | \mbox{ unit loggle() then } \mbox{ unit loggle() then } \\ | \mbox{ unit loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() then } \\ | \mbox{ loggle() then } \mbox{ loggle() then } \\ | \mbox{ loggle() th

```

Initially, in the Idle state, the output of the stopwatch t is always 0. The user can activate the stopwatch by pressing the toggle button. The stopwatch then enters the parametrized state Run with value 0. In state Run, the output is incremented by one at every instant starting from the value of the parameter ti. In this state, it is possible to pause the stopwatch by pressing the toggle button. The stopwatch then enters the parametrized state Stop where the value of the output is maintained until the user presses the toggle button to restart the counter. In any state, it is possible to press a restart button to go back to the Idle state, thus reinitializing the stopwatch.

#### The complete model

The last thing to do is to link the stopwatch controller to the ticks of the pendulum clock. Since the user can choose to press the buttons toggle and restart at any moment, the ticks of the clock (signal tick) and the events button pressed are not synchronized a priori. We thus start by defining a global discrete clock to trigger the stopwatch by taking the union of the emissions of all these signals. In Zélus we write present tick() | toggle() | restart(). Then, by definition, at each step of the base clock, signals toggle and restart are either absent or

Figure 2.5: A simple stopwatch controller.

present. These continuous signals can thus be treated as discrete signals and used as input for the discrete stopwatch controller.

The complete Zélus model is then:

```

let hybrid chrono(toggle, restart) = t where rec init t = 0 and tick = clock(h0, theta0) and present tick() | toggle() | restart() \rightarrow do t = stopwatch(toggle, restart) done val chrono: unit signal \times unit signal \stackrel{\mathrm{C}}{\rightarrow} int

```

A memory t is initialized with value 0. Signal tick is produced by the physical model of the pendulum clock clock. At each step of the base clock, the new value t is computed by the discrete controller stopwatch.

We finally have a complete model of a simple old-fashioned chronometer (in the void, since we do not consider energy loss in our simple model). A more faithful physical model would integrate energy loss and mechanisms to ensure isochronous oscillations of the pendulum [Huy73].

#### 2.4 Conclusion

In this chapter we presented Zélus, a synchronous language extended with continuous time, that we chose for the implementations presented in this thesis. In Zélus it is possible to write discrete controllers in a language reminiscent of Lustre, and to model the continuous dynamics of the environment with ODEs.

The compilation of a Zélus program produces code that must be executed in interaction with a numeric solver. During an execution, the solver approximates the continuous-time variables defined with ODEs and monitors particular events: zero-crossings of continuous-time variables. Such events can be used to trigger discrete computations.

We presented the syntax and key features of Zélus on elementary examples. Then we illustrated the modeling possibilities offered by Zélus with a physical model of an old-fashioned clock coupled with a discrete stopwatch.

Using Zélus, we are able in chapter 3 to propose a discrete model of a quasi-periodic architecture and to link it with its real-time characteristics.

# **Quasi-Periodic Architectures**

Introduced in [Cas00], the *quasi-synchronous approach* is a set of techniques for building distributed control systems. It is a formalization of practices that Paul Caspi observed while consulting in the 1990s at Airbus, where engineers were deploying Lustre/SCADE [HCRP91] designs onto networks of non-synchronized nodes communicating via shared memories with bounded transmission delays.

In contrast to the *Time-Triggered Architecture* (TTA) [Kop11], the quasi-synchronous approach does not rely on clock synchronization. Processors execute periodically with the same nominal period and communicate via a reliable network, but the activation periods of the processors and communication delays are subject to jitter. We call this a *quasi-periodic architecture*. This is a classic model, also called *synchronous real-time model* in the distributed systems community [ADLS94, Cri96]. Such systems arise naturally as soon as two or more microcontrollers running periodic tasks are interconnected. They are common in aerospace, power generation, and railway systems.

This chapter presents the quasi-periodic architectures that are central to this thesis. The aim of this chapter is to provide a global framework to describe embedded applications running on such architectures that can adapted and refined in the following chapters. We adopt a classic approach of modeling distributed systems using a discrete synchronous formalism and give a complete discrete model of the architecture: computing nodes, communication media, and delayed transmission.

Traditionally, the link between the discrete mode and real time is 'pushed outside' the model: real-time constraints are modeled with additional inputs—like activation signals or regular clock signals—and the model does not formally provide any information on how to produce these inputs. We, however, implement our model in Zélus—introduced in chapter 2—which allows us to express both the discrete synchronous model and the real-time constraints of the architecture in an executable language.

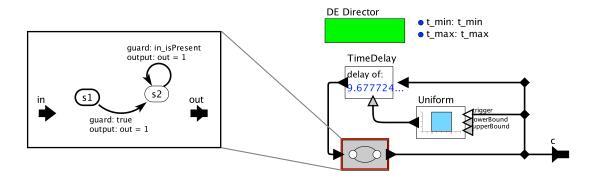

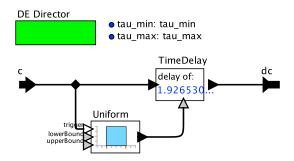

Outline In section 3.1 we define the concept of a quasi-periodic architecture. Running an application on such an architecture introduces sampling artifacts that are described in section 3.2. Then, in section 3.3, we show how to model quasi-periodic architectures in a discrete synchronous formalism. Using Zélus, we link this discrete model to the real-time characteristics of the architecture in section 3.4. Finally, in section 3.5, we show how to adapt our approach to other modeling tools, namely, Ptolemy and Simulink.

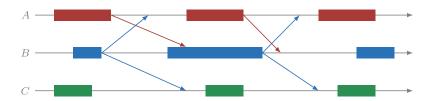

Figure 3.1: Example of a real-time trace of a quasi-periodic architecture with three processors. Rectangles represent tasks and arrows denote message transmissions. Note the jitter both on node activation periods and transmission delays.

### 3.1 Definition

In this section we give an abstract model of quasi-periodic architectures. The goal is to account for all sources of timing nondeterminism—hardware, operating system, communication network—in one simple model.

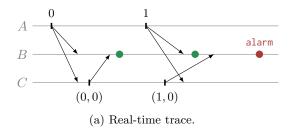

Traces of distributed systems are typically described as a set of tasks and transmissions. Figure 3.1 shows an example of such a trace. In our model, we assume that individual processes are synchronous: reactions triggered by a local clock execute in zero time (atomically with respect to the local environment). The only events are thus processor activations and message transmissions.

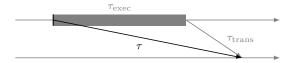

To abstract from the execution time, the easiest solution—illustrated in figure 3.2—is to consider instantaneous activations and capture the execution time as part of the communication delay. This abstraction imposes that a processor cannot receive a message during the execution of a task. For instance, in figure 3.1, the first message sent by processor A is only read by processor B at its third activation. It is, however, safe to assume that a message received exactly when a consumer activates can be read immediately.

For each processor, an execution is now an infinite sequence of instantaneous activations triggered by a local clock.

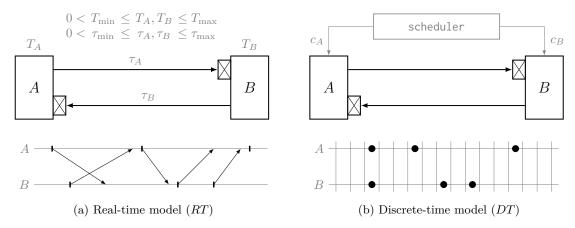

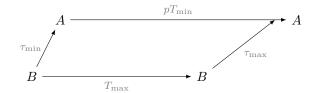

**Definition 3.1** (Quasi-periodic architecture). A quasi-periodic architecture is a finite set of processors, or nodes  $\mathcal{N}$ , where

1. every node  $n \in \mathcal{N}$  executes almost periodically, that is, the actual time between any two successive activations  $T \in \mathbb{R}$  may vary between known bounds during an execution,

$$0 \le T_{\min} \le T \le T_{\max},\tag{RP}$$

2. values are transmitted between processes with a delay  $\tau \in \mathbb{R}$ , bounded by  $\tau_{\min}$  and  $\tau_{\max}$ ,

$$0 \le \tau_{\min} \le \tau \le \tau_{\max}.$$

(RT)

A quasi-periodic system can also be characterized by its nominal period  $T_{\text{nom}} = (T_{\text{min}} + T_{\text{max}})/2$  and maximum jitter  $\varepsilon$ , where  $T_{\text{min}} = T_{\text{nom}} - \varepsilon$  and  $T_{\text{max}} = T_{\text{nom}} + \varepsilon$ , and similarly for the transmission delay.

We assume without loss of generality that all nodes start executing at t=0. Initial phase differences between nodes can be modeled by a succession of *mute* activations before the actual start of the system. The margins encompass all sources of divergence between nominal and actual values, including relative clock jitter, interrupt latencies, and scheduling delays.

Figure 3.2: We abstract a task as an instantaneous activation and a communication delay  $\tau$ . The communication delay  $\tau$  encompasses both the execution time  $\tau_{\rm exec}$  and the transmission delay  $\tau_{\rm trans}$ :  $\tau = \tau_{\rm exec} + \tau_{\rm trans}$ .

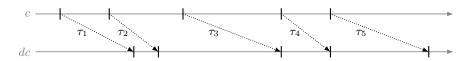

### 3.2 Communication by Sampling

Messages sent by nodes are stored at receivers in local memories which are updated atomically. A producer can send the same message to several receivers. A memory is only sampled when the corresponding node is activated by its local clock. There is no synchronization between producers and receivers since local clocks are unsynchronized. This communication model is called *Communication by Sampling* (CbS) [BCDN<sup>+</sup>07].

To illustrate this communication scheme one imagine a sleepy student in a class room. Periodically, the student wakes up and reads the blackboard. Then he falls asleep until he wakes up and reads the board again. In this example, there is no synchronization between the teacher and the student. During a nap, information written on the board may or may not change. Due to this analogy, this simple communication scheme is sometimes called *blackboard communication* [Ber89, §3].

Finally we assume a reliable communication network, that is, the network guarantees message delivery and preserves message order. If a message  $m_1$  is sent before  $m_2$  then  $m_2$  is never received before  $m_1$ . This is necessarily the case when  $\tau_{\text{max}} \leq T_{\text{min}} + \tau_{\text{min}}$ . Otherwise, with a lossless network, it is always possible to number messages and stall those that arrive out of sequence.

#### Value duplication and loss

The lack of synchronization means that successive variable values may be duplicated or lost. For instance, if a consumer of a variable is activated twice between the arrivals of two successive messages from the producer, it will *oversample* the buffered value. On the other hand, if two messages of the producer are received between two activations of the consumer, the second value *overwrites* the first which is then never read.

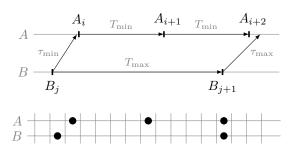

These effects occur for any non-zero jitter  $\varepsilon$ , regardless of how small. The timing bounds of definition 3.1 mean, however that the maximum numbers of consecutive oversamplings and overwritings are functions of the bounds on node periods and transmission delays  $(\forall x \in \mathbb{R}, \lceil x \rceil$  denotes the smallest integer i such that  $x \leq i$ ).

**Property 3.1.** Given a pair of nodes executing and communicating according to definition 3.1, the maximum number of consecutive oversamplings and overwritings is

$$n_{os} = n_{ow} = \left\lceil \frac{T_{\text{max}} + \tau_{\text{max}} - \tau_{\text{min}}}{T_{\text{min}}} \right\rceil - 1.$$

(3.1)

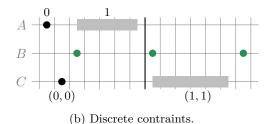

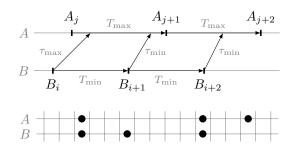

*Proof.* Consider a pair of nodes A and B with B receiving messages from A. In the best case, illustrated in figure 3.3a, a message sent by A at time t arrives in B's shared memory at  $t + \tau_{\min}$ . Then if A runs as slowly as possible the next message is sent at  $t + T_{\max}$  and

(a) Each execution of B samples the first message sent by A.

(b) All messages sent by A are overwritten by the last one.

Figure 3.3: Witnesses for the maximum number of oversamplings (a) and overwritings (b)

arrives in B's shared memory at worst at  $t + T_{\text{max}} + \tau_{\text{max}}$ . The maximal delay between two successive arrivals is thus

$$T_{\max} + \tau_{\max} - \tau_{\min}$$

.

At best, B is activated every  $T_{\min}$ . The maximum number of executions n of B is thus:

$$nT_{\min} < T_{\max} + \tau_{\max} - \tau_{\min}$$

.

Each execution of B that occurs between the two arrivals samples the last received value. The maximum number of oversamplings  $n_{os} = n - 1$  is thus given by equation (3.1).

The proof for the number of consecutive overwritings, illustrated in figure 3.3b, is similar.

Property 3.1 implies that data loss can be prevented by activating a consumer more frequently than the corresponding producer. This can be achieved by introducing mute activations of the receiver at the cost of higher oversampling. Quasi-periodic architectures involving such producer-consumer pairs are studied in  $[BCLG^+02]$ .

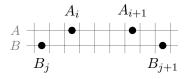

Quasi-periodic architectures are a natural fit for continuous control applications where the error due to sampling artifacts can be computed and compensated for. On the other hand, discrete control systems, like state machines, are generally intolerant to data duplication and loss.

#### Signal combinations

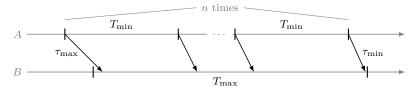

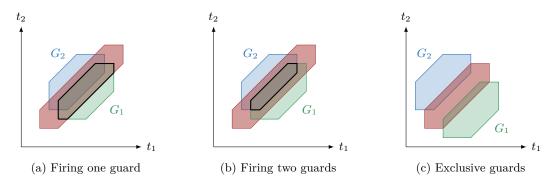

There is another obstacle to implementing discrete applications on a quasi-periodic architecture: naively combining variables can give results that diverge from the reference semantics. Consider the classic example of figure 3.4 [Cas00, CB08, BBC10]. A node C reads two boolean inputs a and b, produced by nodes A and B, respectively, and computes the conjunction,  $c = a \wedge b$ . The first two lines of figure 3.4 show the content of the local memories of node C corresponding to variables a and b.

Figure 3.4: The effect of sampling on signal combinations

Suppose that a is false for three activations of A before becoming true and b is true for three activations of B before becoming false. In a synchronous semantics, with simultaneous activations of A, B, and C, node C should return false at each activation. But, as figure 3.4 shows, since nodes are not synchronized, it is probable that the values of a and b do not change at exactly the same time. There is thus a small interval where both a and b are true.

If node C does not sample the content of the memories during this interval, the output is always false, as expected (case 1). On the other hand, if node C does sample the content of the memories during this interval, the output c is set to true for one period of C (case 2).

In other words, the outputs of this simple application depend on the relative activations of nodes A, B, and C. This phenomenon cannot be avoided by changing the frequency of node activations.

Buffers We consider here one-place buffers, but the previous remarks can be generalized to bounded buffers of arbitrary size. Since nodes are not synchronized it is impossible to ignore the case of producer/consumer pairs where the producer runs as quickly as possible, that is every  $T_{\min}$ , and the consumer runs as slow as possible, that is every  $T_{\max}$ . As soon as the nodes are not perfectly synchronous, that is,  $T_{\min} < T_{\max}$ , the difference between the cumulative tick counts of nodes can diverge without bound. Without any additional synchronization mechanism it is thus impossible to bound the size of the buffers while ensuring that no data will be lost or oversampled.

Properties of quasi-periodic architectures such as the maximal number of lost values (property 3.1), message inversions, and end-to-end message latency have been verified with the proof assistant PVS [LS14]. Ad-hoc abstract domains have also been designed for the static analysis of quasi-periodic architectures [Ber08]. These domains can be used to check quantitative properties such as *How many times a value changed during a time interval* or *Two redundant computing units must agree more than half of the time*. These works are based on the real-time model of definition 3.1. We propose to reason about these quasi-periodic architectures in a discrete-time model. In the following we present the discrete model, and show how Zélus allows us to relate the discrete-time with the real-time characteristics of the architecture.

# 3.3 Discrete model

One of the central ideas in the original quasi-synchronous approach is to replace a model with detailed timing behavior by a discrete model [Cas00, §3]. An embedded application running

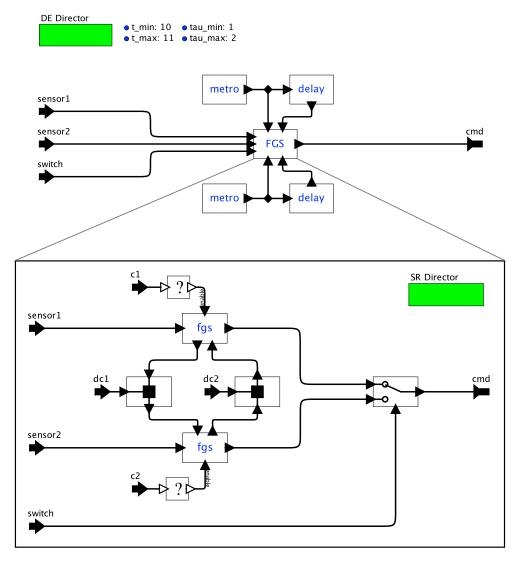

Figure 3.5: Flight guidance system. Only one FGS component, the *pilot* side is active. The crew can switch from one component to the other using a *transfer switch*.

on a quasi-periodic architecture can then be described in the language used to program the application: Scade, Lustre, or (the discrete part of) Zélus. This is a classic approach to architecture modeling using synchronous languages [BS01, HB02].

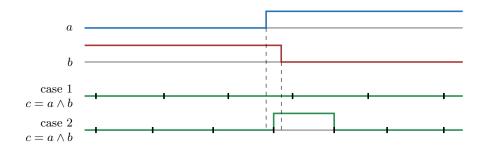

# Illustration: a flight guidance system

Consider the simple embedded application (from [MBT<sup>+</sup>15]) shown in figure 3.5. A *flight guidance system* (FGS) is a part of an aircraft controller. Using data obtained from airplane sensors, the FGS periodically generates yaw, pitch, and roll commands to adapt the trajectory of the plane. For reason of fault tolerance, it is often implemented as two redundant modules.

Most of the time, only one FGS component, the *pilot side*, is active. During flight, the crew can switch from one component to the other using a *transfer switch*. The two components share information to avoid glitches when transferring control from one to the other.

At this level, the controller is a purely discrete application where all elements execute synchronously. For example, in Zélus we write:

```

let node controller(sensor1, sensor2, switch) = cmd where rec cmd1 = fgs(sensor1, cmd2) and cmd2 = fgs(sensor2, cmd1) and cmd = if switch then cmd1 else cmd2 val\ controller:\ data \times\ data \times\ bool \xrightarrow{D}\ cmd

```

At each step, using the input from a sensor and the command emitted by the other component each FGS generates a new command. The controller discards one of these commands depending on the state of the transfer switch.

To model the deployment of the FGS application on a two node quasi-periodic architecture, we introduce additional inputs: activations signals to model the quasi-periodic clocks and transmissions delays. Figure 3.6 illustrates the resulting model. In Zélus, we use signals to model variables that are not necessarily defined at each logical step: the activation signals, and node outputs. In Zélus we write:

Figure 3.6: A quasi-periodic model of the FGS example of figure 3.5. Logical clocks model asynchronous activations. Symbols ■ denote *blackboard* communication.

```

let node qp_controller((c1, c2, dc1, dc2), (sensor1, sensor2, switch)) = cmd where

rec present c1() → do emit cmd1 = fgs(sensor1, mcmd2) done

and present c2() → do emit cmd2 = fgs(sensor2, mcmd1) done

and mcmd1 = link(c1, dc1, cmd1, idle)

and mcmd2 = link(c2, dc2, cmd2, idle)

and cmd = if switch then cmd1 else cmd2

val qp_controller:

(unit signal × unit signal × unit signal × unit signal) × (data × data × bool) → cmd signal

```

Compared to the previous synchronous controller, there are four additional inputs (the small clocks in figure 3.6). Signals c1 and c2 denote the quasi-periodic clocks of the nodes, dc1 and dc2 their delayed versions that model transmission delays (one for each communication channel). The union of these signals gives a base notion of logical instant or step: the global clock. It allows us to model the rest of the architecture in a discrete synchronous framework.

A quasi-periodic node is activated at each tick of its local clock c. In Zélus we write:

```

present c1() \rightarrow do emit cmd1 = fgs(sensor1, mcmd2) done

```

When the unit signal c1 is emitted, the first node executes one step of the fgs application using the input from the sensor, sensor1, and the content of the communication link, mcmd2. The result is emitted on signal cmd1.

The two communication links mcmd1 and mcmd2 allow information sharing between the two fgs despite their asynchronous activations. These links, initialized with a constant value idle of type data, are controlled by the clocks of the nodes, c1 and c2, and their delayed versions, dc1 and dc2.

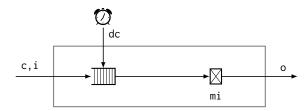

#### Modeling links

A link, shown in figure 3.7, models communication by sampling between two nodes. Since nodes are not synchronized, the output of a link must be defined at each logical step. Received values are thus stored in a memory.

Figure 3.7: Schema of a communication link modeling delayed transmission between nodes. The striped box represents a FIFO queue.

```

let node mem(i, mi) = o where rec init m = mi and present i(v) \rightarrow do m = v done and o = last m in a signal \times \alpha \xrightarrow{D} \alpha

```

The keyword init initializes a memory, that is, a variable defined at each activation of the node, and last(m) is its previous value. Each time the input signal i is emitted, m is updated with the new received value v. By returning last m, we ensure that the output does not depend instantaneously on the inputs.

Delayed communications are modeled using a *first in first out* (FIFO) queue that can be accessed with the following imported functions:

```

empty denotes an empty queue.

is_empty(q) tests if a queue q is empty.

size(q) returns the size of q.

front(q) returns the oldest value in q.

back(q) returns the newest value in q.

enqueue(q, x) pushes a value x into q.

dequeue(q) removes the oldest value from q.

```

The complete Zélus interface, that is, the type signatures of the imported functions, is:

```

val empty: \alpha queue \xrightarrow{A} bool val size: \alpha queue \xrightarrow{A} int val front: \alpha queue \xrightarrow{A} \alpha val back: \alpha queue \xrightarrow{A} \alpha val enqueue: \alpha queue \times \alpha \xrightarrow{A} \alpha queue val dequeue: \alpha queue \xrightarrow{A} \alpha queue

```

To model a communication channel, a queue is triggered by the input signal i and the delayed sender clock dc that models transmission delays. Messages in transmission are stored in the queue and emitted when the transmission delay elapses, that is, when clock dc ticks.

```

let node channel(dc, i) = o where rec init q = empty and present  \mid dc() \ \& \ i(v) \rightarrow \ do \ q = enqueue(dequeue(last q), \ v) \ done \\ \mid i(v) \rightarrow \ do \ q = enqueue \ (last \ q, \ v) \ done \\ \mid dc() \rightarrow \ do \ q = dequeue \ (last \ q) \ done \\ and present \ dc() \rightarrow \ do \ emit \ o = front(last \ q) \ done

```

val channel: unit signal  $\times \alpha$  signal  $\xrightarrow{D} \alpha$  signal

The first present block maintains the queue q. Each new message v received on signal i is added to the queue: q = enqueue(last q, v). When a transmission delay elapses, that is, each time clock dc ticks, the first pending message is removed from the queue: q = dequeue(last q). If both signals i and dc are emitted at the same time we combine the previous behaviors. In parallel, the second present block emits the first pending message on signal o when a transmission elapses.

In this model, we assume that the clock dc models delayed transmission, that is, dc is a delayed version of signal i. This assumption guarantees that the queue is never empty when dc ticks. However, it may be the case that a node does not send a message at each activation of its clock. In this case, dc depends on conditions computed locally by the sender node. This implies that the activation clock of the complete model (the conjunction of all activation signals: c1, c2, dc1, and dc2) depends on conditions computed by one of its components. But our goal is to maintain a clear separation between global inputs modeling the real-time characteristics of the architecture (the activation signals) and the discrete logic of our model.

A classic solution is to keep a delayed version of all activations of a sender node, and use a special value to denote the *absence* of a message. When a node is activated but does not produce a message, an empty message is sent. We use an option type to denote the presence or absence of a value. A value of type  $\alpha$  option is either None or Some(v) where v is a value of type  $\alpha$ .

```

type \alpha option = None | Some of \alpha The expression get(x) returns the value v when x = Some(v). val get: \alpha option \xrightarrow{A} \alpha

```

A more complete model for the links thus takes three inputs instead of two: the clock of the sender node c, its delayed version dc, and messages sent on signal i whose emissions are a subset of the activations of c. Signal s is emitted with value Some(v) when a value v is received on signal i, and with value None if the sender is activated but does not send a message (when c is present but not i). The rest of the code follows the structure of the previous model with signal s as input instead of i.

```

let node channel(c, dc, i) = o where rec init q = empty and trans = present (is_empty (last q)) \rightarrow false else front(last q) \neq None and present | i(v) \rightarrow do emit s = Some(v) done | c() \rightarrow do emit s = None done and present | dc() & s(v) \rightarrow do q = enqueue(dequeue(last q), v) done | s(v) \rightarrow do q = enqueue (last q, v) done | dc() \rightarrow do q = dequeue (last q) done and present dc() & trans \rightarrow do emit o = get(front (last q)) done

```

val channel : unit signal  $\times$  unit signal  $\times$   $\alpha$  signal  $\stackrel{D}{\longrightarrow} \alpha$  signal

Signal o is only emitted when the queue is not empty and when the oldest element of the queue is an actual message, that is, when variable trans is set to *true*. The present construct in the definition of trans ensures that we only check the front of a non-empty queue.

| С     |       | •       | •            |        | •                    |       |      | •       | •      |  |

|-------|-------|---------|--------------|--------|----------------------|-------|------|---------|--------|--|

| i     |       | 1       |              |        | 2                    |       |      | 3       |        |  |

| dc    |       |         |              | •      |                      | •     | •    |         | •      |  |

| S     |       | Some(1) | None         |        | Some(2)              |       |      | Some(3) | None   |  |

| q     |       | [1]     | $[None,\ 1]$ | [None] | $[2, \mathrm{None}]$ | [2]   | []   | [3]     | [None] |  |

| trans | false | false   | true         | true   | false                | false | true | false   | true   |  |

| 0     |       |         |              | 1      |                      |       | 2    |         | 3      |  |

**Bounded FIFO** Using the quasi-periodic nature of the architecture, it is possible to bound the size of the FIFO that models messages in transmission. At worst, a first message is as slow as possible and arrives in the memory after a delay  $\tau_{\text{max}}$ . At best, the producer then sends messages every  $T_{\text{min}}$ . The maximum number of messages in transmission is thus:

$$n_{trans} = \left\lceil \frac{\tau_{\text{max}}}{T_{\text{min}}} \right\rceil.$$

Finally, we can combine a channel and a memory to model the complete link of figure 3.7:

When a message is sent on signal i, it goes through the channel and, after the transmission delay (modeled by the delayed clock dc) is stored in a memory. New messages overwrite previous memory values. The memory contents are output by the link. Note that the memory mem imposes a unit delay between the input i and the output o that precludes instantaneous transmission.

# 3.4 Real-time model

The discrete model of section 3.3 does not make any assumptions on how and when clock signals and their delayed versions are produced. We can now complete our Zélus model with continuous components that simulate the real-time behavior of the quasi-periodic architecture. The discrete model can be simulated and verified using discrete language tools, and the complete Zélus program can be executed to simulate real-time traces.

For instance, the following Zélus program simulates possible executions of the FGS example:

```

let hybrid rt_controller(sensor1, sensor2, switch) = cmd where rec c1 = metro(t_min, t_max) and dc1 = delay(c1, tau_min, tau_max) and c2 = metro(t_min, t_max) and dc2 = delay(c2, tau_min, tau_max) and present c1() | dc1() | c2() | dc2() \rightarrow do emit g done and present g() \rightarrow do cmd = qp_controller ((c1, c2, dc1, dc2), (sensor1, sensor2, switch)) done val rt controller: data \times data \times bool \stackrel{C}{\rightarrow} cmd signal

```