## Energy consumption optimization of parallel applications with Iterations using CPU frequency scaling

Ahmed Badri Muslim Fanfakh

#### ▶ To cite this version:

Ahmed Badri Muslim Fanfakh. Energy consumption optimization of parallel applications with Iterations using CPU frequency scaling. Other [cs.OH]. Université de Franche-Comté, 2016. English. NNT: 2016BESA2021. tel-01514173

### HAL Id: tel-01514173 https://theses.hal.science/tel-01514173v1

Submitted on 25 Apr 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

école doctorale sciences pour l'ingénieur et microtechniques UNIVERSITÉ DEFRANCHE-COMTÉ

# Energy Consumption Optimization of Parallel Applications with iterations using CPU Frequency Scaling

Ву

#### Ahmed Badri Muslim FANFAKH

A Dissertation Submitted to the

University of Franche-Comté

in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

in Computer Science

Thèse soutenue à Besançon le : 17 octobre 2016

#### Dissertation Committee:

DR FABIENNE JÉZÉQUEL(HDR)

PR JEAN-MARC PIERSON

PR NABIL ABDENNADHER

PR RAPHAËL COUTURIER

DR JEAN-CLAUDE CHARR

University of Paris 6 University of Toulouse 3 University of HES-SO, Switzerland University of Franche-Comté University of Franche-Comté Reviewer Reviewer Examiner Supervisor Co-supervisor

### **ABSTRACT**

#### Energy Consumption Optimization of Parallel Applications with Iterations using CPU Frequency Scaling

Ahmed Badri Muslim FANFAKH University of Franche-Comté, 2016

Supervisors: Raphaël Couturier and Jean-Claude Charr

In recent years, green computing has become an important topic in the supercomputing research domain. However, the computing platforms are still consuming more and more energy due to the increase in the number of nodes composing them. To minimize the operating costs of these platforms many techniques have been used. Dynamic voltage and frequency scaling (DVFS) is one of them. It can be used to reduce the power consumption of the CPU while computing, by lowering its frequency. However, lowering the frequency of a CPU may increase the execution time of the application running on that processor. Therefore, the frequency that gives the best trade-off between the energy consumption and the performance of an application must be selected. This thesis, presents the algorithms developed to optimize the energy consumption and the performance of synchronous and asynchronous message passing applications with iterations running over clusters or grids. The energy consumption and performance models for each type of parallel application predicts its execution time and energy consumption for any selected frequency according to the characteristics of both the application and the architecture executing this application.

The contribution of this thesis can be divided into three parts: Firstly, optimizing the trade-off between the energy consumption and the performance of the message passing applications with synchronous iterations running over homogeneous clusters. Secondly, adapting the energy and performance models to heterogeneous platforms where each node can have different specifications such as computing power, energy consumption, available frequency gears or network's latency and bandwidth. The frequency scaling algorithm was also modified to suit the heterogeneity of the platform. Thirdly, the models and the frequency scaling algorithm were completely rethought to take into considerations the asynchronism in the communication and computation. All these models and algorithms were applied to message passing applications with iterations and evaluated over either SimGrid simulator or Grid'5000 platform. The experiments showed that the

proposed algorithms are efficient and outperform existing methods such as the energy and delay product. They also introduce a small runtime overhead and work online without any training or profiling.

**KEY WORDS:** Dynamic voltage and frequency scaling, Grid computing, Energy optimization, parallel applications with iterations and online frequency scaling algorithm.

## RÉSUMÉ

## Optimisation de la consommation énergétique des applications parallèles avec des itérations en réduisant la fréquence des processeurs

Ahmed Badri Muslim Fanfakh Université de Franche-Comté, 2016

#### Encadrants: Raphaël Couturier and Jean-Claude Charr

Au cours des dernières années, l'informatique "green" est devenue un sujet important dans le calcul intensif. Cependant, les plates-formes informatiques continuent de consommer de plus en plus d'énergie en raison de l'augmentation du nombre de noeuds qui les composent. Afin de minimiser les coûts d'exploitation de ces plates-formes de nombreuses techniques ont été étudiées, parmi celles-ci, il y a le changement de la fréquence dynamique des processeurs (DVFS en anglais). Il permet de réduire la consommation d'énergie d'un CPU, en abaissant sa fréquence. Cependant, cela augmente le temps d'exécution de l'application. Par conséquent, il faut trouver un seuil qui donne le meilleur compromis entre la consommation d'énergie et la performance d'une application. Cette thèse présente des algorithmes développés pour optimiser la consommation d'énergie et les performances des applications parallèles avec des itérations synchrones et asynchrones sur des clusters ou des grilles. Les modèles de consommation d'énergie et de performance proposés pour chaque type d'application parallèle permettent de prédire le temps d'exécution et la consommation d'énergie d'une application pour toutes les fréquences disponibles.

La contribution de cette thèse peut être divisé en trois parties. Tout d'abord, il s'agit d'optimiser le compromis entre la consommation d'énergie et les performances des applications parallèles avec des itérations synchrones sur des clusters homogènes. Deuxièmement, nous avons adapté les modèles de performance énergétique aux plates-formes hétérogènes dans lesquelles chaque noeud peut avoir des spécifications différentes telles que la puissance de calcul, la consommation d'énergie, différentes fréquences de fonctionnement ou encore des latences et des bandes passantes réseaux différentes. L'algorithme d'optimisation de la fréquence CPU a également été modifié en fonction de l'hétérogénéité de la plate-forme. Troisièmement, les modèles et l'algorithme d'optimisation de la fréquence CPU ont été complètement repensés pour prendre en

4 Résumé

considération les spécificités des algorithmes itératifs asynchrones. Tous ces modèles et algorithmes ont été appliqués sur des applications parallèles utilisant la bibliothèque MPI et ont été exécutés avec le simulateur Simgrid ou sur la plate-forme Grid'5000. Les expériences ont montré que les algorithmes proposés sont plus efficaces que les méthodes existantes. Ils n'introduisent qu'un faible surcoût et ne nécessitent pas de profilage au préalable car ils sont exécutés au cours du déroulement de l'application.

**MOTS-CLÉS:** l'ajustement dynamique de la tension et de la fréquence d'un processeur, Grille de calcul, l'optimisation de l'énergie des applications parallèles avec des itérations.

| ΑI | bstract                                           | 1  |

|----|---------------------------------------------------|----|

| Re | ésumé                                             | 3  |

| Та | able of Contents                                  | 8  |

| Li | st of Figures                                     | 11 |

| Li | st of Tables                                      | 13 |

| Li | st of Algorithms                                  | 15 |

| Li | st of Abbreviations                               | 15 |

| Li | st of Abbreviations                               | 17 |

| De | edication                                         | 19 |

| Ad | cknowledgements                                   | 21 |

| In | troduction                                        | 23 |

|    | 1. General Introduction                           | 23 |

|    | 2. Motivation of the Dissertation                 | 24 |

|    | 3. Main Contributions of this Dissertation        | 24 |

|    | 4. Dissertation Outline                           | 25 |

| ı  | Scientific Background                             | 27 |

| 1  | Parallel Architectures and Iterative Applications | 29 |

|    | 1.1 Introduction                                  | 29 |

|    | 1.2 Parallel Computing Architectures              | 30 |

|    | 1.2.1 Types of Parallel platforms                 | 33 |

|    | 1.2.2 Parallel programming Models                 | 38 |

|                                             | 1.3                                                        | Iterativ | ve Methods                                                                                                      | 40 |

|---------------------------------------------|------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|----|

| 1.3.1 Synchronous Parallel Iterative method |                                                            | 1.3.1    | Synchronous Parallel Iterative method                                                                           | 41 |

|                                             |                                                            | 1.3.2    | Asynchronous Parallel Iterative method                                                                          | 43 |

|                                             | 1.4 The energy consumption model of a parallel application |          | nergy consumption model of a parallel application                                                               | 44 |

|                                             | 1.5                                                        | Conclu   | usion                                                                                                           | 47 |

| II                                          | Cor                                                        | ntribut  | ions                                                                                                            | 49 |

| 2                                           | Ene                                                        | rgy opt  | timization of homogeneous platform                                                                              | 51 |

|                                             | 2.1                                                        | Introdu  | uction                                                                                                          | 51 |

|                                             | 2.2                                                        | Relate   | ed works                                                                                                        | 52 |

|                                             |                                                            | 2.2.1    | Offline scaling factor selection methods                                                                        | 52 |

|                                             |                                                            | 2.2.2    | Online scaling factor selection methods                                                                         | 52 |

|                                             | 2.3                                                        |          | tion time and energy consumption of parallel tasks running on a honeous platform                                | 53 |

|                                             |                                                            | 2.3.1    | Parallel tasks execution on a homogeneous platform                                                              | 53 |

|                                             |                                                            | 2.3.2    | Energy consumption model for a homogeneous platform                                                             | 54 |

|                                             | 2.4                                                        | Perfor   | mance evaluation of MPI programs                                                                                | 55 |

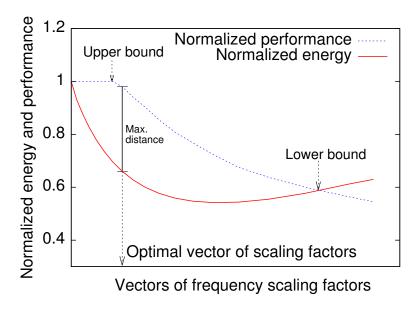

|                                             | 2.5                                                        | Perfor   | mance and energy reduction trade-off                                                                            | 55 |

|                                             | 2.6                                                        | Optima   | al scaling factor for performance and energy                                                                    | 57 |

|                                             | 2.7                                                        | Experi   | mental results                                                                                                  | 59 |

|                                             |                                                            | 2.7.1    | Performance prediction verification                                                                             | 59 |

|                                             |                                                            | 2.7.2    | The experimental results for the scaling algorithm                                                              | 59 |

|                                             |                                                            | 2.7.3    | Results comparison                                                                                              | 62 |

|                                             | 2.8                                                        | The ne   | ew energy model for a homogeneous cluster                                                                       | 63 |

|                                             | 2.9                                                        | The ex   | operimental results using the new energy model                                                                  | 65 |

|                                             | 2.10                                                       | Conclu   | usion                                                                                                           | 66 |

| 3                                           | Ene                                                        | rgy Op   | timization of Heterogeneous Platforms                                                                           | 69 |

|                                             | 3.1                                                        | Introdu  | uction                                                                                                          | 69 |

|                                             | 3.2                                                        | Relate   | ed works                                                                                                        | 70 |

|                                             | 3.3                                                        | The er   | nergy optimization of a heterogeneous cluster                                                                   | 71 |

|                                             |                                                            | 3.3.1    | The execution time of message passing distributed applications with iterations on a heterogeneous local cluster | 71 |

|                                             |                                                            | 3.3.2    | Energy model for heterogeneous local cluster                                                                    | 73 |

|                                             |                                                            | 3.3.3    | Optimization of both energy consumption and performance                                                         | 73 |

|   |     | 3.3.4          | The scaling algorithm for heterogeneous cluster                                    | . 75  |  |  |

|---|-----|----------------|------------------------------------------------------------------------------------|-------|--|--|

|   |     | 3.3.5          | The evaluation of the proposed algorithm                                           | . 78  |  |  |

|   | 3.4 | Experi         | imental results over a heterogeneous local cluster                                 | . 78  |  |  |

|   |     | 3.4.1          | The experimental results of the scaling algorithm                                  | . 79  |  |  |

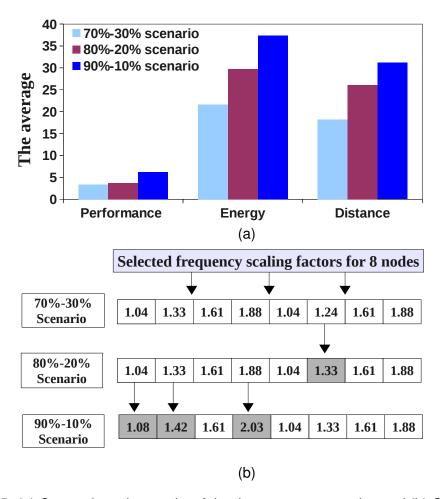

|   |     | 3.4.2          | The results for different power consumption scenarios                              | . 82  |  |  |

|   |     | 3.4.3          | Comparison between the proposed scaling algorithm and the EDP method               | . 85  |  |  |

|   | 3.5 | The er         | nergy optimization of grid                                                         | . 85  |  |  |

|   |     | 3.5.1          | The energy and performance models of grid platform                                 | . 85  |  |  |

|   |     | 3.5.2          | The scaling factors selection algorithm for a grid architecture                    | . 87  |  |  |

|   | 3.6 | Experi         | imental results over the Grid5000 platform                                         | . 90  |  |  |

|   |     | 3.6.1          | The experimental results of the scaling algorithm on a Grid                        | . 92  |  |  |

|   |     | 3.6.2          | The experimental results over multi-core clusters                                  | . 97  |  |  |

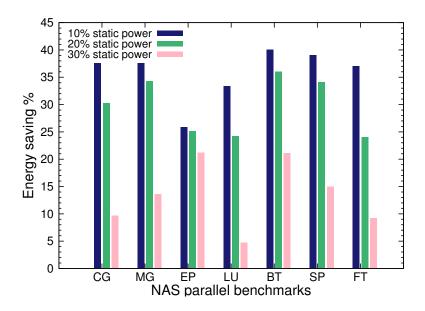

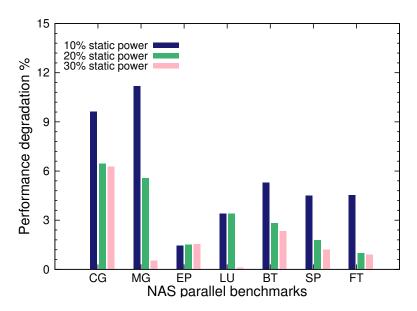

|   |     | 3.6.3          | Experiments with different static power scenarios                                  | . 100 |  |  |

|   |     | 3.6.4          | Comparison between the proposed frequencies selecting algorithm and the EDP method | . 103 |  |  |

|   | 3.7 | Conclu         | usion                                                                              | . 105 |  |  |

| 4 | Ene | rgy Op         | timization of Asynchronous Applications                                            | 107   |  |  |

|   | 4.1 | 1 Introduction |                                                                                    |       |  |  |

|   | 4.2 | Related works  |                                                                                    |       |  |  |

|   | 4.3 | The pe         | erformance and the energy consumption measurement models                           | . 109 |  |  |

|   |     | 4.3.1          | The execution time of iterative asynchronous message passing applications          | . 109 |  |  |

|   |     | 4.3.2          | The energy model and trade-off optimization                                        | . 111 |  |  |

|   | 4.4 | The so         | caling algorithm of asynchronous applications                                      | . 113 |  |  |

|   | 4.5 | The ite        | erative multi-splitting method                                                     | . 115 |  |  |

|   | 4.6 | The ex         | xperimental results over SimGrid                                                   | . 115 |  |  |

|   |     | 4.6.1          | The energy consumption and the execution time of the multi-splitting application   | . 116 |  |  |

|   |     | 4.6.2          | The results of the scaling factor selection algorithm                              | . 118 |  |  |

|   |     | 4.6.3          | Comparing the number of iterations executed by the different MS versions           | . 122 |  |  |

|   |     | 4.6.4          | Comparing different power scenarios                                                | . 123 |  |  |

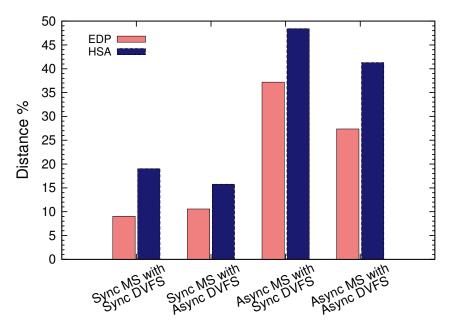

|   |     | 4.6.5          | Comparing the HSA algorithm to the energy and delay product method                 | . 125 |  |  |

|   | 4.7 | The Ex         | xperimental Results over Grid'5000                                                 | . 128 |  |  |

|    |        | 4.7.1   | Comparing the HSA algorithm to the energy and method |     |

|----|--------|---------|------------------------------------------------------|-----|

|    | 4.8    | Conclu  | usions                                               | 132 |

| Ш  | Со     | nclusi  | on and Perspectives                                  | 135 |

| 5  | Con    | clusion | n and Perspectives                                   | 137 |

|    | 5.1    | Conclu  | usion                                                | 137 |

|    | 5.2    | Perspe  | ectives                                              | 139 |

| Pι | ıblica | ations  |                                                      | 141 |

| Bi | blioc  | araphi  | e                                                    | 149 |

## LIST OF FIGURES

| 1.1  | Bit-level parallelism                                                                                            | 30 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Data-level parallelism                                                                                           | 31 |

| 1.3  | Instruction-level parallelism by pipelines                                                                       | 32 |

| 1.4  | Thread-level parallelism                                                                                         | 32 |

| 1.5  | Loop-level parallelism                                                                                           | 33 |

| 1.6  | SISD machine architecture                                                                                        | 34 |

| 1.7  | SIMD machine architecture                                                                                        | 34 |

| 1.8  | MISD machine architecture                                                                                        | 35 |

| 1.9  | MIMD machine architecture                                                                                        | 35 |

| 1.10 | Multi-core processor architecture                                                                                | 36 |

| 1.11 | Local cluster architecture                                                                                       | 37 |

| 1.12 | Grid architecture                                                                                                | 38 |

| 1.13 | The classification of the parallel Programming Models                                                            | 39 |

| 1.14 | The SISC Model                                                                                                   | 42 |

| 1.15 | The SIAC Model                                                                                                   | 42 |

| 1.16 | The AIAC Model                                                                                                   | 43 |

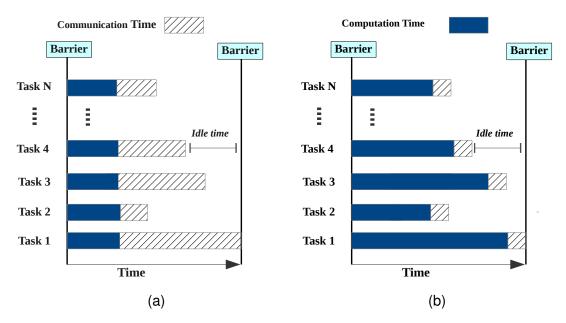

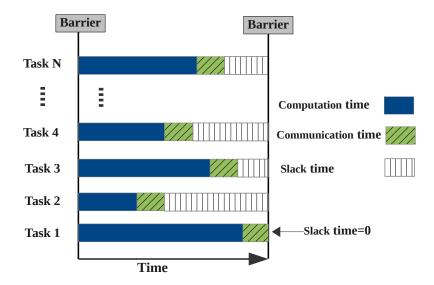

| 2.1  | Parallel tasks execution on a homogeneous platform (a) imbalanced communications and (b) imbalanced computations | 54 |

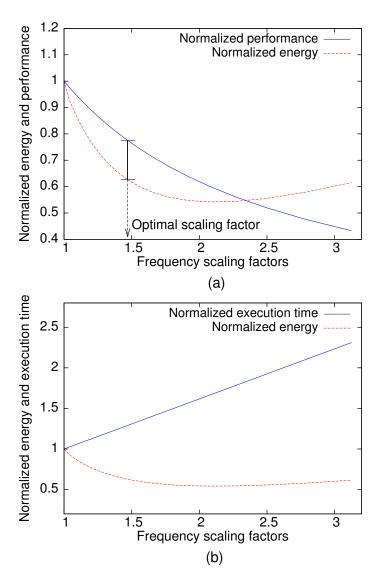

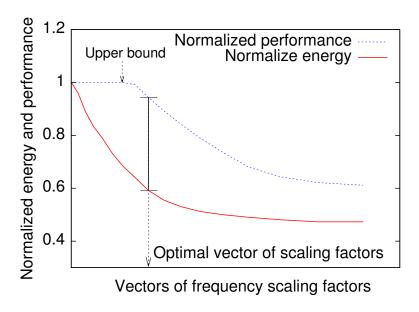

| 2.2  | The energy and performance relation (a) Converted relation and (b) Real relation                                 | 57 |

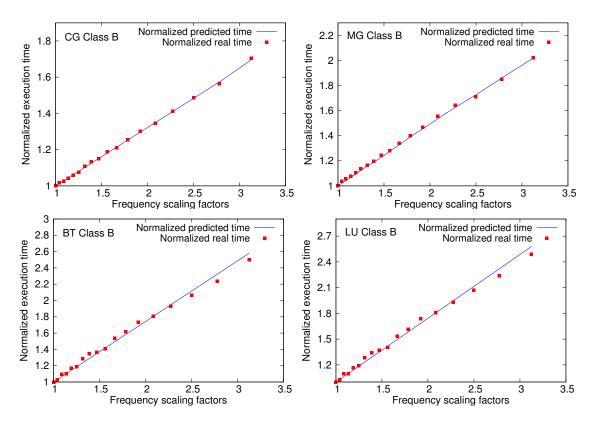

| 2.3  | Comparing predicted to real execution time                                                                       | 60 |

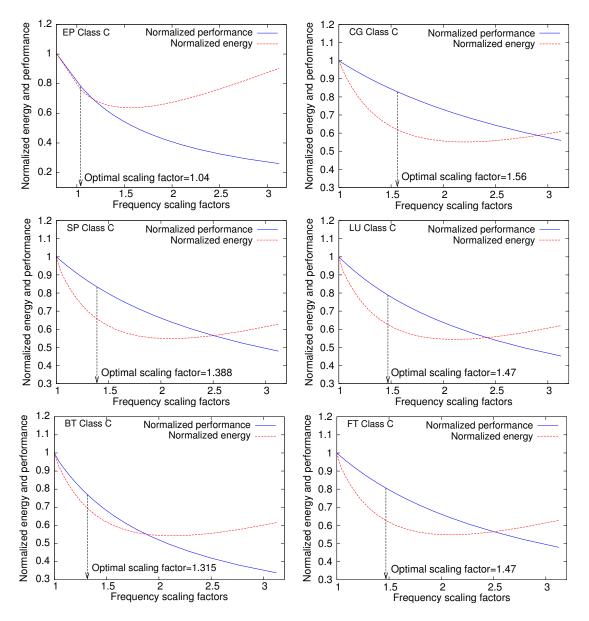

| 2.4  | Optimal scaling factors for the predicted energy and performance of NAS benchmarks                               | 61 |

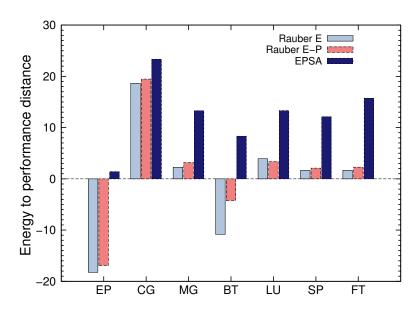

| 2.5  | Comparing our method to Rauber and Rünger's methods                                                              | 62 |

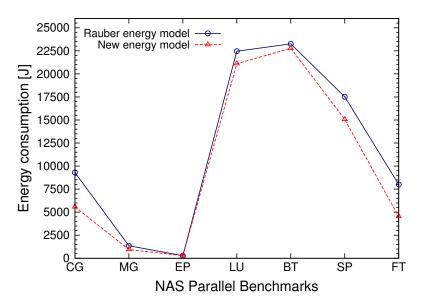

| 2.6  | Comparing the energy consumptions estimated using Rauber energy model and our own                                | 66 |

| 3.1  | Parallel tasks on a heterogeneous platform                                                                       | 72 |

| 3.2  | The energy and performance relation in heterogeneous cluster                                                     | 74 |

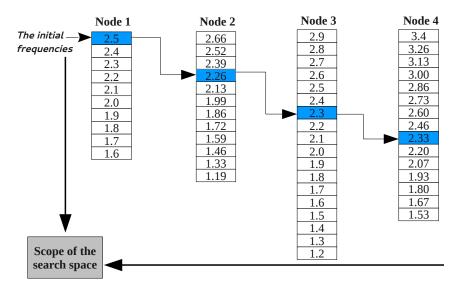

| 3.3  | Selecting the initial frequencies in heterogeneous cluster                                                       | 75 |

10 LIST OF FIGURES

| 3.4  | saving and (b) the performance degradation                                                                                                                   | 81  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.5  | (a) Comparison the results of the three power scenarios and (b) Comparison the selected frequency scaling factors of MG benchmark class C running on 8 nodes | 84  |

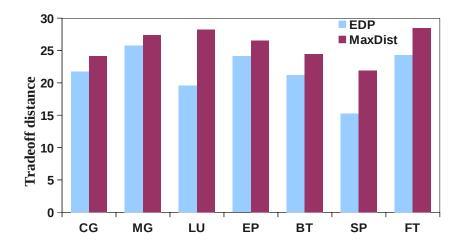

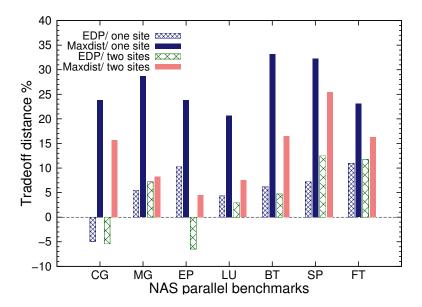

| 3.6  | Trade-off comparison for NAS benchmarks class C                                                                                                              | 84  |

| 3.7  | Selecting the initial frequencies in the grid architecture                                                                                                   | 87  |

| 3.8  | The energy and performance relation in grid                                                                                                                  | 88  |

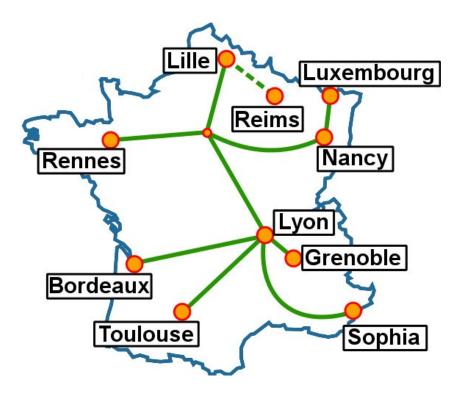

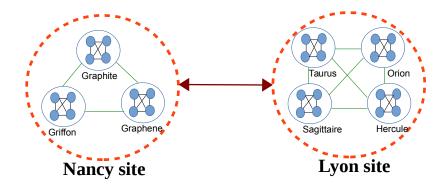

| 3.9  | Grid5000's sites distribution in France and Luxembourg                                                                                                       | 90  |

| 3.10 | The selected two sites of Grid'5000                                                                                                                          | 91  |

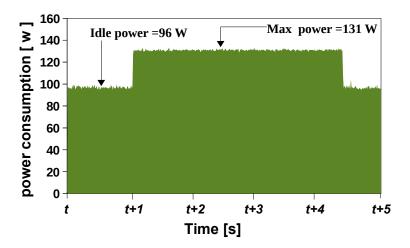

| 3.11 | The power consumed by one core from the Taurus cluster                                                                                                       | 92  |

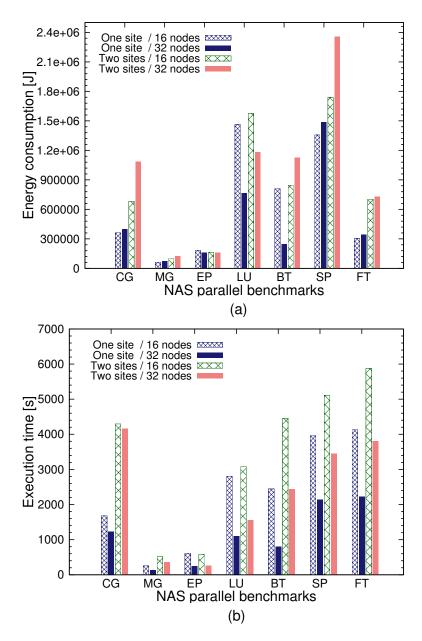

| 3.12 | (a) energy consumption and (b) execution time of NAS Benchmarks over different scenarios                                                                     | 95  |

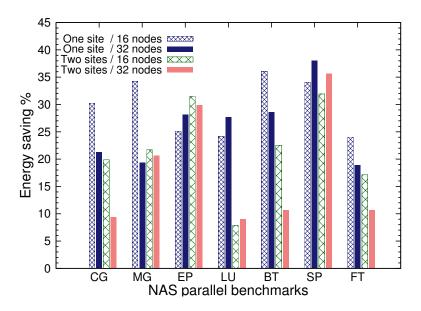

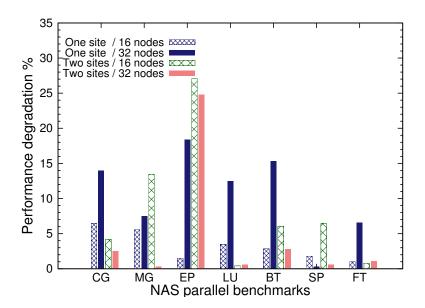

| 3.13 | The energy reduction percentages while executing the NAS benchmarks over different scenarios                                                                 | 96  |

| 3.14 | The performance degradation percentages of the NAS benchmarks over different scenarios                                                                       | 96  |

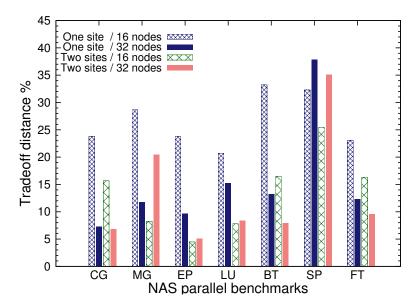

| 3.15 | The trade-off distance percentages between the energy reduction and the performance of the NAS benchmarks over different scenarios                           | 97  |

| 3.16 | The execution times of the NAS benchmarks running over the one core and the multi-core scenarios                                                             | 98  |

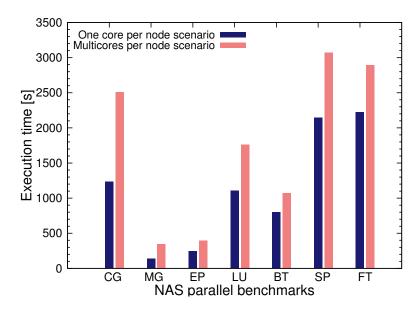

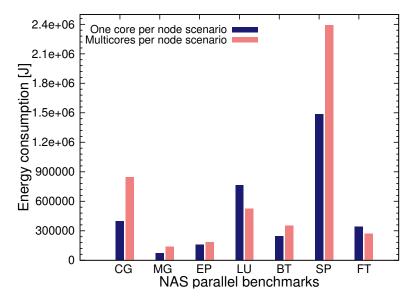

| 3.17 | The energy consumptions and execution times of the NAS benchmarks over one core and multi-core per node architectures                                        | 98  |

| 3.18 | The energy saving percentages of running NAS benchmarks over one core and multi-core scenarios                                                               | 99  |

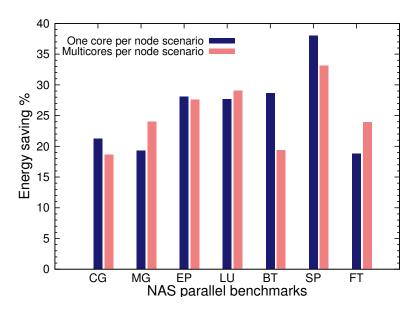

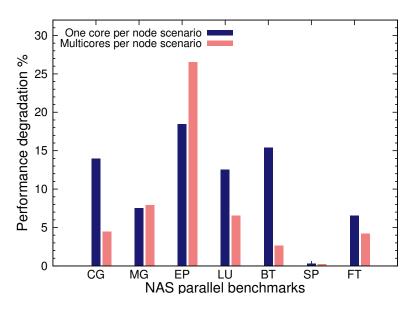

| 3.19 | The performance degradation percentages of running NAS benchmarks over one core and multi-core scenarios                                                     | 99  |

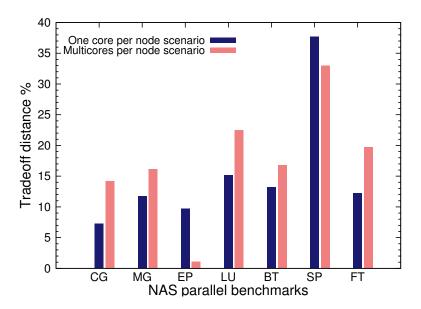

| 3.20 | The trade-off distance percentages of running NAS benchmarks over one core and multi-core scenarios                                                          | 100 |

| 3.21 | The energy saving percentages for the nodes executing the NAS benchmarks over the three power scenarios                                                      | 101 |

| 3.22 | The performance degradation percentages for the NAS benchmarks over the three power scenarios                                                                | 101 |

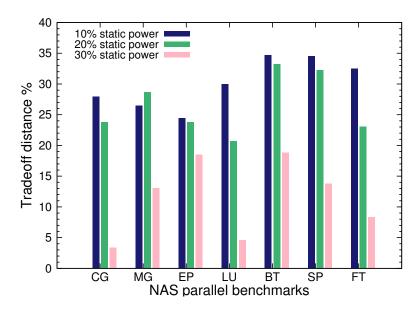

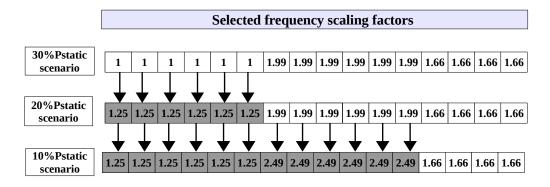

| 3.23 | The trade-off distance percentages between the energy reduction and the performance of the NAS benchmarks over the three power scenarios                     | 102 |

| 3.24 | Comparing the selected frequency scaling factors for the MG benchmark over the three static power scenarios                                                  | 102 |

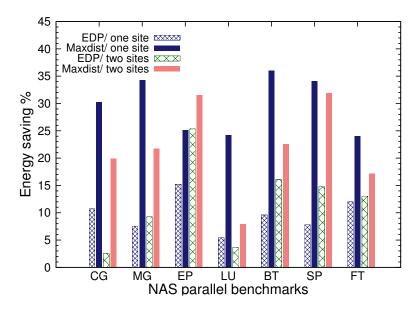

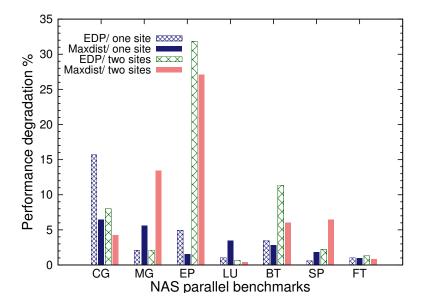

| 3.25 | The energy reduction percentages induced by the Maxdist method and the EDP method                                                                            | 104 |

| 3.26 | The performance degradation percentages induced by the Maxdist method and the EDP method                                                   | 104 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.27 | The trade-off distance percentages between the energy consumption reduction and the performance for the Maxdist method and the EDP method. | 105 |

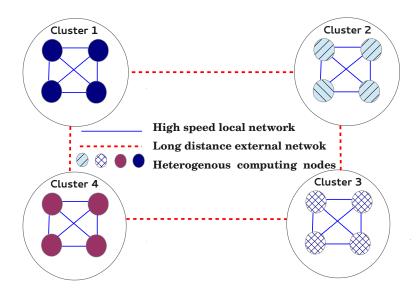

| 4.1  | A grid platform composed of heterogeneous clusters                                                                                         | 110 |

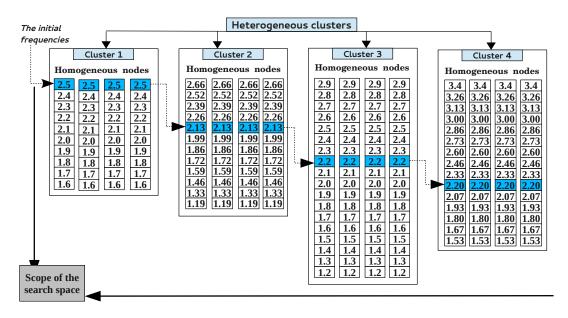

| 4.2  | Selecting the initial frequencies in a grid composed of four clusters                                                                      | 113 |

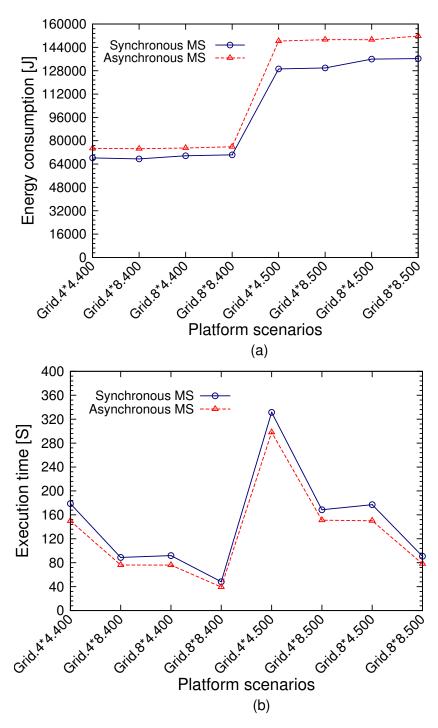

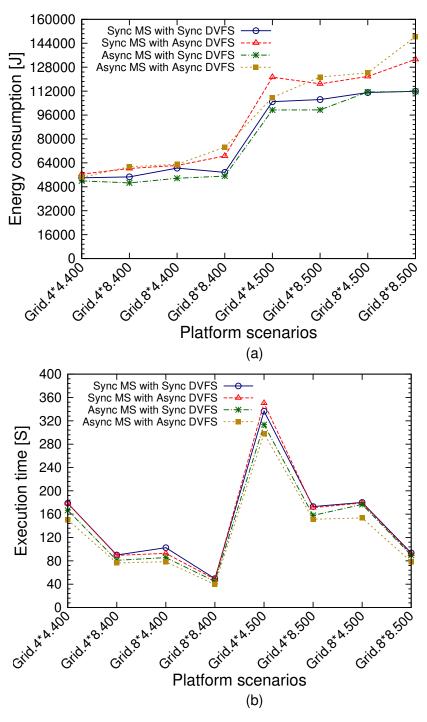

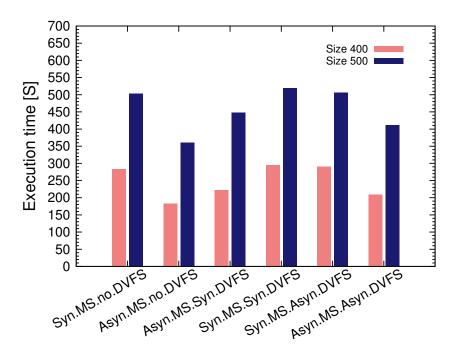

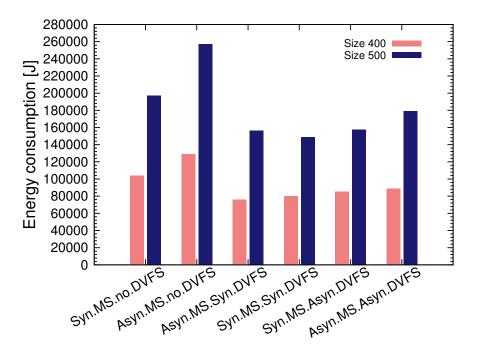

| 4.3  | (a) energy consumption and (b) execution time of multi-splitting application without applying the HSA algorithm                            | 117 |

| 4.4  | (a) energy consumption and (b) execution time of different versions of the multi-splitting application after applying the HSA algorithm    | 119 |

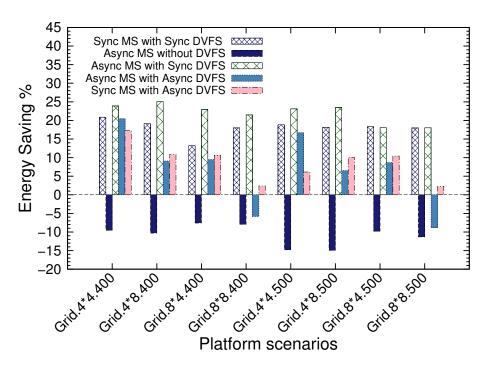

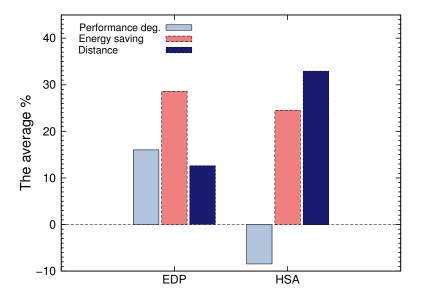

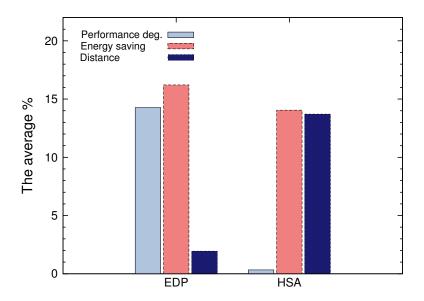

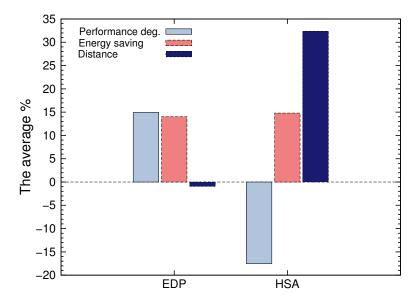

| 4.5  | The energy saving percentages after applying the HSA algorithm to the different versions and scenarios                                     | 120 |

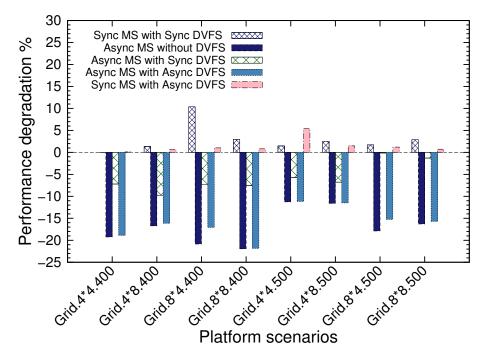

| 4.6  | The results of the performance degradation                                                                                                 | 120 |

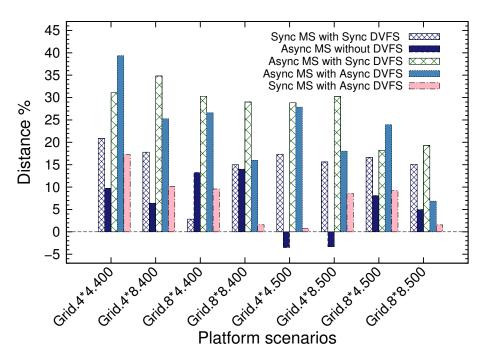

| 4.7  | The results of the tradeoff distance                                                                                                       | 121 |

| 4.8  | The results of the three power scenarios: Synchronous application of the HSA algorithm                                                     | 124 |

| 4.9  | The results of the three power scenarios: Asynchronous application of the HSA algorithm                                                    | 124 |

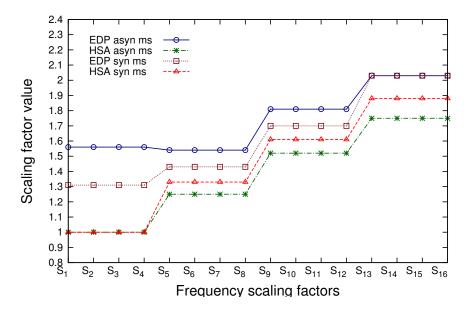

| 4.10 | Comparison of the selected frequency scaling factors by the HSA algorithm for the three power scenarios                                    | 125 |

| 4.11 | Synchronous application of the frequency scaling selection method on the synchronous MS version                                            | 126 |

| 4.12 | Synchronous application of the frequency scaling selection method on the asynchronous MS version                                           | 126 |

| 4.13 | Asynchronous application of the frequency scaling selection method on the synchronous MS version                                           | 127 |

| 4.14 | Asynchronous application of the frequency scaling selection method on the asynchronous MS version                                          | 127 |

| 4.15 | Comparison of the selected frequency scaling factors by the two algorithms over the Grid 4*4 platform scenario                             | 128 |

| 4.16 | Comparing the execution time                                                                                                               | 130 |

| 4.17 | Comparing the energy consumption                                                                                                           | 130 |

| 4.18 | Comparing the trade-off percentages of HSA and EDP methods over the Grid'5000                                                              | 132 |

## LIST OF TABLES

| 2.1  | Platform file parameters                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | NAS Benchmarks description                                                                                                       |

| 2.3  | The scaling factors results                                                                                                      |

| 2.4  | Comparing results for the NAS class C                                                                                            |

| 2.5  | The Results of NAS Parallel Benchmarks running on 16 nodes 65                                                                    |

| 3.1  | Heterogeneous nodes characteristics                                                                                              |

| 3.2  | Running NAS benchmarks on 8 and 9 nodes                                                                                          |

| 3.3  | Running NAS benchmarks on 16 nodes                                                                                               |

| 3.4  | Running NAS benchmarks on 32 and 36 nodes                                                                                        |

| 3.5  | Running NAS benchmarks on 64 nodes                                                                                               |

| 3.6  | Running NAS benchmarks on 128 and 144 nodes 80                                                                                   |

| 3.7  | The results of the 70%-30% power scenario                                                                                        |

| 3.8  | The results of the 90%-10% power scenario                                                                                        |

| 3.9  | Comparing the MaxDist algorithm to the EDP method 83                                                                             |

| 3.10 | The characteristics of the CPUs in the selected clusters                                                                         |

| 3.11 | The different grid scenarios                                                                                                     |

| 3.12 | The multi-core scenarios                                                                                                         |

| 4.1  | The characteristics of the four types of nodes                                                                                   |

| 4.2  | The different experiment scenarios                                                                                               |

| 4.3  | The standard deviation of the numbers of iterations for different asynchronous MS versions running over different grid platforms |

| 4.4  | CPUs characteristics of the selected clusters                                                                                    |

| 4.5  | The experimental results of HSA algorithm                                                                                        |

| 4.6  | The EDP algorithm results over the Grid'5000                                                                                     |

## LIST OF ALGORITHMS

| 1 | The iterative sequential algorithm                                          | 41  |

|---|-----------------------------------------------------------------------------|-----|

| 2 | The synchronous parallel iterative algorithm                                | 41  |

| 3 | Scaling factor selection algorithm for a homogeneous cluster                | 58  |

| 4 | DVFS algorithm of homogeneous cluster                                       | 58  |

| 5 | Scaling factors selection algorithm for heterogeneous cluster               | 76  |

| 6 | DVFS algorithm of heterogeneous platform                                    | 77  |

| 7 | Scaling factors selection algorithm for grid                                | 89  |

| 8 | Scaling factors selection algorithm of asynchronous applications over grid. | 114 |

#### **ABBREVIATIONS**

AIAC ..... Asynchronous Iterations and Asynchronous Communications

BLP ..... Bit Level Parallelism

BT ..... Block Tridiagonal

**CG** ...... **C**onjugate **G**radient

CPU ..... Central Processing Unit

CUDA .... Compute Unified Device Architecture

DLP ..... Data Level Parallelism

**DVFS** ..... **D**ynamic **V**oltage and **F**requency **S**caling

EDP ..... Energy and Delay Product

EP ..... Embarrassingly Parallel

EPSA .... Energy and Performance Scaling Algorithm

FLOPS ... Floating-point Operations Per Second

FT ..... Fast Fourier Transform

GMRES .. General Minimum Residual

GPU ..... Graphical Processing Unit

HSA ..... Heterogeneous Scaling Algorithm

ILP ...... Instruction Level Parallelism

LAN ..... Local Area Network

LLP ..... Loop Level Parallelism

LU ..... Lower-Upper

MaxDist .. Maximum Distance

MG ...... Multi-Grid

MIMD ..... Multiple Instruction and Multiple Data

MISD ..... Multiple Instruction and Single Data

MPI ...... Message Passing Interface

MPICH ... Message Passing Interface of Chameleon

18 abbreviations

MS ...... Multi-Splitting

NAS ..... Numerical Aeronautical Simulation

NASA .... National Aeronautics and Space Administrations

**OPENCL** . **Open C**omputing Language

**OPENMP** . **Open M**ulti-**P**rocessing

RENATER Réseau National de Télécommunications pour la Technologie,

l'Enseignement et la Recherche

SIAC ..... Synchronous Iterations and Asynchronous Communications

SIMD ..... Single Instruction and Multiple Data

SISC ..... Synchronous Iterations and Synchronous Communications

SISD ..... Single Instruction and Single Data

SP ...... Scalar Pentadiagonal

TLP ..... Thread Level Parallelism

WAN ..... Wide Area Network

### **DEDICATION**

I dedicate this dissertation to my beloved wife Dania, my children: Elias, Yasser and Mehdi. My family, your unwavering support, encouragement, and constant love throughout this Ph.D. study was incredible. My wife and children have supported me with prayers, encouraging words that gave me strength to make this dream a reality. I am truly thankful to my God for having you in my life. I love you. This dissertation has also been dedicated to my parents. From an early age, they instilled in me a desire to learn, and made sacrifices so as to I have access to a high- quality education. Without their support and guidance, I would not be where I am today. Dear Mom and Dad, I can not thank you enough for all the support and love you have given me. I know you would have been very proud of me. Thank you so much for your love. I dedicate this work as well to my brothers, sisters, and their families, whose support and encouragement helped me to follow through and not give up. I would like to extend my dedication to my friends who supported me.

#### **ACKNOWLEDGEMENTS**

The long journey of my Ph.D. study has finished. It is with great pleasure that I acknowledge my debts to those who have greatly contributed to the success of this dissertation. It was only through support and encouragement of many that I have been able to complete this amazing journey.

Foremost, I would like to express my sincere gratitude to my supervisors: Prof. Dr. Raphaël Couturier and Asst. Prof. Dr. Jean-Claude Charr for their continuous support, encouragement, and advice they have provided throughout my Ph.D. study. Their patience, motivation, enthusiasm, and immense knowledge taught me a lot. Their tireless guidance has helped me immensely in researching and writing this dissertation. I have been extremely lucky to have supervisors who cared so much about my work, and who responded to my questions and queries so promptly.

Besides my supervisors, I would like to express my gratitude to Prof. Dr. Jean-Marc Pierson and Assoc Prof. Dr. Fabienne Jézéquel (HDR) for accepting to review my dissertation and for their insightful and appreciated comments. I would like to thank also Prof. Dr. Nabil Abdennadher for accepting to participate in my dissertation committee.

I would like to gratefully acknowledge the University of Babylon, Iraq for financial support as well as I would also like to express my thanks to University of Franche-Comté for the received support.

My appreciation and thanks go to the members of the team AND (*Algorithmique Numérique Distribuée*) for the warm and friendly atmosphere in which they allowed me to work. These include Jacques Bahi, Pierre-Cyrille Héam, Abdallah Makhoul, Jean-François Couchot, Ahmed Mostefaoui, Yousra Ahmed Fadil, Pierre Saenger, Zeinab Fawaz, Amor Lalama, Nesrine Khernane, Stéphane Domas, Mohammed Bakiri, Michel Salomon, Karine Deschinkel, Christophe Guyeux, Mourad Hakem, David Laiymani, Gilles Perrot, Fabrice Ambert, Christian Salim, Santiago Costarelli, Carol Habib, Hassan Moustafa Harb and Ke Du. I would like to give a special thanks for Asst. Prof. Dr. Arnaud Giersch who helped me understand the simulation over SimGrid simulator. I would like also to thank my colleague, Dr. Ali Kadhum Idrees University of Babylon for his help. I would like to express my thanks and my best wishes to Ingrid Couturier for all the received assistance during my study.

Finally, I would like to thank all my friends and people who encouraged and supported me along the way.

### INTRODUCTION

#### 1. GENERAL INTRODUCTION

The need and the demand for more computing power have been increasing since the birth of the first computing unit and they are not expected to slow down in the coming years. To meet these demands, at first the frequency of the CPU was regularly increased until reaching the thermal limit. Then, researchers and supercomputers constructors have been regularly increasing the number of computing cores and processors in supercomputers. Many parallel and distributed architectures, such as multi-core, clusters and grids, were implemented in order to obtain more computing power. This approach consists in using at the same time many computing nodes to solve a big problem that cannot be solved on a single node. These two approaches are the most common up to now to get more computing power, but they increase the energy consumption of the resulting computing architecture. Indeed, the power consumed by a processor exponentially increases when its frequency is increased and a platform consisting of N computing nodes consumes as much as the sum of the power consumed by each computing node. As an example, the Chinese supercomputer Tianhe-2 had the highest FLOPS in November 2015 according to the Top500 list [7]. However, it was also the most power hungry platform with more than 3 million cores consuming around 17.8 megawatts. Moreover, according to the U.S. annual energy outlook 2015 [8], the price of energy for 1 megawatt per hour was approximately equal to \$70. Therefore, the price of the energy consumed by the Tianhe-2 platform is approximately more than \$10 million each year. Moreover, the platform generates a lot of heat and to prevent it from overheating a cooling infrastructure [85] which consumes a lot of energy must be implemented. High CPU's temperatures can also drastically increase its energy consumption, see [86] for more details. An efficient computing platform must offer the highest number of FLOPS per watt possible, such as the Shoubu-ExaScaler from RIKEN which became the top of the Green500 list in November 2015 [6]. This heterogeneous platform executes more than 7 GFlops per watt while only consuming 50.32 kilowatts.

For all these reasons energy reduction has become an important topic in the high performance computing (HPC) field. To tackle this problem, many researchers use DVFS (Dynamic Voltage and Frequency Scaling) operations which reduce dynamically the frequency and voltage of cores and thus their energy consumption [69]. Indeed, modern CPUs offer a set of acceptable frequencies which are usually called gears, and the user or the operating system can modify the frequency of the processor according to its needs. However, DVFS reduces the number of FLOPS executed by the processor which may increase the execution time of the application running over that processor. Therefore researchers try to reduce the frequency to the minimum when processors are idle (waiting for data from other processors or communicating with other processors). Moreover, depending on their objectives, they use heuristics to find the best frequency scaling factor during the computation. If they aim for performance they choose the best frequency

24 Introduction

scaling factor that reduces the consumed energy while affecting as little as possible the performance. On the other hand, if they aim for energy reduction, the chosen frequency scaling factor must produce the most energy efficient execution without considering the degradation of the performance. Whereas, it is important to notice that lowering the frequency to the minimum value does not always give the most energy efficient execution due to energy leakage that increases the total energy consumption of the CPU when the execution time increases. However, a more important question is how to select the best frequency gears that minimize the total energy consumption and the maximize the performance of a parallel application, running over a parallel platform, at the same time?

#### 2. MOTIVATION OF THE DISSERTATION

The main objective of an HPC system such as clusters, grids and supercomputers is to execute as fast as possible a given task over that system. Hence, using DVFS to scale down the frequencies of the CPUs composing the system to reduce their energy consumption, it can also significantly degrade the performance of the executed program, especially if it is compute bound. A compute bound program contain a lot of computations and a relatively small amount of communicators and Inputs/Outputs operations. The execution time of the program is directly dependent on the computing powers of the CPUs and their selected frequencies. Therefore, the chosen frequency scaling factor must give the best possible trade-off between the energy reduction and the performance of the parallel application.

On the other hand, the relation between energy consumption and the execution time of parallel applications is complex and non-linear. It is very hard to optimize both the energy consumption and the performance of parallel applications when scaling the frequency of the processors executing them because one affects the other. In order to evaluate the impact of scaling down the CPU's frequency on its energy consumption and computing power, mathematical models should be defined to predict them for different frequencies.

Furthermore, researchers use different optimization strategies to select the frequencies of the CPUs. They might be executed during the execution of the application (online) or during a pre-execution phase (offline). In our opinion a good approach should minimize the energy consumption while preserving the performance at the same time. Finally, it should also be applied to the application during its execution without requiring any training or profiling and with minimal overhead.

#### 3. Main Contributions of this Dissertation

The main objective of this work is to minimize the energy consumption of parallel applications with iterations running over clusters and grids while preserving their performance. The main contributions of this work can be summarized as follows:

I) Energy consumption and performance models for synchronous and asynchronous message passing applications with iterations were developed. These models take into consideration both the computation and communications times of these applications in addition to their relation to the frequency scaling factors. Introduction 25

II) The parallel applications with iterations were executed over different parallel architectures such as: homogeneous local cluster, heterogeneous local cluster and distributed clusters (grid platform). The main goal behind using these different platforms is to study the effect of the heterogeneity in the computing powers of the the commuting nodes and the heterogeneity in the communication networks which connect these nodes on the energy consumption and the performance of parallel applications with iterations.

- III) Depending on the proposed energy consumption and the performance models, a new objective function to optimize both the energy consumption and the performance of the parallel applications with iterations at the same were defined. It computes the maximum distance between the predicted energy consumption and the predicted performance curves to define the best possible trade-off between them.

- **IV)** New online frequency selecting algorithms for clusters and grids were developed. They use the new objective function and select the frequency scaling factors that simultaneously optimize both the energy consumption and performance. They have a very small overhead when comparing them to other methods in the state of the art and they work without training and profiling.

- V) The proposed algorithms were applied to the NAS parallel benchmarks [57] and the Multi-splitting method. These applications offer different computations to communications ratios and a good testbed to evaluate the proposed algorithm in different scenarios.

- VI) The proposed algorithms were evaluated over the SimGrid simulator [18] which offers flexible and easy tools to built different types of parallel architectures. Furthermore, real experiments were conducted over Grid'5000 testbed [3] and compared with the simulated ones. The experiments were conducted over different number of nodes and different platform scenarios.

- **VII)** All the proposed methods were compared with either Rauber and Rünger [66] method or Spiliopoulos et al. [75] objective function. Both the simulation and real experiments showed that the proposed methods give better energy to performance trade-offs than the other methods.

#### 4. DISSERTATION OUTLINE

The dissertation is organized as follows: chapter 1 presents different types of parallel architectures and parallel applications with iterations. It also presents an energy consumption model from the state of the art that can be used to measure the energy consumption of these applications. Chapter 2 describes the proposed energy and performance optimization method for synchronous applications with iterations running over homogeneous clusters. Chapter 3 presents two algorithms for the energy and performance optimization of synchronous applications with iterations running over heterogeneous clusters and grids. In chapter 4 the energy and performance models and the optimization method are adapted for asynchronous iterative applications running over grids. Finally, this dissertation ends with a summary and some perspective works.

## SCIENTIFIC BACKGROUND

## PARALLEL ARCHITECTURES AND ITERATIVE APPLICATIONS

#### 1.1/ Introduction

Most of the software applications are structured as sequential programs. The structure of the program code is a series of instructions that are executed successively one after the other. For many years until a short time, with each new generation of microprocessors, users of sequential applications expected that these applications should run faster over them than over the previous ones. Nowadays, this idea is no longer valid since recent releases of microprocessors have many computing units that are embedded in one chip and programs are running only over one computing unit sequentially. Indeed, new applications have significantly improved their performance over new architectures in parallel compared to traditional applications. To improve the performance of applications, they should be parallelized and executed simultaneously over all available computing units. Moreover, parallel applications should be optimized to the parallel hardwares that will execute them. Therefore, parallel applications and parallel architectures are closely tied together. For example, the energy consumption of one parallel system mainly depends on both: (1) parallel applications and (2) parallel architectures. Indeed, an energy consumption model or any measurement system depends on many specifications, some of them are related to the parallel hardware features such as: (1) the frequency of processor, (2) the power consumption of processor and (3) the communication model. Others rely to the parallel application such as: (1) the computation time and (2) the communication time of the application.

This work of this thesis is focused on studying the iterative parallel applications, where different parallel architectures are used to execute them in parallel, while optimizing their energy consumptions. In this context, this chapter gives a brief overview about parallel hardware architectures and parallel iterative applications. Also, it discusses an energy model proposed by other authors used to measure the energy consumption of these applications. The reminder of this chapter is organized as follows: section 1.2 describes different types of parallelism and different types of parallel platforms. It also explains some models of parallel programming. Section 1.3 discusses both types of parallel iterative methods, synchronous and asynchronous ones and comparing them. Section 1.4, presents a well accepted energy model from the state of the art that can be used to measure the energy consumption of parallel iterative applications when the frequency of processor is changed. Finally, section 1.5 summarizes this chapter.

#### 1.2/ PARALLEL COMPUTING ARCHITECTURES

The process of executing the calculations simultaneously over many computing units is called parallel computing. Its main principle refers to the ability of dividing a large problem into smaller sub-problems that can be solved at the same time [9]. Solving the sub-problems of one main problem in parallel is carried out in parallel on multiple processors. Indeed, a parallel architecture can be defined as a computing system that is composed of many processing elements, which are connected via a network model and some tools that are used to make the processing units work together [31]. In other words, the parallel computing architecture consists of software and hardware resources. Hardware resources are: (1) the processing units, (2) the memory model and (3) the network system that connects them. Software resources include (1) the specific operating system, (2) the programming language and (3) the compile or the runtime libraries. Besides, parallel computing may have different levels of parallelism that can be performed in a software or a hardware level. Five types of parallelism levels have been defined as follows:

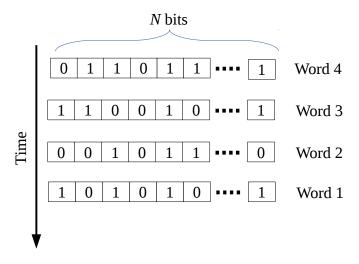

• Bit-level parallelism (BLP): The appearance of very-large-scale integration (VLSI) in 1970s has been viewed as the first step towards parallel computing. It is used to increase the number of bits in the word size which is processed by a processor as illustrated in the figure 1.1. For many successive years, the number of bits have been increased starting from 4 bit to 64 bit microprocessors. For example nowadays, the recent x86-64 architecture is the most common architecture. For a given application, the biggest the word size is the lesser instructions to be executed by the processor.

Figure 1.1: Bit-level parallelism

Data-level parallelism (DLP): Data parallelism is the process of distributing data vector between processors, where each one performs the same operations on its data sub-vector. Therefore, many arithmetic operations can be performed on the same data vector in a simultaneous manner. This type of parallelism can be used in many programs, especially in the area of scientific computing. Usually, data-parallel operations are only provided to arrays operations, for example, as shown in figure

11 5 8 21 8 0 2 4 6 12 19 Input vector A 3 5 13 | 11 Input vector B 13 | 14 Input vector C 5 9 3 10 | 18 | 0 9 12 7 18 20 15 PU<sub>1</sub> PU<sub>2</sub> PU<sub>3</sub> Results

1.2. Vector multiplication, image and signal processing can be considered as an example of applications that use this type of parallelism.

Figure 1.2: Data-level parallelism

All the processors doing the same operations

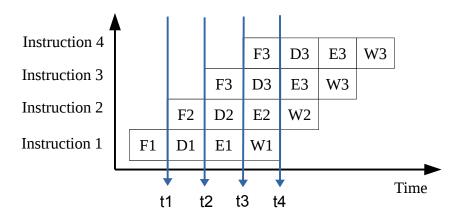

- Instruction-level parallelism (ILP): Generally, a sequential program is composed of many instructions. These instructions can be executed in parallel at the same time, if each one of them is independent from the others. In particular, the parallelism can be achieved in instruction level by using a pipeline. It means the input and output times of each instruction is overlapped by computations from other instructions. For example, if we have two instructions:  $I_1$  and  $I_2$ , they are independent if there is no control and no data dependency between them. In pipeline stages, the execution of each instruction is divided into multiple steps. Then, they can be overlapped with the steps of other instructions by a pipeline hardware unit. Figure 1.3 demonstrates four instructions, where each one has four steps denoted as: (1) fetch, (2) decode, (3) execute and (4) write. Thus, they are implemented in hardware units by pipeline.

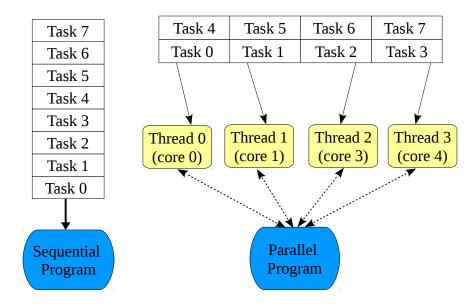

- Thread-level parallelism (TLP): It is also known as task-level parallelism. According to Moore's law [17], the number of transistors in a processor doubles each two years to increase its performance. Cache and main memory sizes must also be increased in order to avoid data bottlenecks. However, increasing the number of transistors may generate some issues: (1) the first issue is related to drastically increase in cache size, which leads to a large access time. (2) the second issue is related to the huge increase in the number of the transistors per CPU, which can increase significantly the heat dissipation. Thus, CPUs constructors couldn't increase the frequency of the processor anymore due to these reasons. Therefore, they created multi-core processors. With multi-core processors, programmers subdivide their programs into multiple tasks which can be then executed in parallel over

Figure 1.3: Instruction-level parallelism by pipelines

them to improve the performance, see figure 1.4. Each processor can have individual threads or multiple threads dedicated to each task. A thread can be defined as a part of the parallel program that shares processor resources with other threads.

Figure 1.4: Thread-level parallelism

Therefore, the execution time of a sequential program that is composed of N tasks, is the sum of the execution times of all tasks. Thus, it is expressed as follows:

Sequential execution time =

$$\sum_{i=1}^{N} T_i$$

(1.1)

Whereas, if tasks are executed synchronously over multiple processing units in parallel, the execution time of the program is defined as the execution time of the task that has maximum the execution time (the slowest task) as follows:

Parallel execution time =

$$\max_{i=1,...,N} T_i$$

(1.2)

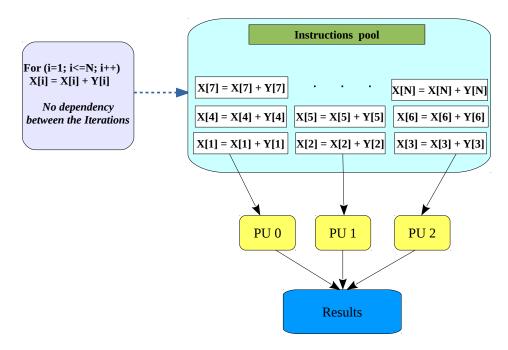

• Loop-level parallelism (LLP): Many algorithms execute iteratively the same program portion, computations, many times using different forms of loop statements. At each iteration, the program needs to scan a large data structure such as an array structure to perform the arithmetic calculations. Inside the loop structure, there are many instructions that are dependent or independent. In a sequential loop execution, the *i* iteration must be executed after the completion of the (*i* – 1) iteration. If each iteration is independent from the others, then all iterations' instructions can be distributed over many processors to be executed in parallel, for example, see figure 1.5. In the parallel programming languages, this type of loop is called the parallel loop.

Figure 1.5: Loop-level parallelism

The execution time of the parallel loop portion can be computed as the execution time of a sequential loop portion has  $N_{iter}$  iterations divided by the number of the processing units  $N_{processors}$  as follows:

Parallel loop time =

$$\frac{S \text{ equential loop time}}{N_{processors}} = \frac{\sum_{i=1}^{N_{iter}} T \text{ ime of iter}_i}{N_{processors}}$$

(1.3)

For more details about the levels of parallelism see [67, 61, 38, 62].

#### 1.2.1/ Types of Parallel Platforms

The main goal behind using a parallel architecture is to solve a big problem faster. A collection of processing elements must work together to compute the final solution of the main problem. Many different architectures have been proposed and classified according

to parallelism in instruction and data streams. In 1966, Michel Flynn has proposed a simple model to categorize all computers models that is still useful until now [33]. His taxonomy is based on considering the data and the operations performed on this data to classify the computing systems into four types as follows:

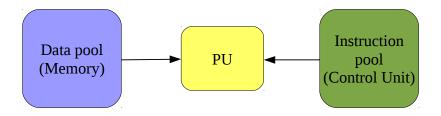

• Single instruction, single data (SISD) stream: A single processor that executes a single instruction stream (i.e executing one data stream stored in an individual memory model, see figure 1.6). The conventional sequential computer, according to Von Neumann model [80], also called the Uniprocessors can be viewed as an example of this type of architecture.

Figure 1.6: SISD machine architecture

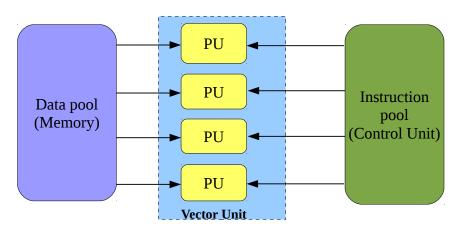

• Single instruction, multiple data (SIMD) stream: All processors execute the same instructions on different data. Each processor stores the data in its local memory. Then, they communicate with each others typically via a simple communication model, see figure 1.7. Many scientific and engineering applications are referred to this type of parallel scheme. Vector and array processors are well known examples of this type. Examples about the applications executed over this architecture: (1) graphics processing, (2) video compression and (3) medical image analysis applications.

Figure 1.7: SIMD machine architecture

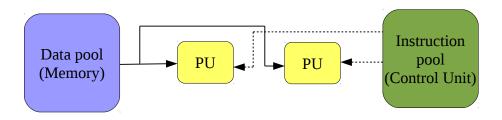

• Multiple instruction, single data (MISD) stream: Many operations from multiple processing elements are executed over the same data stream. Each processing

element has its local memory to store the private program instructions. Then, these instructions are applied to unique global memory data stream as in figure 1.8. While the MISD machine is not commonly used, there are some interesting uses such as the systolic arrays and dataflow machines.

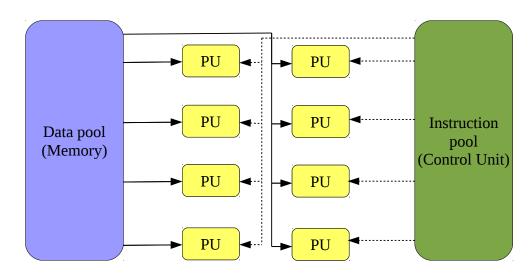

Figure 1.8: MISD machine architecture

• Multiple instruction, Multiple data (MIMD) stream: There are multiple processing elements, each one has a separate instruction and local data memories. At any time, different processing elements may be used to execute different instructions on different data fragment, see figure 1.9. There are two types of MIMD machines: the shared memory and the message passing MIMD machines. In the former, processors communicate via a shared memory model, while in the latter, each processor has its own local memory and all processors communicate with each others via a communication network model. The multi-core processors, local clusters and grid systems are some examples for MIMD machine. Many applications have been developed based on this architecture such as computer-aided design, computer-aided manufacturing, simulation, modeling, iterative applications and so on.

Figure 1.9: MIMD machine architecture

For more details about this architectural taxonomy see [42, 76, 60, 27].

The work of this thesis is dedicated to MIMD machine's architecture. Therefore, we discuss in this chapter some of the commonly used parallel architectures that belong to MIMD machines. As explained before, MIMD architectures can be classified into two types, the shared memory and the distributed message passing ones. Furthermore, these classifications are based on how MIMD processors access the memory model. The shared MIMD machine communication topology can be bus-based, extended or hierarchical type. Whereas, the distributed memory MIMD machine may have hypercube or mesh interconnected networks. In the following some well known MIMD parallel computing platforms are explained:

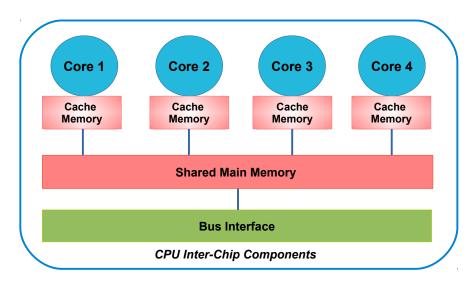

• Multi-core processors: The multi-core processor is a single chip component with two or more processing units. These processing units are called cores, which are connected to each other via a main memory model as in the figure 1.10. Each individual core has its own cache memory to store data. Moreover, each core may have one or more threads to execute a specific programming task as shown in the thread-level parallelism. Historically, the multi-cores of the CPU began as two-core processors, then the number of cores doubled with each semiconductor process generation [46]. The graphic processing units (GPU) use extensively the multi-core architecture, the NVIDIA GeForce TITAN Z has 5700 cores in the year of 2015 [2]. While, in the same year a general-purpose microprocessor (CPU) has a lot less cores, for example the TILE-MX processor from Tilera has 100 cores [4]. For more details about the multi-core processors see [64].

Figure 1.10: Multi-core processor architecture

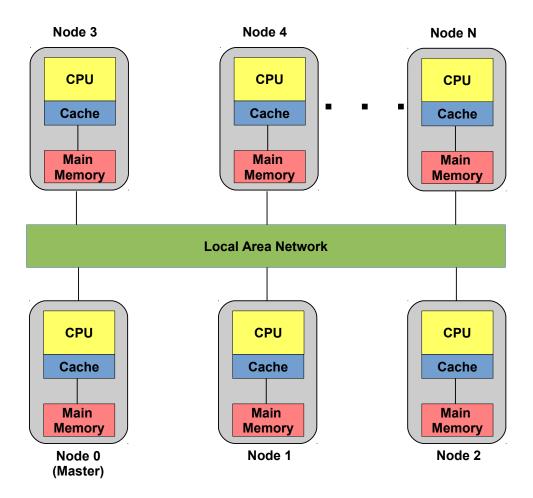

• Local Cluster: is a collection of independent computers that are connected to each other via a high speed local area network (LAN) with low latency and big bandwidth. Moreover, each node communicates with other nodes using messages. All the nodes in the cluster must be controlled by one node called the master node, which is a specific node used to handle the scheduling and the management of the other nodes as shown in the figure 1.11. Usually, all the nodes are homogeneous, they have the same specifications in term of computing power and memory. Also, all the computing nodes in the cluster run the same operating system. See [84, 53] for more information about the cluster and its applications.

Figure 1.11: Local cluster architecture

• Grid (Distributed clusters): Grid is a collection of computing clusters from different sites that are connected via a wide area network (WAN). In particular, different local clusters compose the grid are geographically located far away from each others. Usually, each cluster is composed of homogeneous nodes, which are different from nodes of the other clusters located in different sites. These nodes can be different in their hardware and software specifications (i.e their computing power, their memory size, their operating system and their network: latency and bandwidth). Figure 1.12 presents an example of a grid that is composed of three heterogeneous clusters that are located in different sites and connected via a wide area network. Furthermore, the grid can refer to an infrastructure that applies the integration and the collaboration by using a collection of different computers, networks, database servers and scientific devices, which belong to many companies and universities. Therefore, wide heterogeneous computing resources are available to be used simultaneously by different users. Note that, the main bottleneck of the grid is the high latency communications between the nodes from different sites. See [54] for more information about the grid and its applications.

Figure 1.12: Grid architecture

#### 1.2.2/ Parallel programming Models

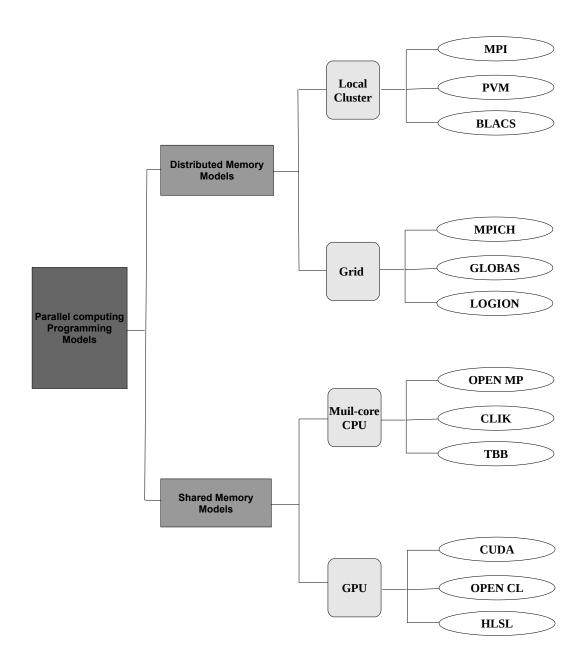

Many parallel programming languages and libraries have been developed to explore the computing power of the parallel architectures. In this section, two types of parallel programming languages are investigated: (1) shared and (2) distributed programming models. Moreover, each type is divided into two subcategories according to their supporting level for the number of computing units from which the parallel platform is composed. Figure 1.13 presents this classification hierarchy of the parallel programming models.

Many programming interfaces and libraries have been developed to compile and run the parallel applications over the parallel architectures. In the following, some examples for each type of the parallel programming models are discussed:

#### Local cluster programming models

MPI [39] is the Message Passing Interface and it is considered as a standard-ization dedicated to message passing in a distributed memory environment. The first version of MPI was designed by a group of researchers in 1991. It is a specification and have been implemented in many programming languages such as C, Fortran and Java. The MPI functions are not only limited to point to point operations for sending and receiving messages, there are many others collective operations such as gathering and reduction operations. While MPI is not designed for grid, it is widely used as the communication interface for grid applications [16]. In this work, MPI was used in programming our algorithms and applications which are implemented in both Fortran and C programming languages.

Figure 1.13: The classification of the parallel Programming Models

#### • Multi-core CPU programming models

OpenMP [19] is a parallel programming tool dedicated to shared memory architectures. The main goal of using this programming model is to provide a standard and portable API (application programming interface) to write shared memory parallel programs. It can be used with many programming languages such as C, C++ and Fortran in order to support different types of shared memory platforms such as multi-core processors. OpenMP uses multi-threading, which is a model in parallel programming that uses a master thread to control a set of slave threads. Each thread can be executed in parallel by assigning it to a processor. Moreover, OpenMP can be used with MPI to support hybrid

platforms which have shared and distributed memory models at the same time.

#### • GPU programming models

- CUDA [26] Modern graphical processing units (GPUs) have increased its chip-level parallelism. Current NVIDIA GPUs consist of many-cores processors that have thousands of cores. To make their GPUs a general purpose computing processor in 2007 the NVIDIA has developed CUDA a parallel programming language. A CUDA program has two parts: host and kernels. The host code is sequentially executed over the CPU. While, the kernels are executed in parallel over the GPUs.

- OpenCL[78] is for Open Computing Language. It is a parallel programming language dedicated for heterogeneous platforms composed of CPUs and GPUs. The first release of this language has initially been developed by Apple in 2008. Functions that are executed over OpenCL devices are called kernels. They are portable and can be executed on any computing hardware such as CPU or GPU cores.

#### 1.3/ ITERATIVE METHODS

In this work, we are interested in solving system of linear equations which are very common in the scientific field. A system of linear equations can be expressed as follows:

$$Ax = b ag{1.4}$$

Where A is a two dimensional matrix of size  $N \times N$ , x is the unknown vector, and b is a vector of constant, each of size N. There are two types of solution methods to solve this linear system: the **direct** and the **iterative methods**. A direct method executes a finite number of steps, depending on the size of the linear system and gives the exact solution of the system. If the problem is very big, this method is expensive or its solution is impossible in some cases. On the other hand, methods with iterations execute the same block of instructions many times. The number of iterations can be predefined or the application iterates until a criterion is satisfied. Iterative methods are methods with iterations that start from an initial guess and improve successively the solution until reaching an acceptable approximation of the exact solution. These methods are well adapted for large systems and can be easily parallelized.

A sequential iterative algorithm is typically organized as a series of steps essentially of the form:

$$X^{(k+1)} \longleftarrow F(X^k) \tag{1.5}$$

Where F is one or set of operations applied to the data vector  $X^k$  to produce the new data vector  $X^{(k+1)}$ . The operation F is applied sequentially many times until satisfying the convergence condition as in the algorithm 1.

The sequential iterative algorithm at each iteration computes the value of the relative error, which is called the residual and denoted as R. This error value can be computed

#### Algorithm 1 The iterative sequential algorithm

```

1: Initialize the vector X^0 randomly

```

- 2: **for** k := 1 to convergence **do**

- 3:  $X^{(k+1)} = F(X^k)$

- 4: end for

as the maximum difference between the data components of the vectors of the last two successive iterations as follows:

$$R = \max_{i=1,\dots,N} \left| X_i^{(k+1)} - X_i^k \right| \tag{1.6}$$

Where N is the size of the vector X. Then, the iterative sequential algorithm stops iterating if the maximum error between the last two successive solution vectors, as in 1.6, is less than or equal to a threshold value. Otherwise, it replaces the new vector  $X^{(k+1)}$  with the old vector  $X^k$  and computes a new iteration.

#### 1.3.1/ Synchronous Parallel Iterative method

The sequential iterative algorithm 1 can be parallelized by executing it on many computing units. To solve this algorithm on M computing units, first the elements of the problem vector X must be subdivided into M sub-vectors,  $X^k = (X_1^k, \ldots, X_M^k)$ . Each sub-vector can be solved independently on one computing unit as follows:

$$X_i^{k+1} = F_i(X_1^k, \dots, X_M^k)$$

where  $i = 1, \dots, M$  (1.7)

Where  $X_i^k$  is the sub-vector executed over the  $i^{th}$  computing unit at the iteration k.

#### Algorithm 2 The synchronous parallel iterative algorithm

```

1: Initialize the sub-vectors (X_1^0, \dots, X_M^0)

2: for k := 1 step 1 to convergence do

3: parfor i := 1 to M do

4: X^{(k+1)} = F(X^k)

5: end parfor

```

6: end for

The algorithm 2 represents the synchronous parallel iterative algorithm. Similarly to the sequential iterative algorithm 2, this algorithm stops iterating when the convergence condition is satisfied. We consider that the keyword **parfor** is used to make a for loop in parallel.

This algorithm needs to satisfy a convergence condition which is called the global convergence condition. In order to detect the global convergence overall computing units, first we need to compute at each iteration the local residual. Then at the end of each iteration, all the local residuals from M computing units must be reduced to one maximum value represented by the global residual. For example, in MPI this operation is directly applied using a high level communication procedure called AllReduce. The goal of this communication procedure is to apply the reduction operation on all local residuals computed by the computing units.

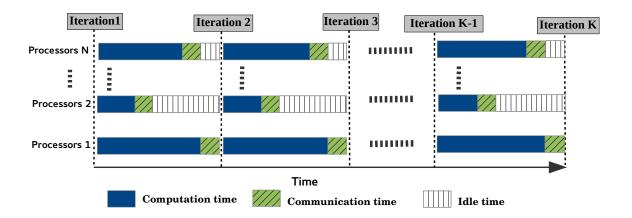

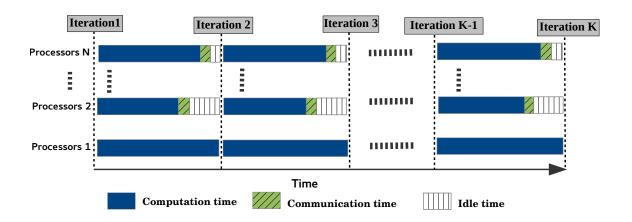

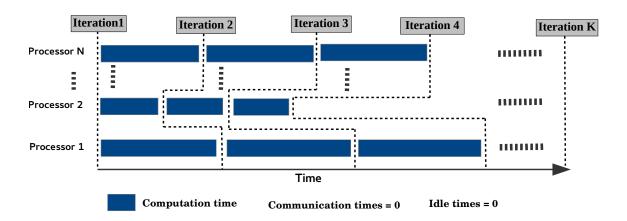

Figure 1.14: The SISC Model

In a synchronous parallel iterative algorithm, computing processors need to communicate with each others to exchange data at each iteration if there is a dependency between the parallel tasks. Algorithm 2 use synchronous iterations and synchronous communications denoted as **SISC** model. At each iteration, the computing processor waits until it receives all the computed data at the previous iteration from other processors to perform the next iteration. Figure 1.14, shows that using SISC model in a heterogeneous platform may result in big periods of the idle times represented by the white dashed spaces between two successive iterations. Indeed, this happens when the fast computing processors wait for the slower ones to finish their iterations to be able to synchronously send their data to them. Using this operation, faster processors waste a big amount of their computing power and thus consume uselessly energy. The increase in the heterogeneity in the computing powers between the processors may increase proportionally these idle times. Accordingly, this algorithm can be effectively run over a local cluster, where a high speed local network is used to reduce these idle times.

Figure 1.15: The SIAC Model

Furthermore, the communications of the synchronous iterative algorithm can be replaced by asynchronous ones. The resulting algorithm is called Synchronous Iterations

with Asynchronous Communications and denoted as **SIAC** algorithm. The main principle of this algorithm is to use synchronize iterations while exchanging the data between the computing units asynchronously. Moreover, each computing unit does not need to wait for its neighbours to receive the data messages that it has sent, while it only waits to receive data from them. This can be implemented with SISC algorithm that is programmed in MPI by replacing the synchronous send of the messages by asynchronous ones, while keeping the synchronous receive. The only advantage of this technique is to reduce the idle times between iterations by allowing the communications to overlap partially with computations, see figure 1.15. The idle times are not totally eliminated because the fast computing nodes must wait for slow ones to send their data messages. SISC and SIAC algorithms are not tolerant to the loss of data messages. Consequently, if one node crashes, all the other computing nodes are blocked.

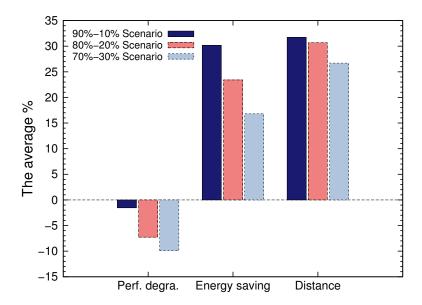

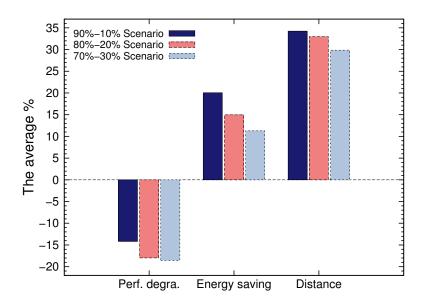

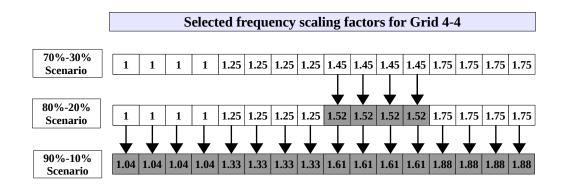

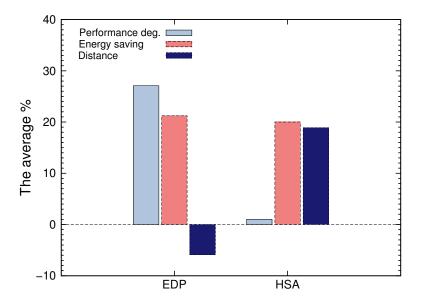

#### 1.3.2/ ASYNCHRONOUS PARALLEL ITERATIVE METHOD