# Methods and tools for rapid and efficient parallel implementation of computer vision algorithms on embedded multiprocessors

Vítor Schwambach

## ▶ To cite this version:

Vítor Schwambach. Methods and tools for rapid and efficient parallel implementation of computer vision algorithms on embedded multiprocessors. Computer Vision and Pattern Recognition [cs.CV]. Université Grenoble Alpes, 2016. English. NNT: 2016GREAM022. tel-01523273

## HAL Id: tel-01523273 https://theses.hal.science/tel-01523273

Submitted on 16 May 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE ALPES

Spécialité: Informatique

Arrêté ministériel du 7 août 2006

Présentée par

## Vítor Schwambach

Thèse dirigée par **Stéphane Mancini** et codirigée par **Sébastien Cleyet-Merle et Alain Issard**

préparée au sein du

Laboratoire TIMA et STMicroelectronics

et de l'École Doctorale

Mathématiques, Sciences et Technologies de l'Information, Informatique

(EDMSTII)

## Methods and Tools for Rapid and Efficient Parallel Implementation of Computer Vision Algorithms on Embedded Multiprocessors

Thèse soutenue publiquement le 30/03/2016 devant le jury composé de:

## **Dominique Borrione**

Université de Grenoble, France, Président

## François Berry

Université Blaise Pascal, Clermont-Ferrand, France, Rapporteur

## **Steven Derrien**

Université de Rennes 1, France, Rapporteur

## **Dietmar Fey**

Friedrich-Alexander Universität Erlangen-Nürnberg, Germany, Examinateur

## Stéphane Mancini

Université de Grenoble, France, Directeur de thèse

## Sébastien Cleyet-Merle

STMicroelectronics, France, Invité

## **Abstract**

Embedded computer vision applications demand high system computational power and constitute one of the key drivers for application-specific multi- and many-core systems. A number of early system design choices can impact the system's parallel performance – among which the parallel granularity, the number of processors and the balance between computation and communication. Their impact in the final system performance is difficult to assess in early design stages and there is a lack for tools that support designers in this task. The contributions of this thesis consist in two methods and associated tools that facilitate the selection of embedded multiprocessor's architectural parameters and computer vision application parallelization strategies. The first consists of a *Design Space Exploration* (DSE) methodology that relies on Parana, a fast and accurate parallel performance estimation tool. Parana enables the evaluation of what-if parallelization scenarios and can determine their maximum achievable performance limits. The second contribution consists of a method for optimal 2D image tile sizing using constraint programming within the Tilana tool. The proposed method integrates non-linear DMA data transfer times and parallel scheduling overheads for increased accuracy.

## Résumé

Les applications de vision par ordinateur embarquées demandent une forte capacité de calcul et poussent le développement des systèmes multi- et many-cores spécifiques à l'application. Les choix au départ de la conception du système peuvent impacter sa performance parallèle finale - parmi lesquelles la granularité de la parallélisation, le nombre de processeurs et l'équilibre entre calculs et l'acheminement des données. L'impact de ces choix est difficile à estimer dans les phases initiales de conception et il y a peu d'outils et méthodes pour aider les concepteurs dans cette tâche. Les contributions de cette thèse consistent en deux méthodes et les outils associés qui visent à faciliter la sélection des paramètres architecturaux d'un multiprocesseur embarqué et les stratégies de parallélisation des applications de vision embarquée. La première est une méthode d'exploration de l'espace de conception qui repose sur Parana, un outil fournissant une estimation rapide et précise de la performance parallèle. Parana permet l'évaluation de différents scénarios de parallélisation et peut déterminer la limite maximale de performance atteignable. La seconde contribution est une méthode pour l'optimisation du dimensionnement des tuiles d'images 2D utilisant la programmation par contraintes dans l'outil Tilana. La méthode proposée intègre pour plus de précision des facteurs non-linéaires comme les temps des transferts DMA et les surcoûts de l'ordonnancement parallèle.

# Résumé Étendu

## **Abstract**

Le développement d'une plateforme multiprocesseur pour une application spécifique, nécessite de répondre à deux questions essentielles : (i) comment tailler la plateforme multiprocesseur pour atteindre les pré-requis de l'application avec la surface minimum et la plus faible consommation ; et (ii) comment paralléliser l'application cible de façon à maximiser l'utilisation de la plateforme. Dans ce travail, nous présentons une méthodologie originale d'estimation de la performance parallèle et d'optimisation des transferts de données, à partir des traces d'une exécution de l'application séquentielle et d'un modèle d'optimisation par contraintes des transferts de données. L'estimation à la fois de la performance parallèle et du temps des transferts de données doit être rapide car elle est au coeur du processus d'exploration de l'espace de conception de la plateforme multiprocesseur. Cette méthodologie est implémentée dans les outils Parana, un simulateur abstrait très rapide, basé sur des traces, et Tilana, un outil pour optimisation des transferts de données selon une modélisation analytique dans le cadre d'une optimisation par contraintes. Les outils ciblent des applications OpenMP sur la plateforme STxP70 Application-Specific Multiprocessor (ASMP) de STMicroelectronics. Les résultats pour un benchmark du NAS Parallel Benchmark et une application de vision embarquée démontrent une marge d'erreur de l'estimation de performance inférieur à 10% en comparaison aux simulateur ISS cycle-approximate de référence et à un prototype FGPA, avec un effort de modélisation réduit. Tilana permet de trouver des paramètres de transferts de données qui optimisent le temps de transferts de tuiles d'images pour une application donnée.

#### **Contents**

| <b>R.1</b> | Introd | Introduction                                     |  |  |  |  |  |

|------------|--------|--------------------------------------------------|--|--|--|--|--|

| <b>R.2</b> | Flot d | e conception proposé                             |  |  |  |  |  |

|            | R.2.1  | Caractérisation de la plateforme x               |  |  |  |  |  |

|            | R.2.2  | Instrumentation de l'application x               |  |  |  |  |  |

|            | R.2.3  | Spécification des scénarios de parallélisation x |  |  |  |  |  |

| R.3        | Paran  | a x                                              |  |  |  |  |  |

|            | R.3.1  | Construction du graphe de tâches xi              |  |  |  |  |  |

|            | R.3.2  | Ordonnancement des tâches xi                     |  |  |  |  |  |

|            | R.3.3  | Analyse de la parallélisation xi                 |  |  |  |  |  |

| <b>R.4</b> | Tilana | a xii                                            |  |  |  |  |  |

| R.5        | Confi  | guration des expériences                         |  |  |  |  |  |

|            | R.5.1  | Architecture de la plateforme xiii               |  |  |  |  |  |

|            | R.5.2  | Outils d'exécution xiv                           |  |  |  |  |  |

|            | R.5.3  | Applications xiv                                 |  |  |  |  |  |

| <b>R.6</b> | Résul  | tats xv                                          |  |  |  |  |  |

|            | R.6.1  | Estimations du facteur d'accélération xv         |  |  |  |  |  |

|            | R.6.2  | Temps d'exécution                                |  |  |  |  |  |

| <b>R.7</b> | Trava  | ux connexes                                      |  |  |  |  |  |

|            | R.7.1  | Modélisation de la performance parallèle xvi     |  |  |  |  |  |

|            | R.7.2  | Techniques de Simulations Multiprocesseurs xvii  |  |  |  |  |  |

|            |        |                                                  |  |  |  |  |  |

| R.8 Concl | lusion               |     | iii |

|-----------|----------------------|-----|-----|

| R.7.4     | Limitations connues  |     | ii  |

| R.7.3     | Principaux avantages | xvi | ii  |

#### **R.1** Introduction

Grâce à leur flexibilité et leur puissance de calcul potentielle, les architectures multicoeurs massivement parallèles devraient être les supports de choix pour de nombreuses applications embarquées. Cependant, concevoir de tels systèmes efficaces nécessite de lever un certain nombres d'obstacles [29]. La difficulté de leur programmation efficace, qui maximise la puissance de calcul effective pour bien utiliser les ressources matérielles, réside non seulement dans la gestion des communications et synchronisations [83], mais aussi dans la prise en compte des ressources matérielles de mémorisation et de calcul de chaque noeud [183]. Dans le domaine de la vision embarquée sur plateforme multiprocesseur, les grandes quantités de données en jeu, la diversité des traitements et les dépendances des calculs aux données poussent ces systèmes à leurs limites.

Dans un système hétérogène multicoeurs, il est envisagé d'intégrer des clusters multicoeurs adaptés aux besoins spécifiques des utilisateurs. Chaqu'un de ces accélérateur multicoeurs est taillé sur mesure pour la gamme d'applications ciblées. Définir les paramètres d'architecture tels que le nombre de coeurs, la topologie des communications et les ressources de mémorisation, nécessite de prédire les performances de l'accélérateur multicoeur au plus tôt lors du processus de conception, et ceci pour les applications typiques envisagées.

La difficulté à estimer les performances d'une architecture multicoeurs exécutant un programme complexe, dont le déroulement dépend des données, provient de phénomènes d'attentes difficiles à prédire car ils sont d'une part liés aux communications et synchronisations des différentes tâches et d'autre part sont aussi dus au comportement de la plateforme matérielle. Ces surcoûts doivent être pris en compte lors de l'estimation de performance de l'application car, sinon, ils peuvent conduire à une sous-évaluation des performances réelles d'un circuit. Par exemple, un simulateur qui ne permet pas de mesurer assez finement certains phénomènes temporels peut conduire à de graves erreurs d'appréciation des performances [183]. Un outil d'estimation de performance doit aussi être suffisamment précis afin de préserver l'ordre des solutions de l'espace de conception. C'est-à-dire que si deux paramétrages de l'architecture et de la parallélisation conduisent à deux estimations de performance, alors l'ordre des performances réelles sur le système doit être le même que celui des estimations.

Pour les applications à parallélisme de données qui nécessitent de transférer d'importantes quantités de données, le logiciel doit être conçu afin de compenser les surcoûts en choisissant des stratégies de parallélisation adaptées. Parmi les options offertes, les politiques d'ordonnancement, les mécanismes de transfert de données ou encore la granularité du parallélisme, liée à la granularité des communications, ont un impact qu'il est nécessaire d'évaluer au plus tôt du processus de conception. Il est nécessaire de pouvoir les évaluer rapidement, avant même que le circuit ne soit disponible.

Les techniques d'estimation de performance disponible offrent différents compromis entre la précision et la vitesse. A l'opposé de la technique la plus lente, la simulation précise au niveau transfert de registre (RTL), les simulations basées sur des *instruction-set simulators* (ISS) ou bien sur de la *dynamic binary translation*(DBT)(§R.7.2), sont les plus rapides mais en contrepartie d'une perte de précision qui peut être dommageable. En tant que solution intermédiaire, le prototypage permet un compromis vitesse/qualité intéressant mais n'est pas toujours possible et nécessite malgré tout une conception RTL poussée. Toutes ces stratégies nécessitent une plateforme de simulation du parallélisme ainsi qu'une version parallèle de l'application qui

l'exploite. Selon le modèle de calcul, il peut aussi être nécessaire de disposer d'un système d'exploitation et d'un environnement d'exécution, qui doivent être simulés aussi. Dans le domaine des serveurs de calcul, il existe également des outils d'estimation de performance qui permettent au concepteur d'obtenir des mesures impossibles à obtenir sur le processeur lui-même. Ces outils, comme Kismet [105], Parallel Prophet [119], et Intel Advisor XE [97], ne sont pas adaptés à l'exploration de l'espace de conception d'accélérateurs multicoeurs.

Dans cette thèse, je propose une méthodologie d'exploration précoce de l'espace de conception basée sur des outils rapides d'estimation de performance à partir d'un code séquentiel (§ R.2). L'objectif est de permettre au concepteur :

- D'estimer le potentiel d'accélération de l'application

- De comparer différentes stratégies de parallélisation

- D'identifier l'origine des surcoûts et des points bloquants

- De paramétrer la plateforme multiprocesseur

La méthodologie est dite « précoce » dans le sens où elle concerne l'estimation du potentiel de parallélisation et non pas la parallélisation proprement dite. Aussi, le premier point est déterminant car il permet au concepteur de rapidement savoir s'il est intéressant de se consacrer à la conception d'une application parallèle plus poussée ou s'il y a des point bloquants à résoudre avant.

Cette méthodologie, implantée dans les outils **Parana** et **Tilana**, se décompose en trois grandes phases :

- Caractériser numériquement une plateforme réelle (ou simulée) et son modèle de programmation en mesurant les surcoûts et différentes caractéristiques ;

- Acquérir des mesures sur une application séquentielle, à l'aide des trace issues d'un simulateur (ISS ou *cycle-true*) ;

- Estimer les performances de l'application par simulation abstraite, à partir des caractéristiques et mesures précédentes ;

- Optimiser les transferts de données selon un modèle d'optimisation par contraintes.

L'étape de simulation abstraite est très rapide car le code de l'application n'est pas exécuté à proprement parler, comme détaille la section R.3. La simulation abstraite est en cela assez proche d'un calcul mathématique des performances, mais avec une vitesse de simulation supérieure celle d'un simulateur de processeur qui doit interpréter ou exécuter chaque instruction de l'application. À la seconde étape, la mesure de performance du code séquentielle à partir d'un simulateur au cycle près (*cycle-true*) permet d'obtenir des mesures de temps bien plus précises que celles d'un simulateur DBT, et ce quel que soit l'implémentation de l'*instruction-set architecture*(ISA) – pipeline, *instruction-level parallelism*(ILP) – ou même en présence d'instructions spécifiques.

Du point de vue du concepteur qui utilise ces outils, l'exploration d'architecture consiste donc soit à caractériser la plateforme en intégrant des paramètres d'architecture au modèle numérique (par exemple le nombre de processeurs), soit à faire une caractérisation pour chaque plateforme étudiée, puis à passer à l'estimation de performance par simulation abstraite, ce qui est plus rapide que de simuler l'application sur chaque plateforme. Cette méthodologie devrait permettre d'obtenir la précision d'un simulateur au cycle-près avec une vitesse d'un ordre de grandeur supérieure aux simulateurs d'instruction.

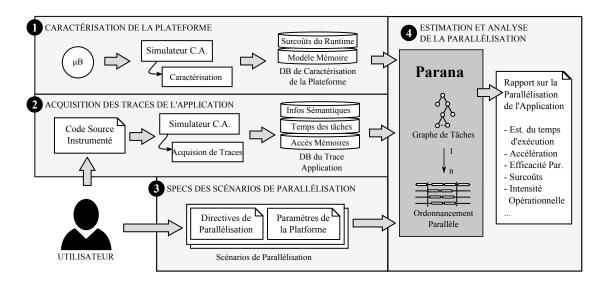

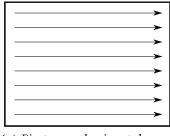

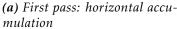

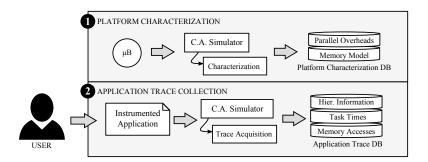

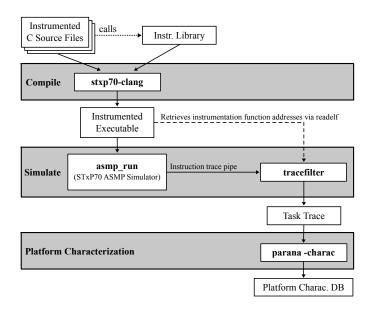

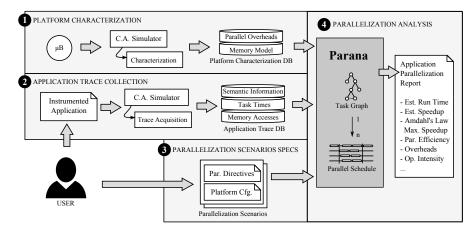

**Figure R.1:** Aperçu des quatre pas du flot proposé pour l'estimation de la performance parallèle d'une application et l'exploration de l'espace de conception avec Parana.

Cette méthodologie et les outils Parana et Tilana ont été validés sur la plateforme Application Specific MultiProcessor (ASMP) de STMicroelectronics. La plateforme est composée de grappes de processeurs STxP70 et le modèle de programmation choisi est OpenMP. La méthodologie et l'outil pourraient être généralisés pour d'autres plateformes. L'outil Parana a été validé en comparant les performances estimées aussi bien aux mesures issues d'un simulateur qu'à un prototype FPGA de la plateforme. Comme détaillé en section R.6, les résultats montrent que Parana donne une très grande précision de l'estimation, avec une erreur de 10% par rapport à la plateforme réelle, et ceci avec une vitesse de simulation supérieure à un simulateur de type ISS d'un ordre de grandeur.

## R.2 Flot de conception proposé

La méthode de simulation rapide proposée repose sur un simulateur abstrait calculant les performances de l'application sur la plateforme parallèle à partir de traces de l'application séquentielle et de mesures de caractérisation des surcoûts induits par la plateforme et son environnement de parallélisation. Ainsi, il devient très rapide d'explorer les performances de configurations logicielles et matérielles à partir de traces et caractéristiques préparées par pré-traitement. Dans ces travaux, la cible consiste à une plateforme multicoeur intégrée STxP70 ASMP (§R.5.1) gérée par l'environnement d'exécution OpenMP. La figure R.1 décrit les quatre étapes de cette méthode, détaillées par la suite :

Etape 1: Caractérisation de la plateforme. La première étape consiste à évaluer numériquement les différentes caractéristiques de la plateforme multicoeur et de son environnement qui ont le plus d'impact sur les surcoût de performance. La base de données des caractéristiques contient des informations statistiques mesurées sur des applications de référence instrumentées. Les informations concernent aussi bien les différents temps de calcul en surplus induits par l'environnement OpenMP et les différentes directives afférentes que des caractéristiques spécifiques à la plateforme matérielle telles que les débits et latences d'accès aux différents niveaux de mémoire et de cache. Les mesures sont réalisées à partir d'une version étendue du micro-benchmark EPCC OpenMP [43]. Les informations temporelles peuvent être extraites à

**Listing R.1:** Exemple d'un code source instrumenté pour parallélisation avec l'outil Parana (c.f. directives dans Listing R.2).

```

void vAdd(int *r, int *a, int *b, int n) {

int i;

//PA_START_TASK(<var>, <label>)

PA_START_TASK(_parallel0_, "parallel0");

for(i=0; i < n; i++) {

PA_START_TASK(_for0_, "for0");

r[i] = a[i] + b[i];

PA_END_TASK(_for0_);

}

//PA_END_TASK(<var>)

PA_END_TASK(_parallel0_);

}

```

**Listing R.2:** Exemple de fichier de propriétés avec des directives de parallélisation pour la fonction vAdd (c.f. code source dans Listing R.1).

```

vAdd = #define NUM_THREADS 8

vAdd = #define CHUNK_SIZE 1

vAdd.parallel0 = #pragma omp parallel num_threads(NUM_THREADS)

vAdd.for0 = #pragma omp for schedule(static, CHUNK_SIZE)

```

partir d'un simulateur (de préférence au cycle-près) ou même d'un émulateur matériel. Les mesures sont traitées par notre outil de caractérisation qui en déduit une base de données spécifique à chaque version de l'architecture ciblée. Cette base de données servira pour générer rapidement des estimations de performance.

Etape 2 : Caractérisation de l'application. À partir du profilage d'un code séquentiel, cette seconde étape extrait les informations spécifiques à l'application. L'objectif est de déduire de l'exécution séquentielle un graphe de tâches à paralléliser par la suite. L'extraction du parallélisme est faite de façon soit implicite soit explicitée par l'utilisateur. Dans la version implicite, l'hypothèse est que, dans l'environnement OpenMP, les tâches sont liées aux appels de fonctions dans les boucles et à la présence de commande OpenMP de parallélisation (pragmas). L'utilisateur peut également indiquer des zones parallèles explicites en insérant des commandes dans le code source à l'aide de macros spécifiques. Le profilage mesure également des statistiques des accès mémoires dans chacune des tâches identifiées afin d'estimer les temps d'accès et collisions aux mémoires partagées. L'utilisateur peut également ajouter divers informations sémantiques pour affiner son analyse. Listing R.1 montre un exemple d'instrumentation d'une fonction de somme vectorielle vAdd.

**Etape 3 : Spécification des scénarios de parallélisation.** L'utilisateur peut définir un ensemble de scénarios de parallélisation qui correspondent chacun à une configuration de l'espace de conception. Un scénario de parallélisation comporte un groupe de paramètres spécifiques à la plateforme matérielle (nombre de processeurs, mémoires, etc.) et un second spécifique à l'application. Ce dernier groupe est en fait le jeu de paramètres qui décrit la stratégie de parallélisation choisie (ordonnancement statique/dynamique, nombre de tâches, etc.) et correspond aux directives OpenMP associées à chaque zone de parallélisme identifiée à l'étape 2. Listing R.2 montre le fichier de propriétés pour un possible scénario de parallélisation de la fonction *vAdd* dans Listing R.1.

**Etape 4 : Estimation de performance de la parallélisation.** Cette dernière étape consiste à estimer les temps de calcul de l'application parallélisée selon les directives indiquées, et ceci à partir de la base de données de caractéristiques et des mesures obtenues par le profilage. Cette

étape produit une analyse détaillée de l'origine des surcoûts induits par l'environnement de parallélisation, l'équilibrage de charge, les zones séquentielles, les accès mémoires et autres phénomènes difficiles à estimer analytiquement. Cette étape est extrêmement rapide car le code de l'application n'est pas exécuté et la plateforme matérielle n'est pas simulée dans le détail, ceci ayant été fait une fois pour toutes à l'étape 1.

La boucle de conception peut se focaliser sur les étapes 3 et 4, et, en quelques secondes, l'utilisateur peut analyser des dizaines de configuration et éliminer les plus aberrantes. Les performances des configurations retenues peuvent alors être validées par une simulation classique. L'avantage de la méthode est qu'elle permet d'éviter d'implanter chaque configuration matérielle et chaque version parallèle du logiciel en partant d'un code séquentiel et de passer au crible rapidement de nombreuses stratégies de parallélisation.

## R.2.1 Caractérisation de la plateforme

## R.2.2 Instrumentation de l'application

Notre infra-structure d'acquisition de traces d'instruction est capable de générer une trace de tâches automatiquement aux appels de fonctions. Accessoirement, nous fournissons une librairie d'instrumentation qui permet à l'utilisateur de agrémenter ces traces avec des tâches labellisées. Ces dernières sont définies de façon explicite par moyen d'un ensemble de macros d'instrumentation qui enserrent la section de code appartenant à chaque tâche. Les tâches explicites créent un niveau hiérarchique supplémentaire dans l'arbre de tâches, ce qui permet de regrouper toutes les sous-tâches à l'intérieur de sa section de code. Listing R.1 montre un exemple d'une fonction de somme vectorielle vAdd instrumenté avec deux tâches labellisées : parallel0 et for0.

## R.2.3 Spécification des scénarios de parallélisation

Lors de la définition d'un scénario de parallélisation, des directives OpenMP peuvent être attachées aux tâches tracés – qu'elles relèvent des appels de fonctions ou de l'instrumentation explicite –, leur ajoutant une sémantique de parallélisme, ordonnancement et/ou synchronisation. Nous utilisons un fichier de *propriétés* pour spécifier les directives de parallélisation et les relier aux tâches. Un fichier de *propriétés* consiste à une série de combinaisons clés-valeurs, où les clés sont les noms des tâches (noms des fonctions ou labels utilisateurs), et les valeurs sont les directives OpenMP. Un deuxième fichier de *propriétés* définit les valeurs des paramètres de la plateforme multiprocesseur.

Listing R.1 montre les directives d'une possible parallélisation pour la fonction vAdd (c.f. § R.2.2) qui ouvre une région parallèle avec 8 threads contenant une boucle for avec ordonnancement statique et un bloc de taille 1. Des multiples fichiers de *propriétés* peuvent être crées pour décrire les différents scénarios de parallélisation à explorer.

## R.3 Parana

Parana utilise les données de la caractérisation de la plateforme multiprocesseur, les traces de l'application et le fichier de spécification des scénarios de parallélisation, pour estimer et analyser la performance parallèle de l'application. Initialement, il construit un graphe de tâches à partir des traces de l'application. Puis, pour chaque scénario de parallélisation, un nouveau graphe est obtenu en attachant aux tâches les directives de parallélisation. Finalement, un

scénario de parallélisation produit un calcul de l'ordonnancement parallèle correspondant. Cet ordonnancement prend en compte les surcoûts liés à l'environnement OpenMP et au modèle mémoire de la plateforme. Finalement, un rapport de parallélisation détaillé est généré.

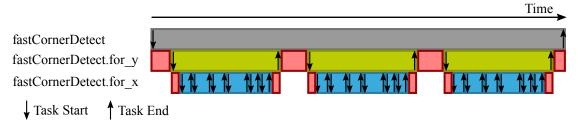

## R.3.1 Construction du graphe de tâches

La représentation interne des traces de tâche consiste en un graphe de tâches hiérarchique – un graphe orienté acyclique (DAG) où les sommets sont des tâches et les arcs représentent des relations père-fils. Du fait du profiling à partir du code séquentiel, il y a un recouvrement temporel entre les tâches pères et les tâches fils, ce qui nécessite un pré-traitement sur le graphe pour procéder à l'ordonnancement car nous n'avons besoin que des tâches feuilles. Cette étape d'insertion de tâches feuilles aux intervalles où il n'y a pas de recouvrement père-fils et de suppression des parties recouvrantes est dénommée segmentation et produit un graphe de tâche hiérarchique.

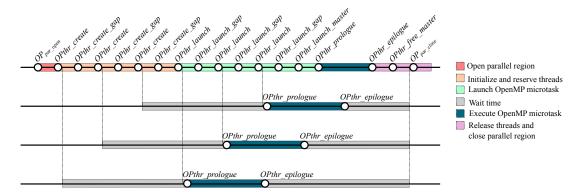

#### R.3.2 Ordonnancement des tâches

Un ordonnancement est à son tour représenté comme un DAG où les sommets sont des tâches dites *ordonnançables* et les arcs représentent des relations de précédence entre de telles tâches. Les tâches *ordonnançables* sont annotées d'informations supplémentaires liées à l'ordonnancement, telles que la date initiale dans l'ordonnancement et l'identifiant du processeur cible.

Initialement, Parana construit un ordonnancement sur un seul coeur qui sera la référence pour le calcul de l'accélération et de l'efficacité parallèle. La génération de l'ordonnancement se fait en parcourant l'arbre de tâches *hiérarchique* en profondeur et, à chaque tâche feuille trouvée, une tâche *ordonnançable* est ajoutée dans le DAG de l'ordonnancement.

Ensuite, l'ordonnancement parallèle est effectué pour chaque scénario de parallélisation défini par l'utilisateur. Pour réaliser l'ordonnancement parallèle, le DAG hiérarchique est parcouru et lorsqu'une tâche possédant une directive OpenMP est trouvée, l'ordonnanceur émule l'ordonnancement qui serait effectué par l'environnement d'exécution OpenMP. C'est à ce moment que le simulateur introduit des tâches supplémentaires pour modéliser les surcoûts liés au lancement, à la synchronisation et au rassemblement des sous-tâches, entre autres, dont les temps ont été estimés selon la caractérisation de la plateforme.

#### R.3.3 Analyse de la parallélisation

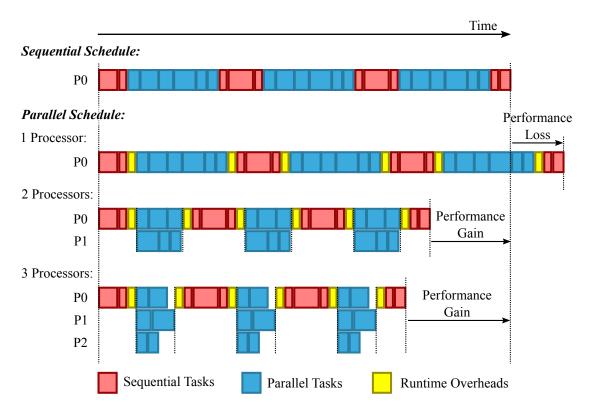

Un rapport détaillé est généré à la suite de chaque ordonnancement, incluant notamment : le temps total d'exécution estimé de l'application ; l'accélération vis-à-vis de la référence séquentielle ; l'efficacité de la parallélisation. Ce rapport note également les statistiques pour les portions séquentielles et parallèles de l'ordonnancement. Toutes les mesures sont décomposées en temps de calcul, temps d'inactivité et surcoûts. Ces informations sont utilisées pour créer des *cycle-stacks*, un type de graphe qui permet de visualiser la décomposition des facteurs qui contribuent au temps d'exécution dans un ordonnancement donné.

En outre, Parana est capable de générer des rapports pour chaque région parallèle de l'application. Dans ce cas, il fournit aussi la localisation de la région parallèle dans l'arbre d'appels et, pour chaque tâche, le nombre de cycles moyen par exécution. Cela permet au concepteur de retrouver sur un seul rapport les statistiques nécessaires pour analyser les gains et les goulot d'étranglement potentiels.

## R.4 Tilana

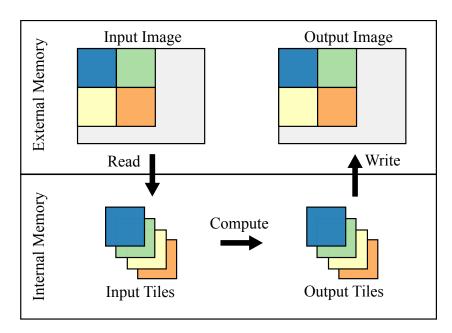

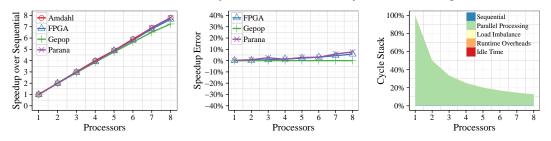

Les applications de traitement d'image embarquées utilisent souvent des buffers d'entrée et sortie placés dans une mémoire externe. Ces buffers de données sont utilisés soit comme un moyen d'échanger des données entre les différents sous-systèmes, ou simplement car la quantité de données est trop importante pour tenir dans la mémoire locale réduite d'un système embarqué. Etant donné que le temps d'accès à la mémoire externe est beaucoup supérieur à celui de la mémoire interne, les données doivent d'abord être transférées à la mémoire locale avant d'être traitées par les unités de calcul. Sur les systèmes avec mémoire gérée explicitement, sans cache de données, il est la responsabilité du programmeur de gérer les transferts de données entre les espaces mémoires interne et externe. Une solution courante consiste à utiliser le tuilage, qui consiste à subdiviser les données en plus petites zones, les tuiles, qui sont assez petites pour rentrer dans la mémoire interne et qui peuvent être traitées de façon indépendante.

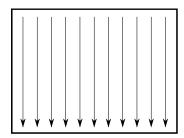

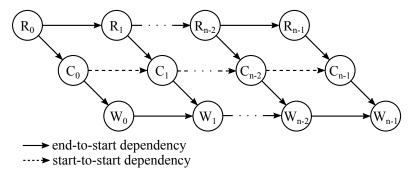

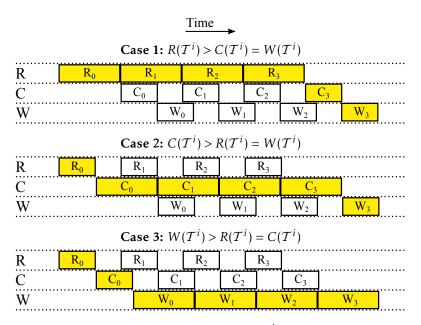

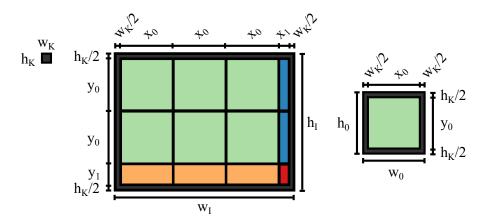

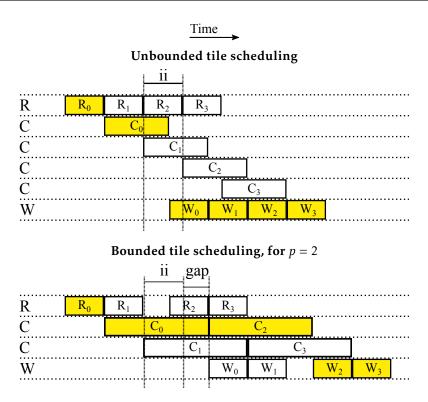

Pour mieux utiliser les ressources disponibles, le tuilage est implémenté comme un pipeline logiciel de trois étapes qui consistent à : (i) lire les données d'entrée depuis la mémoire externe et les écrire dans la mémoire interne ; (ii) processer les données localement ; et (iii) écrire les données de sortie sur la mémoire externe. La Figure 6.1 illustre ce pipeline de calcul de trois étapes. Les avantages du tuilage incluent la réduction de l'empreinte de données dans la mémoire locale et la réduction de la latence de l'application grâce au chevauchement entre transferts de données et calcul.

La question est comment sélectionner les dimensions optimales de tuilage ? La taille et la forme des tuiles ont d'importante conséquences sur le temps et la quantité de données transferts. Ces divers facteurs et leur impact sont difficiles à estimer tôt dans le flot de conception, empêchant les programmeurs de trouver une solution optimale.

Pour relâcher la contrainte sur les programmeurs, certains compilateurs intègrent le support au tuilage automatique, via des techniques récentes de compilation polyédrique. Des exemples de tels compilateurs sont PLuTO [40] et PolyMage [153], les deux par Bondhugula et al., bien comme le compilateur commercial R-Stream [184, 14] par Reservoir Labs. Ces compilateurs performent des transformations affines de boucle qui visent à augmenter la localité des données et la bande passante mémoire sur les architectures avec cache de données. Darte et al. ont prouvé en [58] que les techniques de compilation polyédriques peuvent produire ordonnancements asymptotiquement optimales pour des cas avec dépendances uniformes. Leur optimalité n'est donc pas garantie pour ordonnancements à faible nombre d'itérations (ou tuiles). Même si un nombre élevé d'itérations est une contrainte plausible pour un système de haute performance, cela n'est pas le cas pour des systèmes embarqués de temps-réel. Par ailleurs, les techniques de compilation polyédriques ne peuvent pas intégrer des non-linéarités dans le model, qui comme démontré à la Section 4.7.5, sont nécessaires pour obtenir une bonne précision. D'autres méthodes se basent sur le tuilage pour obtenir un ordonnancement à gros grain sur les systèmes parallèles [111, 152]. Aucune de ces méthodes n'est capable de modéliser des transferts de données explicites avec des caractéristiques non-linéaires.

Dans un travail récent, Saïdi et al. [177] proposent un modèle analytique pour l'optimisation d'algorithmes de traitement de tableaux sur des systèmes avec de la mémoire gérée explicitement et l'expriment en termes d'un modèle pour optimisation par contraintes. Néanmoins, leur travaux repose sur un modèle de régression linéaire des temps de transfert de données du DMA qui, comme démontré en section 4.7.5, peuvent amener à des résultats trop imprécis sur certaines architectures. Par ailleurs, cette méthode assume que les dimensions de l'image sont des multiples entiers de la dimension des tuiles, une contrainte que je juge trop contraignante et que si surmontée pourrait amener à des solutions plus optimales.

Le chapitre 6 présente donc une méthode pour sélectionner les paramètres de tuilage qui minimisent le temps d'exécution d'un noyau d'application parallèle sur un multiprocesseur

Figure R.2: Aperçu du concept de pipeline de tuilage d'image proposé par Ievgen [91]. Cela consiste à décomposer l'image en une série de tuiles d'image qui sont : (i) lues depuis la mémoire externe, (ii) traitées localement, et les résultats (iii) réécrits sur la mémoire externe pour recomposer l'image de sortie.

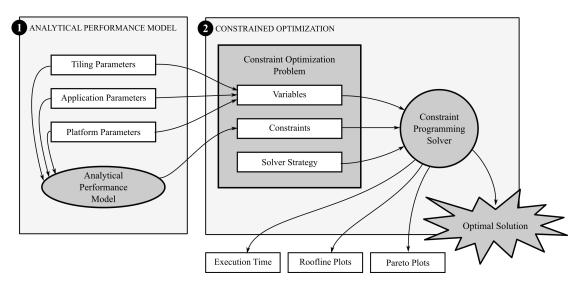

embarqué. Premièrement, un nouveau modèle analytique est présenté. Ce modèle est alors converti en un problème d'optimisation par contraintes implémenté dans l'outil Tilana utilisant le framework d'optimisation par contraintes Choco3 [200].

Les contributions principales du chapitre 6 sont :

- 1. proposer un nouveau modèle analytique pour estimer le temps d'exécution d'un noyau d'application parallèle qui implémente le tuilage, pour toutes les dimensions valides de tuiles ;

- 2. intégrer un modèle non-linéaire de la performance du DMA, décrit en section 4.7.5, pour un meilleure précision sur les estimations du temps de transferts du DMA ;

- 3. dériver et intégrer un modèle des surcoûts d'ordonnancement parallèle et ses dépendances sur une plateforme multiprocesseur ;

- 4. définir et implémenter un modèle d'optimisation par contraintes basé sur des contraintes non-linéaires qui permettent déterminer les dimensions optimales qui minimisent le temps d'exécution du noyau d'application parallèle.

## R.5 Configuration des expériences

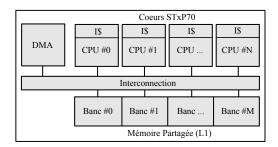

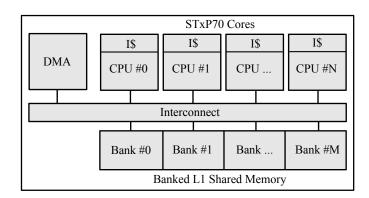

## R.5.1 Architecture de la plateforme

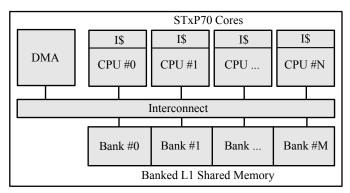

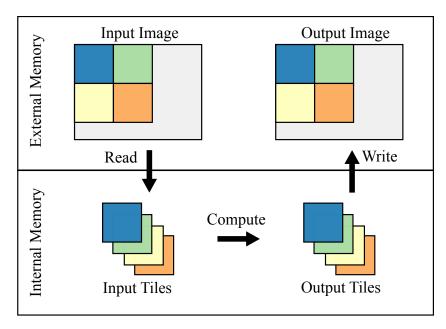

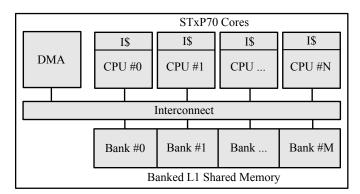

Notre plateforme cible est le STxP70 Application-Specific Multiprocessor (ASMP) de STMicroelectronics. Cette plateforme est très similaire à un cluster STHORM [149]. Le STxP70 ASMP possède une architecture SMP configurable comptant jusqu'à 16 coeurs STxP70 – des CPUs RISC 32-bit dual-issue. La Figure 5.8 illustre son gabarit architectural. L'ASMP possède une mémoire L1 partagée, organisée en bancs, et accessible en un cycle via l'« interconnect », ce qui permet l'accès simultané à plusieurs bancs mémoire. En cas de conflit d'accès sur un banc mémoire, les processeurs sont bloqués et l'accès au banc en question est géré de façon équitable par un arbitre

Figure R.3: Gabarit de l'architecture du STxP70 ASMP.

round-robin. En outre, chaque processeur compte 16KB de cache programme, mais pas de cache de données. Pour les expériences, une configuration avec 512KB de mémoire partagée, organisée en 32 bancs mémoire est utilisée.

#### R.5.2 Outils d'exécution

**Simulateur Gepop.** Gepop est un simulateur cycle-approximate pour la plateforme STxP70 ASMP et est notre simulateur de référence pour la caractérisation de la plateforme dans le flot proposé. Il est basée sur des simulateurs STxP70 monocoeurs ISS et intègre des modèles des autres composants de la plateforme, tels que le DMA, les mémoires, et l'interconnect. Sa précision est évalué à moins de 10% de marge d'erreur par rapport à un circuit physique.

**Prototype FPGA.** Un prototype du STxP70 ASMP sur le FPGA Xilinx VC707 est utilisé pour comparaison. En raison des contraintes d'occupation, le nombre de coeurs et la mémoire L1 sont limités à 8 coeurs et 512KB, respectivement. Le temps d'exécution sur FPGA est utilisé pour valider les temps d'exécution obtenus avec Gepop et Parana.

**Parana.** L'outil proposé, un simulateur basé sur des traces. Il estime la performance parallèle de l'application à partir des traces d'une exécution séquentielle de l'application et d'un ensemble de directives OpenMP pour de différents scénarios de parallélisation. Les traces Gepop sont utilisées à la fois pour la caractérisation de la plateforme et comme base pour les estimations de la performance parallèle.

## **R.5.3** Applications

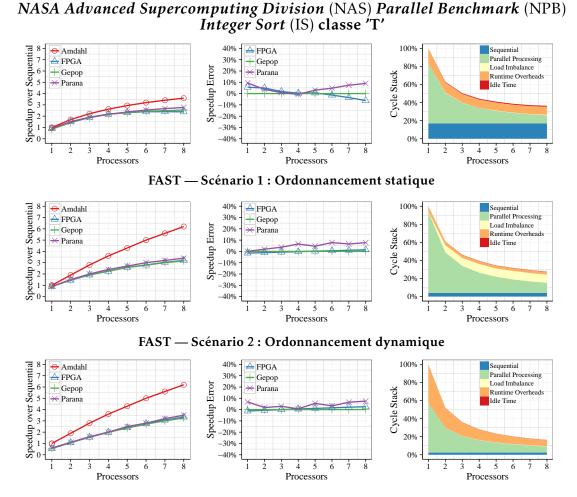

Integer Sort (IS). J'ai sélectionné le benchmark IS parmi ceux de la suite NAS Parallel Benchmarks (NPB) [108], car une implémentation OpenMP en C est disponible. Deux adaptations furent nécessaires : (i) du fait des limitations des ressources mémoire, une classe de données plus petite que celle fournie avec le benchmark a été créée, et a été nommée Tiny (T) ; (ii) le runtime OpenMP pour ASMP ne supporte pas la directive *threadprivate*, utilisée dans la fonction qui génère les valeurs aléatoires à trier, et donc cette dernière a été remplacée par la fonction  $rand\ r$ .

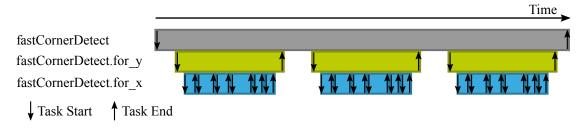

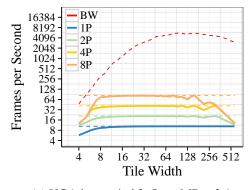

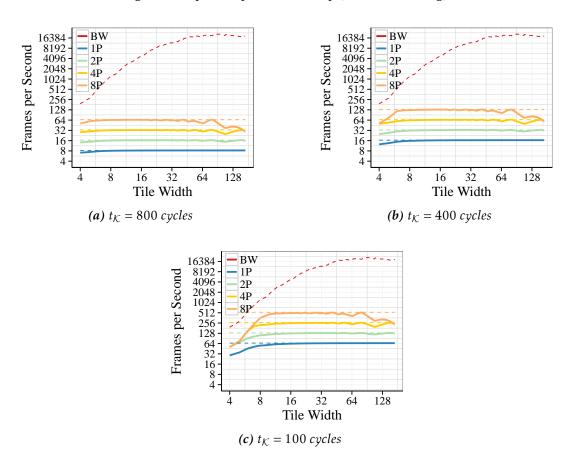

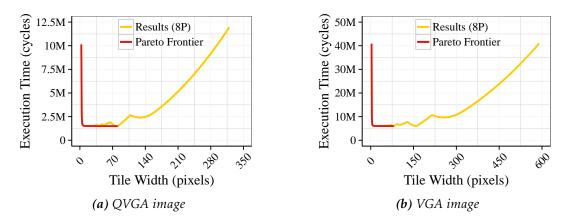

**Détecteur de points caractéristiques FAST.** J'ai porté l'algorithme de détection de points caractéristiques FAST 9-16 sur une cible STxP70 *Application-Specific Multiprocessor* (ASMP). Cet algorithme est couramment utilisé dans le domaine de la vision par ordinateur pour sélectionner les points caractéristiques dans des nombreuses applications de détection et de suivi. La référence est l'algorithme FAST fourni dans OpenCV version 2.4.6, lequel a été transcrit en C pour le STxP70 ASMP et parallélisé avec OpenMP. J'ai évalué deux scénarios de parallélisation distincts, le premier avec un ordonnancement de boucles statique et le deuxième avec un ordonnancement de boucles dynamique.

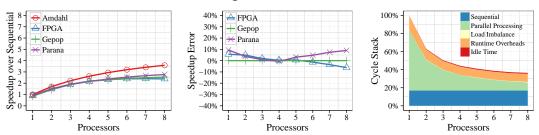

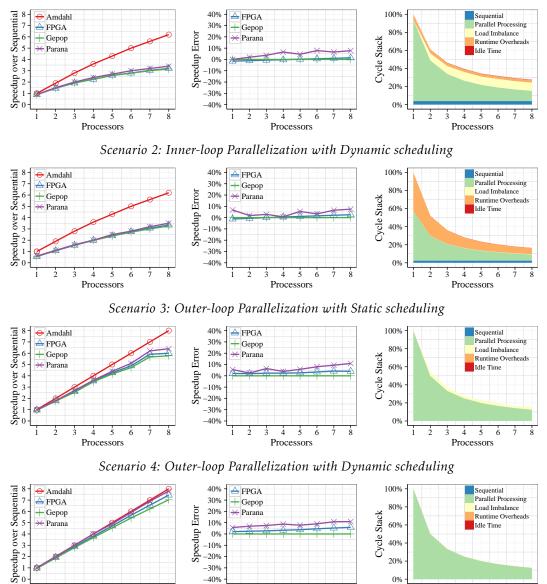

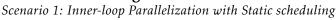

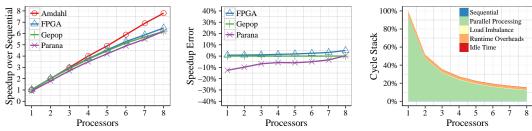

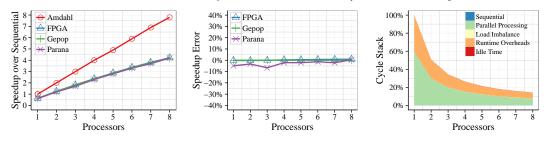

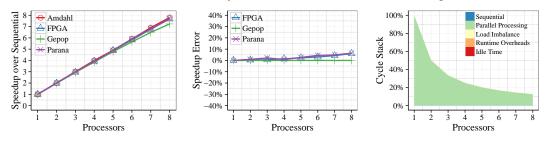

Figure R.4: Comparaison du facteur d'accélération obtenu avec Parana, le simulateur cycle-approximate Gepop (référence pour l'acquisition de traces pour Parana) et un prototype FPGA, pour le benchmark NPB Integer Sort(IS) et le détecteur de points caractéristiques FAST. Gauche : facteurs d'accélération pour 1 à 8 coeurs. Centre : erreur relative au facteur d'accélération obtenu avec Gepop. Droite : Cycle stacks qui montrent la répartition par catégorie des cycles de l'application.

#### R.6 Résultats

#### R.6.1 Estimations du facteur d'accélération

Les résultats sur les facteurs d'accélération pour les applications sélectionnées, ainsi que les erreurs relatives à la plateforme de simulation de référence (Gepop), sont présentés sur la Figure R.4. L'erreur moyenne de l'estimation du facteur d'accélération de l'outil Parana est de 3.8% avec une erreur maximum de 9.5% pour les scénarios testés.

Avec le noyau de référence « tri d'entier » NPB-IS l'erreur de l'estimation augmente avec le nombre de threads. C'est principalement dû à une opération de réduction qui dépend du nombre de threads. Cette opération de réduction n'est pas exécutée dans la version séquentielle de l'application et, par conséquent, n'est pas comptabilisée dans les traces exploitées par l'outil Parana.

Pour l'algorithme de détection de coins FAST, la représentation sous forme de graphique

| Outil    | Type               | Entrées     | 6      | Design  | + Config. |           | DSE          |        |           |

|----------|--------------------|-------------|--------|---------|-----------|-----------|--------------|--------|-----------|

|          |                    | Application | Instr. | Temps   | Effort    | Temps d'- | Productivité | Erreur | Précision |

|          |                    |             |        |         |           | exécution |              |        |           |

| FPGA     | Prototype Matériel | Parallèle   | Non    | Jours   | Important | 60.0s     | Basse        | <5%    | Haute     |

| _        | Sim. C-Accurate    | Parallèle   | Non    | Heures  | Important | _         | Basse        | <5%    | Haute     |

| Gepop    | Sim. C-Approximate | Parallèle   | Non    | Heures  | Moyenne   | 24.3s     | Moyenne      | <10%   | Moyenne   |

| Kismet   | Chemin Critique    | Séquentiel  | Non    | Seconds | Bas       | _         | Basse        | >10%   | Basse     |

| Parallel | Modèle Analytique  | Séquentiel  | Oui    | Minutes | Moyen     | _         | Basse        | <10%   | Moyenne   |

| Prophet  |                    |             |        |         |           |           |              |        |           |

| Parana   | Modèle Analytique  | Séquentiel  | Oui    | Minutes | Bas       | 1.6s      | Haute        | <10%   | Moyenne   |

Table R.1: Comparaison des méthodes de simulation et outils semblables pour l'estimation de la performance parallèle. Effort de mise en oeuvre : temps nécessaire pour préparer le code et la plateforme pour chaque point de l'espace de conception (faible : aucune modification au code original ; moyen : légères modifications du code ; important : modifications significatives du code source). Productivité : liée au temps pour configurer et évaluer de multiples points de conception (basse : long ; haute : rapide). Précision : précision relative à la performance du système physique (basse : >10% d'erreur ; moyenne : <10% d'erreur ; haute : <5% d'erreur).

cumulé des cycles extrait par l'outil Parana met en évidence que l'équilibrage de charge est la principale cause de baisse d'efficacité pour un ordonnancement statique alors que pour un ordonnancement dynamique les pénalités ont plutôt pour origine les surcoûts de l'environnement d'exécution d'OpenMP. Cette analyse permet aussi de conclure que les irrégularités sur le facteur d'accélération avec un ordonnancement statique proviennent du déséquilibre de charge entre les différents threads, dont le nombre varie en fonction du nombre de coeurs. Enfin l'estimation de l'outil Parana est encore plus précise sur cette application avec une erreur moyenne de 3% dans les 2 scénarios (ordonnancement statique ou dynamique des tâches).

En conclusion, la précision de Parana est suffisante pour pourvoir observer les effets des changements de politique de parallélisation et préserve l'ordre des performances.

Les résultats pour les expériences sur l'outil Tilana sont présentés et discutés à la Section 6.6.

## R.6.2 Temps d'exécution

Le tableau R.1 liste les moyennes de temps de simulation sur la machine hôte pour chaque configuration évaluée lors de nos expérimentations avec les plateformes Gepop, le prototype FPGA et l'outil Parana. Le temps de simulation avec Parana est en moyenne 15.9 fois plus rapide que le temps de simulation de la plateforme avec le simulateur Gepop, et jusqu'à 20 fois plus rapide dans certains cas. La plateforme FPGA est encore plus lente à cause du temps de chargement de l'application et des interactions avec le PC hôte pour les appels système. Dans ce cas la simulation avec Parana est 36.7 fois plus rapide que la simulation FPGA.

## R.7 Travaux connexes

#### R.7.1 Modélisation de la performance parallèle

La loi d'Amdhal [25] a été l'un des premiers essais de modélisation de la performance des applications parallèles. De nombreux modèles dérivés ont été proposés, y compris certains modèles récents introduisant des multiprocesseurs hétérogènes [85]. D'autres outils, comme Kismet [105], utilisent une analyse hiérarchique du chemin critique pour estimer le facteur d'accélération potentiel d'une application séquentielle. Ces approches ne demandent que peu d'effort de développement et fournissent une estimation haute et souvent très optimiste.

L'outil Intel Advisor XE [97] estime les performances sur une architecture x86 qui repose sur une instrumentation utilisateur des régions parallèles et des boucles. Il manque à cette approche la modélisation des bandes passantes ainsi que les pénalités de cache. L'outil Parallel Prophet [119] repose aussi sur une instrumentation pour construire un graphe de tâches de l'application et estimer son facteur d'accélération avec différentes politiques d'ordonnancement. D'autres méthodes se concentrent sur le partitionnement et l'assignement de parties de l'application sur un système multiprocesseur [20], mais ne couvrent pas le parallélisme de données. Aucun des outils cités ne s'intéresse à la prédiction de performances pour du parallélisme de données sur des plateformes multiprocesseur spécifiques embarquées. De plus notre outil supporte la définition de différents scénarios de parallélisme avec des stratégies différentes et plusieurs configurations multiprocesseur, ce qui autorise une exploration rapide de l'espace de conception.

## **R.7.2** Techniques de Simulations Multiprocesseurs

Le tableau R.1 compare l'outil Parana avec d'autres outils de simulations, prototypes et outils de prédiction de performance. Les prototypes physiques et les simulateurs au cycle-près (cycle-accurate) sont très précis. Cependant les prototypes prennent du temps à mettre en oeuvre et ont des ressources limitées, alors que les simulations cycle-accurate sont lentes, ce qui limite l'exploration de l'espace de conception. La traduction binaire dynamique (DBT) ou les simulateurs de jeu d'instruction, tel que la plateforme de simulation Gepop, ont une précision de la mesure de cycle plus faible au profit d'une vitesse de simulation plus rapide. Des travaux récents sur des simulateurs au niveau code source (qui annotent le code source avec des informations temporelles et le simulent ensuite avec SystemC [188]) et des simulateurs basés sur l'échantillonnage [47], présentent une précision plus grande et une vitesse de simulation plus grande. Cependant, toutes ces approches nécessitent de travailler sur les versions parallèles de l'application pour chaque point de l'espace de conception. En tant que simulateur analytique, Parana associe une vitesse de simulation rapide, avec une bonne précision, à la possibilité de modéliser différents scénarios d'ordonnancement OpenMP à partir d'une application séquentielle, pour explorer l'espace de conception.

## R.7.3 Principaux avantages

La méthodologie proposée fourni une estimation précise très tôt dans le flot de conception. Avant même d'avoir une version parallèle fonctionnelle de l'application. Ceci permet une exploration rapide de l'espace de conception à la fois pour les scénarios de parallélisation et pour la configuration du système multiprocesseur.

La méthode est extrapolable à d'autres familles de processeur et permet aussi d'évaluer l'impact de l'ajoût d'instructions spéciales. En effet, l'estimation de l'ajout d'une extension du jeu d'instruction du processeur ne nécessite que de produire une nouvelle trace d'exécution de l'application séquentielle recompilée avec l'utilisation de ces instructions.

Finalement, la production de documents d'analyse sous forme de « cycle-stacks » aide significativement l'architecte système à identifier les points bloquants et le potentiel de parallélisation de l'application.

## **R.7.4** Limitations connues

La limitation principale de notre méthode est qu'elle ne modélise pas correctement les applications qui contournent les constructions OpenMP standard pour implanter d'autres types de distributions parallèles (statiques ou dynamiques). Les contentions mémoire et les transferts

DMA ne sont pas encore modélisés et seront adressés dans un futur proche. Les applications de nos expérimentations n'utilisent pas le DMA et ne semblent pas souffrir de dégradations dues aux contentions mémoires. Les appels aux APIs du DMA peuvent aisément être interceptés avec notre méthodologie et ordonnancés sur une ressource dédiée dans le modèle d'ordonnancement de l'outil Parana pour modéliser le DMA. Les contentions mémoires peuvent être estimées en utilisant des histogrammes du nombre d'accès par banc mémoire pour en dériver un modèle statistique des surcoûts associés aux contentions.

## **R.8** Conclusion

Ce travail présente une méthodologie et l'outil Parana pour accélérer l'exploration conjointe de l'espace de conception des stratégies de parallélisation et de la configuration d'une plateforme multiprocesseur. L'estimation se fait à partir d'une trace d'exécution de l'application séquentielle et de directives de parallélisation. Les résultats de la méthodologie proposée ont été comparés aux mesures réalisées sur trois scénarios d'applications OpenMP, chacun ayant été mesuré sur une plateforme de simulation de jeu d'instruction (Gepop) et sur un prototype FPGA de la plateforme STxP70 ASMP. Il a été démontré que la précision de Parana dans l'estimation du facteur d'accélération parallèle est supérieure à 90% par rapport au simulateur de référence. Une telle précision montre ainsi son intérêt dans l'identification des facteurs limitant la performance parallèle via l'analyse détaillée des temps d'exécution. Cette précision est atteinte avec un temps de simulation 15 fois plus rapide que le simulateur de référence. Ainsi, cette simulation très rapide et précise peut être intégrée dans une boucle de conception pour parcourir l'espace de conception.

# **Contents**

| Abstract  |                     |                                                |       |  |  |  |  |  |

|-----------|---------------------|------------------------------------------------|-------|--|--|--|--|--|

| Résumé    |                     |                                                |       |  |  |  |  |  |

| Résumé    | Étend               | u                                              | v     |  |  |  |  |  |

| R.1       | Introduction        |                                                |       |  |  |  |  |  |

| R.2       | Flot de             | e conception proposé                           | viii  |  |  |  |  |  |

|           | R.2.1               | Caractérisation de la plateforme               | . x   |  |  |  |  |  |

|           | R.2.2               | Instrumentation de l'application               | . x   |  |  |  |  |  |

|           | R.2.3               | Spécification des scénarios de parallélisation | . x   |  |  |  |  |  |

| R.3       | Parana              | ı                                              | . x   |  |  |  |  |  |

|           | R.3.1               | Construction du graphe de tâches               | xi    |  |  |  |  |  |

|           | R.3.2               | Ordonnancement des tâches                      | xi    |  |  |  |  |  |

|           | R.3.3               | Analyse de la parallélisation                  | xi    |  |  |  |  |  |

| R.4       | Tilana              |                                                | xii   |  |  |  |  |  |

| R.5       | Config              | guration des expériences                       | xiii  |  |  |  |  |  |

|           | R.5.1               | Architecture de la plateforme                  | xiii  |  |  |  |  |  |

|           | R.5.2               | Outils d'exécution                             | . xiv |  |  |  |  |  |

|           | R.5.3               | Applications                                   | . xiv |  |  |  |  |  |

| R.6       | Résult              | ats                                            | . XV  |  |  |  |  |  |

|           | R.6.1               | Estimations du facteur d'accélération          | . XV  |  |  |  |  |  |

|           | R.6.2               | Temps d'exécution                              | xvi   |  |  |  |  |  |

| R.7       | Travau              | ax connexes                                    | xvi   |  |  |  |  |  |

|           | R.7.1               | Modélisation de la performance parallèle       | xvi   |  |  |  |  |  |

|           | R.7.2               | Techniques de Simulations Multiprocesseurs     | xvii  |  |  |  |  |  |

|           | R.7.3               | Principaux avantages                           | xvii  |  |  |  |  |  |

|           | R.7.4               | Limitations connues                            | xvii  |  |  |  |  |  |

| R.8       | Concl               | usion                                          | xviii |  |  |  |  |  |

| Conten    | ts                  |                                                | xix   |  |  |  |  |  |

| List of l | Figures             |                                                | xxv   |  |  |  |  |  |

| List of   | ist of Tables xxvii |                                                |       |  |  |  |  |  |

| 1 | Intr | roduction    |                                                                       |    |  |  |

|---|------|--------------|-----------------------------------------------------------------------|----|--|--|

|   | 1.1  | Embedded     | Computer Vision                                                       | 2  |  |  |

|   | 1.2  | Application  | n-Specific Multiprocessor Systems Design                              | 3  |  |  |

|   | 1.3  | Parallel Des | sign Aid Tools                                                        | 4  |  |  |

|   | 1.4  | Objectives   |                                                                       | 4  |  |  |

|   | 1.5  | Contributio  | ons                                                                   | 5  |  |  |

|   | 1.6  | Thesis Orga  | anization                                                             | 6  |  |  |

| 2 | Prol | olem Definit | tion                                                                  | 7  |  |  |

|   | 2.1  |              | on                                                                    | 8  |  |  |

|   | 2.2  |              | ectronics's Multiprocessor Architectures                              | 8  |  |  |

|   |      |              | P70 Processor                                                         | 8  |  |  |

|   |      | 2.2.2 STH    | HORM Many-Core Processor                                              | 9  |  |  |

|   |      | 2.2.2        | ·                                                                     | 9  |  |  |

|   |      | 2.2.2        | 2.2 STHORM Programming Models                                         | 10 |  |  |

|   |      | 2.2.3 STxI   | P70 ASMP                                                              | 10 |  |  |

|   |      | 2.2.3        | 3.1 STxP70 ASMP Architecture                                          | 10 |  |  |

|   |      | 2.2.3        | 3.2 STxP70 ASMP Programming Model                                     | 11 |  |  |

|   | 2.3  | Critical Cas | se Study: Parallelization of a Face Detection Application on STHORM . | 11 |  |  |

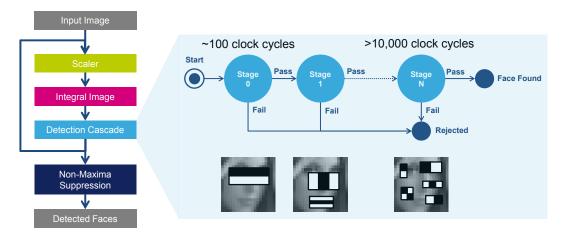

|   |      | 2.3.1 App    | olication Description                                                 | 12 |  |  |

|   |      | 2.3.2 Metl   | chodology                                                             | 14 |  |  |

|   |      | 2.3.3 Hot-   | -Spot Analysis                                                        | 14 |  |  |

|   |      | 2.3.4 Para   | allel Implementation on STHORM                                        | 15 |  |  |

|   |      | 2.3.4        | 4.1 Partitioning into OpenCL Kernels                                  | 15 |  |  |

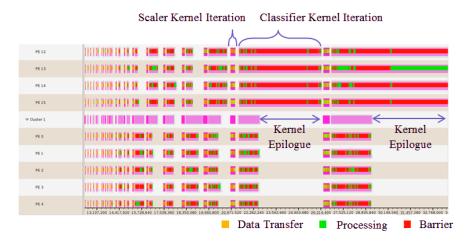

|   |      | 2.3.4        | 4.2 Scaler Kernel                                                     | 15 |  |  |

|   |      | 2.3.4        | 4.3 Classifier Kernel                                                 | 16 |  |  |

|   |      | 2.3.4        | 4.4 Data Management                                                   | 17 |  |  |

|   |      | 2.3.5 Expe   | perimental Setup                                                      | 17 |  |  |

|   |      | 2.3.6 Resu   | ults                                                                  | 18 |  |  |

|   |      | 2.3.6        | 6.1 Performance Measurements                                          | 18 |  |  |

|   |      | 2.3.6        | 6.2 Detailed Analysis                                                 | 19 |  |  |

|   |      | 2.3.6        | 6.3 Discussion                                                        | 19 |  |  |

|   | 2.4  | Observed Is  | ssues                                                                 | 20 |  |  |

|   | 2.5  | Design Cha   | allenges                                                              | 21 |  |  |

|   | 2.6  | Conclusion   |                                                                       | 22 |  |  |

| 3 | Bacl | kgroun         | d and Related Work                                    | 23 |  |  |  |  |  |  |  |

|---|------|----------------|-------------------------------------------------------|----|--|--|--|--|--|--|--|

|   | 3.1  | 1 Introduction |                                                       |    |  |  |  |  |  |  |  |

|   | 3.2  | Embe           | dded Computer Vision                                  | 24 |  |  |  |  |  |  |  |

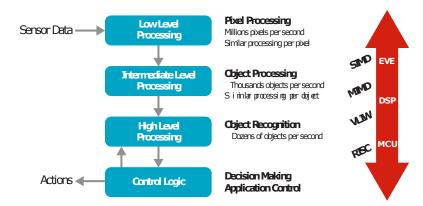

|   |      | 3.2.1          | Concepts and Characteristics                          | 24 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.1 Vision Processing Levels                      | 24 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.2 Data Dependency                               | 26 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.3 Data Locality                                 | 26 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.4 Scale and rotation invariance                 | 27 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.5 Sliding Window                                | 27 |  |  |  |  |  |  |  |

|   |      |                | 3.2.1.6 Tiling and Data Partitioning                  | 28 |  |  |  |  |  |  |  |

|   |      | 3.2.2          | Computer Vision Libraries                             | 29 |  |  |  |  |  |  |  |

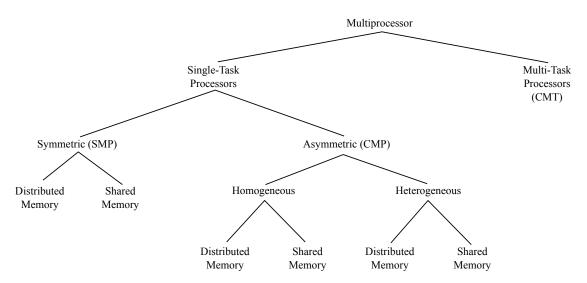

|   | 3.3  | Multip         | processor Architectures for Vision                    | 31 |  |  |  |  |  |  |  |

|   |      | 3.3.1          | Definitions                                           | 31 |  |  |  |  |  |  |  |

|   |      |                | 3.3.1.1 Taxonomy                                      | 31 |  |  |  |  |  |  |  |

|   |      | 3.3.2          | Vision Processors                                     | 32 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.1 Processors with Specialized Instruction Sets  | 33 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.2 Processors with Coupled Hardware Accelerators | 33 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.3 Processors with VLIW/SIMD Accelerators        | 33 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.4 VLIW/SIMD Vector Processors                   | 33 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.5 Vision MPSoCs                                 | 33 |  |  |  |  |  |  |  |

|   |      |                | 3.3.2.6 Discussion                                    | 34 |  |  |  |  |  |  |  |

|   | 3.4  | Embe           | dded Software Parallelization                         | 34 |  |  |  |  |  |  |  |

|   |      | 3.4.1          | Parallelism Classes                                   | 34 |  |  |  |  |  |  |  |

|   |      | 3.4.2          | Maximum Parallel Speedup                              | 35 |  |  |  |  |  |  |  |

|   |      | 3.4.3          | Performance Bottlenecks                               | 36 |  |  |  |  |  |  |  |

|   |      | 3.4.4          | Parallel Programming Models                           | 36 |  |  |  |  |  |  |  |

|   |      |                | 3.4.4.1 OpenMP                                        | 36 |  |  |  |  |  |  |  |

|   |      |                | 3.4.4.2 OpenCL                                        | 38 |  |  |  |  |  |  |  |

|   |      |                | 3.4.4.3 Other Programming Models                      | 39 |  |  |  |  |  |  |  |

|   | 3.5  | Paralle        | el Performance Analysis and Estimation                | 40 |  |  |  |  |  |  |  |

|   |      | 3.5.1          | Parallelism Profiling                                 | 40 |  |  |  |  |  |  |  |

|   |      |                | 3.5.1.1 Profiling Analysis                            | 41 |  |  |  |  |  |  |  |

|   |      |                | 3.5.1.2 Instrumentation and Data Acquisition          | 42 |  |  |  |  |  |  |  |

|   |      | 3.5.2          | Parallelism Discovery and Bounds                      | 42 |  |  |  |  |  |  |  |

|   |      | 3.5.3          | Parallel Speedup Prediction                           | 43 |  |  |  |  |  |  |  |

|   |      | 3.5.4          | Limitations of Current Approaches                     | 44 |  |  |  |  |  |  |  |

|   | 3.6  | Conclusion                                                       | 44 |

|---|------|------------------------------------------------------------------|----|

| 4 | App  | ication and Multiprocessor Platform Characterization             | 47 |

|   | 4.1  | Introduction                                                     | 48 |

|   | 4.2  | Overview of the Characterization Flow                            | 49 |

|   | 4.3  | Function Call Tree Profile                                       | 51 |

|   | 4.4  | Source Code Instrumentation                                      | 51 |

|   | 4.5  | Task Trace Acquisition                                           | 53 |

|   |      | 4.5.1 Task Trace Format                                          | 53 |

|   |      | 4.5.2 File Based Task Trace Generation                           | 54 |

|   |      | 4.5.3 Instruction Based Task Trace Generation                    | 54 |

|   | 4.6  | Application Characterization and Profiling                       | 56 |

|   |      | 4.6.1 Profiling                                                  | 56 |

|   |      | 4.6.2 Video Analytics Library (VAL)                              | 56 |

|   | 4.7  | Multiprocessor Platform Characterization                         | 57 |

|   |      | 4.7.1 Platform Characterization Parameters                       | 57 |

|   |      | 4.7.2 Microbenchmarks                                            | 57 |

|   |      | 4.7.3 Parallel Runtime Characterization                          | 59 |

|   |      | 4.7.3.1 Characterization of OpenMP parallel regions              | 59 |

|   |      | 4.7.3.2 Characterization of OpenMP parallel for loop scheduling  | 60 |

|   |      | 4.7.3.3 Characterization of OpenMP synchronization directives    | 60 |

|   |      | 4.7.3.4 Automating the Parallel Runtime Characterization Process | 61 |

|   |      | 4.7.3.5 Parallel Runtime Characterization Results                | 61 |

|   |      | 4.7.4 Memory Characterization                                    | 62 |

|   |      | 4.7.4.1 Memory Read Latency Characterization                     | 62 |

|   |      | 4.7.4.2 Memory Write Latency Characterization                    | 62 |

|   |      | 4.7.4.3 Memory Characterization Results                          | 63 |

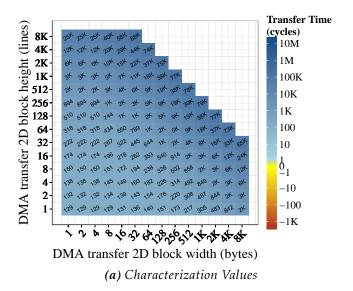

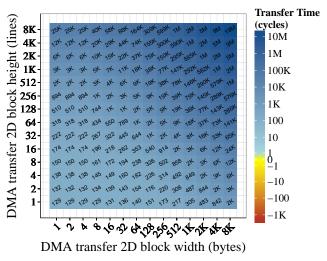

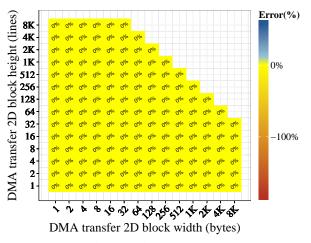

|   |      | 4.7.5 DMA Characterization                                       | 63 |

|   |      | 4.7.5.1 DMA Data Transfer Time Measurements                      | 63 |

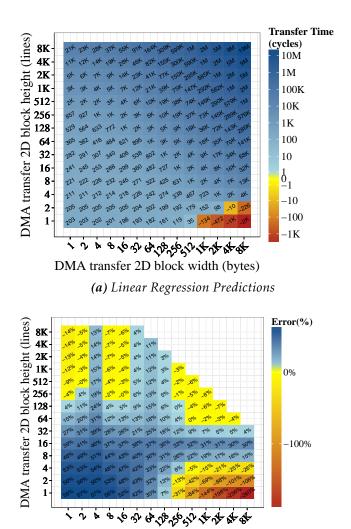

|   |      | 4.7.5.2 Linear Regression Model                                  | 64 |

|   |      | 4.7.5.3 Mixed Interpolation/Regression Model                     | 65 |

|   | 4.8  | Conclusion                                                       | 68 |

| 5 | Para | lel Performance Prediction                                       | 69 |

|   | 5.1  | Introduction                                                     | 70 |

|   | 5.2  | Overview of the Proposed Flow                                    | 70 |

|   | 5.3        | 5.3 Parallel Scenario Specifications               |                                                             |  |  |  |

|---|------------|----------------------------------------------------|-------------------------------------------------------------|--|--|--|

|   | 5.4        | Paran                                              | a                                                           |  |  |  |

|   |            | 5.4.1                                              | Performance Modeling                                        |  |  |  |

|   |            |                                                    | 5.4.1.1 Definitions                                         |  |  |  |

|   |            |                                                    | 5.4.1.2 Performance Estimation Steps                        |  |  |  |

|   |            |                                                    | 5.4.1.3 Memory Latency Modeling                             |  |  |  |

|   |            |                                                    | 5.4.1.4 Task Scheduling                                     |  |  |  |

|   |            | 5.4.2                                              | Parallelization Analysis Report                             |  |  |  |

|   | 5.5        | Exper                                              | imental Setup                                               |  |  |  |

|   |            | 5.5.1                                              | Platform Architecture                                       |  |  |  |

|   |            | 5.5.2                                              | Execution Vehicles                                          |  |  |  |

|   |            | 5.5.3                                              | Applications                                                |  |  |  |

|   | 5.6        | Result                                             | ts 81                                                       |  |  |  |

|   |            | 5.6.1                                              | Speedup Estimates                                           |  |  |  |

|   |            | 5.6.2                                              | Execution Time                                              |  |  |  |

|   |            | 5.6.3                                              | Key Benefits                                                |  |  |  |

|   |            | 5.6.4                                              | Known Limitations                                           |  |  |  |

|   | 5.7        | Concl                                              | usion                                                       |  |  |  |

| 6 | T a        | as Tils                                            | Sizing Based on Non-Linear Constraints 87                   |  |  |  |

| O | 6.1        | _                                                  | Sizing Based on Non-Linear Constraints 87  duction          |  |  |  |

|   | 6.2        |                                                    | em Definition                                               |  |  |  |

|   | 0.2        |                                                    |                                                             |  |  |  |

|   |            | 6.2.1                                              | Target Multiprocessor Architecture and Programming Model 90 |  |  |  |

|   |            | 6.2.2                                              | Application Kernel Tiling as a Software Pipeline            |  |  |  |

|   | ( )        | 6.2.3                                              | Finding the Optimal Tiling Parameters                       |  |  |  |

|   | 6.3        |                                                    | ninaries                                                    |  |  |  |

|   |            | 6.3.1                                              | Input Parameters                                            |  |  |  |

|   |            | ( 2 2                                              | 10                                                          |  |  |  |

|   |            | 6.3.2                                              | Iteration and data footprint spaces                         |  |  |  |

|   | <i>c</i> 1 | 6.3.3                                              | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu                                     | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu<br>6.4.1                            | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu<br>6.4.1<br>6.4.2                   | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu<br>6.4.1<br>6.4.2<br>6.4.3          | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4 | Tile types                                                  |  |  |  |

|   | 6.4        | 6.3.3<br>Execu<br>6.4.1<br>6.4.2<br>6.4.3          | Tile types                                                  |  |  |  |

|   | 6.5                                                        | Consti   | raint Optimization                                  | 100   |  |  |  |

|---|------------------------------------------------------------|----------|-----------------------------------------------------|-------|--|--|--|

|   |                                                            | 6.5.1    | Objectives                                          | 100   |  |  |  |

|   |                                                            | 6.5.2    | Constrained Optimization Problem Definition         | . 101 |  |  |  |

|   |                                                            | 6.5.3    | Constraint Propagation, Solving and Optimization    | 102   |  |  |  |

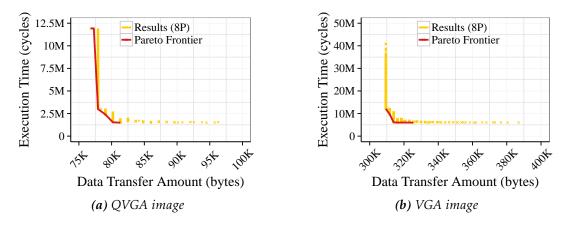

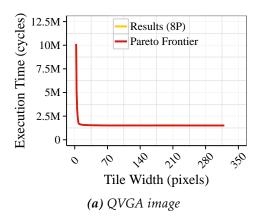

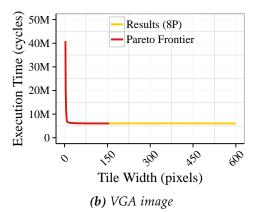

|   | 6.6                                                        | Result   | s                                                   | 102   |  |  |  |

|   |                                                            | 6.6.1    | Experimental Setup                                  | 102   |  |  |  |

|   |                                                            | 6.6.2    | Performance Analysis                                | 103   |  |  |  |

|   |                                                            | 6.6.3    | Exploring Implementation Trade-offs                 | . 104 |  |  |  |

|   |                                                            | 6.6.4    | Execution Time versus Transferred Data or Tile Size | 105   |  |  |  |

|   | 6.7                                                        | Conclu   | usion                                               | 106   |  |  |  |

| 7 | Con                                                        | clusion  | as and Perspectives                                 | 109   |  |  |  |

|   | 7.1 Conclusions                                            |          |                                                     |       |  |  |  |

|   | 7.2                                                        | Future   | e Work                                              | . 111 |  |  |  |

| A | Exar                                                       | nple of  | a Parana's Parallelization Analysis Report          | 113   |  |  |  |

| R | Evar                                                       | nnle of  | a Parana's Application Profile Report               | 121   |  |  |  |

| D | LAUI                                                       | iipic oi | a rurana s apprication r rome report                | 121   |  |  |  |

| C | List of Tiling Parameters and Mathematical Definitions     |          |                                                     |       |  |  |  |

| D | D List of State of the Art Vision Processors and MPSoCs 13 |          |                                                     |       |  |  |  |

|   | 10.                                                        |          |                                                     |       |  |  |  |

|   | Glos                                                       | ssary    |                                                     | 133   |  |  |  |

|   | Pub                                                        | licatior | ns and Other Scientific Activities                  | 135   |  |  |  |

|   | D (                                                        |          |                                                     |       |  |  |  |

|   | Kete                                                       | erences  |                                                     | 137   |  |  |  |

# **List of Figures**

| R.1 | Aperçu des quatre pas du flot proposé pour l'estimation de la performance parallèle d'une application et l'exploration de l'espace de conception avec Parana                                                                                                                                                                                                                                                                                                                                           | viii |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| R.2 | Aperçu du concept de pipeline de tuilage d'image                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xiii |

| R.3 | Gabarit de l'architecture du STxP70 ASMP                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xiv  |

| R.4 | Comparaison du facteur d'accélération obtenu avec Parana, le simulateur <i>cycle-approximate</i> Gepop (référence pour l'acquisition de traces pour Parana) et un prototype FPGA, pour le benchmark NPB Integer Sort(IS) et le détecteur de points caractéristiques FAST. Gauche : facteurs d'accélération pour 1 à 8 coeurs. Centre : erreur relative au facteur d'accélération obtenu avec Gepop. Droite : <i>Cycle stacks</i> qui montrent la répartition par catégorie des cycles de l'application | xv   |

| 2.1 | STHORM many-core architecture block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9    |

| 2.2 | Architectural template of the STxP70 ASMP                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11   |

| 2.3 | Face detection algorithm's main steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12   |

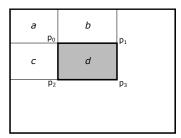

| 2.4 | Integral image and a region of interest                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13   |

| 2.5 | Multiscale processing via a series of lower resolution images forming an image pyramid                                                                                                                                                                                                                                                                                                                                                                                                                 | 13   |