# Low power application architecture adaptation using SMT solvers

Émilien Kofman

### ► To cite this version:

Émilien Kofman. Low power application architecture adaptation using SMT solvers. Other [cs.OH]. COMUE Université Côte d'Azur (2015 - 2019), 2017. English. NNT: 2017AZUR4009. tel-01534440

### HAL Id: tel-01534440 https://theses.hal.science/tel-01534440

Submitted on 7 Jun2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. UNIVERSITÉ CÔTE D'AZUR

### ÉCOLE DOCTORALE STIC

SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

## ΤΗÈSΕ

pour l'obtention du grade de docteur en sciences

de l'Université Côte d'Azur Mention : Informatique

présentée et soutenue par Émilien Kofman

## Low Power Application Architecture Adaptation using SMT solvers

Adéquation Algorithme Architecture automatisée par solveur SMT

Dirigée par: Robert de Simone et François Verdier

Soutenue le 27 Février 2017 à Sophia Antipolis Devant un jury composé de:

| Mme Florence Maraninchi  | Prof.               | INP Grenoble       | Rapporteur  |

|--------------------------|---------------------|--------------------|-------------|

| M Xavier Thirioux        | MCF                 | ENSEEIHT           | Rapporteur  |

| M Rolf Drechsler         | Prof.               | DFKI Bremen        | Examinateur |

| M Dumitru Potop-Butucaru | $\operatorname{CR}$ | <b>INRIA</b> Paris | Examinateur |

| M Robert de Simone       | DR                  | INRIA Sophia       | Directeur   |

| M François Verdier       | Prof.               | UNS                | Directeur   |

## Contents

| 1 | Bac | kgrour | nd on model-based, platform-based design and AAA                                                                 | 15 |

|---|-----|--------|------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | Platfo | rm based design                                                                                                  | 15 |

|   |     | 1.1.1  | The adequation problem                                                                                           | 16 |

|   |     | 1.1.2  | Motivations to the use of models                                                                                 | 16 |

|   | 1.2 | Applic | ation modeling                                                                                                   | 16 |

|   |     | 1.2.1  | Jobs, Agents, Processes and Tasks                                                                                | 17 |

|   |     | 1.2.2  | Graph models                                                                                                     | 18 |

|   |     |        | 1.2.2.1 Dataflow Process Networks                                                                                | 18 |

|   |     |        | 1.2.2.2 Structured graphs                                                                                        | 19 |

|   |     |        | 1.2.2.3 Conflict freeness / functional determinism / latency insensitivity                                       | 20 |

|   |     | 1.2.3  | Relations to general purpose languages                                                                           | 22 |

|   | 1.3 | Applic | ation requirement modeling                                                                                       | 23 |

|   |     | 1.3.1  | Preemption and migration                                                                                         | 23 |

|   |     |        | 1.3.1.1 non-preemptive task models                                                                               | 23 |

|   |     |        | 1.3.1.2 Preemptive task models                                                                                   | 23 |

|   |     | 1.3.2  | Periodicity                                                                                                      | 24 |

|   |     | 1.3.3  | Objective functions                                                                                              | 25 |

|   | 1.4 | Archit | ecture modeling                                                                                                  | 25 |

|   |     | 1.4.1  | Architecture modeling in real-time theory                                                                        | 25 |

|   |     |        | 1.4.1.1 Resources                                                                                                | 26 |

|   |     |        | 1.4.1.2 Communications $\ldots$ | 26 |

|   |     | 1.4.2  | Computer architecture classification in practice                                                                 | 26 |

|   |     |        | 1.4.2.1 Resources $\ldots$      | 27 |

|   |     |        | 1.4.2.2 Communications $\ldots$ | 27 |

|   |     |        | 1.4.2.3 Extracting some knowledge                                                                                | 28 |

|   |     | 1.4.3  | Power saving mechanisms                                                                                          | 29 |

|   |     |        | 1.4.3.1 Dynamic Voltage and Frequency Scaling                                                                    | 29 |

|   |     |        | 1.4.3.2 Power gating $\ldots$                                                                                    | 30 |

|   |     |        | 1.4.3.3 Motivating example                                                                                       | 31 |

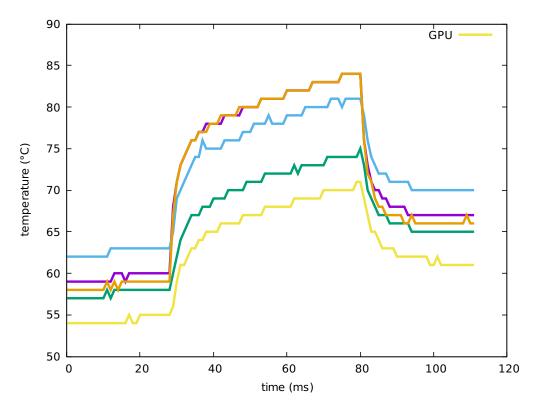

|   |     | 1.4.4  | Temperature modeling                                                                                             | 31 |

|   | 1.5 |        | ng approaches to AAA                                                                                             | 32 |

|   |     | 1.5.1  | Discrete Event models and test by simulation                                                                     | 32 |

|   |     | 1.5.2  | Analytic approaches                                                                                              | 32 |

|   |     | 1.5.3  | Heuristics                                                                                                       | 33 |

|   |     | 1.5.4  | Energy concerns                                                                                                  | 34 |

|   |     | 1.5.5  | Structure and syntax of the result                                                                               | 34 |

|   | 1.6 | Auton  | nated reasoning and solvers                                                                                      | 35 |

|          |     | 1.6.1  | Computer algebra systems                                                                                                                            |

|----------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 1.6.2  | Solvers and methods for categorized mathematical problems                                                                                           |

|          |     | 1.6.3  | Using SMT solvers for automated adequation                                                                                                          |

|          |     |        | 1.6.3.1 Linear programming aspects of AAA                                                                                                           |

|          |     |        | 1.6.3.2 Combinatorial optimization aspects of AAA                                                                                                   |

|          | 1.7 | Relate | ed work                                                                                                                                             |

|          |     | 1.7.1  | Application modeling                                                                                                                                |

|          |     | 1.7.2  | Architecture modeling                                                                                                                               |

|          |     | 1.7.3  | Provisions modeling                                                                                                                                 |

|          |     | 1.7.4  | Solving the adequation problem                                                                                                                      |

|          | 1.8 | Our co | ontributions $\ldots \ldots \ldots$ |

|          |     | 1.8.1  | The SymSched tool, a general presentation                                                                                                           |

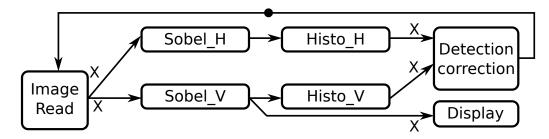

|          |     | 1.8.2  | A running example                                                                                                                                   |

|          | -   |        |                                                                                                                                                     |

| <b>2</b> | •   |        | l modeling and model translation to system of constraints 45                                                                                        |

|          | 2.1 | U      | ched application model                                                                                                                              |

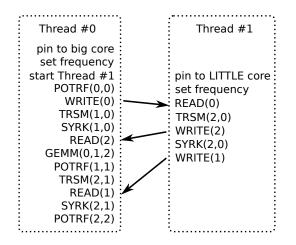

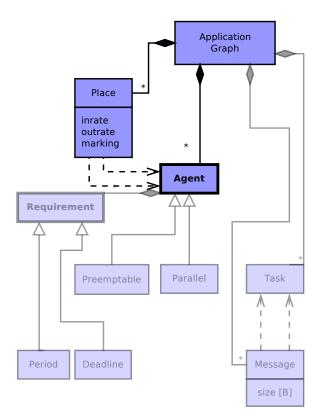

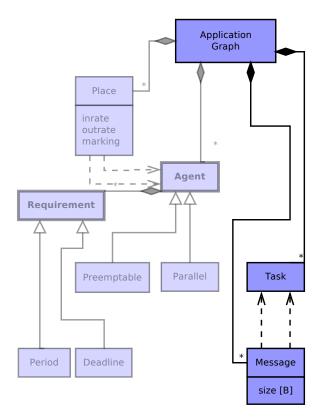

|          |     | 2.1.1  | SymSched task graph meta models                                                                                                                     |

|          |     |        | 2.1.1.1 Agents and Tasks                                                                                                                            |

|          |     |        | 2.1.1.2 Places and Messages                                                                                                                         |

|          |     |        | 2.1.1.3 Loop constructs                                                                                                                             |

|          |     |        | 2.1.1.4 Parallel agents                                                                                                                             |

|          |     |        | 2.1.1.5 Preemptable agents                                                                                                                          |

|          |     | 2.1.2  | Requirements                                                                                                                                        |

|          |     |        | 2.1.2.1 Periodicity                                                                                                                                 |

|          |     |        | 2.1.2.2 Objective functions                                                                                                                         |

|          |     | 2.1.3  | Application transformation to a solver input                                                                                                        |

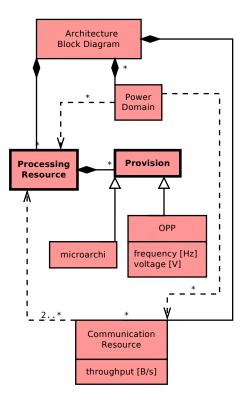

|          | 2.2 | -      | ched Architecture model                                                                                                                             |

|          |     | 2.2.1  | Processing resources                                                                                                                                |

|          |     | 2.2.2  | Communication resources                                                                                                                             |

|          |     | 2.2.3  | Provisions                                                                                                                                          |

|          |     |        | 2.2.3.1 Computing and communication throughput                                                                                                      |

|          |     |        | 2.2.3.2 Power Domains                                                                                                                               |

|          |     | 0.0.1  | 2.2.3.3 Layout and temperature issues                                                                                                               |

|          | 0.0 | 2.2.4  | Architecture transformation to a solver input                                                                                                       |

|          | 2.3 | e e    | ched Adequation model                                                                                                                               |

|          |     | 2.3.1  | Adequation costs (solver input)                                                                                                                     |

|          |     | 2.3.2  | Orthogonality and composability of the models                                                                                                       |

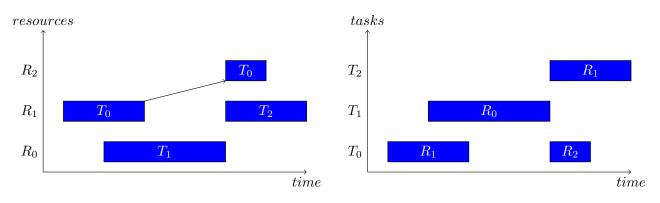

|          |     | 2.3.3  | Mapping representation (solver output)                                                                                                              |

|          |     | 2.3.4  | Comments on expressiveness                                                                                                                          |

|          |     |        | 2.3.4.1 Limitations of the SDF model                                                                                                                |

|          |     |        | $2.3.4.2  \text{Data parallelism}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                 |

|          |     |        | 2.3.4.3 Pre-calculated preemption                                                                                                                   |

|          |     |        | 2.3.4.4 Periodicity                                                                                                                                 |

|          |     |        | 2.3.4.5 Combining agent models and requirements                                                                                                     |

| 3            | Usi  | ng solvers for AAA: lessons learned 69                                                                                                                                       |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 3.1  | Practical aspects of the modeling                                                                                                                                            |

|              |      | 3.1.1 Time discretization $\ldots \ldots \ldots$             |

|              |      | 3.1.2 Modeling cyber physical systems                                                                                                                                        |

|              | 3.2  | Scalability                                                                                                                                                                  |

|              |      | 3.2.1 Independent tasks $\ldots \ldots \ldots$               |

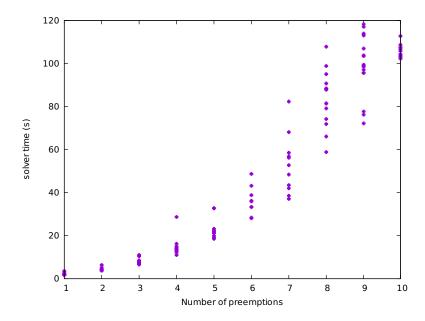

|              |      | 3.2.2 Preemptable agents                                                                                                                                                     |

|              |      | 3.2.3 Parallel agents                                                                                                                                                        |

|              |      | 3.2.4 Optimization and convergence speed                                                                                                                                     |

|              | 3.3  | Symmetry breaking                                                                                                                                                            |

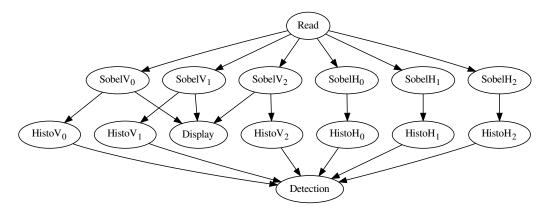

|              |      | 3.3.1 The Platooning application                                                                                                                                             |

|              |      | 3.3.1.1 Symmetries in the application model                                                                                                                                  |

|              |      | 3.3.1.2 Symmetries in the architecture model                                                                                                                                 |

|              | 3.4  | Realistic use cases                                                                                                                                                          |

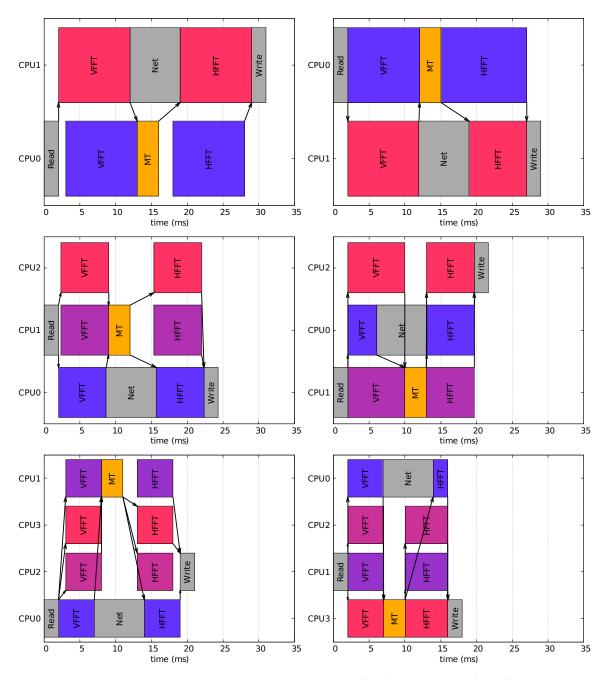

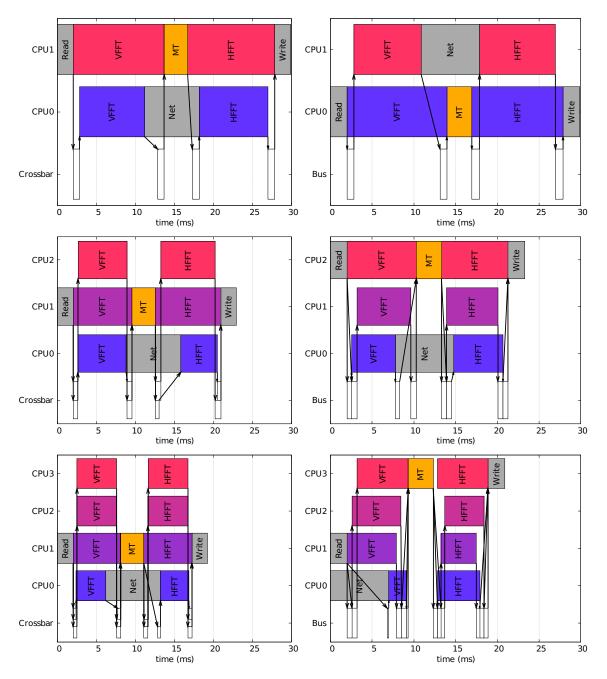

|              | 0.1  | 3.4.1 Fast Fourier Transform application                                                                                                                                     |

|              |      | 3.4.2 Radar application                                                                                                                                                      |

|              | 3.5  | Real use-case   81                                                                                                                                                           |

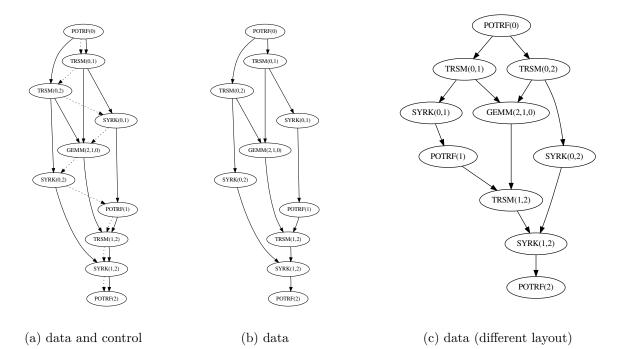

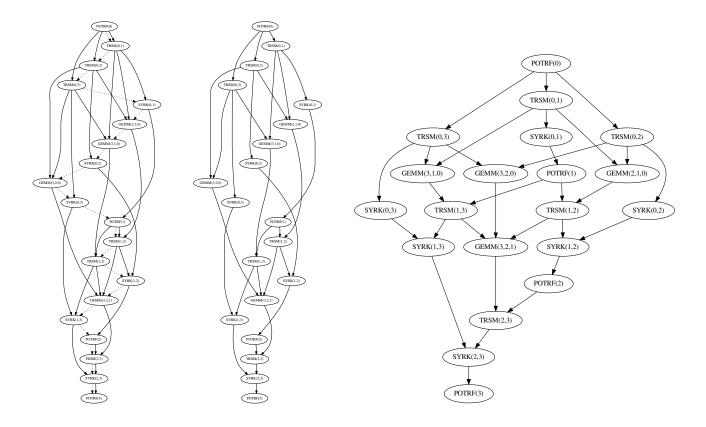

|              | 0.0  | 3.5.1 Cholesky matrix decomposition                                                                                                                                          |

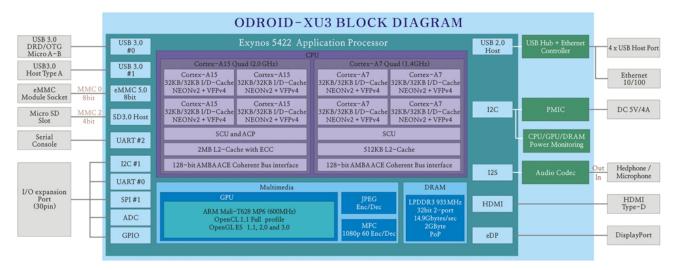

|              |      | 3.5.2 Experimental setup: The ARM big.LITTLE platform                                                                                                                        |

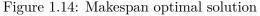

|              |      | 3.5.3 Practical aspects of meta programming                                                                                                                                  |

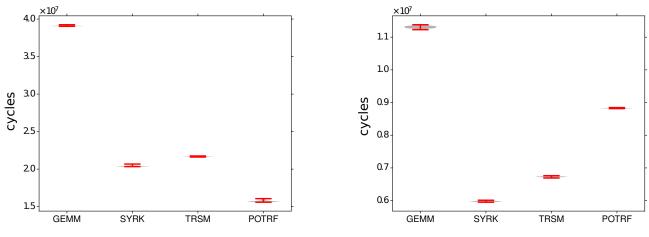

|              |      | 3.5.3.1 Kernel cost estimations                                                                                                                                              |

|              |      |                                                                                                                                                                              |

|              |      |                                                                                                                                                                              |

|              |      |                                                                                                                                                                              |

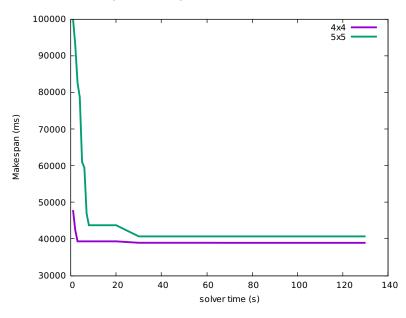

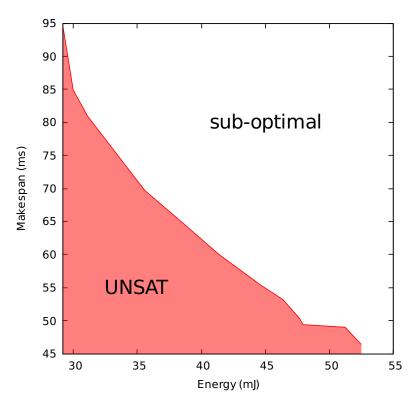

|              |      | 3.5.4.1 Multiobjective optimization                                                                                                                                          |

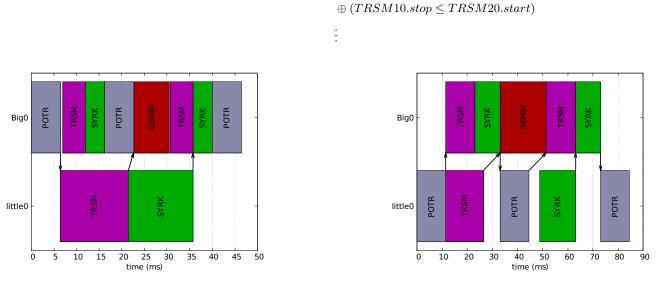

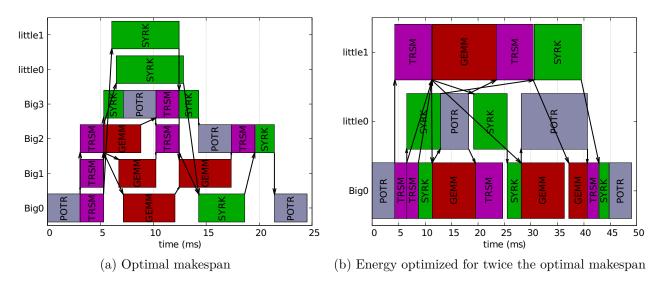

|              |      | 3.5.4.2 Makespan optimization                                                                                                                                                |

|              |      | 3.5.4.3 Energy optimization                                                                                                                                                  |

|              | 0.0  | $3.5.4.4$ Further scalability results $\ldots \ldots \ldots$ |

|              | 3.6  | Summary on the SymSched approach                                                                                                                                             |

|              | 3.7  | Conclusion and future work                                                                                                                                                   |

| A            | ppen | dices 91                                                                                                                                                                     |

| $\mathbf{A}$ |      | le samples 93                                                                                                                                                                |

|              |      | Stress test examples                                                                                                                                                         |

|              |      | Calls to the GNU Scientific library                                                                                                                                          |

|              | A.3  | Calls to the perf API                                                                                                                                                        |

|              |      | A.3.1 Setting up performance counters on Odroid XU3                                                                                                                          |

|              |      | A.3.2 Using the C perf API                                                                                                                                                   |

|              | A.4  | A Proof of concept using z3                                                                                                                                                  |

|              | A.5  | Generated constraints Cholesky big.LITTLE 1+1, 3 tiles                                                                                                                       |

|              | A.6  | Solver logs and relevant tactics descriptions                                                                                                                                |

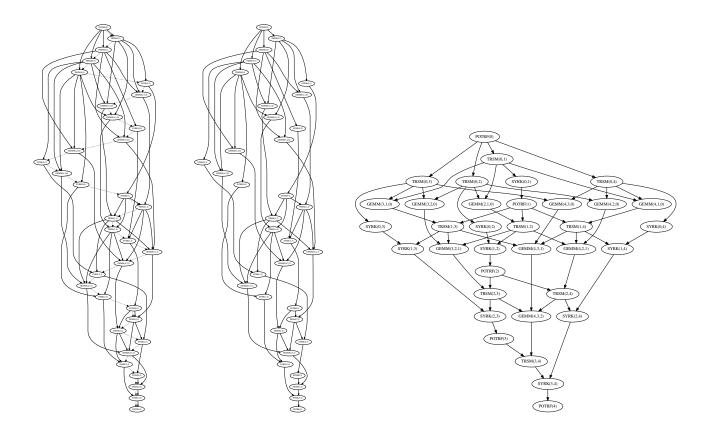

| в            | App  | plication graphs and gantt diagrams 97                                                                                                                                       |

|              | B.1  | Tiled cholesky         97                                                                                                                                                    |

|              | B.2  | Radar application                                                                                                                                                            |

### Résumé

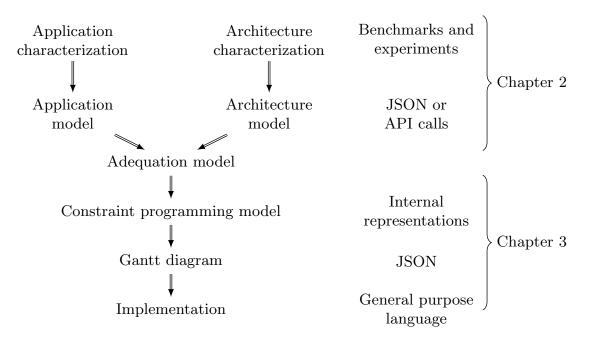

Nous décrivons la méthode Symsched et l'environnement de conception AAA (Adéquation Algorithme Architecture). Cette méthodologie permet d'évaluer les compromis énergie/performance pour un système embarqué. Nous transformons les composants du problème (exigences de l'application et capacités de l'architecture) en un système d'équations et inéquations sur des variables entières pour la modélisation des aspects temporels et sur des variables booléennes pour modéliser les alternative de placement des tâches et de niveau de performance des ressources. Le modèle mathématique généré est ensuite soumis à un solveur SMT (SAT Modulo Theories). Nous étudions le passage à l'échelle de cette approche et ses compromis avec l'expressivité des modèles. Enfin nous appliquons ces outils à des problèmes d'ordonnancement sur des cas synthétiques, réalistes et réels.

Ce travail a bénéficié d'une aide de l'Etat gérée par l'Agence Nationale de la Recherche au titre du programme "Investissements d'Avenir" portant la référence : ANR-11-LABX-0031-01.

### Abstract

We describe the Symsched methodology and environment for AAA design (Application Architecture Adequation). It allows to evaluate the energy/performance balance for a given embedded system. We translate the different components of the problem (application requirements et architecture provisions) in a system of equations and inequations made of integer variables for the modeling of temporal aspects and boolean variables for the modeling of admissible task mapping and resource states. We then submit this problem to an automatic search engine SMT solver (SAT Modulo Theories). We study the scalability of this methodology and its compromises with models expressiveness. We then study synthetic, realistic and real scheduling problems using this approach.

This work was partly funded by the French Government (National Research Agency, ANR) through the "Investments for the Future" Program reference ANR-11-LABX-0031-01.

### Remerciements

Ce travail n'aurait pas été accompli sans le support de ma famille, mes amis et mes collègues. J'essaye dans ces quelques lignes de leur exprimer ma gratitude.

Je remercie mon directeur Robert de Simone pour sa présence, sa confiance et sa motivation, mais également son sens de l'humour sans limite. J'ai par ailleurs apprécié les remarques de mon co-directeur François Verdier et la flexibilité qu'il m'a accordé ces trois dernières années. Je remercie Florence Maraninchi et Xavier Thirioux pour avoir accepté de relire mon manuscrit et d'assister à la soutenance. Merci également à Rolf Drechsler pour avoir accepté de faire partie de mon jury. J'ai également beaucoup apprécié les discussions que nous avons eu avec Dumitru Potop-Butucaru pendant ma troisième année et je suis heureux qu'il soit venu examiner ma soutenance.

Bien entendu je n'oublie pas les collègues de l'équipe AOSTE impliqués dans cette aventure. Je pense tout d'abord à Jean-Vivien Millo que je remercie pour m'avoir très largement mis sur les rails avec une énergie débordante, malgré nos nombreux désaccords et discussions. Je pense aussi à Julien Deantoni avec qui nous avons beaucoup échangé sur des sujets scientifiques au delà de notre domaine d'investigation habituel, parfois simplement par curiosité scientifique. Merci aux autres collègues de l'équipe (y compris les éphémères) pour leur bonne humeur et leur convivialité. Pendant ces trois ans à l'INRIA j'ai également eu l'opportunité d'enseigner à l'école Polytech'Nice sous la direction de Sébastien Bilavarn. Malgré mon anxiété initiale, Sebastien en a fait une expérience agréable et très enrichissante.

Il y a un temps indispensable en dehors du labo que j'ai pris beaucoup de plaisir à partager avec mes amis et ma famille. Merci à Jonathan Viquerat pour avoir supporté mes hauts, mes bas, et les transitions. Je remercie également Camille Sulkowski pour m'avoir fait partager avec lui des moments chaleureux. J'ai également une pensée pour mes amis de l'ASSA et les souvenirs forgés dans nos aventures verticales.

Les dernières lignes et non les moindres iront à ma famille. Merci beaucoup à ma mère et mon frère de supporter mes humeurs changeantes, mes lubies et mes bêtises depuis 26 ans. Leur soutien en particulier ces trois dernières années aura été d'une aide inestimable.

## Introduction

Embedded systems including consumer electronic devices are now very complex systems that may embed several subsystems and resources. For instance a smartphone is a modem, a camera, a video decoder, a GPS planer and much more. Those different resources have to synchronize, exchange data, and compute with very high data throughput. In the area of embedded systems the energy is limited, since the system is by definition not plugged into any outlet.

On the other hand, such devices are pushed to the extreme of decoding an ever increasing number of pixels in images and videos, running voice decoding, object detection, movement detection and signal processing applications, sometimes multitasking among those computationally intensive workloads. In order to satisfy the user, system architects must always offer more computing power.

The solution to raise the computing power of a machine has long been to run it faster, which in the computer science field consists in raising its frequency. It is well understood now that raising the frequency also increases power consumption roughly to the square, which raises also the temperature of the devices since this power is dissipated mainly into heat. In some domains of practical computer science (such as HPC) much effort is conducted towards cooling which is much harder in the area of embedded systems due to the physical limitations.

Another solution to raise the computing power is to distribute the work to multiple computing units. The recent and smaller transistors (expected 10nm in 2017) allow to cluster multiple resources in the same System on Chip (SoC). As a consequence, a typical smartphone CPU is not a single core system anymore (DSPs and GPUs are also often included). Those new upcoming architectures raise multiple issues that are still open research areas. Smaller transistors behave differently regarding energy consumption: recent studies show that leakage current is much higher with small transistors. As a consequence it needs to dissipate more power or to run at a lower frequency. Since the form factor of an embedded system limits the power dissipation, the latter is preffered. Furthermore, those multiple resources have to communicate in an efficient and predictable way. The typical unified and uniform memory architecture will not scale. System of chip architects still face the energy vs computing power compromise, which results in very complex, sometimes heterogeneous asymmetrical micro-architectures.

Various hardware architectures exist: embedded GPUs, heterogeneous multicores, networks on chip, and still no de-facto standard emerged. Those upcoming architectures will thus require different programming models, as the classical sequential languages does not allow to efficiently distribute the workload. Meta-programming is underused in the field of embedded systems (and HPC) although it is used efficiently in other fields such as web-design. This motivates us to investigate which models and which task scheduling and allocation policies can fit those new models.

In a typical server, desktop computer system or consumer electronics system such as smartphones and tablets, a user interacts with the device which can be modeled with sporadic job appearance. Deciding where and when to run those jobs has to be done while the system is running. This is commonly known as "dynamic or online scheduling". On contrary some usage of those devices (such as watching a video) does not involve user interaction as well as other embedded applications such as radars. In this case the system of jobs and resources can be analyzed at compile time, which is known as "static or offline scheduling". Because most often, very little is known about the work-load in dynamic scheduling problem, most of the platform-based design approaches focus on the latter.

The rest of this document is organized as follows:

- In the first Chapter we recall the fundamentals of model-based, platform-based design, and the Application-Architecture Adaptation (or Algorithm-Architecture Adequation) approach. We recall a number of modeling concepts involved. We do not seek here exhaustivity, but rather focus on proximity, and the description of previous efforts that were influential on our work. We end this chapter with a short, rather informal introduction to our SymSched formalism, so as to position it amongst these former references. We also introduce on an illustrative example how low-power modeling and low-power architectures raise specific issues for AAA.

- Chapter 2 is devoted to a presentation of our various models covering all aspects involved in the adequation mapping, and their (sketchy) metamodels (*applications, application requirements, architectures, architecture provisions, costs, mappings,...*). We also describe how these models translate into formulas that will be later input to automatic solvers. In addition, we comment at places on how this global objective of producing such constraint sets of equations led us to restrict or bend the modeling styles at all levels, while keeping in mind the concern for scalability of descriptions and tractability of analysis.

- in Chapter 3 we report on how automatic approaches (mostly SMT solvers) performed for this adequation mapping assignment. We first deal with simple, rather synthetic problems, in order to better tune modeling and analysis regarding complexity. We then show the actual feasability of our approach on non-trivial examples. We consider a number of modeling extensions and/or restrictions motivated by concrete concerns (to match existing architectures), some of them still unexplored. We conlcude with a critical assessment on our results and the projections that could be drawn from then.

- The conclusion section, which also points at several remaining challenges in the definition of proper adequation methods and use of automatic solving techniques, is followed in annex by material which could not fit into the main document body (large examples, interactive solver sessions,...)

### Chapter 1

## Background on model-based, platform-based design and AAA

In this chapter we recall the basics of Platform based design and Application Architecture Adequation <sup>1</sup> (AAA, Section 1.1). In Sections 1.2 and 1.4 we address application and architecture modeling in different fields of computer science, from theoretical scheduling to more practical programming models. Then we give an overview of the existing approaches for solving the adequation problem in Sections 1.7 and 1.5 and we detail our contributions in Section 1.8.

#### 1.1 Platform based design

Platform based design (or Y-chart design) is the general problem of obtaining a system implementation which satisfies a set of constraints and sometimes optimizes one or multiple criteria [82], this can also include hardware synthesis [44, 6, 4, 26]. This hardware and/or software synthesis is performed based on high level (most often abstract) "components" that first need to be associated with given metrics, such that the search can actually be performed. We usually call software components the tasks, and hardware components the resources. The analysis is a high level, not cycle accurate estimation, often performed on abstract models: it does not consider implementations of the components but only some of their characteristics. It is then the responsibility of the designer to make sure that the implementation of those components will perform as expected.

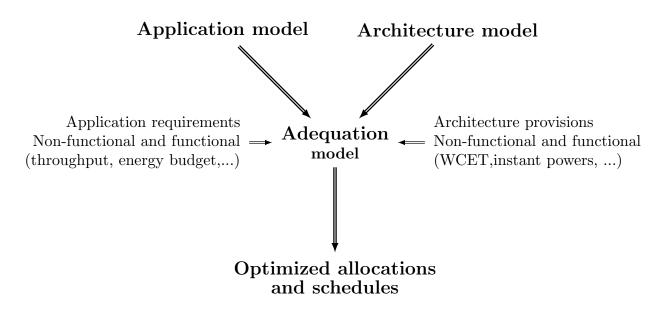

In the hardware synthesis community, exhaustive verification is not often feasible and the validation is most often a simulation of random or corner cases. Platform architects sometimes refer to a similar workflow (Figure 1.2) even though following the legacy practices of hardware design they do not consider the search step and most often perform simulation, using refined hardware components.

In the software engineering community, modeling software with a graph of components is not the mainstream technique. Classical approaches do not consider any architecture model neither, the programmer must be aware of it and must decide how to use it properly. Programmers put a strong focus on the functional aspect of the application and consider that an implementation is one more layer on top of a well separated stack of software layers. On the other side the communities of real-time scheduling, program optimization and parallel compilation study structured models of the software such as activity diagrams, task graphs, state machines, or abstract interpretations of existing software. It is thus an essential concern to bring together theoretical aspects of the latter with the

<sup>&</sup>lt;sup>1</sup>The methods advocating a global system view to the codesign of software and hardware, mainly in the area of embedded applications and architectures

technical aspects of the former. It requires first to identify the modeling granularity to extract a set of components, evaluate them according to relevant metrics, and finally connect or arrange them to achieve a given objective.

#### 1.1.1 The adequation problem

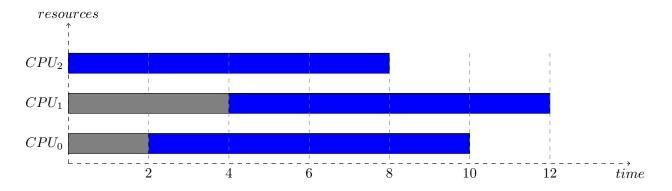

Adequation mostly focuses on adapting algorithms to best fit them on existing architectures although the same models of components is used to describe both architecture and application model. The result of the adequation is an optimized (or valid according to application requirements) task distribution in space (on the different resources) and time. Adequation problems do not consider that the designer is able to add or remove resources, or to connect them differently. Because the target, and thus the number and nature of resources is not any more a variable of the problem, the adequation is a subproblem of platform based design. Since the architectures must also be polyvalent because modifying it costs much more than modifying the software, adequation still remains an essential concern.

We call "allocation" the spatial distribution of the tasks on the resources, and we call "sequencing" the problem of sharing the available resource time in order to fit the allocated tasks. Finally, we call "adequation", or "scheduling" the overall problem of allocation and sequencing. We call "schedule" the result of a static scheduler.

#### 1.1.2 Motivations to the use of models

High level abstractions have long been considered a reason of impaired performance. Recent approaches to software optimization on specific problems such as FFT optimization [78] show on contrary that software optimization is not any more limited to low level implementations. Those high level approaches are welcome since low level programming is cumbersome on cutting edge complex systems. Moreover in the area of embedded and real-time systems, the specification often comes with real-time requirements and obtaining a valid implementation according to the specifications sometimes requires an optimization effort. Modeling and verification is thus a mandatory step towards a predictable and functional implementation.

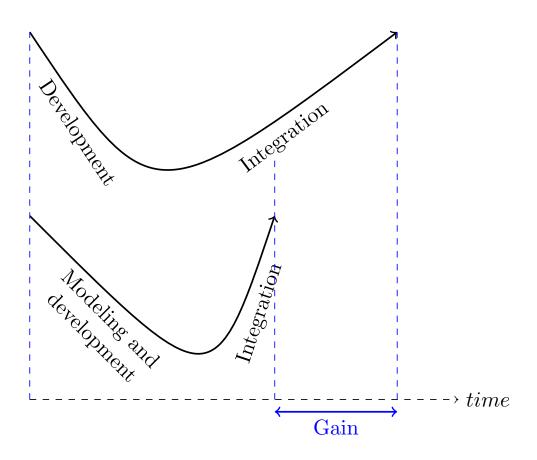

The separation of concerns in the modeling approach joins Model Driven Engineering ideas [83] with a strong focus on re-usability: although the Y-chart approach strictly focuses on software generation, using models and taking apart the application implementation from its target(s) brings portability. Figure 1.1 shows the classical V-shape project development curve with a traditional approach and with an MDE approach. In the last ten years, Model driven Engineering techniques have been used in other fields such as web design with great results. It is however underused in the domains of real-time and embedded systems.

The separation of concerns also allows to run analysis separately on both models, sometimes indicating that further implementation work is not desirable since for instance the application model alone already needs to be improved (or fixed, see Section 1.2.2.3). In the case of dataflow graphs models it is usual to check that the application graph contains no deadlock and has a sufficient maximum throughput before considering any implementation generation regarding the architecture model.

#### 1.2 Application modeling

The keys aspects of application concurrency modeling consists in being expressive enough to model different type of parallelism (task parallelism, data parallelism, and pipeline parallelism) including the ability to combine them hierarchically and sequentially and yet be simple enough to allow static analysis or automated adequation.

Figure 1.1: The benefits of Model Driven Engineering

In Section 1.2.1 we disambiguate some vocabulary. In Section 1.2.2 we describe different application graph models and their properties, and we try to fill the gap between theoretical graph models and programming languages in Section 1.2.3.

#### 1.2.1 Jobs, Agents, Processes and Tasks

The definitions of jobs and tasks depend on the communities and topics. In the field of theoretical scheduling it is generally assumed that a job is made of one or many "tasks" that execute only once such as in the open-shop scheduling problem [38] (or "operations" in the job-shop scheduling problem). A confusion exists regarding the notion of "periodic task" scheduling since a "periodic task" obviously yields a task each amount of time corresponding to the period. In the community of Dataflow Process Networks (DPN), a node of the process network is sometimes called an "agent" or a "process" and can be executed multiple times [62] as long as its input ports are provisioned. Sometimes an "agent" is called a "task" [87] which can introduce more confusions (since a "task graph" for instance could then have cycles). When it comes to practical aspects of software engineering, a "process" often consists in an executing program in the context of an operating system. This process can create other processes (or threads), and communicate with them (Inter Process Communication). Agents or tasks can thus be implemented as processes (or threads), which connects scheduling problems with the software engineering field. Another confusion arises since some celebrated frameworks that are used to build parallel implementations (such as OpenMP) also use the "task" keyword in their syntax [5].

Figure 1.2: The Ychart or AAA methodology

A compiled and optimized (non running) program which executes a basic computation is sometimes called a "kernel".

We adopt the "agent" keyword from the DPN and the definition of a non-preemptive "task" from the field of theoretical scheduling. The model of agent then defines the number, order (if they have dependencies) and costs of the tasks. A task is thus an instance or occurrence of agent. We call "kernel" the implementation of an agent. In our static scheduling approach an essential property of an agent is that even if it yields multiple tasks, we must be able to associate a cost to each of them (cf section 1.4). This means that the kernels implementing those agents must validate some properties, such as data independent behavior, predictable durations, no side effects... Typical examples kernels include dense linear algebra routines such as matrix operations, spectral methods, image or video processing operations.

#### 1.2.2 Graph models

Many scheduling approaches directly consider Direct Acyclic Graphs of tasks as an input of the problem [93, 3]. Agents can be connected together to form different types of graphs, for instance dataflow or control flow graphs.

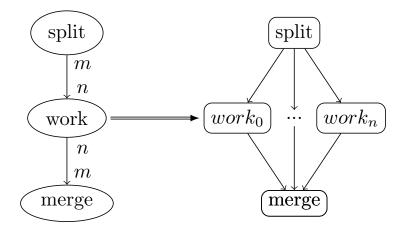

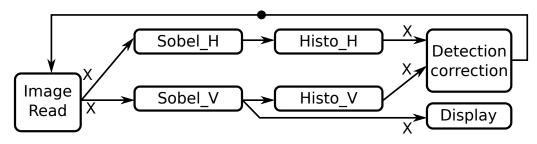

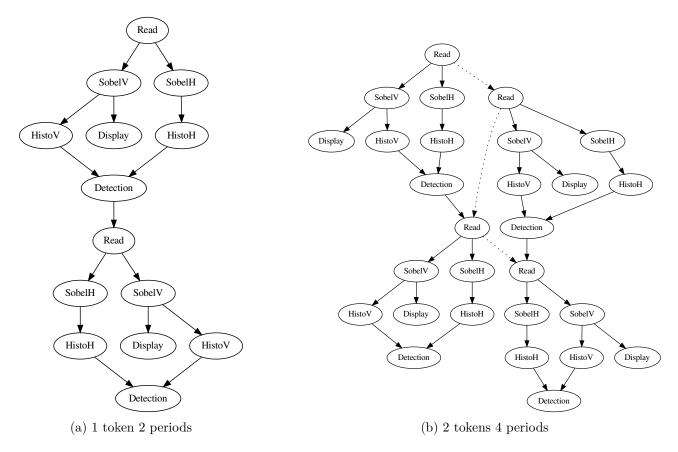

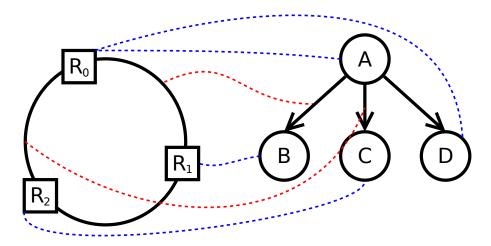

#### 1.2.2.1 Dataflow Process Networks

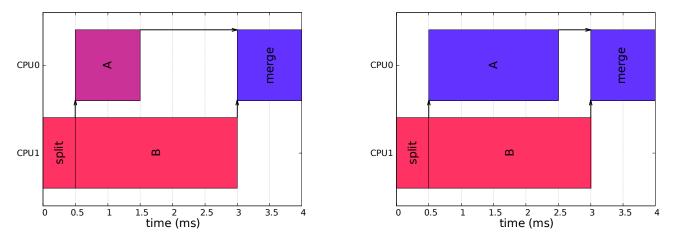

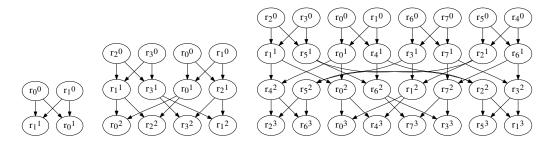

DPN sometimes include redundant or recursive task executions which is a relevant information for the analysis. This pattern can be captured by the model. The typical example of such graph is the classic split merge pattern. We can easily imagine an allocation and scheduling algorithm for such structures, (for homogeneous and heterogeneous resources as well) by using the rates  $m, n \in \mathbb{N}^2 \mid m$ mod n = 0 defined in Figure 1.3 (left). Of course this scheduling algorithm would be specific to split merge graphs. In typical and practical problems the whole graph consists in hierarchical structured graphs or unstructured connections of structured subgraphs. StreamIt graphs (Figures 1.4) and SDF graphs (We use some in Chapter 3) are examples of such graph.

Figure 1.3: Split/merge dataflow process network and its corresponding graph of tasks

One of the most famous attempt to this is the Synchronous Dataflow model [61]. Synchronous Dataflow Graphs (SDFG) allow to model cyclic graphs of processes with input and output data rates, and analyze the correctness of the model. The original model does describe the multiprocessor scheduling of such structured graphs (apart using results from theoretical scheduling). It is however able to sequence them, and sequences can also be optimized given certain metrics such as code size (single appearance schedules) or memory consumption [8]. The classical SDF model does not include cost functions of the tasks, which is not required for sequencing but mandatory for multiprocessor scheduling. An SDFG is a bipartite graph where edges can be divided in two disjoint sets named Agents and Places. Then, the classical technique for multiprocessor scheduling of SDFG [60] is to transform them to Homogeneous SDFG (with unitary input and output rates) or "Acyclic Precedence Graph" (APG, with equal input and output rates) in order to use known heuristics (such as HEFT[93], described in Section 1.5.3) for multiprocessor scheduling of unstructured DAGs.

We refer to this model in section 2.1.1.3, and we define the main concepts here. An "agent" is a functional block that consumes and produces a static amount of data (or tokens) in its input and output buffers called "places". Weighted arcs connect agents with places. Two agents (resp. places) cannot be adjacent. The "marking" associates tokens with each place, the initial marking is the initial number of tokens in all places. We call a "period" a valid execution of agents such as every agent runs at least once and the marking takes its initial value. Tokens are used to abstract the different elements of data that are read/written by the agents. The agents abstract the tasks and should thus read and write a static amount of tokens. The Cyclostatic SDF [9] extension relaxes this requirement and allows to model actors with a cyclic behavior (the number of tokens read/written is periodic). SDF and its variants offer a concise and parametric model to describe data-independent applications, including cyclic behavior such as stream processing applications. When the model admits one or multiple cycles, finding a sufficient and minimal initial marking is a challenging problem. In this case the analysis of the graph also consists in finding an initialization and an optimized steady state.

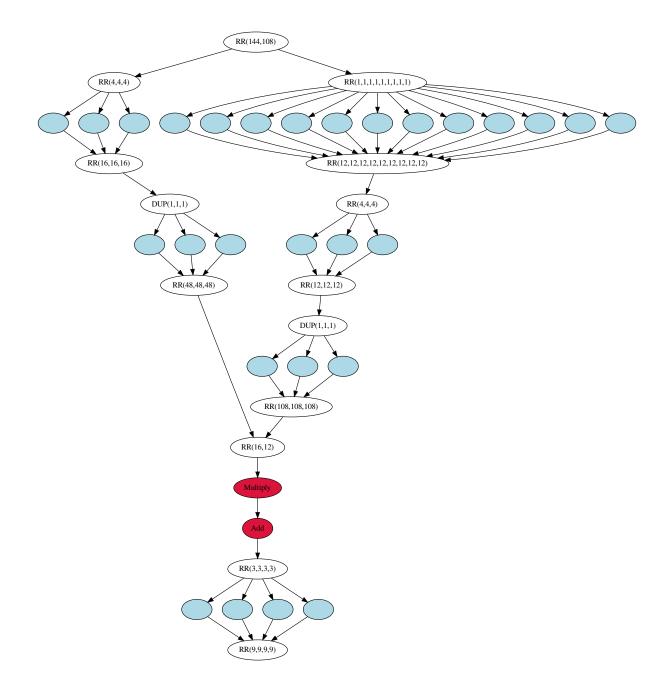

#### 1.2.2.2 Structured graphs

The most well known attempt that uses structured graph constructs to achieve multiprocessor scheduling is StreamIt [92], which allows to use different scheduling heuristics. The StreamIt dataflow language defines sophisticated constructs in order to manipulate the flows of data and organize them as structures such as pipelines, feedback loops, and different ways of splitting and merging data... According to estimated metrics, different structures of the graph can be evaluated. Provided a balanced input dataflow graph and a scheduling policy, a static mapping is generated. It includes optimization such as pipelining periods of cyclic graphs. Figure 1.4 gives one of the StreamIt graph representation of the blocked matrix multiply algorithm, with four types of nodes:

**Identity** (blue) data is copied from the input port to the output port

Roundrobin (white) data is distributed or gathered with a round robin policy according to the rates

**Duplicate** (white) data is duplicated on all the output ports

Actual work (red) where the data is actually modified

In this example the majority of the nodes move data but do not modify it, which gives an idea of the vast search space regarding possible graph transformations.

Other examples of structured graphs include recursive definitions of divide and conquer algorithms such as the Fast Fourier Transform. Structured graphs can also be built from definitions of algorithms such as FFT, blocked matrix multiplication or blocked Cholesky decomposition [3]. We experiment our approach using pseudo code generated graphs in Chapter 3 (Figures 3.11, B.1, B.2).

#### 1.2.2.3 Conflict freeness / functional determinism / latency insensitivity

An important aspect of formal models is the absence of conflicts. Conflict-freeness has a different name depending on the formal model. Conflicts are unspecified aspects of the execution, for instance when two agents compete for reading or writing. Some models introduce non determinism regarding the flow of data (or tokens) such as Petri nets [76]. Petri nets is thus not a conflict free model. The conflict resolution must be modeled with another formalism such as finite state machines. Petri nets can be sub-classed into conflict-free models such as marked graphs [22]. Kahn Process Networks (KPN [50]) or synchronous dataflow graphs[61] are also conflict free: in the SDF model the places connect only one producer to one consumer, thus no two nodes can compete for tokens. We limit our investigations to conflict free models only and we detail the methodology to check conflict freeness regarding the SDF model thereafter.

In an SDF graph, the analysis of the input and output rates of the agents allows to check that no agent will starve or no place will grow infinitely. In SDFG this can be checked by solving the "balance equations" which consists in finding the vector of non null integers X in Equation 1.1. We call X the "repetition vector". If such vector exists then the graph is "balanced". Let  $\mathcal{A}$  be the set of agents and  $\mathcal{P}$  the set of places.  $\mathbf{card}(\mathcal{A})$  (resp.  $\mathbf{card}(\mathcal{P})$ ) is the number of agents (resp. places). The topology matrix  $\Gamma$  is a matrix of  $\mathbf{card}(\mathcal{A})$  columns by  $\mathbf{card}(\mathcal{P})$ ) lines. r(a, p) is the rate or weight of the arc connecting the an agent  $a \in \mathcal{A}$  to a place  $p \in \mathcal{P}$ . It is positive if the place is an output, negative if it is an input, and zero if the agent and place are not connected.

$$a_{i} \text{ is the } i^{th} \text{ agent in } \mathcal{A}$$

$$p_{i} \text{ is the } i^{th} \text{ place in } \mathcal{P}$$

$$\Gamma : \gamma_{i,j} = r(a_{i}, p_{j})$$

$$X = (x_{1}...x_{card}(\mathcal{A})) : \Gamma . X = 0$$

(1.1)

Another analysis consists in finding the maximum throughput of the graph which is limited when the graph admits one or multiple cycles. When the graph has multiple cycles, the throughput of the graph depends on the throughput of the slowest cycle and determining the minimum and optimal marking (regarding throughput) is a challenging issue [67].

Figure 1.4: StreamIt graph of the blocked matrix multiply algorithm

StreamIt graphs are also conflict-free and balanced. In Figure 1.4, when 144 + 108 tokens enter the graph, one complete iteration of the graph is executed down to the output node and the marking of the StreamIt graph comes back in its initial state.

Process networks thus usually define the two properties:

• "liveness": there exists a sequence where every agent fires infinitely often, which means that there is no deadlock or livelock (and there is no data "underflow" in the places)

• "safety" (or "boundedness"): the application can be executed with a finite memory capacity (and thus there is no data "overflow" in the places)

Those structured graph models can thus be used to find the set of correct partial orders for the execution of agents. Then, the classical analysis regarding sequencing and scheduling consists in extracting a complete order that is optimized regarding a criteria (size of the code, memory requirements, makespan, ...). A typical policy for the simulation of process networks consists in firing an actor as soon as its input ports are provisioned (ASAP). Live process networks admit a periodic sequence of firings that can be described for each node with a K-periodic binary word [67].

Even though some structured graph models also define languages (StreamIt does), they are still not commonly used for software engineering purposes. Domain Specific Languages (DSL) focus on a specific topic in order to improve the clarity and the efficiency of the programs (such as Halide[79] which targets image processing). They provide a textual syntax which is used to describe instances of the previously described formal models. In the next section we consider the more pragmatic approach to multiprocessor scheduling and we try to related them to those formal models. In essence the Domain Specific Languages encapsulate the behavior (Section 1.2.1) and the structure (Section 1.2.2) within the same model and thus may fill the gap between formal models and classical sequential languages.

#### **1.2.3** Relations to general purpose languages

In the compilation area, scheduling mostly refers to instruction scheduling which means organizing the instructions such that the micro-architecture executes them faster. With the upcoming parallel architectures scheduling may also include automatic parallelization. On contrary in the HPC area, scheduling mostly refers to load-balancing, thus only to "allocation". HPC runtimes are most often designed to process a large amount of data as fast as possible (with a best effort policy). Most often the predictability of the execution is not the main concern of those tools. It however includes constructs that allows the distribution and reduction of data as like as DPN. MapReduce[32] is an example of a programming model (and implementation) for processing large amounts of data-parallel tasks on a large amount of resources.

Sequential languages such as C and FORTRAN require that the programmer gives a synthetic execution order of the routines or instructions. Since those languages do not provide parallelism or concurrency in their syntax, the granularity of the task, their core affinity and their scheduling is either statically assigned or delegated to an external tool (or runtime scheduler through code annotations or API calls). Some specific constructs can be automatically analyzed and transformed to formal model for further analysis. Static Affine Nested Loop Programs (SANLP) can be transformed to process networks[95]. A SANLP is a set of statements surrounded with nested loops. Input and output data is a multidimensional array. The loop bounds must be immediate values and data read or write is allowed only to affine combinations of the indexes. Dependency analysis allows to build a graph of the statements. Polyhedral optimization approaches [77] manipulate this intermediate representation model of loop nests to find an optimized order to traverse the space of statements, and to tile them for better parallelism. Typical transformations such as loop tiling and unrolling also exist in general purpose language compilers, and the exploration in this state space is still a difficult topic [54, 7].

It's not easy to extract significant information from existing sequential or parallel implementations (which is known as "automatic parallelization") but those languages provide a sufficient backend to implement the result of a preliminary analysis based on previously described models. Early answers to the growing amounts of computing resources consists in annotating sequential application description to parallelize them. Regarding practical aspects, the languages and APIs that are used to leverage parallelism implementations often match the hardware memory organization: shared or distributed. Multithreading matches the former: multiple threads can share memory areas. The conflicts and memory bottlenecks have to be carefully examined by the programmer. Message passing matches the latter, processes cannot share a memory area, but they are able to send and receive messages. Both approaches have many implementations such as POSIX threads, OpenMP, MPI. We use some of those tools in the experiments of Chapter 3.

#### **1.3** Application requirement modeling

Scheduling is a very large topic with plethora of problems, cost models, and publicated algorithm of different nature. The real-time scheduling community often focuses on finding heuristics with interesting properties (regarding schedulability or performance optimization). The analytical approach to scheduling is sometimes referred as "operational research" although this domains also covers different topics (including scheduling). This section describes some modeling elements of the real-time scheduling theory. Extra functional requirements may be added to the application model aside from its former introduction in previous sections. Requirements can deal with performance (data throughput) or real-time criteria. In the current section we focus mainly on performance aspects and task models. We describe preemptive task models in Section 2.1.1.5, periodicity requirements in Section 1.3.2 and objective functions in Section 1.3.3.

we investigate architecture provisions and energy aspects in Section 1.4. In real-time scheduling theory one usually also provide a high level cost function and architectural platform which description is deferred to section 1.4.1.1.

#### 1.3.1 Preemption and migration

"Preemption" is the ability to start a task on a resource, suspend it before it completes and resume it on the same resource. "Migration" is the ability to start a task on a resource, suspend it before it completes and resume it on a different resource. Theoretical scheduling algorithms often target either only preemptive tasks or non-preemptive tasks (and do not consider mixing both task models).

#### 1.3.1.1 non-preemptive task models

We call "Task" the non-preemptive task model in theoretical scheduling. A typical set of variables associated to non-preemptive tasks in scheduling includes:

$$start, stop \mid duration = stop - start$$

$$appearance \mid start \ge appearance$$

$$deadline \mid lateness = stop - deadline$$

$$(1.2)$$

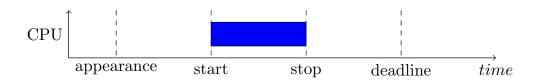

Figure 1.5 gives a graphical definition of those variables. When the lateness is negative it is sometimes referred to as "laxity".

#### 1.3.1.2 Preemptive task models

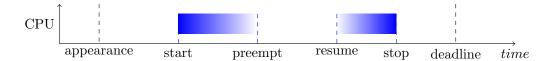

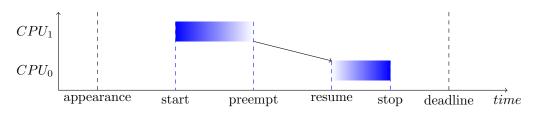

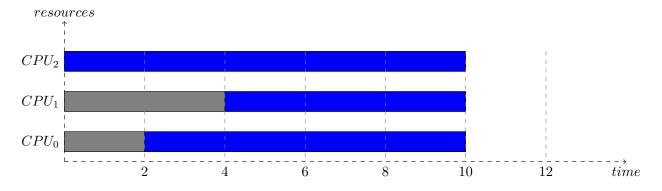

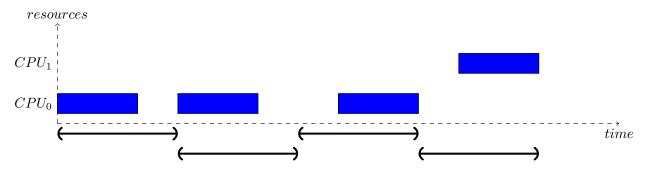

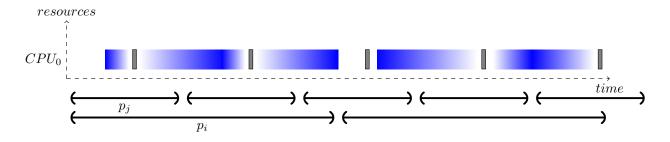

Figure 1.6 gives an example where a task is preempted once (in two tasks). Figure 1.7 shows an example where a task is migrated once from resource  $R_0$  to  $R_1$ . In each case the total duration of the task is the sum of the intervals: duration = preempt - start + stop - resume. However preemption

Figure 1.5: Model of a non preemptive task

and migration have a cost. This cost can be modeled. For instance when an operating system running multiple processes does preempt one of them, it must save and restore its state (which we call a "context switch").

Figure 1.6: Model of a task preempted once

Figure 1.7: Model of a task migrated once

In a preemptive task scheduling problem, the tasks can be preempted and migrated infinitely often. In a practical multiprogramming environment, a process can be preempted or migrated each time the online scheduler runs. This scheduler runs periodically (typically 100Hz to 1kHz). The state space of such problem is finite but very large (depending on the duration of the tasks). This also means that the problem cannot be encoded only using the variables defined in Equations 1.2.

One of the main approaches in preemptive scheduling focuses on periodic task systems and consists in using the rates of the tasks in order to determine if the system is schedulable. Another approach which is not specific to periodic tasks consists in modeling the active time of each task with a binary vector whose length equals the number of time slots (TDMA: Time Division Multiple Access). A third approach consists in transforming the preemptive problem in a non-preemptive one by preempting each task a given number of times (pre-computed preemption).

In the latter the question then arises as to find the smallest amount of preemptions and migrations (or the largest timestep) that still provides the optimal solution in the sense of preemptive task scheduling. This problem is known as "limited preemption" [16] or "precomputed preemption" [18] and we partially address it along with preemptive task modeling in section 2.1.1.5.

#### 1.3.2 Periodicity

Some events are intrinsically periodic because they are related to physical periodic events (such as periodic signals). Sometimes it is necessary for functional reasons to sample or generate a signal at

a given throughput. Another common example of periodic systems is a streaming application that admits a periodic sequencing of the tasks.

We use the confusing notion of "periodic task" (see Section 1.2.1) (calling them periodic jobs or periodic agents is also confusing in the sense of theoretical scheduling and process networks). The definition of a periodic task usually includes a period  $t_{period}$ , a duration  $t_{duration}$  and a deadline (relative to the period)  $t_{deadline}$ . When  $t_{deadline} = t_{period}$  the rate is defined with Equation 1.3

$$t_{rate} = \frac{t_{duration}}{t_{period}} \tag{1.3}$$

A periodic task system can be transformed to a system of independent tasks over its "hyper period". Given a set of periodic tasks  $\mathcal{T}$  of physical time period  $t_period$ , the hyper period is the least common multiplier of the periods:

$$Mc = LCM(t_{period} \mid t \in \mathcal{T}) \tag{1.4}$$

#### **1.3.3** Objective functions

The makespan and the maximum lateness are the most studied objective functions in task scheduling optimization problem (Equations 1.5 give example objective functions), and we mainly focus on the makespan objective in this work. Graham's classification [43] defines multiple objective functions such as:

$$Makespan : \max_{t \in Tasks} t_{stop}$$

$$Maximum \ lateness : \max_{t \in Tasks} (t_{stop} - t_{deadline})$$

$$Weighted \ sum \ of \ lateness \sum_{t \in Tasks} w_i \cdot t_{lateness}$$

$$(1.5)$$

The lateness would typically be used to distinguish hard real-time problems for soft real-time problems: in the former, violating the deadline is not allowed, in the latter it is allowed at a defined cost. It can also be used to distinguish the criticality of some tasks, for instance by using the weighted sum of lateness as an objective function.

The notion of optimality is closely related to the notions of requirements, for instance regarding periodic task systems the main concern is schedulability of the system since the makespan is not relevant. The optimal value can also depend on the task model, for instance it is easy to find an example where a preemptive schedule achieves a better makespan than a non preemptive one.

#### **1.4** Architecture modeling

In Section 1.4.1 we discuss the resources and communication modeling in the real-time scheduling theory. Then in Section 1.4.2 we discuss practical aspects of computer architecture organization. Finally we describe power saving techniques and energy modeling in Section 1.4.3.

#### 1.4.1 Architecture modeling in real-time theory

In this section we describe the common resource models and communication models studied in realtime scheduling theory.

#### 1.4.1.1 Resources

Theoretical problems typically consider three resource types: homogeneous, heterogeneous, and related (as described in Graham's classification [43]). Given two tasks  $t_i, t_j$  in  $\mathcal{T}$  the set of tasks. Let  $c_t^{r_k}$  be the cost of running task t on resource k. Resources k and l are:

- homogeneous  $\forall t_j \in \mathcal{T} : c_j^{r_k} = c_j^{r_l}$

- related with coefficient  $r: \forall t_j \in \mathcal{T}: \frac{c_i^{r_k}}{c_i^{r_l}} = r$

- heterogeneous  $\exists t_i, t_j \in \mathcal{T} \mid \frac{c_i^{r_k}}{c_i^{r_l}} \neq \frac{c_j^{r_k}}{c_j^{r_l}}$

Other models consider an arbitrary cost function where the task costs is a function of various parameters, for instance the task starting time [19].

#### 1.4.1.2 Communications

Graham's classification accounts only for precedence relations between tasks [43]. Later the classification has been extended to better account for communication delays [97].

- Instantaneous communications: there is an infinite amount of links, and an infinite throughput between resources

- Fixed cost model: the application graph specifies communication delays

- Fixed cost models that depends on sender and receiver allocations (such as in [93])

- The cost is an (arbitrary) cost function which may depend on sender task allocation, receiver task allocation, their distance regarding the number of links, the amount of data and other parameters such as the latency and throughput of the link.

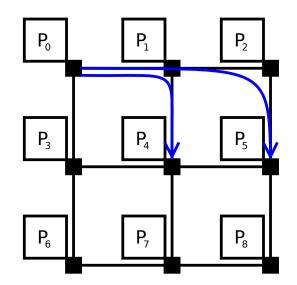

The third model accounts for the "locality principle" described in 1.4.2.2. The fourth model consists in considering structured networks to benefit from special properties such as symmetry, minimum distance between two nodes, robustness to broken links, .... For instance some effort has been conducted towards the study of k-ary n-cubes [25] and such network has then been used to build HPC supercomputers (Blue Gene and Cray use a k-ary 3-cube) and then on-chip networks (Kalray MPPA [28] uses a torus network on chip which is a 4-ary 2-cube). When using such networks, because multiple routes exist between two nodes a routing algorithm is used.

The most complex models (fourth case) can be used for instance for network on chip modeling. Typical network (on chip) communication models include a constant cost  $\alpha$ , a per-byte cost  $\beta$  and a per-hop cost  $\gamma$  such as Equation 1.6 for a message of n bytes traversing h hops. We expected that the same model would apply on a network-on-chip microarchitecture and experimented on the Kalray MPPA but we found no evidence of hop cost.

$$t(n,h) = \alpha + \beta \cdot n + \gamma \cdot h \tag{1.6}$$

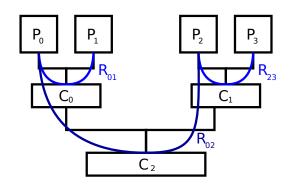

#### 1.4.2 Computer architecture classification in practice

When it comes to practical aspects many computer architectures compete, both regarding their microarchitecture and their memory organization. We recall some of the main microarchitectures and communication resources in Sections 1.4.2.1 and 1.4.2.2.

#### 1.4.2.1 Resources

Finding a versatile architecture and memory organization at the chip level is tricky and there is not yet a de facto standard, which explains the current diversification. The computing resources must support be able to run ever increasing workloads (and thus be scalable) and dynamically adapt to low workloads by dynamically switching to low energy states.

A typical unrelated (or heterogeneous) resources setup is found when different computing microarchitectures are used. For instance in the integrated GPU CPU architectures such as Intel Haswell the GPU is proficient at executing vector operations. Hence the performance of the tasks on the GPU essentially depends on this criteria whereas the cost of the CPU implementation is not very sensitive to this.

In the compilation area, high level architecture modeling tools are not often involved. Acronyms are used to depict the main characteristics of the target architectures, such as:

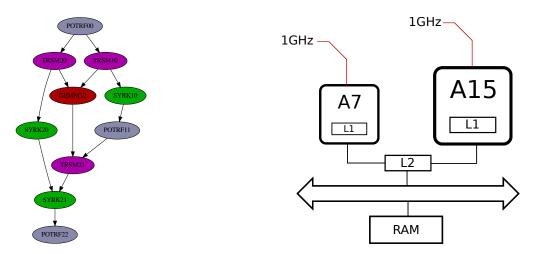

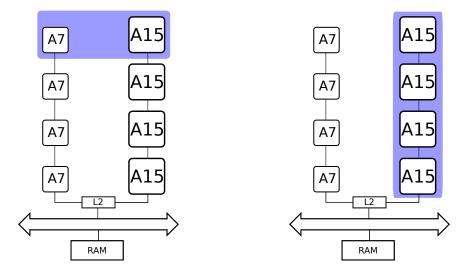

- **SMP** (symmetric shared memory multiprocessor): the resources are identical and symmetric about one memory. Multiple SMP can be combined, but the resulting architecture is thus not an SMP. For instance the big.LITTLE ARM architecture is made of one cluster of four identical big cores that access the main memory through the same path, and another cluster of four identical little cores.

- (GP)GPU (General Purpose Graphical Processing Unit): the resources and interconnects are designed to provide high data throughput for embarrassingly parallel operations

- **DSP** (Digital Signal Processor): an architecture that contain specialized hardware and instructions to increase instruction level parallelism

- **VLIW** (Very Long Instruction Word): the compiler is in charge of clustering instructions that will be executed in parallel

#### 1.4.2.2 Communications

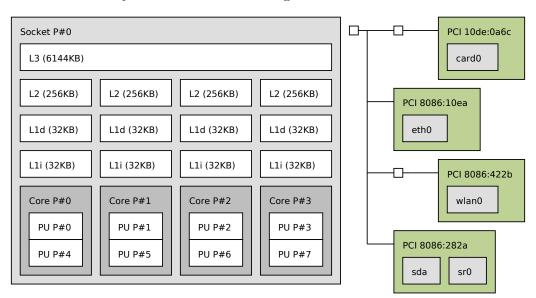

There is no cheap, fast and large memory technology. Applications need to store large amount of data, and also manipulate or transform some of it very quickly. As a consequence every computer architecture needs to interconnect large (but slow) memories with small (and fast) memories (an example is visible in Figure 1.8). The arithmetic and logical units are the components that manipulate data, thus the small and fast memories are connected to those components. This is known as "the locality principle". Moving data between large and small memories makes the complexity of software optimization. We describe thereafter the two memory models of computer architectures: shared and distributed memory.

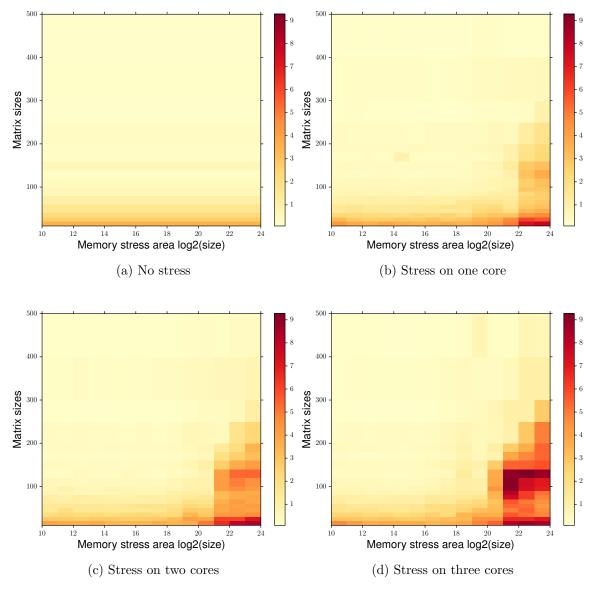

The most widespread solution consists in adding hardware logic that tries to guess which data will most likely be fetch from the main memory, and try to retrieve it before the program uses it. This is the well known shared memory model architecture with sometimes multiple hierarchical levels of caches. The downside is that controlling this memory hierarchy is sometimes very complex since the software is not allowed to explicitly access the caches. When a block of data has to be fetched and is not in the cache, a cache miss occurs and the block is fetched from the main memory. Three types of cache misses can occur:

- Obligatory: The cache is empty (or "cold"), the block of data has to be fetched for the first time

- Capacity: The program runs through a larger memory area than the cache size

• Conflicts: The cache is smaller than the area it caches, thus each block in the cache maps to multiple blocks in memory. Accessing those blocks successively causes conflicts.

In an MPSoC the communication between integrated components (sensors, CPUs, DSPs, ...) usually goes through one or multiple Bus which are also arbitrated by an hardware bus arbiter, with no or little available control from software.

The opposite approach of distributed memory on contrary relies on software to leverage the locality principle. Because the regular compilers are not able to perform it, this programming model is not a very popular choice. Thus the trend in system on chip design is to integrate computing resources (heterogeneous CPUs, GPUs, DSPs, ...) with a shared memory hierarchy (Intel HD Graphics integrated GPUs, ARM Mali integrated GPUs, ARM big.LITTLE heterogeneous multiprocessing, ...). Yet some approaches try to leverage on-chip distributed memory architectures, mainly using network on chip interconnects. In a Network on Chip the resources are connected with a regular network graph, such as 2D meshes, 3D meshes, or torus (see Section 1.4.1.2). There is no de facto standard memory organization. Many attempts exist (Raw, Aethereal, Kalray) and they often come with a specific compiler that handles the communications on the network when they are not explicit in user code. In some architectures each node of the graph is itself an SMP.

"Scratchpad" memory organization is another distributed memory architecture which is organized hierarchically like caches, with the essential difference that every memory can be read/written explicitly from software. As like as network on chips it needs a specific compiler and is not often used in practice.

Modeling shared memory architectures is very hard and most often consists in modeling cache accesses or limiting them. Modeling distributed memory architectures is easier but is harder to leverage in practice since distributed memory embedded system architectures are not widespread.

#### 1.4.2.3 Extracting some knowledge

Existing tools allow to extract information from a (running) target [52]. Hwloc extracts information about memories, memory hierarchy and resources [13]. Netloc[37] is a recent addition that allows to obtain information about the network. Those tools essentially target High Performance Computers. Most often the model is only structural such as in Figure 1.8.

Figure 1.8: lstopo output on a laptop multicore computer

#### **1.4.3** Power saving mechanisms

An embedded system is by definition not plugged into any power outlet, and has thus to run on battery. Moreover, most of the power it consumes is dissipated into heat which is usually not desirable. Increased battery performance and a better energy management improved the autonomy of our devices in the last decade. Energy consumption is due to transistors switching when the microarchitecture is active, and transistors leakage current when it is powered but inactive. In Sections 1.4.3.1 and 1.4.3.2 we study the main two mechanisms of energy management.

#### 1.4.3.1 Dynamic Voltage and Frequency Scaling

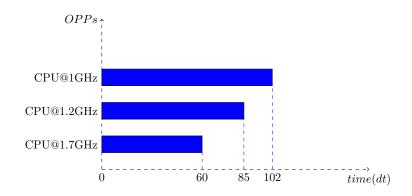

DVFS is the ability of computing resources to decrease their frequency to save some energy. In most DVFS implementations the frequency can be chosen dynamically in a set of available Operating Performance Points (OPP) and not within a continuous range.

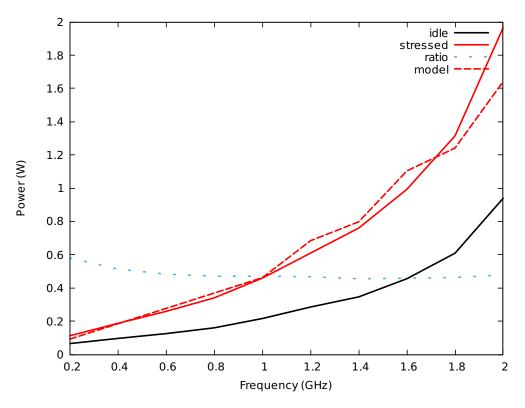

We recall the admitted high level instant power model for microprocessors [53]: given the OPP o = (V, f) of a resource r:

$$P(r, o, t) = P_{dynamic}(t) + P_{static}(t)$$

$$P_{dynamic} = C_r \cdot V^2 \cdot f \cdot A$$

$$P_{static} = V \cdot I_{leak}$$

(1.7)

We define the variables of Equation 1.7 and we give their dimension:

- $C_r$  [Farads]: the model capacitance of the CPU (roughly proportional to the number of the switching devices, i.e. the number of transistors)

- V [Volts]: the voltage of the current operating point

- f [Hertz]: the frequency of the current operating point

- A [dimensionless]: An activity factor that models the average number of bit flips that the task will cause on the resource. Although it is specific to each pair of task and resource it is often considered constant

- *I*<sub>leak</sub> [Amperes]: Transistors leak a small amount of current when they are powered (even if they are not switching)

Regarding only dynamic power, and given a task which costs  $C_y$  cycles and runs on the resource r at OPP o: the task will last  $\frac{C_y}{f_o}$ , thus we can model the consumed energy with the expression 1.8. In order to operate normally, the chip must raise  $f_o$  linearly with  $V_o$  [71]. We can thus remove the dependency to  $f_o$  in E(t) which means that running a task at a low frequency actually consumes less energy than running it at high frequency, even though it lasts longer. This is the purpose of frequency scaling.

$$E(t) = \int_{t} P(t) = \frac{C_y}{f_o} \cdot P(r, o) = C_r \cdot C_y \cdot V_o^2 \cdot A$$

(1.8)

#### 1.4.3.2 Power gating

Setting the CPU to the lowest frequency does not cut all the dynamic power. Power gating is the ability to shut down a subset of the resources and thus eliminate both this remaining dynamic power and static power. When the CPU is not running, its instant power follows the same model, with a reduced activity factor (since fewer gates will flip while idling).

The instant power of the system depends on time because the resources are allowed to change their operating point in time. Given the instant power P(R), the energy with a dimension of  $Watts \cdot seconds = Joules$  is thus calculated for each resource r over the duration of the schedule (which means from zero to makespan M).

$$E_a(r) = \int_{t=0}^{t=M} P(r) \,\mathrm{d}t$$

(1.9)

$$= C_r \cdot \int_{t=0}^{t=M} V^2 \cdot f \cdot A \,\mathrm{d}t \tag{1.10}$$

Let  $t_o$  be the opp for task t, this means that each resources r running at opp o consumes:

$$E(r,o) = C_r \cdot \sum_{t \in Tasks | t_o = o} \cdot \frac{C_y}{f} \cdot V_o^2 \cdot f$$

$$E(r,o) = C_r \cdot \sum_{t \in Tasks | t_o = o} C_y \cdot V_o^2$$

Let  $O_r$  be the set of OPPs of resource r, the energy consumed by the tasks running on r is:

$$E_a(r) = \sum_{o \in O_r} E(r, o)$$

We call that quantity "active" energy consumption.

Finally let  $P_{idle}$  be the idle instant power of the resource,  $t_{pt}$  the physical time duration of task t and  $t_{map}$  the resource where t is mapped. The idle energy can also be expressed as a discrete sum:

$$E_i(r) = P_{idle} \cdot (M - \sum_{t \in Tasks | t_{map} = r} t_{pt})$$

Thus, the consumed energy of the system is:

$$E = sum(E_i(r) + E_a(r) \mid r \in R)$$

Recent studies shows that indeed the energy vs frequency function for a given task is a convex function [31]: If the frequency is very low then static power dominates and on contrary if the frequency is high dynamic power dominates. In the middle lies the most energy-efficient operating point. Validating real-time constraints however sometimes requires to run tasks at higher frequencies.

#### 1.4.3.3 Motivating example

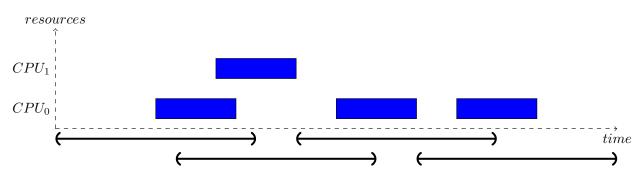

Lowering the frequency of a task does not always mean that the optimization criteria is degraded. For instance if we want to optimize makespan, we can find very simple application descriptions of tasks and dependencies which give evidences that energy can be optimized with a preserved makespan. Figure 1.9 is a typical problem instance with a split merge of two unbalanced workers, where slack time can be used to save energy. Generally speaking, this applies to each non critical path. This also gives evidence that the solver will be able to optimize energy if we allow more slack time from the optimal makespan schedule.

Figure 1.9: Non energy optimized vs optimized split merge pattern (red tasks run with high instant power)

When the application graph is not a simple unbalanced two tasks split/join, it is (computationally speaking) much harder to decide the allocation and the operating point in order to obtain an optimized schedule. For a few tasks with precedences it might even be hard for a human to optimize for makespan, considering only high frequency operating points. Then, the more slack time, the higher possible energy optimization, and the larger state space to explore.

#### 1.4.4 Temperature modeling