## Scheduling of Dense Linear Algebra Kernels on Heterogeneous Resources

Suraj Kumar

#### ▶ To cite this version:

Suraj Kumar. Scheduling of Dense Linear Algebra Kernels on Heterogeneous Resources. Other [cs.OH]. Université de Bordeaux, 2017. English. NNT: 2017BORD0572. tel-01538516

## HAL Id: tel-01538516 https://theses.hal.science/tel-01538516v1

Submitted on 13 Jun 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE

PRÉSENTÉE À

# L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

par Suraj Kumar

POUR OBTENIR LE GRADE DE

## **DOCTEUR**

SPÉCIALITÉ : INFORMATIQUE

## Scheduling of Dense Linear Algebra Kernels on Heterogeneous Resources

Date de soutenance : 12 April 2017

#### Devant la commission d'examen composée de :

| Mme Padma RAGHAVAN      | Professeur, Vanderbilt University            | Rapporteur         |

|-------------------------|----------------------------------------------|--------------------|

| M. Julien LANGOU        | Professeur, University of Colorado Denver    | Rapporteur         |

| M. Denis TRYSTRAM       | Professeur, Grenoble Institute of Technology | Président          |

| Mme Veronika SONIGO     | Maître de conférences, FEMTO-ST institute    | Examinateur        |

| M. Olivier BEAUMONT     | DR1, Inria Bordeaux                          | Directeur de Thèse |

| M. Lionel EYRAUD-DUBOIS | CR, Inria Bordeaux                           | Directeur de Thèse |

| M. Samuel THIBAULT      | MCF, University of Bordeaux                  | Directeur de Thèse |

| M. Emmanuel Agullo      | CR1, Inria Bordeaux                          | Directeur de Thèse |

| M. Abdou Germouche      | MCF, University of Bordeaux                  | Invité Membre      |

Résumé Du fait des énormes capacités de calculs des accélérateurs tels que les GPUs et les Xeon Phi, l'utilisation de machines multicoques pourvues d'accélérateurs est devenue commune dans le domaine du calcul haute performance (HPC). La complexité induite par ces accélérateurs a suscité le développement de systèmes d'exécution à base de tâches, dans lesquels les dépendances entre les applications sont exprimées sous la forme de graphe de tâches et où les tâches sont ordonnancées dynamiquement sur les ressources de calcul. La difficulté est alors de concevoir des stratégies d'ordonnancement qui font une utilisation efficace des ressources de calculs et le développement de telles stratégies, même pour un unique noeud hybride, est un enjeu essentiel de la performance des systèmes HPC.

Nous considérons dans cette thèse l'ordonnancement de noyaux d'algèbre linéaire dense sur des noeuds complètement hétérogènes et constitués de CPUs et de GPUs. Les performances relatives des accélérateurs par rapport aux coeurs classique dépend très fortement du noyau considéré. Par exemple, les accélérateurs sont beaucoup plus efficaces pour les produits de matrices, par exemple, que pour les factorisations. Dans cette thèse, nous analysons les performances de stratégies statiques et dynamiques d'ordonnancement et nous proposons un ensemble de stratégies intermédiaires, en ajoutant des composantes statiques (respectivement dynamiques) à des stratégies d'ordonnancements dynamique (respectivement statiques). Récemment, une stratégie appelée HeteroPrio a été proposée, qui s'appuie sur les affinités entre les tâches et les ressources pour un petit ensemble de tâches différentes s'exécutant sur deux types de ressources. Nous avons étendu cette stratégie d'ordonnancement pour des graphes de tâches généraux pour deux types de ressources puis pour plus de deux types. De manière complémentaire, nous avons également démontré des facteurs d'approximation et des pires cas pour HeteroPrio dans le cas d'un ensemble de tâches indépendantes sur différents types de plates-formes.

Mots-clés Algèbre linéaire dense, systèmes d'ordonnancement dynamiques, plates-formes hétérogènes, ordonnancement à base de graphe de tâches, ordonnancement dynamique

Laboratoire d'accueil Laboratoire Bordelais de Recherche en Informatique, Bordeaux, France

This page is intentionally left blank.

iv Suraj Kumar

**Title** Scheduling of Dense Linear Algebra Kernels on Heterogeneous Resources

Abstract Due to massive computation power of accelerators such as GPU, Xeon phi, multicore machines equipped with accelerators are becoming popular in High Performance Computing (HPC). The added complexity led to the development of different task-based runtime systems, which allow computations to be expressed as graphs of tasks and rely on runtime systems to schedule those tasks among all resources of the platform. The real challenge is to design efficient schedulers for such runtimes to make effective utilization of all resources. Developing good schedulers, even for a single hybrid node, and analyzing them can thus have a strong impact on the performance of current HPC systems.

We consider the problem of scheduling dense linear algebra applications on fully hybrid platforms made of CPUs and GPUs. The relative performance of CPU and GPU highly depends on the sub-routine. For instance, GPUs are much more efficient to process matrix-matrix multiplications than matrix factorizations. In this thesis, we analyze the performance of static and dynamic scheduling strategies and we propose a set of intermediate strategies, by adding static (resp. dynamic) features into dynamic (resp. static) strategies. A resource centric dynamic scheduler, HeteroPrio, which is based on affinity between tasks and resources, has been proposed recently for a set of small independent tasks on two types of resources. We extend and analyze this scheduler for general task graphs first on two types of resources and then on more than two types of resources. Additionally, we provide approximation ratios and worst case examples of HeteroPrio for a set of independent tasks on different platform sizes.

**Keywords** Dense Linear Algebra; Runtime Systems; Heterogeneous Platforms; Task-based Scheduling; Dynamic Schedulers;

## Acknowledgements

I would like to express my sincere gratitude to Olivier Beaumont for his excellent supervision and constant support throughout the course of this thesis. I feel extremely privileged to get so much of his time and to work with him throughout these years. I also thank my co-advisors Lionel Eyraud-Dubois, Samuel Thibault and Emmanuel Agullo for their fruitful collaborations and very interesting discussions. I also wish to thank Abdou Guermouche for his support during this thesis.

I would like to thank all the members of the thesis committee, especially reporters Padma Raghavan and Julien Langou for reviewing my dissertation and providing me very useful remarks, questions and suggestions for future directions of this work. I also thank examiners Denis Trystram and Veronika Sonigo for providing detailed feedback on the dissertation.

I convey my sincere thanks to the team leader Denis Barthou and all the researchers of the team for emphasizing the importance of research and creating a wonderful research environment in STORM team, Inria, Bordeaux.

I am grateful to my family members for their constant motivation, love and support. I would like to thank my colleagues and former colleagues especially Stojce Nakov, Marc Sergent, Luka Stanisic, Florent Pruvost and Terry Cojean for their support during my course at Inria. I would also like to thank all my friends for making my stay at Inria memorable and accompanying me in difficult times.

I express my gratitude to Inria, its founders and the people who helped shape Inria over the years, for providing me a platform to pursue great endeavors in my life.

# Contents

| Contents |            |                                                           | ix |  |

|----------|------------|-----------------------------------------------------------|----|--|

| In       | trodi      | uction                                                    | 1  |  |

| 1        | Background |                                                           |    |  |

|          | 1.1        | Task-based Runtime Systems                                | 9  |  |

|          |            | 1.1.1 StarPU                                              | 9  |  |

|          |            | 1.1.2 QUARK                                               | 14 |  |

|          |            | 1.1.3 PaRSEC                                              | 14 |  |

|          |            | 1.1.4 OpenMP                                              | 15 |  |

|          |            | 1.1.5 StarSs                                              | 16 |  |

|          |            | 1.1.6 XKaapi                                              | 17 |  |

|          |            | 1.1.7 SuperMatrix                                         | 18 |  |

|          |            | 1.1.8 Legion                                              | 19 |  |

|          | 1.2        | Simulation Framework                                      | 19 |  |

|          |            | 1.2.1 Simgrid Simulation Engine                           | 19 |  |

|          | 1.3        | Dense Linear Algebra Libraries                            | 21 |  |

|          |            | 1.3.1 LINPACK (LINear algebra PACKage)                    | 21 |  |

|          |            | 1.3.2 LAPACK (Linear Algebra PACKage)                     | 21 |  |

|          |            | 1.3.3 PLASMA (Parallel Linear Algebra Software for Multi- |    |  |

|          |            | core Architectures)                                       | 22 |  |

|          |            | 1.3.4 MAGMA (Matrix Algebra for GPU and Multicore Ar-     |    |  |

|          |            | chitectures)                                              | 22 |  |

|          |            | 1.3.5 MORSE (Matrices Over Runtime Systems at Exascale).  | 23 |  |

|          |            | 1.3.6 CHAMELEON                                           | 23 |  |

|          | 1.4        | Dense Matrix Factorizations                               | 24 |  |

|          |            | 1.4.1 Cholesky Factorization                              | 24 |  |

|          |            | 1.4.2 QR Factorization                                    | 28 |  |

|          |            | 1.4.3 LU Factorization                                    | 29 |  |

| 2        | Per        | formance and Bounds of Cholesky Factorization             | 31 |  |

|          | 2.1        | Introduction                                              | 31 |  |

|          | 2.2        | Context                                                   | 32 |  |

|     |      | 2.2.1   | Cholesky Factorization                                    |

|-----|------|---------|-----------------------------------------------------------|

|     |      | 2.2.2   | Multiprocessor Scheduling                                 |

|     | 2.3  | Makes   | pan Lower Bounds                                          |

|     |      | 2.3.1   | Linear Programming Formulation                            |

|     |      | 2.3.2   | Constraint Programming formulation                        |

|     |      | 2.3.3   | Upper bounds on performance                               |

|     | 2.4  | Exper   | iments and Results                                        |

|     |      | 2.4.1   | Schedulers                                                |

|     |      | 2.4.2   | Experimental Setup                                        |

|     |      | 2.4.3   | Results                                                   |

| 2.5 |      | Discus  | ssion                                                     |

|     |      | 2.5.1   | dmda vs dmdas Scheduler 50                                |

|     |      | 2.5.2   | Mapping from Constraint Programming Solution 51           |

|     |      | 2.5.3   | Constraint Programming Schedule in Actual Execution . 51  |

|     | 2.6  | Conclu  | usion                                                     |

| 3   | Stat | ic vs l | Dynamic Scheduling Strategies 53                          |

|     | 3.1  | Introd  | <u>uction</u>                                             |

|     | 3.2  | Conte   | <mark>xt</mark>                                           |

|     |      | 3.2.1   | Tile Cholesky Factorization                               |

|     |      | 3.2.2   | Experimental Framework                                    |

|     |      | 3.2.3   | Comparing Static and Dynamic Schedulers                   |

|     | 3.3  | Relate  | ed Work                                                   |

|     | 3.4  | Iterati | ve Bound                                                  |

|     | 3.5  | Static  | <u>Strategies</u>                                         |

|     |      | 3.5.1   | Some Dynamic Strategies with Static Schedule 60           |

|     | 3.6  | Heft-li | kke Solutions (Dynamic, Task-centric) 62                  |

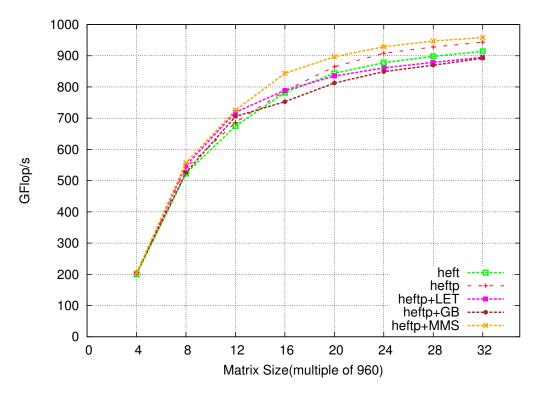

|     |      | 3.6.1   | Improvement of heftp Scheduler 64                         |

|     |      | 3.6.2   | Analysis of Different Improved <i>heftp</i> Schedulers 65 |

|     | 3.7  | Hetero  | oPrio-like Solutions (Dynamic, Resource-centric) 66       |

|     |      | 3.7.1   | Baseline HeteroPrio Scheduler                             |

|     |      | 3.7.2   | Improved HeteroPrio Algorithms 67                         |

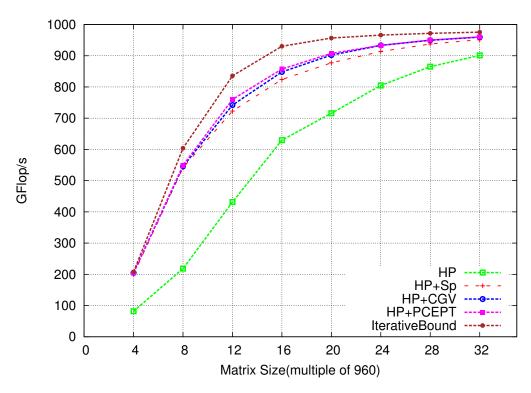

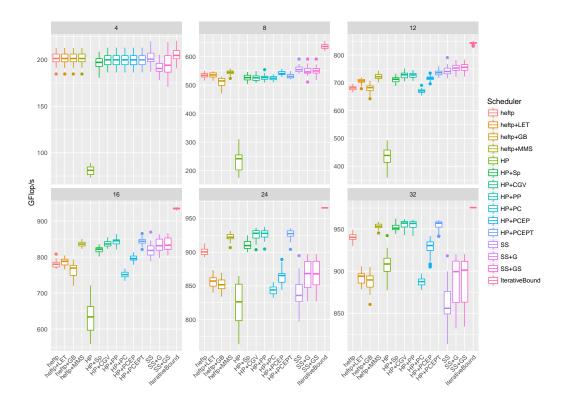

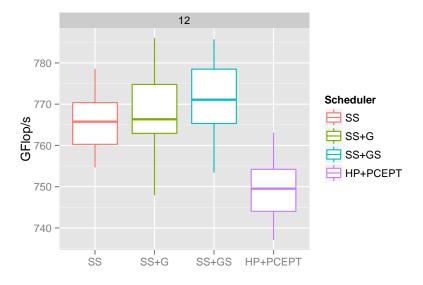

|     |      | 3.7.3   | Performance Comparison of Heteroprio Variants 68          |

|     |      | 3.7.4   | Feasibility of the Implementation of HP Corrections 69    |

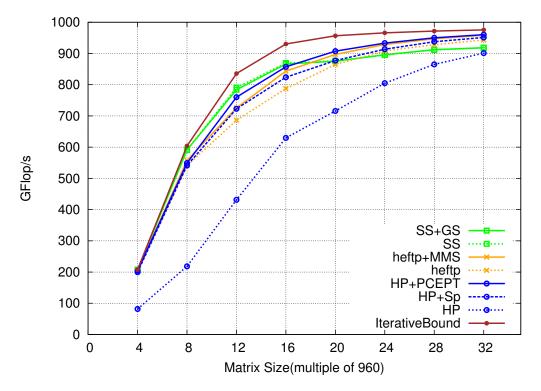

|     | 3.8  | Comp    | arison of All Three Approaches                            |

|     |      | 3.8.1   | Original Timings                                          |

|     |      | 3.8.2   | Perturbed Timings                                         |

|     |      | 3.8.3   | Perturbed Timings within an Execution                     |

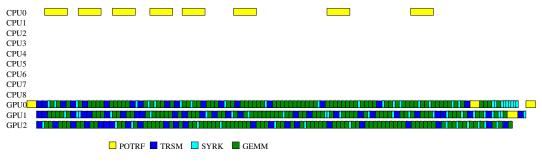

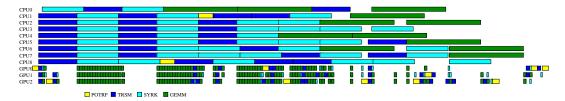

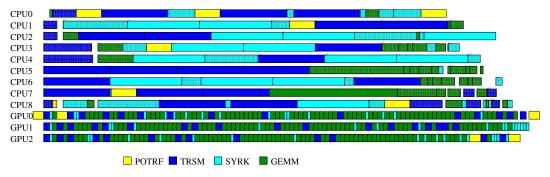

| 3.9 |      |         | Schedule in Actual Execution                              |

|     | 3.10 | Conclu  | usion and Perspectives                                    |

| 4                         | Sch   | eduling of Linear Algebra Kernels on Multiple Heteroge-        |              |

|---------------------------|-------|----------------------------------------------------------------|--------------|

|                           | neo   | is Resources                                                   | 77           |

|                           | 4.1   | Introduction                                                   | 77           |

|                           | 4.2   | Background and Related Work                                    | 79           |

|                           | 4.3   | Affinity Based Scheduling                                      | 80           |

|                           |       | 4.3.1 Affinity Based Scheduling for Two Classes of Resources . | 80           |

|                           |       | 4.3.2 Generalization to more than Two Classes of Resources .   | 81           |

|                           |       | 4.3.3 An Example with Both Scoring Systems                     | 82           |

|                           | 4.4   | Experiments and Results                                        | 83           |

|                           |       | 4.4.1 Tuning of Tile Size Parameter                            | 84           |

|                           |       | 4.4.2 Experimental Framework                                   | 85           |

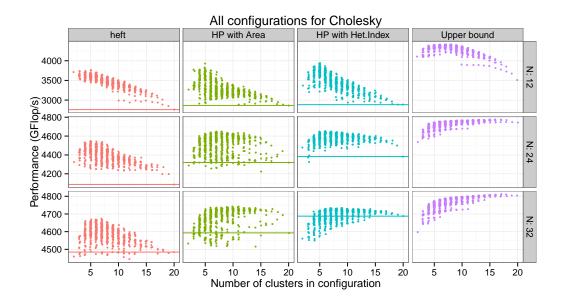

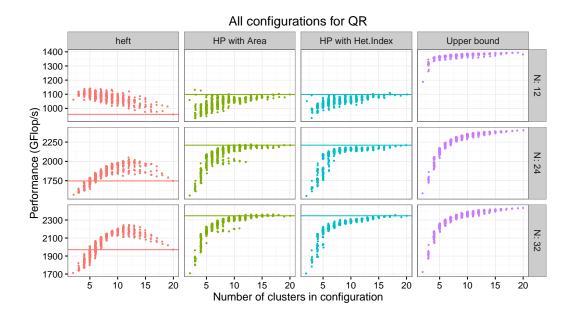

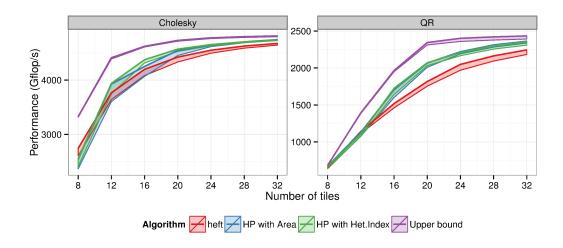

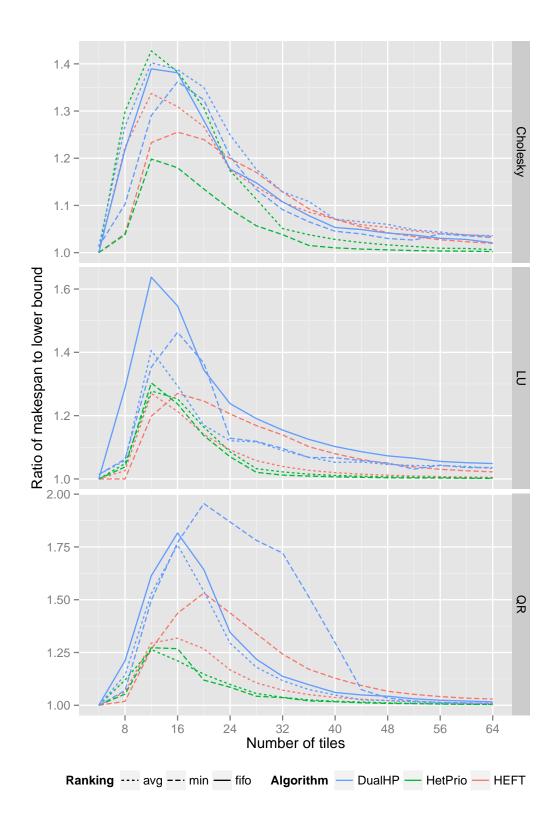

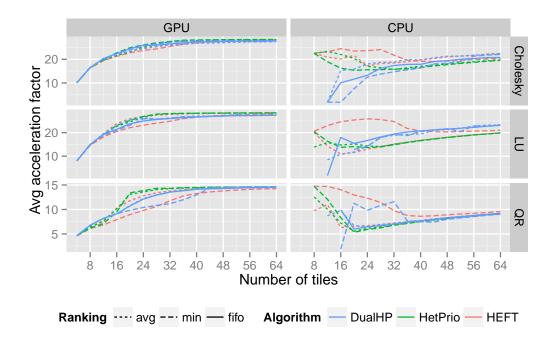

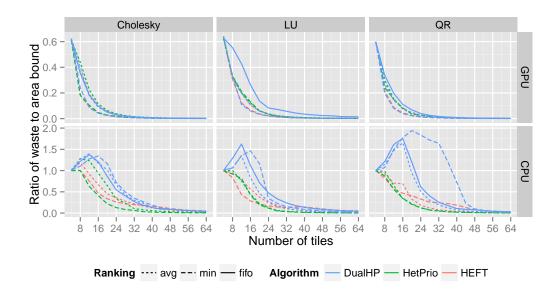

|                           |       | 4.4.3 Simulation Results & Analysis                            | 87           |

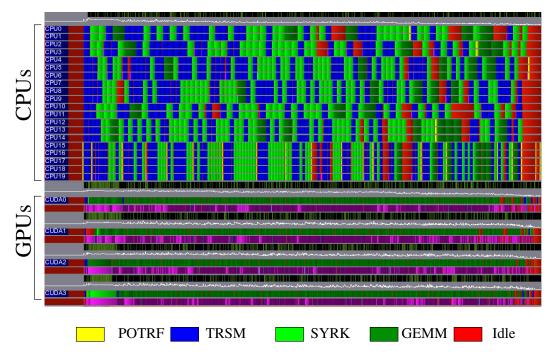

|                           |       | 4.4.4 Analysis of Actual Execution Traces                      | 90           |

|                           |       | 4.4.5 Actual Execution Performance Comparison                  | 92           |

|                           | 4.5   | Conclusion                                                     | 94           |

| 5                         | Het   | eroPrio Approximation Ratios on Two Types of Resources         | 95           |

|                           | 5.1   | Introduction                                                   | 95           |

|                           | 5.2   | HeteroPrio Principle                                           | 97           |

|                           |       | 5.2.1 Affinity Based Scheduling                                | 97           |

|                           |       | 5.2.2 HeteroPrio Algorithm for a set of Independent Tasks      | 98           |

|                           | 5.3   | Related Works                                                  | 99           |

|                           | 5.4   | Notations and First Results                                    | 100          |

|                           |       | 5.4.1 General Notations                                        | 100          |

|                           |       | 5.4.2 Area Bound                                               | 101          |

|                           |       | 5.4.3 Summary of Approximation Results                         | 102          |

|                           | 5.5   | Proof of HeteroPrio Approximation Results                      | 102          |

|                           |       | 5.5.1 General Lemmas                                           | 102          |

|                           |       | 5.5.2 Approximation Ratio with 1 GPU and 1 CPU                 | 104          |

|                           |       | 5.5.3 Approximation Ratio with 1 GPU and $m$ CPUs              | 106          |

|                           |       | 5.5.4 Approximation Ratio with $n$ GPUs and $m$ CPUs           | 108          |

|                           | 5.6   | Experimental evaluation                                        | 115          |

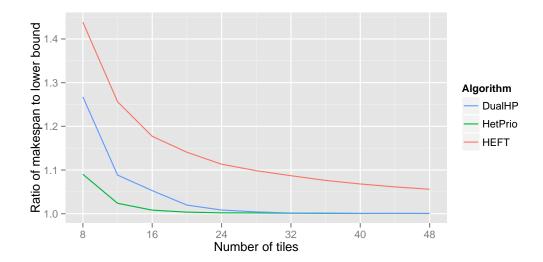

|                           |       | 5.6.1 Independent Tasks                                        | 116          |

|                           |       | 5.6.2 Task Graphs                                              | 117          |

|                           | 5.7   | Conclusion                                                     | 121          |

| C                         | onclu | sion 1                                                         | L <b>2</b> 3 |

| $\mathbf{B}_{\mathbf{i}}$ | bliog | raphy 1                                                        | L <b>27</b>  |

## Introduction

The increasing need to process large amount of computations and to analyze large data in real life with quality and accuracy encouraged the use of High Performance Computing (HPC) systems significantly in recent years. HPC refers to the use of aggregated computing power in a way which delivers much higher performance than one can get on a typical desktop for large problems. HPC provides the ability to analyze and to understand the complexity of a huge amount of information, coming from different sources, and helps us to solve some challenges of our society. In recent years, Cloud computing is becoming increasingly popular in HPC area. It provides a cost effective model of utilization of computing infrastructures. Compute resources, storage resources, even applications can be procured on pay-per-use basis.

HPC is widely used to provide public safety in emergency scenarios. For instance, it allows us to predict the size and patch of storms and flood more precisely and further in advance, which helps us to take preventing measures and to reduce damage. HPC also provides substantial benefits in health-care [89, 55]. It allows us to design and simulate the effect of new drugs, to provide faster diagnosis and better treatment. It helps to detect genetic changes responsible for the onset and mutation of tumors in a simple, quick and precise way. Consider for instance the new born babies with genetic disorders – the main cause of infant death, time is essential as they do not clearly show all of the classical symptoms that make diagnosis possible. HPC allows us to analyze a large set of nucleotides (building blocks of nucleic acids) sequences in a few hours and enables us to provide effective treatment.

HPC is also used in finance market to manage assets and risks. Several companies use supercomputers to measure risks in their fixed income operations by assessing tens of thousand of possible market scenarios [55]. Entertainment field also relies heavily on HPC in order to make animated movies. For instance, to make the movie **Avatar** [3], 40,000 processors were handling around 8 gigabytes of data per second, running 24 hours a day [76].

In last few decades, we collected a large amount of data, which increases the need to analyze the data. HPC can be an useful tool in this area as well. Researchers from different fields such as social media, geology, archeology, materials, graphics, genomics, brain imaging, economics, oil and gas, space, nuclear, even music use HPC platforms to conduct their research [101].

Most applications running on supercomputers such as weather prediction, seismic imaging, nuclear simulation use different linear algebra subroutines. Therefore, improving performance of these linear algebra subroutines has become important since 1970. A specification for these linear algebra subroutines using scalars and vectors, Basic Linear Algebra Subroutines (BLAS) level-1 was published in 1979. To take advantage of vector processors, BLAS was augmented with level 2 operations that perform matrix-vector operations. To take advantage of cached memory, in 1987, level 3 BLAS operations were introduced that perform matrix-matrix computations. Many linear algebra libraries use BLAS libraries to perform linear algebra computations. LINPACK [1] library developed in late 1970s uses BLAS level 1 subroutines. LAPACK [19], released in 1992, is the successor of LINPACK and uses BLAS level 3 operations to exploit caches of modern architectures. LINPACK Benchmark [56] which is initially designed to estimate the performance of a system using LINPACK library, is still used to measure the performance of modern supercomputers. The benchmark used in LINPACK Benchmark is to solve a dense system of linear equations with LU factorization using partial pivoting. The TOP500 list ranks the supercomputers twice a year since June 1993 based on their performance on the LINPACK Benchmark [11].

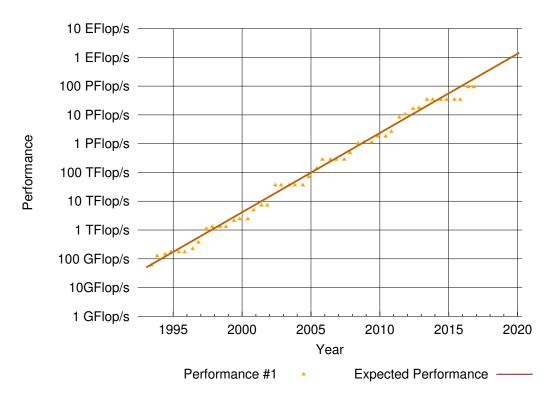

Figure 1: Expected performance of the fastest supercomputer.

Presently the fastest supercomputer in the world is Sunway TaihuLight,

developed at National Supercomputing Center in Wuxi, China. It achieve 93 PFlop/s performance on LINPACK Benchmark, while its theoretical peak is 125 PFlop/s [10]. Figure 1 shows the projected performance of fastest supercomputer for next few years [9]. It exhibits that the fastest supercomputer is expected to achieve exascale performance by 2020. Many countries, such as China, US, Japan, France have plans to deploy their exascale supercomputers in next few years. China is scheduled to deploy a prototype of an exacale computer this year and expected to field it in 2020 [78]. Japan has also plans to bring its first exascale computer by 2020/2021. France is also scheduled to get its first exacale machine deployed at CEA, the French Atomic Energy Agency, by 2020. Paul Messina, head of the US Department of Energy's Exascale Computing Project, recently announced that US will deploy initial exascale system sometime in 2021 [77].

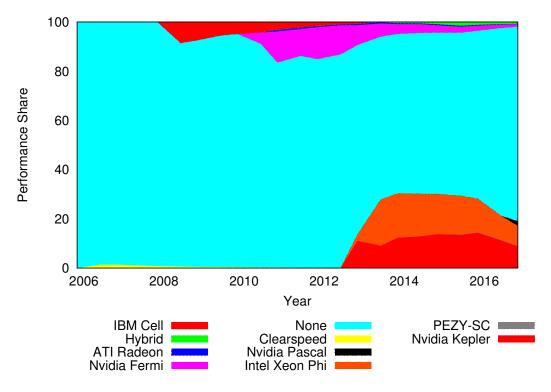

Figure 2: Performance share of different accelerators in TOP500 list.

Massive computation power of accelerator makes them to consider for supercomputers. Figure 2 shows the performance share of accelerators in the TOP500 list. The idea of using accelerators is not new (FPGAs were used in past as coprocessors), it is refurbished in recent years due to huge processing capabilities of the different accelerators. For example, Roadrunner supercomputer built by IBM, which had AMD Opteron processors and cell accelerators, ranked #1 in TOP500 list of June 2008 [2]. The use of accelerators for HPC

community however gained popularity with the advent of GPUs. Initially GPUs were used in rendering, which involves a large amount of computations. This led researchers to think that these devices could be used to accelerate scientific computing applications as well, especially where computation dominates latency, such as for dense linear algebra.

Figure 2 exhibits that presently 21 % performance share of TOP500 list is produced by accelerators. It also indicates that significant amount of computers in TOP500 list is based on hybrid architecture. Most of these systems are using Nvidia GPUs or Intel Xeon Phi coprocessors. The faster US supercomputer, Titan (3rd rank in TOP500 list) is also a hybrid supercomputer, which has AMD Opteron CPUs and Nvidia GPUs [7]. Optimizing performance of a complex computation on such hybrid architectures is very complex. Developing good scheduling algorithms, even on a single hybrid node, and analyzing them can thus have a very high impact on the performance of current HPC systems. This is the goal of this thesis.

Accelerators such as GPUs are employed in processing nodes usually beside multicores. When trying to exploit both CPUs and GPUs, users face several issues. Indeed, several phenomena are added to the inherent complexity of the underlying NP-hard optimization problem.

First, multicores and GPUs are unrelated resources, in the sense that depending on the targeted computation, the performance of the GPUs may be much higher, close or even worse than the performance of a CPU. In the literature, unrelated resources are known to make scheduling problems harder (see [41] for a survey on the complexity of scheduling problems, [73] for the specific simpler case of independent tasks scheduling and [31] for a recent survey in the case of CPU and GPU nodes). Second, the number of available architectures has increased dramatically with the combination of available resources (both in terms of multicores and accelerators). Therefore, it is almost impossible to develop optimized hand tuned kernels for all these architectures. Third, nodes have many shared resources (caches, buses) and exhibit complex memory access patterns (NUMA effects), that render the precise estimation of the duration of tasks and data transfers extremely difficult.

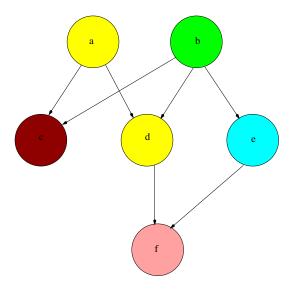

All these characteristics make it hard to design scheduling and resource allocation policies even on very regular kernels such as linear algebra. On the other hand, this situation favors dynamic strategies where decisions are made at runtime based on the state of the machine and on the knowledge of the application (to favor tasks that are close to the critical path for instance). In recent years, several task-based systems have been developed such as StarPU [22], StarSs [82], SuperMatrix [46], QUARK [104], XKaapi [67] or PaRSEC [36]. All these runtime systems model the application as a Direct Acyclic Graph (DAG), where vertices correspond to tasks and edges to dependencies between these tasks. Figure 3 shows an example of a DAG, where vertices a, b, c, d, e and f represent tasks, and edges ac, ad, bc, bd, be, df and ef represent dependencies

dencies. At runtime, the scheduler knows (i) the state of the different resources (ii) the set of tasks that are currently processed by all non idle resources (iii) the set of (independent) tasks whose all dependencies have been solved (iv) the location of all input data of all tasks (v) possibly an estimation of the duration of each task on each resource and of each communication between each pair of resources and (vi) possibly priorities associated to tasks and that have been computed offline. Based on this information, scheduler takes scheduling and allocation decisions. HEFT heuristic [99] is certainly the most popular of this class of algorithms.

Figure 3: A DAG.

In this thesis, we consider the scheduling problems of task based dense linear algebra kernels on a single hybrid node composed of CPUs and GPUs. The contributions of this thesis therefore cover the different aspects of scheduling which must be addressed at the level of the runtime system. More particularly we identify the following contributions.

- Performance comparison between static strategies with dynamic corrections and dynamic strategies with static information. We provide a fair performance comparison between static and dynamic strategies and we propose a set of intermediate strategies by adding more static (resp. dynamic) features into dynamic (resp. static) strategies. We also exhibit that adding simple static information about applications improves performance of dynamic schedulers significantly.

- Theoretical performance upper bounds of task graphs. It is well known that system peak is hard to achieve. Performance of any task based application is limited by its task types and dependencies among tasks. We provide some theoretical performance bounds by considering

heterogenity of tasks and resources as well as some dependencies. Performance bounds on task graphs help us to assess the quality of different schedulers.

- Resource centric schedulers for task graphs. A resource centric scheduler, *HeteroPrio* was proposed recently for a set of small independent tasks on two types of resources, which is based on affinity between tasks and resources [16]. We extend this scheduler for general task graphs. On two types of resources, affinity can be expressed as task acceleration factor but acceleration factor does not make sense when we have more than two types of resources. We consider different heuristics to define affinity and then generalize HeteroPrio to multiresource case. This scheduler is very effective for applications where scheduling decisions are very important, such as Cholesky factorization of medium size matrices.

- Approximation ratios of HeteroPrio. We provide approximation bounds of HeteroPrio compared to the optimal schedule in the case where all tasks are independent and for different platform size. We also provide worst case examples for different platform sizes and prove that almost all our bounds are tight.

The outline of the thesis is the following. Chapter 1 describes different state-of-the-art task based runtime systems, linear algebra libraries and simulators. In Chapters 2 and 3, we analyze different static and dynamic strategies and provide different performance bounds of task graphs. We extend Hetero-Prio to multiple resources in Chapter 4. In Chapter 5, we provide approximation ratios of Hetero-Prio on two types of resources.

The main contributions of different chapters are presented in the following paragraphs.

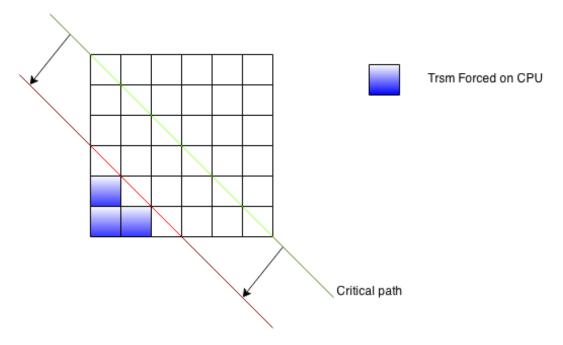

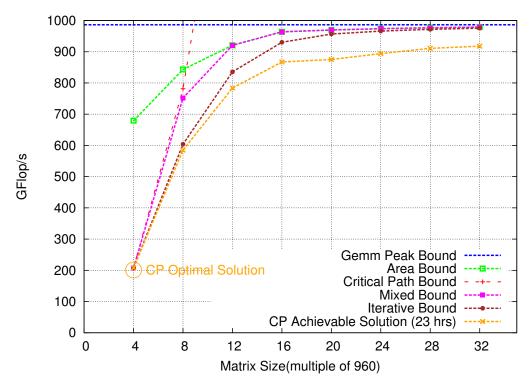

In Chapter 2, we concentrate on the analysis of the behavior of Cholesky factorization on a heterogeneous node consists of CPUs and GPUs. We show how adding simple static rules based on an offline analysis of the problem (such as processing of tasks which are far from critical path on slow resources) into dynamic schedulers improves the overall performance of the application. We also provide theoretical bounds on the performance of task graphs for a given platform. This work has been conducted in collaboration with Julien Herrmann and Loris Marchal from ENS Lyon, France.

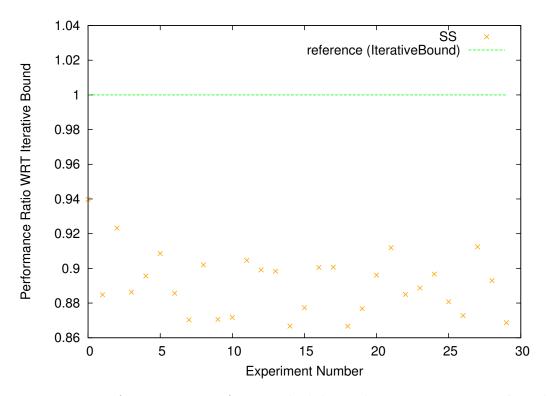

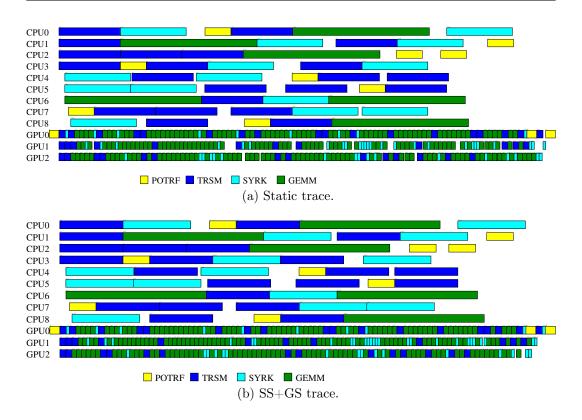

In Chapter 3 we propose different scheduling strategies by adding more static (resp. dynamic) features into dynamic (resp. static) strategies. We propose a dynamic strategy, HeteroPrio, which is based on the acceleration ratio on GPU to establish affinity between the resources and the different types of tasks, for general task graphs. In order to fully exploit the heterogeneous resources, GPUs should preferably execute tasks with higher acceleration factors,

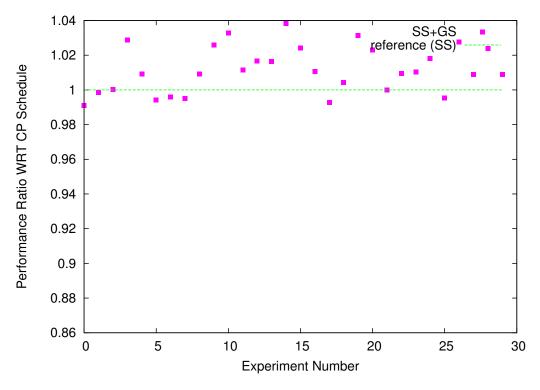

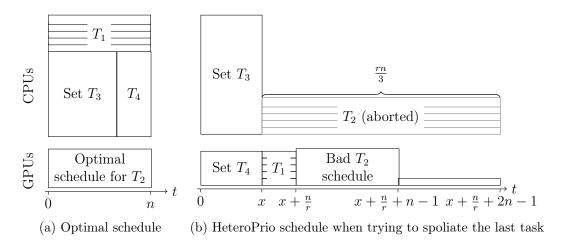

and CPUs should execute tasks with lower acceleration factors. HeteroPrio must be associated to a spoliation mechanism. Indeed, in above description, nothing prevents the slow resource to execute a task for which it can be arbitrarily badly suited, thus leading to arbitrarily bad results. Therefore, when a fast resource is idle and would be able to restart a task already started on a slow resource and to finish it earlier than on the slow resource, then the task is spoliated and restarted (not preempted) on the fast resource. We propose several corrections to HeteroPrio, such as fast (resp. slow) workers select the highest (resp. lowest) priority ready tasks and tasks whose acceleration factors are in a relatively thin range of values are treated equally, to find the best trade-off between acceleration of tasks and progress.

In Chapter 4, we extend HeteroPrio algorithm for more than two types of resources. Since HeteroPrio is based on the notion of heterogeneity, we proposed two heuristics to determine the heterogeneity score of a task on a resource. First heuristic is based on the area solution of the task graph for a given platform. It provides a generic way of detecting which tasks are more suited to which resources. Second heuristic is based on idea of how "good" this resource is compared to the worst one, and how "bad" it is compared to the best one. We exhibited that these heuristics are efficient even in highly heterogeneous configurations and outperform HEFT-based strategy significantly. This work has been conducted in collaboration with Terry Cojean, another PhD student of my research team, and Abdou Guermouche from HiePACS team, Inria Bordeaux, France.

In Chapter 5, we provide approximation ratios and worst case examples for HeteroPrio in the case where all tasks are independent. Interestingly, we show that spoliation allows to prove approximation ratios for a list scheduling algorithm on two unrelated resources, which is not possible otherwise. We also establish that almost all our approximation ratios are tight.

# Chapter 1

# Background

In this chapter, we describe different tasks based runtime systems which allow programmers to express applications at high level with simple APIs and relieve them from the burden of dealing with low-level details such as prefetching, data transfers, scheduling of tasks, or synchronizations. Runtime systems employ a very modular approach. Applications are expressed as directed acyclic graphs (DAG) of tasks, where vertices represent tasks to be executed and edges represent dependencies between those tasks. We also describe a framework to perform simulations, especially Simgrid and StarPU version of Simgrid.

In last, we present various dense linear algebra libraries and matrix factorization algorithms. Most modern linear algebra libraries implement tile versions of different matrix factorizations using a runtime system, where the runtime system takes care of effective scheduling of tasks. In the past few years, while GPUs have gained in popularity, tile algorithms have heavily been employed to handle heterogeneous architectures. In that case, the runtime system may assign some tasks to the GPUs to accelerate them.

## 1.1 Task-based Runtime Systems

Complexity and scale of platform is increasing continuously to satisfy HPC computational needs. To cope with the increasing complexity and scale of hardware architectures and exploit the full capacity of platform with existing code, most of the computational applications are expressed at high level in the form of a DAG of tasks. Then a task scheduler or runtime system is used to schedule those tasks on the given hardware platform. In this section we provide a brief overview of different runtime systems and their important features.

#### 1.1.1 StarPU

StarPU [22] is a runtime system developed at Inria Bordeaux, France, specifically designed for heterogeneous multicore architectures. It allows program-

mers to exploit the computing power of the available CPUs and GPUs, while relieving them from the need to specifically adapt their programs to the target machine and processing units. The StarPU runtime supports a task-based programming model. Applications submit computational tasks, forming a DAG, with CPU and/or GPU implementations. The code for each type of task implementation is provided separately. This separation of concerns not only allows for ensuring a modular design but it is also very convenient for writing portable codes. Indeed if one provides both CPU and GPU implementations of a task, this task can be executed on either of these units. StarPU schedules tasks and associated data transfers on available CPUs and GPUs. The data that a task manipulates is automatically transferred to the computational unit where the task has been decided to execute, so that application programmers are freed from scheduling issues and technical details associated with these transfers. In particular, StarPU takes care of scheduling tasks efficiently, using well-known generic dynamic and task graph scheduling policies from the literature, and optimizing data transfers using prefetching and overlapping, in particular. In addition, it allows scheduling experts, such as compiler or computational library developers, to implement custom scheduling policies in a portable fashion. Complete description of StarPU can be found in the work by Augonnet [20].

#### StarPU Execution Model

In StarPU, the execution is initiated by the main thread, running on a CPU, which submits all the tasks asynchronously and the execution of tasks is performed in parallel by different worker threads (or, simply, workers). A CPU worker is bound to a CPU core while a GPU worker is bound to a GPU core and a CPU core to exploit GPU efficiently. StarPU also allows a worker to submit other tasks at runtime although it is not in the interest of sequential submission. StarPU requires registration of all data associated with a task before submitting the task. Each StarPU task contains a codelet which describes a computational kernel and its possible implementations on different architectures, such as CPU, GPU. Figure 1.1 shows an example of a StarPU codelet. It indicates on what computational units (where field) the corresponding task can be executed and function pointers to different implementations (cpu\_funcs and gpu\_funcs fields). It also indicates the number of data/handles (nbuffers field) manipulated by its task. A task also describes what data are accessed and how they are accessed (read and/or write mode) during computation. Executing a task can be viewed simply as a function applying a codelet on a data set associated with the task. Task dependencies are inferred from data dependencies. However programmers are allowed to express dependencies explicitly for some data.

```

/* Codelet definition for kernel f */

struct starpu_codelet f_cl =

{

.where = STARPU_CPU | STARPU_CUDA,

.cpu_funcs = { f_cpu_func },

.cuda_funcs = { f_cuda_func },

.nbuffers = 2

};

```

Figure 1.1: A StarPU codelet.

#### StarPU Scheduling Model

StarPU scheduler schedules tasks when they become ready to be executed, i.e., all dependencies are satisfied. Each worker pulls tasks one by one from the scheduler. This is up to programmers how to implement a scheduler. However, StarPU provides a few schedulers based on well known dynamic task graph scheduling heuristics. All schedulers usually contain at least one queue to store tasks between the time when they become available and the time when a worker picks them. Here is the description of few StarPU schedulers which are relevant to this thesis.

- random: This scheduler assigns tasks randomly over all the computational resources. It uses an estimation of the relative performance of the resources to balance the randomness. This is thus representative of classical partition heuristics, which take heterogeneity of resources into account but not heterogeneity of tasks.

- ws (work stealing): This scheduler uses a queue of tasks per worker. All tasks released by a worker are added to its own queue. An idle worker steals a task from the most loaded worker.

- eager: This scheduler uses a central task queue to store ready tasks. An idle worker selects a task from the central queue. It does not give time to scheduler to prefetch data since the scheduling decisions are made very late.

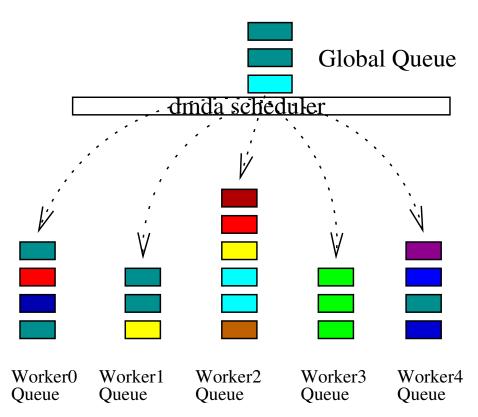

- dmda (dequeue model data aware): This scheduler takes task execution performance models and communication models into account to make scheduling decisions. It is based on the Minimum Completion Time (MCT) heuristic [103] to assign tasks to computational resources. Each task is assigned to the worker which is expected to complete it first, taking both the estimated computation time on the estimated target

resource and the data transfers time into account, thus making it representative of the state-of-the-art HEFT heuristics [99]. Figure 1.2 exhibits working principle of **dmda** scheduler, where scheduler takes a task from global queue, a queue with set of ready tasks, and pushes it to one of the worker queues based on minimum completion time heuristic. In practice, **dmda** does not use any global queue and a ready task is directly pushed to one of the worker queues. However, for better understanding we can think that ready tasks are stored in a global queue.

- **dmdar** (dequeue model data aware ready): This scheduler is a refinement of **dmda**, where each worker picks from its queue the task whose most data is available on its associated memory.

- **dmdas** (dequeue model data aware sorted): This scheduler is another refinement of **dmda**, where tasks are sorted by priority order in each worker queue, which makes it even closer to HEFT.

Figure 1.2: Working principle of **dmda** scheduler.

The work presented in this thesis relies on the StarPU runtime system and StarPU scheduling model. This is mostly due to its large set of features which include full control over the scheduling policy, support for hybrid platforms and efficient handling of data transfers. Here are some features of StarPU which we used extensively in this thesis.

- StarPU can generate execution traces containing execution timings of all executed tasks, data transfers information, runtime overhead and memory loads. The execution trace allows programmers to analyze the application execution in details and help to find what went wrong with the execution. This feature also helps one to develop new scheduling policies and perform different theoretical analysis such as lower bound on performance, distribution of tasks of the execution. StarPU generated trace can be visualized with different visualizer tools, such as ViTE (visual trace explorer) [4].

- Different applications exhibit different types of characteristics and therefore sometimes it is required to implement custom scheduling policies to exploit the platform in an effective way. StarPU allows programmers to implement their own scheduling policies.

- StarPU automatically calibrates and stores the execution timings of different kernels and data transfer time between two memory nodes which have not been calibrated yet. Estimation based schedulers such as **dmda** require this information in order to make scheduling decisions. We have used calibrated timings extensively to perform different simulations throughout this thesis.

- In some scenarios, one may want to force scheduling, for example force a given a set of tasks to a particular resource. StarPU provides this feature by allowing programmer to specify the worker identity while inserting the task. StarPU also allows one to specify the order in which tasks must be executed. This feature provides a total control to implement a static schedule in StarPU. In this case, at runtime it simply follows the order of execution as prescribed by the programmer. We have used this feature extensively in Chapter 2

- StarPU can use Simgrid to provide simulation support on any arbitrary platform [96]. In this case StarPU runs the application normally, except that data transfers and computation kernel calls are replaced by a simple procedure accounting for the time they are expected to take, and gathered coherently by Simgrid.

#### 1.1.2 **QUARK**

Queueing And Runtime for Kernels (QUARK) [104] is a runtime environment for the dynamic scheduling and execution of tasks based applications on multicore and multi-socket shared memory system, which is developed at the Innovative Computing Laboratory (ICL), University of Tennessee. It is similar to StarPU and based on the dataflow model where dependencies are inferred through a runtime analysis of data usage by the different kernels. It dynamically schedules tasks whose all incoming dependencies are satisfied. QUARK was originally designed to support dynamic linear algebra algorithms for the PLASMA linear algebra project [42]. The QUARK runtime contains several optimizations inspired by algorithms in PLASMA. It is capable to support other applications which can be decomposed into tasks with data dependencies. The goal of QUARK project is to provide an easy-to-use interface for application programmers that scales efficiently to large number of cores. QUARK does not support hybrid platforms, mainly because it does not deal with data movements.

#### 1.1.3 Parsec

Parallel Runtime Scheduling and Execution Control (Parallel Section 26) is a generic framework for dynamic scheduling of tasks on distributed many-core heterogeneous architectures, which is developed at the ICL laboratory, University of Tennessee. The high level difference between StarPU and PaRSEC is the way tasks and their dependencies are represented. In StarPU, a thread submits all tasks asynchronously and then runtime detects dependencies among different tasks. While Parasec uses a symbolic Parameterized Task Graph (PTG) [52] to represent tasks and their data dependencies to other tasks. PaRSEC does not build a DAG in memory and does not analyze the way tasks depend on one another by analyzing input and output data. Rather, this information is expressed by programmers in the PTG format. As a consequence, it is harder to write programs in PTG format. In PTG format, programmers have to mention all possible input and output dependencies in a compact form. The size of PTG representation for an application does not depend on the size of the problem, but only on the number of different types of tasks used by the application. As dependencies are explicitly provided by programmer, it also supports irregular applications. The PTG model is extremely scalable, the runtime can determine successors and predecessors information for any local task quickly. The DPLASMA library [35] is a dense linear algebra library implemented on top of Parsec runtime system.

Parsec has limited support for heterogeneous systems, in the case of Cholesky for instance, it only runs GEMM kernels on the GPUs, and thus uses very simple heuristics to determine which kernels to run on the GPUs.

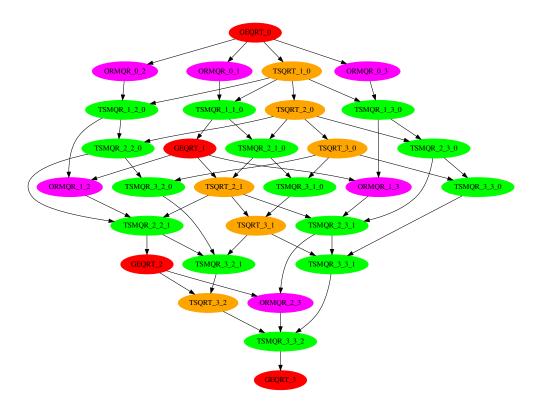

Figure 1.3 shows PTG representation of DPOTRF kernel of Cholesky Factorization. It indicates that we have SIZE instances of DPOTRF, numbered from k=0 to k=SIZE-1, where instance k=0 of DPOTRF is immediately available, while others have to wait for the previous DSYRK tasks, and instance k of DPOTRF releases the corresponding SIZE-k DTRSM tasks. Details about PTG representation and how to write program in PTG can be found in [36].

```

DPOTRF(k)

// Execution space

k = 0 . . SIZE-1

//Flows and dependencies

T < - (k == 0) ? A(k, k) : T DSYRK(k-1, k)

-> T DTRSM(k, k + 1 . . SIZE-1)

-> A(k, k)

```

Figure 1.3: PTG representation of POTRF kernel.

Parallel codes. Then a specific compiler, known as *daguepp*, converts JDF code to C-code.

### 1.1.4 OpenMP

Due to the wide popularity of task based runtime systems, tasking feature was included in OpenMP version 3.0 [80]. Tasking facilitates the parallelization of applications where tasks are created in a recursive way or through a while loop. An explicit task is specified using the task directive. The task directive defines the code associated with the task and its data environment. A thread creates a new task after encountering a task construct. The task construct can be placed anywhere in the program. Note that OpenMP is not really a runtime system, but an interface standard, implemented by various systems, notably compilers. It however guides a lot how the underlying runtime works.

When a thread creates a task, it may defer the execution of the task for later. If task execution is deferred, then the task is placed in a pool of tasks. The threads in the current team will take tasks from the pool and execute them until the pool is empty. The thread that executes a task may be different from the thread that originally submitted it.

By default, tasks are tied to the thread that first executes them, it may not be the creator thread. Programmers can use "untied" clause to remove all restrictions. "untied" tasks provide more freedom to implementation and can be scheduled based on different heuristics, such as load balancing. The task construct was extended with a depend clause in OpenMP version 4.0 [81], which enables OpenMP runtime to automatically detect dependencies among tasks and schedule them appropriately. The same OpenMP version also provides support for accelerators with a target construct. The execution model of OpenMP for accelerators is host centric and it assumes that each accelerator device is attached to a host device. A target region begins as a single thread execution and when a target construct is encountered, the implicit device thread executes the target region and the encountering thread waits at the construct until the execution of region completes.

OpenMP does not provide any freedom to the runtime to decide on which CPU or GPU to run tasks. However, with a few extensions to OpenMP such as OpenMP interface of StarPU [14] (which does not support hybrid platforms yet), we could relax it and improve performance of OpenMP applications.

#### 1.1.5 StarSs

StarSs [82] is a sequential task-based programming model, developed at Barcelona Supercomputing Center (BSC), where programmer writes sequential code in a traditional programming language (i.e., C, C++ or Fortran) which is executed in parallel and runtime manages the data dependencies and data movements between tasks. Many instantiations of StarSs have been developed to target different architectures: CellSs for Cell processors, SMPSs for shared memory machine and homogeneous multicore processors, GridSs for computational grids, GPUSs for heterogeneous multi-accelerator platforms. In StarSs, user annotates the applications to target a particular architecture. It uses a few OpenMP like pragmas to identify tasks in the user code. It implements data renaming to eliminate false dependencies. StarSs implements a task hierarchy which allows instantiation of subtasks within a task in the following way. Each task creates a private context for its subtasks. Synchronization and data dependencies are considered in the same context. A given task waits for the end of its children tasks before finishing.

Planas et al. have exhibited some experiments that combine a first task level with SMPSs and a second task level with CellSs to take advantage of both architectures [82]. Tasks are scheduled in a hierarchical fashion, however CellSs tasks are only scheduled once the corresponding SMPSs task has been assigned to a Cell processor. Therefore, having separate runtime systems does not allow to actually schedule tasks between heterogeneous types of processing units unless the programmer explicitly selects the target platform, and therefore which runtime system should process the task.

The main difference between StarPU and the different instantiations of StarSs is that StarPU really provides a unified abstraction of driver that makes it possible to deal with different types of platforms. In the StarSs programming model, execution timings are not known in advance which prevents it from

implementing estimation based strategies, such as HEFT.

OmpSs is an attempt to integrate features from the StarSs programming model in to a single programming model [57]. It extends OpenMP with new directives to support asynchronous parallelism and hybrid architectures. Similar to StarPU, in OmpSs user writes code for a single address space which may execute in several non coherent address spaces. OmpSs implements data packing to minimize the number of transfers among different memories. It uses locality aware work stealing strategies to achieve load balancing among different processing units. The OmpSs programming model presently supports the following architectures: 1) Intel 32- and 64-bit platforms including support for CUDA on NVidia GPUs, 2) Intel MIC in native and offload modes, 3) IBM Power8 platforms including support for CUDA on Nvidia GPUs, and 4) ARM 32- and 64-bit platforms, including support for OpenCL MALI GPUs (32 bits version only).

#### 1.1.6 XKaapi

XKaapi [67] is a runtime system for data flow programming on multi-CPU and multi-GPU architectures developed at Inria Grenoble, France. It provides different APIs to program heterogeneous parallel architectures in C, C++ and Fortran. It relies on different work stealing heuristics to ensure load balancing among different processing units. It uses fully asynchronous task execution strategy on GPUs to overlap computations with data transfers. It creates a system thread and a work queue for each computational resource. The unique feature of XKaapi is that it minimizes the overhead of critical paths by postponing the data dependencies computations to idle threads. Therefore, it moves the cost of computing ready tasks from task's creations to the steal operations performed by idle threads. It works on the following work stealing mechanism: an idle thread submits a steal request to a randomly chosen victim. On reply, the requesting thread gets a copy of one ready task and original task is marked stolen in victim's queue. To find a ready task, the requesting thread iterates through the victim's queue from the least recent pushed task to the most recent one and computes true data dependencies for each task. The iteration stops when requesting thread finds a ready task in the victim's queue. XKaapi also uses two different locality aware heuristics with work stealing to improve the performance. The first one is based on minimization of data transfers among resources during steal operation. A task is assigned to the resource which owns the largest sum of input bytes. The second heuristic is based on an owner compute rule, a task is assigned to the resource which minimizes the number of invalidation of data replicas. Ties are broken by selecting a resource randomly among the set of eligible resources. Both heuristics actually do not correspond to steal mechanism and push tasks to remote workers. XKaapi also implements different queues for each worker to accelerate the search operation for a ready task while stealing.

Similar to Cilk [32] and OmpSs, in XKaapi, a task can create children tasks which is not the case with other data flow programming libraries, such as StarPU, QUARK. False dependencies can be eliminated in XKaapi through variable renaming by using extra memory and write back policy is used to maintain the data coherency. Similar to StarPU, XKaapi uses codelet based low overhead task representations that allow to handle a high degree of parallelism efficiently. A task may have multiple implementations, such as a CPU implementation and a GPU implementation. At least one implementation is required for each task. The implementation may be recursive, which allows XKaapi to decompose some tasks further to subtasks operating on smaller data.

Most recent GPUs, such as Fermi have one execution engine and two copy engines, which enable to perform a kernel execution and two way memory transfers simultaneously. Similar to other runtimes, XKaapi also takes advantage of this by using a new data structure, called kstream, which combines together three types of CUDA streams: a stream for host to device transfer, a stream for kernel execution and a stream for device to host transfer.

#### 1.1.7 SuperMatrix

SuperMatrix is a multithreaded runtime system that parallelizes matrix operations for SMPs and multi-core architectures [46]. It views matrices hierarchically, matrices of matrices. The unit of computation is operations on a single submatrix. It enqueues the required operations, tracks dependencies, and then executes the operations utilizing out-of-order execution techniques inspired by superscalar processors.

The Formal Linear Algebra Methods Environment (FLAME) project uses SuperMatrix runtime system to parallelize dense and carefully structured sparse linear algebra computations [69]. Detecting dependencies across different iterations is very difficult in FLAME, as different submatix views may reference to the same block. It requires complete knowledge of matrix partitioning to determine what regions of matrix are being referenced. However, FLASH (Formal Linear Algebra Scalable Hierarchical), extension of FLAME API, delimits the block referenced by each submatrix view.

API for defining tasks on OmpSs and SuperMatrix is quite different. OmpSs uses annotations, similar to OpenMP, which are placed around function calls to denote different tasks. Then, a source to source compiler converts these annotations to code that performs dependency analysis and out of order execution. The load balancing of tasks can vary based on the computational runtime of each function. While in SuperMatrix, computation runtime of each task depends on the size of each submatrix created using the FLASH API.

#### 1.1.8 Legion

Legion is a data centric programming model and runtime system for achieving high performance on distributed heterogeneous architectures developed at Stanford University [25]. It provides an interface such that programmers can explicitly declare different properties of program data, such as data organization, partitioning. It also allows programmers to control the mapping of tasks on to different architectures. It uses logical regions to describe the locality and independence of data. Each Legion program executes as a tree of tasks with a top level task generating sub-tasks which can recursively generate further subtasks. It provides the ability to partition data in multiple ways and to migrate data dynamically between these views as application moves between different phases of computation.

The Legion programming model uses a *software out-of-order processor*, or SOOP, for scheduling tasks. The SOOP takes locality and independence properties captured by logical regions into account while making scheduling decisions.

#### 1.2 Simulation Framework

In recent years, advances in hardware and software technologies made it possible to execute different HPC applications over increasingly large sets of resources. The study of scheduling problems for such applications and platforms has been quite significant in recent times. Simulation is a popular and effective way to evaluate and compare different scheduling algorithms over a wide range of scenarios.

Many fine grained simulators such as GPGPU-Sim [23] have been developed for GPUs in past years which simulate at cycle level. There are also a few GPU-specific simulators such as Barra [51] for the Nvidia G80, Multi2Sim [100] for the AMD Evergreen GPU. Simulation time of these simulators is very long because every detail of the specific GPU is simulated. There are a few simulators such as SST [90], TaskSim [88] which are based on multiple levels of abstraction to provide good prediction. However these address only multicore machines with no GPUs so far. We use Simgird [45] simulator in this thesis which is accurate enough for our need while being very fast.

### 1.2.1 Simgrid Simulation Engine

Simgrid is a versatile simulation toolkit initially designed to study the behavior of different scheduling algorithms on large-scale distributed systems like grids, clouds, or peer-to-peer systems. It builds on fluid network models that have been proven as a reasonable alternative to both simple analytic models and expensive, difficult-to-instantiate packet-level simulations.

The Simgrid version of StarPU [96] uses Simgrid to simulate the execution of an application within a single machine. The idea is to run the application normally, except that data transfers and computation kernel calls are replaced by a simple procedure accounting for the time they are expected to take, and gathered coherently by Simgrid. StarPU models each execution unit (CPUs and GPUs) by defining the time taken by each execution unit on each possible task/kernel [21]. It also models the PCI buses between them, using offline bus bandwidth measurements, and relies on Simgrid to compute the interferences on PCI buses between the different transfers.

The resulting simulated times are very close to actual measurements on the real platforms [96], and properly reproduce the various behaviors that can be observed for the different schedulers. This allows one to confidently run experiments with the Simgrid version of StarPU, which provides several advantages:

- The time to simulate execution is reduced, since no actual computation or data transfer is performed. The Simgrid simulator itself is not parallel, so the whole execution gets serialized, but several simulations can be run in parallel for e.g. various matrix sizes or schedulers, and one then gets all the results in parallel.

- The experiments do not depend on the availability of the platform, both in terms of quotas, and in terms of versions of the installed software, thus allowing reproducible experiments. This proved useful while performing the experiments for this thesis, since the platform became unavailable for a couple of times due to different issues such as air conditioning, software upgradation, transition from PBS to SLURM job scheduler.

- The platform can be modified, for instance to change the available PCI bandwidth, the execution times of the kernels, etc. In Chapter 2, we use this feature in order to build a virtual "related" heterogeneous platform.

Simgrid version of StarPU allows to perform simulations on any machine by using the configuration files of target platform and expected execution time of kernels on each resource of the target platform. We use this to evaluate the effectiveness of the different scheduling algorithms on a single heterogeneous node in Chapter 2.

Simgrid does not provide a framework to support simulation within a simulation (two levels of simulations) and to handle spoliation of tasks. These two features were required to evaluate some of our scheduling algorithms. Therefore, we have written our own simulator to support both of these features and used it in Chapters 3, 4 and 5.

## 1.3 Dense Linear Algebra Libraries

Linear systems of equations, Least squares problems, Eigen value problems and Singular value decomposition problems are the basic problems of linear algebra. In this section, we briefly describe some old and some state-of-the-art numerical linear algebra libraries designed for dense matrices.

#### 1.3.1 LINPACK (LINear algebra PACKage)

LINPACK is a software library written in FORTRAN66 by Jack Dongarra, Jim Bunch, Cleve Moler, and Gilbert Stewart [1]. This project had started in 1974 and it was intended for use on supercomputers in the 1970s and early 1980s. During that period, supercomputers with vector processors were very popular, therefore LINPACK was basically designed to exploit vector processors. This library provides routines to solve systems of linear equations for general, banded, symmetric indefinite, symmetric positive definite, triangular, and tridiagonal square matrices. It also provides routines to compute QR and singular value decompositions of rectangular matrices. It makes use of BLAS libraries for performing vector operations (BLAS level 1 operations). LINPACK has been largely superseded by LAPACK [19], which has been designed to run efficiently on machines with hierarchical memory design.

### 1.3.2 LAPACK (Linear Algebra PACKage)

LAPACK [19] is a standard software library for numerical linear algebra. It was originally written in FORTRAN77, but moved to FORTRAN90 in version 3.2 (2008). It provides routines for solving systems of linear equations, least square solutions of systems of linear equations, eigen value problems and singular value problems. It also provides routines to implement different matrix factorizations such as LU, Cholesky, QR, SVD and Schur. It provides routines for both real and complex matrices in both single and double precision. It handles dense and banded matrices, but not general sparse matrices. LAPACK library was first released in 1992.

The original goal of LAPACK project was to make LINPACK and EIS-PACK [59] libraries to run efficiently on shared memory vector and parallel processors. On these machines LINPACK and EISPACK are inefficient because memory access patterns do not take multi layer memory hierarchies into account, therefore spending too much time moving data instead of doing useful floating-point computations. LAPACK solves this problem by reorganizing the algorithms to use block matrix operations such as matrix multiplication in the innermost loop. These block operations can be optimized for each architecture to account for memory hierarchy and so provide a portable way to achieve high efficiency on different modern machines.

Maximum efficacy of LAPACK routines are performed by calls to different Basic Linear Algebra Subprograms (BLAS). LAPACK is designed to exploit BLAS level 3 operations. Coarse granularity of BLAS level 3 operations assists to obtain high efficiency on many high performance computers.

LAPACK uses multi threaded implementation of BLAS libraries to efficiently exploit SMP processors. LAPACK has also been extended to run on distributed memory system in later packages such as ScaLAPACK [28] and PLAPACK [18].

# 1.3.3 PLASMA (Parallel Linear Algebra Software for Multicore Architectures)

The main goal of the PLASMA project is to address performance shortcomings of LAPACK and ScaLAPACK libraries on multicore processors and multisocket systems of multicore processors [42]. PLASMA uses tile based data layout and provides implementation of state-of-the-art algorithms using task based scheduling techniques. It assigns work to cores based on the availability of data for processing at any given point during execution. It is based on data driven scheduling, which is close to the idea of Section 1.1, where computations are expressed through a DAG, and DAG is explored at runtime. PLASMA uses QUARK runtime system to perform dynamic scheduling of tasks.

PLASMA has been designed to supersede LAPACK and ScaLAPACK by restructuring the software to expose more parallelism and achieve much greater efficiency, where possible, on modern computers based on multicore architectures. It also relies on new or improved algorithms. PLASMA does not replace ScaLAPACK as software for distributed memory computers, since it only supports shared memory machines.

PLASMA has also been extended to run on distributed memory system in later package DPLASMA [35].

# 1.3.4 MAGMA (Matrix Algebra for GPU and Multicore Architectures)

MAGMA library is an extension of LAPACK library for GPU and multicore architectures [98]. It uses static scheduler for distribution of work on different computational units. It schedules embarrassingly parallel tasks such as GEMM on GPU and small tasks which are very less parallelizable and often on critical path such as POTRF on CPU. In MAGMA, algorithms are split of varying granularity to utilize different hybrid component efficiently. It also supports out-of-device memory algorithms by dividing the matrix into different sub-matrices and transferring a submatrix to GPU to perform computations and then remaining matrix is updated accordingly. It uses 1-D block cyclic

data distribution [97] to support multiple GPUs. It handles real and complex matrices in both single and double precisions.

The goal of MAGMA is to design linear algebra algorithms and frameworks for hybrid multicore and multiGPU systems that can enable applications to fully exploit the power of each hybrid component. We performed performance comparison of some of our approaches with MAGMA in Chapter 4.

# 1.3.5 MORSE (Matrices Over Runtime Systems at Exascale)

To cope with the increased degree of parallelism, a new class of linear algebra algorithms has been proposed, often referred as tile algorithms in the literature [44, 85]. These algorithms led to the design of new libraries in the past five years such as PLASMA, FLAME and DPLASMA. Although both static and dynamic versions of the algorithms have been initially implemented, the dynamic codes are now predominant since they proved to provide more flexibility. These dynamic codes rely on runtime systems (QUARK, Supermatrix, PaRSEC) that have been specifically designed for the purpose of the numerical software (in the case of PLASMA, FLAME and DPLASMA, respectively).

The advantage of relying on specialized runtime systems is that they can be optimized for both the numerical algorithm and the target architecture. On the other hand, designing and maintaining a runtime system is a highly time consuming task, which makes it difficult to design a fully-featured specialized runtime system.

The main goal of MORSE [5, 6] project is to enable different numerical algorithms to execute on a scalable unified runtime system which exploits the full potential of future exascale machines. To develop numerical linear algebra softwares that will perform well on petascale and exascale systems with thousands of nodes and millions of cores, several challenges have to be overcome, both by numerical linear algebra and runtime system communities. MORSE project aims at describing linear algebra algorithms at a high level of abstraction, which will enable the strong collaboration between linear algebra, runtime system, and scheduling communities to fully benefit from the potential of future large scale machines. This project aims at bridging the immense software gap that has opened up in front of the HPC community.

#### 1.3.6 CHAMELEON

Chameleon is a sub-project of MORSE specifically dedicated to dense linear algebra [8]. It relies on sequential task-based algorithms where tasks of the algorithms are submitted to a runtime system. Such a system is a bridge between the application and the hardware which handles the scheduling, data transfers and the effective execution of tasks on to the processing units. A

runtime system such as StarPU is able to manage automatically data transfers between non-shared memory areas (CPUs-GPUs, distributed nodes). This kind of implementation paradigm allows to design high performing linear algebra algorithms on very different types of architectures.

The Chameleon library is based on the PLASMA tile algorithms (and code) but relies on the StarPU generic runtime system instead of the specialized QUARK runtime system. One advantage is that it allows for handling heterogeneous architectures (whereas PLASMA and QUARK were initially designed for multicore chips). Another advantage is that, when aiming at analyzing different scheduling strategies, it allows to run in simulation mode with the field-proven combination [96] of StarPU and Simgrid. Chameleon also supports PaRSEC, QUARK and OmpSs runtime systems.

#### 1.4 Dense Matrix Factorizations

Dense matrix factorizations are the basis of many scientific applications. In this thesis we consider one of them, namely the Cholesky factorization, extensively for our experiments. We also consider the QR and LU factorizations for some of our experiments. In this section, we briefly describe the Cholesky, QR and LU factorizations.

#### 1.4.1 Cholesky Factorization

The Cholesky factorization (or Cholesky decomposition) decomposes a positive definite matrix A into a unique lower triangular matrix L such that  $A = LL^{\top}$ . This type of factorization is very useful for efficient numerical solutions and different types of simulations such as weather predictions [47], Monte carlo simulations [66] and optics simulations [74]. It involves around  $\frac{N^3}{3}$  floating point operations for  $N \times N$  matrix. Where applicable, it is almost twice more efficient than the LU factorization for solving systems of linear equations. The Cholesky factorization also decomposes a positive semi definite matrix into a lower triangular L such that  $A = LL^{\top}$ , but such decomposition may not be unique.

Here is an example of the Cholesky factorization for a positive definite matrix.

$$\begin{pmatrix} 1 & 2 & 3 \\ 2 & 20 & 26 \\ 3 & 26 & 70 \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 \\ 2 & 4 & 0 \\ 3 & 5 & 6 \end{pmatrix} \begin{pmatrix} 1 & 2 & 3 \\ 0 & 4 & 5 \\ 0 & 0 & 6 \end{pmatrix}$$

The Cholesky factorization is mainly used to solve a system of linear equations Ax = b, where A is a  $N \times N$  symmetric positive-definite matrix, b is a vector, and x is the unknown solution vector to be computed. Ax = b can

be solved by first computing a lower triangular matrix L such that  $A = LL^{\top}$ , then solving Ly = b for y by forward substitution and finally solving  $L^{\top}x = y$  for x by backward substitution.

Linear systems of equations Ax = b often arise in physics applications, especially when looking for numerical solutions of partial differential equations or solving least square problems, where A is positive-definite due to the nature of the modeled physical phenomenon [62]. There is abundant literature on the implementation of dense as well as sparse Cholesky factorization on different platforms [86, 87, 79, 92, 91, 49].

#### Tile Cholesky Factorization

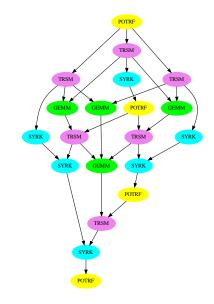

To take advantage of modern highly parallel architectures, state-of-the-art numerical algebra libraries implement tile Cholesky factorizations. The matrix  $A = (A_{ij})_{0 \le i,j \le N}$  is divided into  $N \times N$  tiles (or blocks) of  $N_b \times N_b$  elements, and the tile Cholesky algorithm can then be seen as a sequence of tasks that operate on small portions of the matrix. This approach greatly improves the parallelism of the algorithm and mostly involves BLAS3 kernels whose library implementations are really fast on modern architectures. The benefits of such an approach on parallel multicore systems have already been discussed in the past [65, 44, 85]. Following the BLAS and LAPACK terminology, the tile algorithm for Cholesky factorization is based on POTRF, TRSM, SYRK, and GEMM kernel subroutines.

Algorithm 2 shows the pseudo-code of the tile version of the Cholesky factorization implemented in the Chameleon library. In each instance of the outer loop, a Cholesky factorization (POTRF kernel) on the ith diagonal tile is performed and the trailing panel is updated with triangular solve (TRSM kernel). Then, the remaining trailing submatrix is updated by applying symmetric rank-k updates (SYRK kernel) on the diagonal tiles and general matrix multiplications (GEMM kernel) on non-diagonal tiles.

#### Algorithm 1: Tile Cholesky Factorization.

```

\begin{aligned} & \textbf{for } i = 0 \dots N - 1 \ \mathbf{do} \\ & & A[i][i] \leftarrow \underset{}{\mathsf{POTRF}}(A[i][i]); \\ & \textbf{for } j = i + 1 \dots N - 1 \ \mathbf{do} \\ & & \bot A[j][i] \leftarrow \underset{}{\mathsf{TRSM}}(A[j][i], A[i][i]); \\ & \textbf{for } k = i + 1 \dots N - 1 \ \mathbf{do} \\ & & \bot A[k][k] \leftarrow \underset{}{\mathsf{SYRK}}(A[k][k], A[k][i]); \\ & & \texttt{for } j = k + 1 \dots N - 1 \ \mathbf{do} \\ & & \bot A[j][k] \leftarrow \underset{}{\mathsf{GEMM}}(A[j][k], A[j][i], A[k][i]); \end{aligned}

```

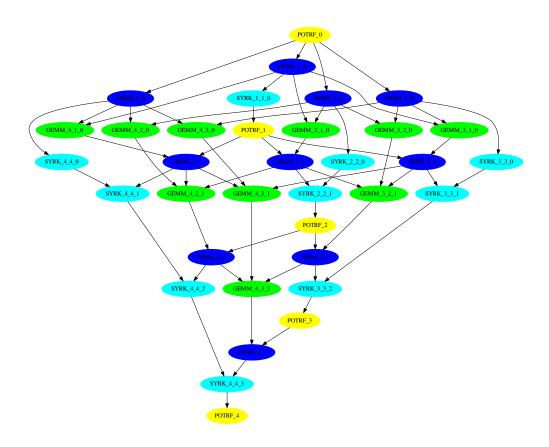

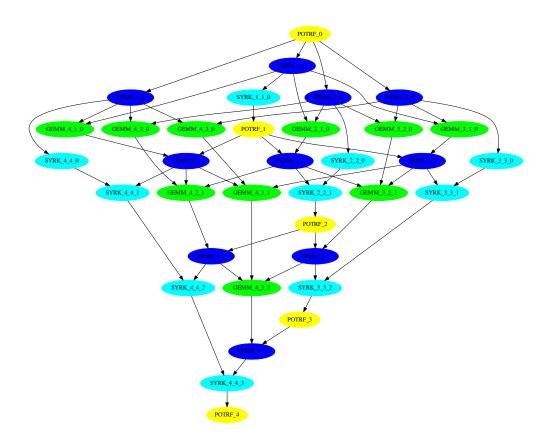

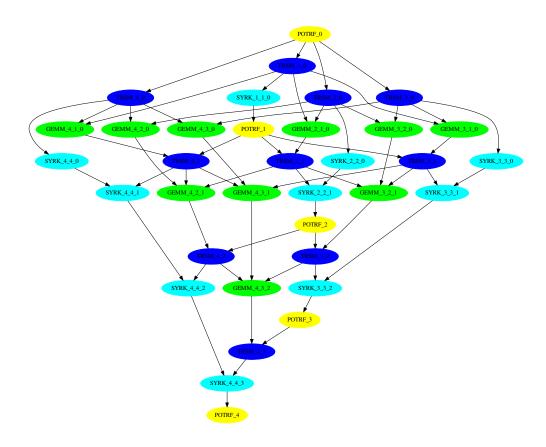

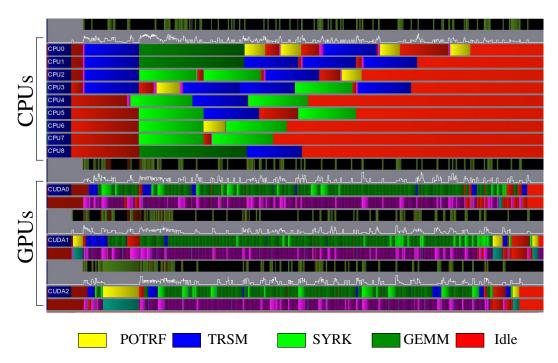

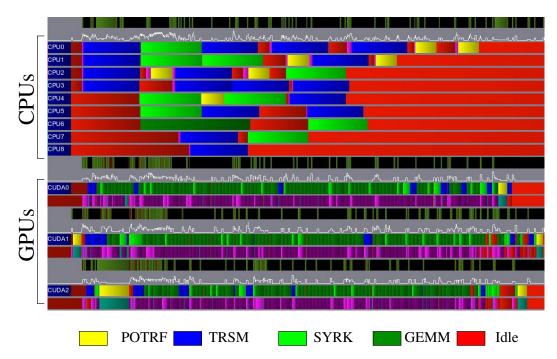

The sequence of computations for tile Cholesky factorization can be represented with a DAG of tasks as depicted in Figure 1.4 in the case of  $5\times5$  tile matrix.

Figure 1.4: DAG of the tile Cholesky factorization -  $5 \times 5$  tile matrix.

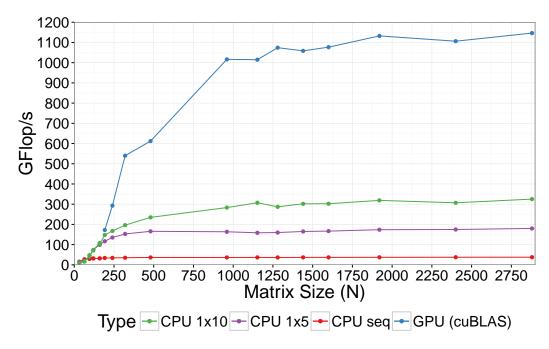

The Cholesky factorization task graph has  $\frac{N(N+1)(N+2)}{6}$  vertices and  $\frac{(N-1)N(N+1)}{2}$  edges for  $N \times N$  tile matrix, more precisely, it has N POTRF,  $\frac{N(N-1)}{2}$  TRSM,  $\frac{N(N-1)}{2}$  SYRK and  $\frac{N(N-1)(N-2)}{6}$  GEMM tasks. Figure 1.5 depicts performance of tile Cholesky factorization in actual ex-

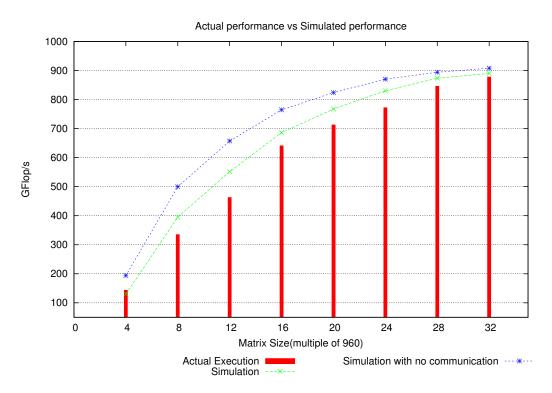

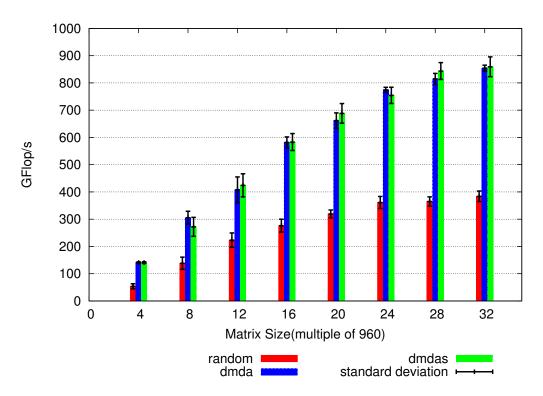

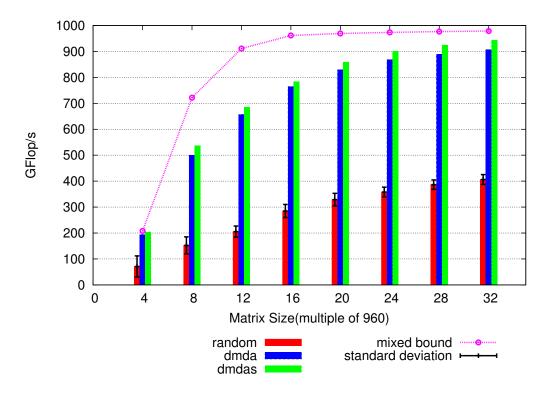

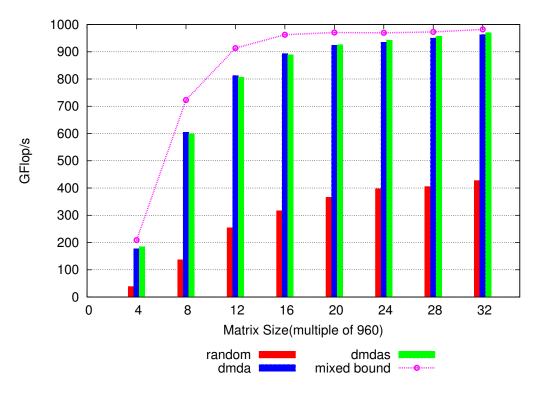

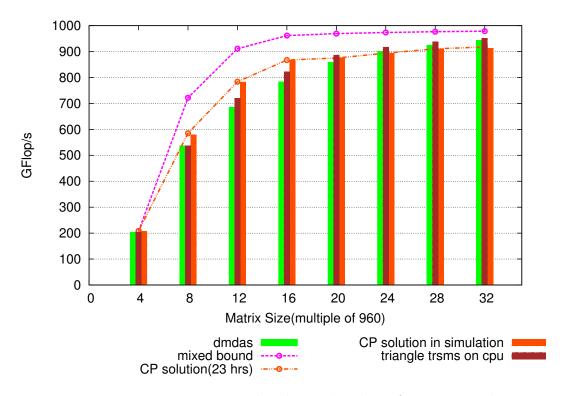

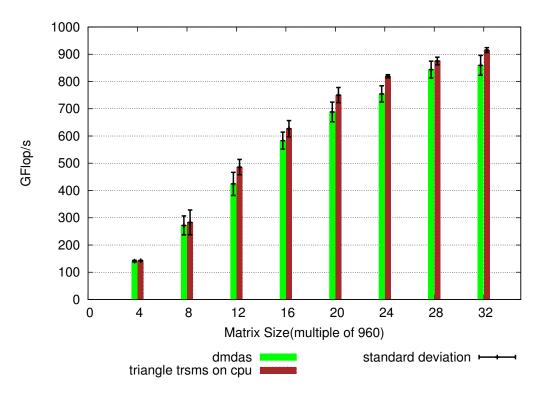

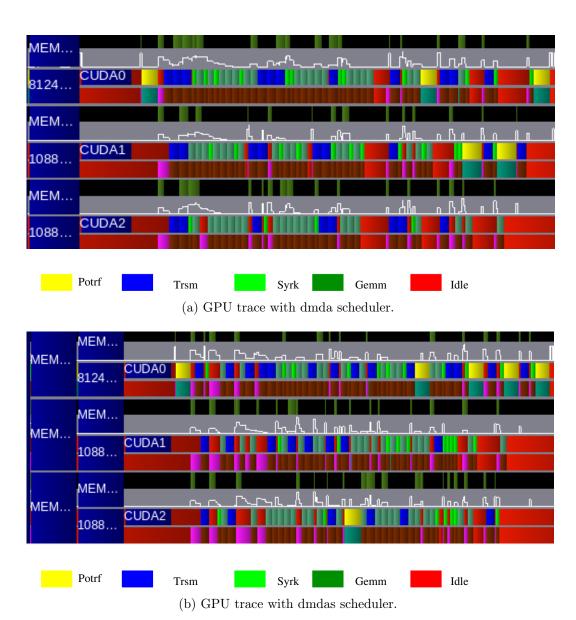

Figure 1.5 depicts performance of tile Cholesky factorization in actual execution and simulation on a heterogeneous node with 9 CPU computing cores of X5650 processor and 3 Nvidia Tesla M2070 GPUs. We use StarPU runtime system for the actual execution and Simgrid version of StarPU for the simulation. In all cases we use HEFT based StarPU scheduler for scheduling of tasks. In "Simulation with no communication" mode, we modify the platform files of the machine and set all transfer associated costs to zero. Figure 1.5 shows that the simulated performance is slightly better than the actual execution performance, which can be explained with the fact that actual execution suffers from scheduling overhead. Simulated performance in both cases, with and without communication costs, is comparable. Therefore we can say that

Figure 1.5: Impact of communication on performance of Cholesky factorization.

| kernel            | PORTF        | TRSM | SYRK | GEMM |

|-------------------|--------------|------|------|------|

| CPU time/GPU time | $\simeq 2.3$ | ≃11  | ≃26  | ≃29  |

Table 1.1: GPU acceleration ratio over CPU core for Cholesky tasks (size 960).

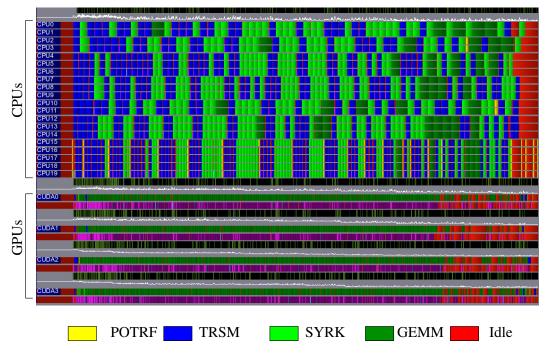

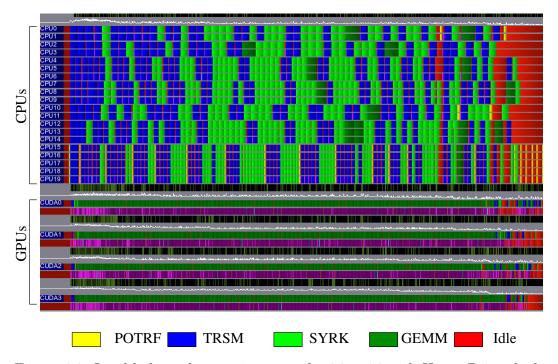

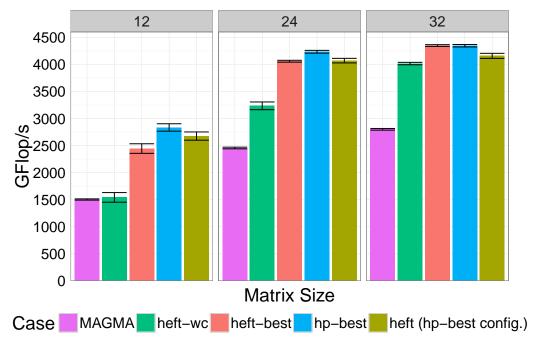

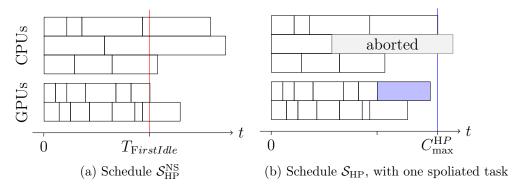

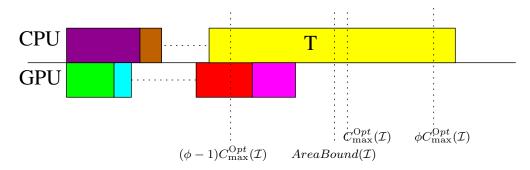

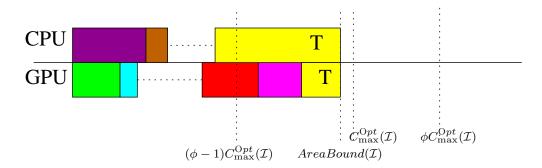

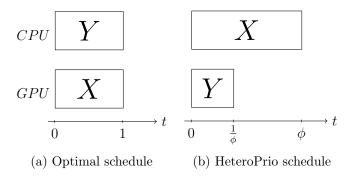

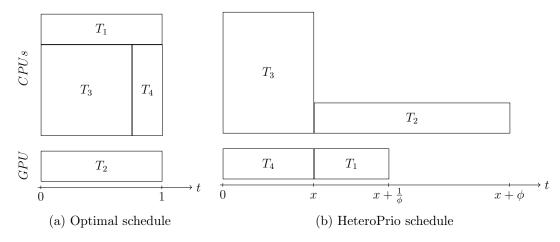

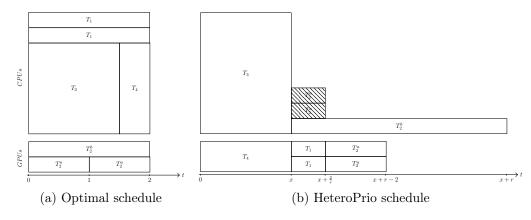

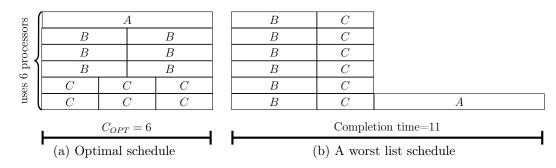

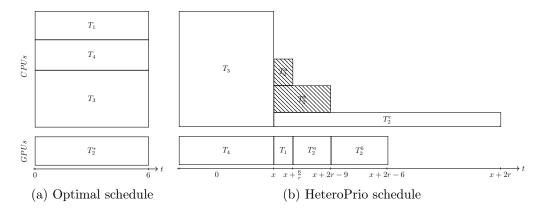

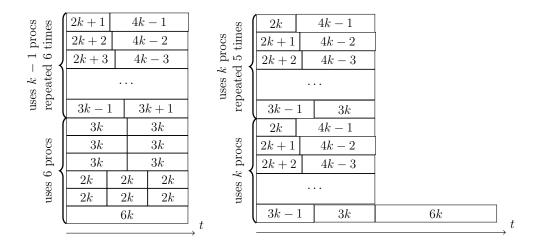

communication costs do not impact the performance of Cholesky much and Cholesky is a compute intensive application.