# Contributions à la traduction binaire dynamique: support du parallélisme d'instructions et génération de traducteurs optimisés

Luc Michel

#### ▶ To cite this version:

Luc Michel. Contributions à la traduction binaire dynamique : support du parallélisme d'instructions et génération de traducteurs optimisés. Informatique et langage [cs.CL]. Université de Grenoble, 2014. Français. NNT : 2014GRENM101 . tel-01547198

# HAL Id: tel-01547198 https://theses.hal.science/tel-01547198v1

Submitted on 26 Jun 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique Arrêté ministériel : 7 août 2006

Présentée par

#### Luc Michel

Thèse dirigée par Frédéric Pétrot et encadrée par Nicolas Fournel

préparée au sein du Laboratoire TIMA et de l'École Doctorale Mathématiques, Sciences et Techniques de l'Ingénieur, Informatique

# Contributions à la traduction binaire dynamique : support du parallélisme d'instructions et génération de traducteurs optimisés

Thèse soutenue publiquement le **18 décembre 2014**, devant le jury composé de :

#### **Mme Florence Maraninchi**

Professeur des Universités, Grenoble INP, Présidente

#### M. Bernard Goossens

Professeur des Universités, Université de Perpignan, Rapporteur

#### M. Erven Rohou

Directeur de Recherche, Inria Rennes, Rapporteur

#### M. Paul Feautrier

Professeur des Universités, ENS Lyon, Examinateur

#### M. Benoît Dupont de Dinechin

Docteur, Kalray, İnvité

#### M. Frédéric Pétrot

Professeur des Universités, Grenoble INP, Directeur de thèse

#### M. Nicolas Fournel

Maître de Conférences, Université Joseph Fourier, Encadrant

# Remerciements

Je tiens en premier lieu à remercier les membres de mon jury de thèse. Merci à Bernard Goossens et Erven Rohou pour leurs retours riches, intéressants et constructifs sur mon travail. Merci aussi à Paul Feautrier et Benoît Dupont de Dinechin d'avoir examiner ma thèse. Ayant utilisé intensivement certains outils de Benoît, j'ai beaucoup apprécié ses retours lors de la soutenance. Finalement, merci à Florence Maraninchi, qui avant d'être présidente de mon jury, a été mon enseignante d'algorithmique à l'Ensimag, et m'a soutenu lorsque les mathématiques s'en prenaient à moi, petit admis sur titre que j'étais. Elle a alors prêté une oreille attentive et m'a fait découvrir le monde de la recherche.

Un immense merci à mon directeur, Frédéric Pétrot. Malgré ses nombreuses responsabilités et son emploi du temps chargé, il a su rester disponible et à l'écoute à la moindre occasion. C'est une chance que j'ai eu de pouvoir discuter avec lui à tout moment de mon avancement, des problèmes sur lesquels je bloquais, des solutions que j'apportais au fur et à mesure de ces trois années. Merci à Nicolas Fournel qui m'a encadré durant ma thèse. Je me souviens de ces *coding night fever*, que l'on pourrait traduire par *soirées code – pizza* pendant lesquelles on s'acharnait à peaufiner notre prototype pour la soumission d'un article.

Merci à tous les gens que j'ai rencontré dans l'équipe SLS du laboratoire TIMA et ailleurs. Olivier et les nombreuses discutions que nous avons eu. Sa grande expérience de l'enseignement m'a beaucoup aidé alors que je débutais dans ce domaine. Merci aussi à Matthieu qui a accepté d'endurer le rôle de "tuteur d'enseignement" et qui lui aussi m'a apporté sa précieuse expertise dans ce domaine. Merci à tous les doctorants, post-doc ou ingénieurs pour ces bons moments en votre compagnie : Adrien, Damien, Clément, Hamayun, Marius, Alban, Ashraf, Marcos et j'en oublie. Merci à Tadeusz qui m'a fait découvrir le monde de la recherche quand j'étais à l'IUT, et qui m'a aiguillé dans mon parcours universitaire.

Enfin, merci à ma famille. Si j'en suis arrivé là c'est grâce à mes parents et surtout à ma maman qui m'a tiré contre vents et marrés vers le haut alors que son fils préférait de loin jouer à taper des commandes MS-DOS sur un vieux 486 plutôt que de faire ses devoirs (en CE1 déja!). Par ailleurs, sa relecture attentive et courageuse de ce manuscrit, qualifié alors d'ésotérique, m'a permis d'éliminer nombre d'erreurs.

Finalement, une pensée toute particulière pour ma femme Sofia, qui a rédigé et soutenu dans les mêmes périodes que moi. On m'a souvent averti que, la rédaction n'étant pas une période particulièrement joyeuse, l'ambiance à la maison risquait d'être morose. Il me suffit aujourd'hui de regarder en arrière pour m'apercevoir que non seulement ces dires étaient faux, mais qu'en plus je garde un excellent souvenir de cette période pendant laquelle chacun à pris soin de l'autre. Cette épreuve est un signe de plus qui me montre que j'ai rencontré la femme de ma vie.

# Table des matières

| 1 | Intr | oduction                                                                      | 1  |

|---|------|-------------------------------------------------------------------------------|----|

| 2 | Prol | plématique                                                                    | 5  |

|   | 2.1  | Les familles de jeux d'instructions                                           | 5  |

|   |      | 2.1.1 Processeurs généralistes, RISC et CISC                                  | 6  |

|   |      | 2.1.2 Jeux d'instructions SIMD                                                | 6  |

|   |      | 2.1.3 Processeurs VLIW et DSP                                                 | 7  |

|   | 2.2  | Les techniques de simulation d'ISA                                            | 10 |

|   |      | 2.2.1 Détail des différentes familles                                         | 11 |

|   |      | 2.2.2 La traduction binaire dynamique                                         | 12 |

|   | 2.3  | Générer automatiquement un simulateur                                         | 14 |

|   |      | 2.3.1 Les ADL                                                                 | 14 |

|   |      | 2.3.2 Génération de simulateurs à l'aide d'ADL                                | 14 |

|   | 2.4  | Conclusion                                                                    | 15 |

| 3 | Ć.   | de l'art                                                                      | 17 |

| 3 | 3.1  | La traduction binaire dynamique                                               | 17 |

|   | 5.1  | 3.1.1 Dans les machines virtuelles                                            | 17 |

|   |      | 3.1.2 Pour le support à la migration de code sur de nouvelles architectures . | 18 |

|   |      | 3.1.3 Pour l'optimisation binaire                                             | 18 |

|   |      | 3.1.4 Pour l'instrumentation et l'aide à la mise au point                     | 18 |

|   |      | 3.1.5 Pour la simulation rapide                                               | 18 |

|   | 3.2  | Simulation rapide d'architectures VLIW                                        | 19 |

|   | 0.2  | 3.2.1 Par traduction statique                                                 | 19 |

|   |      | 3.2.2 Par simulation compilée                                                 | 20 |

|   | 3.3  | Génération de simulateurs rapides à partir d'un ADL                           | 21 |

|   | 0.0  | 3.3.1 Générer des simulateurs basés sur la simulation compilée                | 22 |

|   |      | 3.3.2 UQBT : traduction binaire statique reciblable                           | 24 |

|   |      | 3.3.3 UQDBT et Walkabout : vers la traduction binaire dynamique               | 25 |

|   |      | 3.3.4 Bintrans: DBT optimisée pour le couple cible/hôte                       | 26 |

|   | 3.4  | Conclusion                                                                    | 29 |

|   |      |                                                                               |    |

| 4 |      | ulation d'architectures VLIW à l'aide de la traduction binaire dynamique      | 31 |

|   | 4.1  | Un algorithme pour simuler une architecture VLIW                              | 33 |

|   |      | 4.1.1 Exemple                                                                 | 33 |

|   |      | 4.1.2 Conclusion sur l'algorithme                                             | 35 |

|   | 4.2  | Intégration de l'algorithme dans un traducteur binaire dynamique              | 36 |

|   |      | 4.2.1 Adaptation de l'algorithme                                              | 36 |

### TABLE DES MATIÈRES

|   |     | 4.2.2   | L'allocation des répliques en pratique                                    | 37 |

|---|-----|---------|---------------------------------------------------------------------------|----|

|   |     | 4.2.3   | Les problèmes introduits par la granularité du TB                         |    |

|   |     | 4.2.4   | Gestion des instructions prédiquées                                       |    |

|   |     | 4.2.5   | Conclusion sur l'intégration dans un traducteur DBT                       |    |

|   | 4.3 | Expéri  | imentations                                                               |    |

|   |     | 4.3.1   | Protocole expérimental                                                    | 51 |

|   |     | 4.3.2   | Statistiques sur le code généré                                           | 51 |

|   |     | 4.3.3   | Mesure du temps d'exécution de la simulation                              |    |

|   | 4.4 | Concl   | usion                                                                     |    |

| 5 | Gér | ération | n de simulateurs basés sur la traduction binaire dynamique                | 57 |

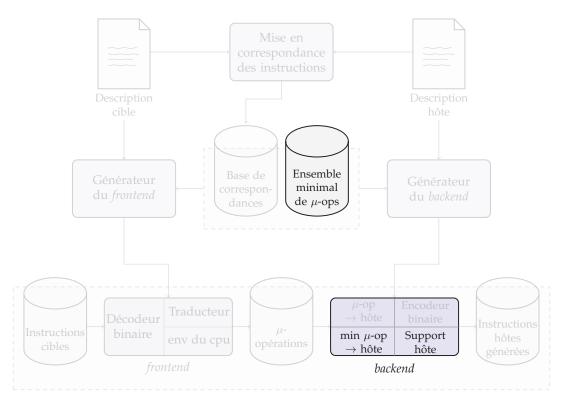

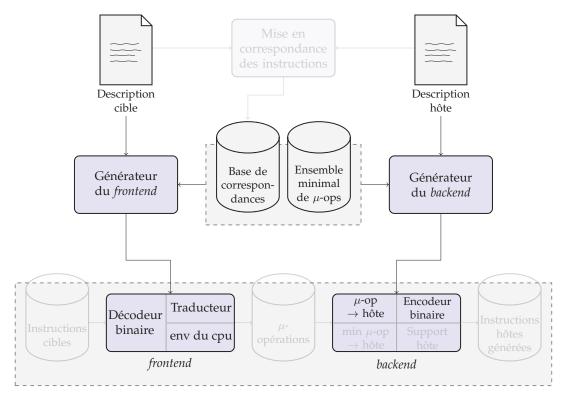

|   | 5.1 | Préser  | ntation du flot de génération                                             | 57 |

|   | 5.2 | MDS:    | un ADL comportemental                                                     | 58 |

|   |     | 5.2.1   | Les espaces mémoires et les registres                                     |    |

|   |     | 5.2.2   | Les instructions et leurs formats                                         |    |

|   |     | 5.2.3   | Les comportements d'instructions                                          | 60 |

|   |     | 5.2.4   | Conclusion sur MDS                                                        | 61 |

|   | 5.3 | Analy   | se et transformation des comportements d'instructions                     | 61 |

|   |     | 5.3.1   | Vérification syntaxiques et premières transformations                     | 62 |

|   |     | 5.3.2   | Expansion des nœuds d'accès aux opérandes                                 | 62 |

|   |     | 5.3.3   | Décoration des nœuds avec leurs types                                     | 64 |

|   |     | 5.3.4   | Uniformisation de l'arbre                                                 |    |

|   | 5.4 | Extrac  | ction des signatures des instructions                                     | 66 |

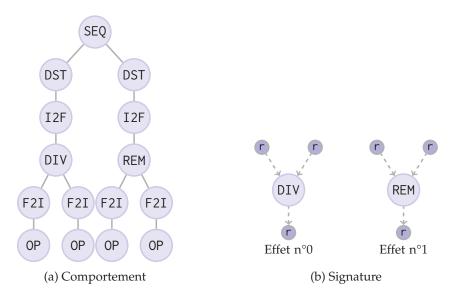

|   |     | 5.4.1   | Exemple de l'instruction div avec plusieurs effets                        | 67 |

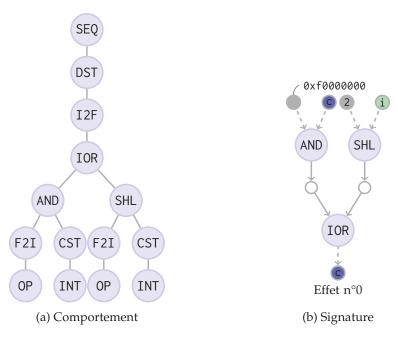

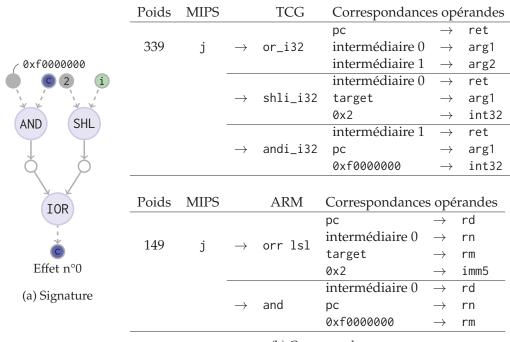

|   |     | 5.4.2   | Exemple de l'instruction j avec registre de contrôle                      | 68 |

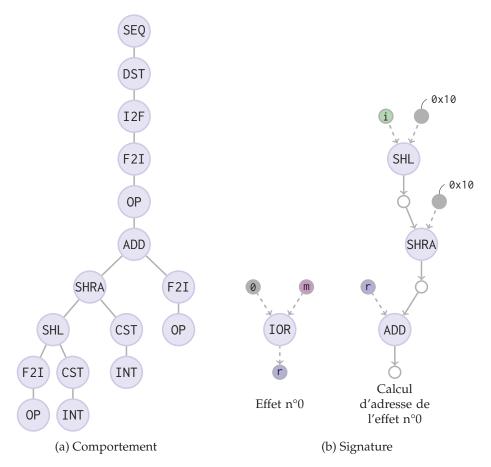

|   |     | 5.4.3   | Exemple de l'instruction lw avec calcul d'adresse                         |    |

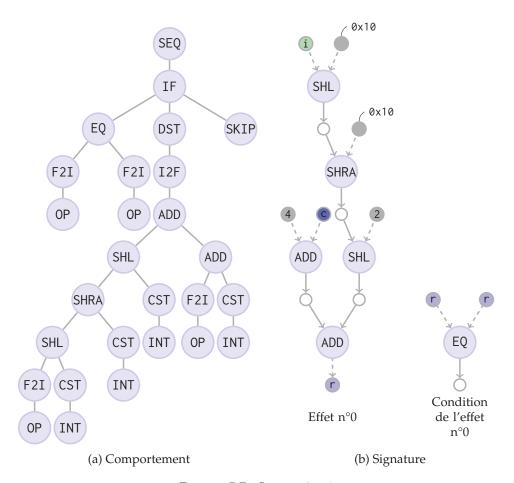

|   |     | 5.4.4   | Exemple de l'instruction beq avec condition                               | 69 |

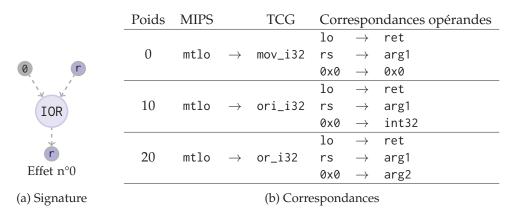

|   | 5.5 | Mise e  | en correspondance des instructions                                        |    |

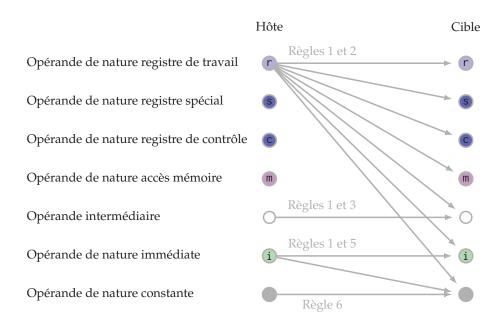

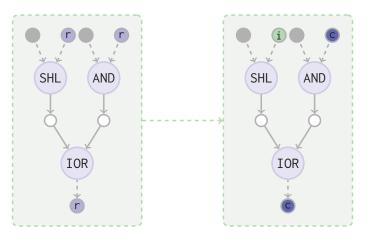

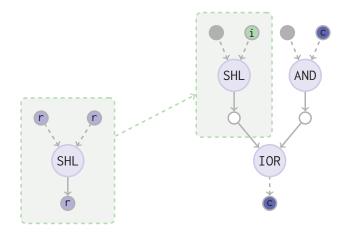

|   |     | 5.5.1   | Correspondances entre nœuds                                               | 71 |

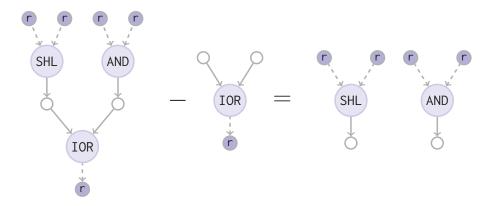

|   |     | 5.5.2   | La correspondance entre effets                                            | 74 |

|   |     | 5.5.3   | La correspondance entre signatures                                        | 76 |

|   |     | 5.5.4   | Algorithme de mise en correspondance                                      |    |

|   |     | 5.5.5   | Version non-exhaustive de l'algorithme                                    | 83 |

|   |     | 5.5.6   | Conclusion de la mise en correspondance                                   | 83 |

|   | 5.6 | Génér   | ation du simulateur                                                       | 83 |

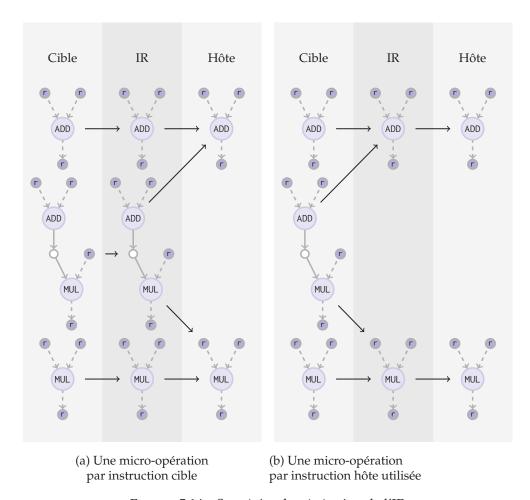

|   |     | 5.6.1   | Le <i>runtime</i> minimal                                                 | 84 |

|   |     | 5.6.2   | Génération de l'IR spécialisée                                            | 86 |

|   |     | 5.6.3   | Génération du frontend et du backend                                      | 86 |

|   |     | 5.6.4   | Conclusion                                                                | 88 |

|   | 5.7 | Expéri  | imentation sur les correspondances                                        | 88 |

|   |     | 5.7.1   | Valeurs attribuées aux constantes d'évaluations pour les expérimentations | 89 |

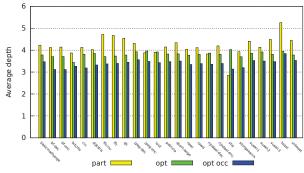

|   |     | 5.7.2   | Comportement de l'algorithme de mise en correspondance                    |    |

|   |     | 5.7.3   | Limitations des transformations et de l'algorithme                        |    |

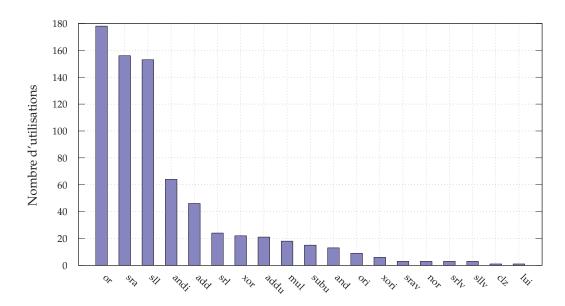

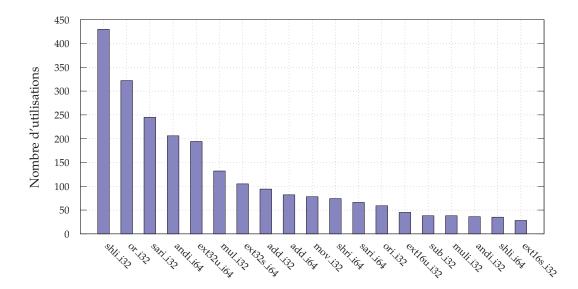

|   |     | 5.7.4   | Statistiques sur les correspondances                                      |    |

|   |     | 5.7.5   | Conclusion                                                                |    |

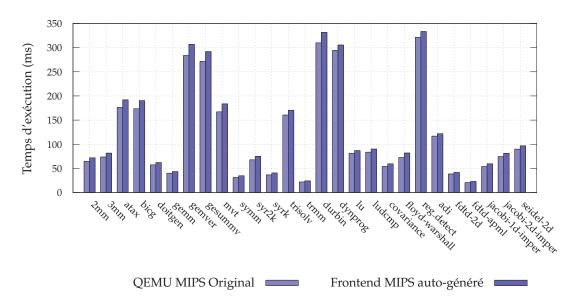

|   | 5.8 | Expéri  | imentation sur la génération d'un frontend pour QEMU                      |    |

|   | 5.9 | Concl   |                                                                           | 98 |

### TABLE DES MATIÈRES

| 6  | Conclusion                                                                             | 101 |

|----|----------------------------------------------------------------------------------------|-----|

| A  | Preuve de correction de l'algorithme de simulation VLIW  A.1 Définitions préliminaires | 103 |

| В  | Résultat d'expérimentations du simulateur VLIW sur la suite Polybench                  | 107 |

| C  | Génération automatique de décodeurs d'instructions                                     | 109 |

| Pu | iblications                                                                            | 119 |

# **Chapitre 1**

# Introduction

A micro-électronique, omniprésente dans notre vie de tous les jours, est au fondement même de la société numérique et connectée d'aujourd'hui. Les progrès de ces trente dernières années ont permis de toujours plus miniaturiser les objets électroniques de notre quotidien, si bien qu'ils tiennent aujourd'hui dans notre poche. La densité d'intégration est telle que les concepteurs parviennent à placer, au sein d'une même puce, de nombreuses unités de calculs, de la mémoire et une foule de périphériques, formant ainsi un système complet. On parle alors de *Système sur la puce* ou *System on Chip (SoC)*.

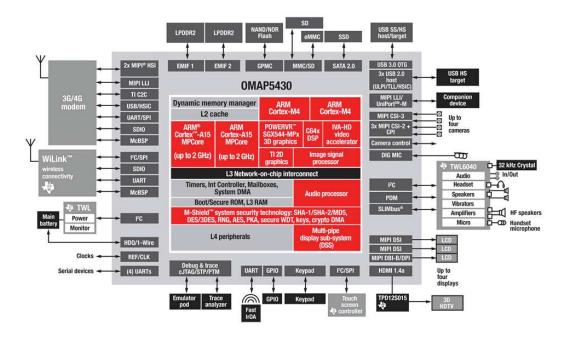

Le nombre d'unités de calculs dans ces systèmes ne cesse de croître. Parmi ces unités, on trouve en général un ou plusieurs processeurs à usage général, et bien souvent des processeurs spécialisés comme des DSP, dédiés à des traitements précis. Un bon exemple d'un tel SoC est l'OMAP5 de Texas Instruments présenté par la figure 1.1. Ce dernier embarque un processeur double cœur à usage général ARM Cortex-A15, deux cœurs Cortex-M4, un DSP de la famille C64x, ainsi que de nombreuses unités dédiées à diverses applications.

Bien que la conception de telles puces soit complexe et demande du temps, elle n'est pas la seule étape dans la réalisation d'un système complet. Le développement du logiciel qui va s'exécuter sur ces puces représente une part sans cesse croissante du temps de conception global. Les fabricants doivent faire face à un marché extrêmement dynamique et en constante évolution, pour lequel le temps d'insertion et le cycle de vie d'un produit est de plus en plus réduit. Une de leurs problématiques est donc de développer le logiciel le plus rapidement possible et au plus tôt. Cependant, le matériel, nécessaire pour développer et mettre au point le logiciel, n'est pas disponible lors la première phase de la conception.

#### Le prototypage virtuel

Afin de pallier ce problème, une technique largement acceptée consiste à réaliser un prototype virtuel du matériel. Un tel prototype reproduit le comportement du matériel dans un environnement simulé s'exécutant sur une machine quelconque. Il permet le développement en amont du logiciel qui peut alors être testé, exécuté et mis au point sur la plateforme virtuelle. Il permet aussi d'aider à la conception du matériel, notamment pour évaluer les besoins et explorer l'espace de conception.

Cependant, réaliser un prototype virtuel est une tâche longue et complexe. La complexité et les cœurs de calculs toujours plus nombreux rendent leur simulation lente et les simulateurs difficiles à concevoir. Un prototype virtuel doit malgré tout conserver une vitesse de simulation acceptable pour être utilisable. Si un système d'exploitation, mettant quelques secondes à démarrer sur le vrai matériel, prend plusieurs heures en simulation,

FIGURE 1.1 - Architecture de l'OMAP 5430 de Texas Instruments

la pertinence du prototype virtuel devient discutable. Une technique de simulation rapide de jeux d'instructions appelée la traduction binaire dynamique (*Dynamic Binary Translation* (*DBT*)) vient répondre à une partie de ce problème. Elle s'inscrit dans la lignée des techniques de simulation de jeux d'instructions en proposant de traduire les instructions du processeur simulé (la cible) en instructions de la machine exécutant la simulation (l'hôte). Elle est dynamique car la traduction est réalisée au fur et à mesure de la simulation, par opposition à une traduction statique faite une fois pour toute. De nombreux avantages découlent de cette technique, et notamment une vitesse de simulation des jeux d'instructions élevée, tout en gardant un haut niveau de flexibilité. Elle reste cependant difficile à développer et à mettre au point ce qui freine son adoption par rapport aux simulateurs interpréteurs classiques.

#### Objectifs de la thèse

Les travaux de cette thèse s'articulent autour de la DBT et explorent deux axes d'améliorations de cette technique. Le premier s'intéresse à la possibilité d'utiliser la technique de la DBT pour simuler un jeu d'instructions d'une architecture de type Very Long Instruction Word (VLIW) sur une architecture hôte scalaire classique. Les architectures VLIW sont souvent utilisées dans les processeurs spécialisés de type DSP comme le C64x dans l'exemple précédent. Elles ont la particularité d'exprimer explicitement le parallélisme entre instructions.

Le second se concentre sur l'aspect automatisation en proposant de générer un traducteur binaire dynamique en partant de la description architecturale du processeur à simuler et de la machine hôte dans l'optique de réduire la difficulté de conception d'un simulateur basé sur la DBT, et d'étudier les possibilités d'optimisations du traducteur lorsque l'on dispose de ces deux descriptions. Ces travaux sont donc une contribution au besoin de simuler

toujours plus vite et plus largement que ce qui est fait aujourd'hui.

#### Plan de la thèse

Le chapitre 2 présente de manière plus précise le contexte dans lequel s'inscrivent les travaux de cette thèse, et formule les questions auxquelles nous essaierons de répondre au fil du manuscrit.

Le chapitre 3 dresse un état de l'art de la simulation de processeurs et plus particulièrement de la technique de DBT. Il s'intéresse aux techniques de simulation rapide d'architectures à parallélisme explicite et à la génération de simulateurs.

Les chapitres 4 et 5 présentent les deux contributions de cette thèse. La première est une solution pour simuler un processeur de type VLIW à l'aide de la DBT, sur un processeur hôte scalaire. La seconde propose de générer un traducteur optimisé pour un couple cible – hôte à partir de leur description architecturale.

Finalement, le chapitre 6 conclut ce manuscrit en faisant un bilan des contributions et en proposant une ouverture vers des perspectives possibles et de futurs travaux.

# **Chapitre 2**

# Problématique

Dans ce chapitre, nous présentons les différents problèmes liés à la simulation rapide de processeurs. La pression sur le marché des ASIC, ainsi que la complexité toujours croissante des SoC dans lesquels les processeurs sont intégrés, poussent les constructeurs à opter pour des solutions de simulation. Cependant, les coûts de développement des simulateurs sont élevés, et conserver une vitesse de simulation correcte dans des environnements multiprocesseurs hétérogènes est un vrai défi.

Afin de comprendre les besoins en simulation, nous passerons en revue les différentes familles de jeux d'instructions (Instruction Set Architecture (ISA)), puis nous verrons les techniques classiques pour les simuler. Enfin, nous étudierons les solutions de description d' ISA haut-niveau pour nous intéresser au problème de la génération automatique de simulation de processeurs.

## 2.1 Les familles de jeux d'instructions

Il existe plusieurs grandes familles de jeux d'instructions que nous allons passer rapidement en revue.

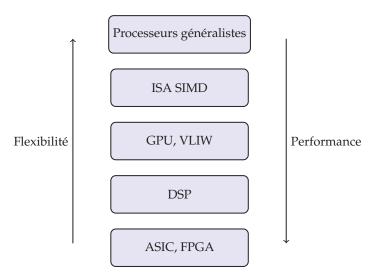

FIGURE 2.1 – Les grandes familles d'ISA

#### 2.1.1 Processeurs généralistes, RISC et CISC

Ces processeurs que nous trouvons généralement dans nos machines de bureau et téléphones portables, sont pourvus d'un jeu d'instructions généraliste, capable d'exécuter de manière efficace le code des programmes courants (système d'exploitation, applications interactives, etc...) Ils sont généralement classés en deux catégories :

**Les processeurs RISC** pour Reduced Instruction Set Computer, ils sont composés d'instructions simples et peu nombreuses. Les instructions sont en général de type *registre-registre*, c'est à dire que les opérandes et la destination des instructions sont des registres. On y trouve aussi des instructions de chargement et écriture mémoire pour accéder à celle-ci. Les architectures *MIPS*, *ARM*, *PowerPC* et *SPARC* font partie de cette famille.

Les processeurs CISC pour Complex Instruction Set Computer, sont composés d'instructions pouvant réaliser des opérations complexes comme un chargement mémoire et une addition au sein de la même instruction. Les instructions acceptent donc une plus grande diversité d'opérandes (accès mémoire avec différents modes d'adressage, valeur immédiate...). On rencontre dans cette famille l'architecture *Intel IA-32* ou *x86*, équipant la majorité de nos ordinateurs personnels, ainsi que son évolution 64bit, l'architecture *Intel 64* ou *x86-64*.

#### 2.1.2 Jeux d'instructions SIMD

Les jeux d'instructions Single Instruction Multiple Data (SIMD) viennent en général en supplément de l'ISA classique de nos processeurs. Ils ont la particularité de réaliser en parallèle la même opérations sur des vecteurs de données. Ces vecteurs sont souvent des registres de 64bits ou plus, l'instruction décidant de la granularité des données dans ces registres. Prenons par exemple l'instruction présentée au listing 2.1.

Listing 2.1 – Exemple d'instruction SIMD MMX/SSE

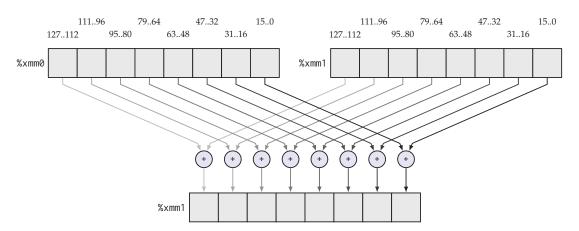

FIGURE 2.2 – Fonctionnement de l'instruction paddw

Elle fait partie du jeu d'instruction SIMD *MMX/SSE* du *x86*. La figure 2.2 décrit son fonctionnement. Les registres %xmm0 et %xmm1 sont des registres de 128bits. L'instruction considère ces registres comme étant des vecteurs de 8 éléments de 16bits. Elle additionne un à un les éléments de ces vecteurs et place le résultat dans %xmm1. Elle réalise donc 8 additions en parallèle.

Ces jeux d'instructions sont souvent utilisés dans les applications multimédia comme le traitement de flux audio ou vidéo, qui réalisent la même opération sur un grand nombre de données. C'est aussi le principe de base de fonctionnement des GPU.

#### 2.1.3 Processeurs VLIW et DSP

Les architectures VLIW, contrairement au processeurs superscalaire classique, ont la particularité de laisser le contrôle de leurs pipelines au compilateur ou au programmeur. Elles exposent pleinement les ressources dont elles disposent, et donnent la possibilité d'exprimer l'ordonnancement des instruction au niveau de l'ISA.

On retrouve souvent ces architectures dans les processeurs de type Digital Signal Processor (DSP), qui sont des processeurs spécialisés dédiés à des tâches de calculs intensifs, comme le traitement d'un signal venant d'un capteur.

#### L'exemple du TMS320C64x

Pour mieux décrire le fonctionnement d'un tel processeur, nous prendrons en exemple dans ce document l'architecture TMS320C64x[Tex10a] de Texas Instrument, que nous abrégerons c64x dans la suite de ce document. Cette architecture est utilisée dans certains de leurs DSP. Elle est particulièrement adaptée à notre problème puisqu'elle possède les caractéristiques qui rendent difficile la simulation de VLIW. Ce sont ces caractéristiques que nous allons détailler.

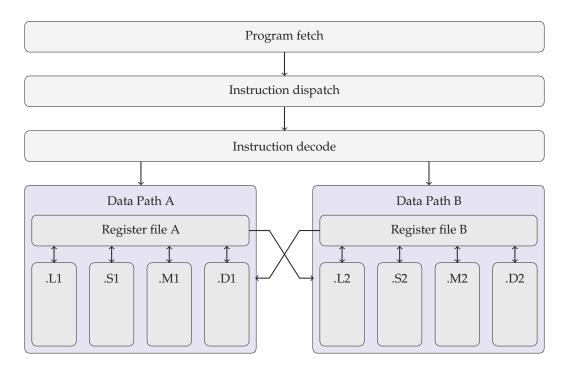

Le c64x est une architecture VLIW disposant de deux fois 4 unités de traitement (ou unités fonctionnelles). On parle alors de processeurs VLIW 8 voies. Ces 8 unités sont découpées en deux chemins de données A et B, disposant chacun de leur banc de registres. Elles sont dénotées .L1, .S1, .M1 et .D1 pour le chemin de données A, et .L2, .S2, .M2 et .D2 pour le chemin de données B. La figure 2.3 illustre le pipeline du c64x.

Chacune de ces unités peut exécuter un sous-ensemble du jeu d'instructions du c64x. Par exemple, les unités .D1 et .D2 sont les seules ayant des instructions de chargement et écriture mémoire alors que les unités .M1 et .M2 prennent en charge les instructions de multiplication du processeur.

Les chemins de données A et B peuvent communiquer par l'intermédiaire d'un *cross* path dans chaque direction. Ainsi, une instruction s'exécutant dans A peut lire un registre du banc B et vice versa.

Une autre particularité importante du pipeline du c64x est l'absence des mécanismes classiques de résolution de dépendance de données inter-instructions. C'est un problème classique qui apparaît dans les processeurs pipelinés. Si une instruction a besoin d'une donnée se trouvant encore dans le pipeline au moment de son exécution, soit la donnée va être récupérée au moyen d'un court-circuit (*bypass*), soit le processeur va insérer une bulle dans le pipeline pour faire patienter l'instruction le nombre de cycles nécessaires. Ces mécanismes permettent de rendre transparent au programmeur ou au compilateur les aléas introduits par les architectures pipelinées.

Certaines architectures font le choix de ne pas résoudre tous les aléas. C'est le cas de l'architecture MIPS et de son *delay slot* pour les instructions de saut. Dans le cas de l'archi-

FIGURE 2.3 – Représentation du pipeline du c64x

tecture c64x, aucun de ces mécanismes n'est mis en place. C'est pourquoi le programmeur ou le compilateur doit connaître la latence de chaque instruction. Afin d'illustrer ce point, prenons l'exemple du code assembleur c64x donné au listing 2.2

```

a0, a3, a2

add

.L1

; a2 <- a0 + a3

|| mpy32

.M1

a0, a1, a2

; a2 <- a0 * a1

2

b0, b1, b2

|| and

.S2

; b2 <- b0 & b1

3

[a0] add

.L1

a1, a2, a3

; a3 <- a1 + a2

.L2X b0, a2, b4

|| or

; b4 <- b0 | a2

7

nop

8

nop

10

11

sub

.L1 a2, a4, a5

; a5 <- a2 - a4

12

```

Listing 2.2 – Exemple de code assembleur c64x

Le symbole | | dénote l'exécution en parallèle d'une instruction avec celle qui la précède. Dans cet exemple, les instructions des lignes 1, 2 et 3 sont exécutées en parallèle. Il en va de même pour les instructions des lignes 5 et 6. Un groupe d'instructions exécutées en parallèle est parfois appelé *bundle*, ou *paquet d'exécution (execute packet)*. Pour le premier bundle de l'exemple, les unités .L1, .M1 et .S2 sont utilisées. On pourrait donc encore compléter ce

bundle avec 5 autres instructions parallèles, pour un total de huit, qui correspond au nombre total d'unités. À la ligne 6, la présence du X à la fin de l'unité indique que le cross path doit être utilisé pour lire un registre du banc voisin (ici le registre a2). Finalement, à la ligne 5, la présence de [a0] signifie que l'instruction est prédiquée, elle ne sera exécutée que si le contenu du registre a0 n'est pas nul.

#### **Instructions et latences**

Intéressons-nous maintenant à la latence de chaque instruction. Dans cet exemple, toutes les instructions sauf une ont une latence de 0. Leur résultat est donc directement disponible pour le bundle suivant. La seule instruction n'ayant pas une latence nulle est l'instruction mpy32 à la ligne 2. Cette instruction de multiplication a une latence de 3, son résultat n'est donc pas immédiatement visible. Par exemple, l'instruction add à la ligne 5 lit le registre a2. Or, à ce moment, le registre ne contient pas encore le résultat de la multiplication entre a0 et a1. C'est l'ancienne valeur de a2 qui est lue. Le résultat est effectivement disponible à la ligne 12 pour l'instruction sub, les 4 cycles nécessaires à l'instruction s'étant écoulés.

Le même principe s'applique pour les instructions de branchement. Prenons l'exemple donné au listing 2.3.

```

b

.S1 some_label

; instruction de branchement

.L1 a0, a1, a2

1

add

2

; 2

nop

3

; 3

nop

4

nop

5

nop

5

6

. L 2

1, b2, b1

; branchement effectué

sub

```

Listing 2.3 – Un branchement en c64x

L'instruction de branchement à la ligne 1 a une latence de 5. Dans notre exemple, les instructions de la ligne 2 à 6 sont exécutées avant que le branchement ne soit effectivement pris. En revanche, l'instruction de la ligne 7 n'est pas exécutée.

#### Optimiser l'utilisation du pipeline

En exécution classique, il n'existe pas de cas où le processeur est susceptible de vider son pipeline. Une instruction qui est rentrée ressortira forcément au bout d'un nombre connu de cycles. Les compilateurs se servent de cette hypothèse pour optimiser au mieux l'utilisation du pipeline. L'exemple du listing 2.4 illustre ce dernier point.

Ce listing présente un programme qui réalise deux branchements consécutifs (ligne 1 et 2), patiente trois cycles, puis fait une multiplication (ligne 4). Le branchement ayant une latence de 5 cycles, et la multiplication une latence de 3 cycles, les instructions des ligne 2 et 4 sont toujours dans le pipeline lorsque le premier branchement est effectivement pris. Lorsque le saut à 1b11 est réalisé, il reste un cycle avant que le deuxième ne survienne. L'instruction add de la ligne 10 est donc exécutée. En revanche au cycle suivant, le processeur branche à 1b12. Le sub de la ligne 11 n'est donc pas exécuté. Finalement, il faut encore patienter trois cycles pour obtenir le résultat de la multiplication de la ligne 4 dans a2.

```

.S1 lbl1

b

b

.S1 lbl2

2

; 1

; 2,3,4

nop

3

; 5

mpy32

.M1 a0, a1, a2

add

.L1 a0, a2, a2

; branchement vers lbl1

[...]

; (add non exécuté)

lbl1:

add

.L1 a2, a2, a3

.L1 a2, a1, a3

sub

; branchement vers 1b12

10

[...]

; (sub non exécuté)

11

12

1b12:

13

nop

14

nop

15

and

.L1 a2, a0, a0

; Résultat du mpy32 disponible

16

dans a2

17

```

Listing 2.4 – Gestion du pipeline et des latences

#### Pour résumer

Nous venons de voir quelques caractéristiques de l'architecture c64x :

- La gestion du pipeline est laissée au compilateur ou au programmeur. Le processeur expose ses ressources et permet d'exprimer le parallélisme entre instructions directement dans l'ISA.

- Chaque instruction a sa propre latence. Le pipeline n'étant pas équipé de mécanisme de résolution d'aléas, le programmeur et le compilateur doivent en tenir compte, et peuvent se servir de ces latences pour optimiser au mieux le flux d'instructions dans le pipeline.

- Le processeur dispose de deux chemins de données, possédant chacun leur banc de registres et unités fonctionnelles. Des crosspath sont disponibles pour échanger la valeur d'un registre d'un chemin de données à l'autre.

- Les instructions peuvent être prédiquées. Elles ne seront exécutées que si la condition est remplie.

- Le pipeline n'est jamais vidé en exécution normale.

L'exemple du c64x est intéressent car il présente les principales caractéristiques des architectures VLIW qui rendent la simulation non triviale.

# 2.2 Les techniques de simulation d'ISA

Comme nous l'avons évoqué précédemment, la simulation connaît un essor important dans le monde de la conception des systèmes sur puce. Elle accélère grandement le développement, tant matériel que logiciel des systèmes. Le débogage sur plateforme de simulation est bien plus aisé que sur un vrai système, du fait d'une meilleure observabilité du système simulé. Elle permet aussi d'obtenir des estimations de performance avant même que

le système réel ne soit conçu, ce qui permet de l'adapter en cas de besoin.

Il existe de nombreuses techniques de simulation d'ISA. Les simulateurs d'ISA sont appelés Instruction Set Simulator (ISS). Le choix de la technique dépend principalement des besoins de l'utilisateur. D'une manière générale, plus la simulation sera proche du modèle réel, plus elle sera précise mais lente. À l'opposé, plus elle s'élèvera en niveau d'abstraction, plus elle sera rapide mais imprécise[PGH<sup>+</sup>11].

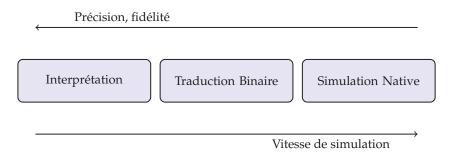

La figure 2.4 présente trois familles de techniques, de la plus précise à la plus rapide. Nous détaillerons par la suite ces trois familles, puis nous nous intéresserons à une technique en particulier, la *traduction binaire dynamique*.

FIGURE 2.4 – Classification des techniques de simulation d'ISA

#### 2.2.1 Détail des différentes familles

#### L'interprétation

Les techniques d'interprétation d'ISA simulent les unes après les autres les instructions du programme. Pour chaque instruction, ce processus passe par une étape de récupération, de décodage, et de simulation de l'instruction. L'algorithme 1 décrit ce processus.

#### **Algorithme 1** Simulation d'ISA par interprétation

```

1tant que simulation running faire2opcode \leftarrow mem(regs[pc])\triangleright Récupération3dec \leftarrow decode(opcode)\triangleright Décodage4selon dec.op faire5...6cas ADD\triangleright Simulation de l'instruction ADD7regs[dec.dst] \leftarrow regs[dec.src1] + regs[dec.src2]8...9fin selon10fin tant que

```

La première étape récupère, dans la mémoire de la machine simulée, le code opération (*opcode*) à l'adresse courante du compteur ordinal. Cet opcode est ensuite décodé pour déterminer le type d'instruction dont il s'agit, les opérandes d'entrées, de sorties, etc. Finalement, le simulateur reproduit le comportement de l'instruction de manière procédurale.

Cette technique reste proche du comportement réel d'un pipeline de processeur. Les simulateurs l'exploitant sont souvent *instruction accurate* voire *cycle accurate*. En revanche,

cette méthode reste très lente puisque pour chaque instruction, le processus présenté par l'algorithme 1 est exécuté.

Une optimisation consiste à stocker le résultat du décodage dans un cache afin de le réutiliser directement les fois suivantes si l'instruction est à nouveau exécutée (par exemple dans le cas d'une boucle). Si le simulateur modélise le cache d'instructions, une bonne technique consiste à stocker dans celui-ci, non pas les opcodes, mais la forme décodée des instructions[PGH+11].

#### La traduction binaire

La traduction binaire, dans le cas de la simulation d'ISA, permet de garder un niveau de précision raisonnable, tout en gagnant très significativement en vitesse de simulation. Le principe de base consiste à traduire le code de la machine simulée (la *cible*) en un code exécutable par la machine exécutant la simulation (*l'hôte*).

Il existe deux techniques qui se distinguent l'une de l'autre :

La traduction binaire statique (Static Binary Translation (SBT)), elle consiste à traduire une fois pour toutes le programme que l'on souhaite simuler. Cette technique est complexe et pose des problèmes de fond lors de la traduction. Il est par exemple délicat de traduire un branchement dont la cible n'est pas connue lors de la traduction, car l'espace d'adressage n'est pas le même entre les deux versions. De plus, il n'est pas possible de supporter simplement le code automodifiant.

La traduction binaire dynamique (DBT), alterne entre les phases de traductions et d'exécutions du code généré. Le fonctionnement de cette technique est décrit en détail dans la section 2.2.2

#### La simulation native

La simulation native est la technique qui s'éloigne le plus de la machine que l'on souhaite simuler. Le gain en vitesse est très important, au prix d'une simulation imprécise. En effet, cette technique ne permet pas d'extraire une quelconque information de performances de la machine simulée (cycles, consommation, . . .). On parle alors de simulation fonctionnelle.

Le principe est de compiler le code que l'on souhaite simuler directement pour la machine hôte. Afin de faire l'interface entre le logiciel et le matériel, il est nécessaire d'implémenter une couche d'abstraction matérielle (Hardware Abstraction Layer (HAL)). Une implémentation de cette HAL spécifique au simulateur permet au programme simulé de s'exécuter de manière transparente sur la machine hôte. La HAL quant à elle communique avec des couches de simulation de plus bas niveau, comme par exemple une implémentation SystemC des périphériques de la plateforme simulée.

Une limite de cette méthode est la nécessité d'avoir les sources du programme que l'on souhaite simuler.

#### 2.2.2 La traduction binaire dynamique

Nous allons maintenant détailler la technique de la DBT puisque c'est elle qui va nous intéresser dans le cadre de ces travaux.

Le principe général de cette technique de simulation d'ISA est de traduire le code de l'architecture cible que l'on cherche à simuler en un code de même comportement, exécutable par la machine hôte. Le code cible est découpé en blocs appelés *blocs de traduction* (Translation block (TB)). Un TB commence à la valeur courante du compteur ordinal de la machine simulée, et se termine sur une instruction de branchement.

Il existe plusieurs manières de réaliser le cœur de traduction du simulateur. La manière la plus simple consiste à traduire directement le code cible en code hôte. Cependant, beaucoup de traducteurs dynamiques choisissent d'ajouter une étape supplémentaire dans la traduction, en utilisant une *représentation intermédiaire* (Intermediate Representation (IR)). Le code cible est d'abord traduit dans cette représentation intermédiaire, puis le code final est généré à partir de celle-ci. Cette représentation intermédiaire est composée d'instructions simples, parfois appelées micro-opérations, en nombre et expressivité suffisante pour simuler n'importe quelle architecture. Elle a plusieurs avantages par rapport à une traduction directe :

- Elle permet la décorrélation de la cible et de l'hôte, il est par la suite plus aisé d'ajouter une nouvelle cible ou un nouvel hôte au simulateur.

- Elle peut bénéficier d'optimisations génériques lors de la traduction, applicables à n'importe quel couple cible – hôte.

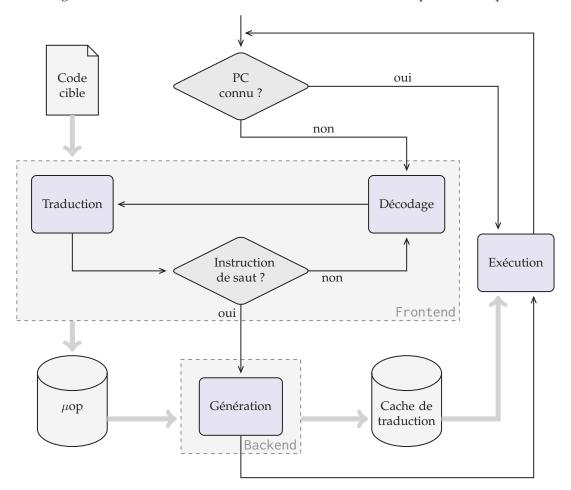

La figure 2.5 illustre le fonctionnement d'un tel simulateur. La première étape consiste

FIGURE 2.5 – Fonctionnement de la simulation par traduction binaire dynamique

à vérifier si la valeur courante du compteur ordinal a déjà été rencontrée. Si oui, on peut

immédiatement exécuter le code généré correspondant. Sinon, le simulateur rentre dans le processus de traduction. Il commence par traduire le code cible en micro-opérations de l'IR à l'aide du *frontend*. Celui-ci remplit le tampon de micro-opérations tant qu'il ne rencontre pas d'instruction de saut, marquant la fin du TB en cours de traduction. Lorsqu'une instruction de saut est rencontrée, le simulateur passe la main au *backend* qui traduit les micro-opérations présentes dans le tampon en code hôte, pour former le *bloc de traduction traduit* (Translated Translation block (TTB)). Ce dernier est placé dans le cache de traduction, et est finalement exécuté pour simuler le code cible. Ce processus est répété pour faire avancer la simulation.

Les TTB étant placés dans le cache de traduction, le simulateur peut les exécuter plusieurs fois sans avoir à les retraduire. Cependant, lorsque ce cache est plein, il faut faire un choix pour y libérer de l'espace, le plus simple consistant à le vider complètement.

Cette technique de la DBT donne de très bons résultats en terme de vitesse de simulation mais reste compliquée à implémenter.

#### 2.3 Générer automatiquement un simulateur

#### 2.3.1 Les ADL

Il existe de nombreux moyens de décrire un système, du niveau le plus bas (niveau transistor) au plus élevé en abstraction (langages de haut niveau), chacun ayant ses avantages et inconvénients.

Les Architecture Description Language (ADL) sont une famille de languages spécialement conçus pour la description d'architectures. Ils sont utilisés comme support à la génération de modèles matériels, de validation, de tests et environnement de développement (compilateurs, simulateurs, débogueurs, . . .).

Ils se découpent suivant deux grandes familles[MD08], les ADL structurels et les ADL comportementaux. Les ADL structurels sont plus adaptés pour le prototypage matériel puisqu'ils capturent la structure, parfois à grain fin, du processeur qui y est décrit. Les ADL comportementaux sont quant à eux orientés prototypage virtuel, compilation, simulation, puisque de plus haut niveau. Ils capturent le comportement du système plutôt que sa structure.

Dans le cadre de la génération automatique de simulateurs en partant d'une description haut-niveau, les ADL comportementaux seront donc plus adaptés. Ils permettent de spécifier l'ISA du processeur et de décrire le comportement de chaque instruction d'un point de vue comportemental, contrairement à un ADL de type structurel, duquel il est plus difficile d'extraire ces informations de manière systématique.

#### 2.3.2 Génération de simulateurs à l'aide d'ADL

La génération de simulateurs à partir d'une description dans un ADL est une technique déjà bien établie[PHM00, BNH+04, RBMD03, CVER99, UC00, CVERL02, Pro01]. Le générateur exploite la sémantique de la description pour produire un simulateur plus ou moins précis suivant les possibilités offertes par l'ADL et les besoins de l'utilisateur. Les simulateurs peuvent fonctionner à base d'interprétation ou de traduction binaire, le premier cas étant le plus courant.

Un point important de cette génération est la manière dont est décrit le comportement des instructions. Dans de nombreux cas, une description de type impérative est utilisée, ce qui rend difficile l'analyse de la sémantique du comportement des instructions par le générateur. Celui-ci doit se contenter de recopier ce comportement dans le simulateur généré, sans pouvoir faire d'optimisations dessus.

#### 2.4 Conclusion

Nous venons d'aborder différents points autour de la simulation rapide de processeurs. Nous avons énoncé les spécificités de quelques familles d'architecture comme les jeux d'instructions SIMD et VLIW, puis nous avons présenté différentes techniques de simulation.

La traduction binaire dynamique est une technique intéressante puisqu'elle permet d'obtenir de bonnes performance en terme de vitesse de simulation, tout en gardant une précision acceptable.

Finalement, nous nous sommes intéressés à la génération automatique de simulateurs à partir d'une description dans un ADL de l'architecture cible.

Voici les questions auxquelles nous tenterons de répondre :

- Comment utiliser la traduction binaire dynamique pour simuler des jeux d'instructions VLIW sur des processeurs scalaires?

- Comment générer des simulateurs d'ISA basés sur des techniques de DBT?

- Comment optimiser le processus de DBT généré pour le couple cible/hôte donné?

# **Chapitre 3**

# État de l'art

Dans ce chapitre, nous présentons un panorama de la simulation rapide de processeurs, principalement axé sur la traduction binaire dynamique. Cette technique consiste à traduire le code binaire exécutable que l'on souhaite simuler en un code binaire exécutable par la machine qui exécute la simulation, et ce de manière dynamique. Par ailleurs, elle est utilisée dans divers domaines, notamment à des fins de support et migration vers de nouvelles architectures, d'optimisation binaire, d'instrumentation et d'implémentation de machines virtuelles.

Nous explorerons ensuite les techniques de simulation d'architectures de type VLIW, en recherchant en particulier s'il existe des techniques qui permettent de simuler de manière efficace ce genre de processeurs autrement que par interprétation tout en étant fonctionnellement correct.

Finalement, nous étudierons les possibilités de génération automatique de simulateurs rapides en partant d'une description de type ADL des architectures cible et hôte.

# 3.1 La traduction binaire dynamique

La traduction binaire dynamique (Dynamic Binary Translation ou DBT) est une technique consistant à traduire le code binaire d'un jeu d'instruction vers un autre.

#### 3.1.1 Dans les machines virtuelles

L'une des premières utilisations de la DBT se fit dans le cadre de l'optimisation des machines virtuelles. Deutsch et Schiffman[DS84] décrivent l'implémentation d'une machine virtuelle optimisée pour le langage Smalltalk-80. Parmi les optimisations décrites, la plus importante selon les auteurs est la traduction du *bytecode* Smalltalk en code binaire pour la machine hôte. Ils s'inspirent de [Rau78] qui semble être le premier à introduire la notion de traduction dynamique. Il décrit ce processus comme étant un bon compromis entre l'interprétation d'un langage intermédiaire peu gourmand en mémoire qui sera forcement coûteuse, et un code binaire directement sur un processeur.

Le monde des machines virtuelles continue d'exploiter cette technique, notamment pour le langage Java[LYBB13, YMP+99, BCF+99]. Elle est alors appelée Just-In-Time Compilation (JIT). Ces machines virtuelles possèdent plusieurs niveaux d'optimisation du code exécuté. Par défaut, le bytecode est interprété sans plus d'optimisation. Si une partie du code est exécutée suffisamment souvent, il est alors traduit en code binaire pour la machine hôte.

C'est le premier niveau d'optimisation. On parle alors de *hot spot* ou *hot path*. Si une partie de code dépasse un deuxième seuil en nombre d'exécutions, il est retraduit en un code de meilleur qualité. C'est le deuxième niveau d'optimisation.

#### 3.1.2 Pour le support à la migration de code sur de nouvelles architectures

Un autre domaine utilisant la DBT est le support à la migration vers de nouvelles architectures. Il s'agit d'exécuter des programmes compilés pour d'anciennes architectures sur de nouveaux processeurs non compatibles d'un point de vue ISA[EA97, CHH+98, ZT00]. La traduction est faite de manière transparente pour l'utilisateur. Par exemple, DAISY[EA97] traduit des binaires PowerPC vers une architecture VLIW en essayant de tirer partie du parallélisme au niveau instruction (Instruction Level Parallelism (ILP)). FX!32[CHH+98] permet l'exécution de programmes x86 sur des architectures Alpha au dessus de Windows NT. Enfin, Aries[ZT00] traduit les programmes HP-PA vers l'architecture IA-64.

#### 3.1.3 Pour l'optimisation binaire

Outre le support vers de nouvelles architectures, la DBT est utilisée pour optimiser à la volée un programme déjà compilé. On parle parfois de recompilation à la volée. Le but est souvent de tirer partie d'une nouvelle version de l'architecture, contenant par exemple de nouvelles instructions plus efficaces. Le traducteur peut aussi tirer partie d'informations propres à l'exécution comme la probabilité pour un branchement conditionnel d'être pris, pour optimiser le flux binaire, informations que le compilateur ne possède pas lors de la compilation. Dynamo[BDB00] optimise le flux binaire au dessus du système HP-UX, arrivant à une accélération entre 10% et 20%.

#### 3.1.4 Pour l'instrumentation et l'aide à la mise au point

La DBT peut aussi être utilisée à des fins d'instrumentation des programmes exécutés. Valgrind[NS07] est un *framework* ainsi qu'un ensemble de modules permettant la mise au point de programmes. Le plus connu est *memcheck*, le module permettant le débogage des erreurs mémoires. Il remplace à la volée les accès mémoires afin de les tracer et de tester leur validité. Dans la même idée, Pin[LCM+05] fournit au programmeur un *framework* de traduction binaire pour réaliser simplement les instrumentations de son choix dans un programme. Le programmeur peut alors créer des outils s'appuyant sur Pin pour effectuer dynamiquement divers traitements sur les instructions d'un programme. Un bon exemple d'une utilisation de Pin est PerPI[GLPP12] qui calcule l'ILP d'un programme en étudiant les dépendances de chaque instruction exécutée.

#### 3.1.5 Pour la simulation rapide

Finalement, on retrouve la DBT dans le domaine de la simulation rapide de processeurs. La première utilisation semble être Mimic[May87] qui simule l'architecture System/370 sur l'IBM PC RT à l'aide de la DBT. L'auteur introduit la notion de bloc de traduction (Translation block), qu'il nomme *code block*. Il distingue trois générations de simulateurs, la première étant la simulation par interprétation comme décrite au chapitre 2.2.1. La deuxième génération est la variante de l'interprétation consistant à stocker le résultat du décodage dans un cache. Finalement, il introduit la troisième génération comme étant la DBT, bien qu'il ne la

nomme pas ainsi. Les expérimentations fournies montrent le gain en terme de nombre d'instructions hôtes utilisées pour simuler une instruction cible. L'auteur part du constat que la première génération de simulateurs réalise un ratio de l'ordre de 100 instructions hôtes pour une instruction cible. Pour la deuxième génération, ce ratio est de l'ordre de dix pour un. Ses expérimentations montrent qu'il arrive à un ratio de l'ordre de quatre pour un avec Mimic, en ne prenant en compte que le code généré, et pas la phase de traduction.

Embra[WR96] simule un système complet à base de MIPS. Il est basé sur Shade[CK93] et est un bon exemple de simulateur fonctionnel abouti. Il peut simuler un système multiprocesseurs ainsi que les caches de chacun.

Finalement, QEMU[Bel05] s'inscrit dans cette lignée en fournissant un simulateur riche et performant. C'est un logiciel libre s'appuyant sur la DBT pour simuler de nombreux systèmes. À l'heure actuelle, il supporte 16 architectures cibles (architectures qu'il peut simuler) et 7 architectures hôtes (architectures sur lesquelles il peut s'exécuter). Il simule aussi une grande variété de périphériques (cartes réseaux, framebuffers, ...).

Son cœur de traduction repose sur le Tiny Code Generator (TCG). Il est muni d'une représentation intermédiaire (IR) composées de micro-opérations. Ces dernières forment un jeu d'instructions simple, similaire à celui d'un processeur RISC élémentaire. La richesse de cette IR permet ou non d'exploiter des instructions spécialisées sur l'hôte, ce qui a un impact non négligeable sur les performances globales du simulateur, comme montré dans [RWY13, MFP11]. Le TCG utilise des *temporaries* comme valeurs intermédiaires dans l'IR lors de la phase de traduction dans le frontend. Un processus d'allocation de registres les remplace par des registres hôtes pendant la phase de génération dans le backend.

QEMU peut aussi fonctionner en mode *user*, mode dans lequel il ne simule pas un système complet. Il permet d'exécuter des binaires compilés pour un système GNU/Linux pour une architecture différente de la machine courante. Il se contente de traduire le code par DBT, et traduit les appels systèmes pour les transférer à l'hôte.

Finalement, il est le frontend officiel pour le système de virtualisation KVM[KKL+07] du noyau Linux. Dans ce mode, le cœur de traduction binaire n'est pas utilisé.

# 3.2 Simulation rapide d'architectures VLIW

De part leur nature, les architectures VLIW sont compliquées à simuler. Le pipeline du processeur doit être reproduit de manière relativement précise pour respecter les latences explicites de chaque instruction. Par interprétation, la conception du simulateur reste simple, mais son exécution résultante lente.

#### 3.2.1 Par traduction statique

Moreno et al. [MME+97] proposent un ensemble d'outils pour aider au développement sur VLIW. Parmi eux, on trouve un traducteur statique de code assembleur VLIW vers l'architecture PowerPC.

Cette traduction a lieu en deux phases. La première consiste à traduire le code VLIW en une représentation intermédiaire correspondant à un ISA VLIW abstrait appelé ForestaPC. Cette représentation intermédiaire est ensuite traduite en code PowerPC. Le code ainsi produit peut être assemblé normalement pour simuler le programme. Le traducteur possède deux modes de fonctionnement. Un mode *exploration* qui permet d'exécuter rapidement le programme mais se contente de simuler seulement l'ISA, et un mode *évaluation* qui simule aussi le processeur et la mémoire, ce qui permet d'extraire des métriques de performances.

Les auteurs comparent la vitesse d'exécution de chacun des deux modes à la vitesse d'exécution de la version native PowerPC. Pour leurs différents programmes de test, le mode *exploration* est jusqu'à 10 fois plus lent que la version native, alors que le mode *évaluation* est entre 500 et 1500 fois plus lent.

Cette solution apporte des résultats satisfaisants en terme de vitesse de simulation en mode *exploration*, mais comporte les inconvénients de la traduction statique comme la difficulté à supporter les indirections calculées à l'exécution (branchements indirects, tableaux de pointeurs, . . .), le chargement dynamique de code, le code auto-modifiant, etc.

#### 3.2.2 Par simulation compilée

La simulation compilée est une technique proche de la traduction binaire statique (SBT). Plutôt que de traduire le code cible en code hôte, le programme à simuler est traduit en langage de haut niveau comme le C. C'est ensuite le compilateur de la machine hôte qui fait le reste du travail. Le programme résultant a le même comportement que le programme à simuler.

Farfeleder et al.[FKH07] utilisent la simulation compilée pour simuler une architecture VLIW. Le code est traduit à la granularité du bloc de base (*basic block*). Chaque bloc de base est traduit en une fonction C. Celle-ci simule le comportement de chaque instruction du bloc et retourne le numéro du bloc suivant à exécuter. Les adresses des fonctions correspondant à chaque bloc sont placées dans un tableau indexé par le numéro de bloc. Il suffit d'utiliser ce tableau à l'index renvoyé par la fonction précédente pour connaître l'adresse de la fonction suivante. La structure de la boucle principale est présentée au listing 3.1.

bb\_num commence par prendre le numéro du bloc correspondant au point d'entrée du programme. La boucle s'exécute tant que le numéro de bloc est positif ou nul. Le cas où le numéro est négatif correspond à une destination inconnue et est discutée au paragraphe suivant. bb\_num est ensuite utilisé pour indexer le tableau bbs contenant les adresses des fonctions simulant les blocs. La fonction correspondante est appelée, et bb\_num est mis à jour avec le retour de celle-ci.

```

int bb_num = first_bb;

while(bb_num >= 0) {

bb_num = bbs[bb_num]();

}

```

Listing 3.1 – Structure de la boucle principale

#### Reconstruction du control flow graph

Pour connaître l'enchaînement des blocs de base, il faut regarder la destination du saut et la faire correspondre au numéro de bloc de base. Dans certains cas, la destination n'est pas connue statiquement. La correspondance [adresse  $\rightarrow$  numéro de bloc] doit donc être conservée à l'exécution.

Finalement, lorsqu'à l'exécution, la correspondance ne peut pas être établie, cela signifie que les limites de la traduction statique ont été atteintes. Le programme essaie de se diriger vers une zone de code qui n'a pas été traduite statiquement. Cela peut être dû à du code auto-modifiant, à un chargement dynamique ou bien à une zone de code qui n'a pas été

découverte statiquement. Dans ce cas, les auteurs choisissent de passer la main à un interpréteur classique, lent mais à même de simuler les instructions de l'architecture cible.

#### Gestion des latences d'instructions

Pour gérer les latences des différentes instructions du VLIW simulé, les auteurs mettent en place plusieurs mécanismes.

Pour les instructions de saut, ils ajoutent à la fin du bloc de base les instructions présentes dans le *delay slot* du saut. Le bloc de base se termine donc au moment effectif du saut et non lorsque l'instruction de saut est rencontrée.

Un problème survient lorsque le bloc de base se termine alors qu'une instruction est toujours dans le pipeline. La fonction simulant le bloc de base suivant doit terminer l'exécution de cette instruction. Dans le cas où le bloc suivant est connu statiquement, il est possible de le générer de manière à prendre en compte cette instruction. Cependant, un bloc peut être la destination d'autres blocs n'ayant pas d'instruction à terminer. Les auteurs choisissent donc de répliquer le bloc destination, laissant une version générée normalement, et une autre autre prenant en compte l'instruction à terminer dans le prédécesseur concerné.

Lorsque le problème n'est pas soluble statiquement, le programme généré passe la main à l'interpréteur en lui fournissant une structure représentant l'état du pipeline à la fin du bloc. Cette structure permet à l'interpréteur de terminer correctement l'exécution d'éventuelles instructions encore dans le pipeline.

#### Performances et conclusion

Les auteurs rapportent une simulation 1000 à 3000 fois plus rapide grâce à leur implémentation de simulation compilée pour l'architecture xDSP, et ce comparée à un interpréteur classique.

Cependant, il n'y a pas d'indication quant au taux d'utilisation de l'interpréteur intégré dans leur programme généré. Les résultats présentés se basent essentiellement sur des benchmarks de calculs intensifs. La traduction statique montre ses limites dans les cas de chargement dynamique de code, cas omniprésent dans un système d'exploitation par exemple.

# 3.3 Génération de simulateurs rapides à partir d'un ADL

Développer un simulateur rapide est une tâche longue et compliquée, notamment lorsqu'on utilise des techniques avancées comme la DBT. La mise au point des parties spécifiques à l'architecture simulée est souvent délicate, et la réutilisation du code pour de futurs développements est en général très limitée.

Est-il possible d'aider à la conception de ces simulateurs rapides en en générant une partie ou la totalité? Pour un simulateur à base de DBT, peut-on obtenir un simulateur performant en le générant à partir d'une description ADL de la cible? Finalement, peut on prendre en compte l'hôte et sa description ADL lors de la génération pour tirer pleinement partie de son ISA?

#### 3.3.1 Générer des simulateurs basés sur la simulation compilée

La génération d'un simulateur utilisant la technique de simulation compilée semble à première vue envisageable. En effet, le résultat de la traduction statique d'un programme en simulation compilée est une représentation dans un langage de haut niveau comme le C. Pour générer un tel traducteur, il est donc nécessaire d'avoir la description de la machine cible seulement, la partie *backend* étant assurée par le compilateur de la machine hôte.

Pees et al. proposent d'utiliser le langage LISA[ZPM96, PHZM99] pour générer un simulateur utilisant la simulation compilée[PHM00]. L'une de leurs cibles de simulation est le TMS320C62x[Tex10b] (c62x), version plus ancienne du c64x présentée section 2.1.3. La simulation générée pour cette architecture est *cycle accurate*.

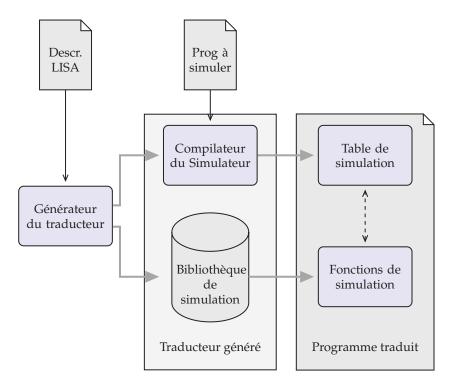

Le flot de traduction est décrit par la figure 3.1. Comme pour la SBT, le programme à simuler est traduit en programme exécutable sur l'hôte, avant la simulation.

FIGURE 3.1 – Flot de génération de simulation compilée

Ici, le traducteur est lui-même généré à partir de la représentation LISA de la machine cible. Il est composé de deux parties :

Le compilateur du simulateur qui s'occupe d'extraire le flot de contrôle du programme à simuler et de créer la *table de simulation* dans le programme final. Celle-ci possède une entrée pour chaque instruction du programme cible. Elle est indexée par l'adresse de l'instruction en question et contient l'adresse des fonctions à appeler pour simuler cette instruction.

La bibliothèque de simulation qui comprend la description comportementale de toutes les instructions de la machine cible. Elle est extraite de la description LISA, et permet de générer les fonctions de simulations référencées par la table de simulation.

La table de simulation contenant une entrée par instruction, la simulation est réalisée à la granularité de l'instruction. La figure 3.2 donne un exemple de table de simulation générée.

| Adresse | fonction de simu | fonction de simu | fonction de simu |  |

|---------|------------------|------------------|------------------|--|

| 0x8000  | fetch()          | decode()         | addi()           |  |

| 0x8004  | fetch()          | decode()         | sw()             |  |

| 0x8008  | fetch()          | decode()         | mult()           |  |

|         |                  |                  |                  |  |

FIGURE 3.2 – Exemple d'une table de simulation

Chaque instruction fait appel à une ou plusieurs fonctions de simulation. On peut voir ici que chaque fonction simule en fait une partie du pipeline du processeur. Ceci est dû à la manière dont sont décrites les instructions en LISA. Leur comportement est découpé par étage de pipeline, ce qui simplifie grandement la génération d'un simulateur *cycle accurate*.

Finalement, la génération de ces fonctions est directe puisque la description comportementale des instructions en LISA est faite dans le langage C++.

Les auteurs rapportent un facteur d'accélération de 36 à 169 par rapport au simulateur interpréteur de Texas Instrument.

Cependant, les simulateurs générés sont impactés par les limitations de la SBT et de la simulation compilée. Ils ne peuvent simuler du code dont des parties sont résolues dynamiquement ni du code auto-modifiant.

Pour pallier ce problème, Braun et al. propose JIT-CCS[BNH+04] qui remet en cause l'aspect statique de la table de simulation. Plutôt que de la générer *hors-ligne* lors de la phase de traduction, celle-ci est générée dynamiquement et placée dans un cache, à la manière de la DBT. Une partie du *compilateur du simulateur* est donc intégrée dans le programme généré, et est appelée dès qu'une instruction n'est pas trouvée dans le cache.

Lors de leurs expérimentations, les auteurs font varier la taille du cache et mesurent le taux de *miss* dans le cache ainsi que les performances en terme de vitesse de simulation, comparé à la version statique. Ils constatent que le cache n'a pas besoin d'être important pour obtenir des performances correctes. Pour un cache d'environ 2Mio, les performances atteignent 95% des performances de la version statique. Cette dernière a besoin de 23Mio pour stocker la table de simulation. Avec un tel cache, le taux de *miss* est de seulement 1%.

Cette approche est intéressante car elle converge vers la DBT. Elle garde en revanche les côtés négatifs de la simulation compilée, tout en en perdant les bienfaits. En effet, dans le cas de JIT-CCS, le compilateur n'est plus en mesure d'optimiser le flot de contrôle du programme généré puisqu'il n'est pas connu à la compilation. Pour chaque instruction, JIT-CCS devra donc faire plusieurs appels de fonctions pour simuler le pipeline. C'est cette granularité de l'instruction qui rend la simulation très lourde. Quitte à intégrer un processus de décodage et de génération dynamique, pourquoi ne pas travailler directement à générer des instructions pour la machine hôte? Cela permet à la fois de se passer des appels de fonctions pour chaque instruction, et offre la possibilité d'obtenir une granularité au niveau bloc de base par exemple, ce qui donne des opportunités d'optimisations bien plus intéressantes.

Reshadi et al. [RBMD03] proposent un *framework* se basant sur un langage de description appelé EXPRESSION[HGG+99] pour décrire l'architecture cible. Ils s'appuient sur la technique de simulation compilée IS-CS[RMD03], similaire à JIT-CCS. Comme ce dernier, le programme final embarque un décodeur d'instructions pour supporter le code dynamique, mais traduit aussi tout le code statique en amont. Cela permet de ne pas générer de surcoût

lors de l'exécution, tout en supportant le cas du code auto-modifiant ou chargé dynamiquement.

#### 3.3.2 UQBT: traduction binaire statique reciblable

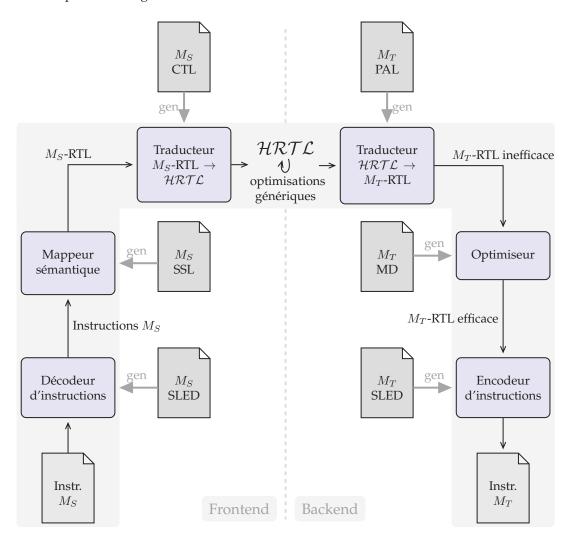

Cifuentes et al. [CVER99] proposent UQBT, un *framework* de SBT reciblable. Son flot de traduction est complexe puisqu'il prend en entrée l'exécutable de la machine cible (notée  $M_S$ ) et produit un exécutable pour la machine hôte (notée  $M_T$ ). Les différentes étapes de ce flot sont présentées figure 3.3.

FIGURE 3.3 – Flot de génération d'UQBT

Pour décrire le comportement des instructions, UQBT utilise plusieurs niveaux de représentations intermédiaires, basés sur le langage RTL. Ce langage décrit une instruction en listant de manière séquentielle ses différents *effets*. Un effet assigne une expression à un emplacement (typiquement un registre ou la mémoire).

Le flot d'UQBT traduit les instructions de la machine  $M_S$  en  $M_S$ -RTL, le langage RTL dédié pour celle-ci. Cette représentation contenant encore les aspects propres à la machine

$M_S$ , une deuxième phase traduit cette représentation en  $\mathcal{HRTL}$ . Ce langage RTL de haut niveau est indépendant de  $M_S$ -RTL et  $M_T$ -RTL. Cette phase élimine les aspects dépendants de  $M_S$  comme des branchements avec *delay slots*. Quelques optimisations génériques sont effectuées sur cette représentation de haut niveau, puis elle est à son tour traduite en  $M_T$ -RTL, représentation adaptée pour la machine  $M_T$ . Un optimiseur propre à  $M_T$  s'occupe d'améliorer le flot de  $M_T$ -RTL, puis il est finalement traduit en instructions de la machine  $M_T$ , et enfin assemblé pour former l'exécutable final.

Chacune des étapes du flot est générée en totalité ou en partie depuis un langage de description dédié :

- Pour générer le décodeur et l'encodeur d'instructions, le flot d'UQBT utilise le langage SLED[RF97] (Specification Language for Encoding and Decoding) qui décrit le format binaire de chaque instruction.

- Pour générer le mappeur sémantique qui traduit les instructions assembleurs de  $M_S$  en  $M_S$ -RTL, c'est le langage SSL[CS98] (Semantic Specification Language) qui est utilisé. Celui-ci associe chaque instruction de  $M_S$  à sa représentation  $M_S$ -RTL.

- Le langage CTL permet de générer le traducteur  $M_S$ -RTL vers  $\mathcal{HRTL}$ . Il traduit les comportements RTL spécifiques de  $M_S$  comme les branchements avec *delay slots* en  $\mathcal{HRTL}$ .

- Le langage PAL décrit l'Application Binary Interface (ABI) de la machine  $M_T$ , permettant par exemple de respecter les conventions d'utilisation des registres et d'appels de fonctions.

En pratique, UQBT ne génère pas les deux dernières étapes de son flot, mais utilise un outil existant (VPO[BD88]) pour optimiser le  $M_T$ -RTL et émettre les instructions assembleurs, et les outils standard de la machine  $M_T$  pour assembler le programme.

#### Performances et conclusion

Pour leurs tests, les auteurs génèrent un traducteur pour les architectures SPARC et x86, dans les 4 combinaisons possibles (SPARC  $\rightarrow$  SPARC, SPARC, SPARC  $\rightarrow$  x86, x86  $\rightarrow$  SPARC et x86  $\rightarrow$  x86). Les traducteurs ayant les mêmes cible et hôte permettent d'évaluer la qualité du code produit comparé au code natif. De ce point de vue, le code est de bonne qualité puisqu'il n'y a pas de dégradation de performance notable entre le code natif et le code traduit. Selon les auteurs, c'est grâce à VPO qui est à même d'optimiser grandement le code traduit.

Aussi prometteur ce *framework* soit-il, il reste néanmoins d'importantes parties qui sont à ce jour écrites à la main, comme VPO. De plus, il souffre des problèmes classiques de la traduction binaire statique et doit embarquer un interpréteur si le flot d'exécution rencontre du code non traduit statiquement. Il n'est donc pas utilisable pour simuler un système complet, mais seulement des fichiers binaires déjà compilés pour un système d'exploitation donné (Solaris dans ce cas). Finalement, le grand nombre de langages de description et d'outils externes utilisés dans UQBT peuvent rendre le ciblage vers de nouvelles architectures fastidieux.

#### 3.3.3 UQDBT et Walkabout : vers la traduction binaire dynamique

UQDBT[UC00, CVERL02] se base sur UQBT en adaptant son flot pour la DBT. Il utilise la granularité du bloc de base lors de la traduction, et stocke le résultat de la traduction dans un cache. Comme dans UQBT, les langages SLED et SSL sont utilisés pour générer certaines parties du flot (les auteurs rapportent que la génération du backend n'est pas implémentée). En revanche, les auteurs ont dû faire plusieurs choix de simplification du flot. En effet, les

contraintes de vitesse de traduction entre la SBT et la DBT ne sont pas les mêmes. Dans le cas de la DBT, les traductions étant faites à la demande au fur et à mesure de l'exécution, elles ne doivent pas prendre un temps trop important sous peine d'impacter les performances. Parmi les principales simplifications du flot, on trouve :

- L'abandon du langage de représentation intermédiaire  $\mathcal{HRTL}$  au profit du I-RTL. Ce dernier est similaire mais n'inclut pas le processus complexe d'inférence des paramètres des fonctions traduites, chose que faisait  $\mathcal{HRTL}$ . À la place, les auteurs ont écrit à la main une partie du flot pour supporter l'ABI de  $M_S$  et  $M_T$ .

- L'abandon de la phase d'optimisation du  $M_T$ -RTL avec VPO. Ce dernier est avant tout destiné à être utilisé dans des compilateurs. Il est donc trop lourd pour être intégré dans un flot de DBT.

Les performances du code généré s'en trouvent ainsi impactées. Pour la traduction de SPARC vers SPARC, les auteurs rapportent un facteur de ralentissement de 2 à 10 fois par rapport à la version native de chaque benchmark. Les benchmarks sont les mêmes que ceux utilisés pour tester UQBT.

Afin d'améliorer les performances du code généré, les auteurs proposent de détecter et optimiser les *hotpaths*[UC01, UC06]. Un *hotpath* est défini comme une suite de blocs de base dépassant un certain seuil en nombre d'exécutions. Les *hotpaths* sont retraduits et placés dans un cache spécial (le *hot cache*). Les optimisations réalisées consistent principalement à améliorer la localité du code pour profiter des effets de cache de l'hôte. Les blocs de base sur un même chemin sont déplacés, fusionnés ou dupliqués pour optimiser le flot d'exécution.

Une autre optimisation améliore la gestion de l'endianness. Si la cible et l'hôte diffèrent de par leur endianness, une conversion est nécessaire à chaque simulation de chargement et d'écriture mémoire. Les auteurs proposent quelques techniques pour supprimer cette conversion lorsqu'elle n'est pas nécessaire (par exemple lors d'une copie mémoire).

Grâce à ces optimisations, les auteurs gagnent environ 15% de performance en temps d'exécution par rapport à la version non-optimisée. On reste donc loin des performances d'UQBT, ce qui montre la différence entre un flot SBT dans lequel des optimisations importantes sont permises, et un flot de DBT ou le temps de traduction doit rester négligeable pour ne pas impacter globalement le temps d'exécution.

Walkabout[CLU02] est un projet similaire dans ces objectifs puisqu'il promet un flot de DBT que l'on peut recibler à l'aide de descriptions de la cible et de l'hôte, avec optimisation des *hot paths*. Cependant la version présentée dans [CLU02] n'inclut pas la génération d'un flot de DBT mais seulement celle d'un interpréteur accompagnée d'un détecteur de *hotspot* et d'un optimiseur binaire du code cible.

#### 3.3.4 Bintrans : DBT optimisée pour le couple cible/hôte

Bintrans[Pro01] propose un générateur de traducteur binaire dynamique en partant à la fois de la description de la machine cible et de la machine hôte. La description d'une machine est faite à l'aide d'un unique langage propre à Bintrans, issu de Lisp. Elle contient la descriptions des registres de la machine, ainsi que la description des formats et du comportement des instructions.

#### Description des comportements d'instruction

Les comportements sont décrits sous forme d'effets, chaque effet modifiant la mémoire ou un registre. Le listing 3.2 donne un exemple de description de l'instruction addu de l'architecture MIPS.

Listing 3.2 – Description de l'instruction MIPS addu dans le langage de Bintrans

D'un point de vue de l'hôte, les effets sont classés en deux catégories, les effets primaires, et les autres. Les effets primaires modifient la mémoire ou un registre à usage général (General Purpose Register (GPR)) contrairement aux autres qui modifient un registre spécial comme le registre d'état sur l'architecture x86.

Les effets peuvent contenir des structures conditionnelles. Prenons l'exemple donné au listing 3.3.

Listing 3.3 – Description de l'instruction Alpha bis

Il s'agit de l'instruction bis de l'architecture Alpha. Elle stocke dans rc le résultat de ra | rb seulement si rc n'est pas le registre 31. De la même manière, elle lit ra et rb seulement si ils ne sont pas le registre 31. Sinon, 0 est lu.

Bintrans supprime les structures conditionnelles des effets en décomposant ces derniers. Il crée autant de sous-effets qu'il y a d'issues possibles aux différentes conditions. Pour l'instruction bis précédente, il crée 5 effets qui ne possèdent plus de structures conditionnelles :

```

(nop) ; rc = 31

(set (reg rc gpr) (logor 0 0)) ; ra = 31, rb = 31

(set (reg rc gpr) (logor (reg ra gpr) 0)) ; rb = 31

(set (reg rc gpr) (logor 0 (reg rb gpr))) ; ra = 31

(set (reg rc gpr) (logor (reg ra gpr) (reg rb gpr))) ; autres cas

```

#### Génération du simulateur

Grâce à la description des machines cible et hôte, Bintrans peut générer le traducteur binaire dynamique propre au couple. Il lit les formats d'instruction de la machine cible pour générer le décodeur d'instructions correspondant.

Pour générer le cœur de traduction binaire, Bintrans réalise des correspondances entre les comportements des instructions pour trouver les instructions hôtes pouvant simuler les

instructions cibles. Pour cela, chaque effet de chaque instruction cible est mis en correspondance avec chaque effet de chaque instruction hôte. Si une instruction hôte possède plusieurs effets, seul l'effet primaire est pris en compte. Si elle a plusieurs effets primaires, alors elle est ignorée dans le processus de mise en correspondance.

Lors de la correspondance, l'auteur distingue trois cas :

Correspondance d'une expression cible avec un registre hôte Si une expression est mise en correspondance avec un registre ou sous-registre de l'hôte, alors la valeur de cette expression doit être placée dans ce registre. Pour cela, un effet temporaire est créé.

Correspondance d'une constante de traduction avec un opérande hôte Certaines valeurs sont connues lors de la phase de traduction. C'est le cas des valeurs immédiates des instructions cibles. Elles peuvent donc être considérées comme des constantes. En revanche, ces valeurs ne sont pas connues au moment de la génération du traducteur. La correspondance doit donc être reportée au moment de la traduction. Cette correspondance consiste à déterminer si la constante de traduction peut être représentée par l'opérande de l'instruction hôte. Par exemple si l'opérande est de taille 8 bits et subit une extension de zéro, alors la constante cible doit être comprise dans l'intervalle  $[0; 2^8 - 1]$ . Sinon, la correspondance est refusée.

Les autres cas Pour tous les cas ne répondant pas au deux critères précédents, la correspondance n'a lieu que si les deux expressions ainsi que leurs opérandes sont les mêmes.

En cas de multiples correspondances pour une même instruction cible, un classement en fonction du nombre d'instructions hôtes nécessaires est effectué. Les correspondances considérées comme les meilleurs sont celles qui génèrent le moins d'instructions hôtes. Les autres ne sont cependant pas éliminées car elle peuvent servir de solution de repli si la correspondance au moment de la traduction échoue.

L'auteur introduit la notion de *transformation*, qui sont des règles génériques qui peuvent être appliquées à des expressions pour les exprimer différemment, en conservant la même sémantique. L'exemple de transformation donné au listing 3.4 indique qu'une négation d'une sous-expression x peut être remplacée par une soustraction de 0 avec x.

```

(define-transformation

(neg (match x))

(- 0 x))

```

Listing 3.4 – Exemple d'une transformation

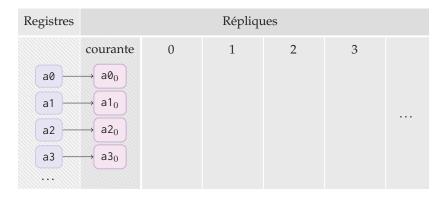

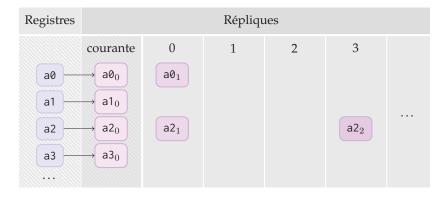

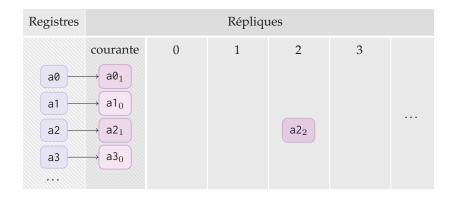

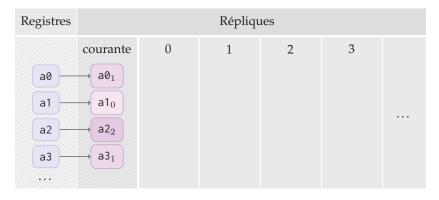

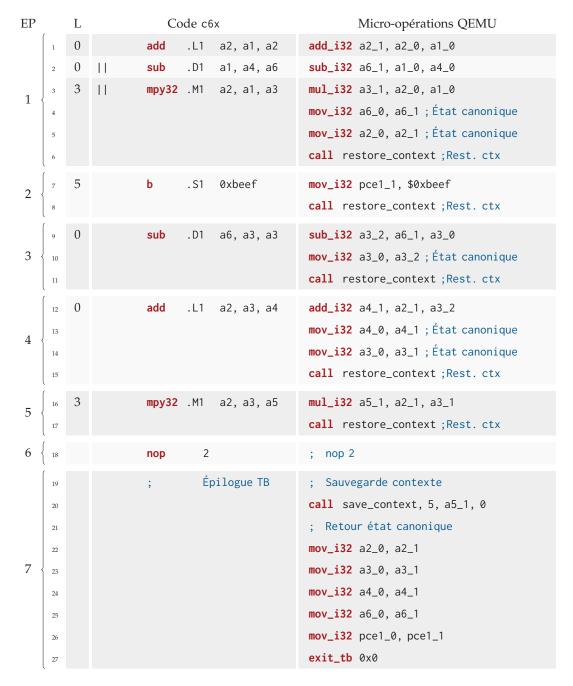

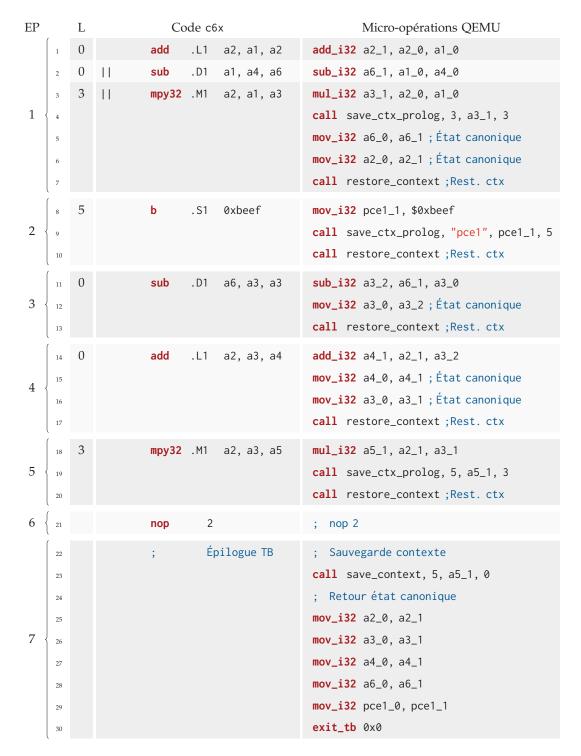

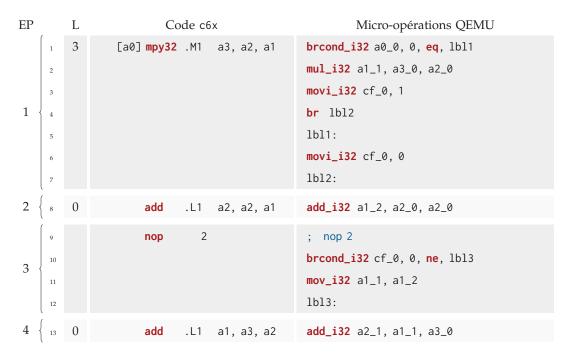

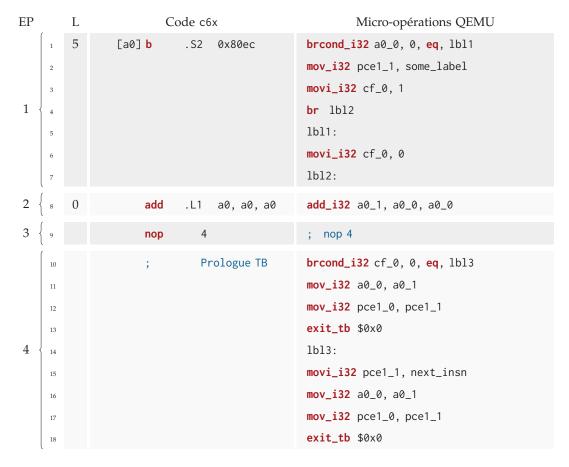

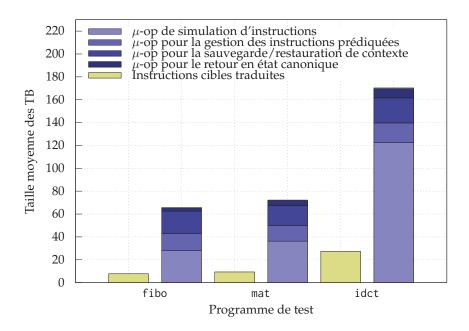

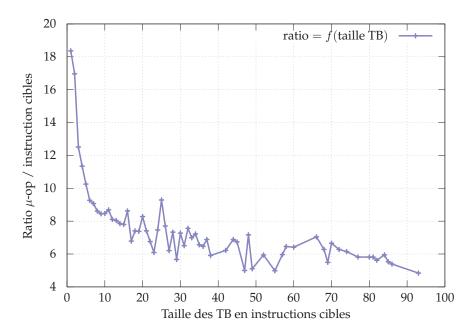

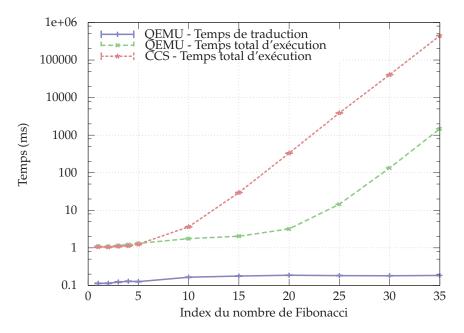

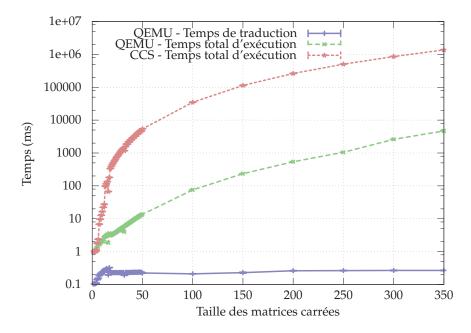

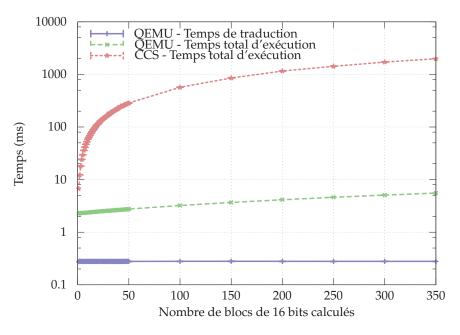

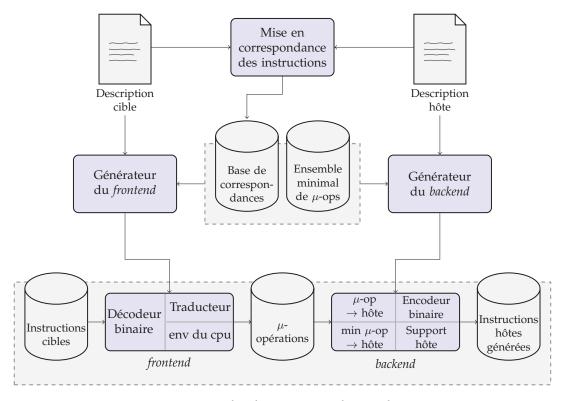

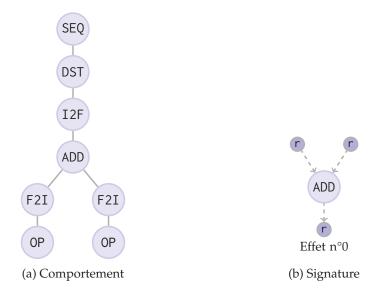

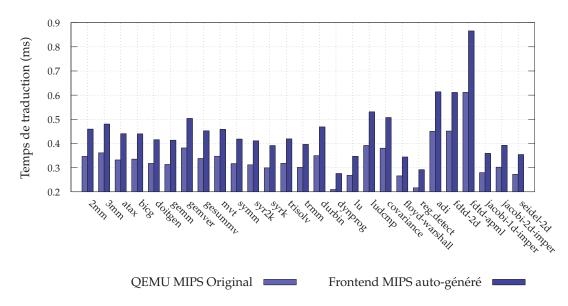

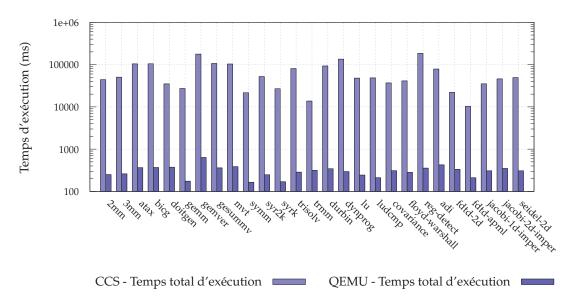

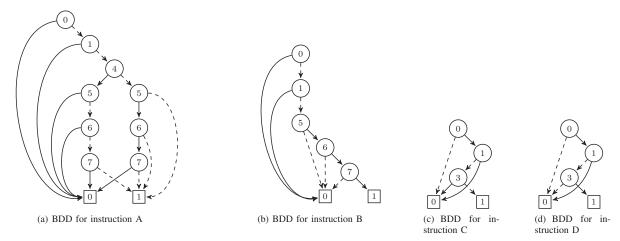

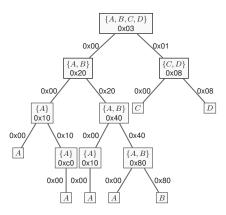

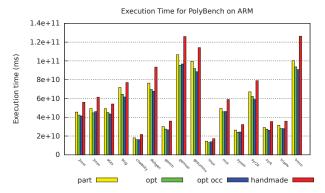

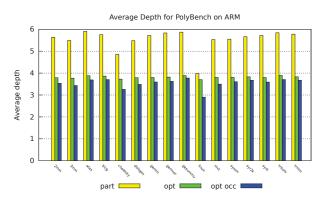

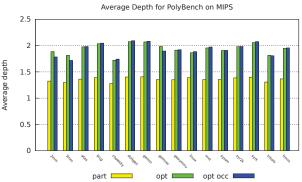

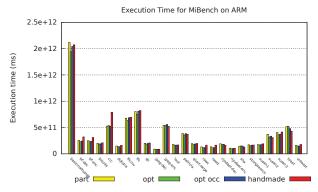

Ces transformations sont utilisées pendant le processus de correspondance pour augmenter les chances de trouver des instructions hôtes candidates pour traduire les instructions cibles.