### On computer-aided design-space exploration for multi-cores

Jean-Francois Kempf

#### ▶ To cite this version:

Jean-Francois Kempf. On computer-aided design-space exploration for multi-cores. Embedded Systems. Université de Grenoble, 2012. English. NNT: 2012GRENM110. tel-01548776

### HAL Id: tel-01548776 https://theses.hal.science/tel-01548776v1

Submitted on 28 Jun 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

### THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministérial : 7 août 2006

Présentée par

### **Jean-François KEMPF**

Thèse dirigée par **Oded MALER** et codirigée par **Marius Bozga**

préparée au sein VERIMAG et de École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# On Computer-Aided Design-Space Exploration for Multi-Cores

Thèse soutenue publiquement le , devant le jury composé de :

Kim G. LARSEN Aalborg University, Rapporteur Bruce KROGH Carnegie Mellon, Rapporteur Boudewijn R. HAVERKORT University of Twente, Examinateur Eugene ASARIN Université Paris Diderot Paris 7, Examinateur Fahim RAHIM Atrenta, Examinateur Oded MALER CNRS, Directeur de thèse Marius BOZGA CNRS, Co-Directeur de thèse

## On Computer-Aided Design-Space Exploration for Multi-Cores

Jean-François KEMPF

August 20, 2012

# Contents

|   | Cont                                          | ents                                              | iii             |  |  |  |  |  |  |  |  |

|---|-----------------------------------------------|---------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| 1 | Introduction 1                                |                                                   |                 |  |  |  |  |  |  |  |  |

| 2 | Mul                                           | Multi-core embedded system                        |                 |  |  |  |  |  |  |  |  |

|   | 2.1                                           | MPSOC Architecture                                | 4               |  |  |  |  |  |  |  |  |

|   |                                               | 2.1.1 Processing Elements                         | 4               |  |  |  |  |  |  |  |  |

|   |                                               | 2.1.2 Memory Organization                         | 5               |  |  |  |  |  |  |  |  |

|   |                                               | 2.1.3 Interconnect                                | 5               |  |  |  |  |  |  |  |  |

|   | 2.2                                           | Design Flow                                       | 6               |  |  |  |  |  |  |  |  |

|   |                                               | 2.2.1 Low Level Modeling                          | 7               |  |  |  |  |  |  |  |  |

|   |                                               | 2.2.2 System-Level Design                         | 10              |  |  |  |  |  |  |  |  |

|   | 2.3                                           | Models of Computation for Embedded Systems Design | 11              |  |  |  |  |  |  |  |  |

|   | 2.4                                           | Performance Evaluation                            | 13              |  |  |  |  |  |  |  |  |

|   | 2.5                                           |                                                   | 15              |  |  |  |  |  |  |  |  |

|   | 2.6                                           | -                                                 | 18              |  |  |  |  |  |  |  |  |

| 3 | Tim                                           | ed automata                                       | 21              |  |  |  |  |  |  |  |  |

| 5 | 3.1                                           |                                                   | <b>21</b><br>22 |  |  |  |  |  |  |  |  |

|   | 3.2                                           |                                                   | 22<br>24        |  |  |  |  |  |  |  |  |

|   | 3.3                                           | ······································            | 24<br>26        |  |  |  |  |  |  |  |  |

|   | 3.4                                           |                                                   | 20<br>28        |  |  |  |  |  |  |  |  |

|   | 5.4                                           |                                                   | 20              |  |  |  |  |  |  |  |  |

| 4 | Dura                                          | Duration Probabilistic Automata: Analysis33       |                 |  |  |  |  |  |  |  |  |

|   | 4.1                                           | Scheduling under Stochastic Uncertainty           | 33              |  |  |  |  |  |  |  |  |

|   | 4.2                                           | Preliminaries                                     | 35              |  |  |  |  |  |  |  |  |

|   | 4.3                                           | Computing Volumes                                 | 39              |  |  |  |  |  |  |  |  |

|   | 4.4                                           | Conflicts and Schedulers                          | 42              |  |  |  |  |  |  |  |  |

|   | 4.5                                           | Implementation and Experimental Results           | 45              |  |  |  |  |  |  |  |  |

|   | 4.6                                           | Conclusions                                       | 50              |  |  |  |  |  |  |  |  |

| 5 | Duration Probabilistic Automata: Synthesis 53 |                                                   |                 |  |  |  |  |  |  |  |  |

| · | 5.1                                           |                                                   | 53              |  |  |  |  |  |  |  |  |

|   | 5.2                                           |                                                   | 55              |  |  |  |  |  |  |  |  |

|   | 5.3                                           |                                                   | 55<br>56        |  |  |  |  |  |  |  |  |

|   | 5.4                                           |                                                   | 50<br>58        |  |  |  |  |  |  |  |  |

|   | 5.4<br>5.5                                    | 1 1                                               | 50<br>60        |  |  |  |  |  |  |  |  |

|   | 5.5<br>5.6                                    | 1 1                                               | 60<br>61        |  |  |  |  |  |  |  |  |

|   |                                               | 1                                                 |                 |  |  |  |  |  |  |  |  |

|   | 5.7                                           | 1                                                 | 64<br>66        |  |  |  |  |  |  |  |  |

|   | 5.8                                           | Concluding Remarks                                | 66              |  |  |  |  |  |  |  |  |

| 6 | Mod  | leling en | nbedded systems with timed automata 6               | 59 |

|---|------|-----------|-----------------------------------------------------|----|

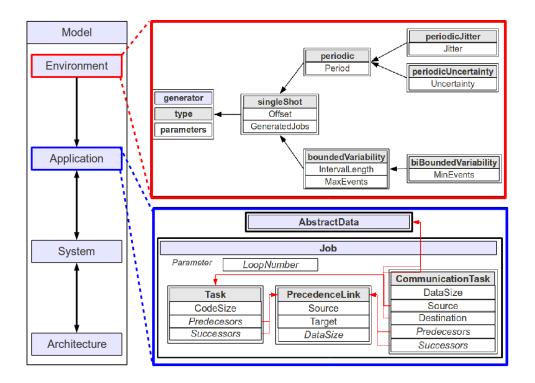

|   | 6.1  | Prelimi   | naries                                              | 59 |

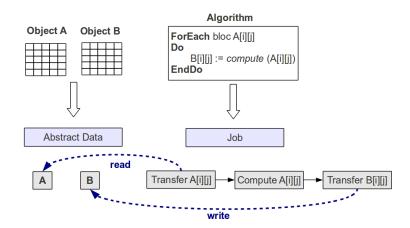

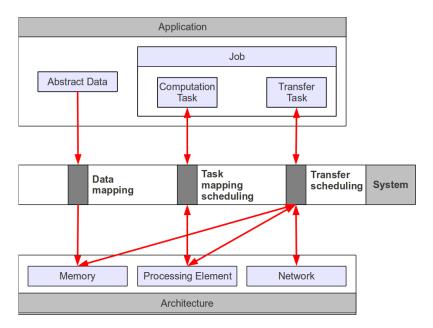

|   | 6.2  | Applica   | ation Model                                         | 70 |

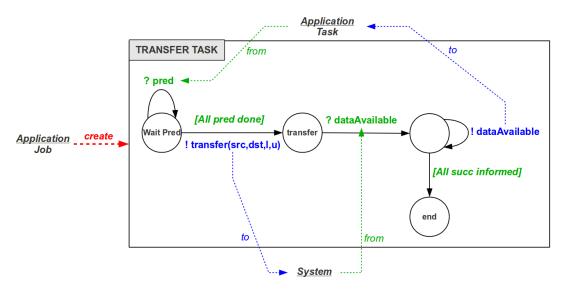

|   |      | 6.2.1     | Task Model         7                                | 71 |

|   |      | 6.2.2     | Data Model                                          | 72 |

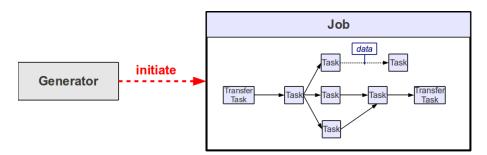

|   |      | 6.2.3     | Job Model                                           | 74 |

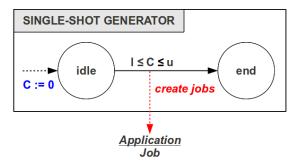

|   | 6.3  | Enviro    | nment Model                                         | 75 |

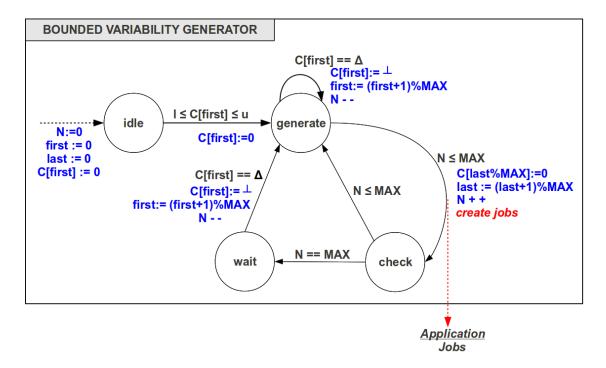

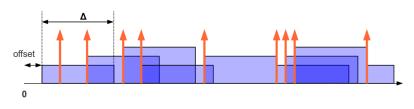

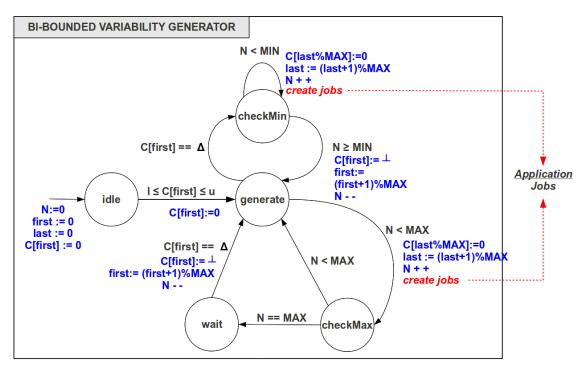

|   |      | 6.3.1     | Generators Characteristics                          | 30 |

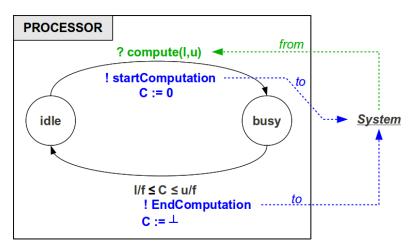

|   | 6.4  | Archite   | ecture Model                                        | 30 |

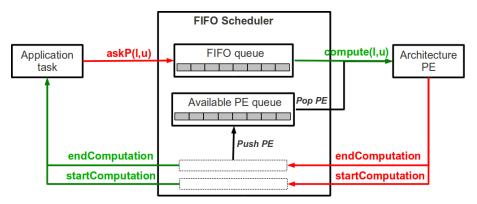

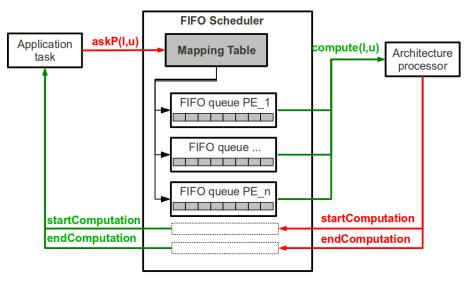

|   |      | 6.4.1     |                                                     | 31 |

|   |      | 6.4.2     |                                                     | 32 |

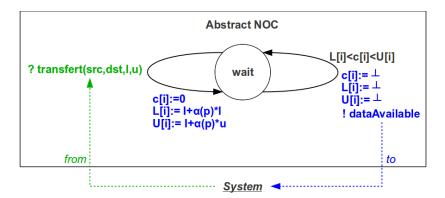

|   |      | 6.4.3     | 5                                                   | 33 |

|   |      | 0.1.5     |                                                     | 33 |

|   |      |           |                                                     | 33 |

|   |      |           |                                                     | 35 |

|   |      | 6.4.4     |                                                     | 35 |

|   | 65   |           |                                                     |    |

|   | 6.5  | •         |                                                     | 37 |

|   | ~ ~  | 6.5.1     |                                                     | 88 |

|   | 6.6  | Evaluat   | tion                                                | 90 |

| 7 | Real | ization:  | The DESPEX Tool 9                                   | 91 |

|   | 7.1  |           |                                                     | 91 |

|   | 7.2  |           |                                                     | 92 |

|   | 7.3  |           | *                                                   | 99 |

|   | 1.5  | 7.3.1     | Reachability Analysis                               | -  |

|   |      | 7.3.2     | Stochastic Simulation                               |    |

|   | 7.4  |           | Analysis                                            |    |

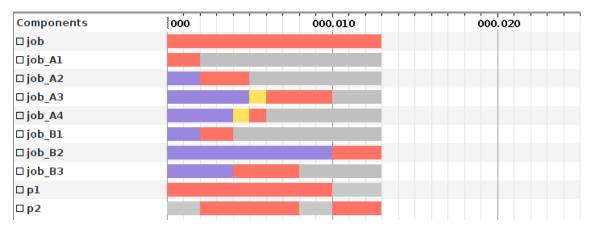

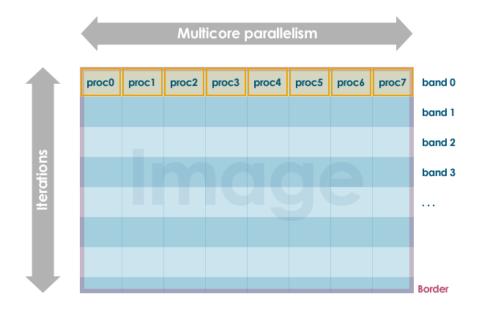

|   | 7.7  | Trace I   |                                                     | ,5 |

| 8 | Case | e Studies | s 10                                                | )9 |

|   | 8.1  | Reacha    | bility vs. Corner-Case Simulation                   | )9 |

|   |      | 8.1.1     | Model Description                                   | )9 |

|   |      | 8.1.2     | Analysis                                            | 10 |

|   |      |           |                                                     | 10 |

|   |      |           | 8.1.2.2 Best Case Analysis                          |    |

|   |      |           | 8.1.2.3 Reachability Analysis with Uncertainty      |    |

|   |      |           | 8.1.2.4 Quantitative Estimation                     |    |

|   |      | 8.1.3     | Summary                                             |    |

|   | 8.2  |           | Processing on P2012                                 |    |

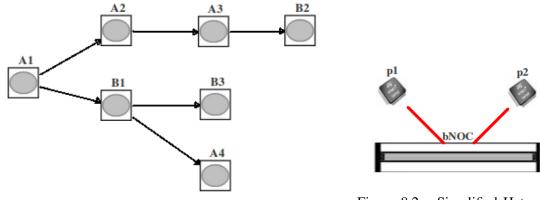

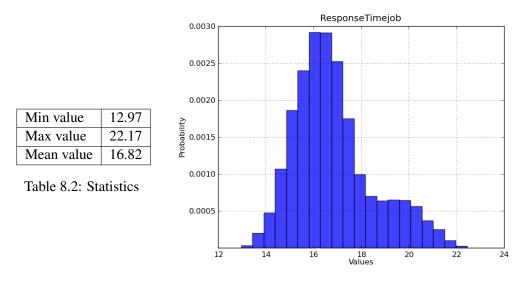

|   | 0.2  | 8.2.1     | Model description                                   |    |

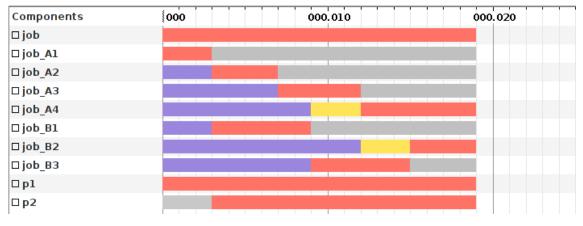

|   |      | 8.2.2     | Analysis                                            |    |

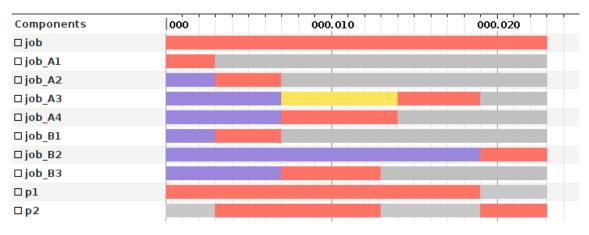

|   |      | 0.2.2     | 8.2.2.1         Worst Case vs Statistics         11 |    |

|   |      |           |                                                     |    |

|   |      |           | 8.2.2.2 Reading Granularity                         |    |

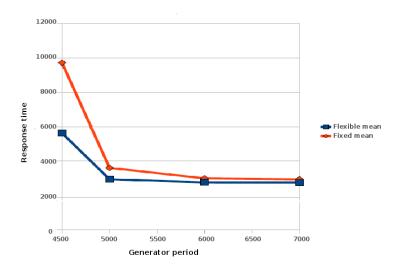

|   |      | 0.0.0     | 8.2.2.3 Fixed vs Flexible Mapping                   |    |

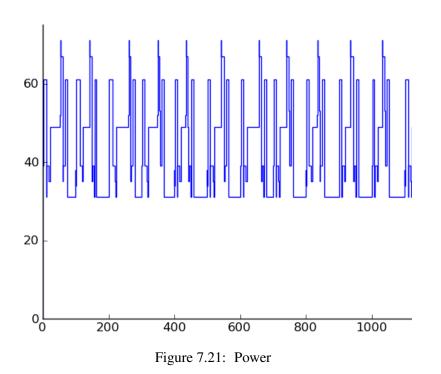

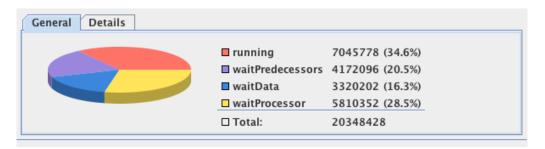

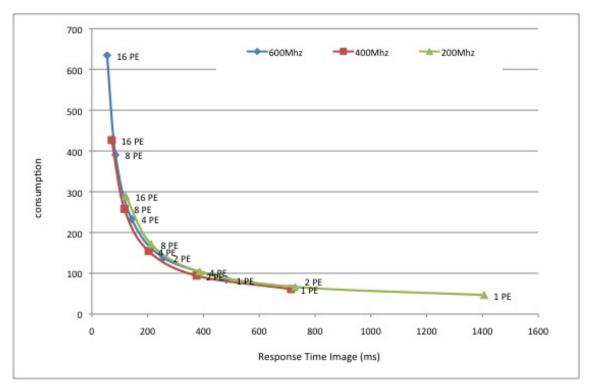

|   |      | 8.2.3     | Power Consumption                                   |    |

|   |      | 8.2.4     | Summary                                             |    |

|   | 8.3  |           | o Sensing Application                               |    |

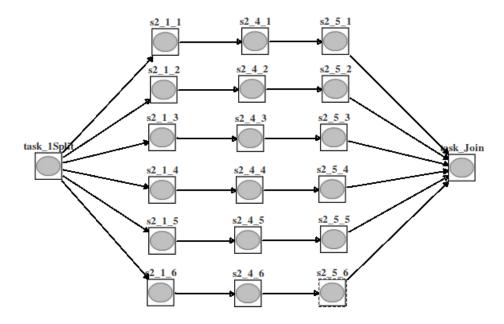

|   |      | 8.3.1     | Model Description                                   |    |

|   |      | 8.3.2     | Performance evaluation                              | 23 |

|   |      | 8.3.3     | Summary                                             |    |

| 9  | Conclusions and Future Work                                 | 125 |  |

|----|-------------------------------------------------------------|-----|--|

| A  | DPA: Optimizing the Value Function (Work in Progress)       |     |  |

|    | A.1 Non-Lazy Schedulers                                     | 127 |  |

|    | A.2 Upward Closed Strategies and Rectangular Approximations | 130 |  |

| Bi | liography                                                   | 135 |  |

# Chapter 1

# Introduction

This thesis is concerned with models, analysis techniques and tools intended to aid hardware and software designers in exploring their systems design space and finding efficient deployments of application programs on multi-processor platforms. The thesis can be viewed as a confluence point between several academic and industrial research currents in a domain which is very important practically and for which no agreed upon unified theoretical framework exists. To better understand the context of this thesis we mention two of the major driving forces behind the thesis.

#### Formal Analysis of Timed Systems

Formal verification is a kind of exhaustive simulation of abstract automaton-based models of software and hardware that capture mostly concurrency and synchronization features. Timed models such as timed automata, add quantitative timing information to the models and allow to reason about delays, execution times, deadlines and other *performance*-related measures. Over the years, a lot of work, at Verimag and elsewhere, explored the applicability of these models to scheduling for embedded (and other) systems and circuits. Although the expressivity of timed automata can be used to model more complex situations than what is possible using classical real-time models, their standard analysis technique (forward computation of reachable states and zones) does not scale up and for the time being cannot be applied to systems beyond a rather low threshold of size and complexity. Moreover, this type of analysis is worst-case oriented and is not always suitable for soft real-time applications where we care more about the average performance. There is a recent trend in verification, sometimes called *statistical model checking*, which replaces verification-style exhaustive exploration by Monte-Carlo simulation. In the timed context this means, implicitly or explicitly, to refine temporal uncertainty intervals into distributions supported by those intervals, resulting in some kind of continuous-time "non Markovian" stochastic processes.<sup>1</sup> We use such models in this thesis in two ways. First we do statistical simulation on high-level models of applications running on multi-core platforms and secondly, we develop new semi-analytic techniques for performance evaluation and optimization for duration probabilistic automata that can model a class problems of scheduling under stochastic uncertainty.

#### **The ATHOLE Project**

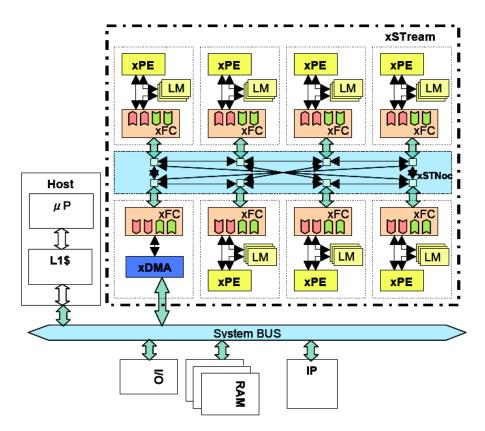

The thesis was aligned, temporally and conceptually, with the ATHOLE project, coordinated by ST Microelectronics, with the participation of CEA-LETI, THALES and CWS. Initially the project was focused on the xSTream architecture but around mid-time, xSTream development has been freezed and the project shifted to Plateform 2012 (P2012). The role of Verimag in the project

<sup>&</sup>lt;sup>1</sup>Tradition aside, the term non-Markovian is misleading. These processes are Markovian (state-based) with respect to extended states that include clock values.

was to apply its expertise in timed systems to help automating deployment decisions (mapping, scheduling) and ease the difficult task of exploiting multi-cores efficiently. The exposure to industrial and quasi-industrial practices and cultures was an opportunity to compare the modeling and analysis methods used by *system builders* (hardware designers and programmers) and those used by *model builders* (in verification and performance analysis). The tool described in this thesis, which brings abstract modeling concepts and analysis techniques to these application domains, was a *major deliverable* in the ATHOLE project.

The thesis is organized as follows:

- Chapter 2 is a very non-exhaustive survey on multi-core embedded systems and the modeling approaches used in various levels of abstraction during the design flow, with emphasis on performance evaluation;

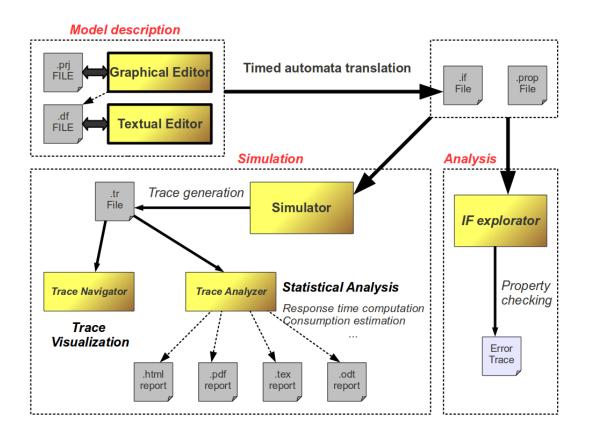

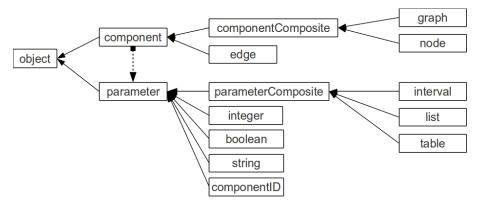

- Chapter 3 is a short introduction to timed automata, symbolic reachability computation on zones and the IF toolset on top of which our tool is implemented;

- Chapter 4 develops a new technique for computing the performance (expected termination time) of schedulers for acyclic scheduling problems (such as job-shop or task-graph) where the duration of each task is considered to be uniformly distributed over a finite interval;

- Chapter 5 attacks the more ambitious *synthesis* problem and develops a dynamic programming approach to derive expected-time optimal schedulers. These two sections constitute the major theoretical contribution of the thesis and are accompanied by a prototype implementation;

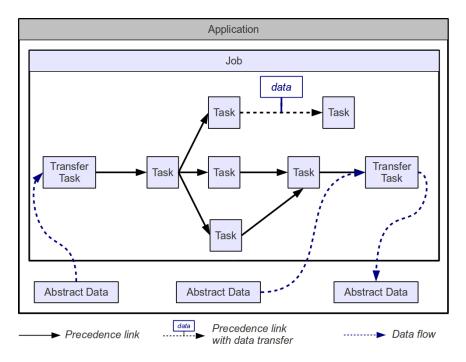

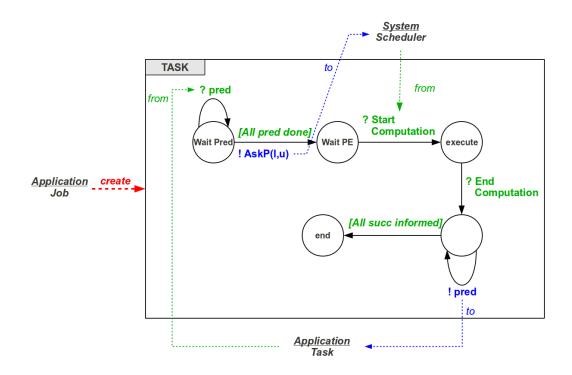

- Chapter 6 is the core of the thesis. It presents our abstract modeling framework for *application programs* (modeled as extended task-graphs), *input generators* (the processes that generate new tasks instances subject to temporal and logical constraints), *execution platforms* (very abstract models of processors, data transfer mechanisms and memories) and *deployment* (mapping and scheduling policies). Each modeled object is transformed into a timed automaton and the composition of these automata represents all the possible systems behavior;

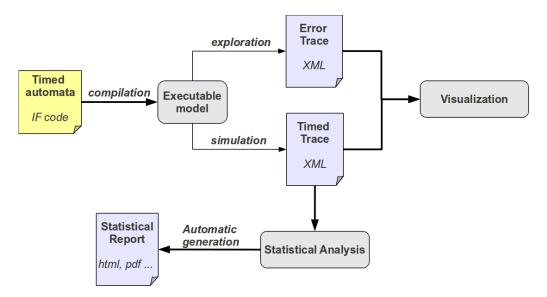

- Chapter 7 describes the tool *DESPEX, the DEsign-SPace EXplorer*, its architecture and the type of analysis it provides, namely symbolic reachability computation and Monte-Carlo discrete event simulation, followed by statistical and visual trace analysis;

- Chapter 8 describes three case studies treated by the tool. The first is a toy problem used to demonstrate the advantage of timed automata verification over corner-case simulation. The second is a video application provided by ST, evaluated for power and performance on P2012 using simulation, and the third is a signal processing application provided by Thales and evaluated on xSTream;

- Chapter 9 concludes the thesis and sketches some ideas for future work.

# **Chapter 2**

# Multi-core embedded system

Current embedded applications necessitate intensive computation and data communication which are difficult to handle by a single processor architecture. The performance demanded by these applications, like for example multimedia applications, requires the use of multi-processors architectures in a single chip endowed with complex communication infrastructures, such as hierarchical buses or networks on chips (NoCs). That's why Multiprocessors System on Chip (MPSoC) architectures have become a very attractive solution for the consumer multimedia embedded market [197].

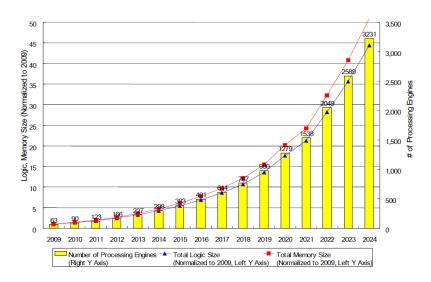

*System on Chip* (SoC) represents the integration of different computing elements and other electronics subsystems into a single integrated circuit. MPSoC [196] are SoC that may contains one or more types of computing subsystems, memories, I/O devices and other peripherals. Additionally, heterogeneous components are exploited to meet the tight performance and cost constraints. This trend of building heterogeneous MPSoC will be even accelerated due to current embedded application requirements. ITRS (International Technology Roadmap for Semiconductors) roadmap [1] predicts that the number of processing engines on future MPSoC platforms will increase rapidly (Fig-2.1), which will introduce a huge complexity into the software development process for such complex platforms. Making the potential parallelism of the applications more explicit so as to exploit the available processing engines, and then efficiently deploying it on the underlying hardware are the new and big challenges for MPSoC software developers.

Figure 2.1: Consumer Portable Design Complexity Trends [1]

We will discuss current MPSOC architectures and their different components. Then we will survey the typical embedded systems design flow and see that performance evaluation is done at different level of granularity. Here we are more interested in performance estimation at early design stage. We will present typical modeling techniques and discuss their utility for performance estimation.

#### 2.1 MPSOC Architecture

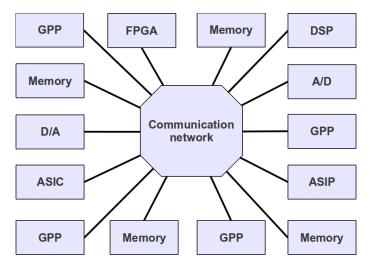

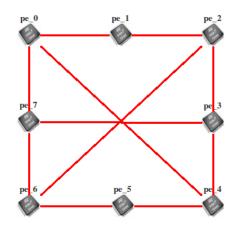

Heterogeneous MPSoC architecture can be represented as a set of *processing elements* (PE) or components which interact via a communication network (Fig-2.2). The PE can be of different type like processors (DSP, microcontroller, ASIP, ...) or memory elements (caches, DRAM ...) connected trough different communication schemes. This type of heterogeneous architecture provides highly concurrent computation and flexible programmability. Heterogeneous MPSoC are composed of different kind of PE as opposed to homogeneous MPSoC where the same type of element is instantiated several times.

Figure 2.2: MPSOC Architecture

Some heterogeneous platforms from the major semiconductor vendors such as NXP Nexperia [157], TI OMAP [185] or ST Nomadik [178] are already available. On the other hand, homogeneous ones were pionnered by the Lucent Daytona architecture [3, 196].

The literature relates mainly two kinds of organizations for multiprocessor architectures, shared memory and message passing [68]. Heterogeneous MPSoCs generally combine both models and integrate a massive number of processors on a single chip. Future heterogeneous MPSoC will be made of few heterogeneous subsystems, where each subsystem includes a massive number of identical processors to run a specific software stack [113].

We will now give an overview of the different hardware components in MPSoC.

#### 2.1.1 Processing Elements

Processing elements range in a spectrum between generality and specificity. We can classify them into two major type: General Purpose Processor (GPP) and Application Specific Processors (ASP). GPPs are flexible because they are built to be used in a variety of applications with different specifications. Changing functionalities or improving a system becomes relatively easy when you only need to change a software program. On the other hand ASPs are designed to execute

exactly one program, increasing performance and reducing power consumption. However, flexibility and reprogramming is limited because it is designed as a custom digital circuit dedicate to restricted application range. We can distinguish different sub-classes of ASP, such as ASIC (Application Specific Integrated Circuit) where algorithms are completely implemented in hardware and programmable microprocessors like DSP (Digital Signal Processor) for extensive numerical real-time computation, or ASIP (Application Specific Instruction Set Processor) where hardware and instruction set are designed together for one particular application.

#### 2.1.2 Memory Organization

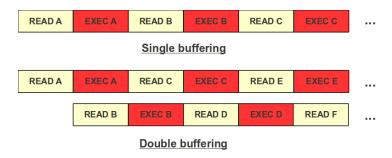

The memory subsystem is an important component of system designs that can benefit from customization. Unlike general purpose processors where a standard cache hierarchy is employed, the memory hierarchy of embedded systems can be tailored in various ways. The memory can be selectively cached. The cache line size can be determined by the application. The designer can opt to discard the cache completely and choose specialized memory configurations such as FIFOs and stream buffers and so on.

The memory is a bottleneck in a computer system since the memory speed cannot keep up with the processor speed and the gap is becoming larger and larger. Memory hierarchy issues are among the most important concerns in designing application-driven embedded systems. A typical embedded system architecture consists of processor cores, reconfigurable hardware, instruction cache, data cache, on-chip scratch memory and on-chip or off-chip DRAM.

The cache is a special high-speed, low volume memory that is in close proximity to the processing hardware that it is reserved for. It can be seen as an interface between the processor and the off-chip memory. Embedded architectures include both data and instruction caches.

Scratch-Pad memory refers to data memory residing on-chip, that is mapped into an address space disjoint from the off-chip memory, but connected to the same address and data buses. Both the cache and Scratch-Pad memory (usually SRAM) allow fast access to their residing data, much faster than accessing off-chip memory. Off-chip memory (usually DRAM) refers to a highest volume memory residing far from the processing element. The main difference between the Scratch-Pad SRAM and data cache is that the SRAM guarantees a single-cycle access time, whereas an access to the cache is subject to cache misses.

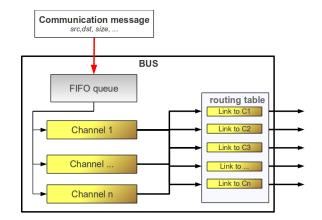

#### 2.1.3 Interconnect

The interconnect is a resource shared between various hardware components. Its role is to transmit data from a *source* to a *destination* component, thus implementing the communication network. Basically the network component is characterized by two metrics:

- Latency: total time to transfer a quantity of data from the source to the destination component;

- Bandwidth: amount of data that can be transmitted per time unit.

On-chip communication architectures can be divided into the following three main classes [126]:

- 1. Point to point interconnect: pairs of processing elements communicate directly over dedicated physically-wired connections [33];

- 2. Bus architectures [151] : long wires are grouped together to form a single physical entity. One can find different bus based architecture:

- FPGA-like Bus [60] with programmable interconnects using static network;

- Arbitrated Bus [110] with time-shared multiple core connectivity;

- Hierarchical Bus [11, 12, 195] combining multiple buses using bus bridges.

- 3. Network on Chip (NoC): Communication is achieved by sending message packets between blocs using an on-chip packet-switched network. NoC is a relatively new chip design paradigm concurrently proposed by many research group [172, 127, 28]. A survey of research and practices of Network-on-Chip can be found in [40].

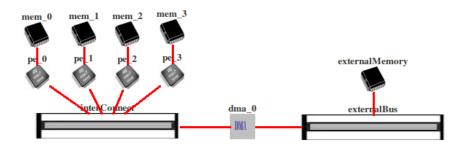

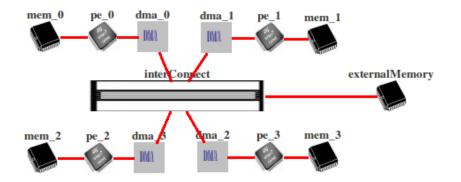

A component which can be seen as part of the interconnect is Direct Memory Access (DMA). It is a device that can control the memory system without using the CPU. On a specified stimulus, the module will move blocks of data from one memory location to another. DMA is essential for embedded systems since it allows large quantities of information to be transferred to or from memory, while the processor can be doing something else.

#### 2.2 Design Flow

Systems-on-chip require the creation and use of radically new design methodologies because some of the key problems in SoC design lie at the *boundary* between *hardware* and *software*.

Classic SoC design flows imply a long design cycle because most of them rely on a sequential approach where complete hardware architecture should first be developed before software could be designed on top of it. This long design cycle is not acceptable because of time to market constraints.

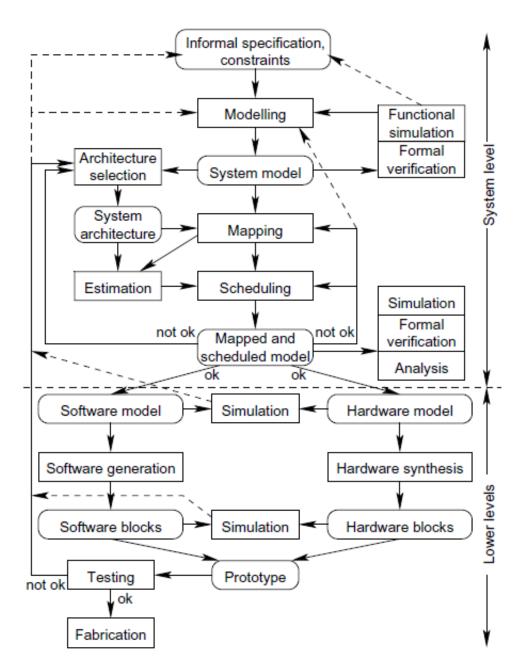

Due to their complexity, the design of embedded systems requires modeling phases at different abstraction levels (Fig-2.3). At each level, many different activities are required during the design flow: specification and functional modeling, performance modeling, design and synthesis, validation and verification. Because the real product is not available before the development task is completed, all activities operate on models. According to [112]:

A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity that are relevant for a given task. A model is minimal with respect to a task if it does not contain any other characteristics than those relevant for the task.

A model is therefore an abstraction of one entity and may be defined differently according to its use (functional validation, performance evaluation). There is an increasing use of early systemlevel modeling, even if it would not contain the entire hardware architecture, but only a subset of components which are sufficient to allow some level of software verification on the hardware before the full hardware is available, thus reducing the sequential nature of the design process. The use of high-level programming models to abstract hardware/software interfaces is the key enabler for concurrent hardware and software designs. This abstraction allows to separate lowlevel implementation issues from high-level application programming (Fig-2.3). It also smoothens the design flow and eases the interaction between hardware and software designers. It acts as a contract between hardware and software teams that may work concurrently. Additionally, this scheme eases the integration phase since both hardware and software have been developed to comply with a well-defined interface.

Furthermore programming an application-specific heterogeneous multi-processor architectures becomes one of the key issues for MPSoC, because of two *contradictory* requirements:

- Reducing software development cost and overall design time: needs high level abstract models;

- Improving performance: needs accurate and precise low level models.

Figure 2.3: Generic Embedded System Design Flow

All models are simplification of reality, an exact copy of a real product can only be the real product itself. So there is always a trade-off as to what level of detail is included in the model, too little detail implies a risk of missing relevant informations and giving wrong predictions, too much detail makes models overly complicated and thus difficult to understand or analyze.

#### 2.2.1 Low Level Modeling

Modeling the hardware is an important phase in the design of an embedded system. It is achieved by developing virtual prototypes that can be fully functional software models of the physical hardware, allowing accurate simulation, design verification and automatic layout generation. The advantage of virtual prototypes lies in their early availability in the development cycle. This way software developers can begin earlier with development and verification of the hardware dependent software.

#### Platform

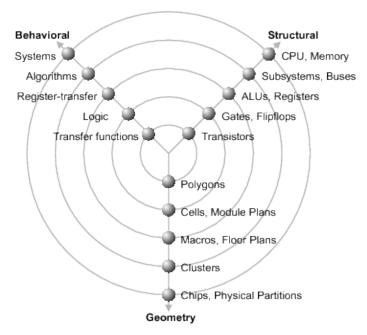

To give an overview about the different levels of abstraction and to illustrate their interrelation to the different specification domains, the Y-Chart of Fig-2.4 proposed by Gajeski is commonly used [96].

Figure 2.4: Gajski-Kuhn Y-chart

The Y-chart model distinguishes between 3 abstraction domains

- Behavioral (functional): describes the temporal and functional behavior of a system without any reference to the particular way in which it is implemented.

- Structural: deals with how the system is composed of interconnected hierarchical subsystems.

- Physical/Geometrical: specifies how the system is laid out in terms of physical placement in space and physical characteristics without any elements of functionality.

Each of these domains can also be divided into levels of abstraction:

- Transistor level

- Logical level

- Register-transfer level (RTL)

- Algorithmic level

- System level

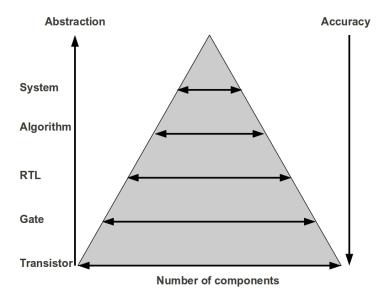

Figure 2.5: Abstraction levels

Each level defines an abstract platform, called *virtual prototype* on which simulation can be done more or less accurately (cycle accurate, instruction accurate, transaction accurate ...). As depicted in Fig-2.5, highest accuracy is obtained by lowest abstraction level but implies a higher modeling effort as the number of components is huge. Simulation or timing analysis on such models is also a major constraint. Typically a cycle-accurate processor model can be simulated at a rate of between 50 and 1000 instructions per second, while execution on the real hardware is on the order of millions of instructions per second.

Hardware Description Languages (HDL) are used to model systems at a low level of abstraction, typically at RTL, and are used to do simulation with high precision or to automatically generate the hardware layer. Tools like Verilog [184] or VHDL [176] are used to specify hardware in a textual format.

#### Applications

Software too can be described at different levels of abstraction. The lowest level is binary machineexecutable code which is typically generated from a program written in a higher level programming language such as C. An application is then evaluated on a real platform if such exists, or by using a virtual platform. C code is compiled and translated automatically to assembly language and machine code.

More generally, applications are written using a programming model. The programming model specifies how application components are running in parallel and how they communicate including synchronization operations that are available to coordinate their activities. The programming model is usually embodied in a parallel language or a programming environment [68].

Examples of parallel programming models are as follows:

- Shared address space: communication is performed by posting data into shared memory locations, accessible by all the communicating processing elements;

- Data-parallel programming: several processing elements perform the same operations simultaneously, but on separate parts of the same data set;

- Message passing: when the communication is performed between a specific sender and a specific receiver.

Examples of such programming models are briefly described in the following:

- StreamIt is an example of programming model for streaming applications [183];

- MPI (message-passing interface) [154] is a message-passing library interface specification. It includes the specification of a set of primitives for point-to-point communication with message passing, collective communications, process creation and management, one-sided communications, and external interfaces;

- MCAPI (multi-core communications APIs) [65] defines a set of communication APIs for multi-core communications, to support lightweight, high performance implementations typically required in embedded applications;

- YAPI (Y-chart application programmer's interface) is an interface to write signal and stream processing applications as process networks, developed by Philips Research [75]. TTL (task transaction level interface) proposed in [188] is derived from YAPI;

- OpenCL (Open computing language) is an open standard for writing applications that execute across heterogeneous platforms consisting of CPUs, GPUs, and other processors, introduced by Khronos working group [136]. OpenCL provides parallel computing using task-based and data-based parallelism;

- OpenMP (open multi-processing) is an application programming interface (API) that supports multi-platform shared memory multiprocessing programming in C, C++, and Fortran on many architectures [59].

Both hardware and software abstraction levels described previously are defined with too much detail for rapid evaluation at early stage of the design flow. It implies a high development effort before performances estimation can be done. The abstraction level close to our work is situated on top of what is generally defined as *system-level design*.

#### 2.2.2 System-Level Design

In modern system-level design methodology, known as HW/SW co-design, the development of hardware platform and application software is done in parallel. Design space exploration needs separate application and architecture specifications. An explicit *mapping* step maps application components to architecture. HW/SW co-design includes various design problems including system specification, design space exploration, performance estimation, HW/SW co-verification, and system synthesis. This can be achieved at system level for early estimation and then models are refined at lower level for more accurate performance evaluation.

Modeling and simulation at high abstraction levels are used to increase and to simplify the development and validation of MPSoC at early design stage. For that we need abstract models of both software and hardware components. Defining such models, requires knowledge about hardware and software architecture details as well as execution environment constraints (timing, power consumption ...) at early design stages. This can be achieve by hardware-software co-designer based on profiling or past experiences.

Description languages have been developed as well at higher levels of abstraction. At system level, these language can describe abstractions of software and a high level component view of hardware. One can cite for example:

• SystemVerilog [180] is an extension of Verilog inheriting capabilities for synthesizable modules description (Verilog) and object oriented language abstraction, that allow the verification of complex systems;

- SpecC [88] is built on top of ANSI-C programming language and is intended for the specification and design of digital embedded systems, including hardware and software portions and supports concepts like behavioral and structural hierarchy, concurrency, communication, synchronization, state transitions, exception handling, and timing;

- SystemC transaction-level modeling (TLM) is another standardization work [92] which offers a set of standard APIs and a library, built on top of C++ programming language, that implements a foundation layer upon which interoperable transaction-level models can be built;

- AADL (Architecture Analysis and Design Language)[87] defines a language for describing both the software architecture and the execution platform architecture of performancecritical, embedded, real-time systems. It describes a system as a hierarchy of components with their interfaces and their interconnections, specifying both functional interfaces and aspects critical for performance;

- SysML [194] is based on an extension of the Unified Modeling Language (UML) and has views that deal with multiple aspects of the system: functional and behavioral, structural, performance, and slew of other models like cost and safety.

Underlying the specification of embedded systems there is the notion of *Model of computation and communication* which defines more formally how concurrent components interact with each other. A multitude of modeling formalisms have been applied to embedded system design. Typically, these formalisms strive for a maximum of precision, as they rely on a mathematical (formal) model. We will presents next the main classes of models used in the design of MPSoC.

#### 2.3 Models of Computation for Embedded Systems Design

Modeling formalisms for embedded system design have been widely studied, and several reviews and textbooks about models of computation (MoCs) can be found in the literature [131, 173, 80, 187, 94]. Usage of formal models in embedded system design allows (at least) one of the following [173]:

- Unambiguously capture functionality of the required system;

- Verification of functional specification correctness with respect to its desired properties;

- Support synthesis onto a specific architecture and communication resources;

- Use different tools based on the same model (supporting communication among teams involved in design, producing, and maintaining the system).

Two basic types of MoCs can be differentiated: process based and state based MoCs [89]. Process-based MoCs describe the system behavior as a set of concurrent processes communicating with each other through message passing channels or shared memory facilities such as:

- Kahn process networks [116]: process are independent of each other and execute in parallel. Communication is done through uni-directional message passing channels incorporating buffers, which enable asynchrony;

- Dataflow model, processes are broken down into atomic blocks of execution, called actors, executing once all their inputs are available. On every execution, an actor consumes the required number of tokens on all of its inputs and produces resulting tokens on all of its outputs. In the same way as KPNs, actors are connected into a network using unbounded,

uni-directional FIFOs with tokens of arbitrary type. More formally, a dataflow network is a directed graph where nodes are actors and edges are infinite queues. Dataflow networks are deterministic and have the same termination semantics as KPNs. It is a basis for many commercial tools such as LabView [39] and Simulink [149];

- Synchronous DataFlow (SDF) [134] is a specialization of dataflow modeling, where production and consumption values on edges are not necessarily the same. Unlike dataflow, states do not influence the number of tokens that are produced and consumed in each firing cycle and these numbers can be specified a priori;

- Process Calculi :

- Communicating Sequential Processes (CSP) [107, 52] allows the description of systems in terms of component processes that operate independently, and interact with each other solely through message-passing communication. CSP uses explicit channels for message passing, whereas actor systems transmit messages to named destination actors;

- Calculus of Communicating Systems (CCS) [150]: the fundamental model of interaction is synchronous and symmetric, i.e. the partners act at the same time performing complementary actions;

- Algebra of Communicating Processes (ACP) [34] focus on the algebra of processes, and sought to create an abstract, generalized axiomatic system for processes.

State based models are defined by a set of states and transitions, called state machines. States explicitly represents the memory state of a program and transitions which can be guarded over specific boolean conditions, represents the changes in the system behavior. Finite State Machines (FSM, automata) is one of the basic model for describing various type of application and is usually sequential, i.e it can only be in one state at a time. Two types of FSM exists: Moore type in which the outputs are determined solely by its current state [153] and Mealy type in which outputs are determined both by its current state and the current inputs.

Several extension of FSM have been proposed:

- Finite State Machine with DataPath (FSMD) introduces a set of variable in order to reduce the number of states;

- Hierarchical and concurrent finite states machines (HCFSM) incorporate notions of hiearchy and concurrency. Hierarchy is defined through the notion of superstates representing an enclosed state machine and communicating through shared variables, events or signals. Statecharts [104] are the most well known formalism;

- Co-Design Finite State Machines (CFSM) [61] connect individual sequentials elements in a global asynchronous network.

Combinations of different models have also been developed such as Program State Machine (PSM) [90] which can be seen as a combination of KPN and HCFSM. Petri nets [161] are directed graphs, similar to dataflows, with two types of nodes: places and transitions. Places correspond to the states of the program and transitions are the computational entities. A firing of the transition implies the consumption of tokens in the input places and output tokens in the output places.

The notion of time is extremely important in many of the modeling formalisms for embedded systems. Untimed MoC, like Petri nets, is based on data dependency only and neither a transition or the transfer of a token from one place to another takes a particular amount of time. Using a

timed MoC reflects the intention of capturing the timing behavior of a component which could also influence its functional behavior. We can distinguish between continuous-time and discretetime system according to the type of the time variables.

In discrete event MoC, events are sorted by a time stamp stating when they occur and are treated in chronological order. Transaction Level Modeling (TLM) is a discrete-event MoC built on top of SystemC, where modules interchange events with time stamps.

Synchronous models of computation divide the time axis into totally ordered slots and everything inside a slot occurs at the same time. This type of MoC is more suited for programming control and real-time systems. Esterel [36], Lustre [102] and Signal [30] are some existing synchronous languages.

Many of the untimed MoC presented previously have also been extended with timing information. One can cite for example, Timed automata [6], that extend finite automata with clock variables which give timing constraints on the behavior of the system, or Timed Petri Nets [37] where a timed interval is associated with each transition.

Modeling implies also the notion of determinism. Deterministic systems produce one unambiguous output for a given input, but a system may not always react with the same outputs when confronted with the same inputs or inputs may not be precisely defined. For example communication times in distributed systems are hard to predict and may vary due to physical effects or interferences. This leads to non-deterministic models where systems may produce different behaviors. Quantitative properties concerning the different outputs are sometimes captured with stochastic systems. We will discuss non determinism and uncertainty in more detail in the next chapters.

#### 2.4 Performance Evaluation

Performance analysis aims to assess and understand some quantitative properties at an early stage of the product development and is as important as functionality. In [148] Marwedel indicates five metrics for the evaluation of the efficiency of an embedded system:

- Power consumption

- Code size

- Run time efficiency

- Weight

- Cost

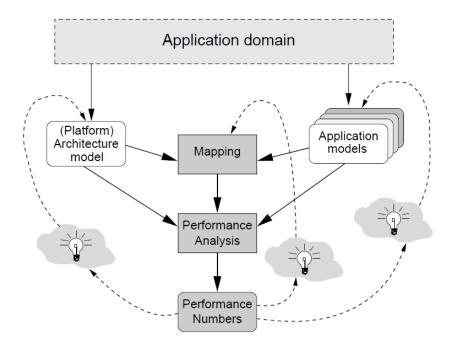

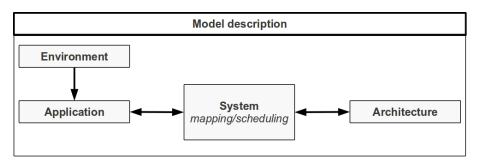

All these metrics can be subject to design requirements of the system, that is appropriate predictions of these characteristics are necessary in early design stage and can be considered objectives of early performance analysis. According to [152], design space exploration is the process of analyzing several implementation alternatives to identify an optimal solution. For efficient system-level design space exploration of complex embedded systems the separation-of-concerns concept has been introduced by [121]. Therefore, Y-chart design methodology [19, 122], depicted on Fig-2.6, became a popular basis for early design space exploration.

To perform quantitative performance analysis, application models are mapped onto the architecture model under consideration, whereafter performance of each application-architecture combination can be evaluated. Subsequently, the resulting performance numbers may inspire the designer to improve the architecture, adapt the application or modify its mapping.

*Performance* is often focus on the analysis of timing aspects e.g. how fast a system can react to events. However power consumption is, in some situation, as important as execution time, and we will focus in this thesis on performance analysis on these two metrics.

Figure 2.6: Y-chart based design space exploration (obtained from [162])

Very often, the timing behavior of an embedded system can be described by the time interval between a specified pair of events. Depending on the application domain timing properties can be more or less critical. Many embedded systems must meet real time constraints, that is, they must react to events within a specific time interval, called *deadline*. A real time constraint is called hard if its violation is considered a system failure, and it is called soft otherwise. First of all it is necessary to distinguish between the following terms (taken from [182]):

- Worst case and best case. The worst case and the best case are the maximal and minimal time interval between the arrival and termination events under all admissible system and environment states. The execution time may vary largely, owing to different input data and interference between concurrent system activities.

- Upper and lower bounds. Upper and lower bounds are quantities that bound the worst- and best-case behavior. These quantities are usually computed offline, that is, not during the runtime of the system.

- Statistical measures. Instead of computing bounds on the worst- and best-case behavior, one may also determine a statistical characterization of the runtime behavior of the system, for example, distributions, expected values, variances, and quantiles.

In hard real time systems, performance is hardwired into correctness, for example requiring that some deadline is *never* violated. For such systems we are more interested in upper bounds and worst case behavior whereas in soft real time system lower and upper-bounds represent very extreme cases and a more quantitative estimation will be more useful.

Performance evaluation is a key challenge in the analysis of MPSoC and can be broadly divided in two main approaches: formal methods and simulation-based approaches. Formal verification is the process of checking whether some properties are satisfied by using mathematical proofs. There are different type of formal verification:

• Model checking [63]: given an abstract model and a property to verify, typically expressed

as a temporal logic formula, a model checker performs exhaustive exploration of the set of all possible states.

- Theorem proving: the system is modeled as a set of mathematical definitions in some formal mathematical logic. Properties of the system are derived as theorems that follow from these definitions by using standard results in mathematical logic [160].

- Equivalence checking: formulas for both the specification and the implementation are reduced to some canonical form (if one exists) by applying mathematical transformations. If their canonical forms are identical, then the specification and the implementation are said to be equivalent.

Simulation consists in exploring a model interactively or randomly, possibly using heuristics for choosing the visiting states. It is a technique of partial validation, i.e if no error is detected, this method increase the confidence in program correctness but can never ensure that all properties are satisfied. Discrete event simulation [56, 140] is widely used for evaluating performance of MPSoCs.

#### **Timing Analysis**

Timing requirements have been widely studied in the real time community where schedulability analysis techniques have been developed such as Rate Monotonic Analysis [141]. Most of these techniques are devoted to single-processor systems but have been extended to distributed systems [186] and more recently for fixed priority multiprocessors scheduling [97].

In the domain of communication networks, abstractions have been developed to model flow of data through a network. In particular Network Calculus [132] provides the means to deterministically reason about timing properties of data flows in queuing networks, and can be viewed as a *deterministic* queuing theory. Modular performance analysis [191] and Real-Time Calculus [181] extends the concepts of Network Calculus to the domain of real-time embedded systems.

Some other model-based solutions for timing design, performance optimization and timing verification are symbolic timing analysis for systems (SymTA/S) [105] or schedulability analysis provided by the tool TIMES [10], which is based on timed automata, a model we will discuss later in detail as it underlies our models.

#### **Power Consumption Evaluation**

Accurate power consumption estimation can be done at transistor or gate level, but due to the complexity of working at this level of abstraction, this is very costly. Thus, to accelerate power estimation analysis, many abstract models have been proposed including TLM approaches [17, 137, 25, 199] or algorithmic descriptions [147, 83, 85, 108, 124].

Generally, high-level models use a reference design model to retrieve more accurate power estimation with RTL power estimation tools. Nevertheless, simulation time and memory requirement of these tools are considerable, making their use impracticable when exploring large design spaces.

#### 2.5 Our Modeling Framework

The models presented in this thesis are much more abstract than those used in the *development* of the software and hardware in the sense that they do not represent the actual computations but attempt to capture the essential features which are relevant for predicting performance. For the application models we abstract away from the actual lines of code and view an application as a

*task graph*, a collection of high-level procedures, each characterized by its execution cost (number of processor cycles), its precedences (to which tasks it needs to wait and which tasks wait for it to terminate) and the amount of data it sends/receives to/from other tasks.

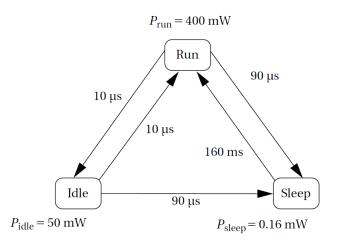

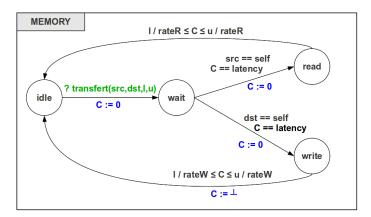

The modeling of the processing elements is even more abstract compared to their real complexity. The state of a processor at a given instant is characterized by its speed (assuming processors that can switch between voltage/frequency levels), whether it is turned on, and which task is executing on it. The speed of the processor is used to translate the quantity of work of a task into a *duration*. In addition we use rough model of static and dynamic power consumption for the processors indicating the power per time unit in either of its speeds, in execution and idling. The same high-level modeling style is applied to other architectural components such as interconnect and memory

In this modeling framework, a task is viewed as a simple *timed automaton* which leaves its active state some *time* after entering it. The advantages of such abstract models in terms of how hard it is to simulate or analyze them are evident: to advance a clock in a discrete event simulation is orders of magnitude faster than a cycle-accurate simulation of the underlying software/herdware system, and even much faster than simulation at the operational semantics level of C programs. And of course, such models need not wait for the *complete* hardware and software to be realized. However the question about the relation between such models and any reality should not be ignored, and we phrase it explicitly: *Where do the numbers that decorate the model come from?*

The answer may vary depending on how developed the system in question is at the time of analysis. If the code is fully written and the architecture fully developed, one may profile the tasks and measure the execution times. In fact, if the systems is fully operational, testing it on the real hardware can be more efficient than any simulation. If a new application is to be deployed on a variant of an existing architecture, numbers can be derived based on a combination of profiling and designers know-how from similar applications. These numbers can be very imprecise and there may also be a large real-life variability among execution times of instances of the same task. To compensate for the imprecision we invoke a very attractive feature of our models, inherited from the tradition of formal verification: unlike "executable" models needed for simulation and for implementation, we use models that are not necessarily *deterministic*: they may exhibit nondeterminism (or under-determination in the sense of [146]) in power consumption, in size of data items and in task *durations* as well as in their *arrival* patterns. The methods applied to handle this non determinism vary from Monte-Carlo simulation where the uncertainty space is randomly sampled to generate statistics, via verification methods that attempt to prove that something such as deadline miss never happens under all possible choices in the uncertainty space, to more sophisticated methods that compute the *expected* performance of a system.

To recapitulate our approach: we replace overly detailed models at a very low-level of abstraction (some of which might be inexistent at the time of the analysis) by very coarse grained models that compensate for their imprecision by taking the under-determination more seriously and explicitly in the analysis method. It seems that software and especially hardware developers bring to performance analysis too many low-level details (which are indispensable for implementation and functional correctness, though) while investing less effort in modeling the external environment of the system, such as the arrival model of tasks, which can have more effect on the performance than the low-level implementation details. This is understood because the external environment is not part of the system that they are responsible for developing and whose detailed implementation model cannot be avoided.

Since our approach originates historically from the tradition of formal verification it is worth making the premises of verification explicit in order to assess both its potential contribution and its current inadequacy for performance evaluation. Algorithmic formal verification is concerned with proving functional correctness of systems such as communication protocols and digital hardware. This is often done on models that abstract away from *data* and focus on *control* (synchronization).

However, functional correctness in the strict sense often used in verification is not a necessary nor sufficient condition for the usefulness of a system. A correct system with an extremely slow response is not likely be ever used, while systems that work well *most* of the time are all around us. To apply the insights of formal verification to system design beyond the very narrow context in which it is currently used, one should rethink some the following premises of the field:

- 1. System models, at least traditionally, are qualitative/logical without quantitative information;

- 2. The questions posed to the verification tool are of a qualitative yes/no nature: is the system correct or not;

- 3. There is an implicit universal quantification over the possible behaviors of the system: a system is correct if *all* its behaviors do not violate the specifications.

The first premise is relaxed by models of automata augmented with numerical variables are used extensively in software verification as well as in hybrid systems. Timed automata [6], the model most relevant to the present thesis, have been invented to model delays and execution times in a quantitative way. Relaxing the second premise has been promoted as *quantitative* analysis/synthesis [57, 42] and it consists of decorating states and transitions with numerical *costs* and tracking their evolution along system behaviors. Such costs typically admit a simpler dynamics than more general numerical variables in programs or hybrid systems. For example, the model of linearly-priced timed automata [46, 128], which are timed automata augmented with costs that can grow at different rates at different states, is simpler to analyze than other hybrid systems with constant slopes [120, 119, 15] because the cost variables are passive observers of the dynamics. The relaxation of universal quantification is what underlies *statistical model checking* [201] [62] [72] and can be viewed as a compromise between the rigor of formal verification and the scalability constraints for real systems. We demonstrate in this thesis that a combination of all these relaxations has a great potential in solving a central problem related to the multi-core revolution: how to evaluate and optimize the performance of application programs on such execution platforms.

Functional correctness and good performance are complementary and sometimes conflicting evaluation criteria. In *hard* real-time systems, performance is hardwired into correctness: a feedback function of a controller should be computed between every two consecutive sensor readings which puts a deadline constraint on its computation time. Using a timed model of the software/hardware architecture, which represents the execution times of the tasks as well as the scheduling policy, one can verify that such a deadline is never missed. In certain simple situations studied extensively by the real-time community [54, 142, 125] one can do the calculation [141] without invoking an explicit dynamic "executable" model at all. For embedded systems where the real-time constraints are *softer* the system is expected to give a *best effort* performance depending on the system load and resource availability. A typical example would be video streaming where a good trade-off between response time and image quality is sought. For such systems, the actual response time is a performance measure of the system, together with additional criteria such as system price or power consumption. Unlike what is common in verification, the quantitative measures are not Booleanized via predicates/constraints into a yes/no answer but remain quantitative and can be used to compare the relative performance of different designs.

Unlike safety-critical verification, soft systems are not evaluated according to their *worst-case* behavior but in a more probabilistic fashion. The traditional verification approach to the problem of performance evaluation based on "classical" timed automata technology [202, 82, 48, 130, 192, 38, 10] is *exhaustive*: it can compute performance measures such as termination time and other costs for *all* possible values of the uncertainty space, thus compute lower- and upper-bounds on termination time. For soft real-time systems this is, at the same time, too much and too little. The

lower and upper-bounds represent very extreme cases which are realized only when all the tasks take their extremal duration values.

Under very reasonable assumptions these extreme values are less likely than termination times that admit many realizations (as 7 is more likely than 12 in dice). In contrast with the exhaustive approach, in Monte-Carlo simulation the uncertainty space is finitely sampled according to some distribution and each sampling point induces a single deterministic behavior whose performance is evaluated by (cheap) simulation. Such an approach is weaker than formal verification because it does not cover all behaviors: it can, at most, put bounds on the probability of error or a deadline miss. On the other hand it is stronger as it can give an estimation of the distribution and *expected value* of the termination times, which can be much more useful for this type of applications than the very conservative bounds computed by the exhaustive approach.

#### 2.6 Related tools

Timed automata are a common and theoretically well-founded formalism for real-time systems. Reachability analysis of timed automata has been implemented in several tools, including KRONOS [73], UPPAAL [130], IF [48] or RABBIT [38]. Literature relates many tools for design-space exploration, based on timed automata or other formalisms. We present in the sequel some of them, close to our work.

#### TIMES [10]

It is a tool suite designed mainly for symbolic schedulability analysis and synthesis of executable code with predictable behaviours for real-time systems. Given a system design model consisting of a set of application tasks whose executions may be required to meet mixed timing, precedence, and resource constraints, a network of timed automata describing the task arrival patterns and a preemptive or non-preemptive scheduling policy, Times will generate a scheduler, and calculate the worst case response times for the tasks. The design model may be further validated using the UPPAAL timed model checker.

#### PTOLEMY [53]

The Ptolemy project studies heterogeneous modeling, simulation and design of concurrent systems with a focus on systems that mix computationnal domains [84] It uses tokens as the underlaying communication mechanism and controllers regulate how actors fire and how tokens are sent between each actors. Actors are software components that execute concurrently and communicate through messages sent via interconnected ports. A model is a hierarchical interconnection of actors. The semantics of a model is not determined by the framework, but rather by a software component in the model called a director, which implements a model of computation including process networks, discrete-events, dataflow, synchronous/reactive, rendezvous-based models, 3-D visualization, and continuous-time models. Each level of the hierarchy in a model can have its own director, and distinct directors can be composed hierarchically. A major emphasis of the project has been on understanding the heterogeneous combinations of models of computation realized by these directors. Directors can be combined hierarchically with state machines to make modal models [133]. For example, a hierarchical combination of continuous-time models with state machines yields hybrid systems [135].

#### OCTOPUS [20]

The octopus toolset supports model-driven design-space exploration based on high level modeling with a clear separation of application, platform and mapping. It provides formal analysis of func-

tional correctness and performance and semi-automatic exploration of alternatives and synthesis of optimized designs. Analysis process works with different type of models:

- Timed automata model checking using UPPAAL [130]

- Petri nets simulation using CPNTools [164]

- Synchronous dataflow for trade-off analysis using SDF3 [179]

#### HOPES [99]

It is a model based framework for MPSoC software development. The application model is based on actor-orientation and is described in UML using PeaCE model [100]:

- Process network: specify execution condition of each task and define interaction between them.

- Synchronous piggybacked dataflow [101]: specify signal processing

- Flexible FSM [123]: specify control tasks.

The hardware platform is separately specified in a block diagram with a set of architectures and constraints parameters described in an xml-style. Application is manually partitioned into the abstract PEs that compose the hardware platform.

#### SESAME (Simulation of Embedded System Architectures for Multilevel Exploration ) [162]

It is a modeling and simulation environment for system-level design based on the Y-chart design approach [122] which allows application and architecture to be modeled separately. The application model can be mapped onto the platform model and both are co-simulated via trace-driven simulation [163].

#### BIP (Behavior, Interaction, Priority) [22]

It is a component framework intended for rigorous system design. BIP allows the construction of composite hierarchically structured systems from atomic components characterized by their behavior and their interface. Components are composed by layered application of interactions and of priorities. Interactions express synchronization constraints between actions of the composed components while priorities are used to filter amongst possible interactions and to steer system evolution so as to meet performance requirements e.g. to express scheduling policies. Interactions are described in BIP as the combination of two types of protocols: rendez-vous, to express strong symmetric synchronization and broadcast, to express triggered asymmetric synchronization.

BIP has a rigorous operational semantics which has been implemented by specific execution engines for centralized, distributed and real-time execution. BIP is used as a unifying semantic model in a rigorous system design flow [21]. Rigor is ensured by two kinds of tools: verification tools such as D-Finder [29] for checking safety properties (and deadlock-freedom in particular) and source-to-source transformers [50], [43] that allow progressive refinement of (purely functional) application software towards platform-dependent implementations.

# **Chapter 3**

# Timed automata

In order to talk about systems behavior in a formal manner, it is necessary to represent them as some kind of mathematical structure. The simplest way to represent behavior is by means of automata or labelled transition system. These are simply graphs containing nodes and directed, labelled edges. Nodes represent the possible states of the system and edges (or transitions) represent activities as moves between two nodes.

In [70] authors have identified a handful of semantic concepts which are well-established in the context of computer-aided verification and modelling formalisms for discrete event systems:

- Action nondeterminism: From a given state several transitions may exist.

- **Probabilistic branching**: From a given state several transitions may exists and the choice is based on some probability distribution.

- Clocks: A way to represent real time constraints and to specify the dynamics of a model in relation to a physical, quantitive notion of time.

- Delay nondeterminism: allows one to leave the precise timing of events under specified.

- **Random variables**: give quantitative information about the likelihood of a certain event to happen within a given time frame.

Working with high level models, implies taking into account uncertainty in order to compensate for the lack of precision. Non-determinism can be modeled in many ways and labeled transition systems possess only action non-determinism. Other formalisms associate some kind of quantitative informations with action non-determinism.

Probabilistic automata have been used [170, 171, 169] for the purpose of modeling and analyzing asynchronous, concurrent systems with *discrete* probabilistic choice in a formal and precise way. Basically, a probabilistic automaton is a labeled transition system where the target of a transition is a probabilistic choice over several next states. Stochastic processes [79] is another formalism which is often used to represent the evolution of some random value, or system, over time. This formalism will be introduced in the next chapters.

In the present chapter we are interested in *timing uncertainty*. Timed automata [6] provide a theory for modeling and verification of real time systems. They provide the ability to constraint the execution of a transition to occur anywhere within a time interval. Timed automata introduce a dense non-determinism which is a very useful modeling feature when we have uncertain information about process durations. Other formalisms with the same purpose include timed Petri Nets [37], timed process algebra [165, 200, 156] and real time logics [9, 58].

We will present next, the timed automaton formalism, which will be used as a basis for our modeling framework presented in chapter 6.

#### **3.1** Clocks, time constraints, zones

We use  $\mathbb{Z}$  and  $\mathbb{R}$  to denote, respectively the integer and real numbers, while  $\mathbb{N}$  and  $\mathbb{R}+$  will stand for their respective non-negative restrictions. We will use  $\mathbb{R}+$  as the time domain on which clock variables range. We use  $\mathbb{R}_{\perp}$  to denote  $\mathbb{R}+\cup \perp$  were  $\perp$  is a special symbol meaning inactive or irrelevant. We extend the addition operation to  $\mathbb{R}_{\perp}$  by letting  $\perp +d = \perp$ .

#### **Clocks and Valuations**

Let  $C = \{c_1, ..., c_n\}$  be a finite set of variables called clocks, each ranging over  $\mathbb{R}_{\perp}$ . A clock valuation is a function  $v : C \to \mathbb{R}_{\perp}$  assigning to each clock  $c \in C$  its value v(c). The set of possible valuations of C is then  $\mathbb{R}^n_{\perp}$ . A clock c is said to be active in valuation v iff  $v(c) \neq \perp$ , otherwise it is inactive. In timed automata, clock valuations change due to two types of activities: time progress which happens inside a discrete state and clock assignment which take place during discrete transitions:

#### **Time progress**

Let d be a non-negative real. We say that clock valuation v' is the result of applying d-timeprogress to clock valuation v, denoted by v' = v + d, if for every clock c, v'(c) = v(c) + d. Note that by the definition of addition on  $\mathbb{R}_{\perp}$ , all the clocks inactive in v do not change their value while all the other clocks advance uniformly.

#### **Clocks assignment**

A clock assignment is a function  $\gamma : \mathbb{R}_{\perp} \to \mathbb{R}_{\perp}$  indicating a transformation of clock values which occurs during a transition.  $v' = \gamma(v)$  denotes the fact that v' is the result of applying assignment  $\gamma$  to clock valuation v. The type of assignments that we allow in the definition of timed automata is restricted to compositions of one or more of the following basic assignments:

- Resetting to zero:  $c_i = 0$

- Deactivation of a clock:  $c_i = \perp$

- Clock copying:  $c_i = c_j$

#### **Clock constraints**

Clock constraints are used to express the influence of clock values on the discrete dynamics (invariants and transition guards). We restrict ourselves to a family of constraints that we denote by  $\Psi_C$ , defined by the following grammar:

$$\psi ::= true \mid c_i \prec k \mid c_i - c_i \prec k \mid \psi \land \psi$$

where  $c_i, c_j \in C, k \in \mathbb{N}$  and  $\prec \in \{<, \leq, =, \geq, >\}$ .

#### **Timed zones**

Clock constraints define naturally the set of clock valuations that satisfy them. These are subsets of  $\mathbb{R}^n_+$ . Every constraint  $\psi \in \Psi_C$  is a conjunction of atomic constraints. Knowing that the set of valuations satisfying an atomic constraint defines a half-space, every constraint  $\psi \in \Psi_C$  will define a convex polyhedron which is the intersection of those half-spaces.  $Z_{\psi}$  denote this polyhedron and it is called the timed zone associated with  $\psi$ . The set of all the zones defined on C will be denoted  $Z_C$ . Since the half-spaces are either orthogonal ( $c_i \prec k$ ) or diagonal ( $c_i - c_j \prec k$ ) with  $k \in \mathbb{N}$ , the vertices of these polyhedra are integer points and there is a finite number of zones in any bounded subset of  $\mathbb{R}^n$ . The most important property of zones is that they can be canonically represented as matrices i.e. DBMs (Difference Bound Matrices) [78].

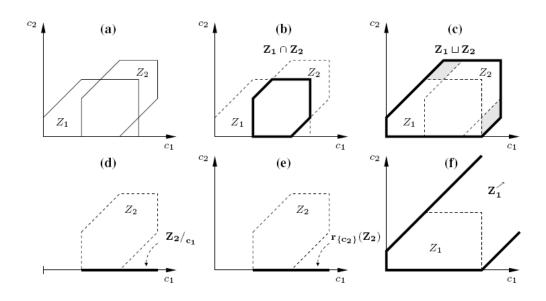

In the following we will define some useful operations on zones that will be used throughout this chapter. Let  $C' \subseteq C$  be a set of clocks, and let  $Z_1, Z_2 \in Z_C$  be two timed zones defined on C, then:

- $Z_1 \cap Z_2$  is the intersection of two zones  $Z_1$  and  $Z_2$ , which is a zone (fig3.1-(b))

- $Z_1 \sqcup Z_2$  is the convex hull of two zones  $Z_1$  and  $Z_2$  defined as

$Z_1 \sqcup Z_2 = \min\{Z \in Z_C \mid (Z_1 \subseteq Z) \land (Z_2 \subseteq Z)\}$ that is the smallest (in terms of inclusion) zone containing both  $Z_1$  and  $Z_2$ , see (fig3.1-(c)). Since zones are not closed under union,  $Z_1 \sqcup Z_2$  is used as an over-approximation of  $Z_1 \cup Z_2$ .

$Z^{\nearrow}$  is the forward projection of Z, i.e. all clock valuations that can result by applying time progress to element of Z (fig 3.1-(f)):

$$Z^{\nearrow} = \{ v \in V_C \mid \exists d \ge 0, v - d \in Z \}$$

- $\begin{aligned} Z_{/C'} & \text{ is the projection of a zone } Z \text{ on a clock subset } C' \subseteq C: \\ Z_{/C'} &= \{ v_{/C'} \mid v \in Z \} \\ \text{ This operation is related to clocks deactivation, (fig 3.1-(d))} \end{aligned}$

- $\gamma(Z)$  is the result of applying the clock assignment function  $\gamma$  to all element of Z:  $\gamma(Z) = \{\gamma(v) \mid v \in Z\}$

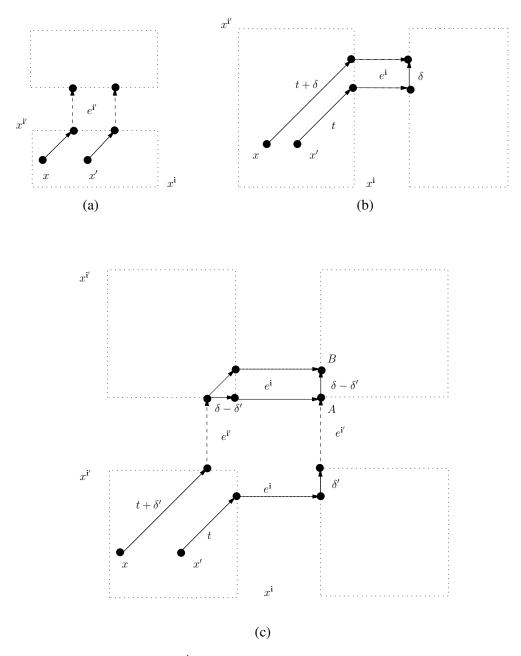

Figure 3.1: Operations on timed zones

All these operations can be computed efficiently on a DBM representation of timed zones. More details can be found, for example, in [203].

#### **3.2** Timed Automata: Syntax and Semantics

Timed automata have been introduced in [8, 6] as finite state *Büchi automata* (a variation of finite automaton that runs on infinite, rather than finite, inputs) extended with a set of real valued variables modeling clocks. Constraints on the clock variables are used to restrict the behavior of an automaton and Büchi accepting conditions are used to enforce progress properties. A simplified version, namely *Timed Safety Automata*, has been later introduced in [106] to specify progress properties using local invariant conditions.

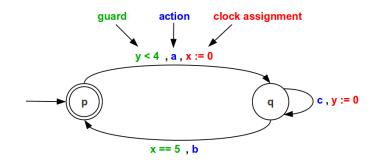

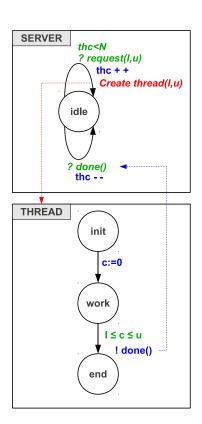

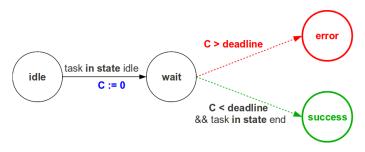

Figure 3.2: Example of timed automaton

A timed automaton is presented as a discrete structure which is essentially a finite automaton (i.e a graph containing a finite set of nodes or locations and a finite set of labeled edges) extended with clock variables. Locations are supposed to capture all information about the current status of the system, except for timing information. Edges represents events or transitions which change the discrete state of the system. Time progress takes place *inside* the discrete states and is not expressed explicitly in this structure. Actually, time passage is recorded using clocks. All clocks of the system increase synchronously at the same rate. These clocks can be set to zero, or deactivated when a transition is taken.

Clocks constraints are used to restrict the behavior of the automaton by forcing it to leave a state or forbidding it from taking a certain transition. In [174, 44] these constraints are associated with the transitions, while in [106] they are divided between states and transition. Constraints on states denote staying conditions (called invariant). The automaton may stay in a state (while the active clocks are progressing ) as long as the staying condition holds, otherwise it has to leave the state via one of the enabled transitions. Constraints on transitions are called *guards*, and a transition can be taken only if its guard constraints are satisfied.

**Definition 3.2.1.** (*Timed automaton*) A timed automaton is a tuple  $A = (Q, q_0, C, \Sigma, I, \Delta)$  where Q is a finite set of discrete states,  $q_0 \in Q$  is the initial state, C is a finite set of clocks and  $\Sigma$  is a finite set of labels.  $I \in Q \rightarrow \Psi_C$  is a function associating a staying condition (invariant) with every state q. The automaton is permitted to stay at q only as long as the clock constraint  $I_q$  is satisfied.

$\Delta \subseteq Q \times \Psi_C \times \Sigma \times \Gamma_C \times Q$  is the transition consisting of elements of the form  $e = (q, g, a, \gamma, q')$  where:

| $q,q' \in Q$        | are, respectively, the source and the target of the transition                          |