# Méthodologie de conception d'architectures reconfigurables dynamiquement pour des applications temps-réel

François Duhem

#### ▶ To cite this version:

François Duhem. Méthodologie de conception d'architectures reconfigurables dynamiquement pour des applications temps-réel. Systèmes embarqués. Univ. Nice-Sophia Antipolis, 2012. Français. NNT: . tel-01573906

#### HAL Id: tel-01573906 https://theses.hal.science/tel-01573906

Submitted on 10 Aug 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE DE NICE - SOPHIA ANTIPOLIS ECOLE DOCTORALE STIC

SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

### THESE

pour obtenir le titre de

#### Docteur en Sciences

de l'Université de Nice - Sophia Antipolis

Mention: Electronique

Présentée et soutenue par

François DUHEM

## Méthodologie de conception d'architectures reconfigurables dynamiquement pour des applications temps-réel

Thèse dirigée par Fabrice MULLER & Philippe LORENZINI

préparée dans l'équipe MCSOC de l'unité de recherche UMR 7248 - LEAT/CNRS

soutenue le 23 novembre 2012

#### Jury:

| Μ. | Serge Weber        | Professeur, LIEN                | Président du jury     |

|----|--------------------|---------------------------------|-----------------------|

| M. | Bertrand Granado   | Professeur, LIP6                | Rapporteur            |

| M. | Christophe Jégo    | Professeur, IMS                 | Rapporteur            |

| M. | François Verdier   | Professeur, LEAT                | Examinateur           |

| M. | Fabrice Muller     | Maître de conférences HDR, LEAT | Co-Directeur de thèse |

| M. | Philippe Lorenzini | Professeur, IM2NP               | Directeur de thèse    |

#### Résumé

La reconfiguration dynamique des FPGA, malgré des caractéristiques intéressantes, peine à s'installer dans l'industrie principalement pour deux raisons. Tout d'abord, les performances du contrôleur natif développé par Xilinx sont faibles et pourront résulter en un rapport entre le temps de reconfiguration et la période de la tâche trop important pour une implémentation dynamique. Ensuite, le développement d'une application reconfigurable dynamiquement demande un effort plus conséquent, notamment concernant l'ordonnancement des tâches. Il est en effet impossible d'évaluer une architecture et/ou un algorithme d'ordonnancement pour vérifier si l'application respectera bien ses contraintes de temps avant la phase d'implémentation.

Cette thèse s'inscrit dans ce contexte et propose des solutions aux problématiques énoncées précédemment. Dans un premier temps, nous présenterons FaRM, un contrôleur de reconfiguration dynamique capable d'atteindre les limites théoriques de la technologie grâce à un algorithme de compression efficient et une architecture optimisée. Ensuite, nous présenterons RecoSim, un simulateur d'architectures reconfigurables en SystemC modélisant à un haut niveau d'abstraction un tel système. Basé sur un modèle de coût du temps de reconfiguration avec FaRM, RecoSim permet notamment le développement et l'évaluation d'algorithmes d'ordonnancement, qui sont des éléments clés des architectures temps-réel. Finalement, nous montrerons comment ces premières contributions sont utilisées au sein de FoRTReSS, un flot d'exploration d'architectures intégré avec les outils de développement Xilinx.

Ces travaux ont été effectués dans le cadre du projet ANR ARDMAHN.

#### **Abstract**

Despite promising capabilities, FPGAs partial reconfiguration feature is not anchored in the industry yet, mostly for two reasons. First of all, Xilinx controller shows low performance and might introduce a large time overhead compared to the task period, incompatible with the use of partial reconfiguration. Also, developing such a dynamic application requires an extra design effort compared to a static solution for developing scheduling strategies. Indeed, it is impossible to evaluate an architecture and/or a scheduling algorithm to verify that real-time constraints are met before the implementation step.

This thesis offers solutions to the issues previously mentioned. We will first introduce FaRM, a Fast Reconfiguration Manager reaching partial reconfiguration theoretical limits thanks to an efficient compression algorithm and an optimised architecture. Then, we present RecoSim, a high-level SystemC simulator for reconfigurable architectures. It makes use of FaRM reconfiguration overhead cost model to allow for developing and verifying scheduling algorithms. Finally, we will show how these contributions are used inside FoRTReSS, a Flow for Reconfigurable archiTectures in Real-time SystemS compliant with Xilinx partial reconfiguration design flow.

This work was carried out in the framework of project ARDMAHN, sponsored by the French National Research Agency.

#### Remerciements

Je tiens tout d'abord à remercier mes collègues de bureau, en particulier Clément Foucher, Sébastien Icart, Laurent Brossier, Umberto Cerasani et Yannick Vaiarello avec qui ces trois années sont passées très vite.

Merci à Alexandra Loisel et Jérémy Belarbi qui ont contribué respectivement au développement de FaRM et de l'outil graphique de FoRTReSS durant leur stage.

Je remercie également Philippe Lorenzini pour son suivi tout au long de la thèse et ses encouragements.

Enfin, je tiens à remercier tout particulièrement Fabrice Muller qui m'a aidé, soutenu et surtout guidé tout au long de la thèse. C'est une vraie chance de l'avoir en tant que co-directeur de thèse et je le remercie de m'avoir donné l'opportunité de faire cette thèse.

## Table des figures

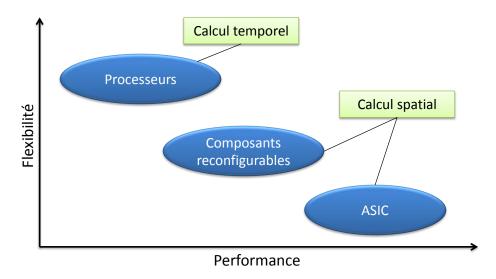

| 1.1  | Comparaison des approches pour les systèmes embarqués                     | 2  |

|------|---------------------------------------------------------------------------|----|

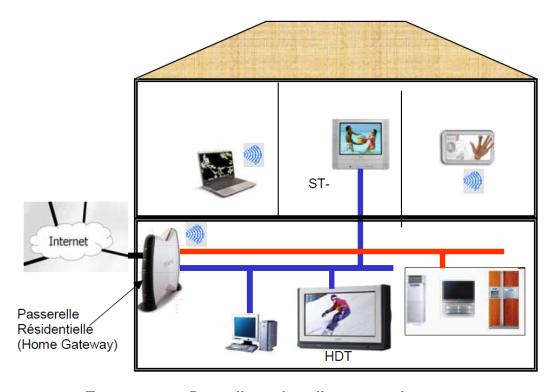

| 1.2  | Passerelle résidentielle et réseau domestique                             | 4  |

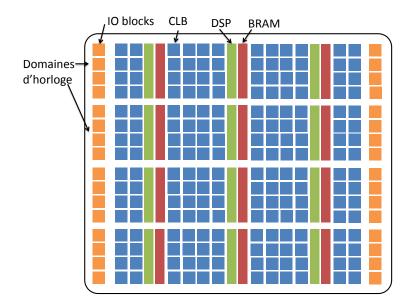

| 2.1  | Architecture des FPGA                                                     | 10 |

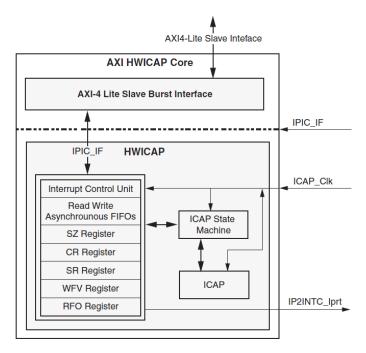

| 2.2  | Architecture du contrôleur d'ICAP Xilinx [1]                              | 13 |

| 2.3  | Comparaison de différents contrôleurs de reconfiguration [2]              | 13 |

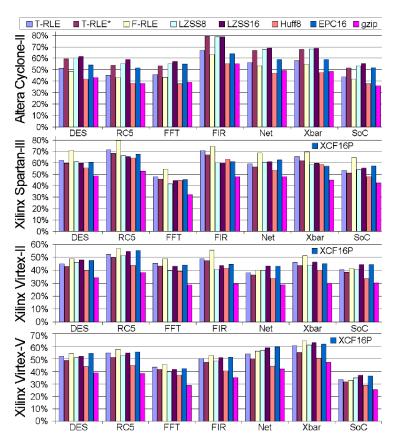

| 2.4  | Comparaison d'algorithmes de compression appliqués à différentes IP $[3]$ | 14 |

| 2.5  | Comparaison d'algorithmes de compression appliqués à différentes IP $[4]$ | 15 |

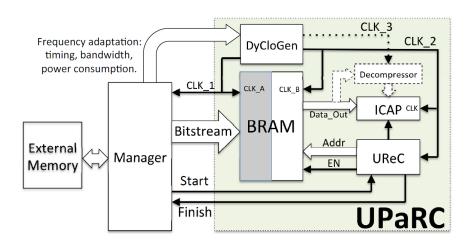

| 2.6  | Architecture du contrôleur UPaRC [5]                                      | 16 |

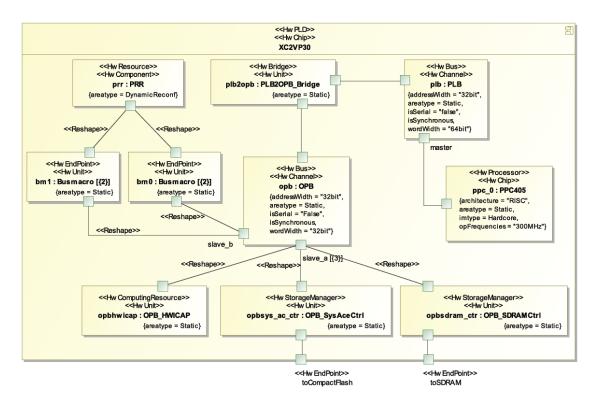

| 2.7  | Exemple de modélisation utilisant UML et MARTE [6]                        | 18 |

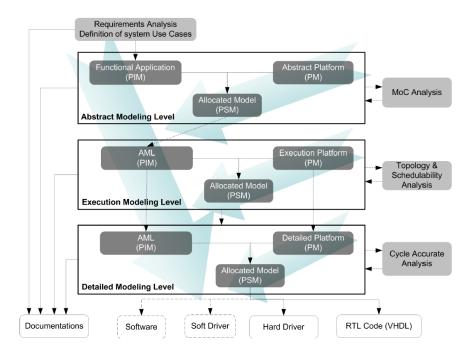

| 2.8  | La méthodologie MoPCoM [7]                                                | 19 |

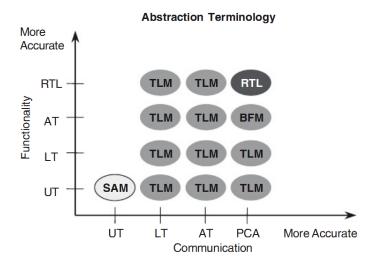

| 2.9  | Différents niveaux d'abstraction pour la modélisation SystemC [8]         | 19 |

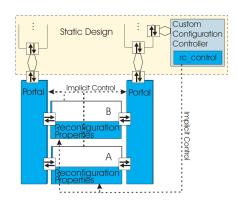

| 2.10 | Exemple de design utilisant ReChannel [9]                                 | 20 |

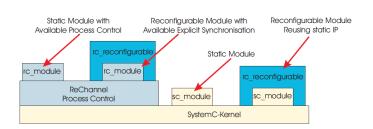

| 2.11 | Processus de contrôle de ReChannel [9]                                    | 20 |

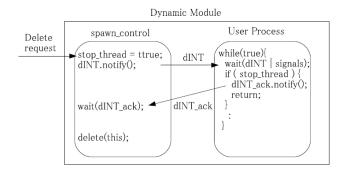

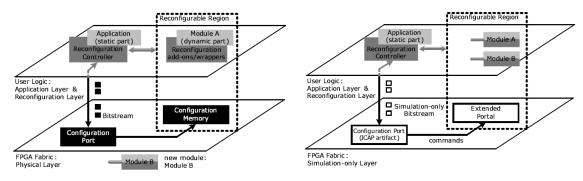

| 2.12 | Contrôle de modules dynamiques [10]                                       | 22 |

| 2.13 | Analyse structurelle de la reconfiguration dynamique [11]                 | 24 |

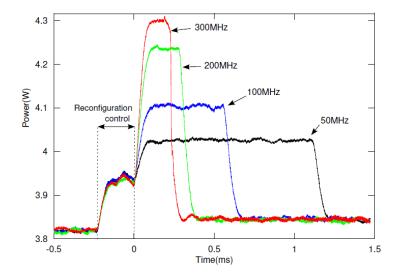

| 2.14 | Mesures de consommation d'UPaRC pendant la reconfiguration $[5]$          | 26 |

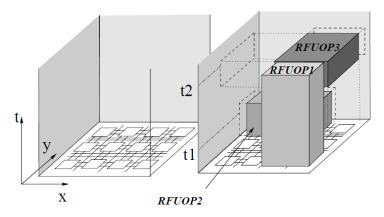

| 2.15 | Représentation des unités reconfigurables RFUOP [12]                      | 27 |

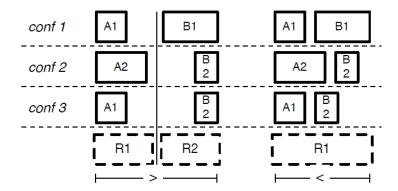

| 2.16 | Regroupement de tâches dans une zone reconfigurable [13]                  | 29 |

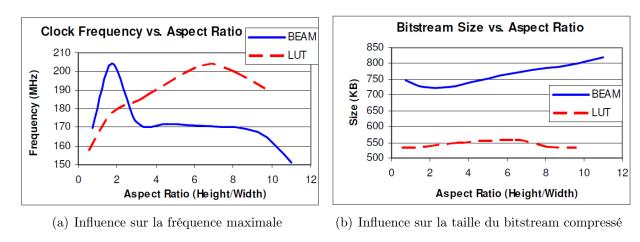

| 2.17 | Influence du rapport hauteur/largeur des zones reconfigurables [14] $$    | 30 |

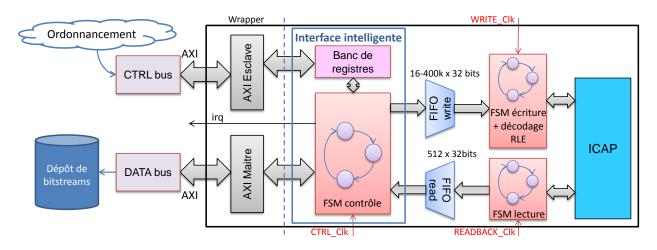

| 3.1  | Architecture de l'IP FaRM                                                 | 34 |

| 3.2  | Sous-système de configuration AXI utilisant FaRM                          | 35 |

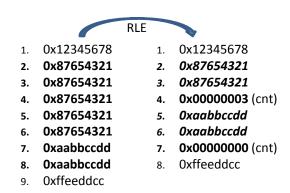

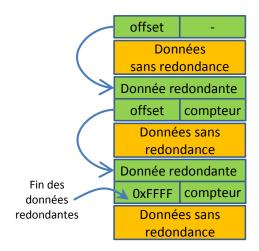

| 3.3  | Exemple de compression RLE                                                | 36 |

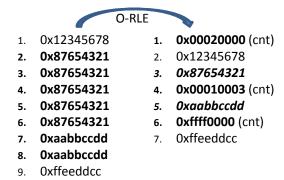

| 3.4  | Principe de la compression O-RLE                                          | 37 |

| 3.5  | Exemple de compression O-RLE                                              | 38 |

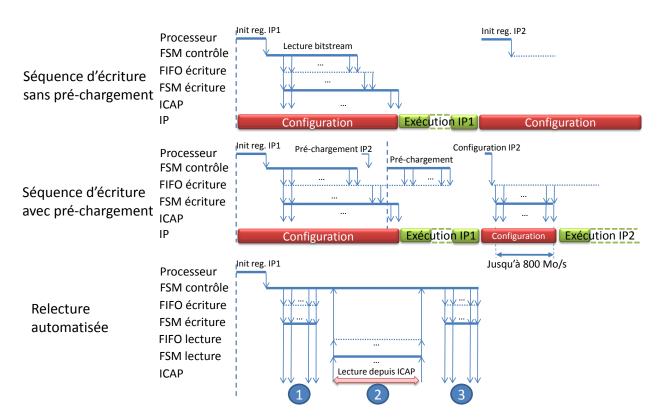

| 3.6  | Modes de fonctionnement de FaRM                                           | 40 |

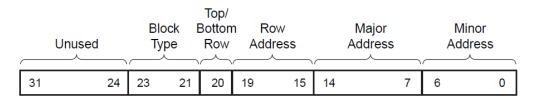

| 3.7  | Adressage des frames de configuration [15]                                | 41 |

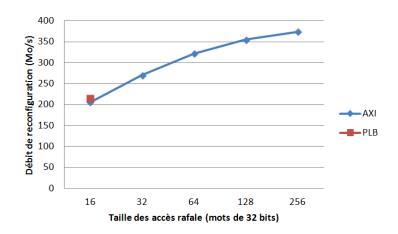

| 3.8  | Influence des tailles des accès rafales sur la reconfiguration            | 41 |

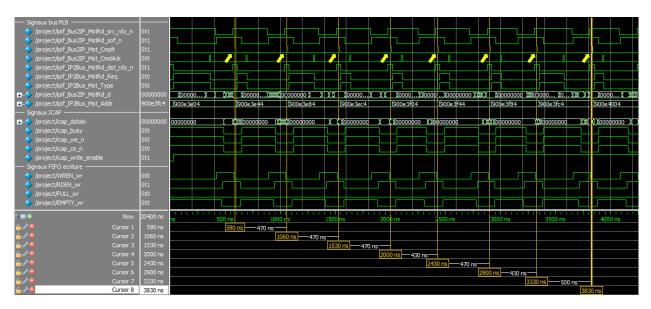

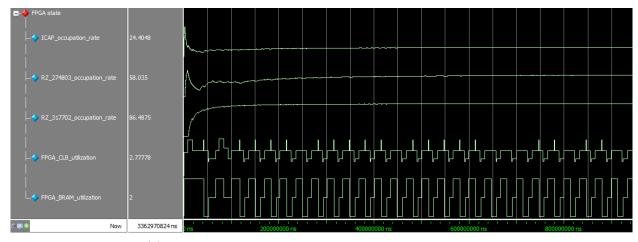

| 3.9  | Exemple de trace obtenue avec Chipscope Pro                               | 43 |

|      |                                                                           |    |

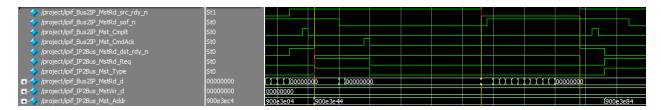

| 3.10 | Trace VCD représentant une transaction sur le bus PLB                 | 44 |

|------|-----------------------------------------------------------------------|----|

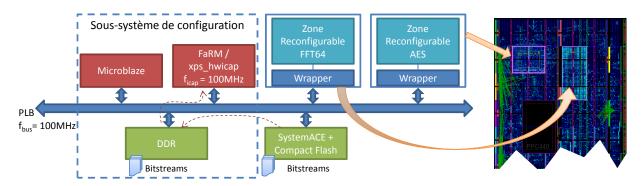

| 3.11 | Architecture de l'application de test AES/FFT64                       | 48 |

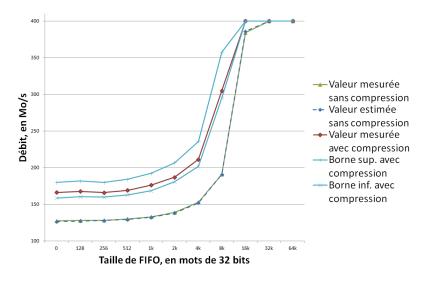

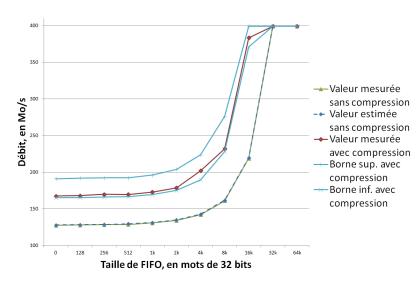

| 3.12 | Influence de la taille de la FIFO sur le débit de l'ICAP              | 51 |

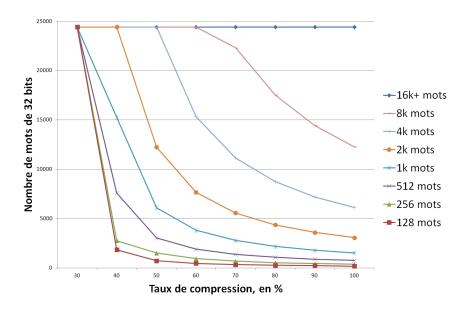

| 3.13 | Nombre de mots écrits au débit maximal                                | 52 |

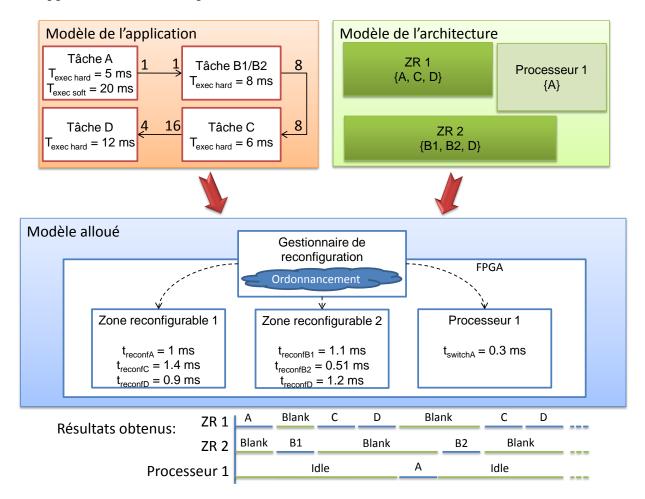

| 4.1  | Approche en Y de la modélisation avec RecoSim                         | 56 |

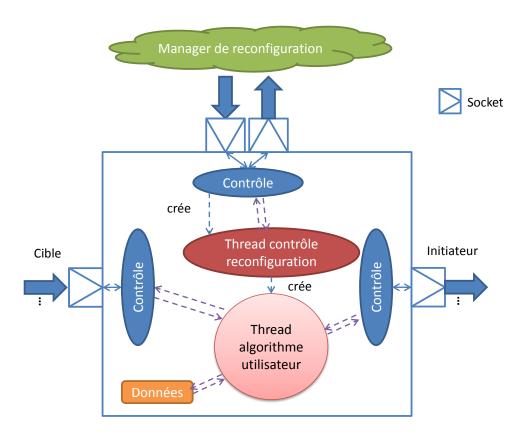

| 4.2  | Architecture d'un module reconfigurable                               | 59 |

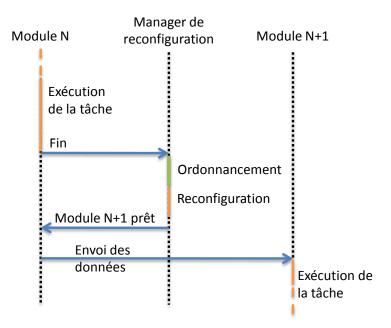

| 4.3  | Diagramme de séquences pour la fin d'exécution d'un module            | 61 |

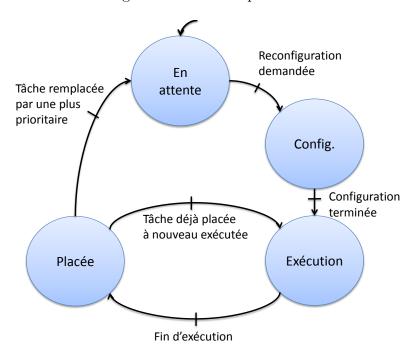

| 4.4  | Automate fini pour les changements d'état des tâches                  | 62 |

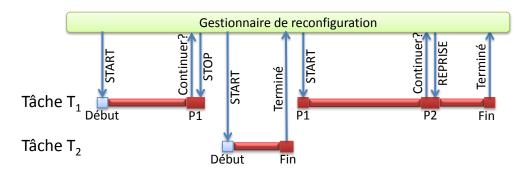

| 4.5  | Gestion de la préemption au sein de RecoSim                           | 64 |

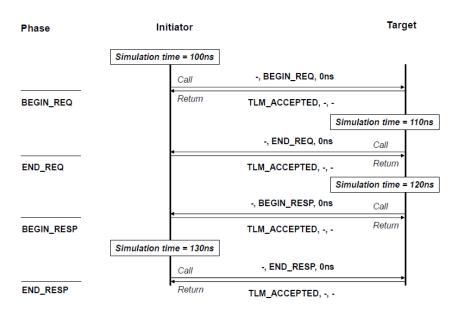

| 4.6  | Diagramme de séquence d'une transaction suivant le Base protocol [16] | 65 |

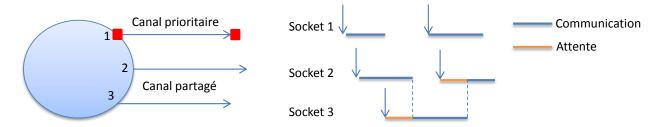

| 4.7  | Exemple de fonctionnement des canaux prioritaires                     | 67 |

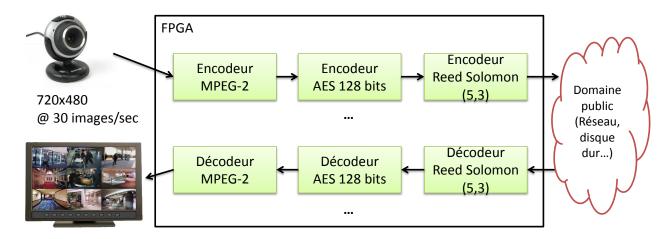

| 4.8  | Application de transmissions vidéo sécurisées                         | 68 |

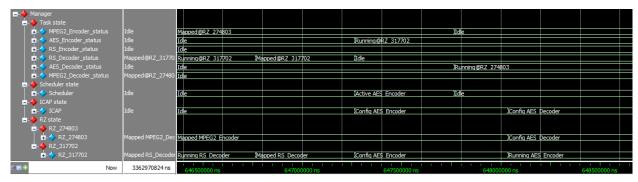

| 4.9  | Exemples de traces VCD                                                | 74 |

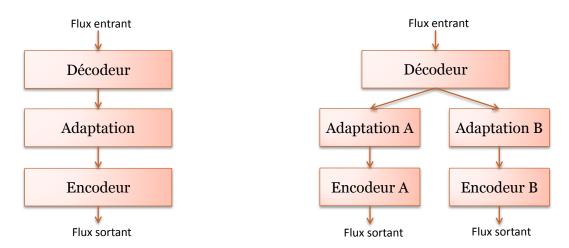

| 4.10 | Schémas-blocs des cas d'utilisation ARDMAHN                           | 76 |

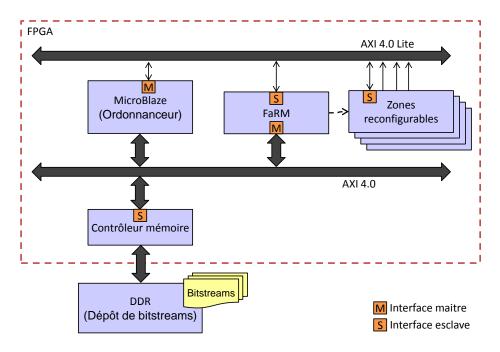

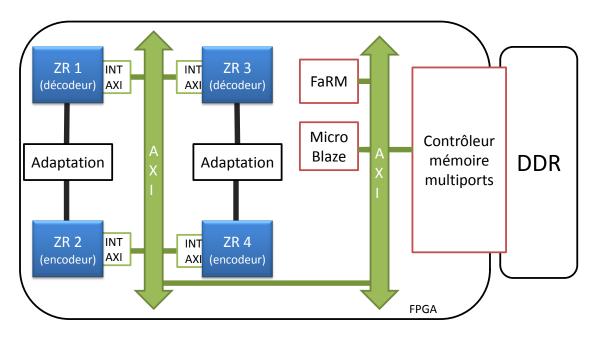

| 4.11 | Architecture du FPGA du démonstrateur ARDMAHN                         | 78 |

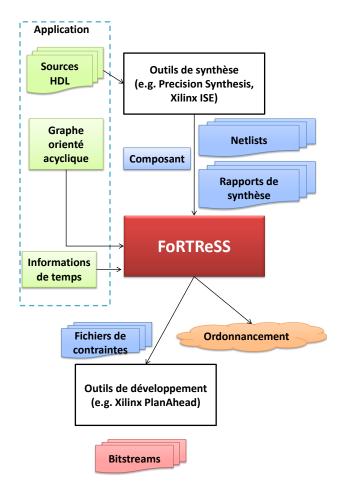

| 5.1  | L'approche FoRTReSS                                                   | 82 |

| 5.2  | Le flot FoRTReSS                                                      | 83 |

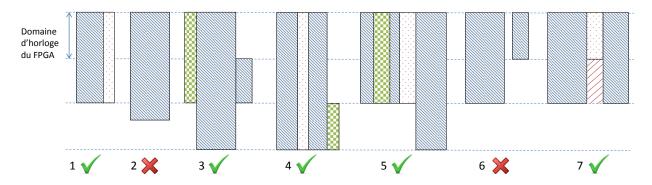

| 5.3  | Formes autorisées pour les zones reconfigurables                      | 84 |

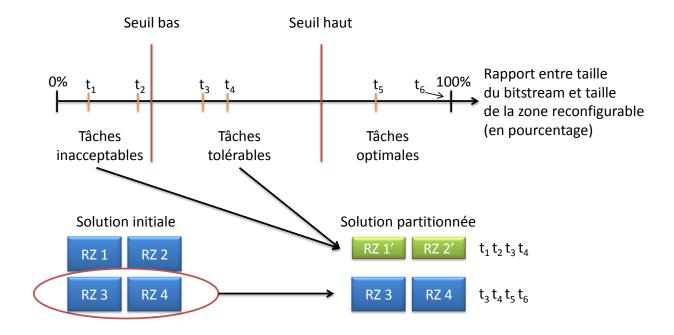

| 5.4  | Principe du partitionnement des tâches avec FoRTReSS                  | 87 |

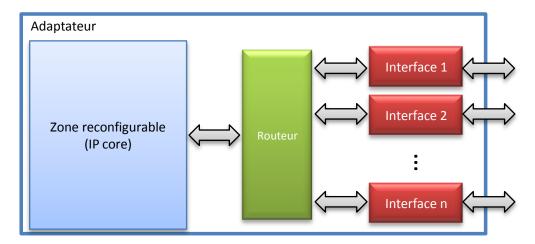

| 5.5  | Gestion des interfaces de la zone reconfigurable                      | 90 |

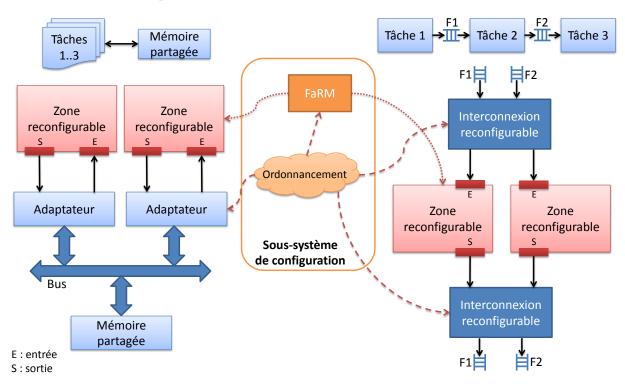

| 5.6  | Exemples d'architectures cibles                                       | 93 |

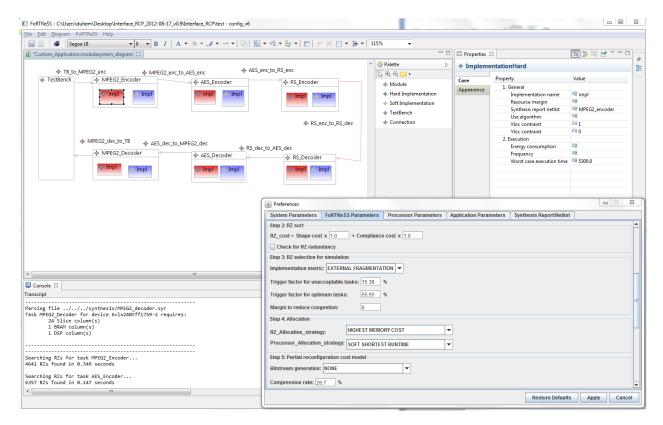

| 5.7  | Interface graphique de FoRTReSS                                       | 96 |

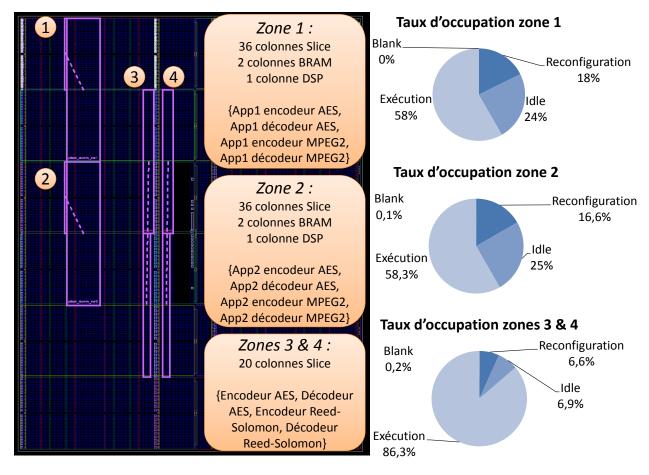

| 5.8  | Floorplan issu de FoRTReSS pour deux chaînes en parallèle             | 99 |

## Liste des tableaux

| 2.1  | Comparaison des principales approches de modélisation                                        | 24  |

|------|----------------------------------------------------------------------------------------------|-----|

| 3.1  | Comparaison de taux de compression pour différents algorithmes                               | 38  |

| 3.2  | Ressources contraintes par les zones reconfigurables                                         | 48  |

| 3.3  | Temps de reconfiguration et de relecture                                                     | 49  |

| 3.4  | Comparaison de FaRM avec l'HwICAP                                                            | 53  |

| 4.1  | Rapports de synthèse des tâches de l'application Secure Box                                  | 68  |

| 4.2  | Taille des zones reconfigurables optimales pour un FPGA Virtex-6                             | 70  |

| 4.3  | Résultats en surface de l'application Secure Box pour un FPGA Virtex-6                       | 71  |

| 4.4  | Temps d'exécution des tâches sur les zones reconfigurables                                   | 72  |

| 4.5  | Résultats en surface de l'application Secure Box après partitionnement $\ \ . \ \ . \ \ .$   | 72  |

| 4.6  | Temps d'exécution des tâches sur les zones reconfigurables après partitionnement             | 73  |

| 4.7  | Cas d'utilisation du démonstrateur ARDMAHN                                                   | 75  |

| 4.8  | Rapports de synthèse des tâches de l'application ARDMAHN                                     | 76  |

| 4.9  | Taille des zones reconfigurables optimales pour les tâches ARDMAHN                           | 78  |

| 4.10 | Résultats en surface de l'application ARDMAHN pour un FPGA Virtex-6                          | 78  |

| 5.1  | Paramètres de la détermination des zones reconfigurables                                     | 84  |

| 5.2  | Paramètres du tri des zones reconfigurables                                                  | 85  |

| 5.3  | Paramètres de la sélection des zones reconfigurables                                         | 88  |

| 5.4  | Paramètres de la sélection des processeurs                                                   |     |

| 5.5  | Paramètres de l'allocation                                                                   | 90  |

| 5.6  | Paramètres du modèle de coût                                                                 | 91  |

| 5.7  | Paramètres de la simulation                                                                  | 92  |

| 5.8  | Paramétrage de FoRTReSS pour l'application Secure Box                                        | 97  |

| 5.9  | Résultats en surface issus de FoRTReSS pour un FPGA Virtex-6 LX240T                          | 98  |

| 5.10 | Résultats en surface pour trois applications sur un FPGA Virtex-6 LX240T $\ensuremath{^{1}}$ | 101 |

| 5.11 | Taux de compression réels (en pourcentage de la taille initiale)                             | 102 |

|      |                                                                                              |     |

### Table des matières

| 1        | $\mathbf{Intr}$      | oduction 1                                                                                      |

|----------|----------------------|-------------------------------------------------------------------------------------------------|

|          | 1.1                  | Présentation des systèmes reconfigurables                                                       |

|          | 1.2                  | Le projet ARDMAHN                                                                               |

|          | 1.3                  | Contributions                                                                                   |

|          |                      | 1.3.1 FaRM                                                                                      |

|          |                      | 1.3.2 Recosim                                                                                   |

|          |                      | 1.3.3 Fortress                                                                                  |

|          | 1.4                  | Organisation du mémoire                                                                         |

| <b>2</b> | Éta                  | de l'art                                                                                        |

|          | 2.1                  | Présentation des concepts de la reconfiguration dynamique                                       |

|          |                      | 2.1.1 Architecture interne des FPGA                                                             |

|          |                      | 2.1.2 Contenu des fichiers de configuration                                                     |

|          |                      | 2.1.3 Sauvegarde de contexte et relecture                                                       |

|          |                      | 2.1.4 Flots de développement                                                                    |

|          | 2.2                  | Optimisation des performances de la reconfiguration dynamique                                   |

|          |                      | 2.2.1 Optimisation de l'architecture                                                            |

|          |                      | 2.2.2 Compression des bitstreams                                                                |

|          |                      | 2.2.3 Optimisation de l'ordonnancement                                                          |

|          | 2.3                  | Modélisation de la reconfiguration dynamique                                                    |

|          |                      | $2.3.1  \text{Mod\'elisation comportementale} \; . \; . \; . \; . \; . \; . \; . \; . \; . \; $ |

|          |                      | 2.3.2 Modèle de coût de la reconfiguration dynamique                                            |

|          | 2.4                  | Exploration d'architectures reconfigurables                                                     |

|          | 2.5                  | Conclusion                                                                                      |

| 3        | FaR                  | M : un contrôleur de reconfiguration dynamique pour l'optimisation                              |

|          | $\operatorname{des}$ | performances 33                                                                                 |

|          | 3.1                  | Notre approche                                                                                  |

|          |                      | 3.1.1 Architecture de FaRM                                                                      |

| .4<br>.5<br>.6<br>.1<br>.2<br>.3<br>.4<br>.4<br>.2<br>.3<br>.4<br>.4<br>.5       | Position Conclusion Conclusion Sim: a des a L'appre 4.1.1 4.1.2 4.1.3 4.1.4 Applied 4.2.1 4.2.2 Perspet Conclusion L'appre 5.1.1 5.1.2 5.1.3 Applied Résult 5.3.1 5.3.2 5.3.3 5.3.4 Perspet Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion  : un flot d'exploration d'architectures reconfigurables temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation ats Floorplanning et résultats de simulation Exploration d'architectures pour trois applications Validation finale Temps d'exécution de FoRTReSS ctives sion  a générale et perspectives | les :                                | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 80 es 81 . 82 . 92 . 95 . 95 . 97 . 98 . 99 . 101 . 102 . 103 |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|---------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| .4<br>.5<br>Recoour<br>.1<br>.2<br>.3<br>.4<br>PoR.<br>.1                        | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dynapplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurable as temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation ats Floorplanning et résultats de simulation Exploration d'architectures pour trois applications Validation finale Temps d'exécution de FoRTReSS ctives                                  | les :                                | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 80 es 81 . 82 . 92 . 95 . 95 . 97 . 98 . 99 . 101 . 102 . 103 |

| .4<br>.5<br>Recoour<br>.1<br>.2<br>.3<br>.4<br>PoR.<br>.1                        | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dynapplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurable as temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation ats Floorplanning et résultats de simulation Exploration d'architectures pour trois applications Validation finale Temps d'exécution de FoRTReSS ctives                                  | les :                                | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 80 es 81 . 82 . 92 . 95 . 95 . 97 . 98 . 99 . 101 . 102 . 103 |

| .4<br>.5<br>Recoour<br>.1<br>.2<br>.3<br>.4<br>PoR:<br>.1                        | Position Conclusion Conclusion Sim: r des a L'appre 4.1.1 4.1.2 4.1.3 4.1.4 Applied 4.2.1 4.2.2 Perspe Conclusion L'appre 5.1.1 5.1.2 5.1.3 Applied Résult 5.3.1 5.3.2 5.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurables temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation ats Floorplanning et résultats de simulation Exploration d'architectures pour trois applications Validation finale                                                                        | ami                                  | qu po                               | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80 es 81 . 81 . 92 . 95 . 95 . 95 . 97 . 98              |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4<br>PoR:<br>.1                    | Position Conclusion Conclusion Sim: r des a L'approprie 4.1.1 4.1.2 4.1.3 4.1.4 Applied 4.2.1 4.2.2 Perspet Conclusion L'approprie 5.1.1 5.1.2 5.1.3 Applied Résult 5.3.1 5.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | un simulateur d'architectures reconfigurables dynapplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion  : un flot d'exploration d'architectures reconfigurables temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation ats Floorplanning et résultats de simulation Exploration d'architectures pour trois applications                                                                                          | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 80 es 81 . 81 . 82 . 92 . 95 . 95 . 97 . 98                   |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4<br>PoR <sup>2</sup><br>ppl<br>.1 | Position Conclusion Conclusion Conclusion Sim: redes at L'appre 4.1.1 4.1.2 4.1.3 4.1.4 Applied 4.2.1 4.2.2 Perspet Conclusion L'appre 5.1.1 5.1.2 5.1.3 Applied Résult 5.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim  Approche en Y de la modélisation  Définition du module reconfigurable  Gestionnaire de reconfiguration  Communications et TLM  ations  Application Secure Box  Application ARDMAHN  ctives  sion  : un flot d'exploration d'architectures reconfigurables temps-réel  oche FoRTReSS  Le flot FoRTReSS  Architecture cible  Environnement graphique  ation  ats  Floorplanning et résultats de simulation                                                                                                                             | ami                                  | qu po                               | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80 es 81 . 81 . 92 . 95 . 95 . 95                        |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4<br>PoR1<br>.1                    | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim  Approche en Y de la modélisation  Définition du module reconfigurable  Gestionnaire de reconfiguration  Communications et TLM  ations  Application Secure Box  Application ARDMAHN  ctives  sion  : un flot d'exploration d'architectures reconfigurables temps-réel  oche FoRTReSS  Le flot FoRTReSS  Architecture cible  Environnement graphique  ation  ats                                                                                                                                                                       | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 73 . 79 . 80 es 81 . 82 . 92 . 95 . 95                                  |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4<br>PoR2<br>ppl                   | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurables temps-réel oche FoRTReSS Le flot FoRTReSS Architecture cible Environnement graphique ation                                                                                                                                                                                           |                                      | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 73 . 79 . 80 es 81 . 81 . 92 . 95 . 95                                  |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4<br>PoR2                          | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim  Approche en Y de la modélisation  Définition du module reconfigurable  Gestionnaire de reconfiguration  Communications et TLM  ations  Application Secure Box  Application ARDMAHN  ctives  sion  : un flot d'exploration d'architectures reconfigurables temps-réel  oche FoRTReSS  Le flot FoRTReSS  Architecture cible  Environnement graphique                                                                                                                                                                                   | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at  55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80 es  81 . 82 . 92 . 95                                |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4                                  | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim  Approche en Y de la modélisation  Définition du module reconfigurable  Gestionnaire de reconfiguration  Communications et TLM  ations  Application Secure Box  Application ARDMAHN  ctives  sion  : un flot d'exploration d'architectures reconfigurables temps-réel  oche FoRTReSS  Le flot FoRTReSS  Architecture cible                                                                                                                                                                                                            | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 73 . 79 . 80 es 81 . 81 . 92                                            |

| .4<br>.5<br>Recoour<br>.1<br>.2<br>.3<br>.4                                      | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurables temps-réel oche FoRTReSS Le flot FoRTReSS                                                                                                                                                                                                                                            | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 73 . 79 . 80 es 81 . 81                                                 |

| .4<br>.5<br>Reco<br>our<br>.1<br>.2<br>.3<br>.4                                  | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim  Approche en Y de la modélisation  Définition du module reconfigurable  Gestionnaire de reconfiguration  Communications et TLM  ations  Application Secure Box  Application ARDMAHN  ctives  sion  : un flot d'exploration d'architectures reconfigurables temps-réel  oche FoRTReSS                                                                                                                                                                                                                                                  | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80 es 81 . 81                                            |

| .4<br>.5<br>Recoour<br>.1<br>.2                                                  | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurables temps-réel                                                                                                                                                                                                                                                                           | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80 es                                                    |

| .4<br>.5<br>.4<br>.2<br>.3<br>.4                                                 | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives sion : un flot d'exploration d'architectures reconfigurable : un flot d'exploration d'architectures reconfigurable                                                                                                                                                                                                                                | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73 . 79 . 80                                                       |

| .4<br>.5<br>Reco<br>our<br>.1                                                    | Position<br>Conclusion<br>Conclusion<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position<br>Position | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN ctives                                                                                                                                                                                                                                                                                                                                                   | ami                                  | qu                                  | em                                                                  |                                     | . 53<br>. 54<br>at<br>. 55<br>. 55<br>. 56<br>. 64<br>. 67<br>. 73<br>. 79<br>. 80                                 |

| .4<br>.5<br><b>Reco</b><br><b>our</b><br>.1                                      | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN                                                                                                                                                                                                                                                                                                                                                          | ami                                  | <b>qu</b>                           | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 67 . 73                                                                 |

| .4<br>.5<br><b>Reco</b><br><b>our</b><br>.1                                      | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN                                                                                                                                                                                                                                                                                                                                                          | ami                                  | <b>qu</b>                           | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 67 . 67 . 73                                                                 |

| .4<br>.5<br>Reco<br>our<br>.1                                                    | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim Approche en Y de la modélisation Définition du module reconfigurable Gestionnaire de reconfiguration Communications et TLM ations Application Secure Box Application ARDMAHN                                                                                                                                                                                                                                                                                                                                                          | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67 . 73                                                                 |

| .4<br>.5<br><b>Reccour</b><br>.1                                                 | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ami                                  | <b>qu</b>                           | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64 . 67                                                                      |

| .4<br>.5<br><b>Reco</b><br>our                                                   | Position Conclusion Sim: r des a L'approprie 4.1.1 4.1.2 4.1.3 4.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a <b>mi</b>                          | qu                                  | em                                                                  |                                     | . 53 . 54 at 55 . 55 . 56 . 58 . 60 . 64                                                                           |

| .4<br>.5<br>Reco<br>our<br>.1                                                    | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ami                                  | qu                                  | em                                                                  |                                     | . 53 . 54  at  55 . 55 . 56 . 58 . 60                                                                              |

| .4<br>.5<br><b>Reco</b><br>our                                                   | Position Conclusion Sim: r des a L'approprie 4.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ami                                  | qu                                  | em                                                                  | uen                                 | . 53 . 54 at . 55 . 55 . 56 . 58                                                                                   |

| .4<br>.5<br><b>Reco</b><br>our                                                   | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna pplications temps-réel oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a <b>mi</b>                          | qu                                  | <br>em                                                              |                                     | . 53 . 54 at 55 . 55 . 56                                                                                          |

| .4<br>.5<br><b>Reco</b><br>our                                                   | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna<br>pplications temps-réel<br>oche RecoSim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ami                                  | qu                                  | <br>em                                                              | en                                  | . 53 . 54 . t . 55 . 55                                                                                            |

| .4<br>.5<br>Reco                                                                 | Position Conclusion Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | un simulateur d'architectures reconfigurables dyna<br>pplications temps-réel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br>ami                              | qu                                  | <br><br>em                                                          | ner                                 | . 53<br>. 54<br>nt<br><b>55</b>                                                                                    |