# Low-cost phase noise measurement with digital test resources

Stéphane David-Grignot

#### ▶ To cite this version:

Stéphane David-Grignot. Low-cost phase noise measurement with digital test resources. Micro and nanotechnologies/Microelectronics. Université Montpellier, 2015. English. NNT: 2015MONTS055. tel-01590614

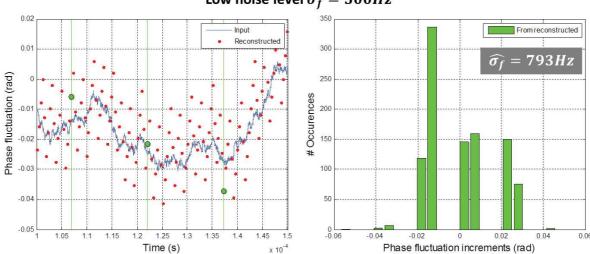

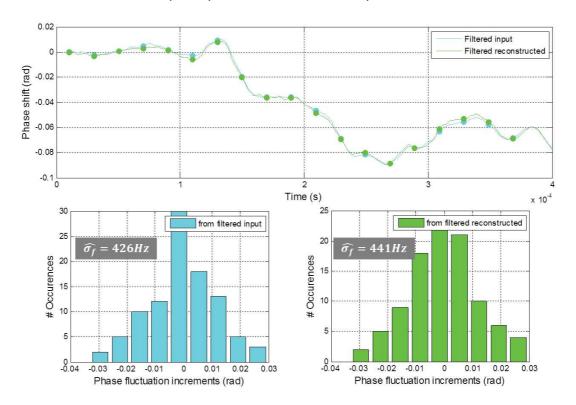

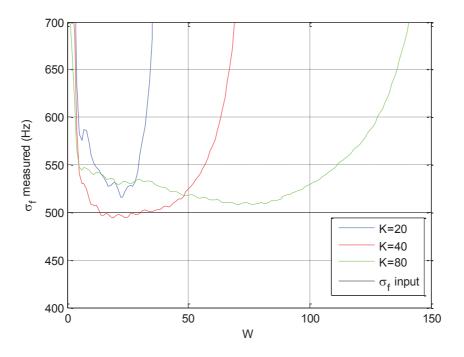

# HAL Id: tel-01590614 https://theses.hal.science/tel-01590614

Submitted on 19 Sep 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE Pour obtenir le grade de Docteur

Délivrée par Université Montpellier

Préparée au sein de l'école doctorale Information, Structure et Systèmes (I2S)

Et de l'unité de recherche Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM)

Spécialité : Systèmes Automatiques et Microélectronique (SYAM)

Présentée par Stéphane DAVID-GRIGNOT

Mesure de bruit de phase faible coût à l'aide de ressources de test numériques

Low-cost phase noise measurement with digital test resources

#### Soutenance prévue le 21 juillet 2015 devant le jury composé de :

Laurent Latorre,

Professeur, Université de Montpellier Directeur de thèse

Florence Azaïs,

Chargé de Recherche, CNRS-LIRMM Co-directrice de thèse

Salvador Mir,

Directeur de Recherche, CNRS-TIMA Rapporteur

Emeric de Foucauld,

CEA Rapporteur

Dominique Dallet, Professeur,

IMS, Bordeaux INP Examinateur

François Lefevre, Ingénieur,

NXP Semiconductors Examinateur

Pascal Nouet, Professeur,

Université de Montpellier Examinateur

# **Acknowledgments**

I would like to thank abundantly my PhD director Laurent Latorre as well as my employer from NXP Semiconductors, François Lefevre, for offering me the opportunity to work on this very entertaining and open subject and guiding my work so adequately. I also thank plentifully Florence Azais, my PhD co-supervisor, for her implication which led to numerous and rich contributions to this work. I would also acknowledge her extensive and impressive writing skills that permitted this study to be fruitfully translated into many publications.

All the team working on this thesis project is also very grateful to the CNFM (Coordination Nationale pour la Formation en Micro électronique et en nanotechnologies) for lending us their Automatic Test Equipment in Montpellier on which many of the most interesting experiments were carried out.

I would also like to thank Salvador Mir, Emeric de Foucauld and Dominique Dallet for their interest on my work and for accepting to be part of my dissertation committee.

I am also grateful to all the team and colleagues from the LIRMM in particular Regis Lorival and Beatrice Pradarelli for their inestimable help on the automated test equipment without which lots of the most interesting hardware results would have been far more difficult to obtain. I also thank Serge Bernard and Pascal Nouet for following the evolution of my thesis work.

I will also thank Alain Jean-Marie for his valuable formation and help on stochastic model, as well as Thierry Gil and Gilles Sassatelli for their advices on FPGA. I equally thank exterior professors Monique Jeanblanc and François Vernotte as well as pseudo-named Norbert from the Stackexchange website for their generous expertise on technical details.

Finally I am eternally grateful to my parents for providing me with a good education path, supporting my choices and generally encouraging me in my life.

# **Table of content**

| Ack | nowl    | edgm   | ents                                                                             | 3   |

|-----|---------|--------|----------------------------------------------------------------------------------|-----|

| Ger | neral i | introd | duction                                                                          | 7   |

| Cha | pter    | 1.     | Context and state of the art                                                     | 9   |

| 1   | 1       | Indu   | strial testing                                                                   | 9   |

|     | 1.1.    | 1      | Generalities                                                                     | 9   |

|     | 1.1.    | 2      | Case of analog/RF circuits                                                       | 10  |

| 1   | 2       | Phas   | se noise testing                                                                 | 10  |

|     | 1.2.    | 1      | Phase noise definition                                                           | 10  |

|     | 1.2.    | 2      | Prior work on phase noise testing                                                | 12  |

|     | 1.2.    | 3      | Current practice for industrial phase noise testing                              | 17  |

| 1   | 3       | The    | sis objective and positioning                                                    | 18  |

| Cha | pter    | 2.     | A phase noise model                                                              | 20  |

| 2   | 1       | Phas   | se noise as a Brownian motion                                                    | 20  |

|     | 2.1.    | 1      | Phase fluctuation model                                                          | 20  |

|     | 2.1.    | 2      | Standardizing factor                                                             | 21  |

|     | 2.1.    | 3      | Hertz: a unit amongst others                                                     | 21  |

|     | 2.1.    | 4      | Validation of model in Matlab <sup>®</sup>                                       | 21  |

| 2   | 2       | Phas   | se noise on hardware signals                                                     | 23  |

|     | 2.2.    | 1      | Experimental setup                                                               | 23  |

|     | 2.2.    | 2      | Validation on practical devices                                                  | 28  |

| 2   | 3       | Rela   | tionship between injected PN in time domain and measured PN in frequency domain  | 130 |

| 2   | .4      | Con    | clusion                                                                          | 36  |

| Cha | pter    | 3.     | First method: phase noise estimation based on instantaneous frequency estimation | 37  |

| 3   | 3.1     | Back   | ground on frequency estimation                                                   | 37  |

|     | 3.1.    | 1      | Frequency estimation from 1-bit capture                                          | 37  |

|     | 3.1.    | 2      | Discretization quantum                                                           | 38  |

|     | 3.1.3   |        | Running average filtering                                                        | 39  |

|     | 3.1.    | 4      | Error on threshold level                                                         | 40  |

| 3   | 3.2     | Stat   | istical dispersion on instantaneous frequency estimations                        | 40  |

|     | 3.2.    | 1      | Standard deviation                                                               | 40  |

|     | 3.2.    | 2      | Mean Absolute Deviation (MAD)                                                    | 42  |

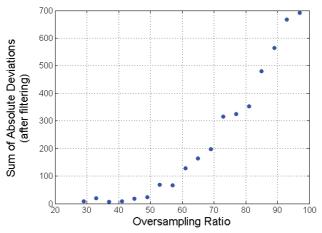

|     | 3.2.    | 3      | Considerations for sampling ratio setting                                        | 43  |

|     | 3.2.    | 4      | Summary of proposed digital technique                                            | 45  |

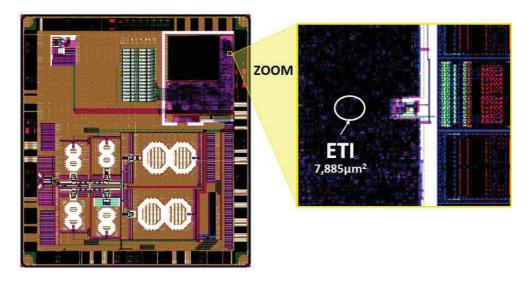

| 3.  | .3     | Integrated module                                                                   | 46 |

|-----|--------|-------------------------------------------------------------------------------------|----|

|     | 3.3.2  | 1 Integrated module overview and principle                                          | 46 |

|     | 3.3.2  | 2 Implementation                                                                    | 48 |

| 3.  | .4     | Preliminary experimental results                                                    | 52 |

|     | 3.4.2  | 1 Experimental setup                                                                | 52 |

|     | 3.4.2  | 2 Results                                                                           | 53 |

| 3.  | .5     | Additional Filtering                                                                | 54 |

|     | 3.5.2  | 1 Origin of Digital Technique Limitation                                            | 54 |

|     | 3.5.2  | 2 Jitter or voltage noise?                                                          | 57 |

|     | 3.5.3  | 3 Improved Digital Technique                                                        | 58 |

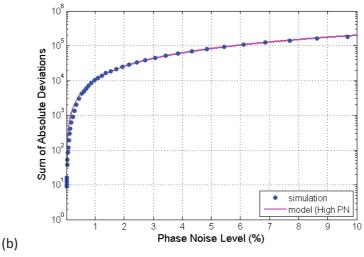

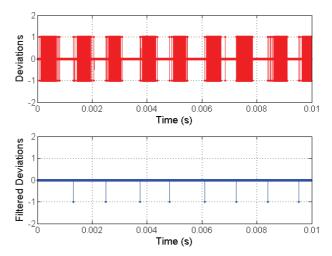

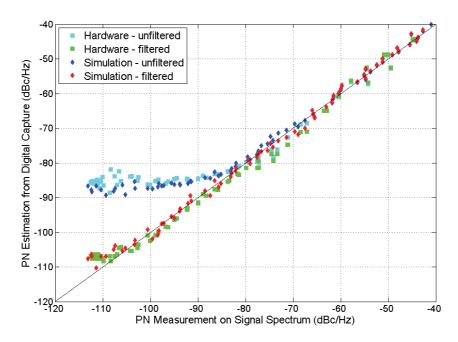

| 3.  | .6     | Experimental results                                                                | 63 |

|     | 3.6.2  | 1 Filter validation                                                                 | 63 |

|     | 3.6.2  | PN Hardware Measurements                                                            | 65 |

| 3.  | .7     | Conclusion                                                                          | 65 |

| Cha | pter 4 | 4. Second method: phase noise estimation based on phase fluctuation reconstruction. | 68 |

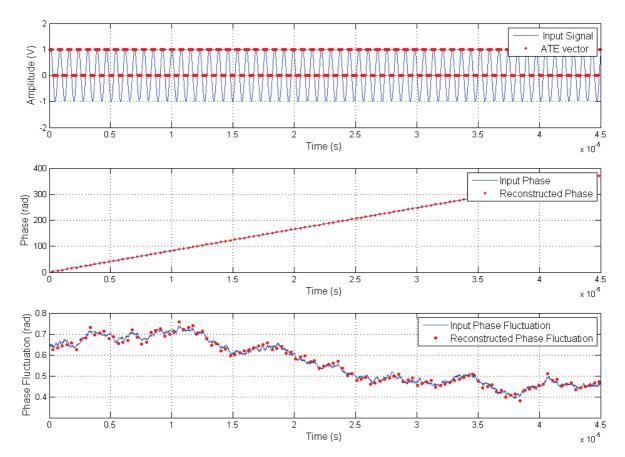

| 4   | .1     | Theoretical background                                                              | 68 |

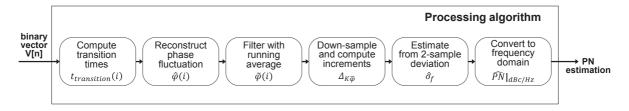

| 4.  | .2     | Algorithm                                                                           | 69 |

|     | 4.2.2  | 1 Phase fluctuation reconstruction                                                  | 69 |

|     | 4.2.2  | 2 Standard deviation of phase fluctuation increments                                | 71 |

|     | 4.2.3  | ·                                                                                   |    |

|     | 4.2.4  | 4 Other approaches                                                                  | 78 |

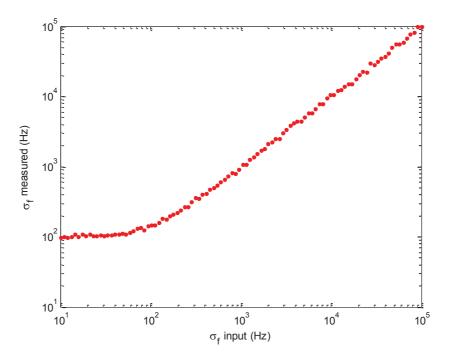

| 4.  | .3     | Performance of the measurement process based on Allan deviation                     | 80 |

|     | 4.3.2  | 1 Minimum phase noise level measurable                                              | 80 |

|     | 4.3.2  | 2 Measurement variability                                                           | 84 |

| 4.  | .4     | Experimental results                                                                | 88 |

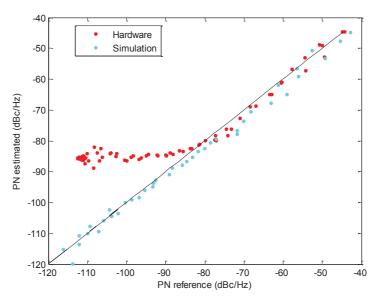

|     | 4.4.2  | 1 On synthesized signals                                                            | 88 |

|     | 4.4.2  | On industrial devices                                                               | 89 |

|     | 4.4.3  | On industrial production line                                                       | 90 |

| 4   | .5     | Conclusion                                                                          | 92 |

| Cha | pter 5 | 5. On chip implementation                                                           | 93 |

| 5.  | .1     | On chip algorithm                                                                   | 93 |

|     | 5.1.3  | 1 Processing only integers                                                          | 93 |

|     | 5.1.2  | 2 Semi-pipelined implementation                                                     | 94 |

|     | 5.1.3  | 3 Modular arithmetic                                                                | 95 |

|       | 5.1.4   | 4      | From digital signature to PN value                | 97  |

|-------|---------|--------|---------------------------------------------------|-----|

|       | 5.1.5   | 5      | Area estimation                                   | 97  |

| 5.    | .2      | FPG    | A implementation                                  | 98  |

| 5.    | .3      | Ехре   | erimental results                                 | 98  |

|       | 5.3.3   | 1      | Measurements on synthesized signal                | 98  |

|       | 5.3.2   | 2      | Measurement on NXP silicon tuner                  | 101 |

| 5.    | 4       | Con    | clusion                                           | 103 |

| Gen   | eral d  | concl  | usion                                             | 104 |

| Bibli | iogra   | phic r | references                                        | 106 |

| Pub   | licatio | ons    |                                                   | 112 |

| Pa    | apers   | S      |                                                   | 112 |

| Pa    | atent   |        |                                                   | 112 |

| List  | of Ta   | bles.  |                                                   | 113 |

| List  | of Fig  | gures  |                                                   | 113 |

| Ann   | ex      |        |                                                   | 118 |

| 1.    | St      | tocha  | stic model                                        | 118 |

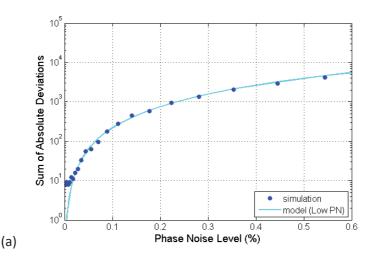

|       | 1.1.    | G      | eneral Behavior                                   | 118 |

|       | 1.2.    | Н      | igh level noise                                   | 120 |

|       | 1.3.    | Lo     | ow level noise without filter                     | 125 |

|       | 1.4.    | Lo     | ow phase noise level with filter                  | 129 |

| 2.    | . Al    | lgorit | hms                                               | 134 |

|       | 2.1.    | Si     | gnal Generation In simulation in Matlab           | 134 |

|       | 2.2.    | Al     | llan Variance Measurement In simulation in Matlab | 135 |

|       | 2.3.    | Si     | mulation Example in Matlab                        | 136 |

|       | 2.4.    | In     | tegrated module in Verilog                        | 136 |

### **General introduction**

With the development of communication and wireless applications, analog and radio frequency (RF) functions have become an essential part of electronic systems. With the efforts of the last decades, we today benefit from solutions that allow design and fabrication of these analog functions with interesting features concerning size, power and operating frequency. As to answer the mass market demand, the main challenge to which semiconductor founders are confronted is the production cost of these circuits. The cost not only includes the cost of fabrication of the circuit but the cost of testing as well. Indeed this step of the process is essential to guarantee the quality of devices delivered to the client. This context has motivated the study on which focuses this thesis: test cost reduction for analog/RF circuits.

This thesis is a collaboration between the LIRMM (Laboratory of Computer science, Robotics and electronics of Montpellier) and NXP Semiconductors, one of the world leading manufacturers of analog/RF integrated circuits. More precisely the study focuses on complex RF devices, such as silicon tuners, on which a lot of time-consuming RF tests should be performed to check the functionality and the specifications of the device. One of the most important tests is checking the phase noise of the analog/RF output signal. This specification parameter is linked to the product sensitivity, specifically at low reception levels. Measuring phase noise requires expensive digitizers to capture the analog signal and then perform signal analysis (FFT). Moreover the quantity of digitizers is limited per industrial tester, so multi-site efficiency is reduced.

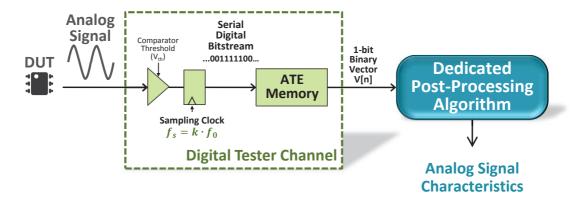

The approach here is to use cheaper digital resources instead of expensive high-performance RF channels of the automatic test equipment (ATE). These digital resources can either be provided by the test equipment or can be integrated on-chip. The main idea is to perform a binary capture of the analog signal under test using the simple comparator available in a standard digital tester channel. Signal characteristics are then computed from this binary vector using specifically developed algorithms, in particular the phase noise level of the signal under test.

The first chapter describes the constraints associated with industrial testing in high volume and introduces several options to reduce the cost of phase noise measurement in the context of production testing with a state of the art of proposed solutions. The approach taken in this thesis is then justified.

The second chapter presents a mathematical model of phase noise. This model is implemented in simulation and is compared to hardware measurements. A hardware solution to synthesize a signal with a controlled phase noise level is also presented.

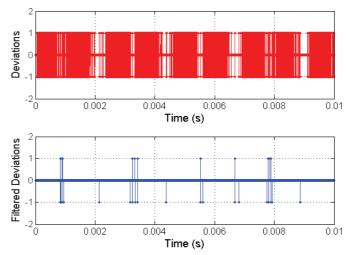

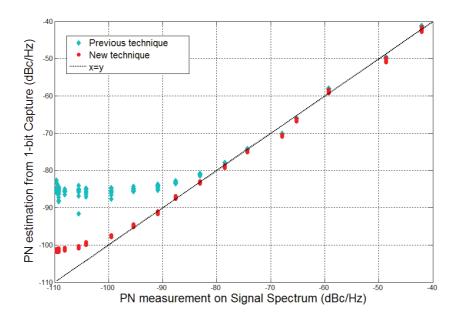

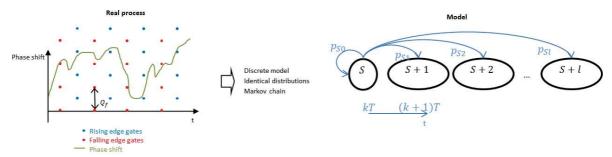

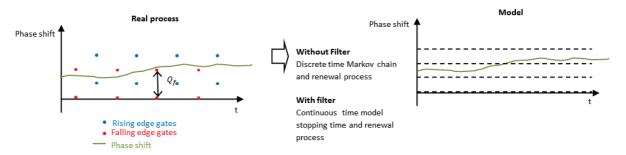

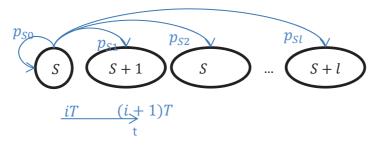

A first solution for phase noise evaluation based on 1-bit capture is presented in chapter three. This solution relies on instantaneous frequency estimation and analysis of the deviation of instantaneous frequency estimates. The technique is validated in simulation and an on-chip implementation is proposed. Hardware experiments are also presented, which demonstrate the validity of the proposed approach but also reveal a limitation in case of very low phase noise level due to the sensitivity of the technique to amplitude noise. An additional filtering step is then designed in order

to discriminate deviations induced by amplitude noise from deviations induced by phase noise. This permits to extend the valid measurement range, but imposes specific constraints on the sampling process.

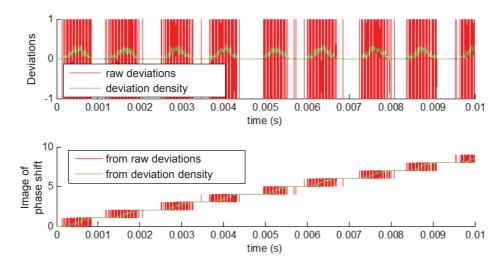

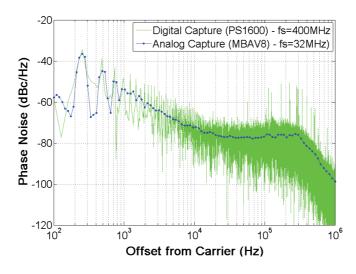

A second algorithm for phase noise evaluation based on 1-bit capture is proposed in chapter four. It relies on instantaneous phase reconstruction rather than instantaneous frequency estimation. This solution is much more robust to amplitude noise and does not suffer from the specific constraints on the sampling process encountered in the previous chapter. Moreover this new technique not only permits to measure the phase noise level at a specific frequency offset, but it also gives access to the frequency-domain characteristics of phase noise. Simulation results as well as a stochastic model and hardware measurements are presented.

The fifth chapter presents an on-chip implementation of this last solution. This built-in self-test solution permits to lower even more the test cost because the digital channel of the automatic test equipment does not have to be as performant as when performing the acquisition. It also allows to measure phase noise during the life cycle of the chip, opening up new possibilities for chip designers.

Finally in the conclusion, the main contributions of this thesis are summarized and perspectives for future work are presented.

# Chapter 1. Context and state of the art

#### 1.1 Industrial testing

#### 1.1.1 Generalities

Test of microelectronic circuits is an essential step in the fabrication process and marketing of new technology products. It aims in guaranteeing the good operation of the system. The test affects two main phases of the fabrication cycle of the integrated circuit: the characterization test of the device, in order to produce its datasheet, and the production test that is performed on every single product in order to guaranty its performance. The two objectives of these tests are quite different.

The characterization test is made on the first samples of the product, coming out of foundry. It validates the conception of the circuit for its operations and specifications. A whole battery of tests is applied to the circuit in different conditions to identify the limits of the product and compare them to the specifications. This characterization test can necessitate high performance equipment and the time of testing is not a primary constraint.

Once the characterization is done, the production of the circuit at high volume begins. Each circuit out of the production line has to be tested to guarantee it is correctly operational. Because of the very high number of fabricated devices, typically several millions a year, and the competitive environment, the time and cost of test is a primary constraint. Effective production test flow has to be cheap, fast and reliable to detect faulty circuits

Test is actually involved in different stages all along the production line of a system. The circuit is first tested at the wafer-level then it is tested once packaged. Once the circuit shipped to the client the system is tested with the circuits mounted on a PCB board. It is important to limit the impact of losses on the global cost. Table 1.1 is an illustration of the replacement cost at each stage of the system integration [1].

| Detection level           | Replacement cost |

|---------------------------|------------------|

| On wafer                  | 0.1              |

| Packaged circuit          | 1                |

| PCB board                 | 10               |

| System in production line | 100              |

| Shipped system            | 1000             |

Table 1.1 Replacement cost with detection level in the integration process

In the end, the cost of testing represents a large part, up to 50%, of the production cost. It is important to develop solutions to limit the testing cost. The solutions for cost reduction are generally focused over 3 targets:

- Test time reduction

- Cheap instrumentation

- Parallelization of testing

Over years, efficient solutions have been developed for digital circuits thanks to structural test approaches, design for test (DFT) and built in self-testability (BIST). This is not the case for analog and RF circuits.

#### 1.1.2 Case of analog/RF circuits

Analog/RF circuits are usually tested with a specification-oriented approach, which consists in measuring the circuit performances and comparing the measured values with specification tolerance limits. This approach offers good test quality but suffers from very high test cost. Several factors contribute to this cost.

First testing time is a critical issue. Indeed, there are usually a high number of specifications to verify which often require different specific test configurations. Measurements are therefore performed sequentially, resulting in long test times. As an example in [2], the test time for analog/RF blocks represents 57% of the total test time, while the test time for memory and digital blocks only represent 2% and 11% respectively.

Second the measurement of analog/RF performances necessitates the use of an Automatic Test Equipment (ATE) equipped with specific dedicated resources. Ranked from the most expensive to the cheapest ones, we find:

- RF resources

- Mixed-signal resources

- Analog resources

- DC measurements

- Digital resources

RF/MS options constitute around 55% of tester cost. A digital channel costs 50 times less than a RF channel. It is clear that the use of specific dedicated resources is a major contributor of the overall test cost. As an example in [3], the test of RF functions represents more than 40% of the testing cost of the SOC, mainly because of the required dedicated resources.

Finally it should be highlighted that due to their high cost, analog/RF resources are usually available in small quantity, limiting the possibility to reduce the testing cost through multi-site testing.

In this context, there is therefore a strong demand in developing test solutions for analog and RF circuits applicable with low-cost test equipment and compatible with multi-site test implementation.

#### 1.2 Phase noise testing

#### 1.2.1 Phase noise definition

Phase noise is a key element in many RF and radio-communication systems as it can significantly affect the performance of systems. For radio receivers, phase noise on the local oscillators within the system can affect specifications such as reciprocal mixing and the noise floor. For transmitters, it can affect the wideband noise levels that are transmitted. Additionally it can affect the bit error rate on systems using phase modulation. Phase noise is also important for many other systems including RF

signal generators, where very clean signals are required to enable the generator to be used as a reference source.

Phase noise refers to random short term fluctuations that affect the nominal frequency of a periodic signal. Note that phase noise and timing jitter are both ways of describing the same parameter. Phase noise describes the performance in the frequency domain, whereas jitter describes the performance in the time domain.

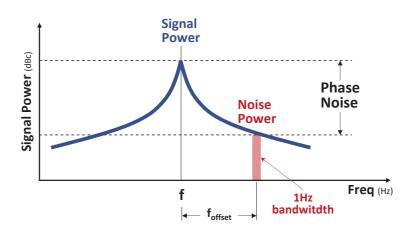

In the frequency domain, phase fluctuations manifest themselves as sidebands that appear on either side of the fundamental tone in the signal power spectrum, as illustrated in figure 1.1a. The phase noise may be specified in a number of ways, but the most common one is to look at the noise level at a given point. Phase noise is typically measured in dBc/Hz and corresponds to the noise power contained in a 1 Hz bandwidth located at a given offset from the carrier, relative to the carrier power.

#### a) Signal power spectrum

#### b) Phase noise spectrum

Figure 1.1 Frequency-domain representations of phase noise

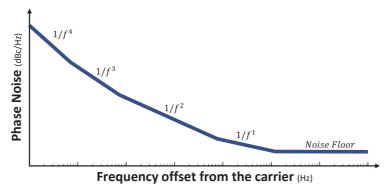

For a complete phase noise specification, several points will be measured to give an indication of the frequency domain characteristics. This leads to the phase noise spectrum illustrated in figure 1.1.b, in which the phase noise level is plotted as a function of the frequency offset from the carrier. Different phase noise sources can be identified on this spectrum, looking at the asymptotic behavior.

Indeed there are various origins for phase noise, and therefore various phase noises with corresponding power laws. Each phase noise has its response in the frequency domain. Each one can be identified by the slope  $S_{\omega}$  of its phase spectrum or by the slope  $S_{\nu}$  of its frequency spectrum.

In the total noise power, the frequency spectrum corresponds to the sum of the different noises contributions, weighted with their power coefficient:

$$S_{y} = \sum_{\alpha=-2}^{+2} h_{\alpha} f^{\alpha} \tag{1}$$

| $S_{y}(f)$     | $S_{\varphi}(f)$ | Noise type     | Origin               |

|----------------|------------------|----------------|----------------------|

| $h_{-2}f^{-2}$ | $b_{-4}f^{-4}$   | Random walk FM | Environment          |

| $h_{-1}f^{-1}$ | $b_{-3}f^{-3}$   | Flicker FM     | Resonator            |

| $h_0$          | $b_{-2}f^{-2}$   | White FM       | Thermal noise        |

| $h_1f$         | $b_{-1}f^{-1}$   | Flicker Phase  | Electronic noise     |

|                |                  | modulation     |                      |

| $h_2f^2$       | $b_0$            | White PM       | External white noise |

Table 1.2 Phase noise power law response

Table 1.2 summarizes the origins of the main noises sources classically encountered in electronic systems [4].

#### 1.2.2 Prior work on phase noise testing

Traditionally, phase noise measurement relies on analog methods in order to evaluate the frequency-domain characteristics of phase noise, using spectrum analyzers or dedicated analog measurement systems [5-7]. Several methods are available for measuring phase noise, including the direct spectrum method, phase lock loop (PLL) method, delay-line discriminator method, and cross-correlation method. These methods differ from one to another in measurement principle, performance and measurement frequency range. Note that the usual goal for measuring phase noise in an R&D environment is to achieve the lowest measurement noise floor possible. However in a production environment, the objective is fast throughput for product phase noise performance testing. Traditional methods are therefore not necessarily appropriate for this specific context.

With the advances in technology and the availability of high-performance data acquisition systems, digital signal processing approaches have been proposed in order to derive the frequency domain characteristics of phase noise from digitized time-domain waveforms.

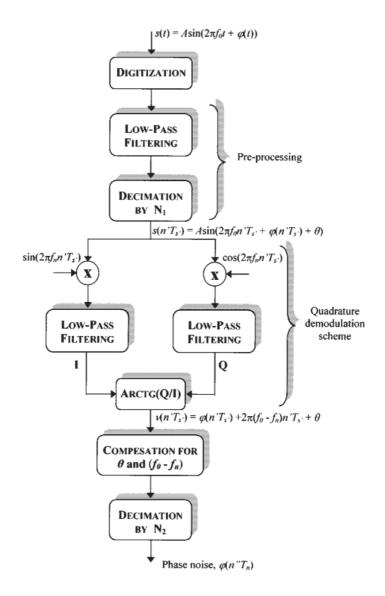

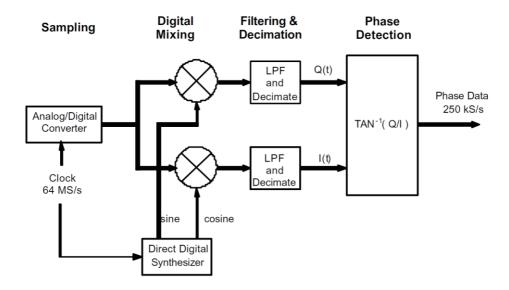

In [8-11], digital signal processing methods are developed based on oversampled capture of the input signal and optimized quadrature demodulation scheme. As illustrated in figure 1.2, the signal is directly digitized with a fast analog to digital converter. A pre-processing consisting in low-pass filtering and decimation is applied to have a better resolution of the signal. A quadrature demodulation scheme is then used to recover the phase. The phase can then be used to compute phase noise with the help of a Fourier transform or Allan deviation. This method has been validated for signals with frequencies around 1MHz.

Figure 1.2 Block diagram of the method proposed in [8]

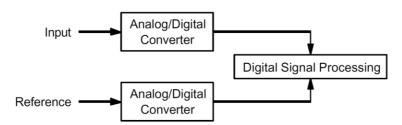

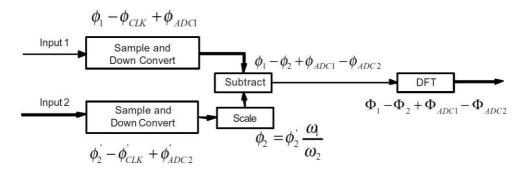

Similarly in [12], the input RF signal and a reference signal are digitized by fast analog-to-digital converters in order to perform direct-digital phase noise measurements. Down-conversion and phase detection functions are then implemented by digital signal processing. The principle of the method is illustrated in figure 1.3.

a) The RF signals are immediately converted to digital samples in order to perform direct - digital phase-noise measurements

b) A local oscillator synthesized from the internal clock down-converts the input to base-band where the samples are used to compute the phase difference between the LO and the input

c) After down-conversion, the phase differences are scaled, subtracted, and Fourier analyzed to determine the frequency content

Figure 1.3 Direct-digital phase noise measurement method proposed in [12]

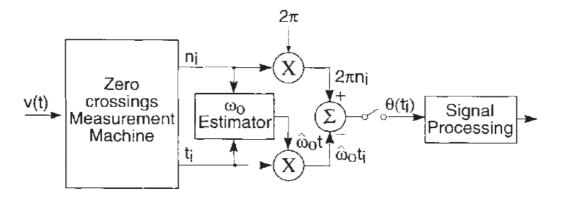

Current phase noise analysis techniques also include all-digital methods for acquiring time-domain data such as waveform crossing points. In particular, Time Interval Analyzers (TIAs) are used in [13,14] to record the zero-crossing times of the analyzed signal. Figure 1.4 show a simplified block diagram of the system including the zero-crossing measurement machine, frequency  $\omega_0$  estimator, phase calculation and numerical signal processing. The zero-crossing times are processed to compute phase deviation, with the reference frequency specified as a numerical value or derived from the times themselves. Phase digitizing can be applied even in the presence of modulation, as the underlying clock can be reconstructed in software to fit the data. Measurements derived from this phase data such as phase noise, jitter analysis, Allan variance (AVAR), maximum time interval error (MTIE), and time deviation (TDEV) can be applied.

Figure 1.4 Block diagram of the proposed method in [13]

The same approach is adopted in [15] in order to characterize phase noise in a spin torque oscillator from time-domain measurements.

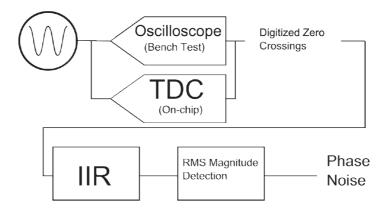

Another all-digital method is presented in [16], which relies on the use of a time-to-digital converter (TDC) to obtain digitized waveform zero-crossing. This technique is directed towards the detection of sinusoidal phase noise components located at particular frequencies. As illustrated in figure 1.5, the classical analog sampling is replaced by a time-to-digital converter, and an infinite-impulse response (IIR) filter is used as a replacement for conventional FFT. This eliminates the need for storing the entire waveform before calculations can begin, and the need for making calculations to evaluate frequencies which are not relevant.

Figure 1.5 IIR extraction technique proposed in [16] for the detection of sinusoidal phase noise at a particular frequency

Finally in order to reduce the testing costs, another approach is to develop Built-In Self-Test (BIST) solutions, where the required test resources are integrated within the circuit itself. While many works can be found in the literature regarding BIST solutions for jitter measurement [17-35], only few deal with BIST solutions for phase noise measurement.

In [36], an on-chip spectrum analyzer using switched-capacitor techniques is proposed. The main characteristic of the system is the inherent synchronization. Both, frequency of the sinewave generator and filter center frequency follow the main clock frequency, making the system self-synchronized and allowing a simple way to perform a frequency characterization. The resolution of this on-chip spectrum analyzer is limited to 8 bits.

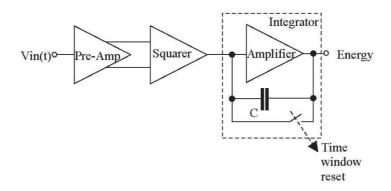

In [37], authors propose an analog BIST circuitry for Go/No-Go testing of synthesizer phase noise. The paper exploits the fact that there is a relation between the output noise of the PLL and the amplitude noise on the control voltage of the VCO. They therefore design a BIST circuit that measures the band-limited, low frequency noise power at the input of the voltage controlled oscillator (VCO). The block diagram of the noise measurement system is illustrated in figure 1.6, which comprises a linear preamplifier, a squarer that takes the time-domain square of the noise signal, and an integrator that accumulates the squared noise signal, effectively calculating its energy over a given time window.

Figure 1.6 Block diagram of the noise power measuring system proposed in [37] for go/no-go testing of synthesizer phase noise

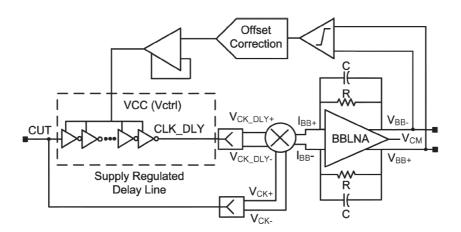

In [38], an on-chip phase noise measurement circuit is proposed, based on a delay-line discriminator architecture. As illustrates in figure 1.7, the proposed circuit uses a low-noise voltage-controlled delay-line (VCDL) and mixer-based frequency discriminator to extract the phase-noise fluctuations at baseband. A self-calibration circuit is used to operate the measurement circuit at its highest sensitivity point. This circuit is intended to measure phase noise of clock signals.

Figure 1.7 Circuit architecture of the phase-noise measurement module proposed in [38]

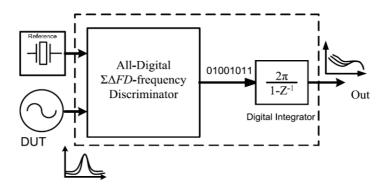

Finally in [39], authors use an all-digital on-chip  $\Sigma\Delta$ -frequency discriminator to compute the instantaneous frequency which they can compare to a reference frequency. The result of the comparison produces a noise shaped digital bit stream whose average value is proportional to the frequency error between the DUT signal and the reference signal. Thanks to phase domain model of the  $\Sigma\Delta$ -frequency discriminator, this technique can trace the phase noise asymptotic behavior. This technique is intended to be integrated as part of a BIST scheme for PLL-based clock synthesizers.

Figure 1.8 Phase noise characterization scheme proposed in [39]

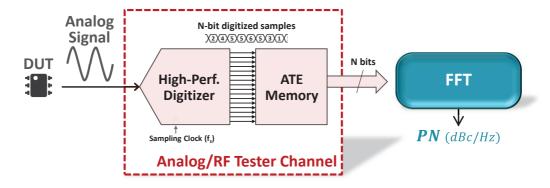

#### 1.2.3 Current practice for industrial phase noise testing

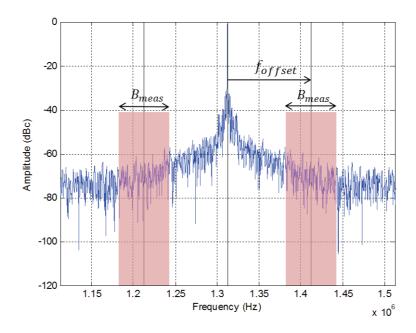

In a standard production test, phase noise is extracted from a spectral analysis of the signal. As illustrated in figure 1.9, the signal is first digitized by means of ATE analog/RF capture resources (a N-bit high-performance Analog-to-Digital-Converter) and stored in the ATE memory. FFT is then performed on the recorded digital data to compute the resulting signal power spectrum. As introduced in section 1.2.1, the widening of the spectral content around the fundamental tone can be associated with phase noise.

Practically, the phase noise value expressed in dBc/Hz is computed by subtracting the signal level to the noise level, where the noise level is measured by integrating noise over a specific bandwidth  $B_{meas}$  on both sides of the signal tone and applying a correcting factor for 1Hz bandwidth normalization. Note that spectral averaging is often implemented using data captured in several time window frames in order to reduce measurement variability. A Blackman window has also to be applied to the signal if the capture is not synchronous.

a) Industrial setup

b) Signal power spectrum with phase noise

Figure 1.9 Current industrial practice for industrial phase noise testing

#### 1.3 Thesis objective and positioning

The main objective of this thesis is to reduce the phase noise testing cost for complex RF devices. Indeed in the market of analog and RF integrated circuits, complex RF devices are gaining more and more importance in modern communication and multimedia applications. An example of such devices is silicon tuners, which have found use in set-top boxes for satellite and cable for nearly more than a decade. Now, thanks to their high performance, broad frequency coverage, compactness, and universality, they are making inroads into phones, service gateways, automobiles, personal computers, and even televisions. In this very competitive market, cost is a crucial factor, and in particular the testing costs which become the dominant part of the total manufacturing cost for this type of devices.

Phase noise is an essential characteristic of RF complex devices. In such devices, phase noise is usually measured on the analog output signal delivered at Intermediate Frequency (IF) and corresponds to the accumulated phase noise contribution of the various elements present along the signal path. The conventional practice for phase noise production testing relies on an analysis in the frequency domain, by taking time-domain data on the IF analog output and computing the Fast Fourier Transform (FFT). This approach requires the use of industrial testers equipped with expensive analog/RF resources, in particular high-performance digitizers to perform the signal capture, as well as computing power for the FFT. Moreover because such expensive resources are available in small quantity, the possibility to reduce the testing cost through multi-site testing is limited.

In order to reduce the testing cost, the strategy we have chosen to explore is this thesis relies on the use of digital test resources to perform phase noise measurement. Note that this work is the continuation of a previous thesis defended at LIRMM in 2011 by Nicolas Pous [40], which laid the foundations of the analysis of analog/RF signals using solely the test resources available in a standard digital tester channel. In particular, the analysis of FM-, AM- and QAM-modulated signals has been

investigated [41-43], as well as SNR estimation of analog sine-wave signals [44]. The same strategy of using a digital ATE for the analysis of analog signals has also been investigated in [45], in case of triangular waveform signals.

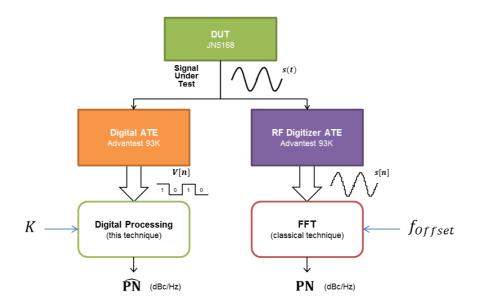

The general idea of this strategy is to perform oversampled 1-bit signal acquisition of the analog/RF signal with a standard digital channel, and to analyze the resulting bit stream with a dedicated digital processing algorithm. Indeed as illustrated in figure 1.10, the comparator included in the digital tester channel realizes a level-crossing operation which converts the amplitude and/or frequency information contained in the analog signal into a timing information in the resulting bit stream. In other words, the sequence of 0 and 1 stored in the ATE memory is somehow representative of some characteristics of the analog signal. It is then the role of the post-processing algorithm to retrieve this information and extract the desired signal characteristics.

Figure 1.10 General idea of analog/RF signal analysis using digital test resources

For a general point of view, this strategy relies on the assumption that it should be possible to retrieve the characteristics of an analog signal using the data resulting from level-crossing operation. The literature actually provides a number of elements that support this assumption. Indeed the concept of level-crossing has been used for many years for signal reconstruction in various fields such as image processing, speech recognition... [46-48] In the microelectronics domain, this concept is at the origin of digital FM demodulator architectures [49-61] proposed from beginning of 90's, and more recently of asynchronous analog-to-digital converter architectures [62-67]. The principle of this new class of converters is to perform sampling in the voltage domain followed by voltage-to-time conversion. The idea is actually to exploit the current trend of technology scaling, which permits to design circuits operating at lower supply voltages but with ever higher frequencies. These circuits therefore undergo a degraded voltage resolution whereas they benefit from an improved time resolution [68]. The same trend is exploited in [13-16] for phase noise testing based on timing measurements. However, proposed methods rely on the use of precise timing measurement instrumentation such as TIAs or TDCs. Our objective in this thesis is to develop a solution that does not require this precise timing measurement instrumentation, but rely only on the standard resources available on a digital ATE channel, so that we can have a very low-cost production test solution.

# Chapter 2. A phase noise model

Because new ideas are best first explored using mathematical and computer simulations, the first step in the study of phase noise measurement was to setup a correct simulation environment. In particular, we need to define a phase noise model that permits to perform realistic phase noise injection in the time-domain in an analog signal.

In this thesis, we target phase noise evaluation for complex RF devices such as silicon tuners for instance. For those kind of products, the total phase noise evaluated on the IF analog output involves the contribution of the various elements present along the signal path. The total phase noise measured on the IF output typically corresponds to white FM phase noise, with  $1/f^2$  characteristics. Our objective is therefore to define a model that permits a time-domain generation of such  $1/f^2$  noise.

Further away in the development of the thesis we will specify how other phase noise types can be measured, but for this simulation model sole white FM is considered first. Later on, other noises such as amplitude noise and jitter, which corresponds to white PM in table 1.2, will also be considered.

#### 2.1 Phase noise as a Brownian motion

#### 2.1.1 Phase fluctuation model

Let us consider an analog sinusoidal signal  $s(t) = A \cdot sin(\Omega(t))$  affected with phase noise and sampled at frequency rate  $f_s$ . The resulting signal  $s(nT_s)$  is expressed by:

$$s(nT_s) = A \cdot \sin(2\pi f n T_s + \varphi_0 + \varphi(nT_s)) \tag{2}$$

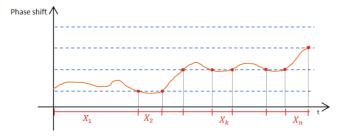

where A and f are nominal values of the amplitude and signal frequency respectively,  $T_s$  ( $T_s = 1/f_s$ ) is the sampling period,  $\varphi_0$  is the initial signal phase, and  $\varphi(nT_s)$  is the time-varying phase instability corresponding to phase noise.

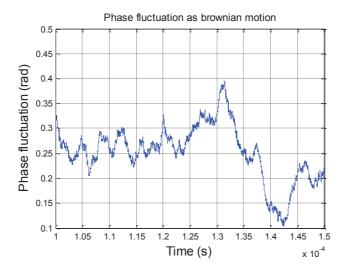

In order to control phase noise, we need to define the phase fluctuation  $\varphi(nT_s)$ . A simple way to generate phase noise with  $1/f^2$  characteristics is to consider a one-dimension Brownian motion [69]. The phase noise model considered here is therefore represented by:

$$\varphi(nT_s) = 2\pi T_s \cdot \sum_{j=0}^n b \cdot r_j \tag{3}$$

where  $r_j$  are random variables associated with a centered normal distribution  $\mathcal{N}\left(0,\sigma_f^{\ 2}\right)$  and b is a standardizing factor explained in the next section. This model allows to control the phase noise level injected in the time-domain signal by adjusting the value of  $\sigma_f$ , which is a standard deviation, in Hertz unit.

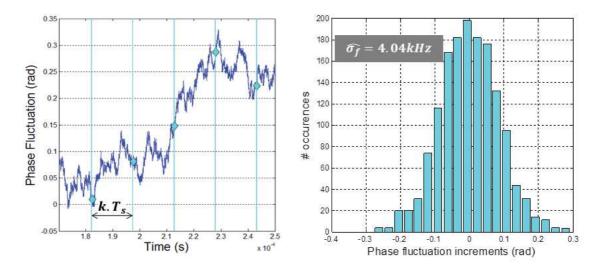

Figure 2.1 gives an example of a time-domain phase fluctuation generated using this model.

Figure 2.1 Example of time-domain phase fluctuation generated using a one-dimension Brownian motion

#### 2.1.2 Standardizing factor

$b=\sqrt{f_S/f}=\sqrt{n}$  is a standardizing factor that ensures independence of the noise level with respect to the sampling frequency. Indeed, we want to have the same deviation over 1 signal period, whatever the sampling frequency. There are  $n=\frac{f_S}{f}$  samples in one period. Since the variation of a Brownian motion is:

$$Var\left(2\pi T_{s} \cdot \sum_{j=0}^{n} b \cdot r_{j}\right) = \frac{4\pi^{2}}{f_{s}} b^{2} n \sigma_{f}^{2} = \frac{4\pi^{2}}{f^{2}} \sigma_{f}^{2}$$

(4)

So the standard deviation is:

$$std\left(2\pi T_{s} \cdot \sum_{j=0}^{n} b \cdot r_{j}\right) = \frac{2\pi}{f} \sigma_{f} \tag{5}$$

#### 2.1.3 Hertz: a unit amongst others

The input of the model is therefore  $\sigma_f$  in hertz. Note that it could be any of the four following variables since it is equivalent to consider any of the standard deviations  $\sigma$ ,  $\sigma_f$ ,  $\sigma_T$  or  $\sigma_{2\pi}$ .

$$\sigma = \frac{\sigma_f}{f} = \frac{\sigma_{2\pi}}{2\pi} = \frac{\sigma_T}{T} \tag{6}$$

The choice to use  $\sigma_f$  with hertz as unit is consequently arbitrary.

Taking the previous equation:

$$std\left(2\pi T_{s} \cdot \sum_{j=0}^{n} b \cdot r_{j}\right) = \frac{2\pi}{f} \sigma_{f} = \sigma_{2\pi} \tag{7}$$

We thus always have the same standard deviation over 1 unit of time: the signal period.

#### 2.1.4 Validation of model in Matlab®

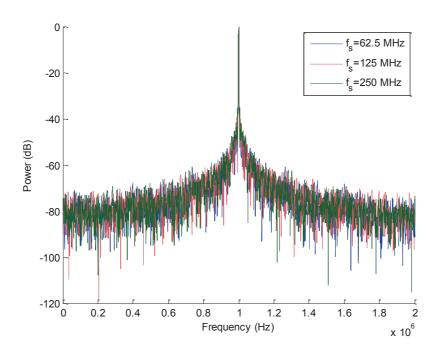

To validate this model, Matlab $^{\circ}$  simulations were performed. In figure 2.2, the spectrum of a simulated noisy  $1\,MHz$  signal is calculated for various sampling frequencies. The obtained spectrums

perfectly overlap as expected. The simulated signal thus has the same behavior whatever the sampling frequency thanks to the b coefficient. On this simulation  $N_{periods}=1000$  and  $\sigma_f=2000Hz$ .

Figure 2.2 Spectrum comparison between simulated signal with injected phase noise for different sampling frequencies

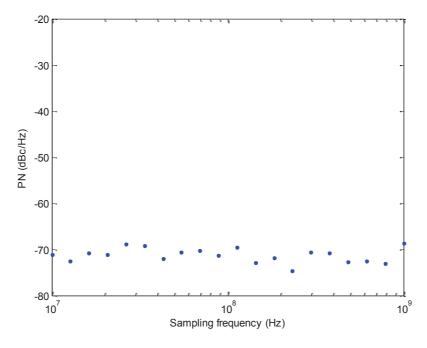

Figure 2.3 reports the phase noise value measured on the spectrum at a frequency offset of 10kHz, for different values of the sampling frequency between 10MHz and 1GHz. Here we compute the spectrum using 10 000 periods to reduce the dispersion; both f and  $\sigma_f$  were kept constant, as previously. As desired, the phase noise value measured on the spectrum does not depend on the sampling frequency.

Figure 2.3 Phase noise measurement on simulation model for different sampling frequencies

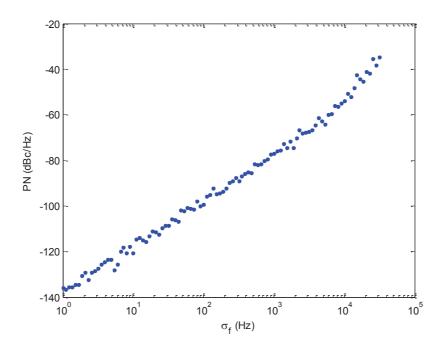

Figure 2.4 demonstrates the ability to control the phase noise level present in the simulated signal by adjusting the value of  $\sigma_f$ . The exact relationship between the two phase noise representations will be addressed later on.

Figure 2.4 Phase noise measurement for different values of injected phase noise level  $\sigma_f$

#### 2.2 Phase noise on hardware signals

#### 2.2.1 Experimental setup

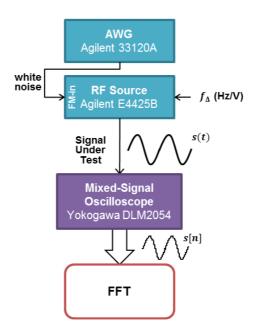

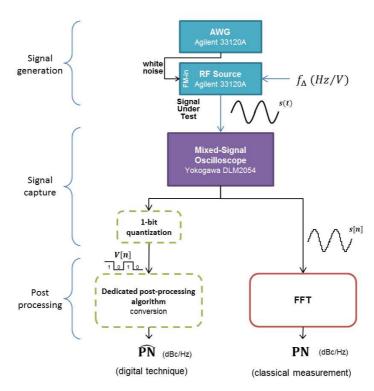

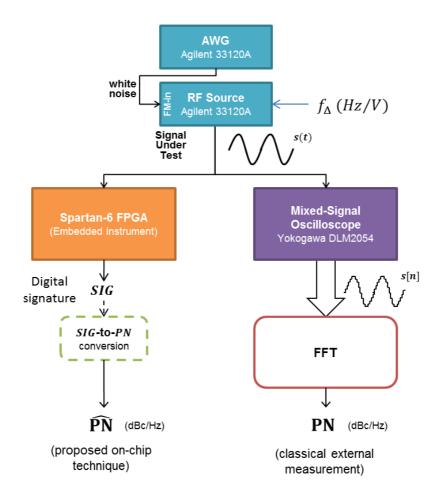

In order to perform measurement on physical signals, we also setup an experimental environment. Test signals are obtained through frequency modulation of a "pure" RF sinusoidal signal with a white noise signal. More precisely, an Agilent 33120A Arbitrary Waveform Generator (AWG) is used to generate a white noise signal. The output of this generator is connected to the FM input of an Agilent E4425B RF signal generator. The output of this RF generator is therefore a sinusoidal signal affected by phase fluctuations, which corresponds to the Signal Under Test (SUT). The phase noise level present in the synthetized signal can be adjusted by means of the modulation depth  $f_{\Delta}$  on the RF generator.

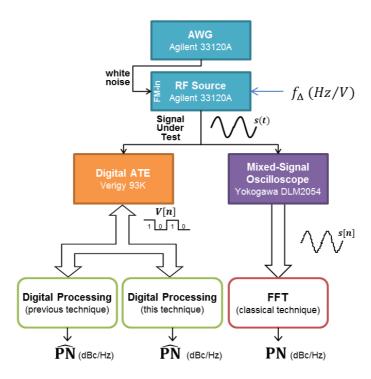

In order to evaluate the phase noise level, acquisition of the synthetized signal capture is realized using a Yokogawa DLM2054 Mixed-Signal Oscilloscope and the signal spectrum is obtained through FFT computation. Classical phase noise measurement is then performed on this spectrum. The complete setup is illustrated in figure 2.5.

Figure 2.5 Experimental setup for phase noise measurement on a synthetized signal affected with phase noise

#### 2.2.1.1 White noise analysis

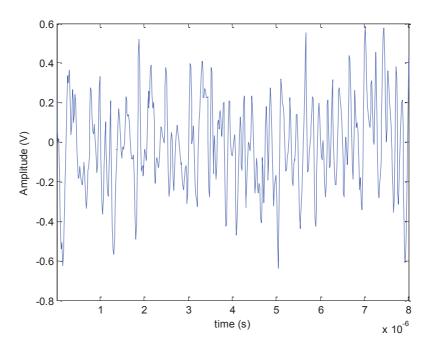

The generation of white noise is accomplished by the arbitrary waveform generator. We arbitrarily set  $V_{PP}=2V$ , which doesn't mean much when generating Gaussian voltage noise. Figure 2.6 shows a short sequence of the output of the AWG captured at 62.5MHz.

Figure 2.6 White noise from arbitrary waveform generator

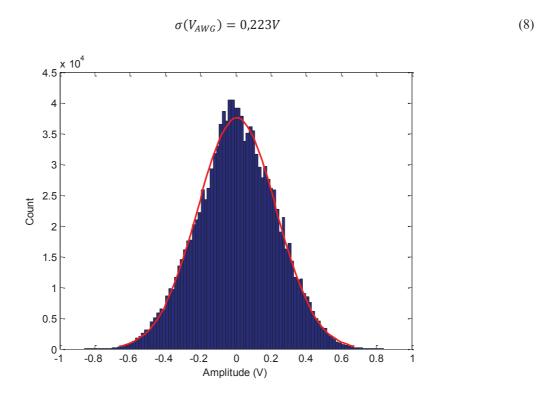

We measured the generated signal to determine the white noise level. Figure 2.7 provides a histogram of the captured samples. As expected, the sample distribution is a Gaussian distribution with zero mean; its standard deviation is:

Figure 2.7 Histogram of white noise signal captured on AWG output

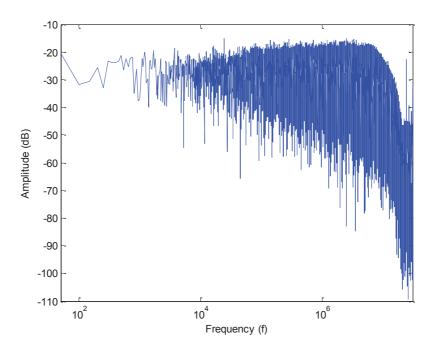

Figure 2.8 represents the Fourier transform of the so-obtained white noise. All the frequencies up to approximately 10MHz have the same power. Having a constant power over all the frequency range is expected to suit the model. This spectrum is equivalent to  $S_y$  in the table 1.2.

Figure 2.8 Spectrum of white noise signal captured on AWG output

#### 2.2.1.2 Synthetized signal analysis

The synthesized signal is to be an analog/RF sinusoidal signal affected with phase noise. For this, we use the RF source to generate a sinusoidal signal, which is modulated in frequency by the white noise signal generated by the AWG. The resulting signal is therefore given by:

$$y(t) = A \cdot \cos\left(2\pi \int_0^t f(\tau)d\tau\right) \tag{9}$$

With  $f(\tau) = f_c + f_\Delta x_m(t)$  where  $f_c$  is the frequency of the sinusoidal signal generated by the RF source,  $f_\Delta$  is the modulation depth and  $x_m(t)$  is the white noise signal generated by the AWG, we obtain:

$$y(t) = A \cdot \cos\left(2\pi f_c t + 2\pi f_\Delta \int_0^t x_m(\tau) d\tau\right) \tag{10}$$

So the phase fluctuation  $\varphi(t)$  is:

$$\varphi(t) = 2\pi f_{\Delta} \int_{0}^{t} x_{m}(\tau) d\tau \tag{11}$$

$\varphi(t)$  corresponds to a Brownian motion if  $x_m$  is Gaussian.

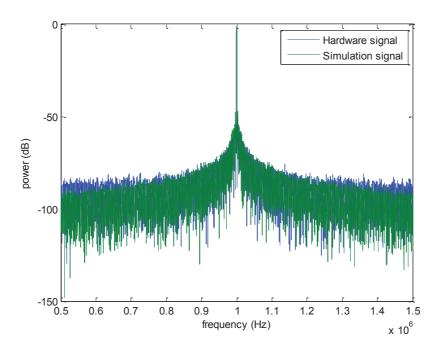

As an illustration, figure 2.9 shows the spectrum a synthetized signal generated with  $f_c=1~MHz$  and  $f_\Delta=11200~Hz$ . The spectrum of a simulated 1~MHz signal with  $\sigma_f=200Hz$  is also reported for comparison (the noise level of the simulated signal has been manually tuned to fit the spectrum of the captured synthetized signal). Both spectrums exhibit the same shape, which demonstrates that both methods generate a signal affected by similar phase noise. Still, one can notice that the physical signal exhibits slightly higher noise level at both ends of the plot (i.e. far from the fundamental tone). This is due to amplitude noise, which exists in the real world but which is not represented in the model so far.

Figure 2.9 Spectrum of simulated and synthesized 1MHz signals affected by phase noise

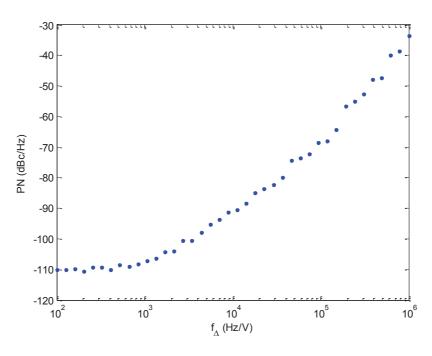

Figure 2.10 reports the phase noise level measured on the spectrum of the synthetized signal at a frequency offset  $f_{Offset}=25kHz$  according to the value of the modulation depth  $f_{\Delta}$  programmed on the RF signal generator. This figure clearly demonstrates that the phase noise level present in the synthetized signal can be adjusted on a large range by changing the modulation depth. However in case of very low phase noise level, i.e. low values of the modulation depth  $f_{\Delta}$ , some other noise sources (amplitude, jitter) take over and we observe a saturation of the phase noise level measured on the spectrum.

Figure 2.10 Phase noise measurement of a 1MHz synthesized signal for different values of the modulation depth

#### 2.2.2 Validation on practical devices

It is important to verify that both simulated and synthetized signals exhibit the same characteristics (regarding phase noise) as signals obtained from real industrial devices to be tested. NXP provided us with one golden device and 10 faulty devices of their TDA18260 silicon tuners. It goes without saying that the faulty devices solely failed for phase noise reason.

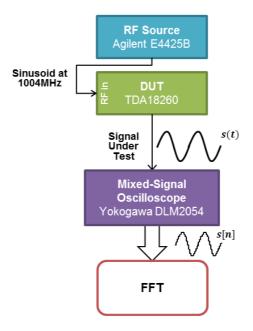

NXP usually do a phase noise test on the IF output of the device. This is what we did here. In order to setup test conditions, the device has to be provided with a 1004MHz input signal and have particular configuration of its gain control chain. Figure 2.11 illustrates the experimental setup.

Figure 2.11 Experimental setup for phase noise measurement on industrial chip

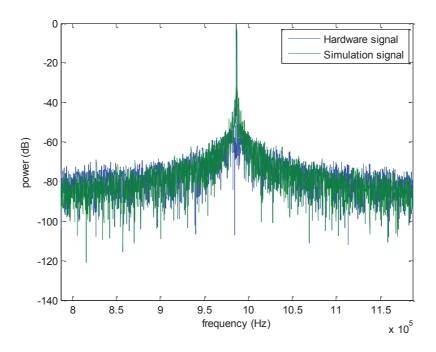

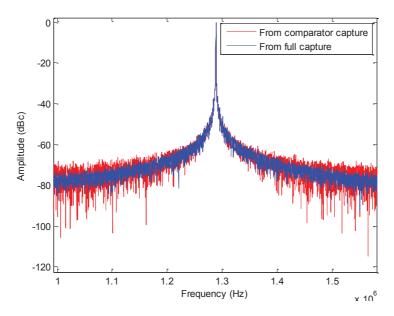

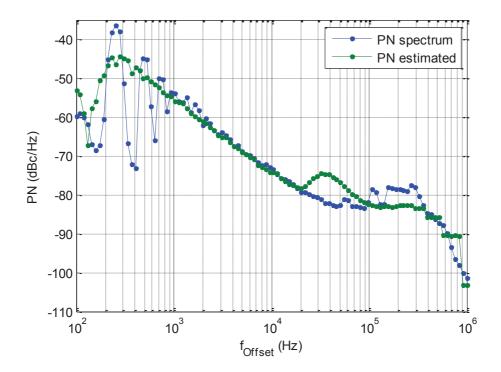

The spectrum of the captured signal is compared to the spectrum of a simulated signal in figure 2.12. Both spectrums exhibit a similar shape, demonstrating the validity of the proposed model to perform realistic time-domain phase noise injection for complex RF devices.

Figure 2.12 Comparison of spectrum of simulated signal with signal from industrial chip

# 2.3 Relationship between injected PN in time domain and measured PN in frequency domain

Using the previously proposed model, we need to establish the relationship between the phase noise level injected in the time domain and the phase noise level measured in the frequency domain, which corresponds to the reference phase noise. To do that, we performed several simulations varying the noise level injected in the time domain, under different signal and measurement conditions.

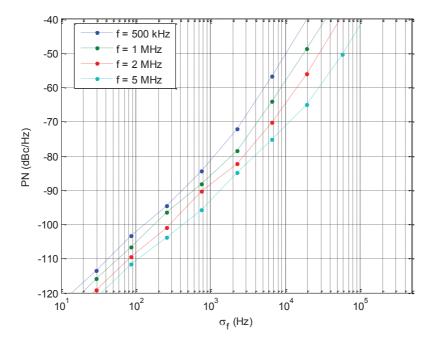

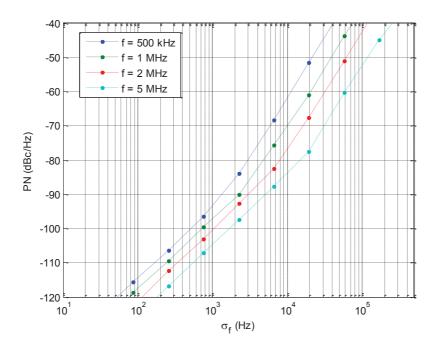

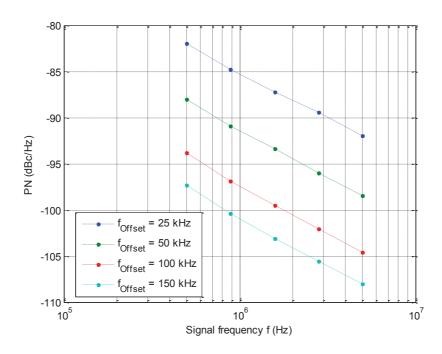

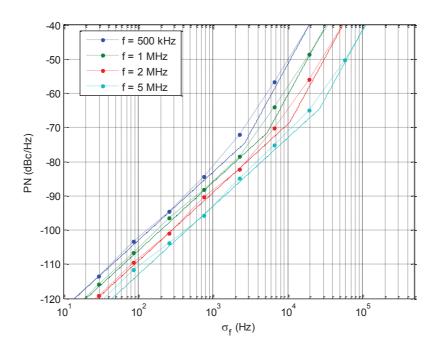

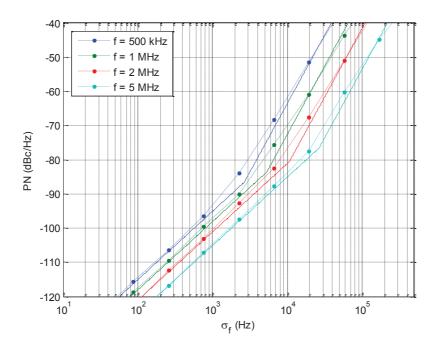

Illustrative results are given in figures 2.13 and 2.14 which report the phase noise measured on the spectrum (PN) as a function of the injected phase noise level  $(\sigma_f)$  for different signal frequencies (f), and for two values of the measurement frequency offset  $(f_{offset})$ . These simulations reveal two distinct behaviors depending on the level of noise. For low values of  $\sigma_f$  we observe a linear relationship with a slope of about +20dB/decade, while for high values of  $\sigma_f$  we still have a linear relationship but with a slope of about +40dB/decade. Note that in both cases, the slope neither depends on the signal frequency nor on the frequency offset. Only the vertical location varies with these parameters.

Figure 2.13 PN measured in frequency domain vs. PN injected in time domain, for different values of the signal frequency with  $f_{offset}=25kHz$

Figure 2.14 PN measured in frequency domain vs. PN injected in time domain, for different values of the signal frequency with  $f_{offset}=100kHz$

These relationships can be expressed with:

$$PN_1 = 20 \log_{10}(\sigma_f) + \alpha_1 \tag{12}$$

$$PN_2 = 20 \log_{10}(\sigma_f^2) + \alpha_2 \tag{13}$$

where Eq.(13) corresponds to the formulation for low level of injected time-domain phase noise, and Eq.(14) to the formulation for high level of injected noise.

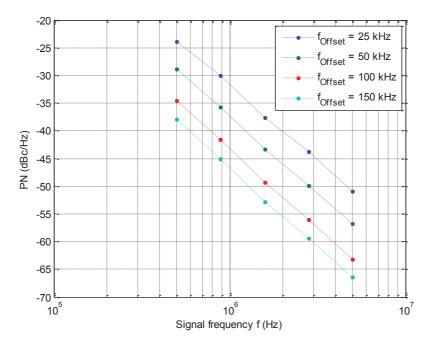

The following step is to model, for both cases, the relation that links the intercept coefficient  $\alpha$  to the signal frequency  $f_0$  and the measurement frequency offset  $f_{offset}$ . For this we considered a fixed level of noise for both cases ( $\sigma_f = 1kHz$  for low noise level and  $\sigma_f = 50kHz$  for high noise level) and we performed simulations varying the signal frequency (f) for different values of the frequency offset ( $f_{offset}$ ). Results are shown in figure 2.15 and 2.16 for the two noise levels.

Figure 2.15 PN measured in frequency domain vs. signal frequency, for different values of the measurement frequency offset with  $\sigma_f = 1 kHz$  (low phase noise level)

Figure 2.16 PN measured in frequency domain vs. signal frequency, for different values of the measurement frequency offset with  $\sigma_f = 50 kHz$  (high phase noise level)

We observe a linear relation on log-lin scale with a slope of about -10dB/decade for low noise level, which corresponds to  $\alpha_1$  varying with a  $-10\log_{10}(f)$  function. A slope of about -30dB/decade is observed high noises, which corresponds to  $\alpha_2$  varying with a  $-30\log_{10}(f)$  function. In both cases, the slope does not depend on the frequency offset, only the vertical intercept term. Consequently, we can express:

$$PN_1 = 20 \log_{10} \left( \frac{\sigma_f}{f^{1/2}} \right) + \beta_1 \tag{14}$$

$$PN_2 = 20 \log_{10} \left( \frac{\sigma_f^2}{f^{3/2}} \right) + \beta_2 \tag{15}$$

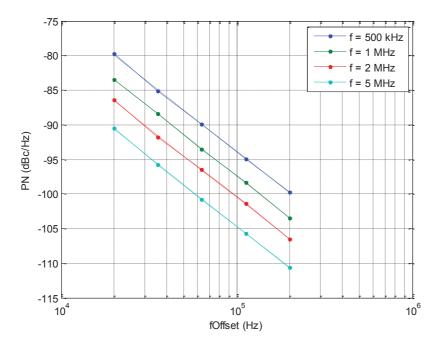

Figures 2.17 and 2.18 report the evolution of PN with respect to the frequency offset for different values of the signal frequency, in case of low and high noise levels respectively. In both cases, we observe a straight line with a slope of about -20dB/decade, leading to:

$$PN_1 = 20 \log_{10} \left( \frac{\sigma_f}{a_1 f^{1/2} f_{Offset}} \right)$$

(16)

$$PN_{1} = 20 \log_{10} \left( \frac{\sigma_{f}}{a_{1} f^{1/2} f_{0ffset}} \right)$$

$$PN_{2} = 20 \log_{10} \left( \frac{\sigma_{f}^{2}}{a_{2} f^{3/2} f_{0ffset}} \right)$$

(16)

Figure 2.17 PN measured in frequency domain vs. measurement frequency offset for different values of the signal frequency with  $\sigma_f=1kHz$  (low phase noise level)

Figure 2.18 PN measured in frequency domain vs. measurement frequency offset for different values of the signal frequency with  $\sigma_f = 50kHz$  (high phase noise level)

The terms  $a_1$  and  $a_2$  are then computed from best fit curve regression for the different values of  $f_{offset}$ . Analytical expressions corresponding to low and high levels of injected phase noise can then be obtained:

$$PN_1 = 20 \log_{10} \left( \frac{\sigma_f}{0.81 \cdot f^{1/2} \cdot f_{offset}} \right)$$

(18)

$$PN_{1} = 20 \log_{10} \left( \frac{\sigma_{f}}{0.81 \cdot f^{1/2} \cdot f_{offset}} \right)$$

$$PN_{2} = 20 \log_{10} \left( \frac{\sigma_{f}^{2}}{4.28 \cdot 10^{-3} \cdot f^{3/2} \cdot f_{offset}} \right)$$

(18)

Finally, the analytical relation between the noise injected in the time domain and the noise measured in the frequency domain is simply given by the maximum the two expressions above:

$$PN = \max(PN_1, PN_2) \tag{20}$$

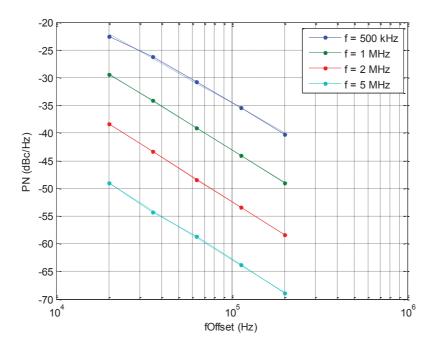

Figures 2.19 and 2.20 compare the phase noise value computed using this analytical expression to the phase noise value measured on the spectrum, for different values of the signal frequency (f), and for two values of the measurement frequency offset ( $f_{offset}$ ). In all cases, a good agreement is observed.

Figure 2.19 PN computed with analytical formulation vs. PN measured through FFT computation,  $f_{\it offset} = 25 kHz$

Figure 2.20 PN computed with analytical formulation vs. PN measured through FFT computation,  $f_{\it offset} = 100 kHz$

## 2.4 Conclusion

In this chapter, we have introduced a phase noise model based on a one-dimensional Brownian motion that permits phase noise injection in a time-domain signal. This model corresponds to phase noise with  $1/f^2$  characteristics, which is typical of complex RF products that are the target of this thesis. The level of injected phase noise can be controlled by means of the standard deviation  $\sigma_f$  of the random variables involved in the Brownian motion. The validity of this model has been checked against a real device fabricated by NXP and an experimental setup allowing to synthetize a physical signal affected by phase noise has been developed. Finally, an analytical relationship between the phase noise level injected in the time domain and the phase noise level measured in the frequency domain has been established through a comprehensive simulation study.

# Chapter 3. First method: phase noise estimation based on instantaneous frequency estimation

This chapter presents the first approach developed in this thesis in order to measure phase noise by means of a simple 1-bit capture. In a first part, background on frequency estimation from 1-bit capture is recalled. The principle of phase noise estimation based on an analysis of instantaneous frequency deviation is introduced in the second part. Then, integration of a measurement module is proposed as a solution toward Built-In Self-Test (BIST). Primary experiments are presented in the fourth part and limitations of the proposed technique are highlighted. An improved version of the technique that includes an additional filtering step is then developed and validated through experimental measurements on hardware signals.

# 3.1 Background on frequency estimation

## 3.1.1 Frequency estimation from 1-bit capture

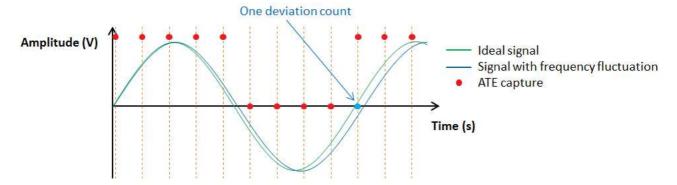

The object of previous work [40] was to analyze RF signals with solely digital resources. One of the main contributions was the ability to recover frequency and amplitude of complex modulated signals using a simple 1 bit capture. Basics of frequency estimation are recalled here.

The analog signal s(t) to be analyzed is first oversampled ( $f_s$ , sampling frequency) and converted to a digital signal by means of the comparator and the latch comprised in the digital tester channel. The resulting signal is therefore a binary vector V[n] expressed with:

$$V(n) = \begin{cases} 1 & \text{if } s(nT_s) \ge 0 \\ 0 & \text{else} \end{cases} \quad n = 1 \dots N$$

(21)

where  $T_S = 1/f_S$  is the sampling clock period, and N is the total number of captured samples. This binary vector stored in the ATE memory is then processed in order to retrieve the analog signal characteristics.

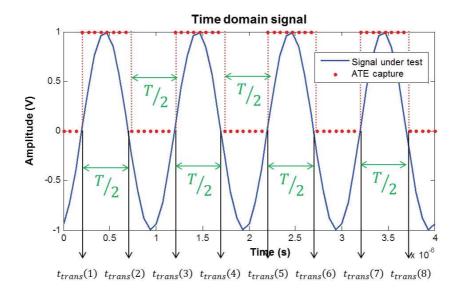

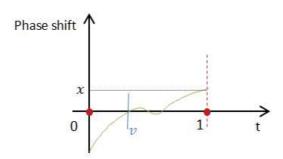

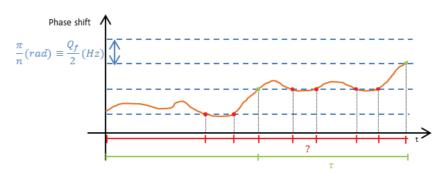

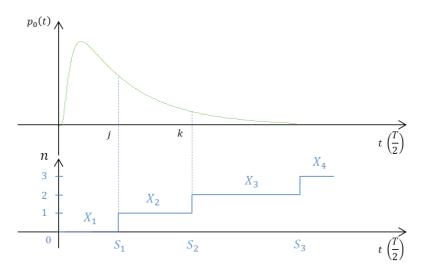

One can exploit the transitions of the captured binary vector V[n] that correspond to the zero-crossings of the analog signal s(t) in order to compute an estimation of the instantaneous period  $\widehat{T}(m)$ . This estimation can be simply obtained by counting the number of samples between successive transitions of the binary vector, which corresponds to the signal half-period:

$$count(m) = \begin{bmatrix} Nb\_samples \end{bmatrix} transition(m+1)$$

$$transition(m)$$

$$\hat{T}(m) = 2 T_s count(m) \qquad m = 1 \dots 2(Nper - 1)$$

(22)

where *Nper* is the number of captured signal periods.

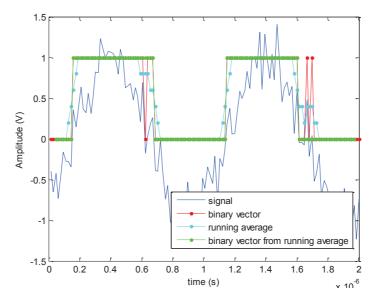

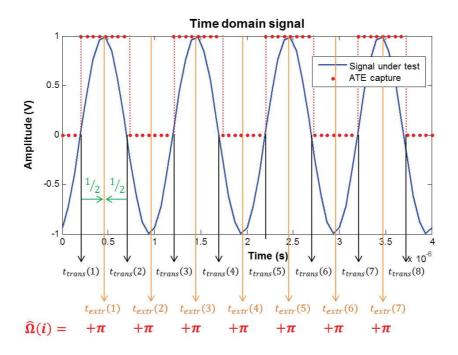

This is illustrated in figure 3.1 where the analog signal is represented in blue and V[n] is represented by red dots. The zero-crossing times of the analog signal can be inferred from the knowledge of rise and fall transition times of the binary vector.

Figure 3.1 1-bit acquisition of the signal under test. The transitions of the binary vector are used to estimate the instantaneous period.

The instantaneous frequency is then simply given by:

$$\hat{f}(m) = \frac{1}{2 T_s count(m)} \tag{23}$$

With this process, we obtain 2(Nper-1) values of the instantaneous frequency. Note that an estimation of the signal frequency can be computed as the arithmetic mean of instantaneous frequency estimations:

$$\bar{f} = \frac{1}{M} \sum_{m=1}^{M} \frac{1}{2 T_s \ count(m)}$$

(24)

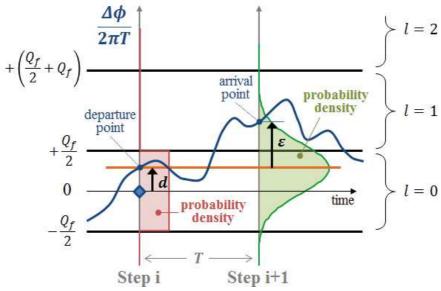

#### 3.1.2 Discretization quantum

The sampling process of the analog signal s(t) introduces a quantization of the estimated values for the instantaneous period or frequency. Indeed as expressed by eq.(22), estimated values of the instantaneous period can take only even integer multiple values of the sampling period. The quantization step of the instantaneous period  $\widehat{T}(m)$  is therefore:

$$Q_T = 2 T_S \tag{25}$$

The quantization step of the instantaneous frequency  $\hat{f}(m)$  can be calculated with a differentiation of f = 1/T:

$$df = -\frac{dT}{T^2} \tag{26}$$

So the quantization step of  $\hat{f}(m)$  is:

$$Q_f = \left| -\frac{Q_T}{T^2} \right| = \frac{2 \, T_s}{T^2} = \frac{2 \, f^2}{f_s} \tag{27}$$

#### 3.1.3 Running average filtering

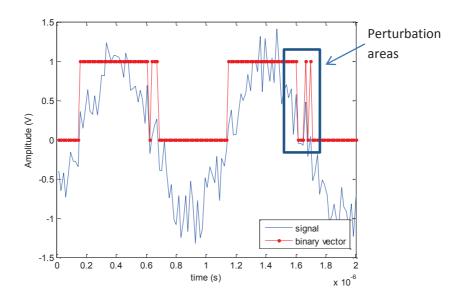

Practically, the signal is noisy in amplitude. In case of high amplitude noise level, the binary vector could be affected by multiple transitions in the zero crossing neighborhoods as illustrated in figure 3.2. In order to get rid of these potential perturbation areas, basic filtering is implemented [40].

Figure 3.2 Amplitude noise may cause perturbation in the binary vector near transitions

A simple running average over the binary vector does the job. The running average is performed over a window of  $N_{avg}$  samples:

$$\tilde{V}[n] = \frac{1}{N_{avg}} \sum_{i=n-N_{avg}}^{n} V[i]$$

(28)

The result of this averaging is compared to 0.5 in order to locate zero-crossing events and obtain another binary vector  $V_1[n]$  that presents a single transition associated to each zero-crossing event.

Figure 3.3 Perturbation in the binary vector can be filtered with a running average

Figure 3.3 illustrates how the binary vector computed from the running average isolates one single transition from the perturbation area where there was multiple transitions. This algorithm is robust and proven to be well functioning for  $N_{avg}$  around  $\frac{f_s}{4f}$  as a rule of thumb.

#### 3.1.4 Error on threshold level

In practice we want to be robust to any error on the threshold voltage of the comparator that performs 1-bit quantization. A simple solution is to consider time of extremums rather than transition time stamps:

$$\widehat{t_{extr}}(i) = \frac{\widehat{t_{trans}}(i) + \widehat{t_{trans}}(i-1)}{2}$$

(29)

This way, any offset error on the comparator threshold will be cancelled by the sum between two successive  $t_{trans}$ . Then we have:

$$count(m) = \begin{bmatrix} Nb\_samples \end{bmatrix}^{t_{extr}} (m+1)$$

$$t_{extr}(m)$$

(30)

for the instantaneous frequency estimations in eq.(22).

Note that this is equivalent to distinguish rising and falling transitions and separately count the number of samples between successive rising events  $count_R(m)$  and successive falling events  $count_F(m)$ , which directly corresponds to the signal period. In this case, the instantaneous frequency is given by:

$$\hat{f}(m) = \frac{1}{T_s count_R(m)}, \qquad \hat{f}(m) = \frac{1}{T_s count_F(m)}$$

(31)

and quantization step of the instantaneous frequency  $Q_f$  changes since the frequency is estimated over one whole period to:

$$Q_f = \frac{f^2}{f_s} \tag{32}$$

# 3.2 Statistical dispersion on instantaneous frequency estimations

From the oversampled 1-bit acquisition of an analog signal, we have established in the previous section how to compute the instantaneous frequency, with two estimations per signal period. In case of an ideal sinusoidal signal with no phase noise, the instantaneous frequency should exhibit the same value at each period of the signal, while in case of a sinusoidal signal affected with phase fluctuation, we expect a dispersion on the computed values. It is therefore our objective to analyze the distribution of the instantaneous frequency in order to derive an estimation of the phase noise affecting the analog signal.

## 3.2.1 Standard deviation

The first natural idea to analyze the distribution of the estimated instantaneous frequency is to compute its standard deviation. Standard deviation is indeed a very commonly-used measure of statistical dispersion. This standard deviation is defined by:

$$\sigma(\hat{f}) = \sqrt{\frac{1}{2Nper - 3} \sum_{m=1}^{2(Nper - 1)} (\hat{f}(m) - \bar{f})^2}$$

(33)

where  $\bar{f}$  is the mean of the instantaneous frequency estimations.

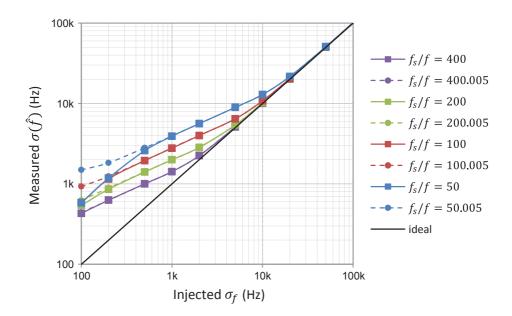

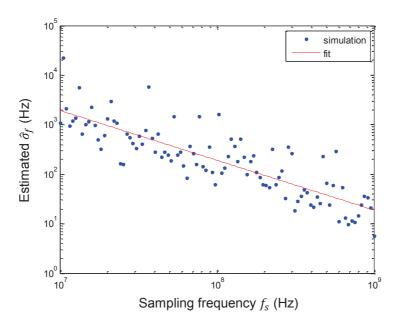

Figure 3.4 gives the evolution of the instantaneous frequency standard deviation  $\sigma(\hat{f})$  according to the injected phase noise level  $\sigma_f$  for different values of the oversampling ratio  $f_s/f$ , in case of a  $1\,MHz$  signal. Analyzing these results reveals that there is a direct correlation between  $\sigma(\hat{f})$  and  $\sigma_f$  for high level of injected phase noise and high oversampling ratio. For instance with an oversampling ratio of 400, there is a perfect match with an ideal straight line for noise level higher than 2 000Hz. In this region, we can directly estimate the phase noise level injected in the time-domain signal with:

$$\hat{\sigma}_f = \sigma(\hat{f}) \tag{34}$$

However validity of this simple correlation is lost when decreasing the oversampling ratio. For instance with an oversampling ratio of 50, Eq.(34) is valid only for noise level higher than 10 000Hz.

Figure 3.4 Standard deviation of estimated instantaneous frequency vs. injected phase noise level, for different values of the oversampling ratio

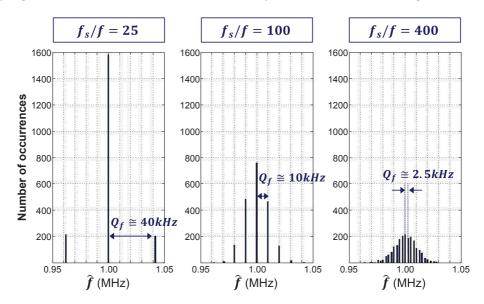

This phenomenon comes from the quantization of the estimated instantaneous frequency introduced by the sampling process, with a quantization step equal to  $Q_f=f^2/f_s$ . As a result, the distribution of the estimated instantaneous frequency is a discrete distribution. Figure 3.5 illustrates this distribution for 3 different values of the oversampling ratio, with a 1% phase noise level injected in a 1MHz signal ( $\sigma_f=10kHz$ ). In case of a low oversampling ratio of 25, the quantization step is large ( $Q_f=40kHz$ ) and the discrete distribution is evaluated with a low resolution. In contrast with a larger oversampling ratio of 400, the quantization step is small ( $Q_f=2.5kHz$ ) and the discrete distribution is obtained with a fine resolution. Direct evaluation of the phase noise level can be achieved using the standard deviation only if the resolution is sufficient, i.e. if the quantization step is smaller than the phase noise level to be estimated. Practical use of standard deviation for phase noise evaluation is therefore limited. For instance, the correct evaluation of -90dBc/Hz phase noise at

25kHz frequency offset on a 1MHz signal ( $\sigma_f = 640Hz$  from Eq.(18)) would require a sampling frequency higher than 1.56GHz, which exceeds the capabilities of a standard digital tester channel.

Figure 3.5 Effect of frequency quantization on distribution of estimated instantaneous frequency

#### 3.2.2 Mean Absolute Deviation (MAD)

In this context, we have looked for another estimator that can apply to our specific case of discrete distribution evaluated with low resolution. Other than the standard deviation, many different measures of statistical dispersion exist, such as the interquartile range, the mean difference, the median absolute deviation, the mean absolute deviation, the distance standard deviation... Among these classical measures, we have identified that the Mean Absolute Deviation (MAD) is a measure that can be easily computed and that permits robust estimation in our specific context.

The Mean Absolute Deviation (MAD) is defined as the mean of the absolute deviations of a set of data measured apart from the data mean value. In our case, we have:

$$MAD(\hat{f}) = \frac{1}{2(Nper - 1)} \sum_{m=1}^{2(Nper - 1)} |\hat{f}(m) - \bar{f}|$$

(35)

In case of a normal distribution, the MAD is related to the standard deviation with:

$$MAD(\hat{f}) = \sqrt{\frac{2}{\pi}} \cdot \sigma(\hat{f}) \tag{36}$$

Consequently, we propose to estimate the phase noise injected in the time-domain signal with:

$$\hat{\sigma}_f = \sqrt{\frac{\pi}{2}} \cdot MAD(\hat{f}) \tag{37}$$

Replacing  $\hat{f}$  by its expression and rearranging the equation, we obtain:

$$\hat{\sigma}_f = \sqrt{\frac{\pi}{2}} \cdot \frac{Q_f}{2(Nper - 1)} \sum_{m=1}^{2(Nper - 1)} |count(m) - n|$$

(38)

where  $Q_f = f^2/f_s$  is the frequency quantization step, Nper is the number of captured signal periods,  $n = f_s/f$  is the oversampling ratio, and count(m) is the number of samples between successive extremums.

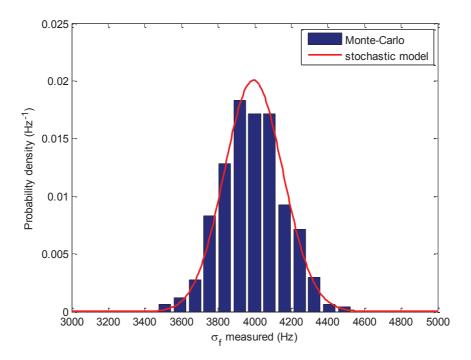

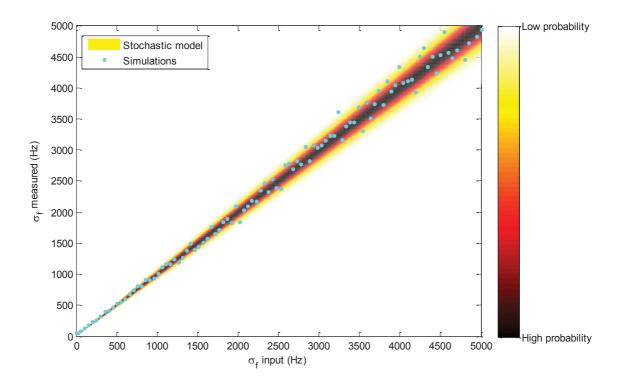

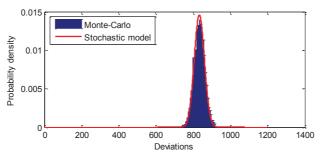

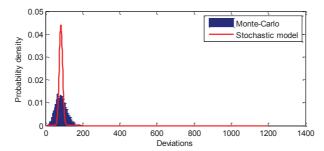

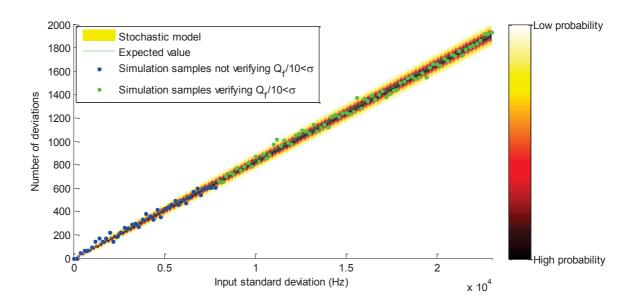

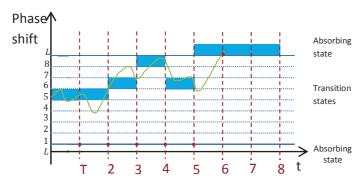

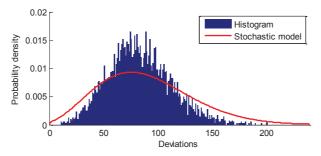

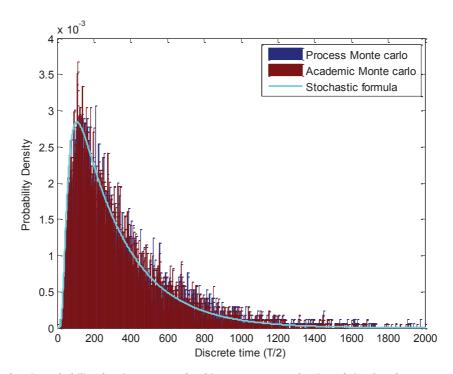

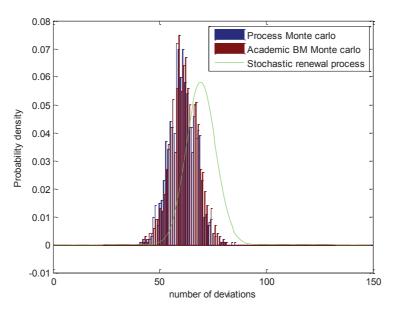

Note that this analytical relationship has been derived based on an intuitive use of the MAD function. The same expression can be established based on a stochastic model of the measurement process, as detailed in Annex A.

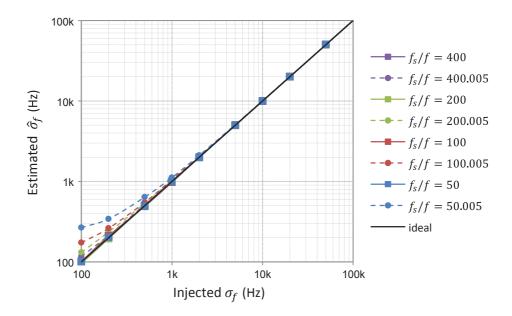

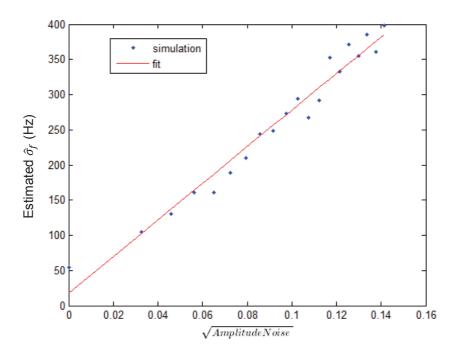

Figure 3.6 reports the estimated phase noise level  $\hat{\sigma}_f$  vs. the injected phase noise level  $\sigma_f$ , for different values of the oversampling ratio  $f_s/f$ . It can be observed that all curves obtained with an integer oversampling ratio perfectly match the ideal straight line, whatever the integer value. In case the oversampling ratio is not exactly an integer, curves deviate from the ideal straight line for low level of injected phase noise. These results clearly indicate that the proposed estimator has the potential to achieve correct phase noise even for low level of noise and low oversampling ratio, provided that the sampling frequency is a perfect multiple of the signal frequency.

Figure 3.6 Estimation of PN level based on Mean Absolute Deviation of estimated instantaneous frequency

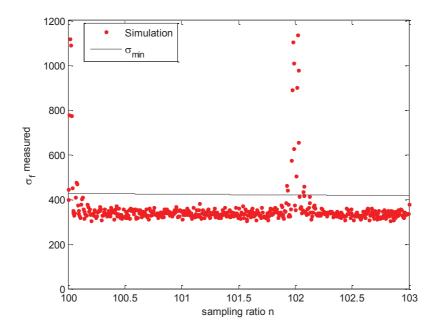

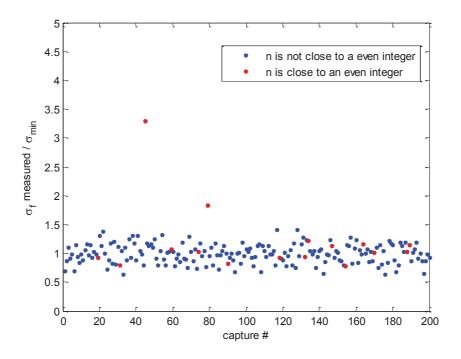

## 3.2.3 Considerations for sampling ratio setting

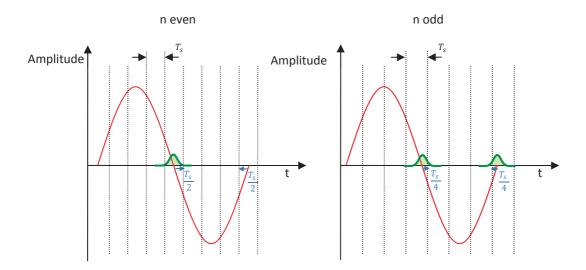

The proposed technique relies on the use on an integer oversampling ratio  $=\frac{f_s}{f}$ . This ratio should preferably be chosen odd. The reason for this is illustrated in figure 3.7.

Figure 3.7 The maximum distance between a zero-crossing event and the closest sampling point is reduced by choosing an odd oversampling ratio  $\boldsymbol{n}$

Considering an ideal sinewave, there are two zero-crossing events per period, one corresponding to the falling slope of the other to the rising slope of the analog signal. The maximum distance between the actual location of these crossing events and the closest sampling points actually depends on the choice of the sampling ratio as odd or even. In case of an even number, this maximum distance is equal to  $\frac{T_S}{2}$  while in case of an odd number, it cannot exceed  $\frac{T_S}{4}$ . This means that with the same phase noise, represented as a Gaussian distribution in green, the signal is much more likely to be detected when n is odd.

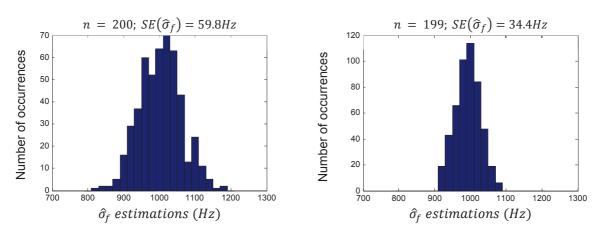

To illustrate this point, we have simulated a 1MHz signal affected with phase noise ( $\sigma_f=1kHz$ ) and sampled using either an even (n=200) or odd (n=199) ratio. In both cases, the phase noise level  $\hat{\sigma}_f$  present in the signal has been estimated using eq.(38). The experiment has been repeated 500 times and we have computed the standard error on the estimated phase noise values  $SE(\hat{\sigma}_f)$ . Results are summarized in figure 3.8 which reports the distribution of estimated values. It clearly appears that correct estimation is achieved in both cases with a distribution well-centered on the expected value of 1kHz. However the dispersion is lower in case the oversampling ratio is odd rather than even, which corresponds to a reduced measurement uncertainty.

Figure 3.8 Distributions of  $\widehat{\sigma}_f$  estimations obtained in simulation with n=200 and n=199

Finally, we have evaluated the impact of inaccuracy on the setting of the oversampling ratio. The number of instantaneous frequency deviations due to an inaccurate oversampling ratio  $n'=\frac{f_S+\Delta f_S}{f}$  should obviously be much smaller than the number of instantaneous frequency deviations generated by phase noise in order to not disturb the estimation. We have established that the sampling frequency error  $\Delta f_S$  should respect the following constraint:

$$\Delta f_{\rm S} \ll \frac{n}{\sqrt{2\pi}} \left. \sigma_{\rm f} \right|_{target}$$

(39)

where n is the ideal integer oversampling ratio and  $\sigma_f|_{target}$  is the typical phase noise level to be measured on the signal under test.

#### 3.2.4 Summary of proposed digital technique

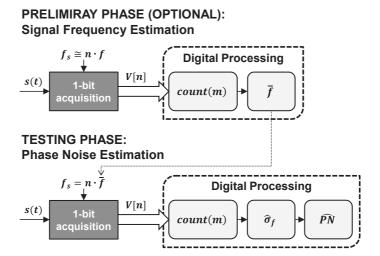

The proposed technique relies on the 1-bit acquisition of the signal to be analyzed with a sampling frequency that is an integer multiple of the signal frequency, associated with simple digital processing to compute the mean absolute deviation of the estimated instantaneous frequency. The technique therefore requires that the signal frequency is known with a good accuracy.

If necessary, the practical implementation many include a preliminary phase dedicated to the determination of the signal frequency before the phase noise test phase, as illustrated in figure 3.9.

Figure 3.9 Block diagram of the proposed digital technique based on instantaneous frequency estimation

In the preliminary phase, 1-bit acquisition of the signal is performed with a sampling frequency that is not necessarily an integer multiple of the signal frequency. From this acquisition, the signal frequency is computed as the arithmetic mean of the instantaneous frequency estimations using eq.(28).

In the testing phase, a novel 1-bit acquisition of the signal is performed with the sampling frequency adjusted at an integer multiple of the computed signal frequency  $f_s = n \cdot \bar{f}$ . From this acquisition, we compute the estimated value of the phase noise level  $\hat{\sigma}_f$  using eq.(38). The final estimation of the phase noise value  $\widehat{PN}$  expressed in dBc/Hz is then obtained from eq.(20).

## 3.3 Integrated module

#### 3.3.1 Integrated module overview and principle

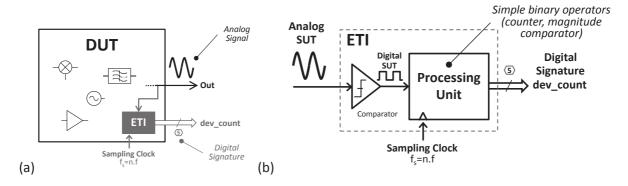

We investigated ways to integrate this technique on chip, in order to perform phase noise measurement directly within the Device Under Test (DUT). The objective is to develop an Embedded Test Instrument (ETI) that delivers a digital signature directly related to the phase noise level present in the analog output signal of the DUT, as shown in Fig.3.10.a. However the direct integration of the method described in previous section is not feasible since it requires excessive area with respect to the area occupied by the DUT itself. Indeed, although the 1-bit digitizer can be implemented with small area using a comparator for instance, the computation of the phase noise level necessitates the integration of both important memory resources and DSP to perform the required arithmetic operations. Our purpose is therefore to redefine the post-processing algorithm in order to implement the computation of the digital signature using a limited number of memory resources and only simple binary operators, as illustrated in Fig.3.10.b.

Figure 3.10 Embedded Test Instrument for phase noise measurement

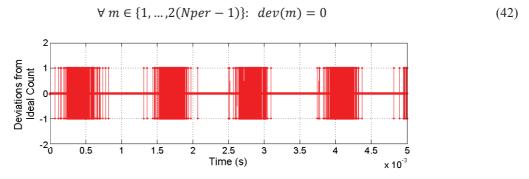

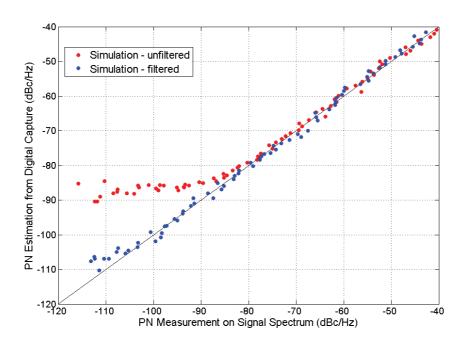

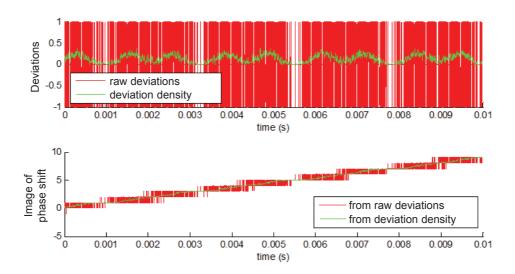

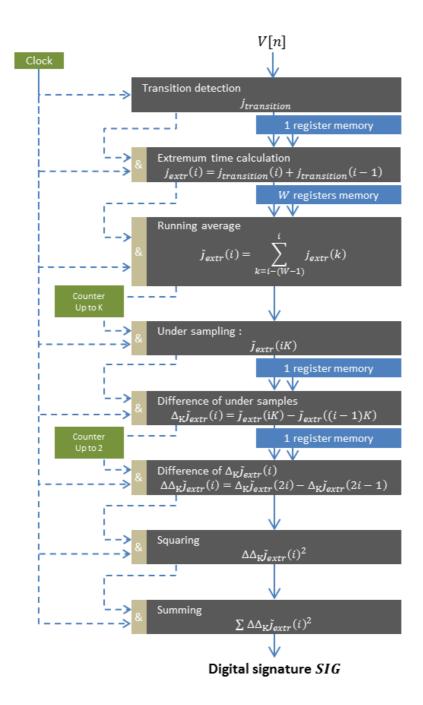

In order to identify an appropriate digital signature, let us first define dev(m) = count(m) - n as the deviation from the ideal count at each estimated value of the instantaneous frequency, where count(m) corresponds to the number of samples between successive transitions of same type (either rising or falling transitions). The phase noise estimator defined in eq.(38) can then be expressed with:

$$\hat{\sigma}_f = \sqrt{\frac{\pi}{2}} \cdot \frac{Q_f}{2(Nper - 1)} \cdot \sum_{m=1}^{2(Nper - 1)} |dev(m)| \tag{40}$$

This equation clearly indicates that the basic operation to be performed for on-chip implementation is a sum of absolute deviations, which can be considered as the digital signature of phase noise level present in the analog signal:

$$dev\_count = \sum_{m=1}^{2(Nper-1)} |dev(m)|$$

(41)

In order to perform the computation of this digital signature with minimal hardware resources, the key idea is to implement on-the-fly processing of the 1-bit signal delivered at the output of the comparator. In particular, the idea is to generate a pulse train signal whose pulse durations correspond to differences between the actual period duration and a reference based on the ideal

period length. The digital signature related to the phase noise level can then be computed with a simple accumulation of these deviations over a number of signal periods.

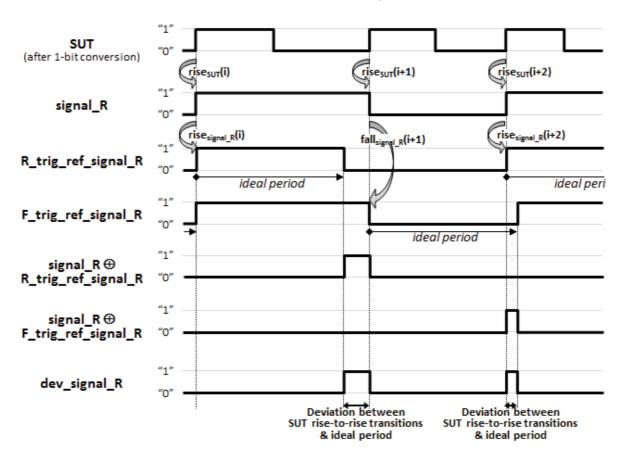

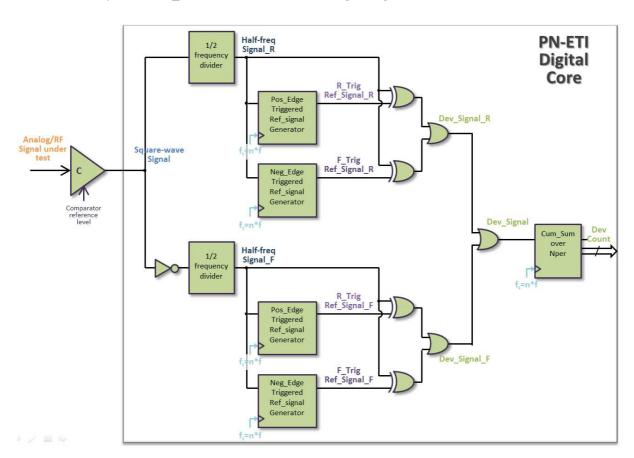

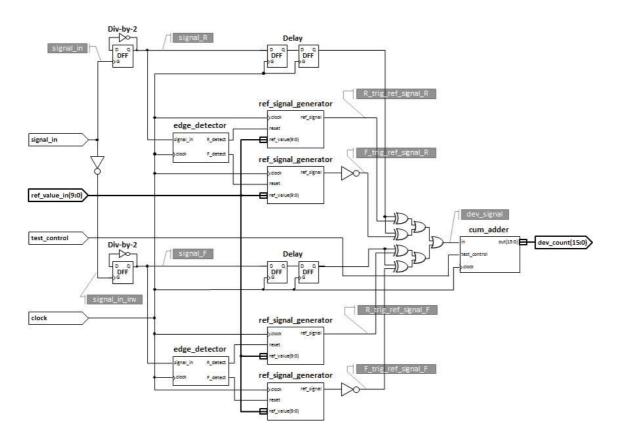

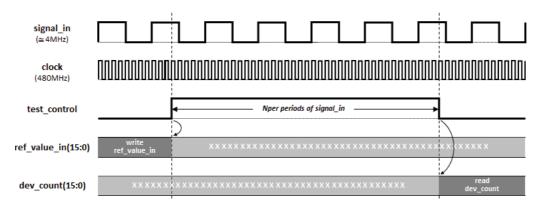

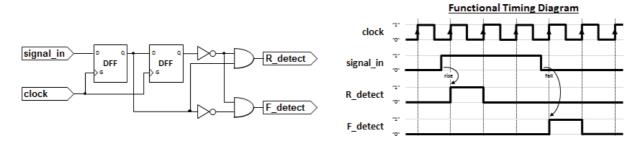

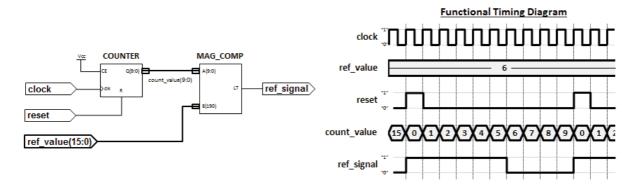

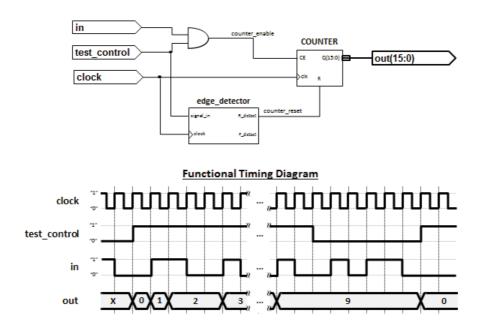

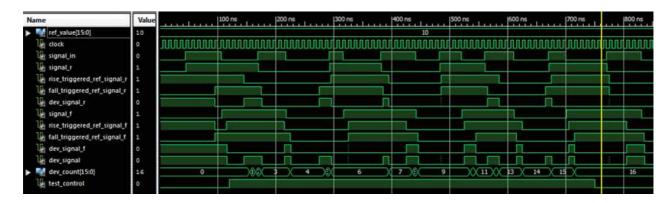

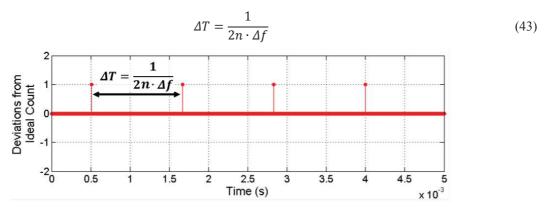

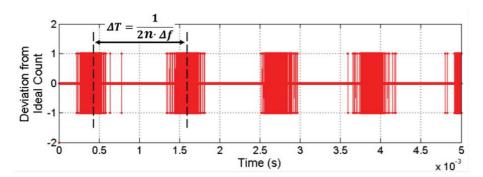

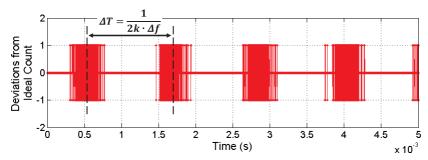

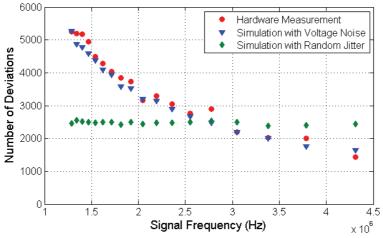

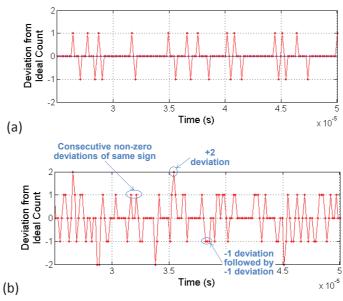

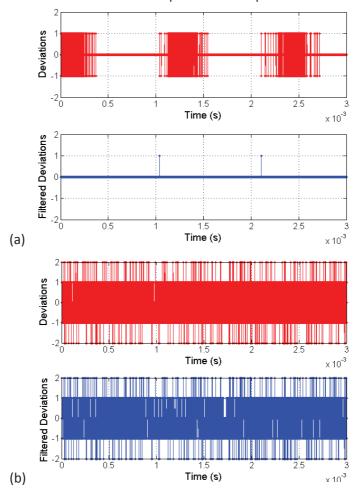

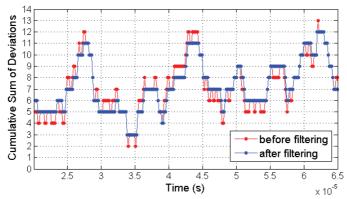

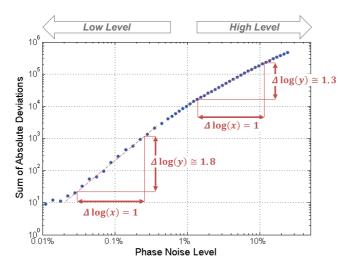

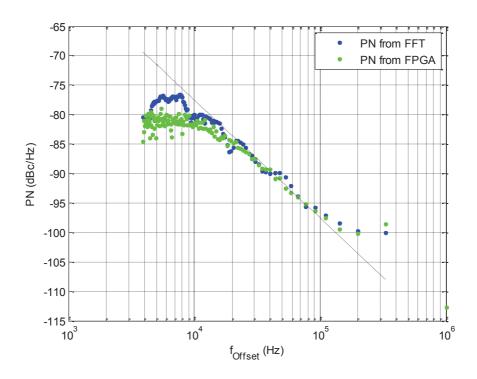

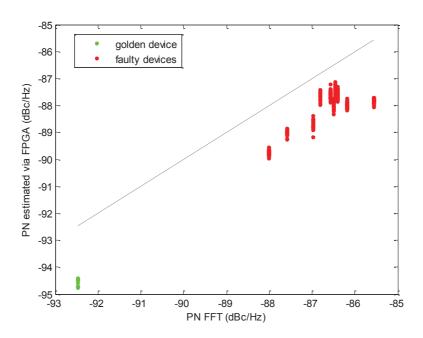

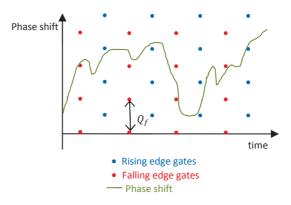

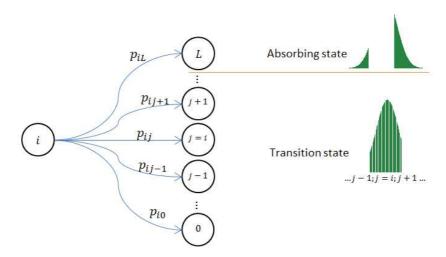

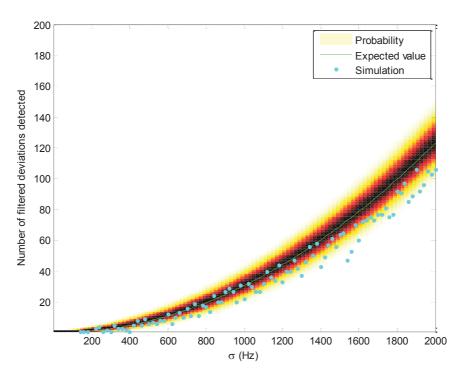

The main principle for generating such pulse train is based on the XOR-comparison between dedicated signals triggered by specific SUT transitions. As depicted in figure 3.11, it involves: