# Computational methods for event-based signals and applications

Xavier Lagorce

# ▶ To cite this version:

Xavier Lagorce. Computational methods for event-based signals and applications. Automatic. Université Pierre et Marie Curie - Paris VI, 2015. English. NNT: 2015PA066434 . tel-01592392v1

# HAL Id: tel-01592392 https://theses.hal.science/tel-01592392v1

Submitted on 24 Sep 2017 (v1), last revised 5 Oct 2017 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

# Spécialité : Robotique

École doctorale : "Sciences mécaniques, acoustique, électronique & robotique de Paris"

réalisée à l'

Institut de la Vision

présentée par

# **Xavier Lagorce**

pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ PIERRE ET MARIE CURRIE

Sujet de la thèse :

# Computational Methods for Event-Based signals and Applications

Dirigée par: Prof. Ryad Benosman

présentée et soutenue publiquement le 22 septembre 2015

|                 | Devant un Jury composé de | :                  |

|-----------------|---------------------------|--------------------|

| Prof.           | Elisabetta Chicca         | Rapporteur         |

| Prof.           | Bernabé Linares-Barranco  | Rapporteur         |

| Prof.           | Stéphane Viollet          | Examinateur        |

| Prof.           | Stéphane Régnier          | Examinateur        |

| Associate Prof. | Sio-Hoi Ieng              | Examinateur        |

| Prof.           | Ryad Benosman             | Directeur de thèse |

Institut de la Vision Université Paris 6 / INSERM / CNRS 17 rue Moreau, 75012 PARIS

T is during my Ph.D. on *Computational Methods for Event-Based signals and Applications* at the Vision Institute, that I have discovered the novel and exciting world of Neuromorphic Engineering. Coming from a standard signal processing and computer vision background, this new way of observing the world and its signals was a radical, but very rewarding experience.

When I joined Prof. Ryad Benosman's team back in 2011, the work on these new asynchronous, event-based sensors had just begun and almost everything was to be done. Since then, the team grew and took an important place in the field of event-based processing. The very exploratory work linked to this kind of adventure led me to play a role in a large number of very different projects which made no day look like another one.

These four years of Ph. D. were a formidable adventure which led to unforeseen territories and lots of uncharted lands. I also met several great collaborators during these years, some of them I am now proud to consider as friends.

I will not enumerate everybody who had an important impact during this period by fear of forgetting someone, but let them be thanked for all they did. I will nevertheless emphasize a few of them:

- *Mr. R.* for all his remarks on *not good enough*-sentences and figures and all these futurethingy we designed or thought of together,

- Michel for his advice about the aforementioned remarks,

- *Christoph* for his *perfect* sensor,

- Everybody from the *Vision Institute* and it's *Vision and Natural Computation* team for their input and all the good memories I will keep from spending time, working and having coffee with them,

- The paintball team for the pain I still feel when the weather is bad,

- Rancilio Silvia for real unending tweaking and experimentation,

- and *The Game* for hours of fun.

# Abstract

#### Computational Methods for Event-Based signals and Applications: abstract

Computational Neurosciences are a great source of inspiration for data processing and computation. Nowadays, how great the state of the art of computer vision might be, it is still way less performant that what our brains or the ones from other animals or insects are capable of. This thesis takes on this observation to develop new computational methods for computer vision and generic computation relying on data produced by event-based sensors such as the so called "silicon retinas".

These sensors mimic biology and are used in this work because of the sparseness of their data and their precise timing: information is coded into *events* which are generated with a microsecond precision. This opens doors to a whole new paradigm for machine vision, relying on time instead of using images. We use these sensors to develop applications such as object tracking or recognition and feature extraction. We also used computational neuromorphic platforms to better implement these algorithms which led us to rethink the idea of computation itself.

This work proposes new ways of thinking computer vision via event-based sensors and a new paradigm for computation. Time is replacing memory to allow for completely local operations, enabling highly parallel machines in a non-Von Neumann architecture.

### Méthodes de Calcul pour les Signaux Événementiels et Applications : résumé

Les neurosciences computationnelles sont une grande source d'inspiration pour le traitement de données. De nos jours, aussi bon que soit l'état de l'art de la vision par ordinateur, il reste moins performant que les possibilités offertes par nos cerveaux ou ceux d'autres animaux ou insectes. Cette thèse se base sur cette observation afin de développer de nouvelles méthodes de calcul pour la vision par ordinateur ainsi que pour le calcul de manière générale reposant sur les données issues de capteurs événementiels tels que les "rétines artificielles".

Ces capteurs copient la biologie et sont utilisés dans ces travaux pour le caractère épars de leurs données ainsi que pour leur précision temporelle : l'information est codée dans des *événements* qui sont générés avec une précision de l'ordre de la microseconde. Ce concept ouvre les portes d'un paradigme complètement nouveau pour la vision par ordinateur, reposant sur le temps plutôt que sur des images. Ces capteurs ont été utilisés pour développer des applications comme le suivi ou la reconnaissance d'objets ou encore de l'extraction de motifs élémentaires. Des plateformes de calcul neuromorphiques ont aussi été utilisées pour implémenter plus efficacement ces algorithmes, nous conduisant à repenser l'idée même du calcul.

Les travaux présentés dans cette thèse proposent une nouvelle façon de penser la vision par ordinateur via des capteurs événementiels ainsi qu'un nouveau paradigme pour le calcul. Le temps remplace la mémoire permettant ainsi des opérations complètement locales, ce qui permet de réaliser des machines hautement parallèles avec une architecture non-Von Neumann.

# Contents

| Co | Contents iii        |                |                                                                       | iii     |

|----|---------------------|----------------|-----------------------------------------------------------------------|---------|

| Li | List of Figures vii |                |                                                                       |         |

| In | trodu               | ction          |                                                                       | 1       |

| 1  | •                   |                | ous Event-Based Multi-kernel Algorithm for High Speed Visual Features |         |

|    |                     | king           |                                                                       | 5       |

|    | 1.1                 |                | action                                                                | 6       |

|    | 1.2                 |                | ncoded imaging                                                        | 6       |

|    | 1.3                 |                | xernel event-based features tracking                                  | 7       |

|    |                     | 1.3.1          | State of the Art                                                      | 8<br>8  |

|    |                     | 1.3.2<br>1.3.3 | Gaussian Blob tracking                                                | 8<br>10 |

|    |                     | 1.3.3          | Multi-kernel features tracking                                        | 10      |

|    |                     | 1.3.4          | Multi-target tracking                                                 | 12      |

|    |                     | 1.3.5          | Global algorithm                                                      | 13      |

|    | 1.4                 |                | S                                                                     | 14      |

|    | 1.4                 | 1.4.1          | Gaussian blob trackers                                                | 14      |

|    |                     | 1.4.2          | Gabor kernels                                                         | 17      |

|    |                     | 1.4.3          | Gabor combinations and general kernels                                | 17      |

|    |                     | 1.4.4          | Computational cost                                                    | 21      |

|    |                     | 1.4.5          | Retrieving feature scale and orientation                              | 22      |

|    | 1.5                 |                | ision and Discussion                                                  | 22      |

|    | 1.0                 | contra         |                                                                       |         |

| 2  | Spat                | iotempo        | oral Features for Asynchronous Event-based Data                       | 25      |

|    | 2.1                 | Introdu        | action                                                                | 26      |

|    | 2.2                 | Materia        | al and Methods                                                        | 27      |

|    |                     | 2.2.1          | Event-based asynchronous sensors                                      | 27      |

|    |                     | 2.2.2          | General architecture                                                  | 28      |

|    |                     | 2.2.3          | Signal pre-processing                                                 | 29      |

|    |                     | 2.2.4          | ESN layer – Input prediction                                          | 30      |

|    |                     | 2.2.5          | Winner-Take-All selection                                             | 31      |

|    |                     | 2.2.6          | Predictability minimization                                           | 32      |

|    | 2.3                 | Results        | S                                                                     | 33      |

|    |                     | 2.3.1          | Experimental setup                                                    | 33      |

|   |      | 2.3.2    | Single receptive field                                                    |

|---|------|----------|---------------------------------------------------------------------------|

|   |      | 2.3.3    | Multiple receptive fields                                                 |

|   |      | 2.3.4    | Complex input stimulus                                                    |

|   | 2.4  | Discus   | sion                                                                      |

|   |      |          |                                                                           |

| 3 | HO   |          | ierarchy Of event-based Time-Surfaces for pattern recognition 4.          |

|   | 3.1  | Introdu  | ction                                                                     |

|   | 3.2  | Event-o  | driven time-based vision sensors                                          |

|   | 3.3  | Model    | Description                                                               |

|   |      | 3.3.1    | Time-surface                                                              |

|   |      | 3.3.2    | Learning Time-surface prototypes                                          |

|   |      | 3.3.3    | Creating a Hierarchical Model                                             |

|   |      | 3.3.4    | Classification                                                            |

|   | 3.4  | Testing  | 5                                                                         |

|   |      | 3.4.1    | Flipped card deck recognition task                                        |

|   |      | 3.4.2    | Letters & Digits recognition task                                         |

|   |      | 3.4.3    | Face recognition task                                                     |

|   | 3.5  | Discuss  | sion                                                                      |

|   | 3.6  |          | sion                                                                      |

|   |      |          |                                                                           |

| 4 | A fr | amewor   | k for plasticity implementation on the SpiNNaker neural architecture 6    |

|   | 4.1  | Introdu  | ction                                                                     |

|   | 4.2  | Learnir  | ng in spiking platforms                                                   |

|   | 4.3  | A nove   | l framework for plasticity implementation on SpiNNaker                    |

|   |      | 4.3.1    | The Deferred Event Driven Model                                           |

|   |      | 4.3.2    | The Dedicated Plasticity Core Approach                                    |

|   | 4.4  | STDP     |                                                                           |

|   |      | 4.4.1    | Methods: Implementation of STDP on the Plasticity Core 7.                 |

|   |      | 4.4.2    | Results: pre-post pairing using a teacher signal                          |

|   |      | 4.4.3    | Results: balanced excitation                                              |

|   | 4.5  | BCM      | 7.                                                                        |

|   |      | 4.5.1    | Methods: Implementation of BCM on the Plasticity Core                     |

|   |      | 4.5.2    | Results: Emergence of orientation selectivity with BCM                    |

|   | 4.6  | Voltage  | e-gated STDP                                                              |

|   |      | 4.6.1    | Methods: Implementation of voltage-gated STDP on the plasticity core . 83 |

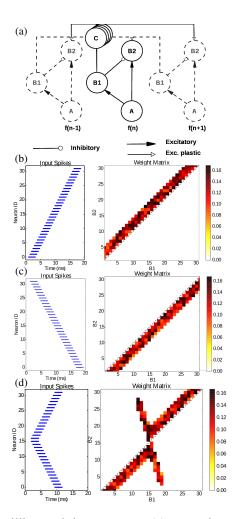

|   |      | 4.6.2    | Results: Learning temporal patterns                                       |

|   | 4.7  | Perform  | nance analysis and discussion                                             |

|   | 4.8  |          | sion                                                                      |

|   |      | 2100000  |                                                                           |

| 5 | Brea | aking Tł | e Millisecond Barrier On SpiNNaker 8                                      |

|   | 5.1  | Introdu  | ection                                                                    |

|   | 5.2  | The Sp   | iNNaker platform                                                          |

|   |      | 5.2.1    | Hardware                                                                  |

|   |      | 5.2.2    | Software                                                                  |

|   |      | 5.2.3    | Limitations of the current implementation                                 |

|   | 5.3  |          | beyond the millisecond                                                    |

|   |      | 0        |                                                                           |

|    | <b>5</b> 4 | 5.3.2 Neural models                                                                 | 94<br>95                                     |

|----|------------|-------------------------------------------------------------------------------------|----------------------------------------------|

|    | 5.4        |                                                                                     | 97                                           |

|    |            | 1                                                                                   | 98<br>)1                                     |

|    |            |                                                                                     | )1                                           |

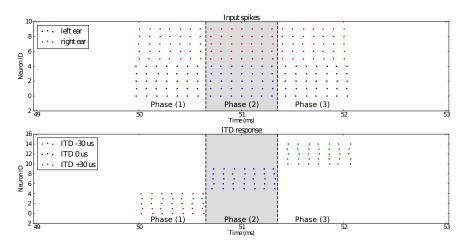

|    |            | 5.4.3 Detecting sub-millisecond spike synchrony in a model of sound localization 10 |                                              |

|    | 5 5        |                                                                                     | )5                                           |

|    | 5.5        | Discussion                                                                          | )7                                           |

| 6  | STI        | CK: Spike Time Interval Computational Kernel 10                                     | )9                                           |

|    | 6.1        | Introduction                                                                        | 10                                           |

|    | 6.2        | Methods                                                                             |                                              |

|    |            | 6.2.1 Neural model                                                                  |                                              |

|    |            | 6.2.2 Signal representation                                                         |                                              |

|    |            | 6.2.3 Storing data: memory                                                          |                                              |

|    |            | 6.2.4 Relational operations                                                         |                                              |

|    |            | 6.2.5 Linear operations                                                             |                                              |

|    |            | 1                                                                                   | 20                                           |

|    |            | 1                                                                                   | 20<br>26                                     |

|    | 6.3        | 1                                                                                   |                                              |

|    | 0.5        |                                                                                     |                                              |

|    |            | 1                                                                                   |                                              |

|    | 6.4        | 6.3.2 Lorenz attractor                                                              |                                              |

|    | 6.4        | Discussion                                                                          |                                              |

|    | 6.5        | Conclusion                                                                          | 34                                           |

| Di | scussi     | ion & Conclusion 13                                                                 | 35                                           |

| A  | List       | of publications 13                                                                  | 37                                           |

|    |            | Conference papers                                                                   |                                              |

|    | A.2        |                                                                                     |                                              |

| _  |            |                                                                                     |                                              |

| В  | List       | of patents 13                                                                       | <u> 59</u>                                   |

| С  | HOT        | <b>IS: Supplemental figures</b> 14                                                  | 41                                           |

| D  | STIC       | CK: Chronograms and detailled proofs 14                                             | <b>1</b> 9                                   |

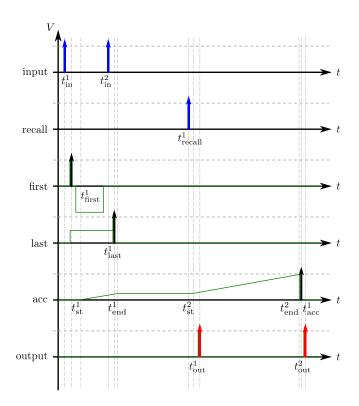

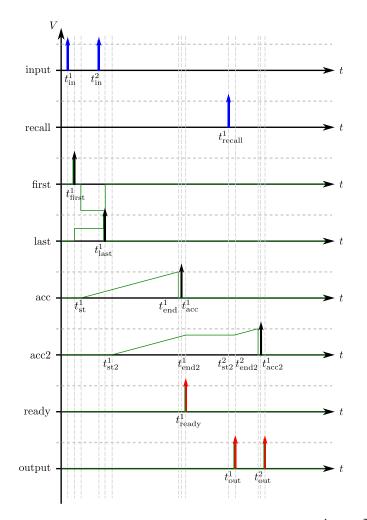

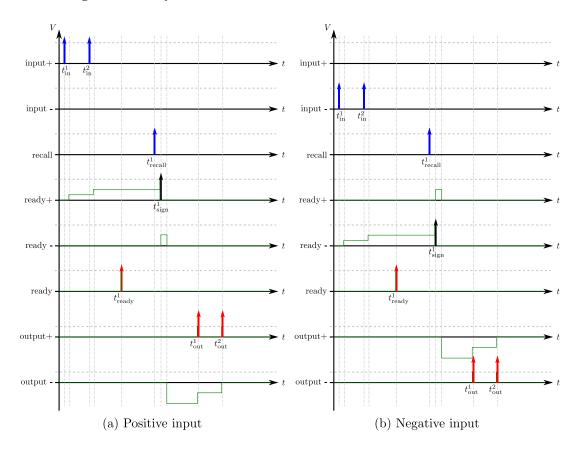

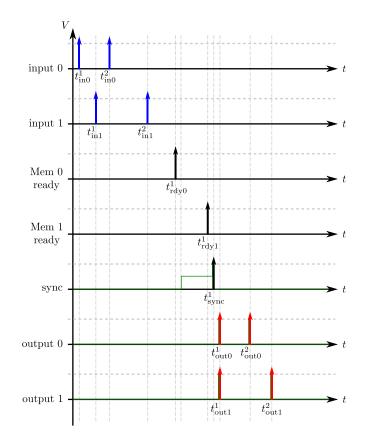

|    | D.1        |                                                                                     | 19                                           |

|    |            |                                                                                     | 19                                           |

|    |            | D.1.2 Memory                                                                        |                                              |

|    |            | D.1.3 Signed Memory                                                                 |                                              |

|    |            | D.1.4 Synchronizer                                                                  |                                              |

|    | D 2        | Relational operations   15                                                          |                                              |

|    | D.2        |                                                                                     | 54<br>54                                     |

|    |            |                                                                                     |                                              |

|    | D 2        |                                                                                     |                                              |

|    | D.3        | 1                                                                                   |                                              |

|    |            | D.3.1 Subtractor                                                                    |                                              |

|    |            | D.3.2 Linear Combination 15                                                         | <u>,</u> ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| bliogr | aphy   |                   | 169 |

|--------|--------|-------------------|-----|

|        | D.4.3  | Multiplier        | 164 |

|        | D.4.2  | Exponential       | 163 |

|        | D.4.1  | Natural Logarithm | 161 |

| D.4    | Non-li | near operations   | 161 |

# Bibliography

# **List of Figures**

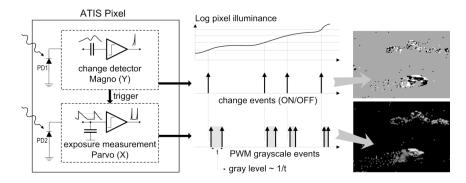

| 1.1        | Functional diagram of an ATIS pixel                                                            |

|------------|------------------------------------------------------------------------------------------------|

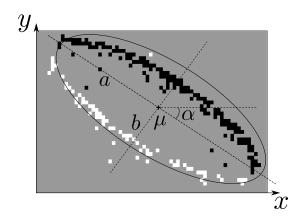

| 1.2        | Error ellipse of a Gaussian tracker                                                            |

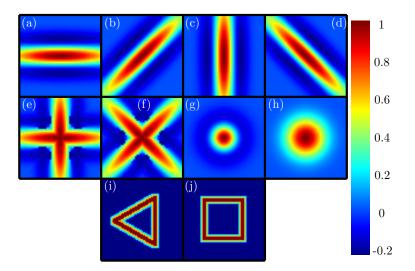

| 1.3        | Examples of kernels used for tracking 11                                                       |

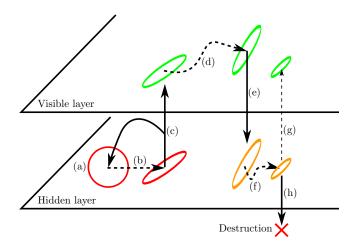

| 1.4        | Activation scheme of trackers                                                                  |

| 1.5        | Evolution of a tracker's state during its lifecycle                                            |

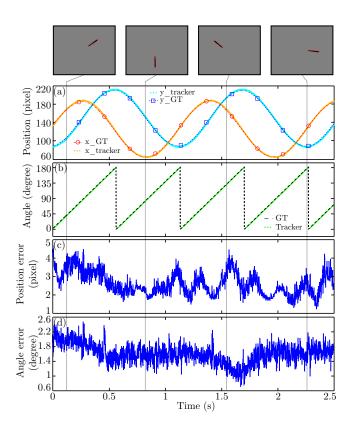

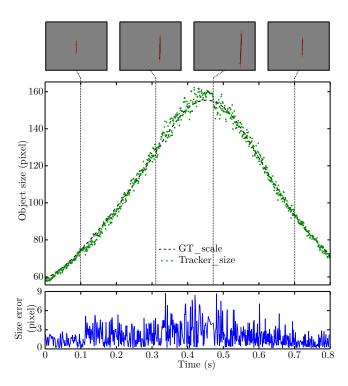

| 1.6        | Gaussian tracker accuracy in position and angle                                                |

| 1.7        | Gaussian tracker accuracy in size                                                              |

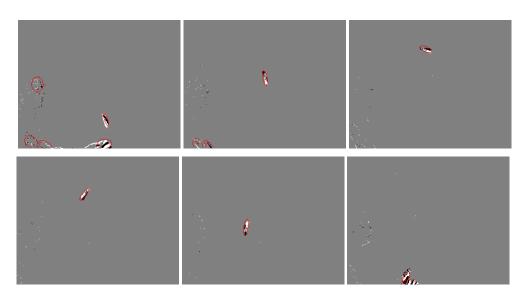

| 1.8        | Gaussain blob tracker following a pen thrown in the air                                        |

| 1.9        | Gabor trackers following a pen thrown in the air                                               |

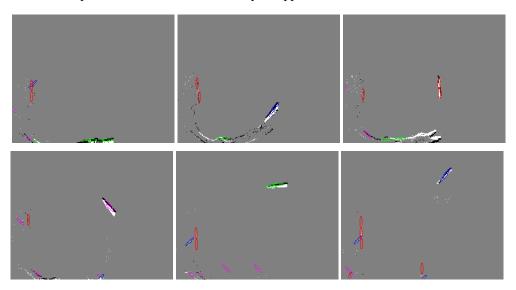

| 1.10       | Tracking results for example kernels                                                           |

| 1.11       | Tracking error with arbitrary kernel 20                                                        |

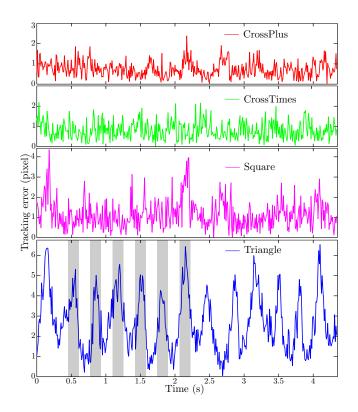

| 1.12       | Tracking error of all used features 21                                                         |

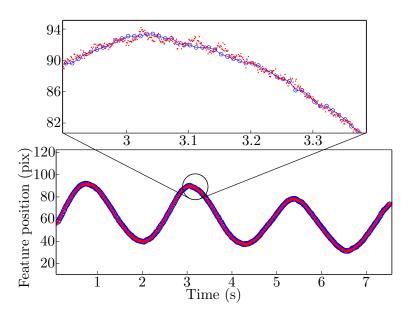

| 1.13       | Tracking error with a triangle kernel                                                          |

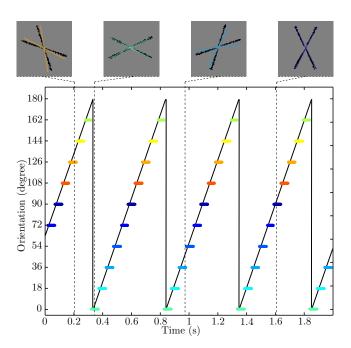

| 1.14       | Continuous tracking of a rotating cross                                                        |

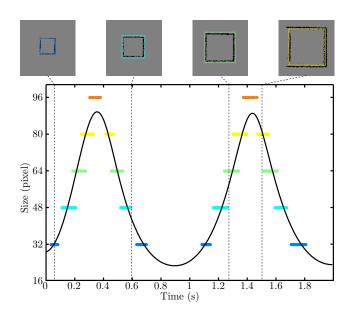

| 1.15       | Continuous tracking of a moving square                                                         |

| 0.1        |                                                                                                |

| 2.1        | Architecture for unsupervised spatiotemporal feature extraction                                |

| 2.2        | signal pre-processing to convert DVS events into equivalent analog input for ESNs 29           |

| 2.3        | Experimental recording setup                                                                   |

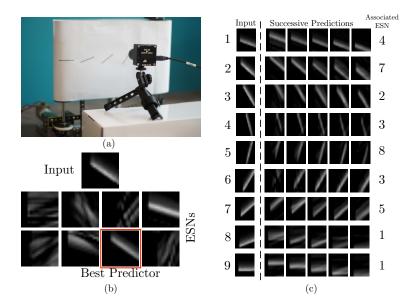

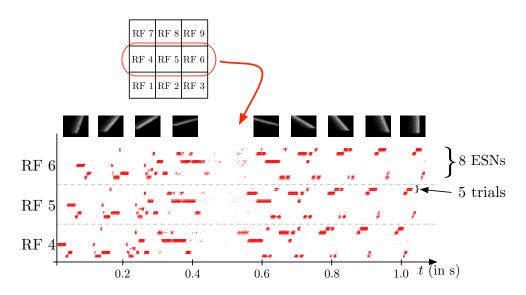

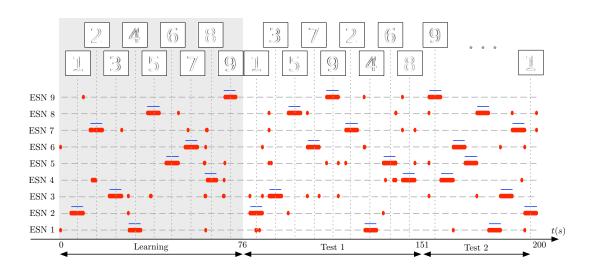

| 2.4        | Output of the WTA network during repeated presentation of a series of nine input patterns      |

| 25         | 1                                                                                              |

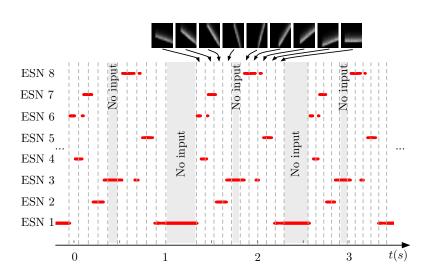

| 2.5        | Prediction error of the 8 ESNs during several presentations of the input stimulus . 34         |

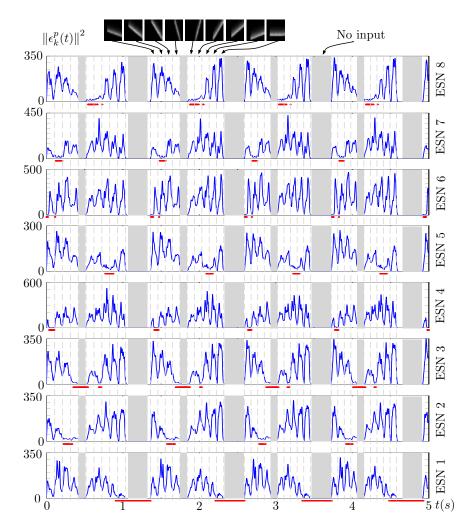

| 2.6        | Predictions of the ESNs with multiple receptive fields                                         |

| 2.7        | Spike output for the WTA neurons corresponding to the eight ESNs for each of the 3 central RFs |

| 20         |                                                                                                |

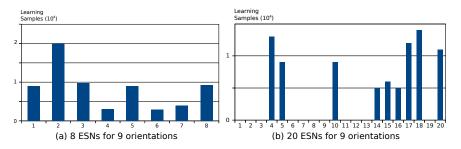

| 2.8        | Number of learning samples per reservoir for two different architectures 37                    |

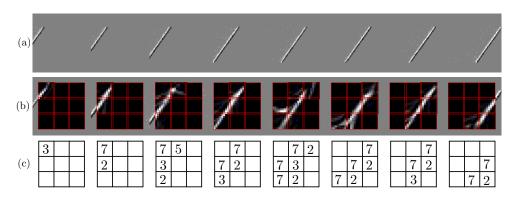

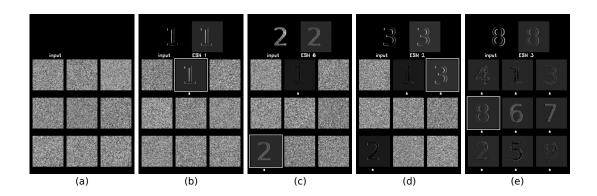

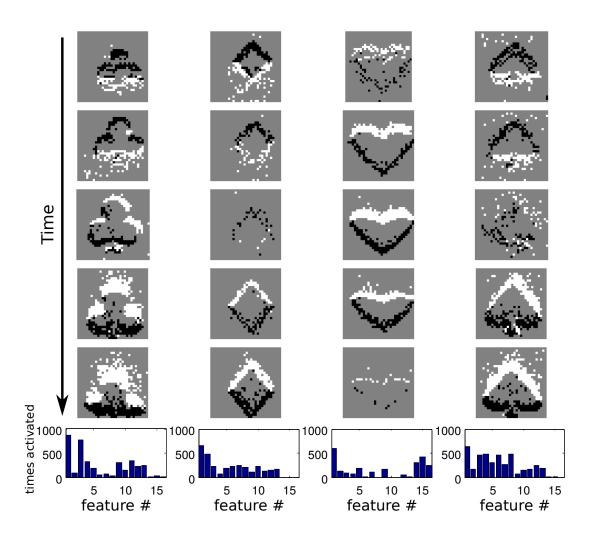

| 2.9        | Learning process of more complex feature detectors                                             |

| 2.10       | Results for complex features from DVS inputs                                                   |

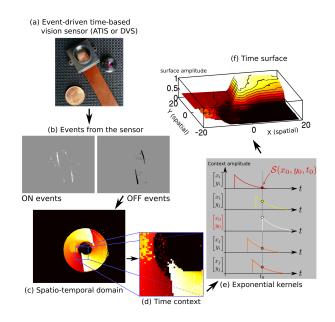

| 3.1        | Definition of a time-surface from the spatio-temporal cloud of events                          |

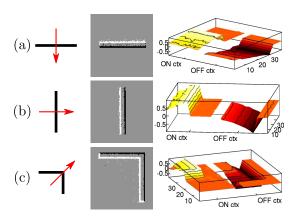

| 3.2        | Examples of some time-surfaces for simple movements of objects                                 |

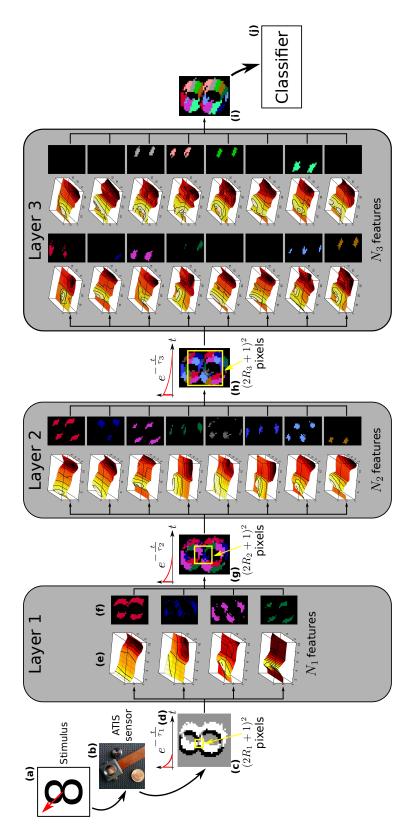

| 3.3        | View of the proposed hierarchical model                                                        |

| 3.4        |                                                                                                |

|            | Flipped cards experiments: Pattern database                                                    |

| 3.5        | 11 1                                                                                           |

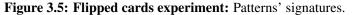

| 3.5<br>3.6 | Flipped cards experiment: Patterns' signatures                                                 |

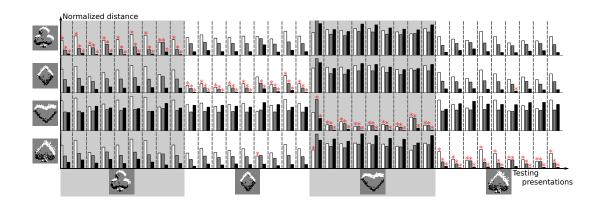

|            | Flipped cards experiment: Patterns' signatures                                                 |

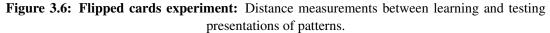

| 3.8        | Letters & Digits experiment: Pattern signatures                             | 56       |

|------------|-----------------------------------------------------------------------------|----------|

| 3.9        | Letters & Digits experiment: Results                                        | 57       |

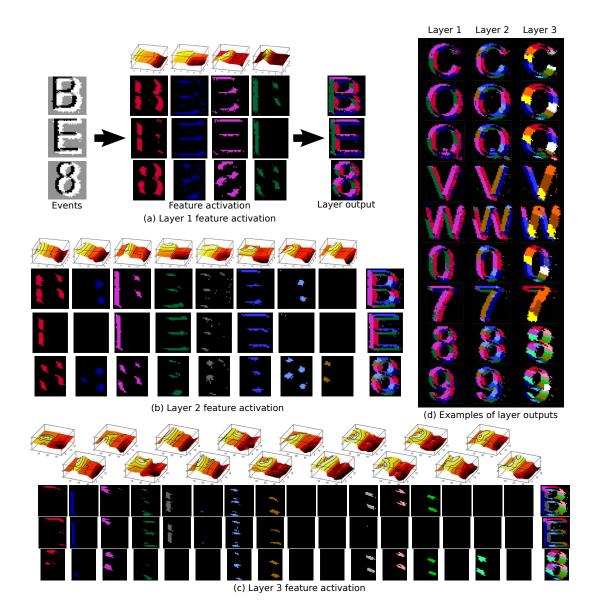

| 3.10       | Letters & Digits experiment: Activation of features in the different layers | 58       |

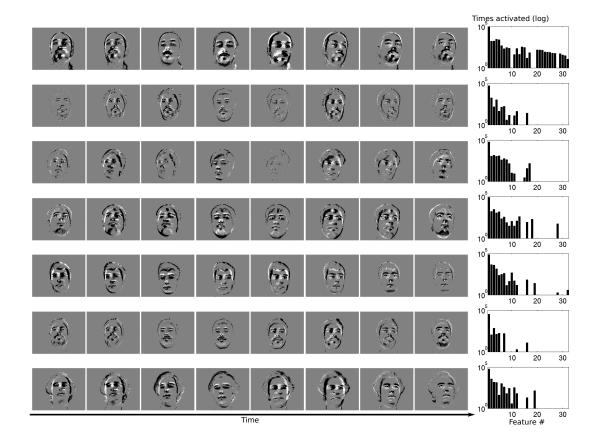

| 3.11       | Faces recognition experiment: Pattern database and signatures               | 60       |

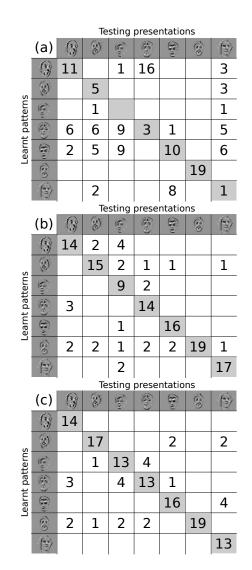

| 3.12       | Face recognition experiment: Results                                        | 61       |

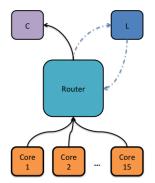

| 4.1        |                                                                             | 70       |

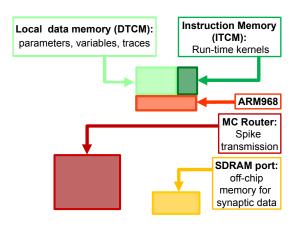

| 4.1        | High-level view of the SpiNNaker chip                                       | 70       |

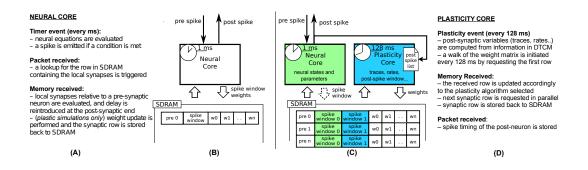

| 4.2        | STDP implementation on SpiNNaker                                            | 71       |

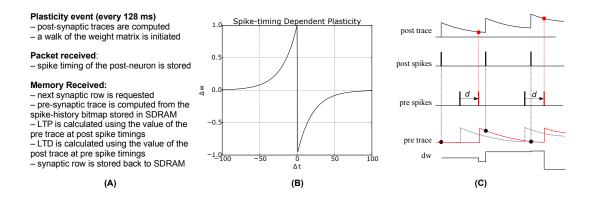

| 4.3        | STDP algorithm                                                              | 74       |

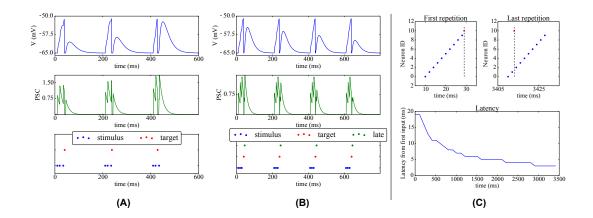

| 4.4        | Shift of post-synaptic firing onset via STDP                                | 76       |

| 4.5        | STDP with a teacher signal                                                  | 77       |

| 4.6        | Competition between synapses undergoing STDP                                | 78       |

| 4.7        | Implementation of BCM plasticity                                            | 79       |

| 4.8        | Emergence of orientation selectivity with the BCM learning rule             | 80       |

| 4.9        | Implementation of voltage-gated STDP                                        | 81       |

| 4.10       | Learning temporal patterns                                                  | 83       |

| 4.11       | Performance evaluation of the three implemented learning rules              | 85       |

| 5.1        | SpiNNaker system overview                                                   | 91       |

| 5.1<br>5.2 |                                                                             | 91       |

| 5.2<br>5.3 | Working principle of the PSP buffers                                        | 93<br>99 |

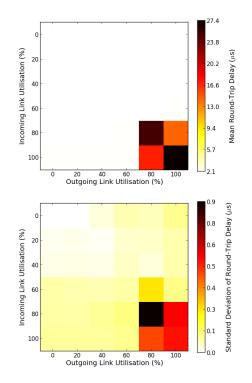

|            | Topology for the intra-chip packet latency test                             |          |

| 5.4        | Intra-chip lantency results                                                 | 100      |

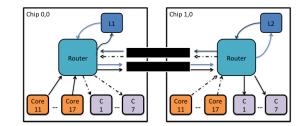

| 5.5        | Topology used for inter-chip packet latency test                            | 101      |

| 5.6        | Inter-chip lantency results                                                 | 102      |

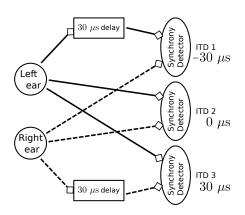

| 5.7        | Model used to detect sub-millisecond spike synchrony for sound localization | 104      |

| 5.8        | ITD experiment results                                                      | 105      |

| 5.9        | Learning sub-millisecond time patterns                                      | 106      |

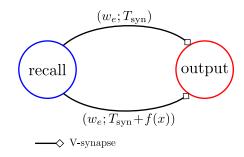

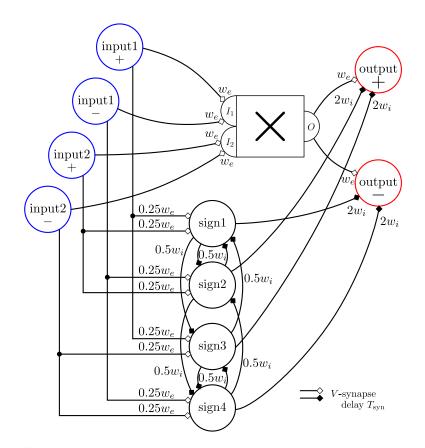

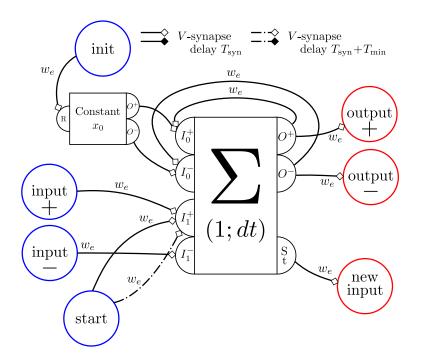

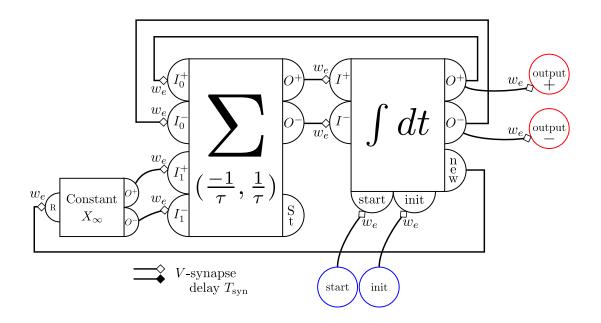

| 6.1        | Constant-value network                                                      | 113      |

| 6.2        | Inverting Memory network                                                    | 114      |

| 6.3        | Inverting Memory chronogram                                                 | 115      |

| 6.4        | Memory network                                                              | 116      |

| 6.5        | Signed Memory network                                                       | 117      |

| 6.6        | Synchronizer network                                                        | 118      |

| 6.7        | Minimum network                                                             | 119      |

| 6.8        | Maximum network                                                             | 120      |

| 6.9        | Substractor network (simple)                                                | 120      |

|            | Substractor network (full)                                                  | 121      |

|            | Linear Combination network                                                  | 122      |

|            |                                                                             |          |

|            | Log network                                                                 | 124      |

|            | Exp network                                                                 | 124      |

|            | Multiplier network                                                          | 126      |

|            | Signed Multiplier network                                                   | 127      |

|            | Integrator network                                                          | 128      |

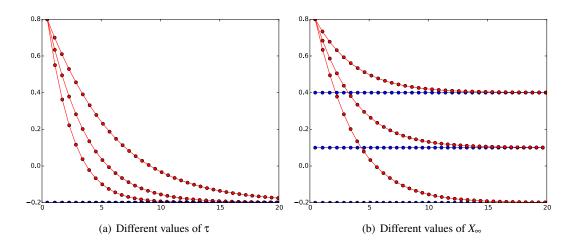

|            | Network for the implementation of a first order differential equation       | 129      |

|            | Results of simulating a first order differential equation                   | 129      |

| 6.19       | Network for the implementation of a second order differential equation      | 130      |

| 0.20                            | Results of simulating a second order differential equation                     | 130                             |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------------|

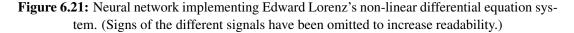

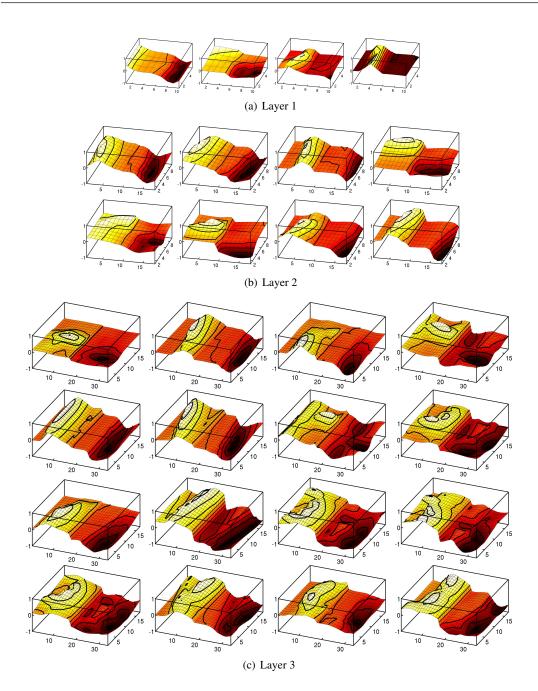

| 6.21                            | Network implementing Edward Lorenz's non-linear differential equation system . | 131                             |

| 6.22                            | Results of simulating Edward Lorenz's non-linear differential equation system  | 132                             |

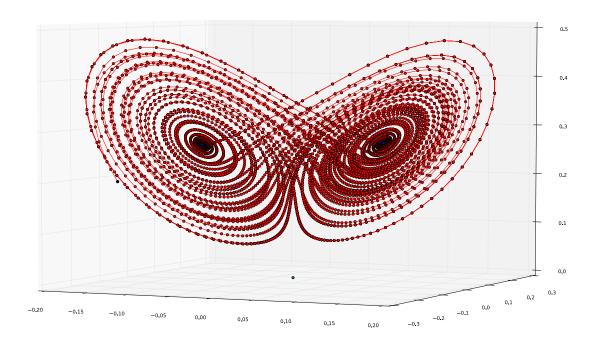

| C.1                             | Flipped cards experiment: Reconstructed features                               | 142                             |

| C.2                             | Letters & Digits experiment: Reconstructed features                            | 143                             |

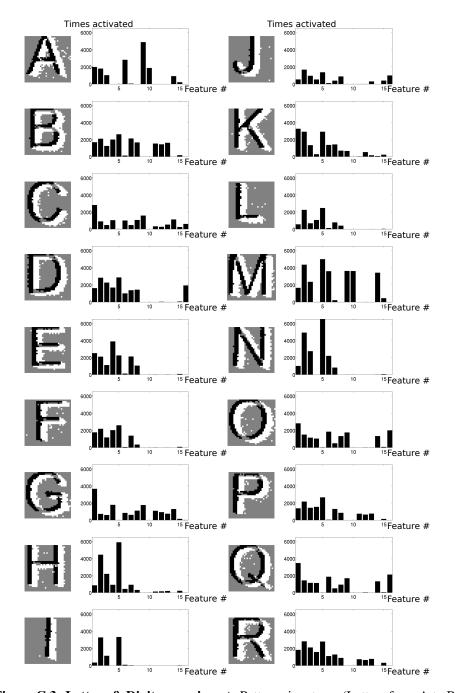

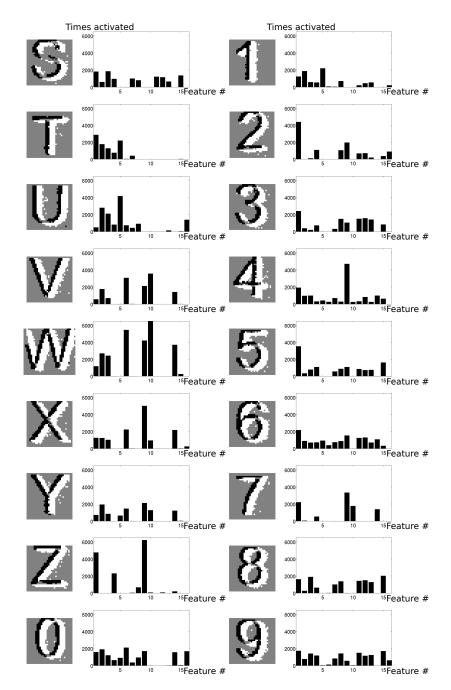

| C.3                             | Letters & Digits experiment: Signatures for letters from A to R                | 144                             |

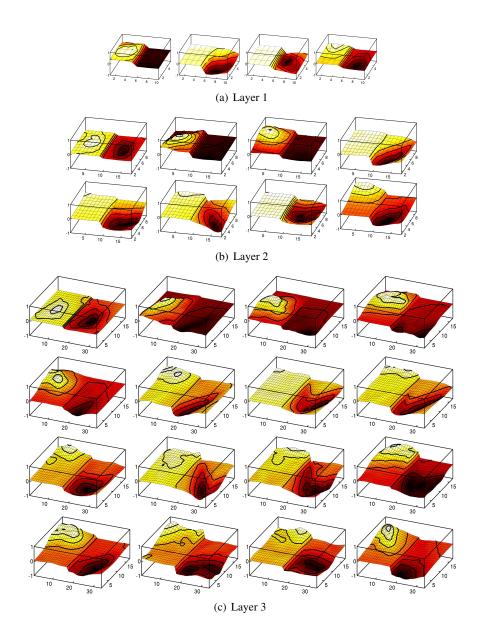

| C.4                             | Letters & Digits experiment: Signatures for letters from S to Z and digits     | 145                             |

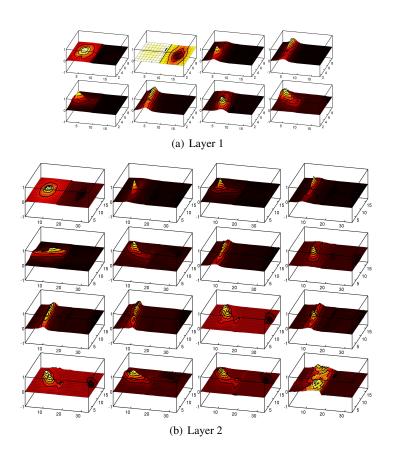

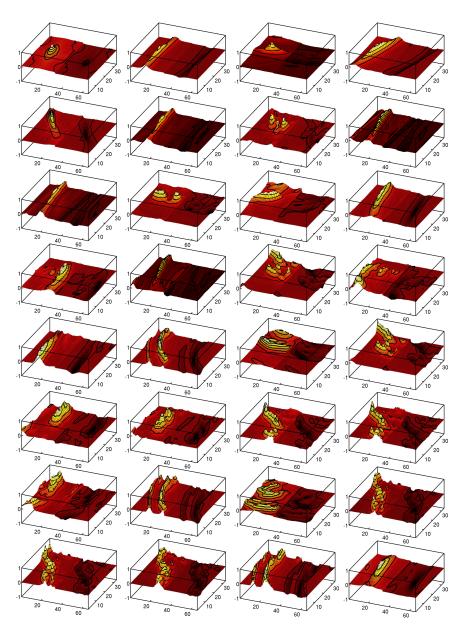

| C.5                             | Face recognition experiment: Reconstructed features for layer 1 and 2          | 146                             |

| C.6                             | Face recognition experiment: Reconstructed features for layer 3                | 147                             |

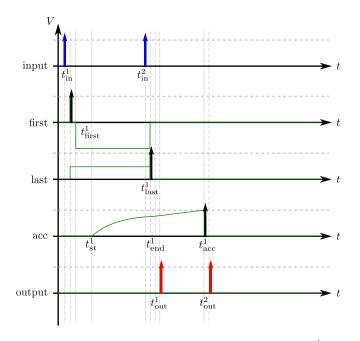

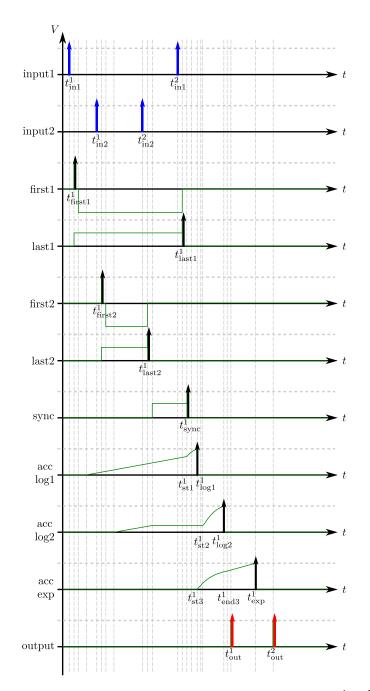

| D.1                             | Inverting Memory chronogram                                                    | 150                             |

| D.2                             | Mamanushranagram                                                               |                                 |

| D.2                             | Memory chronogram                                                              | 151                             |

| D.2<br>D.3                      | Signed Memory chronogram                                                       | 151<br>153                      |

|                                 |                                                                                | -                               |

| D.3                             | Signed Memory chronogram                                                       | 153                             |

| D.3<br>D.4                      | Signed Memory chronogramSynchronizer chronogram                                | 153<br>155                      |

| D.3<br>D.4<br>D.5               | Signed Memory chronogram                                                       | 153<br>155<br>156               |

| D.3<br>D.4<br>D.5<br>D.6        | Signed Memory chronogram                                                       | 153<br>155<br>156<br>157        |

| D.3<br>D.4<br>D.5<br>D.6<br>D.7 | Signed Memory chronogram                                                       | 153<br>155<br>156<br>157<br>158 |

Computational Methods for Event-Based signals and Applications

X

# Introduction

INCE the late 1980s with the work of Carver Mead [1, 2, 3], the field of Neuromorphic Engineering has been a growing field focusing on several applications [4, 5, 6, 7, 8], from auditory processing to vision and processing chips. This Ph.D. work is however mainly focused on biomimetic event-driven time-based vision sensors such as the ones developped in [9, 10].

Event Based cameras - like the biological retina - are driven by *events* happening within the visual scene instead of artificially created timings like conventional vision sensors. When my Ph.D. work started, we were using the DVS silicon retina [11] to begin exploring this frame-less acquisition principle. We started rapidly rethinking and translating standard computer vision algorithms from the *conventional* concept of frames to a pure time based framework.

During this work, it became clear that a deep understanding of the sensor was necessary to develop robust processing event based techniques. We were then joined by chip designers who had been developing their own silicon retina: the ATIS [12, 13]. My involvement in the prototyping of the different versions of the ATIS PCB enabled me to know more about the chip and brought me useful insights in its principle of operations. This also fueled the idea of developing a multithreaded software architecture to develop algorithms for these cameras. This led to the development of kAER, a SDK able to manage event based processing, easy prototyping and realtime implementation of all the algorithms developed in the team. During my Ph.D., I continued updating and improving the software, until its recent acquisition by the Lab's spinoff Chronocam.

The beginning of my Ph.D. was focused on tracking moving object and defining some new kind of features adapted to event-based signals.

In Chapter 1, we focus on object tracking and introduce two methods using the dynamic content of a stream of events produced by an asynchronous camera such as the DVS or the ATIS. The change detection properties of the sensor natively allow these techniques to be very robust to different lighting conditions thus allowing unprecedented performances.

The first technique introduced in this work is to approximate cluster of events by mathematical objects such as Gaussian shapes. It enables to simultaneously track the position and the shape of an object in the focal plane.

The second technique extends the method to any arbitrary kernel. The process only needs few requirements to operate. The trackers are then not only tracking objects but are also detecting shapes in the field of view of the sensor. This detection is made possible by the organization of the trackers in a pool. Prototypes of trackers are covering the whole focal plane, ready to track an object that would match their kernels. If such an object is detected, the tracker gets activated and

starts following this particular object or feature in the scene until it disappears and the tracker is destroyed. Very low computational power is needed by each tracker, this then allows to compute in real-time a larger number of such trackers. Several pools of trackers can be used at the same time to either track different objects or different scales of the same object.

In the work of Chapters 2 and 3, we focused on feature extraction. Similarly to existing computer vision concepts, common feature extraction techniques are adapted to frames, and more than not being directly applicable on events, they completely ignore the dynamics of a scene. Exploiting both spatial and temporal information contained in the output of neuromorphic sensors was then a key point of the features we have developped.

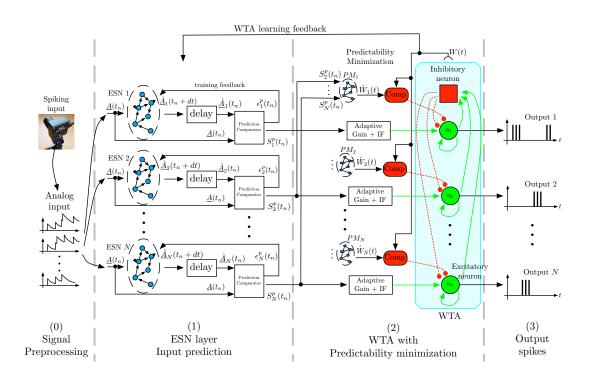

In Chapter 2, we use an unsupervised neural network based on a set of Echo-State Networks (ESN). These recurrent neural networks are capable of extracting dynamics from their input. The proposed architecture consists of a number of these networks where events are sent to their inputs. Each ESN goal is to predict the evolution of its input. ESN also compete, only the best predictor is allowed to learn the presented input at a given time. This selection process results in the specialization of each network in the prediction of particular patterns. One can then deduce the presence of a particular pattern, or feature, in the input scene when a given network is selected. Because of the recurrent connections of the ESNs, the extracted feature is not only spatial but also temporal.

In Chapter 3, we pushed the idea further by directly including this temporal information in a representation of the events. Each input spike from the sensor is associated to a *context* describing the recent history of its neighboring pixels. All contexts can be clustered in an unsupervised manner around a given number of centers. These centers can then be seen as a set of spatio-temporal features describing the scene that the camera is looking at. From these, it is possible to build a hierarchical architecture relying on several layers of such context building and clustering. This increases the complexity of the contexts by increasing their timescale and spatial size. At the end, the feature activation of the last layer of this architecture contains a high-level spatio-temporal information about the presented stimuli.

The proposed algorithms are very promising and well adapted to the event-based representation of the visual information produced by neuromorphic cameras. However, they are not well suited for computation on standard computers. Their local properties and asynchronous nature allow them to be natural candidates for highly-parallel platforms. Standard off-the-shelf computers are mostly linear pipelines processing all the input events sequentially. This lack of adequation between our algorithms and the platforms used to implement them motivated us to start looking in other directions. The first step was to find new computing platforms, highly-parallel and as asynchronous as possible. A good candidate is the SpiNNaker platform [14]. This platform is consituted of numerous small processors (the final version aims at embedding 1 million processors) linked together on a fabric designed for high-speed communication of small packet, from one end of the system to another. To enable fast prototyping with this platform, the SpiNNaker team provides a SDK allowing to implement neural networks and to configure a SpiNNaker machine. Unfortunately, the available SDK did not cover all our needs, we therefore started exploring and extending the SDK ourselves. This is the main focus of the 2 following chapters.

In Chapter 4, we worked on an improvement of the implementation of plasticity implementation on SpiNNaker, learning having such a central part in several of our algorithms. Instead of mixing the code simulating neural populations and the code managing synaptic weights in the network, we separated the two in different processors. This allows to optimize the memory accesses

#### Introduction

needed to route spikes between cores for simulating the network itself and the ones needed to update the weights and connections. The capabilities of this method were demonstrated on several examples of the literature and results show a large improvement over the standard implementation of plasticity provided with the official SpiNNaker software.

In Chapter 5, we tackled the problem of time resolution. When designing the official SpiN-Naker software, the choice was made to simulate all the neural networks with a millisecond time precision as a trade-off between several constraints of the machine. This is enough for lots of applications but very limiting for others such as auditory applications. Sound localization for instance, requires a time precision in the order of the hundred of microseconds or less. After characterizing the time constraints of the communication fabric of the SpiNNaker machines, we proposed a new implementation of the simulation infrastructure to obtain fully asynchronous models which can then cope with a microsecond time resolution. To continue on what was achieved in the previous chapter, plasticity was also reimplemented using these time scales.

Being able to use such a highly-parallel platform as SpiNNaker brought us a very interesting insights into the problems encountered with such systems. It was clear, we had to go further and take another step forward. Taking standard processors and linking them together, even as smartly as the SpiNNaker team does is not enough. The machine itself has to be thought again.

#### No more memory, only time.

This is the focus of Chapter 6. Using a time-based representation of data and neuron-like units (using the same principles and basic rules as biological neurons), we derive neural-like circuits able to compute using data expressed as time intervals. This lays the development of a non von Neumann architecture of a neuromorphic computer. The framework uses spiking neurons to store data, compute any linear or non linear operators and relational tools. From there any algorithm can be implemented easily. The computing system is parallel, neuromorphic and it produces data only when necessary. This framework offers a way to systematically *program* large neural circuits.

All of the chapters presented in this document have led to publications [15, 16, 17, 18] as well as many rewarding collaborations [19, 20, 21, 22, 23]. A full list of publications, including some not yet published papers can be found in Appendix A as well as a list of patents related to the work I have done during my Ph.D. in Appendix B.

# Chapter 1

# Asynchronous Event-Based Multi-kernel Algorithm for High Speed Visual Features Tracking

This chapter presents a number of new methods for visual tracking using the output of an event-based asynchronous neuromorphic dynamic vision sensor. It allows the tracking of multiple visual features in real-time, achieving an update rate of several hundred kilohertz on a standard desktop PC. The approach has been specially adapted to take advantage of the event-driven properties of these sensors by combining both spatial and temporal correlations of events in an asynchronous iterative framework. Various kernels, such as Gaussian, Gabor, combinations of Gabor functions and arbitrary user-defined kernels are used to track features from incoming events. The trackers described in this work are capable of handling variations in position, scale and orientation through the use of multiple pools of trackers. The tracking performance was evaluated experimentally for each type of kernel in order to demonstrate the robustness of the proposed solution.

# Contents

| 1.1 | Introduction                               |                                                     | 6  |

|-----|--------------------------------------------|-----------------------------------------------------|----|

| 1.2 | Time encoded imaging                       |                                                     | 6  |

| 1.3 | Multi kernel event-based features tracking |                                                     |    |

|     | 1.3.1                                      | State of the Art                                    | 8  |

|     | 1.3.2                                      | Gaussian Blob tracking                              | 8  |

|     | 1.3.3                                      | Multi-kernel features tracking                      | 10 |

|     | 1.3.4                                      | Multi-target tracking                               | 12 |

|     | 1.3.5                                      | Mutual repulsion and attraction to initial position | 13 |

|     | 1.3.6                                      | Global algorithm                                    | 14 |

| 1.4 | Result                                     | ts                                                  | 14 |

|     | 1.4.1                                      | Gaussian blob trackers                              | 17 |

|     | 1.4.2                                      | Gabor kernels                                       | 17 |

|     | 1.4.3                                      | Gabor combinations and general kernels              | 17 |

|     | 1.4.4                                      | Computational cost                                  | 21 |

|     | 1.4.5                                      | Retrieving feature scale and orientation            | 22 |

| 1.5 | Concl                                      | usion and Discussion                                | 22 |

# **1.1 Introduction**

6

Visual object recognition and tracking is useful in many applications, such as video surveillance, traffic monitoring, motion analysis, augmented reality and autonomous robotics. Most object tracking techniques rely on sequences of static frames which limits algorithmic efficiency when dealing with highly dynamic scenes. Conventional frame-based video cameras can acquire data at frequency as high as several tens of kilohertz, nevertheless this amount of data remains difficult to process in real-time due to the large amount of redundant acquired information. Real-time processing at high acquisition rates usually requires different techniques such as: sub-sampling of the field of view [24], the use of specific hardware implementations or a restriction to simple tracking algorithm such as image's centroid and moments computation [25].

This chapter presents an event-based approach to fast visual tracking of features using the output of an asynchronous neuromorphic event-based camera. Neuromorphic cameras (sometimes called silicon retinas) mimic the biological visual systems [10][9]. The Asynchronous Time-based Image Sensor (ATIS) camera used in this work reacts to changes of scene contrast and records only dynamic information, thus reducing the data quantity [13][12]. The presented algorithms rely on the change detection circuit of the ATIS, namely it only deals with relative change events. It can also be applied to other sensors such as the Dynamic Vision Sensor (DVS) [9] on which the ATIS is based.

The presented tracking algorithm is computationally inexpensive and is thus capable of tracking objects and updating their properties at rates in the order of hundreds of kilohertz. Firstly, an asynchronous event-based Gaussian blob tracking algorithm is developed and examined. The properties of the Gaussian kernel allow adaptation to the events' spatial distribution by continuously correcting the Gaussian size, orientation and location with each incoming event. This provides the object's position, size, and orientation simultaneously. In a second stage, the model is extended by using oriented Gabor kernels that allow tracking specific oriented edges. This work also considers the combination of several oriented kernels that are useful in tracking specific focal plane structures such as corners. Finally, a general kernel approach is presented. It can use almost any arbitrary kernel and can be seen as a generalization of the process, with the only constraint that their center of mass has to be aligned with the center of the kernels (see section 1.3.3.4).

# **1.2** Time encoded imaging

Biomimetic event-driven time-based vision sensors are a novel class of vision device that - like the biological retina - are driven by "events" happening within the visual scene. They are not like conventional vision sensors, which are driven by artificially created timing and control signals (e.g. frame clock) that have no relation whatsoever to the source of the visual information [26]. Over the past few years, a variety of these event-based devices has been developed, including temporal contrast vision sensors that are sensitive to relative luminance change [13, 27, 26], gradient-based sensors sensitive to static edges [28], and optical-flow sensors [29]. Most of these vision sensors output visual information about the scene in the form of asynchronous address events using the Address Event Representation (AER) protocol [30] and encode the visual information in the time dimension rather than as a voltage, charge, or current. The presented pattern tracking method is designed to work on the data delivered by such a time-encoding sensor and takes full advantage of the high temporal resolution and the sparse data representation.

The ATIS used in this work is a time-domain encoding vision sensors with 304x240 pixels resolution. [12]. The sensor contains an array of fully autonomous pixels that combine an illuminance relative change detector circuit and a conditional exposure measurement block.

Figure 1.1: Functional diagram of an ATIS pixel [13]. Two types of asynchronous events, encoding change and brightness information, are generated and transmitted individually by each pixel in the imaging array.

As shown in the functional diagram of the ATIS pixel in Fig. 1.1, the relative change detector individually and asynchronously initiates the measurement of an exposure/gray scale value only if - and immediately after - a brightness change of a certain magnitude has been detected in the field-of-view of the respective pixel. The exposure measurement circuit in each pixel individually encodes the absolute instantaneous pixel illuminance into the timing of asynchronous event pulses, represented as inter-event intervals.

Since the ATIS is not clocked like a conventional camera, the timing of events can be conveyed with a very accurate temporal resolution in the order of microseconds. The time-domain encoding of the intensity information automatically optimizes the exposure time separately for each pixel instead of imposing a fixed integration time for the entire array, resulting in an exceptionally high dynamic range and improved signal to noise ratio. The pixel-wise change detector driven operation yields almost ideal temporal redundancy suppression, resulting in a maximally sparse encoding of the image data.

In what follows we will rely only on change detector events as the timings of events is the main needed information to perform tracking.

# 1.3 Multi kernel event-based features tracking

This section describes the tracking algorithms developped in this work. After reviewing the state of the art of asynchronous tracking using event-base silicon retinas, we describe how bivariate normal distributions are used to track clouds of events. Then, we will generalize our approach to more arbitrary kernels. The next two sub-sections tackle the problem of tracking several objects at once in a scene and how several trackers interact with one another in a pool mechanism. To conclude this section, a global algorithm is presented and a number of possible optimizations are proposed.

### **1.3.1** State of the Art

8

Image segmentation, feature extraction, optical flow and high level motion filters are usually used to track moving objects but they are known to be computationally expensive tasks. Real-time processing with frame rates reaching several hundreds of hertz can lead to more robust tracking algorithms [31]. However, it is currently an almost impossible task to perform such tasks in real-time unless dedicated hardware is used. Dedicated hardware solutions introduce additional implementation complexity that limits the efficiency of such vision algorithms. Processing at such a high frame rate is only applicable for tackling simple tasks such as the detection of the center of mass (or centroid) of moving objects [32, 33].

The newly developed event-based silicon retinas (Dynamic Vision Sensor [26], Asynchronous Time-based Image Sensor [13]) inspired by the physiology of biological retinas are promising sensors for fast vision applications. These sensors convey a sparse stream of asynchronous time-stamped events suitable for object tracking as only dynamic information is captured. Several tracking algorithms have been developed for this type of sensor. An event clustering algorithm is introduced for traffic monitoring, where clusters can change in size but are restricted to a circular form [34, 35]. A fast sensory motor system has been built to demonstrate the sensor's high temporal resolution properties in [36]. Several event-based algorithms and a remarkable JAVA framework for the Dynamic Vision Sensor can be found at [37]. In [38], a pencil balancing robot is developed to stabilize a pencil using a fast event-based Hough transform. The sensor has been recently applied to track particles in microrobotics [39] and in fluid mechanics [40]. It was also used to track a micro-gripper's jaws to provide a real-time haptic feedback from the micro meter scale world (lengths and sizes of objects around 1e-6m) [41].

To date, the currently developed methods that operate on events focus on the extraction of features such as lines in the whole focal plane. In other cases, they are too general to deal with particular cases where trackers should locally follow a specific oriented edge or a local shape. We will thus extend this methods to provide a more general framework allowing the tracking of specific local features using an event-based methodology. The tracking approach proposed here is inspired by the mean-shift technique that has also been extensively used in conventional frame-based visual tracking [42, 43, 44].

### 1.3.2 Gaussian Blob tracking

A stream of visual events can be mathematically defined as follows: let  $ev(\mathbf{u},t) = [\mathbf{u},t,pol]^T$  be a quadruplet giving the pixel position  $\mathbf{u} = [x,y]^T$ , the time *t* of the event and *pol*, its polarity that can be -1 or 1. When an object moves, the pixels generates events which geometrically form a point cloud that represents the spatial distribution of the observed shape. A moving object generates events that follow a spatial distribution that can be, in a first stage, roughly approximated by a bivariate normal distribution  $\mathcal{N}(\mu, \Sigma)$ , also called bivariate Gaussian distribution). The parameters of  $\mathcal{N}(\mu, \Sigma)$  provide the object's position, size and orientation. The Gaussian mean  $\mu$  indicates the object's position while the covariance matrix  $\Sigma$  represents its size and orientation. Let us suppose that several Gaussian trackers have already been initialized on the focal plane's locations of several moving objects. When a new event occurs, it is assigned a score (up to the normalization term) for each tracker, inspired by the probability this event would be generated by the Gaussian distribution

associated to this tracker which can be calculated by :

$$p_i(\mathbf{u}) = \frac{1}{2\pi} |\Sigma_i|^{-\frac{1}{2}} e^{-\frac{1}{2}(\mathbf{u}-\mu_i)^T \Sigma^{-1}(\mathbf{u}-\mu_i)}$$

(1.1)

where  $\mathbf{u} = [x, y]^T$  is the pixel location of the event.  $\mu_i = [\mu_{ix}, \mu_{iy}]^T$  represents the *i*<sup>th</sup> tracker's location and  $\Sigma_i \in \mathbb{R}^{2 \times 2}$  is its covariance matrix:

$$\Sigma = \begin{bmatrix} \sigma_x^2 & \sigma_{xy} \\ \sigma_{xy} & \sigma_y^2 \end{bmatrix}$$

(1.2)

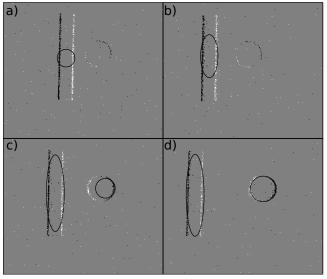

Fig. 1.2 is showing an example of a ellipse shape tracked by such a Gaussian tracker.

If one of the computed scores is superior to a predefined threshold  $p_i(\mathbf{u}) > \delta p$  (usually set to 0.1), then this tracker will adapt its parameters to follow this incoming event. If several trackers respond to the same event, the one with the maximum score is always chosen. After the most probable tracker has been selected, its parameters can be updated using a simple weighting strategy by integrating the last distribution with the current event information (see Eq (1.3) and (1.4)). Since only the chosen tracker is examined hereafter, the subscript *i* indicating the tracker number is omitted for clarity. The position and size of a Gaussian tracker can be updated as follows:

$$\boldsymbol{\mu}_t = \boldsymbol{\alpha}_1 \boldsymbol{\mu}_{t-1} + (1 - \boldsymbol{\alpha}_1) \mathbf{u} \tag{1.3}$$

$$\Sigma_t = \alpha_2 \Sigma_{t-1} + (1 - \alpha_2) \Delta \Sigma \tag{1.4}$$

where  $\alpha_1$  and  $\alpha_2$  are the update factors. They should be adjusted according to the event rate and the nature of the observed scene. These values are typically set between  $10^{-2}$  and  $10^{-1}$  and are chosen according to the size and velocity of the tracked objects. Namely how many events should be received to drag the shape from its old position to the new one and to change its size and shape according to the incoming events' rates.

The covariance difference  $\Delta \Sigma$  is computed using the current tracker's location  $\mu_{\mathbf{t}} = [\mu_{tx}, \mu_{ty}]^T$  and event's location **u**:

$$\Delta \Sigma = \begin{bmatrix} (x - \mu_{tx})^2 & (x - \mu_{tx})(y - \mu_{ty}) \\ (x - \mu_{tx})(y - \mu_{ty}) & (y - \mu_{ty})^2 \end{bmatrix}.$$

(1.5)

Finally, we define the activity of each tracker  $\mathcal{A}_i$  that is updated at each incoming event  $ev(\mathbf{u}, t)$ , following an exponential decay function which describes the temporal dimension of the Gaussian kernel.

$$\mathcal{A}_{i}(t) = \begin{cases} \mathcal{A}_{i}(t - \Delta t)e^{-\frac{\Delta t}{\tau}} + p_{i}(\mathbf{u}), \\ \text{if } ev(\mathbf{u}, t) \text{ belongs to tracker } i \\ \mathcal{A}_{i}(t - \Delta t)e^{-\frac{\Delta t}{\tau}}, \\ \text{otherwise.} \end{cases}$$

(1.6)

where  $\Delta t$  is the time difference between current and previous events and  $\tau$  tunes the temporal activity decrease. This activity measure is useful for inhibition and repulsion procedures that will be explained latter. It allows us to shape the interaction between trackers.

**Figure 1.2:** Error ellipse of the covariance matrix of a Gaussian tracker following a black ellipse moving under a white background. Position, size and orientation of the tracker automatically adapt to the visual stimuli. Black and white dots represent respectively OFF and ON events.

### Remark

The object's size and orientation can be retrieved by computing the principal components of the covariance matrix. Computationally, the lengths of the error ellipse's axes are the two principal components of the covariance matrix, which can be explicitly calculated by decomposing the two eigenvalues  $\lambda_{min}$  and  $\lambda_{max}$ . The semi-axes *a* and *b* and the orientation angle  $\alpha$  of the ellipse can be computed as follows:

$$a = K\sqrt{\lambda_{max}} \tag{1.7}$$

$$b = K\sqrt{\lambda_{min}} \tag{1.8}$$

$$\alpha = \frac{1}{2} \arctan(\frac{2\sigma_{xy}}{\sigma_y^2 - \sigma_x^2}) \tag{1.9}$$

where K is a scaling factor describing the distribution's confidence level. K is given by the confidence intervals, it provides a tuning parameter linking the Gaussian distribution parameters to the size of the event cloud it is fitted to in the image plane. In practice, this value can be set to 1. Readers wishing to know more about the computation of confidence intervals should refer to [45].

Computing these parameters can provide additional information if the trackers are used to identify unknown objects in a scene. The size and orientation of the Gaussian distributions yield information about the shape or orientation of the tracked objects and can be used either to discriminate between interesting and irrelevant objects or to build more complex objects from several trackers.

### 1.3.3 Multi-kernel features tracking

#### 1.3.3.1 Principle

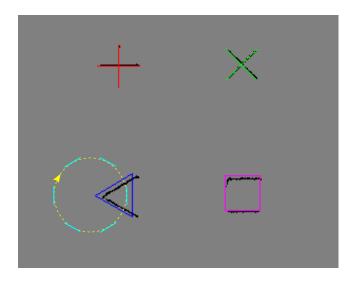

the principle is very similar to the Gaussian tracker, except that the Gaussian kernel is replaced by various other kernels. The examples that will be illustrated here are Gabor oriented kernels, combinations of Gabor functions, Laplacian of Gaussian and more general handmade kernels such as a triangle and a square. Some of these kernels are shown in Fig. 1.3.

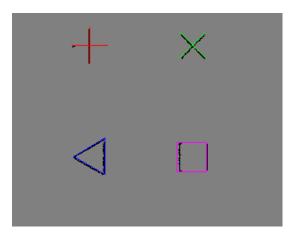

**Figure 1.3:** Examples of kernels used for tracking. (a) to (d) Gabor oriented kernels. (e) and (f) Combinations of Gabor kernels. (g) Laplacian of Gaussian. (h) Gaussian kernel. (i) and (j) Handmade arbitrary kernels.

The feature tracker generalizes to almost any kernel even for kernels with no analytical form. If  $K_i$  has no closed form, then it is a numerically defined function. In this case, the update of size and orientation cannot be performed easily as this implies the estimation of rotation and scaling that go beyond the scope of this work. We chose, in this case, to restrict kernels to a fixed size (scale) and orientation. Due to the low computational cost, this can easily be supplemented by the use of multiple layers of kernels of different scales and orientations as will be shown in section 1.4.

We introduce a local inhibition procedure that prevents the tracker from being active if the same localized area of the kernel is always excited. The activity of tracker i, is then given by Eq (1.10).

$$\mathcal{A}_{i}(t) = \begin{cases} \mathcal{A}_{i}(t - \Delta t)e^{-\frac{\Delta t}{\tau}} + \\ G_{\text{inhib},i}(ev, \mathbf{u})K_{i}(x_{i} - x, y_{i} - y), \\ \text{if } ev(\mathbf{u}, t) \text{ occurs into receptive field of tracker } i \\ \mathcal{A}_{i}(t - \Delta t)e^{-\frac{\Delta t}{\tau}}, \text{ otherwise,} \end{cases}$$

(1.10)

where  $\mathbf{u} = [x_i, y_i]^T$ , is the position of tracker *i*,  $K_i$  is the matrix representing the tracker's kernel and  $G_{inhib}$ , the inhibition gain, is computed as follows :

$$G_{\text{inhib}\ i}(ev,\mathbf{u}) = 1 - e^{-\Delta t_{ev,\mathbf{u}}/\tau_{inhib}}$$

(1.11)

Local inhibition is ensured considering  $\Delta t_{ev,\mathbf{u}}$  as the temporal difference between event ev and the last occurrence of an event into a small spatial neighborhood of the point  $[x_i - x, y_i - y]^T$  in matrix  $K_i$  (we usually considered a neighborhood of one or two pixels radius). This mechanism is equivalent to a local inhibition of neighboring locations of matrix  $K_i$  where the event occurred.

Namely the activated location of the filters and its surrounding will no longer be able to drive the tracker even if an event reactivates that location. In that case,  $\Delta t_{ev,\mathbf{u}}$  will go towards 0 thus leading  $G_{inhib}$  to 0. As the temporal distance increases,  $G_{inhib}$  will gradually tend towards 1. This ensures that a kernel needs to receive events in all its area to lead to the tracker's activation. This inhibition is followed by an exponential reactivation of the inhibited area thus allowing the filter to be active to events arriving at that location.

### 1.3.3.2 Gabor oriented kernels and combinations of Gabors

it is well known that some areas of our visual cortex V1 respond preferentially to oriented stimuli [46]. Consequently, we used Gabor functions to build a model of orientation selective kernels. The response of a  $\theta$ -oriented Gabor kernel  $\mathcal{K}_{G\theta}(\mathbf{v}, \sigma)$  located at position  $\mathbf{v} = [x_G, y_G]^T$  to the incoming event  $ev(\mathbf{u}, t)$  is given by Eq (1.12):

$$G(e, \mathcal{K}_{G\theta}(\mathbf{v}, \mathbf{\sigma})) = e^{\left(-\frac{x_{\mathbf{u}, \mathbf{v}}^2 + \gamma^2 y_{\mathbf{u}, \mathbf{v}}^2}{2\sigma^2}\right)} \cos\left(2\pi \frac{x_{\mathbf{u}, \mathbf{v}}}{\lambda}\right), \tag{1.12}$$

where  $x_{\mathbf{u},\mathbf{v}} = (x - x_G)\cos\theta + (y - y_G)\sin\theta$  and  $y_{\mathbf{u},\mathbf{v}} = -(x - x_G)\sin\theta + (y - y_G)\cos\theta$ . To ensure a correct orientation selectivity, we set the parameters  $\gamma = \frac{\sigma}{15}$  and  $\lambda = 4\sigma$ . Gabor kernels are illustrated in Fig. 1.3 (a) to (d). To track a particular feature like a cross, we also built kernels by combining Gabor functions following orthogonal orientations, as shown Fig. 1.3 (e) and (f).

# 1.3.3.3 Laplacian of Gaussian kernel

this kernel is inspired by center-surround biological structures and can be represented by the *Laplacian of Gaussian* function (LoG), shown in Fig. 1.3(g). This kernel has a behavior similar to Gaussian kernels shown in Fig. 1.3(h) but is also sensitive to the size of the tracked events' cloud. A cloud whose size exceeds the bright central ring (see Fig. 1.3(g)) will induce negative contributions to the activity of events occurring in the dark ring area. This compensates for the effect of centered events, preventing the tracker from being activated.

# 1.3.3.4 General kernels

in fact the algorithm can use any kernel, with the only constraint being that the center of mass of the matrix that represents the kernel has to be aligned with the center of the kernel. This is a weak constraint since any general kernel can be spatially shifted to meet this restriction arising from the position's update principle. Since the tracker is attracted by the neighboring events, its position will naturally match the local events' center of mass. To test if the events' cloud matches the desired feature, both must share the same spatial locations.

As an example, general kernels are shown using a square and a triangle (see Fig. 1.3 (i) and (j)). These kernels are generated using a binary representation of a simple geometric shape (+1 on lines, -1 elsewhere) followed by a dilatation algorithm and a smoothing.

# **1.3.4** Multi-target tracking

The algorithm is first initialized with a hidden layer of pre-constructed trackers that are uniformly distributed among the whole field of view. Hidden trackers refer to those not displayed on the screen as active trackers. A hidden tracker is one that does not represent a real object but serves to

**Figure 1.4:** Activation scheme of trackers (Gaussian tracker in the example). (a) A tracker is initialized in the hidden layer with default parameters. (b) It starts to follow the event cloud from a moving object and adapts to its shape. (c) When its activity goes above  $\mathcal{A}_{up}$  the tracker is upgraded to the visible layer and a new independent tracker is created in the hidden layer with its initial position and parameters. (d) The tracker follows the event cloud. (e) When its activity decreases and falls under  $\mathcal{A}_{up}$ , the tracker is downgraded to the hidden layer but keeps its current parameters and position. (f) Another step of tracking. (g) Eventually, the activity may rise again over  $\mathcal{A}_{up}$  and the tracker can be upgraded again. (h) Finally, if its activity falls under  $\mathcal{A}_{down}$ , the tracker is deleted.

seed a potential tracker.

A tracker will be automatically attracted to the nearest events' cloud. When a new event occurs, and no active tracker responds to it, it directly feeds the nearest hidden tracker with the same update rule as described by equation (1.3) (see Fig. 1.4(b)). When the activity of a hidden tracker increases above a predefined threshold  $\mathcal{A}_{up}$  (Fig. 1.4(c)), the tracker is upgraded to the visible layer, and a new hidden tracker is added with default parameters so that the hidden layer always has a fixed number of trackers distributed across the scene. When its activity falls under  $\mathcal{A}_{down}$ , the visible tracker is deleted (Fig. 1.4(h)). In the intermediary step, between  $\mathcal{A}_{up}$  and  $\mathcal{A}_{down}$  (Fig. 1.4(f)), the tracker is downgraded to the hidden layer but keeps its actual parameters and position. The evolution criteria combines both spatial and temporal correlation of events. Parameters  $\mathcal{A}_{down}$ ,  $\mathcal{A}_{up}$  and the temporal decrease constant  $\tau$  have to be tuned according to the event rate and the desired behavior.

### **1.3.5** Mutual repulsion and attraction to initial position

In case of strong localized activity, all neighboring trackers can be attracted to the same location. In order to prevent the different trackers following the same cloud, a mutual repulsion process is added. Each time a tracker is activated by an event, the distance between each tracker pair is computed and the trackers that are too close are shifted away from each other, following the weighted repulsion function described in equation (1.13). The location  $\mu_i$  of a tracker is updated

compared to the location of another tracker at  $\mu_i$  as follows:

$$\mu_{\mathbf{i}} \leftarrow \mu_{\mathbf{i}} - \alpha_{rep} e^{-\frac{\|\mu_{\mathbf{i}}-\mu_{\mathbf{j}}\|}{d_{rep}}} \frac{\mathcal{A}_{j}^{2}}{\mathcal{A}_{i}^{2} + \mathcal{A}_{i}^{2}} (\mu_{\mathbf{j}} - \mu_{\mathbf{i}}), \qquad (1.13)$$

where parameters  $\alpha_{rep}$  and  $d_{rep}$  set the repulsion behavior. The mutual repulsion between trackers *i* and *j* is designed to ensure a correct repartition of trackers based on the distance that separates them but also on the activity of both trackers. The more a tracker is active (i.e. is efficiently tracking an event cloud), the less it will be influenced by its neighbors.

Due to this mutual repulsion, inactive trackers are often pushed far from their initial position by moving active trackers. Thus empty areas could grow on the field of view. To compensate this possibility, we also added an attraction force that impacts on each inactive tracker in the following way:

$$\mu_{\mathbf{i}} \leftarrow \begin{cases} \mu_{\mathbf{i}}^{\mathbf{0}}, & \text{if } \|\mu_{\mathbf{i}} - \mu_{\mathbf{i}}^{\mathbf{0}}\| > d_{max} \\ \mu_{\mathbf{i}} + \alpha_{att}(\mu_{\mathbf{i}}^{\mathbf{0}} - \mu_{\mathbf{i}}), & \text{otherwise.} \end{cases}$$

(1.14)

where  $\mu_i^0$  is the initial position of tracker *i*. Thus, an inactive tracker that moved too far away from its initial position without being activated will be reset to its initial position.

Two additional constraints are added. Trackers that are near the border and about to move out of the focal plane are deleted. The borders are one pixel thick and a tracker is deleted if the distance of the its center to the border is below its typical size. For a Gaussian blob this typical size is the length of the ellipse's smallest axis (axis b in Fig. 1.2). For a symetric tracker (e.g. square, triangle) the size is the circumscribed circle's radius. The second constraint prevents the  $\Sigma$  matrix going below a low threshold value for the Gaussian trackers to limit the tracking to objects with a reasonable size. These additional constraints do not have much impact on the overall tracking performance as the sensor is usually configured to capture the scene in center of the focal plane.

### 1.3.6 Global algorithm

To summarize, the whole process of event-based features tracking is given by the following algorithm 1.

#### 1.3.6.1 Remarks

For simplicity, repulsion and attraction are computed every time a new event occurs, but as trackers do not move that fast, it is possible to perform computation less frequently. When adding this optimization, processing the repulsion and attraction step can usually be done every millisecond and still yield good performances.

Events are considered regardless of their polarity as we are interested in the global position and orientation of the object. In what follows we will focus on a single polarity. This will be carried out to provide a precise measure of accuracy of the positionning of a tracker for a thin contour.

# 1.4 Results

The experiments have been carried out using the ATIS camera considering only its change detection output and gray levels have not been used. All programs have been written in C++ under

| Algorithm 1 Event-based features tracking Algorithm                                                |

|----------------------------------------------------------------------------------------------------|

| for every incoming event $ev(\mathbf{u},t)$ do                                                     |

| Update the activity $\mathcal{A}_i$ of each tracker of the visible layer using Eq (1.6) or (1.10). |

| Update the best candidate tracker's position (and size) using equations (1.3) (and (1.4)).         |

| for every tracker of both layer do                                                                 |

| if $\mathcal{A}_i > \mathcal{A}_{up}$ then                                                         |

| Upgrade tracker to visible layer.                                                                  |

| else if $\mathcal{A}_i < \mathcal{A}_{down}$ then                                                  |

| Delete tracker <i>i</i>                                                                            |

| else                                                                                               |

| Downgrade tracker to hidden layer, and keep the same parameters and position.                      |

| end if                                                                                             |

| end for                                                                                            |

| for every pair of trackers of both layers do                                                       |

| Update tracker position using repulsion equation (1.13)                                            |

| end for                                                                                            |

| for every tracker of hidden layer do                                                               |

| Update tracker position using attraction equation (1.14)                                           |

| end for                                                                                            |

| end for                                                                                            |

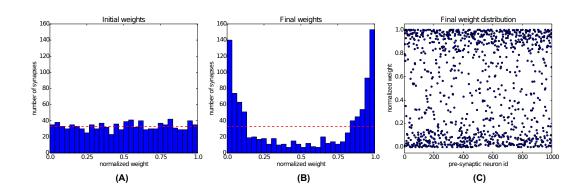

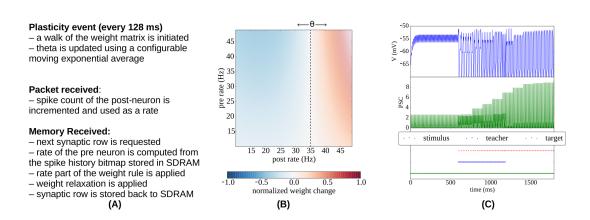

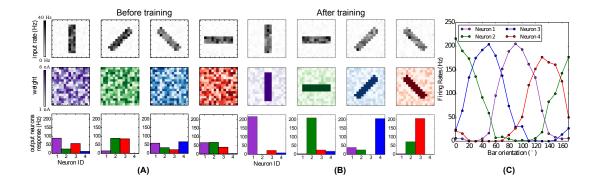

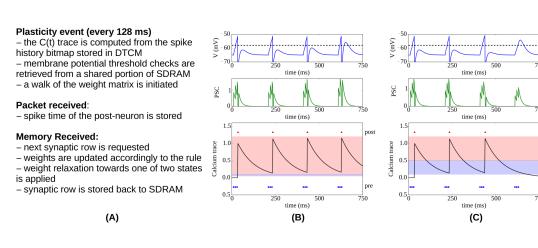

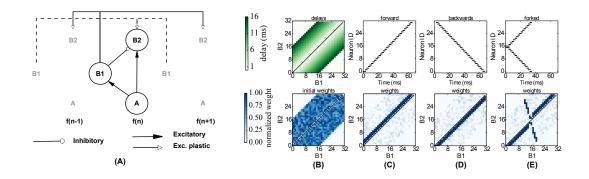

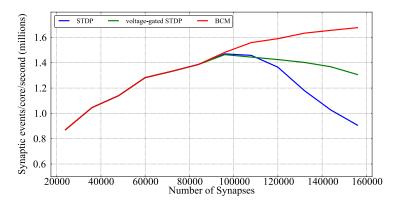

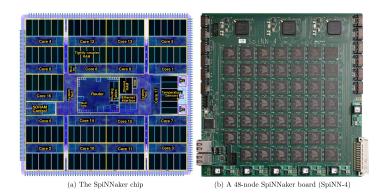

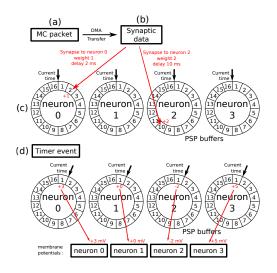

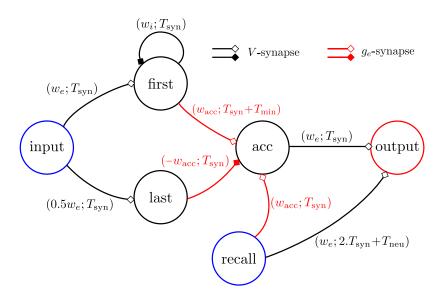

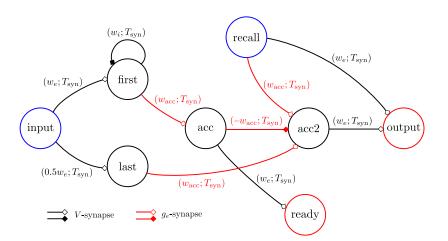

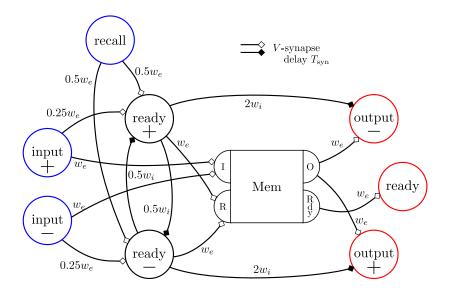

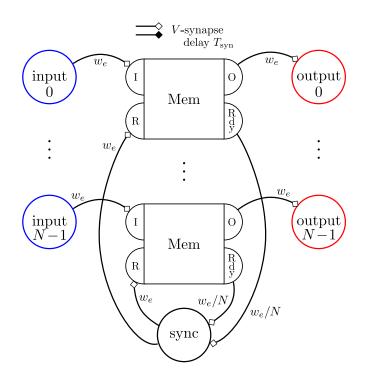

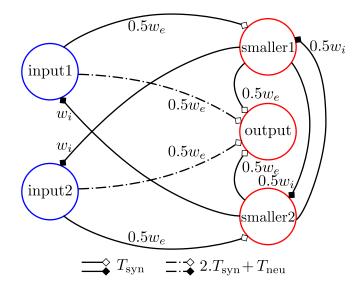

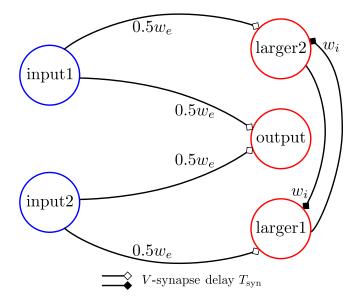

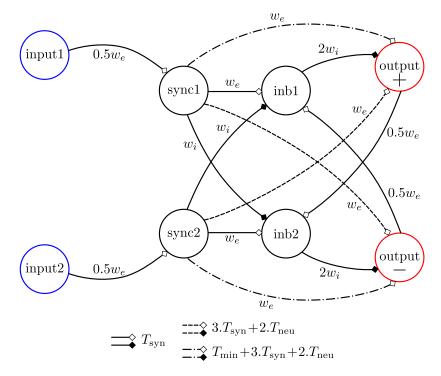

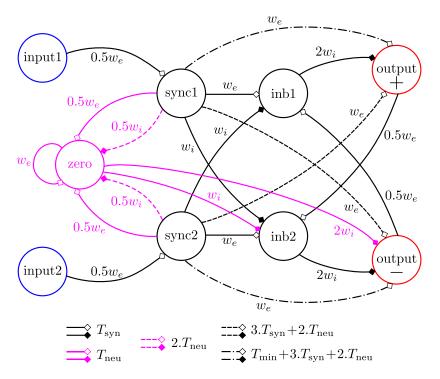

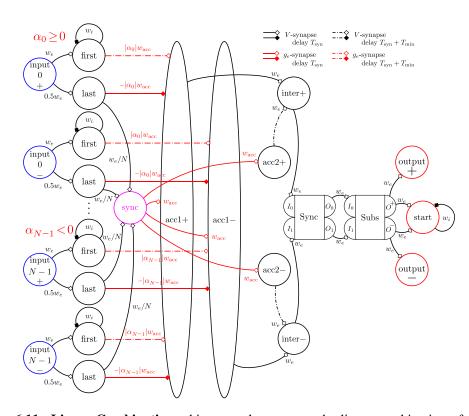

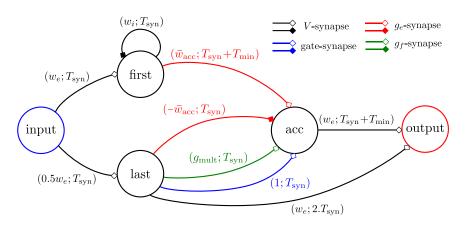

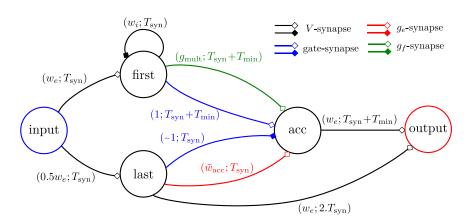

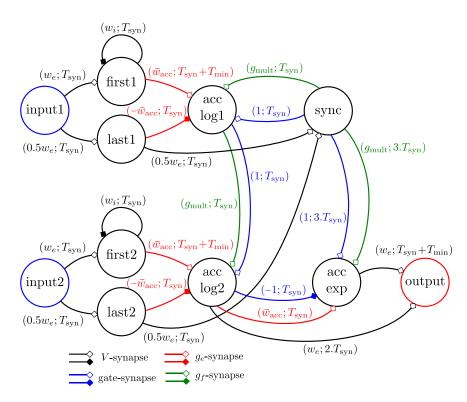

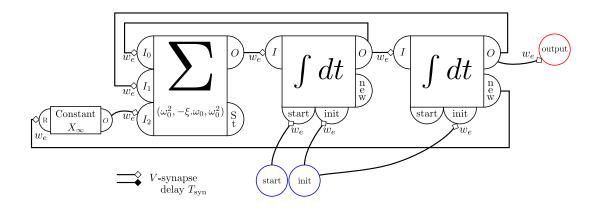

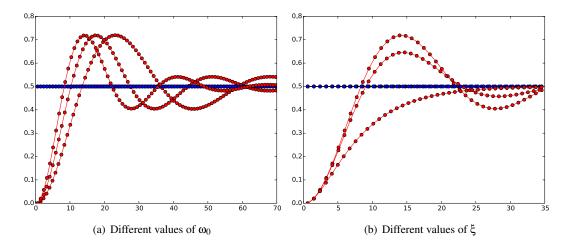

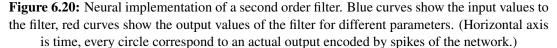

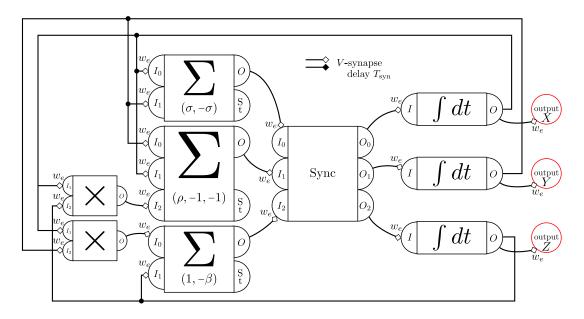

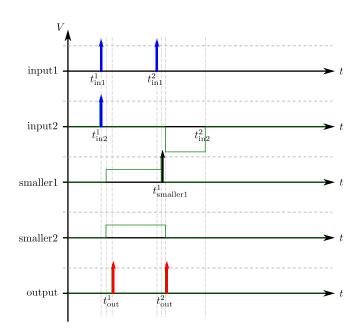

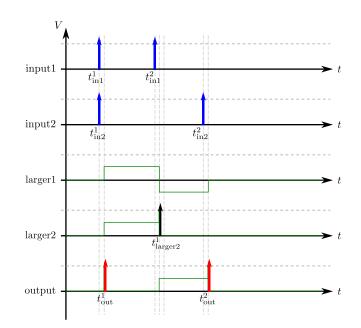

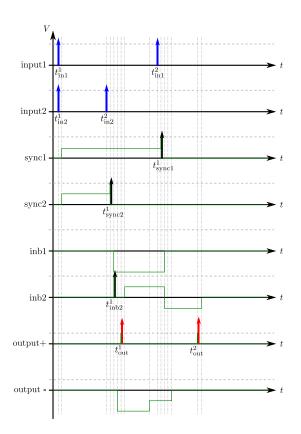

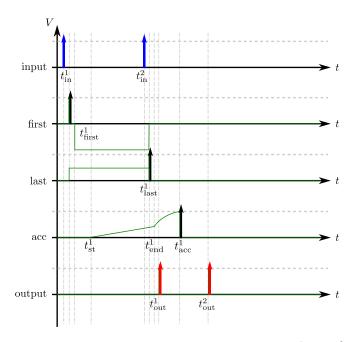

|                                                                                                    |