MAXIME PELCAT

# MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

HABILITATION À DIRIGER DES RECHERCHES Soutenue le 10 juillet 2017 devant un jury composé de

## **RAPPORTEURS:**

MICHEL AUGUIN, DR CNRS JEAN-PIERRE TALPIN, DR INRIA CHRISTOPHE JÉGO, PROF. ENSEIRB-MATMECA **EXAMINATEURS:** JOCELYN SÉROT, PROF. UCA FRANÇOIS BERRY, MCF HDR UCA JEAN-FRANÇOIS NEZAN, PROF. INSA RENNES / IETR DANIEL MÉNARD, PROF. INSA RENNES / IETR SHUVRA S. BHATTACHARYYA, PROF. UMD / TUT

# Contents

|   | List of Personal Publications                       | 5   |

|---|-----------------------------------------------------|-----|

|   | Foreword                                            | 9   |

|   | Abstract                                            | 11  |

|   | 1 Design Productivity                               | 13  |

| A | Using Dataflow MoCs for Raising Design Productivity | 19  |

|   | 2 Improving Design Efficiency                       | 21  |

|   | 3 Improving Implementation Quality                  | 41  |

|   | 4 Evaluating Design Productivity                    | 51  |

| В | Introducing MoAs for Raising Design Productivity    | 71  |

|   | 5 Models of Architecture: A New Design Abstraction  | 73  |

|   | 6 State of the Art of Models of Architecture        | 85  |

|   | 7 Models of Architecture in Practice                | 105 |

|   | 8 Research Perspectives                             | 121 |

|   | Bibliography                                        | 129 |

# List of Personal Publications

- [1] Carlo Sau, Francesca Palumbo, **Maxime Pelcat**, Julien Heulot, Erwan Nogues, Daniel Ménard, Paolo Meloni, and Luigi Raffo. Challenging the best HEVC fractional pixel FPGA interpolators with reconfigurable and multi-frequency approximate computing. *IEEE Embedded Systems Letters*, 2017. IEEE, to appear.

- [2] Alexandre Mercat, Florian Arrestier, Wassim Hamidouche, **Maxime Pelcat**, and Daniel Menard. Energy reduction opportunities in an HEVC real-time encoder. In *Proceedings of the ICASSP conference*. IEEE, 2017.

- [3] Alexandre Mercat, Florian Arrestier, Wassim Hamidouche, Maxime Pelcat, and Daniel Menard. Constrain the docile CTUs: an in-frame complexity allocator for HEVC intra encoders. In *Proceedings of the ICASSP conference*. IEEE, 2017.

- [4] Michael Masin, Francesca Palumbo, Hans Myrhaug, Julio de Oliveira Filho, Max Pastena, Maxime Pelcat, Luigi Raffo, Francesco Regazzoni, Angel Sanchez, Antonella Toffetti, Eduardo de la Torre, and Katiuscia Zedda. Crosslayer design of reconfigurable cyber-physical systems. In *Proceedings of the DATE Conference*. IEEE ACM, 2017.

- [5] Erwan Raffin, Wassim Hamidouche, Erwan Nogues, Maxime Pelcat, and Daniel Menard. Scalable HEVC Decoder for Mobile Devices: Trade-offs between Energy Consumption and Quality. In *Proceedings of the DASIP conference*. IEEE, 2016.

- [6] Alexandre Mercat, Wassim Hamidouche, Maxime Pelcat, and Daniel Menard. Estimating encoding complexity of a real-time embedded software heve codec. In *Proceedings of the DASIP conference*. IEEE, 2016.

- [7] Raquel Lazcano, Daniel Madroñal, Karol Desnos, Maxime Pelcat, Raúl Guerra, Sebastián López, Eduardo Juarez, and César Sanz. Parallelism Exploitation of a Dimensionality Reduction Algorithm Applied to Hyperspectral Images. In *Proceedings of the DASIP Conference*. IEEE, 2016.

- [8] Kamel Abdelouahab, Cédric Bourrasset, Maxime Pelcat, François Berry, Jean-Charles Quinton, and Jocelyn Serot. A holistic approach for optimizing DSP block utilization of a CNN implementation on FPGA. In *Proceedings of the ICDSC Conference*. ACM, 2016.

- [9] Maxime Pelcat, Karol Desnos, Luca Maggiani, Yanzhou Liu, Julien Heulot, Jean-François Nezan, and Shuvra S. Bhattacharyya. Models of Architecture: Reproducible Efficiency Evaluation for Signal Processing Systems. In Proceedings of the SiPS Workshop. IEEE, 2016.

- [10] Karol Desnos, Maxime Pelcat, Jean-François Nezan, and Slaheddine Aridhi. Distributed memory allocation technique for synchronous dataflow graphs. In *Proceedings of the SiPS Workshop*. IEEE, 2016.

- [11] Francesca Palumbo, Carlo Sau, Davide Evangelista, Paolo Meloni, Maxime Pelcat, and Luigi Raffo. Runtime Energy versus Quality Tuning in Motion Compensation Filters for HEVC. In *Proceedings of PDeS*. IEEE, 2016.

- [12] Maxime Pelcat, Cédric Bourrasset, Luca Maggiani, and François Berry. Design productivity of a high level synthesis compiler versus HDL. In *Proceedings of the IC-SAMOS Workshop*. IEEE, 2016.

- [13] Erwan Nogues, Daniel Menard, and Maxime Pelcat. Algorithmic-level approximate computing applied to energy efficient HEVC decoding. *IEEE Transactions on Emerging Topics in Computing*, 2016. IEEE.

- [14] Erwan Nogues, Julien Heulot, Glenn Herrou, Ladislas Robin, Maxime Pelcat, Daniel Menard, Erwan Raffin, and Wassim Hamidouche. Efficient DVFS for low power HEVC software decoder. *Journal of Real-Time Image Processing*, 2016. Springer Verlag.

- [15] John McAllister, Maire O'neill, and Maxime Pelcat. Guest editorial: New frontiers in signal processing applications and embedded processing technologies. *Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology (JSPS)*, 2016. Springer Verlag.

- [16] Erwan Nogues, Maxime Pelcat, Daniel Menard, and Alexandre Mercat. Energy efficient scheduling of real time signal processing applications through combined DVFS and DPM. In *Proceedings of the PDP conference*. IEEE, 2016.

- [17] Manel Ammar, Mouna Baklouti, Maxime Pelcat, Karol Desnos, and Mohamed Abid. On Exploiting Energy-Aware Scheduling Algorithms for MDE-Based Design Space Exploration of MP2SoC. In *Proceedings of the PDP Conference*. IEEE, 2016.

- [18] Miguel Chavarrias, Fernando Pescador, Matias Garrido, Maxime Pelcat, and Eduardo Juarez. Design of Multicore HEVC Decoders Using Actor-based Dataflow Models and OpenMP. In *Proceedings of the ICCE Conference*. IEEE, 2016.

- [19] Karol Desnos, Maxime Pelcat, Jean François Nezan, and Slaheddine Aridhi. On Memory Reuse Between Inputs and Outputs of Dataflow Actors. ACM Transactions on Embedded Computing Systems (TECS), 2016. ACM.

- [20] Simon Holmbacka, Erwan Nogues, Maxime Pelcat, Sébastien Lafond, Daniel Menard, and Johan Lilius. Energyawareness and performance management with parallel dataflow applications. *Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology (JSPS)*, 2015. Springer Verlag.

- [21] Erwan Raffin, Erwan Nogues, Wassim Hamidouche, Seppo Tomperi, Maxime Pelcat, and Daniel Menard. Low power HEVC software decoder for mobile devices. *Journal of Real-Time Image Processing*, 2015. Springer Verlag.

- [22] Erwan Nogues, Erwan Raffin, Maxime Pelcat, and Daniel Menard. A modified HEVC decoder for low power decoding. In *Proceedings of the Computing Frontiers Conference*. ACM, 2015.

- [23] Erwan Raffin, Wassim Hamidouche, Erwan Nogues, Maxime Pelcat, Daniel Menard, and Tomperi Seppo. Energy Efficiency of a Parallel HEVC Software Decoder for Embedded Devices. In *Proceedings of the Computing Frontiers Conference*. ACM, 2015.

- [24] Karol Desnos, Maxime Pelcat, Jean-François Nezan, and Slaheddine Aridhi. Buffer Merging Technique for Minimizing Memory Footprints of Synchronous Dataflow Specifications. In *Proceedings of the ICASSP Conference*. IEEE, 2015.

- [25] Manel Ammar, Mouna Baklouti, Maxime Pelcat, Karol Desnos, and Mohamed Abid. Automatic generation of S-LAM descriptions from UML/MARTE for the DSE of massively parallel embedded systems. In Software Engineering, Artificial Intelligence, Networking and Parallel/Distributed Computing. 2015. Springer Verlag.

- [26] Erwan Nogues, Berrada Romain, Maxime Pelcat, Daniel Menard, and Erwan Raffin. A DVFS based HEVC decoder for energy-efficient software implementation on embedded processors. In *Proceedings of the ICME conference*. IEEE, 2015.

- [27] Karol Desnos, Maxime Pelcat, Jean-François Nezan, and Slaheddine Aridhi. Memory Analysis and Optimized Allocation of Dataflow Applications on Shared-Memory MPSoCs. *Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology (JSPS)*, 2014. Springer Verlag.

- [28] Julien Heulot, Maxime Pelcat, Jean-François Nezan, Yaset Oliva, Slaheddine Aridhi, and Shuvra S Bhattacharyya. Just-in-time scheduling techniques for multicore signal processing systems. In *Proceedings of the GlobalSIP conference*. IEEE, 2014.

- [29] Karol Desnos, Safwan El Assad, Aurore Arlicot, Maxime Pelcat, and Daniel Menard. Efficient multicore implementation of an advanced generator of discrete chaotic sequences. In *Proceedings of the ICITST conference*. IEEE, 2014.

- [30] Zheng Zhou, William Plishker, Shuvra S Bhattacharyya, Karol Desnos, Maxime Pelcat, and Jean-François Nezan. Scheduling of parallelized synchronous dataflow actors for multicore signal processing. *Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology (JSPS)*, 2014. Springer Verlag.

- [31] Julien Heulot, Maxime Pelcat, Karol Desnos, Jean François Nezan, Slaheddine Aridhi, et al. SPIDER: A synchronous parameterized and interfaced dataflow-based RTOS for multicore DSPs. *Proceedings of the EDERC Conference*, 2014.

- [32] Manel Ammar, Mouna Baklouti, **Maxime Pelcat**, Karol Desnos, and Mohamed Abid. MARTE to  $\pi$ SDF transformation for data-intensive applications analysis. In *Proceedings of the DASIP Conference*. IEEE, 2014.

- [33] Simon Holmbacka, Erwan Nogues, Maxime Pelcat, Sébastien Lafond, and Johan Lilius. Energy efficiency and performance management of parallel dataflow applications. In *Proceedings of the DASIP conference*. IEEE, 2014.

- [34] Erwan Nogues, Simon Holmbacka, Maxime Pelcat, Daniel Menard, and Johan Lilius. Power-aware HEVC decoding with tunable image quality. In *Proceedings of the SiPS Workshop*. IEEE, 2014.

- [35] Maxime Pelcat, Karol Desnos, Julien Heulot, Clément Guy, Jean-François Nezan, and Slaheddine Aridhi. PREESM: A dataflow-based rapid prototyping framework for simplifying multicore dsp programming. In *Proceedings of the EDERC Conference*, 2014.

- [36] Jinglin Zhang, Jean-François Nezan, Maxime Pelcat, and Jean-Gabriel Cousin. Real-time GPU-based local stereo matching method. In *Proceedings of the DASIP Conference*. IEEE, 2013.

- [37] Zheng Zhou, Karol Desnos, **Maxime Pelcat**, Jean-François Nezan, William Plishker, and Shuvra S Bhattacharyya. Scheduling of parallelized synchronous dataflow actors. In *Proceedings of the SoC Conference*. IEEE, 2013.

- [38] Karol Desnos, Maxime Pelcat, Jean François Nezan, Shuvra S. Bhattacharyya, and Slaheddine Aridhi. PiMM: Parameterized and interfaced dataflow meta-model for MPSoCs runtime reconfiguration. In *Proceedings of the IC-SAMOS Workshop*. IEEE, 2013.

- [39] Julien Heulot, Jani Boutellier, Maxime Pelcat, Jean François Nezan, and Slaheddine Aridhi. Applying the Adaptive Hybrid Flow-Shop Scheduling Method to Schedule a 3GPP LTE Physical Layer Algorithm onto Many-Core Digital Signal Processors. In *Proceedings of the AHS conference, NASA/ESA*, 2013.

- [40] Karol Desnos, Maxime Pelcat, Jean François Nezan, and Slaheddine Aridhi. Pre- and post-scheduling memory allocation strategies on MPSoCs. In *Proceedings of the ESLsyn conference*. IEEE, 2013.

- [41] Julien Heulot, Karol Desnos, Jean François Nezan, Maxime Pelcat, Mickaël Raulet, Hervé Yviquel, Pierre-Laurent Lagalaye, and Jean-Christophe Le Lann. An Experimental Toolchain Based on High-Level Dataflow Models of Computation For Heterogeneous MPSoC. In *Proceedings of the DASIP Conference*. IEEE, 2012.

- [42] Karol Desnos, Maxime Pelcat, Jean François Nezan, and Slaheddine Aridhi. Memory Bounds for the Distributed Execution of a Hierarchical Synchronous Data-Flow Graph. In *Proceedings of the IC-SAMOS Workshop*. IEEE, 2012.

- [43] Maxime Pelcat, Slaheddine Aridhi, Jonathan Piat, and Jean-François Nezan. *Physical Layer Multi-Core Prototyping: A Dataflow-Based Approach for LTE eNodeB*. Springer Verlag, 2012.

- [44] Yaset Oliva, Maxime Pelcat, Jean-François Nezan, Jean-Christophe Prevotet, and Slaheddine Aridhi. Building a RTOS for MPSoC dataflow programming. In *Proceedings of the SoC Conference*. IEEE, 2011.

The regularly updated list of my publications is available on : http://mpelcat.org/publications.

## Foreword

This *Habilitation à Diriger des Recherches (HDR)* report presents past and future research directions resulting from the work I conducted since 2010 together with colleagues at IETR/INSA Rennes and more recently at Institut Pascal in Clermont-Ferrand, as well as with researchers from University of Maryland, Tampere University of Technology, Texas Instruments, ENIS, Abo Akademi, Scuola Sant' Anna, Università degli studi di Cagliari, Università degli Studi di Sassari, Universidad Politécnica de Madrid and Queen's University Belfast.

I am very grateful for all the enriching discussions I had the chance to participate in during laboratory and project meetings, research stays and seminars. A special thank you to the doctors I co-advised: Karol Desnos, Julien Heulot and Erwan Nogues, as well as to the PhD students I currently co-advise: Alexandre Mercat, El Mehdi Abdali, Jonathan Bonnard, and Kamel Abdelouahab. I would like to thank the colleagues with whom I had the chance to closely collaborate, and in particular Daniel Ménard, Jean-François Nezan, Karol Desnos, and François Berry who have helped many ideas to ripen that now appear in this document. Thanks also to all my colleagues at the VAADER team of IETR and DREAM team of Institut Pascal. Finally, I am grateful to Jocelyn Sérot for accepting to direct this Habilitation à Diriger la Recherche (HDR) and for helping with the creation of this report.

## Abstract

The complexity of systems is currently growing faster than the productivity of system designers and programmers. This phenomenon is called Design Productivity Gap and results in inflating design costs. This *Habilitation à Diriger des Recherches (HDR)* report present models, methods and tool for improving the Design Productivity (DP) of embedded Digital Signal Processing (DSP) systems and reducing this Design Productivity Gap. The notion of Design Productivity (DP) is commonly used without defining it. This report starts by precisely defining DP before presenting different methods to improve and evaluate it.

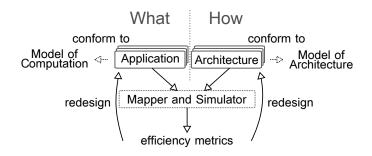

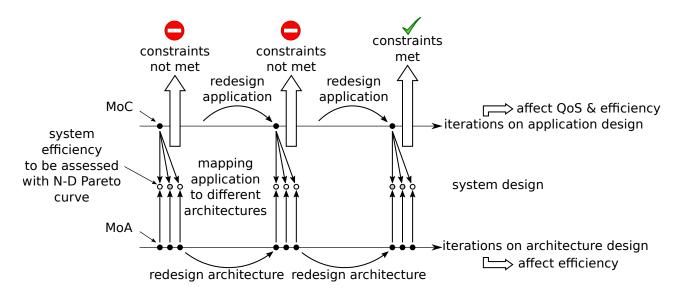

In a first part, methods based on Models of Computation (MoCs) are explored. They constitute our past and present work on the subject. Dataflow MoCs are used to study application properties (liveness, schedulability, parallelism, etc.) at a high level of abstraction, often before implementation details are known. We have over the last seven years explored how dataflow MoCs can influence the performance and design efforts of modern multicore Digital Signal Processing (DSP) systems.

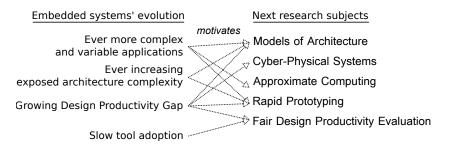

In the second part of this report, the focus is shifted on the notion of Model of Architecture (MoA) we recently introduced. Parallel and heterogeneous platforms are becoming ever more complex. MoAs have the potential to counteract the DP reduction caused by this rising complexity and constitute the main subject I intend to continue studying in the next years.

MoAs, and in general Model-Based Design, can have a great impact on future design methods. Together with the concepts of Cyber-Physical Systems (CPS), Approximate Computing and Rapid Prototyping, they represent new opportunities for reducing the Design Productivity Gap of future DSP systems.

# 1 Design Productivity

### 1.1 Chapter Abstract

In this introductory chapter, the concept of DP is defined in the context of DSP system design. DP a ratio between the quality of a system — in terms of Non-Functional Properties (NFPs) — and the efforts spent to build the system, expressed as Non-Recurring Engineering (NRE) costs. This definition allows for evaluations and comparisons of the DPs from several methods.

My work over the last 7 years is then overviewed under the perspective of DP reduction for DSP embedded systems. DP improvements are finally argued to be necessary in the long run to follow the upward trend of embedded system exposed complexity.

### 1.2 Design Productivity

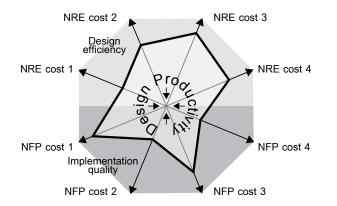

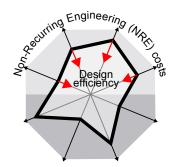

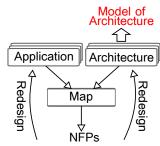

The concept of DP is often evoked in literature but we only recently proposed a definition<sup>1</sup>. Design Productivity (DP) relates to a compromise between the efforts spent to build a system and the quality of the system resulting from these design efforts. A generic representation of system DP is proposed in Figure 1.1. DP may be augmented by two factors:

- when design effort is reduced. This corresponds to augmenting *design effi*ciency,

- when, for a fixed effort, *implementation quality* is increased.

Design effort can be measured by Non-Recurring Engineering (NRE) cost metrics such as design time, test and validation time, the number of lines of code to write, the NRE monetary expenses, etc. Implementation quality can be measured by Non-Functional Property (NFP) costs such as the energy consumption of the system, its latency, throughput, production cost, silicon area, etc. A DSP system can be considered functional when it produces, for a given input data stream, the corresponding correct output data stream. NFPs correspond to all the properties, except functional behavior, that may participate

<sup>1</sup> Maxime Pelcat, Cédric Bourrasset, Luca Maggiani, and François Berry. Design productivity of a high level synthesis compiler versus HDL. In *Proceedings of IC-SAMOS*, 2016 to make a system conform to its specification. For a given design, DP can be characterized by the area under the radar chart curve of Figure 1.1. The smaller this area is, the more DP the design process offers.

Figure 1.1: Design Productivity representation as a combination of Non-Recurring Engineering (NRE) costs and system Non-Functional Property (NFP) costs.

The NRE and NFP cost metrics chosen to appear in the chart strongly impact how the Design Productivity is measured. They should be chosen according to the most important design constraints and the most important features of the built system. As a consequence, a unique scalar value can not alone quantify DP. However, if two design methods are compared on the same use case, in the same conditions and with the same NRE and NFP metrics, a fair DP ratio can be measured, provided that the conditions for producing this ratio are explained. A fair DP comparison will be demonstrated in Chapter 4.

DP fair assessment is a promising tool to promote new system design practices. We recently prototyped such a system DP fair assessment[1] to demonstrate its feasibility. Platform technologies and architectures currently evolve at a tremendous pace but design practices clearly evolve at a more leisurely pace. Fair DP studies have the potential to boost design practices and foster new tools, languages and methods.

The next section illustrates my research activities under the prism of DP augmentation.

## 1.3 Research Activities on Design Productivity

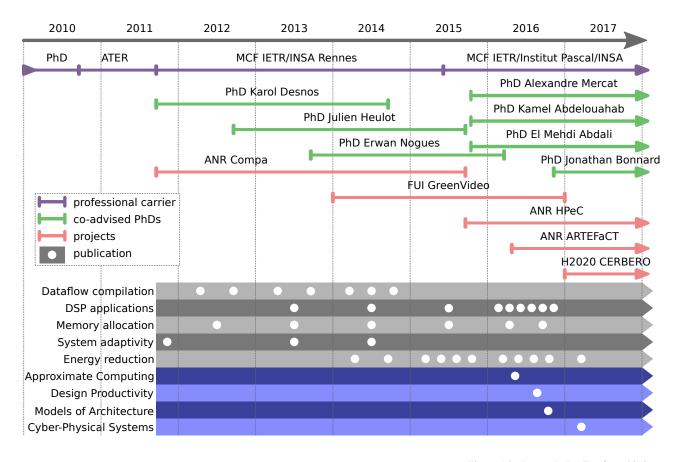

Figure 1.2 illustrates my carrier as maître de conférences over the last 7 years. Dots represent personal publications, ordered by their main subjects.

The research subjects we have tackled over these years are diverse. They however have in common a long term objective of DP enhancement.

In the context of the 3 PhD thesis of Karol Desnos (2011-2013), Julien Heulot (2012-2014) and Erwan Nogues (2013-2015), we have studied different aspects of DP, with a particular focus on application modeling with dataflow MoCs. Playing with a DSP application representation to enhance its performance and portability is possible using dataflow MoCs that represent the high-level aspects (e.g. parallelism, exchanged data, triggering events, etc.) of

Figure 1.2: Research timeline from 2010 to today.

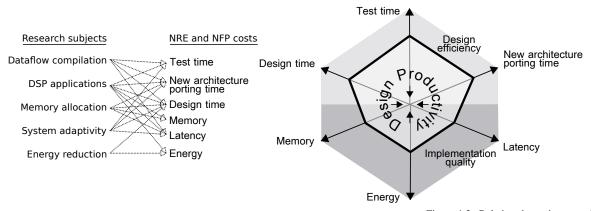

an application while hiding its detailed implementation. We have tackled the subjects of representing complex systems with predictable models, automating memory allocation, automating energy reduction and adapting the execution of a multicore system to hardware and software states. Alongside this work on design methods, we have built several DSP designs to test and demonstrate the methods. This MoC-based design approach is described in Chapters 2 and 3 and illustrated in Figure 1.3 that represents our main past and current research subjects and the NFPs and NREs they address. In the figure, latency corresponds to the real-time response time of the system, energy is the energy consumption due to processing and memory is the memory footprint of the application. New architecture porting time corresponds to the design time necessary to port and application to a new architecture.

Our focus is currently shifting, motivated by the continuous augmentation of the number of cores in systems and their rising heterogeneity. In particular, the complexity of embedded processors is ever more *exposed*. An exposed architecture is a set of hardware features that a designer must know to exploit the potential performance of a platform. We oppose to exposed architectures the *hidden architectures* that are hardware- or software-managed and can be ignored by the designer while still getting acceptable performance. Our focus

## 16 MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

is now set on a new notion we recently proposed<sup>2</sup>: Models of Architecture (MoAs).

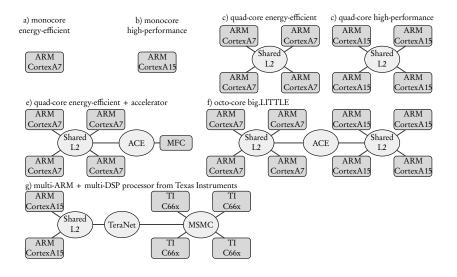

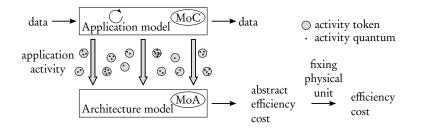

Equivalently to MoCs on the application side, Models of Architecture (MoAs) can be used on the architectural side to extract the fundamental elements affecting efficiency. An MoA is a model abstracting away details of a hardware platform but producing, when combined with an application model, a reproducible evaluation of a system's Non-Functional Property (NFP). The notion of MoA will be defined in Chapter 5. Related works and an example use of an MoA are respectively presented in Chapters 6 and 7.

New ideas are currently emerging into our research: Cyber-Physical Systems (CPS), adaptable hardware, approximate computing, and hardware/software High-Level Synthesis (HLS). All of them can benefit from the concept of MoAs. These starting research directions will be presented in Chapter 8, together with perspectives.

## 1.4 Why Addressing Embedded Systems' DP?

In computer science, system performance is often used as a synonym for realtime performance, i.e. adequate processing speed. However, most DSP systems must, to fit their market, meet at the same time several NFPs, including high performance, low cost, and low power consumption.

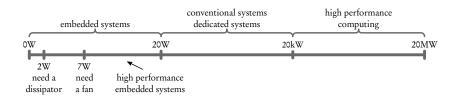

Observing the available processing systems, three categories can be distinguished, based on their power consumption, as displayed in Figure 1.4. Embedded systems are often battery powered and characterized by a processing power dissipation below 20W. Between 20W and 20kW are either conventional processing, including personal computers, and dedicated systems such as cellular base stations or large medical devices. Over 20kW and below 20MW are High Performance Computing (HPC) systems, 20MW being a common upper bound of processing power consumption for future exascale facilities. One data center facility can require even more than 20MW (up to around 200MW) but a data center is constantly shared between millions of independent applications Figure 1.3: Relating the main research subjects addressed by our past and current work (Figure 1.2) and their influence on the addressed DP-related metrics.

<sup>2</sup> Maxime Pelcat, Karol Desnos, Luca Maggiani, Yanzhou Liu, Julien Heulot, Jean-François Nezan, and Shuvra S Bhattacharyya. Models of architecture: Reproducible efficiency evaluation for signal processing systems. In *Proceedings of the SiPS Workshop*. IEEE, 2016 and thus cannot be considered as one processing system.

A great variety of processors is available for the embedded processing domain and **embedded processors have a great influence on all domains of processing as a consequence of their high energy efficiency**. For instance, the influence of embedded systems on HPC is visible in the Mont-Blanc European projects [3] that design ARM-based HPC platforms. Moreover, mobile devices, built around embedded processors, have become the main driver of processing innovation and future systems, either in the Internet of Things (IoT) or in the CPS domain, are predicted to continue this trend.

The energy efficiency of embedded processors comes at the price of very complex design and programming procedures due to considerable exposed complexities. As an example, porting complex applications to an FPGA or a many-core processor can easily take several tens or hundreds of men-months to exploit an acceptable share of platform performances and a large set of hardware skills is expected from the design teams. The 2011 ITRS report warns that "design implementation productivity must be improved to the same degree as design complexity is scaled" for design costs to remain sustainable[4].

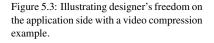

The examples of processors studied in this document have a limited number of cores: for example the Exynos 5410 and 5422 processors, each composed of 4 energy-efficient ARM Cortex-A7 cores and 4 high-performance ARM Cortex-A15 cores, and the Texas Instruments TMS320C6678 processor composed of 8 c66x DSP cores interconnected by a Network-on-Chip (NoC) with access to an internal shared memory. However, both these processors already require hardware knowledge to properly program them. For instance, communicating between cores through the shared memory of the TMS320C6678 processor necessitates manual data cache coherency management, taking account of the cache line size of 128*Bytes* to avoid invalidating or writing back the wrong data in memory.

This kind of programming is difficult to maintain for the currently released many-core processors. The upward trend currently followed by platforms' exposed complexity is likely to continue in the next years and the number of cores in mobile systems is forecast to grow at least until the end of the 2020s [5]. In this context, one major challenge of electronic system design is the growing *Design Productivity Gap* referring to a faster increase in the complexity of systems than in the productivity of system designers. As a consequence, Design Productivity (DP) is at the heart of system costs and should be carefully

Figure 1.4: Categories of processing systems based on their power consumption.

addressed in future research, especially for the cost and performance-critical DSP applications exploiting embedded processors.

This report is organized into two Parts. Part A covers our previous work on augmenting and measuring the DP of DSP embedded systems using dataflow MoCs while part B proposes the new concept of MoAs to further improve DP in the next years.

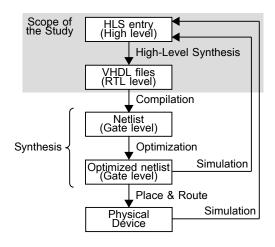

In Part A, Chapter 2 presents our work on augmenting the DP of embedded processing systems by raising the design efficiency while Chapter 3 focuses on the improvement of the implementation quality. Chapter 4 overviews the use cases leveraged on to assess our models and methods and shows on a High-Level Synthesis (HLS) example how DP can be measured in practice. In Part B, Chapters 5, 6 and 7 respectively concentrate on the definition, state-ofthe-art and applicability of Models of Architecture (MoAs) as a new direction to explore. Finally, Chapter 8 presents some research perspectives I intend to follow in the next years.

# Part A

# Using Dataflow MoCs for Raising Design Productivity

# Improving Design Efficiency

### 2.1 Chapter Abstract

This chapter highlights our contributions on Design Productivity (DP) with a particular focus on the design efficiency of DSP systems. These contributions are based on the PiMM dataflow metamodel we introduced in 2013. They aim at automating design phases and hiding parts of the system complexity.

The PiMM metamodel is first presented. PiMM can be used in conjunction with any dataflow MoC. When combining the PiMM metamodel together with the Synchronous Dataflow (SDF) MoC, a hierachical, predictible, compositional and parameterized model of computation is obtained called PiSDF. The benefits offered by the PiSDF dataflow MoC on design efficiency come from the portable nature of a PiSDF algorithm representation. Indeed, PiSDF, inheriting properties from the formerly existing parameterized dataflow and IBSDF models, represents both the parallelism of the application, and the data communicated between computational actors, while supporting dynamic application reconfigurability.

Then, a scheduling method called JIT-MS is introduced. The objective of Just-In-Time Multicore Scheduling (JIT-MS) is to find a balance between a static scheduling that has no runtime overhead but does not take into account the application and architecture modifications, and dynamic scheduling that costs time and resources to take decisions. JIT-MS exploits the information of a PiSDF application representation to adapt a dynamic application execution to potentially dynamic platform resources. JIT-MS maintains a graph of the current application state and optimizes the application execution as soon as its parameters are resolved. It splits the scheduling of a PiSDF dataflow graph into steps to identify locally static regions. It also provides efficient assignment and ordering of actors into Processing Elements (PEs), leveraging on dataflow information.

When compared to the current programming methods for parallel systems based on manual parallelization and imperative languages such as C and extension such as OpenMP or OpenCL, PiMM and JIT-MS aim to foster a shift

Figure 2.1: Improving design efficiency on the DP chart.

## 2

in the programming paradigm of DSP embedded systems from state-machinebased languages to parallelism-aware dataflow representations.

## 2.2 Building the PiMM Metamodel to improve Design Efficiency

Currently available high performance DSP platforms all have multiple cores. They sometimes also bring together programmable cores and programmable hardware. The procedure to design systems for these platforms is complex and specific to each architecture. Our work on design efficiency consists of designing models, methods and tools to decouple the application model from the architecture model.

On the application side, the parameters of applications (e.g. the size of a processed image, the bandwidth of a telecommunication algorithm,, the size of a cryptographic key to generate, etc.) impact their parallelism and the efficiency of their execution. If this impact is extensive, a runtime management of the system is necessary to migrate processing tasks, manage data movements and handle external event. If on the contrary the impact of parameters on concurrency is limited, it is desirable to take as many code and memory locality decisions at compile time, avoiding runtime management overheads.

A common method to design a DSP system today is to first build a versatile simulation model of the application algorithms using Matlab, Scilab or Python. Then, this model is used as a *golden reference* to separately build the hardware and software subparts of the system and then verify the functional properties of the system. The hardware is written in VHDL or Verilog to be ported for instance on an Field-Programmable Gate Array (FPGA) or to be implemented as an ASIC IP. The software is written is imperative code, usually in C code, and must be adapted to the number of of available cores, their performance, their communication facilities, their memory, and the interfaces they use to communicate with the their environment.

There are several ways to reduce the efforts necessary to build a system in this context, and thus increase its design efficiency:

- The **design time** can be reduced, corresponding to the time needed to represent the application in a language or model serving as an input for the compilation/synthesis process. This reduction can come from a more user friendly language, a Domain specific language (DSL) making language semantics fitting closely the applicative needs and automating some repetitive procedures, an Integrated Development Environment (IDE) with advanced language semantics analysis, etc. Another possibility is for the golden reference code to be made executable for the designer to write application functionalities only once and infer the total system.

- The **test time** can be reduced, for instance by setting correct-by-design constructs in the input language or automating the construction of test benches.

• The **porting time** to another platform can be shortened. A processor is currently commercialized only for a few years before being replaced by a new one, often with a very different architecture. Porting applications between architectures of different types is currently very time consuming.

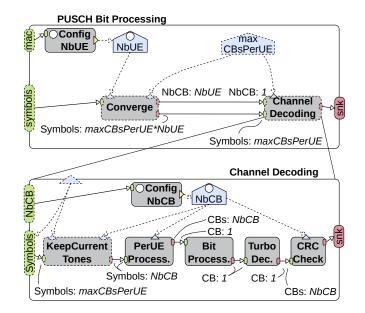

During the last years and particularly as part of the PhD thesis of Karol Desnos and Julien Heulot, we have developed a new dataflow metamodel named Parameterized and Interfaced Dataflow Meta-Model (PiMM) and combined it with the SDF MoC to form a hierachical, predictible and parameterized model named Parameterized and Interfaced Synchronous Dataflow (PiSDF). We have also built the compilation and runtime tools PREESM<sup>1</sup> and Spider<sup>2</sup> to generate multicore software from PiSDF. In a partnership with the Polytechnic University of Madrid (UPM), we are currently extending PiSDF to hardware design.

Our work on dataflow compilation has focused on enhancing the predictability of algorithm modeling because a predictable model is compulsory when a DSP processing algorithm is to be mapped onto a multicore system with a degree of guaranteed efficiency. In particular, the added value of an embedded system lies in the possibility to ensure properties such as real-time and energy consumption. The PiMM metamodel, published in IC-SAMOS 2013 <sup>3</sup> complements previous work on Interface-Based SDF (IBSDF) from Jonathan Piat[9]. It favors the design of highly-efficient heterogeneous multicore systems, specifying algorithms with customizable trade-offs among predictability and exploitation of both static and adaptive task, data and pipeline parallelism.

Next sections discuss a selection of our contributions on PiSDF and JIT-MS.

## 2.3 Dataflow Compilation: The PiMM Meta-Model and PiSDF MoC

#### 2.3.1 State of the Art of Dataflow MoCs

Dataflow MoCs can be used to specify a wide range of DSP applications such as video decoding [10], telecommunication <sup>4</sup>, and computer vision [12] applications. The popularity of dataflow MoCs is due to their great analysability and their natural expressivity of the parallelism of a DSP application which make them particularly suitable to exploit the parallelism offered by heterogeneous Multiprocessor Systems-on-Chips (MPSoCs). The increasing complexity of applications leads to the continuing introduction of new dataflow MoCs, and the extension of previously developed MoCs for different types of modeling contexts. Dataflow MoCs are differentiated by their capacity to either describe dynamic application behaviors (expressive models) or to feed a behaviour prediction process efficiently (predictible models).

Representing an application with a Dataflow Process Network (DPN) [13] consists of dividing this application into persistent processing entities, named

<sup>1</sup> M. Pelcat, K. Desnos, J. Heulot, C. Guy, J.-F. Nezan, and S. Aridhi. PREESM: A dataflow-based rapid prototyping framework for simplifying multicore dsp programming. In *Proceedings of the EDERC Conference*, Sept 2014

<sup>2</sup> Julien Heulot, Maxime Pelcat, Karol Desnos, Jean François Nezan, Slaheddine Aridhi, et al. SPIDER: A synchronous parameterized and interfaced dataflow-based rtos for multicore dsps. *Proceedings of the EDERC Conference*, 2014

<sup>3</sup> K. Desnos, M. Pelcat, J.-F. Nezan, S. S. Bhattacharyya, and S. Aridhi. PiMM: Parameterized and interfaced dataflow metamodel for MPSoCs runtime reconfiguration. In *SAMOS XIII*, 2013

<sup>4</sup> Maxime Pelcat, Slaheddine Aridhi, Jonathan Piat, and Jean-François Nezan. *Physical Layer Multi-Core Prototyping: A Dataflow-Based Approach for LTE eNodeB*. Springer, 2012 actors, connected by First In, First Out data queues (FIFOs). An actor performs processing (it "fires") when its incoming FIFOs contain enough data tokens. The number of data tokens consumed and produced by an actor for each firing is given by a set of firing rules [14]. Firing rules can be static or they can depend on data, as in the CAPH language, or on parameters, as in the Parameterized Synchronous Dataflow (PSDF) MoC [15].

*Static Dataflow MoCs* Synchronous Dataflow (SDF) [16] is a static DPN MoC. Production and consumption token rates set by firing rules are fixed scalars in an SDF graph. A static analysis of an SDF graph ensures consistency and schedulability properties that imply deadlock-free execution and bounded FIFO memory needs.

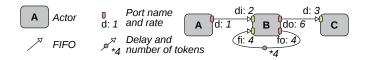

An SDF graph G = (A, F) (Figure 2.2) contains a set of actors A that are interconnected by a set of FIFOs F. An actor  $a \in A$  comprises a set of data ports  $(P_{data}^{in}, P_{data}^{out})$  where  $P_{data}^{in}$  and  $P_{data}^{out}$  respectively refer to a set of data input and output ports, used as anchors for FIFO connections. Functions  $src : F \to P_{data}^{out}$ and  $snk : F \to P_{data}^{in}$  associate source and sink ports to a given FIFO and a data rate is specified for each port by the function  $rate : P_{data}^{in} \cup P_{data}^{out} \to \mathbb{N}$ corresponding to the fixed firing rules of an SDF actor. A delay  $d : F \to \mathbb{N}$  is set for each FIFO, corresponding to a number of tokens initially present in the FIFO.

Figure 2.2: Example of an SDF Graph

If an SDF graph is consistent and schedulable, a fixed sequence of actor firings can be repeated indefinitely to execute the graph, and there is a well defined concept of a minimal sequence for achieving an indefinite execution with bounded memory. Such a minimal sequence is called *graph iteration* and the number of firings of each actor in this sequence is given by the graph Repetition Vector (RV).

Graph consistency means that no FIFO accumulates tokens indefinitely when the graph is executed (preventing FIFO overflow). Consistency can be proved by verifying that the graph topology matrix has a non-zero vector in its null space [16]. When such a vector exists, it gives the RV for the graph. The topology of an SDF graph characterizes actor interconnections as well as token production and consumption rates on each FIFO. A graph is schedulable if and only if it is consistent and has enough initial tokens to execute the first graph iteration (preventing deadlocks by FIFO underflow).

Research on dataflow modeling leads to the continuing introduction of new dataflow models. Static extensions of the SDF model such as the Cyclo-Static Dataflow (CSDF) [17], the multidimensional SDF [18], the IBSDF [9], and the Affine Dataflow (ADF) [19] have been proposed to enhance its expressiveness

and conciseness while preserving its predictability.

The Compositional Temporal Analysis (CTA) model is a non-executable timed abstraction of the SDF MoC that can be used to analyze efficiently the schedulability and the temporal properties of applications [20]. The IBSDF and the CTA models both enforce the compositionality of applications. A model is compositional if the properties (schedulability, deadlock freeness, ...) of an application graph composed of several sub-graphs are independent from the internal specifications of these sub-graphs [21].

*Interface-Based Synchronous Dataflow MoC* Interface-Based SDF (IBSDF) [9] is a hierarchical extension of the SDF model interpreting hierarchy levels as code closures. IBSDF fosters subgraph composition, making subgraph executions equivalent to imperative language function calls. IBSDF has proved to be an efficient way to model dataflow applications [11]. IBSDF interfaces are inherited by the PiMM proposed meta-model (Section 2.3.2).

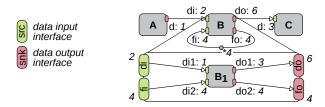

In addition to the SDF semantics, IBSDF adds interface elements to insulate levels of hierarchy in terms of schedulability analysis. An IBSDF graph G = (A, F, I) contains a set of interfaces  $I = (I_{data}^{in}, I_{data}^{out})$  (Figure 2.3).

A *data input interface*  $i_{data}^{in} \in I_{data}^{in}$  in a subgraph is a vertex transmitting to the subgraph the tokens received by its corresponding data input port. If more tokens are consumed on a data input interface than the number of tokens received on the corresponding data input port, the data input interface behaves as a circular buffer, producing the same tokens several times.

A *data output interface*  $i_{data}^{out} \in I_{data}^{out}$  in a subgraph is a vertex transmitting tokens received from the subgraph to its corresponding data output port. If a data output interface receives too many tokens, it will behave like a circular buffer and output only the last pushed tokens.

Figure 2.3: Example of an IBSDF Graph

[9] details the behavior of IBSDF data input and output interfaces as well as the IBSDF properties in terms of compositionality and schedulability checking. Through PiMM, interface-based hierarchy can be applied to other dataflow models than SDF with less restrictive firing rules.

*Parameterized Dataflow MoCs Parameterized dataflow* is a meta-modeling framework introduced in [15] that is applicable to all dataflow MoCs that present graph iterations. When this meta-model is applied, it extends the targeted MoC semantics by adding dynamically reconfigurable hierarchical actors. A reconfiguration occurs when values are dynamically assigned to the

## 26 MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

parameters of a reconfigurable actor, causing changes in the actor computation and in the production and consumption rates of its data ports. As presented in [22], reconfigurations can only occur at certain points, namely *quiescent points*, during the execution of a graph in order to ensure the runtime integrity of the application.

An objective of PiMM is to further improve parameterization compared to parameterized dataflow by introducing an explicit parameter dependency tree and by enhancing graph compositionality. Indeed, in a PSDF graph, ports are simple connectors between data FIFOs that do not insulate levels of hierarchy (Section 2.3.1). Other parameterized dataflow MoCs were previously developed such as the Scenario-Aware Dataflow (SADF) [10], an analysis-oriented model based on a probabilistic description of the dynamic firing rules of actors; or the Compaan generated KPN (CPN) [12], a parameterized extension of the Kahn Process Network (KPN) MoC. In these models, the complexity of the parameterization mechanism is handled by actors that can reconfigure the firing rules of other actors (or their own) via "control channels". This reconfiguration mechanism differs from that of PiMM in that the latter relies on the explicit definition of parameters and their dependencies which allows for a precise specification of what is influenced by a parameter, even in multiple levels of hierarchy, leading to an enhanced predictability and quasi-static scheduling potential for the model.

## 2.3.2 Our Contribution on Parameterized and Interfaced Dataflow Meta-Modeling

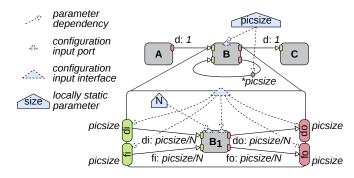

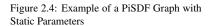

Most of the following discussion is borrowed from our publication on PiMM [8]. PiMM can be used similarly to the *parameterized dataflow* to extend the semantics of all dataflow MoCs implementing the concept of graph iteration. PiMM adds both interface-based hierarchy and an explicit parameter dependency tree to the semantics of the extended MoC. In this section, we formally present PiMM through its application to the SDF MoC, composing the PiSDF model. The pictograms associated to the different elements of the PiSDF semantics are presented in Figures 2.4 and 2.5.

A PiSDF graph  $G = (A, F, I, \Pi, \Delta)$  contains, in addition to the SDF actor set *A* and FIFO set *F*, a set of hierarchical interfaces *I*, a set of *parameters*  $\Pi$ , and a set of *parameter dependencies*  $\Delta$ .

#### Parameterization semantics

A parameter  $\pi \in \Pi$  is a vertex of the graph associated to a parameter value  $v \in \mathbb{N}$  that is used to configure elements of the graph. For a better analyzability of the model, a parameter can be restricted to take only values of a finite subset of  $\mathbb{N}$ . A *configuration* of a graph is the assignation of parameter values to all parameters in  $\Pi$ .

An actor  $a \in A$  is now associated to a set of ports  $(P_{data}^{in}, P_{data}^{out}, P_{cfg}^{in}, P_{cfg}^{out})$

where  $P_{cfg}^{in}$  and  $P_{cfg}^{out}$  are a set of configuration input and output ports respectively. A configuration input port  $p_{cfg}^{in} \in P_{cfg}^{in}$  of an actor  $a \in A$  is an input port that depends on a parameter  $\pi \in \Pi$  and can influence the computation of a and the production/consumption rates on the dataflow ports of a. A configuration output port  $p_{cfg}^{out} \in P_{cfg}^{out}$  of an actor  $a \in A$  is an output port that can dynamically set the value of a parameter  $\pi \in \Pi$  of the graph (Section 2.3.2).

A parameter dependency  $\delta \in \Delta$  is a directed edge of the graph that links a parameter  $\pi \in \Pi$  to a graph element influenced by this parameter. Formally a parameter dependency  $\delta$  is associated to the two functions *setter* :  $\Delta \to \Pi \cup P_{cfg}^{out}$  and *getter* :  $\Delta \to \Pi \cup P_{cfg}^{in} \cup F$  which respectively give the source and the target of  $\delta$ . A parameter dependency set by a configuration output port  $p_{cfg}^{out} \in P_{cfg}^{out}$  of an actor  $a \in A$  can only be received by a parameter vertex of the graph that will dispatch the parameter value to other graph elements, building a parameter dependency tree. Dynamism in PiMM relies on parameters whose values can be used to influence one or several of the following properties: the computation of an actor, the production/consumption rates on the ports of an actor, the value of another parameter, and the delay of a FIFO (Section 2.3.1). In PiMM, if an actor has all its production/consumption rates set to 0, it will not be executed.

A parameter dependency tree  $T = (\Pi, \Delta)$  is formed by the set of parameters  $\Pi$  and the set of parameter dependencies  $\Delta$ . The parameter dependency tree T is similar to a set of combinational relations where the value of each parameter is resolved virtually instantly as a function of the parameters it depends on. This parameter dependency tree is in contrast to the precedence graph (A, F) where the firing of the actors is enabled by the data tokens flowing on the FIFOs.

#### $\pi$ SDF hierarchy semantics

The hierarchy semantics used in PiSDF inherits from the interface-based dataflow introduced in [9] and presented in Section 2.3.1. In PiSDF, a hierarchical actor is associated to a unique PiSDF subgraph. The set of interfaces I of a subgraph is extended as follows:  $I = (I_{data}^{in}, I_{cfg}^{out}, I_{cfg}^{in}, I_{cfg}^{out})$  where  $I_{cfg}^{in}$  is a set of *configuration input interfaces* and  $I_{cfg}^{out}$  a set of *configuration output interfaces*.

Configuration input and output interfaces of a hierarchical actor are respectively seen as a configuration input por  $p_{cfg}^{in} \in P_{cfg}^{in}$  and a configuration output port  $p_{cfg}^{out} \in P_{cfg}^{out}$  from the upper level of hierarchy (Section 2.3.2).

From the subgraph perspective, a *configuration input interface* is seen as a locally static parameter whose value is left undefined.

A *configuration output interface* enables the transmission of a parameter value from the subgraph of a hierarchical actor to upper levels of hierarchy. In the subgraph, this parameter value is provided by a FIFO linked to a data output port  $p_{data}^{out}$  of an actor that produces data tokens with values  $v \in \mathbb{N}$ . In cases where several values are produced during an iteration of the subgraph, the configuration output interface behaves like a data output interface of size 1 and

# 28 MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

only the last value written will be produced on the corresponding configuration output port of the enclosing hierarchical actor (Section 2.3.1).

Figure 2.4 presents an example of a static PiSDF description. Compared to Figure 2.3, it introduces parameters and parameter dependencies that compose a PiMM parameter dependency tree. The modeled example illustrates the modeling of a test bench for an image processing algorithm. In the example, one token corresponds to a single pixel in an image. Images are read, pixel by pixel, by actor *A* and stored, pixel by pixel, by actor *C*. A whole image is processed by one firing of actor *B*. A feedback edge with a delay stores the previous image for comparison with the current one. Actor *B* is refined by an actor  $B_1$  processing one *N*th of the image. In Figure 2.4, the size of the image *picsize* and the parameter *N* are locally static.

$\pi$ SDF Reconfiguration As introduced in [22], the frequency with which the value of a parameter is changed influences the predictability of the application. A constant value will result in a high predictability while a value which changes at each iteration of a graph will cause many reconfigurations, thus lowering the predictability.

There are two types of parameters  $\pi \in \Pi$  in PiSDF: configurable parameters and locally static parameters. Both restrict how often the value of the parameter can change. Regardless of the type, a parameter must have a constant value during an iteration of the graph to which it belongs.

#### Configurable parameters

A configurable parameter  $\pi_{cfg} \in \Pi$  is a parameter whose value is dynamically set once at the beginning of each iteration of the graph to which it belongs. Configurable parameters can influence all elements of their subgraph except the production/consumption rates on the data interfaces  $I_{data}^{in}$  and  $I_{data}^{out}$ . As explained in [15], this restriction is essential to ensure that, as in IBSDF, a parent graph has a consistent view of its actors throughout an iteration, even if the topology may change between iterations.

The value of a configurable parameter can either be set through a parameter dependency coming from an other configurable parameter or through a parameter dependency coming from a configuration output port  $p_{cfg}^{out}$  of a *configuration actor* (Section 2.3.2). In Figure 2.5, *N* is a configurable parameter.

#### Locally static parameters

A locally static parameter  $\pi_{stat} \in \Pi$  of a graph has a value that is set before the beginning of the graph execution and which remains constant over one or several iterations of this graph. In addition to the properties listed in Section 2.3.2, a locally static parameter belonging to a subgraph can also be used to influence the production and consumption rates on the  $I_{data}^{in}$  and  $I_{data}^{out}$  interfaces of its hierarchical actor.

The value of a locally static parameter can be statically set at compile time, or it can be dynamically set by configurable parameters of upper levels of hierarchy via parameter dependencies. For example, a subgraph sees a configuration input interface as a locally static parameter but this interface can take different values at runtime if its corresponding configuration input port is connected to a configurable parameter. In Figure 2.5, *picsize* is a locally static parameter both in main graph and in subgraph *B*.

A *partial configuration state* of a graph is reached when the parameter values of all its locally static parameters are set. Hierarchy traversal of a hierarchical actor is possible only when the corresponding subgraph has reached a partial configuration state.

A *complete configuration state* of a graph is reached when the values of all its parameters (locally static and configurable) are set. If a graph does not contain any configurable parameter, its partial and complete configurations are equivalent. Only when a graph is completely configured is it possible to check its consistency, compute a schedule, and execute it.

#### **Configuration Actors**

A firing of an actor *a* with a configuration output port  $p_{cfg}^{out}$  produces a parameter value that can be used via a parameter dependency  $\delta$  to dynamically set a configurable parameter  $\pi$  (Section 2.3.2), provoking a reconfiguration of the graph elements depending on  $\pi$ . In PiMM, such an actor is called a *configuration actor*. The execution of a *configuration actor* is the cause of a reconfiguration and must consequently happen only at quiescent points during the graph execution, as explained in [22]. To ensure the correct behavior of PiSDF graphs, a *configuration actor*  $a_{cfg} \in A$  of a subgraph *G* is subject to the following restrictions:

- **R1.**  $a_{cfg}$  must be fired exactly once per iteration of *G* before the firing of any non-configuration actor. Indeed, *G* reaches a complete configuration only when all its configuration actors have fired.

- **R2.**  $a_{cfg}$  must consume data tokens only from hierarchical interfaces of *G* and must consume all available tokens during its unique firing.

- **R3.** The production/consumption rates of a  $a_{cfg}$  can only depend on locally static parameters of *G*.

- **R4.** Data tokens produced by  $a_{cfg}$  are seen as a data input interface by other actors of *G*. (i.e. they are made available using a ring-buffer and can be consumed more than once).

These restrictions naturally enforce the local synchrony conditions of *parameterized dataflow* defined in [15] and reminded in Section 2.3.2.

The firing of all configuration actors of a graph is needed to obtain a complete configuration of this graph. Consequently, configuration actors will always be executed before other (non-configuration) actors of the graph to which they belong. Configuration actors are the only actors whose firing is not datadriven but driven by hierarchy traversal.

The sets of configuration and non-configuration actors of a graph are respectively equivalent to the subinit  $\phi_s$  and the body  $\phi_b$  subgraphs of *parameterized dataflow* [15]. Nevertheless, configuration actors provide more flexibility than subinit graphs as they can produce data tokens that will be consumed by nonconfiguration actors of their graph. The init subgraph  $\phi_i$  has no equivalent in PiMM as its responsibility, namely the configuration of the production/consumption rates on the actor interfaces, is performed by configuration input interfaces and parameter dependencies.

Figure 2.5 presents an example of a PiSDF description with reconfiguration. It is a modified version of the example in Figure 2.4 presented in Section 2.3.2. In Figure 2.5, the parameter N is a configurable parameter of subgraph B, while the parameter *picsize* is a locally static parameter. The number of firings of actor  $B_1$  for each firing of actor B is dynamically configured by the configuration actor *setN*. In this example, the dynamic reconfiguration dynamically adapts the number N of firings of  $B_1$  to the number of cores available to perform the computation of B. Indeed, since  $B_1$  has no self-loop FIFO, the N firings of  $B_1$  can be executed concurrently.

Figure 2.5: Example of a PiSDF Graph with Reconfiguration

*Model Analysis and Behavior* The PiSDF MoC presented in Section 2.3.2 is dedicated to the specification of applications with both dynamic and static

parameterizations. This dual degree of dynamism implies a two-step analysis of the behavior of applications described in PiSDF: a compile time analysis and a runtime analysis. In each step a set of properties of the application can be checked, such as the consistency, the deadlock freeness, and the boundedness. Other operations can be performed during one or both steps of the analysis such as the computation of a schedule or the application of graph transformation to enhance the performance of the application.

*Compile Time Schedulability Analysis* PiSDF inherits its schedulability properties both from the interface-based dataflow modeling and the *parameterized dataflow* modeling.

In interface-based dataflow modeling, as proved in [9], a (sub)graph is schedulable if its precedence SDF graph (A, F) (excluding interfaces) is consistent and deadlock-free. When a PiSDF graph reaches a complete configuration, it becomes equivalent to an IBSDF graph. Given a complete configuration, the schedulability of a PiSDF graph can thus be checked using the same conditions as in interface-based dataflow.

In *parameterized dataflow*, the schedulability of a graph can be guaranteed at compile time for certain applications by checking their *local synchrony* [15]. A PSDF (sub)graph is locally synchronous if it is schedulable for all reachable configurations and if all its hierarchical children are locally synchronous. As presented in [15], a PSDF hierarchical actor composed of three subgraphs  $\phi_i$ ,  $\phi_s$  and  $\phi_b$  must satisfy the 5 following conditions in order to be locally synchronous:

- 1.  $\phi_i$ ,  $\phi_s$  and  $\phi_b$  must be locally synchronous, i.e. they must be schedulable for all reachable configurations.

- 2. Each invocation of  $\phi_i$  must give a unique value to parameter set by this subgraph.

- 3. Each invocation of  $\phi_s$  must give a unique value to parameter set by this subgraph.

- 4. Consumption rates of  $\phi_s$  on interfaces of the hierarchical actor cannot depend on parameters set by  $\phi_s$ .

- 5. Production/consumption rates of  $\phi_b$  on interfaces of the hierarchical actor cannot depend on parameters set by  $\phi_s$ .

The last four of these conditions are naturally enforced by the PiSDF semantics presented in Section 2.3.2. However, the schedulability condition number 1., which states that all subgraphs must be schedulable for all reachable configurations, cannot always be checked at compile time. Indeed, since values of the parameters are freely chosen by the application developer, non-schedulable graphs can be described. It is the responsibility of the developer to make sure that an application will always satisfy the schedulability condition; this responsibility is similar to that of writing non-infinite loops in imperative languages.

PiSDF inherits from PSDF the possibility to derive quasi-static schedules at compile time for some applications. A quasi-static schedule is a schedule that statically defines part of the scheduling decisions but also contains parameterized parts that will be resolved at runtime.

#### 2.3.3 Comparison or PiMM with other MoCs

Table 2.1 presents a comparison of dataflow MoCs based on a set of common MoC features. The compared MoCs include the static SDF [16], ADF [19], and IBSDF [9]. Also compared are the dynamic PSDF [15], SADF [10], DPN [13], and PiSDF.

In Table 2.1, a black dot indicates that the feature is implemented by a MoC, an absence of dot means that the feature is not implemented, and an empty dot indicates that the feature may be available for some applications described with this MoC. It is important to note that the full semantics of the compared MoCs is considered here. Indeed, some features can be obtained by using only a restricted semantics of other MoCs. For example, all MoCs can be restricted to describe a SDF, thus benefiting from the static schedulability and the decidability but losing all reconfigurability.

| Feature                  | S | FA | JF B | 3Dr | DF C | SDF<br>SP | DFDP |

|--------------------------|---|----|------|-----|------|-----------|------|

| Hierarchy                |   |    | •    | •   | •    |           |      |

| Compositional            |   |    | ٠    |     | •    |           |      |

| Reconfigurable           |   |    |      | ٠   | •    | •         | •    |

| Configuration dependency |   |    |      |     | •    | •         |      |

| Statically schedulable   | • | •  | •    |     |      |           |      |

| Decidability             | • | ٠  | ٠    | 0   | 0    | ٠         |      |

| Variable rates           |   | ٠  |      | ٠   | •    | ٠         | •    |

| Non-determinism          |   |    |      |     |      | ٠         | •    |

Table 2.1: Features comparison of different dataflow MoCs

The features compared in Table 2.1 are the following: *Hierarchy*: composability can be achieved by associating a subgraph to an actor. *Compositional*: graph properties are independent from the internal specifications of the subgraphs that compose it [21]. *Reconfigurable*: actors firing rules can be reconfigured dynamically. *Configuration dependency*: the MoC semantics includes an element dedicated to the transmission of configuration parameters. *Statically schedulable*: a fully static schedule can be derived at compile time [16]. *Decidability*: the schedulability is provable at compile time. *Variable rates*: production/consumption rates are not a fixed scalar. *Non-determinism*: output of an algorithm does not solely depends on inputs, but also on external factors (e.g. time, randomness).

In the next section on system adaptivity, we put the focus on using the

PiSDF model to efficiently use the resources of a system even in the case of highly variable application, and this without requiring additional design effort.

#### 2.4 System Adaptivity

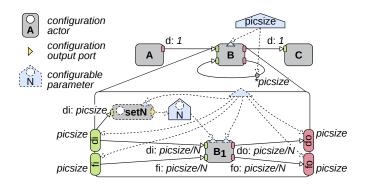

A system is qualified as adaptive when it can use variations on application loads to save resources and optimize Non-Functional Properties. Adaptivity also refers to the capacity to receive, at runtime, a new application, adapt to it and resume execution. We have started in the PhD thesis of El Mehdi Abdali a study of adaptive systems for hardware-defined applications using the Dynamic and Partial Reconfiguration (DPR) capabilities of modern FPGAs. In the former PhD thesis of Julien Heulot, we have targeted software-defined systems over heterogeneous multi-core architectures and a dynamic scheduling method has been developed for the PiSDF MoC. The following discussion has been published in the Proceedings of the GlobalSIP 2014 conference<sup>5</sup>. The proposed scheduling method, named JIT-MS, aims to efficiently schedule PiSDF graphs on multicore architectures. This method exploits features of PiSDF to find locally static regions that exhibit predictable communications.

As evoked in the introduction of this report, embedded processors contain an increasingly number of cores [24, 25, 26]. This trend is mainly due to limitations in the processing power of individual PEs as a result of power consumption considerations. Concurrently, signal processing applications are becoming increasingly dynamic in terms of hardware resource requirements. For example, the Scalable High Efficiency Video Coding (SHVC) standard provides a mechanism to temporarily reduce the resolution of a transmitted video in order to match the instantaneous bandwidth of a network [27].

One of the main challenges of the design of multicore signal processing systems is to distribute computational tasks efficiently onto the available PEs while taking into account dynamic application and architecture changes. The process of assigning, ordering and timing actors on PEs in this context is referred to as *multicore scheduling*. Inefficient use of the PEs affects latency and energy consumption, making multicore scheduling an important challenge [28]. JIT-MS addresses this challenge. JIT-MS is a flexible scheduling method that determines scheduling decisions at run-time to optimize the mapping of an application onto multicore processing resources. In relation to the scheduling taxonomy defined by Lee and Ha [29], JIT-MS is a *fully dynamic* scheduling strategy. In the context of the taxonomy used in Singh's survey [30], our method can be classified as "On-the-fly" mapping, targeting heterogeneous platforms with a centralized resource management strategy.

JIT-MS exploits the fact that between two quiescent points[22], the application can be considered static. Decisions are taken Just-In-Time, immediately after the quiescent points are reached, unveiling new application parallelism.

Various competing frameworks based on OpenMP [31] and OpenCL [32] language extensions are currently proposed to address the multicore schedul-

<sup>5</sup> Julien Heulot, Maxime Pelcat, Jean-François Nezan, Yaset Oliva, Slaheddine Aridhi, and Shuvra S Bhattacharyya. Justin-time scheduling techniques for multicore signal processing systems. In *Proceedings of the GlobalSIP conference*. IEEE, 2014

# 34 MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

ing challenge. However, these extensions are based on imperative languages (e.g., C, C++, Fortran) that do not provide mechanisms to model specific signal flow graph topologies. In the experimental results on this section we demonstrate that JIT-MS is capable of challenging, on an 8-core DSP processor, an OpenMP implementation provided by Texas Instruments. Latency improvements of up to 26% are observed, obtained because advanced information is known by the runtime manager on the application. The next sections detail JIT-MS.

#### 2.4.1 Context

*Runtime Architecture* JIT-MS is applicable to heterogeneous platforms. On such platforms, a locally optimal decision to fire an actor (e.g., based on the availability of its input data) can be inefficient when considering the system globally. In order to take effective decisions globally, a Master/Slave execution scheme is chosen for the system.

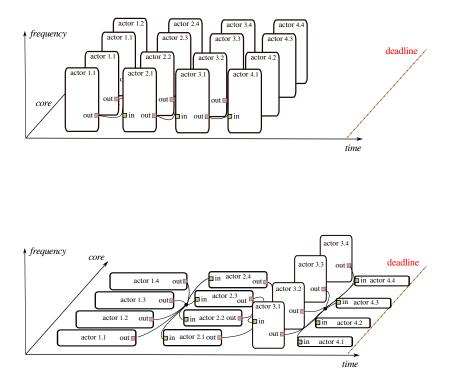

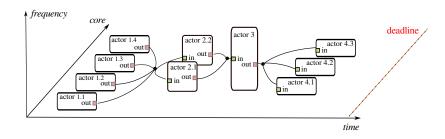

The JIT-MS method relies on multiple software or hardware *Processing Elements (PEs)* that are slave components responsible for processing actors (Figure 2.6). PEs can be of multiple types, such as General Purpose Processors (GPPs), DSPs, or hardware accelerators. The master processor of the JIT-MS system is called *Scheduling Element (SE)*. This is the only component that has access to the general algorithm topology. *Jobs* are used to communicate between the SE and PEs. Each PE has a job queue from which it pops jobs out prior to their execution. *Parameters* influence dataflow graph topology or execution timing of actors. When a parameter value is set by a configuration actor, its value is sent to the SE via a parameter queue. Finally, *Data FIFOs* are used by the PEs to exchange data tokens. A data FIFO can be implemented either over a shared memory or over network-on-chip communication.

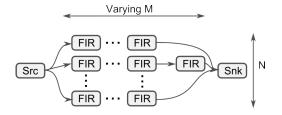

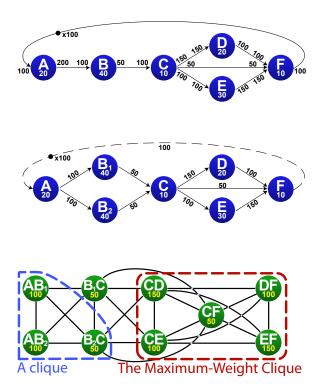

*Benchmark* We illustrate the JIT-MS scheduling algorithm in this report by the scheduling of a benchmark application. This benchmark is an extension of the *MP-sched* benchmark [33]. The MP-sched benchmark can be viewed as a two-dimensional grid involving *N* channels, where each branch consists of *M* cascaded Finite Impulse Response (FIR) filters of *NbS* samples. We extend

the MP-sched benchmark by allowing the *M* parameter to vary across different branches, as illustrated in Figure 2.7. We refer to this extended version of the MP-sched benchmark as *heterogeneous-chain-length MP-sched* (*HCLM-sched*).

Figure 2.7: Description of the HCLM-Shed benchmark used to test JIT-MS scheduling.

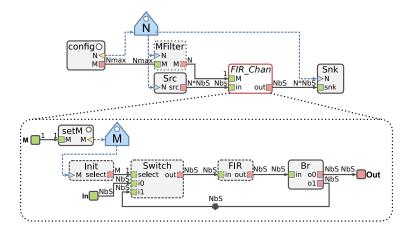

A PiSDF representation of the HCLM-sched benchmark is shown in Figure 2.8. To represent the channels in the HCLM-sched benchmark, a hierarchical actor called *FIR\_Chan* is introduced. The top level graph is designed to repeat *N* times this actor. In the subgraph describing the behavior of the *FIR\_Chan* actor, *M* pipelined FIR filter repetitions in the branches are handled by a feedback loop and specific control actors (*Init, Switch* and *Broadcast*).

Figure 2.8: A PiSDF model of the HCLM-sched benchmark.

*Notations* To describe JIT-MS, the following notation is used. *CA* represents the set of configuration actors of the given PiSDF graphand  $\overline{CA}$  represents all actors in the given PiSDF graph that are not configuration actors.

#### 2.4.2 Just-In-Time Multicore Scheduling (JIT-MS)

*Multicore Scheduling of Static Subgraphs* JIT-MS involves decomposing the scheduling of a given PiSDF graph into the scheduling of a sequence  $X_1, X_2, ...$  of SDF graphs. Different executions (with different sets of input data) can result in different sequences of SDF graphs for the same PiSDF graph. For a given execution, we refer to each  $X_i$  as a *step* of the JIT-MS scheduling process. At each step, resolved parameters trigger the transformation of the

# 36 MODELS, METHODS AND TOOLS FOR BRIDGING THE DESIGN PRODUCTIVITY GAP OF EMBEDDED SIGNAL PROCESSING SYSTEMS

PiSDF graph into an SDF graph, which can be scheduled by any of the numerous existing SDF scheduling heuristics that are relevant for multicore architectures [34]. For example, [35] presents a set of techniques that can be applied upon transforming the resulting SDF graph into an single rate SDF (srSDF) graph. An srSDF graph is an SDF graph in which the production rate on each edge is equal to the consumption rate on that edge. A consistent SDF graph can be transformed into an equivalent srSDF graph for instance by applying techniques that were introduced by Lee and Messerschmitt [36].

The Just-In-Time Multicore Scheduling (JIT-MS) method is based on a static multicore scheduling method which is composed of the following sequence of phases:

- Computing the Repetition Vector (RV) of the *current graph* (the graph that is presently being scheduled). The RV is a positive-integer vector and represents the number of firings of each actor in a minimal periodic scheduling iteration for the graph. We note however, that certain technical details of PiSDF require adaptations to the conventional repetitions vector computation process from [16].

- Converting the SDF graph into an equivalent srSDF graph, where each actor is instantiated a number of times equal to its corresponding RV component.

- 3. Scheduling actors and communications from a derived acyclic srSDF graph onto the targeted heterogeneous platform. Any scheduling heuristic that is applicable to acyclic srSDFs graphs can be chosen here e.g., the applied schedule can be a list scheduler, fast scheduler, flow-shop or genetic scheduler [30, 37, 35]. Upon completing the described scheduling process, the resulting schedule *S* is executed.

A complete JIT-MS schedule of a PiSDF hierarchical graph consists of several of these phases, repeated as many times as needed.

In a PiSDF graph, some data FIFOs behave as Round Buffers (RBs) — i.e., such FIFOs produce multiple copies of individual tokens as necessary to satisfy consumption demand. In particular, FIFOs at the interface of a hierarchical actor have RBs behavior to help ensure composability in hierarchical specifications. FIFOs connecting configuration actors to other actors also behave as RBs to ensure that configuration actors fire only once per subgraph. Application designers using the PiSDF model of computation need to take such RB behavior into account during the development process.

Configuration Actors and such RBs are excluded from the RV computation as they are forced to fire only once.

*Multicore Scheduling of Full Graphs* The JIT-MS method is based on the PiSDF runtime operational semantic. As shown in [8], the JIT-MS scheduler has to proceed in multiple steps, each one unveiling a new portion of srSDF

graph for scheduling. In one step, configuration actors have to be fired first, they produce parameters needed to resolve the rest of the subgraph. When all parameters are solved at one hierarchy level, scheduling of other actors of this hierarchy level is made possible. The complete srSDF graph is only known when all configuration actors have been executed.

Once an srSDF graph has been generated, it can be analyzed to exploit the parallelism of the application (Section 2.4.2). The JIT-MS runtime schedules the actors and communications and fires their execution on the platform. Newly instantiated hierarchical actors are added to a global srSDF graph, called *execution graph*, and the same process can be used until the whole graph has been processed.

To keep track of actor's execution, each actor of the execution graph is tagged with a flag representing its execution state. An actor can be Run(R), *Not Executable* (*N*) or *Executable* (*E*). An actor is *Executable* only when all its parameters are resolved and when all its predecessors are *Executable* or *Run*.

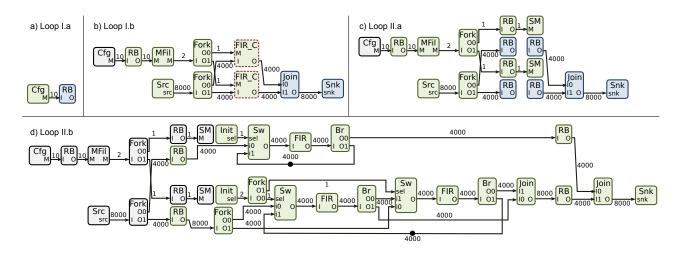

Figure 2.9: single rate SDFs (srSDFs) graphs generated from the HCLM-sched benchmark of Figure 2.8. Blue actors are not executable, green ones are executable and black ones are already run. Red dashed actors are hierarchical.

*Applying JIT-MS to the Benchmark* The *execution graph* shape at each step of the HCLM-sched benchmark can be seen in Figure 2.9.

Figure 2.9.a corresponds to the execution graph state at the end of the first phase of the first iteration of the while loop (loop I.a). At this point, N is set to 2. Then Figure 2.9.b corresponds to execution graph state after the third phase of the first iteration (loop I.b). The hierarchical *FIR\_Chan* actors are instanciated. Then, Figures 2.9.c and 2.9.d correspond to the execution, first of the internal configuration actors of *FIR\_Chan* (*SM*), then of their actors with parameter  $M = \{1, 2\}$ .

#### 2.4.3 Experimental Results

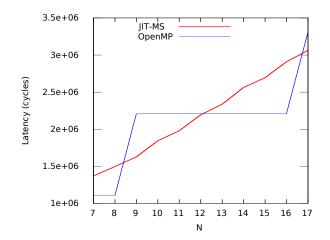

The main goal of JIT-MS is to parallelize dynamic applications. The following experimental results focus on the comparison between the JIT-MS approach and an OpenMP runtime system with similar objectives. Results are acquired by studying the latency of single and multiple iterations of the HCLM-sched benchmark on a Texas Instruments TMS320C6678 multicore DSP processor [24].

OpenMP is a framework designed for shared memory multiprocessing. It provides mechanisms for launching parallel teams of threads to execute an algorithm on a multicore architecture. OpenMP applications are designed with a succession of sequential code sections, executed by a master thread, and parallel code sections, distributed in a team of threads dispatched onto multiple cores [31]. The c6678 processor is composed of 8 c66x DSP cores interconnected by a NoC called TeraNet with access to an internal shared memory. To perform synchronization between cores, hardware queues provided by the Texas Instruments Multicore Navigator[38] have been used in this study.

Results on execution time are displayed in Figure 2.10.a.

Figure 2.10: JIT-MS Latency versus values of *N* for the HCLM-sched benchmark

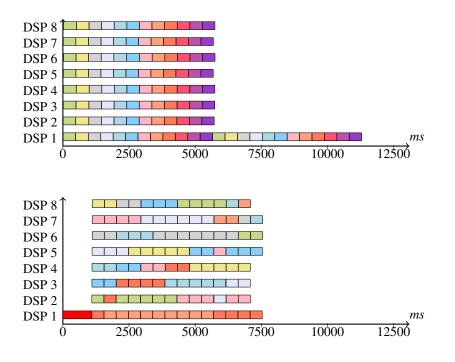

Experimental results of Figure 2.10 show that the OpenMP implementation latency curve displays a step shape when increasing *N*. With the JIT-MS implementation, the graph transformation and scheduling phases introduce an overhead but the execution efficiency over varying parameters is smoother. The overhead can be observed on the figure when N equals to 7 or 8 as the resulting scheduling is the same as OpenMP. The transformation to srSDF extracts more parallelism than OpenMP from the subdivision of channels into multiple FIRs. These choices make JIT-MS suitable for unbalanced applications. In the HCLM-sched benchmark with 9 channels, the overall latency is reduced of up to 26%. Figures 2.11 and 2.12 illustrate this effect by displaying the real Gantt chart of execution, based on measurements from the internal processor timer. Spider scheduling is shown to introduce an initial latency due to graph management (the red block on the left of Figure 2.12) but then efficiently interleaves

the executed actors while OpenMP fails to mix iterations.

Figure 2.11: Gantt Chart of the OpenMP schedule with N = 9 and M = 12

### 2.5 Conclusions on Design Efficiency

PiMM can be applied to a dataflow MoC to increase its expressiveness, enable the specification of reconfigurable applications, and feed either a quasistatic schedule or the JIT-MS dynamic schedule. We have shown on the PiSDF MoC that while bringing dynamism and compositionality, the explicit parameter dependency tree and the interface-based hierarchy mechanism introduced by PiMM maintain strong predictability for the extended model and enforce the conciseness and readability of application descriptions.

JIT-MS aims to find a balance between a static scheduling that has no runtime overhead but does not take into account the application modifications, and a fully dynamic scheduling that costs time and resources. Additionally to the example benchmark presented in this report, the Just-In-Time Multicore Scheduling (JIT-MS) scheduling method applied to a PiSDF-modeled application has been shown to obtain good performance also on a stereo matching algorithm and on large Fast Fourier Transforms (FFTs)<sup>6</sup>. The Spider runtime implementing JIT-MS is currently extended to support manycore Kalray MPPA processors in context of the PhD thesis of Julien Hascoët. Its efficiency results motivate future work on model-based parallel system design where the advanced application knowledge offered by the dataflow MoC is complemented by architecture knowledge stored in an MoA.

Additionally to this work on parameterized dataflow, we have also explored how internal actor parallelism can influence dataflow execution<sup>7</sup>. In this work,

<sup>6</sup> Julien Heulot. *Runtime multicore scheduling techniques for dispatching parameterized signal and vision dataflow applications on heterogeneous MPSoCs.* PhD thesis, INSA Rennes, 2015

<sup>7</sup> Zheng Zhou, William Plishker, Shuvra S Bhattacharyya, Karol Desnos, Maxime Pelcat, and Jean-Francois Nezan. Scheduling of parallelized synchronous dataflow actors for multicore signal processing. *Journal of Signal Processing Systems*, 2016

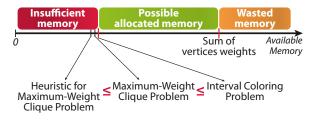

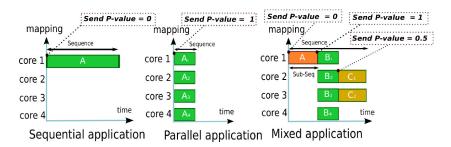

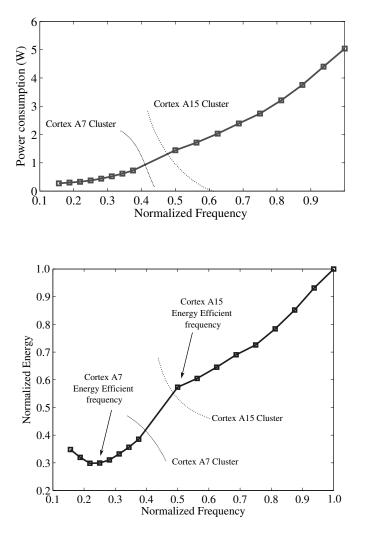

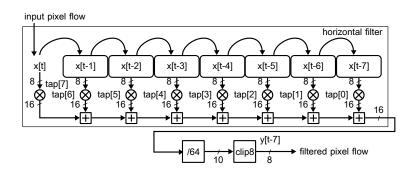

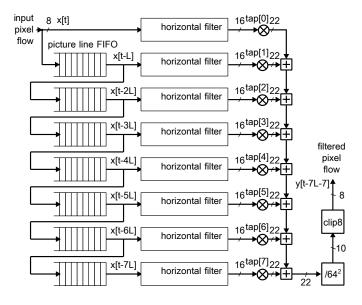

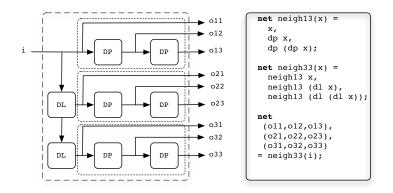

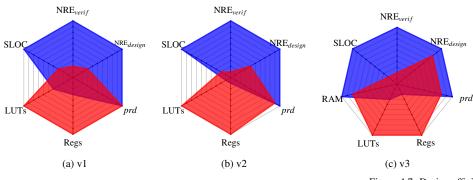

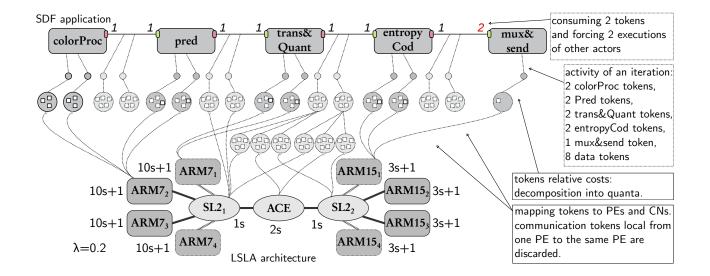

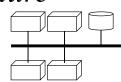

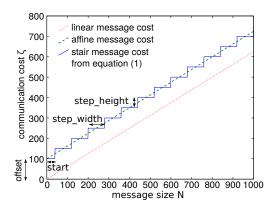

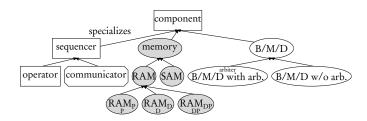

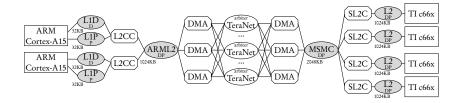

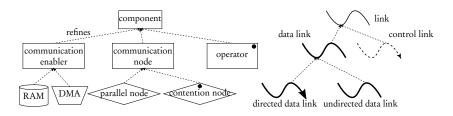

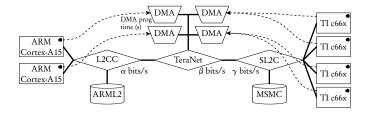

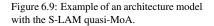

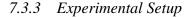

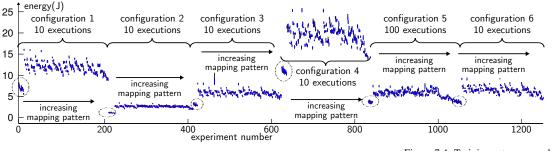

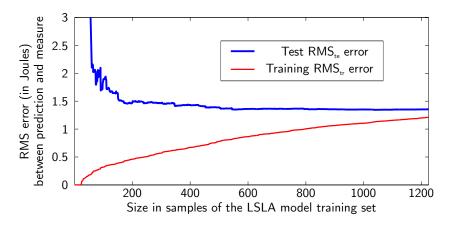

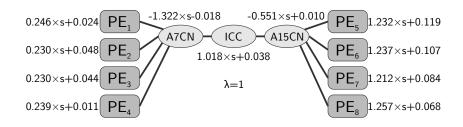

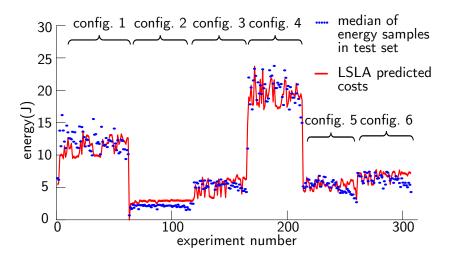

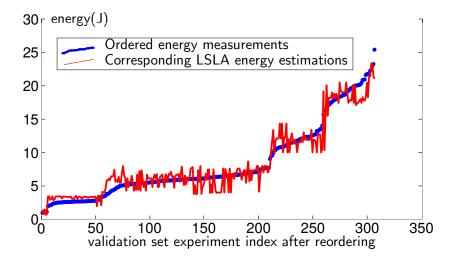

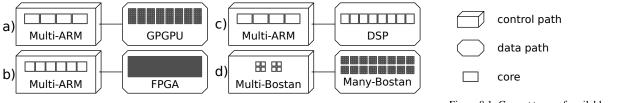

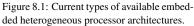

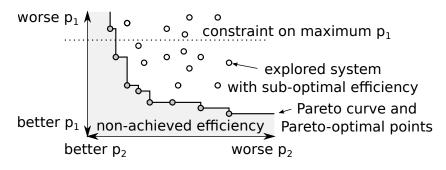

a type of parallel task scheduling problem called Parallel Actor Scheduling (PAS) has been defined. It combines intra- and inter-actor parallelism for platforms in which individual actors can be parallelized across multiple cores. We demonstrated that the PAS-targeted scheduling framework provides a useful range of trade-offs between synthesis time requirements and the quality of the derived solutions.