## Caractérisation électrique des dispositifs FDSOI établie par mesures C-V

Blend Mohamad

#### ► To cite this version:

Blend Mohamad. Caractérisation électrique des dispositifs FDSOI établie par mesures C-V. Micro et nanotechnologies/Micro électronique. Université Grenoble Alpes, 2017. Français. NNT: 2017GREAT001. tel-01618543

### HAL Id: tel-01618543 https://theses.hal.science/tel-01618543

Submitted on 18 Oct 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ GRENOBLE ALPES

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nanoélectronique et nanotechnologies Arrêté ministériel : 7 août 2006

Présentée par

#### Blend MOHAMAD

Thèse dirigée par **Dr. Gérard GHIBAUDO** et codirigée par **Dr. Charles LEROUX**

préparée au sein du CEA-LETI et de l'IMEP-LAHC dans l'École Doctorale d'Électronique, Électrotechnique, Automatique et Traitement du Signal

## Electrical characterization of fully depleted SOI devices based on C-V measurements

Thèse soutenue publiquement le **30 Mai 2017**, devant le jury composé de :

Albdelkader SOUIFI PR. INL/INSA de Lyon, Président Pascal MASSON PR. Université de Nice Sophia Antipolis, Rapporteur Jean Michel SALLESE PR. EPF Lausanne (CH), Rapporteur Francis BALESTRA DR. CNRS Alpes, Examinateur Charles LEROUX ING. CEA-LETI, Co-Encadrant Gérard GHIBAUDO DR. CNRS Alpes, Directeur de thèse

# Acknowledgements

Vorrei ringraziare in primis Charles Leroux, relatore di questa tesi di dottorato, oltre che per l'aiuto fornitomi in tutti questi anni e la grande conoscenza che mi ha donato, per la disponibilità e precisione dimostratemi durante tutto il periodo di stesura. Senza di Lei questo lavoro non avrebbe preso vita!

Un altro sincero ringraziamento va a Gerard Ghibaudo, direttore di questa tesi di dottorato, per la sua esperienza, conoscenza, disponibilità e per tutte le discussioni avute in questi tre anni. Insieme siamo riusciti a ottenere risultati teorici esperimentali importanti, addirittura oltre le attese.

Evidentemente non mancano i ringraziamenti, dovuti, a tutto il team del laboratorio di caratterizzazione elettrica (LCTE) del CEA-LETI: Gilles Reimbold per avermi accolto nel laboratorio, Xavier Garros, Mikaël Cassé, William van den Daele, Carlo Cagli, Giovanni Romano, Alain Toffoli, Jean Coignus, Jacques Cluzel, e Denis Blachier per i continui aiuti tecnici e teorici e ovviamente Antoine, Remy, Pushpendra, Cheikh, Alexandre V., Illias, Clément, Niccolò, Jonathan, Guillaume, Johan, Philippe, Thomas e Genaro per tutti i bei momenti.

Sinceri ringraziamenti vanno anche agli amici più cari per gli splendidi e indimenticabili momenti passati insieme a Erba e a Grenoble: Stefano Pina, Stefano Rossini, Luca Presti, Giulio Torrente, Giulio Marti, Riccardo Zini e la squadra di calcio di ST Crolles.

Un grande ringraziamento va a Joanna, mia compagna di vita, a Rubi e alla sua famiglia. Il loro instancabile sostegno e aiuto mi hanno permesso di arrivare fin qui, contribuendo alla mia formazione personale.

E infine un doveroso ringraziamento va alla mia famiglia per tutto l'aiuto durante questi anni. Senza i quali non avrei neppure iniziato questa carriera. Questa tesi dunque la dedico a loro in segno di riconoscimento per il continuo sostegno.

## Contents

| Ac              | Acknowledgements i                                                                  |                                                                                                                                                                                                                                                  |                                  |  |

|-----------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|

| General Context |                                                                                     |                                                                                                                                                                                                                                                  |                                  |  |

| 1               | <b>Intr</b><br>1.1<br>1.2                                                           | oduction to C-V measurements and operation of MOSIntroductionMOS transistor and operation regime during                                                                                                                                          | <b>5</b><br>5                    |  |

|                 |                                                                                     | C-V measurement                                                                                                                                                                                                                                  | 6<br>7<br>10                     |  |

|                 | 1.3                                                                                 | 1.2.3 Total charge and C-V characteristics of a MOS capacitor $\dots$ V <sub>fb</sub> , EOT and WF <sub>eff</sub> definition $\dots \dots \dots$ | 12<br>16                         |  |

|                 | 1.4<br>1.5<br>1.6                                                                   | Impact of EOT and $WF_{eff}$ on the MOS Electrical performance<br>State of the art                                                                                                                                                               | 20<br>22<br>29                   |  |

| 2               | 1.7<br>FDS                                                                          | Conclusion                                                                                                                                                                                                                                       | 34<br><b>39</b>                  |  |

| 2               | 2.1<br>2.2                                                                          | IntroductionIntroductionFully depleted FDSOI Capacitance and Voltage Relationships2.2.1Introduction to FDSOI technology2.2.2V <sub>G</sub> and V <sub>B</sub> voltage relationship in fully depleted FDSOI                                       | 39<br>39<br>41<br>41<br>42<br>50 |  |

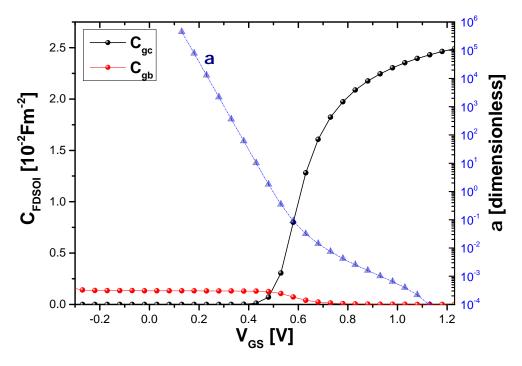

|                 | 2.3                                                                                 | <ul> <li>2.2.3 FDSOI Capacitance relationship</li></ul>                                                                                                                                                                                          | 55<br>55<br>56                   |  |

|                 | 2.4                                                                                 | characteristic of FDSOI stack                                                                                                                                                                                                                    | 64<br>71                         |  |

| 3               | Numerical Extraction of $\mathrm{WF}_{\mathrm{eff}}$ and EOT based on inversion C-V |                                                                                                                                                                                                                                                  |                                  |  |

|                 | 3.1<br>3.2<br>3.3                                                                   | IntroductionIntroductionTechnology and test structuresIntroductionNumerical methodologyIntroduction3.3.1Experimental configurations and inversion C-V characteristics3.3.2PrinciplesPrinciplesIntroduction                                       | 88                               |  |

|                 | 3.4                                                                                 | Results                                                                                                                                                                                                                                          | 95                               |  |

|    | 3.5                                                               | Concl  | usion                                                                                                             | 100 |  |  |  |

|----|-------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 4  | Analytical characterization of FDSOI stack based on inversion C-V |        |                                                                                                                   |     |  |  |  |

|    | mea                                                               | isuren | nents and linear regression                                                                                       | 103 |  |  |  |

|    | 4.1                                                               | Intro  | luction                                                                                                           | 103 |  |  |  |

|    | 4.2                                                               | Analy  | rtical extraction methodology based on linear regression                                                          | 105 |  |  |  |

|    | 4.3                                                               | Comp   | arison with NUMERICAD simulation and quantum correction                                                           | 112 |  |  |  |

|    | 4.4                                                               | Concl  | usion                                                                                                             | 116 |  |  |  |

| 5  | Analytical characterization of FDSOI stack based on               |        |                                                                                                                   |     |  |  |  |

|    |                                                                   |        | curve Q <sub>tot</sub> (E <sub>c</sub> -E <sub>f</sub> )                                                          | 119 |  |  |  |

|    | 5.1                                                               |        | luction                                                                                                           | 119 |  |  |  |

|    | 5.2                                                               | Calcu  | lation of the FDSOI stack charges                                                                                 | 121 |  |  |  |

|    |                                                                   | 5.2.1  |                                                                                                                   |     |  |  |  |

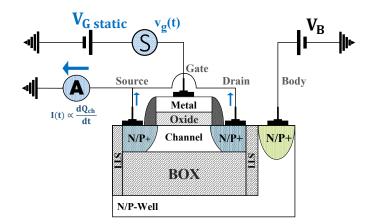

|    |                                                                   |        | set-up on FDSOI transistors                                                                                       | 121 |  |  |  |

|    |                                                                   | 5.2.2  | FDSOI transistor Operation regime during C-V measurement                                                          | 125 |  |  |  |

|    |                                                                   | 5.2.3  | Effect of back and front basing on the Gate-to-Body                                                               |     |  |  |  |

|    |                                                                   |        | capacitance measurement                                                                                           | 132 |  |  |  |

|    |                                                                   | 5.2.4  | Reconstruction of $C_{gb}$ capacitance and comparison with $C_{bg}$                                               |     |  |  |  |

|    |                                                                   |        | characteristic                                                                                                    | 137 |  |  |  |

|    |                                                                   | 5.2.5  | Identification of the well flat band condition ( $V_{fb W}$ ) and                                                 |     |  |  |  |

|    |                                                                   |        | calculation of the total charge                                                                                   |     |  |  |  |

|    | 5.3                                                               | Analy  | tical extraction based on universal curve $Q_{tot}(E_c-E_f)$                                                      |     |  |  |  |

|    |                                                                   | 5.3.1  |                                                                                                                   |     |  |  |  |

|    |                                                                   | 5.3.2  | WF <sub>eff</sub> and EOT extraction based on Q <sub>tot</sub> (E <sub>f</sub> -E <sub>c</sub> ) of MIS structure |     |  |  |  |

|    |                                                                   | 5.3.3  |                                                                                                                   |     |  |  |  |

|    |                                                                   | 5.3.4  |                                                                                                                   |     |  |  |  |

|    | 5.4                                                               | Concl  | usion                                                                                                             | 171 |  |  |  |

| Co | onclu                                                             | sion   |                                                                                                                   | 175 |  |  |  |

| Ré | İsum                                                              | é      |                                                                                                                   | 181 |  |  |  |

vi

# List of Figures

| Schematic of a MOS capacitance                                  | 6                            |

|-----------------------------------------------------------------|------------------------------|

| Typical C-V characteristics of a MOS capacitor                  | 8                            |

| MOS experimental configuration                                  | 8                            |

| MOS capacitance band diagram                                    | 9                            |

| MOS capacitance band diagram at thermodynamic equilibrium       | 9                            |

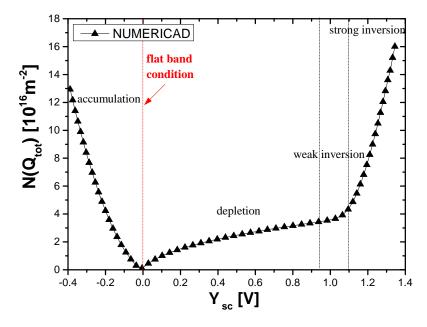

| Total charge as a function of semiconductor potential           | 12                           |

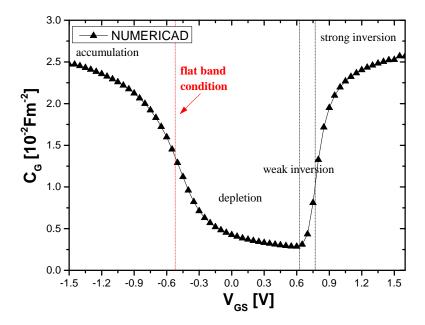

| Total capacitance as a function of the Gate voltage             | 14                           |

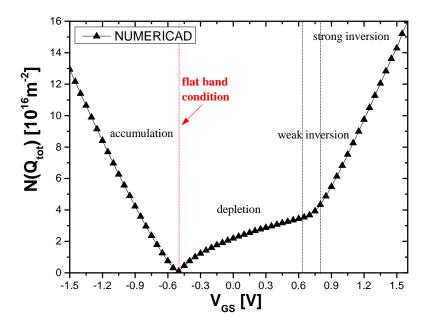

| Total charge as a function of the Gate voltage                  | 15                           |

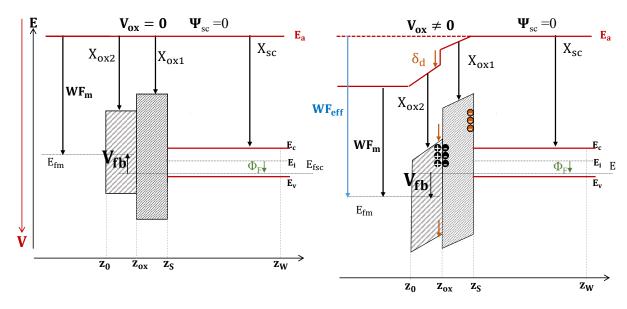

| Flat band condition for ideal and not-ideal MOS capacitor       | 16                           |

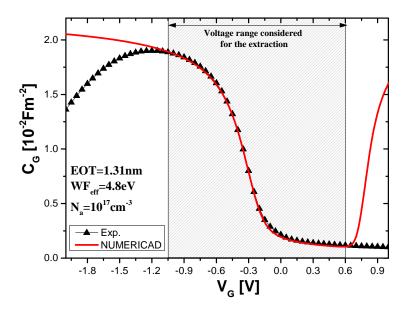

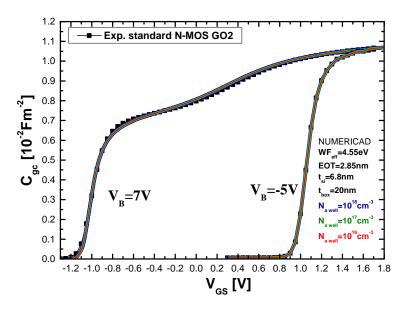

| Comparison between Experimental and NUMERICAD C-V               |                              |

| characteristics                                                 | 23                           |

| Flat band condition of the NUMERICAD and experimental C-V       |                              |

| characteristics                                                 | 23                           |

| Flat band condition for ideal and not-ideal MOS capacitor with  |                              |

| same C-V                                                        | 25                           |

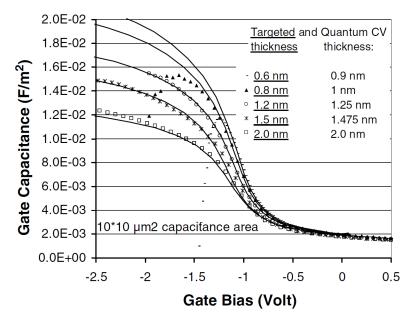

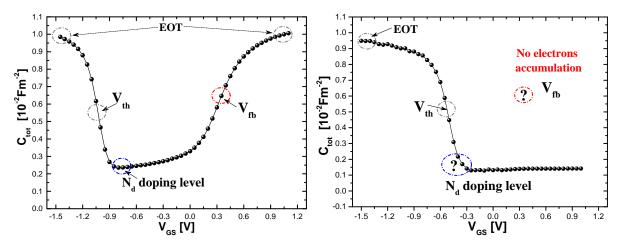

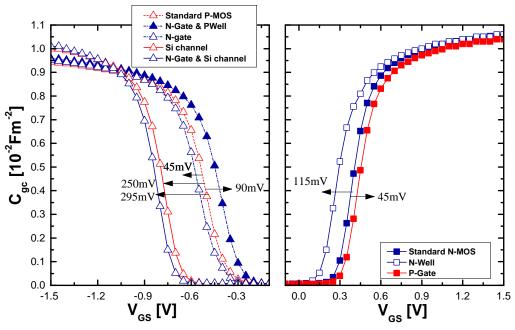

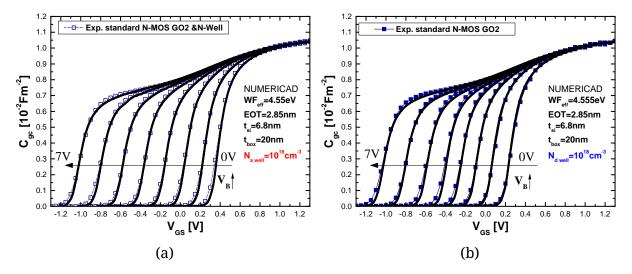

|                                                                 | 29                           |

|                                                                 |                              |

| characteristics                                                 | 30                           |

| 0                                                               |                              |

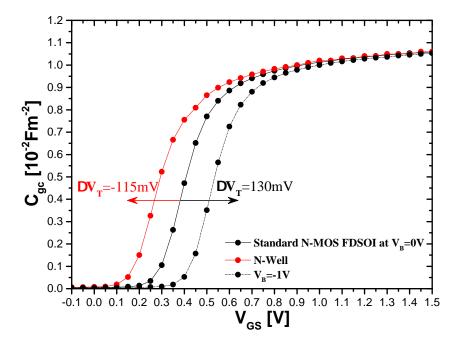

| at $V_B$ =0V and with a P-well at $V_B$ =0V and -1V             | 32                           |

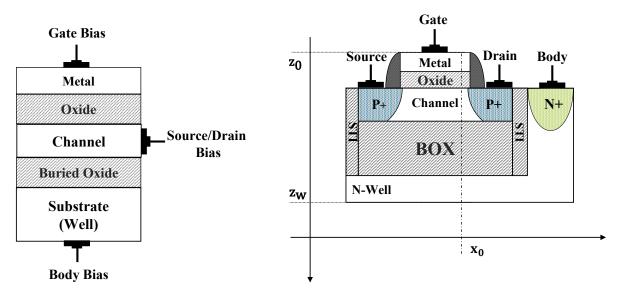

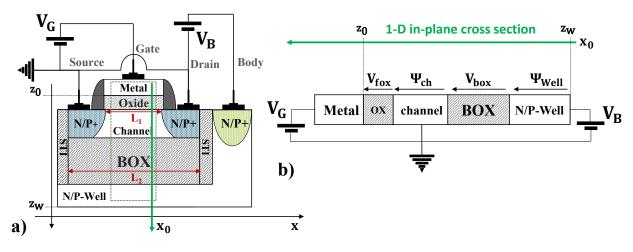

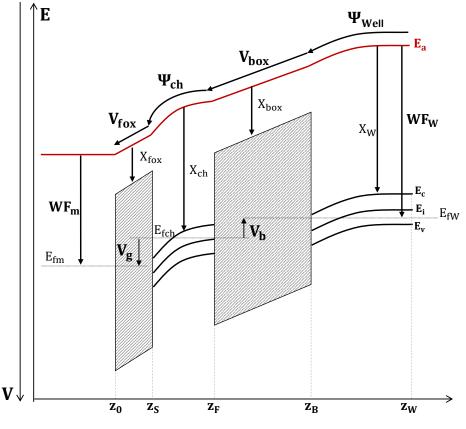

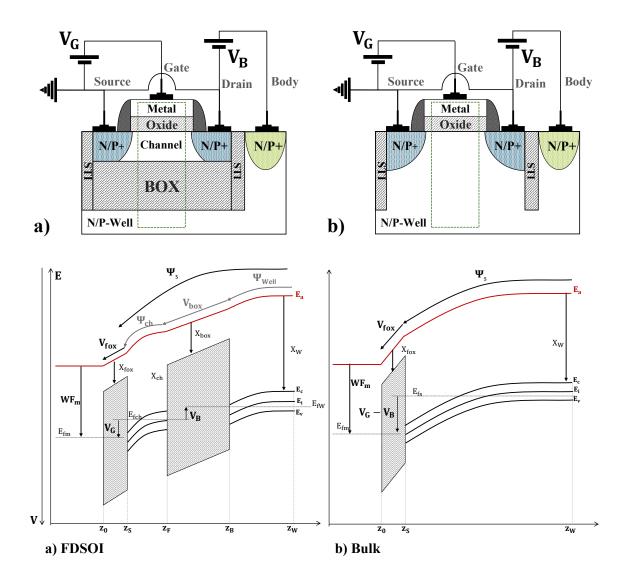

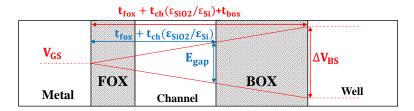

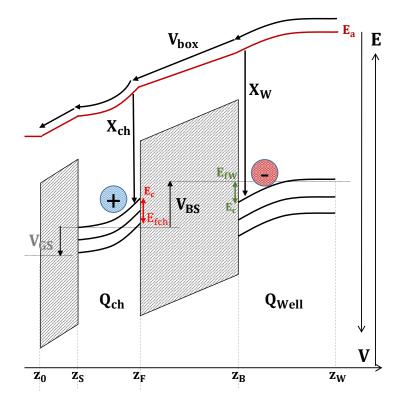

| FDSOI under biasing condition and stack potential drops         | 42                           |

|                                                                 | 44                           |

|                                                                 | 44                           |

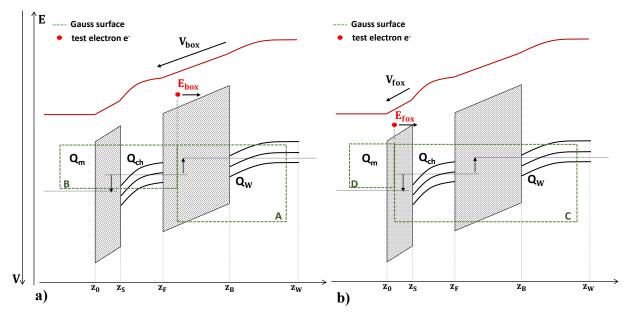

| FDSOI Back and front oxide electric fields                      | 46                           |

|                                                                 | 49                           |

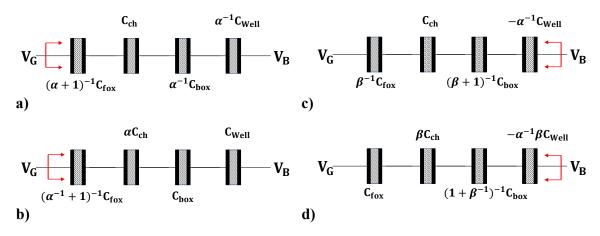

| FDSOI capacitances schemes                                      | 54                           |

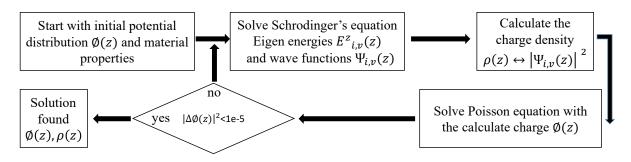

| Poisson-Schrodinger flow chart                                  | 56                           |

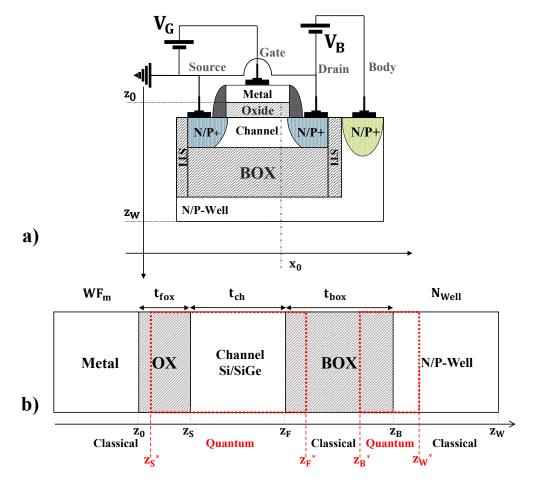

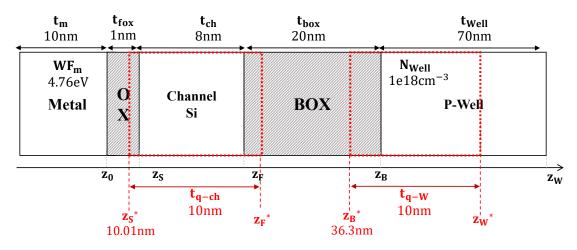

| FDSOI 1-D in-plane cross section for numerical simulation       | 57                           |

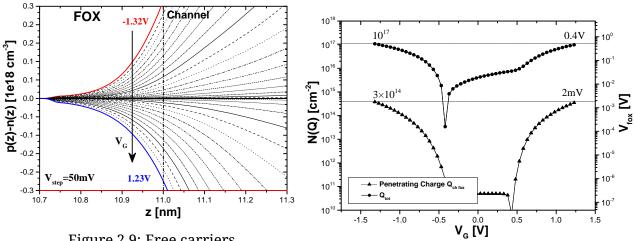

| Distribution of charge penetrating into the oxide               | 60                           |

| Total and Penetrating charge versus the Gate voltage            | 60                           |

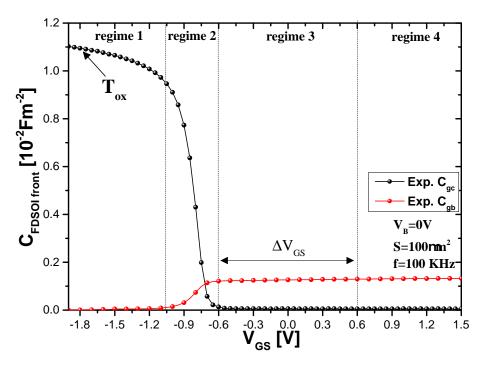

| FDSOI 1-D in plane cross section for specific simulation result | 64                           |

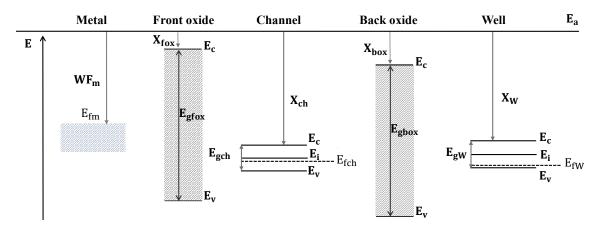

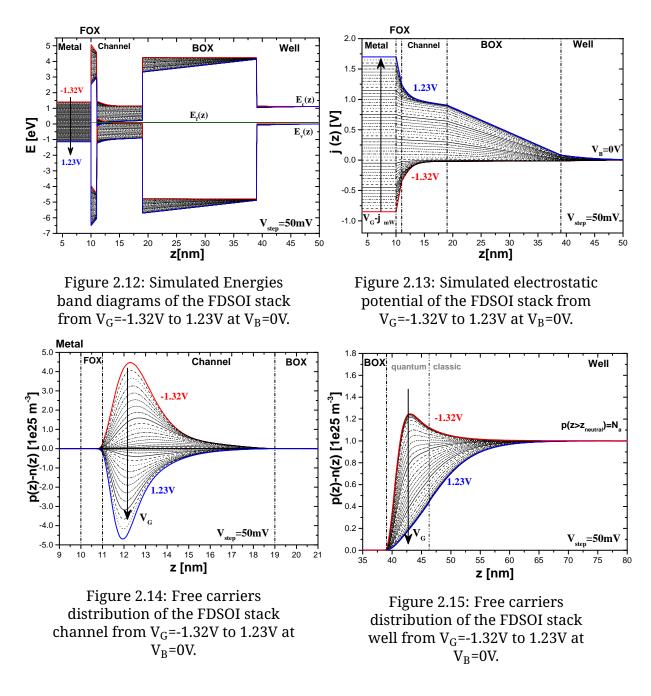

| FDSOI bands diagram at $V_B=0V$                                 | 66                           |

|                                                                 | 66                           |

| FDSOI channel charge at $V_B$ =0V                               | 66                           |

|                                                                 |                              |

| FDSOI well charge at $V_B=0V$                                   | 66<br>67                     |

|                                                                 | MOS capacitance band diagram |

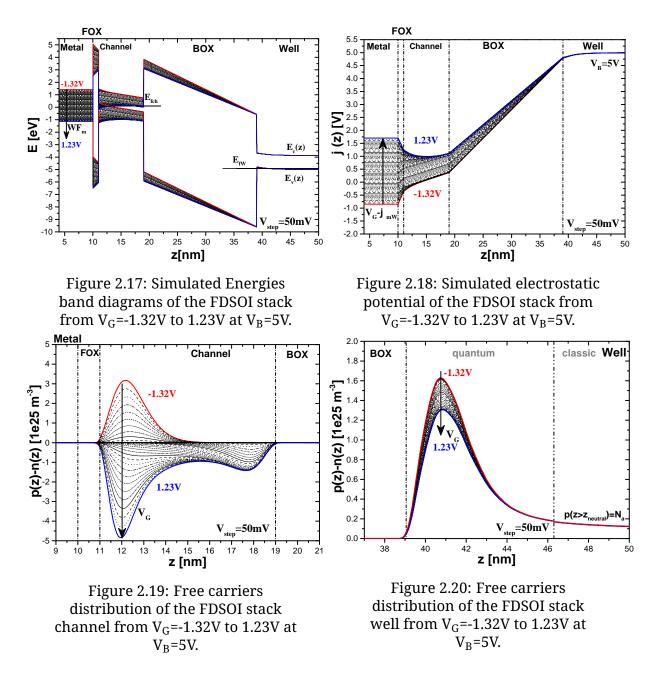

| 2.18<br>2.19<br>2.20                                                | FDSOI bands diagram at $V_B=5V$ FDSOI potential at $V_B=5V$ FDSOI channel charge at $V_B=5V$ FDSOI well charge at $V_B=5V$ FDSOI well charge at $V_B=5V$ Front FDSOI capacitances at $V_B=5V$                                                                                                                                                                                                                                       | 68<br>68<br>68                                     |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

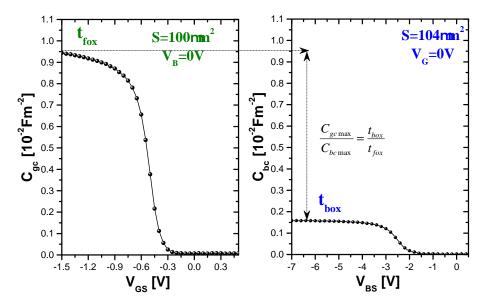

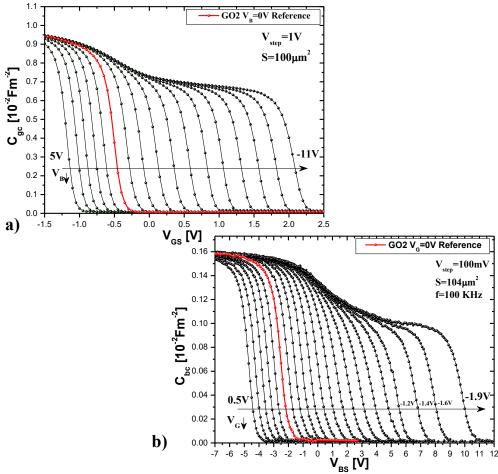

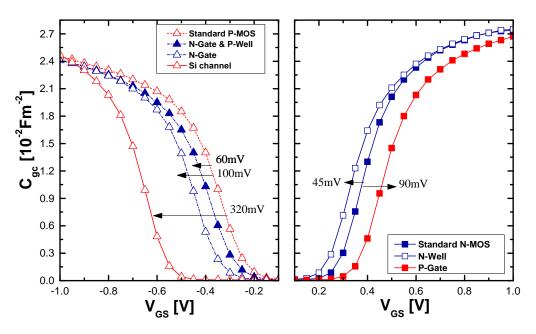

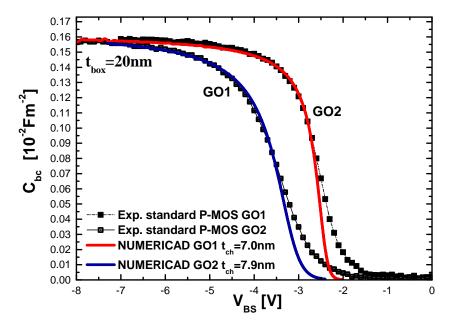

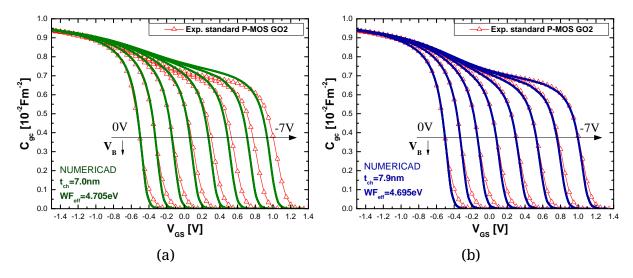

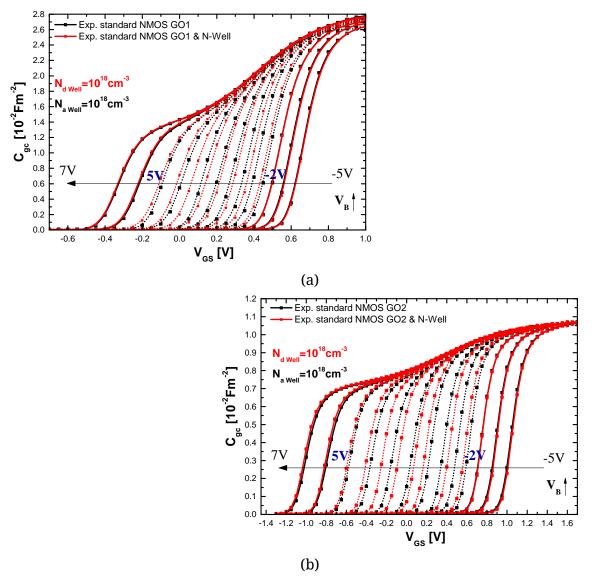

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Standard P-MOS and N-MOS FDSOI devices.Sacrificial metal Gate process.Experimental configuration for $C_{gc}$ .Experimental configuration for $C_{bc}$ . $C_{gc}(V_{GS})$ and $C_{bc}(V_{BS})$ . $C_{gc}(V_{GS})$ and $C_{bc}(V_{BS})$ . $C_{gc}$ for GO1 FDSOI devices at $V_B=0V$ . $C_{gc}$ for GO2 FDSOI devices at $V_B=0V$ . $WF_{eff}$ and EOT Extraction issues.Standard PMOS GO1 and GO2 back-Gate-to-channel capacitance. | 80<br>83<br>83<br>84<br>84<br>86<br>86<br>86<br>89 |

|                                                                     | C <sub>gc</sub> modulation for N-MOS GO2 compared to NUMERICAD with two<br>different channel thickness                                                                                                                                                                                                                                                                                                                              | 91                                                 |

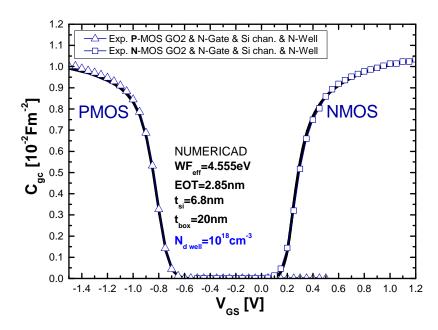

| 3.13                                                                | NMOS devices $\dots$                                                                                                                                                                                                                                                                                                                                        |                                                    |

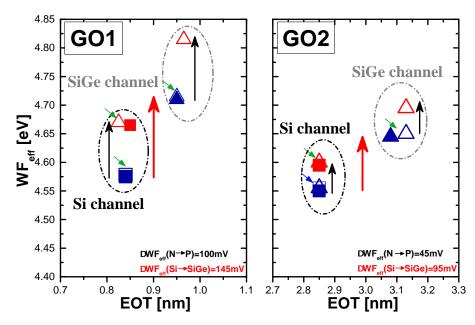

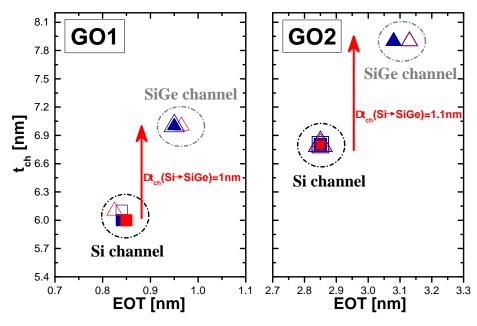

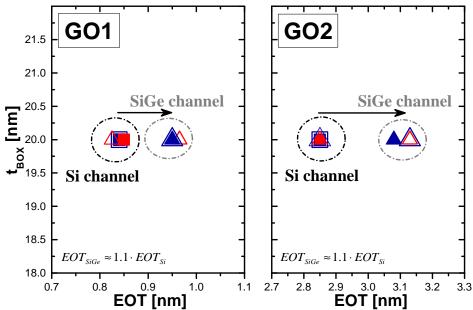

| 3.16<br>3.17                                                        | Cgc characteristics for the same FDSOI stack but with two different         Source-Drain types (n and P)         WF <sub>eff</sub> versus EOT         Vt <sub>ch</sub> versus EOT         t <sub>ch</sub> versus EOT         t <sub>box</sub> versus EOT                                                                                                                                                                            | 96<br>97<br>98                                     |

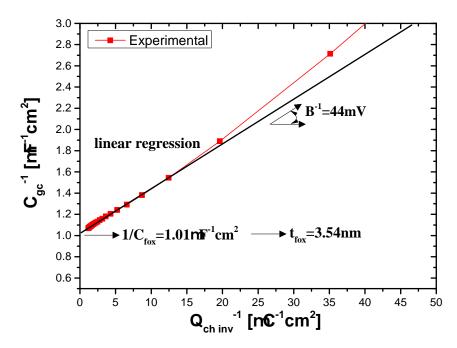

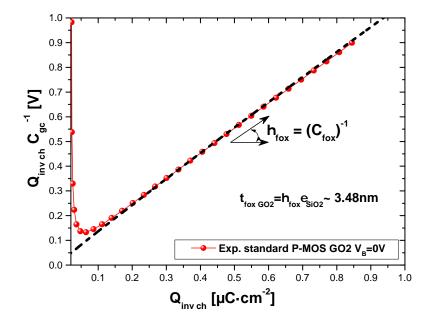

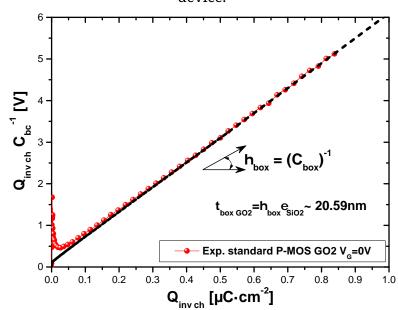

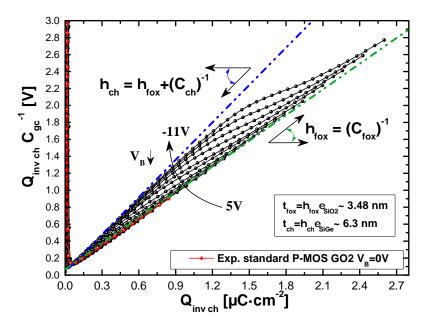

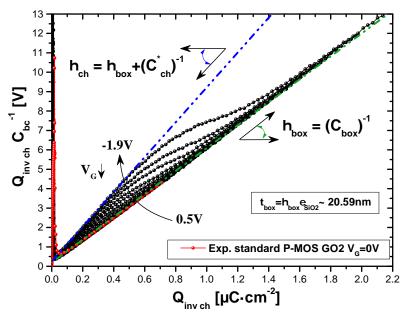

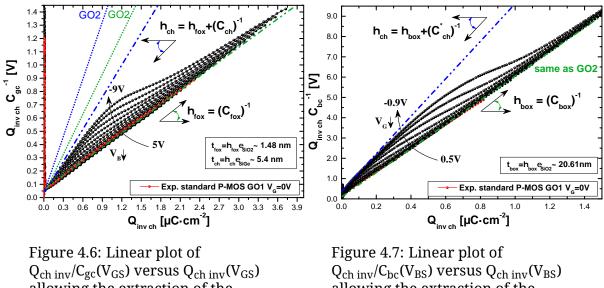

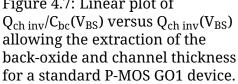

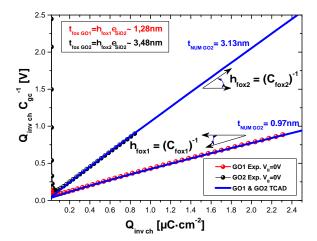

|                                                                     | Linear plot of $1/C_{gc}(V_{GS})$ versus $1/Q_{ch inv}(V_{GS})$<br>Linear plot of $Q_{ch inv}/C_{gc}(V_{GS})$ versus $Q_{ch inv}(V_{GS})$<br>Linear plot of $Q_{ch inv}/C_{bc}(V_{BS})$ versus $Q_{ch inv}(V_{BS})$<br>Linear plot of $Q_{ch inv}/C_{gc}(V_{GS})$ versus $Q_{ch inv}(V_{GS})$ from $V_B=5V$ to $V_B=-11^{\circ}$<br>Linear plot of $Q_{ch inv}/C_{bc}(V_{BS})$ versus $Q_{ch inv}(V_{BS})$ from $V_{GS}=0.5V$ to    | 107<br>107                                         |

| 4.7                                                                 | $ \begin{array}{l} V_G = -1.9V \\ \text{Linear plot of } Q_{ch  inv}/C_{gc}(V_{GS}) \text{ versus } Q_{ch  inv}(V_{GS}) \text{ for a GO1 device } \\ \text{Linear plot of } Q_{ch  inv}/C_{bc}(V_{BS}) \text{ versus } Q_{ch  inv}(V_{BS}) \text{ for a GO1 device } \\ \text{Comparison between NUMERICAD fit and experimental} \end{array} $                                                                                      | 110<br>110                                         |

|                                                                     | methodology for GO1 and GO2 devices                                                                                                                                                                                                                                                                                                                                                                                                 | 112<br>n113                                        |

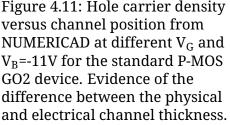

|                                                                     | Numerical simulation of the dark space as a function of the inversion channel charge                                                                                                                                                                                                                                                                                                                                                |                                                    |

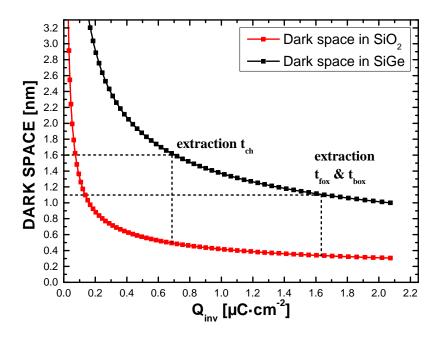

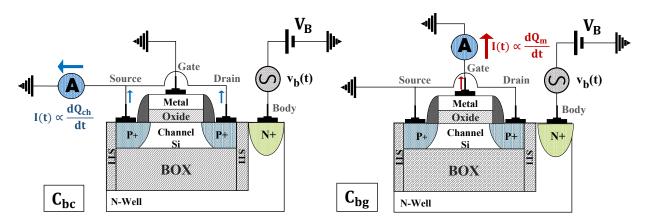

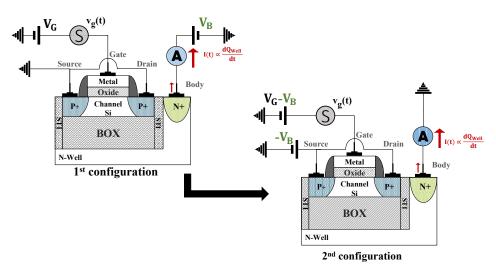

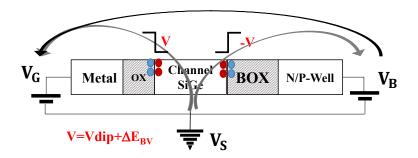

| 5.1                                                                 | Scheme of $C_{gc}$ and $C_{gb}$ configurations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                   | 122                                                |

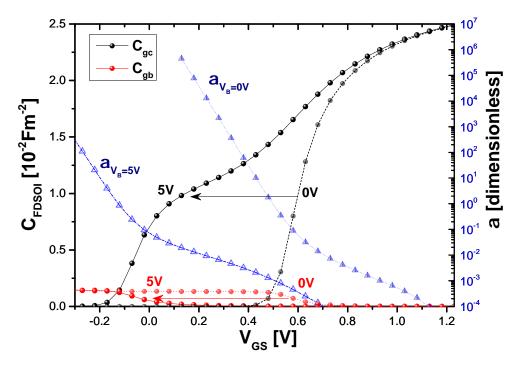

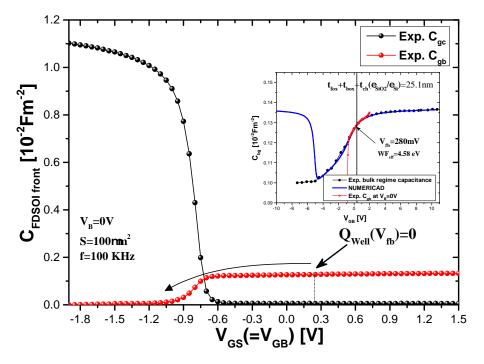

| 5.2   | $C_{gc}$ and $C_{gc}$ versus $V_{GS}$                                                                                                   | 122 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3   | Scheme of $C_{bc}$ and $C_{bg}$ configurations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                | 123 |

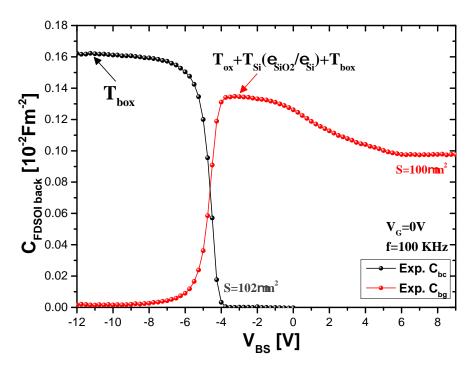

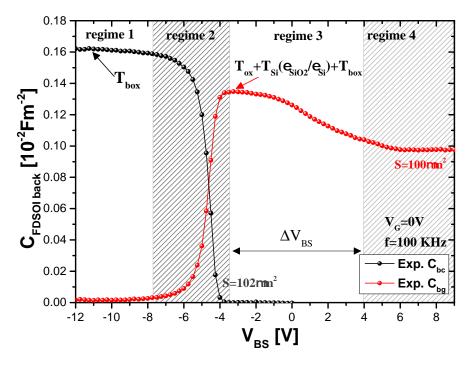

| 5.4   | $C_{bc}$ and $C_{bg}$ versus $V_{BS}$                                                                                                   |     |

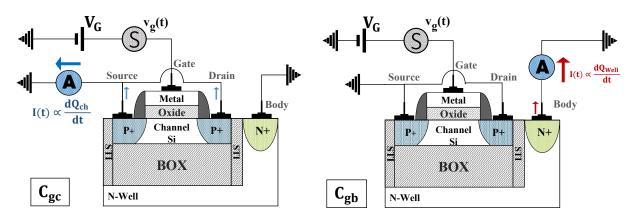

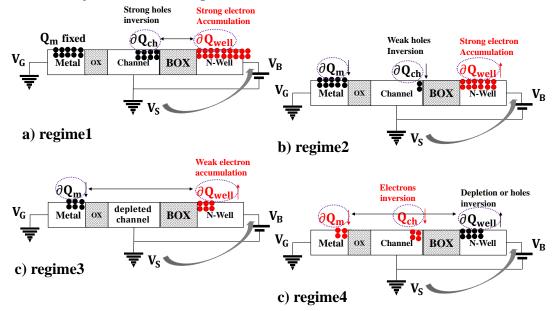

| 5.5   |                                                                                                                                         | 126 |

| 5.6   | FDSOI Electrostatic condition at different operation regimes.                                                                           |     |

| 5.7   |                                                                                                                                         |     |

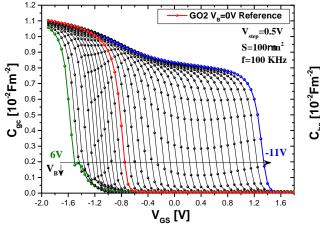

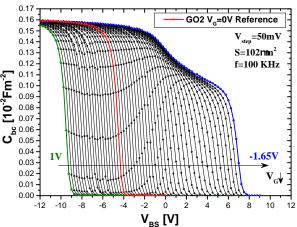

| 5.8   | $C_{gc}$ for different $V_B$ for a P-MOS GO2 Si channel device                                                                          |     |

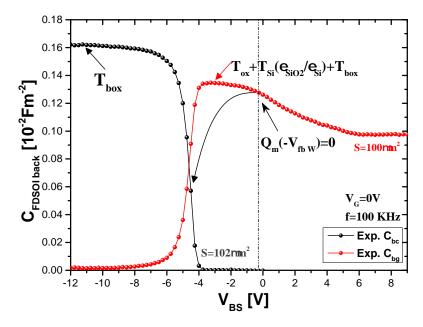

| 5.9   | $C_{bc}^{s}$ for different $V_{G}$ for a P-MOS GO2 Si channel device                                                                    | 132 |

|       | Alternative configuration for $C_{gb}$ measurement with back biasing .                                                                  |     |

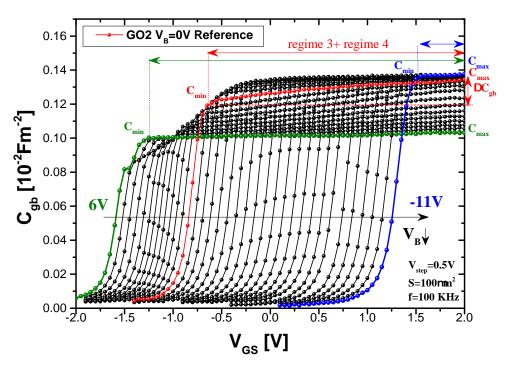

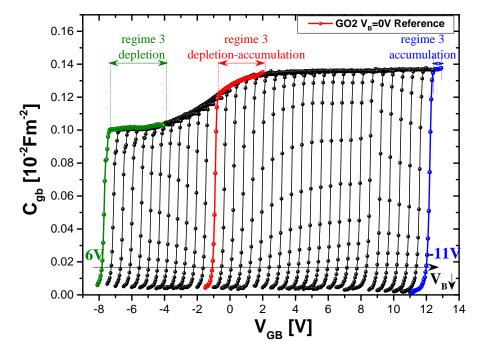

|       | $C_{gb}$ versus $V_{GS}$ with back biasing                                                                                              | 133 |

| 5.12  | Alternative configuration for $C_{bg}$ measurement with front biasing .                                                                 |     |

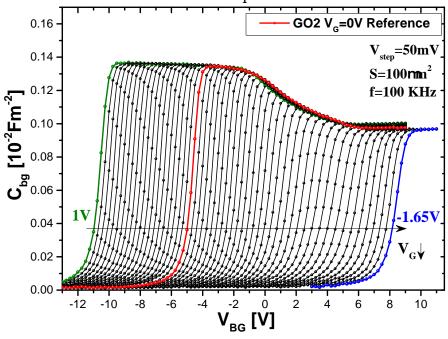

|       | $C_{bg}$ versus $V_{BS}$ with front biasing                                                                                             |     |

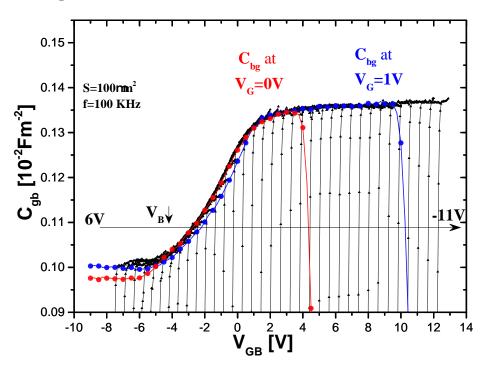

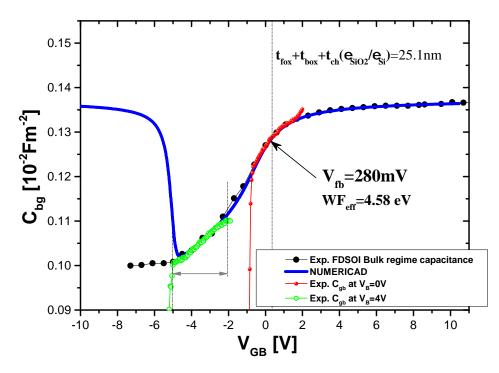

|       | $C_{gb}$ (a) and $C_{bg}$ (b) measurement during FDSOI bulk regime                                                                      | 137 |

|       | $C_{gb}$ versus $V_{GB}$ with back biasing                                                                                              |     |

|       | $C_{bg}$ versus $V_{BG}$ with front biasing                                                                                             |     |

|       | $C_{gb}$ and $C_{bg}$ versus $V_{GB}$ measurement during the $3_{rd}$ regime.                                                           |     |

|       | Extraction of $V_{fb}$ from $C_{bg}$ characteristic                                                                                     |     |

|       | Identification of the flat band on front FDSOI capacitances                                                                             | 143 |

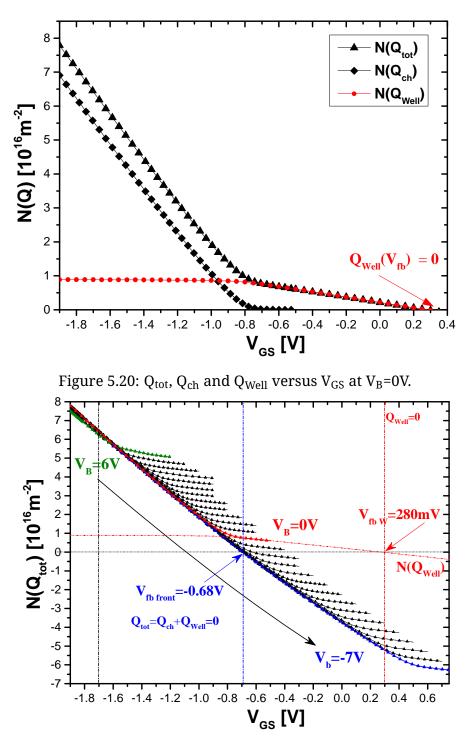

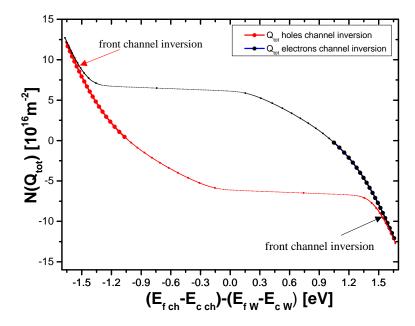

|       | $Q_{tot}$ , $Q_{ch}$ and $Q_{Well}$ versus $V_{GS}$ at $V_B=0V$                                                                         |     |

|       | $Q_{tot}$ versus $V_{GS}$ at $V_B$ from 6V to -7V                                                                                       |     |

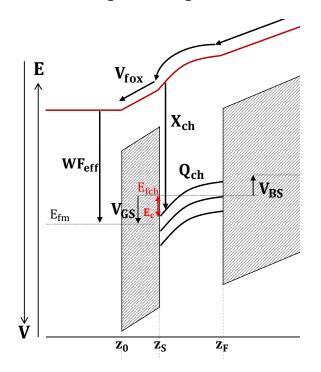

|       | FDSOI band diagrams at the front oxide                                                                                                  | 147 |

| 5 23  | -                                                                                                                                       | 148 |

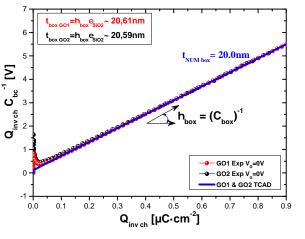

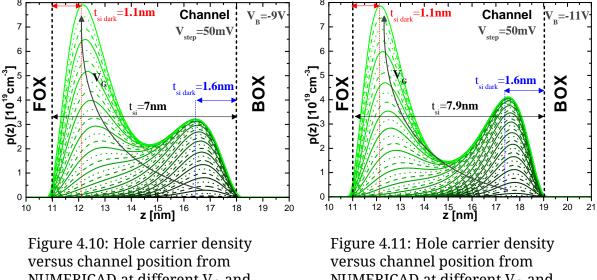

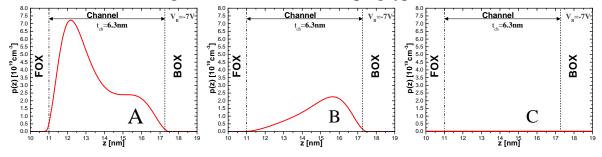

|       | Distribution of the channel charge at 3 different conditions                                                                            | 110 |

| 5.21  | indicated in Fig. 5.23: (A) front channel inversion, (B) back channel                                                                   |     |

|       | inversion and (C) fully depleted channel.                                                                                               | 148 |

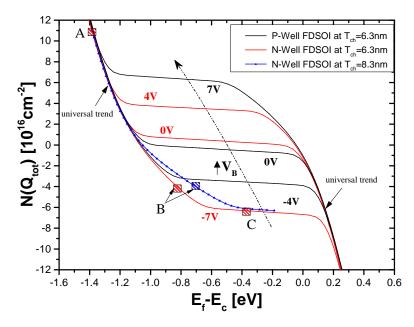

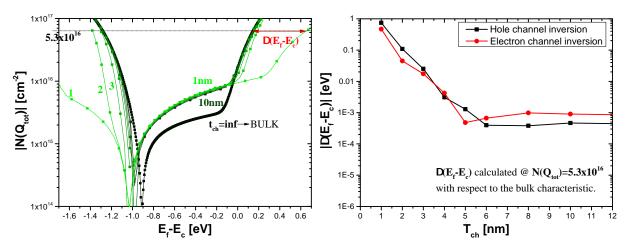

| 5 25  | EMA numerical simulation of $N(Q_{tot})$ as a function of $(E_f-E_c)$ for                                                               | 140 |

| 5.25  | FDSOI devices featuring different channel thicknesses (from 10nm $\frac{1}{2}$                                                          |     |

|       | to 1nm) and for bulk device featuring a 700nm substrate with                                                                            |     |

|       | $10^{16}$ cm <sup>-3</sup> doping level.                                                                                                | 150 |

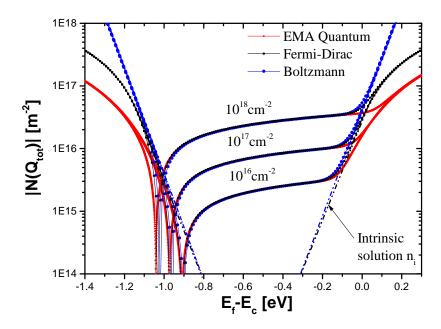

| 5 26  | $N(Q_{tot})(E_f-E_c)$ for different bulk transistors featuring different                                                                | 150 |

| 0.20  | doping levels                                                                                                                           | 151 |

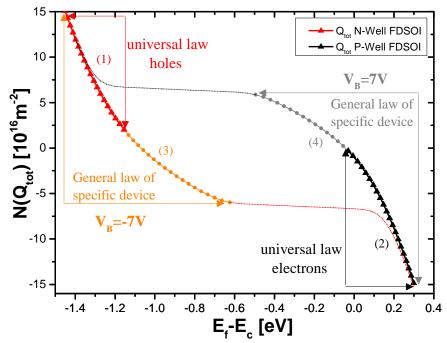

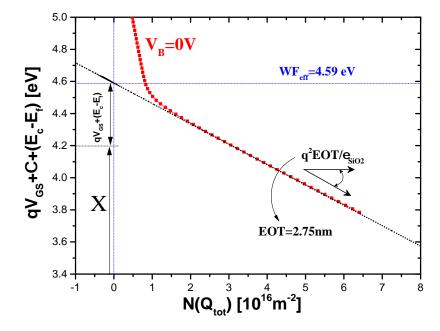

| 5 27  | $N(Q_{tot})(E_f-E_c)$ considered for the extraction of MIS structure                                                                    |     |

|       | $WF_{eff}$ and EOT extraction for a P-MOS GO2 device featuring a                                                                        | 101 |

| 0.20  | Si-channel and N-type well at $V_B=0V$ .                                                                                                | 155 |

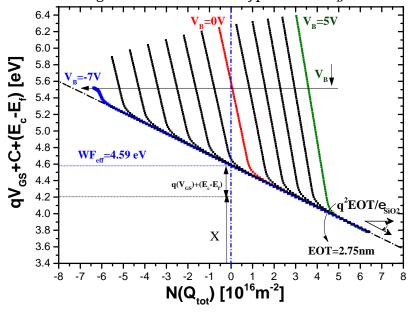

| 5 2 9 | $WF_{eff}$ and EOT extraction for a P-MOS GO2 device featuring a                                                                        | 100 |

| 0.20  | Si-channel and N-type well from $V_B=5V$ to $-7V$                                                                                       | 155 |

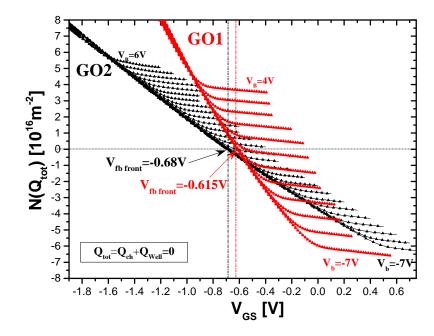

| 5 30  | $N(Q_{tot})$ versus $V_{GS}$ : comparison between GO1 and GO2                                                                           |     |

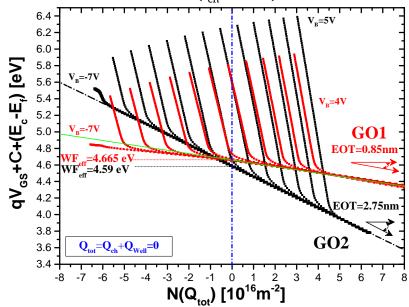

|       | Extraction WF <sub>eff</sub> and EOT for GO1 and GO2 devices                                                                            |     |

|       | FDSOI band diagrams at the back oxide                                                                                                   |     |

|       | $N(Q_{tot})(E_f-E_c)$ considered for the extraction of SIS structure                                                                    |     |

|       | Identification of flat band on $C_{bc}$ and $C_{bg}$ versus $V_{BS}$ characteristics                                                    | 101 |

| J.JT  | at $V_G=0V$                                                                                                                             | 162 |

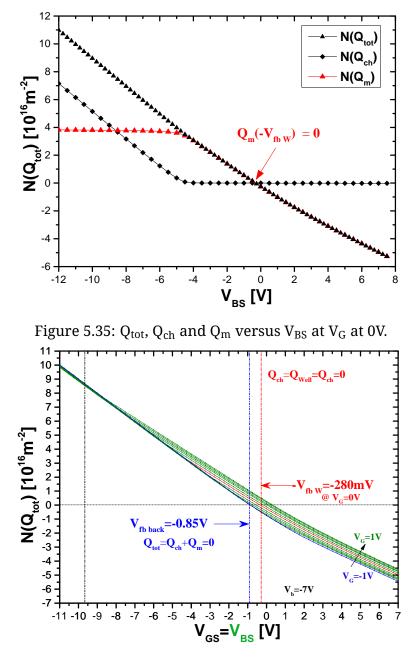

| 5 25  | $Q_{tot}$ , $Q_{ch}$ and $Q_m$ versus $V_{BS}$ at $V_G$ at $0V$                                                                         |     |

|       | $Q_{tot}$ versus $V_{BS}$ at $V_G$ from 1V to -1V with step of 0.2V                                                                     |     |

|       | $X_{eff}$ and $t_{box}$ extraction for a P-MOS GO2 device featuring a                                                                   | 103 |

| 5.57  | Si-channel and N-type well from $V_G=1V$ to $-1V$                                                                                       | 164 |

|       | or charmer and in the open more $v_G - 1v$ to $-1v + \cdots + $ | 104 |

| 5.38 $C_{gc}$ versus $V_{GS}$ at $V_B$ =0V for GO1 (Si and SiGe) and GO2 (Si) 10                | 65 |

|-------------------------------------------------------------------------------------------------|----|

| 5.39 $C_{bc}$ versus $V_{BS}$ at $V_G$ =0V for GO1 (Si and SiGe) and GO2 (Si) 10                | 65 |

| 5.40 $N(Q_{tot}(E_f-E_c))$ characteristics for Si and SiGe material 10                          | 66 |

| 5.41 $\mathrm{WF}_{\mathrm{eff}}$ and EOT extraction for two GO1 devices featuring a Si channel |    |

| and SiGe channel                                                                                | 67 |

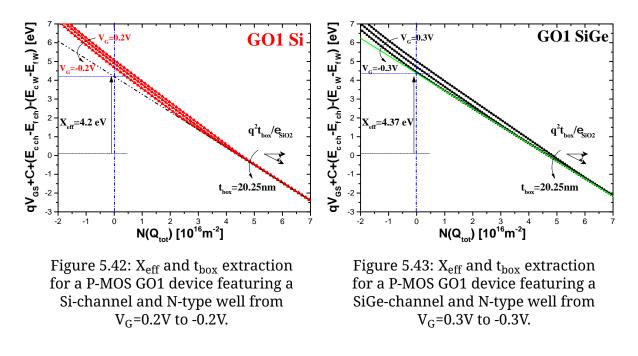

| 5.42 $X_{eff}$ and $t_{box}$ extraction for a P-MOS GO1 device featuring a                      |    |

| Si-channel and N-type well from $V_G$ =0.2V to -0.2V                                            | 68 |

| 5.43 $X_{eff}$ and $t_{box}$ extraction for a P-MOS GO1 device featuring a                      |    |

| SiGe-channel and N-type well from $V_G$ =0.2V to -0.2V                                          | 68 |

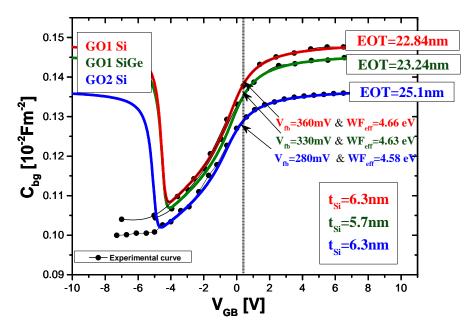

| 5.44 $C_{bg}$ as a function of $V_{GB}$ simulated and experimental characteristics              |    |

| for two GO1 devices featuring a Si and SiGe channel and one GO2                                 |    |

|                                                                                                 | ~~ |

## **List of Tables**

| 2.1 | Silicon masses for calculation of free density charge $n(z)$ . A value of electron longitudinal and transverse mass of 0.916m <sub>0</sub> and 0.190m <sub>0</sub>                                                                                                            |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 0.0 | are used [20]                                                                                                                                                                                                                                                                 | 59  |

| 2.2 | Silicon masses for calculation of free density charge $p(z)$ . A detailed description of the hole masses can be found in the book                                                                                                                                             |     |

|     | of Bhattacharya [20]                                                                                                                                                                                                                                                          | 59  |

| 2.3 | Classical 3-D silicon masses for calculation of free density charges                                                                                                                                                                                                          |     |

|     | $\Gamma(1)$                                                                                                                                                                                                                                                                   | 61  |

| 2.4 | Si <sub>1-<math>\chi</math></sub> -Ge <sub><math>\chi</math></sub> masses for calculation of free density charge $p(x)$ with $\chi$ =0.25                                                                                                                                     | 62  |

| 2.5 | SiO <sub>2</sub> masses for calculation of free density charge $p(z)$ and $n(z)$                                                                                                                                                                                              | 65  |

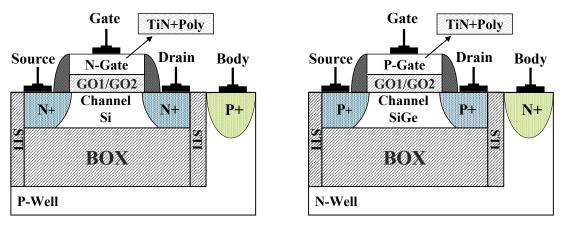

| 3.1 | Set of different FDSOI devices featured by a combination of different process modules on metal gate, channel (Si and SiGe) and well (P and N doped) for GO1 and GO2 dielectrics.                                                                                              | 80  |

| 3.2 | Set of different FDSOI devices featured by a combination of different process modules on metal gate, channel (Si and SiGe) and well (P and N doped) for GO1 and GO2 dielectrics. We also report on the $V_{\rm th}$ shifts that are observed for the different architectures. |     |

| 5.1 | Extraction result using the three previous methodologies                                                                                                                                                                                                                      | 170 |

## **General context**

The invention of the first transistor in 1947 allows John Bardeen, William Shockley and Walter Brattain to obtain the Nobel prize in Physics. This important event leads to a tremendous change in every aspects of life. Indeed after the first developments in 1954, the first general public application based on transistors appears with the radio. The field-effect transistor (MOSFET: Metal Oxide Semiconductor Field Effect Transistor) fabricated for the first time by Atalla and Kahng in 1960, became the key element for the semiconductor industry since 70's to nowadays becoming omnipresent (portable computer, mobile phone, cars, satellite  $\cdots$ ).

The operating principle of this device remains unchanged but its dimensions reduce continuously as predicted by Moore law. This phenomena well-known as "Downscale" from a generation to another (technological node) aims to gain in terms of electrical performance which substantially means to increasingly obtain faster transistors and therefore integrated circuit and high level electronic systems. The other main target of the downscale is to reduce the cost production of the transistor. Therefore, the semiconductor industry engages totally in downscale process with the objective of downscaling the density of transistors each two years as described by the ITRS (international Roadmap for Semiconductor). In this way between the economical considerations and the technological progress, the microelectronic evolution allows to obtain electronic devices (mobile phone, portable computer  $\cdots$ ) more and more fast and complex.

Nevertheless, since 2000's, the reduction of the dimensions is no longer sufficient in order to improve the electrical performance of the transistors which defines the end of the "straight Downscale Era". Indeed at nanometric scale, complex quantum phenomena are occurring, which deviates the standard operation principle of the transistor. Therefore in order to preserve the standard transistor operation, it is necessary to minimize these quantum parasitic effects. Straight downscale has to be accompanied with alternatives technological solutions which are:

- New device based on exotic architecture design: FDSOI (Fully depleted silicon on insulator transistor), Nanowires and Tri-Gate

- New channel material (III-V group) with higher charge mobility substituting the Silicon material.

- Mechanical stress induced during fabrication process which enhances the channel mobility.

- Gate stack process engineering which plays a fundamental role in defining the technological parameters (threshold voltage  $V_t$ , leakage current  $I_{off}$  and operation current  $I_{on}$ ).

Whereas the first solution overcome the limits of the conventional planar architecture on substrate (Bulk technology) from 32nm node technology authorizing downscale to lower technology node (12nm), the others three solutions are simply enhancing the electrical performance without decreasing the dimensions of the transistor. These solutions are widely used in the last decades and their effects on technological parameters of the transistors are more and more complicate to understand.

In this context, new electrical characterization methodologies are necessary to analyze the impact of these new technological solutions, in order to identify optimum solutions to improve the transistors electrical performance and diminish its cost production. This is called "Technology Optimization". Specifically, this work treats in detail the fully depleted FDSOI transistor on which new Gate stack process and different channel material (such as SiGe) including channel mechanical stress are carried out during the process fabrication.

Two parameters are representative of all the electrical performance aspects of a specific technology: the effective work function (WF<sub>eff</sub>) and the Equivalent Oxide Thickness (EOT). The aim of this work is to find new electrical characterization methodologies in order to analytically, rapidly and accurately extract EOT and WF<sub>eff</sub> in case of thin film FDSOI transistors and to pursue the Technology Optimization.

The first chapter generally introduces the operation principles of a standard transistor MOSFET on bulk substrate. Specifically a detailed description of the traditional MOSFET operation during Capacitance-Voltage measurement, the typical extraction methodologies of EOT and  $WF_{eff}$  based on this C-V measurements and the flat band voltage  $V_{fb}$  identification are presented. Moreover a rigorous definition of EOT and  $WF_{eff}$  is given. The incompatibility

of this standard C-V measurement technique with innovative FDSOI transistors and a necessary need of new electrical characterization methodologies in order to extract EOT and  $WF_{eff}$  are evidenced.

The incompatibility of the classical C-V extraction methodologies is due to the missing flat band condition in the FDSOI Capacitance-Voltage characteristics. The necessity of a physical comprehension of the electrostatic behavior of the FDSOI during C-V measurement comes out naturally. The first half of the second chapter is devoted to electrostatic analysis of FDSOI transistor which means to find the fundamental relationships, in terms of Voltage and Capacitance, accounting of the complexity of the electrostatic FDSOI behavior during C-V measurements. The second half fo the chapter is dedicated to the numerical simulation that can reproduce Capacitance-Voltage characteristics for a specific FDSOI transistor. Such simulations are fundamental to understand the electrostatic behavior of the FDSOI device under specific biases conditions (C-V measurement).

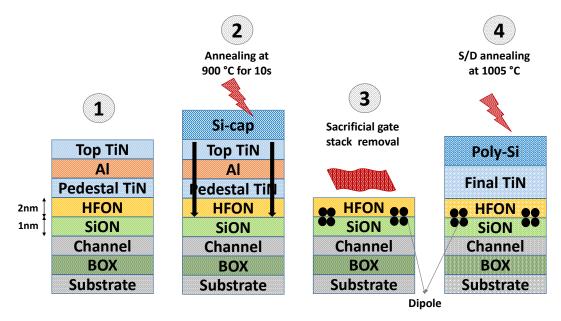

The third chapter presents an extraction methodology to extract EOT and  $WF_{eff}$  which is based on specific strategy (or procedure). This numerical extraction methodology identifies all the FDSOI stack layers thicknesses (Gate oxide, channel and buried oxide). This is carried out for each layer by fitting specific C-V measurements with the numerical simulations that are introduced in the second chapter. The FDSOI stack thicknesses are required in order to obtain the proper value of  $WF_{eff}$  for a specific FDSOI transistor Gate stack. Despite its extraction precision, the numerical methodology appears costly and complex highlighting the need of a faster and simpler analytical methodology.

Therefore in the fourth chapter, we will present an analytical extraction methodology which is faster than the numerical methodology (chapter 3). It is based on the linear regression which leads to the direct estimation of the FDSOI stack layers (Gate oxide, channel and buried oxide) thicknesses. Unfortunately, we will show that this methodology is incomplete since the fundamental identification of  $WF_{eff}$  cannot be carried out. Moreover, the extraction methodology requires a correction (quantum) on the estimated FDSOI stack layers thicknesses due to the quantum effects occurring in the channel and well layers.

Considering the cost of complexity of the numerical extraction presented in chapter 3 and the limit of the analytical method of chapter 4, the necessity of an alternative analytical methodology is evidenced. In the chapter 5, a complete extraction methodology is proposed which leads not only to estimate EOT and  $WF_{eff}$  but as well all the FDSOI stack layers thicknesses, the bulk substrate properties and the total electrostatic condition (channel, well and metal charges) of the the FDSOI transistor during C-V measurement. This extraction methodology is based on new capacitance measurements and an innovative extraction algorithm which allows to compare different technologies (e.g. Si and SiGe channel material). Moreover, this extraction is fast and precise since quantum effects are properly considered.

## **Chapter 1**

# Introduction to C-V measurements and operation of MOS

## **1.1 Introduction**

Metrology, defined by international Bureau of Weights and Measures, as the science of measurements, embraces both theoretical and practical aspects of the measurement. The science of measurements plays a fundamental role in the technology optimization. Indeed electrical measurements and analysis, which are a fundamental part of device engineering, are carried out continuously in order to improve and design optimized transistors in the microelectronic industry. It is in this context that Capacitance-Voltage measurements have been and are one of the most widely used technique to electrically characterize MOSFET transistor and consequently extract the relevant parameters related to specific technologies (materials electrical properties) used in the transistor. These capacitance voltage measurement are carried out on the traditional MOS transistor whose acronym stands for Metal oxide semiconductor field effect transistor. Whereas the Capacitance-Voltage techniques, for traditional MOS transistors, are well known and mastered in the state of the art, new electrical methodologies are required for recent upcoming technologies such as the FDSOI MOSFET transistors, whose acronym, in this case, stands for fully depleted silicon on Insulator MOSFET transistor. Therefore in order to understand the problematics related to the new technologies, and especially the incompatibility of the standard C-V measurement technique with innovative FDSOI transistors, a detailed description of the traditional MOSFET operation during C-V measurement, the typical extraction methodologies based on this C-V measurement and a comparison with FDSOI architecture will be presented.

Moreover, we will present the fundamental technological parameters and their impact over the device electrical performances.

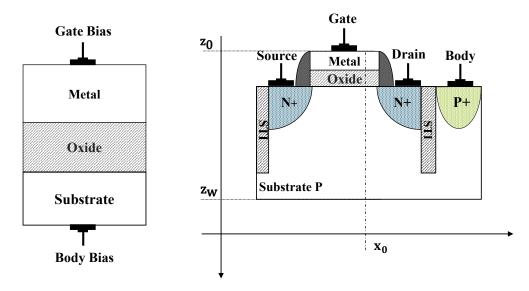

Figure 1.1: Schematic of a MOS capacitance.

## 1.2 MOS transistor and operation regime during C-V measurement

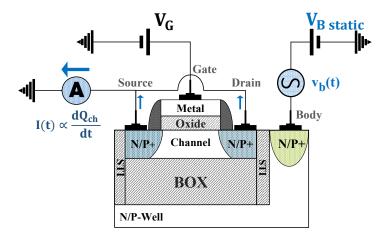

As shown in the right side of Fig. 1.1, the MOSFET is four terminal device: Gate (G), Source (S), Drain (D), and Body (B). The Gate stack is composed of a specific bilayer structure consisting of a metal on the top of an oxide whereas Source and Drain are simply ohmic contacts. The Source and Drain contacts feature highly doped semiconductor wells (10<sup>20</sup>cm<sup>-3</sup>), specifically P or N-type for P or N-MOS device. The Body contact, always ohmic, features as well a highly doped semiconductor well (10<sup>20</sup> cm<sup>-3</sup>) which doping type depends on the MOS type: N-type well for P-MOS and P-type well for N-MOS devices. Finally the substrate (or channel semiconductor) is doped, with the same doping type of the Body well, but at lower level (between 10<sup>16</sup> cm<sup>-3</sup> and 10<sup>18</sup> cm<sup>-3</sup>). In general terms, this MOS transistor is a component which plays the role of an electrical switcher by passing or blocking the channel current between Source and Drain terminals. The basic principle of this technology is based on what is called the field effect, which will electrostatically modulate the density of free charge in the channel by applying a specific Gate Voltage (V<sub>G</sub>). The conductivity of silicon channel, like any other semiconductor, will depend on the quantity of free carriers in the

conduction band (electrons) or the valence band (holes). The voltage applied to the Gate will modulate these quantities, at the semiconductor surface close to the dielectric, thus obtaining a MOS capacitance. The channel features a doping type, as previously said, opposite to the Source and the Drain wells. if no Gate voltage is applied, its resistivity is high and therefore the resistance between Source and Drain is large. This is called 'off-state'. By applying a proper Gate voltage, the channel is enriched by the minority carriers, coming from the Source and Drain wells. The resistivity of the channel decreases sharply and the transistor is said 'on-state'. Thus, in an n-channel transistor (N-MOS), the Source and Drain are source of electrons and the transistor will be on-state if the channel is enriched by minority carriers (electrons). The voltage V<sub>G</sub> applied at the Gate will enable us to create the inversion charge in the channel and a different applied voltage at the Source and Drain terminals ( $V_{DS} = V_D - V_S = V_D$ ) will displace these charges, under the effect of a electrical field induced by V<sub>DS</sub>, from Source to Drain terminal. The analysis of the band diagrams of the MOS capacitor of Fig. 1.1 (left side) will allow us to better understand the transistor regime operation depending on the applied V<sub>G</sub> voltage.

#### 1.2.1 Band diagram of the MOS capacitor

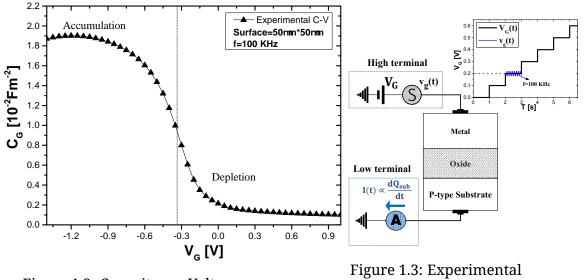

The heart of the MOS transistor is the MOS capacitor (Fig. 1.1), presented and indicated as "varactor" capacitance by Moll [1] and by Pfann and Garrett [2] in 1959. The term varactor was used at that time to indicate that the capacitance between a metal and a semiconductor varies with voltage. It was clear that the semiconductor, different from the metal, had a key role in the deformation of the expected measured capacitance between the metal and the semiconductor. Indeed Pfann, Garrett and Moll got to the conclusion that this variation was due to the behavior of the space-charge layer near the surface of oxide-semiconductor, and therefore the semiconductor electrical behavior or more properly the semiconductor operation regime (the electrostatic condition and the state of its charge). In Fig. 1.2 we report an example of Capacitance-Voltage characteristics of a simple MOS stack with a P-type substrate. The C-V curves of this stack is obtained with a Capacitance-meter, named 4284A, that allows to measure complex impedance thanks to the superimposition of a alternate small voltage signal and a main continuous voltage (High terminal) while induced current is measured on the other grounded terminal (Low terminal). The two terminals are connected to the

electrical contacts of MOS stack test structure, respectively the High terminal to the Gate and Low terminal to the Body, as reported in Fig. 1.3. The measurement has been carried out by varying the Gate voltage from 1V to -1.4V. For each step voltage (50mV), the small signal voltage induced current is read at the low terminal by the Capacitance Meter and the relative capacitance is calculated. These are reported with black triangle symbol in Fig. 1.2.

Figure 1.2: Capacitance-Voltage measurements of a MOS capacitor.

configuration for C-V measurement.

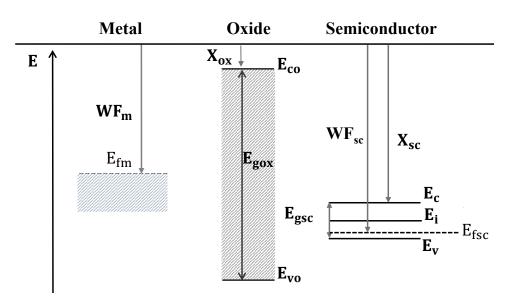

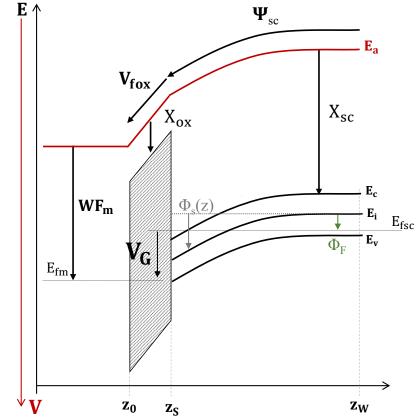

In order to understand the Capacitance variation, we propose hereafter a study of the MOS system through its band diagrams representation, by taking care of the semiconductor layer electrostatic behaviour. Each material of this capacitor is characterized by electrical macroscopic parameters that affect the behaviour of the channel charge induced by V<sub>G</sub> voltage. In figure 1.4, we report the band diagrams as well as the relative technological parameters. WF<sub>m</sub>, the metal work function, corresponds to the energy that has to be supplied (T = 0K) to extract an electron from the metal to the vacuum whereas X<sub>ox</sub> and X<sub>sc</sub> are the electrical affinity of the oxide and semiconductor which represent the energies required to extract an electron from their relative conduction bands. WF<sub>sc</sub> is the necessary energy to extract an electron from the semiconductor: this energy is lower compared to the oxide electrical affinity. By bringing these three materials into contact and applying a Gate voltage, a thermodynamic equilibrium is established among them. We remember that the Gate voltage is the applied voltage at the Gate terminal and corresponds to the difference between the metal and semiconductor Fermi energies. If  $V_G=0V$  these Fermi energies are aligned. For any V<sub>G</sub> bias a potential profile is induced along the z position, perpendicular to

Figure 1.4: Band diagrams of the layers composing the MOS capacitor: Metal-Oxide-Semiconductor.

Figure 1.5: Band diagrams of the MOS capacitor at thermodynamic equilibrium.

oxide semiconductor interface. The type of charge induced at the interface will define the operation regime of the MOS capacitor during C-V measurement.

#### **1.2.2 Operation Regime**

Before introducing the operation regimes, we need to clarify a few things. As reported in Fig. 1.5, the semiconductor band bending represents the variation of potential energy of electrons, in terms of electron Volts (eV). This potential  $\phi_s(z)$  varies from 0, in the neutral region of the semiconductor ( $z_W$ ) to  $V=\phi_s$  at the interface oxide-semiconductor ( $z_s$ ).  $\phi_s$  is known as the potential surface. The operation regimes depend of the applied  $V_G$  voltage. Whereas a detail description of these regimes can be found in Shockley's book [3], here we propose a brief picture of these regimes, that are:

- 1. Accumulation Regime: The channel is enriched of majority carriers. For an N-MOS with a P-type substrate, the amount of holes (p) is therefore higher than the level of the holes induced intrinsically by the semiconductor, that is equal to the number of active acceptors (N<sub>a</sub>). This occurs when  $\phi_s$ <0. The transistor is therefore off-state. In case of P-MOS with a N-type substrate, the amount of electrons (n) has to be bigger than N<sub>d</sub>, where N<sub>d</sub> is the donor concentration. This condition occurs when  $\phi_s$ >0.

- 2. Depletion Regime: The surface of the semiconductor is depleted of the majority carriers. The amount of holes at the oxide-semiconductor interface is lower than the acceptor concentration. Nevertheless, the holes concentration, in the valence band, is still superior to the electrons concentration (n) in the conduction band which means  $0 < \phi_s < \phi_F$  where  $\phi_F$  is the Fermi potential related to the Fermi holes concentration in the neutral region from the doping concentration N<sub>a</sub> (N<sub>d</sub> in case of P-MOS transistor). Therefore we have  $n whereas for a P-MOS we have <math>p < n < N_d$  (- $\phi_F < \phi_s < 0$ ). The depletion region is the result of the displacement of the majority carriers across the semiconductor that are escaping through the semiconductor-electrode ohmic contact (Body contact).

- 3. Inversion Regime: In this operation regime, we have an inversion of free carriers ( $\phi_s > 0$ ). This condition occurs in case of transistors (1.1 right side) and as well simple MOS capacitors. Indeed the creation of inversion charge is related to two specific processes: the inversion supplied by the Source and Drain wells or the carrier generation phenomena [4] that occurs at a specific generation rate. Specifically we have a thermal generation type which is always present whenever the temperature of the semiconductor material is greater than zero kelvin. Once the inversion is generated, independently

by the Source and by Source-Drain diffusion or thermal generation, two sub-regimes are identified during the inversion operation regime:

- (a) weak inversion: This condition occurs while the inversion layer at oxide-semiconductor interface is equal or bigger with respect to the doping concentration of the semiconductor (N<sub>a</sub>). Therefore we have, in case of N-MOS transistor, that  $\phi_s > 0$  and  $\phi_F < \phi_s < 2\phi_F$  while for P-MOS transistor the condition is  $-2\phi_F < \phi_s < -\phi_F$ .

- (b) strong inversion: When  $\phi_s$  is larger than  $2\phi_F$  the minority carriers concentration is larger compared to the majority ones, that means n»p for a N-MOS.  $\phi_s$ => $2\phi_F$  represents the condition that defines the limit between weak and strong inversion. In case of P-MOS transistor we have  $\phi_s$ <=- $2\phi_F$ .

In case of MOS capacitor (Fig. 1.2), inversion characteristic is missing. This is related to the fact that for these measurements there is no Source and Drain diffusion which doping-type is opposite with respect to the substrate and would provide a sufficient amount of minority carriers, able to respond to the potential variations applied to the Gate terminal. The capacitive measurement is then only related to the response of the majority carriers. This is the capacitance measurement between the Gate and substrate (Body) terminals, commonly denoted as C<sub>gb</sub>. In general the C-V characteristic associated to majority carriers is the easiest measurement result to obtain since only two terminals are necessary (Gate and substrate), which allows us to consider simplified test structures. There's no need of specific Source and Drain implantation since the  $V_{\mbox{\scriptsize fb}}$  and EOT can be extracted in the depletion-accumulation region and specifically the EOT at strong accumulation and the  $V_{\rm fb}$  at the beginning (onset) of the accumulation [5, 6]. The missing  $C_{gc}$  characteristic is used in Bulk substrate for the study of the carrier mobility because it gives us access to the carrier concentration in the transistor during channel inversion, as demonstrated by F.Lime et al. [1].

The only phenomena leading to the semiconductor inversion, in this case, is the thermal generation. The inversion carriers are created at a specific rate which is  $f_{gr}$ . As previously said, during C-V measurement, two signals are applied at Gate contact: a constant voltage  $V_G$  ( $f_G$ =0) and a small signal voltage  $v_g(t)$ characterized by a specific frequency  $f_g$ . The inversion charge, created by the thermal generation phenomena, can always respond to the constant voltage  $V_G$ since  $f_{gr}>f_G=0$ , but is not capable to respond to the variations of small signal voltage  $v_g(t)$  if  $f_{gr}<f_g$ . Since the C-V measurement of Fig. 1.2 (MOS capacitor) is carried out at  $f_g$ =100Kz> $f_{gr}$ , only depletion and accumulation regimes are observed on the C-V characteristic.

#### 1.2.3 Total charge and C-V characteristics of a MOS capacitor

As previously seen, depending of the applied Voltage V<sub>G</sub>, the semiconductor is characterized by a specific operation regime during C-V measurement. At this condition, we have a specific distribution of semiconductor charge ( $\rho(z) = p(z) - n(z) + N_d - N_a$ ) from which we can easily calculate the total charge by its simple integration, which leads to:

$$Q_{sc} = -Q_g = \int_{z_S}^{z_W} \rho(z) \,\mathrm{d}z \tag{1.1}$$

In Figure 1.6 we report the dependence of a simulated total charge as a function

Figure 1.6: Variation of the total number of carriers of the semiconductor versus the semiconductor potential drop for a constant doping ( $N_a$ ) concentration level equal to  $10^{18}$  cm<sup>-3</sup>.

of the semiconductor potential drop for P-type semiconductor, for a doping concentration  $N_a=10^{18}$  cm<sup>-3</sup>. As we previously said, the total charge varies with the Gate voltage at different operation regimes. Therefore the C-V characteristic will depend on electrostatic condition of the semiconductor (the charge and the potential drop). Indeed, during C-V measurement, for each specific  $V_G$  we have a different distribution of semiconductor charge whose relationship

with the relative surface potential  $\Psi_{sc}$  affects the expected dielectric capacitance between the two electrodes (metal and semiconductor). We remember that, at the opposite, in a metal electrode, independently of the metal charge, no potential drop occurs which leads to a very large metal capacitance  $C_m = dQ_m / d\Psi_m$  that can be neglected. Therefore the MOS stack capacitor is a system of two capacitances in series: the oxide capacitance and the semiconductor capacitance which is dependent of the Gate Voltage.

If we know the relation between the semiconductor charge  $Q_{sc}$  (Coulomb) and its potential drop  $\Psi_{sc}$  (Volts) we can calculate the associate semiconductor capacitance  $C_{sc}$ =-d $Q_{sc}$  /d $\Psi_{sc}$ , leading then to obtain the total capacitance  $C_g$  from a given specific charge  $Q_{sc}$ :

$$\frac{1}{C_g} = \frac{1}{C_{ox}} + \frac{1}{C_{sc}}$$

(1.2)

where  $C_{ox} = \epsilon_{SiO_2}/t_{ox}$  is the expected capacitance of the oxide between the two electrodes. This total capacitance is normalized by the device area and is measured in Farad/m<sup>2</sup>. When we increase the voltage V<sub>G</sub> for a semiconductor of type P (respect. N), as reported in Fig. 1.2, the substrate evolves from the accumulation of holes (respect. inversion of holes) to the depletion and then to inversion of electrons (respect. accumulation of electrons). As previously explained, inversion cannot be measured in the case a MOS capacitor. From accumulation to depletion, there's a specific voltage condition for which the substrate charge is zero. This means Q<sub>sc</sub>=0 that is well known as flat band condition (V<sub>fb</sub>) at the interface oxide-semiconductor. Once we have identified this voltage condition on the characteristic C-V of Fig. 1.2, we can calculate the semiconductor charge at any V<sub>G</sub> voltage by integrating the total experimental capacitance from the flat band voltage V<sub>fb</sub>:

$$Q_{sc} = -Q_m = -\int_{V_{fb}}^{V_G} C_g \,\mathrm{d}V$$

(1.3)

The applied voltage  $V_G$ , during C-V measurement, is equivalent to the sum of the drop voltages across the dielectric oxide  $V_{ox}$ , the semiconductor  $\Psi_{sc}$  and the difference of Fermi levels between the metal and the semiconductors. From the analysis of Fig. 1.5, we can calculate

$$V_G = \frac{WF_m}{q} - \frac{WF_{sc}}{q} + \Psi_{sc} + V_{ox}$$

(1.4)

This equation takes into account the relation between the charge at the electrodes

and the oxide voltage drop  $V_{ox}$ =- $Q_{sc}/C_{ox}$ . WF<sub>m</sub> and WF<sub>sc</sub> are technological parameters associated to the electrodes materials, their work function. WF<sub>sc</sub> can be estimated from given doping level N<sub>sc</sub> and temperature (T=300 K) by simply solving the following equation

$$WF_{sc} = X_{sc} + E_{gap}/2 + LK_BT \ln \frac{N_{sc}}{n_i}$$

(1.5)

where  $n_i$  is the intrinsic doping level of silicon material ( $n_i$ =10<sup>10</sup>cm<sup>-3</sup> at 300 K) and K<sub>B</sub> is the Boltzmann constant with L equal to 1 for a substrate of type P and -1 for a substrate of type N. This leads us finally to obtain:

$$V_G(Q_{sc}) = \frac{WF_m}{q} - \frac{WF_{sc}}{q} + \Psi_{sc}(Q_{sc}) - \frac{Q_{sc}}{C_{ox}}$$

(1.6)

Using equations 1.2, 1.5, 1.6 and knowing the relation  $\Psi_{sc}(Q_{sc})$  (as reported in Fig. 1.6), we can predict the experimental behavior of a Capacitance-Voltage characteristic of a specific Gate stack (Metal-Oxide-Semiconductor). This Capacitance-Voltage is unique for each specific MOS capacitor (WF<sub>m</sub>, C<sub>ox</sub> and N<sub>sc</sub>). In Figures 1.7 and 1.8, we report the simulated total charge and capacitance as function of the applied voltage V<sub>G</sub>. For this simulation, an oxide thickness (t<sub>ox</sub>) was 1 nm, the metal work function WF<sub>m</sub> 4.76eV and the semiconductor doping level equals N<sub>a</sub>=10<sup>18</sup> cm<sup>-3</sup>. C-V characteristic of MOS capacitor is

Figure 1.7: Total capacitance as function of the Gate voltage for a  $10^{18}$  cm<sup>-3</sup> constant doping (N<sub>a</sub>) concentration level.

a fundamental source of information. Indeed, its dependence is related to

Figure 1.8: Variation of the total number of carriers of the semiconductor versus the Gate voltage for a  $10^{18}$  cm<sup>-3</sup> constant doping (N<sub>a</sub>) concentration level.

the dielectric oxide and the semiconductor electrostatic behavior (macroscopic electrical properties). In the state of the Art, the Capacitance-Voltage (C-V) measurement is used to determine the semiconductor and the dielectric technological parameters, particularly in MOSCAP and MOSFET structures. C-V measurements can reveal oxide thickness, oxide charges, contamination from mobile ions, and interface trap density in wafer processes. These measurements continue to be important after each process steps that has been performed, including lithography, etching, cleaning, dielectric and polysilicon depositions, and metallization processes. C-V characteristics are often used to characterize the flat band and threshold voltage ( $V_{th}$ ) and other parameters during reliability and basic device testing and to model device performance. It is in this context that we will introduce in the next section three important technological parameters that defines the performance of a MOS transistor.

## **1.3** V<sub>fb</sub>, EOT and WF<sub>eff</sub> definition

Based on the work of Troutman [7], the V<sub>fb</sub> is defined as the Gate voltage for which the total semiconductor charge level is zero, as reported in Figures 1.7 and 1.8. By assuming constant doping concentration and classical formalism (Boltzmann), not only the semiconductor charge is zero but as well the semiconductor potential drop  $\Psi_{sc}$ =0. Unfortunately this condition rarely occurs in the real devices where substrates are characterized by a non-constant doping concentration and therefore  $\Psi_{sc} \neq 0$ . From the relation 1.6, we can define the flat band voltage V<sub>fb</sub> as

$$V_G(Q_{sc} = 0) = V_{fb} = \frac{WF_m}{q} - \frac{WF_{sc}}{q} + \Psi_{sc}(V_{fb})$$

(1.7)

This voltage, expressed in Volts (V), allows the WF<sub>m</sub> extraction of the Gate stack expressed in electron-Volts (eV). The flat band voltage takes into account the reference potential of the semiconductor (WF<sub>sc</sub>). This depends only on the semiconductor and it is calculated in eV. Thus, assuming a certain doping level value, the relation between the metal work function and the flat band voltage is direct since no drop voltage occurs at this condition ( $\frac{Q_{sc}}{C_{ox}} = 0$  and  $\Psi_{sc}$ =0) leading to the extraction of the metal work function. This calculation is for an ideal MOS capacitor, that means zero charge inside the oxide including its interface (metal-oxide and oxide-semiconductor). Unfortunately such condition

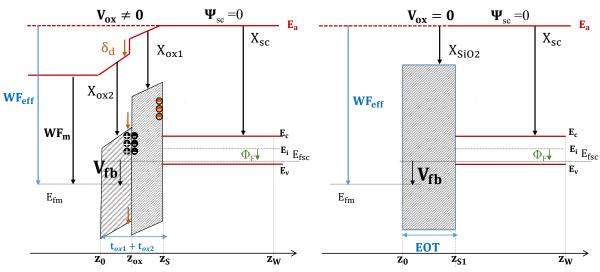

Figure 1.9: Energy band diagrams of a MOS structure at the flat band condition without any oxide charge (left figure) and with charges and dipole in the oxide (right figure).

doesn't occur in the real devices. From the first and simple MOS stack capacitors [1, 2] in the 50-60s, the progressive scaling-down and the necessity of higher electrical performance devices, pushed them to turn the standard MOS Capacitor into a more complex multilayer stack with multiple process steps that induce undesired (or desired) defects across the stack. Indeed the presence of fixed charges and dipole at specific interface location induce a drop voltage across the oxide even when the substrate charge is still zero. In Figure 1.9, in the left side, we show the band diagrams of the ideal MOS capacitor with two different oxides in series at flat band condition and, in the right side, the band diagrams of a non-ideal MOS capacitor characterized by the same dielectric stack, metal and semiconductor but with the presence of fixed charge at the interface between the first oxide and semiconductor and a dipole located at the interface between the two oxides, always at flat band condition. We notice that the presence of these oxide impurities changes the flat band condition with respect to the ideal MOS capacitor. The relation between the flat band and the metal work function has to take into account the voltage drop induced by the oxide charges and dipole. Therefore relation 1.7 becomes:

$$V_G(Q_{sc} = 0) = V_{fb} = \frac{WF_m}{q} - \frac{WF_{sc}}{q} - \frac{Q_{fi}}{C_{ox}} + \delta_d + \Psi_{sc}(V_{fb})$$

(1.8)

where  $\delta_d$  is the impulsed drop voltage located at the interface between the two dielectrics due to the dipole,  $Q_{\rm fi}$  is the the fixed charge,  $C_{\rm ox}$  is the equivalent capacitance of the Gate stack dielectric (series of the two oxide) and  $\Psi_{sc}(V_{fb})=0$  if classical formalism and constant doping are assumed. Moreover, the drop voltage induced by the fixed charges is  $\frac{Q_{fi}}{C_{ox}}$  since we assume that they are located at the interface oxide/semiconductor. Therefore, in terms of V<sub>fb</sub>, equation 1.6 can be written as

$$V_G(Q_{sc}) = V_{fb} + \Psi_{sc}(Q_{sc}) - \frac{Q_{sc}}{C_{ox}} - \Psi_{sc}(V_{fb})$$

(1.9)

The presence of these charges and dipole doesn't affect only the flat band voltage but also the threshold voltage  $V_{th}$  that is defined from equations 1.6 and 1.8 as

$$V_{th} = V_{fb} + 2\phi_f - \frac{\sqrt{2q\epsilon_{Si}N_a(2\phi_f)}}{C_{ox}} - \Psi_{sc}(V_{fb})$$

(1.10)

The impact of the relative fixed charges and dipole is the same for any applied voltage  $V_G$  (accumulation, depletion and inversion). Therefore, since the simulated Capacitance-Voltage characteristics of the ideal MOS capacitor of Fig. 1.9 (left side), is reported in Fig.1.7, the C-V characteristics of the real MOS (Fig. 1.9)

right side) will have the same trend of the ideal MOS C-V but shifted of a voltage  $\delta V_G = -\frac{Q_{fi}}{C_{ox}} + \delta_d$ . This means that we can tune and change the threshold voltage (and the flat band voltage) by inducing charges and dipole inside the oxide and therefore by playing with the fabrication process and not only by tuning the theoretical gate stack parameters (metal work function, oxide thickness and doping level of the semiconductor). The "tunable" shift on the C-V characteristic is interpreted by the process engineers as the result of a new C-V measurement on a different gate stack, with respect to the ideal MOS stack structure, which features a new metal characterized by an "effective work function" WF<sub>eff</sub>. The effective work function is the sum of the metal work function and the shift induced by fixed charges and dipoles expressed in eV ( $q\delta V_G = -\frac{qQ_{fi}}{C_{ox}} + q\delta_d$ ). Indeed from equation 1.8 we define the effective work function as:

$$WF_{eff} = WF_m - \frac{qQ_{fi}}{C_{ox}} + q\delta_d + q\Psi_{sc}(V_{fb}) = WF_m - \frac{qQ_{fi}t_{ox}}{\epsilon_{ox}} + q\delta_d + q\Psi_{sc}(V_{fb})$$

(1.11)

that, in terms of V<sub>fb</sub>, is

$$WF_{eff} = qV_{fb} + WF_{sc} - q\Psi_{sc}(V_{fb})$$

(1.12)

and therefore relation 1.6 becomes

$$V_G(Q_{sc}) = \frac{WF_{eff}}{q} - \frac{WF_{sc}}{q} + \Psi_{sc}(Q_{sc}) - \frac{Q_{sc}}{C_{ox}} - \Psi_{sc}(V_{fb})$$

(1.13)

The effective work function value (eq. 1.11) depends strongly on the technology process through which the process engineers induce fixed charges and dipoles across the dielectric ( $q\delta V_G = -\frac{qQ_{fi}}{C_{ox}} + q\delta_d$ ). Moreover, this value depends on the dielectric constant and thickness, which are as well affected by the process, since they define the drop voltage induced by the fixed charges ( $-\frac{qQ_{fi}}{C_{ox}} = -\frac{qQ_{fi}t_{ox}}{\epsilon_{ox}}$ ). Therefore two Gate stacks (metal-oxide-semiconductor) that differ from the dielectric constant and thickness value ( $\epsilon_{ox1}$ ,  $t_{ox1}$  and  $\epsilon_{ox2}$ ,  $t_{ox2}$ ) with the same amount of dipole and fixed charges at the oxide-semiconductor interface, will have two different effective work function values (WF<sub>eff 1</sub> and WF<sub>eff 2</sub>). Indeed the induced oxide voltage ( $\frac{qQ_{fi}}{C_{ox1}} \neq \frac{qQ_{fi}}{C_{ox2}}$ ), at the flat band condition, will be different for the two dielectrics supposing the same amount of fixed charge.

The choice of the dielectric type and thickness can be crucial for the electric performance of the MOS stack. Indeed, the reduction of the dielectric thickness (SiO2) in the subnanometric range produces dramatic gate leakage issues detrimental for the electrical performance. The process engineers try to replace

this standard dielectric oxide (SiO2) with the introduction of high-k materials (or high-dielectric permittivity material) which allows an increasing electrical performance without reducing the physical dielectric thickness. By convenience, the physical thickness has been replaced by an electrical thickness or Equivalent Oxide Thickness (EOT). This technological parameter is used in order to refer all the dielectric technologies to the reference SIO<sub>2</sub> dielectric technology. We can calculate the equivalent oxide thickness by simply using the following equation

$$EOT = \frac{t_{ox} \epsilon_{SiO_2}}{\epsilon_{ox}}$$

(1.14)

This relation requires the precise value of the Gate stack dielectric constant. Therefore in order to calculate the effective work function and the equivalent oxide thickness of a Gate stack, firstly we need to extract the amount of fixed charge and dipole inside the oxide and secondly the exact value of the dielectric constant. This extraction results tedious and almost impossible. The aim of the extraction is not to find the physical thickness of the dielectric and neither the effective metal work function values but to take into account properly of the electrical coupling between the two electrodes. It is for this reason that alternative approach have been proposed in order to extract WF<sub>eff</sub> and EOT and this will be presented in the next section.

# **1.4 Impact of EOT and WF<sub>eff</sub> on the MOS Electrical performance**

EOT and  $WF_{eff}$  extraction is fundamental due to their impact on the transistor electrical performance. In this paragraph we will define the most important transistor performance parameters, that are:

1. Threshold Voltage: As seen previously we define the threshold voltage as the Gate voltage for which the density of inversion charge becomes equal to the depletion charge. This condition leads to have  $\phi_s = 2\phi_f$ . In this case the inversion charge is the free carrier and the V<sub>th</sub> corresponds to the on-set state of the channel. This parameter is fundamental because it corresponds to the on-state behavior of the transistor. In the case of the N-MOS, for negative V<sub>G</sub>, the transistor will be off-state (accumulation regime). By progressively increasing the voltage, a depletion region forms until its maximum extension and the formation of the first inversion charge at the surface oxide-semiconductor. The threshold voltage is defined, in terms of EOT and WF<sub>eff</sub>, as

$$V_{th} = V_{fb}(\mathbf{WF_{eff}}) + 2\phi_f - \frac{\sqrt{2q\epsilon_{Si}N_a(2\phi_f)}\mathbf{EOT}}{\epsilon_{SiO_2}} - \Psi_{sc}(V_{fb})$$

(1.15)

2. Commutation time: This parameter defines the time necessary to pass from offset to onset state. It's a fundamental parameter that describes, in terms of speed, the efficiency of a single transistor in digital circuits. The intrinsic commutation time is defined by the relation

$$\tau = \frac{C_{ox} \cdot V_{DD}}{I_{on}} = \frac{\epsilon_{SiO_2} \cdot V_{DD}}{I_{on} \text{EOT}}$$

(1.16)

where  $V_{DD}$  is the supplied voltage applied at the Drain that defines the  $I_{on}$  current. The aim is to diminish this time as much as possible in order to reduce the commutation time. An optimization of the dielectric oxide is necessary (comparing different technologies with different EOT).

3. Sub-threshold slope: it is a typical parameter of the transistor during weak inversion regime.

$$S = \frac{\partial V_G}{\partial \log I_D} = \frac{KT}{q} \ln(10) \left( 1 - \frac{1}{C_{ox}} \frac{\partial Q_d}{\partial \phi_s} \right) = \frac{KT}{q} \ln(10) \left( 1 - \frac{\mathbf{EOT}}{\epsilon_{SiO_2}} \frac{\partial Q_d}{\partial \phi_s} \right)$$

(1.17)

with  $(1-dQ_d/\phi_s \times 1/C_{ox})=(1-C_d/C_{ox})$  where  $C_d=-dQ_d/\phi_s$ . It's given in Volts per decade and it corresponds to the variation of the potential barrier at the beginning of the channel (Source-channel) in function of the Gate voltage: It is a fundamental parameter for the optimization of the ratio between the saturation current and leakage current [8, 9]. The theoretical limit of this slope is fixed by the diffusion phenomena of the channel charge at ln(10)KT/q=60mV/Decade at 300K.

4. Gate leakage current: the shrink of the gate oxide thckness have been a critical feature of the overall scaling of transistor dimensions for six decades, enabling a continuous speed improvement even as operating voltage decrease. Further scaling down is not possible due to the leakage currents in such thin oxides that reach such a high value as comparable to ON state current causing very high static power dissipation. The Gate leakage current depends on the macroscopic electrical properties of the Gate dielectric whose relation given by Yee-Chia Yeo [10], for the classical direct tunneling regime, is

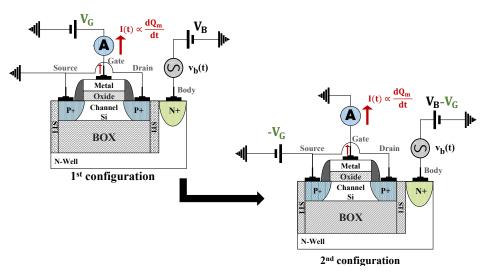

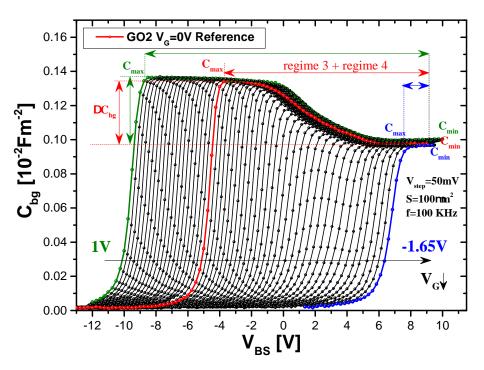

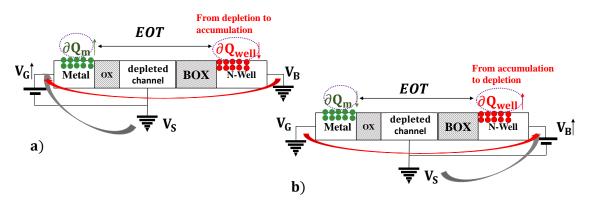

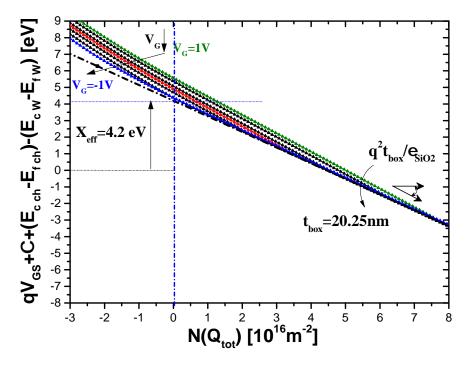

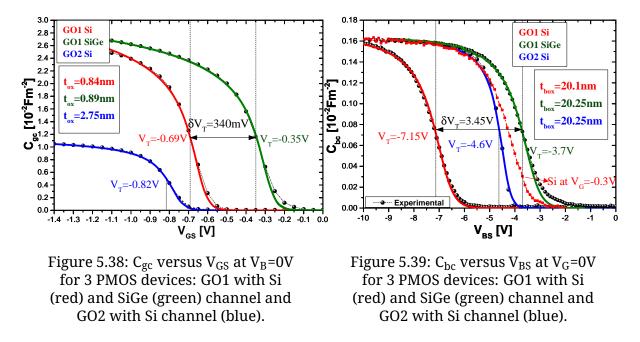

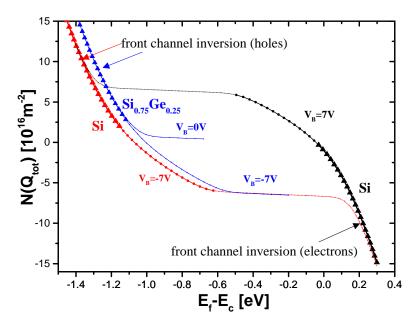

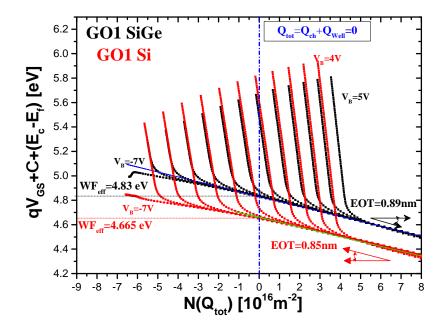

$$J_G = b \exp\left(-\alpha f \cdot EOT\right) \tag{1.18}$$