## Trapping and Reliability investigations in GaN-based HEMTs

Agostino Benvegnù

#### ► To cite this version:

Agostino Benvegnù. Trapping and Reliability investigations in GaN-based HEMTs. Electronics. Université de Limoges; Università degli studi (Padoue, Italie), 2016. English. NNT: 2016LIMO0064. tel-01643704

#### HAL Id: tel-01643704 https://theses.hal.science/tel-01643704v1

Submitted on 21 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

ECOLE DOCTORALE SCIENCES ET INGÉNIERIE POUR L'INFORMATION Discipline: Électronique des Hautes Fréquences, Photonique et Systèmes

Università degli Studi di Padova

SCUOLA DI DOTTORATO DI RICERCA IN: Ingegneria dell'Informazione INDIRIZZO: Scienza e Tecnologia dell'Informazione CICLO XXVIII

Submitted in fulfilment of the requirements for

the Degree of Doctor of Philosophy

## **Trapping and Reliability Investigations**

## in GaN-based HEMTs

by

#### Agostino Benvegnù

Advisors: Denis Barataud, Enrico Zanoni and Raymond Quéré

Dissertation committee:

Olivier Latry, Assistant professor (HDR) at University of Rouen, Referee Nathalie Malbert, Professor at University of Bordeaux 1, Referee Dominique Baillargeat, Professor at University of Limoges, XLIM, President Denis Barataud, Professor at University of Limoges, XLIM, Examiner Gaudenzio Meneghesso, Professor at University of Padova, Examiner Raymond Quéré, Professor at University of Limoges, XLIM, Examiner Jean-Luc Roux, Engineer at CNES Toulouse, Examiner Olivier Jardel, Engineer at Thalès Alenia Space Toulouse, Invite Jean-Luc Muraro, Engineer at Thalès Alenia Space Toulouse, Invite

September 28<sup>th</sup>, 2016

# Copyright

This work is licensed under the Contract:

"Attribution-NonCommercial-NoDerivs 3.0 Unported (CC BY-NC-ND 3.0)" Available online: <u>http://creativecommons.org/licenses/by-nc-nd/3.0/</u>

To my family & friends

« A winner is a dreamer who never gives up! »

Nelson Mandela

#### Acknowledgements

I'd like to begin by thanking my supervisors Professor Denis Barataud and Professor Raymond Quéré from the University of Limoges and Professor Enrico Zanoni from the University of Padova for their advice and continuing support throughout my Ph.D. thesis.

In addition, to the director of the XLIM, Professor Dominique Baillargeat, for welcoming me to the XLIM Research Institute and presiding over the dissertation committee. I'd like to thank the jury members, Professor Olivier Latry, Professor Nathalie Malbert, Professor Gaudenzio Meneghesso, Jean-Luc Roux, Dr. Jean-Luc Muraro, Dr. Olivier Jardel and Dr. Didier Floriot, for reviewing this dissertation.

Having worked on my Ph.D. at both the University of Limoges and Padova and Thales Alenia Space, I got the chance to meet a lot people who guided me, supported me and inspired me. I would like to express my sincere gratitude to them because the success of this work would not have been the same without them. I would like to thank all the Ph.D. students of Limoges, Arnaud, Julien, Pierre, Karthik, Clement, Lotfi, Nicolas, Paul, Johann and Yoann, for introducing me to the RF world and for being my family both in the laboratory and also during daily life. I am extremely grateful to my department secretary Marie Claude Lerouge for her patience and her kindness.

And many thanks to all my colleagues in Brive, Anthony, Frederique, Romain, Amed and Karim, for having hosted me and for the good times we spent together. Special thanks to Dr. Sylvain Laurant for supporting me and for the long days spent performing LSNA measurements.

A sincere thanks to the microelectronic group of University of Padova, Isabella, Carlo, Riccardo, Antonio, Stefano and Davide, for introducing me to the HEMT world and for always being ready to help me. Special thanks go to Professor Matteo Meneghini for his willingness and for the many discussions on the physics of electronic semiconductors.

I'd also like to thank Dr. Dominique Langlez for welcoming me to the LEMMIC group at Thales Alenia Space. I would like to thank Dr. Jean-Luc Muraro for his involvement and for always setting a good mood. I am also thankful to my roommates, Claudio, Thomas and Alexander, who made the first floor of 19th Boulevard Gambetta a very fun place and for the organization of many pizza parties in our living room.

And many thanks to my family, Mum, Dad and Simone, for giving me the opportunity to be here.

And last, but certainly not least, I'd like to thank Francesca for supporting this longdistance relationship and for always being there for me.

## **Table of contents**

| 1 | Bac                                                                                                            | kground                                                                                                                                                                                                                                                                                                                      | 1                          |

|---|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   | 1.1                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                 | 1                          |

|   | 1.2                                                                                                            | GaN based semiconductors                                                                                                                                                                                                                                                                                                     | 1                          |

|   | 1.2.1                                                                                                          | I Two-dimensional electron gas                                                                                                                                                                                                                                                                                               |                            |

|   | 1.3                                                                                                            | GaN technology for satellite equipment                                                                                                                                                                                                                                                                                       | 6                          |

|   | 1.4                                                                                                            | GH50-10 process                                                                                                                                                                                                                                                                                                              | 7                          |

|   | 1.5                                                                                                            | Conclusion                                                                                                                                                                                                                                                                                                                   |                            |

| 2 | Inv                                                                                                            | estigation of trapping phenomena                                                                                                                                                                                                                                                                                             |                            |

|   | 2.1                                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                 |                            |

|   | 2.2                                                                                                            | Basics of trapping phenomena                                                                                                                                                                                                                                                                                                 |                            |

|   | 2.3                                                                                                            | Trapping characterization methodology                                                                                                                                                                                                                                                                                        | 13                         |

|   | 2.3.1<br>2.3.2                                                                                                 |                                                                                                                                                                                                                                                                                                                              |                            |

|   | 2.3.2                                                                                                          | 1 15                                                                                                                                                                                                                                                                                                                         |                            |

|   | 2.3.4                                                                                                          |                                                                                                                                                                                                                                                                                                                              |                            |

|   |                                                                                                                |                                                                                                                                                                                                                                                                                                                              |                            |

|   | 2.4                                                                                                            | Identification of deep-levels                                                                                                                                                                                                                                                                                                | 61                         |

|   | 2.4<br>2.5                                                                                                     | Identification of deep-levels                                                                                                                                                                                                                                                                                                |                            |

| 3 | 2.5                                                                                                            | _                                                                                                                                                                                                                                                                                                                            | 64                         |

| 3 | 2.5                                                                                                            | Conclusions                                                                                                                                                                                                                                                                                                                  | 64<br>68                   |

| 3 | 2.5<br>Nor                                                                                                     | Conclusions                                                                                                                                                                                                                                                                                                                  | 64<br>68<br>68             |

| 3 | 2.5<br>Nor<br>3.1                                                                                              | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction                                                                                                                                                                                                                                               | 64<br>68<br>68<br>68       |

| 3 | 2.5<br>Nor<br>3.1<br>3.2                                                                                       | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction<br>Modeling methods for HEMTs                                                                                                                                                                                                                 | 64<br>68<br>68<br>68<br>70 |

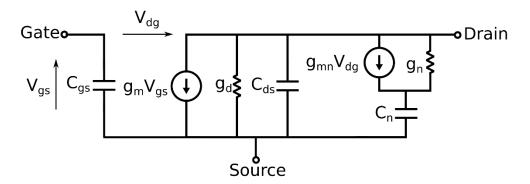

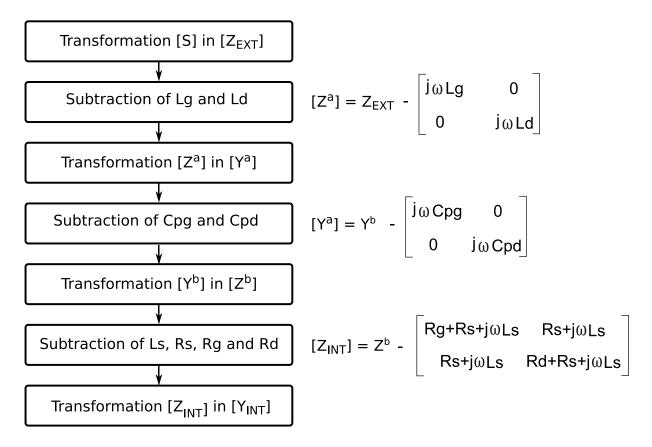

| 3 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1                                                                | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction<br>Modeling methods for HEMTs<br>Modeling methodology<br>Device modeling process<br>Small-signal model                                                                                                                                        |                            |

| 3 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2                                                       | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction<br>Modeling methods for HEMTs<br>Modeling methodology<br>Device modeling process<br>Small-signal model<br>Nonlinear model                                                                                                                     |                            |

| 3 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1                                                                | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction<br>Modeling methods for HEMTs<br>Modeling methodology<br>Device modeling process<br>Small-signal model<br>Nonlinear model<br>Nonlinear trapping and thermal current source model                                                              |                            |

| 3 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2                                              | Conclusions<br>nlinear Electro-Thermal model of AlGaN/GaN HEMT<br>Introduction<br>Modeling methods for HEMTs<br>Modeling methodology<br>Device modeling process<br>Small-signal model<br>Nonlinear model<br>Nonlinear trapping and thermal current source model                                                              |                            |

|   | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2 | Conclusions                                                                                                                                                                                                                                                                                                                  |                            |

| 4 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.5<br>Tin     | Conclusions                                                                                                                                                                                                                                                                                                                  |                            |

| 4 | 2.5<br>Nor<br>3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.5<br>Tin     | Conclusions<br>Introduction<br>Introduction<br>Modeling methods for HEMTs<br>Modeling methodology<br>Device modeling process<br>Small-signal model<br>Nonlinear model<br>Nonlinear trapping and thermal current source model<br>Model validation<br>Conclusion<br>me-domain large-signal reliability investigation of AlGaN/ |                            |

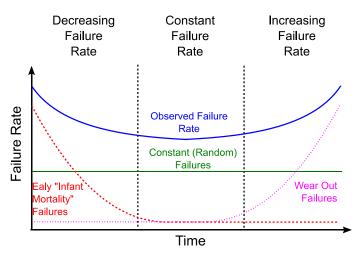

| 4.2.1    | Analysis of reliability                                | 102 |

|----------|--------------------------------------------------------|-----|

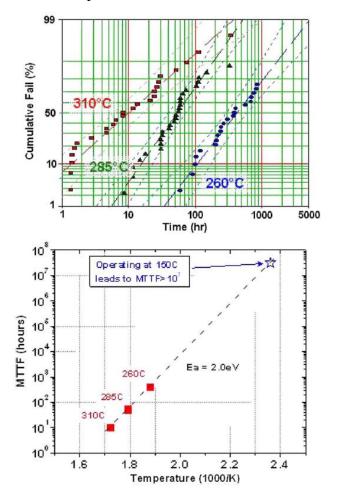

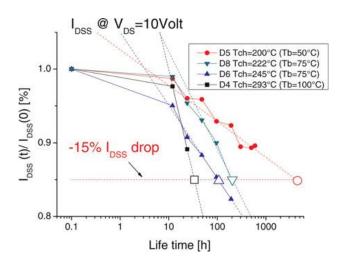

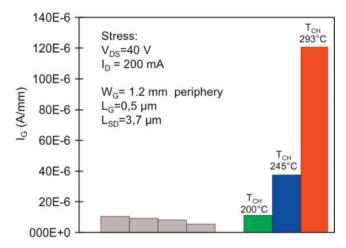

| 4.2.2    | Accelerated life test                                  |     |

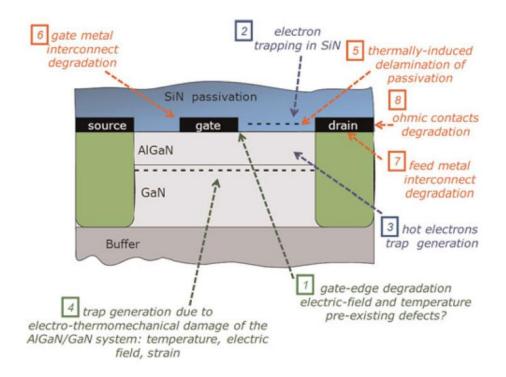

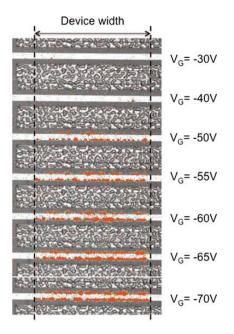

| 4.2.3    | Physical failure mechanisms                            | 106 |

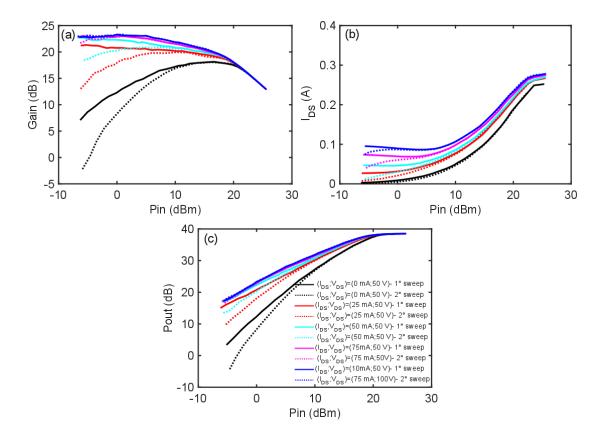

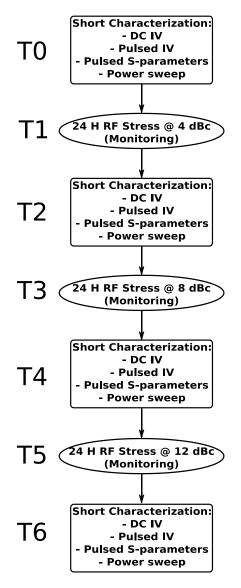

| 4.3 T    | ime-domain continuous RF waveform monitoring under str | ess |

| overdriv | e condition                                            | 110 |

| 4.3.1    | Time-domain continuous RF waveform stress set-up       | 111 |

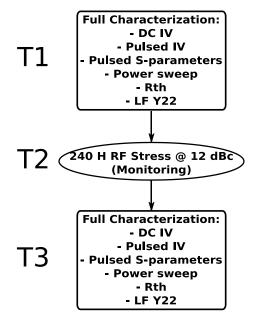

| 4.3.2    | Reliability test procedure                             |     |

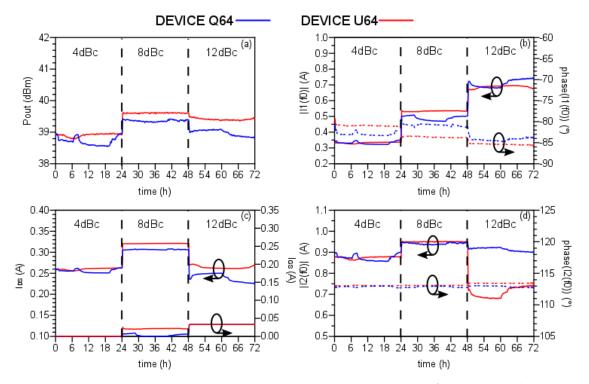

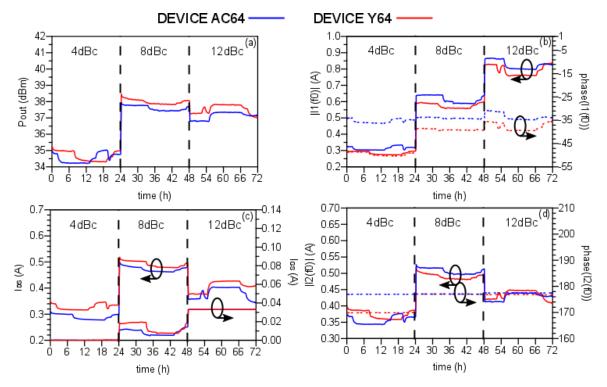

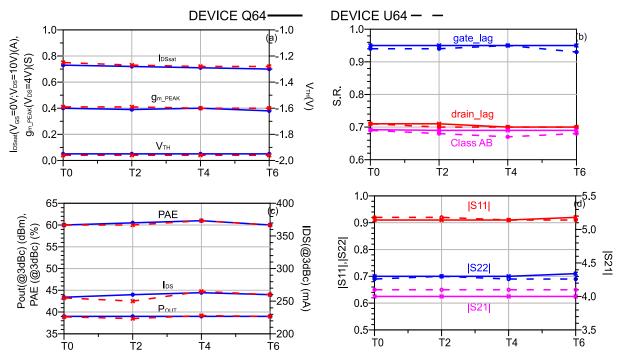

| 4.3.3    | Time-domain stress test results                        |     |

| 4.4 C    | Conclusion                                             | 134 |

| 5 Conc   | lusion                                                 |     |

| 6 Publi  | cations                                                |     |

| 7 Refer  | ences                                                  | 141 |

#### Thesis overview

The excellent physical properties of Gallium Nitride (GaN), Aluminium Nitride (AlN) and related alloys (AlGaN) make the solid-state electronic devices based on an AlGaN/GaN heterojunction the most interesting candidate for the next generation of power electronics, in particular for space applications. Unfortunately, this young technology suffers from reliability difficulties and memory effects (i.e. charge-trapping phenomena). In the last decades, much effort has been devoted to investigating the reliability and trapping effects of this technology. These investigations have identified several physical and technological challenges and have contributed to improve the maturity of the technology. The most significant effort to develop this technology for space applications was made by the American and European space agencies: the national aeronautics and space administration (NASA) and the european space agency (ESA). In particular, in Europe, this research was initially funded through national agencies, innovative component development activities at ESA and EU defense initiatives, such as the Korrigan, and great<sup>2</sup> (GaN Reliability Enhancement and Technology Transfer Initiative) projects [1], [2]. An important step towards using the European GaN technology in satellites has been done by ESA with the first in-orbit demonstration of an X-band transmitter using GaN monolithic microwave integrated circuit (MMIC) technology on board the PROBA-V mission. This transmitter has now been successfully operating in space for image and data transmission for more than 24 months, as shown in [2]. Among the industries supported by ESA and French space agency (centre national d'études spatiales (CNES)), Thales Alenia Space in Toulouse has currently developed a new generation of RF Front-End chain in GaN (MMIC) technology.

In this context, the present joint Ph.D. collaboration between the XLIM laboratory and the University of Padova was developed in order to make some improvements in reliability measurements and trapping characterization.

This work was supported on the one hand by the Thales Alenia Space in Toulouse through the "DEFIS-RF" ANR project (ANR-13-CHIN-0003) under the supervision of Dr. Jean-Luc Muraro and on the other hand by the French space agency (CNES) through contract 131223/00 under the supervision of Jean-Luc Roux. This joint Ph.D. collaboration has benefited from two different environments based on both the

university and industrial approaches. Moreover, this Ph.D. research has brought together the knowledge and skills of distinguished universities, namely, the University of Padova and the University of Limoges, the former on reliability and the latter on RF device modeling.

The main topics of this Ph.D. research concerned the characterization and the modeling of charge-trapping dynamic dispersion and reliability studies with an advanced time-domain methodology of GaN-based high electron mobility transistors.

Chapter 1 includes a brief introduction to the properties and capabilities of GaN technology and its promising applications in the space world.

In Chapter 2, a new investigation of charge-trapping is discussed from DC to radiofrequency operation mode, based on pulsed I/V measurements, DC and RF drain current measurements, and low-frequency dispersion measurements. An extensive analysis of the main charge-trapping mechanisms and the related deep levels identified in state-ofart GaN-based high electron mobility transistors are presented.

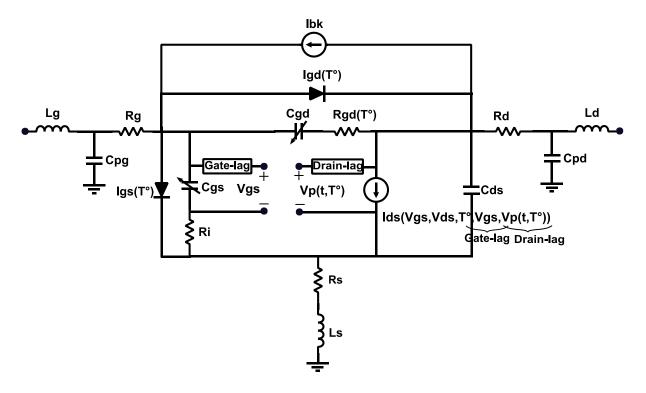

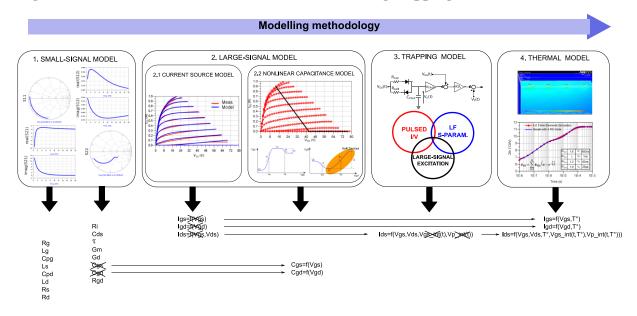

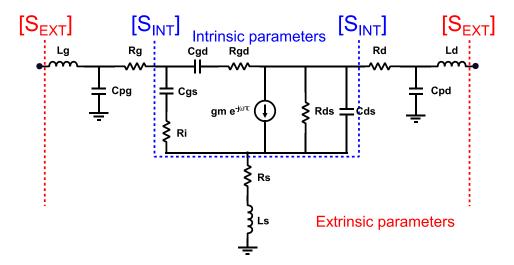

In Chapter 3, the determination and validation of a nonlinear electro-thermal AlGaN/GaN model for CAD application is described with a new additive thermal trap model to take into account the nonlinear dynamic behavior of trap states and their associated temperature variation.

In Chapter 4, an advanced time-domain methodology is introduced to investigate device reliability and determine its safe operating area for different overdrive conditions and different output load impedance conditions.

Lastly, the key points and the novel experimental results of this Ph.D. research are presented.

## 1 Background

## 1.1 Introduction

In this first part of this chapter a brief overview of the properties and capabilities of the more promising wide band-gap semiconductors based on AlGaN/GaN high-electron mobility transistors for the gamut of power electronics applications, from power conditioning to microwaves, is presented. In the second part, the potential usage of this technology in satellite equipment for telecommunications, navigation, Earth observation and science missions is illustrated.

### 1.2 GaN based semiconductors

The greatest scientific and technological revolution of the last century has no doubt changed the world. Nowadays, the need of communication and data processing are fulfilled thanks to the field effect transistor (FET) introduced in the beginning of 20<sup>th</sup> century. Its principle was filed by Julius Lilienfeld in 1925. After the Second World War, at AT&T Bell Labs, William Shockley at the head of a research group decided to attempt the building of a triode (transistor's precursor) like solid-state electronic device.

Later, the history of solid-state electronic devices was marked by the introduction of the highelectron mobility transistor (HEMT). The HEMT was first demonstrated by *Mimura et al.* at Fujitsu Labs in 1980 [3]. The invention of the HEMT represented the latest triumph of bandgap engineering and molecular beam epitaxy. Moreover, the HEMT in III-V compound semiconductors was based on the concept of modulation doping first demonstrated by *Dingle et al.* at Bell Labs in 1978 [4]. A modulation-doped structure creates a two-dimensional electron gas at the interface between two semiconductors of different band-gaps, which is the principle of a heterostructure device.

Today, RF and microwave applications are satisfied by different mature semiconductor technologies, such as Si, GaAs, and other III-V semiconductors. However, the wide band-gap semiconductors, in particular those based on GaN, are the most promising technologies for the next generation applications in communications, signal processing, electrical power management and imaging. Its performance has attracted attention as a highly promising

material for electronic applications because of its excellent transport properties, high critical electric field, robustness and thermal stability when compared to GaAs.

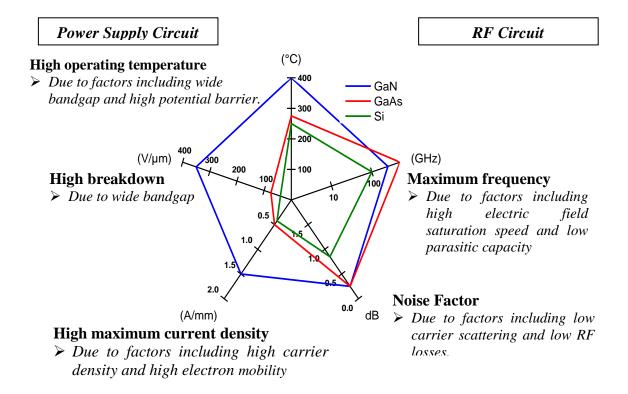

| Figure 1-1: Com | narison of Cal | N with Si and  | Cals semicon | ductors [5] |

|-----------------|----------------|----------------|--------------|-------------|

| rigule 1-1. Com | parison of Gal | N WILL SI ALLU | GaAs senneon |             |

| TABLE 1           Comparison of thermal and electronic properties for different semiconductors and heterostructures [6] |         |                     |                     |                    |                    |

|-------------------------------------------------------------------------------------------------------------------------|---------|---------------------|---------------------|--------------------|--------------------|

| Characteristic                                                                                                          | Silicon | Gallium<br>Arsenide | Indium<br>Phosphide | Silicon<br>Carbide | Gallium<br>Nitride |

| Bandgap (eV)                                                                                                            | 1.1     | 1.42                | 1.35                | 3.25               | 3.49               |

| Electron Mobility at 300 °K (cm²/Vs)                                                                                    | 1500    | 8500                | 5400                | 700                | 1000-2000          |

| Saturated Electron<br>Velocity (x10 <sup>7</sup> cm/s)                                                                  | 1       | 1.3                 | 1                   | 2                  | 2.5                |

| Critical Breakdown<br>Field (MV/cm)                                                                                     | 0.3     | 0.4                 | 0.5                 | 3                  | 3.3                |

| Thermal Conductivity<br>(W/cm °K)                                                                                       | 1.5     | 0.5                 | 0.7                 | 4.5                | >1.5               |

| $\begin{array}{c} Relative & Dielectric \\ Constant  \epsilon_r \end{array}$                                            | 11.8    | 12.8                | 12.5                | 10                 | 9                  |

The GaN-based devices currently have advantages for high-cost microwave applications where device performance is more critical. When compared with other highly commercialized

semiconductors such as Si and GaAs, GaN-based semiconductors have five key advantages: high operating temperatures, high critical electric field, high current densities, high-speed switching, and low on-resistances. A schematic comparison of these five figures of merit is given in Figure 1-1. These different materials can be compared using the Johnson figure of merit (JFoM), which gives a power-frequency limit based on material properties:

$$JFoM = \frac{v_{sat}E_{BD}}{2\pi}$$

(1-1)

where  $v_{sat}$  is the saturation velocity and  $E_{BD}$  is the electric field at which impact ionization initiates breakdown. The GaN JFoM is approximately 27.5 times higher than Si and more than 10 times better than GaAs [7]. Si and GaAs materials are expected to be replaced by wide-band gap GaN material due to the increase of power and frequency request for future communication applications. The GaN material demonstrates promising superior performances over its competitors as shown in Table 1, due to piezoelectric and spontaneous polarization induced effects, the two-dimensional electron gas (2DEG) sheet carrier concentration ( $n_s$ ) of AlGaN/GaN structure is very high (experimental values up to  $10^{13}$  cm<sup>-2</sup>) in comparison with III-V semiconductors. Furthermore, an exciting prospect in the near future is the monolithic integration of GaN HEMT and III-V CMOS devices to give a new lease on life to Moore's Law. The lack of bulk GaN source material has to the need for GaN growth on mismatched substrates such as Si, SiC and sapphire. Moreover, the development of GaN for RF electronics was significantly aided by the intense development of light-emitting diodes (LEDs).

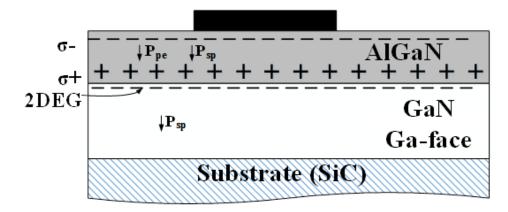

#### 1.2.1 Two-dimensional electron gas

As described in the previous section, the unique feature of AlGaN/GaN HEMTs is 2DEG channel formation. The sheet carrier density and the confinement of the two-dimensional electron gas located close to the interface of undoped and doped AlGaN/GaN heterostructures is due to the bending of the bands. The accumulation of attracted mobile carriers (electrons in the case of a positive sheet charge  $\sigma$ ) in this two-dimensional electron gas is confined in a quantum well along the heterojunction and relies both on piezoelectric and spontaneous polarization induced effects, as shown in Figure 1-2. The piezoelectric effects can exert a substantial influence on the concentration and distribution of free carriers in strained group-III nitride heterostructures. Indeed, in AlGaN/GaN based transistor structures, the piezoelectric

polarization of the strained AlGaN barrier layer is more than five times that of AlGaAs/GaAs structures, which corresponds to an increasing current density. The very high mobility of confined electrons in the quantum well and high saturation velocity associated to GaN make up the key feature of AlGaN/GaN HEMTs.

Figure 1-2: Polarization and charges in AlGaN/GaN HEMTs [5].

The induced sheet charge  $\sigma$  created at the interface between the AlGaN layer and the GaN layer of AlGaN/GaN heterostructures grown along the [0001] direction (*c*-axis) (GaN), shown in Figure 1-2, can be written as the sum of spontaneous and piezoelectric polarization charges at AlGaN and GaN layers (the piezoelectric polarization  $P_{PE-GaN}$  is considered negligible).

$$|\sigma| = |P_{SP-AlGaN} + P_{PE-AlGaN} - P_{SP-GaN}|$$

(1-2)

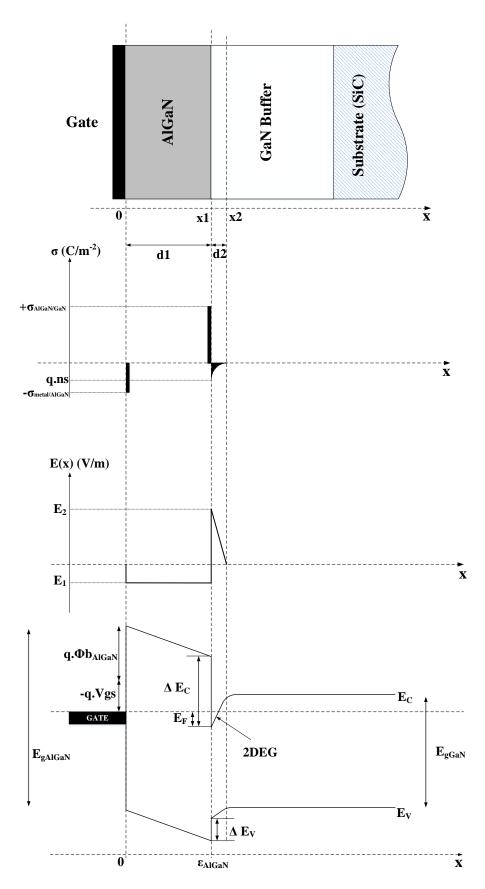

In order to compensate this induced positive sheet charge at the AlGaN interface, an accumulation of free electrons will appear at the GaN interface, as illustrated in Figure 1-2. The sheet electron concentration  $n_S(x)$  can be calculated by using the total bound sheet charge  $\sigma(x)$  (illustrated in Figure 1-3) and the following equation [8]:

$$n_s(x) = \frac{\sigma(x)}{q} - \frac{\varepsilon_0 \varepsilon_r(x)}{q^2 d} [q \Phi_b(x) + E_F(x) - \Delta E_c(x)]$$

(1-3)

where  $\sigma$  is the polarization induced sheet charge density, q is the electron charge, ( $\varepsilon_0$ ,  $\varepsilon_r$ ) are the vacuum and relative permittivities, d is the thickness of the AlGaN barrier,  $q\phi_b$  is the Schottky barrier of the gate contact on top of AlGaN,  $E_F$  is the position of the Fermi level with respect to the edge of the GaN conduction band energy, and  $\Delta E_c(x)$  is the offset of conduction band energy at the AlGaN/GaN interface.

Figure 1-3: Charge distribution, electric field and energy band diagram of an AlGaN/GaN HEMT heterostructure [5].

### 1.3 GaN technology for satellite equipment

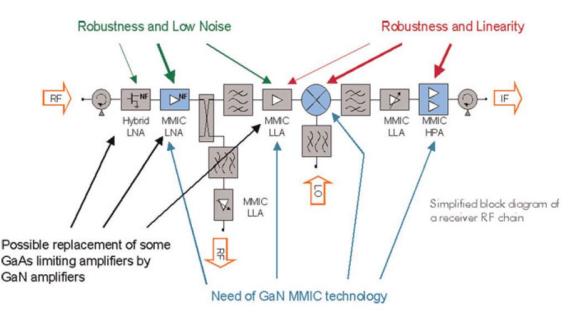

As already mentioned, GaN technology is currently under development and qualification not only for high power amplifier (HPA) module but also for other applications like low noise amplifier (LNA), mixer and local oscillator in a space environment. This technology offers significant advantages for space industries in terms of size reduction/integration, DC power consumption, linearity and RF power.

Solid-state power transistors have, over the past 40 years, started to replace vacuum technology in the vast majority of microwave systems, but the revolution is not complete. In particular, the high RF power microwave and millimeter-wave radar and communications transmitter applications are dominated by microwave tubes for frequency capabilities greater than 100 GHz, and for high device operating temperature capabilities greater than about 250 °C. Nowadays, at lower frequency ranges (L/C/S band), GaN-based solid state power amplifiers (SSPA) obtain impressive RF performance, such as for a Galileo-like navigation satellite 230 W [9], a 170 W L-Band achieved by Thales Alenia Space [10] and the 80 W C-band, which are comparable to a travelling-wave amplifier tube (TWTA) solution but with a smaller size and more flexible architecture.

Figure 1-4: Improvements along the RF chain of satellite receivers [11].

The improvements along the RF chain of satellite receivers are shown in [11], the majority of the functions of the equipment can be replaced by GaN technology with a reduction in the number of MMICs, thus lower equipment cost and increased robustness and linearity of HPA, LNA and mixer modules.

## 1.4 GH50-10 process

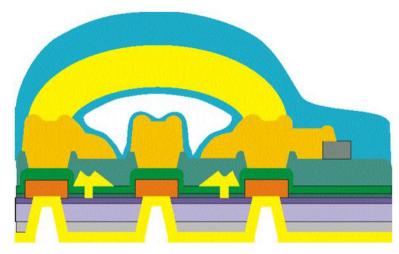

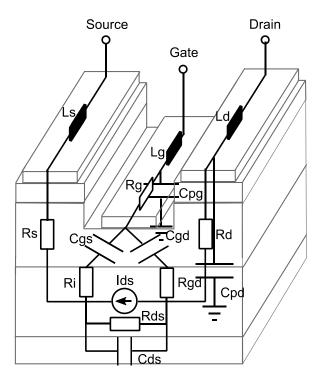

In this thesis, the modeled and characterized device is an  $8x250 \ \mu m$  AlGaN/GaN GH50-10 HEMTs (from the UMS foundry). A schematic cross section of the active region of a GH50-10 transistor is shown in Figure 1-5.

#### Figure 1-5: Schematic cross section of the active region of GH50-10 transistor [12].

The major features of the GH50-10 process extracted from [12] are the following:

- HEMT MOCVD active layer on 3-inch semi-insulating SiC substrate with high sheetresistance uniformity

- Isolation by ion implantation

- 0.5  $\mu$ m T and  $\Gamma$  shaped gold gate with diffusion barriers with low resistance suitable for high frequency operation. The gate foot lithography is made with an e-beam whereas the gate head lithography is made with an I-line stepper.

- $30\Omega/sq$  TaN resistors,  $640\Omega/sq$  semiconductor resistors and  $1000\Omega/sq$  TiWSi resistors

- Thick gold electroplating for interconnects and line reinforcement

- Air bridges to overcome device topography

- SiN-protection of the wafer front side

- 100  $\mu$ m substrate thickness with via interconnects for source contacting / connection to ground pads

- Power density 5 W/mm @ 2 GHz

- Operating frequencies up to 6 GHz

- Operating voltage Vds = 50 V

- Maximum voltage Vdsmax = 150 V

- Pinch-off voltage Vp = -2.2 V

- Drain saturation current Idss = 420 mA/mm

- Transconductance Gm= 190 mS/mm @ Vgs = 0V

- Gate and Drain leakage currents Igl,  $Idl < 200 \mu A/mm$  @ Vds = 50 V, Vgs = -7 V

#### 1.5 Conclusion

This chapter briefly introduced the properties and advantages of GaN in microwave systems with a particular emphasis on space applications. An example of an RF chain of a satellite receiver was presented, but is currently under development to replace most of the functions of the equipment with GaN technology. The presented Ph.D. research was focused on this context, more specifically on HPA modules. At the end of this chapter, further details on the technology process of the studied GaN device was also presented.

## 2 Investigation of trapping phenomena

## 2.1 Introduction

The AlGaN/GaN HEMTs, as described in the first chapter, have shown impressive performance in terms of high electron mobility, high power density, high cut-off frequency and high thermal conductivity. As a consequence, HEMT devices should replace the preceding technologies in most RF and power commercial markets. However, GaN technology suffers severely from dispersion phenomena called trapping effects that, combined with thermal effects (self-heating), limit their initial expectation.

The aim of this chapter is the understanding of the trapping phenomena, in particular the reduction of their effects during real operation mode using appropriate bias conditions.

This chapter presents a detailed trap investigation protocol to obtain a complete overview of trap behavior from DC to radio-frequency operation mode based on combined pulsed I/V measurements, DC and RF drain current measurements and low-frequency (LF) dispersion measurements. The thermal pulsed I/V measurement technique is used to determine the thermal resistance, something which is necessary to calculate the Arrhenius plot. Finally, a discussion and comparison of the Arrhenius plot results of these trap investigation techniques are depicted.

### 2.2 Basics of trapping phenomena

Traps, in solid-state physics, are any locations within a material (generally in a semiconductor) that limit the movement of holes (i.e., energy levels, related to the absence of an electron/hole within a crystal structure and present between the forbidden energy-gap of semiconductor). Trapping effects have required many years to be understood in several semiconductor technologies like FET and GaAs MESFETs. However, in spite of extensive investigation of trapping phenomena, the physics of the active defects is not completely understood in GaN HEMTs. So, a deep knowledge of the origin of the traps, their location, and the physical mechanisms of a trap are important for the optimization of the performance of these devices. The GaN material contains high densities of defects, mostly due to crystalline imperfections, which result from the growth of the material (like impurities in the crystal lattice, dangling bonds on the surface, and lattice mismatches with foreign substrates

such as SiC and sapphire and impurities in the crystal lattice) and the processing of the device.

These imperfections generate trap centers within the band-gap of a semiconductor that facilitate the creation of a free electron in the conduction band and a hole in the valance band. These processes need a smaller amount of energy than a direct band-to-band transition. There are two types of traps: donors and acceptors. A donor-like state can be both positive (ability to emit an electron) or neutral (when filled). Acceptor-like states can be both negative (possibility of capturing an electron) or neutral (when empty).

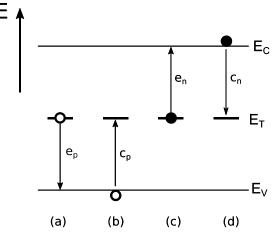

The defects can be classified in terms of their energy level: the traps with an energy-level close to the conduction or valence bands (<1eV) are called shallow-level traps, which are responsible for parasitic doping effects. Traps with an energy level deeper within the forbidden band-gap are called deep level traps. The process of trapping and de-trapping follows the Shockley–Read–Hall theory [13]–[15] which describes the interactions between the free-carriers (electrons and holes) and the generation/recombination mechanisms for a deep level transition to or from a band (as illustrated in Figure 2-1).

Figure 2-1: The basic processes of transition: (a) hole emission (an electron jumps from the valence band to the trapped level), (b) hole capture (an electron drops from an occupied trap to the valence band, and a hole disappears), (c) electron emission (an electron jumps from the trapped level to the conduction band) and (d) electron capture (an electron drops from the conduction band to an unoccupied trap).

In particular, we focus only on the traps related to the conduction band, the same argument can be used for the valence band. To calculate the rate of an occupied trap's density or a function of time, an analysis of the capture and emission processes needs to be considered.

Considering all recombination-generation processes, the overall occupancy trap rate in the conduction band is equal to

Investigation of trapping phenomena

$$\frac{\partial n_T}{\partial t} = (c_n (N_T - n_T) - e_n n_T)$$

(2-1)

where  $c_n$ ,  $N_T$ ,  $n_T$  and  $e_n$  are respectively the electron capture rate, the number of defect states, the number of defect states filled with electrons and the electron emission rate. In thermal equilibrium where every process is balanced by its inverse process, in Equation (2-1) the number of emitted electrons from traps must be equal to the number of those captured (thus  $\partial n_T / \partial t = 0$ ). Therefore, the relationship between the capture and the emission rate for the conduction band can be defined as

$$\frac{e_n}{c_n} = \left(\frac{N_T}{n_T} - 1\right) \tag{2-2}$$

The occupancy probability of trap's energy level is given by the Fermi-Dirac distribution:

$$\frac{N_T}{n_T} = \frac{1}{1 + \exp\left(\frac{E_T - E_F}{kT}\right)}$$

(2-3)

where  $E_T$  is the energy level,  $E_F$  is a reference energy called the Fermi level, k is the Boltzmaann constant (in eV T<sup>-1</sup>) and T is the temperature (in K). Considering the Fermi equations, Equation (2-2) can be rewritten as

$$\frac{e_n}{c_n} = exp\left(\frac{E_T - E_F}{kT}\right) \tag{2-4}$$

The capture rate of electrons  $c_n$ , which represents the ratio of the trapped electrons density to unoccupied trap states, can be expressed as

$$c_n = \sigma_n v_n n \tag{2-5}$$

where  $\sigma_n$ ,  $v_n$  and *n* represent respectively the capture cross-section, the thermal velocity of the electrons, and the number of free-electrons in the conductance band. The last two parameters can be expressed as

$$v_n = \left(\frac{3kT}{m^*}\right)^{1/2} \tag{2-6}$$

and

$$n = N_c exp\left(-\frac{E_c - E_F}{kT}\right) \tag{2-7}$$

The conduction-band effective density of state Nc is expressed as

$$N_c = 2M_c \left(\frac{2\pi m^* kT}{h^2}\right)^{3/2}$$

(2-8)

where  $m^*$  is the effective mass of the electron, h is the Planck's constant, and  $M_C$  is the number of conduction band minima.

Substituting Equations (2-5), (2-6), (2-7) and (2-8) in to Equation (2-4), we obtain the expression of emission electron rate of deep level:

$$\frac{1}{\tau_n} = e_n = \gamma T^2 \sigma_n exp\left(-\frac{E_n}{kT}\right)$$

(2-9)

where

$$\gamma = 2\sqrt{3}(2\pi)^{3/2}k^2m^*h^{-2} \tag{2-10}$$

and

$$\sigma_n = \sigma_\infty exp\left(\frac{\Delta E_\sigma}{kT}\right) \tag{2-11}$$

where  $\tau_n$  represents the electron emission time constant,  $\sigma_{\infty}$  the capture cross section at  $T = \infty$ ,  $E_n$  the apparent activation energy, which is in this case may significantly differ from the zero-field binding energy of the trap with respect to the conduction-band, and  $\Delta E_{\sigma}$  is the activation energy of the capture cross-section.

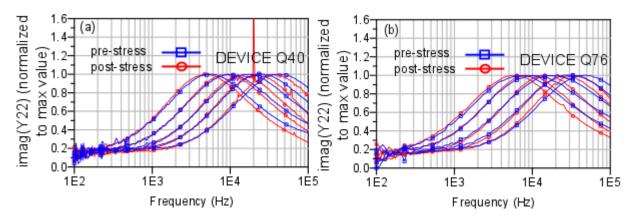

In order to obtain the properties of traps (such as their physical location in the structure of the device), it is necessary to extrapolate the Arrhenius plots of the traps and their signatures in terms of activation energies and capture cross-sections. The determination of the emission time constant for different techniques, drain current transient (DCT) and LF dispersion measurements, is fully discussed in the following.

The activation energy and capture cross-section parameters are the fundamental characteristics of a trapping center. In fact, a comparison with other identified activation energies and capture cross-sections in different devices can help to understand the mechanisms of charge-trapping and to determine the location of the trapping centers in a device.

In GaN-based transistors, the parasitic charge moving of the traps on the surface and/or in the bulk affects the density of the 2DEG channel, causing a modulation of the drain current that is

determined by the effective channel thickness as well as the output conductance and transconductance in the low-frequency range [16]. For this reason, an advanced trapping characterization protocol is proposed in the following paragraph and is based on:

- Pulsed I/V measurements, carried out at several quiescent bias points to quantify the current-collapse (CC), to obtain a preliminary characterization and to understand which trapping mechanisms may affect the transistor's performance [17];

- DC and RF drain current transient spectroscopy [18], [19] through stretched multiexponential fitting of the DCT measurements [20] can provide information about the activation energy and capture cross-section of the trap levels;

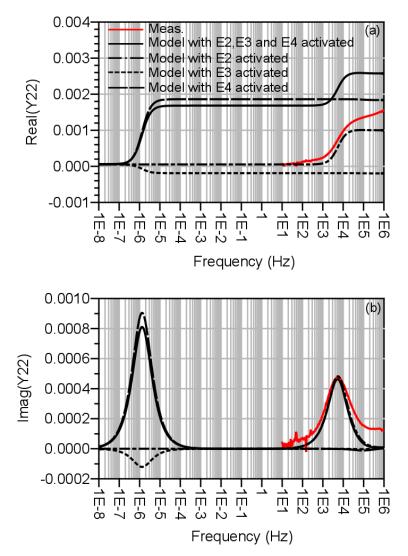

- Output conductance frequency dispersion and transconductance frequency dispersion [21], [22] based on low-frequency 2-port S-parameter measurements can provide information on the characteristics of the trap levels (such as  $E_A$  and  $\sigma_c$ ) promoted by small–signal excitation at a fixed bias point.

#### 2.3 Trapping characterization methodology

#### 2.3.1 Pulsed I/V characterization

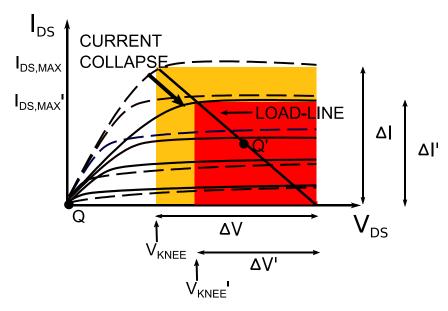

Pulsed I/V measurement is carried out to obtain a preliminary and quick characterization in order to understand which trapping mechanisms may affect the transistor's performance. This technique is very useful because it allows distinguishing the trapping effects from the thermal effects (normally these effects have time constants with the same order of magnitude) and then evaluate only the electrical phenomena of a trap state. One of the most common trap effects is called CC [23], as shown in Figure 2-2.

The  $I_D$ - $V_D$  characteristics in Figure 2-2 obtained before and after the application of a high drain bias with quiescent point Q' show a dynamic increase of the knee voltage and a decrease of the drain current due to large gate-drain voltage swings [24], [25]. These two phenomena are still sufficient to cause a substantial reduction in output power (shown in Figure 2-2), where the maximum output power is proportional to the product of the maximum current and voltage swings and in Class A is equal to

$$p \simeq \frac{1}{8} \Delta V \Delta I \tag{2-12}$$

Thus, these CC effects are related to the presence of deep level which promotes the specific trapping phenomena. The main effects related to CC are the gate-lag effect and the drain-lag effect [26].

Figure 2-2: Schematic of  $I_D$ - $V_D$  characteristics before (dashed curves) and after (full curves) the application of a high drain bias. The maximum device output power with and without trap effects is plotted in red and yellow rectangles respectively.

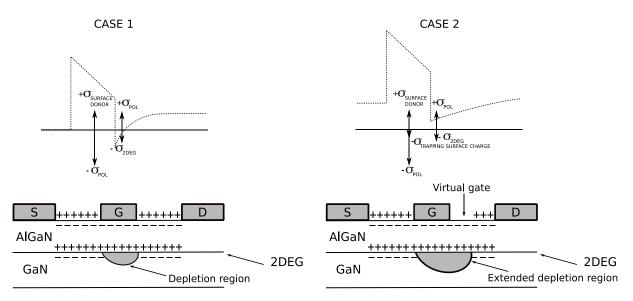

The **gate-lag effect** is a delayed response of the drain current when a gate voltage variation is applied and this is due principally to two mechanisms [17], [27]. The first one has been associated with the ionized donor states located on the surface between the gate and the drain electrodes [25], [28] which influence the series resistances in the source and drain access regions. The ionized donor states can capture a free electron and thus reduce the 2DEG density. *Vetury et al.*[25] explains that the extension of the depletion region is due to the increase of ionized donor states. This effect can be modeled as a second virtual gate when a negative gate pulse is applied. The de-trapping transient associated to this effect shows a slow constant time (in the order of milliseconds-seconds) [27]. The mechanism of a virtual gate is shown in Figure 2-3.

Figure 2-3: Schematic of gate-lag mechanism: (case 1) presence of ionized donor traps, (case 2) trap charged with reduction of the 2DEG density [25].

The second one is related to the positive shift of the pinch-off voltage for negative gate bias that is due to charge trapping under the gate [17]. These traps are normally located in the AlGaN or GaN layers and have faster de-trapping kinetic processes.

In a recent work [29], using a simple simulation framework, it has been demonstrated that a passivation dielectric that minimizes surface leakage and creates a high density of shallow traps at the surface is necessary to minimize the formation of a virtual gate and eliminate gate-lag phenomena. The use of a passivation layer and gate field plating in the last generation of GaN-based transistors has allowed the almost complete reduction of gate-lag effects.

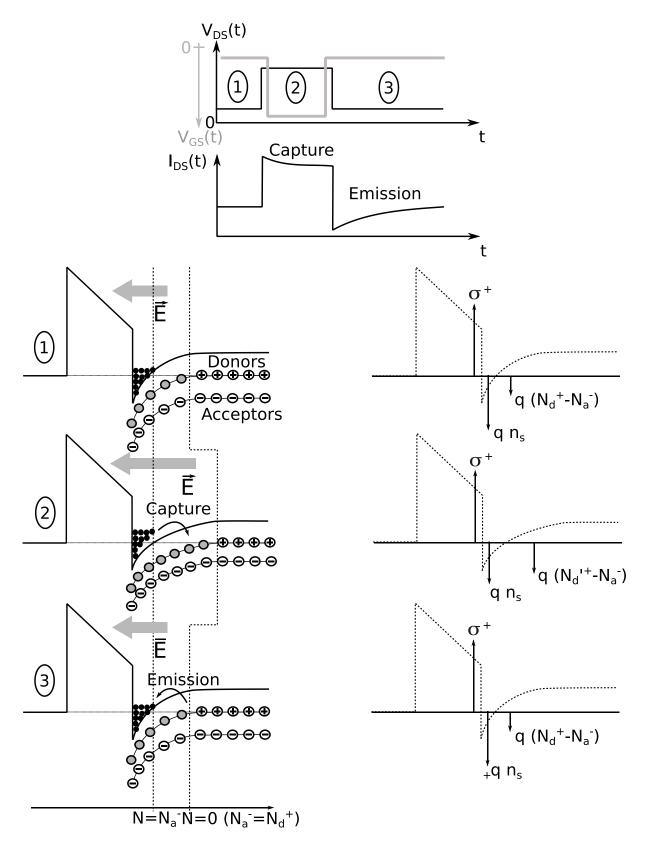

The **drain-lag effect** is a delayed response of the drain current induced when a very high drain voltage and very negative gate voltage (higher than the pinch-off voltage V<sub>P</sub>) during DC pulses are applied. It produces a modulation of the depletion layer into the active region due to free electrons' being injected into the buffer. The drain-lag mechanism is explained in Figure 2-4 when the drain pulse is applied. Figure 2-4 shows the impact of traps related to the buffer on the 2DEG channel when the drain pulsed is applied: (1) the initial state, the device is at equilibrium  $N_d^+=N_a^-$  the density of ionized donors is equal to the density of ionized acceptor when E=0. (2) A very high drain voltage and very negative gate voltage are applied. They produce a very strong vertical electric field due to the high drain voltage and high leakage current due to very negative gate voltage. These two phenomena induce a capture of free-electrons in the 2DEG channel by the donor trap, thus the density of ionized donors is reduced to  $N_d^{\prime+}$  and becomes neutral. (3) The device comes back to initial state when the V<sub>GS</sub> and V<sub>DS</sub> are pulsed down. The device is no longer submitted to a strong vertical electric field

Figure 2-4: Schematic of trapping and de-trapping process of traps located in the buffer (hypothesis  $N_D > N_a$ ) [5], [30].

and high leakage current, so the captured electrons in the last step are re-emitted with a slow emission process. Therefore, the capture and emission processes are asymmetric. Hence, in a GaN-based transistor the capture time constants are in the order of a few nanoseconds and the emission time constants on the order of a few microseconds to minutes.

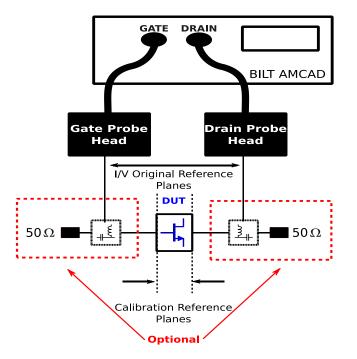

#### 2.3.1.1 Pulsed measurement test bench

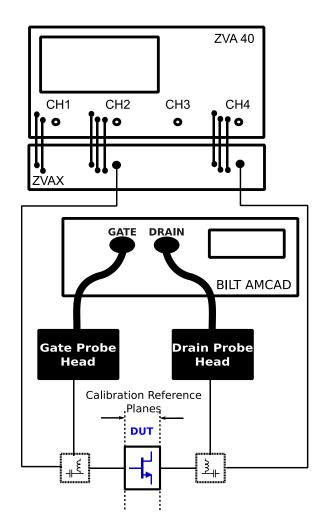

A schematic of the set-up used for pulsed I/V characterization is shown in Figure 2-5. The set-up is based on a 250V/10A pulsed I/V BILT AMCAD system [31]. The pulsed I/V measurements obtained with this set-up can be used for trapping investigation and the extraction of a nonlinear current source model of the transistor. The gate and drain current measurements are made using differential voltage measurements at the terminals of a resistance into the gate (10  $\Omega$ ) and drain (0.5  $\Omega$ ) probe respectively. The pulse generation and the voltage/current measurement are synchronized by an internal trigger. In the system, it is possible also to consider parasitic effects (introduced by the cable, connector, bias tees...) with a special DC calibration. This DC calibration consists of measuring the resistance path from probe head (I/V original reference planes) to on-wafer probing. The use of bias tees is conditioned by the type of device under test (DUT), e. g. it is recommended for transistors with large areas. It must also be considered that the use of bias tees introduces a degradation of the I<sub>D</sub>-V<sub>D</sub> characteristic especially in the ohmic region.

Figure 2-5: Block diagram of pulsed I/V experimental set-up.

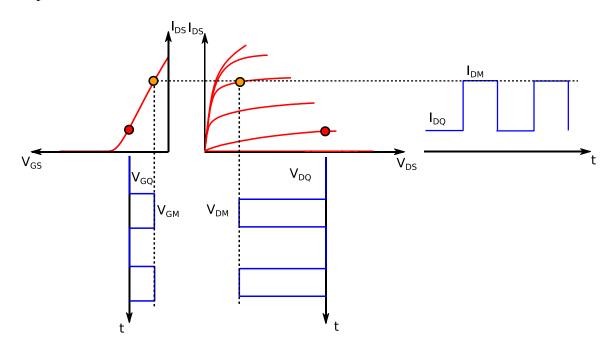

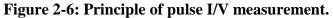

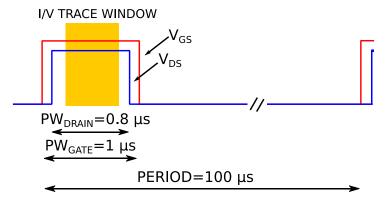

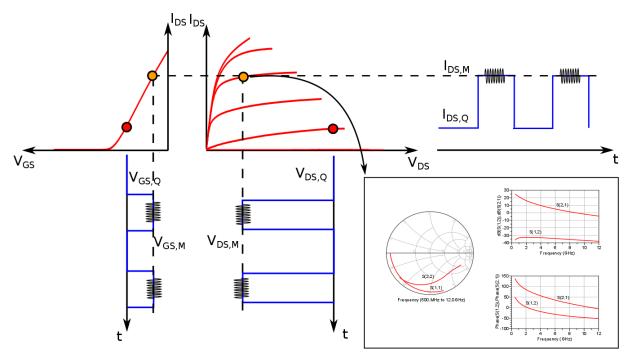

The principle of pulsed I/V measurements is shown in Figure 2-6. Pulsed I/V measurements are carried out in quasi isothermal conditions. Therefore, the gate and drain of the device are pulsed from a quiescent-bias point  $(V_{GQ}, V_{DQ})$  corresponding to a fixed trapping state to the measurement-bias point  $(V_{GM}, V_{DM})$ . In order to overcome the self-heating effect and therefore to investigate principally the electrical phenomena due to the trapping effects, the pulse-width of the gate and drain are chosen as small as possible, within the limit of pulse generation. Moreover, the duration of the pulse period must be much longer than the pulse-width, so as to be sure that the device returns to its steady-state conditions. The timing specification used for the following pulsed I/V measurement is described in Figure 2-7 with a pulse duty cycle (defined as  $PW_{GATE}/PERIOD$ ) equal to 99 and the I/V TRACE WINDOW represents the part of the pulse employed to determine the average currents and voltages for every measurement-bias point.

Figure 2-7: Pulse timing diagram of pulse I/V measurement.

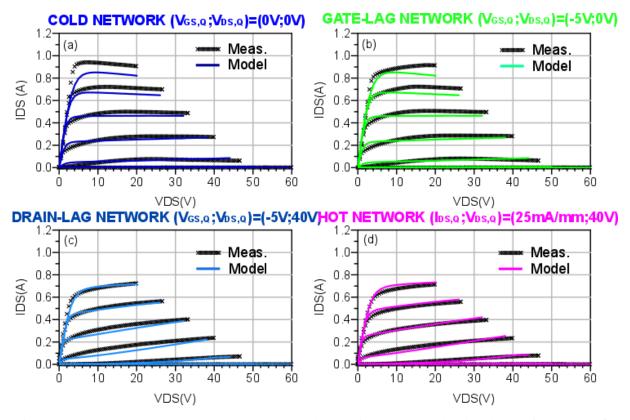

#### 2.3.1.2 Pulsed I/V characterization for trapping investigation

In order to identify and quantify the trapping effects a specific trapping pulsed I/V protocol has been developed, based on pulsed I/V characterization for different quiescent bias points:

- $Q_1$ : (V<sub>GQ</sub>, V<sub>DQ</sub>)=(0V,0V) which corresponds to negligible electron trapping;

- Q<sub>2</sub>: (V<sub>GQ</sub>, V<sub>DQ</sub>)=(-5V,0V) which may favor the trapping of electrons under the gate region (gate-lag);

- Q<sub>3</sub>: (V<sub>GQ</sub>, V<sub>DQ</sub>)=(-5V,40V) which may favor the trapping of electrons under the gatedrain region (drain-lag);

- Q4: (V<sub>GQ</sub>, V<sub>DQ</sub>)=( -1.9V,40V) which is representative of electron trapping under class AB bias condition (I<sub>DS</sub>=50mA at V<sub>DQ</sub>=40V).

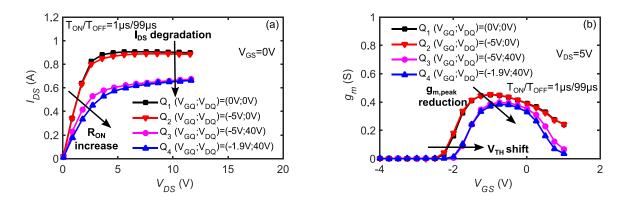

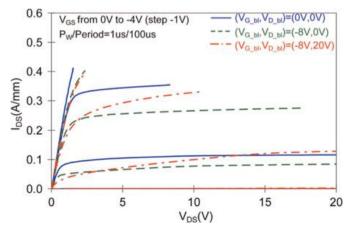

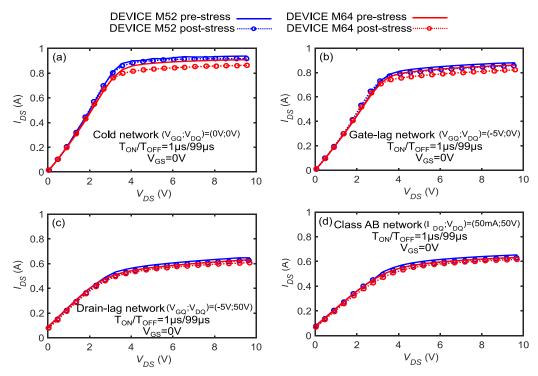

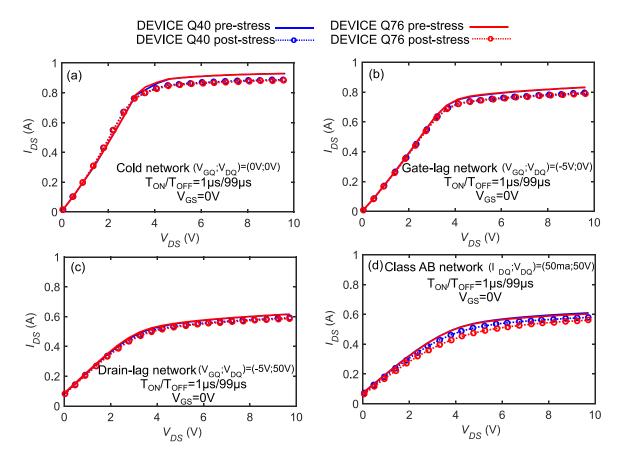

Figure 2-8(a) reports the results of pulsed  $I_D$ - $V_D$  characterization and Figure 2-8(b) shows the  $g_m$  variation (extracted from  $I_D$ - $V_G$  measurements). The results of pulsed  $I_D$ - $V_D$  measurements indicate that the device is less sensitive to gate-lag than to drain-lag: the gate filling pulse  $V_{GQ}$  has a negligible effect on the device characteristics, while the application of  $V_{DQ}$  induces a strong CC and degrades the  $R_{ON}$  value. By comparing the OFF-state quiescent bias point (-5V, 40 V) with the SEMI-ON state, class AB bias condition (same  $V_{DQ}$  but  $V_{GQ}$ =-1.9 V), it can be noticed that the CC is relatively unchanged but the  $R_{ON}$  degradation is enhanced.

Figure 2-8: (a)  $I_D$ - $V_D$  and (b)  $g_m$  (derived from  $I_D$ - $V_G$ ) pulsed characterizations for different quiescent bias points of  $8x250x0.5\mu m^2$  AlGaN/GaN HEMT.

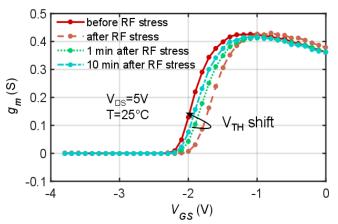

Transconductance  $(g_m)$  measurements, shown in Figure 2-8(b), show that the drain-lag (point  $Q_3$ ) induces both a positive threshold voltage shift and a reduction in  $g_m$  (-15% at peak and more pronounced at higher  $V_{GS}$ ). The  $Q_4$  quiescent point presents the same threshold voltage shift and a slightly more pronounced decrease in  $g_m$  with respect to  $Q_3$ . The threshold voltage shift and a reduction in  $g_m$  for  $Q_3$  and  $Q_4$  quiescent point conditions suggest that CC is related to negative charge trapping both under the gate and in the access regions.

One figure of merit to evaluate and quantify the impact of trapping effects on the device's characteristics is the slump ratio (SR), defined as the saturation drain current in trapping conditions such as  $Q_2$ ,  $Q_3$  and  $Q_4$  measured at  $(V_{GM}; V_{DM}) = (0V; 10V)$  divided by the saturation drain current in negligible trapping condition  $Q_1$  measured at  $(V_{GM}; V_{DM}) = (0V; 10V)$ .

Table 2 summarizes the drop of saturation current due to CC. Notice that the SR has a strong decrease in the drain-lag and Class AB operation bias point. This indicates that traps excited by a high electric field will cause dispersion in RF performance.

|                                     | COLD (Q1) | GATE-LAG (Q2) | DRAIN-LAG<br>(Q <sub>3</sub> ) | CLASS AB<br>BIAS (Q4) |

|-------------------------------------|-----------|---------------|--------------------------------|-----------------------|

| $I_{DS(V_{GM};V_{DM})=(0V;10V)}(A)$ | 0,90      | 0,88          | 0,66                           | 0,65                  |

| SR                                  | //        | 0,98          | 0,73                           | 0,72                  |

# 2.3.1.3 Pulsed I/V characterization for channel temperature investigation

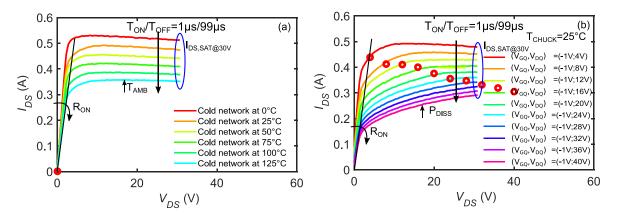

In order to estimate the junction temperature of GaN-based HEMTs, something which is essential to determine the Arrhenius plot, an electrical methodology to determine the thermal resistance is used [32]. This methodology is based on pulsed I/V measurements, which uses a small pulse-width. Thus, the self-heating of the device can be assumed negligible and the junction temperature can be considered dependent of the dissipated power of the quiescent bias point. The extraction of  $R_{TH}$  consists in the characterization of the on-resistance ( $R_{ON}$ ) and saturation drain current ( $I_{DS,SAT}$ ) variations with respect to the temperature and is based on two steps:

• Thermal calibration.  $R_{ON}$  and  $I_{DS,SAT}$  are measured at cold quiescent bias point condition ( $V_{GQ}$ ,  $V_{DQ}$ )=(0V,0V) and at different chuck temperatures. At this condition, there is no dissipated power and the channel temperature can be considered the same as the chuck temperature.

The thermal pulsed I/V measurements are carried out in cold network condition ( $V_{GQ}$ ,  $V_{DQ}$ )=(0V,0V) and for 25°C-150°C temperature range (Figure 2-9(a)).

• **Dissipation power calibration**. In this case, R<sub>ON</sub> and I<sub>DS,SAT</sub> are measured at a fixed chuck temperature (25°C) and the pulses are issued from different quiescent bias

points. The power dissipation and consequently the channel temperature are set by the quiescent bias point ( $V_{GQ}$   $V_{DQ}$ ). The pulsed I/V measurements are carried out at various bias points ( $V_{GQ}$ =-1V,  $V_{DQ}$ = 4-40V) and at 25°C chuck temperature (Figure 2-9(b)).

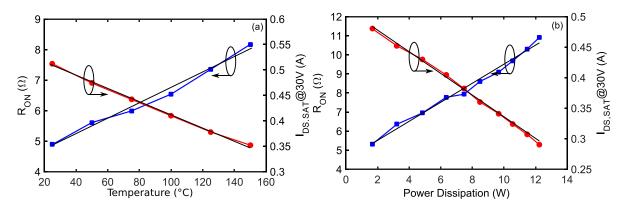

This technology has very slow trapping phenomena. Hence, between successive measurements a relaxation period is applied to the device without any electric bias. The estimated  $R_{ON}$  and  $I_{DS,SAT}$  in Figure 2-10 present for both conditions a linear relationship with temperature and power dissipation: a negative slope for  $I_{DS,SAT}$  and a positive slope for  $R_{ON}$ . The thermal resistance can be defined classically as the relationship between the channel temperature and power dissipation [33]:

$$R_{TH} = \frac{\Delta T}{\Delta P_{DISS}} \tag{2-13}$$

Thus, the thermal resistance is simply the ratio of the slope of the temperature and of the power dissipation. The thermal resistance can be extracted from the linear region ( $R_{ON}$ ) and from the saturation region ( $I_{DS,SAT}$ ). In our case the thermal resistance is determined from the saturation region ( $I_{DS,SAT}$ ) because the linear region, where  $R_{ON}$  is calculated, has a parasitic effect introduced by the bias tees. The thermal resistance extracted from the  $I_{DS,SAT}$  measurement is estimated to be 14 C°/W.

Figure 2-9: (a) Pulsed I/V characteristics ( $@V_{GS}=-1V$ ) at cold network ( $V_{GQ}$ ,  $V_{DQ}$ )=(0V,0V) with zero power condition (in red circles) and at different chuck temperatures. (b) Pulsed I/V characteristics ( $@V_{GS}=-1V$ ) from various bias points ( $V_{GQ}=-1V$ ,  $V_{DQ}=4-40V$ ) (in red circles) and at a chuck temperature equal to 25°C.

Figure 2-10: (a) Extracted pulsed IDS,SAT (@VDS=30V) and RON as a function of chuck temperature TAMB (@ PDISS=0 W), (b) Extracted pulsed IDS,SAT (@VDS=30V) and RON versus power dissipation.

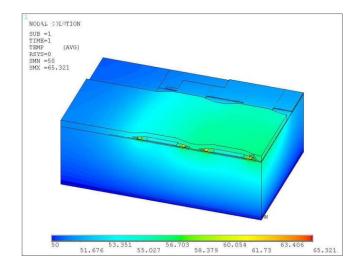

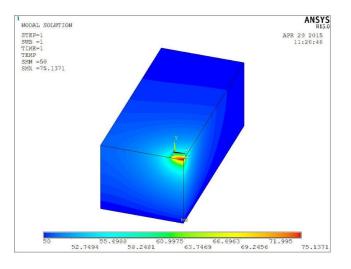

The measured device is soldered onto a copper tungsten mount. The 3-D finite-element simulations with ANSYS software are performed separately on a  $0.5x8x250 \ \mu\text{m}^2$  AlGaN/GaN HEMT (Figure 2-11) and on a copper tungsten mount (Figure 2-12). The overall thermal resistance obtained by the finite-element simulations is

$$R_{TH_{ANSYS}} = R_{DEVICE} + R_{MOUNT} = \frac{15}{2.5} + \frac{25}{4} \approx 12.25 \ ^{\circ}C/W$$

(2-14)

In the first approximation, the channel temperature determined with these two techniques gives similar results. Thus, the estimated thermal resistance is validated with 3-D finite-element simulations.

Figure 2-11: Thermal resistance for a 0.5x8x250 µm<sup>2</sup> AlGaN/GaN HEMT by 3-D finite element simulation with ANSYS software for a dissipated power equal to 2.5 W.

# Figure 2-12: Thermal resistance for a copper tungsten mount by 3-D finite element simulation with ANSYS software for a dissipated power equal to 4 W.

# 2.3.2 Drain current transient spectroscopy

The previous pulsed I/V characterization is very useful for investigating the CC. But, its measurement window (<1 ms) does not provide any information about the dynamic behavior of the trap state. For this reason, DCT spectroscopy [18]–[20], [34]–[36], known as current mode deep level transient spectroscopy (I-DLTS), is used to investigate the time evolution of carriers in the trapping process and therefore to identify the associated deep level.

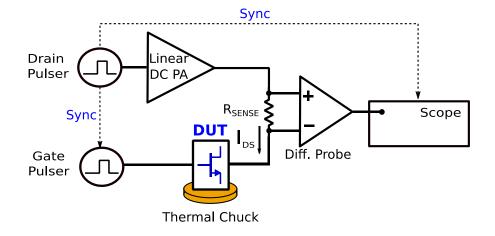

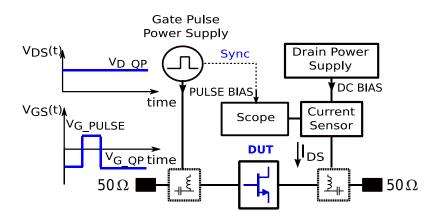

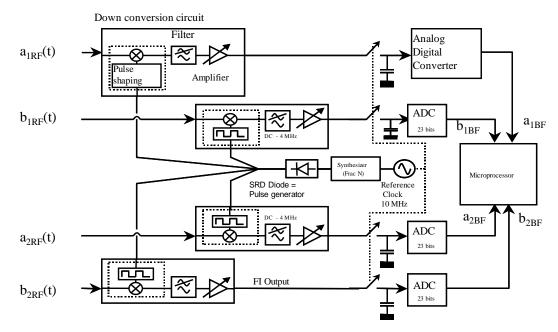

# 2.3.2.1 Drain current transient set-up

The experimental set-up used for DCT measurements is shown in Figure 2-13. In this set-up, the drain current transient is determined by measuring the differential voltage on a resistive load ( $R_{SENSE}=10\Omega$ ) connected between the drain of transistor and the drain pulser (Agilent 33220A arbitrary waveform generator). The drain pulse signal is linearly amplified to reach the required values of drain current and voltage. The digital sampling oscilloscope (Tektronix TDS 645C) and gate pulser (Agilent 33220A arbitrary waveform generator) are trigged by a synchronous pulsed signal generated by a drain pulser. The delay introduced by the linear DC PA (FLC voltage amplifier) has a negligible effect on the synchronized biasing and DC measurement of the transistor.

#### Figure 2-13: Block diagram of thermal DCT measurement set-up.

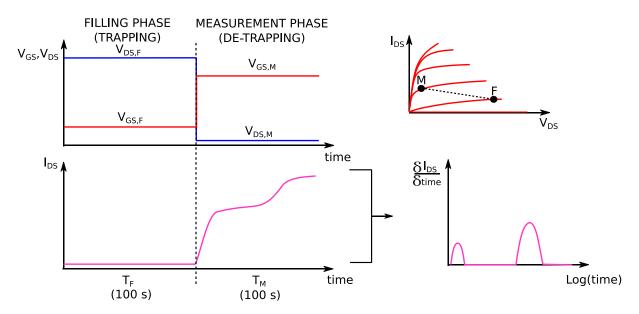

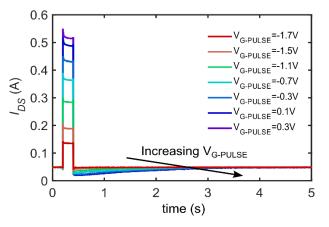

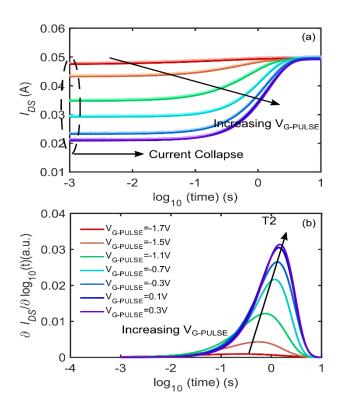

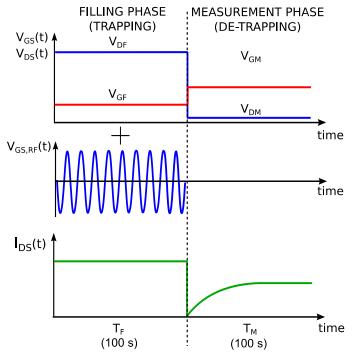

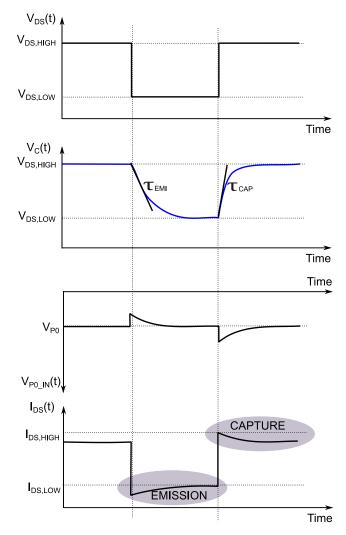

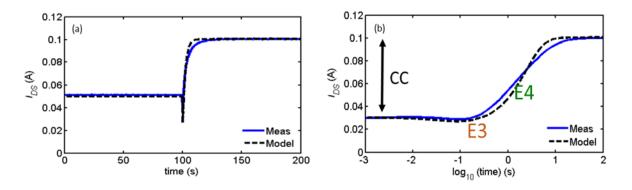

The principle of drain current measurement technique is shown in Figure 2-14. The device is biased for 100 s in filling condition ( $V_{GS,F}$ ; $V_{DS,F}$ ), thus inducing a specific trapping state. Subsequently, the device is switched to a different bias point in a low-field and low-power on-state ( $V_{GS,M}$ ; $V_{DS,M}$ ); the recovery of drain current related to charge de-trapping is measured over 7 time decades (from 10 µs to 100 s) with multiple recording techniques by means of a digital sampling oscilloscope. The measured drain current transients are later elaborated with dedicated fitting to obtain the associated time-constant spectrum.

Figure 2-14: Principle of the drain current transient measurement technique: the device is biased for 100 s in filling condition ( $V_{GS,F}$ ; $V_{DS,F}$ ), then it is biased in de-trapping condition ( $V_{GS,M}$ ; $V_{DS,M}$ ), for another 100 s to measure drain current transient and to obtain a trapping analysis with the related time-constant spectrum [37].

# 2.3.2.2 Time constant extraction methodology

In the literature, several mathematical approaches to fit the de-trapping transient data and to extrapolate both time constants and trap amplitudes are reported:

- polynomial: the fitting of transient data with a polynomial function and the extrapolation of time constant from the peak of associated drain current derivative [20];

- **multi-exponential**: the fitting of transient data with a least mean square function by the sum of 100 exponentials with fixed time constants and variable amplitude coefficients, and the determination of the time constant by the analysis of the peak of associated drain current derivative [18];

- **stretched multi-exponential**: the fitting of the data by a stretched multi-exponential function and the determination of the time constant by the analysis of the peak of the derivative that corresponds to the time constant of the de-trapping behavior [20].

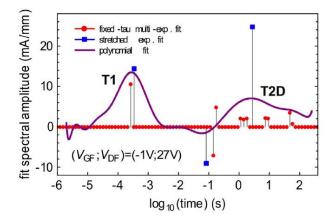

*Bisi et al.* [20] implemented and compared these three methods to evaluate which method has the best performance and precision in determining the time constant. The comparison of the different fitting algorithms is depicted in Figure 2-15. It appears that the three methods involve three different behaviors: the quasi-ideal exponential transient labeled "T1" in Figure 2-15 is correctly detected by all fitting methods. On the contrary, the "T2D" process has a complex stretched multi-exponential behavior. In this case, it is only with the stretched multiexponential fitting that the time constants are correctly extracted: the polynomial and the multi-exponential fits present spectral dispersion introducing additional parasitic components in more to the real time constant. In conclusion, the best method in terms of precision and physical sense is the stretched multi-exponential fit. Following these considerations, this method has been adopted to extract the time constant in our study. The stretched multiexponential function can be expressed as

$$I_{DS,fitting}(t) = \sum_{i}^{N} A_{i} e^{-\left(\frac{t}{\tau_{i}}\right)^{\beta_{i}}} + I_{DS,final}$$

(2-15)

where  $A_i$ ,  $\tau_i$  and  $\beta_i$ , are fitting parameters corresponding respectively to the trap amplitude, time constant and stretching parameter ( $0 < \beta_i < 1$ ) of N detected charge-trappings. In the trapping (de-trapping) behavior,  $A_i > 0$  ( $A_i < 0$ ) corresponds to emission and  $A_i < 0$  ( $A_i > 0$ ) corresponds to the capture process. These parameters are numerically calculated and the plot obtained gives a time constant spectrum [20].

Figure 2-15: Comparison between the three data fitting solutions: though the pureexponential T1 process is correctly detected by all the fitting methods, the nonexponential T2D signal is properly detected only by stretched exponential fit, since its detection by polynomial fit and fixed-tau-multi-exponential fit is affected by spectral dispersion [20].

Another point that strongly affects the DCT results is the choice of the de-trapping bias point. The de-trapping bias point (or measuring-bias point) can be chosen in the linear region or in the saturation region, depending on the intended application of the device, i.e., in the linear region for switch operation mode and in the saturation region for RF operation mode.

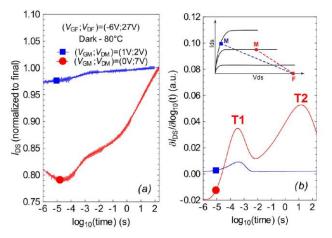

As shown by *Bisi et al.* [20] in Figure 2-16, the choice of the de-trapping bias point can impact the transient results. The device measured in the linear region presents one weak emission process, on the contrary the transient measured in the saturation region presents two emission processes. This difference in the measured peaks is due to the fact that the DUT in *Bisi et al.* [20] are sensitive principally to the threshold voltage. This threshold voltage shift impacts the value of the current more seriously in the saturation region than in the linear (ohmic) region.

Figure 2-16: (a) Drain current transients performed in the linear and saturation regions and (b) related differential signals: in good agreement with pulsed measurement, transients recorded in linear region detect only a weak emission process, while those recorded in saturation region reveal much higher current collapse and the presence of two emission processes-labeled T1 and T2 [20].

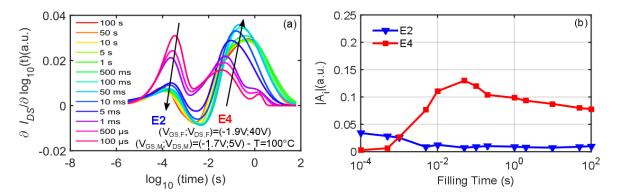

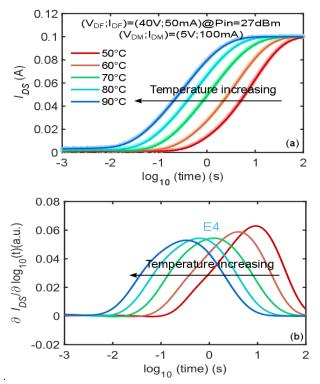

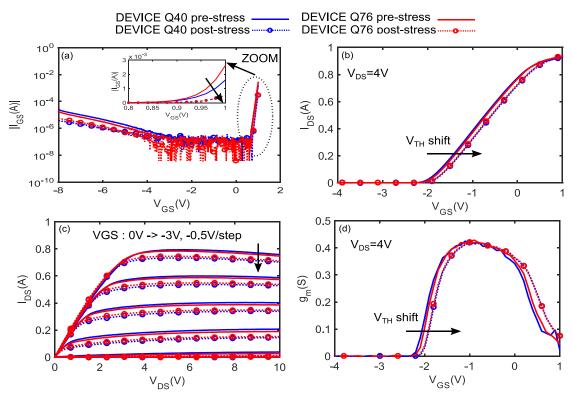

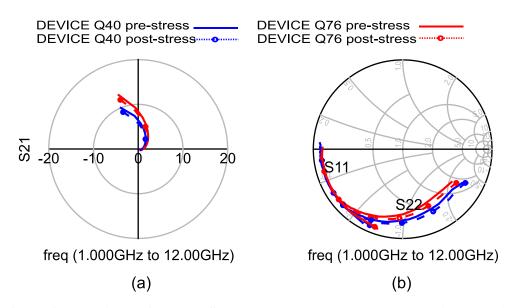

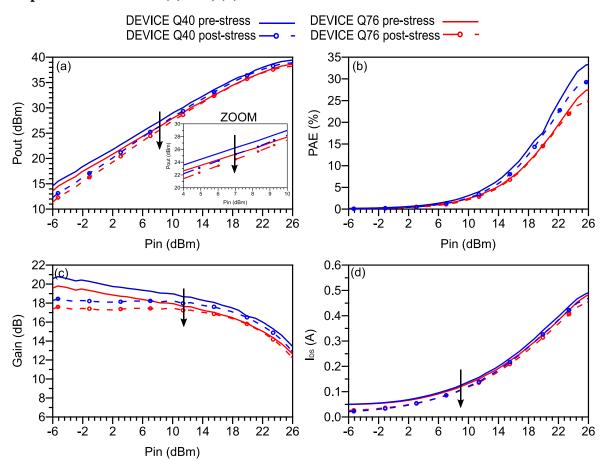

#### 2.3.2.3 Drain current transient results

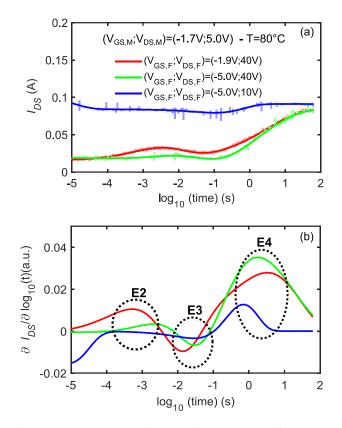

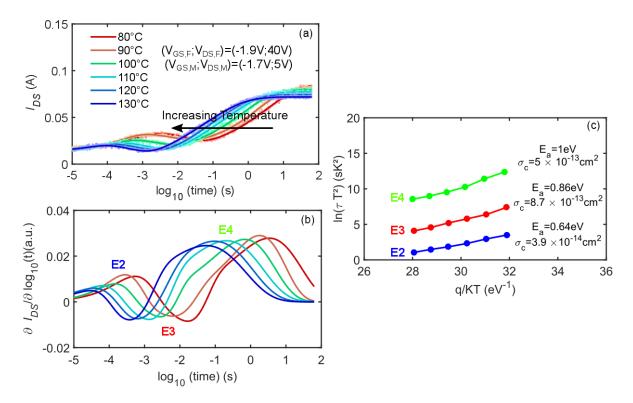

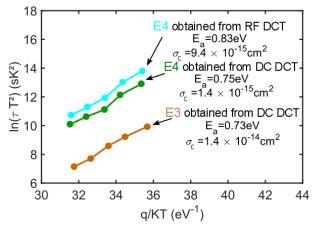

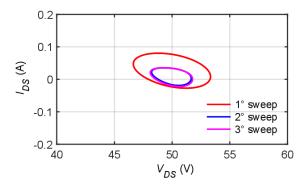

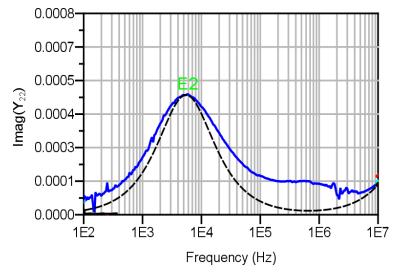

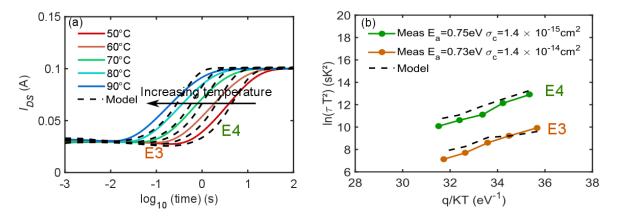

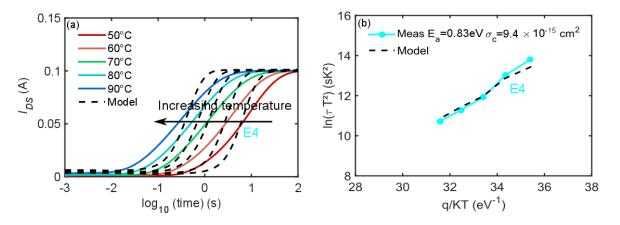

To achieve complementary information about the CC, DCT measurements are carried out, starting from three different filling bias conditions (V<sub>GS,F</sub>;V<sub>DS,F</sub>) (corresponding to the quiescent bias points used in the previously described pulsed I/V measurements). The results are shown in Figure 2-17. The OFF-state condition defined by  $(V_{GS,F};V_{DS,F})=(-5V;10V)$ induces negligible trapping. The emission process "E4" shows a high drain voltage dependence and clearly appears for the two following conditions: OFF-state defined by  $(V_{GS,F};V_{DS,F})=(-5V;40V)$  and SEMI-ON state defined by  $(V_{GS,F};V_{DS,F})=(-1.9V;40V)$ . Furthermore, the emission process "E2" and the capture process "E3" are mostly induced by the  $(V_{GS,F};V_{DS,F})=(-1.9V;40V)$  bias condition. In order to investigate the properties of traps for the SEMI-ON state, the DCT measurements are carried out at different temperatures. Therefore, the determined time constants with applied temperature correction (the determination of the thermal resistance is presented in Section 2.3.1.3) allows us to determine the activation energy  $E_A$  and the capture cross-section  $\sigma_c$  by using Equation (2-9). The time spectrum analysis and Arrhenius plot are represented in Figure 2-18(b) and Figure 2-18(c), respectively. The analysis for the SEMI-ON state is very interesting because it gives information about which traps will affect the class AB operation bias point of the transistor in a power amplifier. It can be noticed that all emission and capture processes "E2", "E3" and "E4" will take place in this class AB operation bias point. The Arrhenius plot analysis will be discussed in Section 2.4.

Figure 2-17: (a) DCT recorded and fitting for three different trapping conditions at 80°C. (b) Related time spectrum analysis (measured for a  $8x250x0.5 \ \mu\text{m}^2 \ AlGaN/GaN \ HEMT$ ).

Figure 2-18: (a) DCT recorded and fitting in SEMI-ON state condition for 80°C to 130°C temperature range, (b) related time spectrum analysis and (c) related Arrhenius plot.

# 2.3.2.4 Filling Time Dependence

To obtain more information on the dynamic behaviour of trap, the evolution of the "E2", "E3", and "E4" time spectrum results is reported versus the duration of the filling pulse in Figure 2-19(a). For this investigation, the trapping phenomena were induced by applying  $(V_{GS,F}, V_{DS,F}) = (-1.9V, 40V)$  at constant temperature (100°C). The width of filling time varies from 100 µs to 100 s. As described in Figure 2-19, the "E4" amplitude increases with time and saturates for a long pulse width. This behavior can be explained by two possible hypotheses. The first one is related to the presence of linear line defects, possibly due to dangling bonds along dislocation core sites. As described in [38], the concentration of the ionized defects has a logarithmic dependency on the duration of the filling pulse ( $t_p$ ) according to the following formula:

$$n_T(t_p) = c_n \tau N_T ln \left( 1 + \frac{t_p}{\tau} \right)$$

(2-16)

where  $c_n$ ,  $\tau$  and  $N_T$  respectively represent the capture probability, the characteristic time for the capture barrier build-up and the total concentration of the defects. Before the saturation of trap occupancy, the charge filling-time may produce a reduction in the capture rate due to the repulsive interaction between the free electrons and the increased negatively charged traps. The second one is related to the presence of acceptor-like traps, where the filling-time is associated with the emission of holes to the valence-band [39]. Simultaneously, the "E2" amplitude decreases when the pulse width increases up to a value which corresponds to the saturation of ionized trap "E4". The evolution of "E4" and "E2" amplitudes with the filling time suggests that there may exist an equilibrium between the ionization of the two trap states.

Figure 2-19: (a) E2 and E4 time spectrum analysis and (b) related amplitude processes dependency on the filling pulse duration.

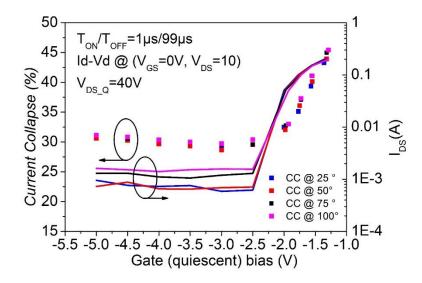

# 2.3.2.5 Capture Mechanism: Dependence on Gate Bias and Temperature

To further investigate the trapping behavior due to the RF working conditions, a complete analysis of the dependence of the CC on the gate quiescent bias point (swept from -5V to - 1.5V) is performed. It allows emulating the RF sweep condition (that corresponds to a constant DC value of V<sub>DS</sub> and an increase DC value of I<sub>DS</sub> with the increase of input power level). The results of this CC analysis (evaluated at V<sub>GS</sub>=0V and V<sub>DS</sub>=10V) are summarized in Figure 2-20. It shows that for the OFF-state (V<sub>GS</sub><-2,4V) the CC is constant and for the ON-state (V<sub>GS</sub>>-2,4V) the CC increases significantly with the drain current I<sub>DS</sub>. These variations cannot be due to the temperature increase when the drain current increases because Figure 2-20 proves that the CC does not depend on the temperature of the device. The CC increases for the ON-state can rather be attributed to the injection of hot electrons towards traps located in the buffer. This hypothesis is also proposed in [40], which demonstrated an increase of the amplitude of the process with an increase of the gate quiescent bias point. It was then demonstrated that the CC is strongly correlated to the value of the gate quiescent bias conditions in the ON- state.

Figure 2-20: Thermal dependence of CC and  $I_{DS}$  on the gate quiescent bias point for a 40 V drain quiescent bias point.

The CC measured with this method should possibly be attributed to the trap "E4" which makes a major contribution to the overall current collapse of the transient, as shown in Figure 2-17.

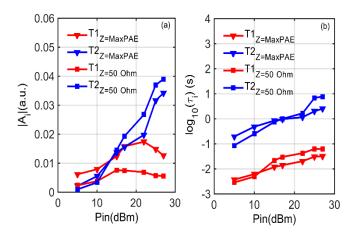

# 2.3.3 Nonlinear microwave drain current transient spectroscopy

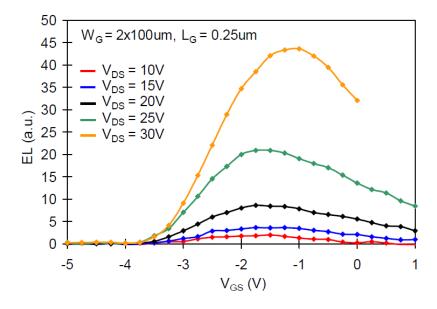

In the last years, many research groups [41]–[46] have shown that the nonlinear dynamics of the dispersion effects play a major role in the modification of the large-signal performances when the device is fed by modulated signals like RF pulses or telecommunications signals.

The time constants associated to these dynamic effects can cover a large range of values from tenths of ns to several minutes and are related to the characteristics of the RF signal in a very complex way.

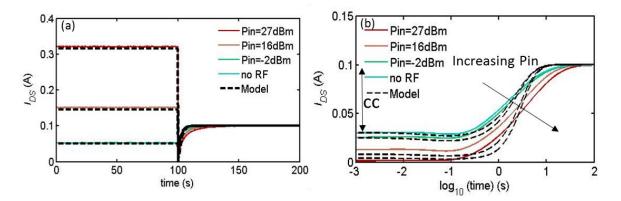

In order to get an insight into the impact of the trapping effects responsible for the modifications in the RF performance, a drain current analysis under RF operation mode is used. The analysis of the charge-trapping through the bias drain current monitoring during RF excitation is of fundamental importance as it provides information about the nonlinear dynamics of the trapping effects in the RF large-signal operation mode. Moreover, this information can be introduced into a CAD model to predict the RF dispersion of the devices.

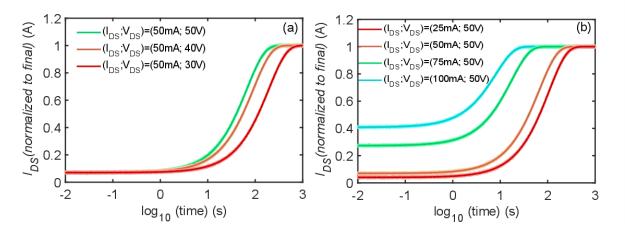

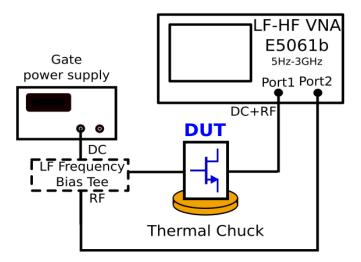

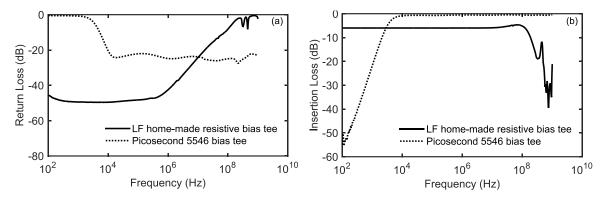

In this case, the previously developed trapping investigation techniques (such as pulsed I-V, drain current transient spectroscopy, and admittance spectroscopy) can give complementary information. All these methods suffer from the fact that the device does not work under real large-signal conditions. In this section, the RF trapping analysis is carried out with different combinations of DC and RF signal excitations to involve different trapping effects:

- Pulsed RF drain current transient measurement (DC continuous and RF pulse);

- Pulsed DC and RF drain current transient measurement (DC pulse and RF pulse);

- CW RF drain current transient measurement (DC continuous and CW RF).

#### 2.3.3.1 Pulsed RF drain current transient measurement

The first set of measurements used for the trapping investigation due to RF excitation is based on drain current evaluation when a RF pulse is applied. Thus, this trapping analysis technique can be applied to GaN-based HEMT for radar application.

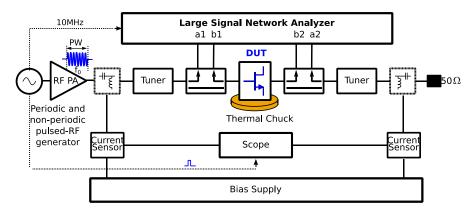

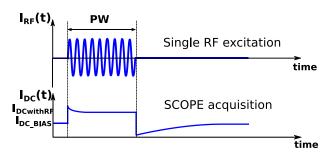

#### 2.3.3.1.1 Pulsed RF drain current transient set-up

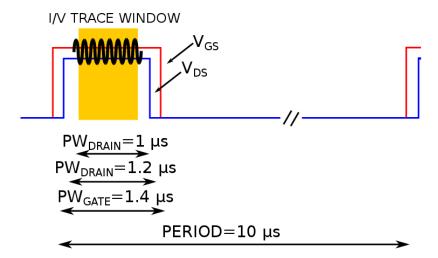

The experimental set-up used for both RF waveforms and drain current measurements is shown in Figure 2-21. In order to characterize the DUT under a single pulse measurement, the RF signal must have the shape shown in Figure 2-22. This pulse has a variable width (PW)

and magnitude. The total acquisition time, which allows monitoring the average drain current, has a range between ms to tenths of seconds in order to identify very slow de-trapping phenomena.

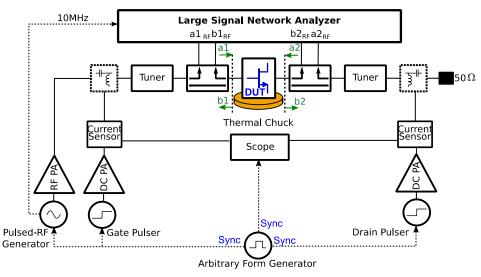

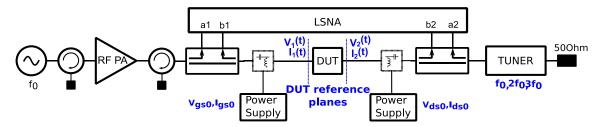

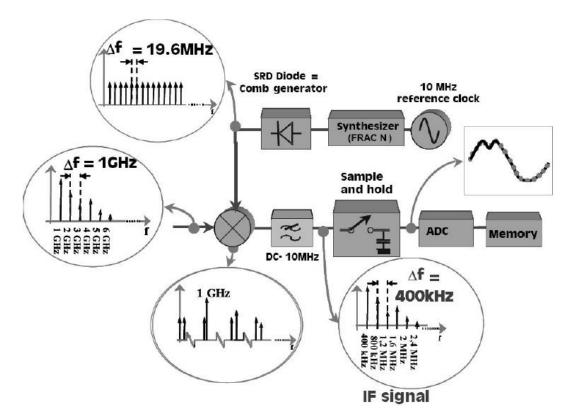

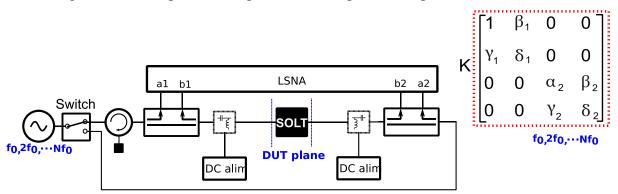

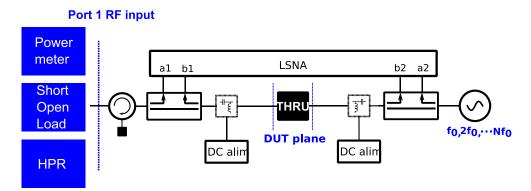

Figure 2-21: Block diagram of the RF experimental set-up based on LSNA system.

Moreover, the measurement algorithm requires the periodicity of the RF pulse which is contradictory with this approach. In order to overcome this difficulty, a two-step characterization protocol has been developed. It allows managing the large duration of the transients, which can run from seconds to hundreds of seconds.

Figure 2-22: Drain current measurement principle for RF trapping characterization for a single pulse RF excitation.

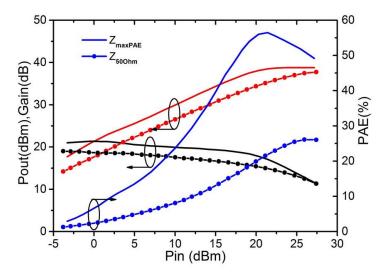

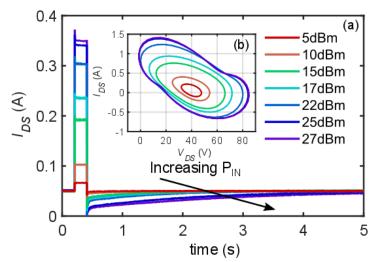

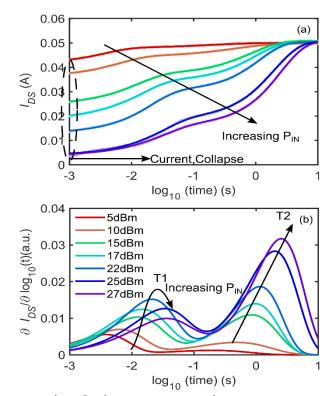

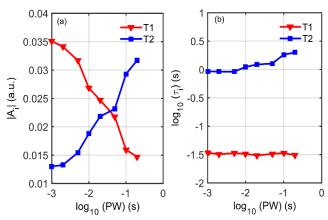

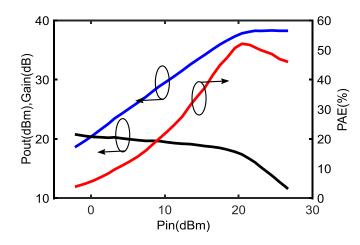

The first step of the measurement method consists in performing CW time-domain largesignal load-pull RF measurements using the LSNA. The details of LSNA set-up and calibration are depicted in Section 4.3.1. The time-domain RF voltages and currents and the CW power performance are obtained by the LSNA at the DUT planes. Of course, the output tuner allows modifying the RF loading of the device and thus the shapes of the drain and gate voltages and currents which could impact the trapping effects.

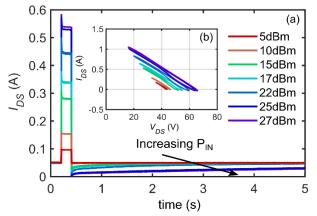

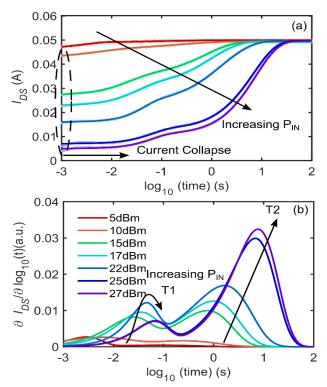

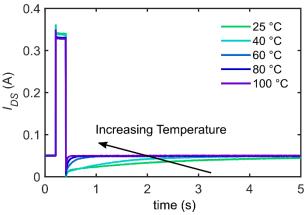

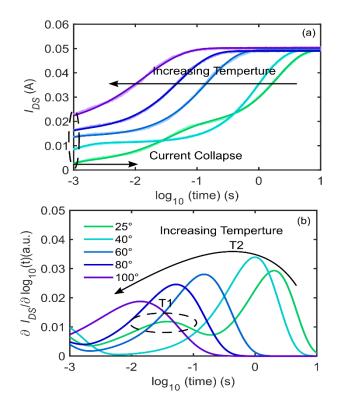

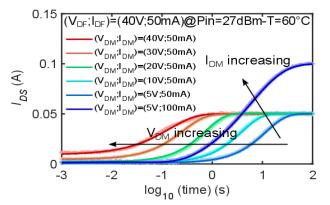

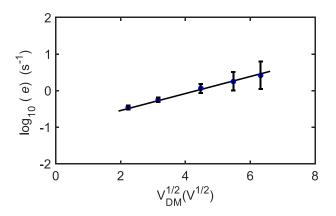

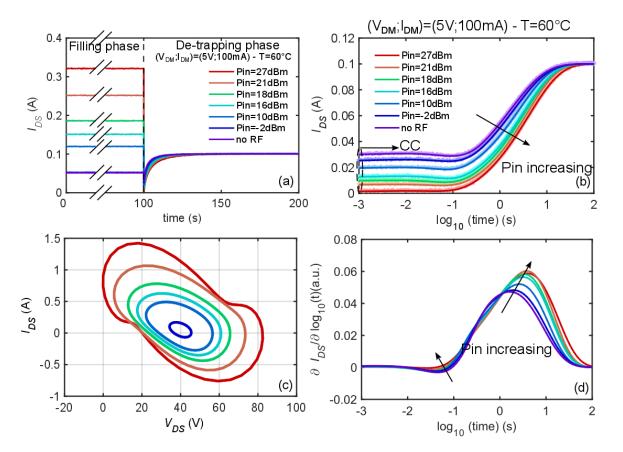

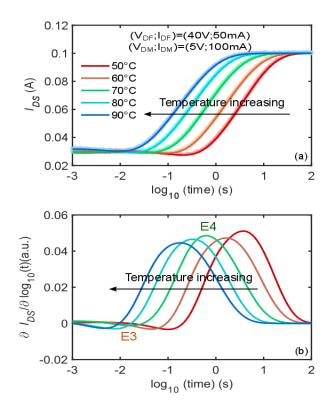

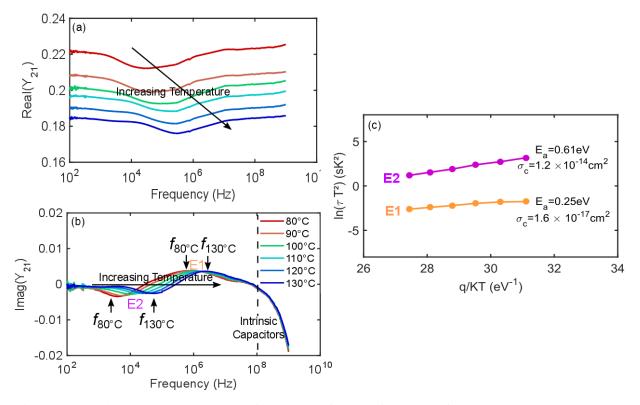

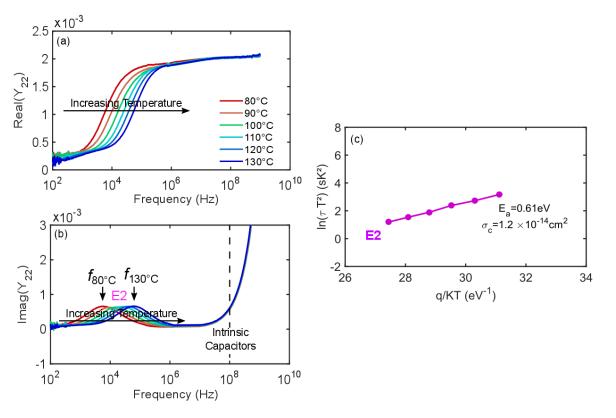

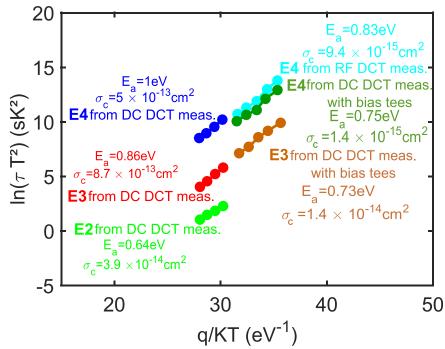

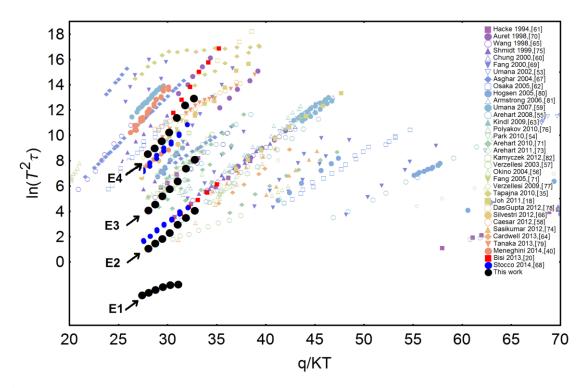

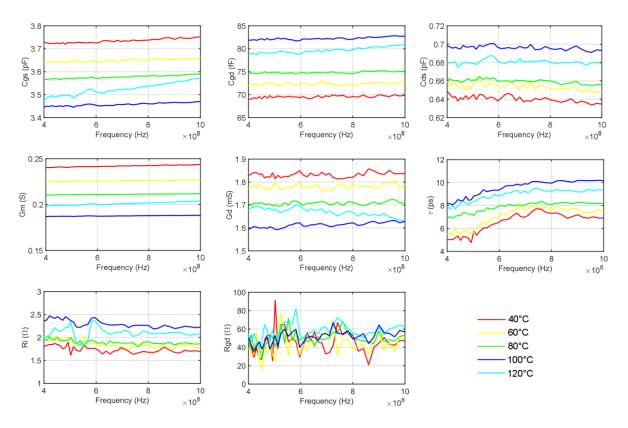

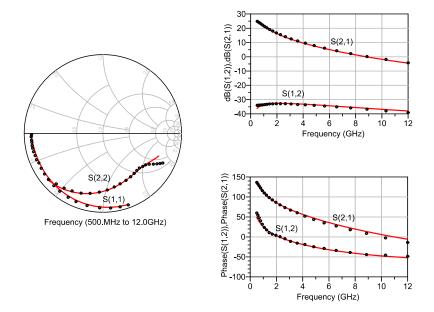

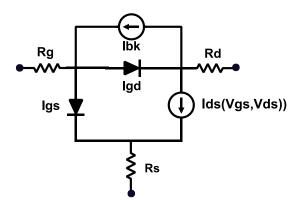

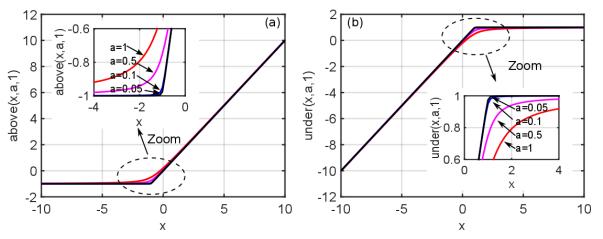

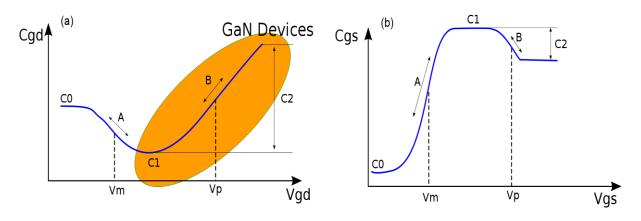

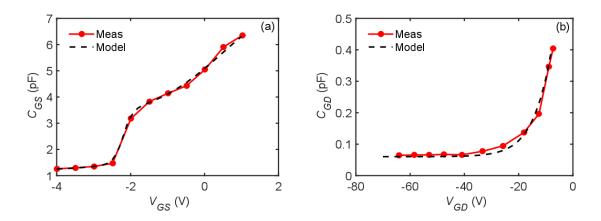

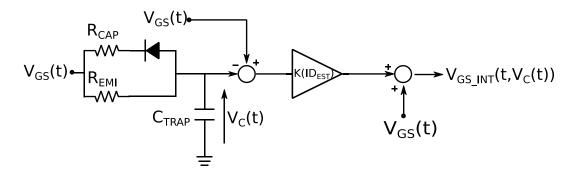

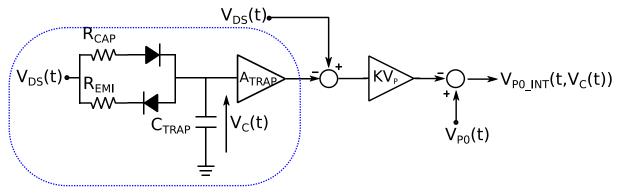

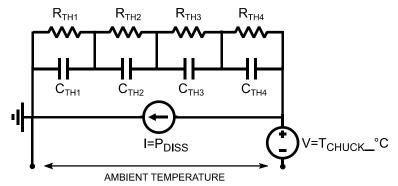

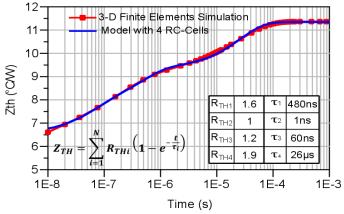

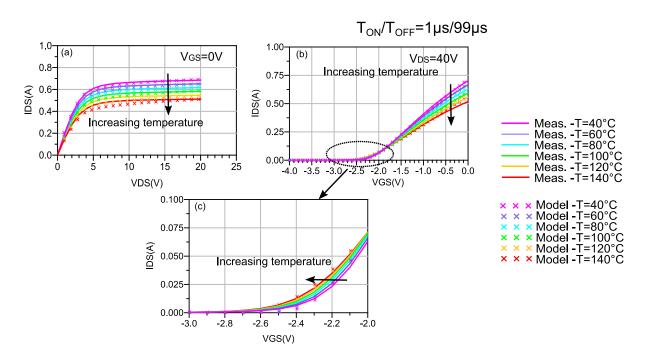

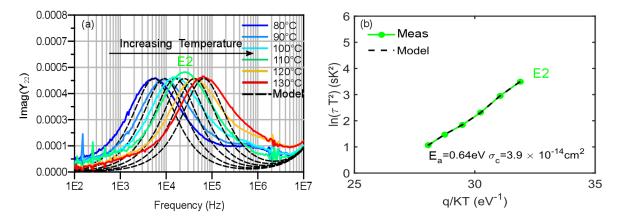

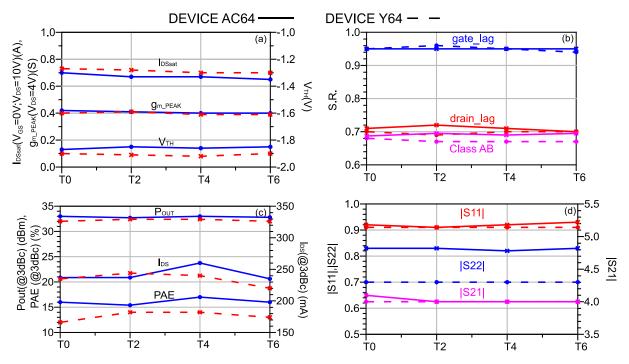

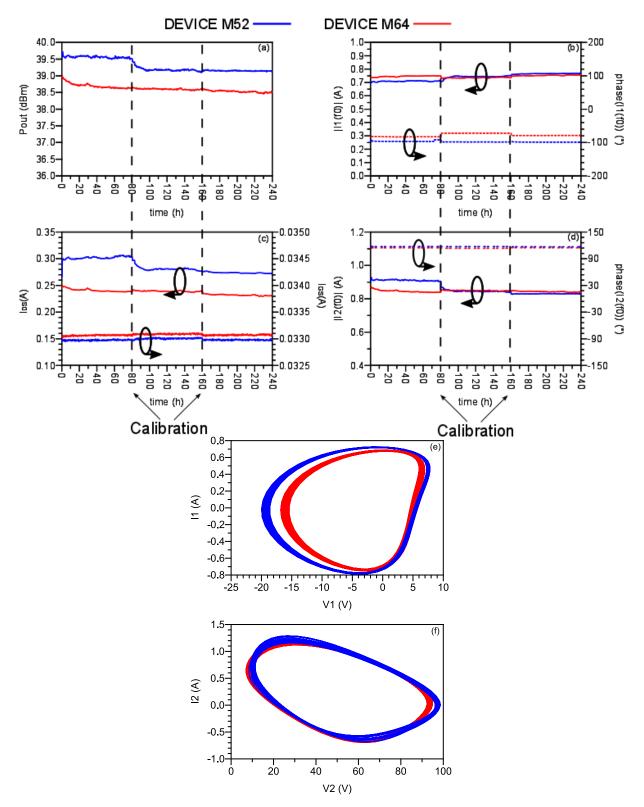

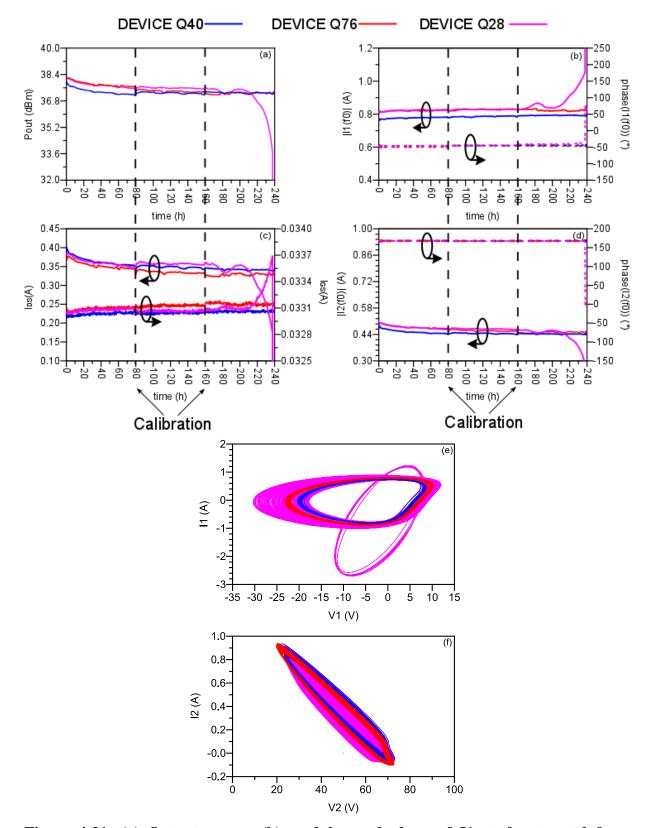

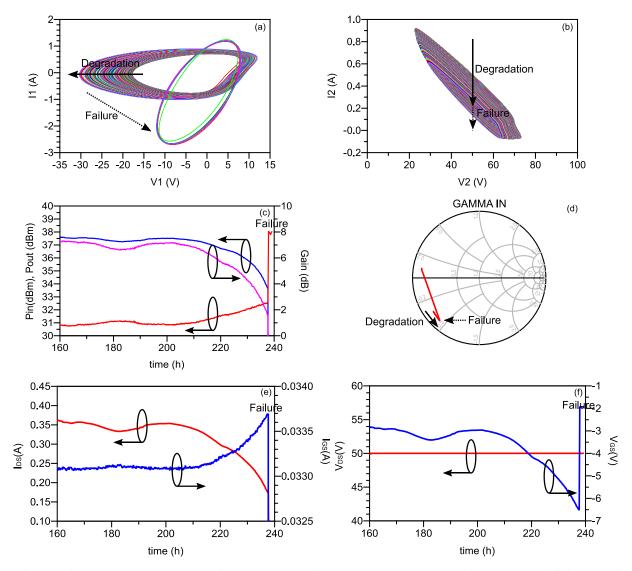

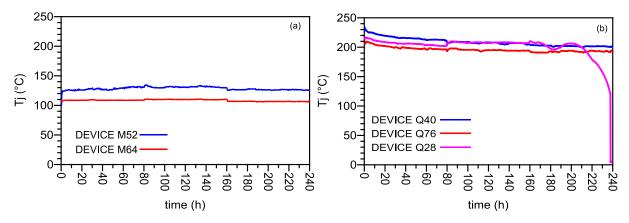

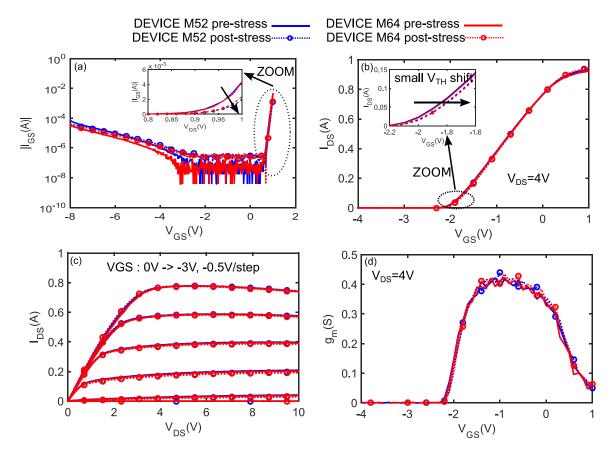

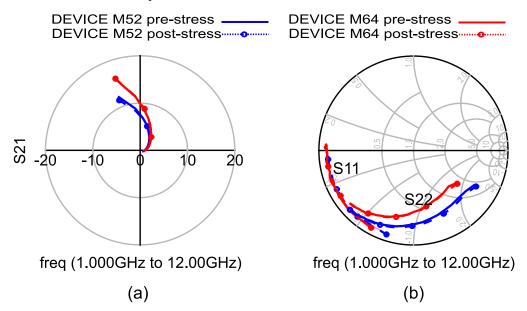

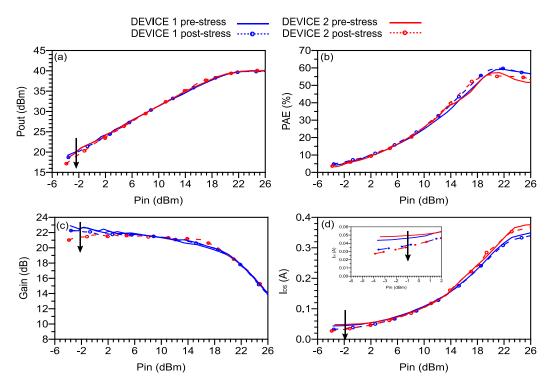

The second step consists in the measurement of the slow transient variations of the bias drain current when a single pulse large-signal excitation is applied or removed. Typical RF PWs range from 1 ms to 200 ms, which is sufficient to excite the traps, as the de-trapping time constants are much slower than the trapping ones. One assumes that the load conditions do