# Design of a virtual prototyping framework for composable heterogeneous systems

Cédric Ben Aoun

### ▶ To cite this version:

Cédric Ben Aoun. Design of a virtual prototyping framework for composable heterogeneous systems. Modeling and Simulation. Université Pierre et Marie Curie - Paris VI, 2017. English. NNT: 2017PA066160. tel-01646431

### HAL Id: tel-01646431 https://theses.hal.science/tel-01646431

Submitted on 23 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité

### Informatique

École doctorale Informatique, Télécommunication et Électronique (Paris)

Présentée par

#### Cédric BEN AOUN

Pour obtenir le grade de :

#### DOCTEUR de l'UNIVERSITÉ PIERRE ET MARIE CURIE

Sujet de la thèse :

Principes et réalisation d'un environnement de prototypage virtuel de systèmes hétérogènes composables

soutenue le 12 Juillet 2017 devant le jury composé de :

M. Frédéric Pétrot Rapporteur ENSIMAG-TIMA/SLS Mme. Cécile Belleudy Université de Nice-Sophia Antipolis Rapporteur M. Ian O'CONNOR Examinateur Ecole Centrale Lyon M. Matthieu Moy Examinateur Laboratoire Verimag M. Filipe VINCI DOS SANTOS Examinateur Ecole Centrale-Supelec Mme. Emmanuelle Encrenaz Université Pierre et Marie Curie Examinateur

Mme. Emmanuelle ENCRENAZ Examinateur Université Pierre et Marie Curie Mme. Marie-Minerve Louërat Examinateur Université Pierre et Marie Curie M. François Pêcheux Directeur de thèse Université Pierre et Marie Curie

### Abstract

Current and future microelectronics systems are more and more complex. In a aim to bridge the gap between the cyber/digital world and the physical world in which we evolve we observe the emergence of multi-disciplinary systems that interact more and more with their close surrounding environment. The conception of such systems requires the knowledge of multiple scientific disciplines (electrical, optical, thermal, mechanical, acoustic, chemical or biological) which tends to define them as heterogeneous systems. Designers of the upcoming digital-centric More-than-Moore systems are lacking a common design and simulation environment able to efficiently manage all the multi-disciplinary aspects of its components of various nature, which closely interact with each other.

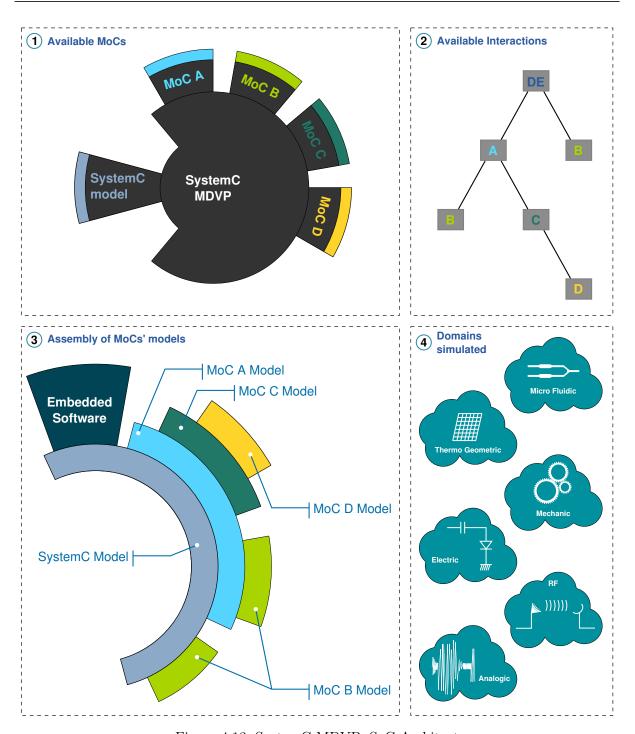

In this thesis we explore the possibilities of developing and deploying a unified SystemC-based design environment for virtual prototyping of heterogeneous systems. In order to overcome the challenges related to their specification and dimensioning this environment must be able to simulate a complex heterogeneous system as a whole, for which each component is described and solved using the most appropriate Model of Computation (MoC).

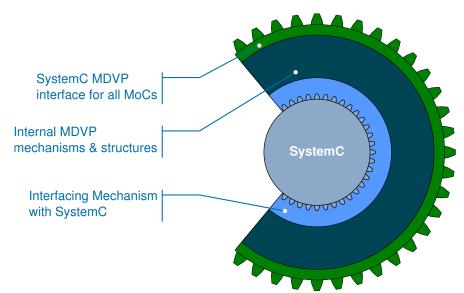

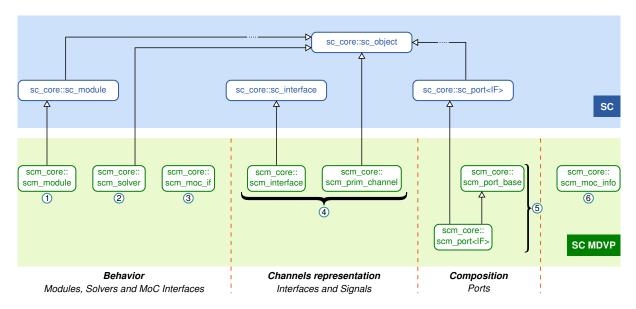

We propose a simulator prototype called SystemC Multi Disciplinary Virtual Prototyping (MDVP) which is implemented as an extension of SystemC. It follows a correct-by-construction approach, relies on a hierarchical heterogeneity representation and interaction mechanisms with master-slave semantics in order to model heterogeneous systems. Generic algorithms allow for the elaboration, simulation and monitoring of such systems.

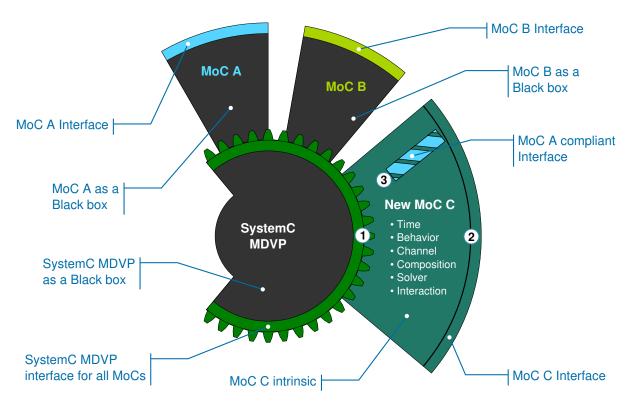

We also provide a methodology to incorporate new Models of Computation within the SystemC MDVP environment. We follow this methodology to integrate a Smoothed Particle Hydrodynamics (SPH) MoC that allows for the description of fluidic network. This MoC is then used to model a prototype of a point-of-care blood analysis system.

Eventually, we realized a case study of a passive RFID reading system that requires several interacting MoCs in order to be modeled. We compare the simulation results with measures acquired on a real physical prototype of a passive RFID reading system.

### Résumé

Les systèmes électroniques d'aujourd'hui et de demain sont de plus en plus complexes. Dans le but de rapprocher le monde numérique et le monde physique dans lequel nous évoluons, nous observons l'émergence de systèmes multidisciplinaires qui interagissent de plus en plus avec leur environnement proche. La conception de tels systèmes nécessite la connaissance de multiples disciplines scientifiques (électronique, optique, thermique, mécanique, acoustique, chimie ou biologie) ce qui tend à les définir comme étant des systèmes hétérogènes. Pour le développement de ces systèmes à venir, il manque aux concepteurs un environnement de conception et de simulation commun permettant de gérer efficacement la multidisciplinarité de ces composants de natures variées qui interagissent fortement les uns avec les autres.

Dans cette thèse nous explorons la possibilité de développer et déployer un environnement de conception unifié, basé sur SystemC, pour le prototypage virtuel de systèmes hétérogènes. Afin de surpasser les contraintes liées à leur spécification et dimensionnement, cet environnement doit pouvoir simuler un système hétérogène dans son ensemble, dans lequel chaque composant est décrit et résolu en utilisant le Modèle de Calcul (MoC) le plus approprié.

Nous proposons un prototype de simulateur, appelé SystemC Multi Disciplinary Virtual Prototyping (MDVP), qui est implémenté comme une extension de SystemC. Il suit une approche correcte-par-construction, repose sur une représentation hiérarchique de l'hétérogénéité et sur un mécanisme d'interaction basé sur des sémantiques maitre-esclave afin de modéliser les systèmes hétérogènes. Des algorithmes génériques permettent l'élaboration, la simulation et le monitoring de tels systèmes.

Nous proposons également une méthodologie afin d'incorporer de nouveaux Modèles de Calcul au sein de l'environnement SystemC MDVP. Cette méthodologie est suivie dans le but d'ajouter à SystemC MDVP le MoC Smoothed Particle Hydrodynamics (SPH) qui permet la description de réseaux fluidique. Ce MoC est ensuite utilisé pour modéliser un prototype de dispositif permettant l'analyse de sang sur un lieu d'intervention.

Nous avons finalement réalisé un cas d'étude portant sur un système RFID passif qui nécessite, afin d'être modélisé, l'utilisation de plusieurs MoCs interagissant entre eux. Les résultats obtenus en simulation sont comparés avec des mesures acquises sur un vrai prototype physique.

# Contents

| Li | st of                     | Figures                                                                                                                                       | ΧI                                                       |  |  |

|----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| Li | List of Tables XIII       |                                                                                                                                               |                                                          |  |  |

| Li | st of                     | Algorithms                                                                                                                                    | $\mathbf{V}$                                             |  |  |

| Li | st of                     | Listings                                                                                                                                      | Ή                                                        |  |  |

| 1  | Intr<br>1.1<br>1.2        | Context                                                                                                                                       | 1<br>2<br>5                                              |  |  |

| 2  | 2.1<br>2.2<br>2.3<br>2.4  | Contributions                                                                                                                                 | 7<br>8<br>8<br>8<br>9<br>9<br>10<br>10                   |  |  |

| 3  | Rela<br>3.1<br>3.2<br>3.3 | Introduction                                                                                                                                  | 13<br>14<br>14<br>16<br>16<br>17<br>17<br>18<br>19<br>20 |  |  |

|    | 3.5                       | 3.4.1 SystemC-A 3.4.2 SystemC-H 3.4.3 HetSC 3.4.4 SystemC AMS Multi Disciplinary Monitoring Mechanism 3.5.1 Aspect-Oriented Programming (AOP) | 22<br>23<br>23<br>23<br>25<br>26<br>28                   |  |  |

|    | 3.6                       |                                                                                                                                               | 28                                                       |  |  |

| 4 | Sys     | temC MDVP: Principles 3                          |

|---|---------|--------------------------------------------------|

|   | 4.1     | Introduction                                     |

|   | 4.2     | Models of Computation                            |

|   |         | 4.2.1 Discrete Event (DE)                        |

|   |         | 4.2.2 Timed Data Flow (TDF)                      |

|   |         | 4.2.3 Bond Graph (BG)                            |

|   |         | 4.2.4 Electrical Network (EN)                    |

|   |         | 4.2.5 Abstract representation of a MoC           |

|   | 4.3     | Interaction Mechanism                            |

|   |         |                                                  |

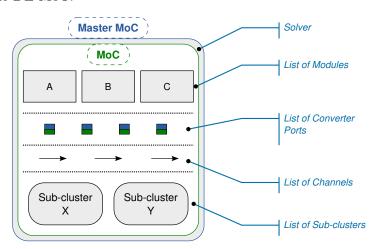

|   | 4.4     | MDVP Hierarchical Approach                       |

|   | 4.5     | User Profiles                                    |

|   |         | 4.5.1 Simulator Architect                        |

|   |         | 4.5.2 MoC Architect                              |

|   |         | 4.5.3 SoC Architect                              |

|   | 4.6     | Conclusion                                       |

| 5 | Sys     | temC MDVP: Implementation 5                      |

|   | 5.1     | Introduction                                     |

|   | 5.2     | SystemC MDVP Kernel Representation               |

|   |         | 5.2.1 SystemC MDVP MoC Abstraction               |

|   |         | 5.2.2 SystemC MDVP core classes                  |

|   | 5.3     | Elaboration Phase                                |

|   | 0.0     | 5.3.1 Composability / Static Analysis Sub-phase  |

|   |         | 5.3.2 Clustering Sub-phase                       |

|   |         | 5.3.3 Solver Instantiation Sub-phase             |

|   |         | 5.3.4 Basic Behavior Block Elaboration Sub-phase |

|   |         | 5.3.5 Port and Channel Elaboration Sub-phase     |

|   |         |                                                  |

|   | F 4     |                                                  |

|   | 5.4     | Simulation Phase                                 |

|   |         | 5.4.1 Simulation Mechanism                       |

|   |         | 5.4.2 Simulation Opportunities                   |

|   | 5.5     | Conclusion                                       |

| 6 | Sys     | temC MDVP: Monitoring 8                          |

|   | 6.1     | Introduction                                     |

|   | 6.2     | Principles                                       |

|   |         | 6.2.1 SystemC Monitoring                         |

|   |         | 6.2.2 SystemC MDVP Monitoring                    |

|   | 6.3     | Monitoring Mechanism                             |

|   |         | 6.3.1 Monitor Handler Instantiation              |

|   |         | 6.3.2 Monitor Slot Instantiation                 |

|   |         | 6.3.3 Initialization                             |

|   |         | 6.3.4 kernel Routine                             |

|   |         | 6.3.5 End of Simulation                          |

|   | 6.4     | Conclusion                                       |

|   |         |                                                  |

| 7 | Nev 7.1 | v MoC Integration Methodology Introduction       |

|   | 7.1     | New MoC integration methodology                  |

|   | 1.4     | 9                                                |

|   |         | J 1                                              |

|   |         | 7.2.2 Implementation Step                        |

|   |         | 7.2.3 Interaction Step                           |

|    | 7.3    | Application to SPH MoC       | 108 |

|----|--------|------------------------------|-----|

|    |        | 7.3.1 Interfacing Step       | 109 |

|    |        | 7.3.2 Implementation Step    | 110 |

|    |        | 7.3.3 Interaction Step       | 114 |

|    | 7.4    | Conclusion                   | 114 |

| 8  | Vali   | dation Case Studies          | 117 |

|    | 8.1    | Introduction                 | 118 |

|    | 8.2    | Application Based on SPH     |     |

|    |        |                              | 118 |

|    |        | 8.2.2 Results                | 120 |

|    | 8.3    | Application based on RFID    | 124 |

|    |        | 8.3.1 Case Study Description | 124 |

|    |        | 8.3.2 Results                | 129 |

|    | 8.4    | Conclusion                   | 135 |

| 9  | Con    | aclusion                     | 137 |

|    | 9.1    | Conclusion                   | 138 |

|    | 9.2    |                              | 140 |

| Ρι | ıblica | ations                       | 143 |

| Bi | bliog  | graphy                       | 151 |

# List of Figures

| 1.1<br>1.2<br>1.3                                           | Exploded view of an Apple Watch                                                                                                 |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8        | Hierarchical Modeling in Ptolemy II                                                                                             |

|                                                             | Running Example: System on Chip representing a 3-axis vibration sensor.  Simple model described with DE MoC                     |

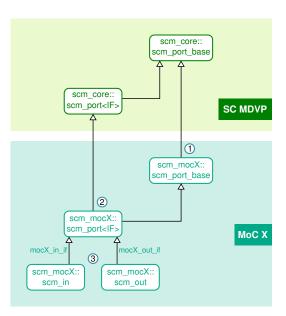

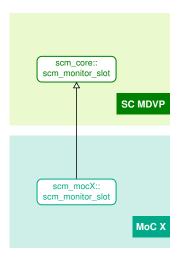

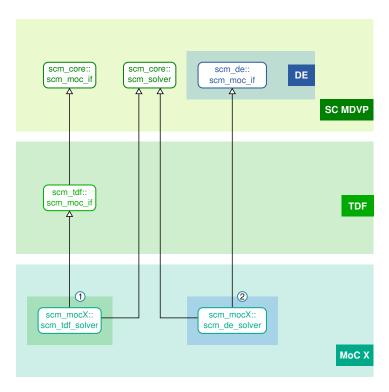

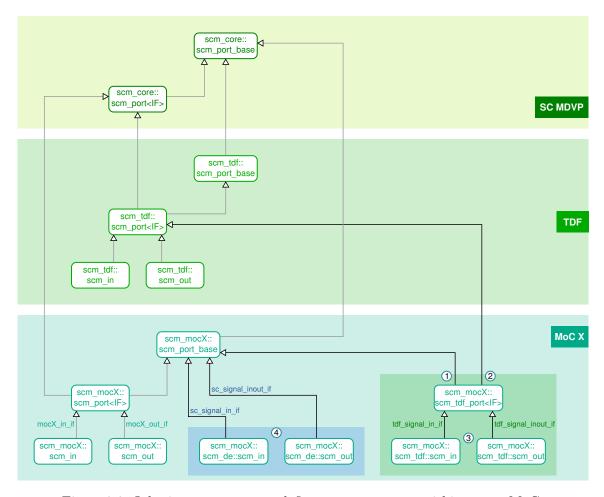

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | SystemC MDVP base classes to abstract a MoC                                                                                     |

| 5.11                                                        | SystemC MDVP kernel simulation phases. 75 Running Example: simulation process. 76 Activity Diagram of a roll back algorithm. 77 |

|      |                                                                                     | 78<br>79 |

|------|-------------------------------------------------------------------------------------|----------|

| 5.14 | Activity Diagram of a multiple execution algorithm.                                 | 78       |

| 6.1  |                                                                                     | 83       |

| 6.2  | 0 1                                                                                 | 84       |

| 6.3  |                                                                                     | 85       |

| 6.4  |                                                                                     | 86       |

| 6.5  | ₹ · · · · · · · · · · · · · · · · · · ·                                             | 88       |

| 6.6  |                                                                                     | 94       |

| 6.7  |                                                                                     | 95       |

| 6.8  | Running Example: Simulation Traces for the Sensor X of the vibration sensor         | 97       |

| 7.1  | MoC Integration Process                                                             | 101      |

| 7.2  | Inheritance pattern to define behavior of a new MoC                                 | 02       |

| 7.3  | Inheritance pattern to define communication channel of a new MoC                    | 02       |

| 7.4  | Inheritance pattern to define composition mechanism of a new MoC                    | 103      |

| 7.5  | Inheritance pattern to define monitoring of a new MoC                               | 104      |

| 7.6  | Inheritance pattern to define an interface solver within a new MoC                  | 106      |

| 7.7  | Inheritance pattern to define converter ports within a new MoC                      | 107      |

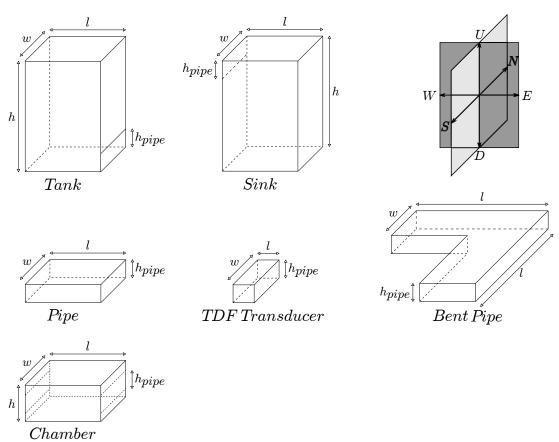

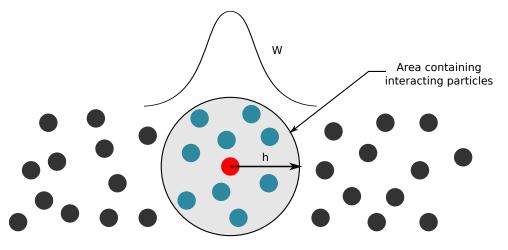

| 7.8  | SPH modeling primitives                                                             | 109      |

| 7.9  |                                                                                     | 110      |

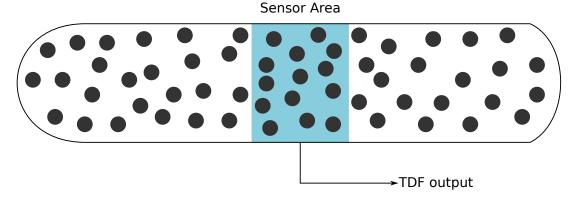

| 7.10 | SPH – TDF transducer                                                                | 14       |

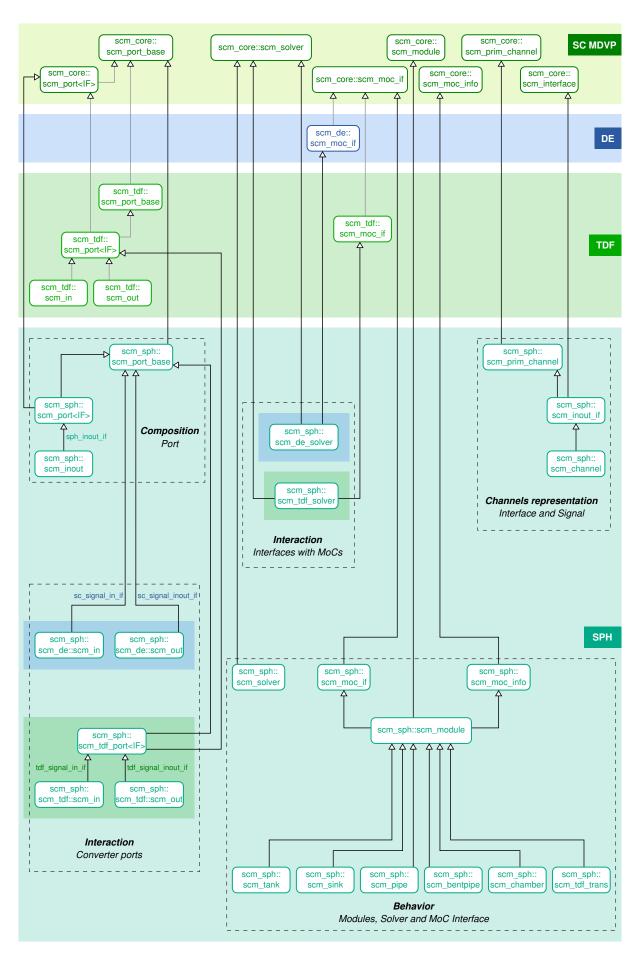

| 7.11 | SPH MoC inheritance diagram                                                         | 116      |

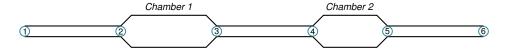

| 8.1  | Micro-fluidic Network                                                               | 119      |

| 8.2  | SPH micro-fluidic chip                                                              | 120      |

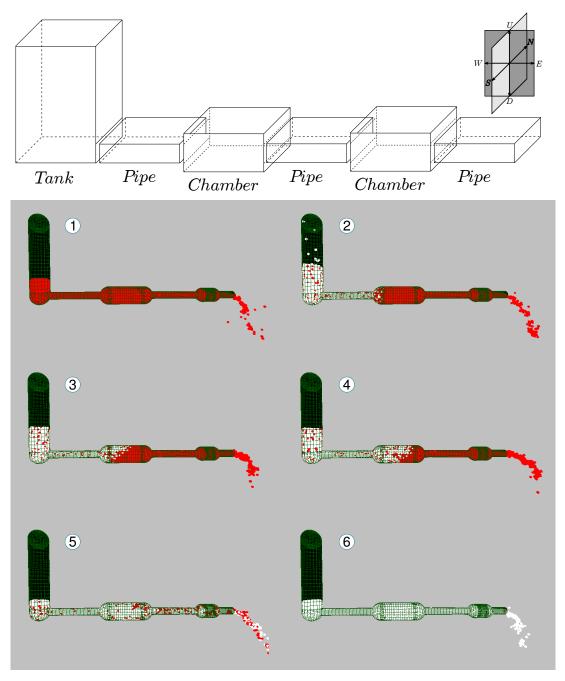

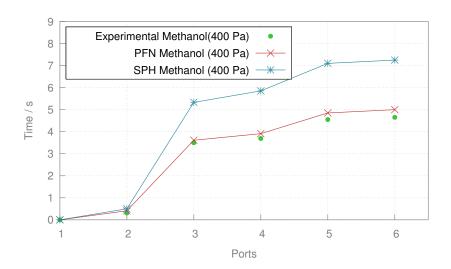

| 8.3  | Experimental, PFN and SPH results for constant flow                                 | 121      |

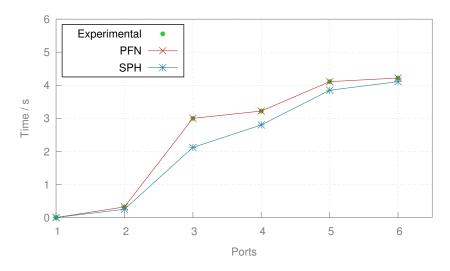

| 8.4  | Experimental, PFN and SPH results for pressure at 200 Pa                            | 122      |

| 8.5  | Experimental, PFN and SPH results for pressure at 400 Pa                            | 122      |

| 8.6  | Experimental, PFN and SPH results for Methanol at 400 Pa                            | 123      |

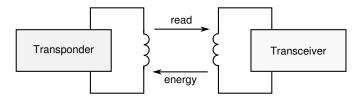

| 8.7  | A passive Radio Frequency Identification (RFID) system                              | 125      |

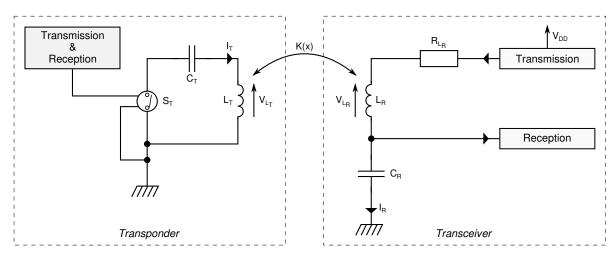

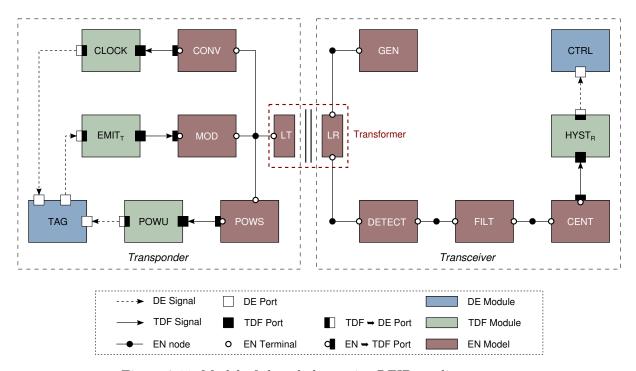

| 8.8  | Simple representation of the RFID system modeled                                    | 126      |

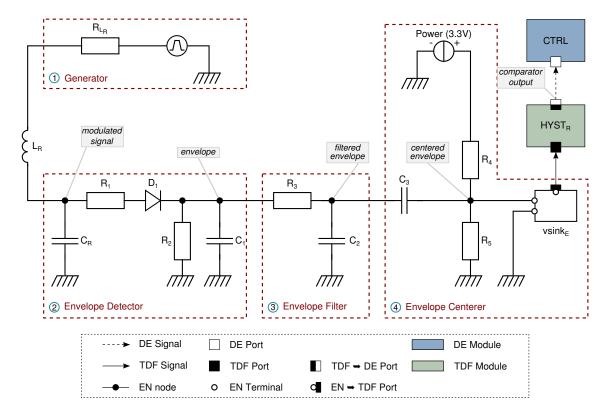

| 8.9  | Detailed representation of the RFID transceiver modeled                             | ١27      |

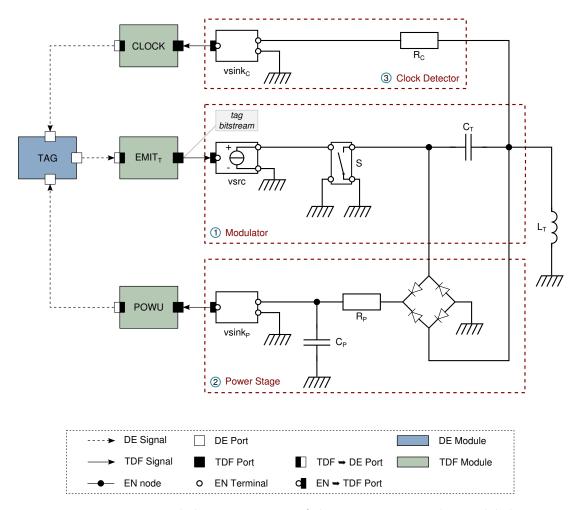

| 8.10 | Detailed representation of the RFID transponder modeled                             | 128      |

| 8.11 | Model of the whole passive RFID reading system                                      | 129      |

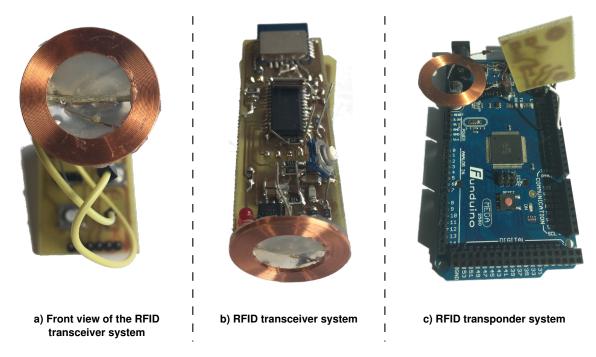

| 8.12 | Existing physical RFID tag reader                                                   | 130      |

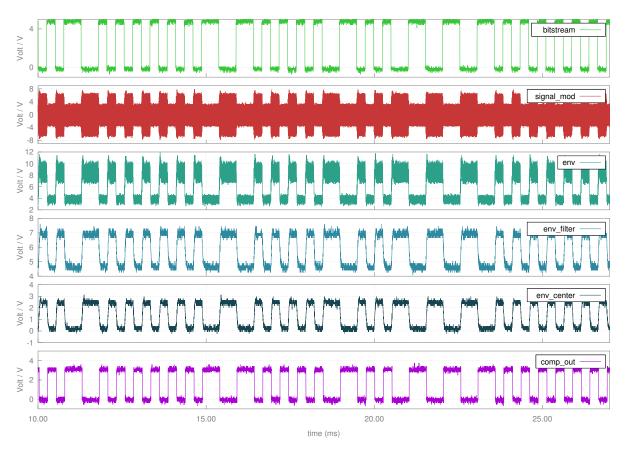

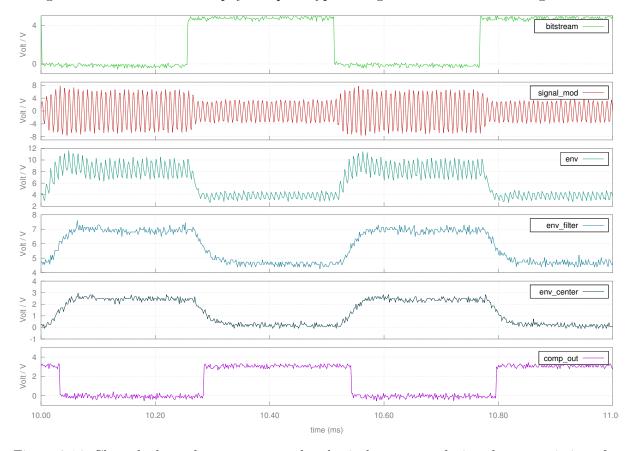

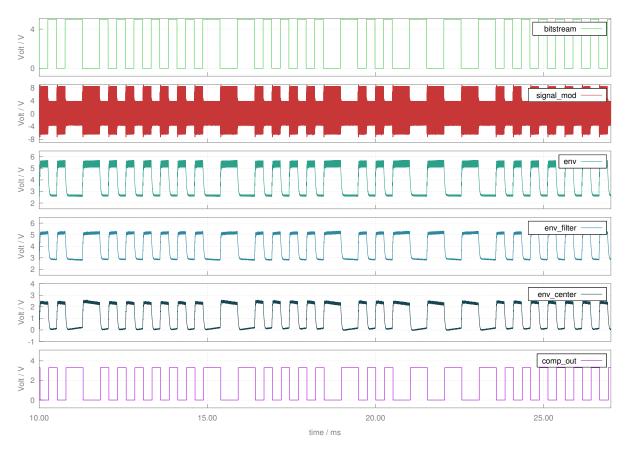

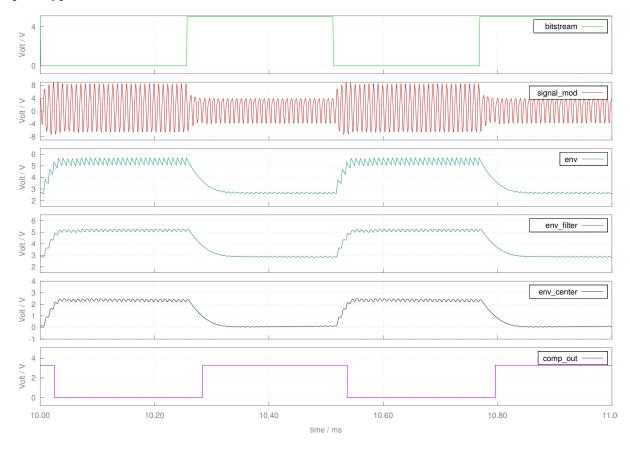

| 8.13 | Measures on the physical prototype during the transmission of a tag marker 1        | 132      |

| 8.14 | Closer look on the measures on the physical prototype during the transmission of a  |          |

|      | tag marker                                                                          | 132      |

| 8.15 | Simulation results for the transmission of a tag marker with the virtual RFID       |          |

|      | prototype                                                                           | 133      |

| 8.16 | Closer look on the simulation results for the transmission of a tag marker with the |          |

|      | virtual RFID prototype                                                              | 133      |

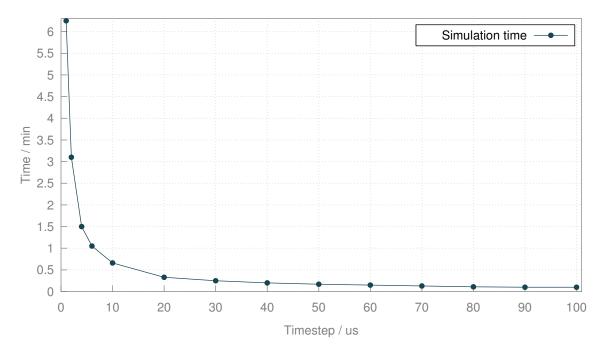

| 8.17 | Simulation time to emit a RFID tag depending of the simulation timestep 1           | 134      |

# List of Tables

| 5.1 | Dictionary of solvers available for the clusters hierarchy shown in Figure 5.6 | 67  |

|-----|--------------------------------------------------------------------------------|-----|

| 8.1 | Modeling and Simulation times                                                  | 124 |

| 8.2 | Parameters values associated with the circuit shown in Figure 8.9              | 126 |

| 8.3 | Parameters values associated with the circuit shown in Figure 8.10             | 127 |

| 8.4 | Simulation time of the passive RFID reading system                             | 135 |

# $List\ of\ Algorithms$

| 5.1 | Recursive clustering algorithm                      |

|-----|-----------------------------------------------------|

| 5.2 | Recursive solver instantiation algorithm            |

| 5.3 | Elaboration of MoC interfaces algorithm             |

| 5.4 | Elaboration of ports and channels algorithm         |

| 5.5 | Generic Elaboration Algorithm                       |

| 6.1 | Generic Algorithm to Instantiate Monitor Handlers   |

| 6.2 | Generic Recursive Algorithm to Create Monitor Slots |

| 6.3 | Generic Algorithm to Instantiate Monitor Slots      |

| 6.4 | Recursive Algorithm to Initialize the Monitor Slots |

| 7.1 | SPH Simulation Loop                                 |

# Listings

| 5.1 | Definition of physical types               | 60  |

|-----|--------------------------------------------|-----|

| 6.1 | End-user monitoring specification          | 91  |

| 7.1 | Code snippet of SPH primitives composition | 113 |

## Chapter

# Introduction

| 1.1 | Context             | 2 |

|-----|---------------------|---|

| 1.2 | Thesis Organization | 5 |

### 1.1 Context

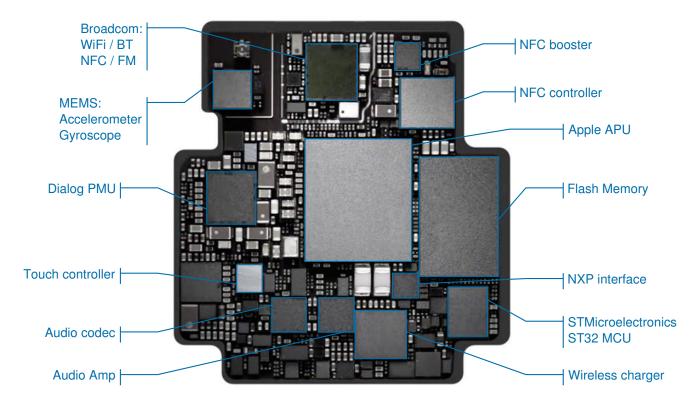

Nowadays, the design of new embedded systems relies on the sound assembly of different IPs, each IP being developed separately and independently. The conception of each of these IPs may involve different physical domains. Figure 1.1 represents an exploded view of an Apple Watch as an example of the IP assembling performed in current available devices. The variety of physical domains that may be involved is quite well-represented. Different kinds of sensors (force touch, optical pulse) are integrated in the system as well as analogical or electronic components (battery, wireless charging coil, antenna). Purely digital systems no longer exist.

Figure 1.1: Exploded view of an Apple Watch, source from [1].

If we take a closer look on the Apple Watch's chip, we notice that even the chip itself is no longer fully digital. The chip layout is illustrated in Figure 1.2; this figure highlights some of the components embedded in the chip. In addition to the digital components (processor, memory) and different controllers for the aforementioned sensors (which are also digital) we find non-digital components such as the wireless charger or several Micro-Electro-Mechanical Systems (MEMS) that act as accelerometer and gyroscope.

According to this example, design engineers who want to build tomorrow's more-than-Moore embedded systems must think, create and design differently than they do today. Electronic design automation tooling must evolve with the upcoming needs and even go so far as to anticipate them. Current and future microelectronics systems are increasingly complex and interact more and more with their close surrounding environment. The conception of such systems requires the knowledge of multiple scientific disciplines (electrical, optical, thermal, mechanical, acoustic,

Figure 1.2: Apple Watch chip's layout, adapted from [2, 3, 4].

chemical or biological).

The emergence of multi-disciplinary systems is the result of the desire to bridge the gap between the cyber/digital world and the physical world in which we evolve. This approach leads to the concept of Cyber-Physical Systems (CPS) [5] and Internet-of-Things (IoT) [6].

We are now witnessing the evolution of an ecosystem of billions of interconnected devices<sup>1</sup> [7]. These systems communicate, interact with and hence impact their environment in a multitude of ways. The use of sensors allows such devices to probe and interact with their immediate environment thus collecting information, whilst the role of actuators is to apply constraints and forces to the real world. Sensors and actuators act as the interface at the border of the physical and the cyber world.

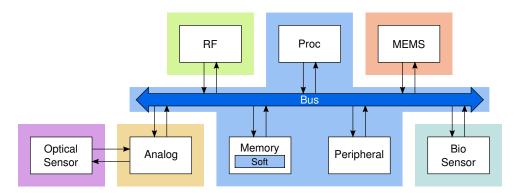

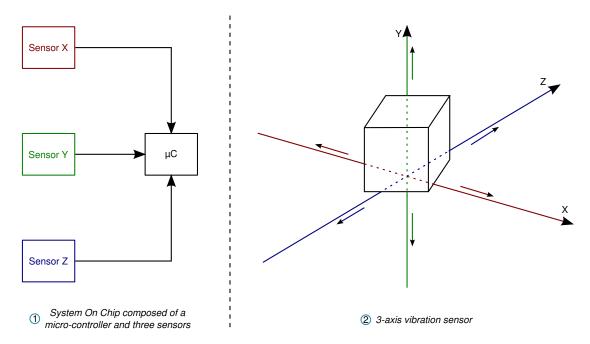

Figure 1.3 provides a generic representation of a System on Chip (SoC) and highlights several interacting disciplines that may be involved in the design of an embedded system. One can see that the SoC device embeds digital components (processor, memory, peripheral) as well as components from other engineering disciplines such as RF transceiver and sensors (MEMS, optical, biological). This figure illustrates how a system can interact with its environment.

New types of emerging applications requiring microelectronics that closely interact with the surrounding environment in different physical domains (optical, mechanical, acoustical, biological, etc.) are referred to as *heterogeneous systems*. They qualify as heterogeneous because

<sup>&</sup>lt;sup>1</sup>Gartner, Inc. forecasts that 6.4 billion connected things will be in use worldwide in 2016, up 30 percent from 2015, and will reach 20.8 billion by 2020. In 2016, 5.5 million new things will get connected every day.

Figure 1.3: System on Chip as a set of interacting disciplines.

they couple digital and physical elements. Moreover, they describe different semantics and time abstraction. Since these systems represent non-homogeneous applications, various physical modeling environments may be used to model and simulate them.

The design of these multi-disciplinary microelectronics-assisted systems is often an iterative process in which the individual parts for each physical domain are developed independently and then combined in the very last stage to realize the final product. Very often, design errors such as functional incorrectness, wrong interfaces, or non-compliance with the initial product specifications are identified too late in the design cycle. This leads to additional design spins and delayed schedules as a result of a necessary reimplementation which hampers the whole market introduction process. It is therefore important to allow the modeling and the simulation of such systems as a whole to truly appreciate their complexity before their expensive fabrication.

Clearly, the main issue is that a global system representation including all involved physical/engineering domains is missing, especially in the early design stages. In such a context, it would be highly beneficial to prove the correctness of the heterogeneous system architecture up-front and to have an accurate view of the way heterogeneous entities interact as a whole. This requires a modeling/design, simulation, and verification environment that can assist system designers to dimension, partition, and thus to "architect" such heterogeneous systems appropriately. Such a solution must be flexible and open in order to allow for the extension of the environment; extending the framework should not involve complex interfacing mechanisms with the existing infrastructure.

To meet these requirements, prior to constructing physical prototypes, virtual prototyping at a high level of abstraction becomes inevitable, especially for such systems which feature a tight coordination between the computational and physical elements. Virtual prototyping provides numerous functionalities and benefits when it comes to the design and conception of new systems. This mechanism consists in the creation of virtual models to describe a design, allowing for the performance of software simulation of the device under development [8, 9]. Virtual prototyping allows for architectural exploration with the possibility of studying several design alternatives quickly and easily. Furthermore, it provides the designer with the possibility to carry out performance analysis and early test design on the developed system, leading to the capacity

to endure testing and validation procedures usually not achieved with a real physical prototype platform due to the cost of such procedures.

Eventually, since virtual prototyping enables the simulation of heterogeneous systems in the early stage of development, it can enable the development of the software associated with the platform prior to the availability of a physical prototype.

This thesis is performed in the frame of the CATRENE European project - Heterogeneous INCEPTION (H-Inception) [10]. The main goal of this project is to develop and deploy a unified design environment for virtual prototyping of multi-domain microelectronics-assisted systems to overcome the challenges related to their specification, dimensioning and verification. This project aims to benefit the European industry in the production of their products with application in several domains such as automotive, wireless, avionics and biomedical areas.

### 1.2 Thesis Organization

After presenting, in Chapter 1, the context in which this work is performed, the document is organized as follows:

In Chapter 2, the challenges related to the simulation of heterogeneous systems are highlighted; they represent the different problem statements that need to be addressed. They cover a wide variety of issues ranging from the characterization of the simulation environment to the monitoring of such systems. Requirements that need to be met in order to ensure a correct simulation are introduced. The contributions brought together in the frame of this thesis, in order to address these challenges, will then be presented.

In Chapter 3, the state-of-the-art related to the simulation of heterogeneous systems is summarized. We present several approaches that address the challenges described in Chapter 2. We describe different frameworks and design environments which allow for the simulation of multi-physical systems. For each framework, the modeling and the behavior of the framework are discussed.

In Chapter 4, we introduce our solution for the simulation of heterogeneous systems. Our work leads to the conception of a new simulator prototype called SystemC MDVP. This chapter focuses on the principles that are the foundations of our framework. We present the different abstraction and representation defined within SystemC MDVP. We explain the hierarchical representation of the system we chose and the underlying semantics, which lead to an environment permitting the simulation of real software coupled with virtual hardware architecture and virtual physical models.

In Chapter 5, we present the implementation details underlying SystemC MDVP that support the principles introduced in Chapter 4. SystemC MDVP is implemented as an extension of SystemC which allows us to achieve the simulation of heterogeneous systems. This chapter presents the different data structures and generic algorithms developed within our framework.

Chapter 6 describes the mechanism defined within SystemC MDVP that allows for the monitoring of multi-disciplinary systems. We present an approach wherein we provide a unified access to the information through the whole system. Information related to digital or physical components of the heterogeneous system are addressed the same way. This chapter presents the principles and the implementation details underlying the monitoring mechanism of our framework.

In Chapter 7, we present a methodology to allow the addition of new MoCs within our virtual prototyping environment. This methodology relies on the principles defined within SystemC MDVP and described in Chapter 4. To support this methodology and our simulator, we present a new MoC called SPH. This MoC allows the modeling and the simulation of fluidic elements through the description of a fluidic network.

Chapter 8 presents two validation case studies to illustrate the possibilities offered by SystemC MDVP and support the principles underlying our framework. First, we describe a case study related to the MoC SPH where a fluidic network is described, simulated and then compared with other solutions. Second, we depict a complete passive RFID reading system involving several MoCs in order to realize its modeling. The RFID system is modeled, simulated and then compared to a real physical prototype of the passive RFID reading system.

Finally, by way of a conclusion, in Chapter 9 we resume the work presented and introduce perspectives on future work.

### Chapter

Contents

2.3

# Problem Statement

| 2.1 | Intr  | oduction                                          | 8 |

|-----|-------|---------------------------------------------------|---|

| 2.2 | Hete  | erogeneous Systems Virtual Prototyping Challenges | 8 |

|     | 2.2.1 | Smooth Management of Heterogeneity                | 8 |

|     | 2.2.2 | Sound Management of Interacting Entities          | 9 |

|     | 2.2.3 | Flexible Virtual Prototyping Environment          | 9 |

Contributions

10

**10**

### 2.1 Introduction

Current and future microelectronics systems are increasingly complex, and interact more and more with their immediate environment. These emerging systems are intrinsically complex in their development and require a lot of time and effort to achieve their conception.

Since the development of multi-disciplinary microelectronics assisted systems involves several disciplines, the individual parts are usually conceived independently and assembled in the final stage of the development process. In such a context, in order to truly appreciate the complexity of multi-disciplinary systems before their expensive fabrication, it is important to allow the modeling and the simulation of such systems as a whole.

With such an approach, we would benefit from an accurate view of a heterogeneous system including the manner in which heterogeneous entities interact with one another. In addition to this, a global system representation including all involved physical/engineering domains, especially in the early design stages, would be beneficial to prove the correctness of the heterogeneous system architecture up-front. In order to assist system designers in the design process of heterogeneous systems, i.e. to help them to dimension, partition and thus to "architect" these systems, a modeling/design, simulation and verification environment is needed.

The simulation of heterogeneous systems raises specific challenges that may be difficult to address due to their very nature. These challenges are presented in Section 2.2. To address them, Section 2.3 introduces the contributions presented in the framework of this thesis. Subsequently, Section 2.4 concludes this chapter and provides an overview of the challenges faced and the resulting contributions.

### 2.2 Heterogeneous Systems Virtual Prototyping Challenges

How does one simulate a heterogeneous system? The answer is not trivial. The heterogeneity aspect can be difficult to address due to the gap between the different disciplines involved in the design of heterogeneous systems (e.g. software engineering vs biological engineering).

We have identified several challenges which represent the different issues that may occur when dealing with the simulation of heterogeneous systems and the requirements induced by these issues.

### 2.2.1 Smooth Management of Heterogeneity

In the context of heterogeneous systems, one key aspect is to define what it is intended by the term *heterogeneous*. Heterogeneity can be defined as the use of several simulation tools, or the use

of different languages, semantics, disciplines, etc. In such a context, a clear definition of the term heterogeneity and the composition of this heterogeneity are required.

These components (entity), which defined the heterogeneity, must be well-defined, not only from the simulator viewpoint, but also from the user viewpoint. The simulator requires a well-known distinction between components in order to correctly simulate each component within its associated environment. The user should have access to well-defined components in order to correctly and easily design the system he wants to simulate. Our approach relies on the definition of these heterogeneous entities by means of interacting Models of Computation (MoCs). We must therefore provide a well-defined interface for these MoCs to interact with the kernel, without neglecting the user's interface.

### 2.2.2 Sound Management of Interacting Entities

Once heterogeneity has been clearly defined, one of the key challenges lies in the interaction between the entities that define this heterogeneity and their composition. They usually express different semantics, with potentially different time abstraction. Incompatibility between physical domains or design errors should be detected by the simulator. It is necessary to be able to identify when two components are connected together when they should not be.

As such, we need a well-defined interaction mechanism between different heterogeneous entities. It should express the constraints associated with each entity and, consequently, it should enable and define their composition. Interaction is not limited to the composition of the heterogeneous entities; it is also required to be able to express semantics information if needed. This information is associated with the data handled within each entity (such as dimension or unit).

### 2.2.3 Flexible Virtual Prototyping Environment

Since multi-physical systems represent non-homogeneous applications, various physical modeling environments may be used to model and simulate them. Multiple approaches exist to perform simulation of heterogeneous systems, from a global simulation framework to the use of multiple specific simulation tools dedicated to each discipline. This situation can be simply summarized as the choice between a unified, unique simulation environment and a co-simulation environment.

Both approaches have their pros and cons, but we believe performing the simulation of the whole system within the same simulation environment allows us to truly appreciate the dependencies and all the interactions involved in the system. It is crucial that each discipline take part in the design exploration phase of the system. Consequently we have to set up an environment which enables the coupling of all the disciplines within the same simulation framework.

In the scope of heterogeneous systems simulation, we have to provide a highly flexible

framework. Flexibility is understood, in this work, in the sense that the simulator must be able to evolve and to simulate any heterogeneous system. Naturally, we want to perform the simulation of a system which involves several heterogeneous entities, therefore we cannot afford to provide a rigid, static simulator.

Heterogeneous entities which may take part in the conception of a multi-physical system are numerous, ranging from biological to optical through mechanical, etc., without forgetting the different semantics or time abstraction associated. It seems unlikely that we would be able to define every existing heterogeneous entity and, furthermore, to define those which do not yet exist. In consequence, heterogeneous simulation requires a way to easily integrate new heterogeneous entities into the simulator, in a convenient manner.

### 2.2.4 Multi-Disciplinary Monitoring

In the context of systems simulation and, more specifically, in the case of heterogeneous systems, the monitoring mechanism constitutes an important feature of the simulator. This mechanism must adapt to, and fit, the different digital/physical parts involved in the design. With the term *monitoring*, we refer to a mechanism which aims to observe and record information about the signals of a system, independently of the outcome of this observation (tracing, profiling, etc.).

The information associated with a digital component (such as a micro-controller) is different from that associated with an analog component (such as a thermal sensor). The relevant data may vary from one domain to another and the way to express them may also differ. Thus, setting up the monitoring mechanism of such systems represents a challenge in itself since it is dependent on the domain modeled, and yet it must remain a generic mechanism in order to manage all the different disciplines and ensure the flexibility of the simulator.

### 2.3 Contributions

The simulation of multi-disciplinary systems is not trivial. Bringing together different physical/engineering disciplines with different semantics is rather difficult. Designing a system that integrates digital and analog parts becomes a complicated process, where heterogeneity represents a key issue.

The objective of this thesis is to explore the possibilities of the simulation and the composition of digital centric multi-disciplinary systems. The contributions brought in the framework of this work are listed below.

• Creation of a reliable framework for the virtual prototyping of heterogeneous systems (SystemC MDVP) based on interoperable Models of Computation (MoCs).

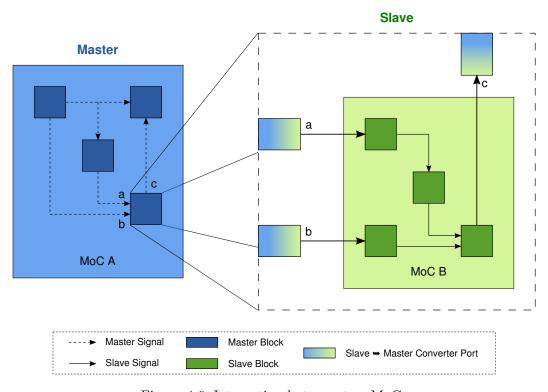

Essentially, we can break down the design of a simulator into two aspects: composition and synchronization. In this thesis, we address the challenges linked to the compositional aspects, some of the synchronization aspects are addressed in another work [11]. We establish a compositional analysis in order to provide a correct-by-construction approach. This analysis relies on validation checks and the definition of interacting mechanisms between MoCs. Within our simulation framework, all the mechanisms provided are generic to guarantee the flexibility of the simulator.

When dealing with heterogeneity, we have to identify the border between the different disciplines involved in the system. We must perform compatibility checks between these interacting disciplines and also provide a mechanism to express the specific semantics associated with a discipline such as dimension and units. The compositional analysis that must be performed should be carried out in the beginning of the life cycle of the simulator in order to ensure a sane structure for the followings simulation steps. The development of the simulator is a joint work with the PhD student in charge of the synchronization [11].

• Definition of a new Model of Computation: Smoothed Particle Hydrodynamics (SPH).

In order to support and verify the principles and mechanisms proposed within our framework SystemC MDVP, we need a various set of several Models of Computation. In the framework of the H-Inception project, the following MoCs were developed by persons involved in the project: Timed Data Flow (TDF) [11], Electrical Network (EN) [12] and Ordinary Differential Equations (ODE).

As part of this thesis, we have accomplished the development of a Model of Computation called SPH, which allows for fluidic networks to be described. The SPH MoC enables the expression of a physical discipline, with its unit and dimension. It elicits a good understanding of the complex interactions between several disciplines. This MoC is included in a proof-of-concept application, which aims to prototype a Lab-on-Chip through a point-of-care blood analysis system.

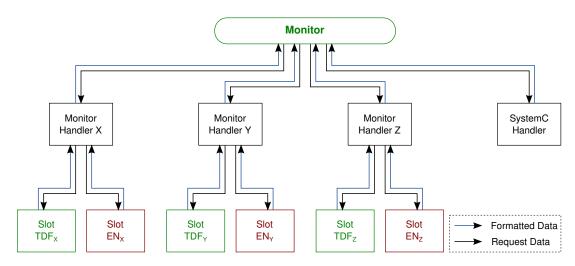

• Development of a generic multi-disciplinary monitoring mechanism.

A global and unified framework for the simulation of heterogeneous systems must provide an efficient monitoring mechanism. In order to support the scalability of the framework, i.e. to handle the upcoming disciplines, the monitoring capabilities must be generic. As such, its development passes through the definition of an internal abstraction within the framework and a generic interface to enable the expression of the discipline's specificities.

### 2.4 Conclusion

Keeping in mind the objective of performing the simulation of multi-disciplinary systems, specific issues related to the very nature of these systems have been raised. The simulation of heterogeneous systems must be based on a solid set of principals and must rely on a convenient and flexible infrastructure It requires the provision of a clear definition of the entities involved in the simulation, that is to say a clear definition within the simulation tool and also from the end-user perspective. It must be supported by a strong and efficient interaction mechanism, allowing for a high level of flexibility and, therefore, the capacity to enhance the simulator with new entities. Finally, an efficient monitoring mechanism that fits the specificities of multi-disciplinary systems must be provided. The difficulty, when you wish to perform the simulation of heterogeneous systems, lies in the method of addressing these challenges together in order to meet the aforementioned requirements.

After describing the contributions of this thesis in order to tackle the challenges raised by the simulation of heterogeneous systems, different approaches to address these issues are discussed in Chapter 3. The following chapters discuss the solutions provided in this thesis in more detail. We introduce our simulation framework SystemC MDVP and the underlying mechanisms (Chapter 4 and Chapter 5), we clearly define the simulation environment and the notion of heterogeneity before describing our interaction mechanism that fits the purpose of simulating heterogeneous systems, without forgetting our multi-disciplinary monitoring mechanism (Chapter 6). We subsequently demonstrate the flexibility of our solution with the integration of a new MoC (Chapter 7), followed by a case study to illustrate the efficiency of our solution (Chapter 8)

# Chapter

# Related Work

| Contents |       |                                      |           |

|----------|-------|--------------------------------------|-----------|

| 3.1      | Intr  | oduction                             | 14        |

| 3.2      | Cou   | pled Simulation                      | 14        |

| 3.3      | Fran  | meworks                              | 16        |

|          | 3.3.1 | Ptolemy II                           | 16        |

|          | 3.3.2 | ModHel'X                             | 17        |

|          | 3.3.3 | Modelica                             | 17        |

|          | 3.3.4 | Matlab                               | 18        |

|          | 3.3.5 | Metropolis                           | 19        |

| 3.4      | Syst  | temC-based Frameworks                | 20        |

|          | 3.4.1 | SystemC-A                            | 22        |

|          | 3.4.2 | SystemC-H                            | 23        |

|          | 3.4.3 | HetSC                                | 23        |

|          | 3.4.4 | SystemC AMS                          | 23        |

| 3.5      | Mul   | ti Disciplinary Monitoring Mechanism | <b>25</b> |

|          | 3.5.1 | Aspect-Oriented Programming (AOP)    | 26        |

|          | 3.5.2 | LLVM - Clang                         | 28        |

| 3.6      | Con   | clusion                              | 28        |

### 3.1 Introduction

This chapter presents a non-exhaustive state-of-the-art concerning the different approaches that allow us to simulate multi-disciplinary systems. This state-of-the-art aims at highlighting the different features required in order to design a virtual prototyping environment for heterogeneous systems.

Section 3.2 introduces a kind of simulation called coupled simulation, where the purpose is to describe different parts of the system to model using different tools and to simulate them in their respective dedicated simulator. We especially detail the *Functional Mock-up Interface (FMI)* standard which follows this approach.

Section 3.3 puts forward different simulation frameworks which aim at performing the simulation of heterogeneous systems. *Ptolemy II*, considered as the pioneer in the field of heterogeneous simulation, is a software environment based on a hierarchical heterogeneous approach. *Metropolis* is based on meta-models and promotes a reusability approach in order to support the simulation of embedded heterogeneous systems. *Modhel'X* relies on the association of sub-models described using different modeling languages. *Matlab*, coupled with *Simulink*, constitutes a commercial solution to perform multi-physical simulation. *Modelica* is an object-oriented language for hierarchical physical modeling.

In Section 3.4 we explore existing SystemC-based frameworks which intended to extend its capacities in order to perform analog simulation. We outlines two sets of frameworks, the first one gathers the frameworks which modify the SystemC kernel to enhance the simulator with analog capacities: HetSC and SystemC-A. The other set gathers those which do not alter the SystemC kernel: SystemC-H and SystemC-AMS.

In Section 3.5 we discuss different technologies that could have been used in order to achieve the monitoring of multi-disciplinary systems such as *Aspect-Oriented Programming* and *LLVM/Clang* approaches.

Thereafer, Section 3.6 provides an overview of the state-of-the-art presented and concludes this chapter.

### 3.2 Coupled Simulation

The Coupled Simulation approach, also referred as co-simulation, consists in modeling and simulating a system composed of different subsystems in a distributed manner; these different subsystems form a coupled problem. The co-simulation intends to couple different tools in a co-simulation environment. The idea is that each model which makes up the system is developed with different tools and is simulated independently from the other models in its own simulator.

This approach allows for the modeling at the subsystems level without addressing the issue of the coupling of the different subsystems involved in the model. The Functional Mock-up Interface (FMI) defines a standard that follows the co-simulation approach.

The Functional Mock-up Interface (FMI) [13, 14, 15] is a tool-independent standard for both the model exchange and co-simulation of dynamic models [16]. The concept of dynamic models exchange provides a modeling environment with the ability to generate an input/output block to represent a dynamic model which can be used later within another modeling environment. The FMI for co-simulation adopts a different approach where instead of transmitting a model to another tool, each model is simulated using its own tool and data resulting from this simulation can be transmitted to other tools.

The FMI for co-simulation consists of two distinct parts: a co-simulation interface and a co-simulation description schema. The first one, the interface, is defined through a set of C functions that allows for controlling the different tools. The data exchange of input and output values can be controlled through this interface. The second one describes, as an XML file, the information that characterizes a tool (input, output, solver capacities ...). Although these models can communicate between them, the data exchange is restricted to discrete communication points. Between these communication points each subsystem is solved independently.

The Functional Mock-up Interface does not rely on direct coupling in order to achieve its co-simulation environment. FMI assumes the existence of a master located between each simulator involved in the co-simulation environment. This master, which is not included in the FMI for co-simulation standard [17], has the responsibility to synchronize, to control and to manage the different tools involved in the simulation. As such, the master appears as an interface which establishes the connections and the data exchange between tools. The FMI standard assumes that the different tools, referred as slaves, only communicate with the master.

Although the master is not considered as part of the standard, there exists a *prototype master* implementation realized in the framework of the MODELISAR European research project [18]. This implementation prototype master provides three simulation algorithms with fixed step size: a data flow algorithm, a fixed point iteration algorithm and a simple implementation of Newton's method. This prototype is developed for commercial purposes.

This approach is interesting, but in term of efficiency using a single simulation engine remains a more efficient approach [17]. Indeed, efficiency and simulation speed strongly depend on the problem to be solved. While simulation of graphs without feedback can be simulated quite efficiently using the non-iterative method, the presence of cycles and the incapacity to use iterative method lead to low accuracy and low numerical stability. Furthermore, the master timestep may have to be very small which increases the computational cost and, hence, may lead to a global simulation speed quite low. In addition, the overhead induced by the synchronization between tools is often too high. Consequently, this approach does not fit our objective and is not considered in this work.

### 3.3 Frameworks

### 3.3.1 Ptolemy II

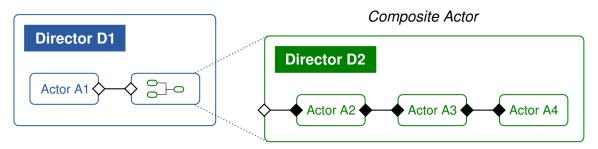

One of the pioneering works in the field of heterogeneous systems simulation was done in Ptolemy Classic [19] and its sequel, Ptolemy II [20, 21]. Ptolemy II is a proof of concept simulator, which addresses the complex issue of modeling heterogeneity in a hierarchy of connected entities. Ptolemy II introduces the notion of *Hierarchical Heterogeneity*. This approach exhibits a heterogeneous composition where the interaction and communication between models are represented while preserving the properties of each individual model. It allows for the decomposition of a complex heterogeneous system as a tree of nested sub-models, each sub-model representing a network of interacting components. Beneath the hierarchical representation, different synchronization mechanisms between models may be used at different levels of abstraction. Each sub-model, i.e. each level in the hierarchy, safeguards the intrinsic properties of each model; the interconnection between the different sub-models gives the opportunity to evaluate the system as a whole.

Ptolemy II relies mainly on an actor-oriented view to describe a heterogeneous system [22, 23]. Two kinds of actor are available:

- Atomic Actor: describes a basic behavior block of the system. It represents a leaf in the hierarchical tree representing the system.

- Composite Actor: represents a netlist of sub-actors which can either be atomic or composite actors; it is a sub-model representing a network of interacting components.

Each local sub-model is managed by a specific and well-defined Model of Computation (MoC) which actually defines how computation and model solving are performed. MoCs are implemented by means of *Domains: Receivers*, which encompass the communication semantics, and *Directors*, which define the execution order of actors. Together, they define the environment of actors. Directors are eventually responsible for the instantiation of domain-specific receivers. Ptolemy II includes domains such as Discrete Event (DE), Continuous Time (CT), Synchronous Data Flow (SDF), amongst others. A list of the available domains is defined in [24].

Figure 3.1: Hierarchical Modeling in Ptolemy II (adapted from [20]).

An illustration of a system designed with Ptolemy II semantics is shown in Figure 3.1. It describes the use of atomic actors and composite actors, highlighting the hierarchical representation of the system. The communication mechanisms through ports and channels are also represented; the different domains interacting are subsequently shown as directors, and receivers are depicted.

Since the whole environment is defined by the domain, actors represent abstract functionalities that are inherently reusable in many domains. The implications of this flexibility, however, can be tricky or overwhelming for the end-user. In addition to building the netlist of components the designer wishes to simulate, he also has to explicitly build the specific composite actors so as to encapsulate the subsystems and he must choose and instantiate the correct directors with respect to the created hierarchy and the simulated domains. Although actors that can be run under different domains are a good idea in order to increase the reusability of models, it is also a source of struggle. The user is forced to fully investigate the impact on the model behavior introduced by a change of directors and receivers as they implement the semantics of a different MoC. As a result of this, the models have to be completely revalidated. Another inconvenience is that the model hierarchy has to reflect the hierarchy of homogeneous domains under control of individual directors instead of following solely the natural decomposition of a system into its sub-systems. Thus, simulator-specific artefacts become intermingled with actual system components. These constraints raise two major issues. Firstly, it forces the user to fully apprehend the director's internals and the underlying simulator semantics. Secondly, the explicit definition of the hierarchy produces an intermingling of system components and simulation-specific artefacts.

#### 3.3.2 ModHel'X

ModHel'X [25] is a framework designed to model heterogeneous systems. It relies on the association of sub-models, described using different modeling languages, to construct the whole model. Like Ptolemy II, it relies on the concept of Models of Computation and a hierarchical heterogeneity approach. To handle a new modeling language, an expert in this language must define the associated MoC with respect to the ModHel'X semantics. This must be done in order for the generic execution engine to perform a correct interpretation of the modeling language's semantics. The need for an expert to define a new Model of Computation is an obstacle to the development of this framework. Consequently, only a few MoCs are available.

#### 3.3.3 Modelica

Modelica is an object-oriented language for hierarchical physical modeling [26]. It relies on several features including non-causal modeling and multi-domain modeling capability [27]. There are several commercial modeling and simulation environments for Modelica available, such as Dymola (Dynamic Modeling Laboratory) [28] or Math-Modelica.

Modelica adopts an approach similar to Ptolemy II with actor-like semantics. However, the

ports used to interconnect different bricks of a model are not specified as input or output, instead the connections are expressed with equation constraints on variables. While this approach has significant advantages in the definition of physical models, it appears to be harder to combine with other entities [29].

The conception of hybrid system with Modelica can prove to be tricky. Indeed, the same notions, depending on the environment they are declared in, can have different meanings. For example, events in an equation environment are simultaneous and cannot be treated sequentially, whereas in algorithm environment, simultaneous events could be lost [30].

#### 3.3.4 Matlab

Matlab [31] is a commercial tool with its own programing language where the models and algorithms are described using mathematical notation. Although it is primary intended for numerical computing, additional optional toolboxes can be interfaced with Matlab in order to enhance the possibilities offered by the Matlab environment. It is worth noting that the Matlab language is an interpreted language which means that it is not compiled. This has an impact on performance with regards to the simulation speed.

Simulink [32] is a commercial toolbox associated with Matlab. It is a graphical programming environment for modeling, simulating and analyzing multi-domain dynamic systems. Simulink relies on libraries which provide access to a set of components from different engineering domains.

Matlab, when associated with Simulink, represents a relatively well-adopted solution for performing interactive design at system level. Designers can create, simulate and modify block diagrams. They are widely used for capturing system requirements and developing signal-processing algorithms [33]. Although they provide powerful possibilities for the description of analog and mixed-signal systems at system level, they support neither the modeling of digital hardware/software systems, nor the simulation of analog subsystems on the electrical circuit level [34]. A support for different Models of Computation is missing and hence Simulink is restricted to the evaluation of abstract models [35].

A study on languages and tools for hybrid system design [30] showed some drawbacks of Matlab. This study states that the behavior of the system is sensitive to the inner workings of the simulation engines, and, consequently, is liable to lead to erroneous results. An in-depth knowledge of the internal of the tool is important in order to prevent such behaviors.

Despite being user-friendly and providing a great set of primitives through the toolbox Simulink, Matlab's simulation performances do not fit our purpose. We are looking for a fast prototyping simulator and with Matlab, depending on the abstraction level within the model, the simulation speed may significantly drop.

#### 3.3.5 Metropolis

Metropolis [36, 37] is a system design environment for heterogeneous embedded systems, which favors reusability of components in the systems through the decoupling of orthogonal aspects [38]. The decoupling of orthogonal aspect addresses three main characteristics:

- Computation and Communication: it represents an important separation since the computation and the communication do not follow the same refinement process.

- Functionality and architecture: the separation is suggested since these two aspects are often defined independently.

- Behavior and Performance indices: the separation between these two characteristics is motivated by the fact that performance indices as constraints are often specified independently from the behavior. And as results, they derive from a specific architectural mapping of a behavior.

To this aim, the Metropolis framework mainly relies on an internal representation called *Metropolis Meta Model (MMM)* that defines a set of abstract classes. This meta-model can be described following three aspects:

- actions: they can be defined in terms of computation (process), communication (medium) and coordination (scheduler or linear temporal logic).

- constraints: they rely on the definition of a quantity object associated with actions that can represent time or power. Constraints can then be specified using the form of predicate logic.

- refinement: through inheritance principle, one can define and model a well-separated computation and communication semantics. This mechanism allows for the definition of a more detailed behavior of the system.

Although Metropolis provides efficient features such as the separation between computation and communication, and its refinement mechanism, the process-based approach within this framework leads to a non-hierarchical modeling approach. Indeed, all processes should be implemented in the same hierarchical level to be interconnected with mediums. We believe a hierarchical approach (as within Ptolemy II) is best suited for heterogeneous modeling. The expression of the synchronization can be a little tricky since it is left up to the model designer. He should express the time synchronization through the definition of constraints upon quantity handled by a quantity manager. Moreover, the communication medium performs the data synchronization, and hence it may be used as a converter channel. Finally, the meta-model does not provide a predefined notion of time, which means that the definition of a global notion of time is left up to the model designer at the language level through a quantity object.

#### 3.4 SystemC-based Frameworks

Besides Ptolemy, several solutions for the simulation of heterogeneous systems have been presented over the course of the last decade. They mainly rely on SystemC [39], a discrete event simulation kernel, which can be used to perform rapid system prototyping at several levels of abstraction.

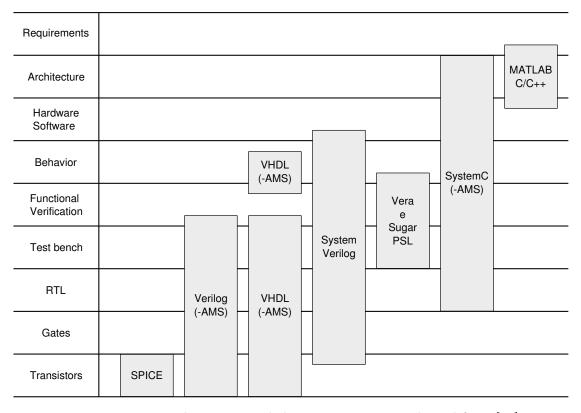

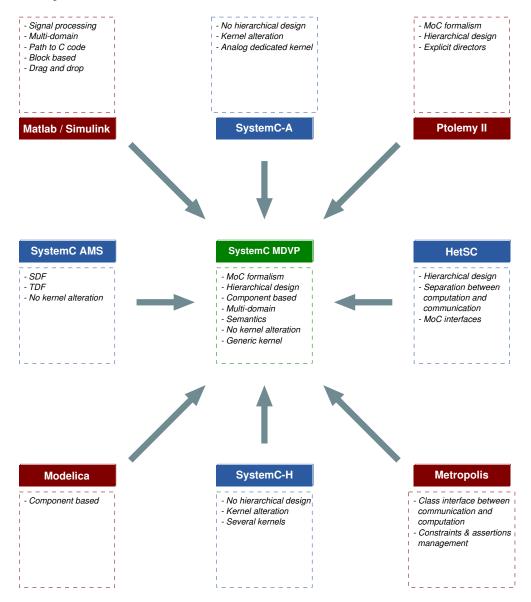

Figure 3.2: Design languages and their main purpose, adapted from [33]

The levels of abstraction covered by SystemC are depicted in Figure 3.2. SystemC goes from the Register Transfer Level (RTL) to the architecture level through several other levels (test bench, functional verification, behavior and hardware/software). Furthermore, this figure illustrates the levels of abstraction cover by other frameworks, notably Matlab.

SystemC [33] is a system design language that allows for the modeling and co-development of hardware and software at a high level of abstraction. It is also a hardware description language (HDL), thanks to its several levels of abstraction which allow it to precisely describe hardware architectures. SystemC comes as a C++ class library and, hence, leverages the powerful and efficient capacities of the C++ language.

The wide range of abstraction levels offered by SystemC allows a designer to describe a system with several levels of accuracy. A designer can describe a subsystem at a lower level of abstraction while the rest of the system remains at a high level of abstraction. For example, the system can be described using the Transaction Level Modeling (TLM) [40] at a high abstraction level and a subsystem can be described using a Cycle Accurate Bit Accurate (CABA) abstraction level. This approach offers the designer a good understanding of the system he is modeling.

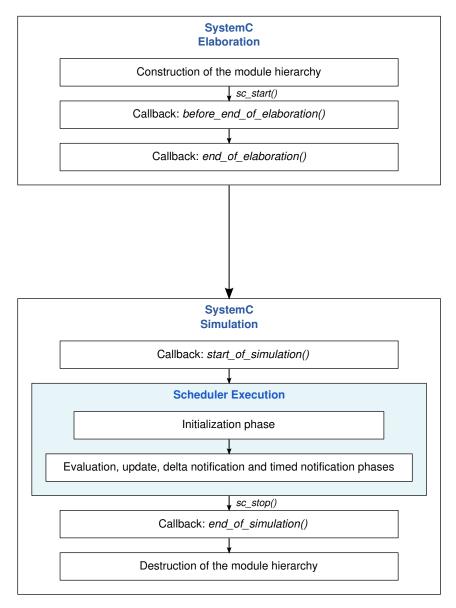

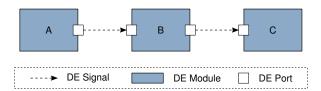

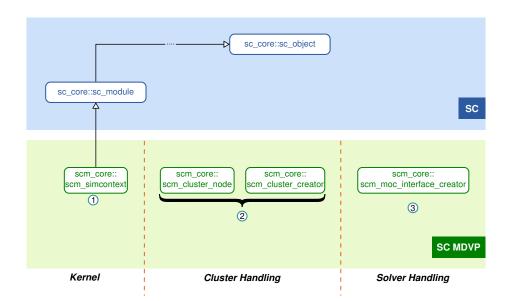

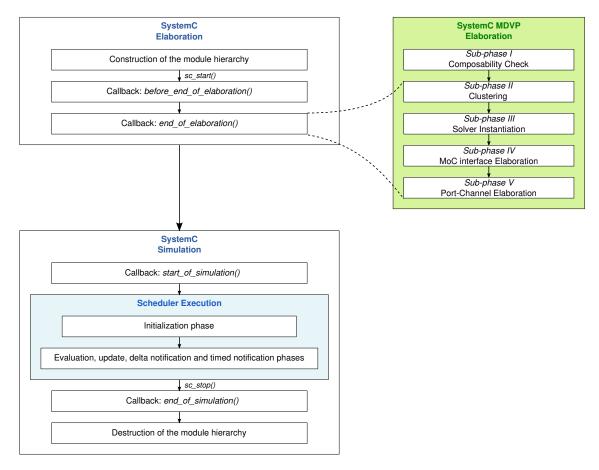

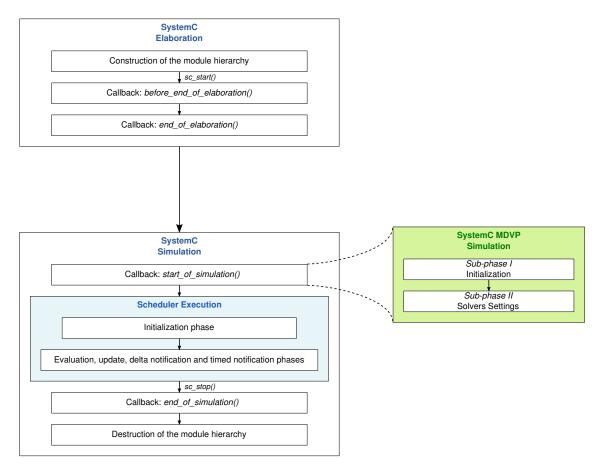

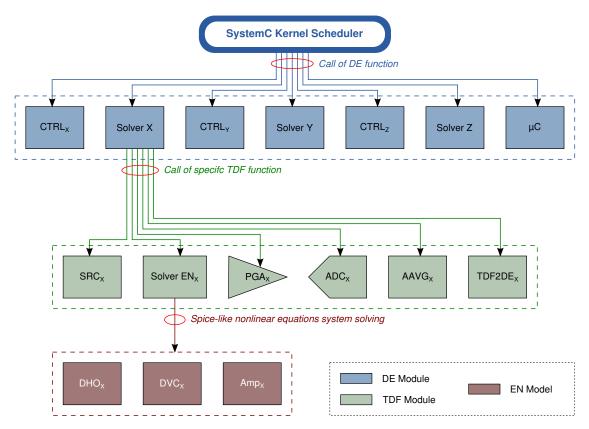

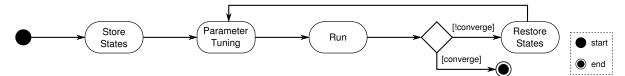

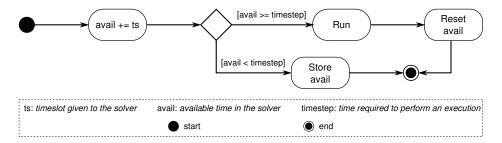

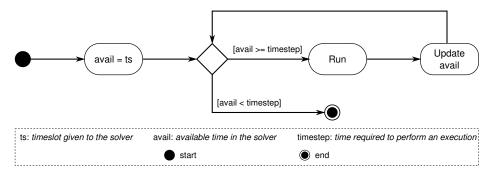

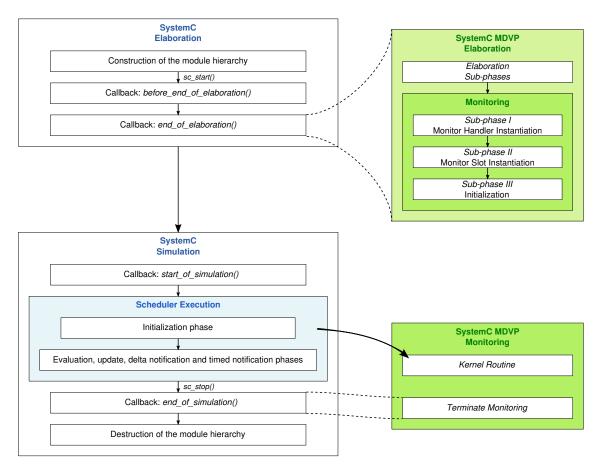

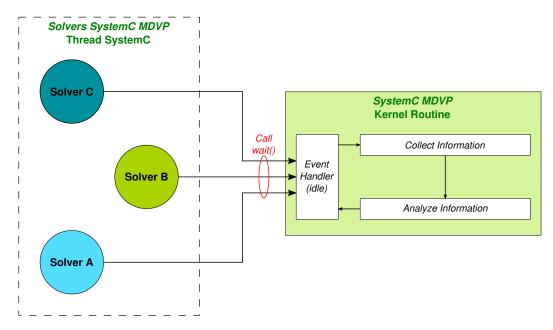

The Discrete Event (DE) simulation kernel of SystemC relies on two main tasks - the *Elaboration* and the *Simulation* phases. The SystemC kernel phases are described in Figure 3.3.

Figure 3.3: SystemC Kernel Phases, adapted from [11].

The Elaboration phase aims to prepare the kernel and building efficient data structures for the simulation. During this phase all the data structures required to support the simulation are created. To this aim, the system modeled is explored.

The objective of the Simulation phase is to execute the model described. To do so, the kernel relies on a scheduler that handles a list of processes to execute. The processes are divided into different lists depending on their status. A process can be runnable, meaning it waits until the scheduler triggers its execution, or a process can be queued in a *pending* list waiting on a notification in order to be runnable.

The kernel catches all the notifications - events that control the execution of the processes. When it receives a notification, the scheduler can move a process from the pending list to the runnable one if this process is sensitive to this notification. The scheduler repeats this scheme until no more notifications are received, no more processes are runnable, or the simulation is stopped.

Figure 3.3 highlights some relevant callbacks provided by SystemC that are automatically called on each primitive by the SystemC kernel. These callbacks can be overridden in order to execute specific behaviors at different stages of the simulation. Hence, these callbacks constitute entry points into the SystemC simulation kernel that do not alter the kernel itself.

- before\_end\_of\_elaboration() is called before the kernel reaches the end of the elaboration phase. During this callback, modifications to the system are still authorized. This callback can be used to program actions to execute during the elaboration phase that may alter the structure of the system modeled

- end\_of\_elaboration() is called when the kernel reaches the end of the elaboration phase. At this moment, the data structures required by SystemC to support the simulation have been created and, consequently, the system can no longer be modified. This callback can be used to program actions, executed during the elaboration phase, that do not alter the structure of the system modeled.

- start\_of\_simulation() is called in the beginning of the simulation. This callback can be used in order to program actions to execute at the beginning of the simulation.

- end\_of\_simulation() is called at the end of the simulation. This callback can be used to program actions to execute at the end of the simulation.

The solutions for the simulation of heterogeneous systems based on SystemC rely on two different approaches. Firstly, we find the solutions which extend and modify the kernel SystemC. Secondly, we find the solutions which extend the functionalities of SystemC without altering its kernel. Solutions following both approaches are introduced in the following.

#### 3.4.1 SystemC-A

SystemC-A [41, 42] is an extended version of SystemC which provides analog, mixed-signal and mixed-domain modeling capabilities. SystemC A enables support for user-defined ordinary differential and algebraic equations which enable the modeling of analog systems. It defines an analog kernel, which provides both linear and nonlinear solvers to solve the analog systems. This kernel is integrated within SystemC through a primitive module but there is a major drawback with the solution proposed - it requires the modification of the SystemC kernel. To make the integration of the analog kernel with the discrete event kernel possible, and to perform the synchronization between them, the authors modified the SystemC kernel which limits portability and standard compliance.

#### 3.4.2 SystemC-H

SystemC-H [43, 44] is an extension of SystemC which enhances the discrete event kernel capacities in order to support heterogeneity. Within this framework, the authors want to provide support for several models of computation. The adopted approach is to provide a simulation kernel dedicated to each MoC. The authors addressed the simulation of heterogeneous systems through the definition of a heterogeneous simulation kernel, each part of the system being simulated by the kernel which fits the MoC used to describe it. They designed a simulation kernel wherein the MoC dedicated kernels are interoperable with the discrete event kernel and thus defined an alternate SystemC kernel. As SystemC-A, they modified the internal structure of the kernel SystemC which limits portability and standard compliance.

#### 3.4.3 HetSC

HetSC [45, 46] is a framework which describes a heterogeneous specification methodology built on top of SystemC kernel. One important thing to notice is that HetSC provides heterogeneous support without modifying SystemC kernel. In the context of this framework, heterogeneity is defined as the ability to specify a set of communicating subsystems described under different Models of Computation (MoCs). This methodology supports untimed MoC and synchronous MoC. We can specify Process Network, Kahn Process Network, Communicating Sequential Processes and Synchronous Data Flow as untimed MoC and distinguish the Synchronous Reactive MoC as synchronous Models of Computation. This framework enables new MoCs to be integrated as long as they can cooperate and be abstracted by the Discrete Event (DE) SystemC simulation kernel. We can say that HetSC is mainly a communication library and that it does not express heterogeneity as we defined it. Within this framework, the Models of Computation (MoCs), which express the heterogeneity, only describe abstracted DE models and cannot express the surrounding physical environment. We should note, for example, that HetSC does not support continuous time.

#### 3.4.4 SystemC AMS

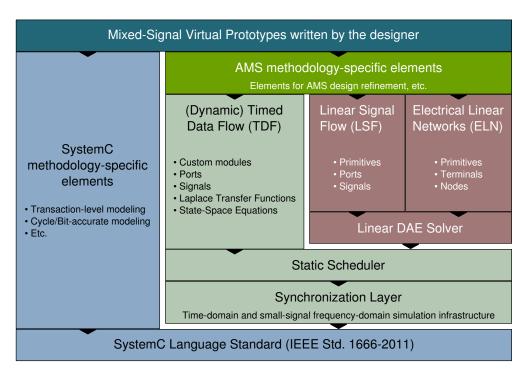

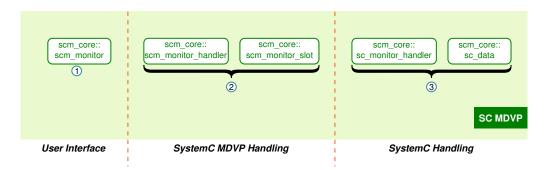

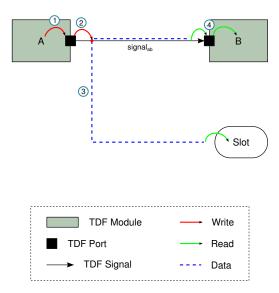

SystemC AMS [47, 48, 49] is a specification methodology developed on top of SystemC by the Accelera Systems Initiative organization<sup>1</sup>. SystemC AMS extensions [50] have been specifically developed in order to improve the modeling capacities of SystemC by allowing the simulation of analog behaviors coupled with digital-centric systems. SystemC AMS comes as a C++ library that follows the same approach of SystemC. It relies on the same definition of objects to realize the design of a system: modules, ports, interfaces and channels. SystemC AMS is defined following a layered architecture approach [51] described in Figure 3.4.

<sup>&</sup>lt;sup>1</sup>The development is carried out by the AMSWG: SystemC AMS Working Group

Figure 3.4: SystemC AMS language Standard Architecture, adapted from [52].

SystemC AMS integrates three layers to the existing set of layers defined in the SystemC environment [48]:

- The view layer: it defines the different descriptive methods provided to the designer in order to write executable models.

- The solver layer: it contains the implementation of different solvers required in order to model specific AMS behaviors.

- The synchronization layer: it defines a mechanism in order to organize the simulation of a SystemC AMS model that may include several views.

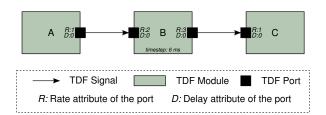

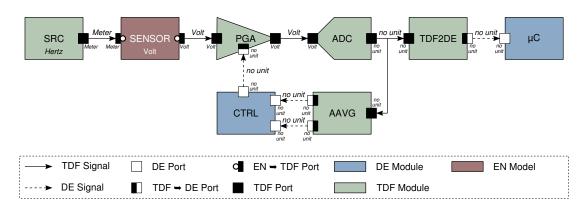

SystemC AMS also supports the notion of MoCs and several abstraction of time: Discrete Time (DT), Continuous Time (CT). Figure 3.4 shows the three MoCs defined within SystemC AMS: Timed Data Flow (TDF), Linear Signal Flow (LSF) and Electrical Linear Network (ELN).

The TDF MoC allows discrete time modeling, and efficient simulation of signal processing algorithms and communication systems at the functional and architectural level. A dynamic approach to the TDF MoC is defined as Dynamic TDF (DTDF) [53]; it allows modifying some of the simulation parameters during the simulation. One should note the strong implication of the TDF MoC in the definition of SystemC AMS. Indeed, TDF is more than a simple Model of Computation within SystemC AMS; Figure 3.4 highlights the fact that TDF constitutes the only synchronization mechanism available within SystemC AMS. Although other MoCs are defined, they all have to go through the TDF semantics in order to be executed.

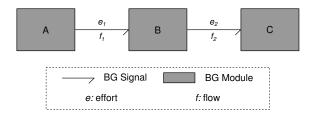

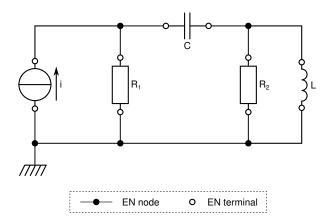

The LSF MoC supports the modeling of continuous time behavior through the definition of predefined primitives (such as addition, multiplication, integration, etc.). LSF allows the modeling of non-conservative systems, the connection of several primitives defines a system of linear equations solved by a linear DAE solver. The ELN MoC enables the modeling of electrical networks through the definition of predefined primitives (such as capacitors, resistors, etc.). The connection of several primitives describes the continuous time relation between voltage and current. However, ELN is restricted to the modeling of linear electrical systems.

These extensions were originally implemented in the Fraunhofer SystemC-AMS proof-of-concept simulator [54]. They have been successfully applied in communication [55], automotive [56] and consumer electronics use cases with good simulation performance and accuracy. The commercial software COSIDE [57] is based on this proof-of-concept simulator.

For the moment, though, it is rather difficult for design teams to extend the current SystemC-AMS simulator with other MoCs than those proposed [55]. The SystemC AMS 2.0 standard [50] does not define an Application Programming Interface (API) for this purpose, nor does the proof-of-concept simulator document its internal API. To our knowledge, only two attempts have been published, the first adding an Non-Linear Network (NLN) [58] and the second, a Bond Graph (BG) MoC [59], respectively, by authors with an in-deep knowledge of the SystemC-AMS implementation. These MoCs rely on internal APIs to integrate themselves without modifying SystemC AMS. An analysis of the SystemC-AMS source code shows that each MoC is required to fully handle its elaboration once the SystemC port binding phase has been finished. SystemC-AMS provides only a minimal support for this task by providing a list of all instantiated modules belonging to a certain MoC. It provides one synchronization mechanism used by all the existing MoCs and no API is provided to define new synchronization schemes between MoCs.

All in all, the modeling of heterogeneous systems can be considerably error prone from a physical perspective, since designers from different disciplines use different measurement units and scales. A major improvement towards heterogeneous simulation was made with the integration of dimensional analysis into SystemC AMS [60] through the use of Boost::Units library [61]. It allows designers to enhance models with the notion of physical quantities, which avoids compositional errors.

# 3.5 Multi Disciplinary Monitoring Mechanism

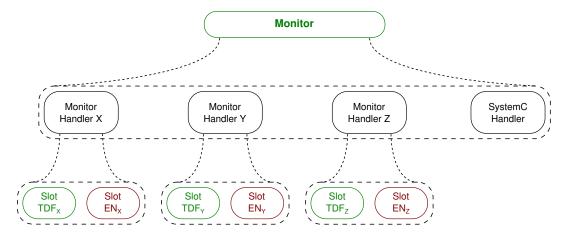

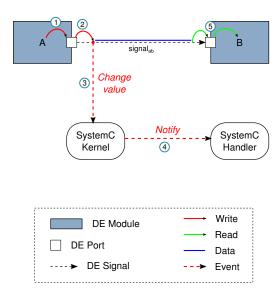

Monitoring is a mechanism which aims to observe and record information about a system. It may be used, for example, to detect threshold crossing, to perform profiling evaluation on a system or as a tracing mechanism. Tracing mechanisms are mainly used for debugging purposes, through the log of information during the simulation.

Monitoring, threshold detection, profiling and tracing functionalities, represents an important feature in a simulator framework. We think that these functionalities should be developed simultaneously. Performing the detection of threshold crossing, the profiling or the tracing involves the same mechanisms, only the outcome is different. All of these capabilities require a mechanism to probe the system in order to gather relevant, specific information.

In the following sub-sections we will introduce existing solutions that may fit the requirement to provide an efficient monitoring mechanism.

#### 3.5.1 Aspect-Oriented Programming (AOP)

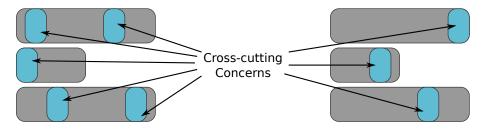

Object-Oriented Programming (OOP) [62] allows us to break up a problem into a set of reusable objects. Although these objects mainly describe a single functionality, they usually share common, secondary behaviors with other objects. These common behaviors are usually scattered throughout the whole system, as shown on Figure 3.5, breaking the encapsulation principle. You can see the same behavior replicated in different components (objects).

Figure 3.5: Classical Object Oriented Programing.

Think of the tracing of the functions called during the simulation. You would have to insert print function within every function of your system (potentially the exact same code line)! These common behaviors are identified as cross-cutting concerns. Cross-cutting concerns denote behavior that cuts across the boundaries of assigned responsibility for a given modular element. They are often shared, and common. They may describe process synchronization, location control, timing constraints, persistence, failure recovery, tracing, monitoring, verification, etc.

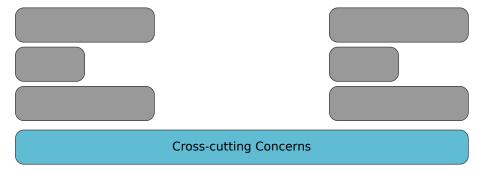

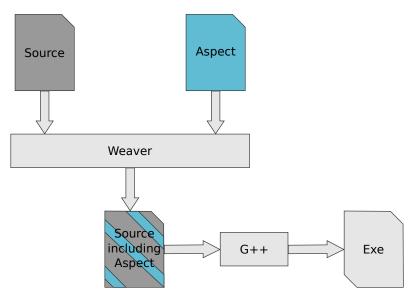

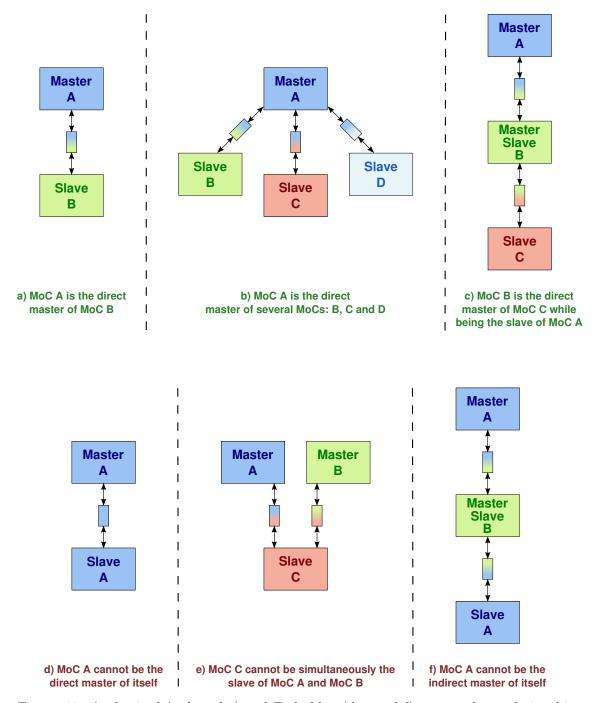

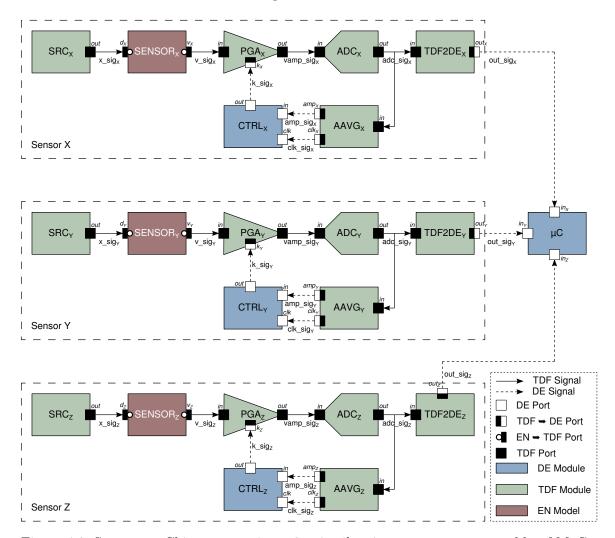

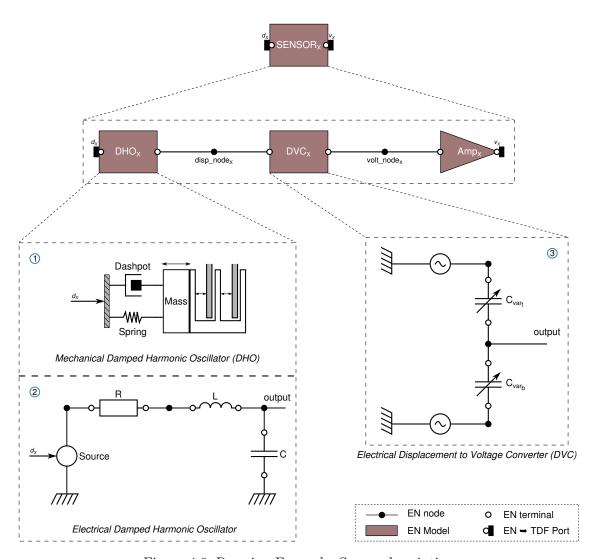

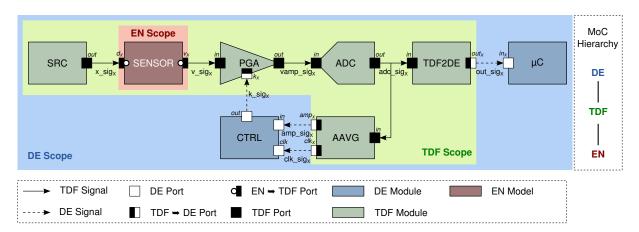

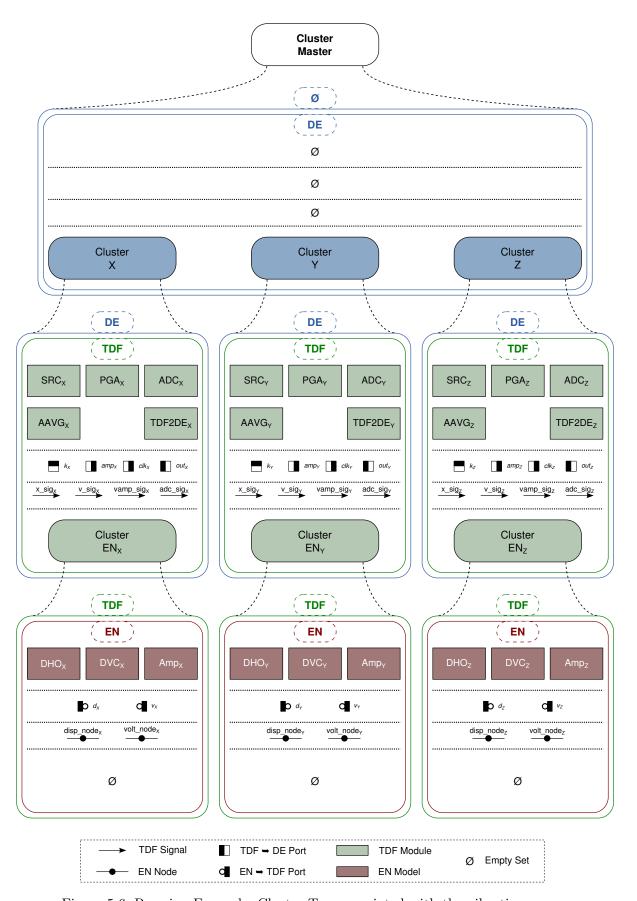

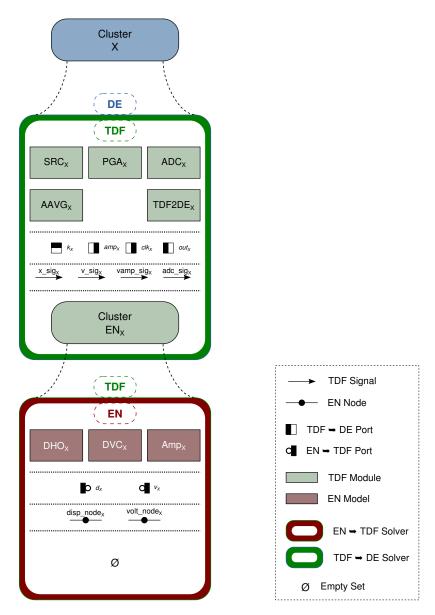

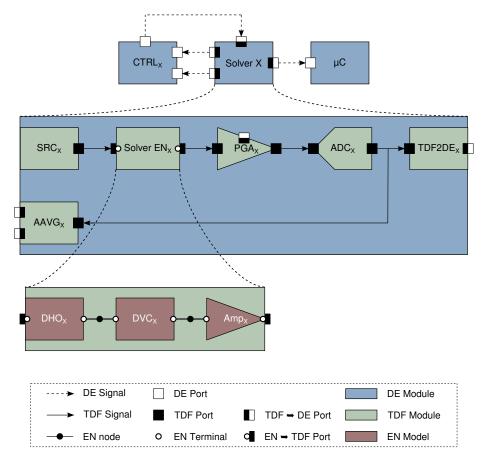

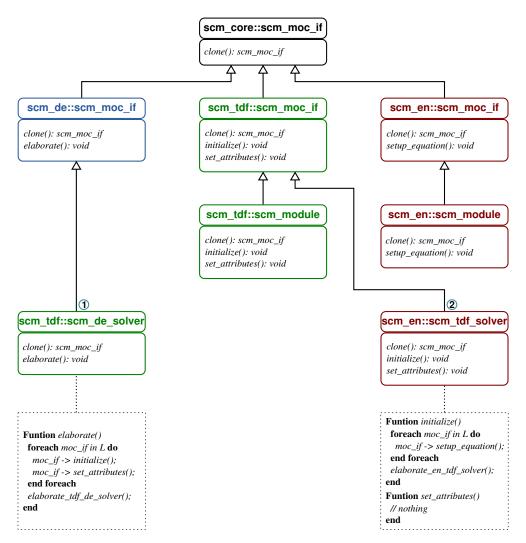

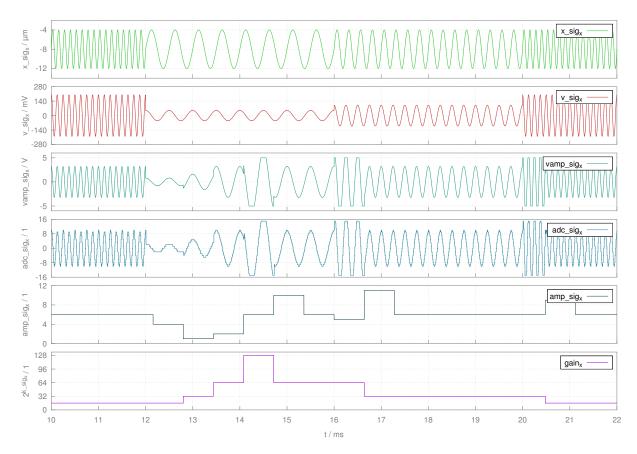

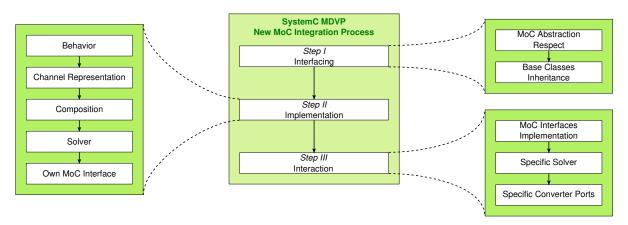

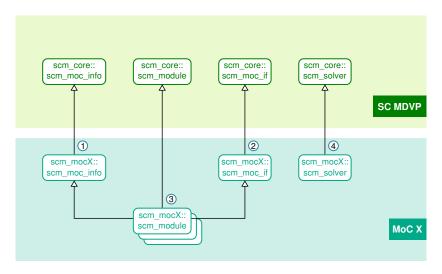

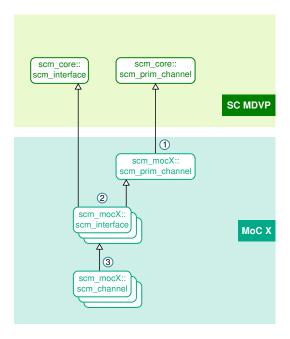

Figure 3.6: Aspect Oriented Programing.