# Gestion hiérarchique de la reconfiguration pour les équipements de radio intelligente fortement hétérogènes

Xiguang Wu

#### ▶ To cite this version:

Xiguang Wu. Gestion hiérarchique de la reconfiguration pour les équipements de radio intelligente fortement hétérogènes. Autre. CentraleSupélec, 2016. Français. NNT: 2016CSUP0002. tel-01646825

# HAL Id: tel-01646825 https://theses.hal.science/tel-01646825

Submitted on 23 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre: 2016-02-TH

# CentraleSupélec

#### **Ecole Doctorale MATISSE**

« Mathématiques, Télécommunications, Informatique, Signal, Systèmes Electroniques »

Laboratoire de Signal, Communication et Electronique Embarquée

# THÈSE DE DOCTORAT

DOMAINE : STIC Spécialité : Electronique

Soutenue le 21 mars 2016

par:

## Xiguang WU

Hierarchical Reconfiguration Management for Heterogeneous Cognitive Green Radio Equipments

#### Composition du jury:

Président du jury : M. Guy GOGNIAT Professeur à Université de Bretagne-Sud

Rapporteurs: Mme. Lirida NAVINER Professeur à Télécom ParisTech

M. Tanguy RISSET Professeur à l'INSA de Lyon

Examinateurs : M. Christophe MOY Professeur à CentraleSupélec

M. Dominique NOGUET Ingénieur à CEA-LETI

M. Xun ZHANG Professeur assistant à ISEP

Directeur de thèse : M. Jacques PALICOT Professeur à CentraleSupélec Co-directeur de thèse : M. Pierre LERAY Professeur à CentraleSupélec

"殊途同归。"

— <<周易●系辞下>>

"Tous les chemins mènent à Rome."

"All roads lead to Rome."

# Acknowledgements

First and foremost, I express my most sincere gratitude to my supervisors, Professor Jacques Palicot and Professor Pierre Leray, for giving me the opportunity to do this work. Thanks to Professor Jacques Palicot for his great guidance, patience and support all along the past three years. Thanks to Professor Pierre Leray for his precious technical guidance and help throughout my Ph.D. Without their guidance and encouragement, this work would not have been successful.

I deeply appreciate the rest of the staff in SCEE team for their encouragement and thoughtful suggestions. I would like to thank all the members of SCEE team for their friendship and help during my time in Rennes. Thanks especially to Malek for the discussions and valuable suggestions on the OFDM scenario of HDCRAM.

I would like to thank Professor Lirida NAVINER and Professor Tanguy RISSET for agreeing to be the rapporteurs of this dissertation. Your valuable suggestions and critical comments are important and helpful for revising and improving the thesis. I am also grateful to Professor Guy GOGNIAT for accepting to serve as the president of the dissertation committee, and Professor Christophe MOY, Dr. Dominique NOGUET, Dr. Xun ZHANG, for accepting to be my committee members. Your feedback and discussion are valuable for guiding and improving the current work.

I would like to acknowledge all my friends for their warm support, care and precious friendship through these difficult years.

It is my pleasure to express my gratitude to all those people who have supported and helped me during this thesis.

vi Acknowledgements

Finally, I would like to dedicate this work to my family for standing behind me with their love, concern, constant support and limitless patience.

$WU\ Xiguang$  Rennes, France

# Contents

| Ackno | wledge  | ements     |                                                            | v  |

|-------|---------|------------|------------------------------------------------------------|----|

| Résun | né      |            |                                                            | 1  |

| Intr  | oductio | n          |                                                            | 1  |

| 1     | Conte   | xte et Po  | osition du problème                                        | 2  |

|       | 1.1     | L'Eco l    | Radio                                                      | 2  |

|       |         | 1.1.1      | Au niveau international                                    | 3  |

|       |         | 1.1.2      | Au niveau Français                                         | 4  |

|       | 1.2     | La Rac     | lio Intelligente                                           | 5  |

|       |         | 1.2.1      | La gestion du spectre                                      | 8  |

|       |         | 1.2.2      | Une vision plus globale                                    | 10 |

|       | 1.3     | l'Ecora    | dio Intelligente                                           | 11 |

|       | 1.4     | HDCR.      | AM                                                         | 13 |

| 2     | Impla   | ntation of | de HDCRAM sur plateformes hétérogènes                      | 16 |

|       | 2.1     | Reconf     | figuration Partielle de FPGA                               | 16 |

|       | 2.2     | Implén     | nentation de HDCRAM sur plate-forme Virtex5                | 17 |

|       | 2.3     | Implén     | nentation de HDCRAM sur plate-forme Zynq 7000              | 17 |

| 3     | Etude   | des mé     | triques liées à la plate-forme dans un contexte d'Ecoradio |    |

|       | Intelli | gente .    |                                                            | 18 |

|       | 3.1     | Les diff   | férentes métriques                                         | 19 |

|       |         | 3.1.1      | La température                                             | 19 |

|       |         | 3.1.2      | La ressource disponible, la surface et la position d'une   |    |

|       |         |            | fonction                                                   | 20 |

viii

|          |        |            | 3.1.3       | Le taux d'activité                                                | 20 |

|----------|--------|------------|-------------|-------------------------------------------------------------------|----|

|          |        |            | 3.1.4       | Implantation série/parallèle                                      | 21 |

|          |        |            | 3.1.5       | La consommation                                                   | 21 |

|          |        | 3.2        | Discussion  | on sur les différentes métriques                                  | 22 |

|          |        | 3.3        | Etude d     | 'un cas particulier : implantation série ou parallèle d'un filtre | 23 |

|          |        |            | 3.3.1       | Influence du nombre de coefficients                               | 26 |

|          |        |            | 3.3.2       | Gestion de ces métriques par HDCRAM                               | 27 |

|          | 4      | Implar     | ntation d'  | un système émission/réception OFDM                                | 28 |

|          |        | 4.1        | Implanta    | ation de la FFT par RP                                            | 29 |

|          |        | 4.2        | Différent   | ts scénarios d'Ecoradio Intelligente                              | 33 |

|          |        |            | 4.2.1       | Adaptation de la constellation                                    | 33 |

|          |        |            | 4.2.2       | Gestion de la FFT en fonction du niveau de batterie               | 34 |

|          |        |            | 4.2.3       | Gestion de la taille de la FFT en fonction du standard à          |    |

|          |        |            |             | utiliser                                                          | 34 |

|          | 5      | Conclu     | usion et P  | Perspectives                                                      | 36 |

| <b>A</b> | bstra  | <b>-</b> + |             |                                                                   | 37 |

| A        | DSII a | Ct         |             |                                                                   | 31 |

| In       | trod   | uction     |             |                                                                   | 39 |

| 1        | Bac    | kgrour     | nd and n    | notivation                                                        | 43 |

|          | 1.1    | Energy     | y Efficienc | cy                                                                | 43 |

|          |        | 1.1.1      | Motivati    |                                                                   | 43 |

|          |        | 1.1.2      | Projects    |                                                                   | 45 |

|          |        | 1.1.3      | Compari     | ison of our work with the state of the art                        | 49 |

|          | 1.2    | Cognit     | ive Radio   | D                                                                 | 50 |

|          |        | 1.2.1      | Spectrur    | m Utilization                                                     | 50 |

|          |        | 1.2.2      |             | Vision                                                            | 53 |

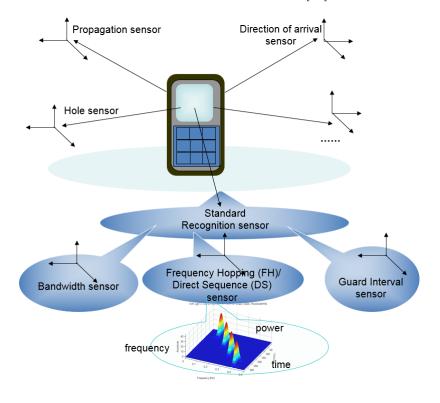

|          |        | 1.2.3      | Sensing     |                                                                   | 54 |

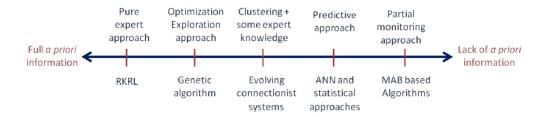

|          |        | 1.2.4      |             | Making                                                            | 57 |

|          |        |            | 1.2.4.1     | Expert approach                                                   | 57 |

|          |        |            | 1.2.4.2     | Exploration based decision making : Genetic Algorithms            | 58 |

ix

|          |     |                 | 1.2.4.3    | Learning approaches : exploration and exploitation                 | 58 |

|----------|-----|-----------------|------------|--------------------------------------------------------------------|----|

|          | 1.3 | HDCF            | RAM Arch   | nitecture                                                          | 59 |

|          |     | 1.3.1           | Introduc   | etion                                                              | 59 |

|          |     | 1.3.2           | Heteroge   | eneous Deployment                                                  | 62 |

|          |     |                 | 1.3.2.1    | Hardware Platforms                                                 | 62 |

|          |     |                 | 1.3.2.2    | Deployment Example                                                 | 64 |

|          |     | 1.3.3           | Software   | e Radio Engines                                                    | 65 |

|          |     |                 | 1.3.3.1    | GNU Radio                                                          | 65 |

|          |     |                 | 1.3.3.2    | RFNoC                                                              | 66 |

|          |     |                 | 1.3.3.3    | IRIS                                                               | 66 |

|          | 1.4 | Conclu          | usion      |                                                                    | 66 |

| <b>2</b> | HD  | $\mathbf{CRAN}$ | I on FP    | GA Platform                                                        | 69 |

|          | 2.1 | Introd          | uction     |                                                                    | 69 |

|          | 2.2 | Partia          | l Reconfig | guration on FPGA Platform                                          | 69 |

|          | 2.3 | HDCF            | RAM Impl   | lementation                                                        | 71 |

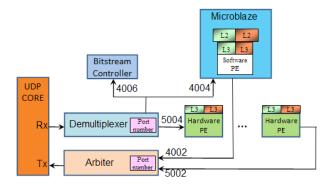

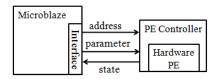

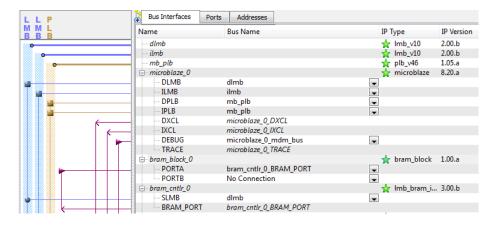

|          |     | 2.3.1           | Virtex 5   | Platform                                                           | 71 |

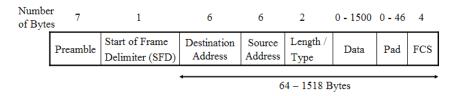

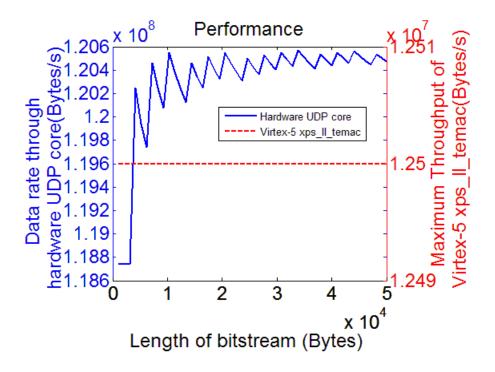

|          |     |                 | 2.3.1.1    | Data transfer between UDP core and Microblaze                      | 78 |

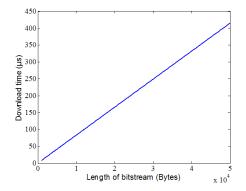

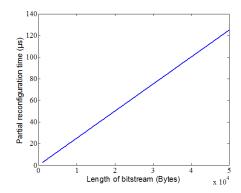

|          |     |                 | 2.3.1.2    | The Speed of Downloading FPGA Partial Bitstreams through           | h  |

|          |     |                 |            | UDP                                                                | 81 |

|          |     |                 | 2.3.1.3    | Discussion on the Reconfiguration time                             | 83 |

|          |     | 2.3.2           | Zynq-70    | 00 Platform                                                        | 85 |

|          |     |                 | 2.3.2.1    | $\operatorname{HDCRAM}$ implementation on ZC702 Evaluation Board . | 85 |

|          |     |                 | 2.3.2.2    | Case study                                                         | 88 |

|          | 2.4 | Conclu          | usion      |                                                                    | 93 |

| 3        | Met | trics o         | n FPGA     | Platform                                                           | 95 |

|          | 3.1 | Introd          | uction     |                                                                    | 95 |

|          | 3.2 | Useful          | Metrics of | on FPGA Platform                                                   | 96 |

|          |     | 3.2.1           | Voltage    |                                                                    | 96 |

|          |     |                 | 3.2.1.1    | How to Get It                                                      | 97 |

|          |     |                 | 3.2.1.2    | How to Use It                                                      | 99 |

<u>x</u> contents

|   |     | 3.2.2  | Temperature                                                    | 99         |

|---|-----|--------|----------------------------------------------------------------|------------|

|   |     |        | 3.2.2.1 How to Get It                                          | 99         |

|   |     |        | 3.2.2.2 How to Use It                                          | 102        |

|   |     | 3.2.3  | Current                                                        | 102        |

|   |     |        | 3.2.3.1 How to Get It                                          | 102        |

|   |     |        | 3.2.3.2 How to Use It                                          | 104        |

|   |     | 3.2.4  | Frequency                                                      | 104        |

|   |     | 3.2.5  | Area, Position, and Resource                                   | 105        |

|   |     |        | 3.2.5.1 How to Get Them                                        | 105        |

|   |     |        | 3.2.5.2 How to Use Them                                        | 106        |

|   |     | 3.2.6  | Activity Rate                                                  | 107        |

|   |     |        | 3.2.6.1 How to Get It                                          | 107        |

|   |     |        | 3.2.6.2 How to Use It                                          | 108        |

|   |     | 3.2.7  | Serial / Parallel                                              | 108        |

|   |     | 3.2.8  | Power Consumption                                              | 108        |

|   |     |        | 3.2.8.1 How to Get It                                          | 109        |

|   |     |        | 3.2.8.2 How to Use It                                          | 111        |

|   |     | 3.2.9  | Performance to Power Consumption Ratio (PTCR)                  | 111        |

|   |     | 3.2.10 | Working Mode                                                   | 111        |

|   | 3.3 | Discus | ssion About the Metrics                                        | 111        |

|   | 3.4 | Case S | Study                                                          | 113        |

|   |     | 3.4.1  | Parallel vs. Serial                                            | 114        |

|   |     | 3.4.2  | Power Consumption with Different Number of Taps                | 117        |

|   |     | 3.4.3  | Evaluation of the Relationship between Power Consumption, Per- |            |

|   |     |        | formance and Resources                                         | 119        |

|   |     | 3.4.4  | Metrics Management by HDCRAM                                   | 120        |

|   |     |        | 3.4.4.1 Case 1                                                 | 120        |

|   |     |        | 3.4.4.2 Case 2                                                 | 120        |

|   | 3.5 | Conclu | asion                                                          | 121        |

| 4 | OF  | DM tra | ansmitter and receiver example                                 | <b>123</b> |

|   | 4.1 | Introd | uction                                                         | 123        |

${f xi}$

|    | 4.2  | OFDM system model                                                       | 124   |

|----|------|-------------------------------------------------------------------------|-------|

|    | 4.3  | Implementation Platform                                                 | 125   |

|    | 4.4  | FFT implementation using partial reconfiguration                        | 125   |

|    |      | 4.4.1 Resource Utilization                                              | 128   |

|    |      | 4.4.2 Transform time                                                    | 130   |

|    |      | 4.4.3 Reconfiguration time                                              | 130   |

|    |      | 4.4.4 Power consumption                                                 | 131   |

|    | 4.5  | Scenario 1 : Modulation Adaptation                                      | 133   |

|    | 4.6  | Scenario 2 : Management of FFT implementation type depending on the     |       |

|    |      | hardware resource utilization                                           | 136   |

|    | 4.7  | Scenario 3 : Management of FFT implementation type depending on the     |       |

|    |      | battery level                                                           | 139   |

|    | 4.8  | Scenario 4 : Modify the FFT size according to the network/user order $$ | 141   |

|    | 4.9  | Scenario 5 : Merge them together                                        | 143   |

|    | 4.10 | Conclusion                                                              | 149   |

| 5  | Con  | clusions and Future Work                                                | 151   |

|    | 5.1  | Conclusions                                                             | 151   |

|    | 5.2  | Future Work                                                             | 153   |

| Α. |      | J:                                                                      | 1 5 5 |

| A. | ppen | dix                                                                     | 155   |

| A  | Har  | dware UDP Core                                                          | 157   |

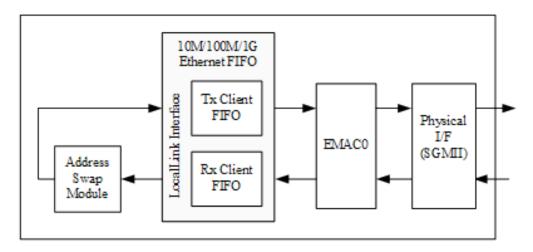

|    | A.1  | $ Introduction \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                  | 157   |

|    | A.2  | Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC Wrapper                    | 158   |

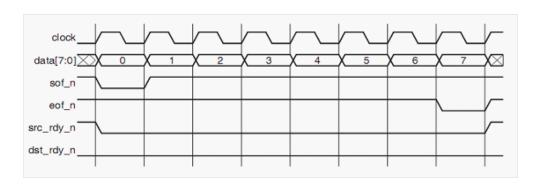

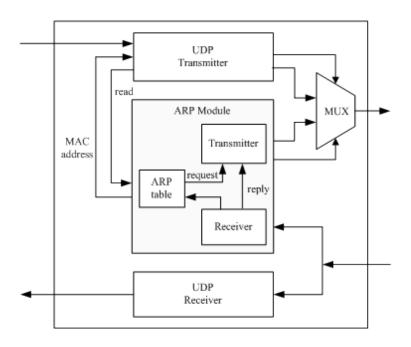

|    | A.3  | UDP module                                                              | 160   |

|    |      | A.3.1 UDP Receiver                                                      | 160   |

|    |      | A.3.2 UDP Transmitter                                                   | 162   |

|    |      | A.3.3 UDP module test                                                   | 163   |

|    | A.4  | ARP module                                                              | 164   |

|    |      | A.4.1 ARP Receiver                                                      | 165   |

|    |      | A.4.2 ARP Transmitter                                                   | 165   |

| ••  |          |

|-----|----------|

| X11 | contents |

|              | A.5    | Architecture                            | 166 |

|--------------|--------|-----------------------------------------|-----|

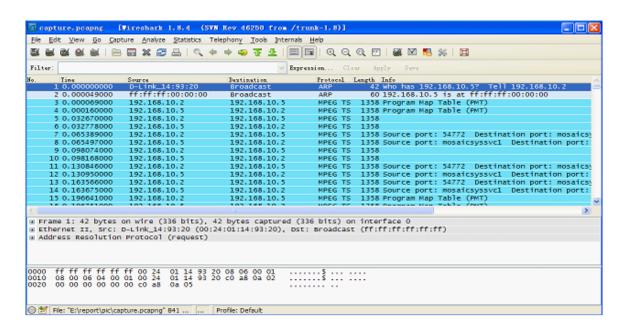

|              | A.6    | Test and validation                     | 167 |

|              | A.7    | Conclusion                              | 170 |

| $\mathbf{B}$ | ML     | 506 Evaluation Platform                 | 173 |

| $\mathbf{C}$ | ZC7    | 702 Evaluation Board                    | 177 |

|              | C.1    | Zynq-7000 AP SoC architecture           | 179 |

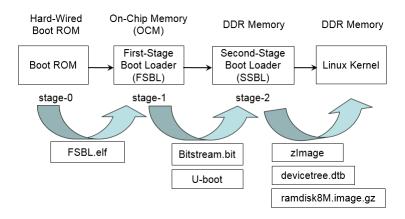

|              | C.2    | Boot Stages                             | 180 |

|              |        | C.2.1 Stage-0 Boot (BootROM)            | 181 |

|              |        | C.2.2 Stage-1 (First-Stage Bootloader)  | 182 |

|              |        | C.2.3 Stage-2 (Second-Stage Bootloader) | 182 |

| D            | FFT    | Γ implementation architectures          | 183 |

|              | D.1    | Pipelined Streaming I/O                 | 183 |

|              | D.2    | Radix-2 Burst I/O                       | 184 |

| Li           | st of  | Abbreviations                           | 187 |

| Li           | st of  | Figures                                 | 191 |

| Li           | st of  | Tables                                  | 197 |

| Pι           | ıblica | ations                                  | 199 |

| Bi           | bliog  | graphy                                  | 201 |

# Résumé

#### Introduction

Cette thèse s'intéresse à la mise en œuvre d'équipements sur plateformes hétérogènes.

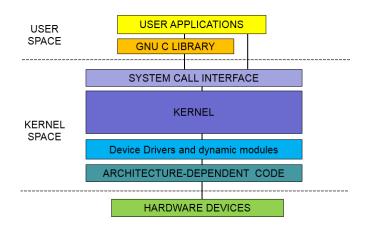

Le contexte principal est celui de l'Ecoradio. A savoir l'étude et le développement de systèmes de radiocommunications économes en énergie, qui de ce simple fait auront une empreinte carbone beaucoup plus faible que les systèmes actuels. Plus précisément nous nous intéressons au domaine de l'Ecoradio Intelligente au niveau électronique d'un équipement. L'Ecoradio est rapidement présentée au chapitre 1-1. Nous (équipe SCEE) avons montré depuis plusieurs années que la Radio Intelligente (RI) peut être un outil très efficace pour réussir à atteindre une Ecoradio. La RI est résumée au chapitre 1-2. Dans ce contexte de RI, les équipements sont considérés comme intelligents car ils obéissent au cycle intelligent proposé pour la Radio Intelligente. Utiliser la RI sous contrainte de consommation d'énergie pour atteindre une Ecoradio, est proposé au chapitre 1-3 et cela aboutit au concept d'Ecoradio Intelligente Les équipements RI étudiés étant complexes et adaptatifs (par principe de la RI) il est nécessaire de les gérer de manière automatique et autonome : c'est précisément le but du gestionnaire développé par l'équipe SCEE depuis une dizaine d'années. Ce gestionnaire, nommé HDCRAM pour Hierarchical and Distributed Cognitive Radio Architecture Management est utilisé pour gérer les équipements étudiés dans cette thèse. Celui-ci est présenté au chapitre 1-4.

Après avoir présenté dans ce premier chapitre le contexte et les outils de base qui serviront à la mise en œvre des équipements étudiés, le second chapitre propose d'implanter le gestionnaire HDCRAM sur des plates formes hétérogènes. En particulier, l'apport et l'intérêt de la Reconfiguration Partielle (RP) de FPGA sera étudié dans ce contexte. Dans le troisième chapitre, les métriques, plus particulièrement celles relatives à l'état de

$oldsymbol{2}$

la plate-forme d'un point de vue électronique, nécessaires à une prise de décision sous contrainte d'économe d'énergie sont étudiées. Elles sont identifiées, leur accessibilité est précisée et leur utilisation dans notre contexte est présentée. Dans le quatrième chapitre la mise en œuvre de l'ensemble des techniques étudiées lors de cette thèse est réalisée pour un système de type émission/réception. Les scénarios, les métriques utilisées lors de ces scénarios, les algorithmes de décision ainsi que le déploiement d'HDCRAM sont détaillés. L'implantation temps réel sur plate-forme du système permet de conclure sur les gains attendus et offre une possibilité de démonstration de l'ensemble. Celle-ci sera présentée lors d'un Workshop ETSI en mars et lors de la soutenance.

#### 1 Contexte et Position du problème

#### 1.1 L'Eco Radio

Il y a quelques dizaines d'années, le développement durable (DD) n'était la préoccupation que de quelques groupes écologistes. Maintenant, depuis l'assemblée générale des Nations Unies de décembre 1987 et la résolution 42/187 [1], ce problème est devenu une préoccupation de la société. La commission Bruntland a défini le DD comme étant un développement qui : "meets the needs of the present without compromising the ability of future generations to meet their own needs". Depuis plusieurs conférences, organisées sous l'égide des Nations Unies, ont confirmé l'importance du DD (de Rio de Janeiro-1992 à Copenhague-2009 et tout récemment la COP 21 à Paris en décembre 2015). L'un des problèmes le plus important que doit prendre en compte le DD est le changement climatique et l'émission de  $CO_2...$

Même s'il est clair que les principaux contributeurs en émission de  $CO_2$  sont la production d'électricité, le transport et l'industrie, les Technologies de l'Information et de la Communication (TIC) y contribuent pour une part non négligeable. En effet, actuellement, 3 % de l'énergie mondiale sont consommées par les TIC, ce qui est à l'origine de 2 % des émissions de  $CO_2$  (ce qui est comparable à l'émission de  $CO_2$  de l'aviation civile mondiale!), ces chiffres continuent de croitre régulièrement malgré les efforts mis en œuvre par les différents acteurs du domaine.

Réduire le niveau d'émission des ondes électromagnétiques est un autre aspect du DD pour les radios communications. Cette réduction offrira une meilleure coexistence entre tous les systèmes et réduira le niveau d'exposition des utilisateurs. Le premier papier relatif à l'écoradio (sous l'angle de la réduction du niveau des ondes électromagnétiques), grâce au concept de radio intelligente, a été présenté lors d'une assemblée générale de l'URSI [2].

Mais, à cette époque, ce type de préoccupation n'était pas à la mode.

L'écoradio  $^{(1)}$  est souvent limité à l'aspect efficacité énergétique, mais nous l'envisageons, dans cette thèse, dans un sens plus large. Dans [3], les différentes implications du DD dans le domaine des radiocommunications ont été décrites. Ces implications vont de l'émission de  $CO_2$  (à cause de la consommation électrique) au recyclage des équipements et des ondes transmises, en passant par la pollution électromagnétique (avec les conséquences de l'exposition aux ondes des utilisateurs). Parmi l'énorme activité sur le sujet quelques projets sont (ou ont été) particulièrement importants et productifs. Nous nous limiterons donc à la présentation de ceux-ci. Plus de projets sont présentes en section 1.1.2 dans le corps du document.

#### 1.1.1 Au niveau international

#### 1. GREENTOUCH

Il s'agit d'un projet très ambitieux piloté par Alcatel, dont l'objectif est de décroître d'un facteur 1000 la consommation énergétique du réseau [4]. Cette décroissance est analysée segment par segment avec des objectifs différents suivant les segments et cela malgré l'augmentation des débits. Parmi les nombreux résultats de ce projet, des architectures, des technologies, des composants, des algorithmes ont été proposés.

#### 2. EARTH

Le projet EARTH pour Energy Aware Radio and NeTwork TecHnologies a été un projet financé lors du programme FP7 de la Commission Européenne [5]. Ce projet a été

<sup>(1).</sup> Le concept anglais de Green Radio pourrait être traduit radio verte. Mais le terme technique Green a récemment été étudié et la traduction éco a été adoptée au journal officiel, c'est pour cela que nous utilisons la formulation écoradio.

$oldsymbol{4}$  Résumé

un des premiers à s'intéresser au problème de l'Ecoradio avec un objectif ambitieux de réduire de 50% la consommation des systèmes de télécom mobiles. Ce projet a été à l'origine de nombreuses idées, définitions et de nombreux algorithmes aujourd'hui reconnus et utilisés par de nombreux autres projets. Parmi d'autres citons les idées d'allumage/exctinction des Stations de Base en fonction du nombre d'usagers, d'allumage/exctinction de l'amplificateur de puissance en fonction des périodes sans transmission, d'algorithmes pour augmenter ces périodes, les protocoles coopératifs, le cell breathing, etc...

#### 3. C2POWER

Ce projet est intéressant, car il est exactement dans la lignée de ce que nous appelons l'Ecoradio Intelligente (voir section suivante) [6]. Il se propose d'étudier comment l'intelligence et les stratégies de coopération permettent de réduire globalement la consommation énergétique. Les résultats de ce projet ont été considérés comme très positifs, ce qui nous conforte dans cette thèse dont le contexte est justement l'Ecoradio Intelligente au niveau électronique d'un équipement.

#### 1.1.2 Au niveau Français

#### 1. SOGREEN

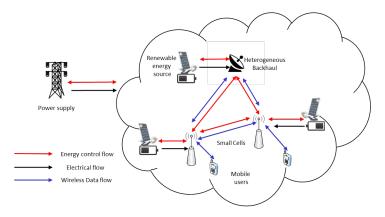

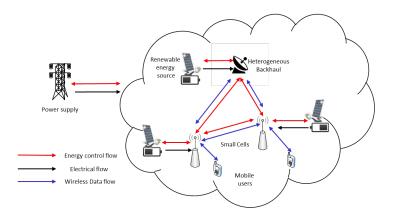

FIGURE 1 – SOGREEN.

Suivant une approche multidisciplinaire, SOGREEN propose un système de gestion intelligente de l'énergie basé sur une intégration étroite entre réseau cellulaire et smart grid, escomptant une amélioration considérable de l'efficacité éco-énergétique [7]. Comme cela est indiqué sur la Figure 1 le réseau de télécommunications cellulaire et le Réseau Electrique Intelligent (REI) sont interconnectés, de manière à globalement optimiser l'énergie consommée. Dans ce schéma, nous pouvons distinguer trois flux différents : celui correspondant aux données du réseau de communications, celui correspondant au REI et enfin celui correspondant aux communications spécifiques du REI. Dans ce projet sont menées des études d'algorithme de prise de décision globale, au niveau de chaque sous réseau. L'application du gestionnaire HDCRAM (voir section suivante) est aussi proposée dans ce projet.

#### 2. TEPN

TEPN est un projet du laboratoire d'excellence Breton CominLabs Le but de ce projet est d'adapter la consommation du réseau à la charge réelle de celui-ci [8]. Parmi les sujets étudiés, figurent la définition de métriques prenant en compte la globalité du problème, l'étude de solutions permettant de diminuer la consommation des amplificateurs de puissance au niveau des stations de base et l'étude d'algorithme de prise de décision sous différentes contraintes et métriques, notamment en se focalisant sur les algorithmes d'apprentissage qui apprennent le comportement du réseau afin de l'optimiser.

#### 1.2 La Radio Intelligente

Après avoir, en 1995, proposé le nouveau concept de radio logicielle (RL) ou Soft-Ware Radio en anglais [9], Joe Mitola lors de son travail de thèse s'est intéressé à l'utilisation du spectre. Il a constaté que celui-ci était très mal utilisé, en grande partie sous-utilisé. Il en a déduit qu'une gestion locale, intelligente du spectre permettrait d'augmenter considérablement son taux d'utilisation. Mitola a compris qu'il fallait mettre de l'intelligence à la fois dans le réseau et dans les équipements pour être au plus près des besoins et de la ressource donc au final pour augmenter l'efficacité spectrale : c'est la raison pour laquelle il a proposé la RI (Cognitive Radio en anglais) [10, 11]. Il a montré que celle-ci serait plus efficace si elle était associée à la technologie RL.

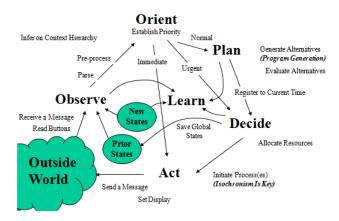

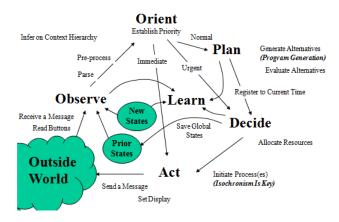

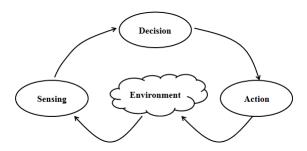

Suivant la description de la Figure 2, un système RI pourra adapter son comportement (fonctionnement) à son environnement grâce à :

$oldsymbol{6}$

FIGURE 2 – Le cycle intelligent de J.Mitola. [10]

- ses capacités d'analyse à travers ses capteurs. La notion de capteurs est, dans notre vision, très large. Elle correspond à tout moyen de fournir de l'information au moteur intelligent qui prendra les décisions. Cette information proviendra de capteurs physiques réels, d'algorithmes de traitement du signal, d'échanges d'information avec les différents nœuds d'un réseau, etc.

- son intelligence qui lui permet de prendre les décisions adéquates (basées sur de l'apprentissage et/ou des bases de connaissance). La connaissance utilisée par la prise de décision est, comme l'information fournie par les capteurs, une notion très large, cela va des paramètres fournis par les capteurs aux considérations technico-économiques, en passant par les règles réglementaires d'utilisation du spectre. Dans le contexte de cette thèse, une contrainte particulière est associée à cette fonction de prise de décision. Il s'agit de la contrainte DD, sous les déclinaisons contraintes de consommation minimale, non pollution électromagnétique...

- ses capacités d'auto reconfiguration (offertes par la technologie support : la RL) pour modifier son fonctionnement.

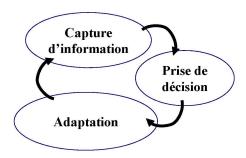

Un schéma simplifié représentant ce fonctionnement est donné sur la Figure 3.

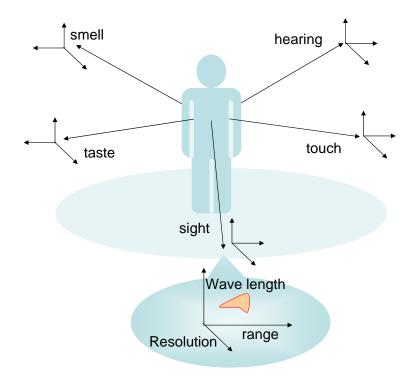

Le mot capteur doit être pris au sens large. Il s'agit de tout moyen donnant de l'information de toute nature pouvant être mise à profit dans le cycle intelligent pour optimiser le lien radio afin d'améliorer le service rendu.

Figure 3 – Cycle intelligent simplifié en trois étapes.

Ces différents moyens vont des capteurs au sens classique du terme (microphone, etc.) aux capteurs appelés intelligents dans la littérature et fournissant une information qui résulte d'un traitement évolué (par exemple la réponse impulsionnelle d'un canal).

Classiquement on peut faire la liste de ces capteurs en fonction de l'environnement considéré comme dans le tableau 1 suivant.

Table 1 – Classification d'une liste (non exhaustive) de capteurs en fonction de l'environnement. [12]

| Capteurs                                                                | Environnent       |

|-------------------------------------------------------------------------|-------------------|

| occupation spectrale, trous ou blancs dans le spectre                   | Électromagnétique |

| rapport Signal à Bruit, réponse impulsionnelle du canal, etc            |                   |

| nombre et positions des Hot Spot, et stations de base, des utilisateurs |                   |

| Standards utilisables à proximité, Opérateurs et services à proximité   | Réseau            |

| charge sur un lien radio, etc                                           |                   |

| niveau de batterie, consommation énergétique                            |                   |

| taux d'utilisation des circuits (FPGA), de la ressource de calcul       | Matériel          |

| taux d'occupation de la mémoire                                         |                   |

| température du matériel                                                 |                   |

| micro, caméra, appareil photo, identification de l'usager               |                   |

| Position spatiale, vitesse, heure, intérieur/extérieur                  | Utilisateur       |

| préférences, profil de l'utilisateur                                    |                   |

| détection, reconnaissance de visage, reconnaissance de voix, etc        |                   |

Le chapitre 3 de cette thèse discutera clairement des métriques (capteurs) relatifs au matériel dans le tableau.

$R\acute{e}sum\acute{e}$

#### 1.2.1 La gestion du spectre

Contrairement à une idée reçue, le spectre est une ressource publique, seule son utilisation est privée. Ce qui fut le cas lors de la vente des licences UMTS.

Le spectre est une ressource naturelle finie. En effet une fréquence n'existe que parce qu'elle peut être générée. De ce point de vue, il est nécessaire d'avoir une quantité d'énergie suffisante pour générer la fréquence et la diffuser. Nous pouvons donc parler de ressource finie puisqu'elle dépend elle-même de ressources énergétiques finies.

Cette ressource finie peut être utilisée indéfiniment (tant que la ressource énergétique est disponible pour générer l'onde électromagnétique).

Les règles d'attribution actuelles des fréquences obéissent à un processus très compliqué et long à mettre en œuvre. L'allocation des fréquences est aujourd'hui fixe et attribuée sur la base de services suivant des règles internationales rigides, elles-mêmes discutées tous les 5 ans (lors de la Conférence Mondiale Administrative) (2). Une telle allocation aboutit à une situation dans laquelle il apparait clairement que l'ensemble du spectre est alloué. Une première conclusion hâtive serait de dire qu'il n'y a plus de place disponible dans ce spectre.

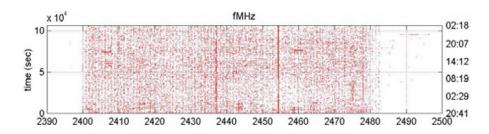

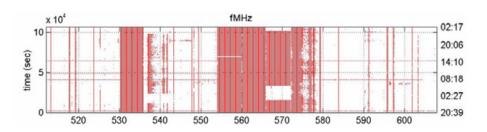

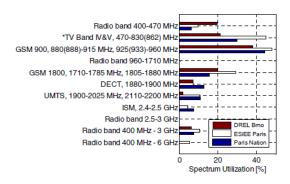

Or les études ont montré que le spectre pouvait être alloué mais non utilisé (cas des bandes réservées aux militaires). Une analyse de l'occupation spectrale telle que celle présentée dans la figure 4 pour la bande à 2.4 GHz et la figure 5 pour la bande TV montre qu'à un instant précis (le 1er septembre 2004) et dans un lieu donné (à New-York) le spectre est sous-utilisé (une utilisation de l'ordre de quelques %). Ce constat a donné naissance à la notion de "Hic et Nunc", qui veut dire, qu'indépendamment de l'attribution des fréquences, le spectre peut être disponible en un lieu et à un instant donné. Par conséquent dans ce lieu et à l'instant considéré, si l'équipement est capable de connaître le spectre utilisé, il pourra établir une communication dans les bandes spectrales sous-utilisées. C'est ce qui est aussi appelé, dans la littérature, une communication opportuniste.

Les techniques mises en œuvre pour identifier l'occupation spectrale sont grossièrement de deux types comme décrit ci-après :

<sup>(2).</sup> WARC process (World Administrative Radio Conference)

FIGURE 4 – Les mesures d'occupation de la bande 2.4 GHz. [13]

FIGURE 5 – Les mesures d'occupation de la bande TV. [13]

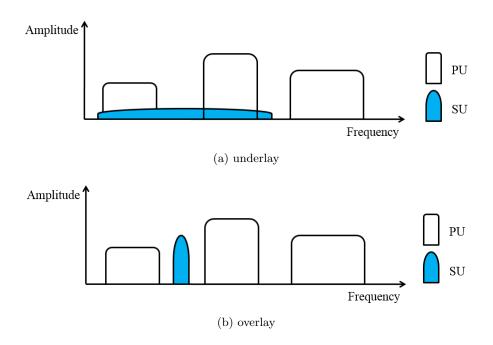

Figure 6 – Dynamic spectrum access modes.

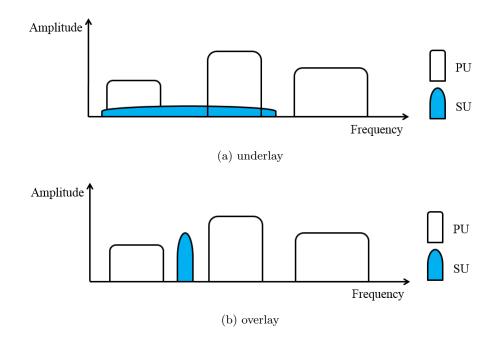

#### La technique underlay

Comme son nom le laisse supposer cette technique consiste à insérer un nouveau signal

10 Résumé

dans le même spectre et en même temps que les signaux d'origine. La contrainte évidente est que le signal additionnel ne perturbe en rien la qualité des signaux d'origine. C'est une contrainte très forte et très peu de systèmes la remplissent.

Dans ce contexte Haykin [14] a défini la notion de température d'interférence.

#### La technique overlay

Lorsque l'on parle d'accès opportuniste au spectre, de détection de blancs du spectre, de trous dans le spectre et d'insertion du signal d'un utilisateur secondaire, c'est généralement par une technique "overlay". Cette technique nécessite 5 étapes successives.

- un filtrage

- une détection de présence ou d'absence d'un utilisateur primaire dans la bande considérée.

- une qualification de la qualité de cette bande

- une prise de décision quant à l'utilisation par l'utilisateur secondaire, grâce aux différentes informations : présence, qualité,...

- une insertion du signal dans le spectre (cette insertion doit se faire de manière très précautionneuse, de façon à ne pas perturber les bandes adjacentes,...)Des modulations avec des DSP présentant des affaiblissements importants dans les bandes adjacentes seront préférées (cas par exemple de l'OFDM/OQAM)

Chacune des ces étapes a des contraintes très spécifiques et nécessite des algorithmes de traitement du signal avancés.

#### 1.2.2 Une vision plus globale

L'équipe SCEE (pour rappel, qui accueille cette thèse), a proposé un modèle en trois couches pour expliciter sa vision de la RI. (voir figure 7)

- une couche de haut niveau, qui regroupe essentiellement la couche application, ainsi que les interfaces de type homme-machine, appelée couche supérieure;

- une couche intermédiaire dans laquelle on retrouve les couches Transport et Réseau,

- une couche de bas niveau dans laquelle on retrouve les couches MAC et physique,

appelée couche inférieure.

| Les capteurs relatifs à la couche                                                                                      | Les trois couches                         | Quelques concepts en vogue dans la<br>littérature |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------|

| Profil utilisateur : (prix , abonnement, choix personnels (radio écologique)) Son, image,position, vitesse, sécurité   | Interface Homme/machine (IHM) Application | "Context Aware"                                   |

| Handover vertical inter-réseaux et intra réseaux, standards, charge sur un lien radio,                                 | Transport,<br>Réseau                      | Interopérabilité<br>Réseaux ambiants              |

| Type d'accès, puissance, modulation,<br>codage,<br>Fréquence, handover<br>Estimation de canal<br>Antennes,consomation, | Liaison,<br>Physique, médium              | Adaptation de liens                               |

|                                                                                                                        | "Middleware" et couche d'abstraction      |                                                   |

| Véritable Radio Logicielle, large bande                                                                                |                                           |                                                   |

Figure 7 – Une vision multicouches de la RI. [12]

L'ensemble de ces couches fonctionne sur une plate-forme RL (si possible idéale), mais ce modèle fonctionne aussi avec une plate-forme radio logicielle restreinte. Ces plates-formes radio logicielle reposent sur une architecture matérielle d'exécution, qui en toute généralité est hétérogène. Cette plate-forme est idéalement abstraite à travers une couche d'abstraction, qui offre une transparence en termes d'implantation de composants logiciels de traitement du signal que l'on y exécute. Dans le modèle de la figure 7, nous avons dans la colonne de gauche fait figurer certains capteurs. Dans la colonne de droite sont cités les domaines de recherche relatifs à la couche en question avec lesquels la RI entretient des liens très étroits. Bien entendu comme notre objectif est d'optimiser le fonctionnement de ces trois couches de manière intelligente, la RI aura aussi un lien très fort avec le domaine de l'optimisation intercouches. Ce que l'on trouve dans la littérature sous la dénomination « radio opportuniste » est, suivant le modèle précédemment présenté, la restriction à la sous-partie de la couche physique de la RI concernée par la gestion du spectre.

#### 1.3 l'Ecoradio Intelligente

L'EcoRadio Intelligente (ERI) est une radio intelligente (RI) qui prend en compte le développement durable (en particulier l'efficacité énergétique) comme une contrainte additionnelle dans le processus de décision du cycle intelligent. L'ERI consiste à : « décroitre le niveau des ondes électromagnétiques en envoyant le signal adéquat dans la direction

12 Résumé

désirée, avec la puissance suffisante, quand cela est nécessaire, tout en conservant la même qualité de service ». Il s'agit du concept d'« ondes utiles ». Pour cela, la RI grâce à ses capteurs, qui permettent d'avoir une vision locale de l'environnement, permettra de répondre efficacement à ce concept d'« ondes utiles ».

D'un point de vue théorique, le gain en efficacité spectrale, quelle que soit la manière d'obtenir ce gain, pourrait être utilisé pour diminuer la puissance des ondes transmises. Cependant, d'un point de vue pratique, l'ensemble des acteurs des télécommunications préfère utiliser ce gain pour accroître le débit transmis (donc le nombre d'utilisateurs) à puissance constante plutôt que de diminuer la puissance à débit constant. Par conséquent, notre approche pourrait sembler en contradiction avec les considérations économiques des acteurs des télécommunications. Or, il n'en est rien, car d'une part diminuer la facture énergétique est devenu une préoccupation majeure de ces différents acteurs et d'autre part l'ERI consiste à : « décroître le niveau des ondes électromagnétiques en envoyant le signal adéquat dans la direction désirée, avec la puissance suffisante, quand cela est nécessaire, tout en conservant la même qualité de service ». Il s'agit du concept d'«ondes utiles»

Pour cela, la RI grâce à ses capteurs, qui permettent d'avoir une vision locale de l'environnement, permettra de répondre efficacement à ce concept d'« ondes utiles ». Cela devrait éviter la pollution de certaines bandes, comme la bande de radioastronomie. En effet, l'écoute passive dans cette bande est très perturbée par le niveau de plus en plus élevé des ondes des signaux de radiocommunications.

Comme déjà expliqué précédemment, nous aimerions obtenir cet éco-comportement dans un sens le plus large possible (diminution de la consommation d'énergie pour réduire l'empreinte carbone, équilibre entre l'efficacité énergétique et l'efficacité spectrale, contrôle de la pollution électromagnétique, impact sur les personnes, cycle de vie des équipements, etc.). Nous avons déjà identifié qu'une intelligence répartie dans le réseau est une condition nécessaire. Par conséquent nous proposons d'utiliser la Radio Intelligente comme une technologie potentielle pour atteindre l'objectif. Cette solution pourrait être implémentée soit côté terminal mobile ou côté station de base, partout dans le réseau radio hétérogène.

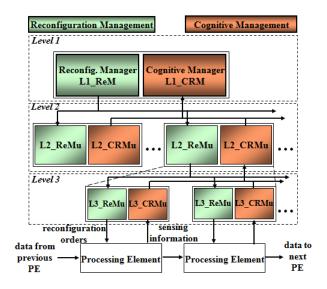

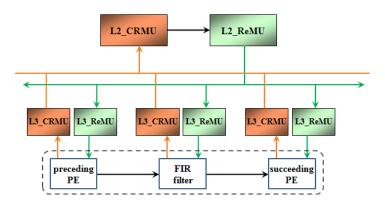

#### 1.4 HDCRAM

Cette section présente une architecture de gestion, initialement proposée pour gérer un équipement de RI. Son acronyme est HDCRAM ce qui signifie en anglais Hierarchical and Distributed Cognitive Radio Architecture Management. HDCRAM peut être ajouté à tout système existant afin de transformer ce dernier en un système intelligent capable de prendre et de gérer des décisions autonomes. Par exemple HDCRAM a été récemment appliqué au Réseau Electrique Intelligent (REI) ou smart grid.

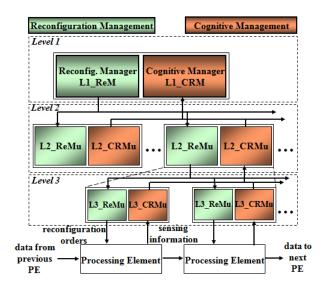

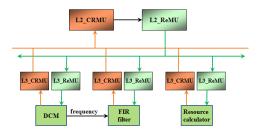

FIGURE 8 – A schematic example of HDCRAM architecture.

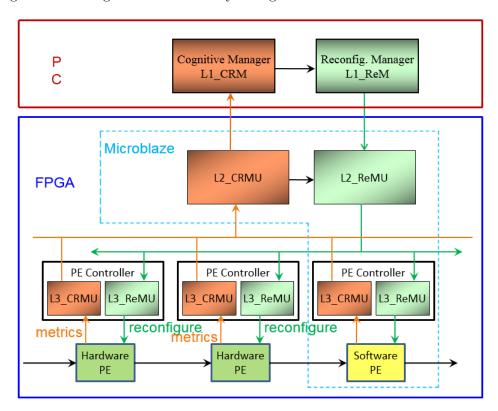

HDCRAM est présenté sur la Figure 8. Le cycle intelligent de la Figure 3 montre qu'un équipement a trois activités principales, capture de l'information, prise de décision et reconfiguration du système. Dans HDCRAM, la reconfiguration et la gestion de l'intelligence (capture des métriques et prise de décision) suivent deux chemins séparés. HDCRAM est composé de 3 niveaux hiérarchiques ainsi qu'un niveau opérateur qui exécute l'ensemble de la chaîne de transmission.

Cette architecture comprend deux sous-gestionnaires:

Le gestionnaire de l'intelligence noté Cognitive Radio Management Units (CRMu) : Un CRMu échange de l'information seulement d'un niveau inférieur à un niveau supérieur. Cette entité possède l'intelligence et peut prendre des décisions. Dans ce cas, elle envoie ses ordres liés à la décision au gestionnaire de reconfiguration de même niveau.

14 Résumé

Le gestionnaire de re-configuration noté Reconfiguration Management Units (ReMu) : Un ReMu échange de l'information seulement d'un niveau supérieur à un niveau inférieur. Comme indiqué précédemment, il existe aussi un échange d'information possible entre un CRU et un CRMu de même niveau.

Les 3 niveaux se comportent de la façon suivante :

- Le niveau 1 est composé d'un seul couple CRM/L1 ReM et est le gestionnaire général du système. C'est à ce niveau que se prennent les décisions globales qui ont un impact sur l'ensemble du système.

- Le niveau 2 est composé d'un certain nombre de couples (L2 CRMu/L2 ReMu). Ils fournissent au niveau L1 l'information utile pour qu'il puisse prendre une décision. Il transmet l'information du niveau L3 sous une forme compressée, il s'agit d'abstraire l'information. S'il possède toute l'information nécessaire, une décision peut être prise à ce niveau.

- Le niveau 3 est composé d'un certain nombre de couples (L3 CRMu/L3 ReMu). Chacun de ces couples est associé à un opérateur. L3 ReMu est l'entité qui est en charge de la reconfiguration de son opérateur et L3 CRMu est en charge de traiter l'information provenant de l'opérateur (une métrique par exemple) et il peut si l'information dont il dispose est suffisante prendre une décision locale.

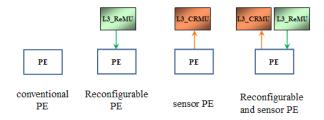

- Un opérateur est un composant (une fonction du système) qui est soit reconfigurable

soit une mesure de métrique (par exemple un filtre ou un SNR).

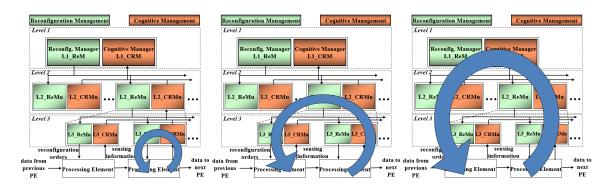

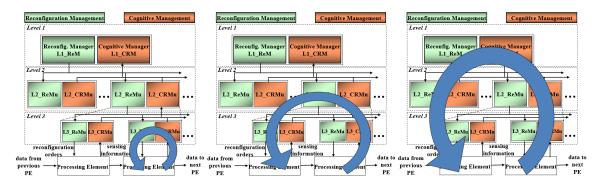

L'intelligence est distribuée dans les 3 niveaux hiérarchiques et à différents emplacements à chaque niveau. De ce fait, il est possible de prendre des décisions à plusieurs niveaux et ainsi de générer des cycles de décision plus ou moins rapides.

- Une décision locale , simple et rapide au niveau 3 (voir le petit cercle de la figure

9).

- Si la décision est plus complexe à prendre et met en jeu plusieurs opérateurs gérés par le même niveau 2, alors elle est prise au niveau 2 (cycle intermédiaire sur la figure 9).

- Enfin, si la décision implique de nombreux opérateurs qui ne sont pas tous gérés par le même L2 alors la décision sera prise au niveau L1 (grand cycle sur la figure 9).

En résumé HDCRAM possède les caractéristiques suivantes :

FIGURE 9 – Scale of the cognitive cycle: small (left), medium (middle), and large (right).

- Deux chemins totalement indépendants, un pour la remontée et la gestion de l'intelligence et un second pour redescendre les ordres de reconfiguration.

- HDCRAM est un modèle d'architecture indépendant des traitements réalisés dans les boîtes interconnectées.

- HDCRAM est un squelette d'une architecture de gestion.

- Pour un scénario donné le modèle HDCRAM est implémenté de manière spécifique.

- Il y a 3 niveaux de décision possible, ce qui correspond à 3 cycles intelligents de taille différente dans l'architecture.

- HDCRAM peut être appliqué à n'importe quel système complexe.

- Les règles et les connections entre les boites permettent de déployer des scénarios intelligents et de spécifier tous les éléments nécessaires, ainsi que leurs connections pour implémenter ce scénario.

- Une implémentation spécifique de HDCRAM peut être émulée, simulée, de façon à pouvoir prédire le fonctionnement d'un système pour un scénario donné.

- Une implémentation spécifique de HDCRAM peut intégrer n'importe quel algorithme de prise de décision.

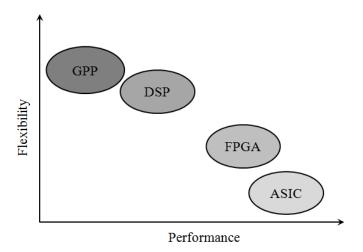

Pour réaliser des équipements de RI, il est nécessaire d'utiliser une plate-forme reconfigurable, qui soit capable de s'adapter à n'importe quel type de traitement et aux différentes contraintes de ces traitements. Ces contraintes peuvent être la flexibilité, la puissance de calcul... . Pour répondre à ces contraintes, une plate-forme hétérogène comportant des composants différents de type GPP, DSP, FPGA, chacun ayant une réponse spécifique à une contrainte particulière, est la solution la plus adaptée. 16 Résumé

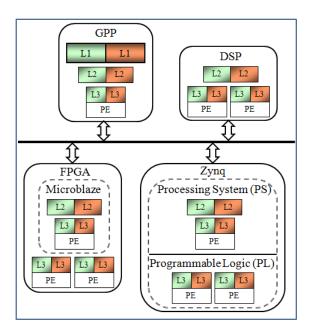

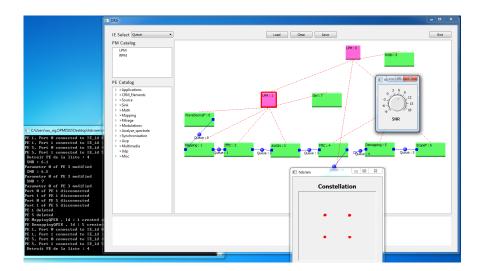

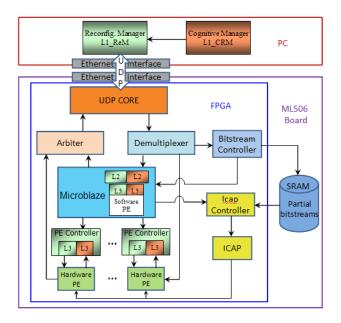

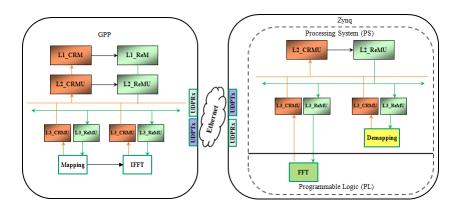

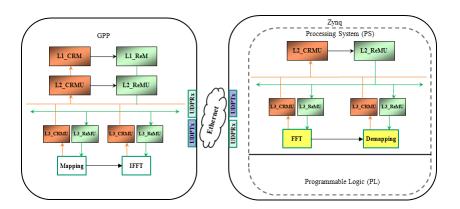

FIGURE 10 – A schematic example of HDCRAM architecture.

Lors d'une thèse précédente le déploiement de HDCRAM sur une cible logicielle de type GPP a été abordé avec succès. Dans cette thèse, notre objectif est de déployer HDCRAM sur une cible matérielle de type FPGA sur une plate-forme hétérogène, c'est précisément l'objet du chapitre 2 suivant que d'étudier ce déploiement.

## 2 Implantation de HDCRAM sur plateformes hétérogènes

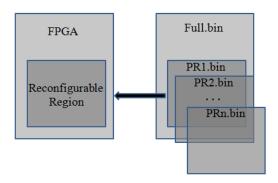

Comme nous l'avons indiqué précédemment HDCRAM a déjà, lors de travaux précédents, été implémenté sur des ressources logicielles. Le but de ce chapitre est donc d'implémenter HDCRAM sur des ressources matérielles, plus précisément sur des FPGA en tirant profit de la Reconfiguration Partielle de FPGA.

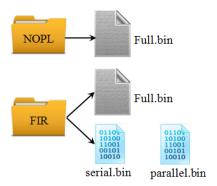

#### 2.1 Reconfiguration Partielle de FPGA

La Reconfiguration Partielle de FPGA permet de modifier dynamiquement des fonctions dans certaines zones du FPGA, permettant à l'application de continuer à fonctionner sur les autres zones, sans aucune interruption des données, du service. En d'autres termes la RP apporte une souplesse équivalente à celle du logiciel dans le monde du matériel. Pour les circuits Virtex la RP est réalisée au travers du port ICAP, qui lit le bitstream partiel correspondant à la nouvelle fonction. Pour les circuits Zynq-7000, celle-ci est réalisée soit au travers du port ICAP ou par l'intermédiaire du port PCAP.

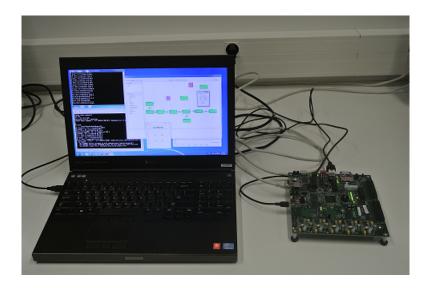

#### 2.2 Implémentation de HDCRAM sur plate-forme Virtex5

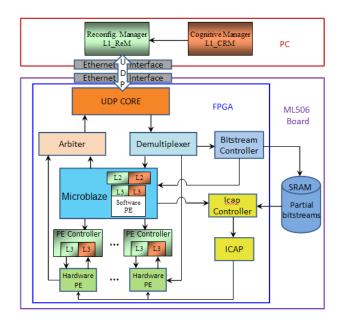

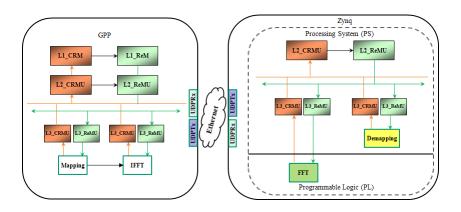

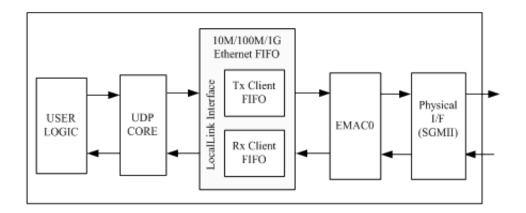

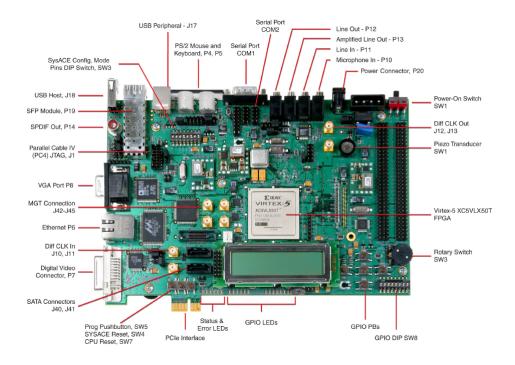

La carte Xilinx ML506 (voir l'annexe B qui décrit cette carte d'évaluation) est connectée à un PC. Le niveau 1 de HDCRAM est implanté sr le PC, donc sur le FPGA sont implantés les niveau 2 et 3 tel que cela est représenté sur la figure 11. L'ensemble des connections entre les différents éléments utilise le protocole UDP, ce qui donne une très grande souplesse car les éléments sont repérables par leurs adresses IP. Un UDP Core a été spécifiquement développé pour les FPGA dans le cadre de cette thèse. Celui-ci est complètement décrit en Annexe A.

FIGURE 11 – The block diagram of the management platform.

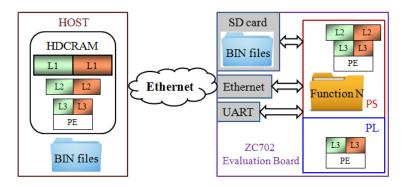

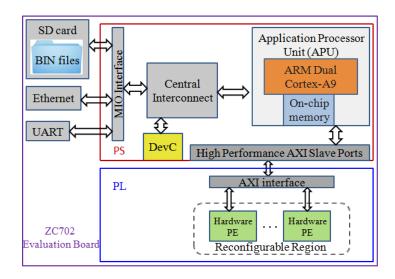

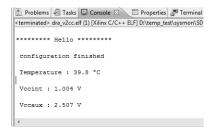

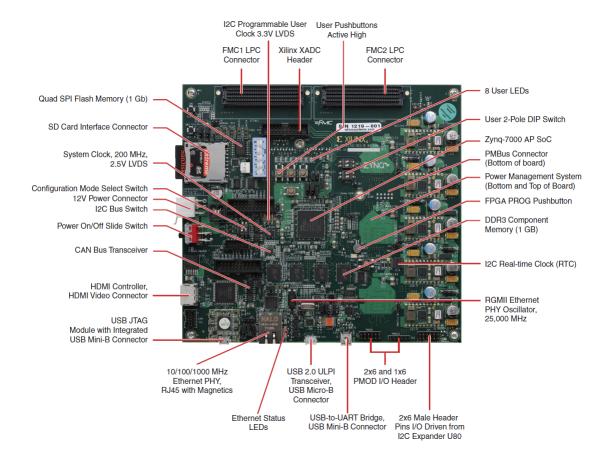

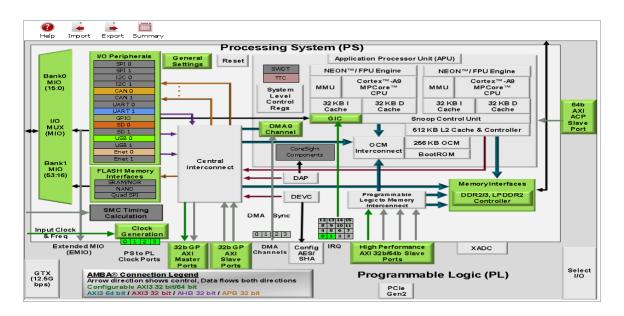

#### 2.3 Implémentation de HDCRAM sur plate-forme Zynq 7000

La carte d'évaluation ZC702 est totalement décrite en Annexe C. Elle comprend un dual core ARM CORTEX pour la partie Processing System (PS) et un FPGA Xilinx

18 Résumé

Artix-7 pour la partie Programable Logic (PL). La figure 12 présente l'implémentation de HDCRAM sur cette plate-forme.

FIGURE 12 – The HDCRAM implementation on the ZC702 evaluation board.

Le niveau L1 est implanté sur le PC. Un niveau L2 est implanté sur la partie PS de la carte. Un opérateur peut être implanté soit en logiciel soit en matériel, par conséquent le niveau L3 associé sera soit sur PS soit sur PL.

Les bitstreams de configuration peuvent être mémorisés soit sur le PC soit sur la mémoire de la carte.

# 3 Etude des métriques liées à la plate-forme dans un contexte d'Ecoradio Intelligente

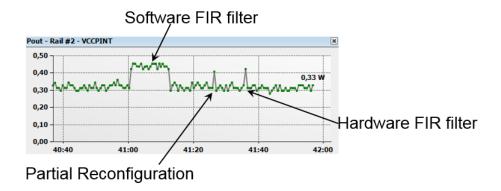

Dans ce chapitre, nous nous intéressons aux métriques permettant de caractériser le fonctionnement d'un équipement et d'optimiser ce fonctionnement d'un point de vue de l'efficacité énergétique. Les différentes métriques accessibles sur une plate-forme sont identifiées, en particulier, celles liées à l'électronique de l'équipement. Chacune est discutée pour savoir comment elle peut être obtenue, et comment elle peut être utilisée pour prendre une décision. Ensuite, ces métriques sont discutées sous différents aspects : accessibilité, statique/dynamique, facilité d'utilisation... Finalement, l'implémentation d'un filtre FIR en série ou parallèle, est discuté sous ses aspects métriques.

#### 3.1 Les différentes métriques

Dans cette section, toutes les métriques identifiées et discutées l'ont été à partir de la plate-forme Xilinx Virtex-5 ML506. Rappelons que cette plate-forme est totalement décrite en Annexe B. Il est donc tout à fait possible que certaines métriques ne s'appliquent pas facilement à d'autres plates-formes.

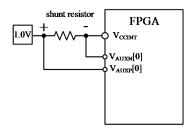

Parmi les métriques identifiées, nous avons la tension, le courant, la fréquence,... Nous décrivons certaines plus en détail ci-après.

#### 3.1.1 La température

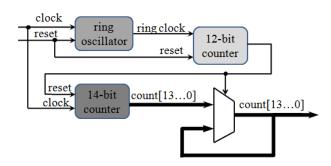

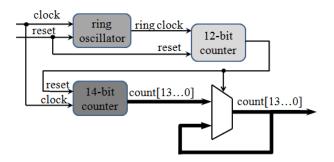

La température est une métrique très utile. Elle peut-être obtenue par les outils Xilinx, tel System Monitor, mais sera, dans ce cas très difficile, voire impossible, à utiliser en fonctionnement. Une autre façon de l'obtenir indirectement est d'utiliser un thermomètre numérique basé sur un Ring Oscillator, dans ce cas il sera possible de l'utiliser en fonctionnement. Nous savons qu'il existe une relation linéaire entre la fréquence de l'oscillateur et la température de la zone. Ce thermomètre utilise très peu de ressources et peut être placé à différents endroits du circuit. Son schéma est donné à la figure 13.

FIGURE 13 – The digital thermal sensor.

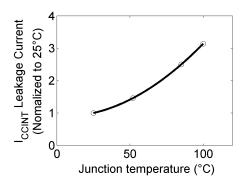

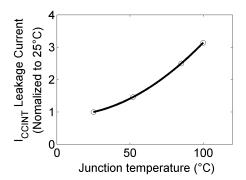

Dans d'autres travaux [15], nous avons montré qu'il existe une relation entre la température et la consommation statique (voir figure 14), cette métrique peut donc servir à connaître la consommation statique et prendre les décisions adéquates. Elle peut aussi être utilisée pour des décisions de sauvegarde comme diminuer la fréquence, la charge de travail, mettre en œuvre le refroidissement pour éviter une surchauffe.

Figure 14 – Leakage current variations with Temperature.

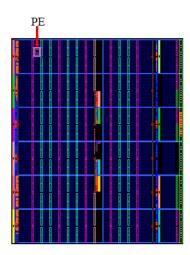

#### 3.1.2 La ressource disponible, la surface et la position d'une fonction

Ces métriques sont connectées les unes aux autres. Elles peuvent être obtenues par le même outil Xilinx PlanAhead. Lors de la phase de design un opérateur peut être dans une certaine position, mais il peut être nécessaire de le modifier en cours de fonctionnement grâce à la RP. Ce cas de figure se produira si plusieurs opérateurs occupent la même position et sont instanciés à différents moments grâce à la RP.

#### 3.1.3 Le taux d'activité

Le taux d'activité d'un opérateur est donné par l'équation (1) :

$$Activity \, rate = \frac{en \times N}{c} \times 100\% \tag{1}$$

Avec c: le durée de la mesure exprimée en nombre de cycles d'horloge.

en : le nombre de cycles d'horloge autorisant l'entrée des données pendant la durée de la mesure.

N: une constante qui donne le nombre de cycles nécessaire pour le traitement d'une donnée en entrée pour obtenir une donnée en sortie.

La Fig. 15 donne un exemple. Dans ce cas si N=1, pendant c=10 cycles, le taux d'activité est =20~%; si N=5, alors taux activité =100~%. Bien sûr ceci est un exemple très simple. c doit être choisi soigneusement, plus c sera grand plus le taux d'activité sera précis.

FIGURE 15 – A timing diagram example.

#### 3.1.4 Implantation série/parallèle

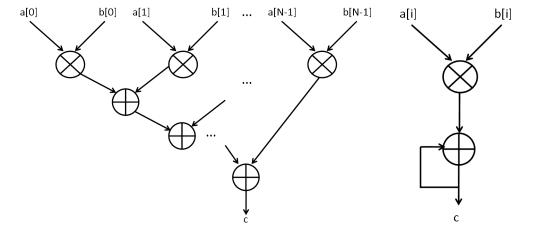

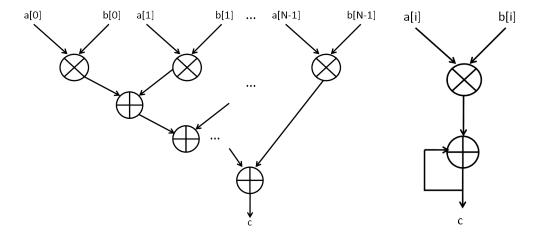

De nombreux opérateurs peuvent être implantés soit en mode série soit en mode parallèle. Prenons l'exemple du calcul de c donné par l'équation (2).

$$c = \sum_{i=0}^{N-1} a[i] \times b[i]$$

(2)

Celle-ci peut-être implantée en mode parallèle (figure 16) ou en mode série (figure 17). Cette métrique peut être définie lors de la phase de design ou modifiée dynamiquement en fonction d'autres métriques (voir l'exemple suivant dans ce chapitre).

FIGURE 16 – Parallel method.

FIGURE 17 – Serial method.

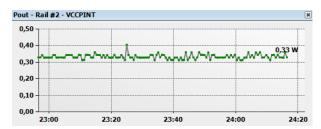

#### 3.1.5 La consommation

Cette métrique est évidemment de la plus grande importance dans notre contexte d'Ecoradio Intelligente. Elle peut être obtenue à partir de la connaissance de la tension

$oldsymbol{22}$  Résumé

et du courant. Elle peut l'être aussi, à partir des outils Xilinx Power Estimator (XPE) et plus particulièrement Xilinx Power Analyzer (XPA), que nous utiliserons par la suite.

Suivant la valeur de cette métrique, l'organe de décision peut décider de modifier tel ou tel paramètre pour diminuer cette consommation.

#### 3.2 Discussion sur les différentes métriques

Certaines métriques sont fixes alors que d'autres peuvent évoluer dans le temps, elles sont alors dynamiques. Certaines s'obtiennent facilement alors que d'autres sont beaucoup plus difficiles à obtenir, c'est la notion d'accessibilité. Certaines sont reconfigurables, d'autres non, alors que d'autres peuvent se modifier suite à une reconfiguration de certaines. C'est le niveau de reconfigurabilité. Est aussi identifié le niveau d'impact de la métrique sur la consommation énergétique.

Le tableau 2 ci-dessous résume cette discussion :

static

Working mode

| Metrics                                | Self-changeability | Configurability | Green impact | At which Level | Susceptibility |

|----------------------------------------|--------------------|-----------------|--------------|----------------|----------------|

| Voltage                                | static             | medium          | strong       | System         | Low            |

| Current                                | dynamic            | unconfigurable  | strong       | system         | medium         |

| Frequency                              | static             | easy            | strong       | PE             | Low            |

| Temperature                            | dynamic            | unconfigurable  | strong       | system         | high           |

| Area                                   | static             | medium          | medium       | PE & system    | Low            |

| Position                               | static             | medium          | weak         | PE             | Low            |

| Resource                               | static             | difficult       | strong       | PE & system    | Low            |

| Activity rate                          | dynamic            | unconfigurable  | medium       | PE             | medium         |

| Serial / parallel                      | static             | easy            | medium       | PE             | low            |

| Power consumption                      | dynamic            | unconfigurable  | strong       | PE & system    | medium         |

| Performance to power consumption ratio | dynamic            | unconfigurable  | strong       | PE             | medium         |

Table 2 – Consideration of the metrics.

La fréquence de fonctionnement d'un opérateur ou PE peut être reconfigurée par l'intermédiaire d'un Digital Clock Manager (DCM), par conséquent, il s'agit d'une métrique reconfigurable pour cette plate-forme. Le mode Série/Parallèle est similaire si l'on a la

easy

strong

system

low

possibilité de commuter entre différentes options existantes notamment par RP. La surface et la position sont reconfigurables notamment grâce à la RP. Mais la ressource ne l'est pas car celle-ci est définie lors de la configuration de l'opérateur.

En ce qui concerne l'impact Eco, certaines métriques telles que la tension, le courant, la fréquence, la température, la ressource, la consommation... ont un impact important et certaines ont une influence directe sur la consommation. La position d'un opérateur n'a pas d'impact alors que le mode série/parallèle a un impact complexe et indirect. C'est précisément cette métrique que nous étudions en détail dans la section suivante.

# 3.3 Etude d'un cas particulier : implantation série ou parallèle d'un filtre

Le filtrage est une fonction classique et nécessaire dans tout équipement de radiocommunications. Il peut s'agir de filtrer une bande de fréquence pour éviter de polluer les bandes adjacentes, ou de filtrer une bande d'intérêt pour optimiser le convertisseur analogique/numérique, ou de réaliser un filtre de Nyquist,...

Très classiquement, ces filtres sont réalisés à partir de filtre à Réponse impulsionnelle finie (FIR). Un FIR comporte des retards et des coefficients (multiplieurs). Il peut être implanté sous forme parallèle ou série chacune ayant ses avantages. La figure de la section précédente présente ces deux possibilités. De manière évidente la forme parallèle sera plus rapide mais consommera plus de ressources que le mode série. Nous pourrions donc en déduire que la forme parallèle consommera plus, mais cela n'est pas si simple. Lors d'une implémentation d'un filtre FIR à 32 coefficients avec 32 MAC (multiplieurs /accumulateurs) pour le mode parallèle et un seul MAC pour le mode série le tableau 3 confirme que le mode parallèle consomme plus de ressource :

Table 3 – Resources used by the two implementation architectures.

| Architecture | #FF  | #LUTs | #DSPs |

|--------------|------|-------|-------|

| Parallel     | 3051 | 1067  | 64    |

| Serial       | 1192 | 542   | 2     |

24 Résumé

Pour étudier l'influence sur la consommation, nous avons implanté ce filtre sur le FPGA, sans aucune autre fonction. La consommation est estimée en utilisant l'outil XPA.

| Table 4 – Power | consumption of | of the FIR | filter. |

|-----------------|----------------|------------|---------|

|-----------------|----------------|------------|---------|

| Engerners | Power consumption (W) |           |       |         |           |       |

|-----------|-----------------------|-----------|-------|---------|-----------|-------|

| Frequency |                       | parallel  |       |         | serial    |       |

| (MHz)     | Dynamic               | Quiescent | Total | Dynamic | Quiescent | Total |

| 40        | 0.058                 | 0.545     | 0.603 | 0.019   | 0.544     | 0.564 |

| 50        | 0.069                 | 0.545     | 0.614 | 0.022   | 0.544     | 0.566 |

| 66.67     | 0.087                 | 0.545     | 0.632 | 0.025   | 0.544     | 0.570 |

| 75        | 0.096                 | 0.545     | 0.641 | 0.027   | 0.544     | 0.572 |

| 100       | 0.123                 | 0.545     | 0.668 | 0.033   | 0.545     | 0.578 |

| 125       | 0.150                 | 0.545     | 0.695 | 0.039   | 0.545     | 0.583 |

| 133.33    | 0.159                 | 0.545     | 0.704 | 0.040   | 0.545     | 0.585 |

| 150       | 0.176                 | 0.546     | 0.722 | 0.044   | 0.545     | 0.589 |

| 166.67    | 0.194                 | 0.546     | 0.740 | 0.048   | 0.545     | 0.592 |

On peut constater que la consommation dynamique est plus faible pour le mode série à fréquence identique. Mais comparer à fréquence identique n'est pas une comparaison intéressante. En effet, la comparaison doit se faire à débit identique, ce qui nécessitera d'augmenter la fréquence de fonctionnement du mode série et, comme nous le verrons, inversera la conclusion sur la consommation. Notons aussi sur ce tableau, que la consommation totale pour les 2 modes est très proche. Comme l'outil XPA ne donne qu'une consommation totale du FPGA, il est très difficile de conclure sur la consommation statique du filtre suivant le mode d'implantation. En effet cette surface, quel que soit le mode, est faible relativement à l'ensemble du FPGA. Elle aura donc peu d'influence sur la consommation totale.

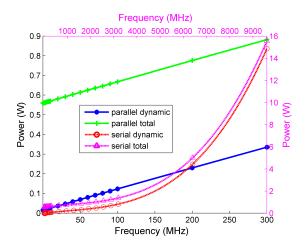

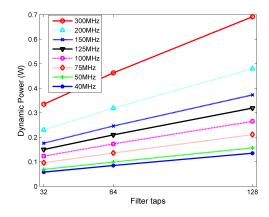

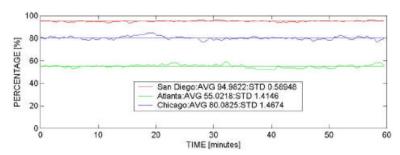

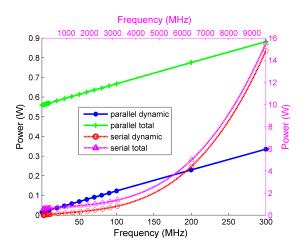

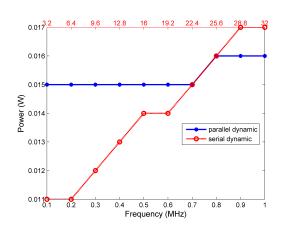

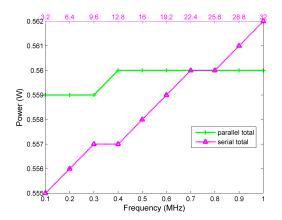

Nous nous focalisons maintenant sur la consommation dynamique. Nous implantons dans cette étude les deux modes de manière à obtenir le même débit en sortie du filtre. La figure 18 présente la consommation dans ce contexte.

FIGURE 18 – The power consumption.

A cause de la différence importante en consommation entre les deux modèles les axes concernant l'architecture parallèle sont ceux de gauche et bas alors que pour l'architecture série ce sont ceux de droite et haut.

En mode parallèle la consommation croît presque linéairement et reste sous 1W, mais en mode série, pour garder le même débit, la fréquence doit aller de 3.2 MHZ à 9600MHz. En dessous de 3200MHz la consommation est sous 1,5 W mais croît très rapidement ensuite jusqu'à croiser la courbe parallèle. Cela s'explique facilement par le fait que l'horloge est l'élément qui consomme le plus à l'intérieur du FPGA, à partir d'une certaine fréquence elle devient prépondérante.

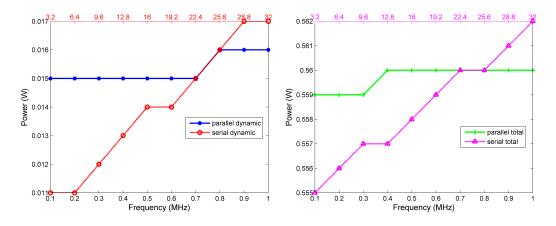

Comme la Figure 18 a des axes différents, il est difficile de comparer les détails des 2 architectures. Les 2 figures (Figure 19 et Figure 20) suivantes font un zoom sur la région 0.1 MHz à 1MHz.

On constate que le mode parallèle consomme plus que le mode série mais que l'inverse se produit pour une fréquence série supérieure à 25.6 MHz.

Une première conclusion (surprenante) de cette étude consiste à dire que sous une certaine fréquence il est préférable d'utiliser le mode série, qui utilise moins de ressource et consomme moins, et qu'au-delà il est préférable d'utiliser le mode parallèle. Cette conclusion sera très utile pour prendre les bonnes décisions dans HDCRAM.

26  $R\acute{e}sum\acute{e}$

FIGURE 19 – The dynamic power.

FIGURE 20 – The total power.

#### 3.3.1 Influence du nombre de coefficients

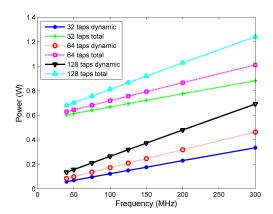

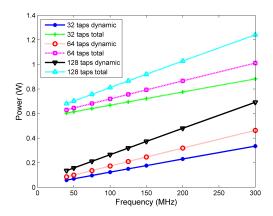

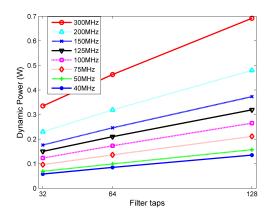

Nous souhaitons étudier dans cette section l'influence du nombre de coefficients sur la consommation. Pour cela nous avons implanté des filtres de 32, 64, 128 coefficients. La Fig. 21 donne la consommation, en fonction de la fréquence pour les 3 longueurs de filtre. Comme attendu le filtre comprenant le plus grand nombre de coefficients consomme le plus, lorsqu'ils travaillent à la même fréquence. A mesure que la fréquence augmente, la consommation croît plus rapidement avec le filtre le plus long.

FIGURE 21 – Power consumption of the filter with three different numbers of taps when the frequency increases.

La Fig. 22 montre la consommation en fonction du nombre de coefficients. A 40MHz, la consommation croît faiblement quand le nombre de coefficients augmente, mais quand la fréquence passe à 300MHz, la consommation croit nettement plus vite.

FIGURE 22 – Dynamic power consumption according to the number of taps.

Ce qui veut dire que plus le filtre est long et plus le débit souhaité sera élevé plus la consommation sera élevée. Ce résultat n'est pas surprenant.

#### 3.3.2 Gestion de ces métriques par HDCRAM

Les métriques utilisées dans cette analyse sont :

- Série/parallèle

- Fréquence

- Consommation

- Ressource

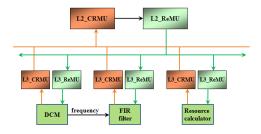

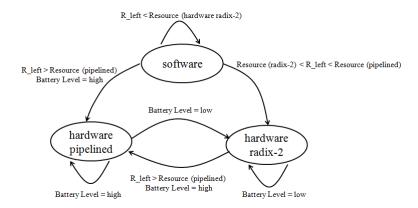

Lorsque celles-ci ont été obtenues elles sont alors utilisées par les algorithmes de décision de HDCRAM. La Fig. 23 donne un exemple d'utilisation de celles-ci. Les trois opérateurs (générateur de fréquence DCM, filtre, calcul de la ressource) sont gérés par leurs gestionnaires respectifs de niveau 3.

- Si le débit demandé est faible (< 0.8 MHz) alors le gestionnaire de niveau 3 va prendre la décision de fonctionner en mode série.

- Si le débit demandé est élevé, alors il est possible de l'atteindre en augmentant la fréquence de travail ou en augmentant le nombre de MACs. Le niveau L3 ne peut

28 Résumé

pas prendre de décision seul, l'information remonte donc au niveau L2 qui pourra prendre une décision. Par exemple pour doubler le débit, si l'opérateur ressource indique que celle-ci est suffisante, L2 peut décider de multiplier par 2 le nombre de MAC sinon, il décidera d'augmenter la fréquence de fonctionnement. Cette décision de L2 se répercutera sur les L3 de reconfiguration de DCM et du filtre.

FIGURE 23 – An example of level 2 HDCRAM management.

### 4 Implantation d'un système émission/réception OFDM

Afin de valider les différentes études des chapitres précédents, nous avons implanté sur une plate-forme une transmission réelle qui intègre l'ensemble de nos propositions. Cette transmission est basée sur une modulation de type OFDM largement utilisée aujourd'hui dans de nombreux standards et qui a fait ses preuves, notamment pour lutter contre les évanouissements sélectifs.

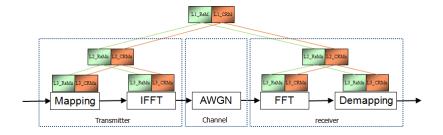

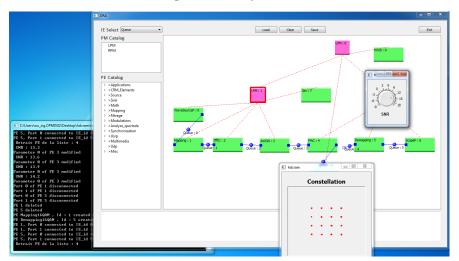

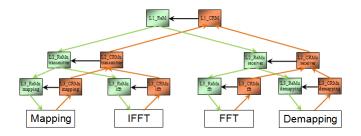

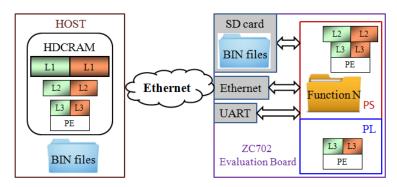

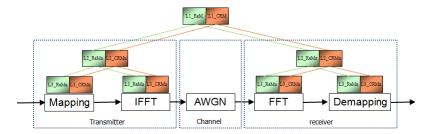

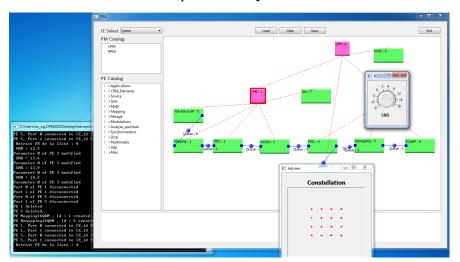

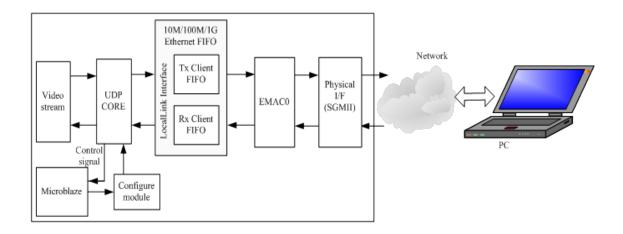

La figure 24 présente la gestion avec HDCRAM du système OFDM. Afin de démontrer l'aspect distribué de HDCRAM et l'aspect plate-forme hétérogène de notre réalisation, l'émetteur est implanté sur un PC (GPP) alors que le récepteur est implanté sur la plate-forme Zynq. L'émetteur est considéré comme la station de base alors que le récepteur est considéré comme le terminal. Le lien entre le PC et la plate-forme se fait par le protocole UDP à travers Ethernet.

Plusieurs scénarios ont été étudiés, parmi ceux-ci trois sont présentés dans ce résumé.

FIGURE 24 – The block diagram of a simplified OFDM system model.

Figure 25 – Implementation platform.

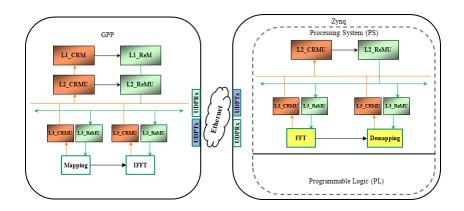

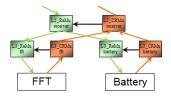

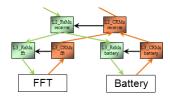

#### 4.1 Implantation de la FFT par RP

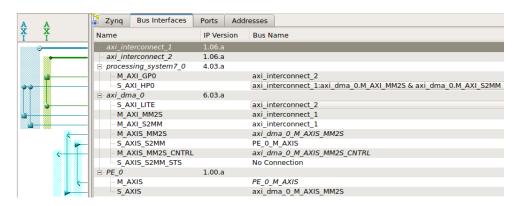

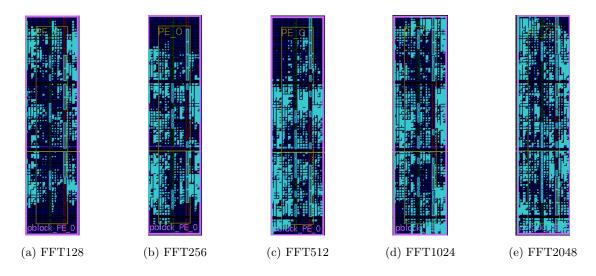

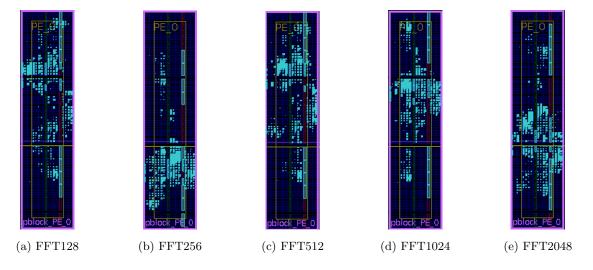

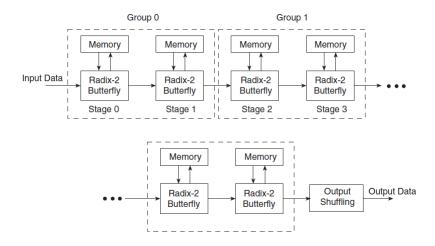

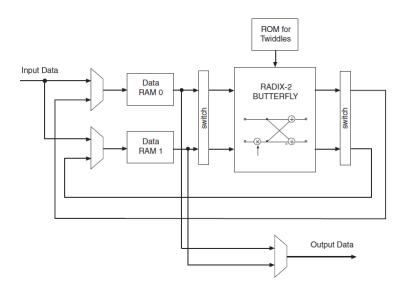

Comme la FFT est la fonction la plus coûteuse en termes de calculs, elle peut avantageusement être réalisée en matériel sur PL (voir Figure 26), même s'il est possible de l'implanter en logiciel sur PS (voir Figure 27).

Dans un but d'optimisation de la surface et de la consommation, nous proposons d'implanter la FFT par reconfiguration partielle, ce qui nous permettra, au lieu d'implanter une grosse FFT reconfigurable entre toutes les tailles nécessaires, de choisir et modifier à la volée la FFT de bonne taille pour le scénario envisagé. Deux types d'implantation sont considérées dans ce travail : une architecture de type pipe-line et une autre de type Radix2 (voir Annexe D).

$R\acute{e}sum\acute{e}$

Figure 26 – The hardware implementation of FFT.

FIGURE 27 – The software implementation of FFT.

La figure 28 présente l'implantation de la FFT Radix2 pour différentes tailles en utilisant la RP.

Le tableau 5 suivant dresse une comparaison des ressources nécessaires pour les différents cas envisagés. Ces résultats doivent être comparés avec ceux du tableau 6 correspondant au cas d'une FFT reconfigurable entre toutes les tailles envisagées. On constate que la ressource nécessaire est supérieure à celle de la FFT de plus grande taille : cela est du à la logique de contrôle pour la reconfiguration entre toutes les tailles.

Les différents temps de transformation sont listés dans les tableaux 7. Il apparaît que ce temps est le plus faible avec l'architecture pipe-line hardware au prix d'une ressource supérieure comparée à l'architecture Radix 2. Le temps supplémentaire lié à la RP doit aussi être pris en compte il est donné tableau 8.

Table 5 - Resources available and used by different FFT implementations in the reconfigurable region.

| Transform | Resource  | LUT  | Register | SLICE | DSP48E1 | BRAM |

|-----------|-----------|------|----------|-------|---------|------|

| length    | Available | 5184 | 10368    | 1359  | 32      | 48   |

| 100       | pipelined | 2806 | 3196     | 702   | 9       | 9    |

| 128       | radix-2   | 1067 | 1316     | 268   | 3       | 11   |

| 25.6      | pipelined | 3175 | 3578     | 795   | 9       | 10   |

| 256       | radix-2   | 1101 | 1361     | 276   | 3       | 11   |

| F10       | pipelined | 3589 | 4113     | 898   | 12      | 12   |

| 512       | radix-2   | 1154 | 1392     | 289   | 3       | 11   |

| 1004      | pipelined | 3993 | 4507     | 999   | 12      | 14   |

| 1024      | radix-2   | 1153 | 1425     | 289   | 3       | 11   |

| 20.40     | pipelined | 4455 | 5086     | 1114  | 15      | 19   |

| 2048      | radix-2   | 1194 | 1491     | 299   | 3       | 13   |

Table 6 – Resources used by traditional reconfigurable FFT implementation with pipelined architecture.

| LUT  | Register | SLICE | DSP48E1 | BRAM |

|------|----------|-------|---------|------|

| 5741 | 6056     | 1435  | 15      | 19   |

Table 7 – The transform time of different FFT implementations.

| Transform | Software  | Hardware $(\mu s)$ |         | Traditional reconfigurable |

|-----------|-----------|--------------------|---------|----------------------------|

| length    | $(\mu s)$ | pipelined          | radix-2 | FFT $(\mu s)$              |

| 128       | 166       | 4.81               | 8.29    | 4.92                       |

| 256       | 364       | 8.71               | 16.77   | 8.93                       |

| 512       | 798       | 16.49              | 34.85   | 16.61                      |

| 1024      | 1751      | 31.91              | 73.41   | 32.13                      |

| 2048      | 3867      | 62.73              | 155.49  | 62.85                      |

**32** Résumé

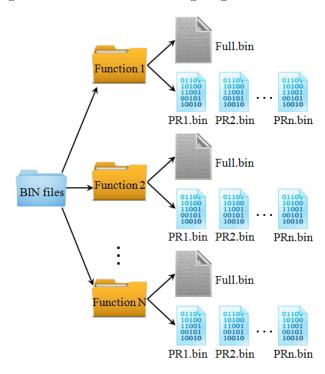

$\label{eq:Figure 28-Implementation of FFT with single radix-2 architecture using partial reconfiguration.$

Table 8 – Full and partial configuration time of the FFT design.

| Type    | Size (bytes) | Time $(\mu s)$ |

|---------|--------------|----------------|

| Full    | 4 045 564    | 211 413        |

| Partial | 384 512      | 35 122         |

De même les tableaux 9 et 10 comparent la consommation des différentes architectures.

Table 9 – The power consumption of different FFT implementations of the DPR approach.

| Transform | Power consumption (W) |         |  |

|-----------|-----------------------|---------|--|

| length    | pipelined             | radix-2 |  |

| 128       | 0.103                 | 0.096   |  |

| 256       | 0.105                 | 0.097   |  |

| 512       | 0.108                 | 0.098   |  |

| 1024      | 0.113                 | 0.099   |  |

| 2048      | 0.121                 | 0.101   |  |

Table 10 – The power consumption of software FFT and traditional reconfigurable FFT.

|                       | Software FFT | Traditional reconfigurable FFT |

|-----------------------|--------------|--------------------------------|

| Power consumption (W) | 0.12         | 0.135                          |

En conclusion, le meilleur compromis sur tous ces critères est l'implantation de la FFT avec l'architecture pipe-line en utilisant la RP.

#### 4.2 Différents scénarios d'Ecoradio Intelligente

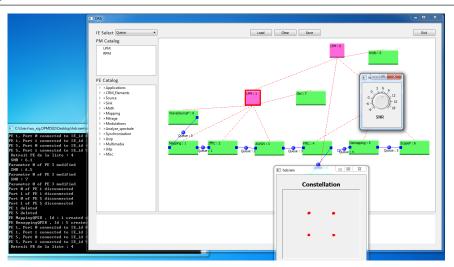

#### 4.2.1 Adaptation de la constellation

Dans ce scénario, la constellation est modifiée en fonction du SNR du signal reçu. Ce scénario implique qu'il y ait une communication entre le terminal et à la station pour lui demander de modifier la constellation émise.

Remarque : Ce scénario, dans une version figée a déjà été implanté au laboratoire et une démonstration existe déjà. Cependant, dans cette nouvelle version le scénario est complètement géré par HDCRAM, ce qui offre une très grande souplesse.

FIGURE 29 – Scenario 1.

### L3 CRMu SNR

Le capteur SNR mesure le niveau de bruit et envoie cette information au niveau L2 CRMu supérieur.

#### L3 CRMu demapping

Informe le L2 de la modulation en cours.

#### <u>L2 CRMu receiver</u>

En se basant sur la valeur de SNR remontée par le niveau L3, L2 CRMu receiver prend une décision très simple pour adapter la modulation :

- Si 5dB < SNR <= 10dB, la QPSK sera choisie.

- Si SNR > 10dB, la 16QAM sera utilisée.

En fonction de la modulation en cours, L2 CRMu receiver informe ou non le niveau L1 d'une reconfiguration de la modulation.

#### L1 CRM

Si L1 ReM reçoit une commande de son L1 CRM associé, alors il envoie l'ordre aux L2 ReMu transmitter et L2 ReMu receiver concernés.

#### <u>L2 ReMu transmitter</u>

Si le L2 ReMu transmitter reçoit l'ordre du L1 ReM il execute l'action et envoie l'ordre de reconfiguration au L3 ReMu mapping.

#### L3 ReMu mapping

Le L3 ReMu mapping gère la reconfiguration de son opérateur Mapping associé.