## Allocation dynamique de bande passante pour l'interconnexion RF d'un réseau sur puce

Eren Unlu

## ▶ To cite this version:

Eren Unlu. Allocation dynamique de bande passante pour l'interconnexion RF d'un réseau sur puce. Autre. CentraleSupélec, 2016. Français. NNT: 2016CSUP0006 . tel-01647665

## HAL Id: tel-01647665 https://theses.hal.science/tel-01647665

Submitted on 24 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$\rm N^{\underline{o}}$  d'ordre : 2016-06-TH

## CentraleSupélec

## École Doctorale MATISSE

« Mathématiques, Télécommunications, Informatique, Signal, Systèmes Electroniques »

## THÈSE DE DOCTORAT

Domaine : STIC Spécialité : Télécommunications

Soutenue le 21/06/2016

Présentée par :

Eren UNLU

## Allocation Dynamique de Bande Passante pour l'Interconnexion RF d'un Réseau-sur-Puce

| Composition du jury : |                  |                                    |

|-----------------------|------------------|------------------------------------|

| Directeur de thèse :  | Christophe Moy   | Professeur de CentraleSupélec/IETR |

| Président du jury :   | Lionel Torres    |                                    |

| Rapporteurs :         | Fabien Clermidy  | Chercheur CEA-Leti                 |

|                       | Lionel Torres    | Professeur de                      |

|                       |                  | Université de Montpellier 2        |

| Examinateurs :        | Myriam Ariaudo   | Maître de Conférences              |

|                       |                  | à ENSEA de Cergy/ETIS              |

|                       | Sébastien LeBeux | Maître de Conférences              |

|                       |                  | à Ecole Centrale de Lyon           |

|                       | Yves Louët       | Professeur de CentraleSupélec/IETR |

# Contents

| Ac | know | led | geme | ents |

|----|------|-----|------|------|

|    |      |     |      |      |

vii

| 0 |      |        | n Français : Allocation Dynamique de Bande Passante pour<br>nexion RF d'un Résau-sur-Puce | r<br>1 |

|---|------|--------|-------------------------------------------------------------------------------------------|--------|

| 1 | Intr | roduct | ion                                                                                       | 39     |

| 2 | 100  | 0-core | Era and On-Chip Challenge                                                                 | 44     |

|   | 2.1  | Chip 1 | Multiprocessors                                                                           | 44     |

|   |      | 2.1.1  | Caches and Memory                                                                         | 45     |

|   |      | 2.1.2  | Cache Coherency                                                                           | 47     |

|   | 2.2  | Netwo  | ork-on-Chip                                                                               | 48     |

|   |      | 2.2.1  | From buses to NoC                                                                         | 48     |

|   |      | 2.2.2  | NoC topologies                                                                            | 50     |

|   |      | 2.2.3  | Tera-Scale Multi-core Processor Architecture (TSAR)                                       | 51     |

|   | 2.3  | RF an  | d Optical Interconnects                                                                   | 51     |

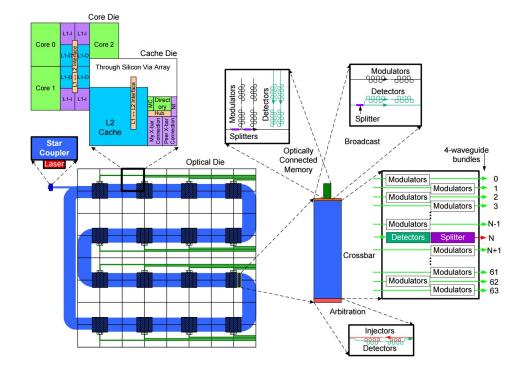

|   |      | 2.3.1  | Optical Interconnects                                                                     | 52     |

|   |      |        | 2.3.1.1 ATAC                                                                              | 55     |

|   |      |        | 2.3.1.2 Corona                                                                            | 57     |

|   |      | 2.3.2  | RF Interconnects                                                                          | 59     |

|   |      |        | 2.3.2.1 Wireless RF Interconnects                                                         | 59     |

|   |      |        | 2.3.2.2 Wired RF Interconnects                                                            | 60     |

|   | 2.4  | Chara  | acteristics of On-Chip Traffic                                                            | 61     |

|   |      | 2.4.1  | Temporal Burstiness : Hurst Parameter                                                     | 62     |

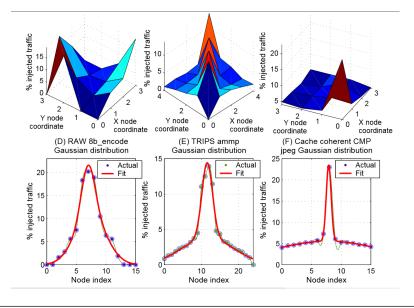

|   |      | 2.4.2  | Spatial Burstiness : Standard Deviation                                                   | 63     |

|   |      | 2.4.3  | Statistical Distance Property of on-chip Transactions                                     | 64     |

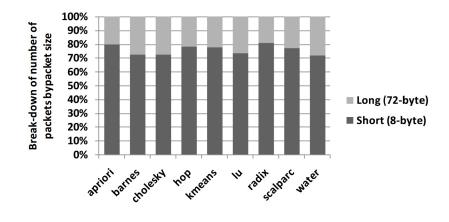

|   |      | 2.4.4  | Bimodal on-chip Packets                                                                   | 64     |

|   | 2.5  | Conclu | usion                                                                                     | 65     |

| 3 | Wi   | ΝοϹοΓ  | O Project and Wired OFDMA Based RF Interconnect                                           | 67     |

|   | 3.1  |        | CoD On-Chip Architecture                                                                  | 68     |

|   |      | 3.1.1  | Need for independent communication layers                                                 |        |

|   |      | 3.1.2  | 3-level hierarchy                                                                         |        |

|   |      |        | 3.1.2.1 A Tile                                                                            |        |

|   |      |        | 3.1.2.2 A Tileset                                                                         |        |

|   |     | 3.1.2.3 Inter-tileset Communication                                                                | 72  |

|---|-----|----------------------------------------------------------------------------------------------------|-----|

|   |     | 3.1.3 Details of Cache Coherence Protocol                                                          | 73  |

|   | 3.2 | Basics of OFDMA                                                                                    | 76  |

|   |     | 3.2.1 OFDM                                                                                         | 76  |

|   |     | 3.2.2 OFDMA                                                                                        | 79  |

|   | 3.3 | OFDMA Based RF Interconnect                                                                        | 81  |

|   |     | 3.3.1 RF Controller                                                                                | 82  |

|   |     | 3.3.2 RF Front-end                                                                                 | 83  |

|   |     | 3.3.2.1 Transmitter Side                                                                           |     |

|   |     | 3.3.2.2 Receiver Side                                                                              | 85  |

|   |     | 3.3.2.3 Transmission Line and Access                                                               | 85  |

|   | 3.4 | Conclusion                                                                                         | 86  |

| 4 | RF  | NoC Bandwidth Allocation Problem                                                                   | 88  |

|   | 4.1 | WiNoCoD's OFDMA RF Interconnect                                                                    | 89  |

|   |     | 4.1.1 Motivation                                                                                   | 89  |

|   |     | 4.1.2 Cognitive Radio                                                                              | 90  |

|   |     | 4.1.3 LTE                                                                                          | 91  |

|   | 4.2 | Dynamic Bandwidth Scheduling for Parallel Queues                                                   |     |

|   |     | 4.2.1 Longest Queue First                                                                          |     |

|   |     | 4.2.2 Queue Length Proportional Scheduling                                                         |     |

|   |     | 4.2.3 Square Root of Queue Length Proportional Scheduling                                          |     |

|   |     | 4.2.4 Oldest Packet First Scheduling                                                               |     |

|   | 4.3 | Preliminaries of Bandwidth Allocation in WiNoCoD                                                   |     |

|   |     | 4.3.1 Partitioning Bandwidth Statically                                                            |     |

|   |     | 4.3.2 A Quasi-Static and Quasi-Dynamic Modification                                                |     |

|   |     | 4.3.3 Resource Blocks, Frames and QSI Signaling                                                    |     |

|   |     | $4.3.3.1  \text{Resource Blocks}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |     |

|   |     | $4.3.3.2  \text{Frames}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $          |     |

|   |     | 4.3.3.3 Decentralized and Centralized Allocation                                                   |     |

|   |     | 4.3.3.4 Direction of Resource Block Allocation in a Frame                                          |     |

|   |     | 4.3.3.5 Idle Resource Blocks-Default Frame Configuration                                           |     |

|   |     | 4.3.3.6 QSI Encoding and Signaling                                                                 |     |

|   |     | 4.3.3.7 Taking Into Account the Outdated QSI                                                       |     |

|   |     | 4.3.4.1 Metrics of Interest                                                                        |     |

|   |     | 4.3.4.2 Employed Traffic Models                                                                    |     |

|   | 4.4 | Using Generic Cores for Bandwidth and Modulation Order Allocation                                  | 110 |

|   | 1.1 | Algorithms                                                                                         | 113 |

|   | 4.5 | Conclusion                                                                                         |     |

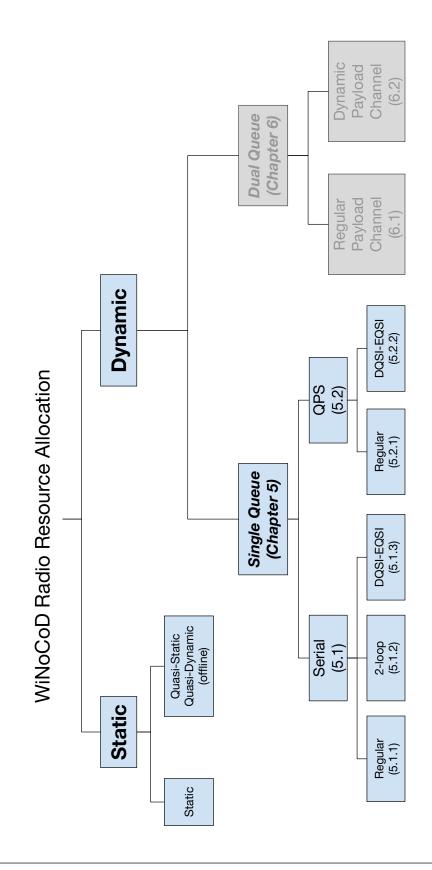

| 5 | Wi  | NoCoD Bandwidth Allocation Algorithms                                                              | 116 |

|   | 5.1 | Serial QSI Allocation                                                                              | 116 |

|   |     | 5.1.1 Regular Serial QSI Allocation                                                                |     |

|   |     | 5.1.1.1 Decentralized Approach                                                                     |     |

|   |     | 5.1.1.2 Centralized Approach                                                                       |     |

|   |     | 5.1.2 Serial QSI with 2-loop Allocation                                                            | 122 |

|   |     | 5.1.2.1 Decentralized Approach                                             | . 124 |

|---|-----|----------------------------------------------------------------------------|-------|

|   |     | 5.1.2.2 Centralized Approach                                               | . 127 |

|   |     | 5.1.3 Serial QSI Allocation with DQSI and EQSI                             | . 129 |

|   |     | 5.1.3.1 Decentralized Approach                                             | . 129 |

|   |     | 5.1.3.2 Centralized Approach                                               | . 132 |

|   | 5.2 | Queue Proportional Allocation                                              | . 134 |

|   |     | 5.2.1 Regular Queue Proportional Allocation                                | . 134 |

|   |     | 5.2.1.1 Decentralized Approach                                             | . 137 |

|   |     | 5.2.1.2 Centralized Approach                                               | . 139 |

|   |     | 5.2.2 QPS Allocation with DQSI and EQSI                                    | . 140 |

|   |     | 5.2.2.1 Decentralized Approach                                             | . 141 |

|   |     | 5.2.2.2 Centralized Approach                                               | . 144 |

|   | 5.3 | Implementation of Algorithms                                               | . 145 |

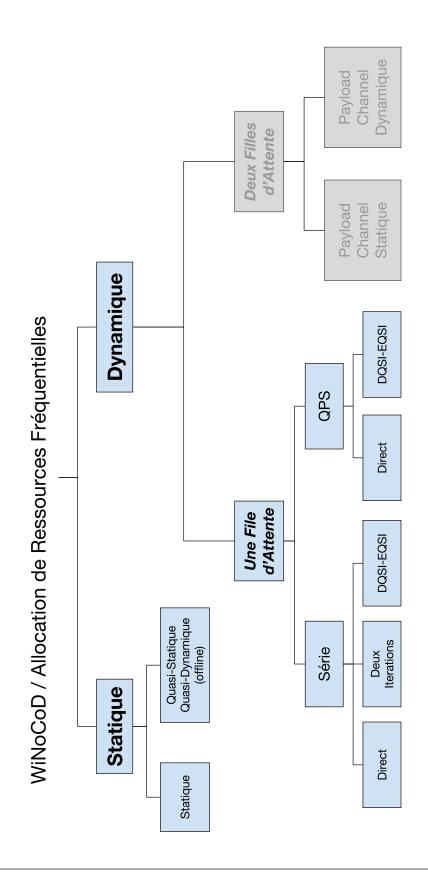

|   | 5.4 | Classification of Bandwidth Allocation Algorithms                          |       |

|   | 5.5 | Comparison of Bandwidth Allocation Algorithms                              |       |

|   | 5.6 | Conclusion                                                                 |       |

|   |     |                                                                            |       |

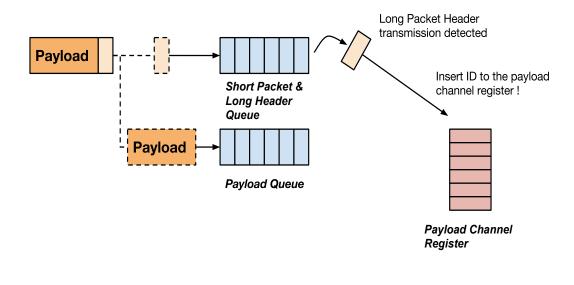

| 6 | Pay | load Channel Algorithm                                                     | 151   |

|   | 6.1 | Context                                                                    |       |

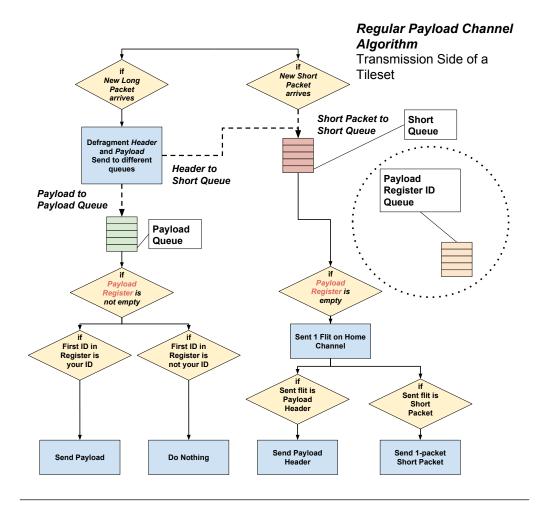

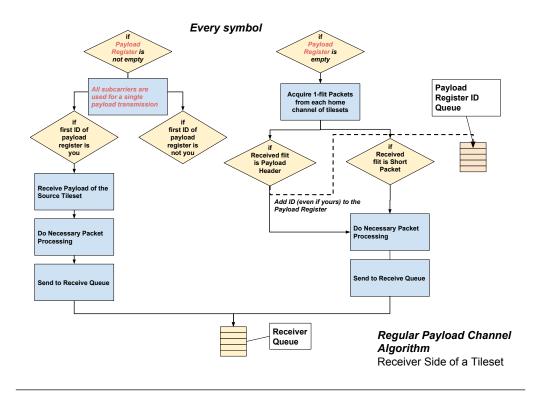

|   | 6.2 | Regular Payload Channel Algorithm                                          |       |

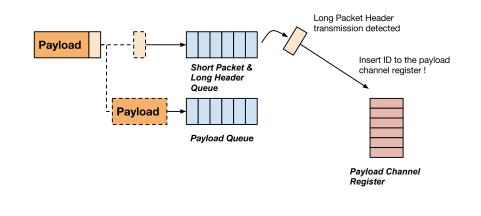

|   |     | 6.2.1 Description of Regular Payload Channel Algorithm                     |       |

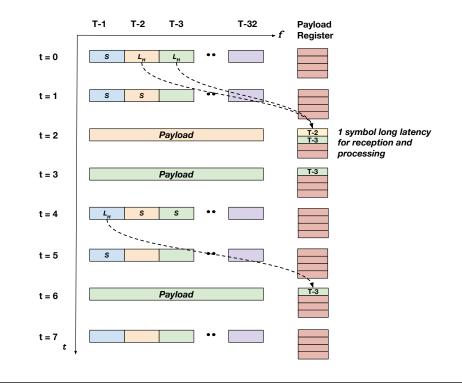

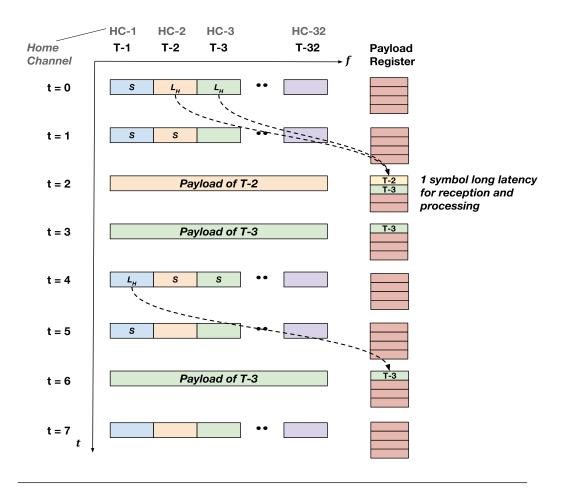

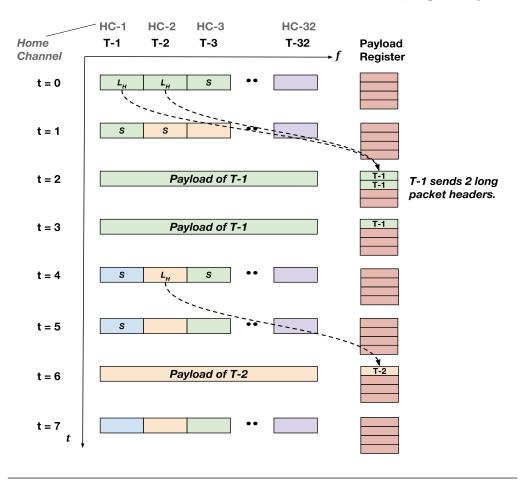

|   |     | 6.2.2 An Illustrative Scenario                                             | . 156 |

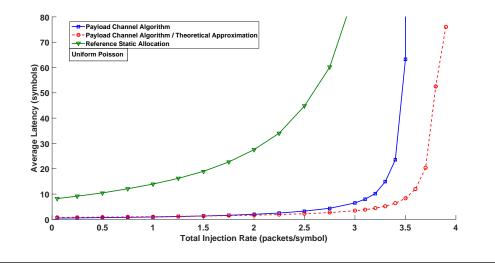

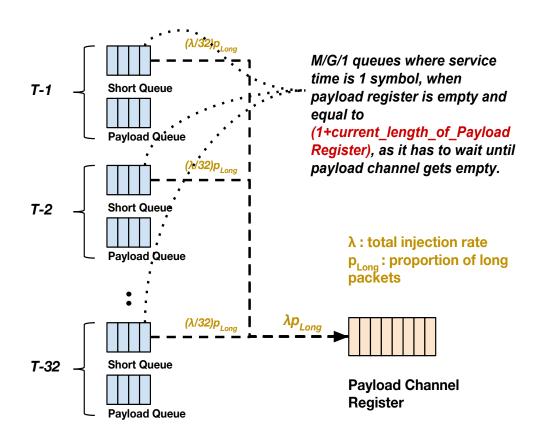

|   |     | 6.2.3 Analytic Approximation for Average Latency Calculation               | . 158 |

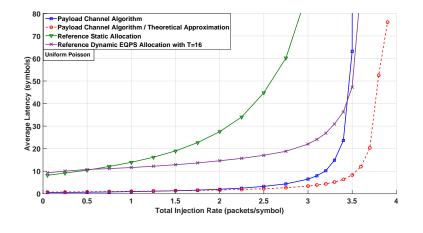

|   |     | 6.2.4 Experimental Results for Payload Channel Algorithm                   | . 162 |

|   | 6.3 | Dynamic Payload Channel Algorithm                                          | . 166 |

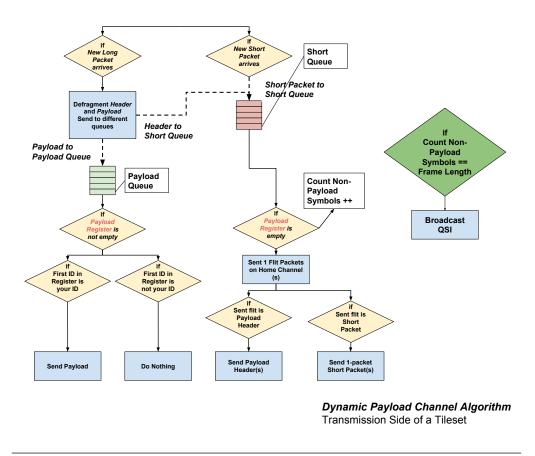

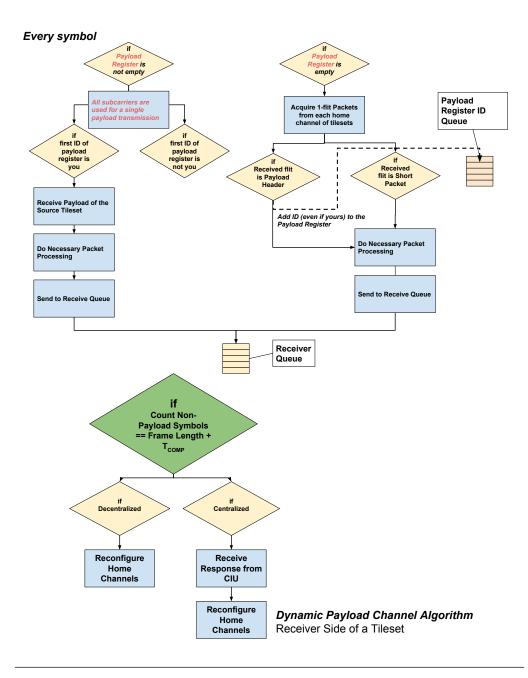

|   |     | 6.3.1 Description of Dynamic Payload Channel Algorithm                     | . 166 |

|   |     | 6.3.1.1 Illustrative Scenario                                              | . 169 |

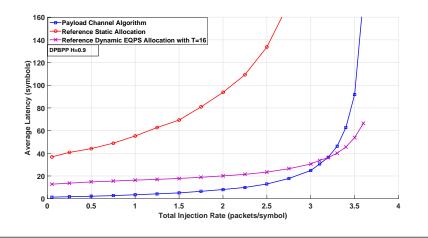

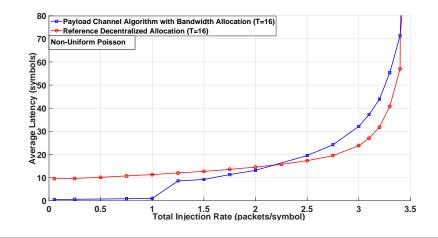

|   |     | 6.3.2 Experimental Results for Dynamic Payload Channel Algorithm .         | . 169 |

|   | 6.4 | Conclusion                                                                 | . 172 |

| _ |     |                                                                            | 1 20  |

| 7 |     | aptive Modulation Order Selection                                          | 173   |

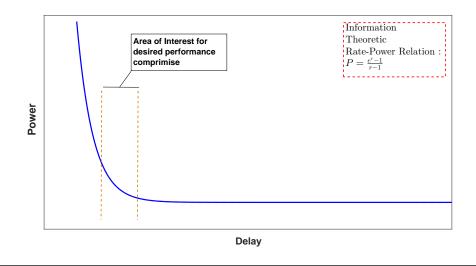

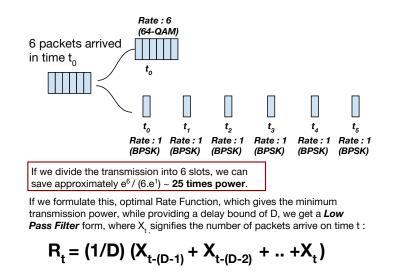

|   |     | Delay-Power Trade-off                                                      |       |

|   | 7.2 | Adaptive Modulation Option in OFDMA and Delay                              |       |

|   | 7.3 | Decentralized and Centralized Modulation Order Selection Policy            |       |

|   |     | 7.3.1 Decentralized Modulation Order Selection                             |       |

|   |     | 7.3.2 Centralized Modulation Order Selection                               |       |

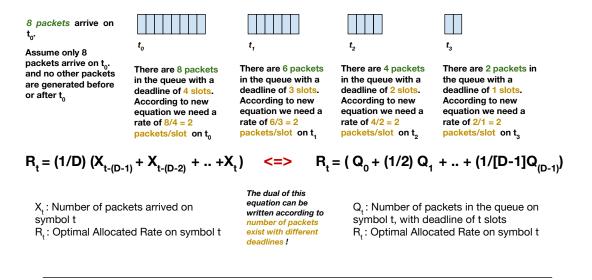

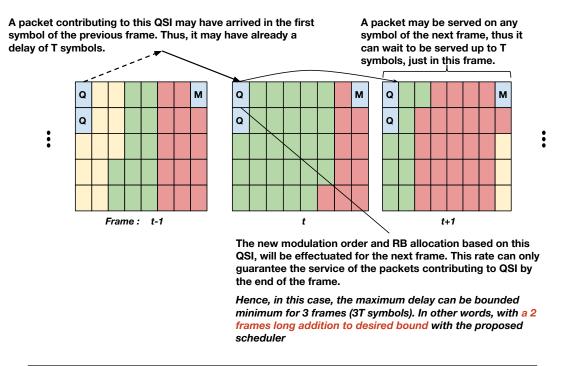

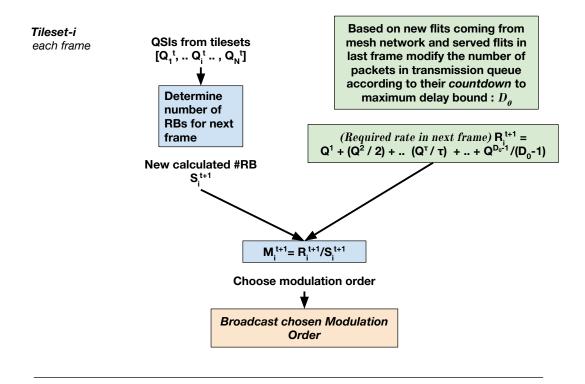

|   | 7.4 | Maximum Delay Bounded Scheduler                                            |       |

|   |     | 7.4.1 Extension of Delay Bounded Scheduler to Multiple Channels            |       |

|   |     | 7.4.2 Maximum Delay Bounded Scheduler for WiNoCoD                          |       |

|   |     | 7.4.2.1 Experimental Evaluation                                            |       |

|   | 7.5 | Average Delay Bounded Scheduler                                            |       |

|   |     | 7.5.1 Average Delay Bounded Scheduling with Centralized Approach           |       |

|   |     | Based on EQPS                                                              |       |

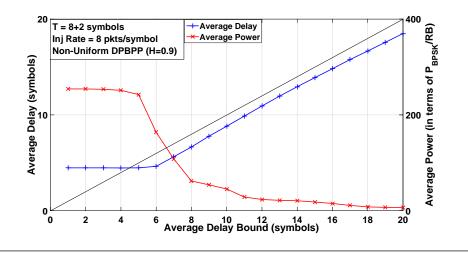

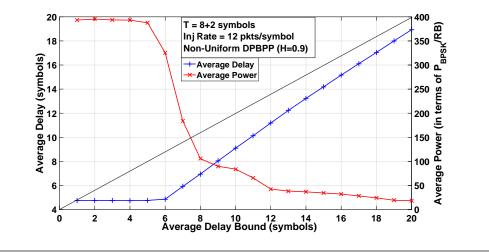

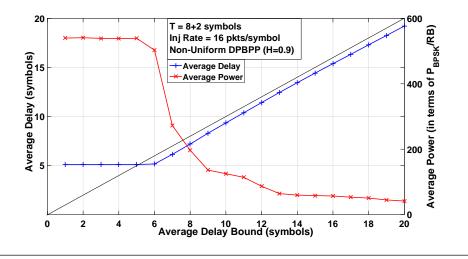

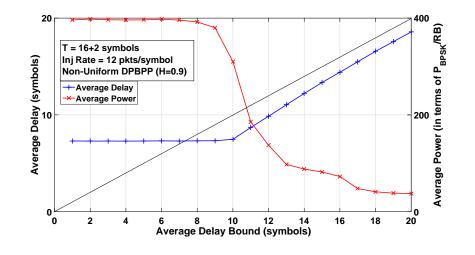

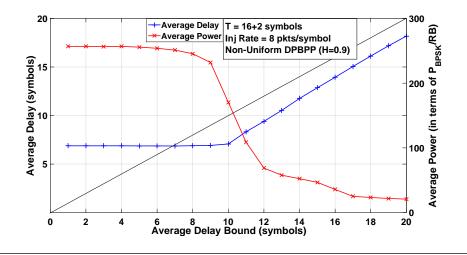

|   |     | 7.5.2 Experimental Evaluation                                              |       |

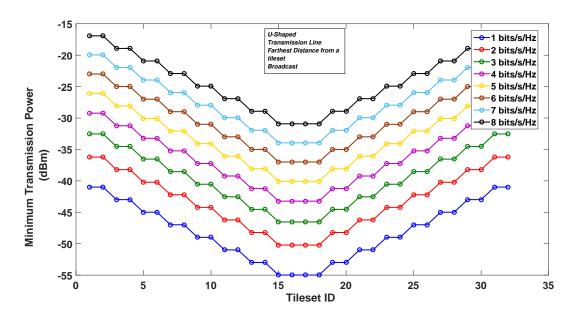

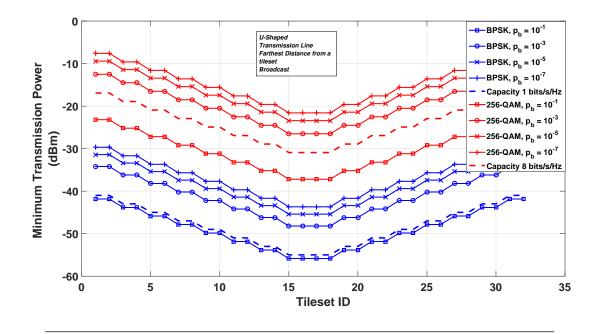

|   | 7.6 | Information Theoretic Study of the WiNoCoD RF Interconnect                 |       |

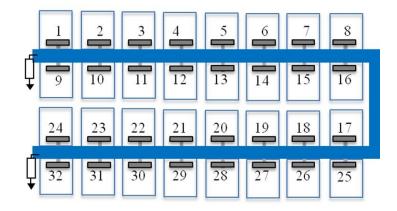

|   |     | 7.6.1 U-Shaped Transmission Line                                           |       |

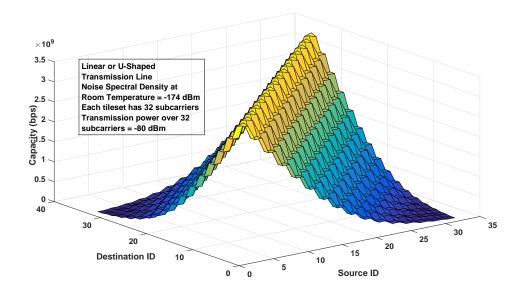

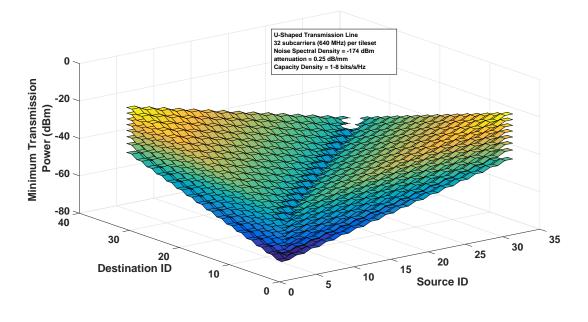

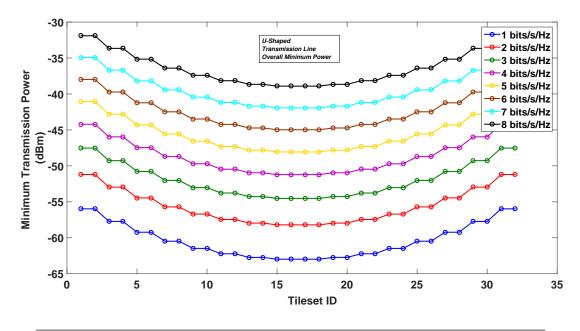

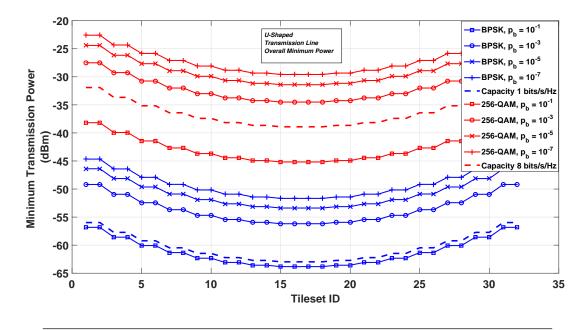

|   |     | 7.6.1.1 Unicast communication $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | . 207 |

| Conclusio | ons and H | Perspectives            | 222 |

|-----------|-----------|-------------------------|-----|

| 7.7 Concl | usion .   |                         | 220 |

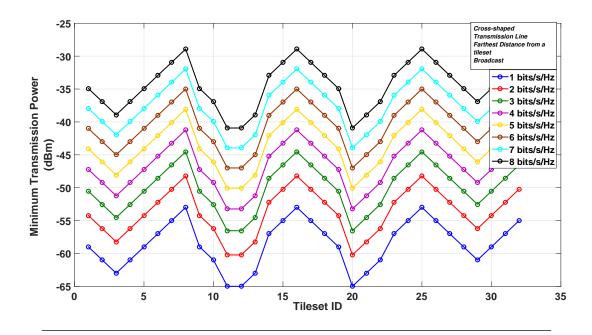

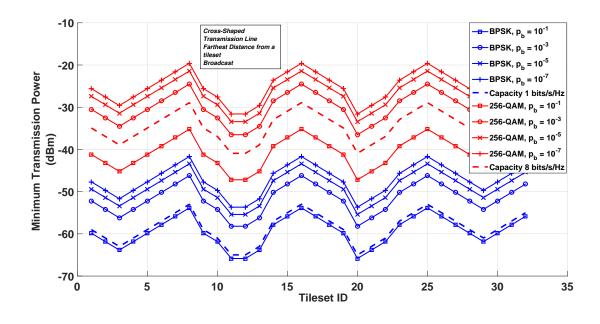

|           | 7.6.2.2   | Broadcast communication | 218 |

|           | 7.6.2.1   | Unicast communication   | 214 |

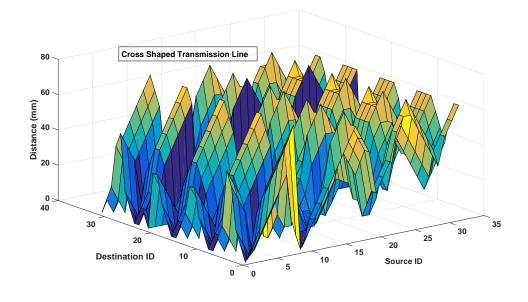

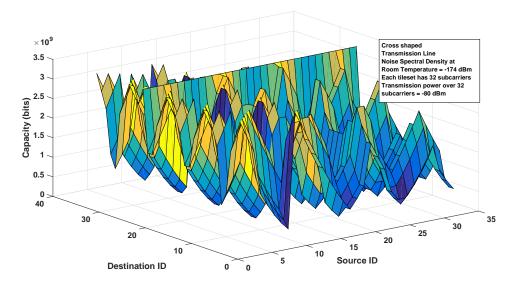

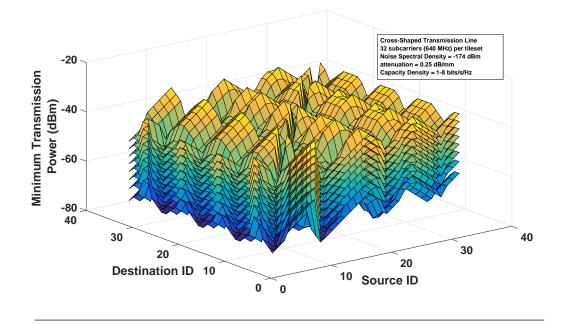

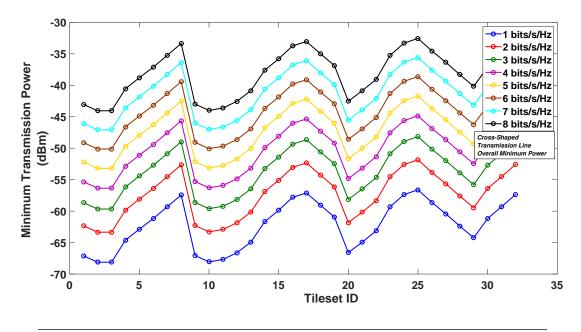

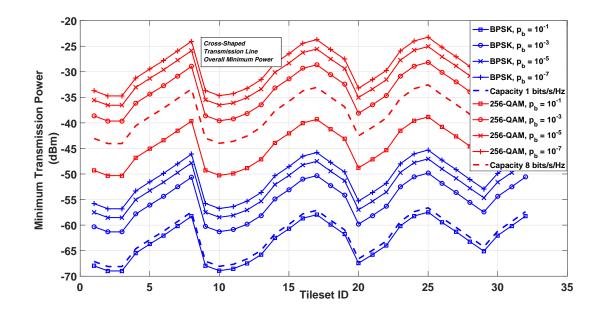

| 7.6.2     | Cross-S   | haped Transmission Line | 214 |

|           | 7.6.1.2   | Broadcast communication | 211 |

## 8 Conclusions and Perspectives

### **A** Personal Publications

227

| B | Exp | lanatio | on of ON   | INeT++ Codes                                                 | 229 |

|---|-----|---------|------------|--------------------------------------------------------------|-----|

|   | B.1 | Genera  | al Organiz | zation of the Main C++ Files and OMNeT++ Classes $\ . \ .$   | 229 |

|   |     | B.1.1   | Symbol     | Accurate Mechanism                                           | 230 |

|   |     | B.1.2   | Regular    | Channel Allocation                                           | 230 |

|   |     | B.1.3   | Payload    | Channel Allocation                                           | 231 |

|   |     | B.1.4   | Dynamie    | e Modulation Order Allocation                                | 231 |

|   |     |         | B.1.4.1    | Maximum Delay Bounded Dynamic Modulation Order<br>Allocation | 231 |

|   |     |         | B.1.4.2    | Average Delay Bounded Dynamic Modulation Order Al-           |     |

|   |     |         |            | location                                                     | 232 |

|   | B.2 | Stocha  | stic Pack  | et Generation and Traffic Models                             | 232 |

|   |     | B.2.1   | DPBPP      | packet generation                                            | 233 |

|   | B.3 | Collect | tion of M  | etrics of Interest                                           | 234 |

|   |     |         |            |                                                              |     |

| Bibliography    | 235        |

|-----------------|------------|

| List of Figures | <b>248</b> |

| List of Tables  | 256        |

| Abbreviations   | 257        |

## ABSTRACT

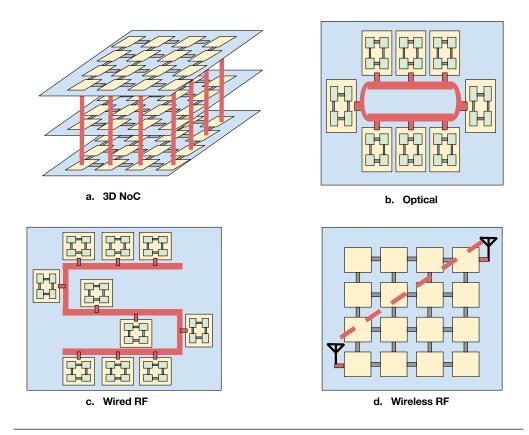

With increasing silicon manufacturing capabilities, it is expected that chip multiprocessors (CMPs) with thousands of cores will be ready before 2030. With increasing number of cores, the main bottleneck for the CMPs is to sustain the communication between these cores and traditional Network-on-Chip (NoC) interconnects start to be not sufficient, as number of routers to traverse for packets, distances and congestion increase. Recently, 3D stacking, optical and RF communications have been proposed to overcome these challenges for on-chip interconnects.

Wired RF interconnect seems the most feasible one compared to wireless RF connection or optical interconnects, as it is full CMOS compatible and required high operating frequency for signal modulation is available. Proposed state-of-the-art RF or optical on-chip interconnects require high amount of CMOS or optical components to generate orthogonal channels and lack the effective bandwidth reconfiguration capacity. *Wired RF Network-on-Chip Reconfigurable-on-Demand (WiNoCoD)* project aims to break this bottleneck by proposing an Orthogonal Frequency Division Multiple Access (OFDMA) based on-chip RF interconnect, for the first time to the best of our knowledge. This approach enables a fully flexible RF architecture managed in a pure digital manner.

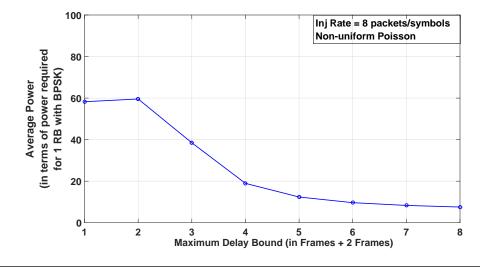

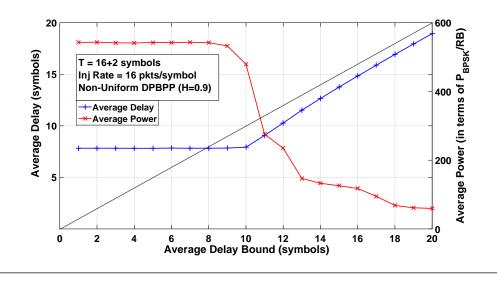

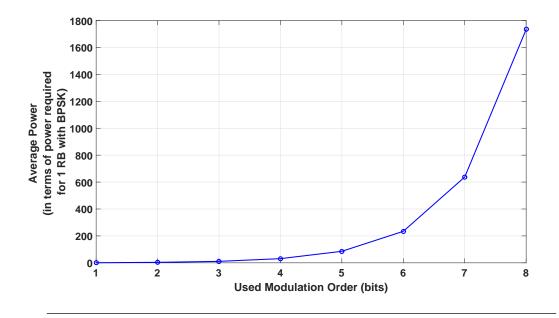

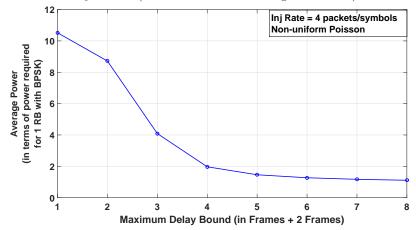

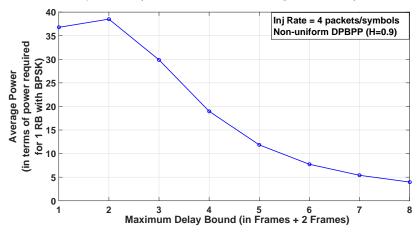

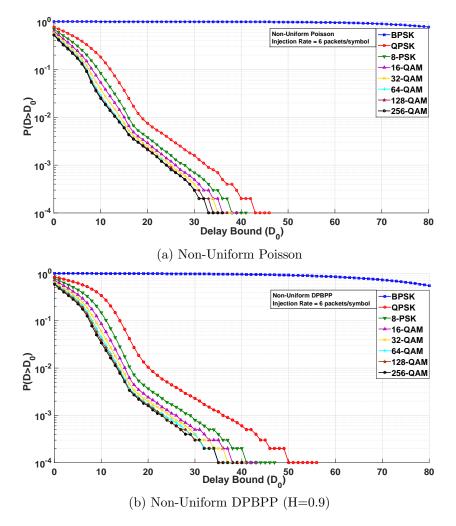

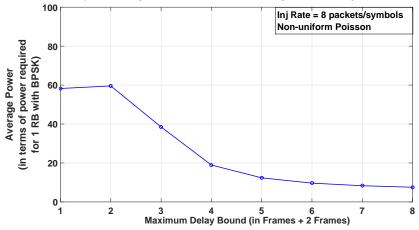

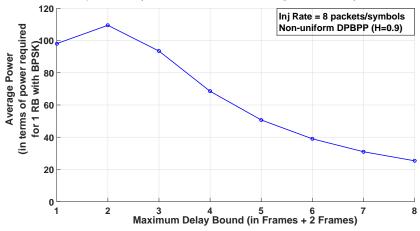

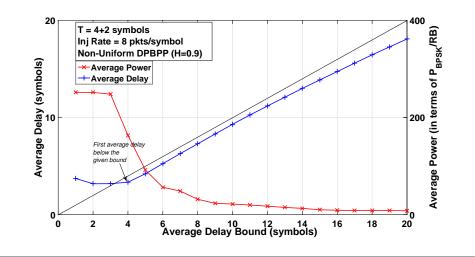

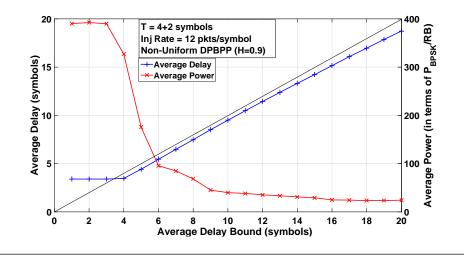

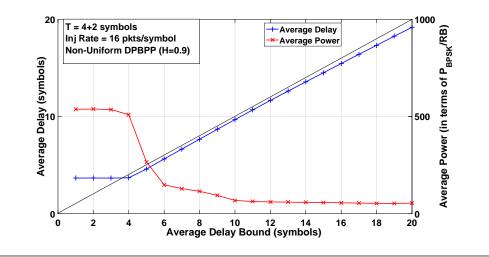

This thesis, which contributes to WiNoCoD chip, proposes a 3-level hierarchical architecture for a 2048-core generic CMP and OFDMA based RF interconnect. In this work, we propose dynamic decentralized and centralized bandwidth reconfiguration schemes for this interconnect, concerning the very specific constraints and requirements of the CMP environment. Built on this framework, several effective RF bandwidth allocation algorithms are proposed and examined using realistic stochastic on-chip traffic models. This dynamic approach can achieve remarkably low latencies even under traffic loads near the network capacity, without requiring elevated computational complexity. In addition to these, a novel bandwidth allocation algorithm is introduced, which intends to decrease transmission latency by exploiting the bimodal nature of on-chip cache-coherency packets. We have shown that, this specialized infrastructure can decrease average latency up to 10 times further compared to previously proposed algorithms in this thesis under lower traffic intensity and longer cache lines. We also consider the utilization of dynamic modulation orders as an additional degree of freedom and propose intelligent selection algorithms which seek optimal delay-energy trade-off. For instance, with this approach average power can be decreased up to 15 times under certain circumstances, by relaxing average latency requirement to a few symbols long. Information theoretic capacity analysis of this interconnect is done for different transmission line topologies.

## Résume

L'essor des technologies micro-électroniques permet d'envisager que les puces de traitement intégreront plusieurs milliers de coeurs dans la prochaine décennie. Le principal défi de conception de ces puces se situe alors au niveau des échanges de données entre les cœurs car les interconnexions NoC (Network on Chip) traditionnelles atteignent leurs limites en termes de congestion et de temps de latence. Les communications RF guidées sont préférées aux connexions RF non guidées pour leur plus faible puissance d'émission requise ou optiques en raison de leur compatibilité avec la technologie CMOS, qui désormais peut supporter les fréquences de fonctionnement exigées pour moduler les signaux RF. Mais, les solutions envisagées jusque là nécessitent une circuiterie importante pour générer des canaux RF orthogonaux, avec des capacités limitées en termes de flexibilité d'allocation de ces canaux. Pour y remédier, le projet WiNoCoD (Wired RF Neetwork-on-Chip Reconfigurable-on-Demand) propose pour la première fois une approche basée sur l'OFDMA (Orthogonal Frequency Division Multiple Access) pour l'accès à l'interconnexion RF intra-puce. En effet, cette approche permet une gestion purement numérique de l'allocation des ressources fréquentielles de communication, apportant ainsi une grande flexibilité exploitable à la volée. La puce WiNoCoD propose une architecture générique à 2048 coeurs de traitement répartis en trois niveaux de hiérarchie dont les éléments du niveau supérieur sont reliés par une interconnexion RF basée sur l'OFDMA. Dans cette thèse, nous proposons des schémas de reconfiguration de l'allocation des ressources fréquentielles centralisés et décentralisés adaptés aux contraintes spécifiques de l'environnement intra-puce à très grand nombre de coeurs. Plusieurs algorithmes d'allocation de fréquence sont étudiés dans le cas de modèles stochastiques de trafic réalistes. L'approche dynamique proposée permet d'obtenir des performances remarquables en termes de latence, dans des conditions de trafic à la limite de la capacité du NoC, pour une faible complexité de calcul. En outre, un nouvel algorithme d'allocation est introduit pour décroître la latence de transmission en tenant compte de la nature bimodale des paquets de cohérence de cache d'une telle puce. Nous montrons que cela permet de diminuer la latence moyenne de livraison des paquets d'un facteur 10 en comparaison des autres solutions étudiées dans un contexte d'intensité de trafic modérée et pour des lignes de cache plus longues. Nous étudions aussi l'utilisation dynamique d'ordres de modulation comme un degré de liberté supplémentaire et nous proposons un algorithme de sélection du meilleur compromis entre consommation d'énergie et délai de livraison des paquets. Nous montrons ainsi que la puissance moyenne peut être améliorée d'un facteur 15 en relaxant le délai de livraison de quelques symboles. Une analyse de capacité au sens de la théorie de l'information est aussi effectuée pour différentes topologies de la ligne guidée.

## Acknowledgements

First of all, i would like to express my sincere gratitude to my thesis advisor Christophe Moy, SCEE team member and contributor to our project Yves Louët and head of SCEE team Jacques Palicot for giving me the chance to pursuit research in a warm and productive environment. Their guidance and friendship made my 3 years in Rennes a great life experience. I wish also to thank Carlos Bader, Amor Nakfha, Pascal Cotret and all professors of CentraleSupélec-Rennes.

I wish to thank especially to my office mates Marwa Chafii and Lamarana Diallo for their helps and kindness. In addition to this, special thanks to all my friends Vincent Savaux, Malek Naoues, Yacine Abdellaoui, Jerome Manceau, Amine Kacete, Vincent Gouldieff, Samba Traore, Sumit Darak, Navikkumar Modi, Xiguang Wu, Oussama Lazrak, Quentin Bodinier, Abir Amri and all fellows in CentraleSupélec-Rennes. Dedicated to my parents

## Chapter 0

# Résumé en Français : Allocation Dynamique de Bande Passante pour l'Interconnexion RF d'un Résau-sur-Puce

#### Chapitre 1 : Introduction

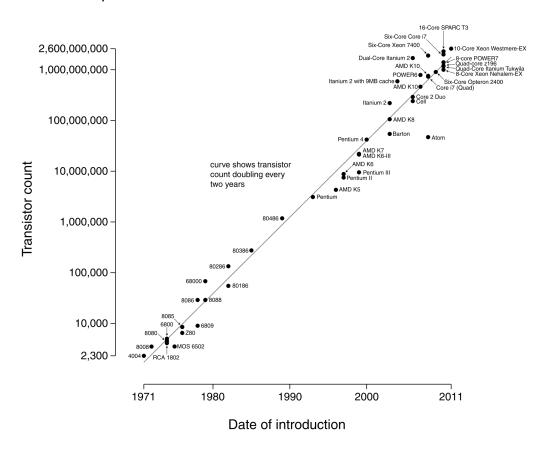

L'accélération des traitements numériques a été portée depuis un demi-siècle par la diminution de la géométrie des transistors, mais cette tendance est dorénavant freinée en raison de problèmes thermiques et lithographiques liés aux dimensions nanométriques actuelles. Par ailleurs, le compromis entre puissance de calcul et consommation a poussé l'utilisation de plusieurs processeurs en parallèle sur une même puce pour exécuter des applications à forte exigence en termes de calculs. Aujourd'hui, il est fréquent de voir des puces avec plusieurs cœurs dans nos téléphones, ordinateurs, serveurs, terminaux ADSL, appareils photo numériques, etc.. En électronique embarquée, on parle de systèmes sur puces (System-on-Chip ou SoC) où les unités sont généralement de natures différentes (hétérogènes). Dans le domaine informatique, cela se traduit par la mise en parallèle de plusieurs voire nombreuses unités de traitement identiques (homogène), comme dans les GPU (Graphical Processing Units), processeurs superscalaires, etc.. Dans un avenir proche, on estime à quelques milliers le nombre de cœurs présents sur une seule puce. Ces systèmes sont appelés généralement avec la dénomination anglaise Chip Multiprocesseurs (CMPs) ou processeurs ManyCore.

Avec l'augmentation du nombre de cœurs dans une même puce, le problème des communications entre les cœurs devient prépondérant. Il est devenu impossible d'implanter des fils dédiés point à point entre tous les coeurs et des problèmes de congestion apparaissent avec les bus conventionnels. Les chercheurs ont introduit un nouveau paradigme connu sous le nom de réseau sur puce (Network-on-Chip ou NoC), où la couche de communication est détachée des coeurs et la transmission entre cœurs est effectuée par paquets via des routeurs, comme dans un réseau. Même si les NoC ont démontré leur performance en termes de latence et de bande passante, ils atteignent à leur tour des limites à partir de plusieurs dizaines de cœurs.

Récemment, les interconnexions optiques et radiofréquence (RF) sur puce ont été proposées pour fournir une solution à l'apparition de ce goulot d'étranglement. Ces interconnexions utilisent des ondes électromagnétiques pour transmettre des signaux à des vitesses plus proches de celle de la lumière, à la différence du câblage de cuivre classique utilisé jusqu'ici. Cependant, ces deux architectures, optiques et RF, ont besoin d'implanter des circuits spécialisés dans les émetteurs-récepteurs de chaque noeud (en regroupe plusieurs cœurs entre eux car connecter chaque cœur serait trop complexe) qui a un accès au canal de communication. En raison de la nature statique des architectures d'émission réception jusqu'à présent identifiées dans la littérature, l'allocation dynamique des canaux de communication à différents noeuds, en fonction de leur demande instantanée de bande passante est impossible. Cependant, en raison du trafic très fluctuant généré par les applications entre les cœurs, les approches RF et optiques apportent jusqu'à présent une solution limitée, ou surdimensionnée entre les capacités qu'elles apportent et celles qui peuvent être exploitées effectivement en cours de fonctionnement.

Afin de remédier à ces limitations, le projet WiNoCoD (Wired RF Network-on-Chip Reconfigurable-on-Demand) a été initié grâce au financement de l'Agence Nationale de Recherche (ANR). Les partenaires du projet sont ETIS-ENSEA, LIP6 -UPMC, NXP Semiconductors et IETR-CentraleSupélec. Ce travail de thèse contribue au projet WiNoCoD. La contribution majeure du projet WiNoCoD pour la communauté scientifique des réseaux-sur-puce est son interconnexion de communication RF basée sur l'OFDMA (Orthogonal Frequency Division Multiplexing Access). Contrairement aux interconnexions sur puce existantes, la modulation OFDM, support de l'OFDMA, permet de générer de nombreux canaux orthogonaux grâce à un nombres de circuits analogiques réduit (non pas une chaîne RF à bande étroite par canal, mais une seule chaîne RF globale à large bande). En outre, l'encodage des données sur les canaux de fréquences orthogonales est une procédure purement numérique en OFDM et sa capacité intrinsèque de diffusion est un atout très important en raison des caractéristiques particulières du trafic des données dans un réseau sur puce. Les contributions de cette thèse sont :

- Une structure de contrôleur de RF est proposée pour l'interconnexion OFDMA de WiNoCoD.

- Plusieurs algorithmes d'allocation de bande passante efficaces (distribués et centralisés) sont proposés et leurs performances évaluées, concernant les demandes et contraintes très spécifiques de l'environnement sur-puce.

- Un protocole innovant pour l'arbitrage des sous-porteuses pour des longueurs bimodales de paquets sur-puce, qui ne nécessite aucune signalisation supplémentaire est introduit.

- Une évaluation de l'utilisation des ordres de modulation élevés est étudiée en fonction du compromis entre délai et consommation d'énergie.

- Les algorithmes proposés ne sont pas restreints aux limites de WiNoCoD, mais peuvent être étendus à d'autres interconnexions RF basées sur l'OFDMA pour les architectures CMP ou des réseaux à haute vitesse.

## Chapitre 2 : L'Ere des «1000 cœurs» et le défi des réseauxsur-puce

#### 2.1 Multiprocesseurs

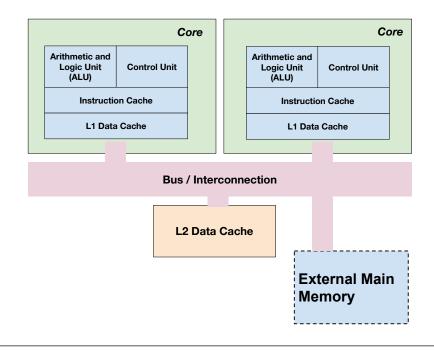

Les CMPs offrent une nouvelle réponse aux limitations des monoprocesseurs en utilisant de nombreux cœurs relativement simples plutôt qu'un seul cœur puissant, ce qui augmente les performances à la fois en termes de puissance de calcul et d'efficacité énergétique en exploitant le parallélisme. Un cœur est une unité de traitement arithmétique qui effectue les opérations logiques et de commande, qui est généralement composé de deux entités distinctes: unité arithmétique et logique (ALU) et une unité de commande (CU).

#### 2.1.1 Caches et Mémoire

Dans un processeur multi-cœurs, chaque cœur dispose d'une mémoire pour les données et les instructions, sous la désignation Mémoire cache de niveau 1 (L1 - Level 1). La mémoire cache (antémémoire) est composée de registres temporaires pour un volume relativement faible de données, qui stocke les copies de la mémoire principale et qui offre un accès très rapide pour le cœur de traitement. En fonction de l'architecture, il peut y avoir des niveaux plus élevés de caches tels que L2 et L3. Cependant, toutes les architectures ne partagent pas cette hiérarchie. Par exemple, le CMP qui est envisagé dans ce travail de thèse a seulement un cache L1 pour chaque cœur et une mémoire RAM partagée et distribuée physiquement entre tous les coeurs, qui peut être considéré comme un cache L2.

#### 2.1.2 Protocole de Cohérence de Cache

Les cœurs d'un multiprocesseur peuvent accéder à tout endroit dans la mémoire partagée. Cependant, quand un cœur modifie les données dans un emplacement d'adresse, il peut y avoir déjà des copies des caches simultanées dans d'autres cœurs. Par conséquent, lorsque les nouvelles données sont écrites, les cœurs (qui utilisent cette adresse) risquent d'avoir une copie erronée pour cette ligne d'adresse. Par conséquent, ces cœurs doivent être informés du changement de contenu. Ce problème d'incohérence est connu sous le terme de cohérence de cache. Il existe différents protocoles pour résoudre le problème de la cohérence de cache, mais les plus largement connus sont "espionnage de bus" et "espionnage à répertoire". Dans l'espionnage, à chaque fois qu'un cœur ne peut pas retrouver les données dans son cache, il diffuse une requête de lecture sur le bus reliant tous les cœurs et les caches. Comme chaque contrôleur de cache des autres cœurs écoute ces émissions, ils invalident les copies dans leurs caches avec l'étiquette de la ligne d'adresse dans cette demande. La deuxième approche est le protocole par répertoire (directory), où les répertoires sont responsables de la mise à jour et de mémoriser les états et les propriétaires de blocs mémoire (lignes d'adresse). Chaque cœur, qui veut extraire la copie d'une adresse dans la mémoire principale, doit se référer au répertoire en premier lieu. Afin d'orchestrer l'exécution d'applications et fournir la cohérence des caches, les cœurs et les éléments de mémoire doivent communiquer entre eux. Ces messages de cohérence de cache constituent la base du profile des communications sur une telle puce.

#### 2.2 Réseau-sur-Puce

#### 2.2.1 Des Bus au Réseau-sur-Puce

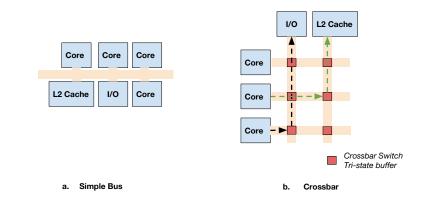

Quand le nombre d'éléments reliés à un même bus augmente, la charge capacitive et résistance parasite augmentant également, ce qui est une cause supplémentaire de retard dans les transmissions sur le bus. Dans les architectures submicroniques classiques, les informations numériques sont transmises entre les noeuds par des fils de cuivre en augmentant ou en diminuant la tension électrique sur ces fils. En outre, comme le nombre d'unités qui veut accéder au bus augmente, la bande passante par unité diminue, ce qui cause d'autant plus de risques de congestion. A l'échelle des CMPs, avec un nombre de cœurs de plus en plus important, jusqu'à atteindre plusieurs milliers d'unités, un cadre de communication de manière paquetisée a été introduit, connu sous le nom de Réseau-sur-puce (NoC).

#### 2.2.2 Topologies de NoC

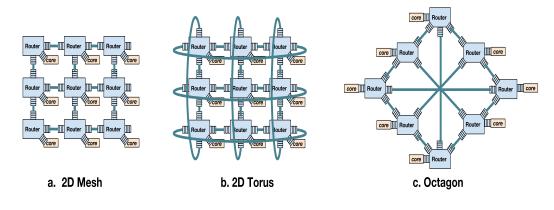

Depuis les recherches initiales sur les NoC, différentes topologies ont été proposées : 2Dgrille, 2D-tore, octogone etc. (Fig 0.1). Malgré ses avantages, comme nous approchons d'une ère avec des centaines, voire des milliers de cœurs, ces NoC classiques sont aux prises avec un problème d'extensibilité. Par exemple, on peut voir que la distance entre les deux cœurs les plus éloignés dans un réseau de grille est  $2\sqrt{N_{cores}}$ , où  $N_{cores}$  est le nombre de cœurs.

FIGURE 0.1: Trois des topologies les plus classiques pour les NoCs 2D, où les éléments sont interconnectés via des routeurs tamponnées: (a) grille (b) tore (c) octogone

#### 2.2.3 Tera-Scale Multi-core Processor Architecture (TSAR)

Il est important de mentionner ici le projet TSAR (Tera-Scale Multicore processeur Architecture) [1]. Parmi les partenaires de ce projet, l'UPMC-LIP6 et NXP Semiconductors sont aussi des partenaires du projet WiNoCoD. Dans un sens, ce projet peut être considéré comme une base primordiale de WiNoCoD, comme ses principes architecturaux en termes de mémoire et de protocole de cohérence de cache a de nombreuses caractéristiques communes avec TSAR. La différence fondamentale du projet WiNoCoD est son infrastructure NoC. En effet, TSAR a été modélisé avec un réseau de grille-2D classique pour la communication entre les tuiles (unité atomique de 4 cœurs avec sa RAM, un contrôleur de répertoire).

#### 2.3 Interconnexion RF et Optiques

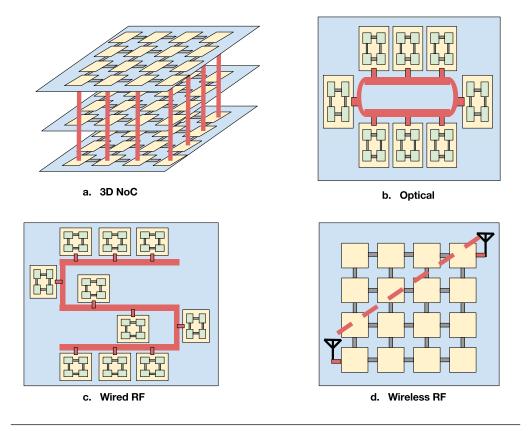

Avec un horizon où des milliers de cœurs seront concentrés sur une même puce, l'industrie des semi-conducteurs a compris que les NoCs filaires classiques sont loin de fournir les besoins attendus en termes de latence, de bande passante et de contrainte de puissance électrique. Ainsi a émergé l'idée de communiquer par ondes électromagnétiques à une vitesse plus proche de celle de la lumière. L'International Technology Roadmap for Semiconductors (ITRS) affirme que les interconnexions optiques et RF représentent l'avenir pour satisfaire les besoins à long terme de bande passante, de latence, la puissance, considérant que l'on s'attend à ce que le nombre de cœurs sur une puce dépasse plusieurs milliers avant la fin de la prochaine décennie (Fig. 0.2).

FIGURE 0.2: L'illustration d'options d'interconnexion sur puce innovante récemment proposées

#### 2.3.1 Interconnexions Optiques

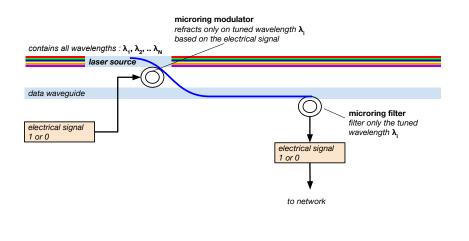

Les développements récents de la nanophotonique ont permis l'implantation d'éléments optiques tels que des guides d'ondes denses, des filtres, des modulateurs etc. sur une seule puce. Toutefois, ces tentatives sont encore dans la phase de début. Récemment, [2] a démontré sa faisabilité dans le cas d'un simple multiprocesseur avec 2 cœurs, avec une interconnexion optique sur puce complète. Pour permettre le transfert simultané de plusieurs signaux sur le même guide d'ondes, des canaux orthogonaux (longueurs d'onde) sont générés. Une source laser sur la puce ou hors de la puce génère et fait circuler l'énergie photonique sur un guide d'onde dédié, capable de véhiculer toutes les longueurs d'onde utilisées dans le système. Des résonateurs en micro-anneaux (microring resonators) sont utilisés en tant que modulateurs pour la transmission de données et en tant que filtres pour la réception. Donc, nous pouvons comprendre que nous avons besoin d'implanter un grands nombre de ces modules pour créer tous les canaux orthogonaux nécessaires, ce qui est encombrant et consommateur d'énergie d'une part et peu évolutif d'autre part. Chacun de ces micro-anneaux est fabriqué pour une longueur d'onde spécifique, qui est déterminée par traitement thermique, et par différence de quantité de charge électrique injecté, ou en faisant varier le rayon de l'anneau au cours du processus de fabrication. Ainsi, ce système est statique par nature et il est impossible de redistribuer la bande dynamiquement entre les nœuds de traitement. ATAC et Corona sont deux exemples de l'état de l'art des architectures optiques sur puce.

Les interconnexions photoniques sont considérées comme une technologie efficace pour réduire la latence de manière significative grâce à leur grande bande passante, tout en offrant une faible consommation électrique. Cependant, leur praticabilité est mise en doute, au moins pour un avenir proche, à cause du bruit du couplage de guide d'ondes et de la taille relativement importante des composants optiques pour les intégrer en grands nombres dans une puce. La fabrication de composants photoniques sur puce est encore confrontée à de nombreux défis. Il impose la juxtaposition de deux technologies differents : la technologie CMOS pour l'architecture de traitement et la technologie optique pour l'interconnexion. En outre, il n'existe pas d'éléments de stockage optique, ainsi un tel système dépend d'une infrastructure électrique additionnelle. Comme mentionné précédemment, les NoC optiques nécessitent des sources laser constantes soit sur la puce, soit hors puce, avec un guide d'onde dédié séparé.

#### 2.3.2 Interconnexions RF

En raison des inconvénients des interconnexions optiques, les chercheurs ont orienté leurs investigations vers les interconnexions Radio Fréquence (RF), qui utilisent encore les ondes électromagnétiques (EM). La fréquence de transition des transistors CMOS est toujours dans une tendance d'augmentation exponentielle de génération en génération, permettant désormais d'envisager des fréquences maximales jusqu'à 1 THz. Cela positionne les composants RF CMOS comme des candidats naturels pour les émetteurs récepteurs sur puce à haute fréquence. L'avantage de cette approche est sa compatibilité CMOS avec la partie traitement de la puce (cœurs, mémoires, etc.). De plus, c'est une technologie beaucoup plus mature par rapport à l'optique sur puce.

Il y a deux propositions distinctes pour les interconnexions RF: par la propagation en espace libre (sans fil mais avec une antenne d'émission et une antenne de réception) ou la propagation guidée (RF filaire ou sur guide d'ondes). Pour la RF sans fil, l'idée est de générer des liaisons à haut débit entre les cœurs distants, afin de réduire la latence et la congestion, sans la nécessité d'un milieu de propagation supplémentaire dédié. Le défi majeur dans ce paradigme est la difficulté de caractériser les effets de la propagation, ainsi que la fabrication de petites antennes en nanotechnologies avec des caractéristiques électromagnétiques adéquates. La viabilité des antennes sur puce sans fil n'est pas encore démontrée et les propositions innovantes qui apparaissent, telles que les antennes en nanotubes de carbone, ne sont pas encore des technologies matures. Ainsi, la propagation RF via une ligne de transmission guidée (RF filaire) a reçu plus d'attention dans la communauté de la recherche sur puce par rapport à son homologue sans fil. Comme la distance de communication est faible, la méthode de couplage capacitif efficace peut être utilisée pour réaliser la transmission. En outre, le guide d'ondes permet une atténuation réduite, donc une puissance de transmission, qui est la plus consommatrice d'énergie dans un système de communication, limitée au plus juste (et non dispersée dans toutes les directions). C'est l'option qui sera considérée dans ce travail.

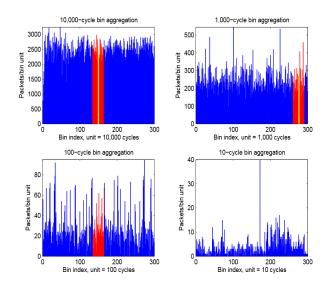

#### 2.4 Caractéristiques du Trafic sur Puce

Comme première étape, les chercheurs se sont appuyés sur des modèles de trafic synthétiques primitifs pour évaluer leurs conceptions, mais ces modèles se révèlent souvent trop naïfs pour assurer la validité des simulations. D'autre part, il y a un nombre trop limité d'applications sur multicœurs, telles que celles fournies par PARSEC ou Splash-2. Un modèle statistique réaliste universel d'émulation du trafic d'un NoC est essentiel. Il existe différents modèles stochastiques de trafic pour la simulation sur puce dans la littérature, utilisant la notion d'auto-similarité, phénomène ayant pour origine la hiérarchie de cache dans les systèmes à mémoire partagée. Nous nous basons sur ces modèles de l'état de l'art dans notre travail.

## Chapitre 3 : Projet WiNoCoD et Interconnexion RF filaire basée sur l'OFDMA

Nous avons vu que les interconnexions RF filaires apparaissent comme le candidat le plus réaliste à court terme. Cependant, tout comme leurs homologues optiques, les interconnexions RF proposées dans l'état de l'art reposent sur des circuits analogiques pour générer des canaux fréquenciels, ce qui limite leurs capacités d'allocation dynamique des ressources, notamment en termes de coût, de surface occupée et de consommation. Pour surmonter tous ces désavantages et fournir une réelle avancée en termes de bande passante reconfigurable, le projet WiNoCoD (Wired RF Network-on-Chip Reconfigurable on Demand) a été initié en 2013, en partenariat avec l'ANR, par ETIS-ENSEA, LIP6-UPMC, Supelec-IETR et NXP Semiconductors.

#### 3.1 L'architecture sur Puce de WiNoCoD

#### 3.1.1 Niveaux de Communication

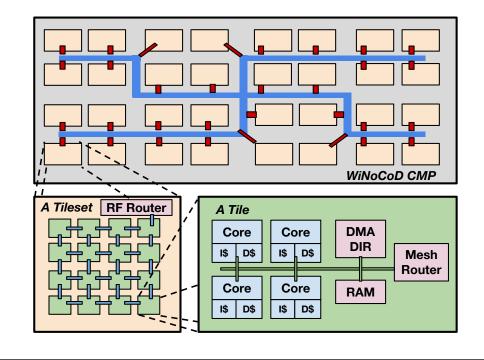

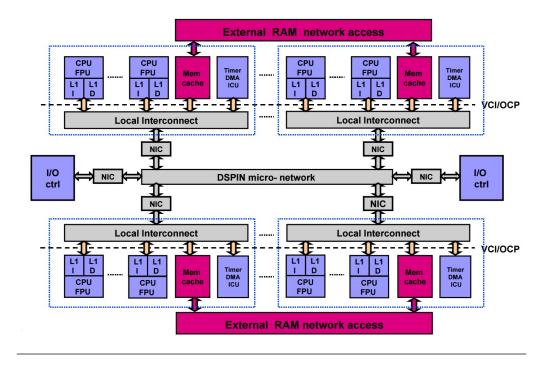

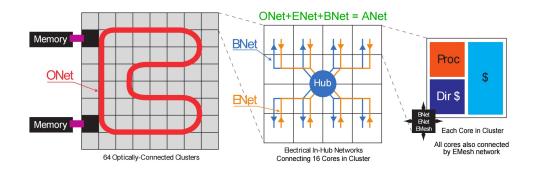

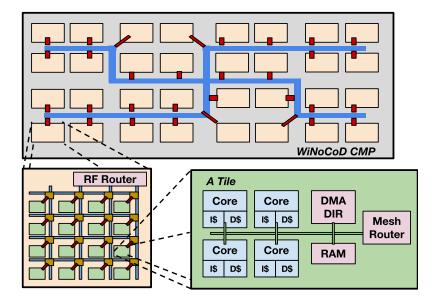

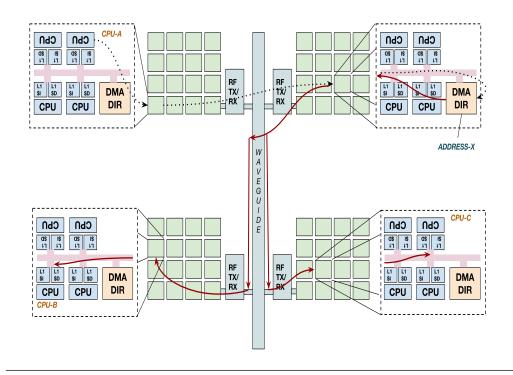

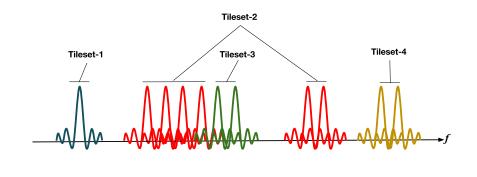

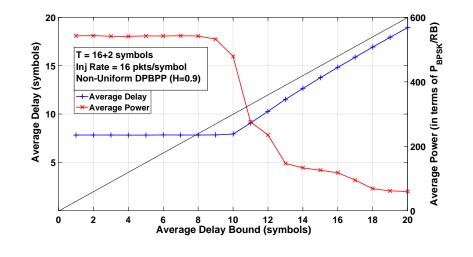

Le circuit issu de WiNoCoD est un multiprocesseur massivement parallèle et générique de 2048 cœurs de traitement. Un principe de mémoire partagée est adopté, où tout l'espace d'adresse est accessible par tous les cœurs (NUMA - Non Uniform Memory Architecture). Il existe 3 niveaux hiérarchiques principaux, avec un type d'infrastructure de communication particulier pour chaque niveau. Au niveau le plus bas se trouve la tuile, constituée de 4 cœurs, 2 Go de RAM (une sous-partie de la mémoire globale du système) et un contrôleur de mémoire. Tous ces éléments sont reliés entre eux par un crossbar switch. Au niveau suivant, 16 tuiles sont interconnectés par un réseau en quadrillage (mesh 2D). Ceux-ci sont appelés tuilesets (ou grappes de tuiles) et il y a 32 tuilesets au total. Au plus haut niveau, ces 32 tuilesets sont interconnectés par la ligne de transmission RF. Par exemple, si un cœur veut transmettre des informations à un autre cœur dans un tuileset différent, le message doit traverser les 3 différentes couches de communications. L'architecture de WiNoCoD avec 2048 cœurs est illustrée sur la Fig. 0.3.

#### 3.1.2 Détails du Protocole de Cohérence de Mémoire Cache

Nous employons dans WiNoCoD un protocole de cohérence de cache hybride par répertoire (Distributed Hybrid Cache Coherency Protocol), comme dans TSAR [1]. Une approche similaire est adoptée pour ATAC [3], qui est une architecture à 1024 cœurs interconnectés en optique. Une approche d'écriture transversale (Write Through) est adoptée,

FIGURE 0.3: L'architecture à 3 niveaux de WiNoCoD, avec 2048 cœurs au total

c'est-à-dire que dans le cas où un cœur veut écrire une donnée à une ligne d'adresse, il transmet une demande d'écriture dans le répertoire responsable de cette ligne d'adresse. Par conséquent, si la ligne d'adresse destinataire est associée au répertoire de la même tuile, le message ne va pas à l'extérieur de la tuile, et utilise uniquement le crossbar switch. De même, si la ligne d'adresse est dans une tuile différente mais dans le même tuileset, il utilise uniquement le réseau en quadrillage. Si la ligne d'adresse est dans une tuile d'un tuileset différente, alors il doit utiliser l'interconnexion RF. Dans le protocole DHCCP de WiNoCoD, lorsque le nombre de cœurs partagants d'une ligne d'adresse dépasse un certain seuil (par exemple 8), le répertoire commence à garder le nombre de partageurs, plutôt que de garder les identificateurs (ID) de chaque cœur explicitement. Dans ce cas, pour chaque invalidation, le répertoire diffuse un message à chacun des 2048 cœurs et compte le nombre de messages d'ACK pour vérification. C'est la seule façon d'être en mesure de suivre des milliers de partageurs possibles. Le répertoire dans une tuileset est représenté sur la Fig. 0.4.

#### 3.2 Notions Préliminaires sur l'OFDMA

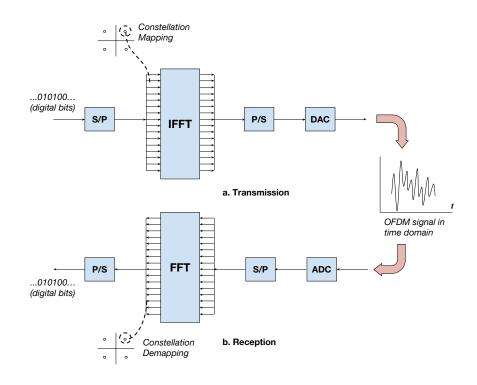

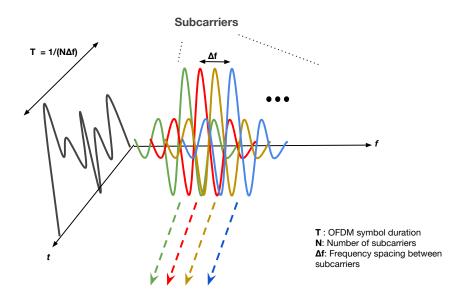

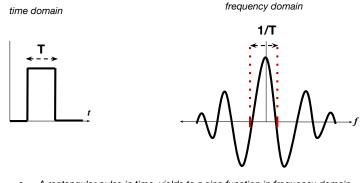

L'OFDM (Orthogonal Frequency Division Multiplexing) est une technique de modulation qui transforme un signal de bande passante large en plusieurs canaux orthogonaux plus étroits. L'OFDM code ainsi l'information numérique sur le domaine des fréquences plutôt que dans le domaine temporel. Pour le mettre en oeuvre, les données numériques

| Address Line | Flag | Sharer Cor | es          |   |        |

|--------------|------|------------|-------------|---|--------|

| #0000000     | 0    | C-0013     | C-0048      |   | C-1004 |

| #000000F     | 1    | 27 (Number | of sharers) |   |        |

| •            |      |            |             | • |        |

| #0000100     | 0    | C-0203     |             | : |        |

Memory Directory in a Tileset

FIGURE 0.4: Context du répertoire de la mémoire dans une tuileset

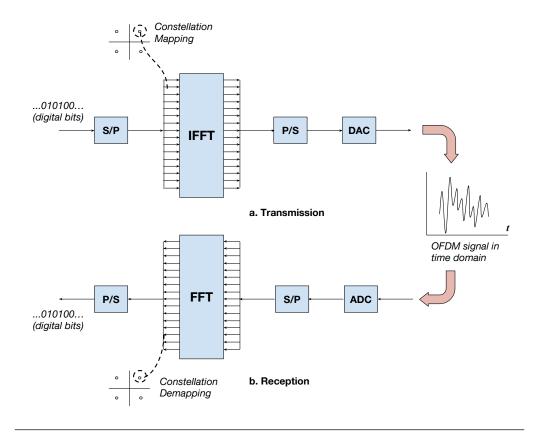

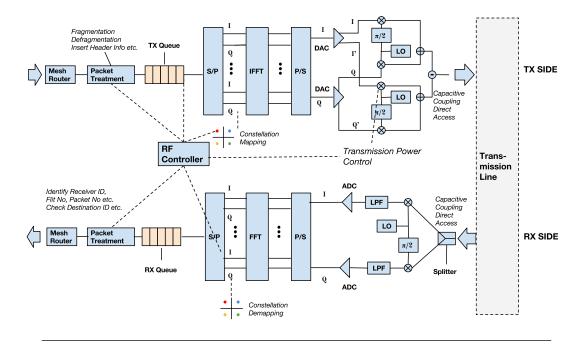

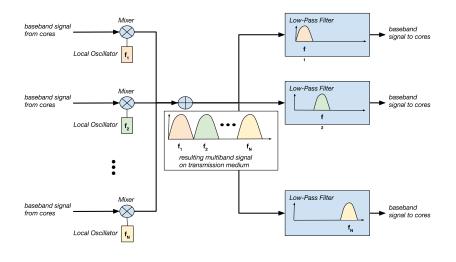

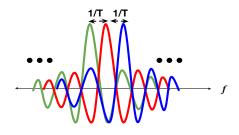

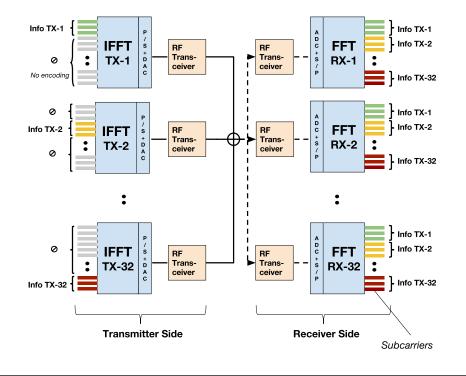

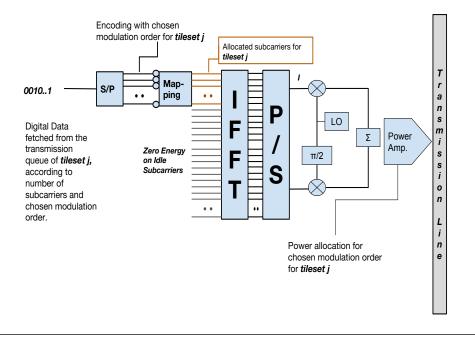

sont tout d'abord mises en symboles de constellations BPSK, QPSK, M-QAM, etc., et chaque symbole de la constellation est associé à une sous-porteuse. La sous-porteuse est l'unité de fréquence atomique dans un signal OFDM, ou en d'autres termes c'est l'ensemble de toutes les sous-porteuses à bande étroite qui sont émises en parallèle. C'est une transformée de Fourier discrète inverse (IDFT) qui est appliquée au vecteur de N symboles pour les positionner sur N sous-porteuses en parallèle, où chacun d'eux est maintenant un nombre complexe associé au symbole de la constellation codée (chaque nombre complexe représente un certain nombre de bits). Le résultat de cette transformation donne un vecteur de N nombres complexes. Après, ce vecteur de N points est sérialisé et converti en un signal dans le domaine temporel. Ce signal s'est appelé un symbole OFDM. A la réception, l'inverse de ces opérations est effectuée. Les blocs élémentaires d'un émetteur-récepteur OFDM sont montrés sur la Fig. 0.5.

Les avantages de l'OFDM peuvent être énumérés comme suit :

- Robustesse contre les canaux sélectifs en fréquence et l'égalisation est simple pour chaque sous-porteuse.

- Génération de canaux fréquentiels par un processus numérique, d'où l'économie de nombreux circuits analogiques.

- Une bande passante reconfigurable grâce à une mise en œuvre numérique.

- Haute efficacité spectrale grâce à des sous-porteuses fenêtrées par des fonctions sinc orthogonales.

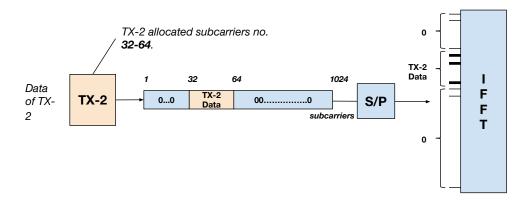

L'OFDMA (Orthogonal Frequency Division Multiple Access), d'autre part est un schéma d'accès multiple basé sur l'OFDM, avec tous les avantages de la couche physique de l'OFDM dont une bande passante reconfigurable par utilisateur. Un utilisateur encode l'information sur ses sous-porteuses allouées à la transmission comme expliqué

FIGURE 0.5: Les blocs de base d'un émetteur-récepteur OFDM

précédemment, et maintient les autres inactives (zéro avant IFFT) pour les laisser libres à d'autres utilisateurs. Cette procédure est mise en oeuvre dans le domaine numérique, simplement en manipulant le vecteur de bits avant l'IFFT. Cette tâche peut être réalisée par un microprocesseur ou un circuit numérique. En outre, comme chaque noeud dans le système doit décoder un symbole OFDM en entier pour extirper le signal le concernant, l'OFDMA est doté de capacités de diffusion intrinsèques.

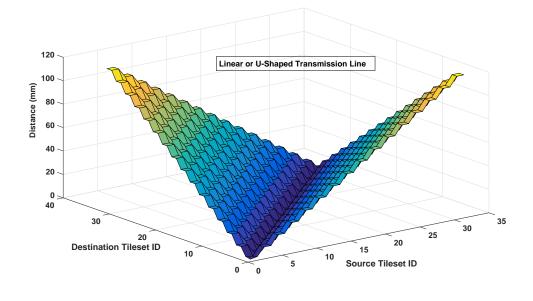

#### 3.3 L'Interconnexion RF guidée de WiNoCoD basée sur l'OFDMA

La technologie des convertisseurs fournis par notre partenaire NXP a une bande passante de 20 GHz. En raison des contraintes d'adaptation et de la propagation guidée, le spectre le plus approprié a été choisi entre 20-40 GHz. Il est décidé d'avoir 1024 sous-porteuses OFDM, ainsi des modules FFT et IFFT de 1024 points sont nécessaires. Comme nous avons la bande passante est de 20 GHz, avec 1024 sous-porteuses l'espacement de fréquence entre les sous-porteuses est de 19.53 MHz, soit une durée symbole de T = 1 / 19.53 MHz = 51.2 nanosecondes.

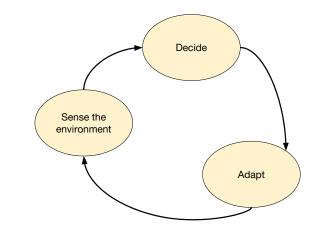

#### 3.3.1 Contrôleur RF

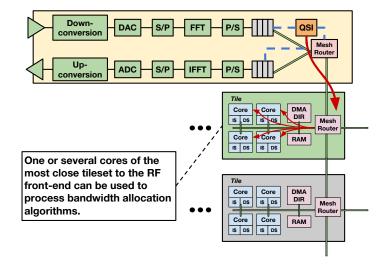

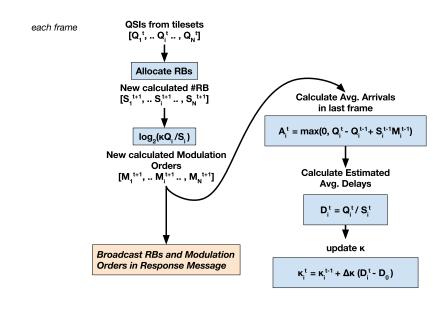

Un paquet qui doit être envoyé par une tuile dans la ligne guidée RF est routé à travers le réseau en quadrillage du tuilset vers le contrôleur RF de ce tuileset. Ces paquets sont traités si nécessaire, c'est-à-dire fragmentation ou défragmentation, extraction ou insertion d'informations telles que l'identifiant de la source, etc., puis insérés dans la file d'attente de transmission. Le contrôleur RF prend certaines décisions selon des informations qu'il possède de l'état de sa file d'attente (Queue State Information - QSI) de transmission (TX) et les informations de trafic en provenance d'autres tuilesets qu'il peut recevoir directement des autres tuilesets, soit lui être fournis par une unité centrale intelligente (Central Intelligent Unit-CIU). Le contrôleur RF modifie en fonction la position et l'encodage en symboles des données dans son buffer précédent la IFFT et configure ainsi son occupation des sous-porteuses du symbole OFDM qui va être transmis. Chaque tuileset fait de même pour chaque symbole OFDM et les porteuses d'un symbole OFDM sont ainsi réparties entre tous les tuilesets. La répartition de l'occupation des sous-porteuses entre les tuilsets est l'enjeu de la thèse et plusieurs algorithmes vont être proposés dans le manuscrit. L'un ou l'autre pourra être utilisé en changeant le programme du ou des processeurs du contrôleur RF gérant le buffer d'émission.

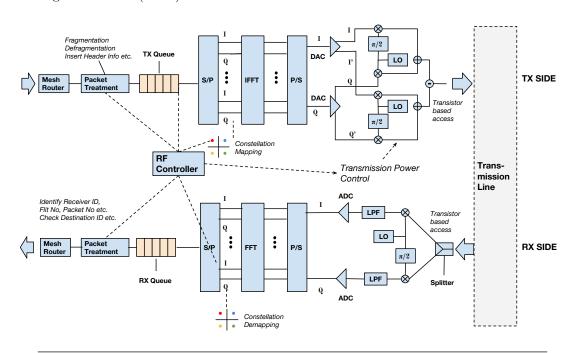

#### 3.3.2 Tête analogique RF

Cette partie est le travail de thèse de Frédéric Drillet et Lounis Zerioul du laboratoire ETIS. Dans la tête d'émission analogique RF, les mélangeurs associent un signal OFDM en bande de base avec la porteuse issue de l'oscillateur local. Le mélange se produit dans un MOSFET, dont la grille et le drain sont respectivement alimentés par l'oscillateur local et le signal en bande de base. La sortie de fréquence plus élevée est récupérée dans la source de transistor MOSFET. Grâce aux sorties différentielles du convertisseur numérique-analogique (CNA), deux modulateurs-I/Q sont combinés pour supprimer les replicas de fréquences. Ensuite, ce signal est amplifié par un amplificateur et injecté sur la ligne RF par un couplage à transistors qui a été préféré à un couplage capacitif classique.

En réception, le signal reçu de la ligne de transmission est amplifié par un amplificateur à faible bruit (LNA) et envoyé aux mélangeurs et l'oscillateur local de 30 GHz pour obtenir les composantes en phase (I) et en quadrature (Q). Des filtres passe-bas (LPF) sont également utilisés puis les composantes I et Q sont converties dans le domaine numérique par les convertisseurs analogique-numérique (CAN). Apres une conversion série vers parallèle, ce vecteur de valeurs I et Q est transposé dans le domaine fréquenciel par un module de transformée de Fourier rapide (FFT). Les symboles de la constellation qui en résultent sont extraits sous forme de bits; sérialisés et finalement sont fournies au contrôleur RF en réception. La tête d'émission et de réception analogique d'un tuileset est illustrée sur la Fig. 0.6.

FIGURE 0.6: La tête numérique et la tête analogique RF pour la transmission et la réception dans un tuileset

Les modules FFT et IFFT sont conçus en technologie CMOS 120 nm. Il a été estimé que la superficie de chacun de ces modules est de 0,31 mm2 et la consommation d'énergie de 67.5 mW. La durée de calcul pour FFT / IFFT est considérée comme une latence du pipeline de la communication. Chacun des CAN et CNA sont conçus avec la technologie 120 nm et ont une superficie estimée de 0,12 mm<sup>2</sup> et leur consommation d'énergie de 81 mW.

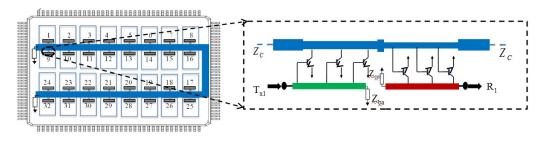

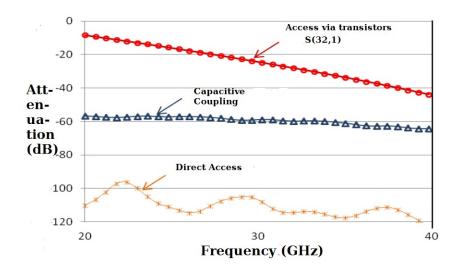

L'étude de la ligne de transmission s'est effectuée dans le cadre de la thèse de Mohamad HAMIEH du laboratoire ETIS. Une ligne de transmission en forme de croix, comme illustré sur la Fig. 0.3 a été conçue pour minimiser la distance entre les deux tuilesets plus éloignés du CMP. Dans cette configuration, la distance maximale entre deux noeuds est de 80 mm. La forme en croix donne également un avantage supplémentaire, en fournissant une réponse en fréquence plate sur la bande passante de 20 GHz. Sur la gamme de fonctionnement, entre 20 et 40 GHz, l'atténuation attendue (issue des simulations) est de -10 dB à -42 dB entre les deux nœuds les plus éloignés et relativement linéaire sur toute la gamme de fréquence. Ceci peut paraitre variable mais comparativement au cas aérien qui connait beaucoup de variations fréquentielles et temporelles, on peut faire l'approximation ici de une certaine stabilité. On retrouve cette quasi-invariabilité en fréquence entre tous les autres noeuds, avec des atténuations plus faibles au fur

et à mesure que la distance décroît entre les deux nœuds considérés. Cela simplifie l'utilisation de l'OFDM puisque toutes les sous-porteuses subiront la même atténuation quelle que soit la fréquence utilisée dans le système. Seule la position relative entre les nœuds fera varier l'atténuation qui donc sera prévisible. Le choix des porteuses ne nécessitera pas ainsi de modifier la puissance de transmission, mais seulement le choix de l'ordre de modulation. Une ligne coplanaire en technologie CMOS à 0.25 micromètre fournie par NXP semiconductor est utilisée. Un mécanisme d'accès par transistor est préféré la celui d'un couplage capacitif classique pour accéder à la ligne de transmission depuis les têtes analogiques d'émission et de réception des tuilesets. Le signal est transmis entre la ligne guidée de transmission et la tête RF sans contact physique. Cette méthode réduit le phénomène des réflexions et de l'atténuation fluctuante sur différentes fréquences (désadaptation).

## Chapitre 4 : Problème d'allocation de la bande passante d'un RF NoC

#### 4.1 Interconnection OFDMA de WiNoCoD et motivation

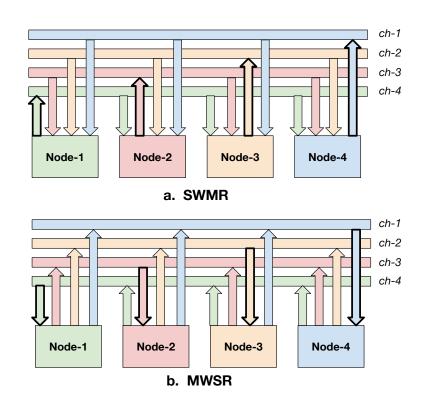

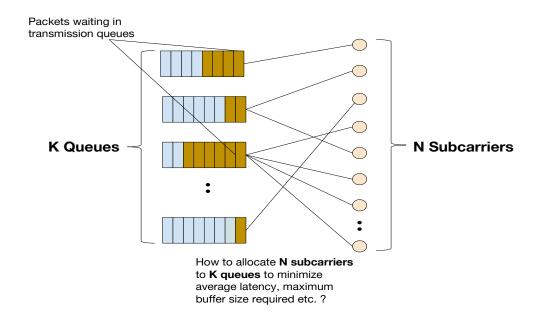

Nous avons vu que chaque tuileset a un point d'accès à la ligne de transmission via un modulateur/démodulateur OFDMA. Grâce à la capacité de diffusion intrinsèque de l'OFDMA, chaque paquet envoyé n'a pas besoin d'être dupliqué pour être diffusé, comme toutes les transmissions effectuées par un utilisateur sont reçues par tous les autres (SWMR). Ceci augmente considérablement la capacité du système compte tenu de l'exigence particulière, dans le cas d'un système à cohérence de cache de répertoire, en termes de nombre de paquets de diffusion / multidiffusion. Une sous-porteuse sur un symbole OFDM peut être considérée comme un élément servant à la transmission de l'information (1,2, etc. bits sur la base de l'ordre de modulation utilisé BPSK, QPSK, etc.). Comme mentionné précédemment, la motivation principale derrière l'utilisation de l'OFDMA sur puce est sa capacité de reconfiguration, qui se réfère à la facilité de changer les utilisateurs de sous-porteuses, ou le nombre de porteuses par utilisateur, au cours du temps. Par conséquent, notre problème peut être formulé sous la forme de l'attribution des sous-porteuses au cours du temps (par exemple sur une durée de un ou plusieurs symboles OFDM) aux différentes files d'attente de transmission des tuilesets. Dans l'hypothèse où les files d'attente de réception en sortie de la ligne de transmission peuvent être vidées avec une rapidité élevée, en tout état de cause supérieure à celle d'arrivée des paquets, nous pouvons affirmer que l'allocation dynamique de sous-porteuses devrait diminuer les latences dans les files d'attente du côté de la transmission. Il est à noter que cette hypothèse est très légère, puisque cela signifie que les paquets reçus en sortie de la ligne de transmission peuvent être transmis dans le réseau intra-grille d'un tuileset à haute vitesse, ce qui est le cas car le réseau en quadrillage est un réseau parallèle sur 32 ou 64 bits fonctionnant habituellement à plusieurs centaines de mégahertz de fréquence d'horloge. Il peut donc drainer 64 bits toutes les nanosecondes à 1 GHZ d'horloge, soit bien plus que des données sur 64 bits (ou un multiple de 64 bits inférieur à 10) arrivant de la ligne de transmission toutes les 51.2 ns. Par conséquent, dans ce projet, nous cherchons des mécanismes d'arbitrage de l'allocation des sous-porteuses afin de minimiser le retard dans les files d'attente de transmission des tuilesest, en entrée de la ligne de transmission, et les probabilités de dépassement de capacité des mémoires tampons ou files d'attente de l'émetteur des tuilesets vers la ligne de transmission. Les détails de la spécification des protocoles proposés dans le cadre de cette thèse, tels que la structure détaillée des bits d'un paquet, etc., ne sont pas compris dans ce travail de thèse. Un processus générique de mécanisme d'allocation de la bande passante est prévu, qui peut être utilisé pour tout type d'architecture massivement multicoeurs, au-delà du cas de WiNoCoD.

# 4.2 Ordonnancement dynamique de la bande passante pour les files d'attente parallèles

La problème présenté précédemment est référencé dans la littérature comme "l'ordonnancement multi-utilisateur multi-serveur" ou "l'ordonnancement des files d'attente parallèles". La recherche sur les politiques d'ordonnancement multi-utilisateurs pour le cas multiserveurs intègre les domaines de la théorie des files d'attente, la théorie des réseaux, l'optimisation stochastique et les processus de décision markoviens. Considérant la nature de notre interconnexion OFDMA, nous allons étudier les algorithmes les plus efficaces en termes de politiques dynamiques d'ordonnancement. Ce type d'approches réassignent habituellement les serveurs aux files d'attente à chaque (ou chaque multiple) intervalle de temps, basé sur l'état instantané du système.

Pour le cas où il ya un seul serveur, qui doit être attribué à l'une des K files d'attente à chaque intervalle de temps (multi-utilisateur/serveur unique), il a été prouvé que la politique d'allocation prioritaire à la plus longue file d'attente (Longest Queue First: LQF) fournit la plus faible latence moyenne, sachant que les arrivées des paquets aux files d'attente sont indépendantes et identiquement distribuées. L'optimalité de cet algorithme pour le cas de plusieurs serveurs est toujours valable sous l'hypothèse d'arrivées indépendantes. L'inconvénient de cet algorithme est sa complexité de calcul. Il procède par itérations sur les N serveurs, et à chaque itération, le serveur effectue une itération pour toutes les files d'attente K. Après l'affectation, les longueurs des files d'attente sont mises à jour. Même si sa mise en œuvre dans WiNoCoD est impossible, en raison de la puissance de calcul requise excessive et, plus important en raison du fait que l'algorithme a besoin de connaître le temps d'attente instantanée de chaque paquet dans le système, nous utilisons cet algorithme comme référence pour comparer les performances de nos politiques d'allocation de bande passante.

#### 4.3 Allocation de la bande passante dans WiNoCoD

L'innovation de l'interconnexion RF de type OFDMA de WiNoCoD nécessite de développer de nouvelles techniques. La durée relativement longue des symboles OFDM à l'égard de temps d'arrivée des paquets dans les files d'attente d'émission des tuilesets, les longueurs des paquets et les exigences en termes de retard extrêmement strictes rendent cet environnement vraiment unique par rapport aux protocoles de communication existants, basés sur l'OFDMA. Par conséquent, dans cette section, nous introduisons certaines notions préliminaires liées à ce contexte particulier, et qui auront un impact sur l'allocation de la bande passante dans WiNoCoD.

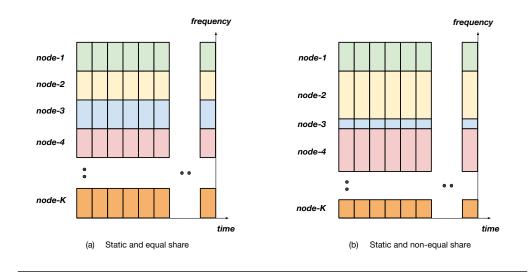

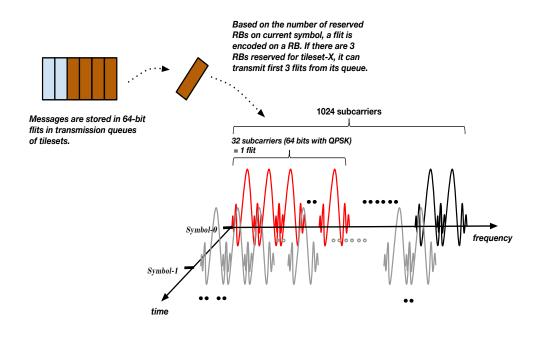

#### 4.3.1 Bloc de ressources et trames

La première notion que nous présentons est le bloc de ressources (Resource Block: RB), qui définit un groupe de sous-porteuses adjacentes sur un seul symbole. Considérant que nous avons 1024 sous-porteuses, il est évident qu'une granularité très fine pour allouer la bande passante avec une seule ou quelques sous-porteuses est coûteuse et inutile. Elle est notamment coûteuse en termes d'adressage et nécessitera l'échange de nombreux bits d'adresse pour informer les contrôleurs RF des tuilesets de leur allocation respective. Nous avons choisi de définir un RB pour servir exactement 1 paquet court (1 flit - 64 bits), en supposant que la modulation QPSK est utilisée par défaut. Un RB correspond donc à 32 sous-porteuses. Il est aussi à noter que comme le projet WiNoCoD prévoit l'utilisation de 1024 porteuses et 32 tuilesets, il y a en moyenne un RB de 32 porteuses disponible par tuileset. C'est une configuration qui pourra être utilisée par défaut, au lancement notamment, avec un RB d'émission pour chaque tuileset.

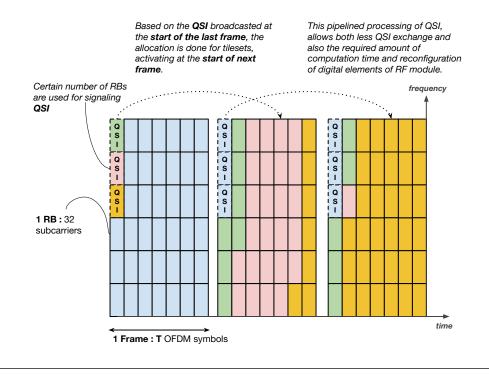

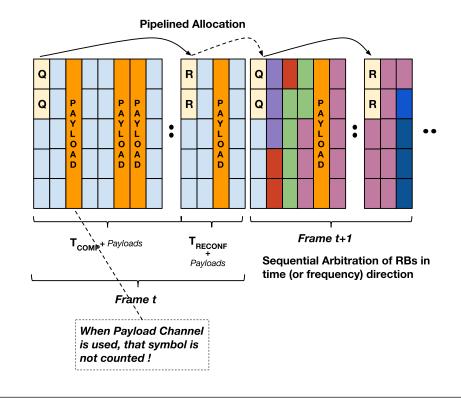

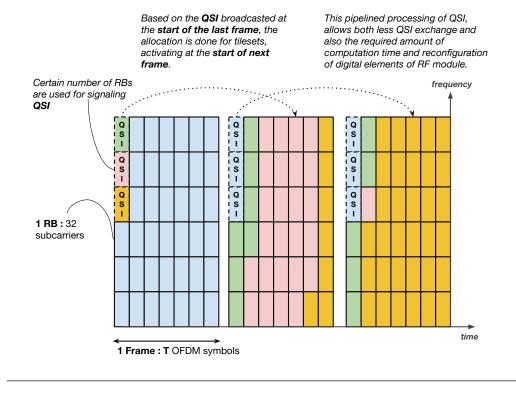

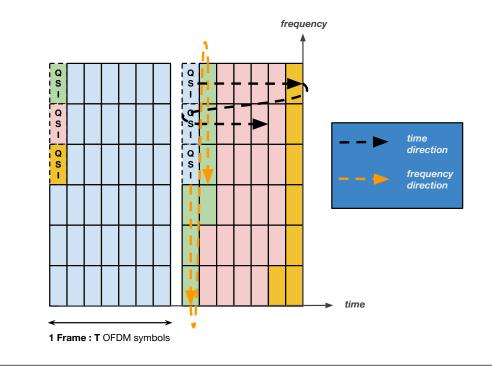

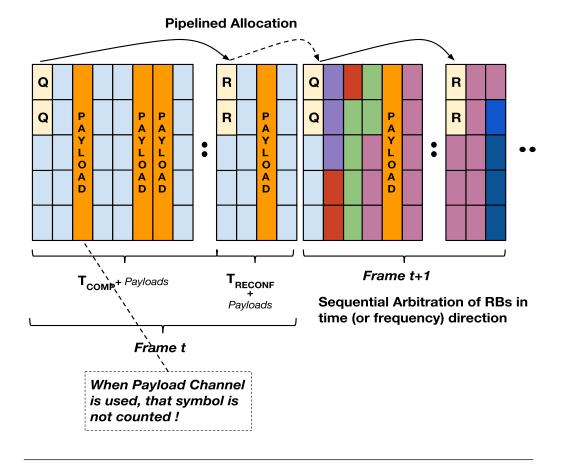

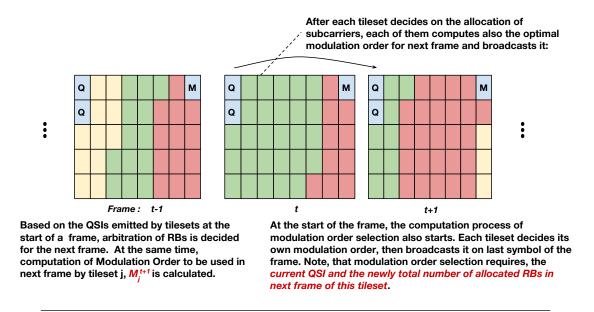

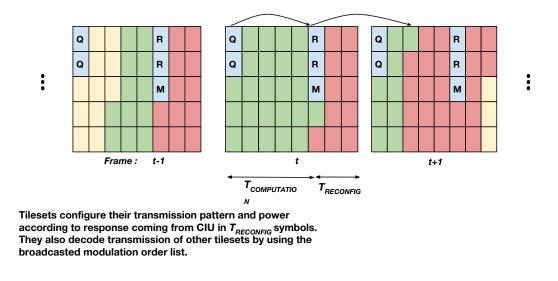

Le spectre de 20 GHz est donc divisé en RBs de 32 porteuses soit 625 MHz. Etudions maintenant les politiques de répartition des RB entre les tuilesets et le processus de reconfiguration associé. Comme nous l'avons examiné précédemment, les algorithmes efficaces d'allocation de bande passante nécessitent d'utiliser l'information de longueur des files d'attente (QSI). En outre, il est nécessaire que cette information soit récente, afin d'atteindre de faibles délais de livraison des paquets et de faibles tailles de files d'attente au niveau de l'émetteur d'accès à la ligne de transmission, géré par le contrôleur RF de chaque tuileset. Cependant, l'échange de l'information de QSI entre les tuileset à chaque symbole n'est pas réaliste en raison des besoins de signalisation excessive qu'il provoquerait d'une part. D'autre part, des paquets peuvent arriver à la file d'attente d'émission pendant la durée d'un symbole OFDM de 51,2 ns. L'information de QSI n'est donc par définition jamais complètement à jour quand elle est envoyée. Nous envisageons un système, où les QSIs (ou d'autres indicateurs de trafic local, en tenant compte d'autres algorithmes possibles) sont diffusés par les tuilesets tous les T symboles et la nouvelle répartition des sous-porteuses est effectuée tous les T symboles. Grâce à la capacité de diffusion de l'interconnexion OFDMA, les QSIs qui sont envoyés par chaque tuileset peuvent être reçus par tous les autres. Nous appelons «trame» ce groupe de T symboles. Ainsi, à la fin, nous avons un système d'allocation en mode pipeline, c'est-à-dire décalé d'une trame au moins. L'allocation est calculée au début d'une trame selon des informations de QSI envoyées T symboles avant par les autres tuilsets, comme le montre la Fig. 0.7.

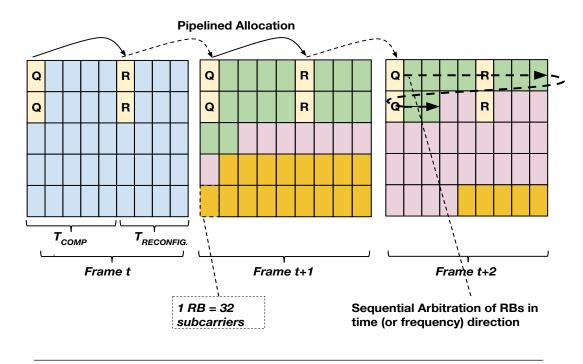

Dans le cas spécifique de WiNoCoD, où 1 symbole est d'environ 50 ns, le temps de calcul apparaît comme un paramètre important. Cette exigence temporelle stricte et peu orthodoxe fait de ce problème d'attribution, qui est examiné dans cette thèse, un travail original par rapport aux systèmes classiques. En effet, il n'est pas possible d'amortir sur une durée inférieure à celle d'un symbole, non seulement le temps des calculs d'un algorithme d'allocation, mais aussi le retard cumulé du temps de reconfiguration des sous-porteuses, du traitement des paquets, la synchronisation, le temps de propagation etc. D'où la nécessité de gérer le problème en trames de T symboles.

FIGURE 0.7: Les trames et blocs de ressources (RBs) dans WiNoCoD

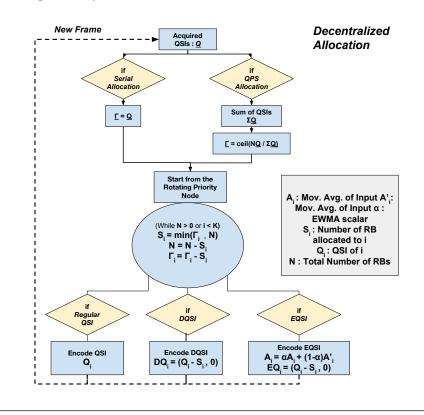

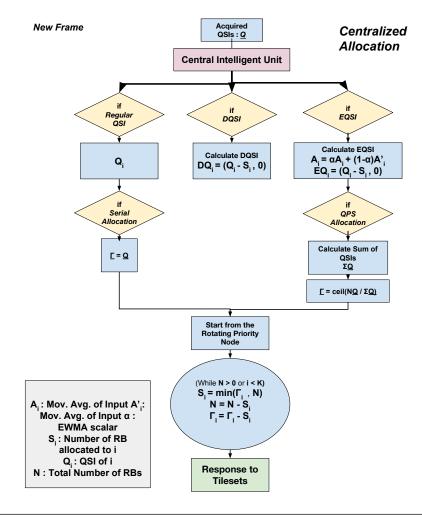

#### 4.3.2 Allocation décentralisée et centralisée

Les mécanismes d'arbitrage d'allocation des sous-porteuses que nous avons développé pour l'interconnexion WiNoCoD, peuvent être divisés en deux catégories : décentralisés et centralisés. Chacune des approches a des avantages et des inconvénients. Si une allocation centralisée est préférée, une seule unité centrale intelligente (Central Intelligent Unit: CIU), qui peut être soit un circuit numérique soit un microprocesseur simple, peut être installé à l'intérieur de la tête RF d'un tuileset (avant les modules IFFT/FFT). De cette façon, il peut utiliser les modulateur/démodulateur OFDM de ce tuileset. L'unité centrale intelligente doit diffuser sur la ligne guidée le nombre de RBs alloués à chaque tuileset. Ceci est une surcharge de signalisation supplémentaire évidente, ce qui n'est pas souhaitable afin d'épargner au maximum la bande passante sur la ligne guidée pour les échanges de données entre tuilesets.

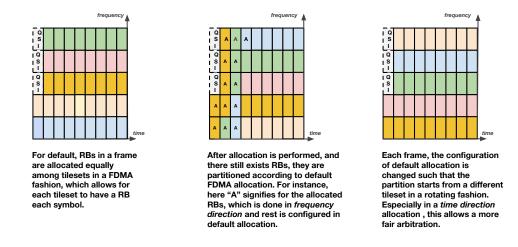

Un autre inconvénient est la robustesse. D'une part si le CIU connaît une panne, toute la puce est en panne. Mais l'approche proposée ici peut permettre de choisir n'importe quel tuileset pour héberger le CIU, ce qui atténue légèrement cet effet (l'étude de capacité du dernier chapitre tempèrera cette affirmation en révélant qu'il faut mieux que le CIU soit au centre la la ligne guidée). D'autre part, nous avons positionné la réponse du CIU sur des sous-porteuses réservées sur quelques symboles avant la fin de la trame. Nous nous réservons  $T_{configuration}$  symboles de temps pour que les processeurs de la tête RF des tuilesets puissent recevoir et démoduler le nombre de RBs alloués à chaque tuileset dans la trame suivante et reconfigurer leurs transmissions en conséquence. Nous proposons deux approches différentes pour l'attribution des RBs de chaque trame entre les tuilesets: l'allocation «en fréquence» ou «en temps».

Cependant, par moments, la somme des demandes de RB de tuilesets peut être beaucoup plus faible que le nombre total de RBs dans une trame. Dans ces cas là, il peut exister des RBs inutilisés. Considérant que des nouveaux paquets peuvent arriver dans les files d'attente d'émission des tuilesets pendant ces symboles inactifs, on répartit les RBs vides uniformément entre les tuilesets, ce qui permet à un tuileset d'utiliser un RB par symbole pour tout paquet qui arriverait pendant une trame. La nature numérique de la répartition des RBs en OFDMA rend ce processus trivial.

#### 4.3.3 Encodage et signalisation des QSIs

Un autre aspect important est l'encodage des QSIs des tuilesets au début d'une trame. En cas de constellation QPSK, nous avons 2048 bits disponibles dans chaque symbole OFDM. Sur la base de nos simulations, l'utilisation de 8 bits par tuileset et par trame pour coder les QSI s'est révélé offrir le meilleur compromis en termes de performance globale. Avec 8 bits, il est possible de coder 256 niveaux différents. Bien sûr, la file d'attente vide (0 QSI) doit aussi être codée. En regardant les résultats de simulation, nous avons vu que le nombre de flits dans une file d'attente de transmission dépasse très rarement 255 dans les scénarios évalués. Par conséquent, toutes les valeurs de longueur de QSI entre 0 et 255 sont directement codées, et si le nombre de flits est supérieur à 255, il est codé par 255. Bien sûr, on peut choisir différentes approches et granularité de codage des QSI. Chaque valeur de QSI pourrait aussi représenter plusieurs flits. Il y a un compromis évident entre une surcharge de signalisation de QSI et la précision de l'algorithme d'allocation. Cependant, à partir de nombreuses possibilités, et en prenant en compte des configurations d'interconnexion réalistes, nos simulations ont révélé que l'encodage sur 8-bits proposé semble viable et efficace.

Les contraintes très spécifiques des interconnexions sur puce en OFDMA imposent de respecter certaines exigences. Compte tenu de la durée relativement longue des symboles par rapport aux exigences de retard sur les paquets, même une latence de quelques symboles est importante, contrairement aux cas classiques d'utilisation de l'OFDM. Dans ce contexte particulier, la dynamique de la file d'attente peut changer radicalement en quelques symboles. Comme expliqué ci-dessus, en raison des contraintes de temps de calcul et de surcharge de signalisation, la répartition est effectuée en «pipeline» entre trames. En d'autres termes, la répartition se fait avec sur des QSI ayant T symboles de retard. Compte tenu du trafic temporellement très hétérogène, nous introduisons la notion de "QSI Définitif" (Definitive QSI - DQSI). Au début de chaque trame, avant de coder son QSI sur les sous-porteuses réservées, chaque tuileset connaît déjà le nombre de RBs attribué dans la trame actuelle. Par conséquent, plutôt que de coder directement le QSI, il soustrait le nombre de RBs déjà alloué de son QSI courant. Une fois que le nombre minimum de flits dans la file d'attente est déterminé, nous pouvons également prendre en compte le nombre de flits qui arriveront au cours du processus d'allocation (sur la durée de la trame actuelle). Pour ce faire, les tuilesets doivent estimer le nombre de flits qui arriveront pendant une trame. Cela peut se faire en utilisant un filtre à moyenne mobile. Nous appelons ce modèle comme "QSI prédit" (Expected Queue State Information - EQSI).

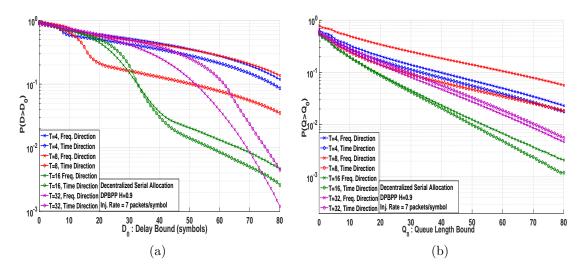

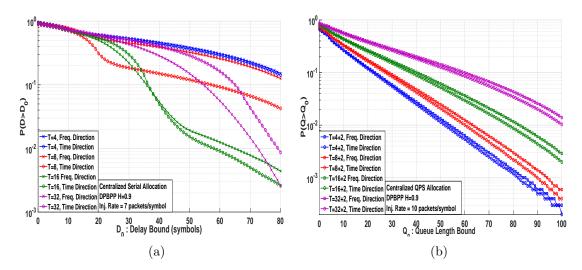

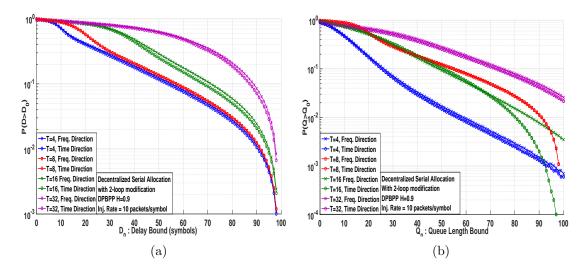

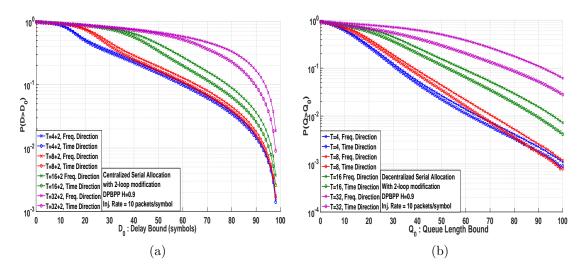

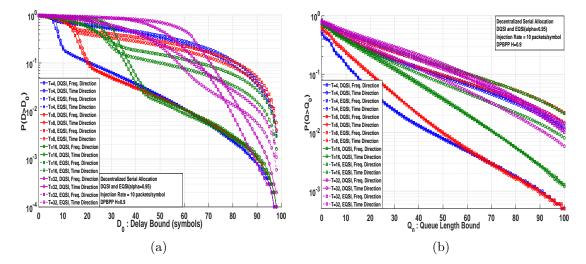

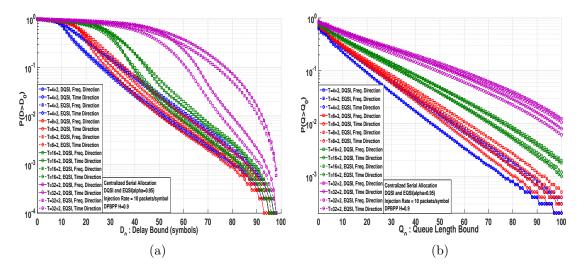

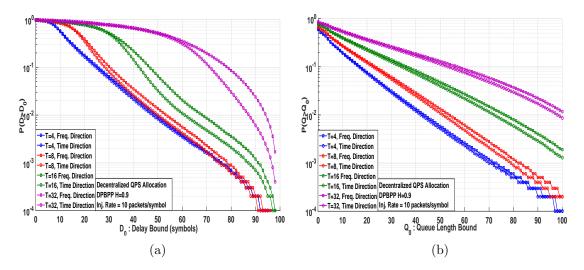

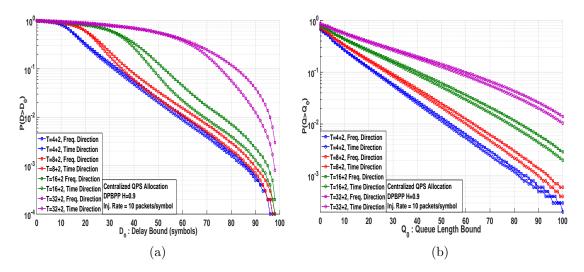

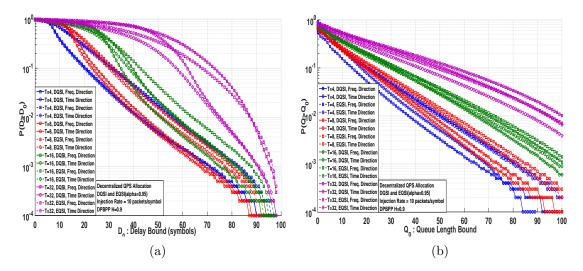

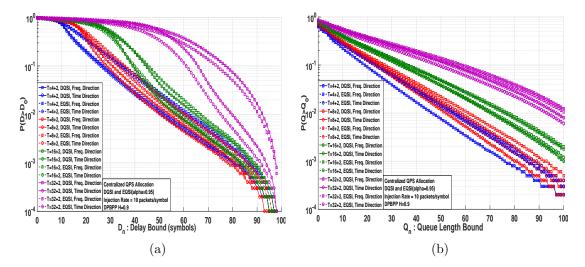

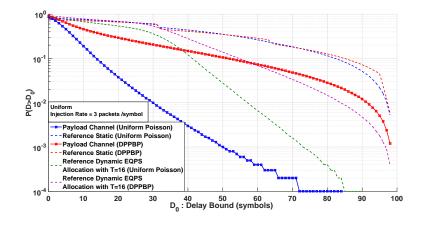

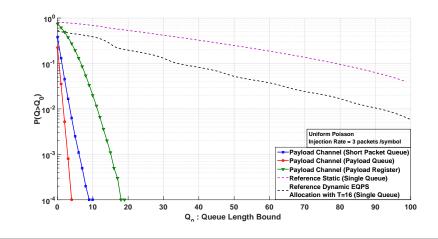

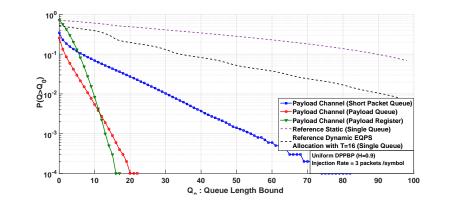

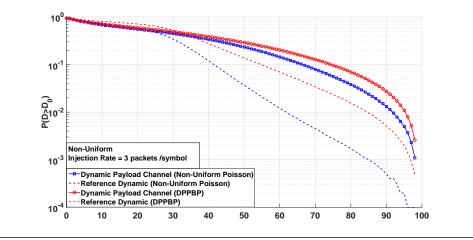

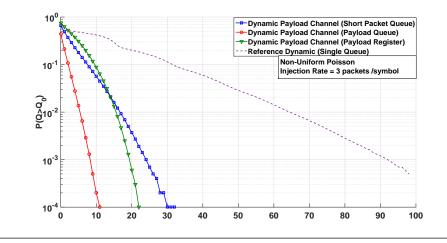

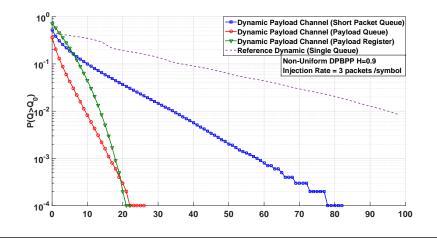

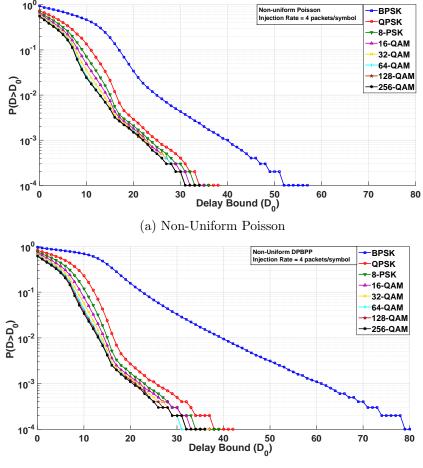

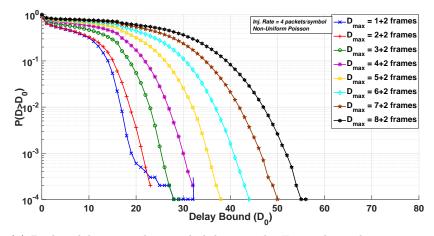

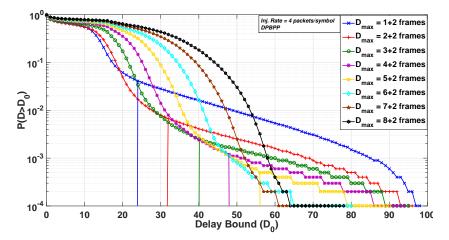

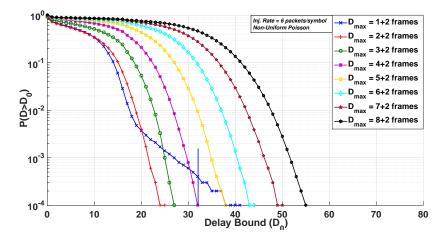

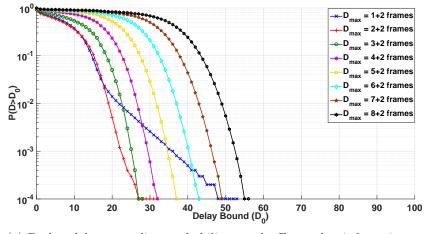

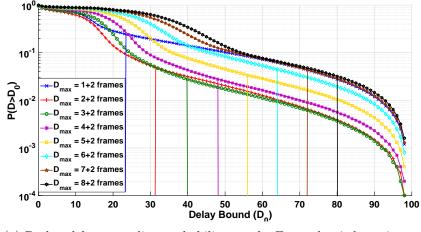

Avant de présenter nos algorithmes, il est essentiel d'introduire les techniques et les scénarios que nous allons utiliser pour les évaluer. Nous utilisons OMNeT++, un simulateur d'événements discrets qui est utilisé largement auprès la communauté réseau sur puce. OMNeT++ est utilisé pour émuler la dynamique des files d'attente de transmission des 32 tuilesets. Les simulations sont exécutées avec un pas temporel égal à celui d'un symbole OFDM, qui est donc l'unité atomique temporelle. L'objectif est l'amélioration des performances de l'interconnexion RF en termes de latence de délivrance des paquets présents dans les files d'attente d'émission des tuilest. la première métrique d'intérêt que nous essayons d'améliorer est la latence moyenne. La latence moyenne d'un réseau sur puce, pour différents modèles de trafic et des charges de trafic différentes, est la mesure la plus significative de sa performance. L'importance du retard des paquets dans un NoC est particulièrement sensible pour les applications temps réel. Par conséquent, notre interconnexion RF est testée en premier pour cette métrique. En outre, pour chaque simulation; nous traçons la courbe de la probabilité de dépassement de limite de latence, qui indique la probabilité qu'un paquet dépasse une limite de latence spécifiée,  $D_0 : P(D > D_0)$ . La troisième métrique d'intérêt, est la courbe de probabilité de dépassement de la limite de longueur de queue :  $P(L > L_0)$ .

Cependant, pour tester les performances du NoC, les benchmarks de référence actuels en termes de génération de trafic sur la ligne guidée sont loin de représenter la charge générée par les futurs algorithmes qui seront embarqués sur des architectures de plusiuers milliers de cœurs de traitement. Par conséquent, pour évaluer la validité de notre interconnexion OFDMA et des algorithmes d'arbitrage des ressources fréquentielles proposés, nous avons choisi d'utiliser des modèles de trafic stochastiques et synthétiques.

## Chapitre 5 : Algorithmes d'Allocation de bande passante de WiNoCoD

#### 5.1 Allocation Série avec QSI Directe

Le première algorithme que nous proposons est relativement simple à mettre en œuvre. Après que les valeurs des QSIs soient diffusées dans la ligne guidée, puis acquises par chaque tuileset, le contrôleur RF de ces derniers alloue simplement les RBs en série dans la prochaine trame (matrice de RBs), en itérant sur les valeurs de QSI issues de chaque tuilesets (puisque chaque tuileset peut décoder toutes les valeurs émises par tous les autres tuilesets). L'algorithme se termine lorsqu'il n'y a plus de RBs vides ou si toutes les demandes des tuilesets sont servies. Pour le cas où le QSI total de tous les tuilesets est inférieur au nombre total de RBs dans la trame, les RBs restants sont partagés entre les tuilesets en utilisant la matrice d'allocation par défaut. On peut se demander si l'allocation des RBs peut également être faite unité par unité, en itérant sur chaque tuilesets pour chaque RB à allouer ou avec une approche complètement différente. Cependant, limiter le nombre d'itérations est essentiel. Considérant que le budget temporel est de quelques centaines de cycles de processeur pour le calcul de l'arbitrage de la bande passante entre les tuilesets, itérer sur 32 tuilesets n'est réalisable qu'une seule fois. Comme l'algorithme d'allocation de QSI en série est de faible complexité (de calcul), on peut le dupliquer dans chaque tuileset pour un surcoût négligeable et on s'affranchit des problèmes déjà évoqués, inhérents à l'utilisation d'une unité centralisée. Cependant, nous effectuons la même expérimentation que pour le cas décentralisé, pour des raisons de cohérence. Tout au long de cette thèse, quand nous comparons l'approche centralisée à l'approche décentralisée, nous utilisons toujours un temps de reconfiguration  $T_{configuration} = 2$  symboles. Par exemple, lorsque l'on compare une longueur de trame décentralisée de 4 symboles (principalement en raison du temps de calcul), nous utilisons une longueur de trame de 6 symboles pour l'approche centralisée. Rappelons que, dans l'approche centralisée, nous avons des RBs réservés pour la transmission des paquets de réponse.

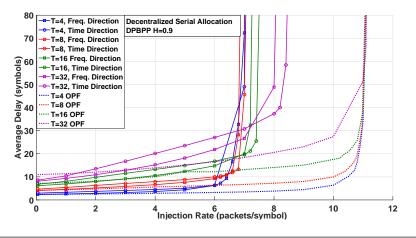

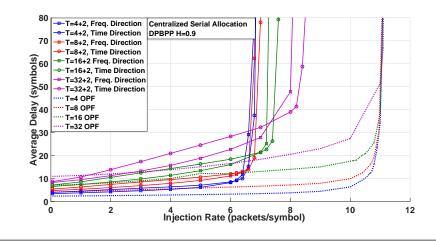

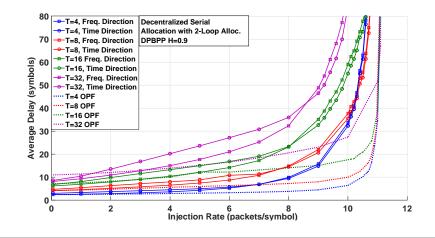

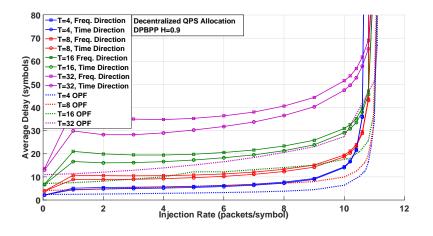

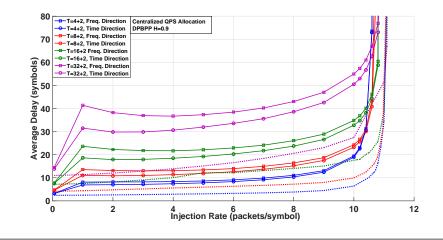

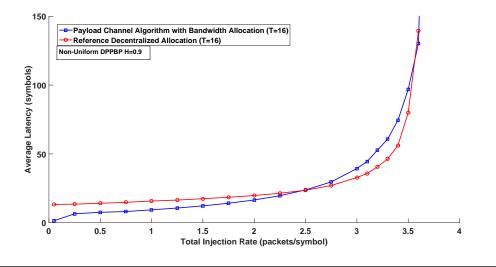

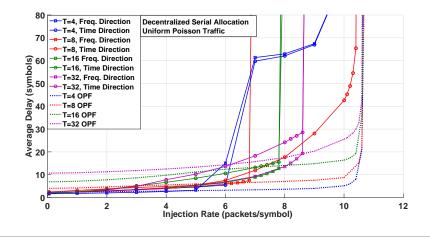

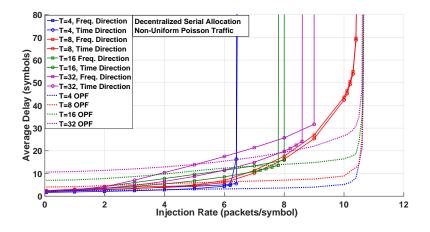

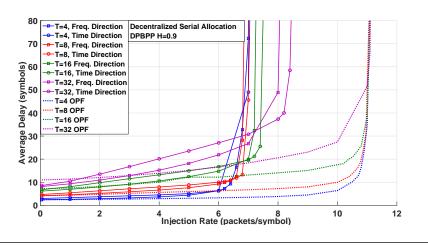

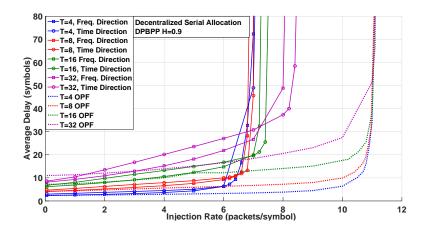

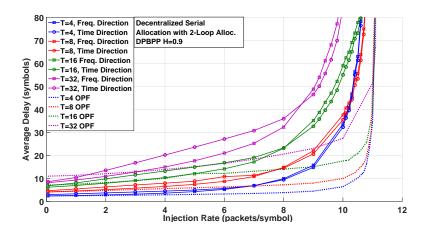

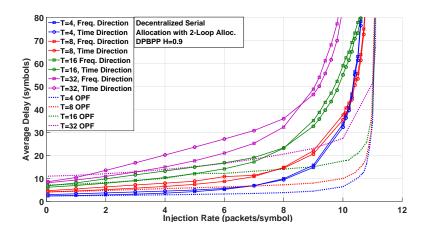

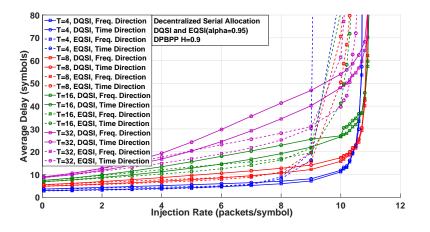

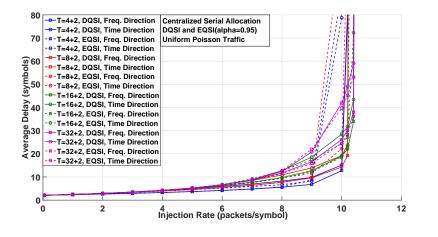

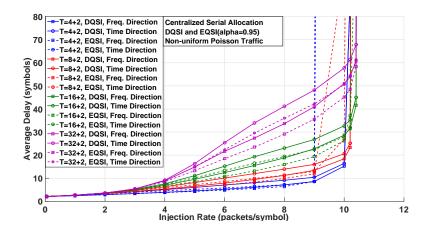

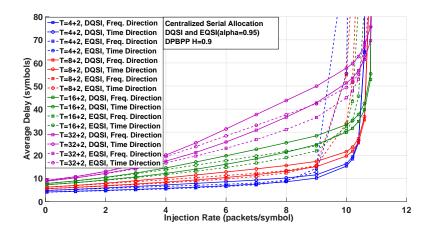

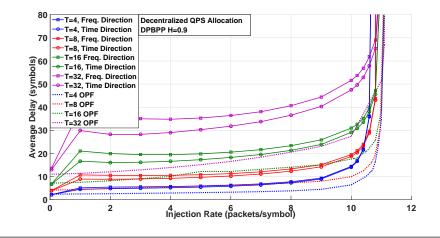

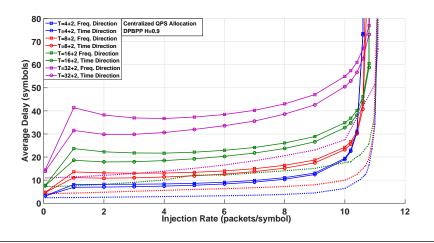

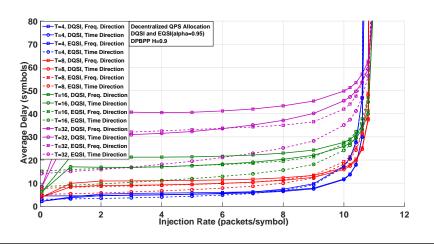

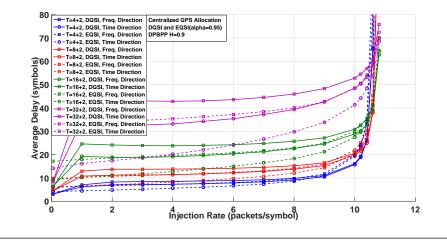

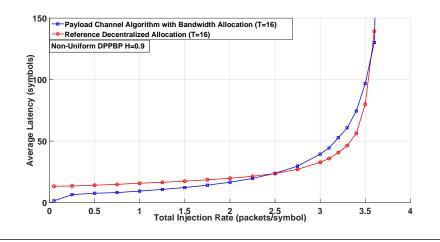

Par exemple, les Fig. 0.8 et Fig. 0.9 montrent les variations de la latence moyenne en fonction du taux d'injection dans le cas d'un trafic réaliste non-uniforme (DPBPP) pour l'allocation série, avec l'approche centralisée et décentralisée, pour différentes longueurs de trame.

FIGURE 0.8: Latence moyenne en fonction de l'augmentation du taux d'injection pour un trafic réaliste non-uniforme (DPBPP) pour l'allocation serie avec l'approche décentralisée pour différentes longueurs de trame.

#### 5.1.1 Allocation Série à Deux Itérations

L'algorithme serie ne permet pas d'approcher de près les performances idéales en termes de capacité du réseau. Une allocation de bande passante très fréquente, donc avec des longueurs de trames très courtes, provoque une augmentation significative de la latence moyenne. Nous avons observé que cet effet contradictoire est dû au faible nombre de RBs à allouer pour des longueurs de trames courtes. En utilisant la même priorité pour tous les tuilesets, certains vont prendre les RBs, et vont priver de ressources d'autres tuilesets qui en auraient besoin. Afin de résoudre ce problème d'équité, et d'augmenter

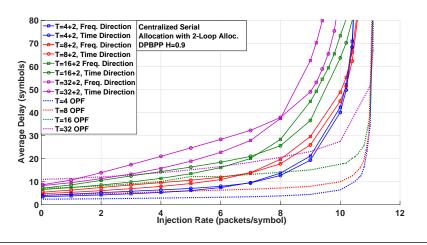

FIGURE 0.9: Latence moyenne en fonction de l'augmentation du taux d'injection sous le trafic réaliste non-uniforme (DPBPP) pour l'allocation serie avec l'approche centralisée pour différentes longueurs de trame.

l'équité entre les files d'attente de transmission des tuilesets, nous avons établi une modification de l'algorithme série. Cette fois, la répartition des RBs est effectuée en 2 étapes, comme le nom de l'algorithme l'indique. Tout d'abord après avoir reçu les QSIs de chaque tuileset, les contrôleurs RF des tuilesets les additionnent et divisent le résultat obtenu par le nombre de tuilesets afin d'obtenir le "QSI moyen" de la trame courante. A la première étape de l'algorithme, une itération sur les 32 tuilesets est effectuée comme dans l'allocation série précédente. Toutefois, lors de cette première itération, seulement les tuilesets qui ont un QSI plus grand que le "QSI moyen" courant peuvent prendre des RBs. Après cette première itération, les valeurs de QSI sont mises à jour en soustrayant le nombre de RBs déjà alloués à cette itération. À la deuxième étape, la même itération est effectuée sur les valeurs mises à jour de QSI des tuilesets, mais cette fois avec l'algorithme d'allocation série par défaut. De cette manière, nous nous assurons que les tuilesets qui ont vraiment besoin de RB vont obtenir leur part. Cette extension de l'algorithme d'allocation de QSI série directe peut être considérée comme une tentative pour compenser les déséquilibres dans les files d'attente.

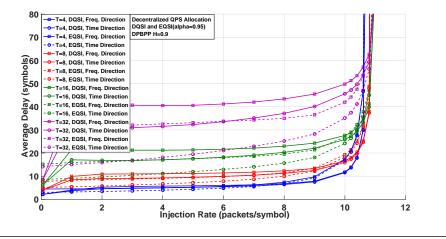

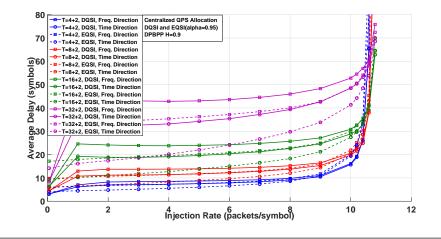

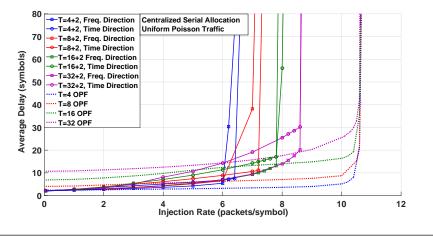

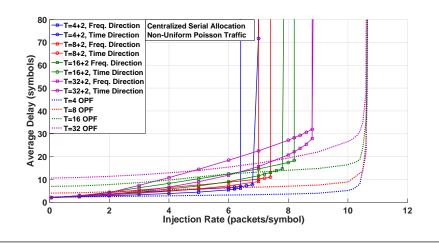

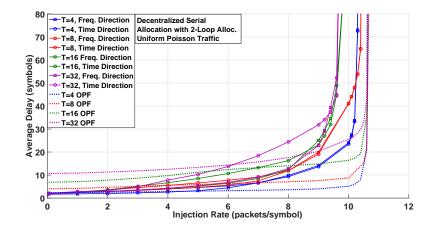

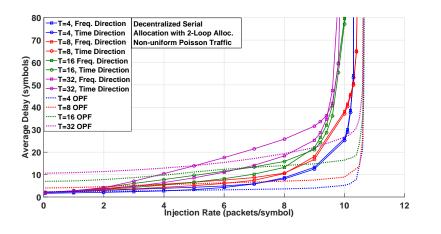

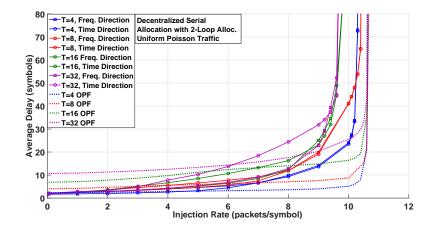

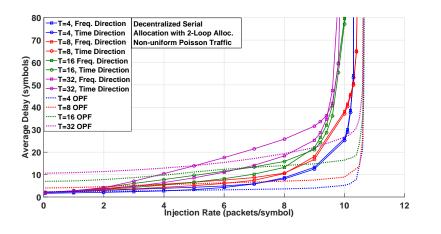

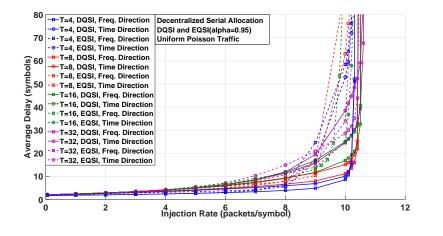

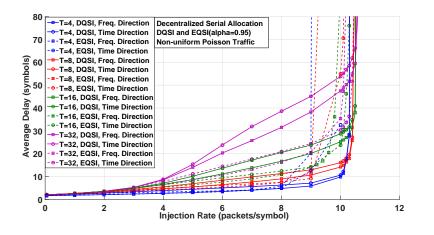

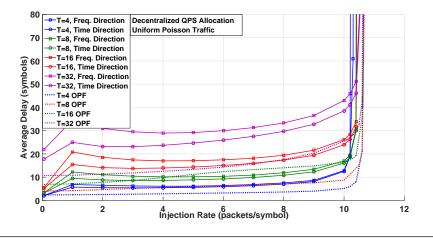

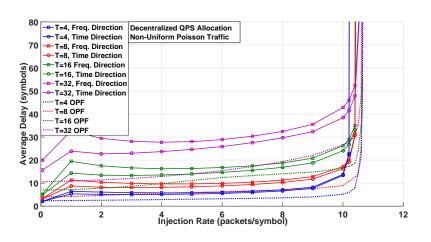

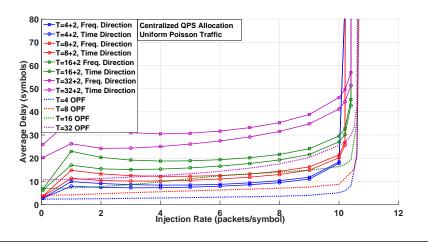

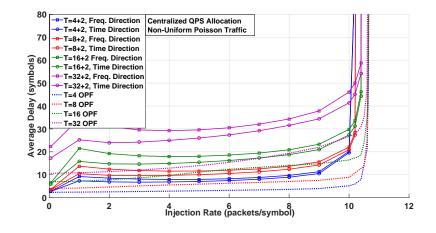

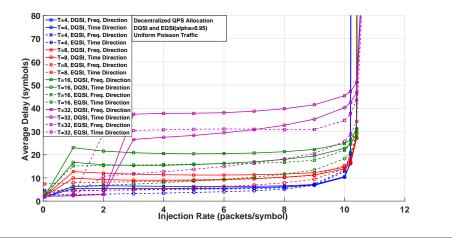

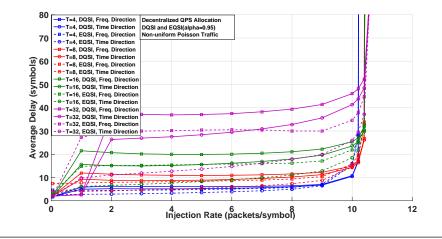

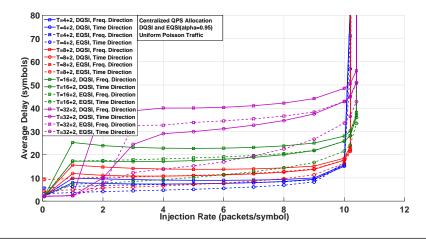

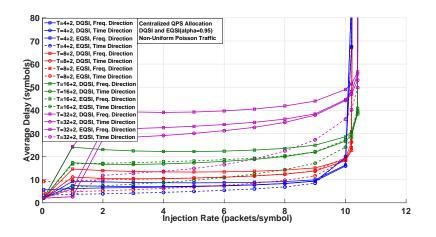

Les Fig. 0.10 et Fig. 0.11 montrent la variation de la latence moyenne en fonction du taux d'injection sous le trafic réaliste non-uniforme (DPBPP) pour l'allocation série avec deux itérations, dans le cas de l'approche centralisée et décentralisée, pour différentes longueurs de trame.

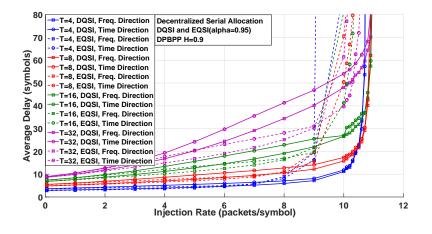

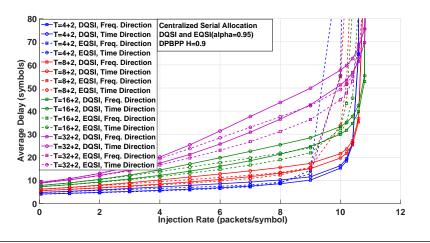

#### 5.1.2 Allocation Série avec DQSI et EQSI

Nous avons vu qu'il était possible d'augmenter la capacité du réseau en utilisant une modification de l'algorithme série, en le passant à deux iterations. Dans l'approche décentralisée, chaque tuileset calcule sa propre valeur de DQSI ou EQSI en utilisant le

FIGURE 0.10: Latence moyenne en fonction de l'augmentation du taux d'injection pour un trafic réaliste non-uniforme (DPBPP) pour l'allocation serie (2 iterations) avec l'approche décentralisée pour différentes longueurs de trame.

FIGURE 0.11: Latence moyenne en fonction de l'augmentation du taux d'injection pour un trafic réaliste non-uniforme (DPBPP) pour l'allocation serie (2 iterations) avec l'approche centralisée pour différentes longueurs de trame.