# Programmable Low Overhead, Run Length Limited and DC-Balanced Line Coding for High-Speed Serial Data Transmission

Julien Saade

#### ► To cite this version:

Julien Saade. Programmable Low Overhead, Run Length Limited and DC-Balanced Line Coding for High-Speed Serial Data Transmission. Networking and Internet Architecture [cs.NI]. Université Grenoble Alpes, 2015. English. NNT: 2015GREAM079. tel-01679262

## HAL Id: tel-01679262 https://theses.hal.science/tel-01679262

Submitted on 9 Jan 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ GRENOBLE ALPES

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

#### Spécialité : Mathématiques et informatique

Arrêté ministériel : 7 août 2006

Présentée par

### Julien Saadé

Thèse dirigée par M. Frédéric Pétrot

préparée au sein du Laboratoire TIMA, CNRS/Grenoble INP/UJF (CIFRE STMicroelectronics) dans l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique (MSTII)

# Encodage de donnée programmable et à faible surcoût, limité en disparité et en nombre de bits identiques consécutifs

Thèse soutenue publiquement le « **3 juin 2015** », devant le jury composé de :

M. Bernard TOURANCHEAU

Professeur université Grenoble Alpes (Président)

M. Michel PAINDAVOINE

Professeur université de Bourgogne (Rapporteur)

M. Olivier SENTIEYS

Professeur université Rennes 1 (Rapporteur)

M. Thierry DIVEL

Ingénieur Fogale Sensation Suisse (Membre)

M. Joel HULOUX

Ingénieur STMicroelecronics Grenoble (Membre)

M. Frédéric PETROT

Professeur Institut Polytechnique Grenoble (Membre)

# Programmable Low Overhead, Run Length Limited and DC-Balanced Line Coding for High-Speed Serial Data Transmission

By

Julien Saadé

# Supervised by Prof. Frédéric Pétrot

In collaboration with

TIMA Laboratory, Université Grenoble-Alpes

and

**STMicroelectronics**

A thesis submitted for the degree of Docteur de l'université Grenoble Alpes

May 2015

#### Abstract

Thanks to their routing simplicity, noise, EMI (Electro-Magnetic Interferences), area and power consumption reduction advantages over parallel links, High Speed Serial Links (HSSLs) are found in almost all today's Systemon-Chip (SoC) connecting different components: the main chip to its Inputs/Outputs (I/Os), the main chip to a companion chip, Inter-Processor Communication (IPC) and etc... Serial memory might even be the successor of current DDR memories.

However, going from parallel links to high-speed serial links presents many challenges; HSSLs must run at higher speeds reaching many gigabits per second to maintain the same end-to-end throughput as parallel links as well as satisfying the exponential increase in the demand for throughput. The signal's attenuation over copper increases with the frequency, requiring more equalizers and filtering techniques, thereby increasing the design complexity and the power consumption.

One way to optimize the design at high speeds is to embed the clock within the data, because a clock line means more routing surface, and it also can be source to high EMI. Another good reason to use an embedded clock is that the skew (time mismatch between the clock and the data lanes) becomes hard to control at high frequencies. Transitions must then be ensured inside the data that is sent on the line, for the receiver to be able to synchronize and recover the data correctly. In other words, the number of Consecutive Identical Bits (CIBs) also called the Run Length (RL) must be reduced or bounded to a certain limit.

Another challenge and characteristic that must be bounded or reduced in the data to send on a HSSL is the difference between the number of '0' bits and '1' bits. It is called the Running Disparity (RD). Big differences between 1's and

0's could shift the signal from the reference line. This phenomenon is known as Base-Line Wander (BLW) that could increase the BER (Bit Error Rate) and require filtering or equalizing techniques to be corrected at the receiver, increasing its complexity and power consumption.

In order to ensure a bounded Run Length and Running Disparity, the data to be transmitted is generally encoded. The encoding procedure is also called line coding. Over time, many encoding methods were presented and used in the standards; some present very good characteristics but at the cost of high additional bits, also called bandwidth overhead, others have low or no overhead but do not ensure the same RL and RD bounds, thus requiring more analog design complexity and increasing the power consumption.

In this thesis, we propose a novel programmable line coding that can perform to the desired RL and RD bounds with a very low overhead, down to 10 times lower that the existing used encodings and for the same bounds. First, we show how we can obtain a very low overhead RL limited line coding, and second we propose a very low overhead method which bounds the RD, and then we show how we can combine both techniques in order to build a low overhead, Run Length Limited, and Running Disparity bounded Line Coding. Dedication

To my Mother and Father

For everything.

# Acknowledgments

I would like to warmly thank my four thesis supervisors, in scrambled order, André Picco, head of the High-Speed Links team at STMicroelectronics, and Frédéric Pétrot, SLS team leader at TIMA laboratory, for welcoming me, directing my thesis and always giving me advices that helped me stay on the right path. I thank Joel Huloux, MIPI Alliance's chairman, for taking the time to advise me and giving me the opportunity to participate to MIPI's PHY and LLI Working Groups, assist and contribute to discussions with experts from the leading semiconductor companies all over the world, from whom I've learned and gained a lot of experience. I want to thank Abdelaziz Goulahsen, MIPI's LLI Working Group chairman, for all his help and expertise, the many technical meetings we had and all the things I learned from him. I consider myself lucky being supervised by such experienced people.

I also must thank Erwan Le-Saint for offering me this opportunity and welcoming me in his team.

I thank my thesis committee members, Bernard Tourancheau, Olivier Sentieys, Michel Paindavoine and Thierry Divel for accepting to review and comment my thesis.

Many thanks to Steve Kwiatkowski, Jérôme Deroo, Mohamed Daoudi, Klodjan Bidaj and Gilles Ries, experts and engineers at STMicroelectronics, for the many fruitful technical discussions we had and the help they have provided me.

Last but not least, I thank my parents and my brothers for all the love and support they have provided me throughout my thesis, and my entire life. This thesis, for all its worth, is dedicated to them.

#### **TABLE OF CONTENTS**

| Contributions                        |                                                            |     |

|--------------------------------------|------------------------------------------------------------|-----|

| List of Acronyms, Figures and Tables |                                                            |     |

| <u>1.</u> IN                         | TRODUCTION                                                 | 1   |

| <b>2</b> . <b>PR</b>                 | OBLEM STATEMENT                                            | 7   |

| 2.1                                  | CHAPTER'S INTRODUCTION                                     | 7   |

| 2.2                                  | HIGH SPEED SERIAL LINKS                                    | 9   |

| 2.3                                  | LINE CODING'S EFFECT ON DATA TRANSMISSION                  | 14  |

| 2.4                                  | CHAPTER'S CONCLUSION                                       | 21  |

| 3. ST                                | ATE OF THE ART                                             | 25  |

| 3.1                                  | CHAPTER'S INTRODUCTION                                     | 25  |

| 3.2                                  | SYSTEM-LEVEL COMPARISON OF THREE HSSLS: LLI, PCIE AND USB  | 26  |

| 3.3                                  | LINE CODING'S STATE OF THE ART                             | 33  |

| 3.4                                  | STATE OF THE ART'S CONCLUSION                              | 44  |

| 4. LC                                | <b>DW EMI ENCODING METHOD</b>                              | 47  |

| 4.1                                  | CHAPTER'S INTRODUCTION                                     |     |

| 4.2                                  | PROBABILITY OF A REPETITIVE PATTERN                        | 47  |

| 4.3                                  | METHOD TO ELIMINATE THE PROBABILITY OF REPETITIVE PATTERNS | 49  |

| 4.4                                  | CHAPTER'S CONCLUSION                                       |     |

| 5. LC                                | W OVERHEAD RUN LENGTH LIMITED ENCODING METHO               | D57 |

|                                      | CHAPTER'S INTRODUCTION                                     |     |

| 5.2                                  | BIT STUFFING OVERHEAD VS. DATA'S DISTRIBUTION              | 58  |

| 5.3                                  | PROPOSAL FOR A LOW OVERHEAD RUN LENGTH LIMITED ENCODING    | 61  |

| 5.4                                  | CHAPTER'S CONCLUSION                                       |     |

| 6. LC                                | OW OVERHEAD DC-BALANCED ENCODING METHOD                    | 69  |

| 6.1                                  | CHAPTER'S INTRODUCTION                                     |     |

| 6.2                                  | A NOVEL DC-BALANCED LINE CODING                            |     |

| 6.3                                  | OVERHEAD ESTIMATION                                        |     |

| 6.4                                  | CHAPTER'S CONCLUSION                                       | 78  |

| 7. DC                                | C-BALANCED AND RUN LENGTH LIMITED LINE CODING              | 81  |

| 7.1                                  | CHAPTER'S INTRODUCTION                                     |     |

| 7.2                                  | MERGING POSSIBILITIES                                      |     |

| 7.3                                  | PROPOSAL FOR A DC-BALANCED AND RL LIMITED ENCODING         |     |

| 7.4                                  |                                                            |     |

| 8. EX                                | XPERIMENTAL RESULTS                                        | 89  |

|                                      | CHAPTER'S INTRODUCTION                                     |     |

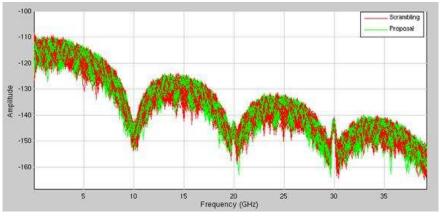

| 8.2                                  | DOUBLE SCRAMBLING (METHOD 1) PSD SIMULATION                |     |

| 8.3                                  | MORE OVERHEAD SIMULATION RESULTS                           |     |

| 8.4                                  | VHDL MODEL AND GATE-COUNT ESTIMATION                       |     |

| 8.5                                  | EYE DIAGRAMS RESULTS AND COMPARISON                        |     |

| 8.6                                  | CHAPTER'S CONCLUSION                                       |     |

|                                      | ONCLUSION                                                  |     |

|                                      | Bibliography                                               |     |

|                                      | [es                                                        |     |

| 1 11110/                             |                                                            | /   |

#### Contributions

#### **Patents:**

**"Serial Transmission Having a low level EMI", 2013** Inventors: **J. Saadé**, A. Goulahsen

**"Polarity-Bit data Encoding Method using Aperiodic Frames"**, 2014 Inventors: **J. Saadé**, A. Goulahsen

#### **Conference papers and oral presentations:**

"A System-Level Overview and Comparison of Three High-Speed Serial Links: USB 3.0, PCI Express 2.0 and LLI 1.0", IEEE 16th Symposium on Design and Diagnostic of Electronic Circuits and Systems (DDECS 2013) – Karlovy Vary, Czech Republic Authors: J. Saadé, F. Pétrot, A. Picco, J. Huloux, A. Goulahsen

**"A Scalable Low Overhead Line Coding for Asynchronous High Speed Serial Transmission"**, IEEE 18th Workshop on Signal and Power Integrity (SPI 2014) – Gent, Belgium Authors: **J. Saadé**, A. Goulahsen, A. Picco, J. Huloux, F. Pétrot

**"Low Overhead, DC-Balanced and Run Length Limited Line Coding",** IEEE 19th Workshop on Signal and Power Integrity (SPI 2015) – Berlin, Germany Authors: **J. Saadé**, A. Goulahsen, A. Picco, J. Huloux, F. Pétrot

#### **Other Participations:**

"Latest Version of Interface Protocol Speeds Mobile Device Development, Lowers e-BoM. MIPI Alliance's Low Latency Interface Working Group Delivers LLI v2.1" Published in Design & Reuse Magazine Authors: A. Goulahsen (STMicroelectronics) and V. Leonov (Intel) Thanked contributors: B. Balakrishnan (Ericsson), U. Leucht-Roth (Intel) and J. Saadé (STMicroelectronics)

# List of acronyms

| HSSL  | High Speed Serial Link              |

|-------|-------------------------------------|

| SoC   | System on Chip                      |

| I/O   | Input/Output                        |

| IPC   | Inter Processor Communication       |

| DDR   | Double Data Rate SDRAM              |

| EMI   | Electro-Magnetic Interferences      |

| CIB   | Consecutive Identical Bits          |

| RL    | Run Length                          |

| RD    | Running Disparity                   |

| BLW   | Base-Line Wander                    |

| BER   | Bit Error Rate                      |

| AP    | Application Processor               |

| RFIC  | Radio Frequency Integrated Circuit  |

| NRZ   | Non-Return to Zero                  |

| Mbps  | Megabits per second                 |

| Gbps  | Gigabits per second                 |

| MLT-3 | Multi-Level 3                       |

| PAM   | Pulse Amplitude Modulation          |

| MIPI  | Mobile Industry Processor Interface |

| LLI   | Low Latency Interface               |

| Unified Protocol                          |

|-------------------------------------------|

| Digital RF                                |

| Radio Frequency                           |

| Universal Flash Storage                   |

| Camera Serial Interface                   |

| Display Serial Interface                  |

| Peripheral Component Interconnect express |

| Mobile-PCIe                               |

| SuperSpeed Inter-Chip                     |

| International Standards Organization      |

| Open Systems Interconnection              |

| Physical Layer                            |

| Phase Locked Loop                         |

| Transmitter                               |

| Receiver                                  |

| Differential positive                     |

| Differential Negative                     |

| Clock and Data Recovery                   |

| Cyclic Redundancy Check                   |

| electronic Bill of Materials              |

| Linear Feedback Shift Register            |

| Pseudo-Random Binary Sequence             |

|                                           |

# **List of Figures**

# Chapter 2 :

| Figure 2.1  | Some High Speed Serial Links speed evolution                       |

|-------------|--------------------------------------------------------------------|

| Figure 2.2  | HSSLs different domains of application9                            |

| Figure 2.3  | MIPI® System Diagram for mobile devices [3]10                      |

| Figure 2.4  | Open Systems Interconnection (OSI) Layers11                        |

| Figure 2.5  | Simplified block diagram of HSSLs Physical Layer13                 |

| Figure 2.6  | Eye diagram example14                                              |

| Figure 2.7  | Common mode voltage representation (voltage mismatch = $5\%$ ,     |

| time misma  | tch = 5%)                                                          |

| Figure 2.8  | Power Spectral Density example of the Vcm of raw picture data at   |

| 1.4 GHz     |                                                                    |

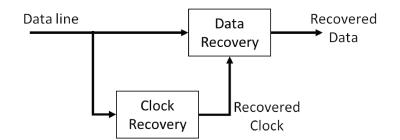

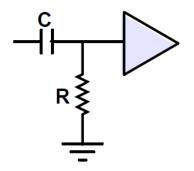

| Figure 2. 9 | Clock and Data Recovery simplified schematic16                     |

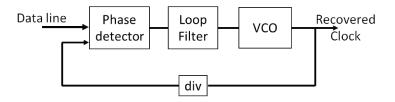

| Figure 2.10 | PLL-based Clock Recovery simplified schematic                      |

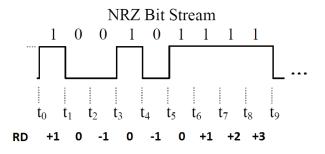

| Figure 2.11 | Running disparity calculation example for NRZ signaling18          |

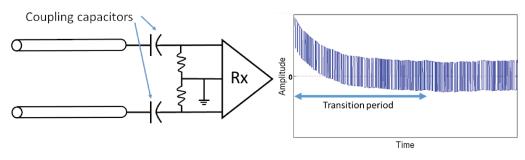

| Figure 2.12 | AC-coupling and transition period18                                |

| Figure 2.13 | Simplified AC-coupling                                             |

| Figure 2.14 | Baseline Wander and jitter introduced by the high pass filter [17] |

|             |                                                                    |

# Chapter 3:

| Figure 3.1   | Example of an LLI environment (not exhaustive)               | 27  |

|--------------|--------------------------------------------------------------|-----|

| Figure 3.2   | Example of PCIe link environment                             | 28  |

| Figure 3.3   | USB Structure                                                | 29  |

| Figure 3.4   | USB, PCIe and LLI Layering model comparison                  | 30  |

| Figure 3.5   | Throughput efficiency comparison for USB, PCIe and LLI for   | a   |

| write transa | ction and before line coding                                 | 31  |

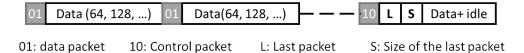

| Figure 3.6   | Bit Stuffing Example for Run length limitation of 5          | 34  |

| Figure 3. 7  | Simplified representation of scrambling                      | 36  |

| Figure 3.8   | LFSR Galois representation of the polynomial: $X16 + X5 + X$ | 4+  |

| X3 + 1       |                                                              | 36  |

| Figure 3.9   | RD representation of the PRBS generated by the polynomial:   | X16 |

| + X5 + X4 -  | + X3 + 1, seed value FFFFh                                   | 37  |

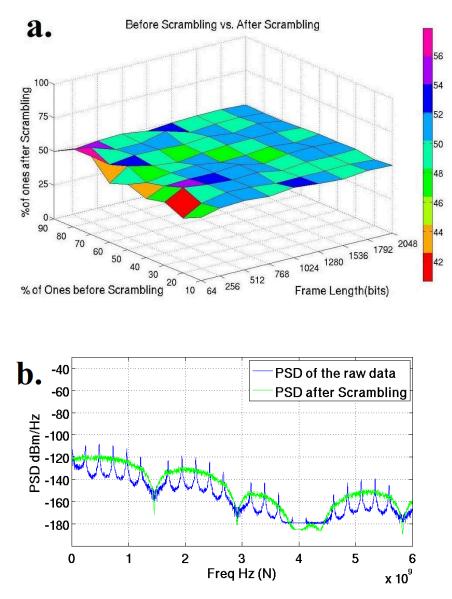

| Figure 3.10 a. Percentage of 1's before and after scrambling b. spectrum of                                 | f    |

|-------------------------------------------------------------------------------------------------------------|------|

| the $V_{cm}$ of the data before and after scrambling                                                        | .39  |

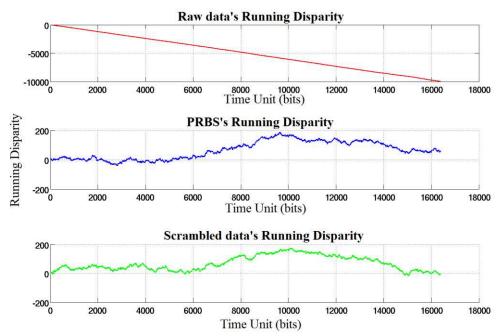

| Figure 3.11 Raw data's disparity vs Scrambled data's disparity (raw data                                    |      |

| distribution 80% of 0's and 20% of 1's, polynomial: $X16 + X5 + X4 + X3 + X4 + X3 + X4 + X4 + X3 + X4 + X4$ | - 1, |

| seed value FFFFh)                                                                                           | .40  |

## Chapter 4:

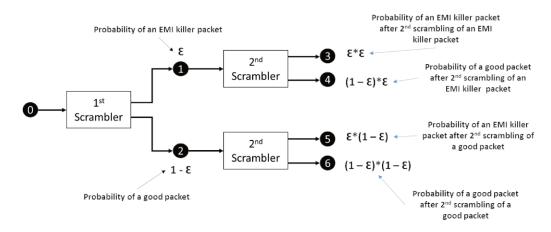

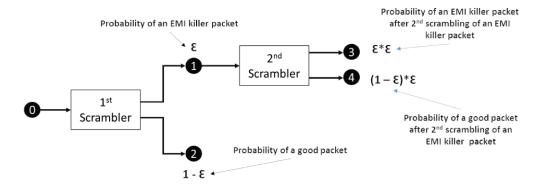

| Figure 4.1    | Probability of a repetitive pattern after a 2nd scrambling    | 50 |

|---------------|---------------------------------------------------------------|----|

| Figure 4.2    | Probability of a repetitive pattern after a 2nd scrambling of |    |

| repetitive pa | ckets only                                                    | 52 |

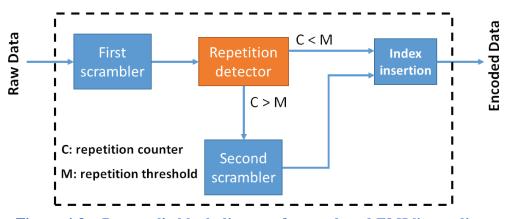

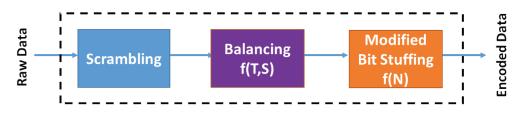

| Figure 4.3    | Proposal's block diagram for a reduced EMI line coding        | 53 |

| Figure 4.4    | Proposal's framing example                                    | 54 |

#### Chapter 5:

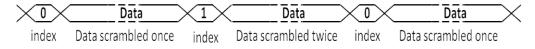

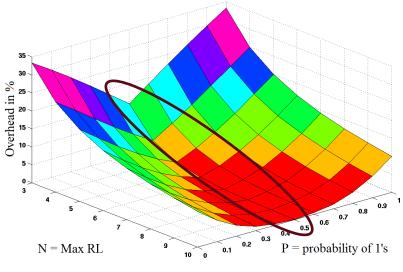

| Figure 5.1   | Bit Stuffing Maximum Overhead for different N58               |

|--------------|---------------------------------------------------------------|

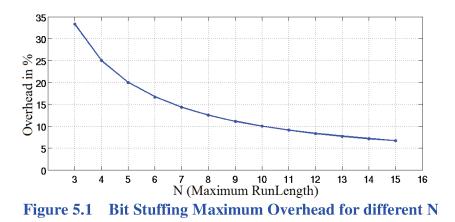

| Figure 5.2   | Markov Chain representation of Bit Stuffing for a maximum RL  |

| of N         |                                                               |

| Figure 5.3   | Theoretical Bit Stuffing Overhead estimation60                |

| Figure 5.4   | Bit Stuffing minimum vs. Maximum Overhead for different N .60 |

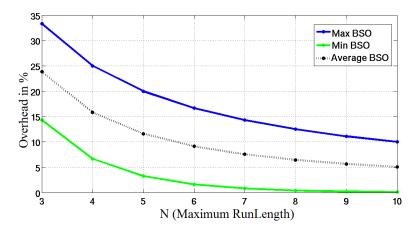

| Figure 5.5   | Proposal's block diagram for low overhead RL limited encoding |

| •••••        |                                                               |

| Figure 5.6   | PSD of the proposed RL limited method vs. PSD of Scrambling-  |

| only at 10 G | Hz frequency62                                                |

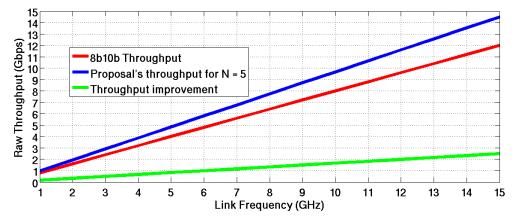

| Figure 5.7   | Raw Throughput comparison vs. Link frequency for data encoded |

| with 8b/10b  | and the proposed RL-Limited encoding63                        |

| Figure 5.8   | Lane-count reduction thanks to our proposed RL-limited        |

| encoding in  | the case of MIPI's M-PHY running at HSG4 (11.64 Gbps)65       |

## <u>Chapter 6:</u>

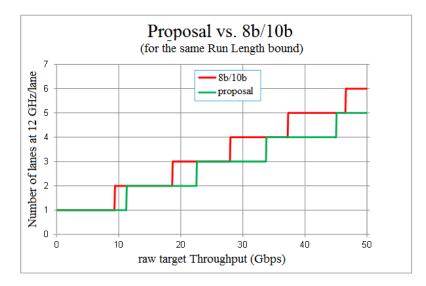

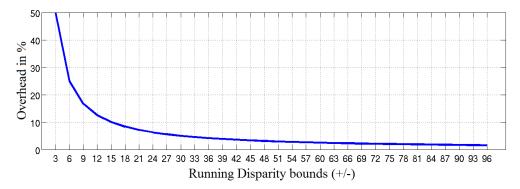

| Figure 6.1 | Polarity-bit encoding's overhead (deduced from equation 3.1) | .70 |

|------------|--------------------------------------------------------------|-----|

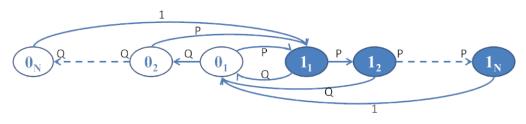

| Figure 6.2 | Organization chart of the proposed balancing method          | .71 |

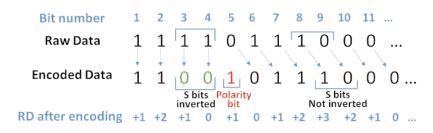

| Figure 6.3 | Example of data coded with our proposed method               | .72 |

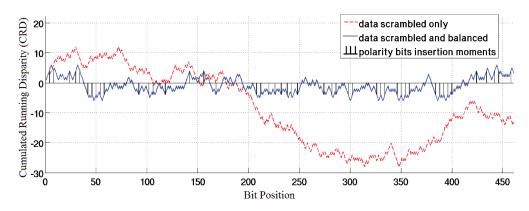

| Figure 6.4   | Example of the CRD of scrambled before and after balancing         |

|--------------|--------------------------------------------------------------------|

| with our pro | pposal for T=5 and S=2 (scrambling polynomial: X23 + X21 +         |

| X16 + X8 +   | -X5 + X2 + 1 with seed value FFFFFh)                               |

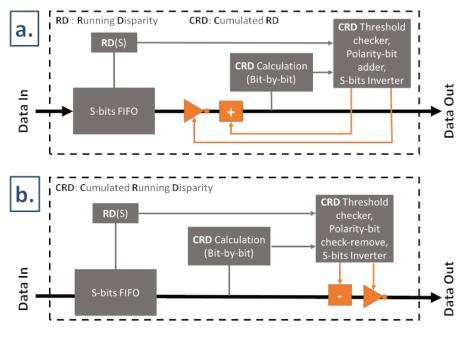

| Figure 6.5   | Proposed DC-balancer's block diagram a. Transmitter b. Receiver    |

| •••••        |                                                                    |

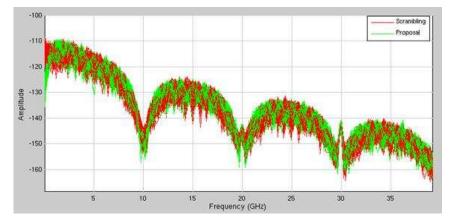

| Figure 6.6   | PSD of the $V_{cm}$ of our proposed method vs. Scrambling's PSD at |

| 10 GHz free  | quency75                                                           |

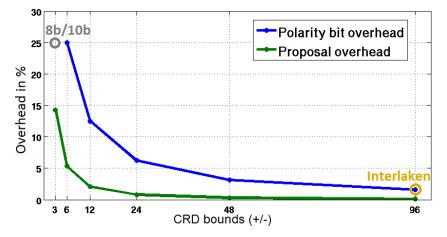

| Figure 6.7   | Proposal's overhead (green) compared to the polarity-bit           |

| encoding (b  | lue), 8b/10b encoding and Interlaken's protocol76                  |

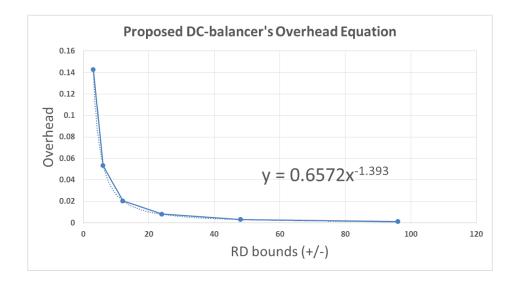

| Figure 6.8   | Excel representation of the overhead and equation generation77     |

# <u>Chapter 7:</u>

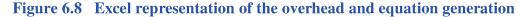

| Figure 7.1  | Block diagrams of the methods presented in a. chapter 5, and b.      |   |

|-------------|----------------------------------------------------------------------|---|

| chapter 6   |                                                                      | ) |

| Figure 7.2  | DC-balancer and RL limiter's block diagram83                         | ; |

| Figure 7.3  | PSD of the $V_{cm}$ of the proposed solution vs. scrambling's PSD at |   |

| 10 GHz free | quency85                                                             | í |

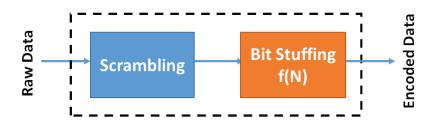

## Chapter 8:

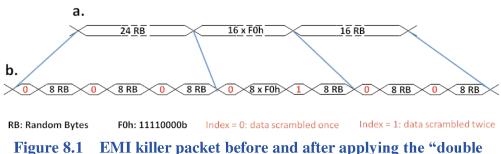

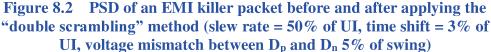

| Figure 8.1   | EMI killer packet before and after applying the "double             |    |

|--------------|---------------------------------------------------------------------|----|

| scrambling"  | method                                                              | 91 |

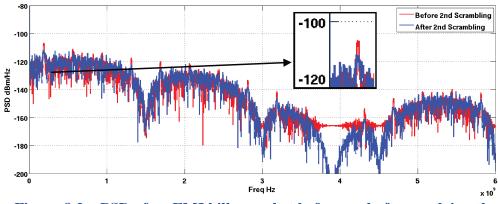

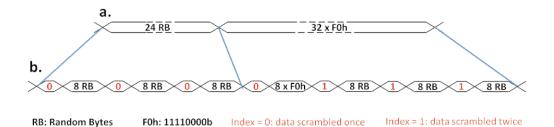

| Figure 8.2   | PSD of an EMI killer packet before and after applying the           |    |

| "double scra | mbling" method (slew rate = $50\%$ of UI, time shift = $3\%$ of UI, |    |

| voltage misr | natch between $D_p$ and $D_n$ 5% of swing)                          | 92 |

| Figure 8.3   | EMI killer packet before and after applying the "double             |    |

| scrambling 1 | nethod"                                                             | 92 |

| Figure 8.4   | PSD of an EMI killer packet before and after applying the           |    |

| "double scra | mbling" method (slew rate = $50\%$ of UI, time shift = $3\%$ of UI, |    |

| voltage misr | natch between $D_p$ and $D_n$ 5% of swing)                          | 93 |

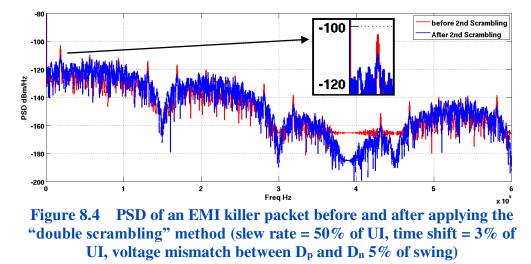

| Figure 8.5   | Bit Stuffing Overhead for: a. Non-Scrambled data / b. Scrambled     | d  |

| data         |                                                                     | 95 |

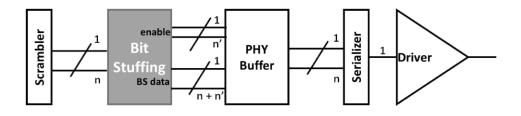

| Figure 8.6   | Bit Stuffing PHY Hardware implementation example                    | 98 |

# List of Tables

#### Chapter 3:

| Table 3.1 | Overview Table of some HSSLs               | 32 |

|-----------|--------------------------------------------|----|

| Table 3.2 | Run Length Distribution after scrambling   | 40 |

| Table 3.3 | Overview on some existing encoding methods | 43 |

#### Chapter 5:

| Table 5. 1 | RL-limited encoding proposal's overhead              |

|------------|------------------------------------------------------|

| Table 5.2  | Real use cases that can benefit from lanes reduction |

#### Chapter 6:

| Table 6. 1 | Proposed DC-balancer's | overhead76 |

|------------|------------------------|------------|

|------------|------------------------|------------|

## <u>Chapter 7:</u>

Table 7.1 DC-balanced and RL-limited line coding's overhead examples ...84

#### Chapter 8:

| Table 8.1   | Summary of the encoding methods presented in this thesis          | 39             |

|-------------|-------------------------------------------------------------------|----------------|

| Table 8. 2  | "scrambling + bit stuffing" method theoretical, image and rando   | m              |

| data's over | head                                                              | 96             |

| Table 8.3   | Modified Bit Stuffing Overhead (MBSO) in % for different RD       |                |

| and RL bou  | ands / $MBSO = f(RD_{bound}, RL_{bound})$                         | 97             |

| Table 8.4   | Total Overhead in % for different RL and RD bounds /              | 97             |

| Table 8.5   | Gate count estimation of the bit stuffing block for different bus |                |

| width       |                                                                   | <del>9</del> 9 |

#### Chapter

# Introduction

Smartphones and tablets have emerged in the last decade as an essential part of our lives. The number of applications handled is increasing and the quality of service provided to the user is still improving, resulting in more and more onboard hardware components, design complexity and bandwidth increase. One of the main challenges is then the power consumption, especially when focusing on a mobile device and its battery life, in addition to the worldwide environmental impact of the power consumption when expecting 4 billion smartphones and tablets by 2017 [1].

Essential elements that directly affects the performance of mobile devices are High Speed Serial Links (HSSLs). HSSLs connect the different components of a mobile device; the Application Processor (AP) to the modem or a companion chip, the AP to the camera or the display, the AP to the mass storage device, the RFIC (Radio Frequency Integrated Circuit) to the modem and etc... HSSLs are also used in laptops and computers as well as in networking. This results in a variety of HSSLs because each application have different requirements, and different protocols are designed to fulfill their needs.

In this thesis, a system-level overview on high-speed serial links is made, with special focus on three protocols: the Universal Serial Bus (USB), the Peripheral Component Interconnect express (PCIe) and the Low Latency Interface (LLI). We will make a comparison between the different parameters and justify their field of use. With the increasing demand for bandwidth, the speed of HSSLs is doubling every two to three years presenting many challenges to the designers in terms of complexity and power consumption. The design must then be optimized as much as possible.

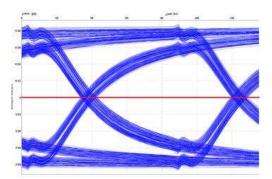

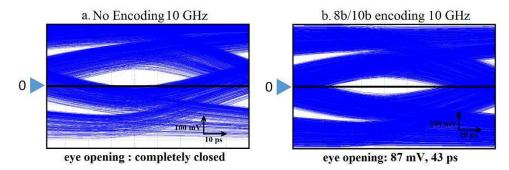

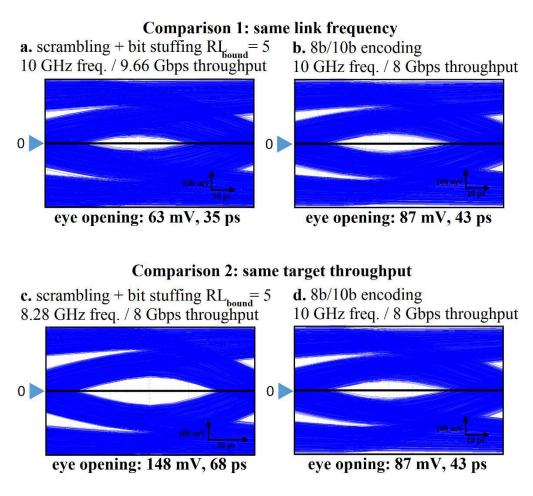

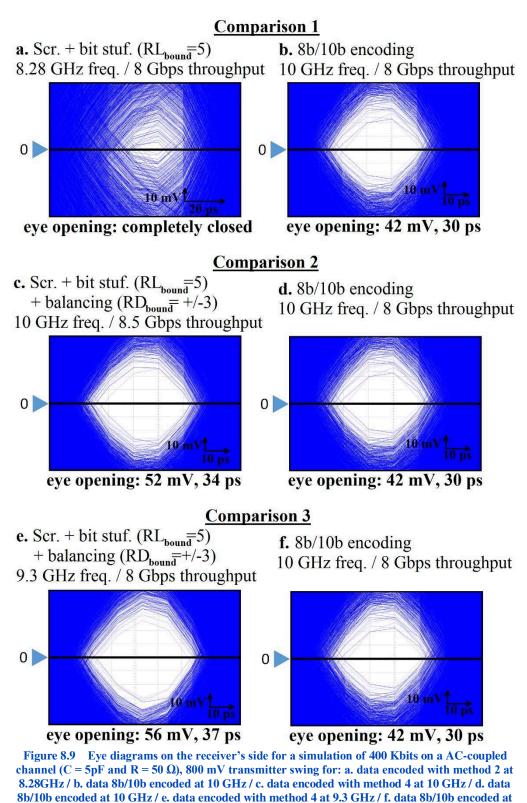

One of the parameters that directly affects the bandwidth and the performance of a HSSL is the line coding. In many, if not most of the HSSLs, the data to transmit on the link is encoded to ensure two main characteristics: a bounded Run Length (RL), which means that a certain number of consecutive identical bits must not be exceeded so the data contains enough transitions. The receiver benefits from the transitions to synchronize and recover the clock and the data correctly. The second characteristic that the encoding must bound is the Running Disparity (RD), which means that the difference between the numbers of transmitted 0's and 1's must not exceed a specific limit to reduce the BaseLine Wander (BLW) which is the signal shifting from the zero reference. The BLW closes the eye diagram (which is the superposition of all the bits of a signal) and might create sampling errors when recovering the data.

For those reasons, the line coding intervenes to present solutions. However, Line coding comes at the cost of added bits also called overhead, affecting the throughput. Over time, many encodings have been used in the standards, some present very good characteristics but at the cost of high overhead, reducing the bandwidth efficiency of the link. Other encodings have low overhead but do not ensure the same bounds for RL and RD and require analog components such as filters and equalizers to compensate. This means more design complexity and power consumption.

In this thesis, an overview on the existing methods which bound the RL and the RD is made. We will highlight their advantages and their drawbacks. Then we will present an optimized low overhead method that bounds the Run Length. Another main contribution of this thesis is a low overhead method that bounds the Running Disparity with an overhead down to 10 times lower than the existing methods, and for the same bounds. After presenting both methods separately, we will show how we can combine them to build a low overhead, run length limited and running disparity bounded line coding.

In addition to its low overhead characteristic, other advantages of the line coding proposed in this thesis will be highlighted such as providing interoperability between links with different RL and RD requirements as well as early errors detection.

#### **Thesis Organization**

The remainder of this thesis is organized as follows:

Chapter 2, "Problem Statement", explains in details today's High Speed Serial Links challenges. We will focus on the line coding's effect on the performance of HSSLs and the need for a new line coding.

Chapter 3, "State of the art", is divided into two main sections; the first one presents the state of the art of HSSLs focusing on three of today's HSSLs' protocols. The second section presents the state of the art of the encodings that were proposed and used in HSSLs, we will name their advantages and drawbacks and show the overhead-performance tradeoff.

In Chapter 4, "Low EMI encoding method", we present a line coding that ensures reduced EMI that could be caused by the data.

In Chapter 5, "Low overhead run length limited encoding Method", we will present an overhead-optimized line coding to limit the Run Length and evaluate its advantages over existing equivalent methods.

In Chapter 6, "Low Overhead DC-Balanced encoding method", we will present an overhead-optimized line coding, but this time to bound the Running Disparity. A comparison will also be made with the existing equivalent methods.

Chapter 7, "DC-Balanced and run length limited line coding" presents a method to combine both encoding methods presented in chapters 5 and 6, to build a low overhead, RL limited and RD limited Line Coding.

In Chapter 8, "Experimental results", we present the overhead results of the proposed line coding based on simulation, we show the resulting eye diagrams, the VHDL model and the gate count estimation, we compare those results with other encodings and highlight the advantages of our proposal.

In Chapter 9 we conclude and summarize the work presented in this thesis.

#### Chapter

# 2 Problem Statement

- 2.1 Chapter's Introduction

- 2.2 High Speed Serial Links

- 2.2.1 High Speed Serial Links' variety

- 2.2.2 HSSLs' layering model

- 2.2.3 Focusing on the physical layer

- 2.3 Line Coding's effect on data transmission

- 2.3.1 Introduction

- 2.3.2 Data's impact on EMI

- 2.3.3 Data's Run Length impact

- 2.3.4 Data's Running Disparity impact

- 2.4 Chapter's Conclusion

#### 2.1 *Chapter's* Introduction

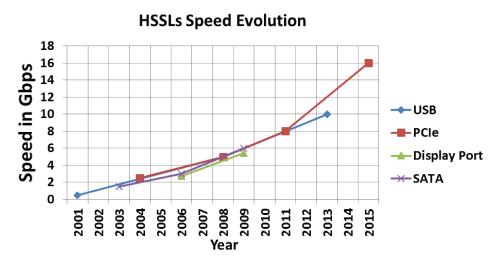

With the increase demand for throughput, High Speed Serial Links are now facing important challenges to transmit the data over a channel. In less than 15 years, the frequency has drastically increased from 500 Mbps (Megabits per second) to 16 Gbps (Gigabits per second) as we can see in figure 2.1 and copper-based channels are still used in most HSSL as transmit medium because of their many advantages in terms of area and cost over optical links.

Figure 2.1 Some High Speed Serial Links speed evolution

Another characteristic that is still used and scheduled for the future generations of HSSL is NRZ (Non-Return to Zero) signaling [2], which means that the binary information is sent with two voltage levels, i.e. V1 to indicate a 1 bit and V0 to indicate a 0 bit. NRZ has gained success because of its coding/decoding simplicity and its low voltage swing requirement that enables lower power consumption when compared to multi-level signaling. When power consumption is not the main constraint, multi-level signaling could be used such as MLT-3 (Multi-Level Transmit 3), PAM-4 (Pulse Amplitude Modulation 4), PAM 8, PAM 16 and etc... enabling better throughput at the same frequency, e.g. for PAM-4, 4 voltage levels are assigned for 00b, 01b, 10b and 11b. Thereby, 2 bits are sent in each clock period instead of 1 bit. Multi-level signaling is used in protocols such as Ethernet, where power consumption is not the main constraint. In this thesis, we will mainly focus on copper channels and NRZ signaling.

This chapter's purpose is to explain the functioning of HSSLs, the layering model and the role of each layer. We will then focus on the line coding and its effect on NRZ signaling over copper, and on the bandwidth efficiency as well.

#### 2.2 High Speed Serial Links

#### 2.2.1 High Speed Serial Links' variety

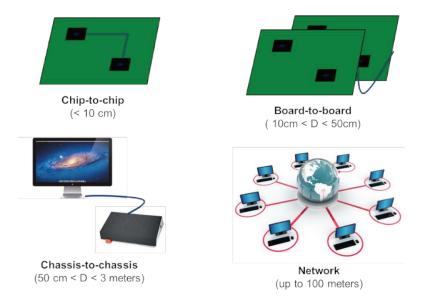

High Speed Serial Links (HSSLs) are found in almost all data communication processes from small channels lengths of few centimeters to long distances of tens of meters as we can see in Figure 2.2. From here, several HSSLs' protocols have been designed to fulfill the needs of each situation.

Figure 2.2 HSSLs different domains of application

In addition to the difference in the applications' distances, differences are also found in the applications' type; e.g. a display link have different requirements than a mass storage link or a modem link and etc... resulting in a variety of protocols. More details will be provided in chapter 3.

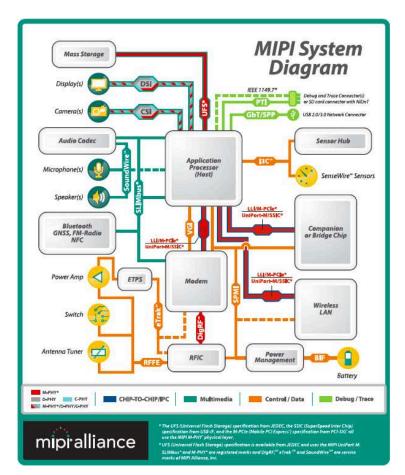

To reduce the variety and complexity of HSSLs, mobile components manufacturing companies joined their forces in the MIPI® Alliance (Mobile Industry Processor Interface). Founded in 2003 by ARM, Intel, Nokia, Samsung, STMicroelectronics and Texas Instruments, the MIPI alliance's aim is to define and standardize interfaces for connecting the different components of a mobile device as we can see in Figure 2.3 and now joins more than 280 companies.

Figure 2.3 MIPI® System Diagram for mobile devices [3]

In Figure 2.3, we can find the different HSSLs connecting the components: the LLI (Low Latency Interface), the UniPro (or UniPort, Unified Protocol), the DigRF (Digital RF), CSI (Camera Serial Interface), DSI (Display Serial Interface), M-PCIe (Mobile Peripheral Component Interconnect express, also called low power PCIe), and SSIC (SuperSpeed Inter-Chip, or the low power USB 3.0). Those protocols sometimes use different physical layers.

#### 2.2.2 HSSLs' layering model

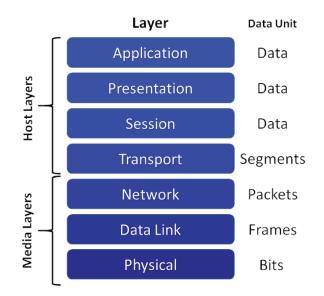

High Speed Serial Links' layering model follows the Open Systems Interconnection (OSI) reference model provided by the International Standards Organization (ISO) which is essentially constituted of 7 layers. Not every system uses all the layers, the functions and protocols which support the forwarding of data are then provided in the lower layers. HSSLs generally define the three to four lowest layers (See figure 2.4).

Figure 2.4 Open Systems Interconnection (OSI) Layers

The seven OSI layers' functioning can be summarized as follows [4]:

7. **Application:** The application layer serves as the window for users and application processes to access network services. This layer contains a variety of commonly needed functions.

6. **Presentation:** formats the data to be presented to the application layer. It can be viewed as the translator for the network. This layer might also provide compression and encryption such as password encryption.

5. Session: allows session establishment, maintenance and termination: allows two application processes on different machines to establish, use and terminate a connection.

4. **Transport:** provides end to end communication control, splits the message into smaller units (if not already small enough), and passes the smaller units down to the network layer. This layer can also provide message acknowledgment, traffic control and session multiplexing when there's many.

3. **Network:** controls the operation of the subnet, deciding which physical path the data should take based on network conditions, priority of service, and other factors.

2. **Data Link:** provides error-free transfer of data frames from one node to another over the physical layer by errors checking and sometimes correction. This layer also provides link establishment and termination, frame traffic control, sequencing, acknowledgement, and delimiting.

1. **Physical:** describes the electrical/optical, mechanical, and functional interfaces to the physical medium, and carries the signals for all of the higher layers. This layer provides data encoding and physical medium attachment.

HSSL's role in a system is then to route the different components and provide reliable data transmission and reception at the desired speed over the channel.

#### 2.2.3 Focusing on the physical layer

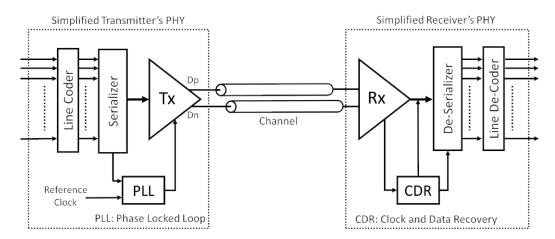

In this paragraph, we will focus on the lowest layer of HSSLs. In figure 2.5 we can see a simplified schematic of the Physical Layer (PHY).

Figure 2.5 Simplified block diagram of HSSLs Physical Layer

The essential elements that constitutes the PHY of a HSSL are represented in the figure above; the data coming from the higher layers comes in parallel (inside the HSSL IP) at the PHY layer to be transmitted in series to the peer destination. The PHY has to reliably, serially transmit the data. The digital part of the PHY is the Line Coder; the line coder encodes the data before transmission and plays a major role in ensuring the reliability of the transmission. This will be detailed in the next paragraph.

After encoding, the data goes to the serializer that uses a PLL (Phase Locked Loop) to multiply the reference parallel clock up to the serial frequency. The data goes then to the Tx (Transmitter) Driver that sends the Dp/Dn (Differential positive/negative) signals over the channel. Differential signaling is used to reduce noise [5] and radiated emissions.

We note that the described mechanism above is a simplified mechanism and other components could exist, e.g. a pre-driver might exist before the driver to do the pre-emphasis, which is a mechanism that amplifies high frequencies as a prevention from the channel's attenuation.

At the receiver, the Rx driver receives the serial data and the CDR unit (Clock and Data Recovery) recovers the clock and the data. The serial data is then made parallel by the de-serializer, de-encoded, and then forwarded to the upper layer.

# 2.3 Line Coding's effect on data transmission

## 2.3.1 Introduction

The most important measures to evaluate the performance of HSSLs are the BER (Bit Error Rate) and the eye diagram, which is the plot of the superposition of all the bits during transmission as we can see in figure 2.6. The eye diagram is judged by its vertical and horizontal opening. The protocol specification defines the minimum opening required at the receiver. The transmission should respect the specification so the system could ensure the defined BER.

Timing Jitter and the Signal-to-Noise Ratio (SNR) are two of the factors that affect the BER and the eye diagram's opening. Data encoding has a direct impact on both and in this section we're going to see how. Transmitted data can also contribute to increase Electro-Magnetic Interferences (EMI), causing errors in neighboring lanes or even neighboring devices. We will start by explaining how the data can increase EMI, and then we'll show the impact of the RL and RD of the data on the transmission.

Figure 2.6 Eye diagram example

#### 2.3.2 Data's impact on EMI

According to Maxwell, whenever electrons are moved, magnetic fields will be generated. Those fields could interfere with Radio Frequency (RF) components sending radio signals nearby. This is what we call Electro-Magnetic Interferences (EMI). Radiations could also aggress neighboring lanes of the same link creating errors. With the ascending data rates in electronics, care must be taken to mitigate EMI.

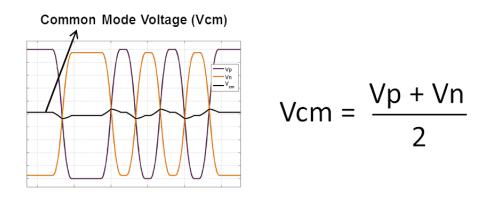

One of the reasons why HSSLs use differential signaling is EMI reduction. In a perfect world, the differentials create opposite fields that will cancel each other resulting in EMI suppression. But imbalance between differentials is inevitable and results in common mode voltage ( $V_{cm}$ ) that will be source to EMI [6]. The common mode voltage is represented in figure 2.7.

Figure 2.7 Common mode voltage representation (voltage mismatch = 5%, time mismatch = 5%)

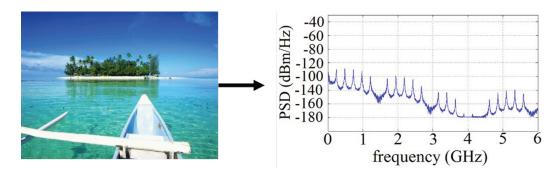

EMI are judged then on the Power Spectral Density of the common mode voltage [7] resulting from sending the data on the link. Repetitive data (e.g. repetitive bytes) can generate EMI [8] and will create peaks in the spectrum of the  $V_{cm}$  as we can see in figure 2.8. In this example, the peaks are due to repeated pixels data. To mitigate EMI, engineers work on reducing the peaks and spreading the spectrum of the  $V_{cm}$ . Many techniques exist to reduce EMI [6 – 9] and line coding is one of them. Line coding helps in reducing the redundancy

in the data and spreading the spectrum of the  $V_{cm}$  as we are going to see in chapter 3.

Figure 2.8 Power Spectral Density example of the Vcm of raw picture data at 1.4 GHz

## 2.3.3 Data's Run Length impact

The Run Length (RL) is a major factor in Clock and Data Recovery (CDR) unit at the receiver's side (see figure 2.5). A simplified schematic of the CDR unit is shown in figure 2.9 as follows:

Figure 2.9 Clock and Data Recovery simplified schematic

The clock recovery part of the CDR detects the transitions on the data line and recovers the clock that is synchronized with the received data. The recovered clock is then used to sample the data at the right moment and deduce the bits value.

Data transitions have a direct impact on the clock recovery part. Most of clock recovery in HSSLs are Phase Locked Loop based (PLL) because of many

advantages that are out of scope of this thesis. A simplified schematic of the PLL-based Clock Recovery is shown in figure 2.10.

#### Figure 2.10 PLL-based Clock Recovery simplified schematic

The PLL acts like a low pass filter to its input's jitter, and as a high pass filter to the VCO's (Voltage Controlled Oscillator) jitter. The PLL is characterized by its cutoff frequency which could be written according to [10] as follows:

$$f_{-3dB} \cong \frac{K_P \cdot (TD \cdot K_{PD}) \cdot K_{VCO}}{2 \cdot \pi}$$

(2.1)

where TD is the transitions density and equals 1/(Run Length)

and  $K_{p}$ ,  $K_{PD}$ , and  $K_{VCO}$  are coefficients that are related to the loop filter, the phase detector and the VCO, that are out of scope of this thesis.

As we can see from equation (2.1), the transition density affects in first place the phase detector's output, making the PLL's bandwidth RL-dependent and not predictable. While for many reasons the PLL's bandwidth should be carefully chosen [11], this RL dependency could have many consequences. The increase in RL (decrease in TD) also means PLL bandwidth decrease which results in jitter peaking [12] and degradation of the receiver jitter tolerance characteristic (increase system Bit Error Rate).

Designers have addressed the problem of pattern dependency of the phase detector [12] [13] [14] but have done so with a significant increase, about twice, in hardware [10].

While PLL-based CDR architectures already suffer from a relatively large total layout area [15], adding more complexity might not be a good choice.

#### 2.3.4 *Data's* Running Disparity impact

The Running Disparity (RD) also called the Cumulated Bits Difference (CBD) is known as the difference between the 1's and 0's in the data to send over the link. The RD is counted by adding +1 for a '1' bit and -1 for a '0' bit. Figure 2.11 shows a simple example.

Since the early days of data communication, data coding methods have been introduced to limit the RD and bound it to reduce the baseline wander initially due to AC-Coupling at the receiver. AC-coupling is generally used when interconnecting drivers with different voltage thresholds [16]. This results, after a transition period, in differential signaling centered to Zero volts at the receiver whatever the Dp and Dn voltages levels sent by the transmitter. This is illustrated in figure 2.12. AC-coupling is then an advantage when using cables and connectors to connect different devices, allowing interoperability between constructors using different technologies.

Figure 2.12 AC-coupling and transition period

However, AC-coupling has a big drawback; after the transition period for the signal to stabilize, the capacitive effect can make the signal shift up and down (charging and discharging the coupling capacitor) creating Baseline Wander, closing the eye diagram and degrading the SNR. This could be explained differently; the coupling capacitor forms with the termination resistor a high-pass RC filter that attenuates low frequency components formed by runs of consecutive bits, but more precisely by the difference between 1's and 0's, which is the running disparity. This is why one of the main interests of a line coding is to reduce or bound the RD.

Because it is a capacitance charge/discharge phenomenon, BLW due to the coupling capacitor can be estimated. For the sake of simplicity, we consider a single ended receiver (Dp or Dn). The simplified schematic is shown in figure 2.13.

Figure 2.13 Simplified AC-coupling

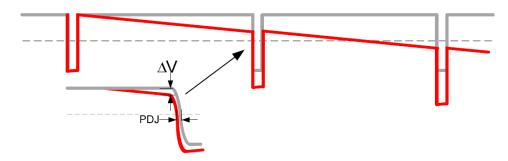

The BLW also creates timing Jitter as we can see in figure 2.14. This type of Jitter is part of the Pattern Dependent Jitter (PDJ) (also called Data Dependent Jitter (DDJ) or Inter-Symbol Interference (ISI)) and from [17] and [18] we can calculate both the BLW and the PDJ.

Figure 2.14 Baseline Wander and jitter introduced by the high pass filter [17]

In figure 2.14,  $\Delta V$  represents the BLW, and PDJ is the Jitter and they can be calculated according to the following equations:

$$BLW = 0.5*V_{pp}(1-e^{-t/RC})$$

(2.2)

$$PDJ = \frac{BLW}{slope}$$

(2.3) with  $slope = Vpp \frac{0.6}{Tr}$  (2.4)

Where t is the discharge time

V<sub>pp</sub> is the peak-to-peak voltage (voltage swing)

R is twice R<sub>t</sub> (considering the driver's resistor)

C is the coupling capacitor

and Tr is the rise time (20% to 80% of the signal)

The discharge time of the capacitor is represented by the signal being at the same level for a certain moment, this means consecutive identical 1's. But when the signal goes to 0, this will recharge the capacitor for a certain duration. The charge or discharge time will then be represented by the difference between number of 1's and 0's which is the Running Disparity times the bit duration. The BLW can thus be written as follows:

BLW =

$$0.5*V_{pp}(1-e^{-(RD*Tb)/(R*C)})$$

(2.5)

where RD is the running Disparity

and Tb is the bit time or 1/frequency

Equation (2.3) shows that PDJ can be reduced by reducing the BLW. To reduce BLW, according to equation (2.5), we should increase the values of R and C. The resistor's value should be adapted to the driver and the channel, so its value cannot be simply manipulated. When it comes to the value of the capacitor, the best is to have an infinite value. But the more the capacitor's value gets bigger, the bigger is its surface and harder is the integration in the chip. On-chip capacitance per lane is limited to a few picoFarads (pF) at best in practical real estate of chip area [19]. Another consequence from increasing the capacitor's value is increasing the transition period, creating a high latency. R and C values are then forced by the system's obligations and their negotiation margin is tight. When there's no choice, filters and equalizers are used to counter the BLW's effect adding more complexity, area and power consumption. More details are provided in the next chapter.

Even when the transmitter and the receiver are DC-Coupled, BLW and PDJ exist, due to the channel and other factors, and are affected by the RD as we will observe later on. But it is more complex to get an estimation because it is channel-dependent and case-dependent.

# 2.4 Chapter's Conclusion

As seen in this chapter, the redundancy, Run Length and the Running Disparity of the data have an immediate impact on signal's integrity and system performance. For this reason, encodings have been designed to transform the raw data and limit or reduce the RL and the RD, but this comes at the cost of added bits called bandwidth overhead that sometimes reaches up to 25% of the initial size of the data, reducing the throughput. With the increasing demand for throughput, every bit sent on the link counts. Line coding is then a big challenge;

so is it possible to design a line coding that can bound the RD and the RL to low values with a **low overhead**?

High Speed Links are also applied on a wide range on data communication as we saw earlier in this chapter and a big variety exists. The bounds to the RL and RD requested by the link could be variable and case-dependent. Is it then possible to design a **programmable** low overhead line coding that performs to the desired Run length and Running Disparity?

### Chapter

# 3 State of the Art

3.1 Chapter's Introduction

- 3.2 System-level comparison of three HSSLs: LLI, PCIe and USB

- 3.2.1 The Low Latency Interface (LLI)

- 3.2.2 The Peripheral Component Interconnect express (PCIe)

- 3.2.3 The Universal Serial Bus (USB)

- 3.2.4 Layering model comparison

- 3.2.5 Other parameters Comparison

- 3.2.6 Comparison's conclusion

- 3.3 Line Coding's State of the Art

- 3.3.1 Introduction

- 3.3.2 The Bit Stuffing (BS)

- 3.3.3 The 8b/10b encoding

- 3.3.4 Data Scrambling

- 3.3.5 The Polarity Bit Coding

- 3.3.6 Summary of some existing encoding methods

3.4 State of the Art's Conclusion

# 3.1 *Chapter's* Introduction

In the previous chapter we saw that a variety of high speed serial links exists to satisfy different types of applications, and then we saw the impact of the noncoded data on a HSSL.

This chapter is divided into two main parts: in the first part we will make a system-level comparison between three HSSLs that are used for three different

kinds of application: the Universal Serial Bus (USB), the Peripheral Component Interconnect express (PCIe) and the Low Latency Interface (LLI). We analyze their different parameters, we show the relation between these parameters and how improving one parameter could result in a degradation of another. Based on this analysis, our conclusion outlines the reason why USB is used for I/Os, PCIe is used for data hungry devices and LLI for memory sharing.

In the second part of this chapter, we overview most of the existing line coding methods that were designed for NRZ signaling. We compare them and show the advantages and the drawbacks of each, then highlight the overhead/performance tradeoff.

# 3.2 System-level comparison of three HSSLs: LLI, PCIe and USB

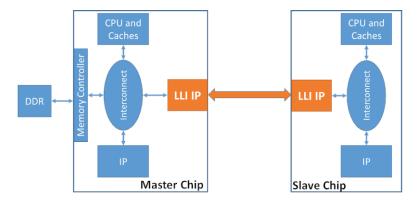

#### **3.2.1** The Low Latency Interface (LLI)

One additional challenge in mobile phones industry is to reduce the electronic Bill of Materials (e-BoM). With today's phone peripherals becoming more and more complex, as most of them are having their own CPU-DDR subsystem, reducing BoM is not a simple task. That's why the Mobile Industry Processor Interface (MIPI<sup>®</sup>) Alliance developed the LLI 1.0 (Low Latency Interface 1.0) [20] [21] which is a serial interface that enables peripherals, like modems for example, to share the system's main DDR located on the application processor's side, which enables mobile phones manufacturers to remove the modem's DDR and reduce the total phone's cost. LLI 2.0 version extended the use of LLI and made it a general chip-to-chip interconnect. LLI is also used for Inter-Processor Communication (IPC).

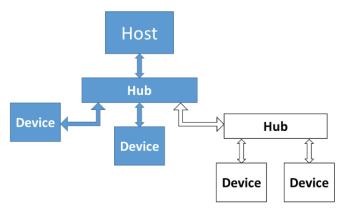

Figure 3.1 Example of an LLI environment (not exhaustive)

As we can see in Figure 3.1, LLI can be considered as a tunnel between two chips and it is memory mapped from both sides. The DDR on the main chip can be then considered as it was on the slave chip. LLI uses the M-PHY<sup>SM</sup> from MIPI as physical layer. The LLI benefits from M-PHY's three high-speed gears: G1 at 1.4 Gbps, G2 at 2.9 Gbps and G3 at 5.8 Gbps. Gear 4 is expected to be released soon and will run at 11.6 Gbps. Seven low speed gears are featured as well.

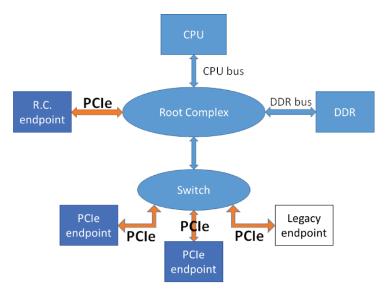

#### **3.2.2** The Peripheral Component Interconnect express (PCIe)

PCIe [22] [23] is a serial interconnect developed as a replacement to the parallel PCI bus. PCIe 1.0 runs at 2.5 Gbps, PCIe 2.0 at 5 Gbps and PCIe 3.0 runs at 8 Gbps. As shown in figure 3.2, the PCI Express is a central element of a modern computer and connects many of its components.

Figure 3.2 Example of PCIe link environment

In figure 3.2 we can see the following components:

- The 'Root Complex' (R.C., North Bridge) primary usage is to connect the CPU and the main DDR, and is also used for high throughput devices that need to access the DDR.

- The 'Switch' (South Bridge in PCI) is used to connect I/Os on the system.

- The R.C. Endpoints e.g. external Graphics Card, are directly routed to the R.C. because they need maximum performance and the root complex allows the Graphic Card to share the system's main DDR.

- PCIe Endpoints are PCIe native devices. They are routed to the switch.

- Legacy Endpoints: e.g. USB or SATA controllers, they are not PCIe devices but their controllers communicate with the switch using the PCIe protocol.

PCI express's instructions are Memory Mapped.

PCIe features Hot Plug.

## **3.2.3** The Universal Serial Bus (USB)

The Universal Serial Bus (USB) [24] is a high-speed serial interface developed to connect I/O peripherals to a computer. USB3.0 runs at 5 Gbps. Figure 3.3 shows the USB structure. The host is the intelligent element, it initiates all the transfers, and so, unlike PCIe and LLI, the USB devices cannot initiate a transaction (but they can ask the host to reschedule the transaction when they are not ready and they ask the host to reinitiate when they are ready). The Hub allows the extension option; it acts like a device in the Host's point of view.

Figure 3.3 USB Structure

As mentioned in the PCIe's section above, the USB's Host is connected to the Southbridge in a system which might be the PCIe Switch.

USB's instructions are not Memory Mapped; The CPU does not have direct access to devices, the Host must have an integrated memory to temporary store devices' data and the CPU comes later on to retrieve data from the Host's memory.

USB features Hot Plug.

### 3.2.4 Layering model comparison

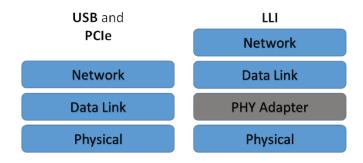

Figure 3.4 USB, PCIe and LLI Layering model comparison

The USB and PCIe layers are designed according to the OSI model. They both have 3 layers: the Transaction Layer (TL), the Data Link Layer (DLL) and the Physical Layer (PL). The TL is the upper layer; its duty is to generate header and data packets. The DLL adds CRC (Cyclic Redundancy Check) info to the header and data packets on the transmit side, checks the CRC on the receive side, generates flow control packets to the remote data link layer and manages the local flow control. The PL makes the coding/encoding and sends the data on the link.

In comparison to USB and PCIe layering model, the LLI has one additional layer: the PHY Adapter Layer (PA).

The LLI's transaction and physical layers does the same main duties such as in USB and PCIe. The DLL adds flow control on each data packet on the transmit side, and manages flow control on the receive side. The PA layer adds CRC and sequence number for each transmit packet and does the CRC and sequence number checking on the receive side.

## 3.2.5 Other parameters Comparison

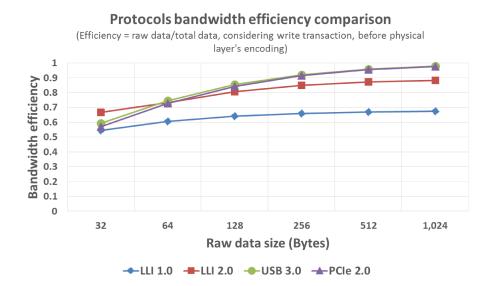

Figure 3.5 Throughput efficiency comparison for USB, PCIe and LLI for a write transaction and before line coding

LLI's packet partitioning was designed to provide very fast errors detection and retry mechanism, enabling the low latency feature. The Physical Layer of LLI ensures a BER of 10<sup>-10</sup>. But with the 8-bits CRC for every 64 bits in the 1.0 version, LLI targets a BER of 10<sup>-20</sup> to meet the requirements of a DDR and cache refill operations. This packets partitioning affects LLI's throughput efficiency as we can see in Figure 3.5. The maximum efficiency (raw data/total data) in LLI 1.0 is 0.67, LLI 2.0 introduced a new packet partitioning increasing the efficiency to 0.88. This comes at the cost of latency increase, but the LLI's 1.0 partitioning is still kept with higher priority level for latency-sensitive transactions.

USB and PCIe have the throughput as priority and the efficiency is about 0.98 ensuring high throughput beneficial to the transfer of huge amounts of data. However, they have a BER of  $10^{-12}$  ensured by the Physical layer and their retry mechanism is slow compared to LLI.

More details about latency, throughput and others parameters comparison can be found in the overview we made in [25].

## 3.2.6 Comparison's Summary

| Parameter                        | Protocols   | Advantages                                                        | Consequences                                                        |  |

|----------------------------------|-------------|-------------------------------------------------------------------|---------------------------------------------------------------------|--|

| Differential Swing =<br>800mV    | USB<br>PCIe | Long distances applications<br>(cables)                           | High power consumption                                              |  |

| Differential Swing =<br>400mV    | LLI         | Low power consumption                                             | Short distances applications                                        |  |

| Memory mapping                   | LLI<br>PCIe | Direct access to data<br>(memory sharing<br>possibilities)        | Occupying the CPU bus                                               |  |

| No memory mapping                | USB         | Not occupying the CPU<br>bus                                      | No direct access to data (No memory sharing)                        |  |

| Multi-lane scalability           | LLI<br>PCIe | Multiplying throughput and<br>decreasing latency                  | More power consumption and<br>no external connectors<br>possibility |  |

| No multi-lane<br>scalability     | USB         | External connectors possibility                                   | No throughput increasing possibility                                |  |

| Low latency error retry<br>time  | LLI         | Cache refill operations possibility                               | Low data efficiency<br>(throughput)                                 |  |

| High latency error<br>retry time | PCIe<br>USB | High data efficiency<br>(throughput)                              | No possibility for cache refill operations                          |  |

| Time Framing QoS                 | USB         | All devices are served                                            | High latency for interrupts                                         |  |

| Priority based QoS               | LLI<br>PCIe | Low latency for interrupts<br>and for high priority<br>operations | Other devices or operations have to wait to be served               |  |

Table 3.1 summarizes the overview.

#### Table 3.1Overview Table of some HSSLs

We conclude that USB with its intelligent software and hot plug feature allows easy Human Interface Device usage, and with its high throughput, it allows mass storage device usage. But with its high latency, high BER, and because USB is not memory mapped, it can allow neither memory sharing nor cache refill operations. PCIe with its intelligent NorthBrigde/ SouthBridge system design allows I/O connecting, and with its memory mapped instructions and its high throughput, even though it is latency-criticized [26], it allows datahungry devices (like graphics card) to share the system's main DDR when connected directly to the root complex and using up to 32 lanes to increase throughput and decrease latency. But using multi-lanes will increase power consumption which is an important issue in mobile applications.

To allow DDR chip-to-chip sharing and cache refill operations inside mobile phones, and in order to enable manufacturers to remove the modem's DDR and reduce the e-BoM, MIPI Alliance created the LLI featuring a low BER, low latency and low power consumption physical layer (the M-PHY), but at the cost of lower throughput efficiency.

# **3.3** Line Coding's State of the Art

### **3.3.1** Introduction

As mentioned in chapter 2, Line Coding is one of the biggest challenges in data transmission. That's why there is a big variety of coding methods that were proposed over time, and it is quite difficult to go through all of them.

As seen earlier in this chapter, HSSLs protocols add information to the data and decrease the efficiency before the PHY layer. Line coding must then be optimized as much as possible to not degrade the efficiency furthermore.

In this section, "line coding's state of the art", we will try to go through the most efficient line coding methods, and especially the ones implemented in HSSLs standards.

The next paragraphs will overview the following line coding methods: the Bit Stuffing, the 8b10b encoding, the Scrambling and the polarity-bit coding.

## **3.3.2** The Bit Stuffing (BS)

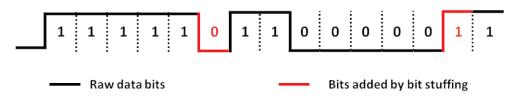

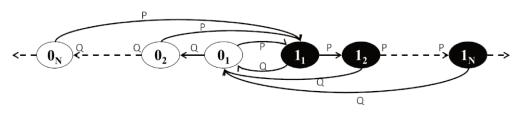

The Bit Stuffing is a method to limit the Run Length (RL). At the transmitter, the number of Consecutive Identical Bits/Digits (CIBs/CIDs) is counted. Whenever the RL reaches a specific value that we will call N, an inverted bit will be added to create a transition, even if the next data bit contains a transition.

On the other side, the receiver will benefit from this transition to recover the clock and the data without the risk of time sampling errors. And then the bit stuffing decoder will count the number of CIDs, and whenever it reaches N, the next bit will be removed. The data is then restored to its raw state.

Bit Stuffing for N = 5

Figure 3.6 Bit Stuffing Example for Run length limitation of 5

Bit Stuffing's advantage is its simplicity but there is a major drawback. The number of added bits is data dependent. If the raw data contains enough transitions and does not exceed the limit fixed by the bit stuffing, the bit stuffing will not intervene and the overhead will be zero. The worst case is when the data is all ones or all zeroes, the bit stuffing's overhead is 1/N.

When a certain throughput is targeted, the frequency must be pushed to the worst case overhead to ensure the throughput. Let's consider the case of a link that should ensure 10 Gbits/s for video data transmission. This link is encoded with Bit Stuffing at N = 5. Even though the BS might add few percent overhead, the worst case should be considered which is 1/5 = 20%. The frequency at which the link should run to ensure 10 Gbits/s will be f<sub>link</sub> = 10+10\*20% = 12 GHz.

Bit Stuffing is used in protocols such as CAN (Controller Area Network) that uses the NRZ signaling and does the BS with N = 5. BS is also used by the USB 2.0 [27] that uses NRZI signaling and does the BS with N = 6 for consecutive 1's only, because a 0 already contains a transition in NRZI.

We note that Bit Stuffing does not help in reducing the EMI and in spreading the spectrum. Repetitive patterns will stay repetitive with bit stuffing. Bit stuffing also does not help in reducing the RD.

## 3.3.3 The 8b/10b encoding

The 8b/10b encoding [28] [29] was introduced back in 1983 and has gained success because of its excellent characteristics. 8b/10b encoding is made via 5b/6b and 3b/4b sub-block encoding for every byte to be transmitted. If we look at it in a different point of view, 8b/10b encoding transforms each data byte into a 10-bit symbol providing  $2^{10} = 1024$  valid data words instead of  $2^8 = 256$  valid data words necessary to transmit an 8-bit information. Only the "best" combinations out of 1024 are chosen to represent the data bytes, i.e. the ones ensuring a Run Length limited to 5, and a Running Disparity bounded to +/- 3. In addition, 8b/10b encoding provides control symbols from the remaining combinations. The rest will be non-valid combinations used for errors detection.

However, because of adding 2 bits to each byte, 8b/10b encoding has an overhead of 2/8 = 25%. With the increasing demand for bandwidth, 25% of overhead seems to be an important issue.

8b/10b encoding helps in reducing by a factor of 2 the repetition of some bytes, but not all of them. There is then a positive effect on EMI but this might not be enough.

## 3.3.4 Data Scrambling

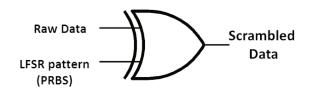

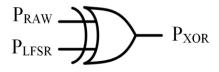

Scrambling is a XOR (eXclusive OR, modulo-2 addition) operation between the raw data (the data to scramble) and the output pattern of an LFSR (Linear Feeback Shift Register). The output pattern of the LFSR is called PRBS (Pseudo-Random Binary Sequence). A simplified schematic of the scrambling operation is represented in Figure 3.7.

Figure 3.7 Simplified representation of scrambling

#### The Linear Feedback Shift Register (LFSR):

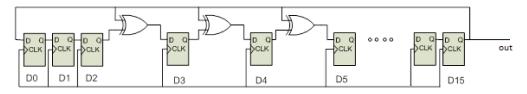

An LFSR is a shift register that, when clocked, advances the signal through the register from one bit to the next most-significant bit. Some of the outputs are combined in eXclusive-OR configuration to form a feedback mechanism. An LFSR is represented by a polynomial: for example  $X^{16} + X^5 + X^4 + X^3 + 1$ represents an LFSR formed by 16 shift registers for which the 3<sup>rd</sup>, the 4<sup>th</sup> and the 5<sup>th</sup> shift registers content are modified by a XOR between the output and the previous shift register as we can see in figure 3.8. The LFSR is initialized at a seed value.

Figure 3.8 LFSR Galois representation of the polynomial: X16 + X5 + X4 + X3 + 1

We note that there are two representations of the LFSR, the Galois and Fibonacci. We won't go through the details and the differences because it is out of scope of this thesis. We also note that the polynomial's value (even when it is from the same degree) should be carefully chosen to generate a good pseudorandom sequence. In the simulations in this thesis, we will use polynomials that were implemented in famous standards and have been proven to provide good characteristics.

#### The Pseudo-Random Binary Sequence (PRBS) characteristics:

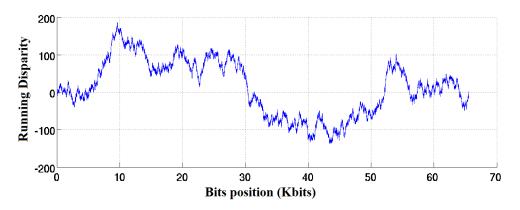

An N-bit LFSR generates a repetitive PRBS of length  $2^{N}$ -1 bits. The PRBS pattern ensures a Run Length bounded to N bits. The PRBS provides equal probability of 1's and 0's. The Running Disparity of the PRBS pattern varies from a polynomial to another. An example of the  $X^{16} + X^5 + X^4 + X^3 + 1$  polynomial with FFFFh as seed value is represented in Figure 3.9.

Figure 3.9 RD representation of the PRBS generated by the polynomial: X16 + X5 + X4 + X3 + 1, seed value 1FFFFh

#### Scrambled data's characteristics:

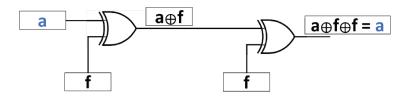

As mentioned before, scrambling is a XOR between the raw data and the PRBS sequence. The XOR operation was chosen because of its characteristics:

• Binary data with any probability distribution of 1's and 0's, once XORed with a sequence of equal distribution of 1's and 0's, results in data (scrambled data) with equal probability of 1's and 0's. This isn't the case

for other logic gates. In other terms, if we consider P as the probability of 1's:

- o If P(PRBS) = 0.5 → P(scrambled data) = 0.5 if the data window is long enough, whatever P(raw data) is. This is explained in details in Annex A and a simulation in Figure 3.10.a shows the percentage of 1's after scrambling for frames with different percentages of 1's before scrambling.

- The raw data (initial data) can be reproduced on the receive side from the scrambled data by reproducing the PRBS (applying the same LFSR). It is a well know result that the XOR and NXOR functions are the only binary functions of two variables that feature this involution property.

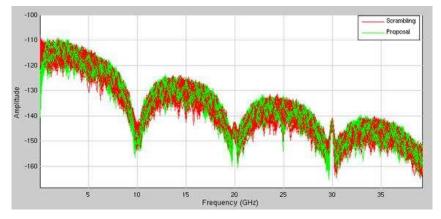

• When the data is XORed with the PRBS, the scrambled data will be statistically randomized. This results in spreading the PSD spectrum of the  $V_{cm}$  eliminating the peaks, and reducing the EMI. This is illustrated in Figure 3.10.b.

Figure 3.10 a. Percentage of 1's before and after scrambling b. spectrum of the  $V_{cm}$  of the data before and after scrambling

Balancing the number of 1's and 0's inside the data results in two major benefits:

Scrambled data has statistically more transitions than raw data before scrambling especially if the raw data is very unbalanced in terms of 1's and 0's. By using Markov Chains, we can get a theoretical estimation of the run length distribution. Table 3.2 summarizes the distribution from a RL of 5 to a RL of 20. The values in Table 3.2 are deduced from the theoretical study in **Annex B**. We also made a simulation on long sequences of data and made a comparison.

| Run Length | Occurs Theoretically in average (Bytes) | Occurs according to our<br>simulation<br>Min/Average/Max (Bytes) |  |  |

|------------|-----------------------------------------|------------------------------------------------------------------|--|--|

| 5          | 4                                       | 1/8.45/26                                                        |  |  |

| 6          | 8                                       | 1/17/49                                                          |  |  |

| 7          | 16                                      | 2/35.6/100                                                       |  |  |

| 10         | 128                                     | 9/302/748                                                        |  |  |

| 14         | 2 K                                     | 128/6.34 K/19.3 K                                                |  |  |

| 18         | 32 K                                    | 5.42 K/64.6 K/240.3 K                                            |  |  |

| 20         | 128 K                                   | 5.7 K/262 K/784.3 K                                              |  |  |

| :          | :                                       | :                                                                |  |  |

2. Scrambling statistically reduces the Running Disparity especially if the raw data is not balanced. Figure 3.11 shows an example.

Figure 3.11 Raw data's disparity vs Scrambled data's disparity (raw data distribution 80% of 0's and 20% of 1's, polynomial: X16 + X5 + X4 + X3 + 1, seed value FFFFh)

#### Scrambling's advantages:

To summarize, we can deduce the following advantages from scrambling:

- 1. Scrambling helps in reducing EMI by randomizing the data and eliminating redundant patterns.

- 2. Scrambling creates transitions by balancing the number of 1's and 0's. This is beneficial in clock and data recovery.

- 3. Scrambling reduces the Running Disparity, which means Baseline Wander reduction and Data Dependent Jitter reduction.

- 4. Scrambling has 0% overhead. No bits are added to the transmission

#### Scrambling's drawbacks:

Despite all of its advantages, scrambling has the following drawbacks:

- Scrambling could produce repetitive patterns that will cause peaks in the V<sub>cm</sub> spectrum, causing EMI. We will call them EMI Killer packets. Even though their probability of happening is low, they could still happen.

- 2. Scrambling creates transitions inside the data, but it does not ensure a guaranteed bound for the RL. Let's suppose a CDR that can handle a maximum run length of 9. According to table 3.2, a run length of 10 happens theoretically every 128 bytes. An error could then occur on the recovery every 128 bytes requiring a retry and degrading system performance. Even when the CDR can handle big values of RL, patterns could be designed (aligned with the PRBS) to create hundreds of consecutive Identical Bits [30] that are known as killer packets.

3. Scrambling reduces the RD but it does not guarantee a certain bound. The RD could still reach high values that can go more than +/- 1000. In addition to analog filters that could be added to correct the BLW, Protocols like PCIe 3.0 cut the transmission when the RD reaches high values and send special patterns to balance the RD. This also affects system performance and latency.

#### Standards using scrambling:

Many scrambling-based encodings have been implemented on HSSLs standards. The 64b/66b encoding used in 10G Ethernet uses scrambling and adds 2 bits "sync header" ('10' or '01') to every 64 bits to ensure a transition and indicate whether the frame is control or data. PCIe 3.0 uses 128b/130b encoding using the same principle. USB 3.1 uses 128b/132b encoding adding 4 bits sync header ('1010' or '0101') enabling a single error in the sync header to be corrected without going through a retry.

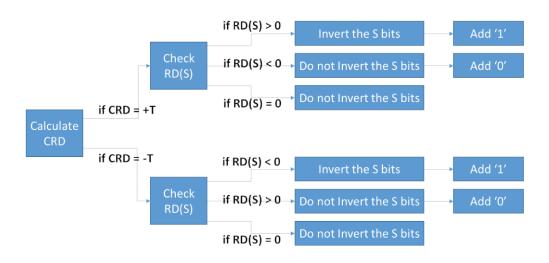

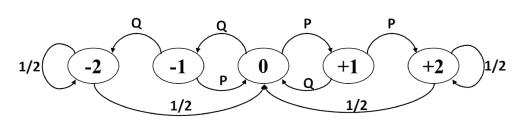

## 3.3.5 The Polarity Bit Coding

The polarity bit coding is one of the most overhead-optimized methods that bounds the Running Disparity. Over time, DC-balanced codes have been introduced. In 1986, Knuth proposed a method [31] to construct frames with equal number of 0's and 1's. Knuth proved that any binary sequence of a specific size, could be balanced by inverting, at a specific bit position, all the rest of the sequence. The drawback of this method is that this particular bit position must be sent with the frame (and should be balanced as well) for the receiver to know how to reconstruct the original frame. This will add a relatively important number of bits for small frames. For large frames, the number of added bits is less important, but the RD could reach high values inside the frame before going back to zero. Other Knuth-based methods were proposed, but as far as we know, they did not solve the high overhead issue. The simplest and the lowest overhead method is the polarity-bit coding. It consist of systematically adding 1 bit to a frame of a specific size to indicate whether it is inverted or not depending on the Cumulated RD (CRD) and the RD of the frame itself; i.e. if the CRD is positive, and the RD of the frame is positive as well, all the bits inside the frame will be inverted and the polarity bit will transmit the info to the receiver.

The polarity bit coding is used by the 64b/67b encoding; 3 bits are added to the 64 bits of the frame: 2 bits ('10b' or '01b') to ensure a transition and indicate whether the frame is raw data or control, and 1 polarity bit to indicate if the 64 bits (which are scrambled) are inverted or not. The CRD bound ensured by such coding could be deduced from the worst case scenario according to equation (3.1):

$CRD_{bound} = +/- (FrameSize + FrameSize/2)$  (3.1) Which gives for the 64b/67b encoding  $CRD_{bound} = +/-$  96 for FrameSize = 64. The overhead cost for the CRD bound is 1/64 = 1.56 %. The total overhead cost is 3/64 = 4.687 %.

#### **3.3.6** Summary of some existing encoding methods

| Line Coding                                          | Standards         | Max RL | <b>RD Bound</b> | Overhead    |  |  |

|------------------------------------------------------|-------------------|--------|-----------------|-------------|--|--|

| Bit Stuffing                                         | CAN               | 5      | N/A             | 0% to 20%   |  |  |

|                                                      | USB 2.0           | 6      | N/A             | 0% to 16.6% |  |  |

| 8b/10b                                               | PCIe 2.0, USB 3.0 | 5      | +/- 3           | 25 %        |  |  |

| Scrambling-Based codings                             |                   |        |                 |             |  |  |

| 64b/66b                                              | 10G Ethernet      | 64     | N/A             | 3.125 %     |  |  |

| 128b/130b                                            | PCIe 3.0          | 128    | N/A             | 1.562 %     |  |  |

| 128b/132b                                            | USB 3.1           | 128    | N/A             | 3.125 %     |  |  |

| Scrambling + polarity bit based coding               |                   |        |                 |             |  |  |

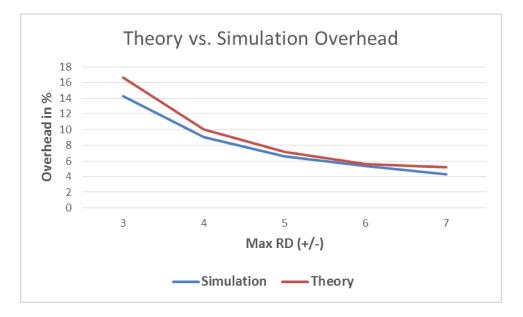

| 64b/67b                                              | Interlaken        | 64     | +/- 96          | 4.687 %     |  |  |