### Analyzing the memory behavior of parallel scientific applications

David Beniamine

### ▶ To cite this version:

David Beniamine. Analyzing the memory behavior of parallel scientific applications. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Grenoble Alpes, 2016. English. NNT: 2016GREAM088. tel-01681008v2

### HAL Id: tel-01681008 https://theses.hal.science/tel-01681008v2

Submitted on 11 Jan2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Communauté UNIVERSITÉ Grenoble Alpes

### THÈSE

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministérial :

### Présentée par David Beniamine

Thèse dirigée par **Bruno Raffin** et codirigée par **Guillaume Huard**

préparée au sein LIG et de EDMSTII

# Analyzing the memory behavior of parallel scientific applications

Thèse soutenue publiquement le 5 décembre 2016 devant le jury composé de :

Pr, Martin Quinson

Professor at ENS Rennes, Président

Pr, Jesús Labarta Mancho

Professor at Universitat Politècnica de Catalunya, Rapporteur

Pr, Raymond Namyst

Professor at University of Bordeaux, Rapporteur

Dr, Lucas M. Schnorr

Associate professor at Institute of Informatics of the Federal University of Rio Grande do Sul, Examinateur

Pr, Bruno Raffin

Professeur at INRIA Grenoble, Directeur de thèse

Dr, Guillaume Huard

Associate professor at Grenoble Alpes University, Co-Directeur de thèse

### Acknowledgments

I first would like to thank the members of my jury for the time they spent on my work and for their helpful remarks.

I would like to thank all the members of the Informatica team of Porto Alegre for welcoming me there. Especially Mathias and Marcos, I enjoyed working with you guys, it has been a great experience.

Eu gostaria de agradecer todos os meus colegas em Porto Alegre que me receberam de braços abertos e fizeram da minha estadia um período inesquecível. Dentre outros, gostaria de agradecer todos os moradores do condomínio Riachuelo e os visitantes regulares pelos momentos divertidos e discussões interessantes. And thank you Fernando for the translation.

Je tiens à remercier tous les membres présents et passés des équipes Polaris/Moais/Datamove/Mescal, travailler avec vous à été très enrichissant, scientifiquement comme humainement. Et surtout merci à Annie Simon et Christine Guimet qui plus d'une fois ont rattrapé mes bêtises administratives. Je voudrais aussi remercier les enseignants de l'UFR IM2AG qui m'ont motivé à pousser les études jusqu'à la thèse et ont continué à suivre mon évolution, en particulier Anne Rasse. Dans un autre registre, tous les coincheur.euse.s grâce à qui les pauses midi finissent souvent en fou rire et concours de mauvaise foi. Tous mes co-bureaux même temporaires qui ont rendu les heures de déprime de rédaction ou de debug supportables et souvent même agréables. Plus particulièrement Raphaël (avec ou sans son genou) et Alexis pour tous les interminables débats mi-Trolls mi-sérieux et les croissants du lundi. Swann qui rentre à la fois dans toutes ces catégories et dans aucune, et sans qui je n'aurais peut-être pas atterri dans ce laboratoire. Enfin je voudrais remercier mes encadrants et surtout Guillaume pour ces 5 années durant lesquelles il m'a accompagné et encouragé dans mon travail, qu'il s'agisse de la thèse ou d'autres projets, toujours avec beaucoup d'humour, parfois même sur un vélo ou derrière un verre (heureusement jamais les deux à la fois). Bref j'ai eu de la chance d'avoir un aussi bon encadrant<sup>1</sup>, j'espère vraiment que nous continuerons à travailler ensemble.

Je voudrais finalement remercier tou.te.s mes ami.e.s qui depuis des années me supportent avec tous mes défauts et sont toujours présent malgré tout. Tous les sportifs occasionnels ou réguliers, sans nos sorties vélo, via, rando, etc. je serais probablement devenu fou. Parmi eux je tiens à remercier spécifiquement Seb pour sa capacité à transformer n'importe quelle "petite sortie d'une heure" en aventure, parfois en y laissant une roue, des sacoches ou carrément un genou (encore un). Je tiens aussi à remercier mes parents et Sacha pour avoir subi mon incapacité à organiser ma vie hors de la thèse sans jamais se plaindre ni m'en tenir rigueur mais aussi pour leurs encouragements. Enfin, Flo, je ne peux pas imaginer ce qu'auraient été ces dernières années ni comment aurait fini cette thèse sans toi, je ne peux pas non plus te dire tout ce pour quoi je veux te remercier sans doubler (au minimum) la taille de ce manuscrit, alors je dirais juste: "thanks for all the fish" (mais pas "so long", bien au contraire).

$<sup>^1</sup>$  "le mauvais encadrant, il voit un thésard, il l'encadre, alors que le bon encadrant, il voit un thésard, il l'encadre, mais c'est un bon encadrant $\ldots$ "

### Abstract

Since a few decades, to reduce energy consumption, processor vendors builds more and more parallel computers. At the same time, the gap between processors and memory frequency increased significantly. To mitigate this gap, processors embed a complex hierarchical caches architecture. Writing efficient code for such computers is a complex task. Therefore, performance analysis has became an important step of the development of applications performing heavy computations.

Most existing performance analysis tools focuses on the point of view of the processor. Theses tools see the main memory as a monolithic entity and thus are not able to understand how it is accessed. However, memory is a common bottleneck in High Performance Computing (HPC), and the pattern of memory accesses can impact significantly the performance. There are a few tools to analyze memory performance, however theses tools are based on a coarse grain sampling. Consequently, they focus on a small part of the execution missing the global memory behavior. Furthermore, these coarse grain sampling are not able to collect memory accesses patterns.

In this thesis we propose two different tools to analyze the memory behavior of an application. The first tool is designed specifically for Non-Uniform Memory Access (NUMA) machines and provides some visualizations of the global sharing pattern inside each data structure between the threads. The second one collects fine grain memory traces with temporal information. We can visualize theses traces either with a generic trace management framework or with a programmatic exploration using R. Furthermore we evaluate both of these tools, comparing them with state of the art memory analysis tools in terms of performance, precision and completeness.

# Résumé

Depuis plusieurs décennies, afin de réduire la consommation énergétique des processeurs, les constructeurs fabriquent des ordinateurs de plus en plus parallèles. Dans le même temps, l'écart de fréquence entre les processeurs et la mémoire a significativement augmenté. Pour compenser cet écart, les processeurs modernes embarquent une hiérarchie de caches complexe. Développer un programme efficace sur de telles machines est une tâche difficile. Par conséquent, l'analyse de performance est devenue une étape majeure lors du développement d'applications exécutant des calculs lourds.

La plupart des outils d'analyse de performances se concentrent sur le point de vue du processeur. Ces outils voient la mémoire comme une entité monolithique et sont donc incapables de comprendre comment elle est accédée. Cependant, la mémoire est une ressource critique et les schémas d'accès à cette dernière peuvent impacter les performances de manière significative. Quelques outils permettant l'analyse de performances mémoire existent, cependant ils sont basés sur un échantillonnage à large grain. Par conséquent, ces outils se concentrent sur une petite partie de l'exécution et manquent le comportement global de l'application. De plus, l'échantillonnage à large granularité ne permet pas de collecter des schémas d'accès.

Dans cette thèse, nous proposons deux outils différents pour analyser le comportement mémoire d'une application. Le premier outil est conçu spécifiquement pour pour les machines NUMA (Not Uniform Memory Accesses) et fournit plusieurs visualisations du schéma global de partage de chaque structure de données entre les flux d'exécution Le deuxième outil collecte des traces mémoires à grain fin avec information temporelles. Nous proposons de visualiser ces traces soit à l'aide d'un outil générique de gestion de traces soit en utilisant une approche programmatique basé sur le langage R. De plus nous évaluons ces deux outils en les comparant à des outils existant de trace mémoire en terme de performances, précision et de complétude.

## Résumé étendu

Les scientifiques de toute les disciplines utilisent des ordinateurs pour faciliter leurs calculs et exécuter des simulations afin de tester leurs hypothèses. Plus la science avance, plus ces simulations deviennent complexes, les scientifiques ont donc toujours besoin de plus de capacité de calcul. Pour augmenter la capacité de calcul de leurs processeurs, les constructeurs ont dans un premier temps augmenté la fréquence de ces derniers. Cependant cette approche a vite été stoppée par plusieurs limites physiques. Afin de contourner ces limites, les constructeurs se sont mis à concevoir des processeurs parallèles.

La première limite provient de l'énergie nécessaire pour augmenter la fréquence d'un processeur. En effet, d'après Intel, augmenter la fréquence d'un processeur de 20 % n'augmente les performances que d'un facteur 1.13 mais requière 1.73 fois plus d'énergie. A l'opposé, utiliser un processeur identique mais avec deux cœurs de calculs au lieu d'un en diminuant la fréquence de ce dernier de 20 %, permet d'obtenir 1.73 fois plus de performances pour uniquement 1.02 fois plus d'énergie. La deuxième limite est la vitesse de la lumière : en effet les données doivent transiter de la mémoire jusqu'au processeur et ne peuvent pas se déplacer plus vite que la lumière. Si cette limite peut paraître élevée, elle a déjà été atteinte. En effet si nous voulons construire une machine séquentielle capable de traiter 1 To de données par seconde, du fait de cette limite, il faudrait faire tenir 1 To dans une aire de  $0.3 \,\mathrm{mm}^2$ , ce qui signifie que 1 bit occupe uniquement  $0.1 \,\mathrm{nm}$ , la taille d'un petit atome.

Si ces processeurs parallèles sont en théorie plus puissants que les séquentiels, les utiliser efficacement est bien plus complexe et relève de la responsabilité des développeur.euse.s. De plus, depuis plusieurs années nous sommes face à une troisième limite physique. Nous somme capable de réduire la taille des transistors, donc d'augmenter le nombre de transistors sur une puce. Cependant, plus de transistors signifie plus de chaleur et la quantité de chaleur qu'une puce peut produire avant que des effets indésirables tel que des courants de fuites se produisent. De ce fait, les constructeurs font désormais des machines avec plusieurs puces (processeurs), chacune étant composée de plusieurs cœurs.

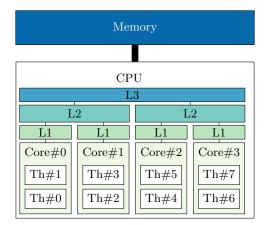

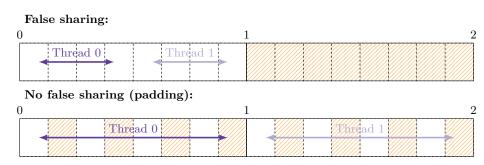

Dans le même temps, les processeurs sont devenus significativement plus rapides que la mémoire; pour palier à cet écart, ils embarquent des petites mémoires cache. Ces caches sont conçus pour tirer profit de deux schémas d'accès communs à la plupart des programmes : la localité spatiale et temporelle qui correspond respectivement au fait d'accéder à des données proches et d'accéder plusieurs fois aux mêmes données dans un temps restreint. Une des choses qui rend ces caches plus rapides que la mémoire est leur taille, plus ils sont petits, plus il est rapide d'y trouver une donnée. C'est pourquoi les processeurs embarquent plusieurs niveaux de cache (en général trois). Le premier est très petit et rapide, quelques kilo octets, et conçu pour des accès très proches (boucles sur un tableau), le dernier plus grand et lent, environ 10 Mo, et conçu pour des accès plus espacés. Comme les processeurs sont multi-cœurs, ces caches sont organisés hiérarchiquement, le dernier niveau est partagé par tous les cœurs, et chaque cœur a accès à un cache de niveau 1 privé. Cette hiérarchie permet d'isoler les données privées et de tirer profit des partages correctement structurés; de plus cela réduit la bande passante nécessaire entre les caches. Pour des raisons similaires, les ordinateurs comportant plusieurs processeurs ont une organisation mémoire non uniforme (NUMA) ce qui signifie que chaque puce a un accès privilégié à une sous-partie de la mémoire. Par conséquent, les schémas d'accès à la mémoire d'une application peuvent avoir un impact significatif sur ses performances.

En fin de compte, écrire un programme efficace nécessite de prendre en compte l'architecture de la machine qui va l'exécuter, les schémas d'accès et leur adéquation, même si le programme est séquentiel. Bien qu'il y ait des règles générales : privilégier les accès séquentiels, travailler sur des petits ensembles de données, cette tâche est extrêmement complexe même pour des spécialistes de calcul haute performance (HPC). Les outils d'analyse de performances sont donc extrêmement utiles pour comprendre et optimiser les performances d'une application.

La première étape lors de l'optimisation des performances d'une application consiste à identifier les points chauds, c'est à dire les parties du code qui sont inefficaces et comprendre la nature des erreurs qui entrainent cette inefficacité. C'est uniquement après cette étape qu'il est possible de décider quelle partie du code peut être améliorée et comment. Il existe de nombreux outils conçus pour analyser les performances d'une application [Pillet et al., 1995, Browne et al., 2000, Shende and Malony, 2006, Treibig et al., 2010, Adhianto et al., 2010], la plupart d'entre eux utilisent les compteurs de performances pour collecter la trace d'une application. Ces compteurs sont des registres processeurs dédiées à l'analyse de performances,

Dans cette thèse nous avons mené une étude de cas sur l'analyse de performance d'un outil de simulation physique : Simulation Open Framework Architecture (Sofa). Afin d'analyser les performances de cette application, nous avons utilisé "Like I Knew What I am Doing" (Likwid) [Treibig et al., 2010], un outil classique d'analyse de performances, et nous avons tracé plusieurs métriques concernant l'utilisation de la mémoire. Avec cet outil nous avons été capable de détecter des problèmes de performances liés à la mémoire, mais il était impossible de trouver leur position dans la mémoire et les schémas responsable des mauvaises performances. En effet, si ces compteurs peuvent s'avérer très utiles, ils voient la mémoire comme une entité monolithique ce qui n'est pas le cas pour les architecture récentes. Par conséquent, des outils spécifiques doivent être utilisés pour analyser les performances du point de vue de la mémoire.

Analyser les performances d'une application au regard de la mémoire soulève deux défis techniques : le premier est la collecte de la trace elle-même. C'est une tâche compliquée car il n'existe pas de matériel comparable aux compteurs de performances pour tracer les accès mémoire. De plus, chaque instruction d'un programme déclenche au moins un accès mémoire : collecter chaque accès mémoire d'une application n'est donc pas possible. Par ailleurs, l'absence de matériel pour tracer les accès mémoire implique qu'un outil de collection peut facilement devenir envahissant et modifier significativement le comportement de l'application analysée. Le deuxième défi technique consiste à présenter la trace de manière simple et compréhensible. En effet, les traces mémoire sont extrêmement complexes puisqu'elles sont étalées sur cinq dimensions : le temps, l'espace d'adressage, la localité processeur, les flux d'exécution et le type d'accès. De plus, certaines de ces dimensions ne sont pas triviales à représenter, par exemple l'espace d'adressage peut être physique ou virtuel, et la localité processeur est organisée de manière hiérarchique. Finalement, les outils d'analyse mémoire doivent extraire les données pertinentes et les présenter de manière compréhensible.

Un outil idéal d'analyse mémoire devrait être capable de présenter les schémas d'accès mémoire d'un programme à ses développeur.euse.s, en incluant des informations concernant le partage de données entre flux d'exécution et la localisation des accès sur l'architecture de la machine. De plus, un tel outil devrait mettre en avant les schémas inefficaces.

Plusieurs outils ont été conçus dans le but d'analyser les performances mémoire [Lachaize et al., 2012, Liu and Mellor-Crummey, 2014, Giménez et al., 2014], cependant la plupart d'entre eux collectent la trace à l'aide de la technique d'échantillonnage d'instructions. L'échantillonnage d'instructions est une technique assistée par le matériel, qui permet de tracer certaines instructions à une fréquence[Drongowski, 2007, Levinthal, 2009] définie. Si cette méthode permet de collecter rapidement une trace, elle manque la plupart de l'espace d'adressage. De ce fait, il est impossible de visualiser les schémas d'accès mémoire à partir de la trace collectée.

### Contributions

Dans cette thèse, nous proposons deux outils pour analyser le comportement mémoire d'une application. Notre premier outil, nommé Tool for Analyzing the Behavior of Applications Running on NUMA ArChitecture (Tabarnac), collecte des traces globales de l'utilisation de la mémoire sans informations temporelles et présente une vue d'ensemble des schémas de partage à l'intérieur des structures de données entre les flux d'exécution. Le deuxième, nommé Memory Organisation Cartography & Analysis (Moca), collecte des traces mémoire génériques à grain fin, avec informations temporelles. Nous proposons deux approches différentes pour visualiser les traces collectées par Moca, la première est basée sur FrameSoc, un outil existant d'analyse de gestion de traces, la deuxième approche est basée sur une exploration programmatique utilisant le langage R. Conduire une campagne d'expérience en informatique peut être extrêmement simple, mais le faire de manière reproductible requiert davantage de planification et de méthodologie. L'analyse de performances, qu'elle soit conduite dans le but d'optimiser une application ou pour évaluer un outil requiert une campagne d'expériences complète. Dans cette thèse, nous avons porté une attention particulière à rendre nos expériences aussi reproductibles que possible. Dans ce but, nous décrivons clairement notre méthodologie expérimentale et distribuons tous les fichiers requis afin de reproduire chaque étape des expériences présentées.

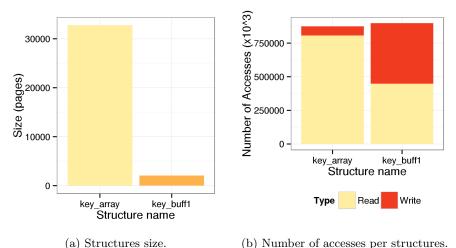

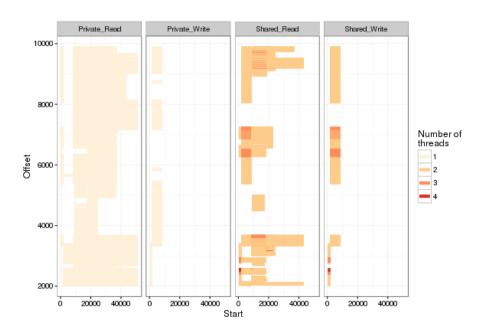

#### Vue d'ensemble des schémas de partage

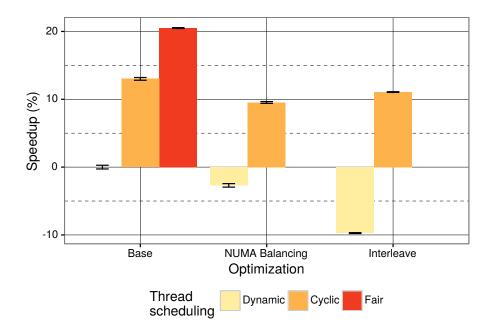

Nous avons conçu Tabarnac afin d'analyser les schémas de partage d'applications s'exécutant sur des machines NUMA. Cet outil est basé sur une instrumentation binaire légère pré-existante, elle-même basée sur la bibliothèque Pin d'Intel. Cette instrumentation compte le nombre d'accès de chaque flux d'exécution à chaque page mémoire d'une application. Nous avons ajouté à cette bibliothèque la capacité de retrouver des informations contextuelle afin d'associer les adresses mémoire à des structures de données (statiques ou allouées). De plus, nous avons conçu plusieurs visualisations simples et compréhensibles pour les traces collectées. En utilisant ces visualisation, nous avons pu identifier des problèmes d'utilisation mémoire et augmenter de 20 % les performances d'une application de test largement étudiée.

Ces résultats ont été publiés dans un article à Visual Performance Analysis (VPA) 2015, un séminaire de Super Computing [Beniamine et al., 2015b]. De plus, Tabarnac est distribué en tant que logiciel libre sous la licence General Public License (GPL) : https://github.com/dbeniamine/Tabarnac. Ce travail est le fruit d'une collaboration avec M. Diener et P.O.A Navaux de l'équipe informatica de l'Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Bresil, financé par CAMPUS France.

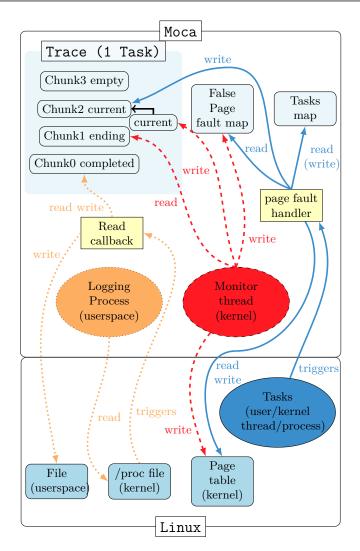

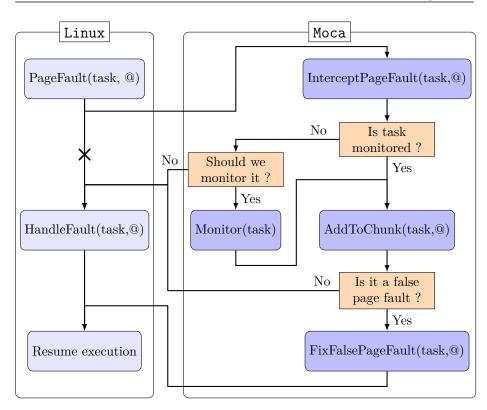

#### Collecte de traces mémoires à grain fin

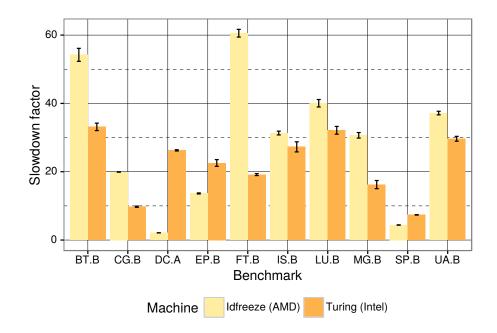

Moca est notre contribution principale. Cette outil est basé sur un module noyau Linux pour collecter efficacement des traces mémoires à grain fin. Ce module noyau intercepte les défauts de pages, qui sont déclenchés par le processeur et gérés par le système d'exploitation, afin de tracer les accès mémoire. Comme ces défauts de pages n'ont pas lieu fréquemment, il injecte aussi périodiquement de faux défauts de pages. De plus nous avons porté notre bibliothèque qui trace les structures de données dans Moca en s'affranchissant de sa dépendance à Pin. Nous avons aussi exécuté une campagne expérimentale approfondie, comparant Moca à Tabarnac ainsi que deux outils existants de collecte de traces mémoire, en termes de surcout, précision et complétude.

Ce travail est le sujet de deux rapport de rechercher Inria [Beniamine et al., 2015a, Beniamine and Huard, 2016] et a été soumis à Cluster, Cloud and Grid Computing (CCGRID) 2017. Comme l'outil précédent, Moca est distribué sous licence GPL : https://github.com/dbeniamine/Moca.

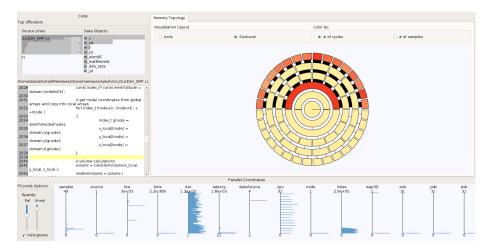

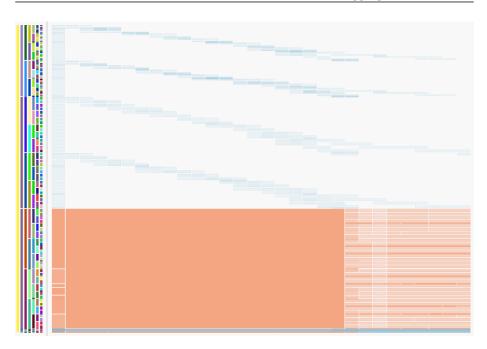

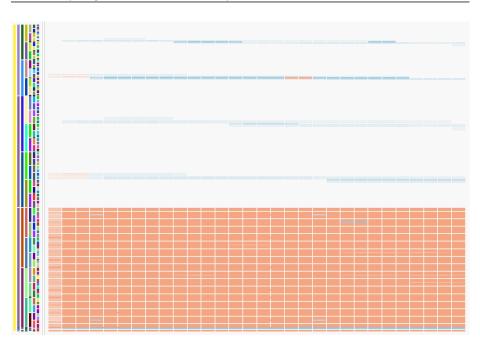

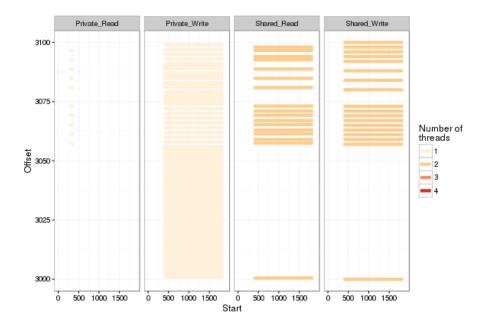

#### Analyse de traces mémoires à grain fin

Nous proposons deux approches différentes pour visualiser les traces de Moca. La première est basée sur un outil générique de gestion et d'analyse de traces : FrameSoc [Pagano and Marangozova-Martin, 2014]. Plus particulièrement, elle repose sur Ocelotl [Dosimont et al., 2014], un outil FrameSoc qui agrège les parties similaires de la trace et présente une vue globale simplifiée qui met en avant les anomalies. Avec cet outil nous avons pu identifier des schémas inefficaces en mémoire connus sur une application de test. Cependant nous avons rencontré plusieurs problèmes de passage à l'échelle dus à la représentation générique de la trace dans FrameSoc.

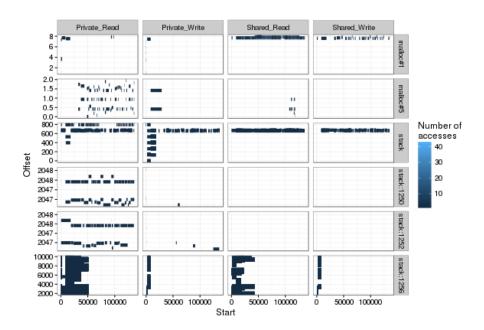

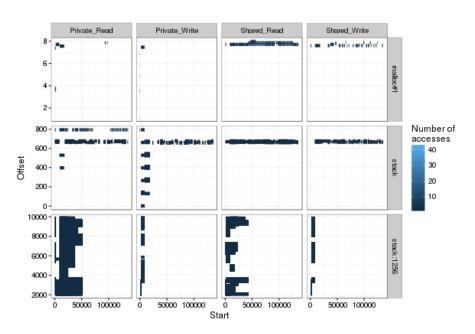

Afin de dépasser ces limites, nous avons aussi exploré plusieurs traces Moca avec une approche programmatique utilisant le langage R. Cette approche permet d'utiliser des filtres et zooms avancés, et de concevoir des visualisations spécifiques pour chaque trace. Avec cette méthode, nous avons pu analyser des traces plus complexes et détecter des comportements mémoires inconnus et intéressants. Afin d'être reproductibles, ces analyses sont sauvées et versionnées dans un cahier de laboratoire publiquement accessible sur github : https://github.com/dbeniamine/Moca\_visualization.

### Organisation de cette thèse

Cette thèse est organisée de la manière suivante : dans le chapitre 2, nous présentons une étude de cas sur l'analyse de performances de Sofa, un outil de simulation physique. Ce chapitre commence par présenter Sofa, ses spécificités ainsi que les tentatives précédentes de l'optimiser et souligne le besoin d'analyser les performances de Sofa. Ensuite, nous discutons des outils génériques d'analyse de performances existants et notre méthodologie expérimentale. Cette étude de cas met en avant le besoin d'outils spécifiques pour l'analyse de performance du point de vue de la mémoire. Dans le chapitre 3, nous présentons certaines spécificités des architectures mémoires récentes, des problèmes de performances classique liés à l'utilisation de la mémoire et des façons de les contourner. Puis nous traitons des outils d'analyse de performances mémoire existants, de leurs limites et ce que l'on attendrais d'un outil idéal. Après cela nous présentons Tabarnac, notre première contribution, dans le chapitre 4. Nous présentons sa conception et son utilisation, évaluons son surcout et finalement présentons des optimisations de performances réalisées grâce à la connaissance acquise en analysant des traces produite par Tabarnac. Dans le chapitre 5, nous décrivons notre contribution principale : Moca. Nous expliquons d'abord en détail les mécanismes utilisés par Moca, sa conception interne et comment il répond aux défis soulevés par la collecte de traces mémoire à grain fin. Puis, nous proposons une analyse expérimentale approfondie comparant Moca à deux outils existants de collecte de traces mémoires ainsi qu'à Tabarnac en termes de performances, précision et complétude. Le chapitre 6 traite de la visualisation des traces de Moca. Nous présentons d'abord FrameSoc et Ocelotl puis les résultats obtenus avec ces outils. Après cela nous proposons une approche programatique et présentons les visualisations obtenues avec cette approche. Enfin nous tirons nos conclusions et proposons des perspectives de travail futures dans le chapitre 7.

# Outline

| Acknowledgments |                                                |                                                                                               |                        |  |  |

|-----------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|--|--|

| A۱              | Abstract · · · · · · · · · · · · · · · · · · · |                                                                                               |                        |  |  |

| Re              |                                                |                                                                                               |                        |  |  |

| Re              | ésum                                           | é étendu                                                                                      | xi                     |  |  |

| I               |                                                | Introduction                                                                                  | 3                      |  |  |

|                 | $1.1 \\ 1.2$                                   | Contributions                                                                                 | $\frac{6}{7}$          |  |  |

| Π               |                                                | Case Study                                                                                    | 11                     |  |  |

|                 | 2.1<br>2.2<br>2.3<br>2.4                       | Motivations          Profiling tools          Experimental methodology          SOFA Analysis | $12 \\ 15 \\ 16 \\ 25$ |  |  |

| III             |                                                | Memory Performance Analysis                                                                   | <b>31</b>              |  |  |

|                 | $3.1 \\ 3.2 \\ 3.3$                            | Architectural considerations                                                                  | 32<br>39<br>43         |  |  |

| IV              |                                                | Collecting and Analyzing Global Memory Traces                                                 | 45                     |  |  |

|                 | 4.1                                            | Design                                                                                        | 46                     |  |  |

|                 | $4.2 \\ 4.3$ | Experimental validation                       | $50 \\ 57$                                |  |

|-----------------|--------------|-----------------------------------------------|-------------------------------------------|--|

| V               |              | Collecting Fine Grain Memory Traces           | 61                                        |  |

|                 | 5.1          | Moca components                               | 62                                        |  |

|                 | 5.2          | Background knowledge                          | 63                                        |  |

|                 | 5.3          | Design                                        | 63                                        |  |

|                 | 5.4          | Experimental validation                       | 70                                        |  |

|                 | 5.5          | Conclusions                                   | 78                                        |  |

| V               | [            | Analyzing Fine Grained Memory Traces          | 81                                        |  |

|                 | 6.1          | Interactive visualization of aggregated trace | 82                                        |  |

|                 | 6.2          | Programmatic exploration                      | 90                                        |  |

|                 | 6.3          | Conclusions                                   | 96                                        |  |

| VII             |              | Conclusions and perspectives                  | 99                                        |  |

|                 | $7.1 \\ 7.2$ | Contributions                                 | $\begin{array}{c} 100 \\ 101 \end{array}$ |  |

| Contents        |              |                                               |                                           |  |

| List of Figures |              |                                               |                                           |  |

| List of Tables  |              |                                               | 113                                       |  |

| Acronyms        |              |                                               | 115                                       |  |

| Glossary        |              |                                               | 119                                       |  |

| Bibliography    |              |                                               | 125                                       |  |

# Chapter I

# Introduction

### Contents

| 1.1 Contributions                                    | 6 |

|------------------------------------------------------|---|

| 1.1.1 Global overview of the memory sharing patterns | 6 |

| 1.1.2 Fine grain memory traces collection            | 6 |

| 1.1.3 Fine grain memory traces analysis              |   |

| 1.2 Thesis organization                              | 7 |

Scientists from all fields use computers to ease their calculations and run simulations to test their hypothesis. These simulations are more and more complex as science advances and therefore requires always more computing power. In a first time, computer vendors increased this power by increasing the frequency of their Central Processing Units (CPUs), but this approach reached quickly several hard physical limits. To overpass them, they started to build parallel processors.

The first limit comes from the energy required to increase the frequency of a CPU. Indeed, according to Intel [Ganesan, 2016], over-clocking a processors by 20% only increase the performance by a factor 1.13 but requires 1.73 times more energy. At the opposite, using an identical processor with two cores instead of one with a frequency 20% lower provides 1.73 times more performance for only 1.02 times more energy. The second limit is the speed of light: data have to travel from memory to the CPU and cannot go faster than the speed of light. While this limit may seem high, we have already reached it. Indeed, if we want to build a sequential machine able to process 1 TByte of data per second, due to this limit it would require to stick 1 TByte of data on an area of  $0.3 \,\mathrm{mm}^2$  which mean that 1 bit occupies only 0.1 nm, the size of a small atom.

While these parallel processors are theoretically more powerful than sequential ones, it is way more complex to use them efficiently and it is the responsibility of the developer to do so. Moreover since a few years we are reaching yet another physical limitation. We are capable of reducing the size of transistors, hence increasing the number of transistors in a chip. Still, more transistors means more heat, and there is a maximum of heat that an area can produce before unexpected effects such as leakage occurs. As a result, vendors are now building machines with several sockets, each one embedding several cores.

At the same time, processors became significantly faster than memory, thus, CPUs embed small caches memory to limit the impact of this gap on performance. Theses caches are designed to benefit from two patterns that occurs in most programs: spacial and temporal locality, which respectively means using data close in memory and using several times the same data in a short time lapse. One of the things that makes the caches faster than the main memory is their size, the smaller they are, the faster it is to access them. Therefore CPUs embed several level of caches (usually three), the first level is very fast and small few kilo bytes and designed for very close accesses (loop on an array), while the last level is bigger and slower, about 10 MBytes and designed for more distant accesses. As the CPUs embed several cores, theses caches are organized hierarchically, the last level is shared by all cores while each core has a private access to a level one cache. This hierarchy helps isolating private data and benefit from well structured sharing, moreover it reduces the required bandwidth in the caches. For similar reasons, computers with several sockets have a Non-Uniform Memory Access (NUMA) which means that each socket has a privileged access to a subpart of the memory. Consequently, the memory access patterns of an application can significantly impact its performance [Drepper, 2007]. Indeed, four threads working on small and separate piece of data will benefit from their private caches while patterns such as all to all sharing will result in a lot of conflicts in the caches. Moreover, if some sharing occurs between threads that are close in this hierarchy, the shared caches will contain shared data and one thread will benefit from the accesses of the other. At the opposite, if theses threads are far in the hierarchy, the sharing will generate some noise and maybe

some contention on the memory bus.

In the end, writing an efficient program requires to consider the architecture of the computer that will run it, and the patterns, and their matching, even if the program is sequential. Although there are some general rules: privileging sequential accesses, working on small set of data, this task is extremely complex, even for High Performance Computing (HPC) specialists, as every accesses matters. Thus, performance analysis tools are extremely helpful to understand and optimize the performance of any application.

The first step to optimize the performance of an application is to find the hotspots, which means the parts of code that are inefficient and understand their nature. Only at this point it is possible to decide what part of code should be improved and how. There are many tools designed to analyze the performance of an application [Pillet et al., 1995, Browne et al., 2000, Shende and Malony, 2006, Treibig et al., 2010, Adhianto et al., 2010] most of them rely on performance counters to collect a trace of the application. These are CPU register dedicated to performance analysis which enable efficient collection of performance data.

In this thesis we ran a case study on the performance analysis of a physical simulation framework: Simulation Open Framework Architecture (Sofa). To analyze the performance of this application, we used "Like I Knew What I am Doing" (Likwid) [Treibig et al., 2010], a classical performance analysis tool and traced several metrics concerning the memory usage. With this tool we are able to detect memory related performance issues and guess the nature of some of them, but it was impossible to spot their location on the memory and the patterns responsible for the bad performance. Indeed, if these counters can be very useful, they consider the memory as a monolithic entity which is not the case on recent architecture. Thus, specific tools should be used for analyzing performance in view of memory.

Analyzing an application performance in view of the memory raises two challenges: the first one is the collection of the trace itself. This is a complex task as there is no hardware comparable to the performance counters for tracing memory accesses. Furthermore, every instructions of a program triggers at least one memory access, thus, collecting every single memory accesses of an application is not possible. Additionally, due to the lack of hardware tracing, a memory collection tool might easily become invasive and significantly change the behavior of the analyzed application. The second challenge is the presentation of the trace. Indeed, memory traces are extremely complex as they are spread over five dimensions: time, address space, CPU location, threads and access type. Furthermore, some of these dimensions are not trivial to represent, for instance the address space can be virtual or physical and the CPU location is organized hierarchically. In the end, memory analysis tools have to extract pertinent data and present them in an understandable way.

An ideal memory analysis tool should be able to present the memory access patterns of a program to its developer, including information about data sharing between threads and the location of the access on the machine architecture. Furthermore, such tool should highlight inefficient patterns.

Several tools were designed for memory performance analysis [Lachaize et al., 2012, Liu and Mellor-Crummey, 2014, Giménez et al., 2014], however most of them addresses the trace collection challenge by doing an instruction sampling. Instruction sampling is a hardware based technique that enable tracing some

instructions at a defined frequency [Drongowski, 2007, Levinthal, 2009]. While this method enables efficient tracing, it does not trace the whole memory space addressed. As a result, it is impossible to visualize memory patterns from the collected trace.

### **1.1** Contributions

In this thesis we propose two tools to analyze the memory behavior of an application. Our first tool, called Tool for Analyzing the Behavior of Applications Running on NUMA ArChitecture (Tabarnac), collects global memory traces without temporal information and presents an overview of the sharing patterns inside the data structures, between the threads of the execution. The second one, called Memory Organisation Cartography & Analysis (Moca), collects generic, fine grained memory traces with temporal information. We propose two approaches to visualize Moca traces, the first one is based on FrameSoc an existing generic trace analysis framework, while the second one relies on a programmatic exploration using R.

Conducting experiments in computer science can be extremely simple, but doing it in a reproducible way requires more planning and methodology. Performance analysis, whether it is for optimizing an application or to evaluate a tool requires to do complete experimental campaigns. In this thesis, we take a particular attention at making our experiments as reproducible as possible. To do so, we clearly describe our experimental methodology and distribute the files required to reproduce each step of the presented experiments.

### 1.1.1 Global overview of the memory sharing patterns

We designed Tabarnac to analyze the memory sharing patterns of applications running on NUMA machines. This tool relies on an existing, lightweight binary instrumentation, based on the Intel Pin library, which counts how much each thread of an application accesses each page. We added to this library the capacity to retrieve contextual information to associate memory addresses to data structures (static and allocated). Moreover we designed several comprehensive visualizations of the collected traces. Using these visualizations we were able to identify some performance issues and improve the performance of the NAS Parallel Benchmarks (NPB), IS by 20 %.

These results were published in an article at Visual Performance Analysis (VPA) 2015 a Super Computing workshop [Beniamine et al., 2015b]. Furthermore Tabarnac is distributed as a free software under the General Public License (GPL): https://github.com/dbeniamine/Tabarnac. This work is the result of a collaboration with M. Diener and P.O.A Navaux from the Parallel and Distributed Processing Group (GPPD) of the Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Brazil, financed by CAMPUS France.

#### 1.1.2 Fine grain memory traces collection

Moca is our main contribution. This tool relies on a Linux kernel module to collect efficiently fine grain memory traces. This kernel module intercepts page faults, which are triggered by the hardware and handled by the Operating System (OS), to trace memory accesses. As these page faults does not occur frequently, it also injects periodically false page faults. It handles memory traces in the kernel space and flush them to userspace periodically. Moreover we incorporated our data structures tracking library in Moca without the dependency to Pin. Additionally we ran an extensive experimental comparison of Moca comparing it to Tabarnac and two state of the art memory analysis tools in terms of overhead, trace precision and completeness.

This work is the subject of two Inria research reports [Beniamine et al., 2015a, Beniamine and Huard, 2016] and has been submitted at Cluster, Cloud and Grid Computing (CCGRID) 2017. As the previous tool, Moca is distributed under the GPL license: https://github.com/dbeniamine/Moca.

#### 1.1.3 Fine grain memory traces analysis

We proposed two different approaches to visualize Moca traces. The first one is based on an existing general trace management and analysis framework called FrameSoc [Pagano and Marangozova-Martin, 2014]. More precisely, it relies on Ocelotl [Dosimont et al., 2014] a FrameSoc tool that aggregates similar parts of the trace and present a simplified overview highlighting anomalies. With this tool we were able to identify classical inefficient memory patterns on a test application. Nevertheless we encountered several scalability issues due to the generic representation of the trace inside the tool.

To overpass theses scalability issues, we also explored several Moca traces with a programmatic approach using R. This approach enables using advanced filtering and zooms, and to design specific visualization for each traces. With this method we were able to explore more complex traces and detect some interesting and unknown memory patterns. For reproducibility, these analysis are saved and versioned in a labbook publicly available at github: https://github.com/dbeniamine/Moca visualization.

### 1.2 Thesis organization

The remaining of this thesis is organized as follow: in Chapter 2 we present a case study on the performance analysis of Sofa, a physical simulation tool. This chapter first introduces Sofa, its specificities and previous attempts to optimize it, and highlight the need for performance analysis on Sofa. We then discuss the existing generic performance analysis tools and our experimental methodology. This case study emphasize the need for specific memory performance analysis tools. In Chapter 3, we introduce some specificities of recent memory architectures, usual memory performance issues and workarounds. Then we discuss the existing memory performance analysis tools, their limitations and what we would expect from an ideal tool. After that we present Tabarnac, our first contribution, in Chapter 4. We discuss its design and usage, evaluate its overhead and finally present some performance optimization done with the knowledge obtained thanks to Tabarnac. In Chapter 5, we describe our main contribution, Moca. We first explain in details the mechanisms used by Moca, its internal design and how it handles the challenges raised by fine grain memory trace collection. Then we provide an extensive experimental evaluation comparing Moca I – Introduction

to two state of the art memory analysis tools and Tabarnac. Chapter 6 discusses the visualization of Moca traces. We first introduce FrameSoc and Ocelotl and then discuss the results obtained with these tools. Then we propose a programmatic approach and present the visualizations and results obtained with it. Finally we draw our conclusions and present some perspectives of future work in Chapter 7

# Chapter II

# Case Study

### Contents

| 2.1 Motivations                                    | 12        |

|----------------------------------------------------|-----------|

| 2.1.1 SOFA: a physical simulation framework        | 12        |

| 2.1.2 Previous efforts toward SOFA parallelization | <b>14</b> |

| 2.2 Profiling tools                                | 15        |

| 2.3 Experimental methodology                       | 16        |

| 2.3.1 Reproducible research                        | 16        |

| 2.3.2 Experimental workflow                        | <b>18</b> |

| 2.3.3 Methodology                                  | <b>20</b> |

| 2.4 SOFA Analysis                                  | <b>25</b> |

| 2.4.1 Experimental plan                            | <b>25</b> |

| 2.4.2 Results and discussion                       | <b>26</b> |

Optimizing a computational kernel is a complex task, which requires a deep understanding of both the algorithm mechanics and the machine that will execute it. Simple computational kernels such as matrix multiplication or Cholesky factorization have been subject of years of optimizations, yet some scientists still manage to improve them. The task is even more complex when it comes to optimizing a whole actual application. We first need to identify hotspots which means understand where and why the performance are suboptimal. Then we have to understand their nature and localization both in terms of code and data structure (if they are memory related). Finally, when optimizing a real life application, it is important to make the code modifications as clear as possible. Indeed not all developers are specialized in High Performance Computing (HPC) and a code is only maintainable if understandable.

Simulation Open Framework Architecture (Sofa) [Allard et al., 2007] is a simulation framework designed for exact and interactive physical simulation, it aims at assisting surgeons with real time medical simulation. Hence it cannot afford to improve its efficiency by relying on approximations. Therefore optimizing Sofa performance is crucial. Yet, most of the developers are not from the HPC community. To guide them into this optimization process, we need to analyze the performance of Sofa and identify precisely the hotspots.

In this chapter, we present a case study about the performance optimization of Sofa. This case study aims at demonstrating the usage of classical analysis tools and emphasize their limits concerning memory related performance issues. It is organized as follow: first we present Sofa, its specificities and previous attempt to parallelize or optimize it in Section 2.1. Then, we discuss the existing profiling tools that can be used to analyze the performance of application in Section 2.2. After that we detail our experimental methodology and discuss reproducibility matters in Section 2.3. Finally we present our analysis and first conclusions in Section 2.4.

### 2.1 Motivations

Several efforts were made to parallelize the different part of Sofa, using its specificities. Before discussing these efforts, we need to present more precisely the Sofa framework.

# 2.1.1 SOFA: a physical simulation framework

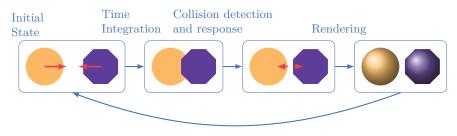

Figure 2.1 – The simulation loop.

In Sofa, simulation can be seen as a loop depicted in Figure 2.1: we start from an initial configuration were a set of objects are subject to a force field. The second step, called time integration, solves a system of equation to compute the next position of each object. At that point, some objects might be overlapping. Thus the third step consist in detecting these overlaps and applying repulsing forces to simulate the collision. Finally the result of these step is displayed (rendered) and we are back the beginning. The time integration and the collisions detection are the most costly steps. Hence many algorithms were developed to compute them efficiently, each algorithm being more appropriate for simulating one type of object depending on its form and stiffness.

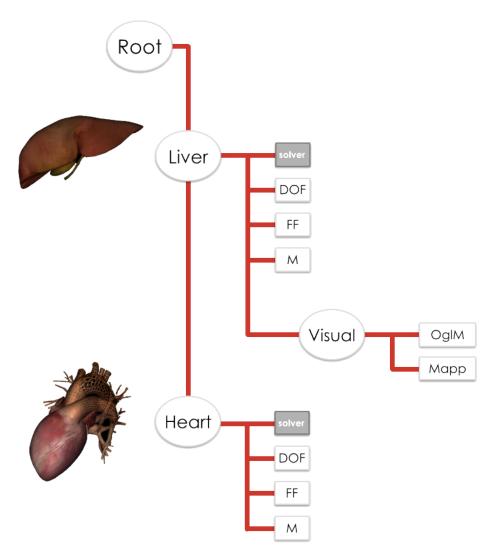

Figure 2.2 – SOFA representation of a scene with two objects: a liver and a heart. Each node of the scene can embed its own set of solvers and visual representations.

Image from SOFA documentation [SOFA, 2016].

One of Sofa main specificity is that it has a multi-model representation of each component. A simulation scene is represented as a tree, as shown in Figure 2.2 where each physical object is a node. Each level of the graph can embed solvers, collision detector and visual representation, overriding the defaults. This hierarchical representation enable dependencies management between objects and the representation of complex embedded objects [Nesme et al., 2009, Faure et al., 2011].

#### 2.1.2 Previous efforts toward SOFA parallelization

It is important to note that the main developers of Sofa are mostly computer scientists with a physical or medical background but not specialized in HPC. Several efforts were made by external developers to parallelize Sofa, most of these efforts consist in optimizing some algorithms which, according to Sofa developers, are time consuming. For instance, Everton Hermann proposed an efficient (sequential) collision detection algorithm based on ray tracing and a parallelization of this algorithm [Hermann et al., 2008]. More recently, Julio Toss has been developing several algorithms on Graphical Processing Units (GPUs) to improve the computation time of Voronoi diagrams [Toss and Comba, 2013, Toss et al., 2014]. Although their computation generates a considerable overhead before the simulation, these diagrams enable efficient simulation of forces propagation in heterogeneous materials [Faure et al., 2011]. Hence optimizing their computation is critical for Sofa.

E. Hermann also proposed a more global approach, exploiting the hierarchy of the scene tree, to parallelize the time integration step [Hermann et al., 2009]. This parallelization relies on the KAAPI runtime [Gautier et al., 2007] which consider an application as a set of tasks and dependencies between these tasks. Each task can provide one or several implementations (Central Processing Unit (CPU), GPU ...), the runtime choose online which implementation to use depending on the current performance, which results in portable performance. With this method, the amount of parallelism depends on the number of objects simulated. As most Sofa scenes only include a few objects, this parallelization is not suitable for them.

While this approach is more generic it was never actually used by Sofa developers for several reasons. First of all, they are not specialized in parallelism, hence not used to write programs in parallel languages. Second, KAAPI is a research runtime that evolve quickly, maintaining code based on it seemed to costly for them. Last but not least, while this approach helps to parallelize the code, it does not help finding hotspots and optimizing existing code. In the end, Sofa is currently parallelized using simple Open Multi-Processing (OpenMP) **#pragma**. These **#pragma** are compiler directives to tells the runtime that a region of code should be run in parallel. While adding such annotation to an existing code is trivial, it requires to spend some time at improving data structures and algorithms to obtain an efficient parallelization. This method impacts small chunks of code and miss the global aspect of the previous one. Thus it is considerably less efficient than the KAAPI version.

To conclude, it appears that optimizing algorithms or chunk of codes pointed out by Sofa developers is not sufficient. Indeed this approach can miss unknown hotspots and therefore opportunities for optimizations. Moreover, while the global, runtime based approach seems potentially more efficient than local optimizations, it does not overpass this limitation. At the end of the day, it appears that identifying precisely unknown hotspots and digging into Sofa performance would be more profitable than writing pieces of highly optimized code.

### 2.2 Profiling tools

Performance analysis consists of two steps: data collection and presentation. The first step aims at extracting as much pertinent information as possible from an execution. Nevertheless, observing an execution is not free: it takes time to count and record events. As a result, it can impact the application performance or, worst, modify its behavior. Consequently, any analysis provides a tradeoff between the amount of data collected and the impact on the monitored application. The second step is also challenging as the analysis tool has to to find out which data are pertinent and to present them in a meaningful way to the user. Many tools were designed to address one or both of these challenges.

Performance counters are dedicated CPU registers that were originally designed by vendors to debug their processor prototypes. They count events such as cache misses, or branch miss-predicts at a very low cost compared to software based solutions. They can directly be accessed using the Perf driver which is part of the Linux kernel since version 2.6.31. Yet, as a result of their initial aim, the available counters depends of the CPU model and vendor. Furthermore, it requires a deep knowledge of CPUs mechanisms to understand the meaning of some counters. Hence, higher level libraries such as Performance API (PAPI) [Browne et al., 2000, Malony et al., 2011, Weaver et al., 2013] and "Like I Knew What I am Doing" (Likwid) [Treibig et al., 2010] were designed to make performance counter access and interpretation more convenient. These libraries provide performance groups and automatically compute comprehensive metrics. In addition they provide markers that can be used in the code in order to collect counters only during some parts of the execution. This is useful once hotspots are identified, but can lead to miss a part of the execution if used too early.

Another approach to make performance counters more understandable consists in combining them with contextual informations. Such informations can be obtained by intercepting libraries calls (system calls, C standard library, Message Passing Interface (MPI), OpenMP ...). The easiest way to intercept a library call is by overriding it at runtime with the LD\_PRELOAD environment variable<sup>1</sup>. A second method is to rely on binary instrumentation libraries such as Intel Pin [Luk et al., 2005] or Dyninst from the Paradyn Project [Miller et al., 1995]. This method is more flexible and usually enable higher level data collection, but it is more intrusive, thus it can impact the behavior of the studied application. Simulators such as SimGrid [Casanova et al., 2014] can be used to overpass these limitations. However HPC simulators often focus on explicit communications (via MPI or OpenMP) discarding the actual computations. Hence they might miss memory related issues. Several tools such as HPCToolkit [Adhianto et al., 2010], PARAllel Visualization end Events Representation (PARAVER) [Pillet et al., 1995], Tunning and Analysis Utilities (TAU) [Shende and Malony, 2006], Modular Assembler Quality Analyzer

$<sup>^1</sup>$  One can use the LD\_PRELOAD environment variable to tell the linker to load a library before running a program. As a result, each call to a function from an external library overwritten in the preloaded library will be intercepted.

and Optimizer (MAQAO) [Djoudi et al., 2005], AMD CodeXL [AMD, 2016] (the successor of AMD CodeAnalyst [Drongowski, 2008]) and Intel VTune [Reinders, 2005] combine several of these methods to collect traces.

When it comes to presenting performance traces in a readable way, we can split these tools in three groups. The first ones only provides textual traces and let the user extract pertinent information from them. It includes the Perf driver, Likwid and PAPI library as well as several Pintools. Such tools are very useful for small applications as they do not require complex tools to be read. Moreover they are usually easy to parse and one can build more complex visualization on top of it using R, for instance. Tools from the second group, that includes VTune, CodeXL tries to present data in a more readable way. Usually their visualization consist in a set of tables and plots, where they highlight values that seem to be pertinent (for instance cache miss above a fixed threshold) pointing important parts to the user. Finally, while tools like MAQAO, HPCToolkit and PARAVER propose similar visualizations, but they also provide Application Programming Interfaces (APIs) to design new visualizations or import external traces. FrameSoc [Pagano et al., 2013, Pagano and Marangozova-Martin, 2014] is very similar to the previous tools, the main difference is that it is designed for trace management and analysis. Consequently it does not provide any way to collect traces but is able to import traces collected by the user. It describes them with a generic representation and enable easy navigation through different visualizations of the same trace.

To conclude, many tools were developed to monitor the performance of an application. The best tool depends on the kind of issues we are looking for and the application that is monitored. Most of the tools discussed here are based on performance counters and thus present data from the point of view of the CPU. In our specific case, we are studying a complex application, yet we are in contact with the developers of Sofa. Consequently they can give us hints about the important parts and the kind of issues we should look for. Therefore low level tools such as Likwid are well suited as they can both compute pertinent metrics and focus on specific parts of the application.

### 2.3 Experimental methodology

In computer science we can easily monitor our experiments and restart them quickly if something goes wrong. At the opposite, in other domains, such as biology, this reactivity is not possible, scientist are forced to write very precise protocols to avoid loosing large amounts of time and money. By inspiring ourselves from their protocols we could make our experiments reproducible and our research more trustable.

In this section we first introduce reproducibility and how people have tried to reach it in HPC, then, we present the methodology we have developed during this thesis to make our experiments as reproducible as possible.

#### 2.3.1 Reproducible research

Measurement bias, which means attributing a consequence to the wrong cause due to an issue in our measurement and analyze method, is a widely known phenomena in scientific communities and is analyzed in most fields. Mytkowicz et al. [Mytkowicz et al., 2009] highlighted several ways to introduce significant measurement bias in computer science experiments without noticing it. Its experiments showed that measurement bias is both commonplace and unpredictable in our field. Therefore, the easiest way to deal with this bias is to reproduce studies published by other teams in order to confirm or invalidate their results. Still, reproducing experiments in computer science, and more specifically in HPC, is not trivial.

A previous study [Collberg et al., 2015] tried to evaluate how reproducible the experiment presented in computer science article are. To do so, they only focused on the capacity to compile the experimental code and evaluated 601 articles published in "top ACM conferences and journal". From these 601 articles they were only able to build the environment of 217 articles. Moreover it took more than half an hour to build the experimental code of 64 of these papers and 23 others required the intervention of the authors.

At this point we need to define precisely reproducibility, for the remaining of this thesis, we will use the definition proposed by Dror G. Feitelson [Feitelson, 2015]:

**Repeatability** concerns the exact repetition of an experiment, using the same experimental apparatus, and under the same conditions.

**Reproducibility** is the reproduction of the gist of an experiment: implementing the same general idea, in a similar setting, with newly created appropriate experimental apparatus.

Repeating an experiment in the sense of Feitelson in HPC is nearly impossible. Indeed repeating an experiment first requires the access to the machine that executed the original one, with the exact same software stack and all the scripts to run it. Yet, several unpredictable factors can impact the repeatability: between the two experiments, some hardware (for instance a disc) could have been replaced by one faster. While we can log the whole hardware configuration during the experiment, some other factors, such as the room temperature, can impact the performance and are nearly impossible to measure during the experiment and impossible to reproduce. Still there is a gap between the definitions of repeatability and reproducibility. Indeed if we have access to a machine, with the exact same software stack and comparable hardware, as well as the experimental scripts, we can repeat the experiment in **similar** conditions. This definition of *similar* repeatability is stronger than reproducibility as we do not re-implement the experiment but re-run it on a similar settings. Nevertheless we cannot expect the exact same results. If the experiments compares raw execution times, changing the machine may significantly changes the results, although if we compare relative time (speedup or slowdown) we are more likely to lessen the discrepancy. Finally, adaptive algorithms may be a limit to similar repetition. Indeed, small hardware differences might be enough to trigger a change on the executed code of an adaptive algorithm.

Several tools can help us making experiments more repeatable. For instance, by running our experiment on a shared platform such as grid5000 [Cappello et al., 2005], we can argue that other people have access to the same set of machines. Moreover on these machines, it extremely easy to make a deployable image of our environment. Using an image provides controls on the installed

library, but it is impossible to know or change the version a library without deploying it. Kameleon [Ruiz et al., 2015] overpass this limit by describing an environment as a recipe. It also make the distribution of the environment easier as we only need to distribute the recipe which is a lightweight piece of code instead of an archive containing a whole Operating System (OS).

To reproduce an experiment it is important to understand how it has been designed and how it has evolved from the first version to the results presented in the paper. Stanisic et al. [Stanisic, 2015, Chapter 4, p31-44] described an experimental workflow based on Git and Org-mode to keep track of these evolutions and make easy for anyone to understand it. One of the main drawback of this workflow is that it is not suitable for experiment generating huge ( $\geq$ 500 Mib) trace files as Git is not designed to handle such files.

Many tools were designed to conduct experiments in computer science however they are not designed for HPC and using them in our context would require some adjustments. A comprehensive survey can be found in [Stanisic, 2015, Chapter 3, p17-19].

#### 2.3.2 Experimental workflow

We design experiments to analyze the behavior of an application, compare it to other applications or to test it under specific circumstances. The goal of the experiment is to answer a question or confirm an hypothesis. Answering scientifically a question requires to define:

- The environment: the circumstances under which we do the measure. In computer science that includes the OS, libraries and any user configurations.

- The reference cases to which we will compare our results. These are usually state of the art existing applications comparable to the one we evaluate.

- The inputs given to the tested applications.

- The parameters used for each application.

- The metrics: a set of quantifiable and measurable indicators used to evaluate our results.

- The expected results: what behavior do we expect, what should be considered as abnormal.

Designing an experiment consists in translating high level questions into an experimental plan that answers them scientifically.

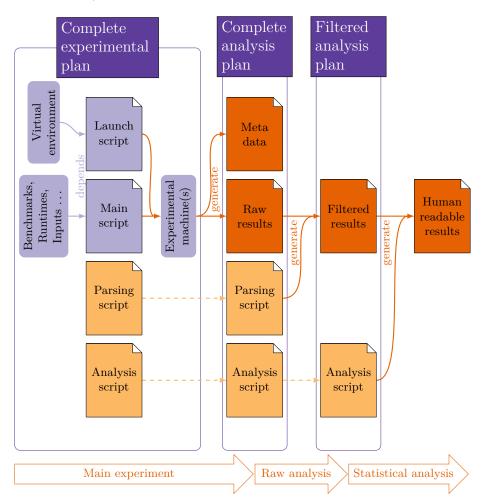

**Complete experimental plan:** We consider an experiment as a three steps workflow depicted in Figure 2.3 determined by a *Complete experimental plan*. We define the *Complete experimental plan* as the smallest set of scripts and documentation required to repeat an experiment. It includes the main script that actually run the experiment with all its dependencies. These dependencies consists in the tested applications (Git version, modifications) along with their inputs or the benchmarks used for testing them and the environment on which it is run. The complete experimental plan also contains the description of the

experimental machine(s) and the command(s) or script(s) used to deploy the environment on them and start the main script. Finally all the scripts used for parsing and analyzing the experimental results are part of the complete experimental plan as they are required to repeat it. Moreover, designing the analysis at the same time as the experiment help reduce some bias. Indeed, preparing data presentation before obtaining the actual data forces us to express our expectations. In the end, if the results do not match theses expectations we are more likely to notice it.

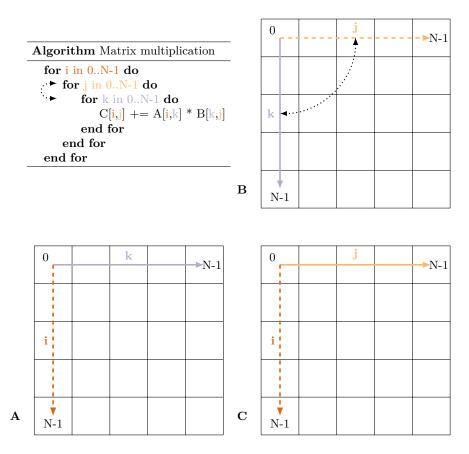

Figure 2.3 – Experimental workflow.

**Main experiment:** The first step of the experimental workflow consist in execution the main experiment on the experimental machines. This step produces two types of results: the raw results which are the actual output of the experiment and the meta data. These meta data include all pertinent informations on how the data were produced (information about the environment, commands executed, Git version of every applications) and how to interpret them. **Raw analysis:** We call *Raw Analysis* the second step that extract the raw values needed to compute the metrics defined in the complete experimental plan from the raw results. This step only aims at reducing the amount of data to analyze (from 100 Gio to few Mib in some of our experiments). The result of the raw analysis is usually one or two Comma-Separated Values (CSV) files that can be easily read by any statistical tool.

**Statistical Analysis:** Finally comes the *Statistical Analysis* which first reads the filtered results and computes statistics such as means, standard error, slow-down and speedup etc. The second aim of this step is to present a comprehensive visualization of these statistics.

While the complete experimental plan is required to repeat the experiment, some people may want to reproduce only the statistical analysis to change it and inspect the results from another point of view. Furthermore they might want to extract other values from the raw results or get more information about the experimental environment from the meta data. To enable such partial reproduction we can distribute the *Complete analysis plan* and the *filtered analysis plan* that each includes all the files generate by the previous step and all the files required to redo the next step. Finally while repeating the whole experiment requires access to the experimental machines, the two last steps are not machine dependent, thus, are easily repeatable.

### 2.3.3 Methodology

Implementing such an experimental plan is not trivial, we describe here how we design, implement and distribute our plans.

#### Construction of an experimental plan

In HPC, an experiment usually consists in evaluating the performance or the correctness of an application or of a tool that uses an application as an input (scheduler, simulator, analysis tool . . . ). For both we need to find a set of *benchmarks* to conduct our experiments, which means an input representative of the case we want to test. A benchmark can be either the input of a computational kernel or an actual application used by the tool we evaluate. Additionally, if the aim of the experiment is to evaluate the performance of a code that we have developed and there are some existing comparable applications, we need to test it against these applications. Yet, a set of benchmarks might not be a sufficient input as HPC applications are often highly configurable. Consequently, we must determine for each application which parameters are the most efficient for the evaluated metrics and the defined benchmarks. In the end, we evaluate each program under at least two set of parameters: the default and a tuned version.

Once the benchmarks are chosen, we need to decide on one machine or a set of machines on which we will run the experiment. This step is crucial as computers architectures are getting more and more complex and applications are (usually) designed for one type of machines. Furthermore some tools (such as Pin, Precise Event Based Sampling (PEBS) [Levinthal, 2009], Instruction Based Sampling (IBS) [Drongowski, 2007]) are either vendor specific or optimized for some architecture. Therefore, we often have to repeat the same experiment on several different machines to conduct a fair comparison.

At this point, we need to find some relevant metrics to answer the questions that we are asking. These metrics should remain simple as they will be interpreted by humans. Still, they must also cover every aspect that we are studying. A complete set of simple measurable metrics is often easier to understand that one complex metric providing an overall score in an obscure unit.

An experimental environment should be both *minimalist* and *sufficient*. Indeed if the environment is not sufficient we will have to install packages or library before the experiment. Hence the installed version will depend on the date at which the experiment is run, making it almost impossible to repeat. At the opposite if we include more libraries than we need or worst several version of the same library when it is not required, finding the version actually used during the original experiment might require to pay an extra attention to the whole building pipeline.

Finally it is crucial to write both parsing and analysis scripts before running the experiment. To do so, we can generate a filler set of (fake) results representing our expectations. From this set we can design some data visualizations. Furthermore using this set we can complete the plots with some text describing these expected results. Such information will prevent us from trying to explain a posteriori results that infirm our hypothesis.

#### Automation and documentation

It is crucial that a all the steps of the experiment from the deployment of the environment to the final analysis are properly scripted in a language that can be understood by other developers. Any manual step can make the experiment impossible to repeat and an obscure code might make it difficult to modify the experiment without breaking it.

Moreover, the traces generated by an experiment must be *self explanatory* or at some point they will only be a (large) set of meaningless Bytes on a hard drive. We consider that a trace is **self explanatory** if and only if we can easily answer the following questions from the raw trace:

- How the trace was generated, what is the exact command that launched it ?

- What software were used (including their versions and possible modifications) ?

- What were the hypotheses and expectations ?

- When was it executed ?

- On which machines (description, name and physical location) ?

- How are the trace files organized (file hierarchy) ?

- What scripts are used to do the analysis ?

To do so, all our experimental scripts starts the same way: they first create a new directory that will hold the traces. Then they copy themselves with all the scripts which are inside their directory to this new directory. After that they duplicate their output to a file in this new directory and log every sensitive meta data as show in Listing 2.1. During the experiment, each command is echoed before executing it. Regarding the data analysis we use R as it provides a large set of reliable statistic analysis libraries. Additionally, thanks to Rmarkdown, we can produce a standalone structured output that contains the original questions, our assumptions, the results and plots, our observations and comments. Finally, before distributing an experimental trace, we write a small Readme that explain the file hierarchy and the experiment design (although these informations could be recovered from the meta data and by reading the experiment code).

Listing 2.1 Logging experimental informations.

```

1

exec > >(tee $OUTPUT) 2>&1

2

3

echo "Expe started at $START_TIME"

echo "#### Cmd line args : ###"

4

echo "$CMDLINE"

5

echo "EXP_NAME $EXP_NAME"

6

7

echo "OUTPUT $OUTPUT"

8

echo "NUMBER OF RUNS $RUN"

9

echo "#### Hostname: ########

10

11

hostname

12

echo "#### Kernel:

#######

13

uname -a

14

echo "#### Path:

#######

echo "$PATH"

15

16

echo "##### git log: ########

17

18

git log | head

19

20

echo "#### git diff: ########

21

git diff

22

23

lstopo --of txt

24

cat /proc/cpuinfo

25

26

27

# Copying scripts

28

cp -v $0 $EXP_DIR/

29

cp -v ./*.sh $EXP_DIR/

30

cp -v *.pl $EXP_DIR/

cp -v *.rmd $EXP_DIR/

31

32

cp -v Makefile

$EXP_DIR/

```

To evaluate the variability and reduce the effect of external noise, we run each configuration several times. The more variability there is, the more runs we need to execute. These runs are all independent therefore we must avoid to make them artificially dependent. The Algorithm 2.2 shows a very simple experiment where the runs are launched by the process that actually do the experiment. As we do not create a new process for every run, some cache effects might appear after the first the run improving the performance of subsequent runs. Thus, these runs are artificially dependent. An easy way to avoid this bias is to start a new process for each run, as shown in Algorithm 2.3. However, this is not enough to protect our experiment from system noise Indeed if at some point of the experiment a system process (such as logrotate) interfere with our experiment, the performance of a set of runs will drop. As the runs are executed in order, it might be correlated with the size, and therefore we will not realize that it is due to external noise, and we will consider it as a consequence of the size. While, if we randomize the runs, the performance drop will affect several runs (but not all) for different sizes. As a result we will observe abnormal results for the impacted sizes and conclude that something might have interfered. To do so, our experimental scripts generate a list of runs that should be executed, shuffle it and then execute them in this randomized order.

| Algorithm 2.2 Dependent runs. | Algorithm 2.3 Independent runs.                                  |

|-------------------------------|------------------------------------------------------------------|

| MatAdd:                       | MatAdd:                                                          |

| function DO_RUN(size)         | function MAIN(size)                                              |

| for i in $1size$ do           | for i in $1size$ do                                              |

| for j in 1 <i>size</i> do     | for j in 1 <i>size</i> do                                        |

| C[i][j] = A[i][j] + B[i][j]   | C[i][j] = A[i][j] + B[i][j]                                      |

| end for                       | end for                                                          |

| end for                       | end for                                                          |

| end function                  | end function                                                     |

| function MAIN                 | Experiment:                                                      |

| for size in $1N$ do           | function MAIN                                                    |

| for run in $1R$ do            | for size in $1N$ do                                              |

| do_run(Param)                 | for run in $1R$ do                                               |

| end for                       | $\operatorname{EXEC}(\operatorname{MatAdd} \operatorname{size})$ |

| end for                       | end for                                                          |

| end function                  | end for                                                          |

|                               | end function                                                     |

|                               |                                                                  |

Each run consists of three step: a pre-command that can set specific environment values, the actual command that execute the benchmark and the post-command that can save data, pre-process it, compute metrics must restore the normal state. Pre-processing data during the experiment can reduce the raw trace, and interfere with the raw analysis, but it is sometimes unavoidable, for instance when some evaluated tools generate binary traces that can only be interpreted inside the experimental environment. The first and last steps are not mandatory, however any environment change must be restored on the last step. Each of the commands executed by these 3 steps are logged before execution as shown in Listing 2.4.

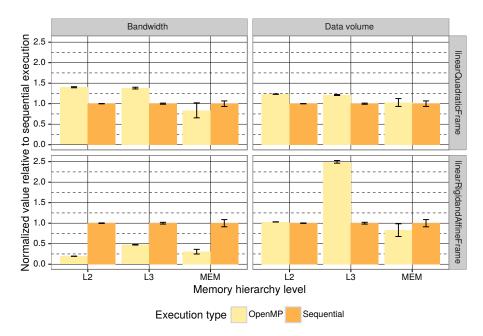

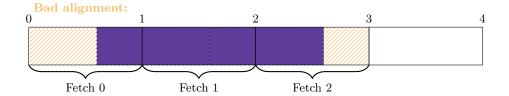

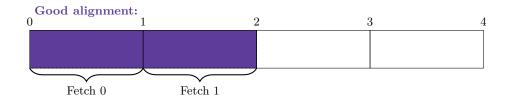

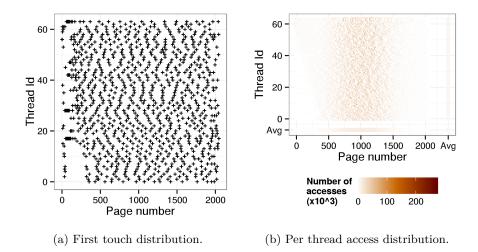

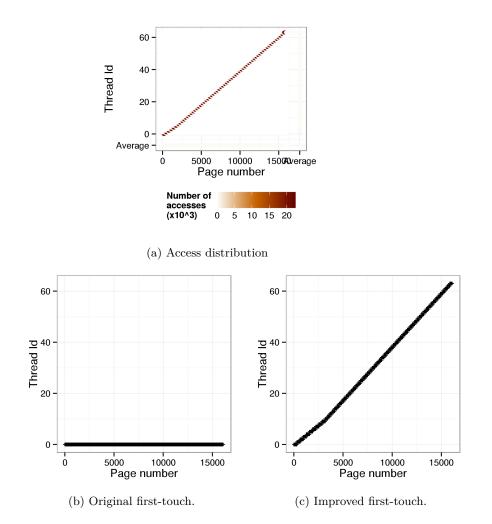

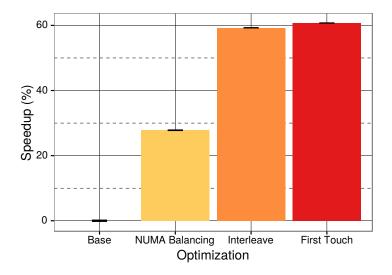

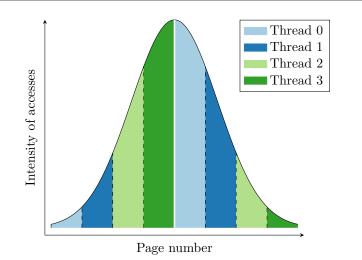

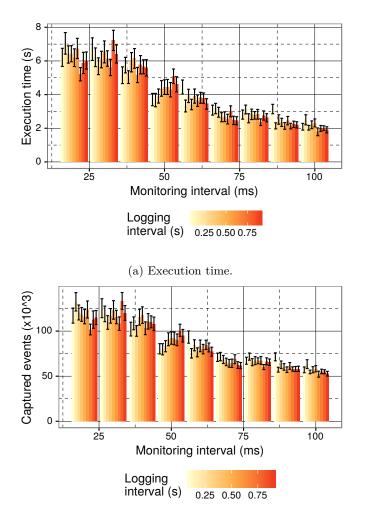

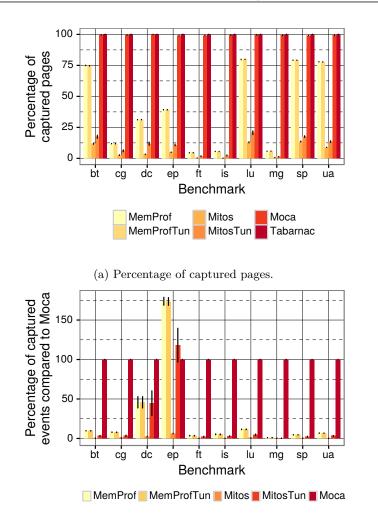

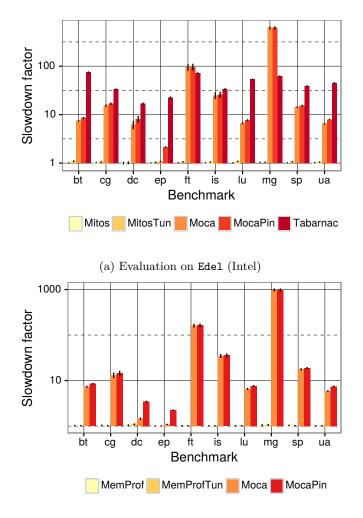

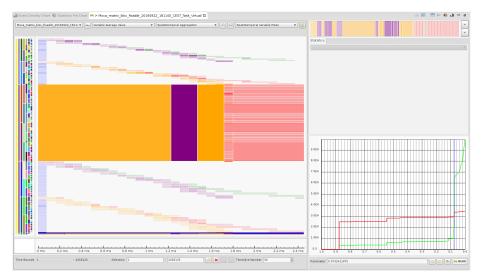

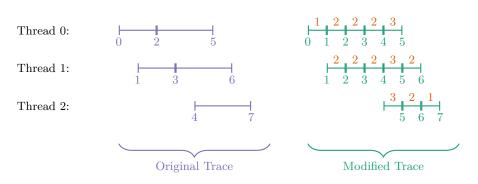

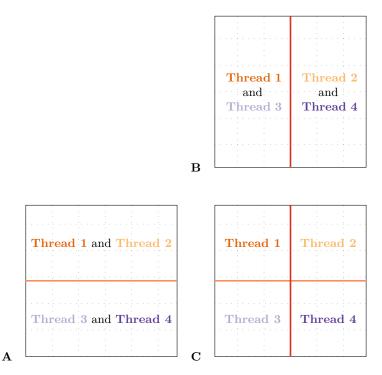

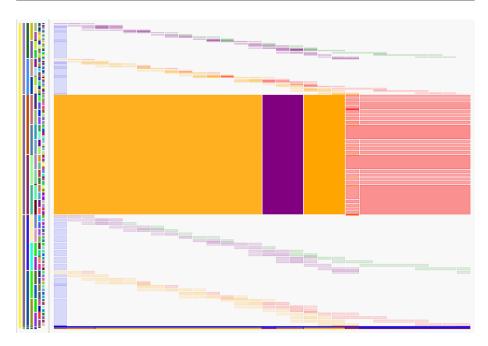

#### Distribution