# high-level component-based models for functional verification of systems-on-a-chip

Yuliia Romenska

#### ▶ To cite this version:

Yuliia Romenska. high-level component-based models for functional verification of systems-on-a-chip. Computer science. Université Grenoble Alpes, 2017. English.  ${\rm NNT}:~2017{\rm GREAM019}$ . tel-01681425v2

### HAL Id: tel-01681425 https://theses.hal.science/tel-01681425v2

Submitted on 12 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Mathématiques et Informatique

Arrêté ministérial : 25 mai 2016

Présentée par

#### Yuliia ROMENSKA

Thèse dirigée par Florence MARANINCHI, Professeur, Grenoble INP

préparée au sein du Laboratoire Verimag dans l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# **Composants Abstraits pour la Vérification Fonctionnelle des Systèmes sur Puce**

Thèse soutenue publiquement le **10 mai 2017**, devant le jury composé de :

#### Laurence PIERRE

Professeur, UNIVERSITÉ GRENOBLE ALPES, Président

#### Erika ABRAHAM

Professeur, UNIVERSITÉ D'AIX-LA-CHAPELLE, Rapporteur

#### Franco FUMMI

Professeur, UNIVERSITÉ DE VÉRONE, Rapporteur

#### Kim GRÜTTNER

Chercheur principal à OFFIS, UNIVERSITÉ CARL VON OSSIETZKY D'OLDENBOURG, Examinateur

#### **Laurent MAILLET-CONTOZ**

Directeur de recherche, STMICROELECTRONICS, Examinateur

#### Florence MARANINCHI

Professeur, GRENOBLE INP, UNIVERSITÉ GRENOBLE ALPES, Directrice de thèse

#### Acknowledgements

The work presented in this thesis would not be possible without the help of many people. First of all, I would like to thank my supervisor *Florence Maraninchi* for all our fruitful discussions, for the knowledge she gave me, for teaching me to be a researcher, for support and her patience, for faith in me and my work, for the freedom she gave in developing my ideas, for availability and readiness to help despite the busy schedule.

I would like to thank the members of my jury who paid attention to this work. Thanks to Erika Abraham (RWTH-Aachen, Germany) and Franco Fummi (University of Verona, Italy) for the time they spent reviewing the manuscript; to Laurent Maillet-Contoz (STMicroelectronics, France) and Kim Grüttner (OFFIS, Germany) for their role as examiners; to Laurence Pierre (TIMA, France), for accepting to be a president of the jury. Their questions and insightful comments contributed the quality of this work. I would like to thank Laurent also for the evaluation of this thesis from the industrial perspective, and for the management of the OpenES project which made this thesis possible.

I have been lucky in doing a Ph.D. at the Verimag laboratory. I thank all my colleagues for the creative environment they make, for our seminars and events. They always inspired me to discover and to learn things beyond my field, to improve and to move forward in my scientific inquiries.

Thanks to the members of the *Synchrone* team for the good atmosphere, for their feedback on some parts of the presented work, for their readiness to help and support. In particular, I would like to thank: *Matthieu Moy* for showing me the "SystemC world"; *Nicolas Halbwachs* and *Pascal Raymond* for their feedback on my attempts to encode order non-determinint PSL, *Erwan Jahier* for showing me the Lurette tool. I also thank *Claire Maiza*, *Susanne Graf*, *Karine Altisen*, *Fabienne Carrier*, *Catherine Parent-Vigouroux* and *Stéphane Devismes* for the short and long talks we had on various scientific and non-scientific topics.

I would not be able to complete the PhD without the fundamental knowledge I got at V. N. Karazin Kharkiv National University. I thank *Grygoriy N. Zholtkevych*, *Lilia P. Belova*, *Irina T. Zaretska*, ... for being my professors.

In addition I thank Frédéric Mallet who gave me the first taste of what research is.

Many thanks are addressed to my friends: to those I met at Verimag (*Irini*, *Abhinav*, *Mihail*, *Irina*, *Thomas*, *Lijun*, *Wei-Tsun*, *Anais*, *Maxime*, *Denis*, *Moustapha*, *Amaury*, *Souha*, ...) for all nice time we spent together and for the cultural exchange; to *Vera* for all the sweets she made for me and for her positiveness; to *Atefeh* for our trips and small discoveries; to my *Ubinet* friends.

I am endlessly grateful to *Hamza Rihani* who was always by my side during this adventure and shared with me good and less good times. It is hard to overestimate the importance of his support for the success of this PhD. He proofread entirely the manuscripts and helped me to improve the quality of text.

Finally, I would like to thank my family, who always supported and encouraged me in what I undertook.

# Contents

| Ι  | Prel | liminaries                                               | 1               |

|----|------|----------------------------------------------------------|-----------------|

| 1  | Intr | roduction                                                | 3               |

|    | 1.1  | Context                                                  | 3               |

|    | 1.2  | Summary of Contributions                                 | 4               |

|    | 1.3  | Outline of the Document and Suggestions for Readers      | 5               |

|    | 1.4  | Dissemination Activities                                 | 6               |

| 2  | Bac  | ekground                                                 | g               |

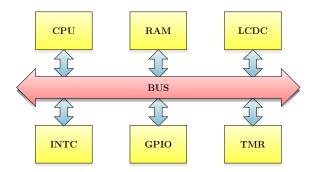

|    | 2.1  | Systems-on-Chip                                          | ç               |

|    |      | 2.1.1 Definition                                         | ç               |

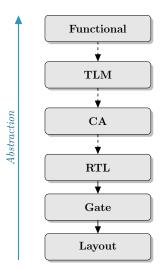

|    |      | 2.1.2 Design Flow                                        | 11              |

|    |      | 2.1.3 Functional Verification                            | 12              |

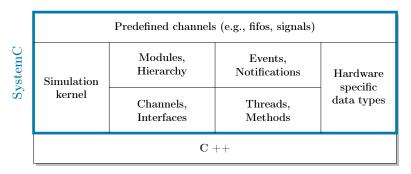

|    |      | 2.1.4 SystemC                                            | 15              |

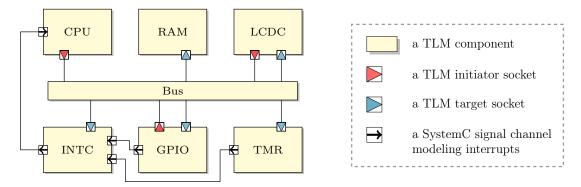

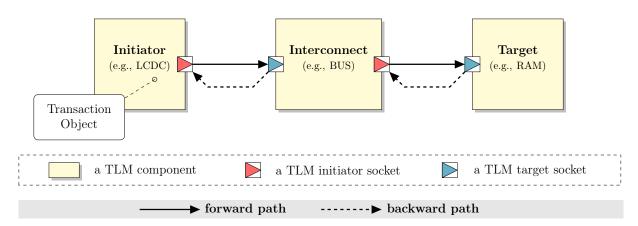

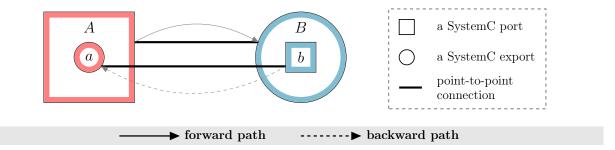

|    |      | 2.1.5 Transaction Level Modeling                         | 21              |

|    | 2.2  | Formal Models for Discrete Concurrent Systems            | 24              |

|    | 2.2  | 2.2.1 Synchronous Models                                 | $\frac{24}{24}$ |

|    |      | 2.2.1 Synchronous Models                                 |                 |

|    | 0.2  |                                                          | 28              |

|    | 2.3  | Formal Specifications                                    | 29              |

|    |      | 2.3.1 Intuition                                          | 29              |

|    |      | 2.3.2 Defining Properties (The Discrete-Time Case)       | 30              |

|    |      | 2.3.3 Specification Languages for Hardware Designs       | 33              |

|    | 2.4  | Recognition of Regular Languages, Continuous Recognizers | 34              |

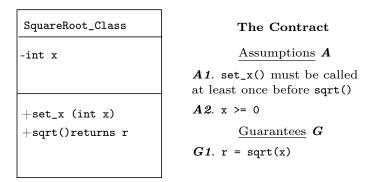

|    | 2.5  | Components and Contracts                                 | 36              |

|    | Ъ    |                                                          | 0.              |

| 11 | Ru   | nning Example                                            | <b>37</b>       |

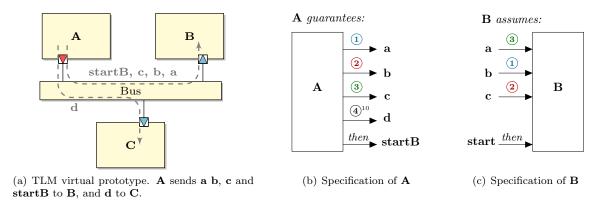

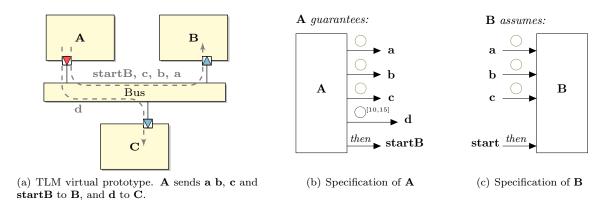

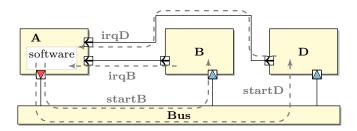

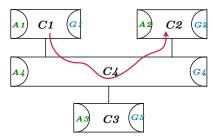

| 3  |      | e Running Example                                        | 39              |

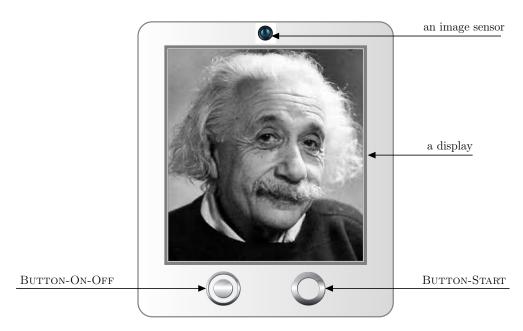

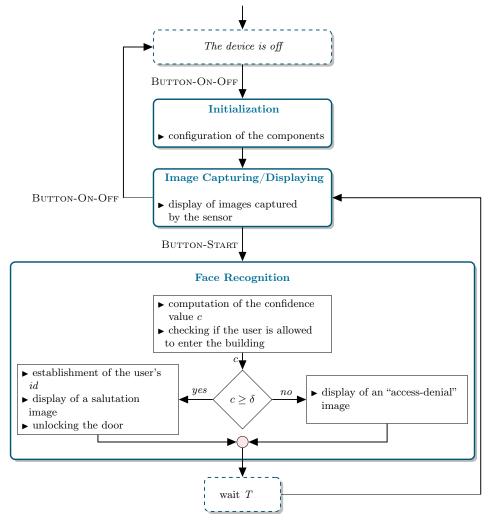

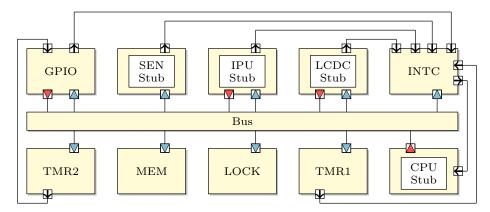

|    | 3.1  | The External View and Functionality of the System        | 39              |

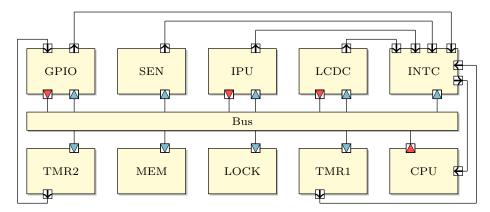

|    | 3.2  | SystemC/TLM Virtual Prototype                            | 41              |

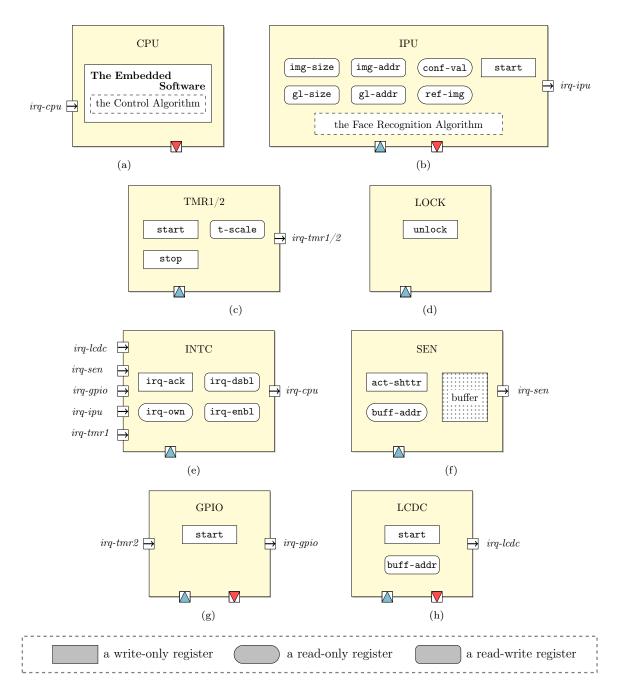

|    |      | 3.2.1 TL Models of the Components                        | 41              |

|    |      | 3.2.2 SystemC/TLM-2.0 Implementation of the Components   | 45              |

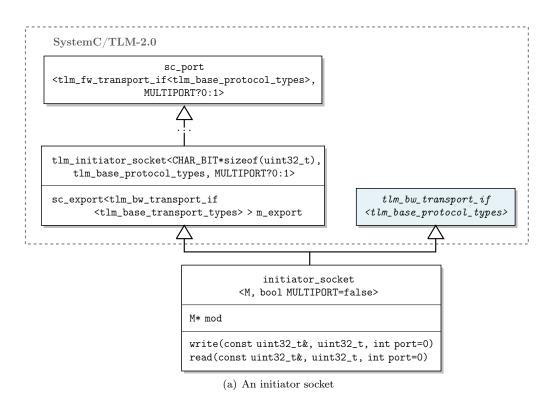

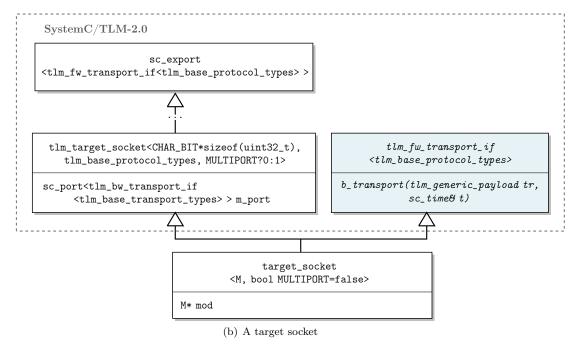

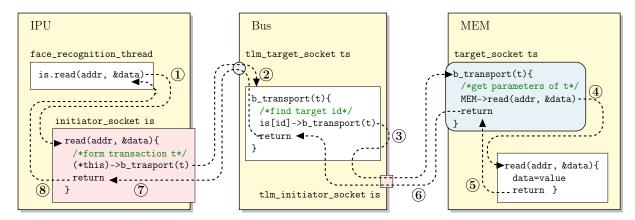

|    |      | 3.2.3 Communication Mechanism                            | 47              |

|    | 3.3  | The Embedded Software and the CPU                        | 50              |

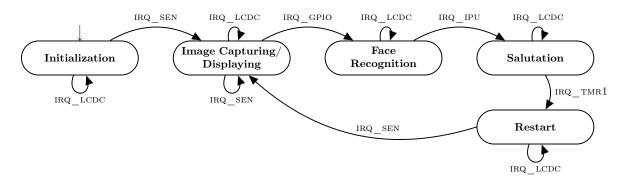

|    |      | 3.3.1 The Control Algorithm                              | 50              |

|    |      | 3.3.2 Interrupt Handling                                 | 50              |

|    |      | 3.3.3 Execution Modes                                    | 52              |

|    | 3.4  | Formal Specification of Components                       | 53              |

|    |      | 3.4.1 The Embedded Software and the CPU                  | 54              |

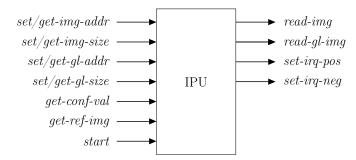

|    |      | 3.4.2 The Image Processing Unit (IPU)                    | 57              |

|    |      | 3.4.3 The Liquid Crystal Display Controller (LCDC)       | 58              |

|    |      | 3.4.4 The Image Sensor (SEN)                             | 59              |

|    |      | 3.4.5 Other Components                                   | 59              |

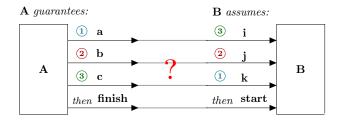

|    | 3.5  | Synchronization Bugs                                     | 60              |

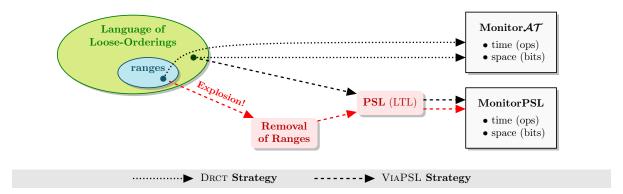

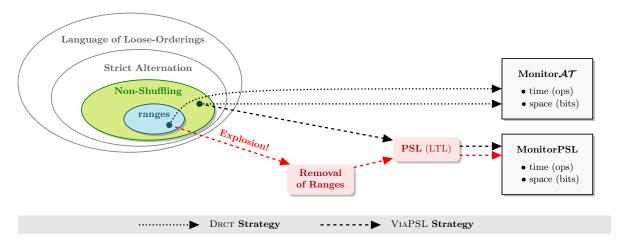

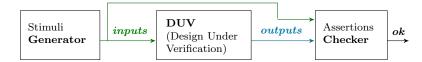

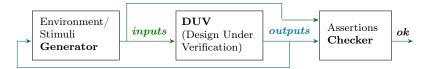

| II  | I E    | fficient Monitoring of Loose-Ordering Properties for SystemC/TLM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>63</b>  |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4   | Int    | roducing the Notion of Loose-Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65         |

|     | 4.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65         |

|     | 4.2    | Motivation for Loose-Orderings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67         |

|     | 4.2    | 4.2.1 Over-Constraining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 67         |

|     |        | 4.2.2 Robustness of the Embedded Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68         |

|     | 4.9    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|     | 4.3    | Proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69         |

|     |        | 4.3.1 Loose-Orderings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69         |

|     |        | 4.3.2 Loose-Ordering Patterns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69         |

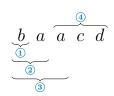

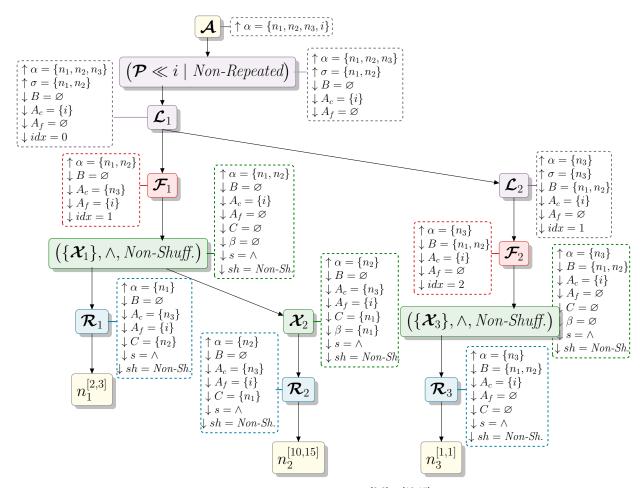

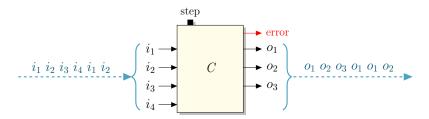

|     | 4.4    | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70         |

|     |        | 4.4.1 Input/Output Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71         |

|     |        | 4.4.2 Loose-Orderings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71         |

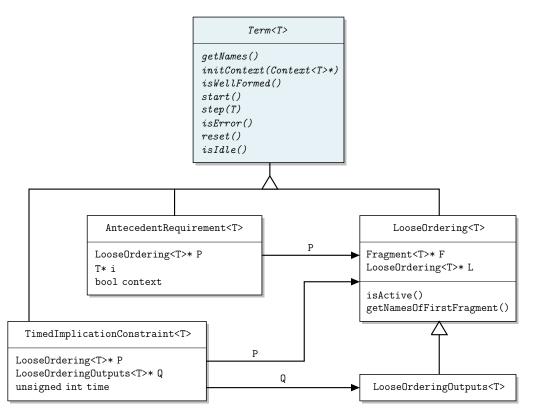

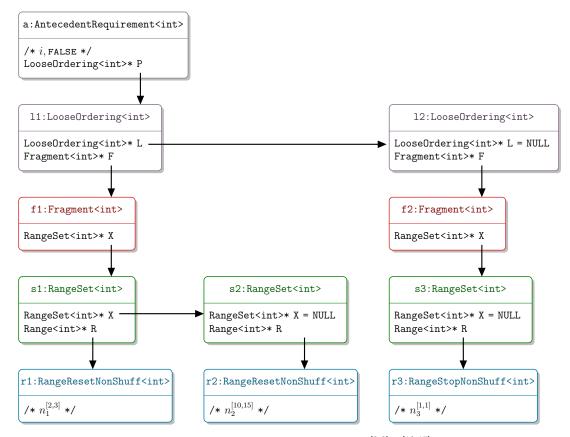

|     |        | 4.4.3 An Antecedent Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72         |

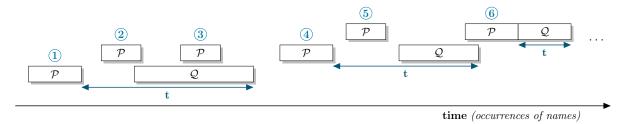

|     |        | 4.4.4 A Timed Implication Constraint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74         |

|     | 4.5    | Encoding Loose-Ordering Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75         |

|     |        | 4.5.1 The Encoded Subset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75         |

|     |        | 4.5.2 Encoding Using SERE Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76         |

|     |        | 4.5.3 Encoding Using LTL Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78         |

|     |        | 4.5.5 Encoding Using LTD Operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10         |

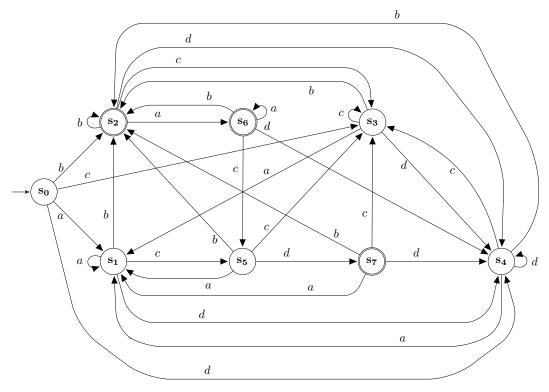

| 5   | Cor    | mpositional Building of Recognizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89         |

| •   | 5.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89         |

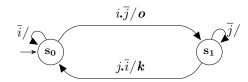

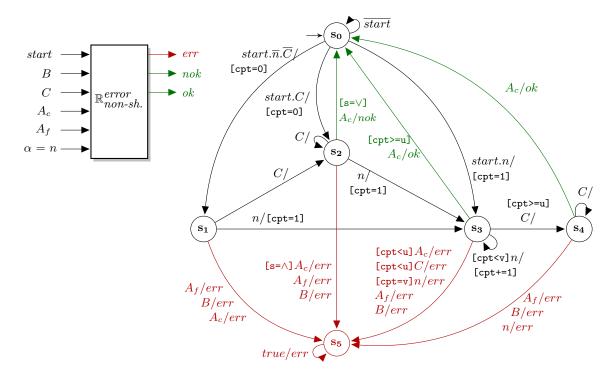

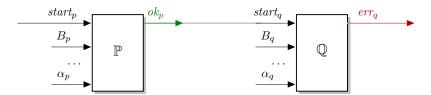

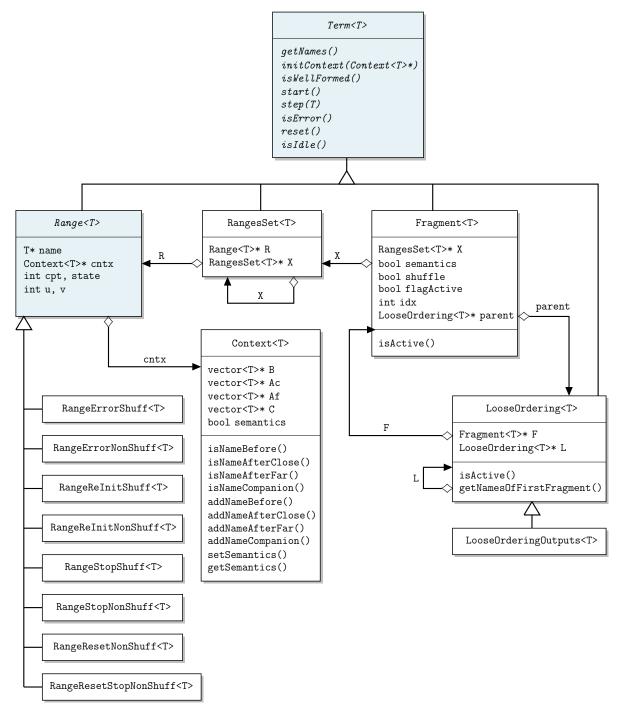

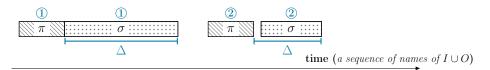

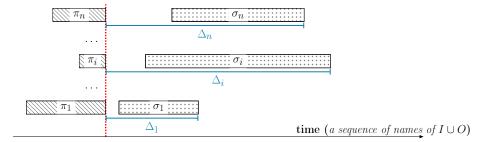

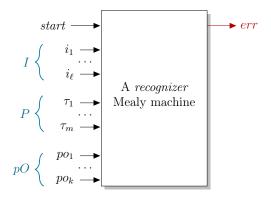

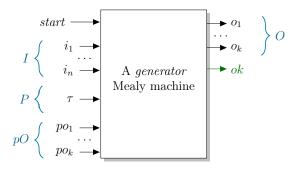

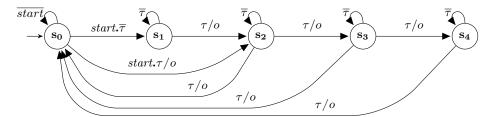

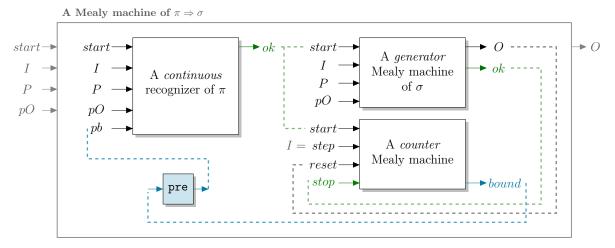

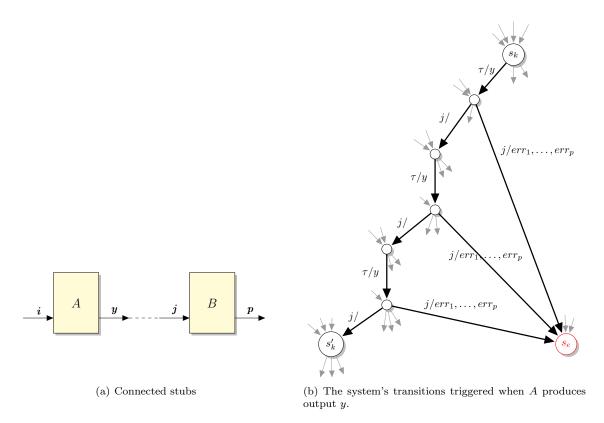

|     | 5.2    | Recognition Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90         |

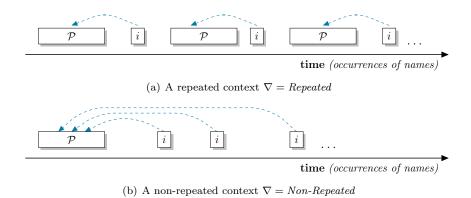

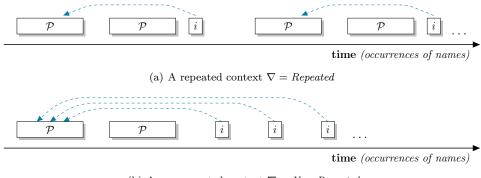

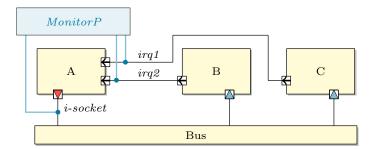

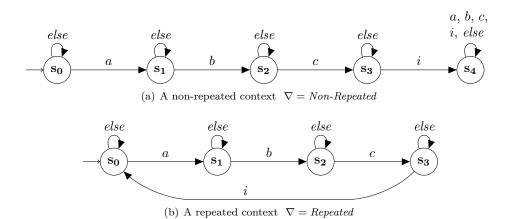

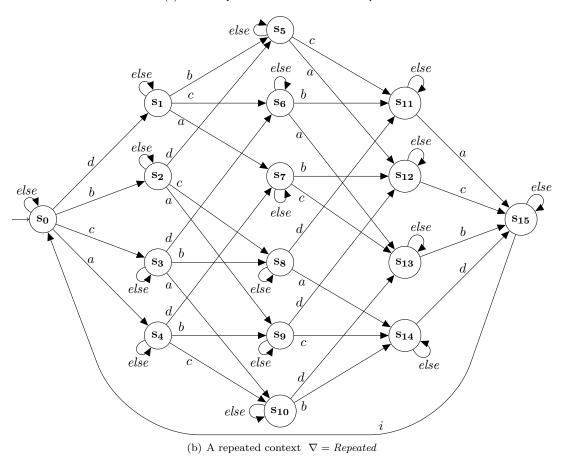

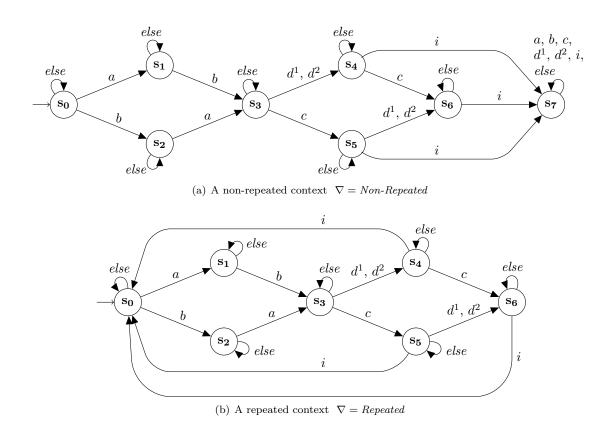

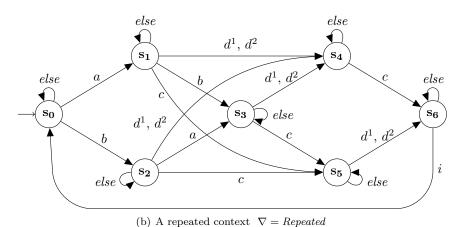

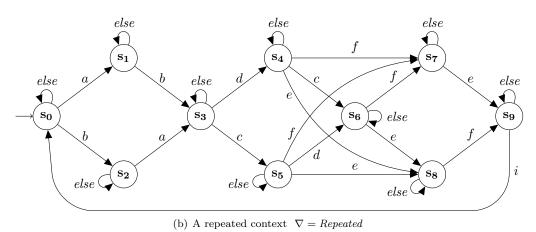

|     | 5.3    | Recognition Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91         |

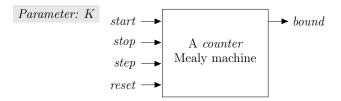

|     | 5.4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92         |

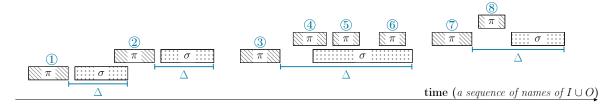

|     | 5.4    | Building Recognizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

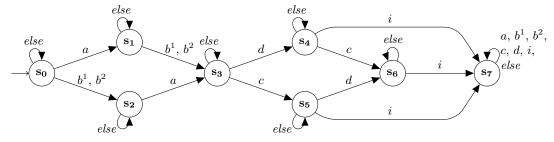

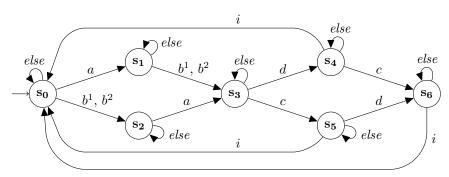

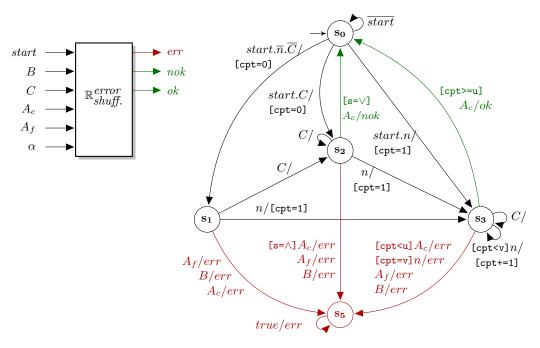

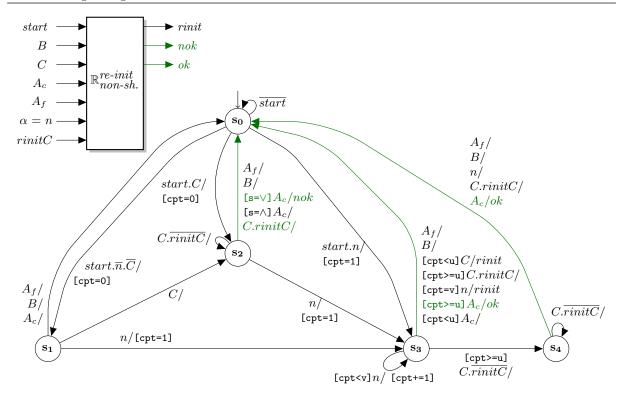

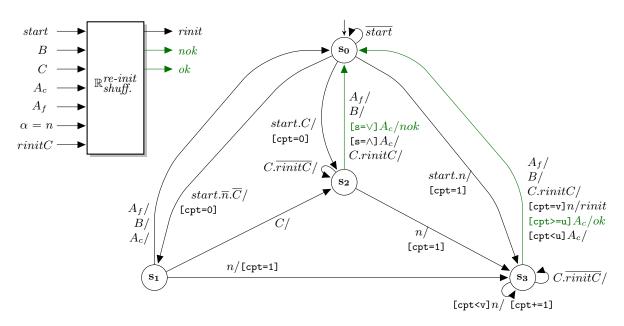

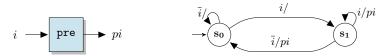

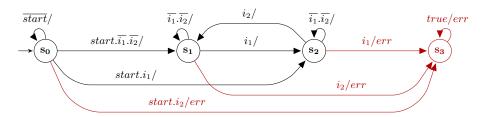

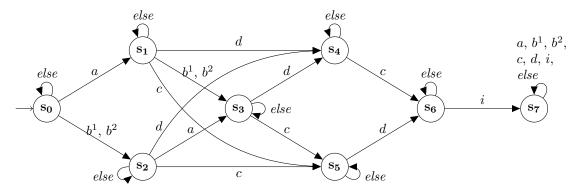

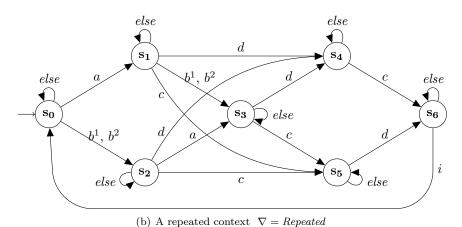

|     |        | 5.4.1 Elementary Recognizers of Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93         |

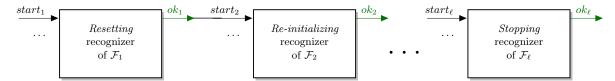

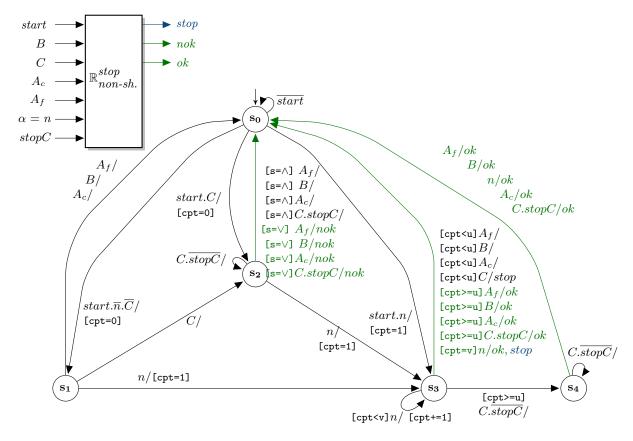

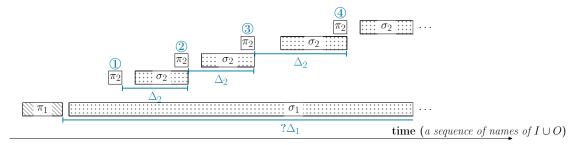

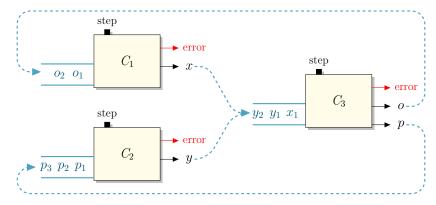

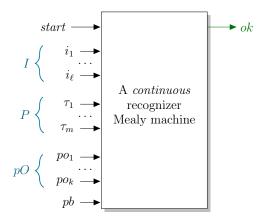

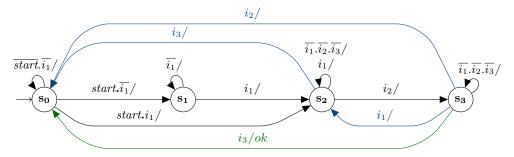

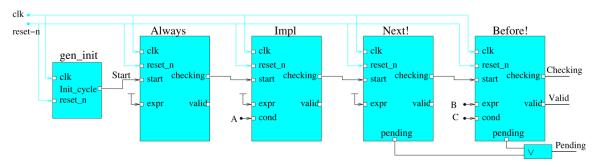

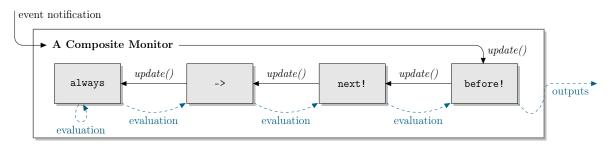

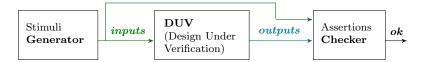

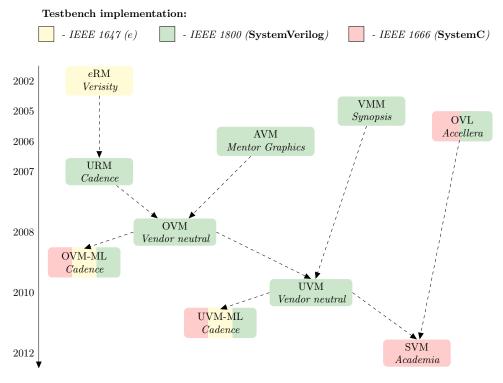

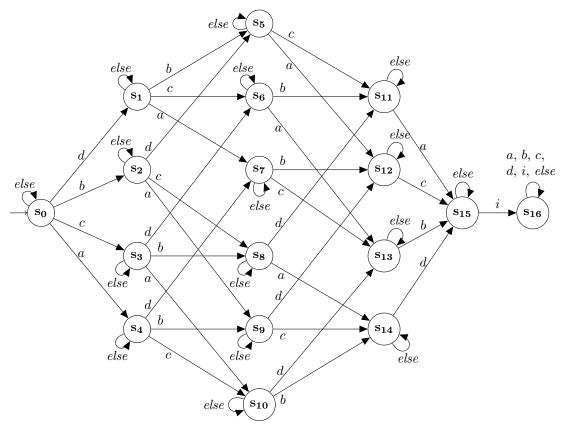

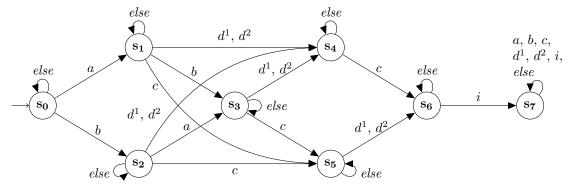

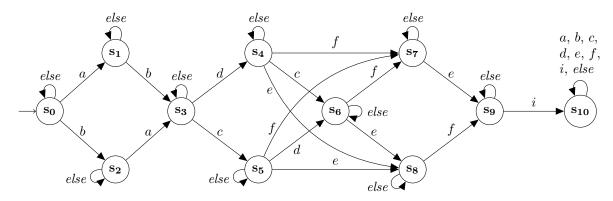

|     |        | 5.4.2 Composite Recognizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99         |

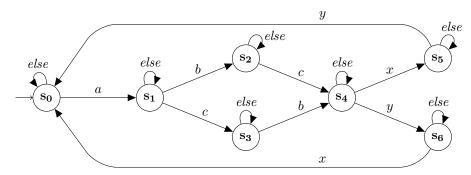

|     |        | 5.4.3 Recognizers of Loose-Ordering Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102        |

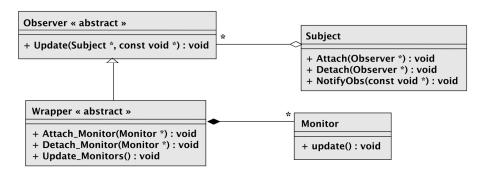

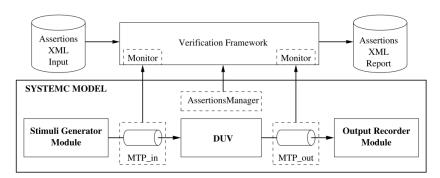

|     | 5.5    | Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 103        |

|     |        | 5.5.1 Implementing Recognizers in Lustre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103        |

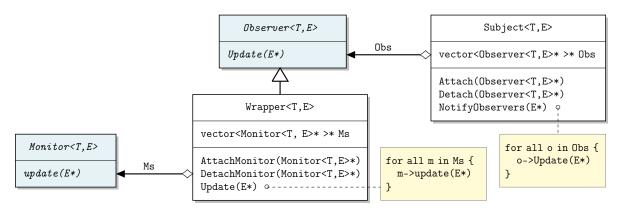

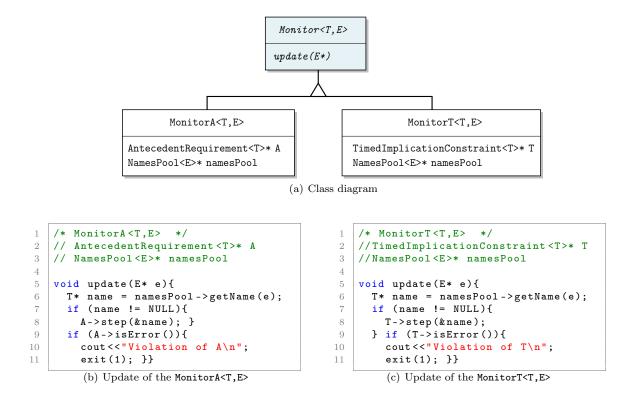

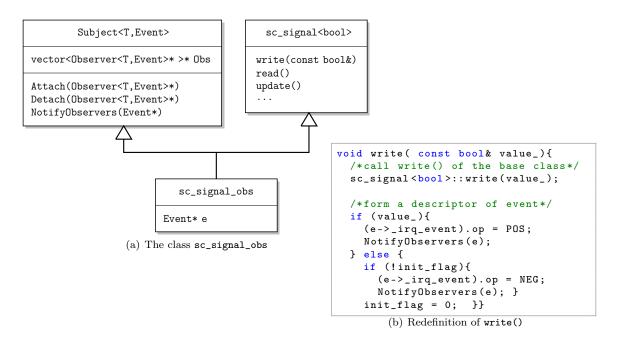

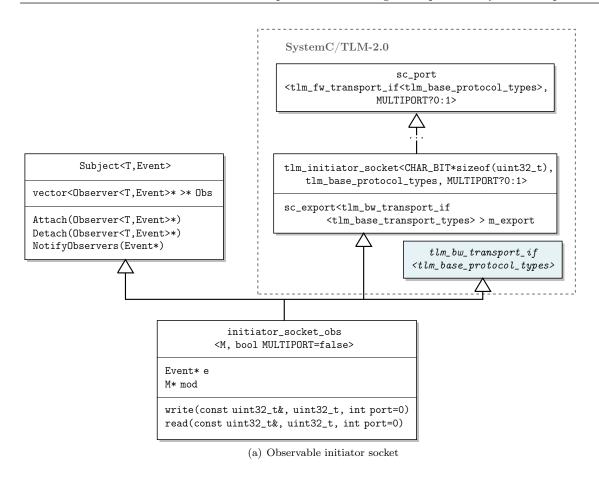

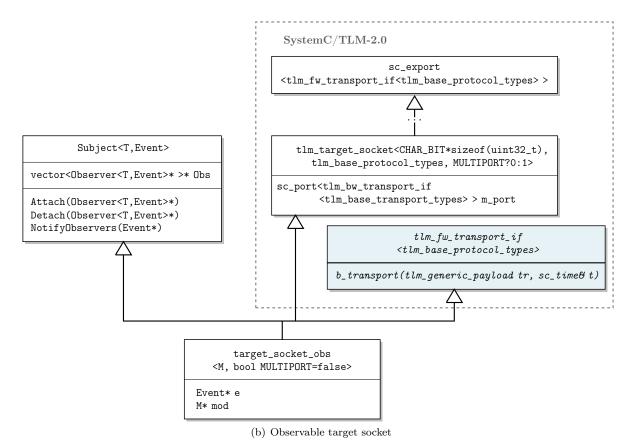

|     |        | 5.5.2 Obtaining Monitors from the LUSTRE Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 104        |

| c   | ъ.     | that a District and A. C. I. and the state of the state o | 107        |