# Integration of innovative ohmic contacts for heterogeneous III-V/Silicon Photonic devices

Elodie Ghegin

#### ▶ To cite this version:

Elodie Ghegin. Integration of innovative ohmic contacts for heterogeneous III-V/Silicon Photonic devices. Condensed Matter [cond-mat]. Université Sorbonne Paris Cité, 2017. English. NNT: 2017USPCC008. tel-01685738

# HAL Id: tel-01685738 https://theses.hal.science/tel-01685738

Submitted on 16 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse de doctorat de l'Université Sorbonne Paris Cité Préparée à l'Université Paris Diderot Ecole doctorale Physique en Île-de-France [ED 564]

STMicroelectronics / CEA-LETI / C2N site de Marcoussis

# Integration of innovative ohmic contacts for heterogeneous III/V-Silicon Photonic devices

# Par Elodie GHEGIN

Thèse de doctorat de Physique

Dirigée par Isabelle SAGNES

Présentée et soutenue publiquement à Grenoble le 10 Mars 2017

Présidente du jury : Angela Vasanelli Professeur UPD - MPQ

Rapporteur : Christian Seassal Directeur de Recherche CNRS Ecole centrale de Lyon

Rapporteur : Guilhem Larrieu Chargé de recherche de 1ère classe CNRS - LAAS

Examinateur : Dries Van Thourhout Professeur UGent

Examinateur: Emmanuel Dubois Directeur de Recherche CNRS IEMN Lille

Directrice de thèse : Isabelle Sagnes Directrice de recherche CNRS C2N Marcoussis

Encadrant: Fabrice Nemouchi Chercheur CEA-LETI

Encadrant: Aomar Halimaoui Chercheur STMicroelectronics

Membre invité :Philippe RodriguezChercheurCEA-LETIMembre invité :Christophe JanyChercheurCEA-LETIMembre invité :Menyhárd MiklósProfesseur émériteMTA TTK

Except where otherwise noted, this work is licensed under <a href="http://creativecommons.org/licenses/by-nc-nd/3.0/">http://creativecommons.org/licenses/by-nc-nd/3.0/</a>

#### Titre de la thèse :

Intégration de contacts innovants pour dispositifs photoniques III/V-Si

#### Résumé:

Depuis les années 2000, en raison d'une multitude de moyens de communication émergents, les besoins en termes d'échange de données n'ont cessé d'augmenter. Ces modifications ont conduit à l'initiation d'une transition depuis les technologies électroniques vers les technologies et interconnexions optiques. Entre autres, ces nouvelles technologies nécessitent l'utilisation de composants émetteurs et récepteurs de photons constitués de matériaux III-V. De façon à miniaturiser ces composants et à augmenter leurs performances tout en diminuant leur coût de fabrication, un modèle d'intégration innovant consiste à intégrer directement les sources III-V sur le circuit photonique silicium 200 mm. Afin d'optimiser les performances du laser III-V tout en respectant les contraintes liées à une salle blanche front-end / middle-end silicium, la réalisation d'une telle intégration nécessite notamment le développement de contacts innovants sur n-InP et p-InGaAs.

Ces travaux de thèse sont ainsi centrés autour du développement d'une nouvelle architecture de contacts répondant aux exigences d'une salle blanche front-end / middle-end silicium 200 mm, tout en optimisant les performances du laser III-V. Un schéma d'intégration innovant des contacts est tout d'abord présenté dans sa globalité puis une optimisation des procédés d'intégration disponibles est proposée. Ceci permet de profiter de l'avantage économique que procure le fait d'utiliser l'expertise existante tout en préservant les surfaces III-V et en optimisant les performances d'émission du laser. Une attention particulière est portée sur le développement de la métallisation de contact, elle-même reposant sur la formation de composés intermétalliques à l'interface entre le métal déposé et le semi-conducteur. Une étude métallurgique approfondie est ainsi conduite sur les systèmes Ni/n-InP, Ni/p-InGaAs et Ti/n-InP dans le but d'identifier les séquences de phases ainsi que des mécanismes mis en jeu et enfin leur stabilité thermique. Finalement, l'ensemble de ces métallisations sont intégrées au sein de dispositifs dédiés au test électriques des contacts. Les résistivités spécifiques de contacts associées sont ainsi extraites. Grâce à l'ensemble de ces travaux, les métallisations et procédés permettant d'optimiser les performances électriques des contacts intégrés tout en garantissant leur stabilité sont finalement identifiés.

#### Mots clefs:

Contact Métal/n-InP, Contact Métal/p-InGaAs, Photonique sur Silicium, Laser III-V, Intégration, Réaction à l'état solide, Caractérisation électrique, résistivité de contact.

#### Title:

Integration of innovative ohmic contacts for heterogeneous III-V/Silicon Photonic devices

#### Abstract:

Since the 2000s, the requirements in terms of data exchange never stopped rising owing to a multitude of emerging communication means. These extensive modifications lead the signal processing and electrical technologies to switch towards optical devices and interconnections. Among others, these new technologies require the use of III-V-based emitters and receptors. In order to miniaturize these devices, to optimize the performances and to minimize the fabrication cost of such a technology, an innovative manufacturing model consists in integrating directly the III-V laser source onto the 200 mm Si photonics circuit. To enable the development of contacts meeting the constraints of a front-end / middle-end Si-environment along with those of an operating laser, one of the keys lies in the development of contacts on n-InP and p-InGaAs which are necessary to electrically pump the III-V laser.

This Ph.D thesis therefore deals with the development of an innovative contact architecture fulfilling the requirements of a front-end / middle-end Si-dedicated clean room environment while optimizing the performances of the III-V laser. An integration scheme is firstly presented in its wholeness before optimizing every available process that is required. This kind of development leverages the advantage of utilizing existing infrastructures and processes while preserving the III-V surfaces and optimizing the performances of the III-V laser. Special attention is devoted to the development of the contact metallization which relies on the formation of intermetallic compounds at the interface between the deposited metal and the semiconductor. Extensive studies are therefore conducted on the Ni/n-InP, Ni/p-InGaAs et Ti/n-InP systems in order to identify the phase sequences, the involved mechanism and finally the thermal stability of the various phases. Ultimately, these metallizations are integrated in structures dedicated to their electrical characterization. The corresponding specific contact resistivities are thus extracted. Thanks to these studies, the metallizations and processes allowing an optimization of the electrical performances of the integrated contacts while ensuring their stability are finally identified.

#### **Keywords:**

Metal/n-InP contact, Metal/p-InGaAs contact, Si Photonics, III-V laser, Integration, Solid state reaction, Electrical characterization, Contact resistivity.

Nothing is impossible,

The word itself says 'I'm possible'!

[Audrey Hepburn]

#### Remerciements

Lorsque je repense à ces trois années de thèse, de nombreux visages et échanges me viennent en tête. L'ensemble de ces travaux de thèse n'auraient pas été possibles sans l'investissement de nombreux acteurs. Je pense bien évidemment tout d'abord à ma directrice de thèse, Isabelle, sans qui cette thèse n'aurait pu aussi bien se dérouler. Je pense également à toutes les équipes du DTSI, qui, grâce à leur expertise et leurs conseils, nous ont permis de mener à bien l'intégration des contacts en salle blanche en quelques mois. Au-delà de ce travail quotidien, les interactions que j'ai pu avoir avec les différents experts ont également apporté une valeur ajoutée indéniable à ces travaux. Je pense également aux équipes du DCOS qui m'ont largement accompagnée au cours de ces trois ans. Je tiens notamment à remercier Yves dont les connaissances et l'aide nous ont permis de développer de nouveaux masques et d'imaginer une nouvelle intégration pour les contacts. Bernard et Claude ont également été d'une aide primordiale dans ces développements, que ce soit en termes de support au suivi de l'activité ou en termes de caractérisations, toujours en un temps record. Enfin, je souhaite remercier Louis pour les nombreuses discussions que nous avons eues autour des caractérisations électriques des contacts, mais aussi autour de sujets plus légers. L'ensemble de ces travaux de recherche a bien évidemment été mené en collaboration avec le département applicatif d'optoélectronique, le DOPT. En son sein, je souhaiterais tout d'abord remercier Bertrand pour son aide tout au long du projet. J'ai bien évidemment une pensée toute particulière pour Christophe qui n'a pas compté ses heures quand il s'agissait de m'expliquer les secrets de la photonique, ou de m'aider à intégrer les contacts. Dans ce cadre, je tiens également à remercier tout particulièrement Tiphaine et Jeremy pour leur efficacité et leur implication pour l'intégration des structures de test électriques.

Ces travaux de thèse ont également fait appel à des collaborations qui se sont avérées extrêmement fructueuses. De nombreuses caractérisations et études présentées dans ce manuscrit ont effectivement été menées en collaboration avec l'IM2NP, et plus particulièrement avec Khalid et Carine. Je tiens à les remercier pour le temps qu'ils nous ont accordé en termes de caractérisations, mais aussi au cours de nombreuses discussions. De la même façon, l'étude métallurgique présentée aurait été bien différente sans l'apport conséquent de l'Hungarian Academy of Sciences, et plus précisément de János et Miklós. Merci à eux deux pour leur efficacité et pour la qualité des caractérisations et discussions auxquelles nous avons eu accès.

Je souhaiterais bien évidemment remercier mon entourage proche au cours de cette thèse. Je pense ici à la team contact, qui a été redimensionnée au rythme des stages et thèses mais qui n'a jamais perdu de son esprit d'équipe et de sa cohésion. Je tiens ainsi à remercier Sylvie, Laura, Emilie, Mattia, Mathilde, Coralie, Romain, Salma, Fabrice et Philippe pour leur bonne humeur et leur support au quotidien. Parmi ces personnes, je souhaite notamment remercier Mattia pour l'excellent travail qu'il a réalisé au cours de son projet de fin d'études. Je souhaite également remercier tout particulièrement Fabrice et Philippe pour leur encadrement. Ils ont su être présents et toujours disponibles tout en me faisant confiance au cours de ces trois ans. Ils m'ont ainsi permis de mener à bien ce projet en autonomie tout en ayant un support de tous les instants. Au-delà d'être de simples collègues, l'ensemble des membres de cette équipe est devenu, au fil des années, de vrais amis.

Enfin, je souhaite remercier l'ensemble de mes amis pour leur présence tout au long de ces années. J'ai également une pensée toute particulière pour ma famille sans qui rien de tout ceci n'aurait été possible. Finalement, je tiens à remercier mon mari, Julien, pour son support au quotidien et dans les moments les plus stressants de cette thèse.

Un grand merci à vous tous ainsi qu'à tous ceux je j'aurais maladroitement oubliés.

TABLE OF CONTENTS

# **TABLE OF CONTENTS**

| GEN  | ERAL INTRODUCTION                                                   | 1  |

|------|---------------------------------------------------------------------|----|

| Снар | PTER 1: Introduction to Silicon Photonics                           | 3  |

| 1.1  | The information revolution                                          | 5  |

| 1.2  | Silicon photonics                                                   | 6  |

|      | 1.2.1 Why do we need silicon photonics?                             | 6  |

|      | 1.2.2 Description of a silicon photonics integrated circuit         | 6  |

| 1.3  | III-V heterogeneous integration on Silicon                          | 8  |

|      | 1.3.1 Hetero-epitaxial growth of III-V on silicon                   | 8  |

|      | 1.3.2 Flip Chipping                                                 | 8  |

|      | 1.3.3 Bonding of III-V on silicon                                   | 9  |

| 1.4  | The III-V laser structure                                           | 10 |

|      | 1.4.1 The LASER effect                                              | 10 |

|      | 1.4.2 The laser structure                                           | 11 |

| 1.5  | The optical gain and losses                                         | 16 |

|      | 1.5.1 The optical gain                                              | 16 |

|      | 1.5.2 The optical losses                                            | 17 |

| 1.6  | The electrical pumping of the laser: contacts to n-InP and p-InGaAs | 20 |

|      | 1.6.1 State of the art about contacts to III-V materials            | 20 |

|      | 1.6.2 Transition towards CMOS-compatible contacts                   | 25 |

| 1.7  | ' Conclusion                                                        | 27 |

|      | PTER 2: The Electrical Pumping of The III-V Laser: How To Integ     |    |

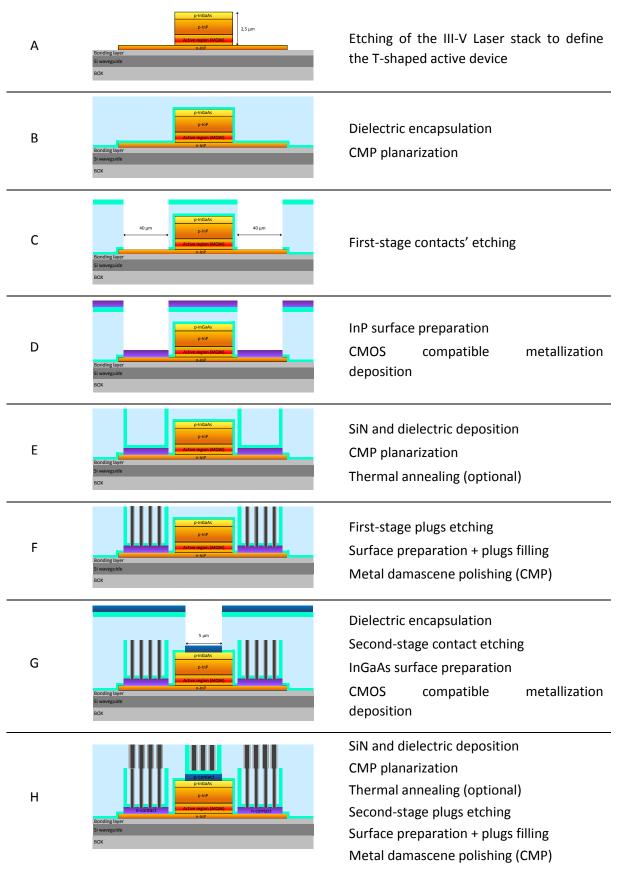

| 2.1  | CMOS-compatible contacts integration to III-V surfaces              | 37 |

| 2.2  | ! Transfer of the III-V stack on the silicon substrate              | 42 |

| 2.3                 | Etching of the III-V stack via a SiN hard mask                                                                                                                                                                                                                                                                                                                                                                                                    | 43               |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.4                 | Dielectric encapsulation                                                                                                                                                                                                                                                                                                                                                                                                                          | 47               |

|                     | 2.4.1 Criteria for the selection of the candidates                                                                                                                                                                                                                                                                                                                                                                                                | 47               |

|                     | 2.4.2 Optical characteristics of the dielectric compounds                                                                                                                                                                                                                                                                                                                                                                                         | 49               |

|                     | 2.4.3 Thermal characteristics of the dielectric compounds                                                                                                                                                                                                                                                                                                                                                                                         | 51               |

|                     | 2.4.4 Summary of the results                                                                                                                                                                                                                                                                                                                                                                                                                      | 52               |

| 2.5                 | Contact cavities opening                                                                                                                                                                                                                                                                                                                                                                                                                          | 53               |

| 2.6                 | III-V surface preparation and CMOS-compatible contact metallization                                                                                                                                                                                                                                                                                                                                                                               | 58               |

|                     | 2.6.1 III-V surface preparation                                                                                                                                                                                                                                                                                                                                                                                                                   | 58               |

|                     | 2.6.2 CMOS-compatible metallization                                                                                                                                                                                                                                                                                                                                                                                                               | 60               |

| 2.7                 | Metallization encapsulation and Plug integration                                                                                                                                                                                                                                                                                                                                                                                                  | 62               |

| 2.8                 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65               |

| C                   | TER 3: Metallurgical Studies of Si-Compatible Metallizations on                                                                                                                                                                                                                                                                                                                                                                                   | n_InD and        |

|                     | GaAs                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| p-In@               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73               |

| p-In@               | GaAs                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73               |

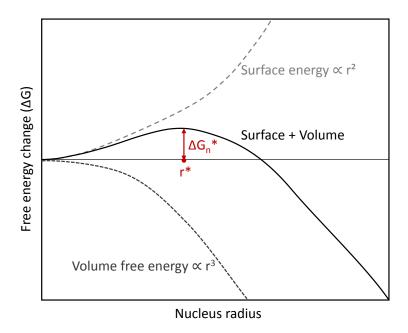

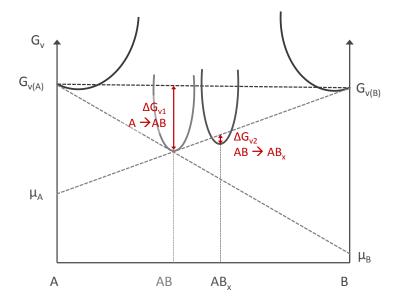

| p-In@               | Formation of intermetallic compounds in the case of thin films                                                                                                                                                                                                                                                                                                                                                                                    | 73<br>75         |

| p-In@               | Formation of intermetallic compounds in the case of thin films                                                                                                                                                                                                                                                                                                                                                                                    | 737576           |

| p-In@               | Formation of intermetallic compounds in the case of thin films                                                                                                                                                                                                                                                                                                                                                                                    | 73 75 76 77      |

| p-In@               | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities  3.1.2 Thin films reactive diffusion  3.1.3 Kinetics of phase(s) formation                                                                                                                                                                                                                                              |                  |

| <b>p-In©</b><br>3.1 | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities                                                                                                                                                                                                                                                                                                                         |                  |

| <b>p-In©</b><br>3.1 | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities  3.1.2 Thin films reactive diffusion  3.1.3 Kinetics of phase(s) formation  3.1.4 Impact of defects on intermetallic formation  3.1.5 Thermal stability of the intermetallic compounds                                                                                                                                  |                  |

| <b>p-In©</b><br>3.1 | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities  3.1.2 Thin films reactive diffusion  3.1.3 Kinetics of phase(s) formation  3.1.4 Impact of defects on intermetallic formation  3.1.5 Thermal stability of the intermetallic compounds  Experimental procedure and characterization techniques                                                                          | 73757679828383   |

| <b>p-In©</b><br>3.1 | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities.  3.1.2 Thin films reactive diffusion.  3.1.3 Kinetics of phase(s) formation.  3.1.4 Impact of defects on intermetallic formation.  3.1.5 Thermal stability of the intermetallic compounds.  Experimental procedure and characterization techniques.  3.2.1 Experimental procedure.  3.2.2 Characterization techniques. | 7375767779828383 |

| <b>p-In©</b><br>3.1 | Formation of intermetallic compounds in the case of thin films  3.1.1 Formation of intermetallic compounds – Generalities                                                                                                                                                                                                                                                                                                                         | 73757679838383   |

|     | 3.4.2  | Study of the amorphous layer on InP surfaces                           | 96    |

|-----|--------|------------------------------------------------------------------------|-------|

|     | 3.4.3  | Analysis of the annealed samples                                       | . 101 |

|     | 3.4.4  | Discussion                                                             | . 105 |

|     | 3.4.5  | Summary of the results                                                 | . 109 |

| 3.5 | State  | of the art about Ni-based metallizations on InGaAs                     | . 110 |

| 3.6 | Metal  | lurgical study of Ni-based metallizations on InGaAs                    | . 115 |

|     | 3.6.1  | Analysis of the as deposited Ni/InGaAs                                 | . 115 |

|     | 3.6.2  | Analysis of the annealed samples and discussion                        | . 117 |

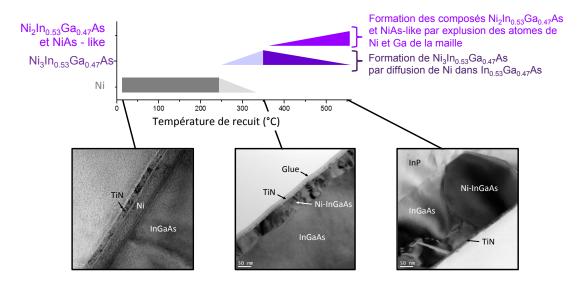

|     | 3.6.3  | Summary of the results                                                 | . 125 |

| 3.7 | State  | of the art about Ti-based metallizations on InP                        | . 126 |

| 3.8 | Metal  | lurgical study of Ti-based metallizations on InP                       | . 130 |

|     | 3.8.1  | Analysis of the as deposited samples                                   | . 130 |

|     | 3.8.2  | Analysis of the annealed samples                                       | . 132 |

|     | 3.8.3  | Discussion                                                             | . 135 |

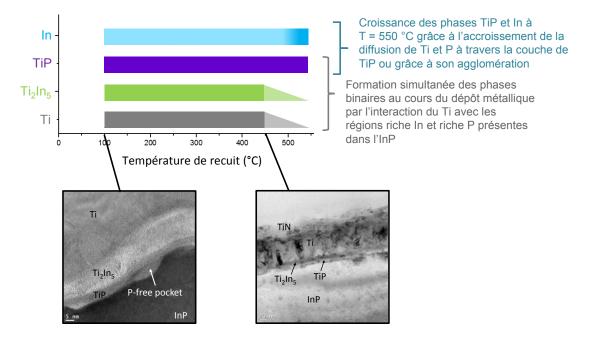

|     | 3.8.4  | Summary of the results                                                 | . 140 |

| 3.9 | Conclu | usion                                                                  | . 141 |

|     |        | Si-Compatible Ohmic Contacts to n-InP and p-InGaAs: Theory             |       |

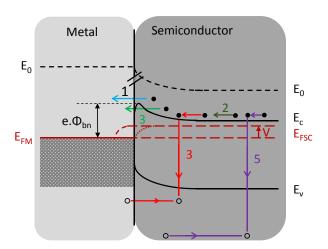

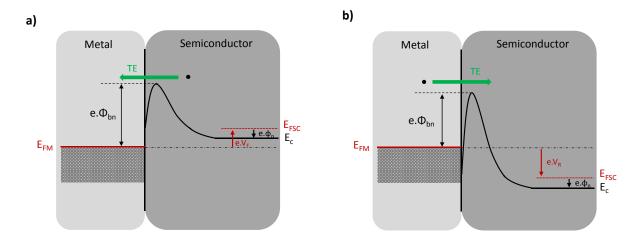

| 4.1 | Metal  | / Semiconductor band diagrams and transport mechanisms                 | . 153 |

|     | 4.1.1  | Metal / Semiconductor band diagrams                                    | . 153 |

|     | 4.1.2  | Current transport mechanisms                                           | . 158 |

| 4.2 | From I | Metal / Semiconductor band diagram to the specific contact resistivity | . 161 |

|     | 4.2.1  | Definition of the contact resistance and resistivity                   | . 161 |

|     | 4.2.2  | Metal / Semiconductor system presenting a negative barrier             | . 162 |

|     | 4.2.3  | Enhancement of the conduction above and through the barrier            | . 163 |

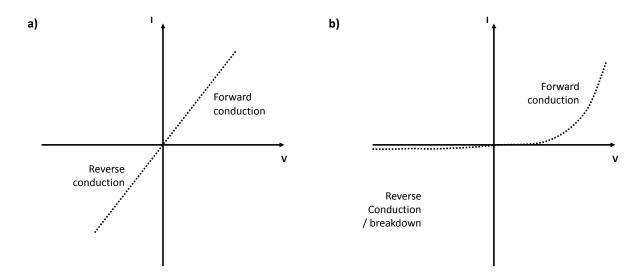

|     | 4.2.4  | Resulting I(V) characteristics                                         | . 165 |

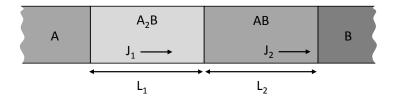

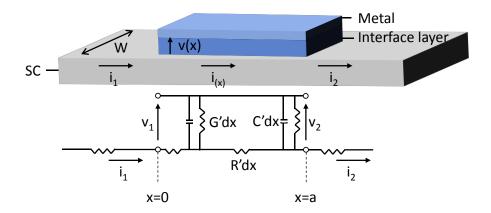

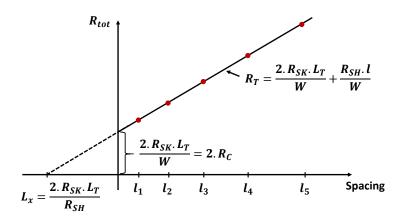

| 4.3        | The Tr         | ransfer Length Method (TLM)                                                                  | 166         |

|------------|----------------|----------------------------------------------------------------------------------------------|-------------|

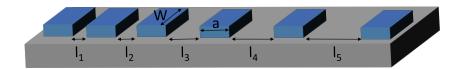

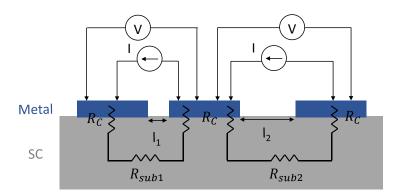

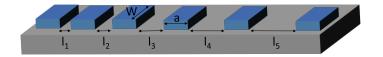

|            | 4.3.1          | Measurement principle                                                                        | 166         |

|            | 4.3.2          | Important definitions                                                                        | 168         |

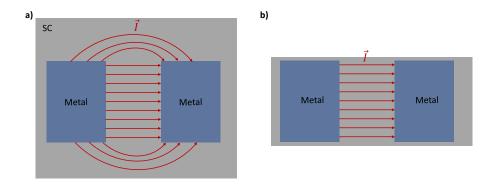

|            | 4.3.3          | Extraction of the specific contact resistivity – general case                                | 169         |

|            | 4.3.4          | Extraction of the specific contact resistivity – alloyed contacts                            | 171         |

|            | 4.3.5          | Limitation of the TLM method                                                                 | 173         |

| 4.4        | Descri         | ption of the experimental electrical test structures                                         | 174         |

|            | 4.4.1          | General presentation of the adopted strategy                                                 | 174         |

|            | 4.4.2          | Description of the electrical test structures (MELT)                                         | 175         |

| 4.5        | Electri        | cal characterization of the Si-compatible Ni and Ti-based metallizations                     | 178         |

|            | 4.5.1          | Experimental procedure                                                                       | 178         |

|            | 4.5.2          | Experimental extraction of the specific contact resistivity – Schottky contact               | 180         |

|            |                | Experimental extraction of the specific contact resistivity – Non-alloyed ohmic con          |             |

|            | 4.5.4          | Experimental extraction of the specific contact resistivity – Alloyed ohmic contact          | 183         |

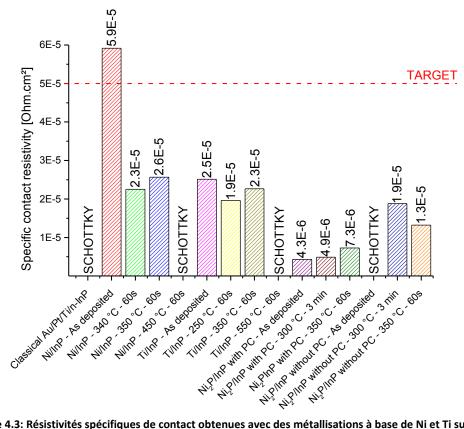

|            | 4.5.5          | Electrical characterization of Si-compatible metallizations on n-InP                         | 191         |

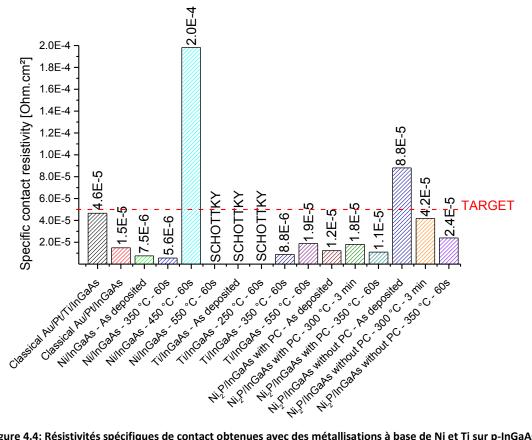

|            | 4.5.6          | Electrical characterization of Si-compatible metallizations on p-InGaAs                      | 194         |

|            | 4.5.7          | Conclusion on the choice of the metallization                                                | 196         |

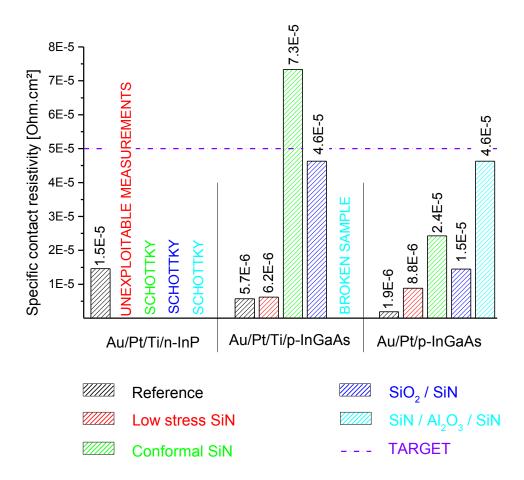

| 4.6        | Impac          | t of the dielectric stack on the contact resistivity                                         | 198         |

|            | 4.6.1          | Experimental procedure                                                                       | 198         |

|            | 4.6.2          | Experimental results                                                                         | 199         |

|            | 4.6.3          | Conclusion on the impact of the dielectric encapsulation                                     | 204         |

| 4.7        | Conclu         | usion                                                                                        | 205         |

| GENE       | RAL <b>C</b> O | nclusion2                                                                                    | 213         |

| APPEI      | NDIX           | 2                                                                                            | <u>2</u> 17 |

| A1.<br>com |                | termination of the Transmittance, Reflectance and Absorbance of the dielector is [Chapter 2] |             |

TABLE OF CONTENTS V

| CONT  | RIBUTIONS 269                                                                             |

|-------|-------------------------------------------------------------------------------------------|

| Résur | <i>π</i> É EN FRANÇAIS243                                                                 |

| A5.   | Transmission Line Model (TLM) and specific contact resistivity extraction [Chapter 4] 236 |

| A4.   | Current transport mechanisms in a M/SC system [Chapter 4]                                 |

|       | Metallurgical study of the Ti/InGaAs system: determination of the phase sequence [Chapter |

| A2.   | Determination of the refractive index of the dielectric compounds [Chapter 2] 223         |

# **List of Acronyms**

# Α

| A    |                                         |  |  |

|------|-----------------------------------------|--|--|

| AFM  | Atomic Force Microscopy                 |  |  |

| AES  | Auger Electron Spectroscopy             |  |  |

|      | В                                       |  |  |

| вох  | Buried Oxide                            |  |  |

| BEOL | Back-End Of Line                        |  |  |

| C    |                                         |  |  |

| CMOS | Complementary Metal Oxide Semiconductor |  |  |

| CVD  | Chemical Vapor Deposition               |  |  |

| СМР  | Chemical-Mechanical Polishing           |  |  |

| CELO | Confined Epitaxial Lateral Growth       |  |  |

VIII LIST OF ACRONYMS

| СТІМ     | Circular Transfer Length Method                         |  |

|----------|---------------------------------------------------------|--|

| D        |                                                         |  |

| DIGS     | Defect-Induced Gap States                               |  |

| DFB      | Distributed Feedback Laser                              |  |

|          | E                                                       |  |

| ESH      | Environment Security Health                             |  |

| EDS /EDX | Energy-Dispersive X-Ray spectroscopy                    |  |

|          | F                                                       |  |

| FIB      | Focused Ion Beam                                        |  |

| FEOL     | Front-End Of Line                                       |  |

| FFT      | Fast Fourier Transform                                  |  |

| FE       | Field Emission                                          |  |

| н        |                                                         |  |

| HF       | Hydrofluoric acid                                       |  |

| HRTEM    | High Resolution Transmission Electron Microscopy        |  |

| ı        |                                                         |  |

| ITRS     | International Technology Roadmap for Semiconductors     |  |

| ICP      | Inductively Coupled Plasma                              |  |

| L        |                                                         |  |

| LASER    | Light Amplification by Stimulated Emission of Radiation |  |

LIST OF ACRONYMS IX

| M         |                                                   |  |  |

|-----------|---------------------------------------------------|--|--|

| MQW       | Multi Quantum Well                                |  |  |

| MEOL      | Middle-End Of Line                                |  |  |

| MEMS      | Micro-Electro-Mechanical Systems                  |  |  |

| MIGS      | Metal Induced Gap States                          |  |  |

| MOSFET    | Metal Oxide Semiconductor Field Effect Transistor |  |  |

|           | Р                                                 |  |  |

| PIC       | Photonic Integrated Circuit                       |  |  |

| PVD       | Physical Vapor Deposition                         |  |  |

| PECVD     | Plasma Enhanced Chemical Vapor Deposition         |  |  |

| PDF       | PDF Powder Diffraction Files                      |  |  |

|           | R                                                 |  |  |

| RTP / RTA | Rapid Thermal Processing / Annealing              |  |  |

| RTA       | Rapid Thermal Annealing                           |  |  |

| RMS       | Root Mean Square                                  |  |  |

| S         |                                                   |  |  |

| SOI       | Silicon On Insulator                              |  |  |

| SCH       | Separate Confinement Heterostructure              |  |  |

| SCL       | Separate Confinement Layer                        |  |  |

X LIST OF ACRONYMS

| SEM  | Scanning Electron Microscope                                                                  |  |

|------|-----------------------------------------------------------------------------------------------|--|

| SBH  | Schottky Barrier Height                                                                       |  |

| SIMS | Secondary Ion Mass Spectrometry                                                               |  |

| SAD  | Selected Area Diffraction                                                                     |  |

|      | Т                                                                                             |  |

| TEOS | Tetraethyl orthosilicate (chemical formula: Si(OC <sub>2</sub> H <sub>5</sub> ) <sub>4)</sub> |  |

| TEM  | Transmission Electron Microscopy                                                              |  |

| TOF  | Time Of Flight                                                                                |  |

|      | Transmission Line Model                                                                       |  |

| TLM  | Transfert Length Method                                                                       |  |

| TE   | Thermionic Emission                                                                           |  |

| TFE  | Thermionic Field Emission                                                                     |  |

| X    |                                                                                               |  |

| XRR  | X-Ray Reflectometry                                                                           |  |

| XRD  | X-Ray Diffraction                                                                             |  |

| XPS  | X-ray Photoelectron Spectroscopy                                                              |  |

LIST OF SYMBOLS XI

# **List of Symbols**

| Symbol          | Signification                                                               | Units                               |  |  |  |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------|--|--|--|

|                 | A                                                                           |                                     |  |  |  |

| a               | Length of the contact (TLM)                                                 | nm / μm                             |  |  |  |

| A*              | Effective Richardson constant for thermionic emission                       | A.cm <sup>-2</sup> .K <sup>-2</sup> |  |  |  |

| A**             | Effective reduced Richardson constant for thermionic emission               | A.cm <sup>-2</sup> .K <sup>-2</sup> |  |  |  |

|                 | D                                                                           |                                     |  |  |  |

| D <sub>n</sub>  | Diffusion coefficient for electrons                                         | cm <sup>2</sup> .s <sup>-1</sup>    |  |  |  |

| E               |                                                                             |                                     |  |  |  |

| е               | Elementary charge                                                           | eV                                  |  |  |  |

| E <sub>0</sub>  | Vacuum level energy                                                         | J                                   |  |  |  |

| E <sub>00</sub> | Characteristic energy for the determination of the dominant conduction mode | J                                   |  |  |  |

| E <sub>b</sub>  | Schottky barrier height                                                     | J                                   |  |  |  |

| E <sub>C</sub>  | Conduction band energy                                                      | J                                   |  |  |  |

| E <sub>F</sub>  | Fermi level                                                                 | J                                   |  |  |  |

XII LIST OF SYMBOLS

| E <sub>FM</sub>   | Metal Fermi level                                                                | J                  |

|-------------------|----------------------------------------------------------------------------------|--------------------|

| E <sub>FSC</sub>  | Semiconductor Fermi level                                                        | J                  |

| E <sub>g</sub>    | Semiconductor bandgap                                                            | J / eV             |

| E <sub>V</sub>    | Valence band energy                                                              | J                  |

|                   | F                                                                                |                    |

| h                 | Plank constant                                                                   | J.s                |

| ħ                 | Reduced Plank constant                                                           | J.s                |

|                   | l I                                                                              |                    |

| I                 | Current                                                                          | А                  |

|                   | J                                                                                |                    |

| J                 | Current density                                                                  | A.cm <sup>-2</sup> |

| J <sub>M→SC</sub> | Current density with a flux from metal to semiconductor                          | A.cm <sup>-2</sup> |

| J <sub>n</sub>    | Electron flux current density                                                    | A.cm <sup>-2</sup> |

| J <sub>sc→M</sub> | Current density with a flux from semiconductor to metal                          | A.cm <sup>-2</sup> |

| J <sub>FE</sub>   | Reverse saturation current density in FE (field emission) conduction mode        | A.cm <sup>-2</sup> |

| J <sub>TE</sub>   | Reverse saturation current density in TE (thermionic emission) conduction mode   | A.cm <sup>-2</sup> |

| J <sub>TED</sub>  | Reverse saturation current density in thermionic emission diffusion theory       | A.cm <sup>-2</sup> |

| J <sub>TFE</sub>  | Reverse saturation current density in thermionic field emission diffusion theory |                    |

| J <sub>D</sub>    | Reverse saturation current density in diffusion theory                           | A.cm <sup>-2</sup> |

|                   | К                                                                                |                    |

| k, k <sub>B</sub> | Boltzmann constant                                                               | J.K <sup>-1</sup>  |

|                   | L                                                                                |                    |

| l <sub>i</sub>    | Spacing between two adjacent contacts (TLM)                                      | m                  |

| L                 | 1                                                                                |                    |

LIST OF SYMBOLS XIII

| L <sub>T</sub>                  | Transfer lenght                                                     | nm / μm                |

|---------------------------------|---------------------------------------------------------------------|------------------------|

|                                 | M                                                                   |                        |

| m*                              | Majority carriers effective mass                                    | Kg                     |

| m <sub>T</sub> *                | Majority carriers tunneling effective mass                          | Kg                     |

|                                 | N                                                                   |                        |

| $N_{A,}N_{a}$                   | Acceptor impurities concentration                                   | at.cm <sup>-3</sup>    |

| N <sub>C</sub>                  | Density of states in the conduction band                            | at.cm <sup>-3</sup>    |

| N <sub>D</sub> , N <sub>d</sub> | Donor impurities concentration                                      | at.cm <sup>-3</sup>    |

| n(x)                            | Charge carriers concentration (electrons)                           | cm <sup>-3</sup>       |

|                                 | 0                                                                   |                        |

| R <sub>C</sub>                  | Contact resistance                                                  | Ω                      |

| R <sub>E</sub>                  | End resistance                                                      | Ω                      |

| R <sub>SH</sub>                 | Sheet resistance of the bulk semiconductor                          | Ω / Ω.sq <sup>-1</sup> |

| R <sub>SK</sub>                 | Sheet resistance of the semiconductor underneath the contact region | Ω / Ω.sq <sup>-1</sup> |

| R <sub>sub</sub>                | Resistance of the substrate                                         | Ω                      |

| R <sub>tot</sub>                | Total resistance measured                                           | Ω                      |

|                                 | Т                                                                   |                        |

| Т                               | Absolute temperature                                                | К                      |

|                                 | V                                                                   | I                      |

| V                               | Voltage                                                             | V                      |

| V <sub>a</sub>                  | Applied voltage                                                     |                        |

| V <sub>bi</sub>                 | Built-in voltage                                                    | V                      |

| V <sub>F</sub>                  | Forward bias                                                        | V                      |

| $V_R$                           | Reverse bias                                                        | V                      |

XIV LIST OF SYMBOLS

|                | W                                                                                     |                                                   |  |  |

|----------------|---------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

| W              | Width of the contacts (TLM)                                                           |                                                   |  |  |

| $W_{dep}$      | Space charge region width                                                             | nm                                                |  |  |

|                | X                                                                                     |                                                   |  |  |

| X <sub>m</sub> | Distance from the metal / semiconductor interface of the extremum of potential energy |                                                   |  |  |

|                | γ                                                                                     |                                                   |  |  |

| γ              | Sensibility of the Schottky barrier to the metal work function                        | -                                                 |  |  |

|                | δ                                                                                     |                                                   |  |  |

| δ              | Interfacial layer thickness                                                           | Å                                                 |  |  |

| ΔΦ             | Image-force barrier lowering                                                          | eV                                                |  |  |

|                | ε                                                                                     |                                                   |  |  |

| E (chap II)    | Electric field                                                                        | V.cm <sup>-1</sup>                                |  |  |

| $\epsilon_0$   | Permittivity of vacuum                                                                | F.m <sup>-1</sup>                                 |  |  |

| ٤ <sub>s</sub> | Permittivity of semiconductor                                                         | F.m <sup>-1</sup>                                 |  |  |

|                | μ                                                                                     |                                                   |  |  |

| μ              | Carrier mobility                                                                      | cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> |  |  |

| $\mu_{n}$      | Electron mobility                                                                     | cm <sup>2</sup> .V <sup>-1</sup> .s <sup>-1</sup> |  |  |

|                | ρ                                                                                     |                                                   |  |  |

| ρ <sub>c</sub> | Specific contact resistivity                                                          | Ω.cm²                                             |  |  |

|                | ф                                                                                     |                                                   |  |  |

| Φ <sub>0</sub> | Charge neutrality level (relative to the valence band)                                | eV                                                |  |  |

| Фь             | Schottky barrier height                                                               | eV                                                |  |  |

| $\Phi_{bn}$    | Effective Schottky barrier height for electrons                                       | eV                                                |  |  |

| Фьр            | Effective Schottky barrier height for holes                                           | eV                                                |  |  |

| Фм             | Metal work function                                                                   | eV                                                |  |  |

LIST OF SYMBOLS XV

| $\Phi_{n}$  | Position of the Fermi level relative to $E_{\text{c}}$ (n-type semiconductor) | eV |  |

|-------------|-------------------------------------------------------------------------------|----|--|

| Фѕс         | Semiconductor work function                                                   | eV |  |

| Х           |                                                                               |    |  |

| Х           | Semiconductor affinity                                                        | eV |  |

| ψ           |                                                                               |    |  |

| $\psi_{bi}$ | ψ <sub>bi</sub> Built in potential                                            |    |  |

GENERAL INTRODUCTION 1

# **GENERAL INTRODUCTION**

Since the 2000s, the requirements in terms of data exchange never stopped rising owing to a multitude of emerging communication means. These extensive modifications lead the signal processing and electrical technologies to switch towards optical devices and interconnections. Among others, these new technologies require the use of III-V-based emitters and receptors which are traditionally processed in III-V dedicated clean rooms on 2" to 4" wafers before being packaged in optoelectronic systems. In order to miniaturize these devices, to optimize the performances and to minimize the fabrication cost of such a technology, an innovative manufacturing model consists in integrating directly the III-V laser source onto the 200 mm Si photonics circuit. However, up to now these 200 mm wafers were reduced to 100 mm wafers after the bonding of the III-V laser and processed in III-V-dedicated clean rooms. In order to leverage the advantages of utilizing the silicon expertise and the existing Si-compatible equipments, an innovative integration is being developed by STMicroelectronics and the CEA-LETI in the frame of IRT Nanoelec Photonics programs. The latter consists in fully integrating the III-V laser on the 200 mm Silicon Photonics wafer and therefore in a 200 mm Si-compatible clean room after its bonding. In order to enable such an integration, one of the keys lies in the development of contacts on n-InP and p-InGaAs which are necessary to electrically pump the III-V laser. Because the contacts that were classically used on III-V lasers up to now are not compatible with a Si-compatible clean room in terms of integration and composition, a deep overhaul is required. The latter must enable the development of contacts meeting the constraints of a Si-environment along with those of an operating laser, i.e.:

- The contacts must be integrated on 200 or 300 millimeters-compatible equipments in a Sicompatible clean room thanks to planar processes which exclude any lift-off or related processes;

- All thermal budget must be minimized (T ≤ 450 °C) in order not to degrade the active region

of the laser composed of multi quantum wells;

- The materials in contact with / close to the active region of the laser must not generate important losses at the emitting wavelength of the laser;

- The contacts must be comprised of front-end compatible materials only, such as Ni, Ti and their alloys;

- The metallization must be selected to form ohmic contacts with specific contact resistivities lower than  $5.10^{-5} \, \Omega.\text{cm}^2$ .

2 GENERAL INTRODUCTION

Within this framework and in order to satisfy the above mentioned requirements, this Ph.D thesis was dedicated to the development of such innovative contacts.

After presenting the benefits offered by Silicon Photonics, Chapter 1 will present an overview of III-V / Si heterogeneous photonic integrated circuits. Several notions related to the integration and to the functioning of the III-V laser will be discussed in order to identify the critical parameters that could affect its functioning. The contacts that were classically integrated on III-V lasers in III-V dedicated clean rooms will then be presented in terms of composition and integration. This section will highlight the incompatibility of such contacts with 200 mm or 300 mm Si-compatible clean rooms, and therefore the need to develop innovative contacts.

Chapter 2 will thus be dedicated to the presentation of the innovative contacts' integration scheme that was fully developed in the 200 mm Si-compatible clean room. A special emphasis will be placed on optimizing the contacts while fulfilling the requirements of such an environment and without degrading the optical performances of the III-V laser.

After the overall presentation of the integration scheme, a particular attention will be paid to the contact metallization which must be chosen to form thermally stable and ohmic contacts both on n-InP and p-InGaAs. In order to develop fully Si-compatible contacts, the two metals that will be assessed are the Ni and the Ti. In chapter 3, the as deposited an annealed Ni/InP, Ni/InGaAs and Ti/InP systems will firstly be investigated thanks to metallurgical studies. The latter will enable an identification of the system's composition and morphology along with the related phase sequences and involved mechanisms.

Finally, chapter 4 will focus on the corresponding electrical study. After a description of the current transport mechanisms arising in a metal / semiconductor contacts, the Transfert Length Method (TLM), classically used to extract contact resistivities, will be presented and discussed. After these theoretical considerations, Si-compatible contacts presenting Ni and Ti-based metallizations will be electrically characterized thanks to dedicated test structures. Finally, in order to further optimize the electrical performances of these contacts, the effect of the dielectric encapsulation which is required in the frame of the innovative integration scheme will be probed.

To conclude, a scheme enabling the integration of the contacts on a III-V laser in a Si-compatible clean room will be displayed. The extensive studies conducted on the metallization will additionally enable the identification of the most adapted metal and subsequent thermal treatment on n-InP and p-InGaAs. Additional refinements will be proposed in order to further optimize the performances of the contacts and therefore of the overall laser device.

# **CHAPTER 1**

# **INTRODUCTION TO SILICON PHOTONICS**

# Outline

- 1.1 The information revolution

- 1.2 Silicon photonics

- 1.3 III-V heterogeneous integration on Silicon

- 1.4 The III-V laser structure

- 1.5 The optical gain and losses

- 1.6 The electrical pumping of the laser: contacts to n-InP and p-InGaAs

- 1.7 Conclusion

THE INFORMATION REVOLUTION 5

#### 1.1 The information revolution

Over the past decades the computing power of Complementary Metal Oxide Semiconductor (CMOS) based devices has considerably increased. While the dimensions of the transistors were scaled down, their integration density and switching speed never stopped rising. We have now reached a point where the calculation capacity is less limited by the performances of the devices than by the rate at which the data can be transferred. In this context, the electrical interconnects were identified as the upcoming bottleneck in the International Technology Roadmap for Semiconductors (ITRS) [1, 2]. It has become increasingly difficult for conventional metal based electrical interconnects to satisfy the design requirements in terms of power, bandwidth, delay and delay uncertainty. To address this issue, a transition from electrical to optical interconnects was proposed [1-5].

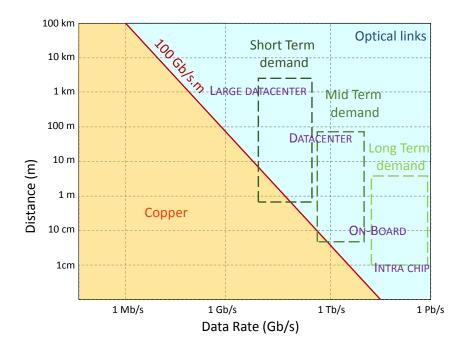

Optical interconnects offer various advantages ranging from wider bandwidths on longer distances and lower sizes to their insensibility to the electromagnetic noise. However, because of the cost advantage of their electrical counterparts, optical interconnects have usually ended up to be limited to long-distance links where the attenuation in copper cables is too high for the electrical circuits to compensate. Yet, their use becomes more and more required in the market of short distance links as they can meet the requirements in terms of data rates (Figure 1.1). To enable such a transition, optical technologies must be brought into the world of mass production.

Figure 1.1: Distance versus data rates of commercial electrical and optical interconnects. Electrical links are bounded by the 100 Gb/s-m bandwidth-distance product [6, 7].

# 1.2 Silicon photonics

# 1.2.1 Why do we need silicon photonics?

Following the path of miniaturization and integration in electronics, the concept of Photonic Integrated Circuit (PIC) emerged. The co-integration of several optical components on a chip opens the way to a miniaturization, a lowering of the manufacturing costs along with an increase of the complexity and performances of such devices. The integration of these optical components on Silicon wafers was firstly proposed by R. Soref during the 80s [8, 9] and leverages the economic advantages of utilizing existing infrastructures.

The important index contrast between silicon (n = 3.51) and its oxide (n = 1.45) makes Silicon On Insulator (SOI) a suitable platform for the integration of most photonics components (multiplexers, mirrors, resonant cavities...). Additionally, silicon being transparent at the wavelengths used for optical communication transmission (1.3 – 1.55  $\mu$ m) SOI wafers are well adapted for optical guidance. Finally, this kind of wafers is widely used in microelectronics, abundant and available in large sizes (200 mm and 300 mm). The main issue lies in the fact that silicon cannot be used to produce the totality of the functions in a photonics circuit. While it is well adapted for the making of most active and passive components, its indirect band gap prevents it from being an efficient light emitter. In this respect, one solution is to heterogeneously co-integrate silicon with III-V materials such as InGaAs, InP and InGaAsP. The latter are indeed widely used for the making of stand-alone emitting devices such as laser diodes because of their direct bandgap.

The meeting point between the worlds of Silicon and optics is that of Silicon Photonics. The current challenge is to identify and develop integration schemes on hybrid devices that would benefit from the silicon expertise and meet the requisites of the emerging photonics applications. In this thesis, a special attention will be paid to the development of CMOS-compatible contacts on III-V-based laser devices in this respect.

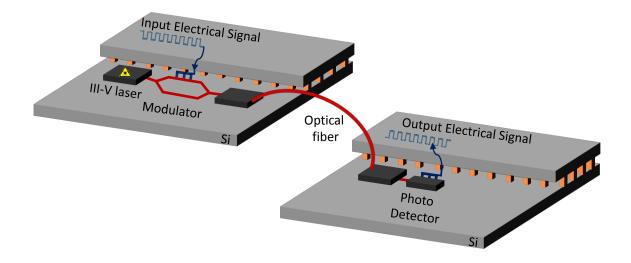

# 1.2.2 Description of a silicon photonics integrated circuit

In order to propagate the logical information from one hand of the device to the other, a silicon photonics circuit is made of several elementary components that we are briefly going to describe in the following section (Figure 1.2):

<sup>&</sup>lt;sup>1</sup> III-V materials are composed of with at least one group III element and at least one group V element in the periodic table.

- A photon source, such as a semiconductor-based laser diode, emits light at a defined wavelength. One or several sources can be used in the case of a signal multiplexing. In this case, the several lasers must emit at different wavelengths that will give rise to different channels.

- A modulator converts the electrical information coming from the electronics circuit into an optical signal. An example of modulator is a Mach-Zehnder<sup>2</sup>.

- A multiplexer is used to combine the several laser beams into one beam. The latter is separated into several channels (not shown in Figure 1.2).

- A waveguide or an optical fiber carries the optical signal to the other hand of the photonics circuit.

- A demultiplexer separates the various canals that where created by the multiplexer (not shown in Figure 1.2).

- Finally, a photo-detector converts the optical information into an electrical signal which will be processed in the CMOS circuit by the transistor afterwards.

Figure 1.2: Schematic representation of an optoelectronic circuit.

<sup>&</sup>lt;sup>2</sup> In a Mach-Zehnder interferometer a beam splitter divides the laser light beam into two paths, one of which can be modulated in phase. The two beams are then recombined. Changing the electric field on the phase modulating path will then determine whether the two beams interfere constructively or destructively at the output, and thereby create logical 0 or 1.

# 1.3 III-V heterogeneous integration on Silicon

Several integration schemes can be used for co-integrating the III-V devices with the Si ones. In the following sections, we will discuss the most common techniques to achieve integration of III-V with silicon.

# 1.3.1 Hetero-epitaxial growth of III-V on silicon

Epitaxial growth of III-V materials on silicon might appear as the most fitted solution as it does not involve any alignment procedure which is critical between the laser and the entrance of the optical circuit. However, the lattice mismatch between silicon and III-V compounds is very important (8% between Si and Indium Phosphide (InP) or Gallium-Indium Arsenide (In<sub>0.47</sub>Ga<sub>0.53</sub>As, noted InGaAs in the following). Their thermal expansion coefficients are also very different from one another ( $\alpha_{Si} = 2.6 \times 10^{-6} \, ^{\circ}\text{C}^{-1}$ ),  $\alpha_{InP} = 4.6 \times 10^{-6} \, ^{\circ}\text{C}^{-1}$ ,  $\alpha_{InGaAs} = 5.66 \times 10^{-6} \, ^{\circ}\text{C}^{-1}$ ). Both characteristics result in an important density of defects (dislocations, phase boundaries...) which are severely harmful in active components as they act as non-radiative recombination sites<sup>3</sup>. A solution is to use buffer layers for example combining InGaP, low temperature grown GaAs, InP and a superlattice of InP/InGaAs [10]. While these layers allow a confinement of the defects, they are very thick (several micrometers) and therefore prevent an efficient evanescent coupling of the photons between the active device and the waveguide.

The CELO (Confined Epitaxial Lateral Growth) technique was proposed to overcome these issues [11]. High quality and defects free InGaAs and InP layers were grown on SiO<sub>2</sub> thanks to this method. Based on it, an integration scheme enabling an evanescent coupling between III-V layers and a silicon waveguide was demonstrated [12].

# 1.3.2 Flip Chipping

Flip chipping is a mature process that consists in reporting the individually fabricated III-V active device on top of the circuit. The interconnections are realized thanks to gold or gold-tin solder bumps. The main advantage of the solution is that the two elements being independently developed, they can be tested separately and the constraints linked to one do not affect the other. On the other hand, the important alignment precision required between the laser and the optical entrance of the circuit results in a slow and expensive alignment process. Moreover, the distance separating them

<sup>&</sup>lt;sup>3</sup> Non-radiative recombination is a process in semiconductors whereby charge carriers recombine without releasing photons. A phonon is released instead. Non-radiative recombination in optoelectronics is an unwanted process as it lowers the light generation efficiency and increases heat losses.

typically corresponds to the thickness of the solder bumps, *i.e.*, a few micrometers, and further complicates the light coupling. Finally, the level of integration of such a technique is poor which results in a low compactness and in an increase of the fabrication costs.

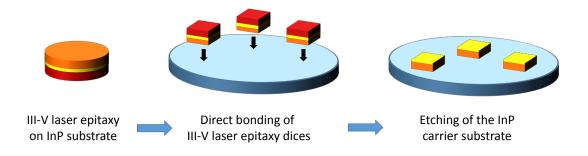

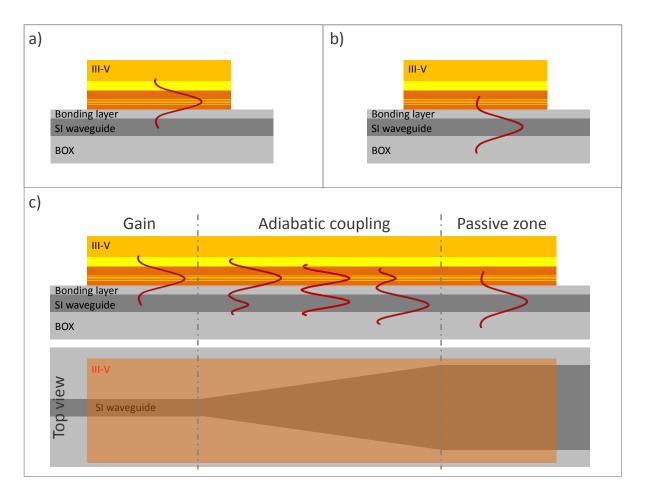

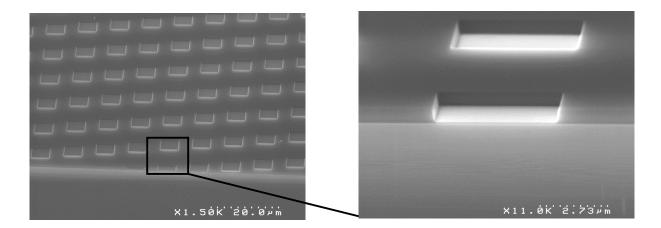

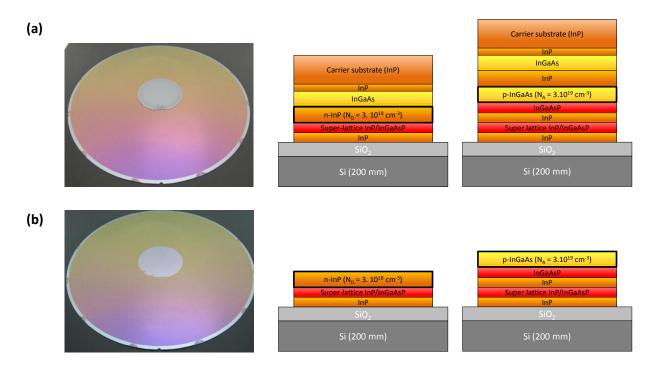

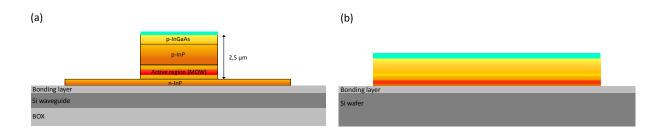

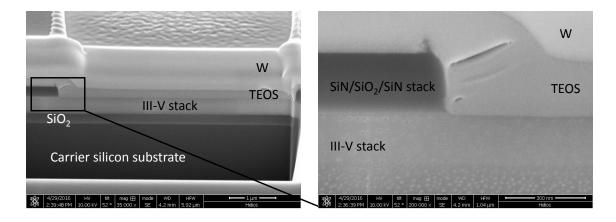

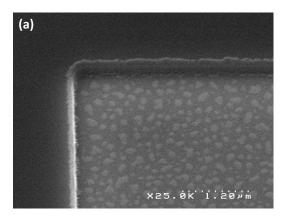

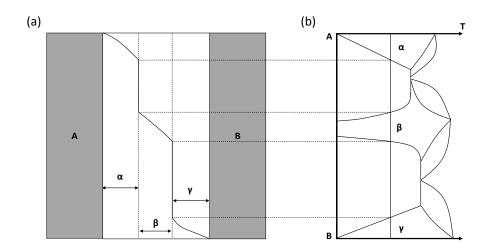

## 1.3.3 Bonding of III-V on silicon

The last integration solution consists in bonding the III-V laser stack on a SOI wafer. The III-V carrier substrate is then removed in order to reveal the laser stack (Figure 1.3). An etching of the III-V is finally performed on top of the Si-based devices to form the T-shaped laser. As a consequence the laser alignment precision is that of lithography, meaning that it is only of a few tens to a few hundreds of nanometers. This integration method also provides a high crystalline quality leading to a good emitting efficiency of the laser. Three main bonding techniques are available:

#### Metallic bonding

The metallic bonding is based on the use of a metallic alloy as a bonding agent. The most commonly used alloys are gold, tin and indium. The main advantage of this technique is that the bonding layer can also be used to dissipate a great part of the heat produced by the functioning devices. The main drawback is the important absorbency of such materials, leading to large losses in the case of evanescent coupling between the III-V laser and the waveguide located in the SOI wafer.

#### Polymer bonding

The polymer bonding uses the DVS-BCB (divinylsiloxane benzocyclobutene) as a bonding via. The thickness of the BCB layer can be relatively small (down to 30 nm) and does not lead to any optical losses [13]. This bonding technique is particularly adapted to surfaces that present particles and/or roughness as both would be compensated by a deformation of the BCB.

#### Direct bonding

The direct bonding utilizes the Van der Waals attraction that exists between two hydrophilic surfaces. To do so, an oxide layer (about 200 nm-thick) is either deposited on the substrates and planarized by chemical-mechanical planarization (CMP) or formed in an oxygen plasma. The two substrates are then put in contact at room temperature leading to the formation of Van der Waals bonds. A low temperature annealing process ( $T \approx 300~^{\circ}\text{C}$ ) converts these bonds into covalent ones. When using this technique, one can choose to bond III-V wafers (up to 150 mm [14]) or millimeters square dices to save the expensive III-V material. The main advantage of this technique compared to the polymer bonding is that oxide provides a better thermal conductivity than BCB ( $\sigma_{\text{oxide}} = 1.2$

W/M.m;  $\sigma_{BCB}$  = 0.3 W/M.m). This characteristic leads to a lower heating of the operating III-V laser and then to better emission characteristics. However, the direct bonding requires flat and defect-free surfaces (RMS roughness < 0.5 nm, bow < 10  $\mu$ m and [defects] < 100 cm<sup>-2</sup>). Because they share a high level of expertise in this field, the laser integration strategy followed by STMicroelectronics and the CEA-LETI exploits the direct bonding of III-V epitaxies on 200 mm SOI substrates.

Figure 1.3: Schematic representation of the direct bonding of III-V dices on Si substrates in the scope of Silicon Photonics.

#### 1.4 The III-V laser structure

### 1.4.1 The LASER effect

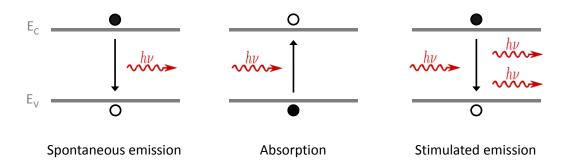

While several types of laser exist (e.g., the hybrid evanescent lasers developed by UCSB and Intel [15] or the DFB lasers developed by the Tokyo Institute of Technology [16]) all of them are based on the same physical principal: the stimulated emission of photons. This principal has its origins in quantum physics and was described for the first time by Albert Einstein in 1917 [17]. The stimulated emission is related to another quantum phenomenon: the stimulated absorption of photons.

The stimulated absorption of photons occurs when a photon is sent on an atom. The absorption of this photon enables the transition of an electron to an upper energy level. The stimulated emission takes place when a photon is sent on this excited electron. The latter being disturbed by the incident photon, it goes back to its initial state releasing a second photon which is identical in all respects to the first one (Figure 1.4). As a consequence, the emitted photon has the same propagation direction, phase and polarity as the incident photon. The laser effect corresponds to the use of the cascaded stimulated emission phenomenon which gives rise to a coherent amplification of the signal and then to the LASER effect (Light Amplification by Stimulated Emission of Radiation).

THE III-V LASER STRUCTURE 11

Figure 1.4: Illustration of the electronic transitions that can occur between the conduction band and the valence band in a semiconductor. The stimulated emission of photons gives rise to a coherent amplification of the signal.

#### 1.4.2 The laser structure

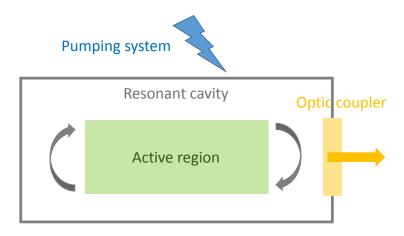

All lasers are composed of four basic building blocks as detailed in Figure 1.5: The *active region* is the zone where the stimulated emission of photons occurs. The latter relies on a population inversion that requires the supply of external energy provided by a *pumping system*. In order to maximize the probability of radiative recombination, the photons are forced to make round trips in the active region thanks to a *resonant cavity*. Finally, the created photons are extracted from the cavity and directed toward the waveguide by means of an *optic coupler*.

Figure 1.5: Schematic representation of the four elementary blocks constituting a laser: the active region, the resonant cavity, the pumping system and the optic coupler.

### Active region and resonant cavity

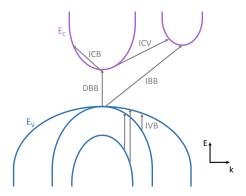

The active region of the laser corresponding to the zone where the photons are created, it must be composed of semiconductors that present a direct band gap. The choice of the materials that compose this region is a function of the targeted emission wavelength. For example, InGaAsP and AlGaInAs are commonly used in the telecommunications where wavelengths range from 1.3  $\mu$ m to 1.55  $\mu$ m [18-24]. The amplification of the signal is maximized thanks to the use of quantum wells

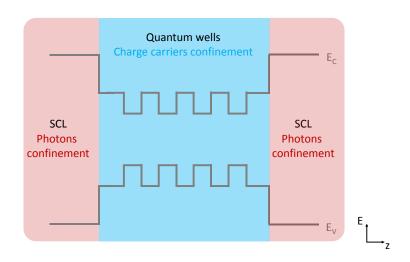

which confine the charge carriers. The probability of radiative recombination and thus the gain at a given polarization are therefore increased. The thickness of the layers forming these quantum wells can be decreased down to the De Broglie electrons wavelength, *i.e.*, down to a few nanometers. The photons must also be confined so that they can make round trips in the active region, once again increasing the probability of stimulated emission. However, the wavelength of photons in the infrared being in the range of a few micrometers, their confinement cannot be achieved thanks to the quantum wells. This contradiction leads to the idea of a separate confinement heterostructure (SCH). Several thin layers form the quantum wells where the electrons and holes are trapped, while thick external layers, the separate confinement layers (SCL) guide the optical modes of photons [25] (Figure 1.6).

Figure 1.6: Typical band diagram (energy of conduction band E<sub>C</sub> and valence band Ev versus growth direction) of quantum wells in separate confinement laser heterostructure (SCH).

#### **Pumping system**

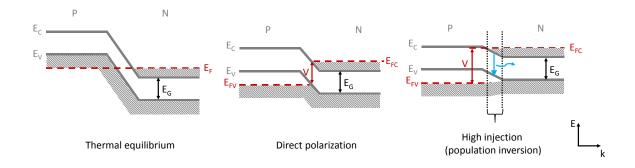

In order to obtain a net production of photons in the active region, the stimulated emission process must dominate over the absorption. To do so, electrons must be promoted in the conduction band and holes in the valence band for a given k. This phenomenon called population inversion requires the use of degenerated semiconductors and the supply of external energy. The first requirement restricts the quasi Fermi levels positions into the valence (p-doped semiconductor) and conduction (n-doped semiconductor) bands and is described by the Bernard and Duraffourg inequality (Equation 1.1) [26].

$$e.V = E_{F,C} - E_{F,V} > h.v = E_g$$

THE III-V LASER STRUCTURE 13

To meet the second requirement and supply the laser with energy, two main means are available: the optical and the electrical pumping. In the first case an external laser is used; its emitting energy must be higher than the band gap energy of the materials composing the active region. In this way, the atoms can be excited and emit photons when going back to their equilibrium state. When using the electrical pumping, the population inversion is achieved by integrating the quantum wells and SCH in a P-N junction. The polarization of the junction gives rise to the so called inversion zone. A subsequent voltage increase extends the width of this zone in the k space and increases as a consequence the radiative radiations as represented in Figure 1.7. We will see in the following sections that the lasers that we are dealing with in the frame of this PhD are electrically pumped, and therefore require the integration of innovative and efficient contacts.

Figure 1.7: Schematic representation of the obtaining of the so called population inversion obtained thanks to a polarized P-N junction.

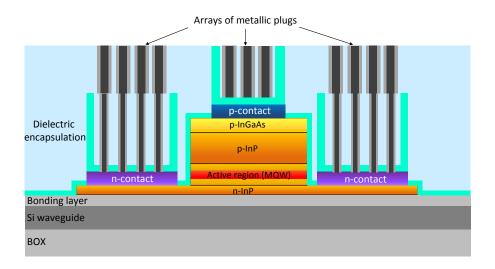

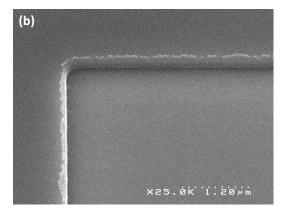

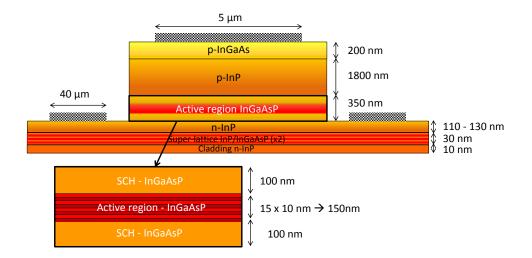

#### Resulting laser structure

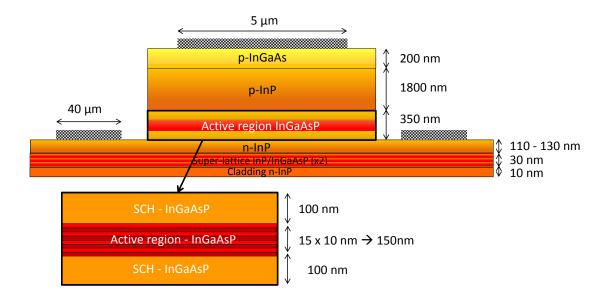

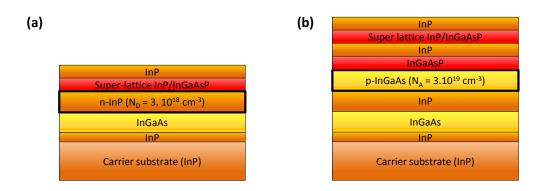

When combining these elementary components, the resulting laser structure is composed of an InP-based P-N junction in which the multi quantum wells and SCL are placed. In STMicroelectronics and CEA-LETI's devices, this active region is composed of  $InGa_xAs_{1-x}P_y$  layers emitting between 1.3 and 1.55 µm. Metallic contacts are integrated on each side of the P-N junction in order to electrically pump it. In this respect and to favor the formation of ohmic contacts ( $\Phi_M > \Phi_{SC}$ , where  $\Phi_M$  and  $\Phi_{SC}$  are respectively the work function of the metal and of the p-doped semiconductor), an additional p-InGaAs layer is epitaxially grown on top of the p-InP ( $\Phi_{p-InP} = 5.65$  eV and  $\Phi_{p-InGaAs} = 5.29$  eV). Finally, an InP/InGaAsP super lattice and an InP layer are added at the base of the laser to facilitate the bonding process. The arising laser structure is schematized in Figure 1.8.

Figure 1.8: InP/InGaAsP-based laser structure used in STMicroelectronics and in the CEA-LETI. Note that the laser length is about 500 μm.

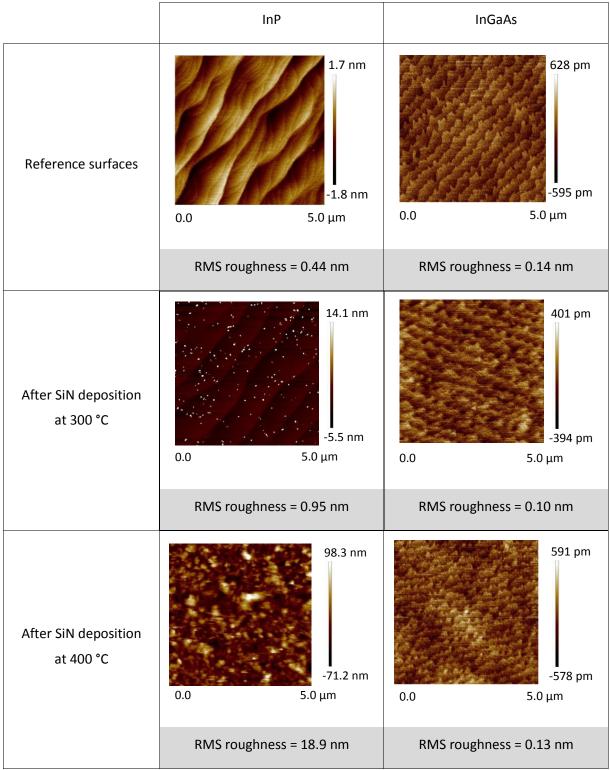

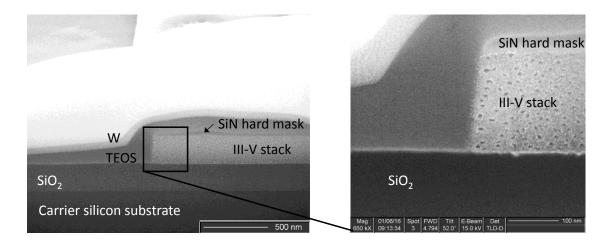

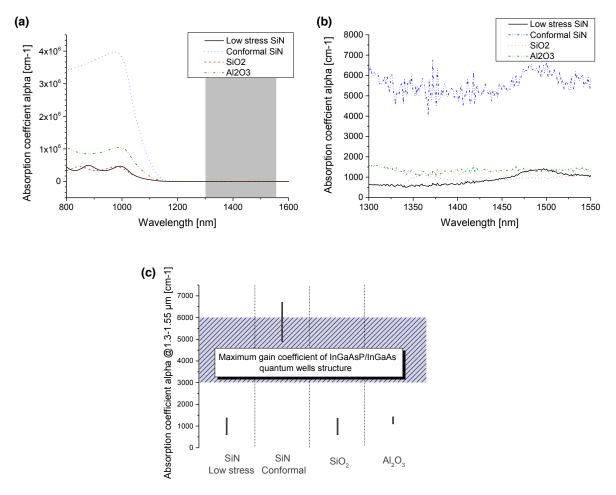

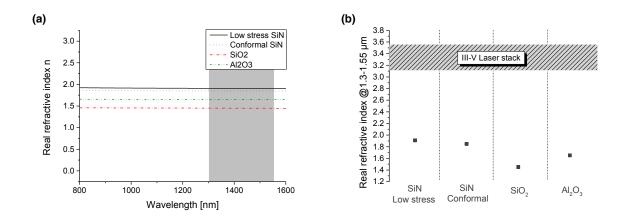

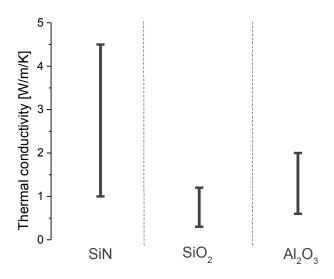

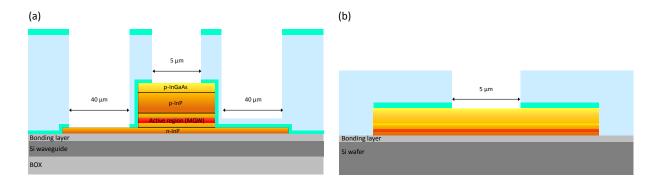

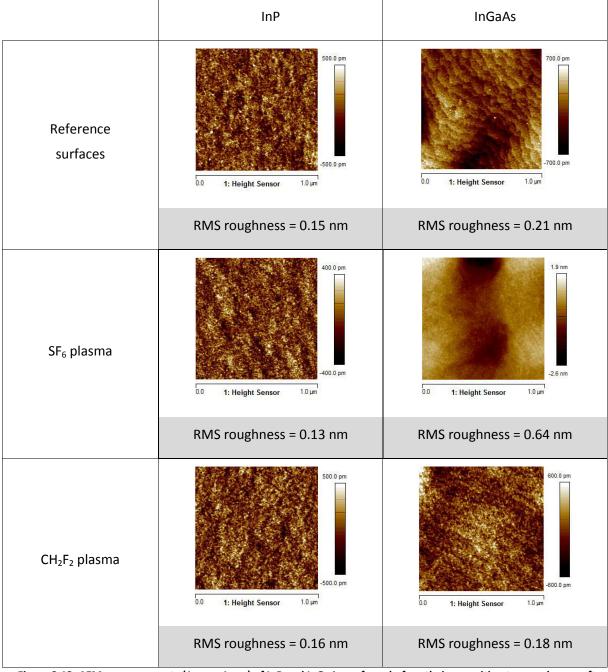

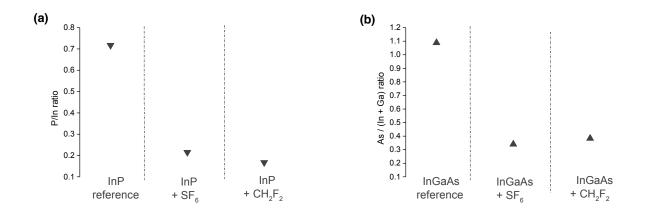

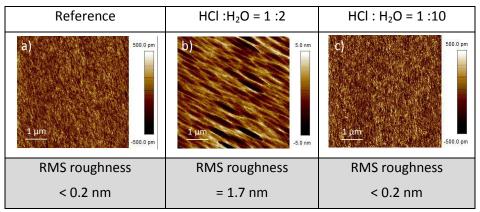

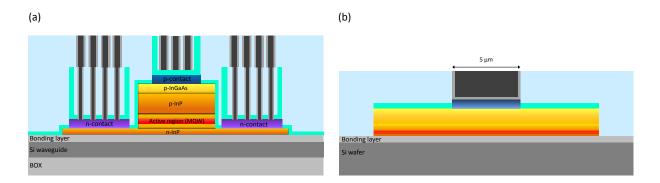

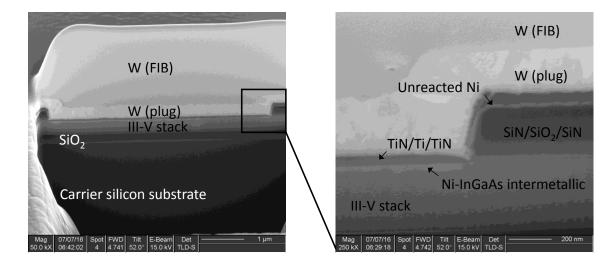

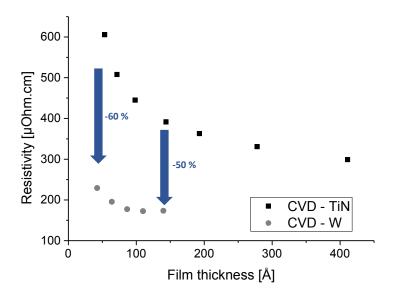

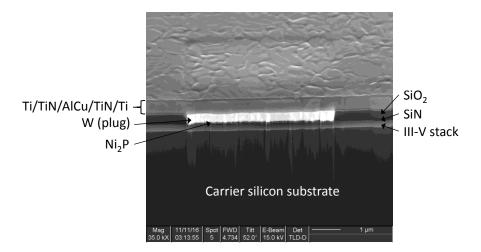

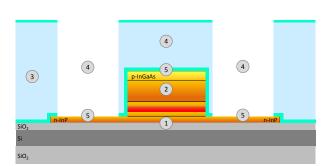

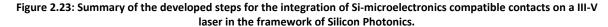

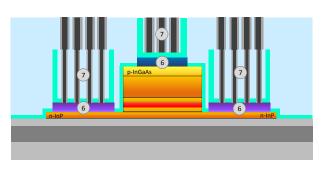

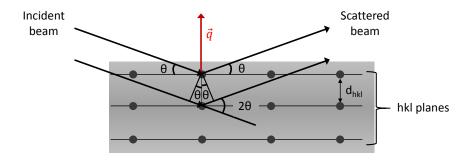

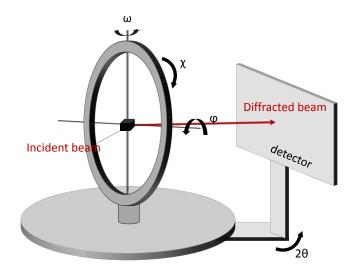

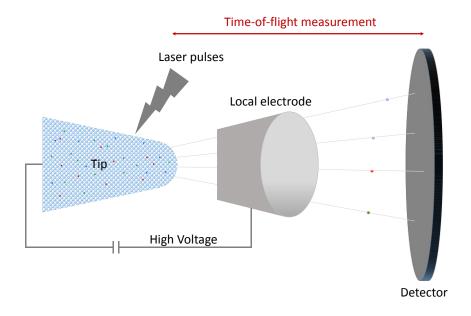

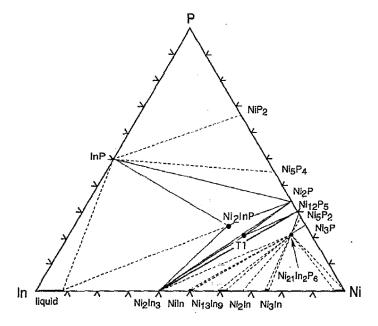

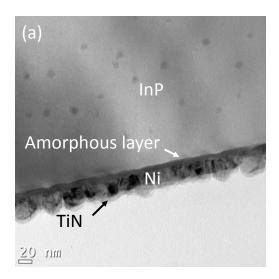

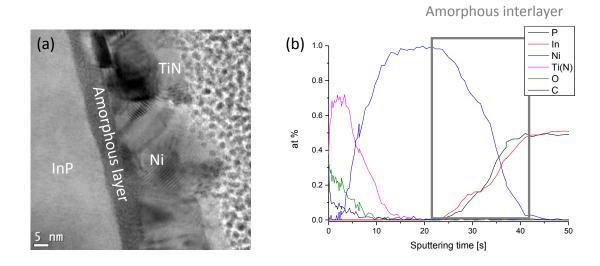

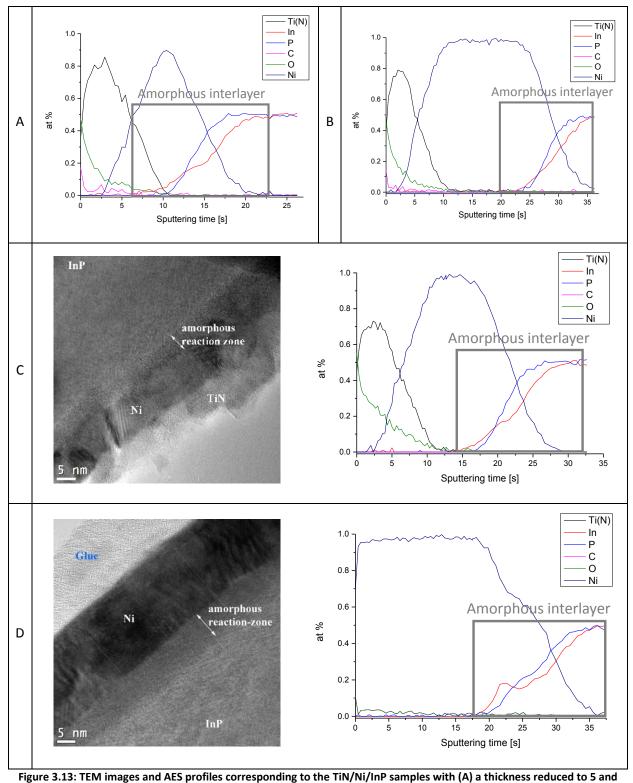

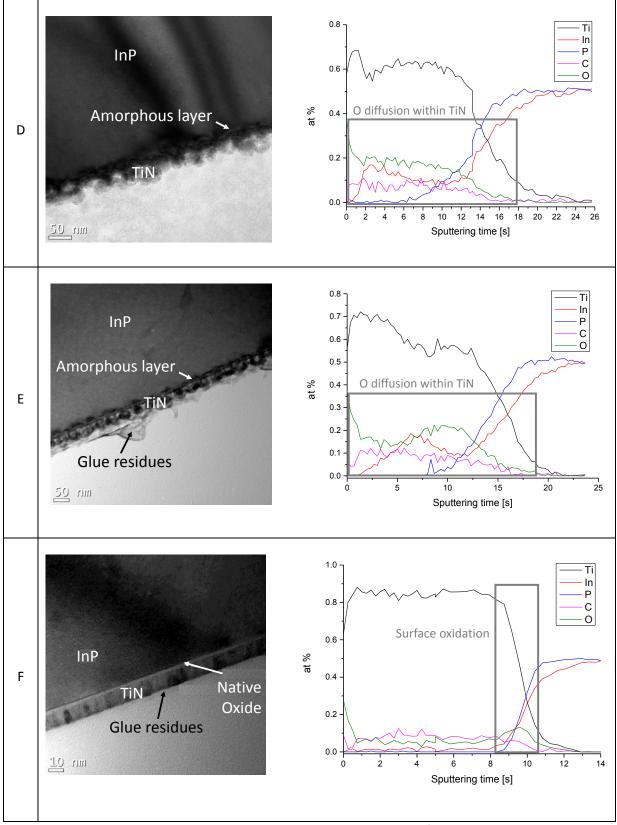

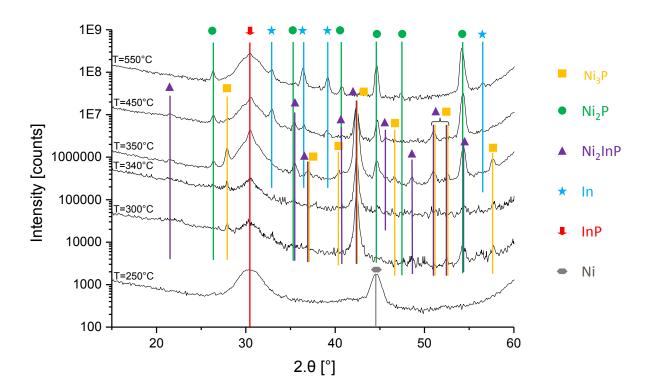

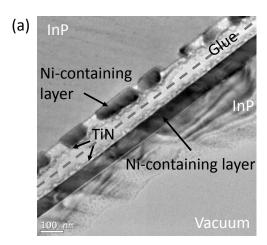

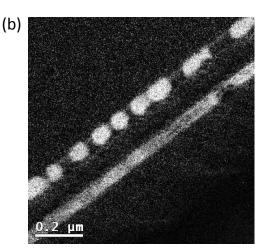

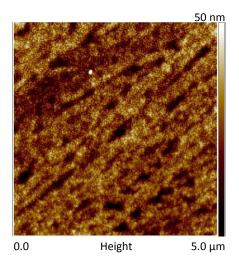

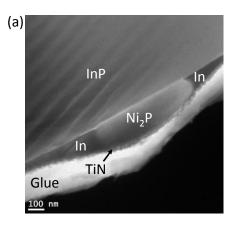

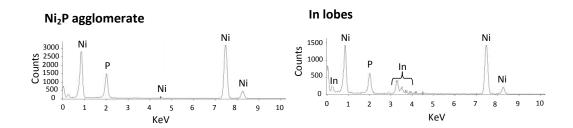

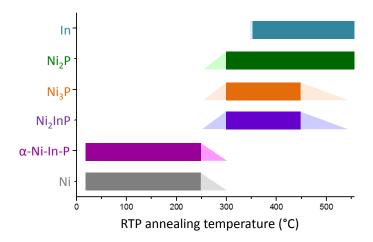

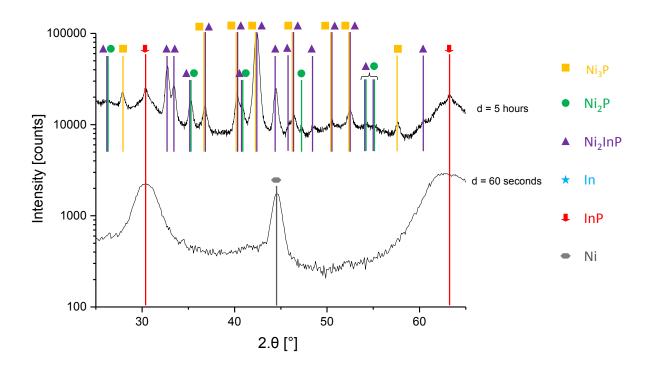

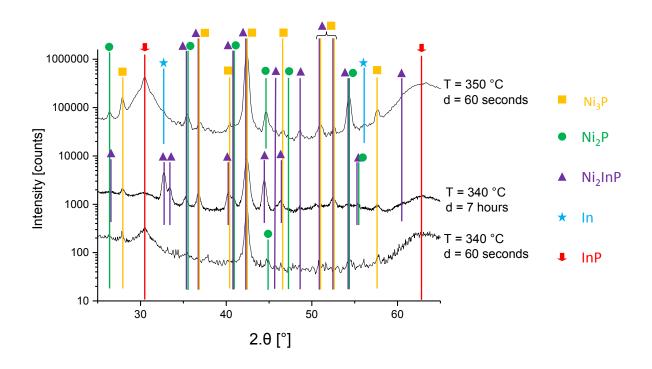

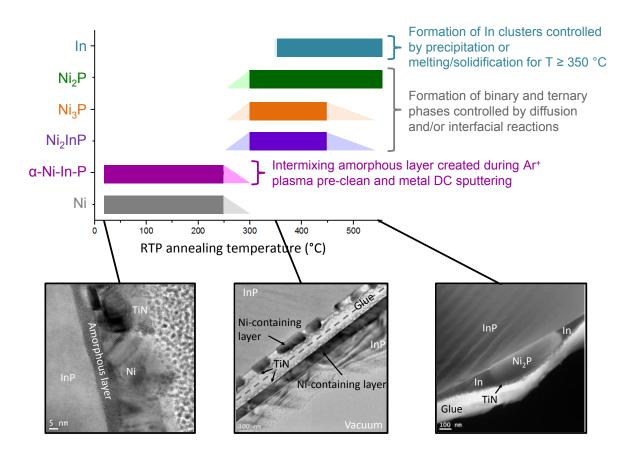

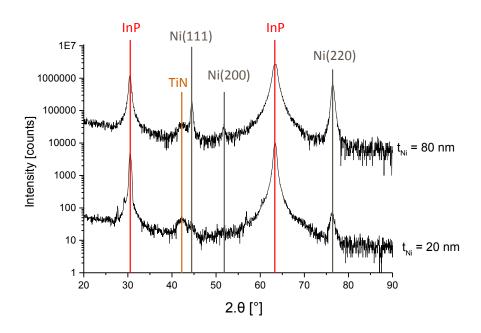

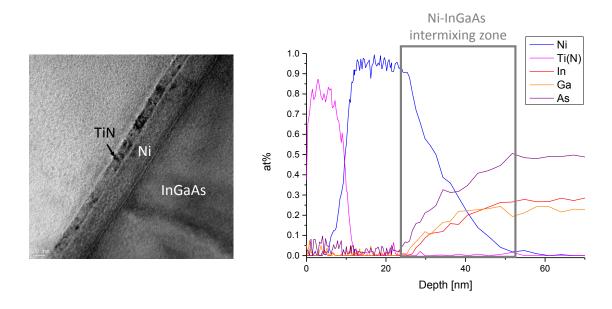

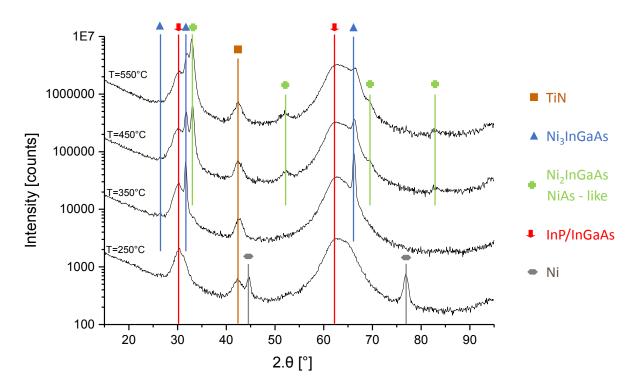

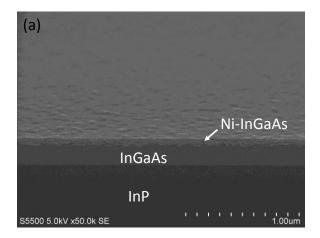

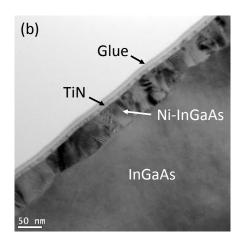

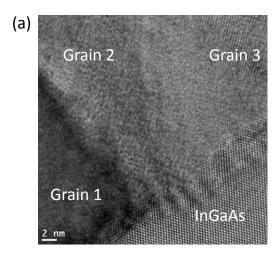

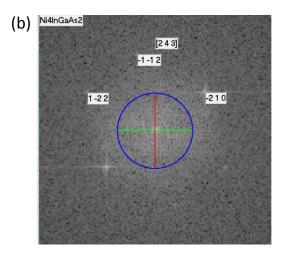

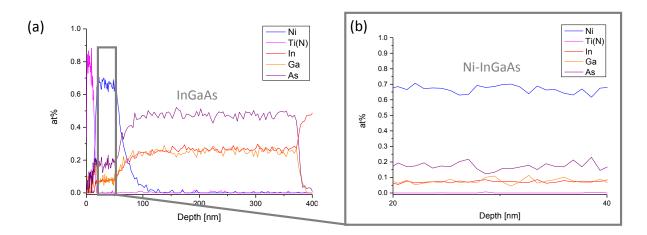

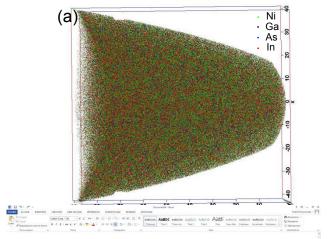

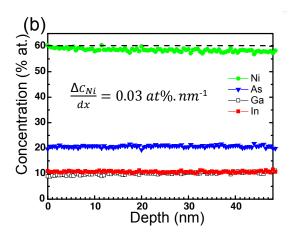

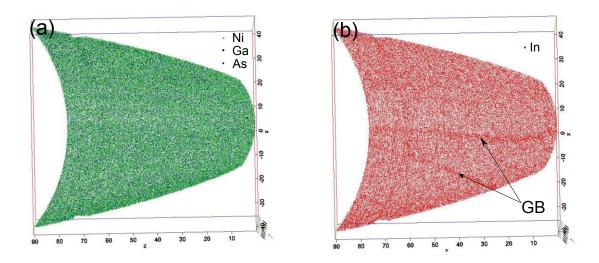

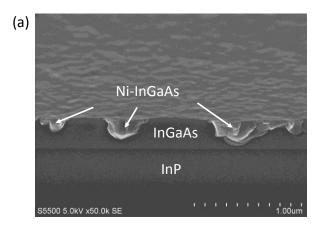

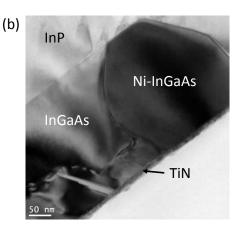

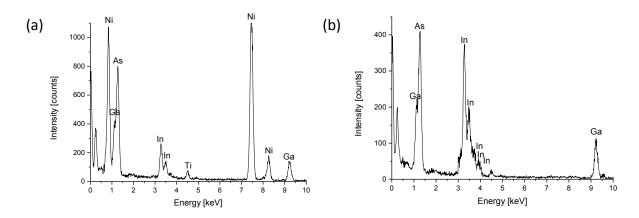

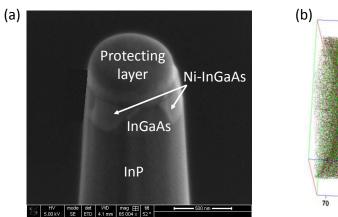

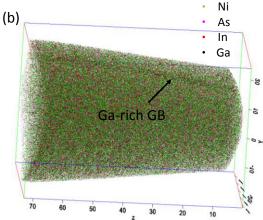

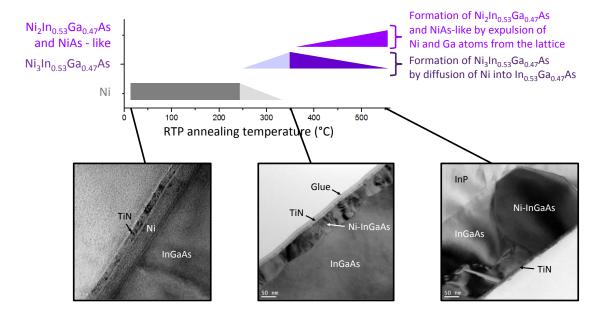

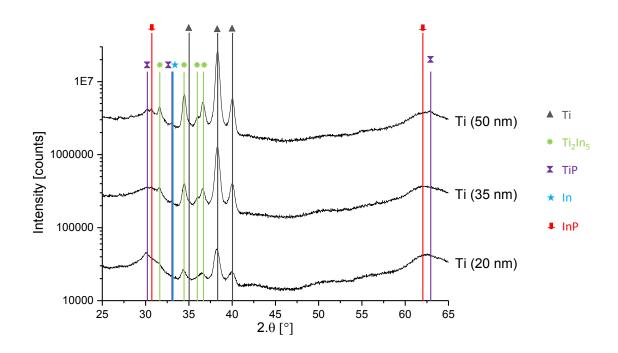

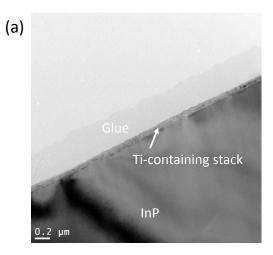

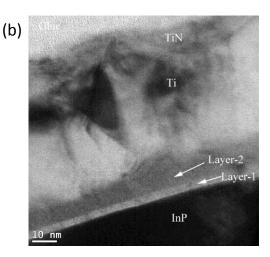

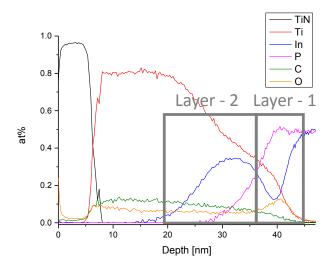

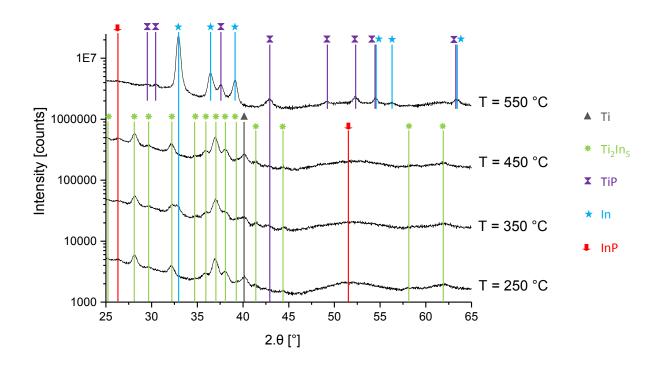

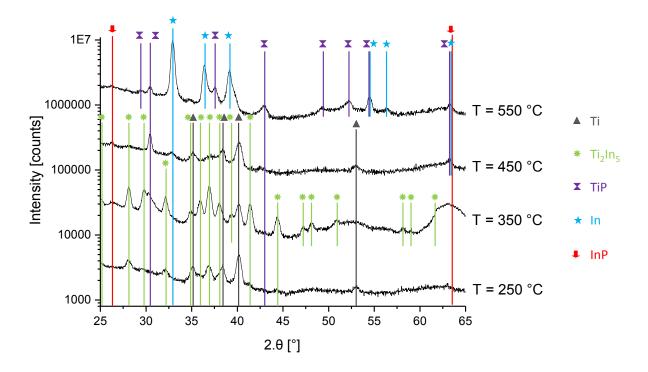

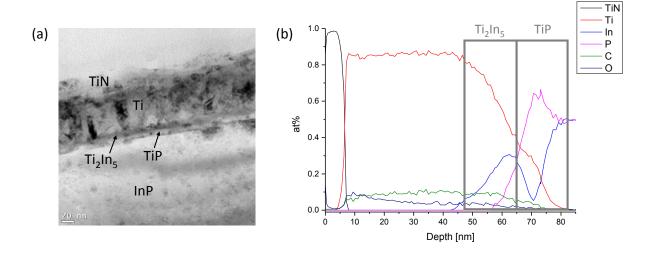

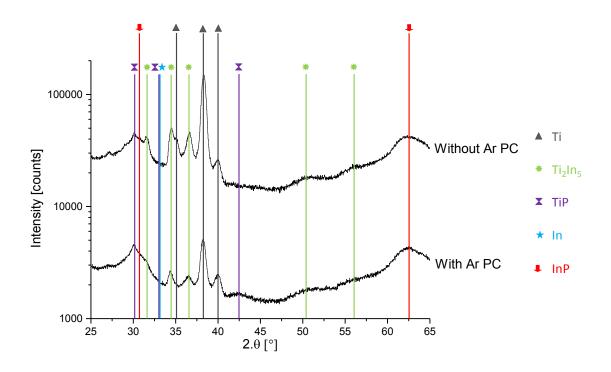

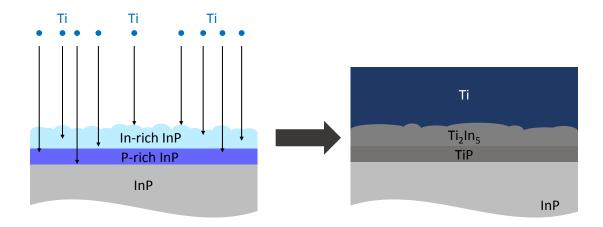

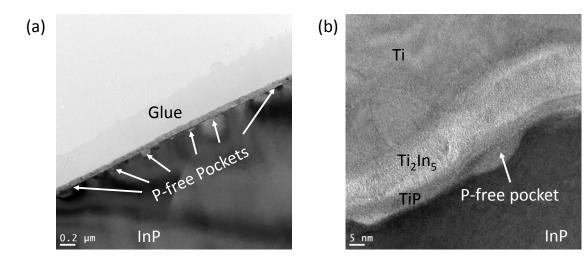

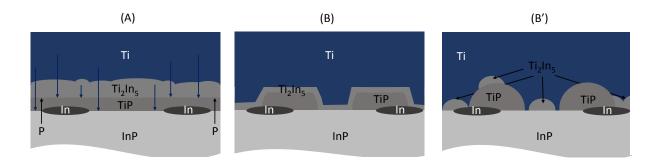

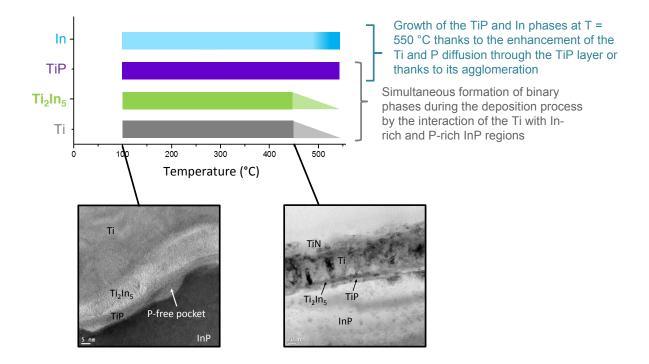

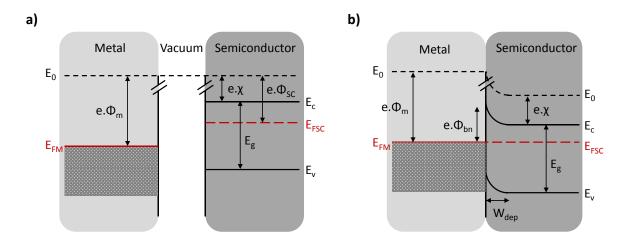

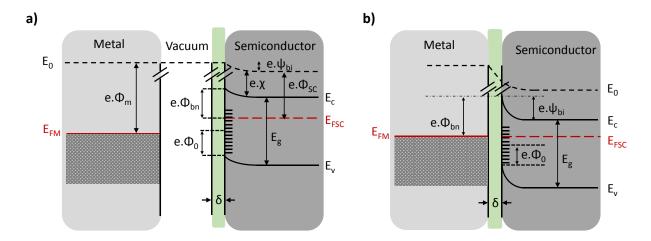

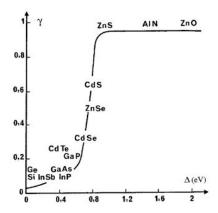

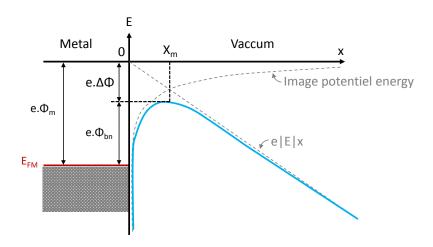

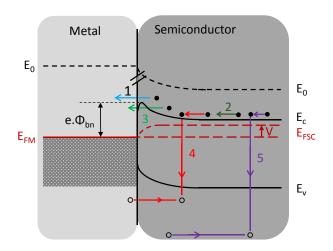

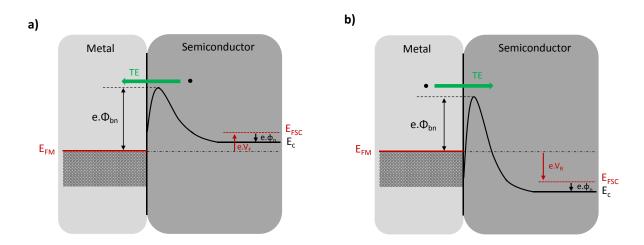

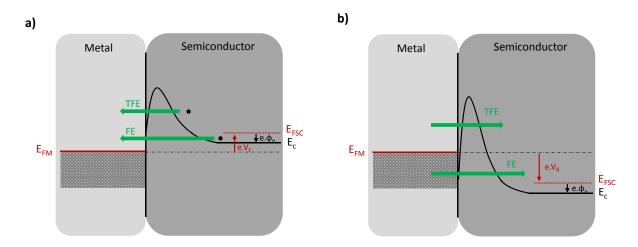

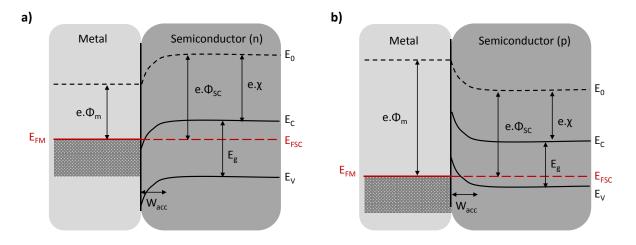

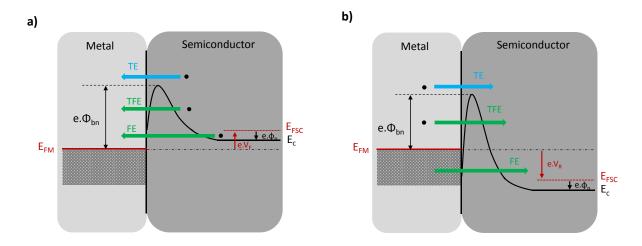

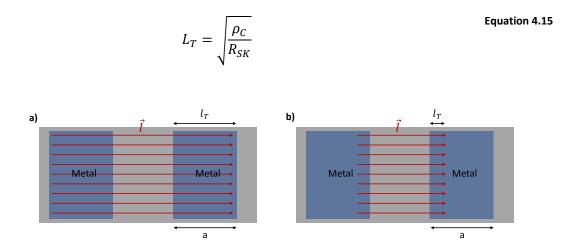

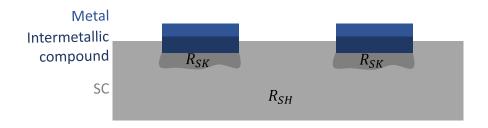

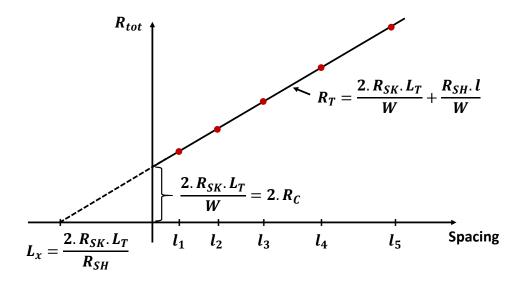

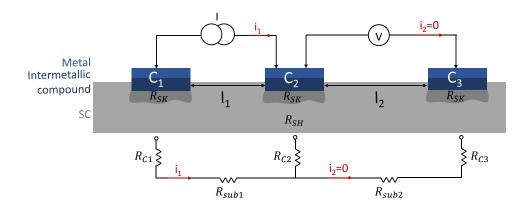

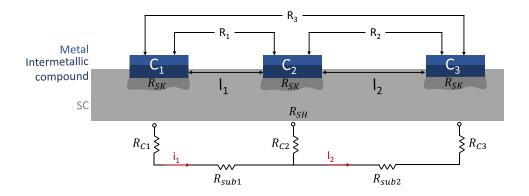

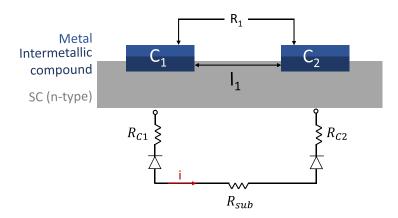

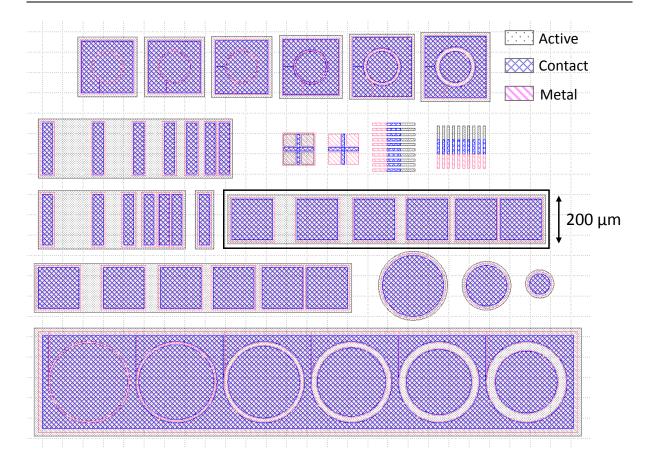

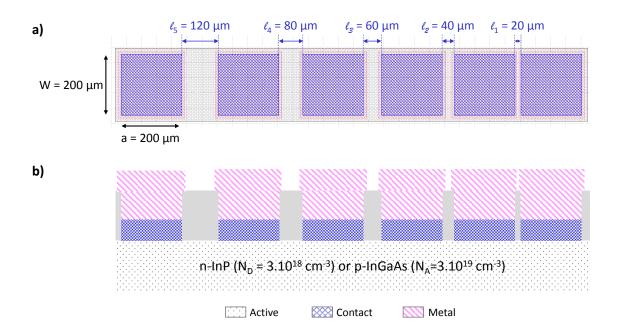

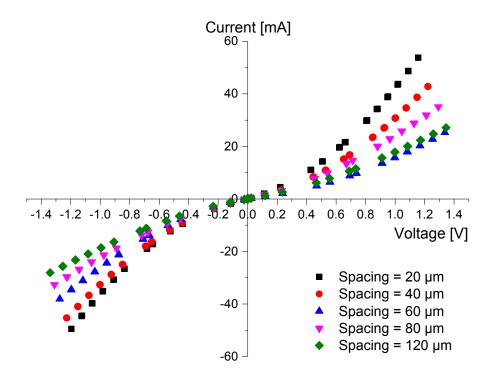

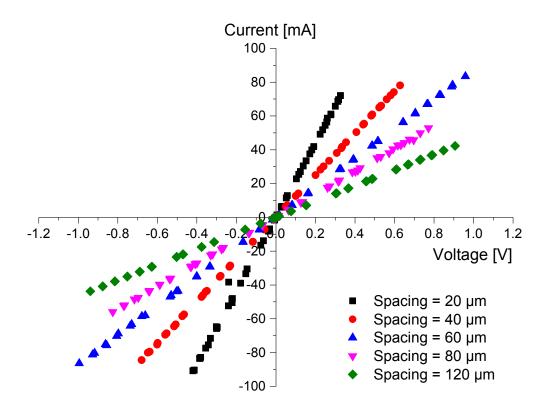

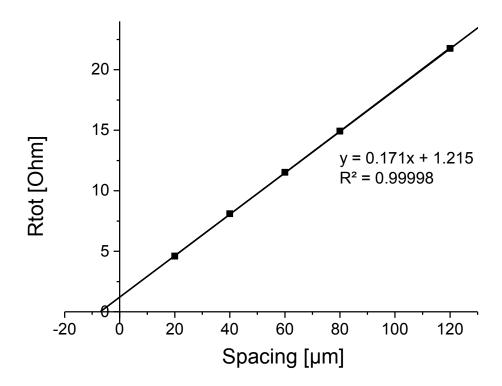

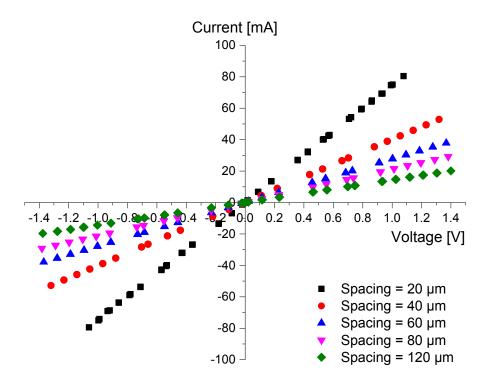

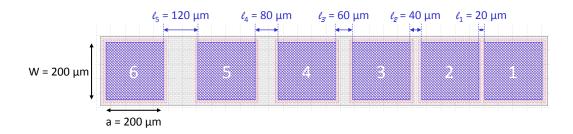

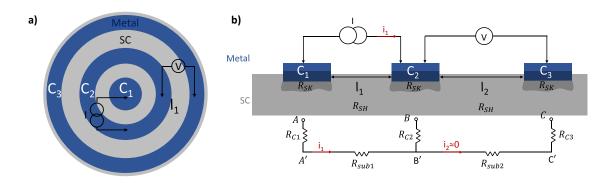

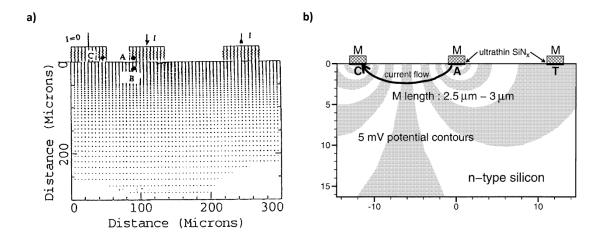

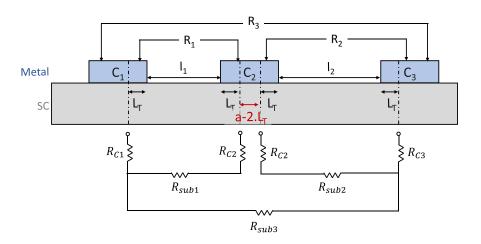

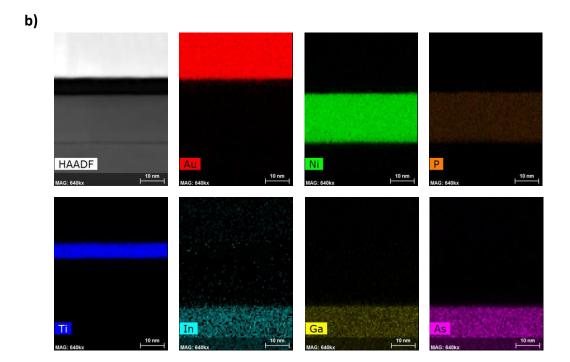

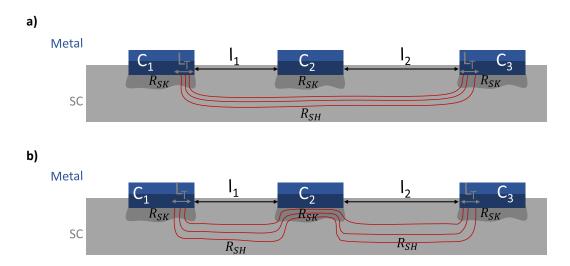

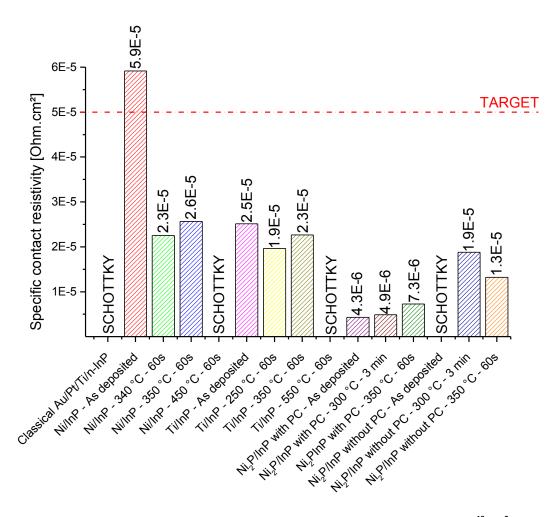

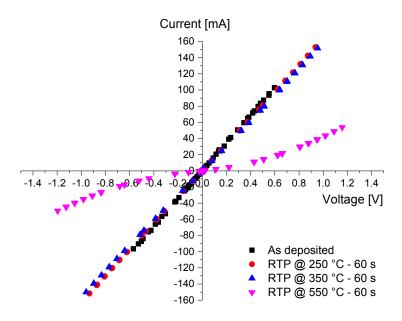

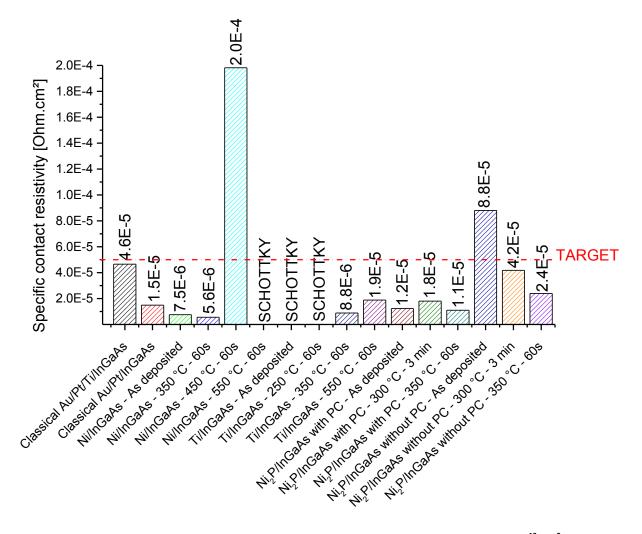

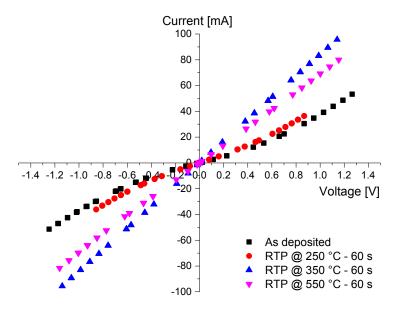

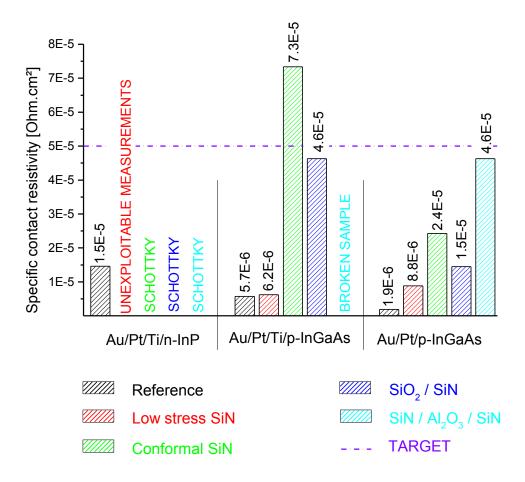

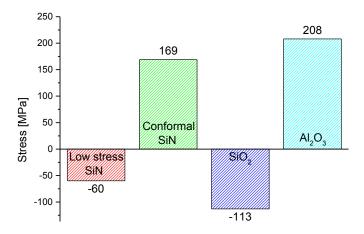

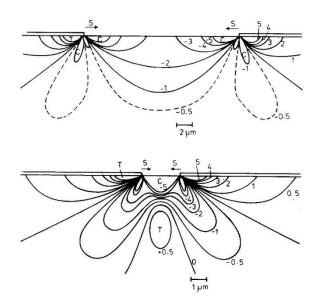

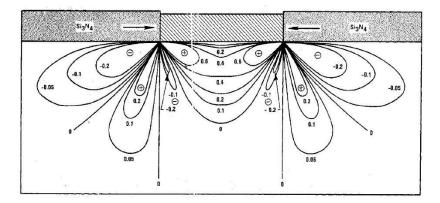

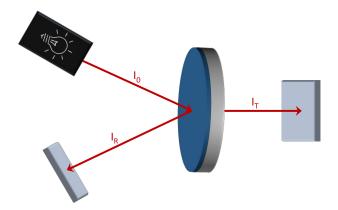

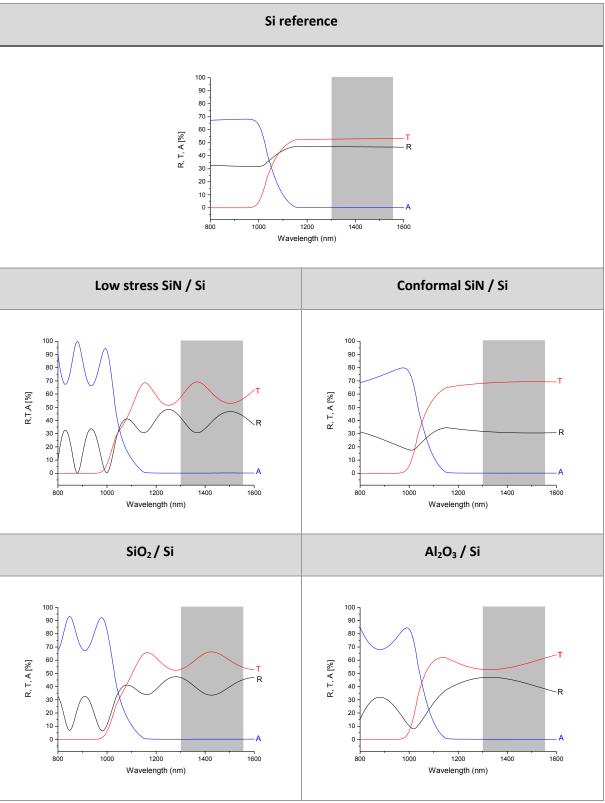

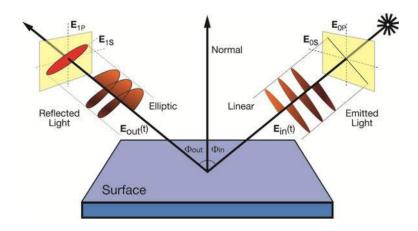

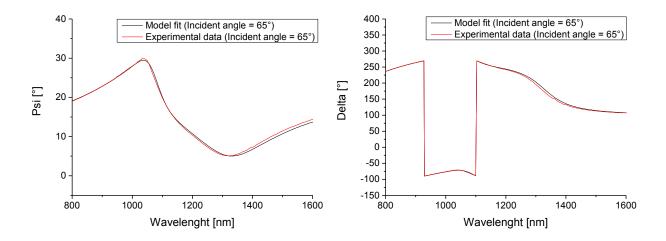

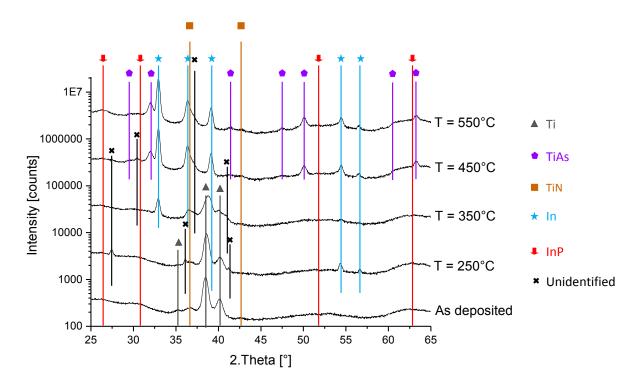

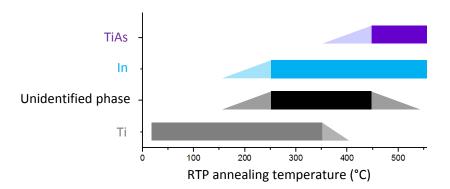

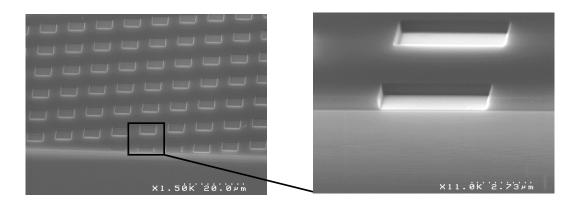

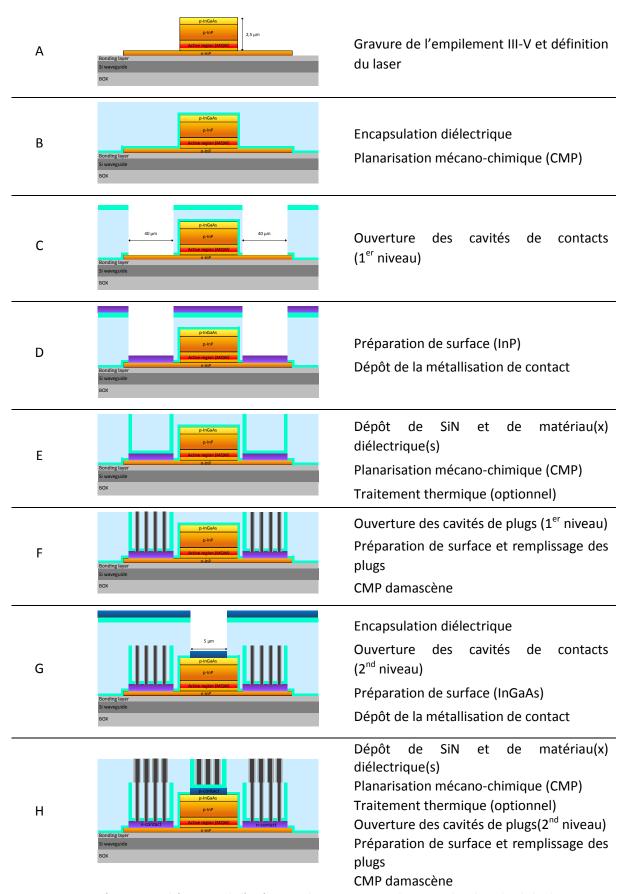

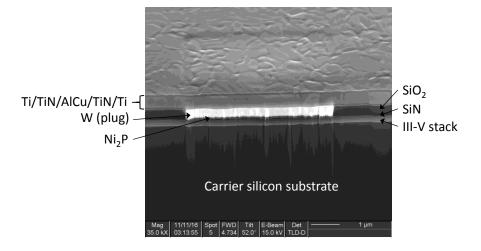

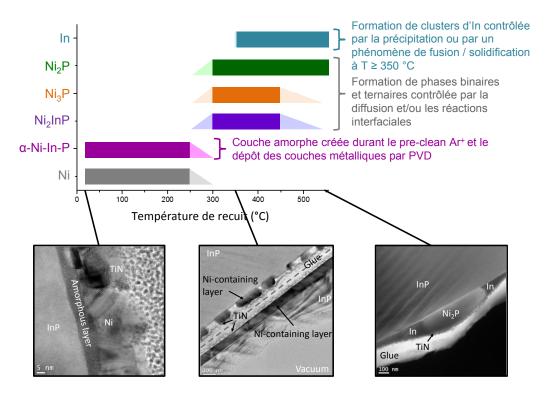

## Optic coupler