# Caractérisation et modélisation de UTBB MOSFET sur SOI pour les technologies CMOS avancées et applications en simulations circuits

Theano Karatsori

# ▶ To cite this version:

Theano Karatsori. Caractérisation et modélisation de UTBB MOSFET sur SOI pour les technologies CMOS avancées et applications en simulations circuits. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes; Université Aristote (Thessalonique, Grèce), 2017. Français. NNT: 2017GREAT035. tel-01690112

# HAL Id: tel-01690112 https://theses.hal.science/tel-01690112

Submitted on 22 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

préparée dans le cadre d'une cotutelle entre la Communauté Université Grenoble Alpes et l'Université Aristote de Thessalonique

Spécialité : Nanoélectronique et nanotechnologies

Arrêté ministériel : le 6 janvier 2005 - 7 août 2006

Présentée par

# Théano KARATSORI

Thèse dirigée par **Prof. Gérard GHIBAUDO** et codirigée par **Prof. Charalabos DIMITRIADIS**

préparée au sein de l'IMEP-LAHC et de l'Université Aristote de Thessalonique

dans l'École Doctorale d'Électronique, Électrotechnique, Automatique et Traitement du Signal

# Caractérisation et modélisation de UTBB MOSFET sur SOI pour les technologies CMOS avancées et applications en simulations circuits

Thèse soutenue publiquement le **12 Juillet 2017**, devant le jury composé de :

### Francis BALESTRA

Directeur de recherche CNRS Alpes, Président

# **Brice GAUTIER**

Professeur, INSA-Lyon, Rapporteur

# **Nathalie MALBERT**

Professeur, Université de Bordeaux, Rapporteur

# **Spyridon NIKOLAIDIS**

Professeur, Université Aristote de Thessalonique, Examinateur

### **Dimitrios TASSIS**

Professeur Associé, Université Aristote de Thessalonique, Examinateur

# **Charalabos DIMITRIADIS**

Professeur, Université Aristote de Thessalonique, invité

# **Gérard GHIBAUDO**

Directeur de recherche CNRS Alpes, invité

# **THESIS**

For the degree of

# DOCTOR OF PHILOSOPHY OF THE UNIVERSITY GRENOBLE ALPES

prepared under a co-supervision between the *University Grenoble Alpes* and the *Aristotle University of Thessaloniki*

Specialty: Nanoelectronics and nanotechnologies

Ministerial Order: 6 January 2005 - 7 August 2006

Presented by

# Theano KARATSORI

Thesis directed by **Prof. Gérard GHIBAUDO** and Co-directed by **Prof. Charalabos DIMITRIADIS**

prepared in the laboratory IMEP-LAHC and the Aristotle University of Thessaloniki

in the École Doctorale d'Électronique, Électrotechnique, Automatique et Traitement du Signal

# Electrical characterisation and modeling of advanced nano-scale ultra-thin body and burried oxide (UTBB) MOSFETs and applications in circuit simulations

Thesis defended in public on the **12 Juillet 2017**, in front of the jury composed of :

# Francis BALESTRA

Research director CNRS Alpes, President

# **Brice GAUTIER**

Professor, INSA-Lyon, Rapporteur

### Nathalie MALBERT

Professor, University of Bordeaux, Rapporteur

# **Spyridon NIKOLAIDIS**

Professor, Aristotle University of Thessaloniki, Examiner

# **Dimitrios TASSIS**

Associate Professor, Aristotle University of Thessaloniki, Examiner

# **Charalabos DIMITRIADIS**

Professor, Aristotle University of Thessaloniki, invited

# **Gérard GHIBAUDO**

Research director CNRS Alpes, invited

# **Abstract**

The progressive down-scaling of CMOS technology has driven the semiconductor industry to the realization of faster and lower power consumption VLSI circuits and systems. Among the most common solutions for high performance nano-scale area devices are the finshaped field-effect transistors (FinFETs) and the fully-depleted silicon-on-insulator (FDSOI) MOSFETs, which can provide a high immunity to the short-channel effects (SCEs), low threshold voltage variability and an improved drain-induced barrier lowering level (DIBL). Compared to FinFET, the UTBB FDSOI technology utilizes a much simpler fabrication process thanks to its planar structure. Furthermore, its back-gate bias option makes it particularly interesting for multi- $V_t$  applications.

The present thesis is dealing with issues arising from the scaling of new-era devices in the modern MOSFET design: the development of an analytical and compact drain current model, valid from weak to strong inversion, describing accurately the transfer and output characteristics of short-channel FDSOI devices and the investigation of performance issues namely reliability and variability issues- of such advanced nano-scale transistors. Meanwhile, the accurate determination of the MOSFET electrical parameters is also essential for understanding the physics and engineering of the devices, particularly if we take into account that as the supply voltage is reduced with device scaling, the operating gate bias moves closer to the threshold voltage (near threshold operation), and the assumption that the inversion charge varies approximately linearly with gate voltage overdrive becomes less and less accurate. Thus, an additional goal is the development of a methodology which allows the extraction of MOSFET parameters over the full gate voltage range i.e. from weak to strong inversion region, enabling to fully capture the transition between subthreshold and above threshold region, despite the reduction of supply voltage.

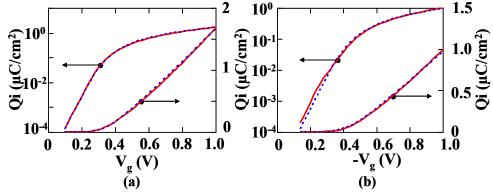

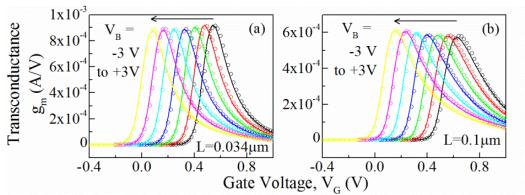

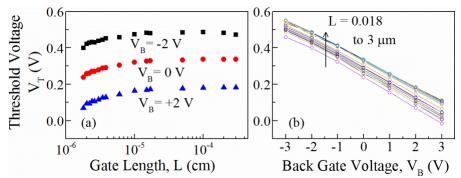

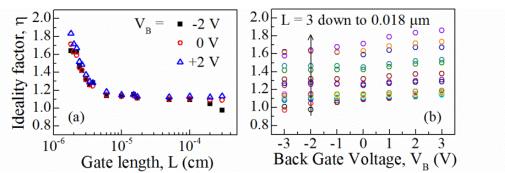

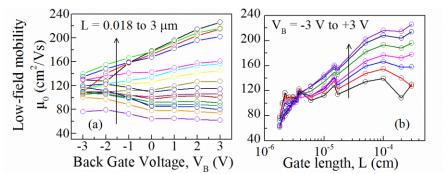

First, we present a new full gate voltage range methodology using a Lambert W function based inversion charge model, for extracting the electrical parameters in FDSOI nano-MOSFET devices. Split capacitance-voltage measurements carried out on 14 nm technology FDSOI devices show that the inversion charge variation with gate voltage can be well described by the Lambert W function. Based on the drain current equation in the linear region including the inversion charge described by the Lambert function of gate voltage and the standard mobility equation enables the extraction of five electrical MOSFET parameters from experimental transfer characteristics (ideality factor, threshold voltage, low field mobility, first and second order mobility attenuation factors). The extracted parameters were compared with those extracted by the well-known Y-function in strong inversion region. The present methodology for extracting the electrical MOSFET parameters has been verified over a wide range of channel lengths and back gate voltages on nano-scale FDSOI devices, demonstrating its simplicity, accuracy and robustness.

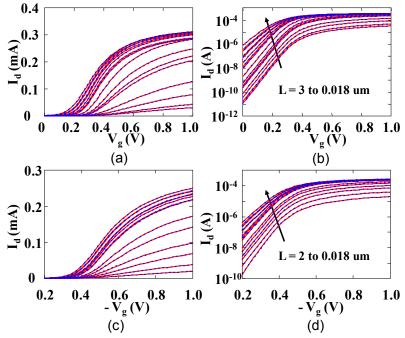

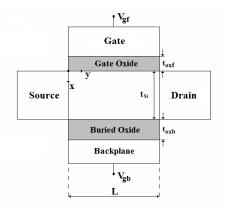

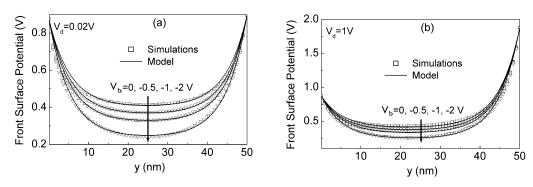

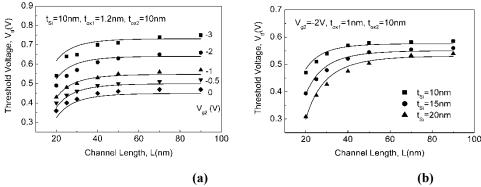

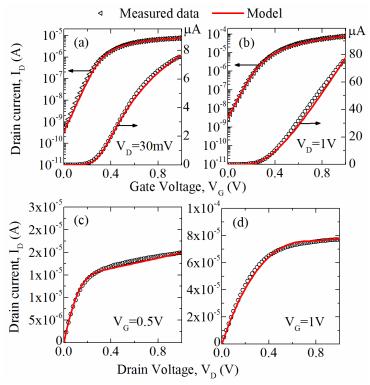

Second, we have derived simple expressions for the minimum value of the front and back gate surface potentials with which we have developed analytical models for the respective threshold voltages and ideality factors with back gate control of lightly doped short channel UTBB FDSOI MOSFETs. The threshold voltage and ideality factor models of the front and back gates have been verified with numerical simulations in terms of the device geometry parameters and the applied bias voltages, as well as with experimental results for devices with channel length down to 17 nm. Based on these models we have developed an analytical drain current compact model for lightly doped short-channel UTBB FDSOI

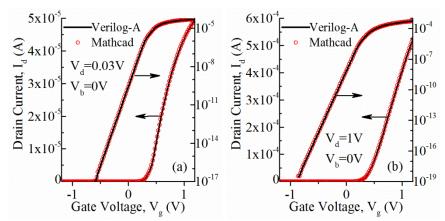

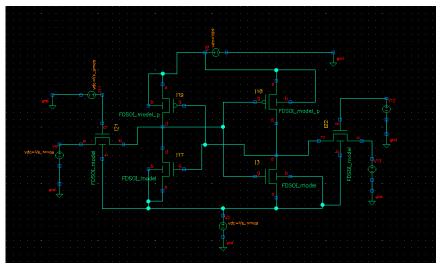

MOSFETs with back gate control. The model, which includes the effects of drain-induced barrier lowering, channel-length modulation, saturation velocity, mobility degradation, quantum confinement, velocity overshoot and self-heating, has been validated by comparing with experimental transfer and output characteristics of various devices and back-bias conditions. The good accuracy of the model makes it suitable for implementation in circuit simulation tools. Indeed, the drain current compact model is implemented via Verilog-A code for simulation of fundamental circuits in circuit simulators.

Following the drain current compact model development, reliability issues including hot-carrier injection (HCI) and negative bias temperature instability (NBTI) are discussed for these nano-scale UTBB FDSOI MOSFETs. The hot-carrier effect, which occurs near the drain end due to hot carriers accelerated in the channel, is prominent in n-MOS devices, while the NBTI is prominent in p-MOS devices along the entire channel when negative gate-to-source voltage is applied.

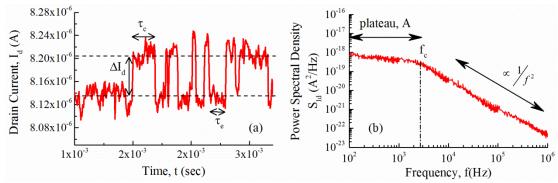

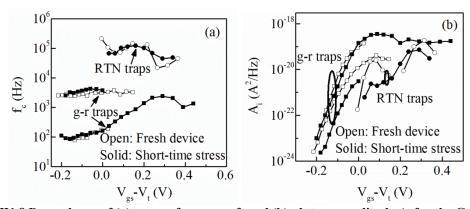

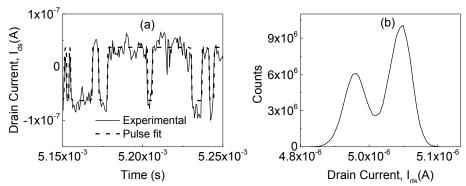

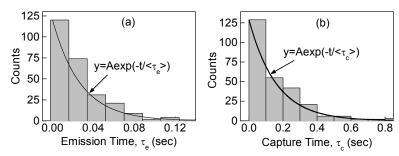

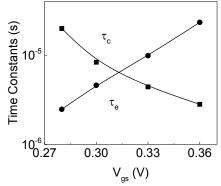

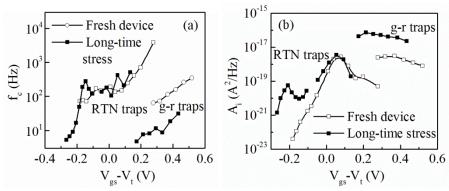

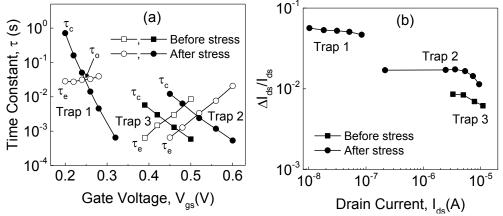

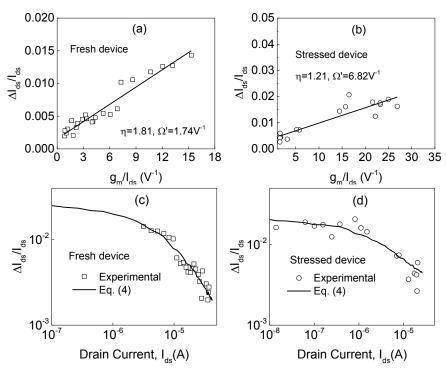

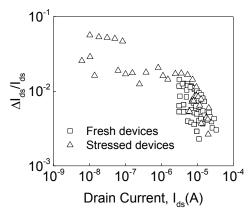

- ✓ In our analysis, the hot-carrier (HC) induced traps are investigated by lowfrequency noise (LFN) measurements in the frequency and time domain. The measured noise spectra are composed of 1/f and Lorentzian-type components. The Lorentzian noise is due either to generation-recombination noise or to random telegraph noise (RTN). Based on the LFN results, the effect of the HC-stress on FDSOI MOSFETs is investigated after short and long-time stress. Analysis of RTN traps detected in fresh and HC-stressed devices indicate that the RTN amplitude is uncorrelated to the trap time constants, i.e. the impact of the trap depth from the interface is masked by that of the trap location over the channel. The overall results lead to an analytical expression for the RTN amplitude, enabling to predict the RTN changes from the subthreshold to the above threshold region. After we identified the degradation mechanisms and based on our analytical compact drain current compact model, we developed a semi-empirical aging hot-carrier model predicting with good accuracy the device degradation stressed under different bias conditions using a unique set of model parameters.

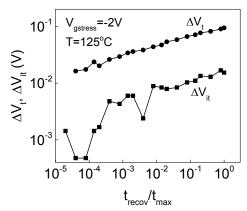

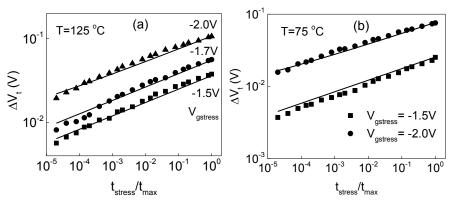

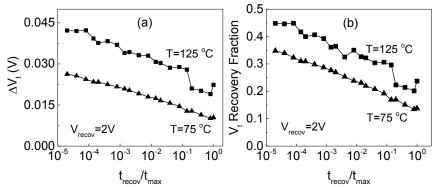

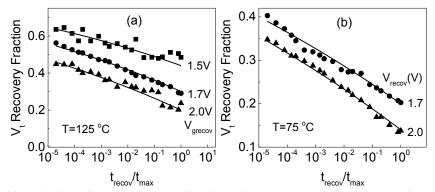

- ✓ Concerning the NBTI phenomenon, the threshold voltage shifts during stress at different temperatures and gate bias voltage conditions show that the NBTI is dominated by trapping of holes in pre-existing traps of the gate dielectric, while the recovery transient follows a logarithmic-like time dependence. In this way, we have developed an NBTI model capturing the temperature and gate voltage dependence in such UTBB FDSOI p-MOSFETs with zero back gate bias and small drain bias voltage.

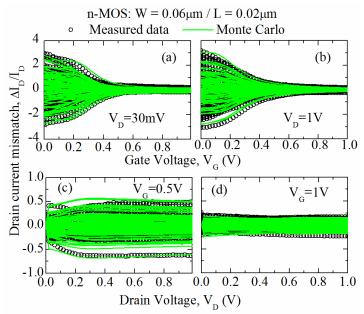

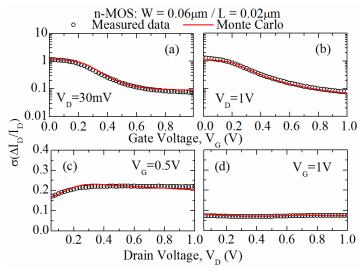

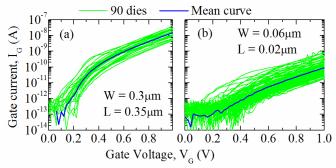

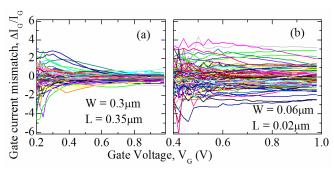

Finally, the last part of our research work which is covering a significant part of the thesis, deals with the local variability phenomenon in advanced nano-scale devices. The main sources of drain and gate current local variability have been thoroughly studied. In this aspect, we developed a fully functional drain current mismatch model, valid for any gate and drain bias condition, including all main sources of drain current local variability assumed to be uncorrelated, namely the threshold voltage, the current gain factor, the source-drain series resistance and the subthreshold slope ideality factor mismatches. Concerning the gate current local variability modeling the local fluctuations of the threshold voltage and the gate oxide thickness were taken into account. The proposed models for the drain and gate current mismatch were verified, using a Lambert function based compact model and performing

Monte Carlo simulations that reproduce accurately the experimentally measured current variations. Then, owing to the proposed mismatch models, we characterized various advanced technologies in terms of local and global variability performance. Indeed, a detailed statistical characterization of drain current local and global variability in 14 nm Si bulk FinFET devices and in sub 15 nm gate length Si/SiGe trigate nanowire p-MOSFETs is performed. To this end, we extracted the main matching parameters showing that, despite their very aggressive dimensions, such devices exhibit relatively good local and global variability performance. Furthermore, we investigated the impact of the source-drain series resistance mismatch on the drain current variability for 28 nm Bulk MOSFETs. Finally, we performed a complete investigation of the gate and drain current mismatch in 14 nm FDSOI devices. In conclusion, these drain and gate current mismatch compact models can easily be implemented in circuit simulation tools for circuit design and are applicable to both bulk and FDSOI technologies. To this end, our drain current compact model implemented in Verilog-A code has been used to examine the impact of drain current variability on fundamental circuits in Cadence Spectre.

# **Acknowledgements**

This work has been performed under financial support from the following scientific projects: ENIAC Places2Be project, ARISTEIA II (project 4154) of the Greek General Secretariat for Research and Technology co-funded by the European Social Fund and national funds, ECSEL Waytogo Fast European project and Horizon 2020 ASCENT EU project (Access to European Nanoelectronics Network -Project no. 654384).

First of all, I would like to warmly thank my supervisors Prof. Charalabos Dimitriadis and Dir. de Recherche Gérard Ghibaudo for their immense knowledge, constant guidance and support on all levels. Their contribution was really vital and inspiring; it was an honor to work with them and I will never forget their kindness and patience.

Also, I would like to kindly thank all the remaining members of my PhD committee: The president Francis Balestra, the rapporteurs Brice Gautier and Nathalie Malbert for spending time to study my manuscript and give me constructive remarks, Spyros Nikolaidis and Dimitrios Tassis from my university in Thessaloniki that honored me by co-supervising my Thesis.

Another person from the laboratory I certainly owe thanks to is Post-doc researcher Christoforos Theodorou for his persistent support and explanation of phenomena mainly related to noise. His long experience proved to be invaluable to me. Special thanks to Xavier Mescot as well, as his help and insight into my measurements was really significant.

Moreover, I would like to thank my close friends Nikoletta, Katerina and Theano and especially my beloved friend Lamprini for all the moral support and kindness every day through this difficult journey.

What is more, I am very grateful to my life partner, who showed a unique support during these three years and an incomparable patience and understanding, especially during the period of my preparation for this moment.

Finally, no acknowledgements could be complete without expressing my warm gratitude to my family, and especially my parents, Antonis and Anastasia for constantly supporting me and believing in me all these years. I would also like to thank my sisters - all four of them - Zoe, Ioanna, Georgia, Melina, for being patient and my uncle, Anastasios as well, who inspired me to follow his steps.

# **Contents**

| I      | Intr          | oduction                                                                    | 12  |

|--------|---------------|-----------------------------------------------------------------------------|-----|

|        | I.1           | Overview of microelectronics evolution                                      | 12  |

|        | I.2           | Advanced nano-scale devices                                                 | 13  |

|        | I.3           | Impact of scaling on the device performance                                 | 16  |

|        | I.4           | Necessity of compact modeling in MOSFETs                                    | 19  |

|        | I.5           | Dissertation goals and outline                                              | 21  |

| II     | Cha           | racterization techniques and parameter extraction                           | 24  |

|        | II.1          | Introduction                                                                | 24  |

|        | II.2          | Basic operation of bulk MOS transistors                                     | 25  |

|        | II.3          | Y-Function Methodology                                                      | 29  |

|        | II.4          | Split C-V Methodology                                                       | 31  |

|        | II.5          | Lambert-W Function Methodology                                              | 36  |

|        | II.6          | Low-Frequency Noise in Semiconductor Devices                                | 46  |

|        | II.7          | Summary                                                                     | 52  |

| II     | I A           | analytical Compact Modeling in FDSOI MOSFETs                                | 53  |

|        | III.1         | Introduction                                                                | 53  |

|        | III.2         | Surface Potential Model Formulation                                         | 54  |

|        | III.3         | Threshold Voltage Model                                                     | 57  |

|        | III.4         | Analytical Drain Current Model                                              | 67  |

|        | III.5         | Drain Current Modeling for Electronic Circuit Simulations                   | 75  |

|        | III.6         | Summary                                                                     | 80  |

| IV     | V R           | Reliability Issues in FDSOI Devices                                         | 81  |

|        | IV.1          | Introduction                                                                | 81  |

|        | IV.2          | Hot Carrier Injection (HCI) in FDSOI n-MOS                                  | 82  |

|        | IV.3          | Negative Bias Temperature Instability in FDSOI p-MOSFETs                    | 100 |

|        | IV.4          | Summary and conclusions                                                     | 107 |

| V      | Var           | iability Issues in nano-scale MOSFETs                                       | 109 |

|        | V.1           | Introduction                                                                | 109 |

|        | V.2           | Mismatch test structures                                                    | 110 |

|        | V.3           | Drain Current Local Variability from Linear to Saturation Region            | 111 |

| mismat | V.4<br>ch sou | Drain Current Local Variability in linear region including all drain curces |     |

|        | V 5           | All operation region Drain Current Local Variability                        | 130 |

| V.6                                                  | Gate Current Local Variability                         | 137              |  |  |

|------------------------------------------------------|--------------------------------------------------------|------------------|--|--|

| V.7                                                  | Impact of Drain Current Local Variability on a Circuit | 's Operation 140 |  |  |

| V.8                                                  | Summary and Conclusions                                | 142              |  |  |

| VI C                                                 | onclusions and Perspectives                            | 144              |  |  |

| VI.1                                                 | Summary and Conclusions                                | 144              |  |  |

| VI.2                                                 | Future Research Directions                             | 146              |  |  |

| Bibliography                                         |                                                        |                  |  |  |

| Appendi                                              | 167                                                    |                  |  |  |

| Appendix A: Drain current compact model in Verilog-A |                                                        |                  |  |  |

| Apper                                                | ndix B: Scientific Publications                        | 171              |  |  |

| Apper                                                | ndix C: List of Abbreviations                          | 173              |  |  |

| Appendix D: Greek Abstract                           |                                                        |                  |  |  |

| Appendix E: French Abstract                          |                                                        |                  |  |  |

# I Introduction

# I.1 Overview of microelectronics evolution

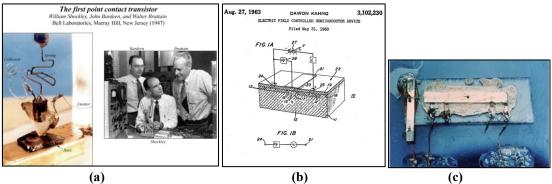

Microelectronic components are the core elements of all modern technological devices that serve the needs of informatics, communications and audiovisual systems. They consist of conductor, semiconductor and insulator materials, arranged in a certain way to create new electrical properties. Although the first experiments on the electrical properties of semiconductor materials date back to the beginning of 19<sup>th</sup> century, the event that brought them on the edge was the invention of the Bipolar Junction Transistor (BJT) by W. Shockley, J. Bardeen and W. Brattain (Figure I-1(a)) at Bell Laboratories at the end of 1947 [1]. Almost ten years later, in 1959 D. Kahng and M. M. Atalla invented the Metal-Oxide-Semiconductor (MOS) Field Effect Transistor (FET) (Figure I-1(b)) as an offshoot to the already patented by J. E. Lilienfeld, FET design [2], [3]. At the same time, in September 1958 J. Kilby of Texas Instruments presented the first working Integrated Circuit (IC) (Figure I-1(c)) [4].

Figure I-1 The first working (a) BJT, (b) MOSFET and (c) IC.

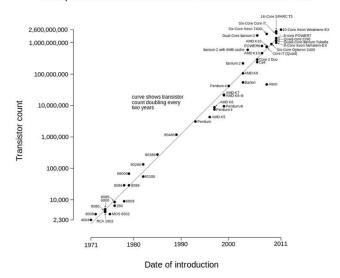

Very soon, the successful development of the MOSFET led to the progress of the IC technology, since these devices were incorporated into integrated circuits in the early 1970s. Almost at the same period of time G. Moore estimated that the number of transistors per chip would double about every two years [5] (Figure I-2), since the idea was that smaller devices improve almost every aspect of an IC's operation, including the reduction of cost and switching power consumption per transistor, as well as the memory capacity and speed enhancement.

The semiconductor industry's need to transform Moore's observation into reality led to the creation of the International Technology Roadmap for Semiconductors (ITRS) in the early 90's. Therefore, the ITRS is a comprehensive guide produced by a group of semiconductor industry experts for advanced semiconductor device research and manufacturing purposes [6]. Since the first edition of the roadmap, the Moore's 'law' and the ITRS have been complementing each other. Even though Moore's 'law' has been successfully followed until recently, pursuing MOSFET scaling trend becomes more difficult as time passes. According to ITRS many challenges have to be overcome in order to continue progress to the same direction concerning the transistor's performance. Silicon (Si) remains the main semiconductor material for the time being but the required performance improvements for the end of the roadmap concerning high performance, low and ultra power applications as well as memories will lead to a substantial widening in the number of new materials, fabrication processes and device architectures used.

Figure I-2 Microprocessor transistor counts versus year plotted together with Moore's law.

# I.2 Advanced nano-scale devices

It is clear that the main aspect in modern era microelectronics is concerning the device area: how to effectively reduce the device size without compromising its functionality [4] is the constant question in all electronic engineers' mind. The main advantage of reducing the transistor active area is the power consumption decrease since the voltage needed for the device operation is reduced accordingly to its size [7], [8]. On the other hand, loss of electrostatic control [9], mobility degradation [10], [11], short-channel effects (SCEs), and inability of further reducing the series resistance are some of the main disadvantages arising from the device shrinking. Finally, variability and reliability issues are also other crucial impacts of reducing the MOSFET area. These latter issues are addressed by the present work.

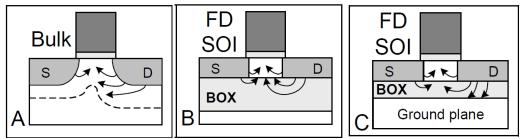

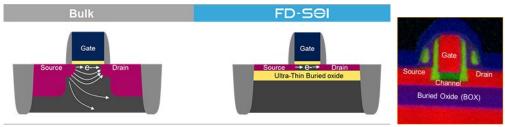

To address the problems mentioned above, various technological concepts have already been absorbed and used from transistor technology. Planar bulk silicon MOSFET has been the traditional workhorse of the semiconductor industry to achieve continuous scaling. However, bulk planar FETs suffer from SCEs as the electric field lines propagate through the depletion regions associated with the junctions (Figure I-3(A)). To overcome this problem Silicon-On-Insulator (SOI) substrates have been proposed. Indeed, these devices are interesting candidates for the manufacturing of mainstream semiconductor products like microprocessors or low-power devices [12]. As illustrated in Figure I-3(B) in a fully depleted SOI (FDSOI) device, most of the field lines propagate trough the buried oxide (BOX) before reaching the channel region. However, the improvement regarding the SCEs in FDSOI devices depends on device parameters such as the silicon film thickness, buried oxide thickness, and doping concentrations. With reducing the BOX thickness from the typical 145-300 nm value down to 8-25 nm, the device is called ultra-thin body and buried-oxide (UTBB) FDSOI MOSFET [13]. The silicon film thickness can vary from around 7 to 14 nm. Another solution contributing to the reduction of SCEs in FDSOI MOSFETs is the addition of a thin buried oxide layer and an underlying ground plane. In that case, most of the electric field lines from the source and drain terminate on the buried ground plane instead of the channel region (Figure I-3(C)).

Figure I-3 Electric field lines from source (S) and drain (D) on the channel region in (A) bulk, (B) FDSOI and (C) FDSOI with thin buried oxide and ground plane MOSFETs [14].

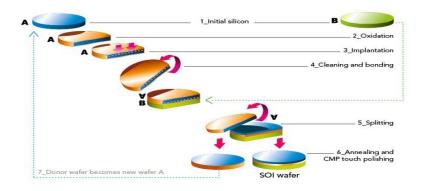

In Figure I-4 the "Smart Cut" fabrication process for manufacturing ultrathin SOI wafers is illustrated, achieving a complete division between an ultrathin film of single crystalline silicon and the bulk substrate [15].

Figure I-4 Fabrication process of manufacturing ultrathin SOI via Smart Cut process [15].

Furthermore, other technological solutions suggested and applied in order to maintain the level of performance while shrinking down the device area, include:

- ✓ Gate stacks consisting of more than two material layers combined with highk materials, like hafnium oxide HfO₂, instead of SiO₂ as gate insulators to decrease tunneling leakage current and increase gate capacitance [16].

- ✓ Techniques like substrate rotation, stress or strain to improve mobility [17], [18].

- ✓ Insertion of Halo implants near the drain and source contacts [19] in order to eliminate the SCEs and drain-induced barrier lowering (DIBL) effect.

- ✓ Shallow trench isolation (STI) technique [20] to electrically isolate one device from the other and thus to prevent leakage currents.

In Figure I-5 a typical bulk and an FDSOI MOSFET fabricated by ST Microelectronics in France are presented. This PhD thesis is addressing various new technologies, among which the 28 nm and 14 nm FDSOI technologies as well as the 28 nm bulk technology.

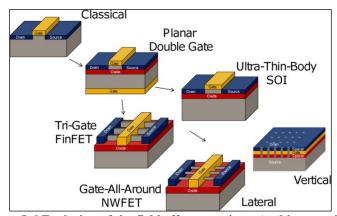

Another configuration, proposed for the first time in 1984 [22] and considered to be a further promising candidate to have a larger immunity for SCEs compared to classical single planar gate devices is the multi-gate structure. Indeed, multi-gate devices (double, triple, quadruple, and gate all around structures presented in Figure I-6) provide several advantages such as enhanced gate controllability, increased gate-drive current, reduced sub-threshold swing and subsequently suppressed gate leakage current, reinforced pinch off effects, and

improved process reliability [9], [23]. On the other hand, however, there are technological and economical challenges such as the fabrication cost and process complexity that make these devices not as compatible as conventional bulk planar CMOS devices.

Figure I-5 Representation of a (a) bulk and an (b) FDSOI MOSFET fabricated by ST Microelecronics. In (c) a scanning electron microscopy (SEM) cross section of an FDSOI MOSFET is presented. [21]

Figure I-6 Evolution of the field effect transistor Architecture [24].

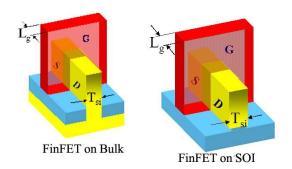

Furthermore, another design idea that seems to prevail over the bulk CMOS technology is the Fin-Shaped FET (FinFET). As illustrated in Figure I-7 in FinFET devices, where the channel width plays here the role of  $t_{Si}$ , the body has a fin-like shape and is surrounded by the gate electrode. Due to this design SCEs can be well suppressed, demonstrating lower DIBL [25] and enhanced field-effect mobility [26]. Nevertheless, as FinFETs are three-dimentional (3D) devices, they demonstrate additional challenges for manufacturing and circuit design [27].

Figure I-7 Representation of a FinFET device on bulk and SOI substrates.

Finally, tri-gate nanowire (NW) MOS transistors are nowadays recognized as promising architectures for continuing the scaling down beyond FinFET and FDSOI CMOS technologies [28], [29], [30]. By wrapping a gate around the NW, the optimal control of the NW conduction by the gate potential is ensured. A large number of techniques exist to

fabricate silicon nanowires, that can be classified into bottom-up and top-down fabrication techniques. Superior gate control, immunity of threshold voltage from substrate bias and excellent carrier transport properties along with more aggressive channel length scaling possibility have made gate-all-around (GAA) architecture with semiconductor NW channel a potential candidate for post-planar transistor design.

# I.3 Impact of scaling on the device performance

In order to achieve performance improvement, reduced power consumption and higher-density integration by shrinking down the device dimensions, major reliability and variability issues have emerged. The first case includes phenomena like hot carrier injection (HCI), and negative bias temperature instability (NBTI), while the second one, as indicated from the term, variations of the main device parameters. These reliability mechanisms cause drifts in the MOS transistor parameters; namely, threshold voltage shift and mobility degradation. Additionally, dispersions in device level are propagated on a circuit level (e.g. SRAM) leading to reduced circuit performance and functionality. Consequently, it is evident that the study of these issues is considered of great importance and this is the reason they cover a large part of the present thesis. Before analyzing these phenomena, some basic elements of the MOS device reliability and variability are described.

# **I.3.1** Reliability issues in MOSFETs

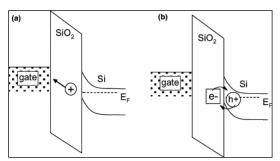

# I.3.1.1 Negative Bias Temperature Instability

Bias Temperature Instability (BTI) is a phenomenon that introduces a significant reliability issue in advanced devices and in circuit operation. It occurs when the device is subjected to elevated temperatures (0°C to 300°C) and high gate voltages (creating electric fields up to approximately 10 MV/cm) while the remaining MOSFET terminals are grounded [31]. These conditions, usually referred to as stress, have detrimental effects on the device characteristics, as they result in positive charge built-up in the gate insulator causing shift in device parameters, like for example in the threshold voltage or in the sub-threshold slope. However, as soon as the stress conditions are removed, the device characteristics are found to recover, meaning that the device parameters slowly revert towards their initial values. The effect has been identified to be stronger in p-type transistors under negative bias conditions and this is the reason it is called NBTI.

Figure I-8 Effect of negative gate bias on MOS capacitor. (a) Positive ion drift causes a reduction in the net amount of positive charge near the Si/SiO<sub>2</sub> interface. The resulting flat band shift is positive. (b) Charge exchange with the Si substrate, either hole trapping or electron detrapping causes an increase in the net positive charge at the Si/SiO<sub>2</sub> interface. The resulting flat band shift is negative [32].

As indicated in Figure I-8, at first the phenomenon was remarkable as an increase in positive charge under negative gate bias implicated a mechanism distinct from the migration of mobile ions which were of much concern [32].

Although this phenomenon is not a new topic - it was first reported in 1966 [33] - there are still significant issues to study concerning the nature and modeling of NBTI, especially in advanced nano-scale devices.

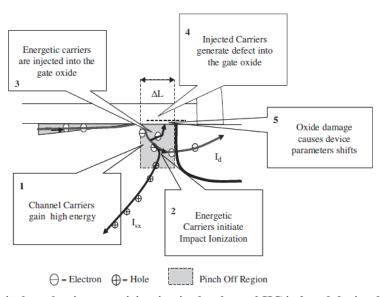

# **I.3.1.2** Hot Carrier Injection

At small channel dimensions, the electric fields are high near the drain region resulting in hot carrier (HC) degradation issues. First of all, by using the term "hot" we mean that the mean carrier energy is significantly larger than that associated with the lattice in thermal equilibrium, namely E > (3/2)kT. Indeed, electrons (or holes) can gain enough energy passing through high electric fields so that they are injected into normally "forbidden" regions of the device, as the gate dielectric, where they can get trapped or lead to generation of interface traps at the silicon-oxide interface known as fast surface states. As a result, MOSFET parameters such as threshold voltage, sub-threshold swing and on-current will be modified limiting the lifetime of the transistor and causing degradation of the ICs performance.

In general, hot carriers can be introduced into the gate dielectric with 4 different mechanisms [34]:

- 1. Channel HC injection

- 2. Drain avalanche HC injection

- 3. Secondary generated HC injection

- 4. Substrate HC injection

In this thesis we are interested mainly in the first case, illustrated in Figure I-9 where some "lucky" carriers [35] flowing in the MOSFET inverted channel ( $V_{gs} > V_t$ ), gain significant energy beyond the channel pinch-off point [31].

Figure I-9 Physical mechanisms participating in the channel HC induced device degradation in MOSFET in saturation [31].

# **I.3.2** Variability issues in MOSFETs

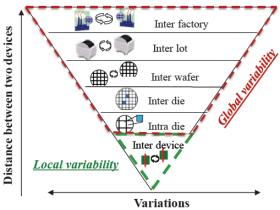

As new technology nodes with their decreasing geometries come into existence, process variations in general and especially intra-die (differences between areas on the same die) and inter-device (differences between "matching" pair devices on the same die) variations become increasingly significant. As shown in Figure I-10, process variations, which are observed at several levels and in one way or the other, are related to distance, can be categorized into global and local variations.

Figure I-10 Variability at several levels [36].

Additionally, local variability, usually referred to as mismatch, can be further divided into systematic and stochastic. Systematic mismatch stems from sources that can be predicted, like asymmetries in layout [37] and therefore it can be reduced to a certain degree by following more mismatch-aware practices, like for example use of "dummies" in MOS transistors conception [38].

On the other hand stochastic variations arise from intrinsic sources of random dispersions within the devices. This means that these variations stem from the random nature of processing steps in general, for example due to the discrete nature of dopant impurities or point defects. Stochastic fluctuations are independent of the distance between the devices under study, and by this they determine the maximal obtainable accuracy within a certain technology [39]. In this work, we study the stochastic fluctuations of the MOSFET and from this point on we will refer to this kind of fluctuations as mismatch or local variability.

In general, the physical mechanisms that are responsible for these local fluctuations were identified as: 1) doping fluctuations in the channel, 2) doping fluctuations in the gate, which are enhanced by the poly-grain structure of the gate material, 3) fluctuations in fixed-oxide charge, 4) fluctuations due to Coulomb scattering and 5) fluctuations due to surface roughness scattering. These mechanisms affect transistor behavior by influencing: 1) the threshold voltage, 2) the amount of gate depletion, 3) the magnitude of quantum mechanical effects, 4) the effective field, 5) the amount of carrier screening and 6) the mobility in general. It was found that none of the above mentioned effects can safely be neglected [39].

Concerning the research on the mismatch phenomenon, the majority of the works done dates from 1998 and beyond. The first mismatch studies, however, demonstrating that local fluctuations on MOSFET operation need to be taken into account for accurate modeling of the weak inversion current, were conducted in 1973 by Van Overstraeten, Declerck and Broux [40]. Keyes study in 1975 was focused on the creation of a model to predict the amplitude of the threshold voltage variations, without considering the MOSFET operation

[41]. One of the most referred to the literature and popular studies has been realized by Pelgrom in 1989 who translated the mismatch in MOSFET parameters into a mismatch in the drain current [42]. Indeed, in this work a direct dependency was demonstrated between the local fluctuations of an electrical MOSFET parameter and the channel area through a coefficient A. This way, the so-called Pelgrom's Law was derived:

"The standard deviation of the local variability of a MOSFET parameter is found to be inversely proportional to the square root of the device area."

These preliminary studies, in combination with the shrinking of the device dimensions, have set the ground for increasing research efforts aimed at achieving a deeper understanding of the causes of mismatch phenomena and characterizing their effects, with the objective of guaranteeing reliable integrated circuits performance.

# I.4 Necessity of compact modeling in MOSFETs

Device models are essential tools for electronics engineers in order to design and simulate electronic systems. All integrated circuit designs are verified using circuit simulators before being reproduced in real silicon since detecting errors early in the design process avoids the costly and time consuming prototyping. The first circuit simulator, SPICE (Simulation Program with Integrated Circuit Emphasis), was developed in 1973 by Laurence Nagel of University of California, Berkeley [43]. Since then, many advanced circuit simulators have been developed such as HSPICE (Avant!), SSPICE (Silvaco) or SPECTRE (Cadence), with a single goal of reducing the time-to-market for IC designs.

Electronic circuit simulations demand clearly defined requirements in order to predict the performance of a CMOS design. First of all, the simulator should be user-friendly, fast and precise. Second, it should utilize accurate models which are capable to describe the behavior of the transistors in the circuit. It is obvious that most of the requirements are related to the device models the simulator applies. Besides, device models form a bridge between the design world and the manufacturing world with which the designers can design circuits without worrying about the intricate details of transistor fabrication. The goal of a device model is to accurately predict the transistor's electrical characteristics - terminal currents, charges and capacitances for a given transistor bias and transistor temperature.

In general, device models can be divided in three groups [44]:

- Numerical device models

- \* Table look-up models

- Analytical (or compact) models.

Concerning the first group, there are two- and three-dimensional numerical models [45]. Both of them use device geometry, doping profiles, and carrier transport equations, which are solved numerically, to get the device electrical characteristics. The main disadvantage of this kind of models is that they are computationally intensive and thus they are not applied for large circuits' simulations. Regarding the table look-up models, the measured device current and capacitance are presented as functions of bias voltages and device sizes in a tabular form for access by the circuit simulators [46]. A disadvantage of this second category is the need of extensive measurements and large set of tables so that the

models cover a large range of transistor geometry, bias and temperature. Secondly this kind of models is based on measured data from measured devices making them non-predictive.

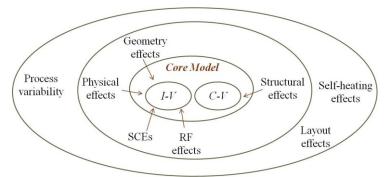

The most popular and appropriate for circuit simulations models are those described by the third group. Indeed, compact device models describe the device characteristics of a manufacturing technology by a set of physics-based analytical expressions with technology-dependent device model parameters that are solved by a circuit simulator for circuit analysis during IC design [47]. As illustrated in Figure I-11, a compact model consists of a core model -describing the drain current and capacitance behavior of the device or more precisely of the MOSFET of a specific technology- along with the various models to account for the effects of the geometry and physical phenomena in the device. The compact model equations are almost always long and complex as they describe the device characteristics accurately in all the operation regimes [48], [49], [50], [51]. Moreover, to improve the accuracy of the model fitting parameters are introduced.

Figure I-11 A typical composition of a compact model of a specific technology: the core model includes the basic behavior of a large area device and is accompanied by models for physical phenomena within the devices and geometry and other structural effects, while the final compact model includes all the external phenomena like process variability or layout effects.

Compact models can be further categorized in:

- Threshold-voltage-based models,

- Surface-potential-based models

- Charge-based models.

Threshold-voltage-based modeling is founded on the computation of the inversion charge density in the MOSFET channel in terms of the terminal voltages, namely gate and drain voltages [52]. In this approach a linear approximation is made between the surface potential and the applied drain and gate voltages. This eliminates the surface potential and relates the input gate voltage to the output drain current giving a relatively simple current-voltage equation. In these models all the main parameters are defined based on the threshold voltage and this is the reason they are called "threshold-voltage-based" models. The initial version of SPICE models falls into this category. The main advantages of these models are the simplicity and flexibility to add features resulting from technology advancements. Unlike the surface-potential-based models based on internal quantities (like potentials etc.), the threshold-voltage-based models based on experimentally measured external quantities (like threshold voltage, ideality factor) are expected to be more efficient for low-frequency noise (LFN/RTN), reliability (NBTI/HCI) and variability compact modelings.

Concerning the charge-based-models, the current is formulated in terms of the inversion charge density at the source and drain ends of the channel. EKV model [53] for example falls into this category.

Finally, the surface-potential-based models are based on the calculation of the channel potential, as indicated by the term. Although accurate MOSFET device physics is applied in such models -thus they are more accurate than threshold-voltage-based models-difficult and complex iterative techniques are required to solve the implicit relations of the surface-potentials making them unpractical.

To conclude, it is obvious from all the above that in general, the use of compact models -regardless of the category they fall into- in circuit simulators allows the optimization of circuit performance for robust IC design and cost-effective IC products. This optimization is getting more and more difficult as device area is shrinking down. As already mentioned in the previous sections phenomena like SCEs, variability and reliability issues become critical for such advanced devices, making extremely difficult and hard the understanding and prediction of the performance of VLSI circuits containing billions of nano-scale devices. Therefore nowadays the main motivations for compact model development include [47]:

- ✓ Improving design efficiency using compact models instead of measured data from billions of transistors with different dimensions operating under different voltages that are used in an IC chip.

- ✓ Bypassing the conventional manual techniques for design and analysis of today's complex VLSI circuits.

- ✓ Designing an IC chip under the worst case conditions in order to examine the manufacturing tolerances before the production.

- ✓ Design-for-reliability enabling designers to predict and optimize circuit performance.

- ✓ Design-for-variability performing statistical analysis to optimize circuits in terms of the induced variability to circuit level.

# I.5 Dissertation goals and outline

The progressive scaling-down of CMOS technology has driven the semiconductor industry for the realization of faster and lower power consumption VLSI circuits and systems. Currently, silicon technology has entered the nano-CMOS era with 28 nm gate length MOSFETs in mass production, while sub-10 nm transistor is scheduled for production within 2017 [54], [55]. FDSOI transistors and FinFETs are the most promising architectures for scaling CMOS devices down to nanometer size, since they allow a significant reduction of the short channel effects. This dissertation seeks to contribute towards the development of generic simple and accurate compact models for advanced nano-scale MOSFETs and more precisely for FDSOI MOSFETs, suitable for incorporation into design tools, enabling the circuit designers to make projections beyond the available scaled dimensions and also to achieve device/circuit co-optimization. In this thesis we have decided to mainly study the FDSOI technology, because apart from the direct access to different FDSOI technologies, these devices offer efficiency in many levels. Compared to the fin-shaped field-effect transistors, the UTBB FDSOI technology has a much simpler fabrication process, thanks to its planar structure. Furthermore, its back-gate bias option makes it particularly interesting for multi-V<sub>t</sub> applications. Nevertheless, as already stated, at the same time serious reliability and performance issues emerge in such advanced nano-scale CMOS technologies. Besides the reliability phenomena, another challenge faced by researchers chasing the "scaling trend" is the transistor local variability.

Consequently, the motivations of this dissertation on the key issues arising from the scaling of new-era devices in the modern MOSFET design are two: the development of an analytical and compact drain current model, valid from weak to strong inversion, below and above threshold describing accurately the transfer and output characteristics of short-channel FDSOI devices and the investigation of reliability and variability issues of such advanced nano-scale transistors.

Chapter II provides a more detailed theoretical and technical background for better understanding of this dissertation, focusing on the critical MOSFET electrical parameters and the techniques for their extraction. More precisely, it demonstrates the so-called Y-Function and Split-CV methodologies for electrical characterization in diverse types of semiconductor devices based on current-voltage (I-V) and capacitance-voltage (C-V) measurements. The influence of AC signal oscillator level on the effective mobility measurement by split C-V technique in MOSFETs is also analyzed. Additionally, a new methodology allowing the extraction of MOSFET parameters is presented, based on the Lambert W (LW) function for the inversion charge which is valid over the full gate voltage range, i.e. from weak to strong inversion region and from linear to saturation region. At the end of the chapter, some fundamental issues concerning characterization of the low-frequency noise (LFN) in MOSFETs are described.

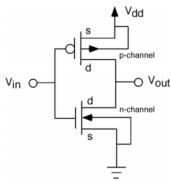

Chapter III presents the analytical drain current compact modeling in nanoscale FDSOI MOSFETs. First, simple analytical models for the front and back gate threshold voltages and ideality factors have been derived in terms of the device geometry parameters and the applied bias voltages with back gate control. Then, an analytical compact model for the drain current has been also developed for lightly doped short-channel UTBB FDSOI MOSFETs with back gate control, accounting for small geometry and other significant in such technologies effects like, saturation velocity, mobility degradation, quantum mechanical, velocity overshoot and self-heating effects. Finally, the drain current compact model is implemented via Verilog-A code for simulation of fundamental circuits in Cadence Spectre.

Chapter IV is dealing with reliability issues in FDSOI transistors. The hot-carrier degradation of nanoscale UTBB FDSOI n-MOSFETs has been investigated under different drain and gate bias stress conditions. The degradation mechanisms have been identified by combined LFN measurements at room temperature in the frequency and time domains. Additionally, the impact of the HC degradation on the device parameters has been expressed with semi-empirical models in terms of the stress time, channel length, drain bias and gate bias. Based on our analytical compact model of Chapter III, an HC aging model is proposed enabling to predict the device degradation stressed under different bias conditions, using a unique set of few model parameters determined for each technology through measurements. Finally, the NBTI stress characteristics and the recovery behavior under positive bias temperature stress of HfSiON gate dielectric UTBB FDSOI p-MOSFETs have been investigated. A model for the NBTI has been developed by considering hole-trapping/detrapping mechanisms, capturing the temperature and bias voltage dependence.

In Chapter V, studies of variability issues in advanced nano-scale devices are presented. The main sources of drain and gate current local variability have been thoroughly studied. First, the impact of the source-drain series resistance mismatch on the drain current variability has been investigated for 28 nm Bulk MOSFETs. A mismatch model that takes into consideration the source-drain series resistance local variability has been developed and

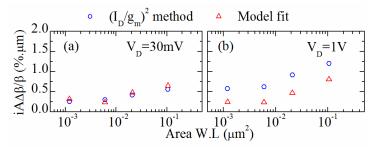

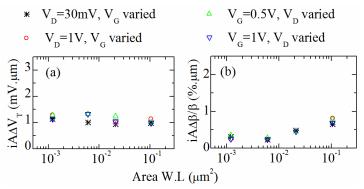

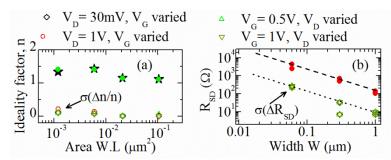

used to extract all mismatch parameters, including  $\sigma(\Delta V_d)$ ,  $\sigma(\Delta \beta/\beta)$  and  $\sigma(\Delta R_{sd})$ , in the linear and saturation regions. Then, a detailed statistical characterization of the drain current local and global variability in sub 15 nm Si/SiGe tri-gate nanowire p-MOSFETs and in 14 nm Si bulk FinFETs has been conducted. The main local and global variability MOSFET parameters  $(\sigma(\Delta V_d), \sigma(\Delta \beta/\beta), \sigma(\Delta R_{sd})$  and  $\sigma(\Delta n/n)$  have been extracted owing to a generalized analytical mismatch model valid in linear region. Finally, a complete investigation of the gate and drain current mismatch in advanced FDSOI devices has been performed. In this aspect, a fully functional drain current mismatch model, valid for any gate and drain bias condition has been developed. Finally, the drain current compact model of Chapter III implenteded in Verilog-A code has been used to examine the impact of drain current variability on fundamental circuits in Cadence Spectre.

An overall summary of this dissertation is presented in Chapter VI, which highlights the key research contributions and future research directions are suggested.

# II Characterization techniques and parameter extraction

# **II.1 Introduction**

In this chapter, firstly the basic structure of a MOSFET and the modes of operation are briefly described in Section II.1, assuming that the fundamental semiconductor concepts are already known. Next, using the long-channel MOS model, the expression of drain current as a function of the applied voltage bias is presented in Section II.2. In view of the fact that the accurate determination of the MOSFET electrical parameters is essential for understanding the physics and engineering of the devices, particularly for advanced ultrascaled devices, the powerful and useful Y-function method is analyzed in Section II.3 [56]. Furthermore, the concept of the new modified Y-Function method for parameter extraction of nanoscale MOSFETs is recalled.

Concerning the extraction of the intrinsic MOSFET parameters, like oxide thickness  $t_{ox}$ , oxide capacitance  $C_{ox}$ , effective mobility  $\mu_{eff}$  and doping concentration ( $N_D$  for n-MOS or  $N_A$  for p-MOS), the well-known split C-V method is presented in Section II.4. However, especially regarding the extraction of  $\mu_{eff}$ , this methodology always leads to underestimated mobility values below threshold voltage [10], [57], [58], [59], [60], [61], [62]. A too large amplitude of the drain voltage,  $V_d$  could be one of the reasons for this collapse below threshold due to the extreme non linear  $I_d(V_d)$  characteristics in weak inversion [59]. Another reason could reside in a systematic difference between the threshold voltage of the inversion charge  $Q_i$  (deduced from gate-to-channel capacitance  $C_{gc}$ ) and drain current transfer characteristics, yielding overestimation of the real inversion charge [59], [60], [62]. Within this context, one of the aims of this section is to investigate how the  $\mu_{eff}$  extraction is influenced by the AC signal oscillator level used by the impedance meter to measure the gateto-channel capacitance of the MOS transistor. Indeed, as with the amplitude of the drain voltage in  $I_d$  measurement, a too large AC signal level could induce a significant overestimation of the gate-to-channel capacitance below threshold due to the strong non linearity (exponential dependence) of inversion charge variation with gate voltage.

In Section II.5 a new MOSFET parameter extraction methodology is presented, which is based on the Lambert W function and allows the exploitation of the full gate voltage range i.e. from weak to strong inversion region, enabling to fully capture the transition between subthreshold and above threshold region, despite the reduction of supply voltage. A lot of methods have been proposed for the MOSFET parameter extraction - one of the most popular will be described in Section II.3 - but they are generally restricted to the above threshold region and mostly assume that the inversion charge varies linearly with gate voltage overdrive [56], [63], [64], [65], [66], [67], [68], [69], [70], [71], [72]. As the supply voltage  $V_{dd}$  is reduced with device scaling, the operating gate bias moves closer to the threshold voltage (near threshold operation), and the assumption that the inversion charge varies approximately linearly with gate voltage overdrive becomes less and less accurate. Few attempts to extend the parameter extraction from above to near threshold region was carried out using  $g_m/I_d(V_g)$  derivative [73], Lambert W function [74] or logarithmic function [75] of gate voltage overdrive for the inversion charge control, but it was not applied to the entire gate voltage range from weak to strong inversion. To this end, we first validate the usefulness of the LW function to describe accurately the gate-to-channel capacitance characteristics  $C_{gc}(V_g)$ , and, by turn, the MOSFET inversion charge  $Q_i(V_g)$  from weak to strong inversion region. Then, in conjunction with the conventional mobility expression, we apply this

analytical  $Q_i(V_g)$  law for the parameter extraction in advanced MOS devices from a 14 nm FDSOI CMOS technology. Finally, the new methodology has been validated for a wide range of back bias voltage and different channel lengths.

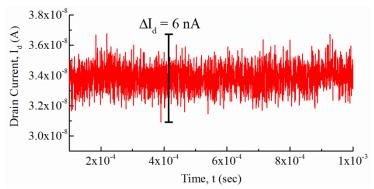

In order to characterize the quality and reliability of MOS transistors, low-frequency noise characteristics are rated especially important, since they can provide information like the oxide trap distribution and density, as well as the carrier scattering mechanisms. Furthermore, the scaling down of the transistors has led to the observation of a new type of noise, namely the random telegraph signal noise (RTN) due to individual carrier trapping at the silicon-oxide interface. To this aspect, the fundamental noise mechanisms as well as the basic LFN/RTN models used for the characterization of MOSFETs will be discussed in Section II.6.

# II.2 Basic operation of bulk MOS transistors

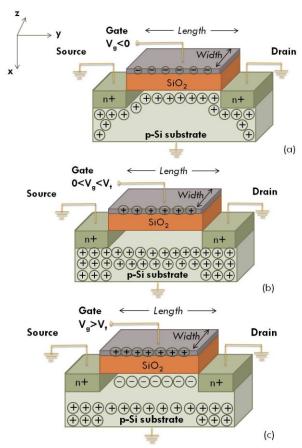

In this section the basic MOSFET operation principles will be recalled. MOSFET is a device where minority carriers (electrons for an n-MOS or holes for a p-MOS) flow in a conducting channel between the source and the drain creating current which is controlled by a voltage applied to the gate. Figure II-1 presents the basic structure of a bulk n-MOS transistor. The description that follows refers to the operation of the n-MOSFET, since the p-MOSFET operates in just the opposite way concerning the carriers and the polarizations. As shown in Figure II-1, the structure consists of three layers and four terminals, namely the Drain, Source, Gate and Substrate terminals. Regarding the first layer, the preferred gate material initially was the polycrystalline silicon. Nevertheless, metal gates with a high-k dielectric are used in modern CMOS transistors. The intermediate layer constitutes the dielectric layer which separates the gate terminal from the underlying source and drain terminals as well as the conducting channel that connects source and drain when the transistor is on, as is explained below. Finally, the last layer is the doped silicon body where the conducting channel will be developed.

As can be seen, the body is grounded and a voltage,  $V_g$  is applied to the gate. In case the applied voltage is negative (Figure II-1(a)), negative charges will be gathered in the gate while holes will be accumulated beneath it. Thus, this mode of operation is called accumulation mode. If a small positive gate voltage is applied (Figure II-1(b)) then we proceed to the depletion mode, where some positive charges will be gathered in the gate, while beneath the gate a layer without charges will be developed. Finally, if the applied gate voltage range is sufficient (Figure II-1(c)), namely  $V_g > V_t$  where  $V_t$  is a critical gate voltage value, more positive charges will be attracted to the gate, consistuting an inverted charge with regards to the initial p-type substrate, this is the reason it is called inversion layer.

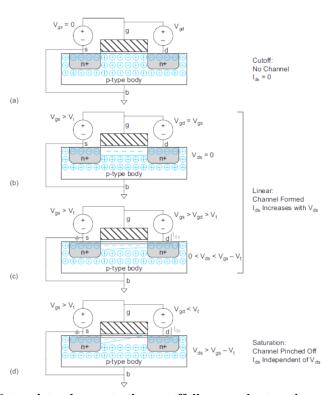

Figure II-2 demonstrates an n-MOS transistor and its three regions of operation, namely the *cutoff*, *linear* and *saturation* regions. When the gate-to-source voltage,  $V_{gs}$ , is lower than the threshold voltage,  $V_t$ , the transistor is in the *cutoff* or *subthreshold* mode of operation (Figure II-2(a)). At this state, the source and drain have free electrons, while the body has free holes [76]. If the source is grounded and the body and drain or source junctions are zero-biased or reverse-biased, the electron charge is small and the drain current is called *subthreshold current* [77], [78]. Only for reasons of simplicity, this current can be sometimes approximated equal to zero.

Figure II-1 n-MOS structure illustrating the accumulation (a), depletion (b) and inversion (c) modes of operation.

When  $V_{gs}$  is greater than  $V_t$ , the *channel* is formed and connects the source and drain current depends on both the gate and drain voltage, is called *linear* or *triode*. If the drain-to-source voltage,  $V_{ds}$  is zero (Figure II-2(b)), there is no electric field to push the drain current from drain to source. But as  $V_{ds}$  increases Figure II-2(c), drain current flows through the channel from drain to source. While  $V_{ds}$  continues increasing, there is a critical value of drain-to-source voltage,  $V_{ds,sat}$  in which the gate-to-channel voltage at the drain end,  $V_{gd}$  becomes equal to  $V_t$ . Under this condition, namely at  $V_{ds} = V_{gs} - V_t$  we say that that the channel is *pinched off* (Figure II-2(d)). Above this drain voltage the channel depends only on the gate voltage and the transistor is in *saturation* or *active* mode of operation.

Mathematically, in order to produce the basic drain current equations for every region of operation, the MOSFET gradual channel approximation is used. According to this, if a drain voltage,  $V_{ds}$  is applied, then the voltage along the channel,  $U_c$  varies. Consequently, at every position x (see Figure II-1(a)) of the channel, a channel voltage  $U_c$  is applied, implying that the charge density in the inversion layer,  $Q_i$  also varies along the channel. Thus, we have:

$$I_d(V_{ds}, V_{gs}) = W Q_i(V_{ds}, V_{gs}) \mu_{eff} \frac{dU_c}{dx} \iff I_d(V_{ds}, V_{gs}) = \int_0^{V_{ds}} \frac{W}{L} Q_i(V_{ds}, V_{gs}) \mu_{eff} dU_c \qquad \text{Eq. II.1}$$

where W is the channel width and  $\mu_{\it eff}$  the effective mobility defined in the next paragraph.

In subthreshold region, namely in weak inversion where  $V_{gs} < V_t$ , the charge in the channel will be [79]:

$$Q_i(V_{ds}, V_{gs}) = Q_{i0}(V_{ds}, V_{gs})e^{\frac{q}{kT}U_C}$$

Eq. II.2

Figure II-2 n-MOS transistor demonstrating cutoff, linear and saturation regions of operation [76].

Yielding to the exponential drain current equation in weak inversion:

$$I_d(V_{ds}, V_{gs}) = I_{d0} \left( 1 - e^{\frac{q}{kT}V_{ds}} \right)$$

Eq. II.3

In strong inversion where  $V_{gs} > V_t$ , we have for the inversion charge:

$$Q_i(V_{ds}, V_{gs}) \approx -C_{ox}(V_{gs} - V_t - U_c)$$

Eq. II.4

And thus, we obtain the following two equations for the drain current in linear and saturation region, respectively:

$$I_{d}(V_{ds}, V_{gs}) = \frac{W}{L} \cdot \mu_{eff} \cdot C_{ox} \cdot (V_{gs} - V_{t}) \cdot V_{ds} \text{ if } V_{ds} < V_{gs} - V_{t}$$

$$I_{d}(V_{gs}) = \frac{W}{2 \cdot L} \cdot \mu_{eff} \cdot C_{ox} \cdot (V_{gs} - V_{t})^{2} \text{ if } V_{ds} \ge V_{gs} - V_{t}$$

(b)

$$Eq.$$

II.5

# **II.2.1** Effective Mobility

As it has been already mentioned, the presence of  $V_{ds}$  creates a lateral electric field along the channel. Therefore, due to this field, each carrier in the channel is accelerated to an average velocity, v, which will be proportional to it:

$$v = \mu \cdot E$$

Eq. II.6

where  $\mu$  is a constant called *mobility* [80]. When strong lateral or vertical electric field is applied, Eq. II.6 is no longer valid since degradation in the carriers' effective mobility is observed.

Mobility degradation in the linear region of operation can be modeled by replacing  $\mu$  with a smaller  $\mu_{eff}$  that is a function of  $V_{gs}$ :

$$\mu_{eff} = \frac{\mu_0}{1 + \theta_1 (V_{gs} - V_t) + \theta_2 (V_{gs} - V_t)^2}$$

Eq. II.7

where  $\mu_0$  is the *low-field mobility*, and  $\theta_1$  and  $\theta_2$  are the first and second order mobility attenuation factors [81]. Parameter  $\theta_1$  describes the phonon scattering due to enhanced confinement and larger wave function overlap integrals, while  $\theta_2$  describes the surface roughness scattering.

Concerning the saturation region where higher electric fields are applied the carriers gain considerable energy from the field so that their velocity reaches a value, the so-called saturation velocity,  $v_{sat}$ . This effect can be introduced to the effective mobility as follows:

$$\mu_{eff} = \frac{\mu_0}{1 + \mu_0 \frac{V_{ds}}{L \cdot v_{sat}}}$$

Eq. II.8

# **II.2.2** Source-Drain Series Resistance

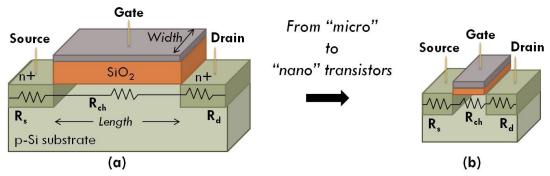

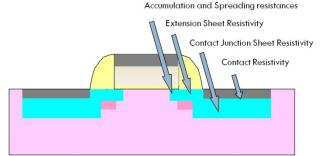

Another component which has an important impact on the drain current is the *Source-Drain (SD) Series Resistance*,  $R_{sd}$ . As the channel length is scaled down, the  $R_{sd}$  ( $R_{sd} = R_s + R_d$ ) contributes more and more to the total device resistance,  $R_{tot}$  ( $R_{tot} = R_{ch} + R_s + R_d$ ) as indicated in Figure II-3. At this point it should be mentioned that source resistance  $R_s$  and similarly drain resistance  $R_d$ , include all the parasitic resistance elements related to the source and the drain respectively, as presented in Figure II-4.

Figure II-3 Impact of  $R_s$  and  $R_d$  on the total resistance,  $R_{tot}$  in a long (a) and a short (b) channel bulk n-MOSFET.

Figure II-4 Parasitic resistance elements in MOSFETs [82].

In general, due to the presence of source and drain resistances,  $R_s$  and  $R_d$  respectively, when a gate-to-source and a drain-to-source voltage is applied to the device, then a difference is observed between these external voltages on the outer pad, indicated as  $V_{gs}$  and  $V_{ds}$  respectively, and the internal voltages  $V_{gs}$  and  $V_{ds}$ . Therefore:

$$V_{gs}^{'} = V_{gs} + R_s \cdot I_d$$

Eq. II.9

$$V_{ds}^{'} = V_{ds} + (R_s + R_d) \cdot I_d$$

Eq. II.10

Consequently, taking into account the SD series resistance, the measured attenuation factor,  $\theta_l$  is [81]:

$$\theta_1 = \theta_{1,0} + G_m \cdot R_{sd}$$

Eq. II.11

where  $\theta_{I,0}$  is the intrinsic first order mobility attenuation factor and  $G_m$  is the static transconductance parameter:

$$G_m = \frac{W}{L} \cdot C_{ox} \cdot \mu_0$$

Eq. II.12

# **II.3 Y-Function Methodology**

A powerful and physically meaningful method to extract the MOSFET parameters, namely  $V_{b}$   $\mu_{0}$ ,  $L_{eff}$ ,  $\theta_{1}$  and  $\theta_{2}$  is the *Y-Function*. This useful function, firstly presented in [56], is defined as following:

$$Y = \frac{I_d}{\sqrt{g_m}}$$

Eq. II.13

where  $I_d$  is the drain current in linear region (Eq. II.5(a)) and  $g_m$  is the *transconductance*, one of the most important MOSFET quantities:

$$g_m = \frac{\partial I_d}{\partial V_{gs}}$$

Eq. II.14

Combining Eq. II.5(a) and Eq. II.14 we have:

$$g_{m} = \frac{W}{L} C_{ox} \frac{\mu_{0} \cdot (1 - \theta_{2} (V_{gs} - V_{t})^{2})}{(1 + \theta_{1} (V_{gs} - V_{t}) + \theta_{2} (V_{gs} - V_{t})^{2})^{2}} V_{ds} \Leftrightarrow g_{m} = \beta \frac{(1 - \theta_{2} (V_{gs} - V_{t})^{2})}{(1 + \theta_{1} (V_{gs} - V_{t}) + \theta_{2} (V_{gs} - V_{t})^{2})^{2}}$$

**Eq. II.15**

where  $\beta$  represents the *current gain factor*:

$$\beta = \frac{W}{L} \cdot C_{ox} \cdot \mu_0 \cdot V_{ds}$$

Eq. II.16

Consequently, from equations II.5(a), II.13 and II.15, we obtain:

$$Y = \sqrt{\beta} \cdot \frac{\left(V_{gs} - V_t\right)}{\sqrt{1 - \theta_2 \left(V_{gs} - V_t\right)^2}}$$

Eq. II.17

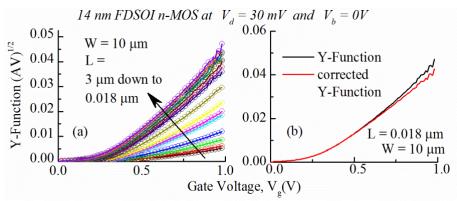

In Figure II-5(a) the calculated Y-Function,  $Y(V_g)$ , is depicted for several gate lengths of n-MOS transistors issued from a 14 nm FDSOI CMOS technology. In strong inversion the Y-Function varies linearly with  $V_g$  and thus, normally the threshold voltage can be extracted from the x-axis intercept. The current gain factor  $\beta$  and thus,  $G_m$  can also be extracted from the slope of the curves. Therefore,  $\mu_0$  can be calculated from Eq. II.12.

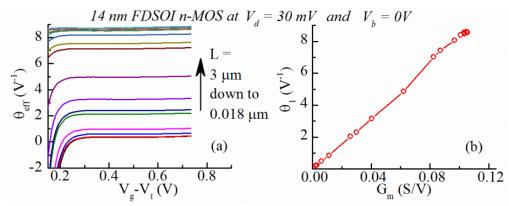

Afterwards, in order to extract the first and second order mobility attenuation factors, we define  $\theta_{eff}$ :

$$\theta_{eff} = \frac{\beta}{I_d} - \frac{1}{V_{gs} - V_t} \iff \theta_{eff} = \theta_1 + \theta_2 (V_{gs} - V_t)$$

Eq. II.18

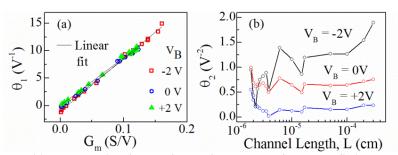

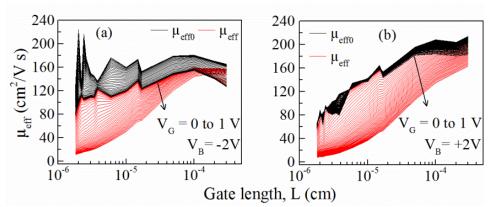

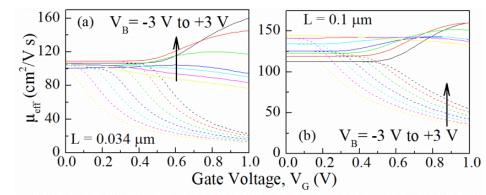

By plotting parameter  $\theta_{eff}$  with the gate overdrive voltage,  $V_{gt} = V_{gs}$  -  $V_t$  for different gate lengths, we observe that  $\theta_{eff}$  reaches a plateau for high gate overdrive voltages. Indeed, an example for 14 nm FDSOI n-MOSFETs is presented Figure II-6(a). Consequently, we obtain  $\theta_I$  from the x-axis intercept of  $\theta_{eff}$  -  $(V_{gs}-V_t)$  plot and  $\theta_2$  from the corresponding slope. Therefore, after having extracted  $\theta_I$  for several gate lengths, we can plot  $\theta_I$  as a function of  $G_m$ . This plot will ideally, result in a straight line, whose slope corresponds to the SD series resistance (Eq. II.11). An example of the plot  $\theta_I$ -  $G_m$  for 14 nm FDSOI devices is illustrated in Figure II-6(b).

As can be seen in Figure II-5(a), the presence of  $\theta_2$  results in a non-linearity of  $Y(V_g)$  curves in strong inversion. In order to overcome this problem, we applied the new Y-Function method [83]. In general, this method relies on *i iteration steps*, until a linear curve is obtained (see Figure II-5(b)). More precisely, after having applied the Y-Function as described above and obtained a first approximation of  $\theta_2$ , we make a correction by eliminating the influence of  $\theta_2$ .

Figure II-5 Y-Function as a function of the gate voltage for different gate lengths of n-MOS 14 nm FDSOI devices in linear region (a) and Y-Function before (black line) and after correction (1 iteration step) (red line) of an FDSOI MOSFET with L=0.018 μm (b).

For this reason it is defined:

$$Y_{i+1}(V_{gs}) = Y_i(V_{gs}) \cdot \sqrt{1 - \theta_{2,i}(V_{gs} - V_t)^2}$$

Eq. II.19

It is obvious from the example presented in Figure II-5(b), that Y-Function becomes more linear in a wider range of  $V_g$  in strong inversion even from the first round of iteration and thus, resulting in a more precise parameter extraction.

Figure II-6  $\theta_{eff}$  as a function of  $(V_g - V_t)$  for different gate lengths of n-MOS 14 nm FDSOI devices in linear region (a) and the corresponding  $\theta_1$  as a function of  $G_m$  (b).

# **II.4** Split C-V Methodology

Except for the drain current transfer characteristics  $(I_d - V_g)$  in linear region, it is widely known that capacitance characteristics (C-V) are also useful for transport parameter extraction in MOSFETs. Especially, *split C-V technique* is one of the most popular methods for the extraction of several intrinsic channel properties, like  $C_{ox}$ ,  $L_{eff}$ , the flat-band voltage,  $V_{fb}$  or the substrate doping concentration,  $N_A$  or  $N_D$ . This method relies on the mobile channel charge density measurement and composes of gate-to-channel capacitance,  $C_{gc}$ , gate-to-bulk capacitance,  $C_{gb}$  and total capacitance,  $C_{tot}$ , measurements.

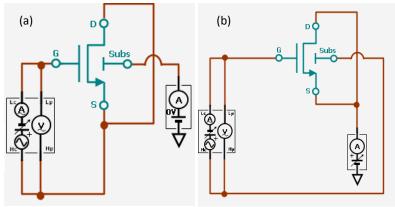

Concerning the  $C_{gc}$  measurement, this is realized by connecting the "high" terminal of an LCR-meter to the gate (G) of the device, the "low" terminal to the Source (S) and Drain (D) and the Substrate (B) to the ground (Figure II-7(a)).

Figure II-7 Configuration for  $C_{gc}$  (a) and  $C_{gb}$  (b) measurements.

On the other hand, in order to obtain the  $C_{gb}$ , the gate has to be connected again to the "high" terminal of the LCR-meter, but this time the substrate to the "low", while the source and the

drain have to be grounded (Figure II-7(b)). Finally, the  $C_{tot}$  measurement consists of a superposition of the two previous measurements since  $C_{tot} = C_{gc} + C_{gb}$ . This means that the gate is connected to the "high" terminal while the source, drain and substrate are shorted and connected to the "low" terminal.

# II.4.1 Principle of effective mobility extraction

As has been already mentioned, the split C-V technique is one of the most popular methods for the extraction of the effective mobility in MOSFETs. To achieve this, the inversion charge,  $Q_i(V_g)$  has to be calculated by integrating the  $C_{gc}(V_g)$  curves starting from the accumulation until the inversion region of operation [57], [58]:

$$Q_i(V_g) = \int_{V_{gc}}^{V_{g,\text{max}}} \frac{C_{gc}(V_g)}{W \cdot L_{eff}} dV_g$$

Eq. II.20

The drain current of a MOSFET in linear operation is given by Eq. II.5(a). Further, in the linear regime, where  $V_{ds}$  is small, the drain current can be expressed in terms of the inversion charge:

$$I_d = rac{W_{eff}}{L_{eff}} \cdot \mu_{eff} \cdot V_{ds} \cdot Q_i$$

Eq. II.21

Thus, the effective mobility can be extracted by combining both drain current and capacitance measurements in the linear region as a function of the gate voltage.

$$\mu_{eff} = \frac{L_{eff}}{W \cdot V_{ds}} \cdot \frac{I_d}{Q_i}$$

Eq. II.22

# II.4.2 Influence of AC signal oscillator level on effective mobility measurement by split C-V technique in MOSFETs

When capacitance measurements are performed, some critical points in the measurement configuration should be taken into account. One of them for example is the measurement frequency. Usually we select a high frequency range, namely in MHz range, in order to eliminate the influence of possible interface states, which contribute also to the capacitance especially in the transition between the accumulation and inversion region. Another critical point is the choice of the AC signal oscillator level. Thus, we investigated the impact of the AC signal oscillator level on the effective mobility measurement by *split C-V technique* in MOSFETs [84].

# II.4.2.1 Device fabrication process and electrical measurements conditions

Both  $C_{gc}(V_g)$  and  $I_d(V_g)$  characteristics were measured on  $10\times10~\mu\text{m}^2$  nMOS transistors from an advanced FDSOI technology [85]. The gate stack consists of TiN/Hf-based oxide dielectric with equivalent oxide thickness 1.2 nm. The channel Si thickness is about 6-7 nm and the buried oxide BOX is 20 nm thick. Capacitance and drain current measurements were performed at wafer level with an Agilent B1500 semiconductor parameter analyzer. The AC signal oscillator level  $(\Delta V_g)$  was varied from 10 to 250 mV for

capacitance measurements carried out at 1 MHz frequency. The drain voltage  $V_d$  for  $I_d(V_g)$  acquisition was changed from 5 to 50 mV.

### II.4.2.2 Results

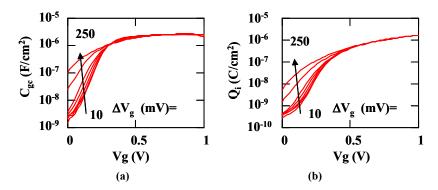

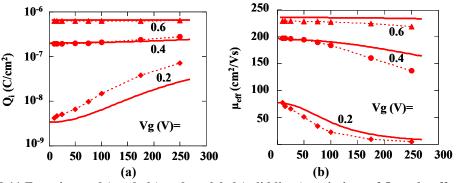

Figure II-8 shows typical  $C_{gc}(V_g)$  and corresponding  $Q_i(V_g)$  characteristics obtained for various AC signal oscillator levels. Note the huge overestimation of the capacitance and inversion charge in weak inversion region below threshold (here  $V_t$ =0.35V) as the oscillator level increases.

Figure II-8 Typical  $C_{gc}(V_g)$  and  $Q_i(V_g)$  characteristics as obtained on  $10\times10~\mu m^2$  nMOS transistors for various oscillator levels  $\Delta V_g$ .

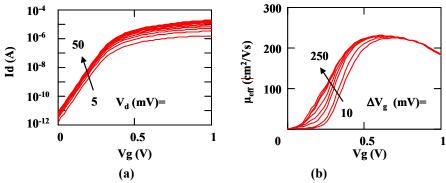

Figure II-9(a) displays typical  $I_d(V_g)$  characteristics obtained with various drain voltage varying from 5mV to 50mV. In Figure II-9(b) are shown the associated  $\mu_{eff}(V_g)$  curves calculated with Eq. II.22 for various oscillator levels  $\Delta V_g$  and using the  $I_d(V_g)$  curve measured with the smallest  $V_d$  value (5mV) for minimizing the error due to  $V_d$  [59]. Moreover, provided that the measurement was performed on a large device, the difference between the effective and the real dimensions is negligible. Note the strong influence of the oscillator level on the effective mobility below threshold.

Figure II-9 a) Typical  $I_d(V_g)$  for various drain voltages and b)  $\mu_{eff}(V_g)$  characteristics as obtained on  $10\times10~\mu\text{m}^2$  n-MOS transistors for various oscillator levels  $\Delta V_g$  ( $V_d$ =5mV).

However, even for the smallest oscillator level (here 10mV),  $\mu_{eff}$  is still cancelling out for very low gate voltage values (here  $V_g < 0.15V$ ). This means that, despite the use of very small oscillator amplitude, the  $C_{gc}$  capacitance could not be measured with enough accuracy at very small gate voltage in order to follow the huge dynamic of  $Q_i(V_g)$  and, by turn, of  $I_d(V_g)$  variations (5-6 decades) in weak inversion.

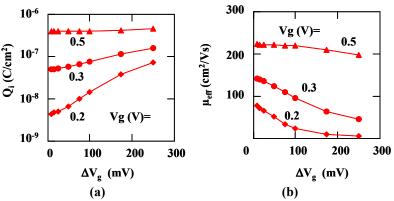

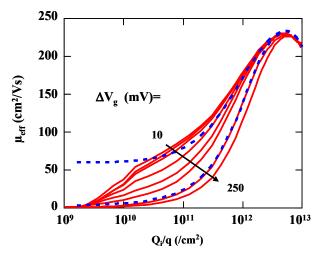

Figure II-10 shows the variations of the inversion charge and associated effective mobility with the AC signal oscillator amplitude for different values of gate voltage going from very weak to medium inversion region. As can be seen from this figure, the oscillator

level has a strong influence on the inversion charge and related effective mobility even for oscillator level  $\Delta V_g$  as small as few tens of mV. Actually, the effective mobility decreases linearly with  $\Delta V_g$  up to 100mV for gate voltage below threshold. Then,  $\mu_{eff}$  smoothly tends to zero for large  $\Delta V_g$  values due to enhanced non linear distortion. Indeed, for gate voltage above threshold,  $\mu_{eff}$  becomes nearly independent of the oscillator level, as the transistor operates more and more in linear region at strong inversion regime.

Figure II-10 a) Variations of  $Q_i$  and b)  $\mu_{eff}$  with AC signal oscillator level  $\Delta V_g$  for various gate voltages ( $V_g$ =0.2V, 0.3V, 0.5V).

### II.4.2.3 Modeling and Simulation

For modeling the impact of the oscillator level on the gate-to-channel capacitance, we remark that  $C_{gc}$  is no longer exactly equal to the derivative of  $Q_i$  with respect to  $V_g$ , as it should be for very small  $\Delta V_g$  values. Instead, we consider that the apparent measured capacitance,  $C_{gcapp}$ , is now given by the average of the inversion charge variation over one period of time (t) of the AC sinusoidal signal,  $\delta V_g(t) = \Delta V_g.sin(2\pi t/T_p)$ , applied on top of the DC gate voltage such that,

$$C_{cgapp}(V_g, \Delta V_g) = \frac{1}{T_p} \int_0^{T_p} \frac{Q_i(V_g + \delta V_g(t)) - Q_i(V_g)}{\delta V_g(t)} dt$$

Eq. II.23

where  $T_p$  is signal period.

The associated apparent inversion charge,  $Q_{iapp}(V_g, \Delta V_g)$  is then obtained by integration over gate voltage of  $C_{gcapp}(V_g)$  as done for measured data.

For the inversion charge modeling, we assume that it is well described by a Lambert W function, which provides a very good analytical approximation of  $Q_i(V_g)$  as shown elsewhere [86].

For the effective mobility modeling, we adopt an approach combining, using the Matthiessen rule, a screened Coulomb scattering limited mobility below threshold and a surface roughness limited mobility well above threshold [87] such that  $\mu_{eff}$  reads as a function inversion charge,

$$\mu_{eff}(Q_i) = \left[ \frac{1}{\mu_C (1 + Q_i/Q_c)} + \frac{1 + \theta_2 \cdot (Q_i / C_{ox})^2}{\mu_0} \right]^{-1}$$

Eq. II.24

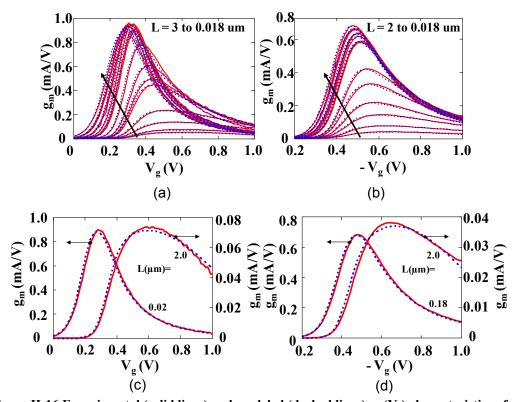

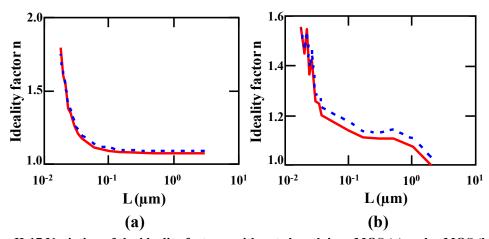

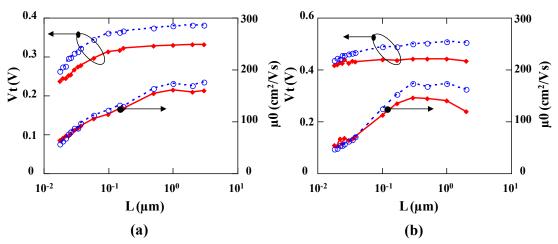

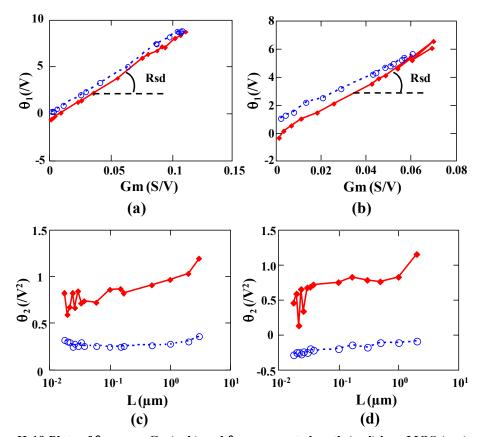

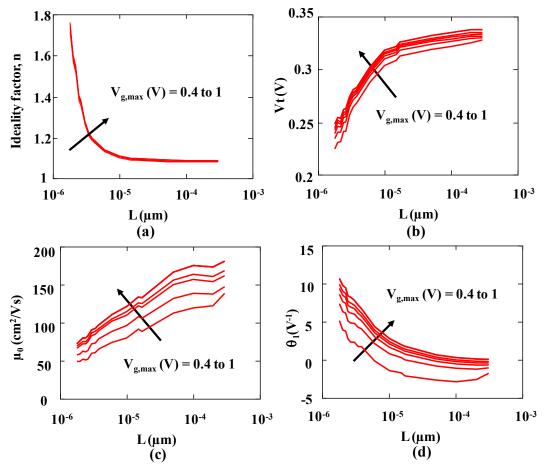

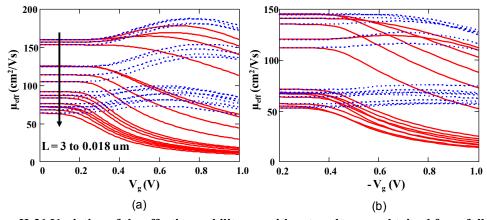

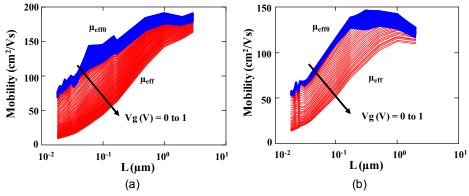

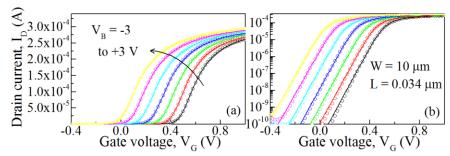

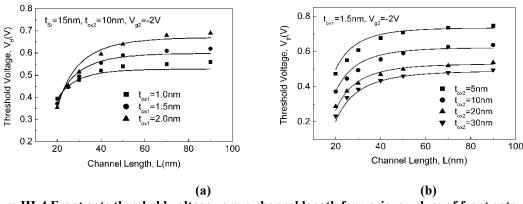

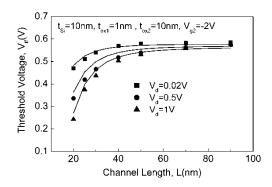

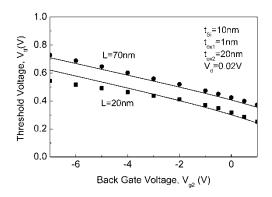

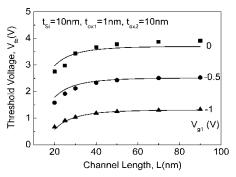

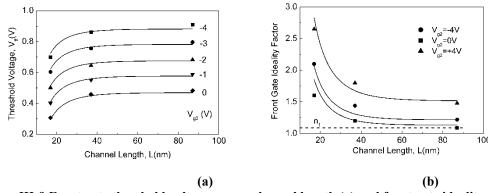

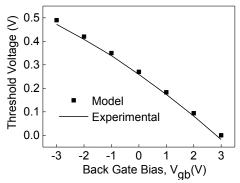

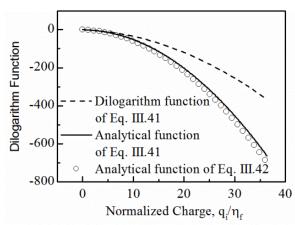

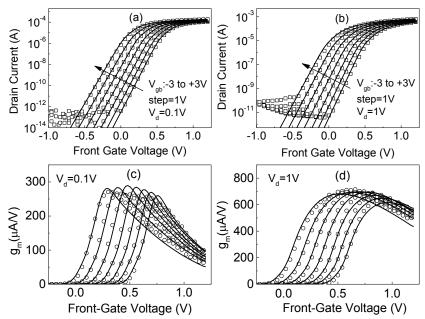

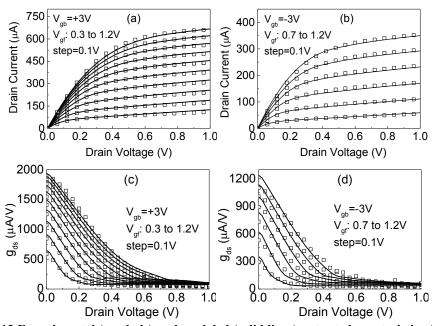

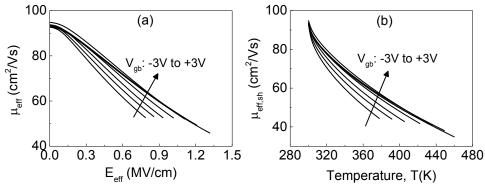

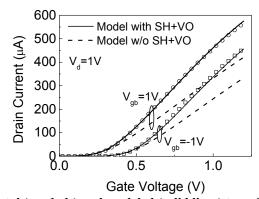

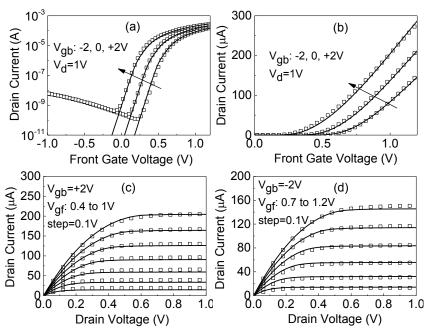

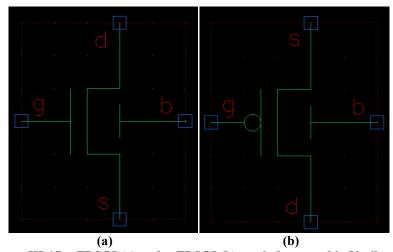

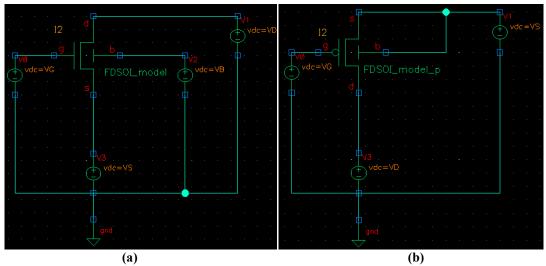

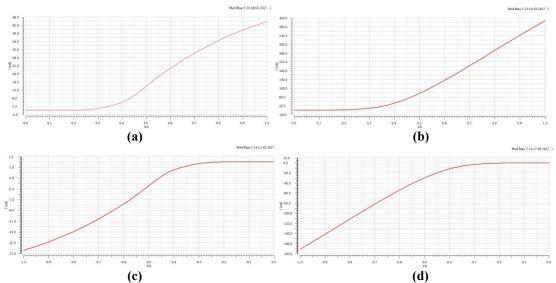

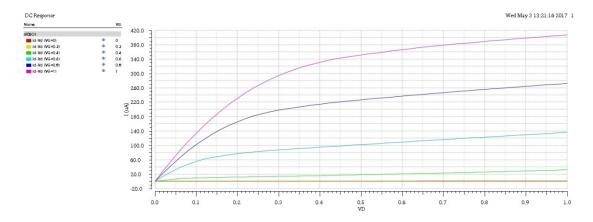

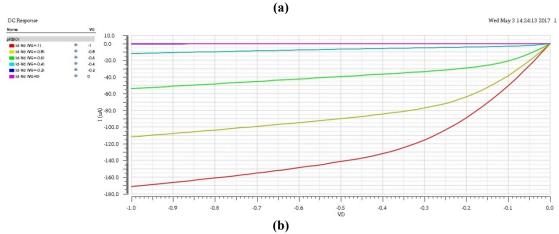

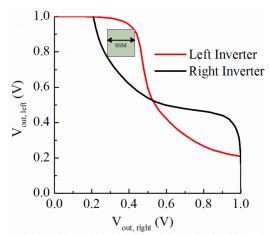

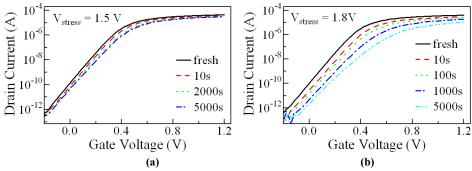

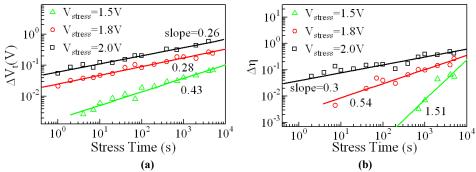

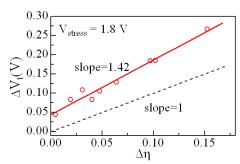

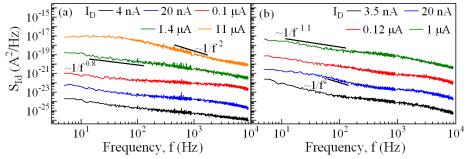

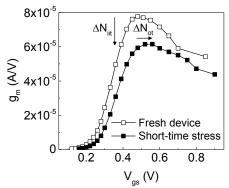

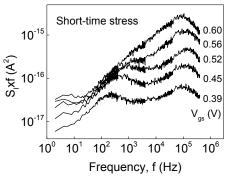

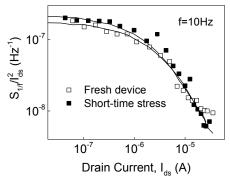

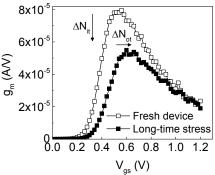

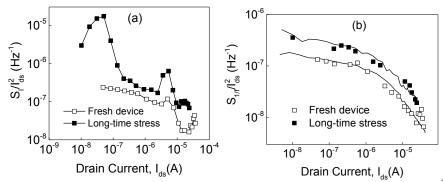

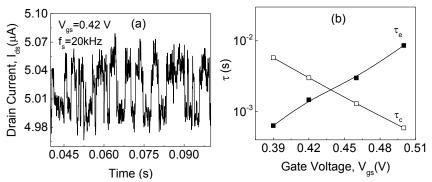

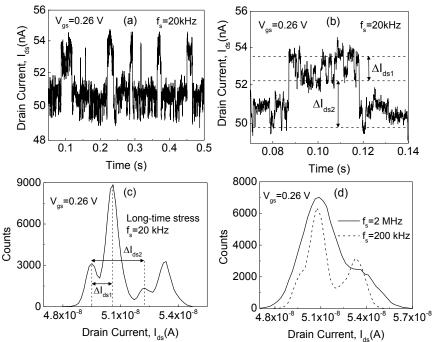

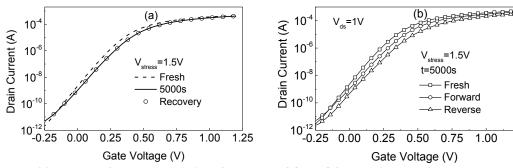

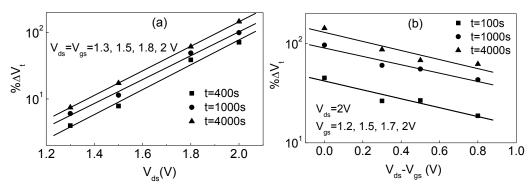

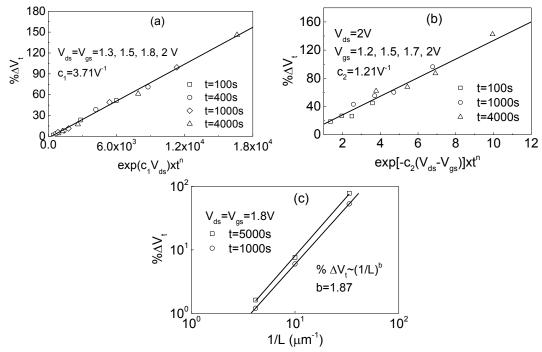

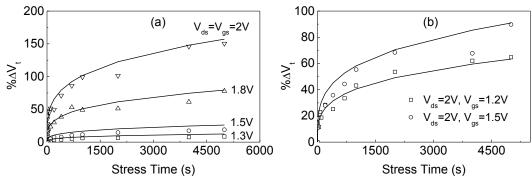

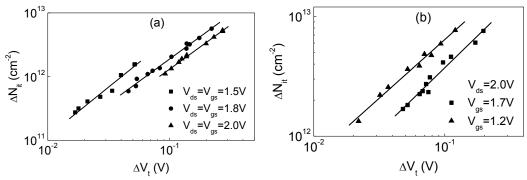

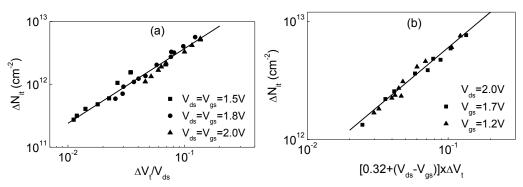

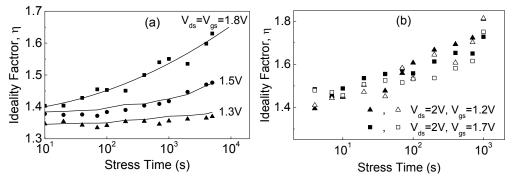

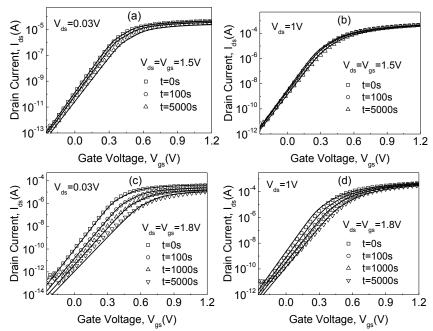

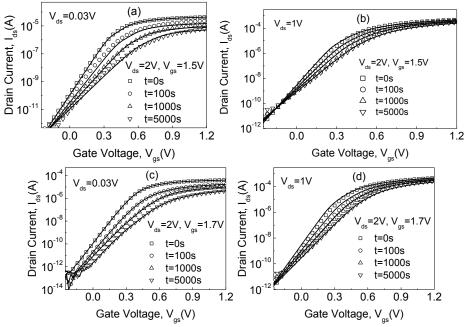

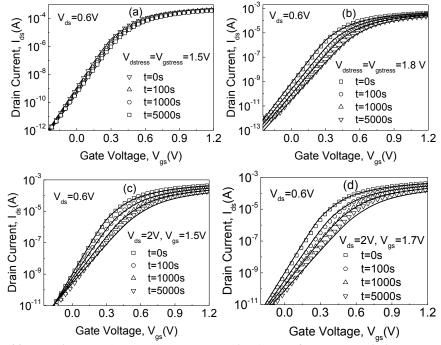

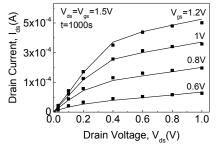

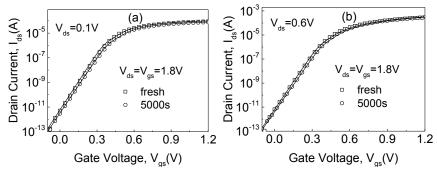

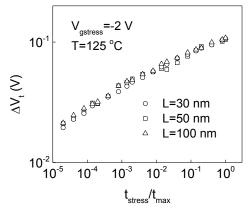

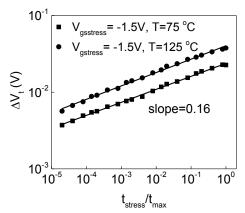

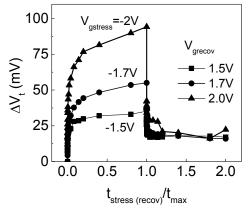

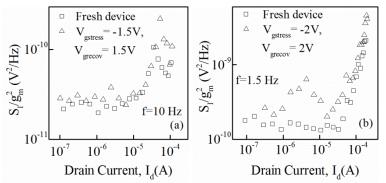

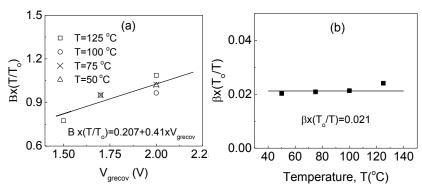

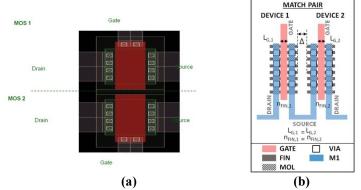

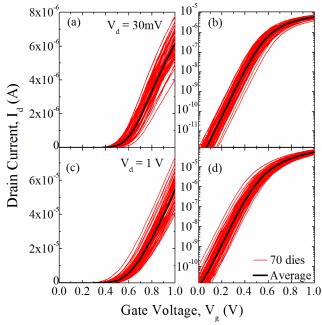

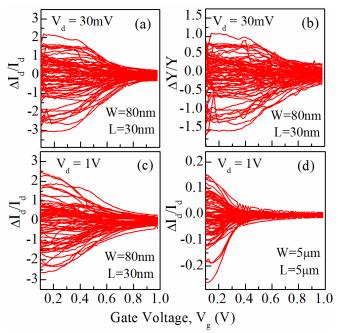

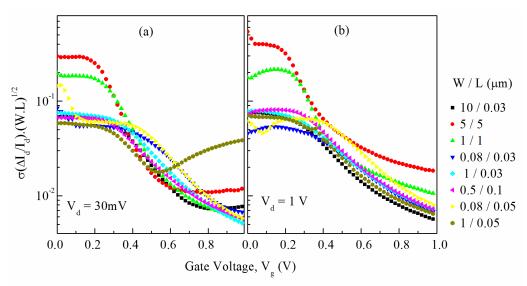

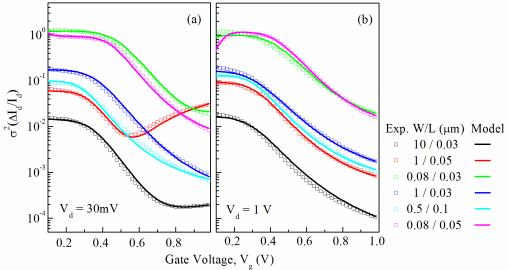

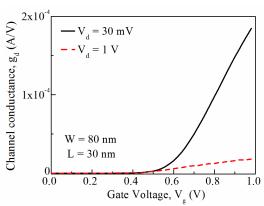

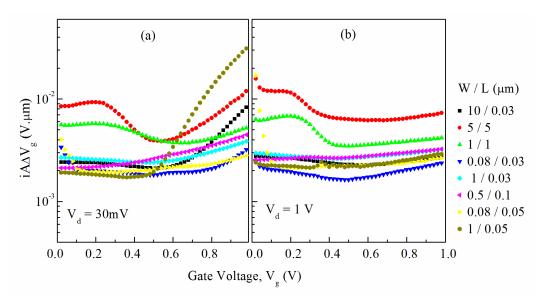

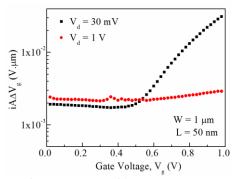

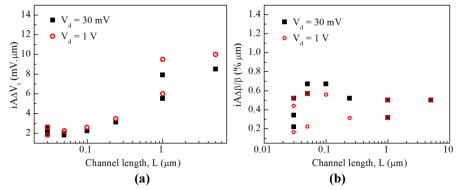

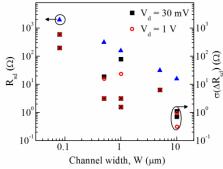

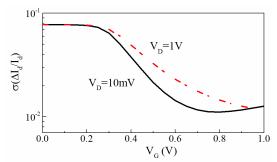

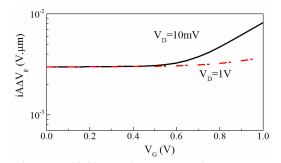

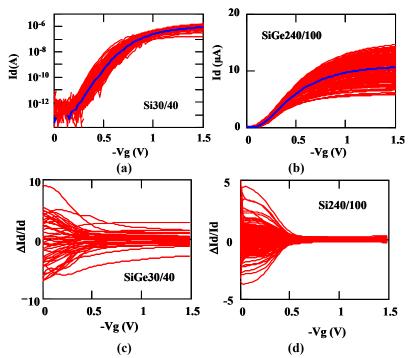

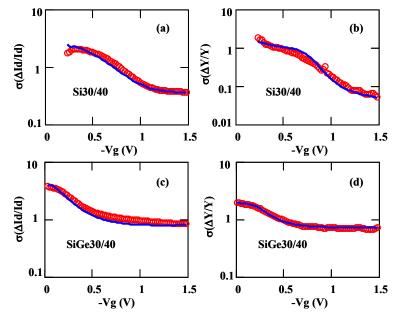

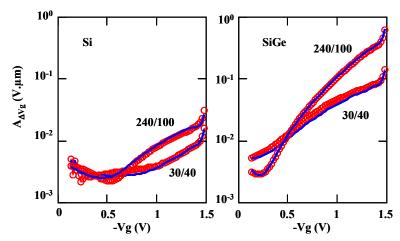

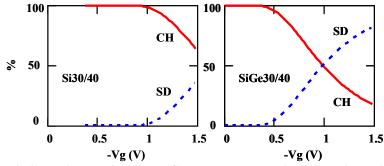

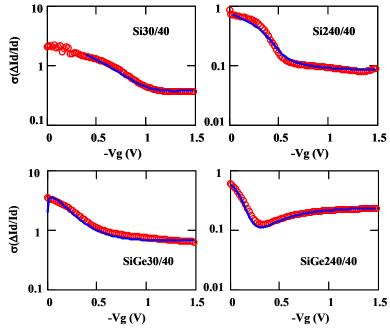

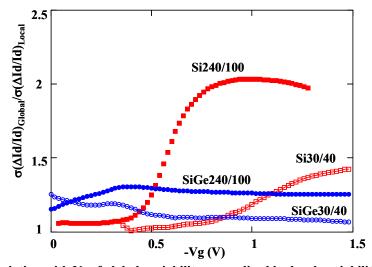

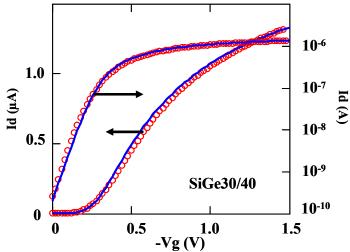

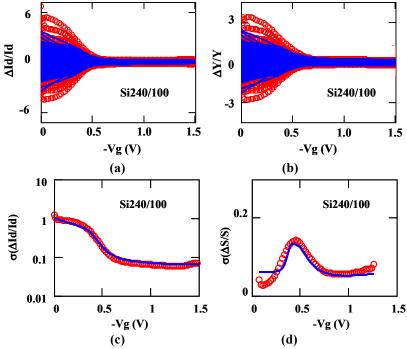

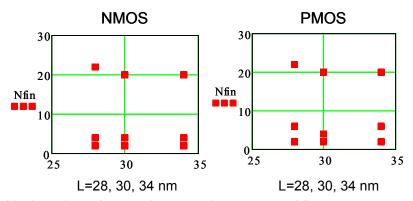

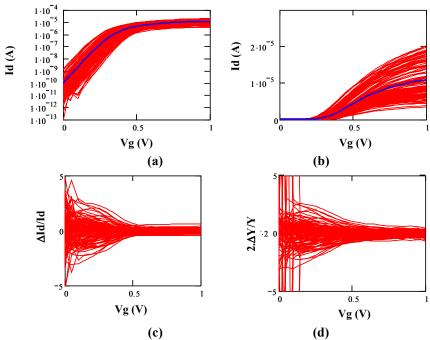

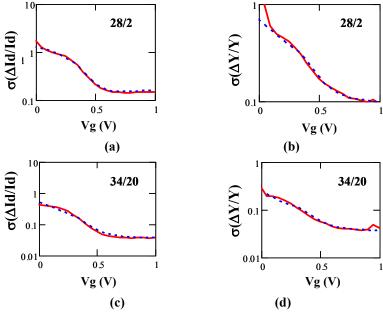

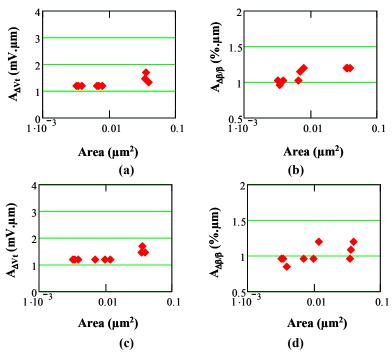

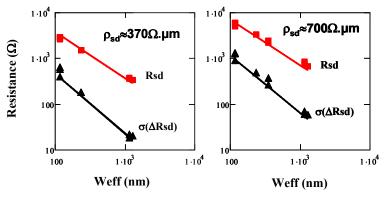

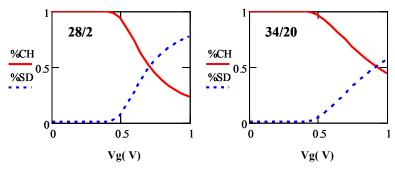

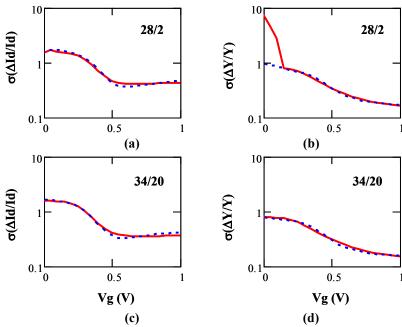

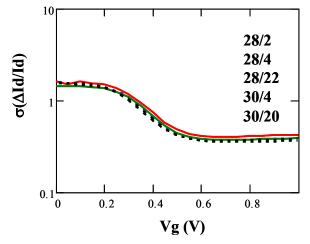

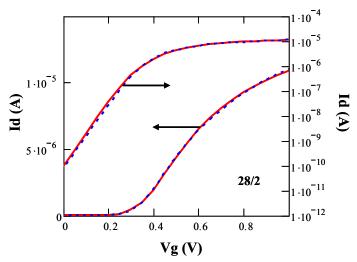

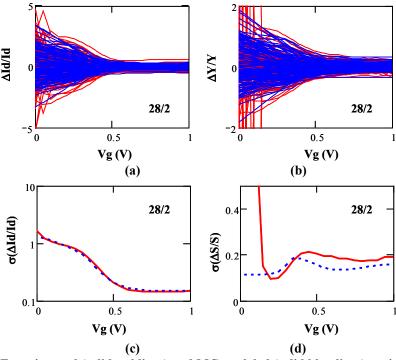

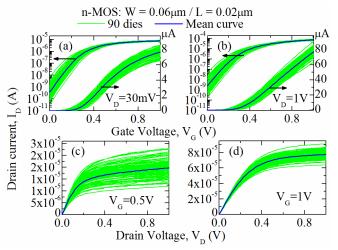

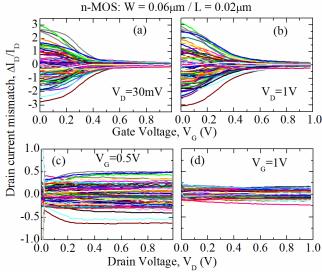

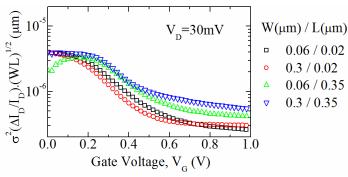

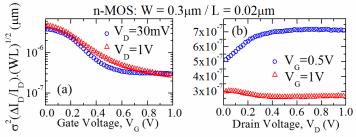

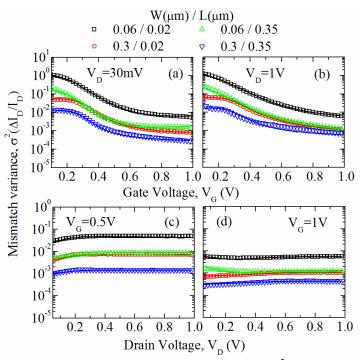

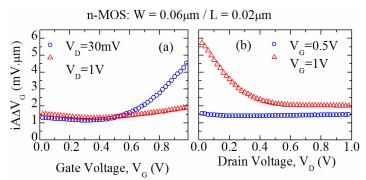

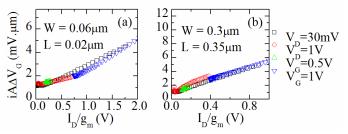

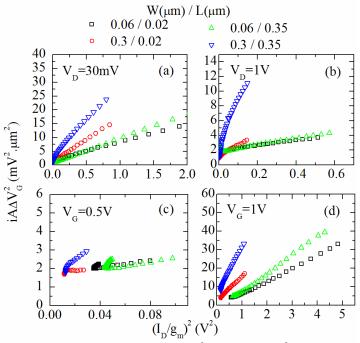

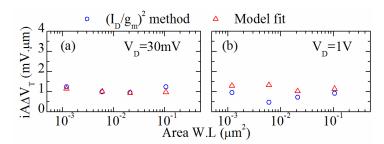

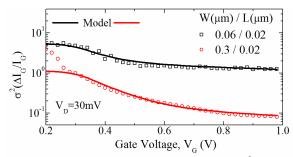

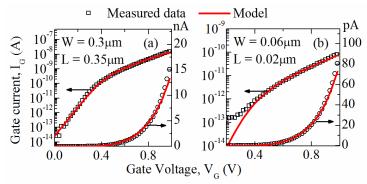

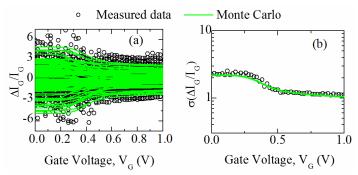

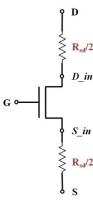

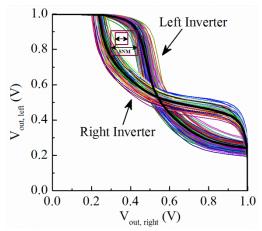

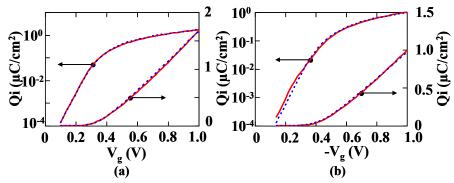

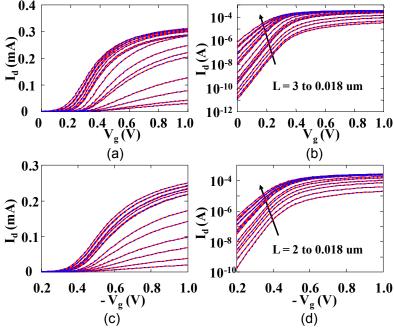

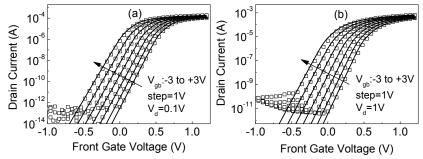

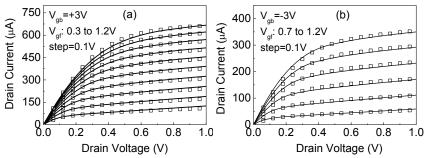

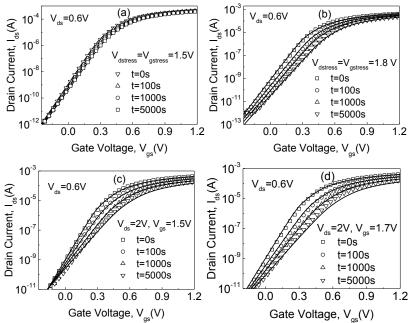

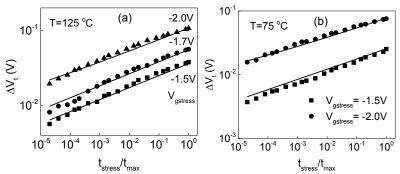

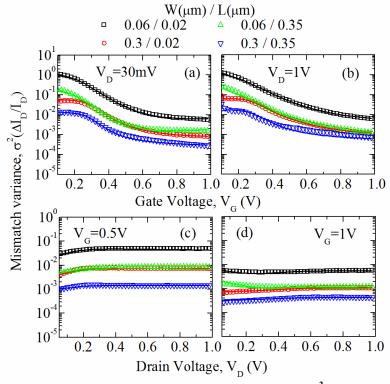

where  $\mu_C$  refers to the unscreened Coulomb mobility below threshold and  $\mu_0$  to the phonon limited low field mobility,  $\theta_2$  is the second order mobility attenuation coefficient,