## Approche logicielle pour améliorer la fiabilité d'applications parallèles implémentées dans des processeurs multi-cœur et many-cœur

Vanessa Carolina Vargas Vallejo

#### ▶ To cite this version:

Vanessa Carolina Vargas Vallejo. Approche logicielle pour améliorer la fiabilité d'applications parallèles implémentées dans des processeurs multi-cœur et many-cœur. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes, 2017. Français. NNT: 2017GREAT042. tel-01693054

## HAL Id: tel-01693054 https://theses.hal.science/tel-01693054

Submitted on 25 Jan 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ÉLECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministérial : 25 mai 2016

Présentée par

## Vanessa Carolina VARGAS VALLEJO

Thèse dirigée par Raoul VELAZCO, Directeur de Recherche, CNRS et codirigée par Jean-François MÉHAUT, Professeur, Grenoble UJF

préparée au sein Laboratoire Techniques de l'informatique et de la Microélectronique pour l'Architecture des Systèmes Intégrées et de l'École Doctorale Électronique, Électrotechnique, Automatique, Traitement du Signal (EEATS)

# Approche logicielle pour améliorer la fiabilité d'applications parallèles implémentées sur des processeurs multi-cœur et many-cœur

Thèse soutenue publiquement le **28 avril 2017**, devant le jury composé de :

#### Monsieur Fréderic PÉTROT

Professeur, Président, Grenoble INP

#### **Monsieur Luc GIRAUD**

Directeur de recherche, Rapporteur, INRIA Délegation aquitaine

#### **Monsieur Olivier ROMAIN**

Professeur, Rapporteur, Université de Cergy-Pontoise

#### **Monsieur Nacer-Eddine ZERGAINOH**

Maître de conférences, Examinateur, Université Grenoble Alpes

# Acknowledgement

First and all above, I would like to thank God, the almighty, for all the blessings He shed in my life, without Him and his support this work would not be possible.

Special thanks to the Ecuadorian government through the Secretaría de Educación Superior, Ciencia, Tecnología e Innovación del Ecuador and Universidad de las Fuerzas Armadas ESPE for the confidence placed in me and my abilities to fulfill this challenge.

I would like to express my deep thankfulness and appreciation to my academic advisor, Dr. Raoul Velazco for his helpful guidance, valuable availability and precious optimism throughout the development of this research.

I want to express my deep gratitude to my academic co-advisor, Prof. Jean -François Méhaut for his constant involvement, constructive advices, and priceless readiness during this thesis.

Special thanks to my thesis reviewers Prof. Luc Giraud et Prof. Olivier Romain, for their invaluable comments and relevant questions that help me to improve this document.

I acknowledge all the staff of TIMA and LIG laboratories for their hospitality and cooperation, special thanks to Anne-Laure Fourneret, Fréderic Chevrot and Christian Seguy for their availability and service.

I would like to greatly appreciate Maud Baylac, Francesca Villa and Solene Rey from the LPSC laboratory for their long-lasting cooperation in the execution of the radiation tests experiments.

I want to express my gratitude to Stéphane Gailhard and Renaud Stevens from Kalray Company for their support in the applications' development and the experiments on the MPPA-256 many-core processor.

I would like to thank all my friends that I met during this stage of my life, specially Robert, Jessica, Alejandro, Audrey, Martin, Anaïs, Adrien, Cristina et Edison.

Special deep thanks to my mother, my mother-in-law and my aunt Talita for all the efforts and sacrifices that they have made on behalf of my family and for taking care with love of my children during different periods along these research years.

I want to thank all my family for their prays, invaluable support and love, specially to my parents, who have always trusted in me and encouraged me to fight for my dreams, and my siblings for their unconditional availability, confidence and help during these years.

I want to thank my little children, for their great comprehension and tenderness, for their smiles, kisses and hugs that fortify my soul.

Lastly, I want to thank my wonderful husband for his motivation, encouragement, and patience during the development of this thesis, for support me every time especially in the tough moments, love me and make me happy.

Vanessa Varqas

# Dedication

To the love of my life, Pablo, and my tresors, Matías and Emmanuel...

To my beloved parents Guido and Lorgia...

"The Lord is my strength and my shield; my heart trusts in him, and he helps me" Ps~28:7

# Contents

| Lı | st of | Table  | S                                                          | VI   |

|----|-------|--------|------------------------------------------------------------|------|

| Li | st of | Figur  | es                                                         | viii |

| Li | st of | abbre  | eviations                                                  | ix   |

| 1  | Intr  | oduct  | ion                                                        | 1    |

|    | 1.1   | Resea  | rch issues                                                 | 3    |

|    | 1.2   | Conte  | ext of the thesis                                          | 4    |

|    | 1.3   | Thesis | s outline                                                  | 4    |

| 2  | Bac   | kgrou  | nd                                                         | 7    |

|    | 2.1   | Radia  | tion Effects on Electronic circuits                        | 7    |

|    |       | 2.1.1  | Radiation Environment                                      | 7    |

|    |       | 2.1.2  | Single Event Effects                                       | 9    |

|    |       | 2.1.3  | Consequences caused by transient effects                   | 10   |

|    |       | 2.1.4  | Evaluation of the radiation effects on electronic circuits | 11   |

|    |       | 2.1.5  | Mitigation of Radiation effects                            | 13   |

|    | 2.2   | Multi- | -core and many-core processors                             | 14   |

|    |       | 2.2.1  | Architectural concept                                      | 14   |

|    |       | 2.2.2  | Memory hierarchy models                                    | 16   |

|    |       | 2.2.3  | Software issues                                            | 17   |

|    |       | 2.2.4  | Sensitivity to neutron radiation                           | 20   |

|    | 2.3   | Reliab | pility of multi-core and many-core                         | 23   |

|    |       | 2.3.1  | Conceptual basis                                           | 23   |

|    |       | 2.3.2  | Redundancy techniques                                      | 26   |

|   |     | 2.3.3          | Partitioning                                                         | 28       |

|---|-----|----------------|----------------------------------------------------------------------|----------|

|   | 2.4 | Discus         | ssion                                                                | 29       |

| 3 | Exp | erime          | ntal Methodology to evaluate the impact of SEEs Sensitivity          | 31       |

|   | 3.1 | Gener          | ralities                                                             | 31       |

|   | 3.2 | Evalua         | ation strategies                                                     | 33       |

|   |     | 3.2.1          | Fault-injection strategy                                             | 34       |

|   |     | 3.2.2          | Neutron-radiation facility                                           | 35       |

|   | 3.3 | Exper          | rimental Platforms                                                   | 36       |

|   |     | 3.3.1          | P2041RDB Development Board                                           | 37       |

|   |     | 3.3.2          | MPPA Developer                                                       | 37       |

|   | 3.4 | Bench          | nmark applications                                                   | 38       |

|   |     | 3.4.1          | Traveling Salesman Problem                                           | 38       |

|   |     | 3.4.2          | Matrix Multiplication                                                | 40       |

|   |     | 3.4.3          | Intrinsic characteristic issues                                      | 41       |

|   | 3.5 | Concl          | uding Remarks                                                        | 41       |

| 4 | Cas | e-stud         | lies based on the multi-core processor                               | 43       |

|   | 4.1 | Descri         | iption of the P2041 multi-core processor                             | 43       |

|   | 4.2 | Case-s         | study A: Multi-core processor running each core independently        | 45       |

|   |     | 4.2.1          | System configuration                                                 | 45       |

|   |     | 4.2.2          | Experimental evaluation by neutron radiation                         | 46       |

|   | 4.3 | Case-s         | study B: Multi-core implementing TMR as a fault-tolerant technique   | 47       |

|   |     | 4.3.1          | System configuration                                                 | 48       |

|   |     | 4.3.2          | Fault-injector details                                               | 48       |

|   |     | 4.3.3          | Experimental evaluation by fault injection                           | 49       |

|   | 4.4 | Case-s         | study C: Multi-core sharing resources and maximizing inter-core com- |          |

|   |     | munic          | cation                                                               | 52       |

|   |     |                |                                                                      |          |

|   |     | 4.4.1          | System configuration                                                 | 53       |

|   |     | 4.4.1<br>4.4.2 | System configuration                                                 | 53<br>54 |

|   |     |                | ·                                                                    |          |

|   |     | 4.4.2          | Fault-injector details                                               | 54       |

| 5 C | ase-stud | dies based on the many-core processor                            |

|-----|----------|------------------------------------------------------------------|

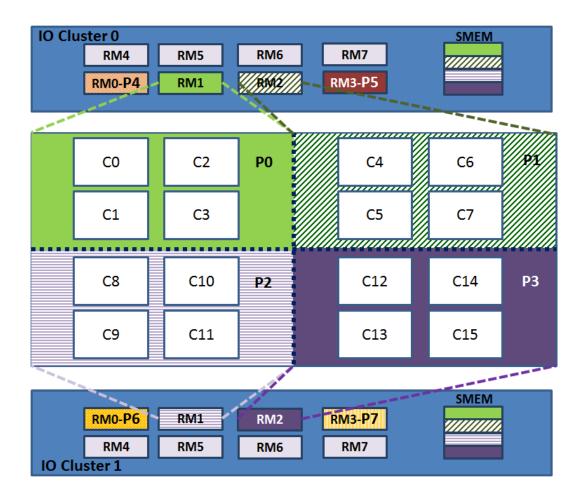

| 5.  | 1 Desci  | ription of the MPPA-256 many-core processor                      |

|     | 5.1.1    | Sensitive zones                                                  |

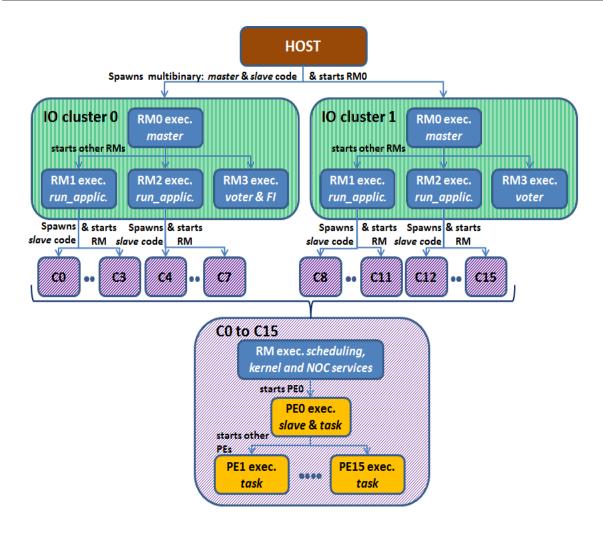

|     | 5.1.2    | Programming MPPA issues                                          |

| 5.  | 2 Case-  | study D: Many-core execution with minimal use of Network-on-Chip |

|     | (NoC     | () services                                                      |

|     | 5.2.1    | System configuration                                             |

|     | 5.2.2    | Fault-injector details                                           |

|     | 5.2.3    | Experimental evaluation by fault injection                       |

|     | 5.2.4    | Experimental evaluation by neutron radiation                     |

| 5.  | 3 Case-  | study E: Many-core execution with intensive use of NoC services  |

|     | 5.3.1    | System configuration                                             |

|     | 5.3.2    | Benchmark details                                                |

|     | 5.3.3    | Fault-injector details                                           |

|     | 5.3.4    | Experimental evaluation by fault injection                       |

| 5.  | 4 Discu  | assion of the overall results                                    |

| 5.  | 5 Conc   | luding remarks                                                   |

| 6 N | MR-M     | Par: a fault-tolerant approach                                   |

| 6.  | 1 Desci  | ription                                                          |

| 6.  | 2 Case-  | Study F: NMR-MPar implemented on the MPPA-256 processor $$       |

|     | 6.2.1    | System configuration                                             |

|     | 6.2.2    | Fault-injector details                                           |

|     | 6.2.3    | Experimental evaluation by fault injection                       |

| 6.  | 3 Over   | all result comparison                                            |

| 6.  | 4 Conc   | luding remarks                                                   |

| 7 R | elated v | vork                                                             |

| 7.  | 1 SEE    | sensitivity of multi-core and many-core processors               |

| 7.  | 2 Relia  | bility in multi-core and many-core processors                    |

|     | 7.2.1    | Fault-tolerance by redundancy                                    |

|                                          |                             | 7.2.2 Fault-tolerance by partitioning | 110 |  |  |  |

|------------------------------------------|-----------------------------|---------------------------------------|-----|--|--|--|

|                                          | 7.3                         | Contributions to the state-of-the-art | 111 |  |  |  |

| 8                                        | Con                         | aclusions and perspectives            | 113 |  |  |  |

|                                          | 8.1                         | Contributions                         | 114 |  |  |  |

|                                          | 8.2                         | Future Works                          | 115 |  |  |  |

| Annexe                                   |                             |                                       |     |  |  |  |

| A Implementation details of case-study F |                             |                                       |     |  |  |  |

|                                          | ВР                          | ublications during this thesis        | 121 |  |  |  |

| Ex                                       | Extended Abstract in French |                                       |     |  |  |  |

| Pr                                       | Projects references         |                                       |     |  |  |  |

| Bi                                       | bliog                       | graphy                                | 139 |  |  |  |

# List of Tables

| 4.1  | Sensitive areas of the P2041 targeted in this work                           | 44 |

|------|------------------------------------------------------------------------------|----|

| 4.2  | Results of radiation experiments for the P2041 working in AMP scenario       | 46 |

| 4.3  | Results of fault injection at register level for TMR MM AMP                  | 50 |

| 4.4  | Results of fault injection in variables for TMR MM AMP                       | 51 |

| 4.5  | Injection Error-Rates in Variables for TMR MM AMP                            | 52 |

| 4.6  | Applications summary for TMR scenatio                                        | 55 |

| 4.7  | Fault-injection campaigns' details for TMR scenario                          | 56 |

| 4.8  | Results of fault injection in registers for SMP scenarios                    | 56 |

| 4.9  | Results of fault injection in memory for SMP scenarios                       | 57 |

| 4.10 | Error-rates for SMP scenarios in P2041                                       | 58 |

| 4.11 | Test campaigns characteristics for TSP-SMP-P2041-NR scenario                 | 59 |

| 4.12 | Results of radiation experiments for TSP-SMP-P2041-NR scenario               | 60 |

| 4.13 | Test campaigns characteristics for MM-SMP-P2041-NR scenario                  | 61 |

| 4.14 | Results of neutron radiation tests for MM-SMP-P2041-NR                       | 62 |

| 5.1  | Memory cells of the MPPA-256 many-core processor                             | 71 |

| 5.2  | Results of the fault-injection campaigns for MM-AMP-MPPA $\ \ldots \ \ldots$ | 75 |

| 5.3  | Results of the dynamic radiation tests for MPPA scenarios $\ldots \ldots$    | 77 |

| 5.4  | Standard execution time for different configuration of TSP on the MPPA       | 80 |

| 5.5  | Fault-injection campaigns details for the Multi Purpose Processing Array     |    |

|      | (MPPA)                                                                       | 84 |

| 5.6  | Results of the fault-injection campaigns on applications running on the      |    |

|      | MPPA                                                                         | 84 |

| 5.7  | Error-rate by fault injection for POSIX scenarios in MPPA                    | 85 |

| 5.8  | Summary of the different fault-injection scenarios evaluated on the MPPA     | 88 |

| 6.1 | Execution-time comparison for different Traveling Salesman Problem (TSP)  |     |

|-----|---------------------------------------------------------------------------|-----|

|     | configurations on the MPPA                                                | 99  |

| 6.2 | NoC connections on applications running NMR-MPar on the MPPA              | 99  |

| 6.3 | Fault-injection campaigns details of the 4MR-8Par applications running    |     |

|     | on the MPPA                                                               | 101 |

| 6.4 | Results of fault-injection campaigns on 4MR-8Par applications with no TTY | 101 |

| 6.5 | Exceptions produced by fault-injection on the 4MR-8Par applications $$ .  | 102 |

| 6.6 | Error-Rates for 4-MoRePaR applications implemented on the MPPA $$         | 103 |

| 6.7 | Failure rates per hour at 35000 feet for 4MR-8PaR applications imple-     |     |

|     | mented on the MPPA                                                        | 104 |

| 6.8 | FIT values at NYC for 4MR-8PaR applications implemented on the MPPA       | 106 |

# List of Figures

| 2.1 | Earth's magnetosphere [NASA]                                              | 8  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Cosmic-ray air showers [NASA]                                             | 9  |

| 2.3 | Evolution of processor architecture                                       | 15 |

| 2.4 | Many-core processor architecture                                          | 16 |

| 2.5 | Memory architectural model in multi-core processors                       | 17 |

| 2.6 | AMP and SMP modes                                                         | 18 |

| 2.7 | Algorithm for $n \times m$ matrix addition                                | 21 |

| 2.8 | Comparison of reliability for different systems [Sho02]                   | 25 |

| 2.9 | Reliability of NMR containing $2n+1$ circuits $[Sho02]$                   | 28 |

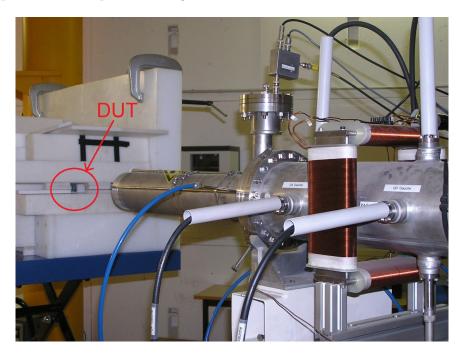

| 3.1 | P2041 Experiment at GENEPI2 facility                                      | 35 |

| 3.2 | Pseudo-code for TSP sequential algorithm [FCP+15]                         | 39 |

| 3.3 | Pseudo-code for multi-threading TSP version [FCP <sup>+</sup> 15]         | 39 |

| 3.4 | Algorithm for $n \times n$ matrix multiplication                          | 40 |

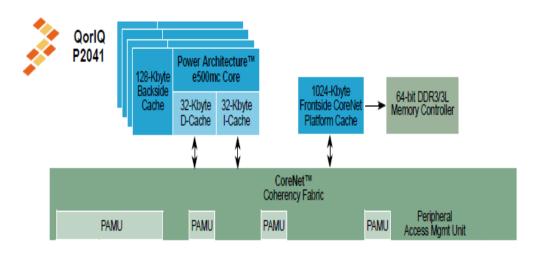

| 4.1 | Memory hierarchy model for P2041 multi-core [Fre13b]                      | 43 |

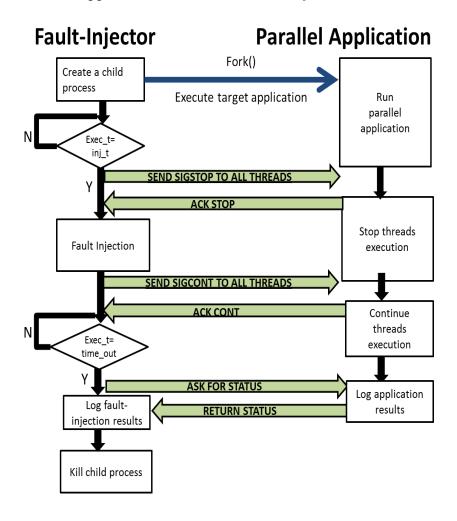

| 4.2 | Proposed software fault-injector by fork principle                        | 54 |

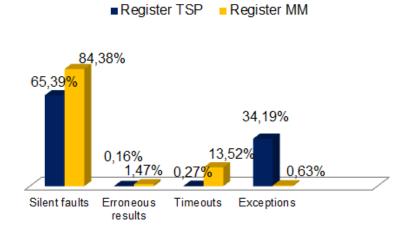

| 4.3 | Fault-injection consequences when targeting registers on P2041 under SMP  | 56 |

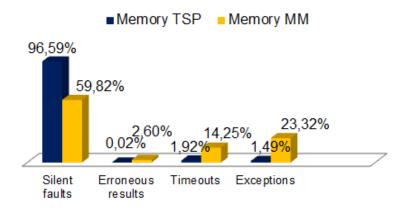

| 4.4 | Fault-injection consequences when targeting memory locations on P2041     |    |

|     | under SMP                                                                 | 58 |

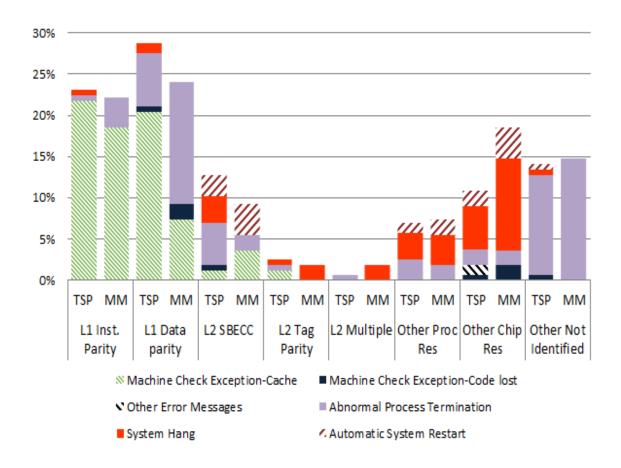

| 4.5 | Distribution of OS faults by zones affected by SEE in SMP P2041 NR $$     |    |

|     | scenarios                                                                 | 63 |

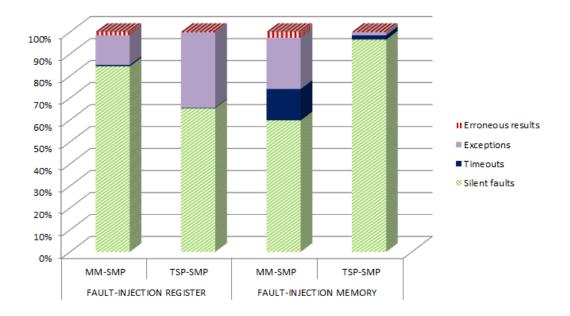

| 4.6 | SEE consequences per scenario from fault-injection campaigns on $P2041$ . | 64 |

| 4.7 | SEE consequences per scenario from radiation testing on P2041 $ \dots $ . | 64 |

| 4.8 | Evaluation of reliability under neutron radiation for the P2041           | 65 |

| 4.9 | Evaluation by fault-injection of the MM reliability implementing TMR on   |      |

|-----|---------------------------------------------------------------------------|------|

|     | P2041                                                                     | 66   |

| 5.1 | MPPA-256 many-core processor components                                   | 70   |

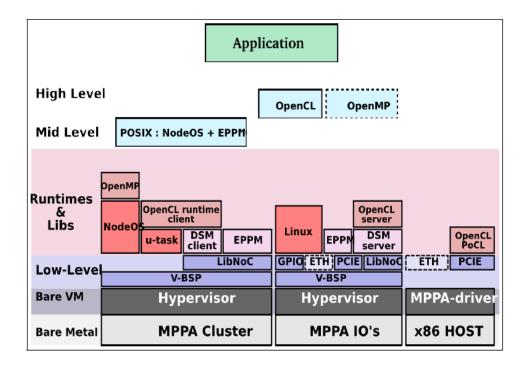

| 5.2 | Kalray software stack [Kal15]                                             | 79   |

| 5.3 | Generic master pseudo-code for the applications running on the MPPA .     | 81   |

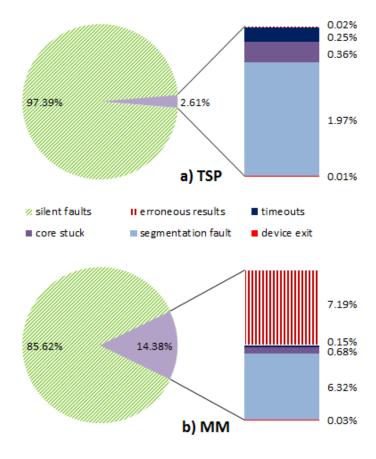

| 5.4 | Fault-injection consequences on MPPA when targeting registers             | 85   |

| 5.5 | Example of erroneous result logged by the TSP                             | 86   |

| 5.6 | Evaluation of reliability by neutron radiation for MM -Bare-board running |      |

|     | on MPPA at 35000 ft                                                       | 87   |

| 5.7 | Distribution of fault-injection consequences on MPPA for different scena- |      |

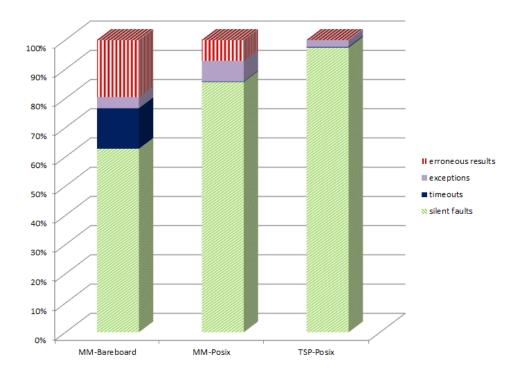

|     | rios                                                                      | 89   |

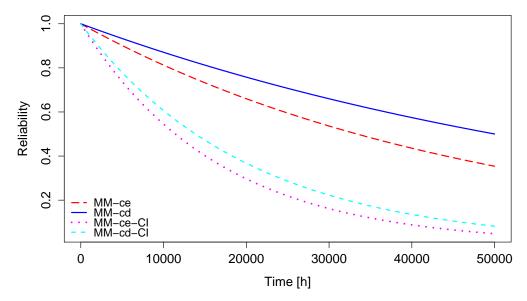

| 5.8 | Evaluation of reliability for MPPA-POSIX applications at 35000 ft         | 90   |

| 6.1 | NMR-MPar Approach                                                         | 94   |

| 6.2 | Proposed configuration for case-study F implemented on the MPPA-256       | 96   |

| 6.3 | General flow diagram of the 4MR-8Par application                          | 97   |

| 6.4 | Proposed configuration for case-study F - part 2                          | 97   |

| 6.5 | Comparison of SEE consequences per scenario in NMR-MPar applications      | 103  |

| 6.6 | Evaluation of reliability for MM application at 35000 ft                  | 105  |

| 6.7 | Evaluation of reliability for TSP application at 35000 ft                 | 105  |

| 8.1 | Pseudo-code for the implementation of the N-MoRePar applied to the MPPA   | .118 |

| 8.2 | Flow diagram of main function run in RM0                                  | 119  |

# List of abbreviations

ACROSS Advanced Cockpit for Reduction Of StreSs and workload

ALU Arithmetic Logic Unit

**AMP** Asymmetric Multi-Processing

**API** Application Programming Interface

ARINC Avionics Application Standard Software Interface

AVF Architectural Vulnerability Factor

BMP Bound Multi-Processing

**BSP** Board Support Package

CAPACITES Calcul Parallèle pour Applications Critiques en Temps et Sureté

CAST Certified Associate in Software Testing

**CC** Compute Cluster

CEU Code Emulated Upset

**CL** Confidence Level or Limit

CMOS Complementary Metal-Oxide Semiconductor

**CMP** Chip Multi-Processor

C-NoC Control NoC

**CORSE** Compiler Optimizations and Runtime Systems

COTS Commercial Off-The-Shelf

CPU Central Process Unit

**CR** Condition Register

CRC Cyclic Redundancy Check

CS Compute Status

**DCR** Device Control Register

**DECOS** Dependable Embedded Components and Systems

**DECC** Double ECC

**DMR** Double Modular Redundancy

**D-NoC** Data NoC

**DPAR** Data Parity

**DSU** Debug Support Unit

**DUT** Device Under Test

EASA European Aviation Safety Agency

ECC Error Correcting Code

**EDAC** Error Detection And Correction

EMC2 Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real time environments

**EnergySFE** Energy-aware Scheduling and Fault Tolerance Techniques for the Exascale Era

FAA Federal Aviation Administration

FIT Failure In Time

FLOPS Floating-Point Operation per Second

FPGAs Field Programmable Gate Arrays

**FPR** Floating Point Register

GCC GNU Compiler Collection

**GENEPI2** GEnerator of NEutron Pulsed and Intense

GPR General Purpose Register

GPU Graphic Processing Unit

**GRP** Guaranteed Resource Partition

**HPC** High Performance Computing

HWIFI Hardware-Implemented Fault Injection

IMA Integrated Modular Avionics

INRIA Institut National de Recherche en Informatique et en Automatique

**IPAR** Instruction Parity

JTAG Joint Test Action Group

LC Loop Counter

LE Loop Exit Address

LIG Laboratoire d'Informatique de Grenoble

LPSC Laboratoire de Physique Subatomique et Cosmologie

LS Loop Start Address

LR Link Register

MBU Multiple Bit Upset

MCE Machine Check Exception

MCU Multiple Cell Upset

MIMD Multiple Instructions Multiple Data

MM Matrix Multiplication

MPPA Multi Purpose Processing Array

MPPA IPC MPPA inter process communication

MTTF Mean Time To Failure

MWBF Mean Workload Between Failures

MultiPARTES Multi-cores Partitioning for Trusted Embedded Systems

NMR N-Modular Redundancy

NMR-MPar N-Modular Redundancy M Partitions

NoC Network-on-Chip

${f NP}$  Non-deterministic Polynomial

OpenMP Open Multi-Processing

**OS** Operating System

**PC** Program Counter

**PCIe** Peripheral Component Interconnect

PE Processing Engine

**PID** Process IDentification number

PLR Process-Level Redundancy

PMC Performance Monitor Control

PMR Performance Monitor Register

**PS** Processing Status

pSWP parallel Software Partition

**RA** Return Address

**RECOMP** Reduced Certification Costs for Trusted Multi-core Platforms

RHBD Radiation Hardened By Design

**RIS** Robust Integrated Systems

RISC Reduced Instruction Set Computer

RM Resource Manager

RTEMS Real-Time Executive for Multiprocessor Systems

**SDK** Sofware Development Kit

**SEB** Single Event Burn-out

**SECC** Single ECC

**SEE** Single Event Effect

**SEFI** Single Event Failure Interrupt

**SEGR** Single Event Gate Rupture

SEL Single Event Latch-up

SENESCYT Secretaría de Educación Superior, Ciencia, Tecnología e Innovación del Ecuador

**SER** Soft Error Rate

**SET** Single Event Transient

**SEU** Single Event Upset

SFR System Function Register

**SIFT** Software Implemented Fault Tolerance

**SMEM** Static Memory

SMT Simultaneous multithreading

**SMP** Symmetric Multi-Processing

**SOI** Silicon-On-Insulator

**SP** Stack Pointer

**SPC** Shadow Program Counter

**SPR** Special Purpose Register

**SPS** Shadow Program Status

**SRR0** Save/Restore Register 0

**SRR1** Save/Restore Register 1

SSCA3 third Scalable Synthetic Compact Application

SWIFI Software-Implemented Fault Injection

TIMA Techniques de l'Informatique et de la Microeléctronique pour l'Architecture des systèmes integrés

TMR Triple Modular Redundancy

TSMC Taiwan Semiconductor Manufacturing Company

TSP Traveling Salesman Problem

TTY Tele TYpewriter

${\bf TVF}$  Thread Vulnerability Factor

VHDL VHSIC Hardware Description Language

VLIW Very Long Instruction Word

VR Vector Register

V-BSP Virtual Board Supporting Package

**XER** Exception register

# Chapter 1

## Introduction

Nowadays, advances in integrated circuit technologies allow having processors with multiple cores which offer a very large computing capacity through the implementation of massive parallelism within an affordable power budget. These devices also provide a great flexibility because they allow implementing different multi-processing modes, programming paradigms and types of applications. In addition, their inherent redundancy capability makes them ideal for implementing fault-tolerant mechanisms. Consequently, most modern computing systems use multi-core and many-core processors as a standard solution to fulfill the increasing demand of performance and reliability without a critical increase of power consumption.

For instance, in High Performance Computing (HPC) systems, the first two SUPER-COMPUTERS Top500 (November 2016) are based on these devices: (1) 1er Top500: Sunway TaihuLight - Sunway MPP, based on the Sunway many-core processor SW26010 (260 cores) 1.45GHz, and (2) 2nd Top500: Thiane-2, based on the multi-core processor Intel Xeon E5-2692 (12 cores) 2.2GHz + Intel XeonPhi 31S1PL.

In addition, the use of multi-cores is widespread in embedded systems. However, when critical tasks are required only one core is used [MEA $^+$ 10]. Therefore, international research projects  $^1$  involving industrial and academic partners such as, ACROSS, ARTEMIS -  $EMC^2$ , CAPACITES, DECOS, MultiPARTES, are exploring the development of new solutions that allow the use of multi-processors in critical systems. Hence, avionics and spacecraft industries are interested in validating the use of these components for their applications (e.g. international teams are working on this behalf: CAST, EASA,

<sup>&</sup>lt;sup>1</sup>For further information see Projects References section

#### RECOMP project, etc).

The trend to promote the use of general purpose or Commercial Off-The-Shelf (COTS) devices in critical systems is done mainly because: (1) the cost reduction by using standard components instead of custom-designed ones, and (2) the significant reduction in the ratio performance to power consumption by using commercial components instead of radiation hardened components [MSM<sup>+</sup>02, KSD<sup>+</sup>97].

Having more performing chips requires the improvement of circuit manufacturing process by shrinking the die size. Unfortunately, the degree of miniaturization makes these circuits potentially more sensitive to the effects of natural radiation. Its impact is aggravated by the chip complexity and the huge amount of memory cells that they contain. For this reason, physical designers are continuously searching for new methods to improve manufacturing technologies to reduce Single Event Effect (SEE) consequences. Additionally, manufacturers have implemented protection mechanisms such as parity and Error Correcting Code (ECC) in devices' memories. Besides, some mitigation techniques based on hardware and software approaches are proposed in the literature to minimize the consequences of this phenomenon.

In spite of the manufacturing efforts, there are some areas that remain vulnerable to the effects of natural radiation. Several interesting works dealing with the sensitivity of electronic components can be found in the literature. However, there are very few available works regarding multi-core and many-core processors sensitivity to the radiation effects. Therefore, it is mandatory to evaluate at what extent this sensitivity affects the reliability of applications running on such devices. Furthermore, due to the massive parallelism used for improving the performance of computing systems, the evaluation of the impact on parallel applications becomes essential.

Software fault tolerance for parallel and distributed systems has been largely studied. However, studies regarding systems-on-chip fault tolerance are limited. Taking in advantage of the multiplicity of cores of multi/many-core processors, it is suitable to implement redundancy techniques to improve the reliability of parallel applications.

In this context, the purpose of this thesis is, first, to evaluate the impact of SEEs on parallel application running on multi-core and many-core processors and, second, to propose an approach based on N- Modular Redundancy and partitioning to improve the reliability of parallel applications running on many-core processors.

## 1.1 Research issues

Considering the wide range of possible software-environment configurations, the evaluation was done by multiple case-studies:

- A) A multi-core running each core independently of the others.

- B) A multi-core sharing resources and using inter-core communications.

- C) A multi-core implementing Triple Modular Redundancy (TMR) as fault-tolerant technique.

- D) A many-core execution with minimal use of NoC services.

- E) A many-core execution with intensive use of NoC services.

- F) A many-core implementing a new proposed fault-tolerant approach on massive parallel applications.

The evaluation considers the use of Asymmetric Multi-Processing (AMP) and Symmetric Multi-Processing (SMP) modes, and two benchmark applications: the Traveling Salesman Problem and the Matrix Multiplication. It was carried-out by Software-Implemented Fault Injection (SWIFI) or by neutron radiation ground testing.

For the experimentation, two COTS devices were considered. The first one was the Freescale PowerPC P2041 -core processor, which was selected because of its manufacturing technology (SOI) and its capability to allow different multi-processing modes. The second one was the KALRAY MPPA many-core processor, which was selected due to its advanced CMOS 28nm manufacturing technology, its architecture, and the huge number of processing cores (256) that it integrates.

The main contributions of this research are: (1) the evaluation of SEE sensitivity of different parallel applications implemented on multi-core and many-core processors, (2) the evaluation of the impact of the programming model and multi-processing mode on the system's SEE sensitivity (3) the development and evaluation of an approach based on redundancy and partitioning called NMR-MPar to improve the reliability of parallel applications running on multi/many-core processors.

## 1.2 Context of the thesis

This thesis was carried out in the context of a collaboration of two research teams of the University of Grenoble-Alpes: (1) the Robust Integrated Systems (RIS) team of TIMA laboratory, and (2) the INRIA Compiler Optimizations and Runtime Systems (CORSE) team of LIG laboratory. The RIS team has vast experience concerning the reliability of circuits and systems, while the CORSE team has an extensive background on compiler optimization and run-time systems for multi-core and many-core processors. The synergy produced by the contribution of the know-how of both teams was fundamental in the development and success of this research.

In addition, during the development of this thesis I have collaborated with members of other international teams in the context of the project Stic-AMSUD Energy-aware Scheduling and Fault Tolerance Techniques for the Exascale Era (EnergySFE) regarding the development of parallel applications on multi/many-core processors.

Finally, this thesis was funded by two scholarships: (1) the Secretaría de Educación Superior, Ciencia, Tecnología e Innovación del Ecuador (SENESCYT) Program "Convocatoria Abierta 2012 Segunda fase" grant 752-2012, and (2) by the Universidad de las Fuerzas Armadas ESPE grant 14-005-LCS-DOC-ESPE-a2. It was also supported by the French authorities through the "Investissement d'Avenir" program - Calcul Parallèle pour Applications Critiques en Temps et Sureté (CAPACITES) project.

## 1.3 Thesis outline

The remaining of this document is organized as follows:

- Chapter 2: summarizes the concepts and principles needed for the understanding of this research regarding: (1) radiation environment and its effects on electronic circuits, (2) main characteristics of multi-core and many-core processors, and (3) reliability issues concerning mentioned devices.

- Chapter 3: describes the methodology and tools used to evaluate the impact of natural radiation on applications running on multi-core and many-core processors.

- Chapters 4 and 5: present the evaluation of the impact of neutron radiation on dif-

ferent scenarios implemented on the Freescale P2041 multi-core and the KALRAY MPPA-256 many-core processor respectively.

- Chapter 6: proposes a fault-tolerant software-approach to improve the reliability of applications running on multi-core and many-core processors. It also presents its evaluation through a case study implemented on the MPPA-256 many-core processor.

- Chapter 7: discuss the most relevant related work.

- Chapter 8: provides general conclusions and gives some future research perspectives.

# Chapter 2

# Background

This chapter describes the principal concepts needed for a correct understanding of this thesis. Three main topics are considered. The first one is related to radiation environment, its effects and consequences on electronic systems. The second one is dedicated to present the main characteristics of multi-core and many-core processors. The last one summarizes key concepts on reliability and some useful techniques for improving it. Finally, this chapter concludes with a discussion about the thesis subject.

#### 2.1 Radiation Effects on Electronic circuits

The normal operation of electronic circuits and systems are affected by the environment where they operate. One of the most important factors is the radiation that decreases their reliability. Hence, it is essential to understand this phenomenon and its possible consequences.

#### 2.1.1 Radiation Environment

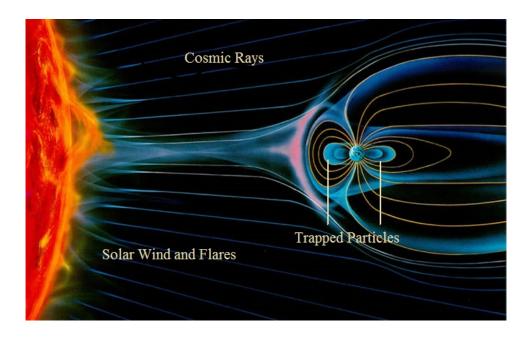

Natural and artificial radiation affecting electronic devices are present in atmospheric and spatial environments. On the one hand, radiation in the space comes principally from cosmic rays, solar wind and flares, and the Van Allen radiation belts. Cosmic rays are high energy particles coming from the outer space including electrons, protons, heavy-ions and other subatomic particles. Solar wind is a flux of particles originated by the high temperatures of the solar corona which mainly consists in electrons, protons and alpha

particles. A Solar flare is the product of the sudden release of magnetic energy from the solar atmosphere. The radiation belts is a torus of charged and energetic particles around the Earth held by its magnetic field. Figure 2.1 illustrates the Earth's magnetosphere which is formed by the interaction of solar wind and Earth's magnetic field.

Figure 2.1: Earth's magnetosphere [NASA]

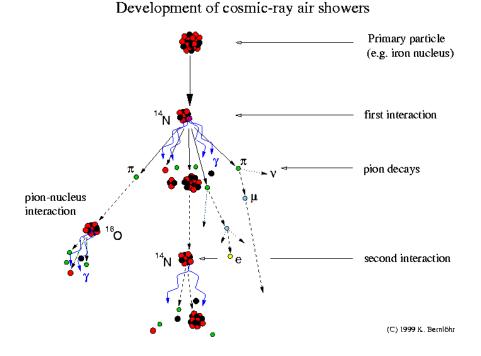

On the other hand, the atmospheric radiation environment is the result of the interaction of cosmic rays with the atoms of the Earth's atmosphere. Particles hit with a nucleus of the air generating a shower of new particles that increase while descending in the atmosphere. Figure 2.2 depicts the development of a cosmic-ray air shower.

Spatial and atmospheric radiation may produce transient, permanent and destructive effects in integrated circuits. This radiation effects can be classified in two categories: cumulative effects and Single Event Effects. Cumulative effects are the result of charges trapped in the oxide volume of a semiconductor which appear after a long period of radiation exposure. SEEs in turn, cause abrupt changes or transient behavior in circuits if the amount of collected charge at a junction exceeds a threshold [MFMR08]. From the sixties, there were observed several problems in space electronics. However, the first proofs of malfunctions in electronic devices on spacecrafts due to space radiation were reported in 1978 [MW79].

### Figure 2.2: Cosmic-ray air showers [NASA]

## 2.1.2 Single Event Effects

SEEs are all the effects induced by the interaction of a single energetic particle with a semiconductor material. Typically, heavy-ions, protons and neutrons particles produce SEEs when colliding with electronic devices compromising their reliability [Nic11].

- Single Event Transient (SET): An instantaneous voltage spike in a node (analog devices or combinatorial logic) of an integrated circuit produced by a single energetic particle strike.

- Single Event Upset (SEU): the impact of a ionizing particle on a memory cell provoked the change of the bit content also called bit-flip.

- Multiple Bit Upset (MBU): When two or more bits are altered in the same word.

- Multiple Cell Upset (MCU): When a single event upsets different storage cells.

- Single Event Failure Interrupt (SEFI): A malfunction state of a complex circuit which can be caused by an upset in a control bit or register, forcing the component

to be reset or reinitialised.

- Single Event Latch-up (SEL): A destructive event related to a high increase of power supply current due to the activation of a parasitic PNPN structure induced by the impact of an ionizing particle.

- Single Event Burn-out (SEB): A hard error affecting power MOSFET, IGBT or power BJT transistors by inducing a current flow that turns-on the parasitic NPN bipolar structure which leads to the destruction of the device.

- Single Event Gate Rupture (SEGR): A hard error produced when the incident particle generates a conduction path in a gate oxide which leads to the component damage.

## 2.1.3 Consequences caused by transient effects

Transient effects may cause dysfunctions in electronic devices, performance degradation and even partial or total destruction of the device. These perturbations can affect directly a component of the device (clock line, memory cells, etc) or can be propagated to other parts of the circuit. Sometimes a SET can be propagated in the system generating a SEU or a SEFI [MFMR08].

This work deals with the consequences of bit-flips in memory cells ("soft error"). They can be classified as follows:

- Silent fault: there is no apparent effect on system, all the system and application processes are terminated in a normal way and the results are correct.

- Application erroneous result: the result of the application is not the expected one.

- *Timeout*: when the program does not respond after a duration equal to the nominal execution time.

- Exception: the application triggers an exception routine.

- System crash: the system stops working and it is necessary a restart.

- Segmentation fault: is a type of memory dysfunction error where the software (system and application) tries to access a non-valid memory address.

- Abnormal process termination: when the application is terminated in an abnormal manner either by an abnormal code return or by the Operating System (OS).

- Unreliable condition: when an application or system process is affected by the fault.

From the above list, the most critical one is the "Application erroneous result" because it is not detected by the system and can cause unpredictable consequences. Throughout the analysis of the results, in some cases the last five types were grouped as Exceptions.

#### 2.1.4 Evaluation of the radiation effects on electronic circuits

Accelerated radiation ground tests and real-life tests are widely used to evaluate memory devices and processor-based architectures in terms of SEE cross-section. The cross-section provides the average number of particles needed to cause a bit-flip in a memory cell, and is defined as follows:

$$\sigma = \frac{Number\ of\ Upsets}{Fluence} \tag{2.1}$$

Where fluence is the integration of the flux of particles  $\phi$  in the time.

#### Real-life tests

Real-life tests are the only and trustworthy way to study the effects of radiation on electronic circuits and to measure the soft-error rate of a device, since it is tested in the radiation environment where it is supposed to work (terrestrial atmosphere or space) [PVH09]. It consists in gathering as many devices as possible with the aim of increasing the number of SEEs to obtain valid statistics. The drawback of this evaluation strategy is the necessity of a huge number of devices and the long exposure time to obtain satisfactory results.

#### Radiation ground tests

There are many ways to characterize integrated circuits to radiation at ground level. Particle accelerators, laser beams and equipments based on fission decay sources are useful to obtain significant results in a short time. The more particles interact with the device, the more SEE can be obtained. The drawbacks of this evaluation strategy are: particle beam spectrum is not really that of the natural radiation, there are few facilities around the world, high cost in experiment setup and tests<sup>1</sup>.

- Particle accelerator: is a machine that uses electric fields to accelerate elementary particles such as heavy-ions, protons, electrons to very high energies producing a beam of charged particles. There are two main types of accelerators: linear accelerators, where particle travel along a straight beam line, and circular accelerators where a beam travels in a loop [Dot].

- Laser beam: is a narrow and coherent light beam produced by optical amplification that focus its energy in a single tiny spot with intense power [Eri17].

- Fission sources: The radiation emission is produced by a spontaneous fission of certain radioactive isotopes such as californium-252 or Cf-252, or by alpha particles impinging upon a low atomic weight isotope such as beryllium, carbon and oxygen [OLA96].

#### Fault Injection

Due to the high cost of accelerated testing and the long-lasting exposures in real-life tests, fault-injection technique has been rapidly adopted for evaluating the dependability of an electronic device or system. It accelerates the occurrence of faults allowing designers assessing and improving detection and protection mechanisms [HTI97]. Fault-injection campaigns in processor-based architectures are typically performed for simulating the consequences of SEUs at application level to estimate its SEE sensitivity. For devices intended to be used in safety-critical applications, the evaluation of the reliability of the application is a mandatory step.

In the literature, it can be found five categories of fault injection:

• Hardware-Implemented Fault Injection (HWIFI): this technique allows injecting faults in the target system by means of a dedicated hardware platform. HWIFI includes several approaches being the most used the pin-level injection. Pin-level injection is based on stuck-at operations where pins are forced to a particular value

<sup>&</sup>lt;sup>1</sup>Only as reference the cost of radiating heavy-ions per hour is around 650 USD.

to generate a soft error. Other approaches such as electromagnetic interference and power supply alteration are also used to produce soft errors [Ini11].

- Software-Implemented Fault Injection: is a fault injection technique used to emulate the effects of faults in an electronic device by means of software [Sch10]. Faults can be emulated in Central Process Unit (CPU) registers, Arithmetic Logic Unit (ALU) or main memory by producing bit-flips, and can be classified in compile-time and run-time injection. Other approaches corrupt the function call parameters.

- Simulation-Based Fault Injection: this technique use a fault-simulator for modeling and simulating the target device and the faults [KN14]. The simulation models are built using hardware description language such as VHDL.

- Emulation-Based Fault Injection: This technique is based on the use of Field Programmable Gate Arrays (FPGAs) with the aim of reducing the simulation time compared to simulation-based fault injection [KN14].

- Hybrid Fault Injection: this technique is based on the combination of two or more of the above techniques aiming at improving the fault injection time. It can benefit of the versatility of software fault injection and the accuracy of hardware measuring [ZAV04].

## 2.1.5 Mitigation of Radiation effects

The continuous technology scaling in integrated circuits makes them more sensitive to the effects of natural radiation [DM03]. For this reason, physical designers are continuously searching for new methods to improve manufacturing technologies to reduce SEE consequences.

In the literature there are different approaches that deal with hardening radiation components. These can be grouped as follows:

• Hardening during conception and fabrication: during the design stage, the manufacturers improve the fault tolerance capabilities of the devices by modifying the technological parameters, applying additional layouts, and changing the electrical construction.

- Radiation Hardened By Design (RHBD): also called hardening-by-system, these techniques do not modify the fabrication process nor the electrical design. They mitigate errors by applying to COTS components some approaches including duplication in logic modules, implementation of error detection and correction circuits, memory cell interleaving, among others.

- Shielding: increases the reliability and useful life-time of devices that operate in radiation environments. For protecting against neutron and gamma radiation, heavy and large shielding blocks of lead and concrete can be used.

## 2.2 Multi-core and many-core processors

A consensus has been reached in the computing community: the only viable way to keep performance improvement rates within a given power budget is by building multi-core processors and exploiting massive paralleling [GPA+11]. Consequently, most of computing systems are nowadays using multi-core processors as a standard solution to fulfill the increasing demand of performance and reliability without a critical increase of power consumption. Moreover, multi-core and many-core processors can reduce the execution time of an application by performing parallel processing instead of increasing system frequency.

In this context, it would seem that increasing the number of cores per chip would be the most suitable solution to improve performance. Nevertheless, there are other factors affecting multi-core performance that should be analyzed, such as the latency produced by complex inter-core communications due to shared workloads, the scalability based on the increasing of workloads, the cache coherency among cores, and the memory and I/O bandwidth.

## 2.2.1 Architectural concept

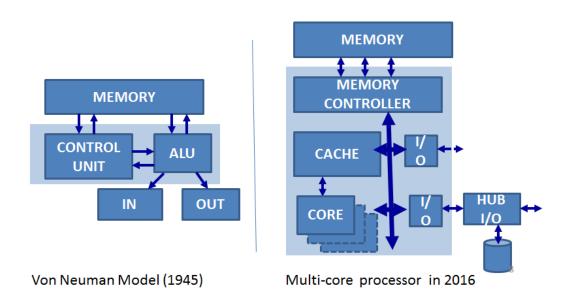

A multi-core processor is an electronic circuit which integrates on a single chip multiple processor cores running in parallel. It can integrate multiple dies in the same package or several cores in a single die, Chip Multi-Processor (CMP). Figure 2.3 illustrates the processor evolution from the first conceptual model proposed by Von Neuman in 1945.

Typically, the Reduced Instruction Set Computer (RISC) is implemented on multi-core processors. There is an instruction-level paralleling implemented in the core architecture to increase the speed up of processing based on pipelined.

Figure 2.3: Evolution of processor architecture

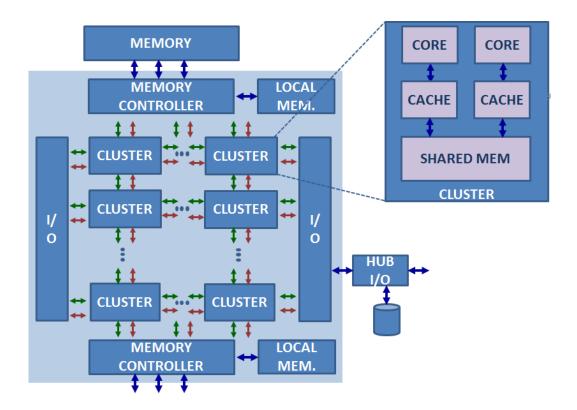

Inside the chip, each core acts as an independent processor. The OS manages the internal resources and its scheduler assigns the processes to cores. Reference [Vaj11] details the architectural issues of both multi-core and many-core processors. Regarding the many-core processor, the large increase in the number of cores implies considerable evolution in the architecture of the device. The main constraints are related with the inter-core communications and the management of memory resources and I/O devices. Regarding the intercore communication mechanisms, traditionally in a multi-core processor each core communicates by a common shared bus with the other cores; however, in many-core processor the use of NoC is indispensable. On the other hand, for managing efficiently the memory resources some approaches are proposed such as ring, mesh and crossbar interconnections. Figure 2.4 illustrates a many-core processor architecture.

Figure 2.4: Many-core processor architecture

# 2.2.2 Memory hierarchy models

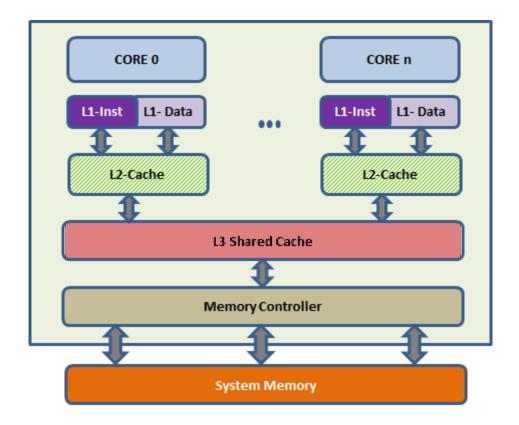

Multi-core and many-core processors include the use of cache memories as fast memories to reduce the memory access time by minimizing the access to main memory. Indeed, its use increases significantly the performance of the system, so several levels of caches are proposed. Figure 2.5 illustrates a typical hierarchy memory model used in these devices.

L1 caches memories are always private while L2 can be private or shared depending on the specific architecture device. The main advantages of private caches is its closer location to the processing unit which reduces access time. Also, its implementation minimizes contention. In contrast, by using shared cache, if few threads run on the device, the system performance could be improved due to the more cache space availability. On the other hand, by implementing private caches, the problem of keeping data consistent across cache memories arises. For solving this cache coherence problem, many solutions based on algorithms and coherence protocols are proposed.

Figure 2.5: Memory architectural model in multi-core processors

Multi-core and many-core processors use shared and distributed memory models. In shared memory models, there is one common shared memory accessed by all processors while in distributed memory each processor or group of processors has its own local memory. Typically, multi-core processors use shared memory model and many-core processors use a mixed model. Some manufacturers group several cores in clusters. Inside each cluster, they implement a shared memory.

#### 2.2.3 Software issues

To exploit massive paralleling, the application developers have to move from serial to parallel execution model and choose the appropriate system configuration to achieve maximum concurrency and consequently performance improvement. In addition, some capabilities need to be isolated to guarantee the dependability of the system. This implies that the software designer has to take into account issues such as multi-processing mode, programming model and the access level to hardware resources to better deploy the application.

#### Multi-processing modes

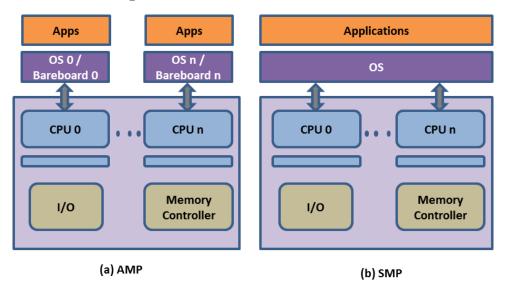

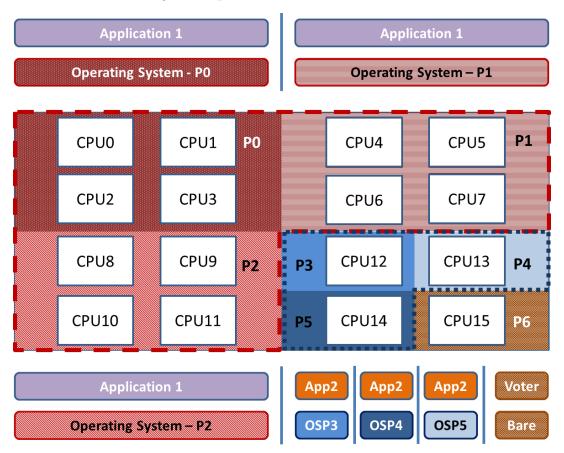

Regarding the multi-processing modes, there are two principal models: a) Symmetric Multi-Processing (SMP) and b) Asymmetric Multi-Processing (AMP). Figure 2.6 depicts these two Multi-Processing modes.

Figure 2.6: AMP and SMP modes

In AMP mode, the processor cores in the device are largely independent of each other. It can be configured with or without OS. Each core has its own private memory space, although there is a common infrastructure for inter-core communications. Hence, each core is managed by a separated OS image that exists in the main memory. Therefore, the OS can be different for each core which may be very useful when working with embedded systems. Typically, each software process is locked to a single core. Also, resources can be dedicated to critical tasks, resulting in more deterministic performance [Fre12].

On the contrary, in SMP mode a single OS manages all processors and schedules the processes. It is the simplest model. For the user, it seems that the program runs on a single core. In SMP mode, a single OS that runs on all the cores is responsible for achieving paralleling in the application. It dynamically distributes the tasks among the cores, manages the organization of task completion, and controls the shared resources.

The main advantages of these modes can be summarized as: (1) SMP provides greater scalability and paralleling than AMP, along with simpler shared resource management, (2) AMP is the only approach that works with two separate OSs, thus allows that resources can be dedicated to critical tasks resulting in more deterministic performance, and (3)

AMP often has higher performance than SMP since the cores spend less time handshaking one with another [Fre12].

#### Programming models

A programming model refers to the manner that the software assigns the application tasks to the hardware. Throughout the development of this research, the following programming models were used:

- Bare-metal: no OS is used, the programmer uses the Board Support Package (BSP) functions provided by the manufacturer to access hardware resources. There is no abstraction layer from hardware architecture. All the configurations and the distribution of the tasks must be programmed. The programmer has the control of each function.

- Low Level: no OS is used; however, there are a set of libraries that can be used. It provides a little abstraction from hardware architecture. The functions and commands used are closely related to the specific device capabilities on which the application is implemented.

- *POSIX*: is a low-level Application Programming Interface (API) defined on top of OS. It allows the control of parallel tasks (*threads*) where the programmer must control the management of threads. It is independent of the hardware architecture [IEE01].

- OpenMP: is a higher level of multi-threading API defined on top of POSIX which is easier and more portable. It consists on a group of compiler directives that can be executed on shared memory architectures, and its implementation is independent of hardware and the OS [Ope15].

#### Access levels to hardware resources

Multi-core and many-core processors provide different levels of protection that allow software access to hardware resources and configurations. These levels are also called *privilege modes*. The most common privilege modes are:

- Hypervisor: is the highest level and has access to all instructions and resources. This state provides partitioning and virtualization for OS software. It serves as a host of the possible OSs managing any shared resource and prevents from interfering one with the others.

- Supervisor or Guest supervisor: has a medium privilege level that concerns the OS which is a guest to the hypervisor. This state allows to perform several privileged operations that are not hypervisor privileged. When it attempts to access hypervisor privileged resources and instructions, an hypervisor interrupt is produced, so the hypervisor has to provide an appropriate emulation.

- User: has no privileges and commonly has access to the majority of instructions. In this state a program can run under the control of an OS guest to a hypervisor, of an OS running in bare-metal or under control of a hypervisor. These cases differ in the manner that some interrupts are managed when the user program tries to access a privileged resource.

# 2.2.4 Sensitivity to neutron radiation

The SEE sensitivity of multi/many-core devices can be evaluated through static and dynamic radiation tests. The first one is considered as the worst-case sensitivity of the device since all the accessible memory cells are monitored. The test consists in writing fixed patterns, and while the Device Under Test (DUT) is exposed to radiation, a program continuously reads the memory-cells to verify their content. If ECC is implemented in the device, the machine-check error-architecture reports Single ECCs (SECCs) and Double ECCs (DECCs) events. At the end of the test, the static cross-section ( $\sigma_{Static}$ ) that characterizes the intrinsic sensitivity of the device's manufacturing technology is obtained.

On the side, the dynamic test consists in exposing to radiation the DUT while it executes the selected application to obtain the dynamic cross-section ( $\sigma_{Dyn}$ ). This straightforward method described in [FVM<sup>+</sup>07] is performed to evaluate the behavior of an application implemented in processor-based devices.

Several works dealing with the sensitivity of electronic components to neutron radiation can be found in the literature. Reference [ND10] summarizes the sensitivity to SEEs

induced by neutrons of different integrated circuits (i.e., SRAMs, microprocessors and FPGAs) applicable to avionics. However, there are very few works available regarding multi-core and many-core processors sensitivity.

Some factors coming from emerging technologies increase this sensitivity to natural radiation: (1) the voltage scaling permits low energy particles produce SEE [Nor96], (2) the increase in size of cache memories produces a spline increase in soft error-rates [AVTK05, CSE+06], (3) the vulnerability on non-volatile memories [NAR+13].

#### Vulnerable zones

In a general way, every memory cell inside a device is a potential target of a SEE. However, the randomise in time (when) and space (where) of the bit-flip, and how the memory cell is used, affect the vulnerability of the system. The vulnerability to SEE is defined as the inability to resist the effects of radiation. In the context of this thesis the term SEEs refers to SEUs, MBUs, MCUs and SEFIs.

In order to modelling the vulnerability, in the literature there are several works that propose different metrics [MV16]. The Architectural Vulnerability Factor (AVF) proposed by [MWE+03] is one of the most used. The AVF is defined as the probability that a bit-flip in a component does not produce an error. Concerning the improvement of the reliability by reducing the system vulnerability, some approaches are also proposed in [MMM12, FZLF08].

The vulnerable zone of an application depends on the used resources and the exposure time of the data stored in memory cells. For a better comprehension of the problem of the vulnerability of an application, one could consider a simple example, such as a matrix addition, C = A + B of size  $n \times m$ . The algorithm for this application is illustrated in figure 2.7.

$$\begin{array}{cccc} & \textbf{for} \ i & \longleftarrow 0 \ \textbf{to} \ n\text{-}1 \\ & \textbf{do} & \left\{ \begin{array}{c} & \textbf{for} \ j & \longleftarrow 0 \ \textbf{to} \ m\text{-}1 \\ & \textbf{do} & C[i][j] = A[i][j] + B[i][j] \end{array} \right. \end{array}$$

Figure 2.7: Algorithm for  $n \times m$  matrix addition

In a bare-metal version running sequentially, the code section of this application is small and there are few registers (i,j, accumulator) used by the compiler for computing it. Therefore, the register-sensitive zone is minimal being the memory occupied by the

variables (A,B,C) the main sensitive zone. However, when the same application is executed on the same device but managed by an OS, the determination of the vulnerable zone becomes complicated due to the analysis difficulty of the functions and resources used by the kernel services and scheduling during the execution of the application. This determination becomes even more difficult when a parallel algorithm is applied and multi-threading is used due to factors such as synchronization between threads, data coherence, among others. Hence, authors of [OTKT12] propose a methodology for measuring the Thread Vulnerability Factor (TVF).

Moreover, if a multi-core or a many-core is used, additional issues should be considered: (1) the complexity of system configuration, such as distributed memory systems, (2) the use of many special registers at hardware level that are hidden to the programmer (3) the dynamic allocation of resources and processing cores used by the application.

#### **Protection Mechanisms**

The complexity of multicore architectures, due to the number of cores, concurrency issues, shared resources and interconnections among cores is a potential source of a wide range of errors. In order to facilitate error handling, the manufacturers have introduced the error reporting architecture by the machine check error registers to provide information of the possible sources of errors. A fault injection framework was proposed in [LPC+12] for supporting dependability analysis of multi-core systems, where machine-check-errors are emulated to analyze how the system responds to errors.

Reference [GPA<sup>+</sup>11] summarizes the most representative error detection and repair techniques that have been proposed in the literature for dependable multicore architectures. Mentioned work focused on dependable multicore-processor's architectures that integrate solutions for online error-detection, diagnosis, recovery, and repair during field operation.

Designers continuously improve the reliability of computing systems. Some techniques are proposed for microarchitectural components, such as processor registers, functional units, cache and main memories. Indeed, additional hardware implementations have been included at architecture level for improving their reliability. Examples of these protection mechanisms are the implementation of ECC and parity in memories. Hamming codes are very useful to mitigate SEUs since they can detect double errors and correct single ones.

Nevertheless, new hardware introduces an extra area with the corresponding increase in power consumption and performance degradation [AVTK05].

To reduce the overhead of the implementation of these mechanisms in cache memories, there are some approaches that proposes mixed mechanisms. For instance, in [Kim09] is proposed the use of ECC to only dirty cache lines <sup>2</sup> while clean lines are protected by parity. Also, authors of [LSI+06] propose partially protected caches by ECC and the use of selective data protection criteria. That means, critical functions use the protected area whereas the non-critical used the not protected one.

# 2.3 Reliability of multi-core and many-core

The impact of faults produced by SEE in the reliability of computing systems is worrying all domains since a single particle can produce system malfunction with important financial consequences. In reference [MV16] several examples of SEE consequences are referred.

The high demand of reliability for several applications implies that device manufacturers implement complex error-detection and correction circuits. Nevertheless, these implementations lead to an overhead that causes unpredictable slowdowns to the system [MV16]. For this reason, it is not possible to protect all the sensitive areas even if a physical protection is feasible. Furthermore, device vendors search to decrease the cost of designing and testing circuits for critical/embedded applications. Therefore, it is essential to improve the reliability of the system by using a fault-tolerance technique that minimizes the impact of its implementation cost.

# 2.3.1 Conceptual basis

Shooman in [Sho02] defines the reliability as the probability of no failure within a given operation time. It can be expressed in terms of the hazard function z(t) which is also called *failure rate*.

<sup>&</sup>lt;sup>2</sup>Dirty cache lines contain data that have been modified only at cache memory level and must be written back in main memory.

$$R(t) = e^{-\int z(t)dt} \tag{2.2}$$

The description of the failure rate function becomes complicated for complex systems with many components. Therefore, the Mean Time To Failure (MTTF) was introduced to simplify the interpretation of the system reliability. It is defined as the expected time to operate until a failure occurs. Considering a constant failure rate  $z(t) = \lambda$ , the reliability function R(t) and the MTTF become the following expressions:

$$R(t) = e^{-\lambda t} (2.3)$$

$$MTTF = \frac{1}{\lambda} \tag{2.4}$$

If failure rate increases with time z(t) = kt, the reliability and MTTF can be expressed as follows [Sho90]:

$$R(t) = e^{-kt^2/2} (2.5)$$

$$MTTF = \sqrt{\frac{\pi}{2k}} \tag{2.6}$$

From [Vig], the behavior of the failure rate on semiconductors, typically considers that its value slightly decreases over early life, then stabilizes during its useful life, and increases outside the limit of useful life. Hence in semiconductors, the failure rate is considered as a constant  $\lambda$  in most of the cases. Additionally, there are other terms used to describe failure rate in semiconductors:

- Failure In Time (FIT): Measure of failure rate in  $10^9$  device hours.

- Confidence Level or Limit (CL): Upper confidence interval level of the estimation of the probability of a population failure rate.

Generally, when a particular radiation environment is known, the Soft Error Rate (SER) is expressed in terms of FIT value. It is computed as follows [Gai11]:

$$FIT value = \sigma \times \phi \times 10^9 \tag{2.7}$$

Where  $\sigma$  is the cross-section of the device expressed in  $cm^2/device$ , and  $\phi$  is the flux of neutrons n in the real environment expressed in  $n/cm^2/h$ . In FIT calculations, the flux at New York  $\phi_{ref} = 14n/cm^2/h$  is considered as a reference.

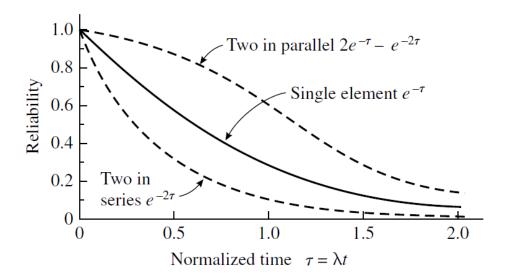

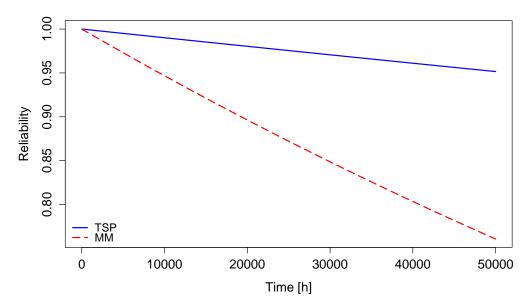

In order to have an idea of the reliability of a system composed by various elements, a comparison of the system reliability under three different scenarios is illustrated in Figure 2.8. In all the cases the systems comprise the same element with a constant failure rate  $\lambda$ : (1) a system with a single element, (2) a system composed by two elements in series, and (3) a system with two elements in parallel.

Figure 2.8: Comparison of reliability for different systems [Sho02]

From the above figure, one can see that the reliability is improved by the use of parallel systems. In contrast, the reliability decreases when the system uses two elements configured in series mode.

In the literature can be found several techniques used for modeling and improving the reliability of computing systems. Reference [MV16] presents an interesting survey of a considerable number of techniques. Techniques based on redundancy have been largely studied to improve the reliability of computing systems for both permanent and transient

faults. Furthermore, the partitioning concept is being applied to multi-core systems to guarantee the reliability in mixed-criticality systems.

# 2.3.2 Redundancy techniques

Redundancy allows a system to continue working properly in case of one or more components fail. This is possible due to the fact that parallel components added to the system provide an alternative path to operate. In general, the improvement in reliability can be achieved by *parallel* or *standby redundancy*. In the first case, the parallel components are powered-up and operating, while in the *standby* case some components are powered-down and they are turned-on when the main system fails. Regarding the nature of the replication, redundancy can be classified as:

- Spatial Redundancy: uses different physical components. It can separate identical data signals in space. The main advantage is that there is no inherent maximum operating frequency. The latter depends on the components characteristics. The main disadvantage is the overhead.

- Temporal Redundancy: uses the same physical components. It separates identical data signals in time. The maximum operating frequency depends on the technique implemented. The main advantage is the use of fewer components while the main disadvantage is the latency penalty.

- Redundancy in data: replicates the information. It stores the data in different memory spaces. The main advantage is the error detection and correction during the execution. The main disadvantage is the latency in memory access.

- Redundancy in execution: it replicates states machines. It performs copies of the same process. The main advantage is the transparency for the user. The main disadvantages are: (1) it deals with divergent causes on processes such as asynchronous signals and non-deterministic functions, and (2) the access to shared memory is a constraint.

Traditionally, the cost of implementing redundant systems has been significant. However in multi-core and many-core processors, various approaches based on redundancy techniques can be considered due to the multiplicity of cores. Reference [HBR11] exploits several redundancy techniques to improve the reliability in multi-core processors. Its authors propose the use of redundancy in all the stages involving the device, from its design to the execution of applications.

There are several approaches that improve the reliability by the replication of contents of processor components during the execution of an application without modifying the hardware: caches [KS99, ZGKS03, Zha05, SIM07], instructions [SAL+08], and registers contents [MKO05, TS12]. In contrast, other redundancy techniques modify the hardware. Among them, the TMR [LV62] is a well-known fault-tolerant technique that implements triplication of modules and majority voting. This technique has been largely used to avoid errors in integrated circuits but imposes very high hardware overhead. Nevertheless, this method becomes more attractive when implemented on multi-core and many-core processor architectures.

#### N-Modular redundancy

A N-Modular Redundancy system consists of N identical parallel systems with the same input. It also includes a voter to obtain the system output. The voter compares the outputs of each parallel systems and applies majority criteria to select the response. In general N is an odd integer to simplify voting operation. However, it is possible to use an even integer depending on the characteristics of the system [Sho02].

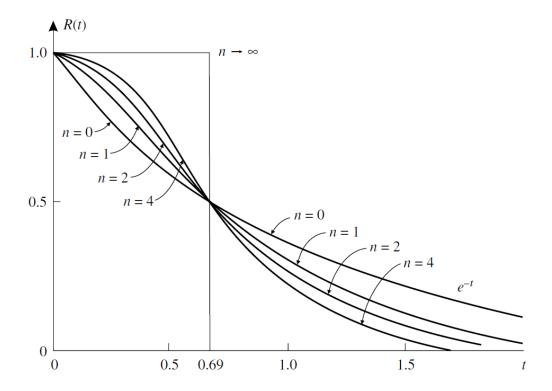

Regarding the reliability of the system, it is important to note that N-modular redundancy is better to a single module only for  $\lambda t < 0.69$ . Figure 2.9 illustrates the reliability for diverse N-modular redundancy parallel-systems implementing 2n + 1 modules. The curves consider a perfect voter with reliability  $R_v = 1$ .

It is clear that the reliability of a N-modular redundancy systems depends on the voter [KS79]. Therefore, considering the limitations of an imperfect voter, it is also possible to implement redundant voters. The most common implementations of this kind of systems are the Double Modular Redundancy (DMR) that allows error's detection, and the TMR that masks faults by detecting and correcting errors. Reference [Sho02] presents an extensive analysis of the reliability and availability of parallel TMR, standby TMR and repair TMR, and the corresponding voting systems.

Figure 2.9: Reliability of NMR containing 2n+1 circuits [Sho02]

# 2.3.3 Partitioning

Mixed-criticality systems use partitioning to increase reliability of embedded systems [TCAP14]. For achieving fault tolerance by partitioning, the behavior of one partition must not be affected by other partitions. Hence, time and spatial partitioning must be satisfied.

- *Time partitioning*: the use of resources are exclusively assigned to a partition during a scheduled period of time. In a general manner, this is associated with the CPU time assigned to each partition.

- Space partitioning: a function can not change the code or data of another partition.

This is associated with the memory space assigned to each partition.

Robust partitioning is a traditional concept used by Federal Aviation Administration (FAA) and European Aviation Safety Agency (EASA) to certify safety-critical avionics applications. It is defined in the standard RTCA/DO-297. However, according to [JFG<sup>+</sup>12], with the introduction of Integrated Modular Avionics (IMA) and multi-cores this concept must be clarified.

Space partitioning can be easily carried out by multi-core and many-core processors since the system can prevent invalid memory accesses while achieving spatial partitioning in such devices, which is not a trivial issue. Reference [LNT14] gives some directions concerning temporal partitioning on multi-core processors used for avionics.

# 2.4 Discussion

The use of multi-core and many-core processors allows improving the overall performance in terms of: (1) speed, performing parallel processing, (2) efficiency, choosing the appropriate mode of multi-processing and programming paradigm to achieve maximum concurrency, and (3) reliability, implementing fault tolerant applications through redundancy and partitioning.

Expensive dedicated devices combined with the high cost of the implementation of spatial and aircraft applications, makes suitable the use of COTS for their applications. However, in spite of the efforts done by the researchers to improve the security of applications running on COTS devices, it usage is limited due to the high reliability requirements. Regarding multi-cores, to the author knowledge, until now only dual cores are certified for being used in cockpit application in a mono-core configuration [Cer16].

Considering the multiplicity of cores and the use of redundancy techniques to improve reliability, it is important to determine the possibility of using multi/many-core COTS processors for running applications in harsh radiation environments. For that, it is necessary to study the degree of sensitivity to radiation of multi-core and many-core processors, evaluate how these effects impact the reliability of applications running on these devices, and improve the reliability of the system.

There are very few works in the literature that evaluates the SEE sensitivity of multi/many cores which are summarized in section 2.2.4. It is well known that the reliability of the application is intimately related to the reliability of the platform where it runs. However, there are other issues related to hardware and software configurations that may influence this sensitivity (e.g. the configuration of cache memories, management of interrupts, traps and exceptions). Moreover, if paralleling is performed, factors coming from the implementation of the multi-threading or distributed paradigms can also alter this sensitivity. Therefore, this thesis focuses on the evaluation of the SEE sensitivity of

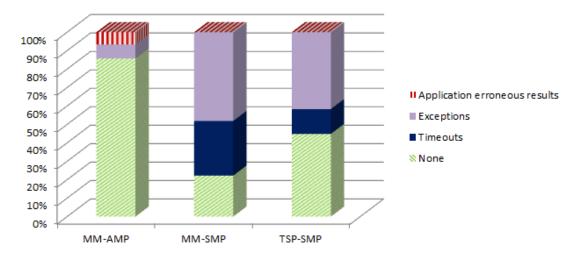

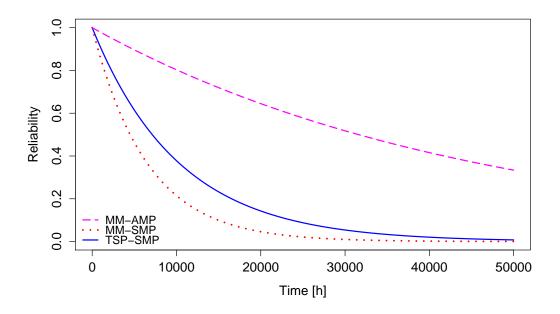

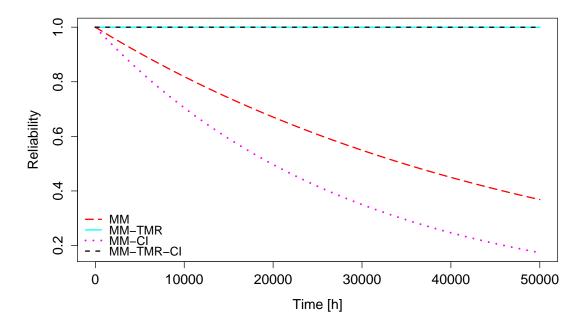

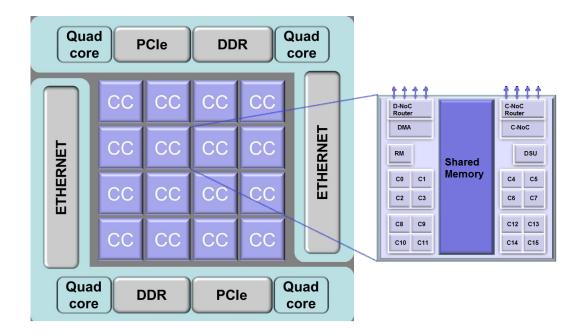

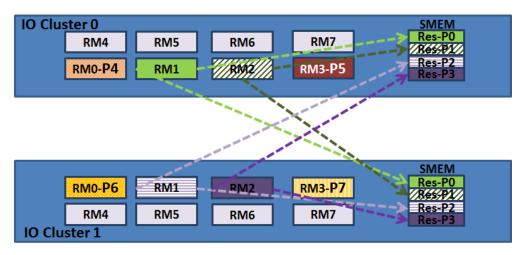

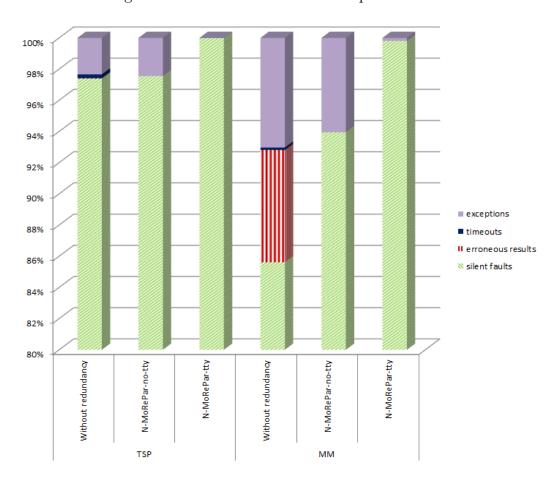

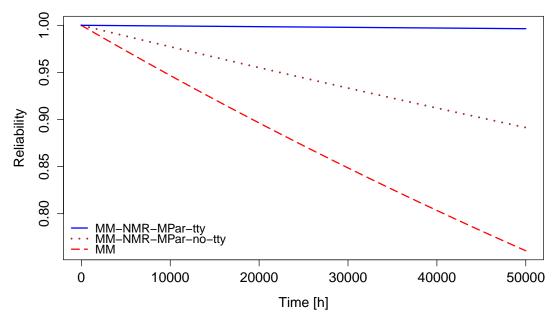

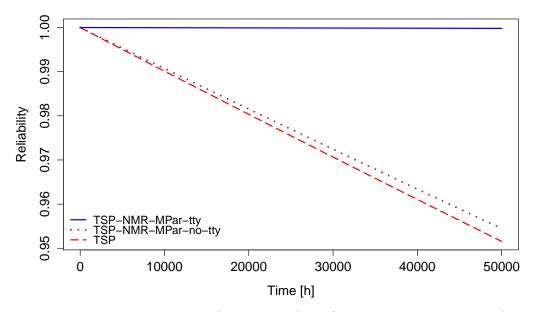

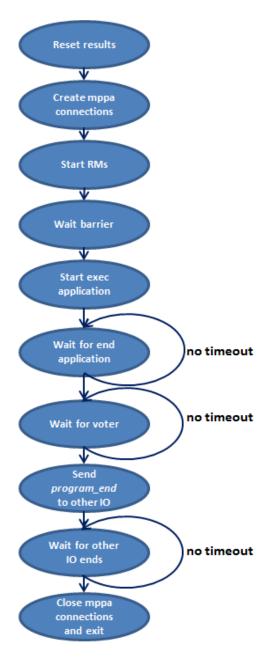

applications running on multi-core and many-core processors considering different scenarios. Chapter 3 describes the methodology and tools used by this research to address this issue.