# Digitally controlled CMOS low noise amplifier for adaptative radio

Marcelo de Souza

#### ▶ To cite this version:

Marcelo de Souza. Digitally controlled CMOS low noise amplifier for adaptative radio. Electronics. Université de Bordeaux; Universidade tecnológica federal do Paraná (Brésil), 2016. English. NNT: 2016BORD0295. tel-01705889

# HAL Id: tel-01705889 https://theses.hal.science/tel-01705889

Submitted on 10 Feb 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE EN COTUTELLE PRÉSENTÉE POUR OBTENIR LE GRADE DE

# **DOCTEUR DE**

# L'UNIVERSITÉ DE BORDEAUX ET DE L'UNIVERSITÉ TECNOLOGIQUE FEDERALE DU PARANÁ

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGENIEUR

PROGRAMME D'ETUDES SUPERIEURES EN GENIE ELECTRIQUE ET INFORMATIQUE

SPÉCIALITÉ: ÉLECTRONIQUE

Par Marcelo DE SOUZA

# CONCEPTION D'AMPLIFICATEUR FAIBLE BRUIT RECONFIGURABLE EN TECHNOLOGIE CMOS POUR APPLICATIONS DE TYPE RADIO ADAPTATIVE

Sous la direction de Thierry TARIS et de André MARIANO

Soutenue le 15 decembre 2016

#### Membres du jury :

M. G. O. BRANTE, Glauber Professeur UTFPR, Curitiba Président M. NUNES DE LIMA, Robson Professeur UFBA, Salvador Rapporteur M. RANGEL DE SOUSA, Fernando Professeur UFSC, Florianópolis Rapporteur IMS Bordeaux M. TARIS, Thierry Professeur Directeur de thèse M. MARIANO, André UFPR, Curitiba Professeur Co-directeur de thèse

# **Titre**: CONCEPTION D'AMPLIFICATEUR FAIBLE BRUIT RECONFIGURABLE EN TECHNOLOGIE CMOS POUR APPLICATIONS DE TYPE RADIO ADAPTATIVE

**Résumé**: Les systèmes de communication mobiles permettent l'utilisation de l'information en environnements complexes grâce à des dispositifs portables qui ont comme principale restriction la durée de leurs batteries. Des nombreux efforts se sont focalisés sur la réduction de la consommation d'energie des circuits électroniques de ces systèmes, une fois que le développent des technologies des batteries ne avance pas au rythme nécessaire. En outre, les systèmes RF sont généralement conçus pour fonctionner de manière fixe, spécifiés pour le pire cas du lien de communication. Toutefois, ce scénario peut se produire dans une petite partie du temps, entraînant ainsi en perte d'énergie dans le reste du temps. La recherche des circuits RF adaptatifs, pour adapter le niveau du signal d'entrée pour réduire la consommation d'énergie est donc d'un grand intérêt et de l'importance. Dans la chaîne de réception radiofrequence, l'amplificateur à faible bruit (LNA) se montre um composant essentiel, autant pour les performances de la chaîne que pour la consommation d'énergie. Au cours des dernières décennies, des techniques pour la conception de LNAs reconfigurables ont été proposées et mises en œuvre. Cependant, la plupart d'entre elles s'applique seulement au contrôle du gain, sans exploiter Le réglage de la linéarité et du bruit envisageant l'économie d'énergie. De plus, ces circuits occupent une grande surface de silicium, ce qui entraîne un coût élevé, ou NE correspondent pas aux nouvelles technologies CMOS à faible coût. L'objectif de cette étude est de démontrer la faisabilité et les avantages de l'utilisation d'um LNA reconfigurable numériquement dans une chaîne de réception radiofrequence, du point de vue de la consommation d'énergie et de coût de fabrication.

**Mots clés :** CMOS, LNA, Haute Linearité, Faible Bruit, Large Bande, Reconfigurable, Gain variable, Sans Inductance, Faible Consommation de Surface, Faible Consommation de Puissance, Faible Coût, Radio Adaptative.

# TITLE: DIGITALLY CONTROLLED CMOS LOW NOISE AMPLIFIER FOR ADAPTIVE RADIO

**Abstract**: Mobile communication systems allow exploring information in complex environments by means of portable devices, whose main restriction is battery life. Once battery development does not follow market expectations, several efforts have been made in order to reduce energy consumption of those systems. Furthermore, radio-frequency systems are generally designed to operate as fixed circuits, specified for RF link worst-case scenario. However, this scenario may occur in a small amount of time, leading to energy waste in the remaining periods. The research of adaptive radio-frequency circuits and systems, which can configure themselves in response to input signal level in order to reduce power consumption, is of interest and importance. In a RF receiver chain, Low Noise Amplifier (LNA) stand as critical elements, both on the chain performance or power consumption. In the past some techniques for reconfigurable LNA design were proposed and applied. Nevertheless, the majority of them are applied to gain control, ignoring the possibility of linearity and noise figure adjustment, in order to save power. In addition, those circuits consume great area, resulting in high production costs, or they do not scale well with CMOS. The goal of this work is demonstrate the feasibility and advantages in using a digitally controlled LNA in a receiver chain in order to save area and power.

**Keywords:** CMOS, LNA, High Linearity, Low Noise, Wide-band, Reconfigurable, Variable Gain, Inductorless, Low-area, Low-power, Low-cost, Adaptive Radio.

# **TÍTULO**: AMPLIFICADOR DE BAIXO RUÍDO DIGITALMENTE CONTROLADO PARA APLICAÇÕES DE RÁDIO ADAPTATIVO

**Resumo:** Os sistemas de comunicação móveis permitem a exploração da informação em ambientes complexos através dos dispositivos portáteis que possuem como principal restrição a duração de suas baterias. Como o desenvolvimento da tecnologia de baterias não ocorre na velocidade esperada pelo mercado, muitos esforços se voltam à redução do consumo de energia dos circuitos eletrônicos destes sistemas. Além disso, os sistemas de radiofrequência são em geral projetados para funcionarem de forma fixa, especificados para o cenário de pior caso do link de comunicação. No entanto, este cenário pode ocorrer em uma pequena porção de tempo, resultando assim no restante do tempo em desperdício de energia. A investigação de sistemas e circuitos de radiofreguência adaptativos, que se ajustem ao nível de sinal de entrada a fim de reduzir o consumo de energia é assim de grande interesse e importância. Dentro de cadeia de recepção de radiofrequência, os Amplificadores de Baixo Ruído (LNA) se destacam como elementos críticos, tanto para o desempenho da cadeia como para o consumo de potência. No passado algumas técnicas para o projeto de LNA reconfiguráveis foram propostas e aplicadas. Contudo, a maioria delas só se aplica ao controle do ganho, deixando de explorar o ajuste da linearidade e da figura de ruído com fins de economia de energia. Além disso, estes circuitos ocupam grande área de silício, resultando em alto custo, ou então não se adaptam as novas tecnologias CMOS de baixo custo. O objetivo deste trabalho é demonstrar a viabilidade e as vantagens do uso de um LNA digitalmente configurável em uma cadeia de recepção de radiofrequência do ponto de vista de custo e consumo de potência.

**Palavras-chave:** CMOS, LNA, Alta linearidade, Baixo Ruído, Banda Larga, Reconfigurável, Ganho Variável, Sem Indutor, Pequena Area, Baixo Consumo de Potência, Baixo Custo, Rádio Adaptativo.

### Unité de recherche

Laboratoire d'Intégration du Matériau au Système, UMR 5218, 351 Cours de la Libération 33405 Talence

#### **ACKNOWLEDGEMENTS**

To my family, especially my wife, for always supporting and encouraging me. To my parents, my eternal masters, that guided me in the long walk here and always guide me.

I would like to thank CAPES - Brazilian Federal Agency for R&D Support of the Brazil Ministry of Education for facilitating my experience in France.

I would also like to give special thanks to:

My three homes during this time: the Federal Technological University – Parana, UTF-PR, the Federal University of Parana, UFPR, and the Bordeaux University, UB.

My advisors Prof. Dr. André A. Mariano, Prof. Dr. Thierry Taris and Prof. Dr. Volnei A. Pedroni, for the great collaboration in this work. For the technical and personal support, and several hours of work, design and paper reviews. For the opportunity to develop this first cooperation UTF-PR, UFPR, UB.

The professors Oscar Gouveia, Luis Lolis, Bernardo Leite, Sibilla França and members of the Group of Integrated Circuits and Systems – GICS of the UFPR, for the access to the GF 130 nm and the RF circuit development tools. Aside from the help and dedication in important moments.

Magali de Matos and the IMS lab for the chip measurement support.

John Nicot for the paper reviews.

My collegues and friends at the IMS lab.

All the people that helped me directly or indirectly in this work and were not mentioned above.

# **LIST OF FIGURES**

| Figure 1.1 – Evolution of mobile technology by generation                                                                                                                                                         | .19 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 – Continuous development wireless standards                                                                                                                                                            | .22 |

| Figure 1.3 – Number of smart devices and mobile video expected growth                                                                                                                                             | .22 |

| Figure 1.4 – Apple iPhone 6S board showing the multi-chip RF design                                                                                                                                               | .23 |

| Figure 1.5 – Broadcom 13mm2 40nm GSM/EDGE/HSPA+/TDSCDMA/LTE<br>Transceiver                                                                                                                                        | .24 |

| Figure 1.6 – Skyworks Digital RF 3G transceiver                                                                                                                                                                   | .24 |

| Figure 1.7 – Qualcomm WTR3925 die. 28 nm RF transceiver used in Samsung<br>Galaxy S6 and Apple iPhone 6S                                                                                                          | .25 |

| Figure 1.8 – Wireless communication system, transmitter and receiver                                                                                                                                              | .26 |

| Figure 1.9 – Conventional RF Analog Signal processing in a receiver                                                                                                                                               |     |

| Figure 1.10 – a) Super-heterodyne receiver. b) Principle of Weaver receiver                                                                                                                                       | .28 |

| Figure 1.11 – Homodyne 802.11a receiver                                                                                                                                                                           | .29 |

| Figure 1.12 – a) Low IF receiver. b) General description of a polyphase filter. c) frequency response of a 5th order active band-pass complex filter                                                              | .30 |

| Figure 1.13 – The concept of an adaptive radio receiver                                                                                                                                                           | .31 |

| Figure 1.14 – Discrete-time RF-sampling receiver architecture                                                                                                                                                     | .32 |

| Figure 1.15 – Software-Defined Radio Receiver Using Discrete-Time RF Signal Processing                                                                                                                            | .32 |

| Figure 1.16 – Reconfigurable receiver and the adaptive RF amplifier challenge                                                                                                                                     | .33 |

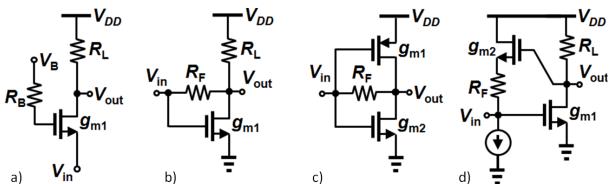

| Figure 2.1 – Inductorless LNA structures. a) Common-gate b) Resistive SFB c) Current-reuse d) Active SFB                                                                                                          | .36 |

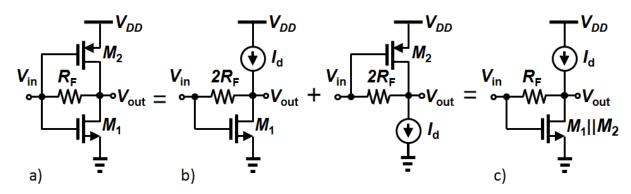

| Figure 2.2 – CR small signal model. a) CR b) Superposition of two ideal resistive S c) Final model of the resistive SFB with a single transistor combining M1 and M2 ir parallel driven by a ideal current source | 1   |

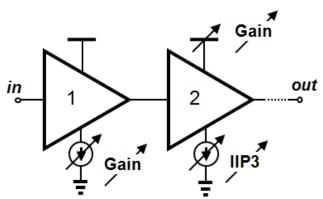

| Figure 2.3 – LNA reconfiguration: Bias control                                                                                                                                                                    | .41 |

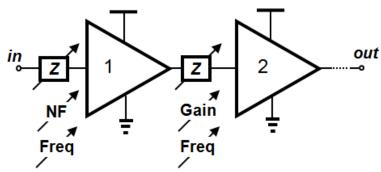

| Figure 2.4 – LNA reconfiguration: impedance control                                                                                                                                                               | .42 |

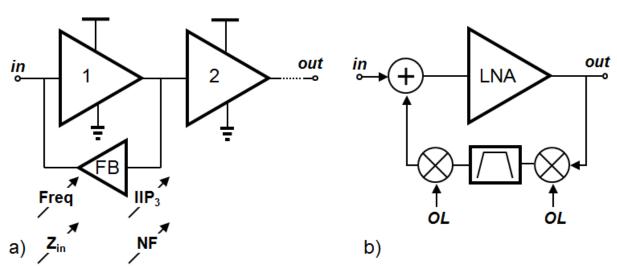

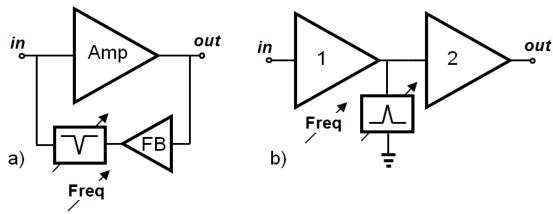

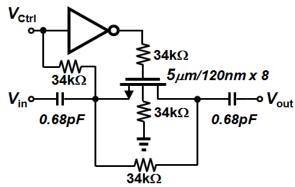

| Figure 2.5 – LNA reconfiguration: a) adaptive feedback. b) N-Path filter LNAs                                                                                                                                     | .44 |

| Figure 2.6 – N-Path filter LNAs. a) Notch-filter in the feedback b) Band-pass filter a the load of the first stage                                                                                                |     |

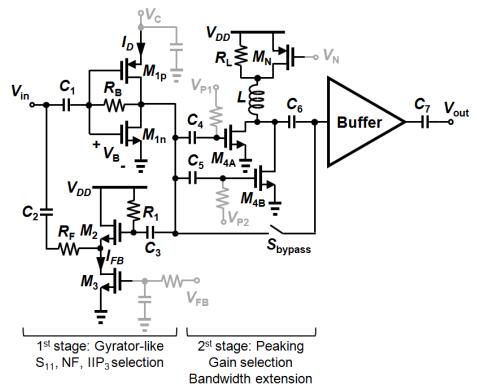

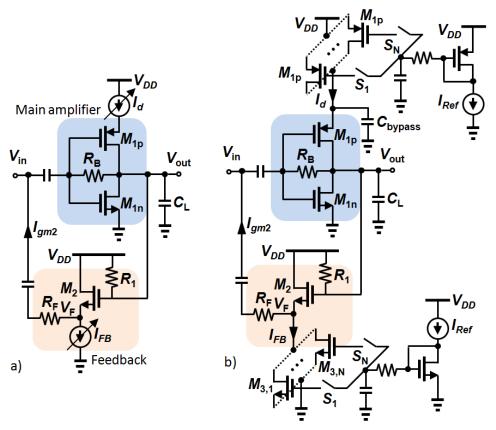

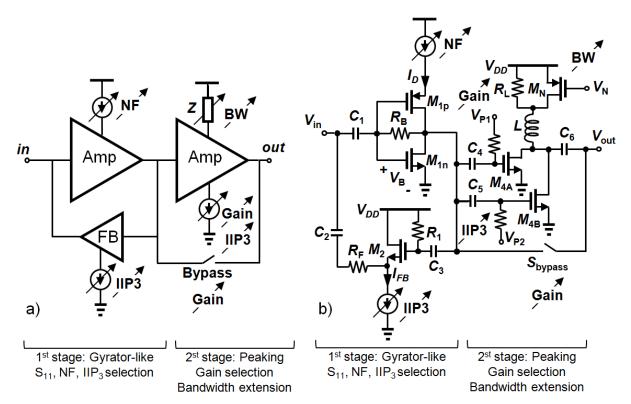

| Figure 2.7 – Proposed solutions. a) single-stage inductorless Gyrator-like LNA b) two-stage bandwidth extension fully reconfigurable LNA                                                                          | .46 |

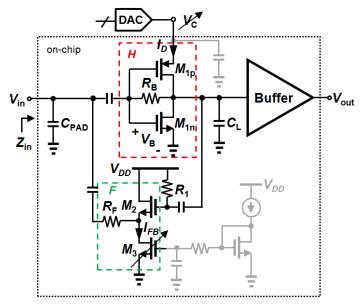

| Figure 2.8 – a) Proposed LNA b) small signal equivalent circuit c) gyrator circuit                                                                                                                                | .47 |

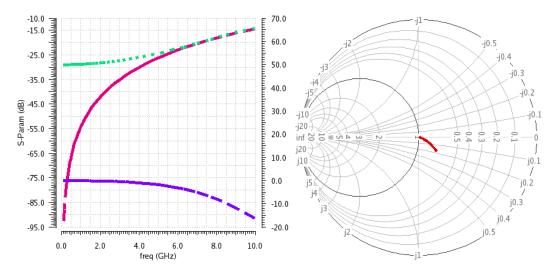

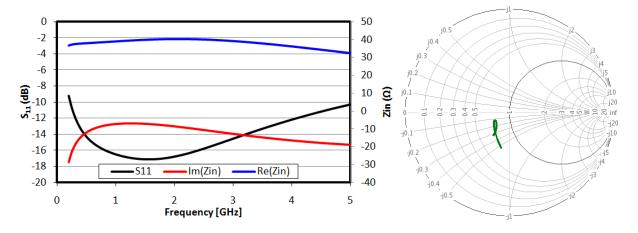

| Figure 2.9 – a) Re(Zin) - green, Im(Zin) - blue and S11 - red b) Smith chart                                                                                                                                      | .49 |

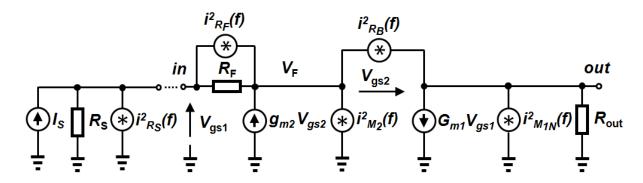

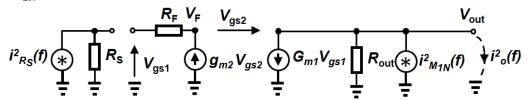

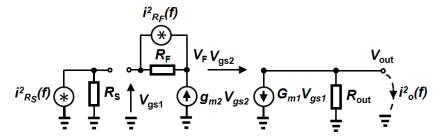

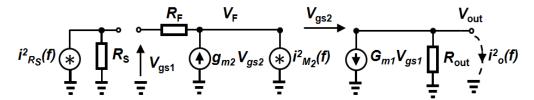

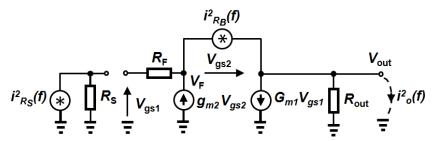

| Figure 2.10 – LNA small signal model with noise sources                                                                                                                                                           | .50 |

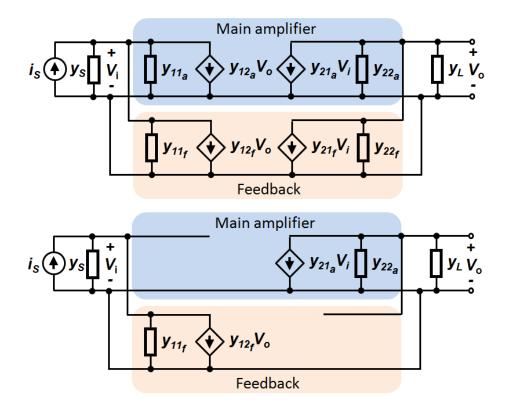

| Figure 2.11 – a) y-parameter of a shunt-feedback amplifier b) simplified circuit whe y21a >> y12a and y12f >>y21f, y11a ≈ 0 and y22f ≈ 0, the case of the amplifier in                                            |     |

| Figure 2.8(a)                                                                                                                                                                                                     | .52 |

# LIST OF FIGURES

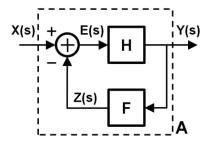

| Figure 2.12 – Nonlinear amplifier A, composed of a nonlinear main amplifier H and nonlinear feedback amplifier F.                                                                                                                                                         | l a<br>54 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

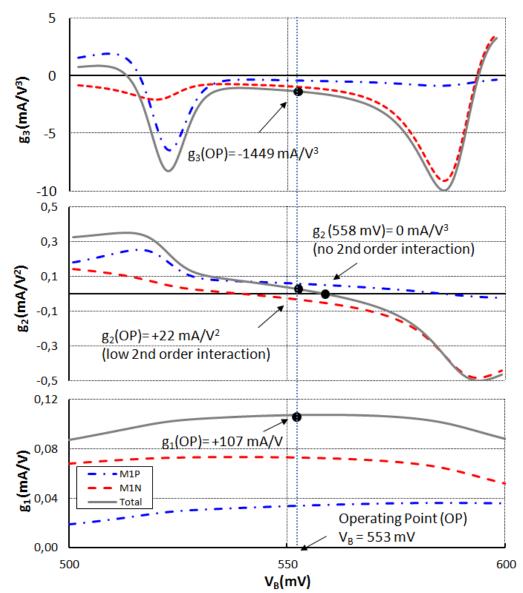

| Figure 2.13 – Current-reuse block complementary derivative superposition. gk vers bias voltage VB. At the operating point, set by RB, VB = 553 mV, leading to g2 = 0 g1 and g3 = -13.1 g1                                                                                 | ).2       |

| Figure 2.14 – Peaking stage                                                                                                                                                                                                                                               |           |

| Figure 3.1 – LNA parameters and bias variables                                                                                                                                                                                                                            |           |

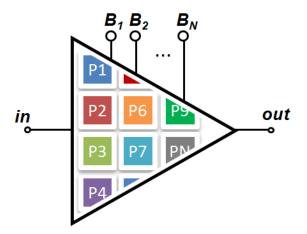

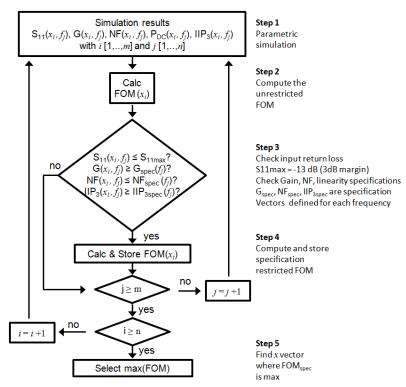

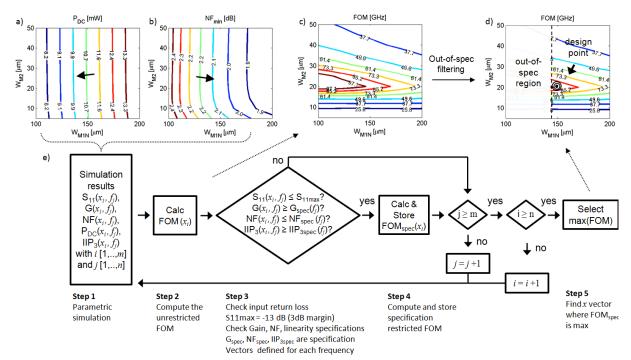

| Figure 3.2 – Parameter set selection algorithm                                                                                                                                                                                                                            |           |

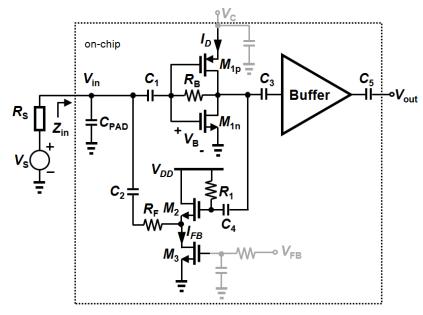

| Figure 3.3 – CHIP1: implemented circuit                                                                                                                                                                                                                                   |           |

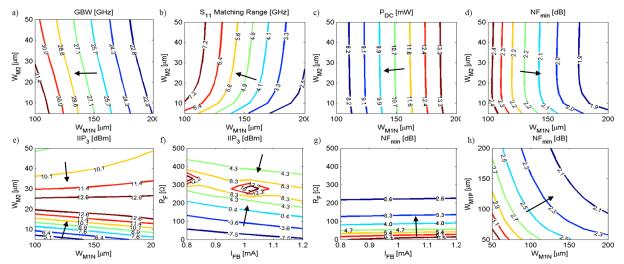

| Figure 3.4 – Design space exploration. LNA performance parameters vs design                                                                                                                                                                                               | 64        |

| Figure 3.5 – Selection process of parameter sets to address the specifications and FOM optimization. a) $P_{DC}(W_{M1n}, W_{M2})$ b) $NF_{min}(W_{M1n}, W_{M2})$ c) Unrestricted $FOM(W_{M1n}, W_{M2})$ d) Specification restricted $FOM(W_{M1n}, W_{M2})$ e) Design flow |           |

| Figure 3.6 – LNA schematic                                                                                                                                                                                                                                                | .66       |

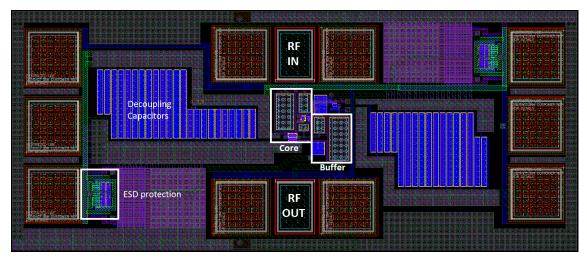

| Figure 3.7 – CHIP1 layout                                                                                                                                                                                                                                                 | .67       |

| Figure 3.8 – Gyrator-like LNA and current-reuse structure layout                                                                                                                                                                                                          | .67       |

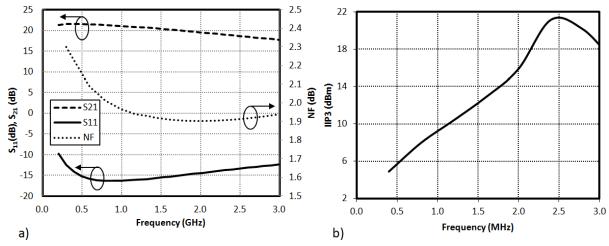

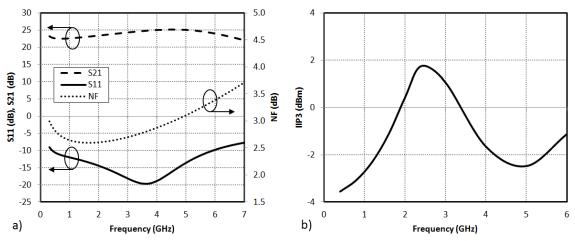

| Figure 3.9 – PLS results at best performance (P <sub>DC</sub> = 7 mW). a) S21, S11 and NF b                                                                                                                                                                               |           |

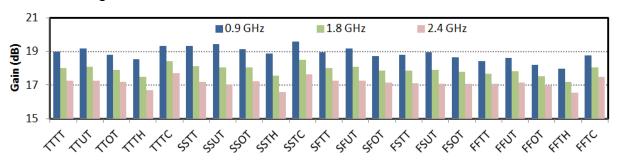

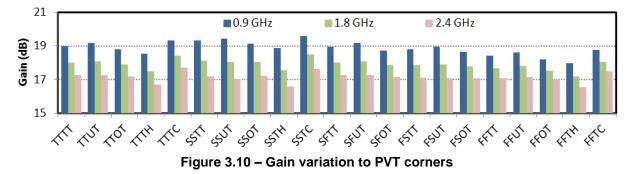

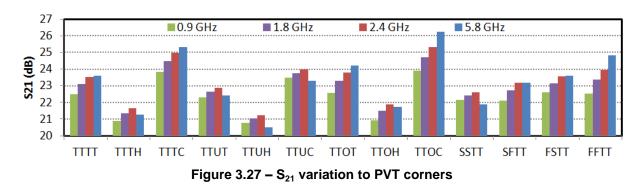

| Figure 3.10 – Gain variation to PVT corners                                                                                                                                                                                                                               | .70       |

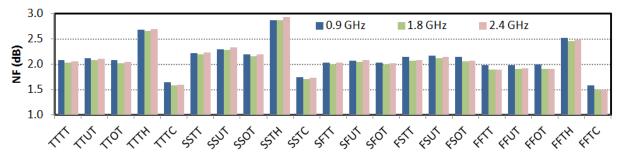

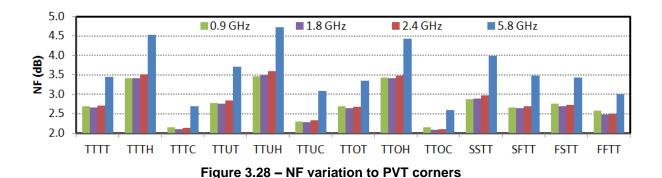

| Figure 3.11 – NF variation to PVT corners                                                                                                                                                                                                                                 |           |

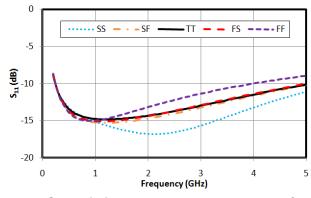

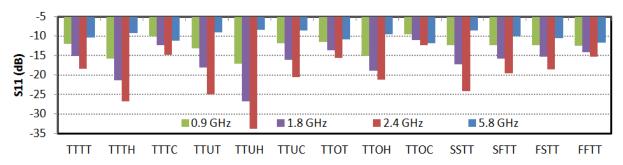

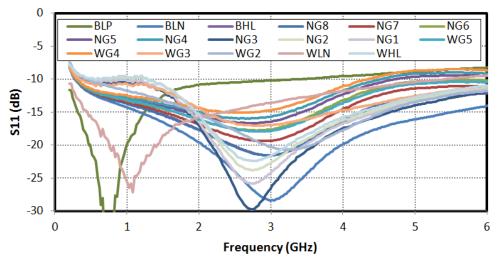

| Figure 3.12 – S <sub>11</sub> variation to process corners at 27°C and 1.3V                                                                                                                                                                                               |           |

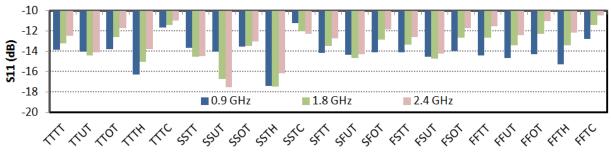

| Figure 3.13 – S <sub>11</sub> variation to PVT corners                                                                                                                                                                                                                    |           |

| Figure 3.14 – IIP3 variation to PVT corners                                                                                                                                                                                                                               |           |

| Figure 3.15 – LNA reconfigurability. a) S21, NF b) IIP3                                                                                                                                                                                                                   |           |

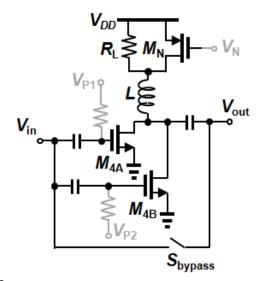

| Figure 3.16 – Bandwidth extension and gain control stage                                                                                                                                                                                                                  |           |

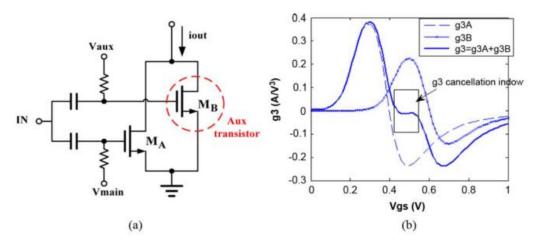

| Figure 3.17 – DS method with dual-NMOSs. (b) Third-order distortion terms of the main transistor ( $g_{3A}$ ), auxiliary transistor ( $g_{3B}$ ), and total output ( $g_3$ )                                                                                              |           |

| Figure 3.18. Bypass switch schematic                                                                                                                                                                                                                                      |           |

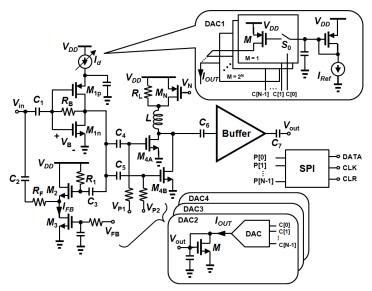

| Figure 3.19 – LNA biasing with current mode DACs                                                                                                                                                                                                                          |           |

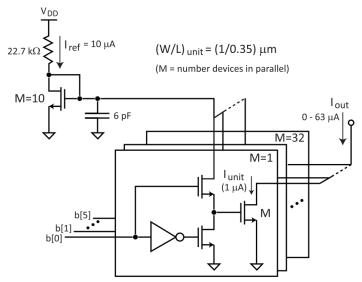

| Figure 3.20 – Width variable current source                                                                                                                                                                                                                               |           |

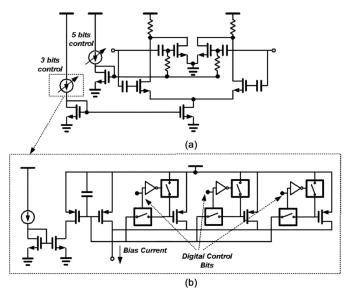

| Figure 3.21 – Current-reuse biasing a) Reconfigurability b) Transistor level                                                                                                                                                                                              |           |

| implementation                                                                                                                                                                                                                                                            | .80       |

| Figure 3.22 – Width variable current source                                                                                                                                                                                                                               | .81       |

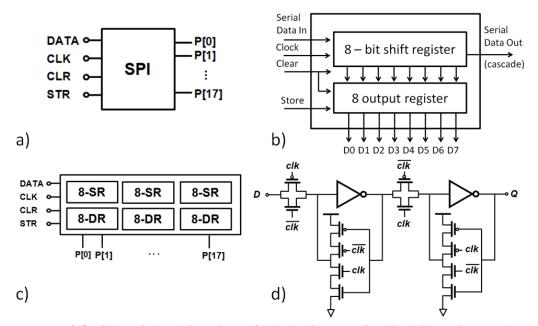

| Figure 3.23 – a) Serial peripheral interface b) block diagram c) 8 bit shift register a output register d) TG-C <sup>2</sup> MOS DFF                                                                                                                                      |           |

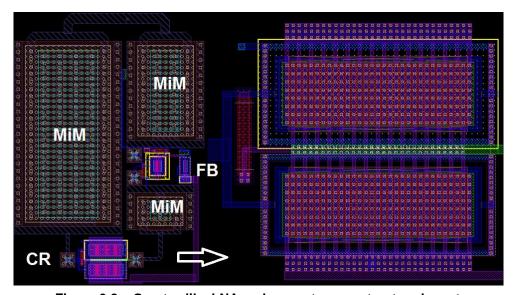

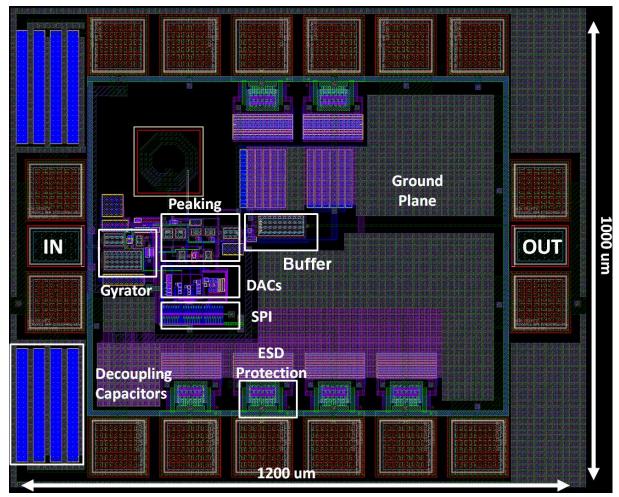

| Figure 3.24 – CHIP2 Layout                                                                                                                                                                                                                                                | .83       |

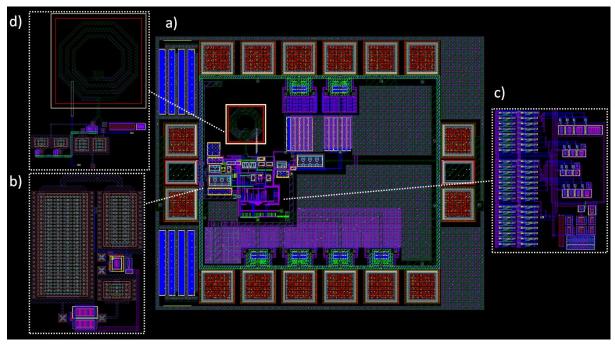

| Figure 3.25 – Digital LNA layout. a) chip layout b) gyrator stage c) peaking stage d SPI and bias generation                                                                                                                                                              | l)        |

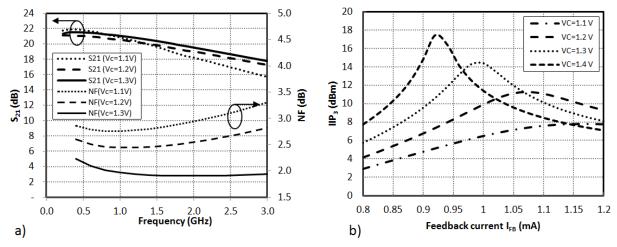

| Figure 3.26 – PLS results at high performance (P <sub>DC</sub> = 16.9 mW). a) S <sub>21</sub> , S <sub>11</sub> and Nlb) IIP3                                                                                                                                             | F         |

| Figure 3.27 – S <sub>21</sub> variation to PVT corners                                                                                                                                                                                                                    | 86        |

# LIST OF FIGURES

| Figure 3.28 – NF variation to PVT corners                                                                                               | 87                    |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Figure 3.29 – S <sub>11</sub> variation to PVT corners                                                                                  |                       |

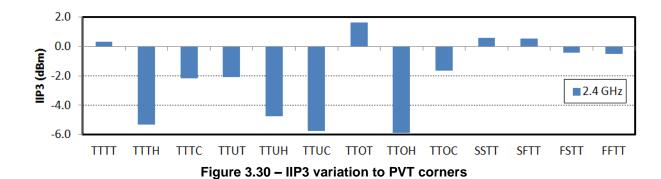

| Figure 3.30 – IIP3 variation to PVT corners                                                                                             |                       |

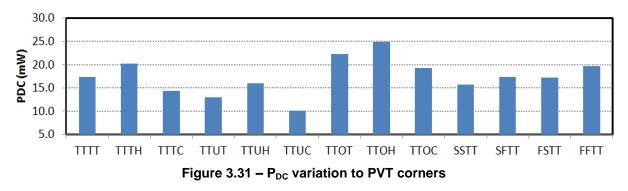

| Figure 3.31 – P <sub>DC</sub> variation to PVT corners                                                                                  |                       |

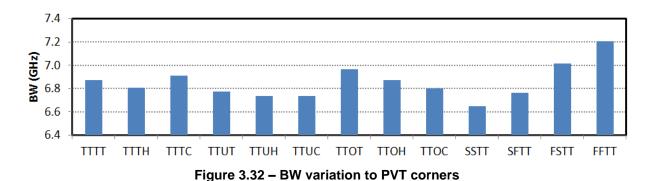

| Figure 3.32 – BW variation to PVT corners                                                                                               |                       |

| Figure 3.33 – LNA reconfiguration. a) system level b) transistor level                                                                  |                       |

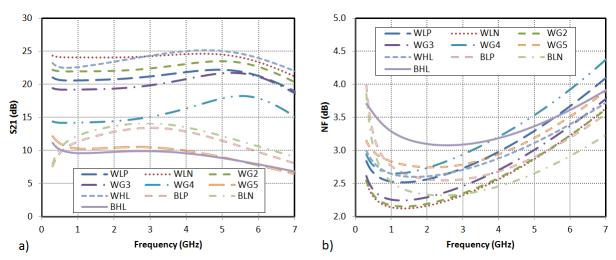

| Figure 3.34 – Reconfigurability a) S21 b) NF                                                                                            |                       |

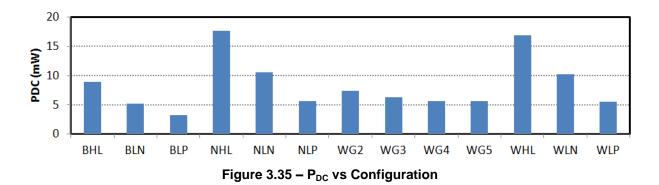

| Figure 3.35 – P <sub>DC</sub> vs Configuration                                                                                          | 92                    |

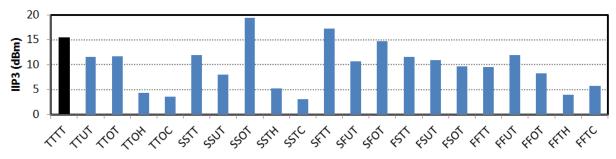

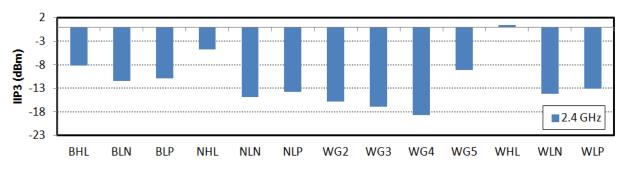

| Figure 3.36 – IIP3 vs Configuration                                                                                                     |                       |

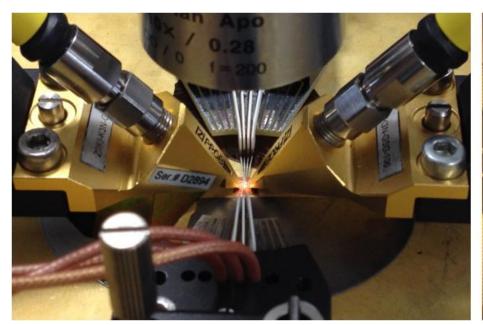

| Figure 4.1 – RF wafer probe station and chip under measurement                                                                          |                       |

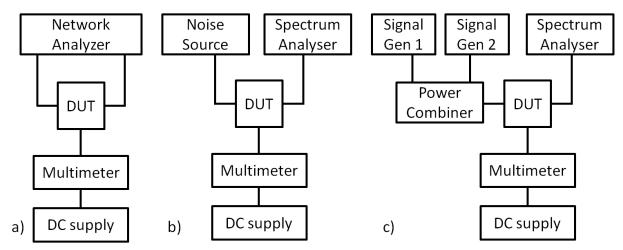

| Figure 4.2 – Measurement setups. a) S-parameters setup b) NF setup c) IIP                                                               |                       |

| Figure 4.3 – CHIP1 micrograph                                                                                                           |                       |

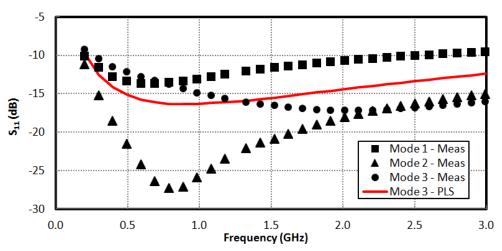

| Figure 4.4 – $S_{11}$ , measured vs PLS (post layout simulation)                                                                        |                       |

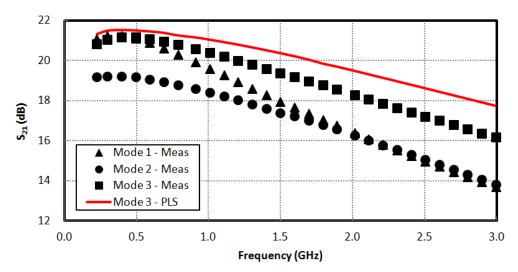

| Figure 4.5 – $S_{21}$ , measured vs PLS.                                                                                                |                       |

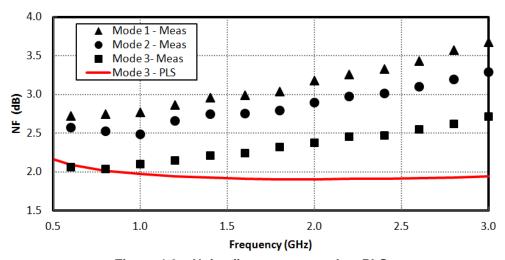

| Figure 4.6 – Noise figure, measured vs PLS                                                                                              |                       |

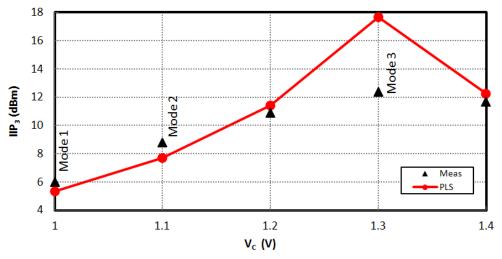

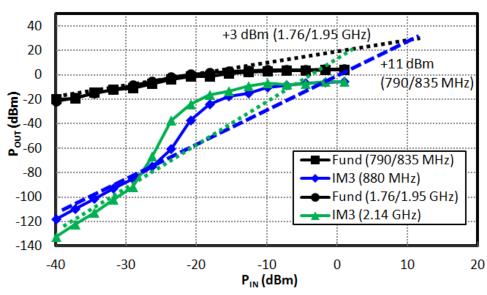

| Figure 4.7 – IIP <sub>3</sub> for different values of V <sub>C</sub> and respective operating modes a                                   |                       |

| $f_0$ = 2 GHz and $\Delta f$ = 20 MHz                                                                                                   |                       |

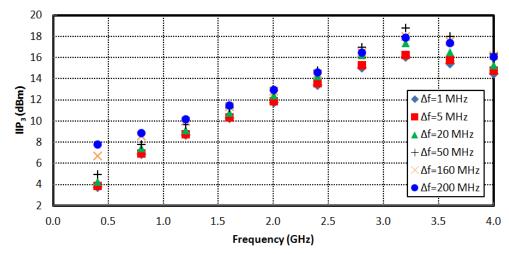

| Figure 4.8 – IIP <sub>3</sub> vs frequency for different tone spacings (Mode 3)                                                         | 99                    |

| Figure 4.9 – Measured IIP <sub>3</sub> while evaluating the effects of cross-band blocks 3)                                             |                       |

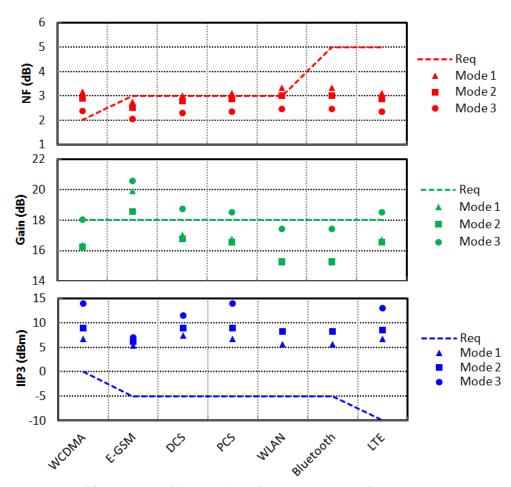

| Figure 4.10 – Measured performance vs requirements                                                                                      | 100                   |

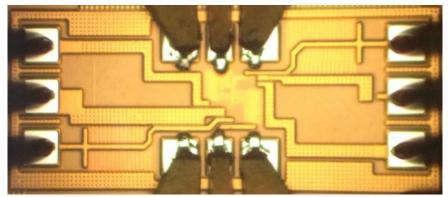

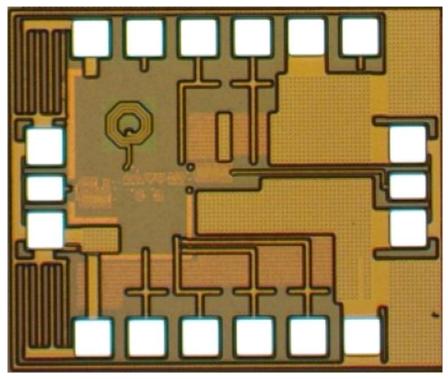

| Figure 4.11 – CHIP2 micrograph                                                                                                          | 103                   |

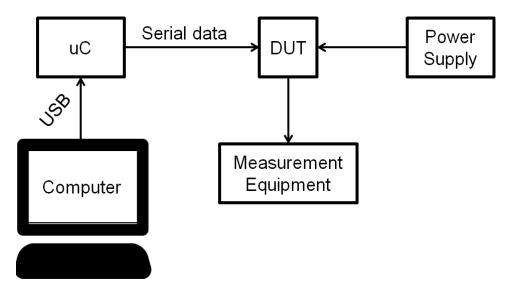

| Figure 4.12 - CHIP2 measurement setup: Digital configuration of the SPI                                                                 | 103                   |

| Figure 4.13 – Measured input impedance vs operating modes                                                                               | 105                   |

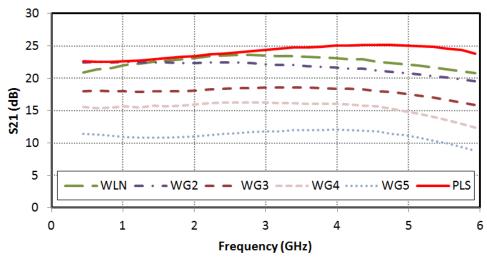

| Figure 4.14 – Wideband gain control                                                                                                     | 105                   |

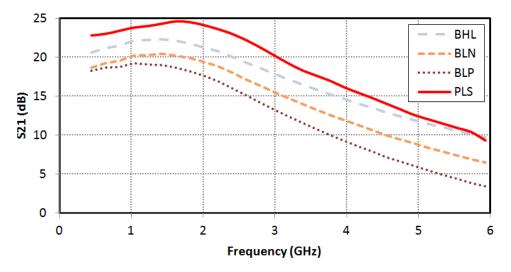

| Figure 4.15 – Second stage bypassed gain control                                                                                        | 106                   |

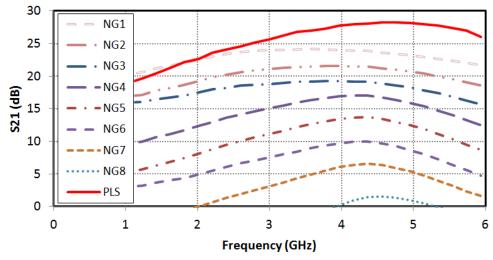

| Figure 4.16 – Peaking stage gain control                                                                                                | 106                   |

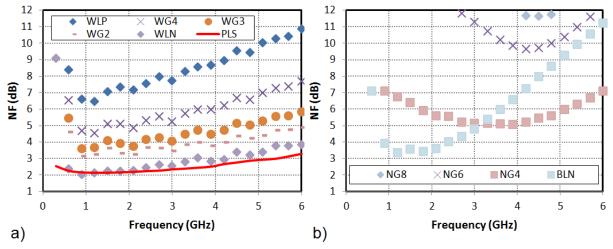

| Figure 4.17 – NF control. a) Measured NF in wideband modes and low-noise (WLN) PLS result b) Measured NF in narrowband and bypass modes |                       |

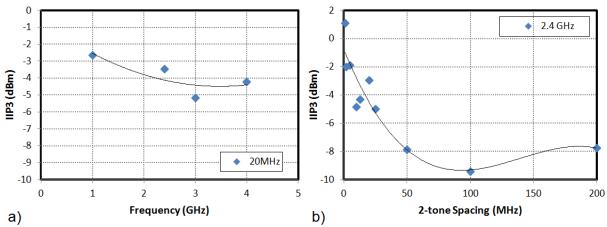

| Figure 4.18 – Measured IIP3 vs PLS results in different operating modes                                                                 |                       |

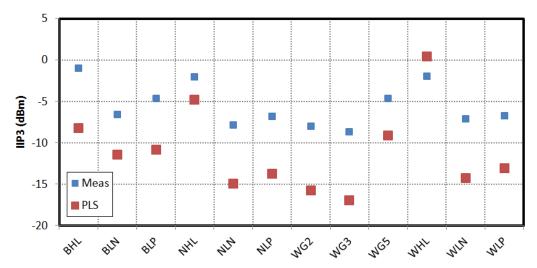

| Figure 4.19 – Measured IIP3 a) IIP3 vs frequency variation at $\Delta f$ = 20 MHz b different tone spacings at $f_0$ = 2.4 GHz          | ) IIP <sub>3</sub> vs |

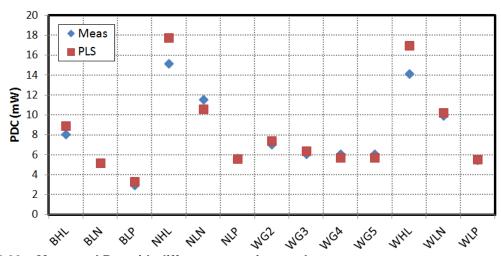

| Figure 4.20 – Measured P <sub>DC</sub> with different operating modes                                                                   |                       |

| Figure 4.21 – Measured performance vs requirements                                                                                      |                       |

# LIST OF TABLES

| Table 1.1 – Wireless standards for data transmission               | 18  |

|--------------------------------------------------------------------|-----|

| Table 1.2 – LNA requirements by wireless standard                  | 34  |

| Table 2.1 – Indutorless LNA summary                                | 40  |

| Table 2.2 – Classical LNA topologies comparison                    | 40  |

| Table 2.3 – Gyrator-like LNA low frequency y-parameters            | 52  |

| Table 3.1. Device sizes                                            | 66  |

| Table 3.2 – Overall noise breakdown                                | 69  |

| Table 3.3 – PVT corner list. Evaluated (black), unevaluated (gray) | 70  |

| Table 3.4. Device sizes                                            | 76  |

| Table 3.5 – PVT corner list. Evaluated (black), unevaluated (gray) | 86  |

| Table 3.6 – CHIP2 Operation Modes                                  | 91  |

| Table 3.7. LNA Performance Summary (PLS)                           | 93  |

| Table 4.1 – Measurement instruments                                | 95  |

| Table 4.2 – Performance Comparison Of Inductorless LNAs            | 102 |

| Table 4.3 – Operating mode codes                                   | 104 |

| Table 4.4 - Performance Comparison Of Multistandard LNAs           | 111 |

#### LIST OF ABREVIATIONS

ADC Analog to Digital Converter

BEOL Back-End-Of-Line

BER Bit Error Rate

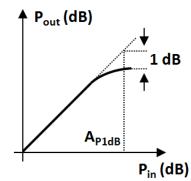

CP1 1dB Compression Point

CMOS Complementary Metal Oxide Semiconductor

DSP Digital Signal Processor

F Noise Factor

IF Intermediate Frequency

IIP3 Third-order Input Intercept Point

IM3 Third-order Intermodulation Product

FBB Forward Body Bias

FDM Frequency Division Multiplexing

FET Field Effect Transistor

LNA Low Noise Amplifier

MI Moderate Inversion

MiM Metal-Isolating-Metal

MIMO Multi-Input-Multi-Output

MOS Metal Oxide Semiconductor

NF Noise Figure

PA Power Amplifier

P1dB 1dB Compression Point

PVT Process, Voltage, Temperature

Q Quality Factor

RF Radio Frequency

RMS Root Mean Square

Rx Receiver

SAW Surface Acoustic Wave

SI Strong Inversion

SoC System-On-a-Chip

Tx Transmitter

UWB Ultra Wide Band

ULP Ultra Low Power

# LIST OF ABREVIATIONS

ULV Ultra Low Voltage

VLSI Very Large Scale Integration

WI Weak inversion

WSN Wireless Sensor Network

# **SUMMARY**

| 1 INTRODUCTION                                                     | 17 |

|--------------------------------------------------------------------|----|

| 1.1 A BRIEF STORY OF WIRELESS STANDARDS                            |    |

| 1.2 RADIO CONCEPT IN SMARTPHONE: OVERVIEW AND LIMITATION FOR       |    |

| FUTURE                                                             |    |

| 1.3 A BRIEF ON RX ARCHITECTURES                                    |    |

| 1.3.1 Conventional Receivers and Limitations                       |    |

| 1.3.2 Multi-standard/multi-band receiver Rx Architectures attempts |    |

| 1.4 LNA BASICS : FROM SYSTEM APPROACH TO CIRCUIT METRICS           |    |

| 1.5 RESEARCH GOAL AND THESIS ORGANIZATION THIS                     |    |

| 2 PROPOSED TOPOLOGY                                                |    |

| 2.1 WIDEBAND INDUCTORLESS LNA TOPOLOGIES                           |    |

| 2.2 RECONFIGURABLE LNA TECHNIQUES                                  |    |

| 2.2.1 Biasing control                                              |    |

| 2.2.2 Impedance control                                            |    |

| 2.2.3 Adaptive feedback                                            |    |

| 2.3 GYRATOR-LIKE LNA                                               |    |

| 2.3.1 Gain and bandwidth                                           |    |

| 2.3.2 Input impedance                                              |    |

| 2.3.3 Noise                                                        | 50 |

| 2.3.4 Stability                                                    |    |

| 2.3.5 Linearity                                                    |    |

| 2.4 SHUNT PEAKING STAGE                                            |    |

| 2.5 SUMMARY                                                        |    |

| 3 CIRCUIT DESIGN                                                   |    |

| 3.1 WIDEBAND LNA DESIGN METHODOLOGY                                |    |

| 3.2 CHIP1: GYRATOR-LIKE LNA                                        | 62 |

| 3.2.1 Design                                                       | 62 |

| 3.2.2 Layout considerations                                        | 66 |

| 3.2.3 Post-layout simulation results                               | 68 |

| 3.2.4 PVT sensitivity                                              | 69 |

| 3.2.5 Reconfigurability                                            | 72 |

| 3.3 CHIP2: DIGITAL FULLY RECONFIGURABLE LNA                        |    |

| 3.3.1 Design                                                       | 74 |

| 3.3.1.1 Biasing                                                    | 77 |

| 3.3.1.2 Design for testability                                     | 81 |

| 3.3.2 Layout considerations                                        | 83 |

| 3.3.3 Post-layout simulation results                               | 85 |

| 3.3.4 PVT sensitivity                                              | 86 |

| 3.3.5 Reconfigurability                                            | 89 |

# SUMMARY

| 3.4 SUMMARY                                           | 92  |

|-------------------------------------------------------|-----|

| 4 EXPERIMENTAL RESULTS                                | 94  |

| 4.1 MEASUREMENT SETUP                                 |     |

| 4.2 CHIP1: SINGLE STAGE INDUCTORLESS GYRATOR-LIKE LNA |     |

| 4.2.1 Measurement results                             | 96  |

| 4.2.2 Discussions                                     | 101 |

| 4.3 CHIP2: DIGITAL FULLY RECONFIGURABLE LNA           |     |

| 4.3.1 Measurement results                             | 104 |

| 4.4 SUMMARY                                           | 111 |

| 5 CONCLUSION AND PERSPECTIVES                         | 113 |

| 5.1 CONCLUSIONS                                       | 113 |

| 5.2 SUMMARY OF CONTRIBUTIONS                          | 113 |

| 5.3 PERSPECTIVES FOR FUTURE WORK                      | 114 |

| 5.4 SCIENTIFIC PRODUCTIONS                            | 115 |

| APPENDIX A – RF BLOCK DEFINITIONS AND CHARACTERISTICS |     |

| APPENDIX B - GYRATOR-LIKE LNA CALCULATIONS            | 138 |

#### 1 INTRODUCTION

The need for communication is part of human nature and long distance communication has being a challenge since the ancient times. In the last two centuries, the telecommunication evolved dramatically, with Maxwell, Hertz, Marconi, and many others who contributed to the development of radio communications we know today. Long distance broadcasting happened and the world got smaller. With market competition, new technologies were developed, lowering costs, and making wireless communications more and more affordable. This evolution changed the world, and since the development of microelectronics, the human societies changed as well. The creation of mobile phones, with AMPS, GSM and CDMA technologies, popularized cell phone systems, allowing millions of people to communicate with each other giving rise to new ways of communication. As wireless devices got more popular, the limited spectrum became a problem, and new ideas were proposed to address this technical challenge. Modulation schemes combined with multiple access mechanism made possible the increase of users over the same limited frequency spectrum. New services were born, short message services (SMS), data communication, multimedia message services (MMS), video calls, and by the middle of the 2000s, the computer and the mobile phones were merged, giving rise to smartphones. With the smartphones the internet actually get into the mobile world, and mobile computers spread out. In these mobile hyper-connected devices, battery life is key, where the success or failure of a product depends on it. Much research effort has been made to increase the energy storage density of batteries. However, the pace of chemical and physical development is not fast enough, so battery life is being extended in a faster pace through power saving from the electronics side. New digital technologies evolving according to Moore's Law, have greatly increased the computation power, with reduced power consumption.

Table 1.1 - Wireless standards for data transmission

|                           | Frequency              | Max<br>Range  | Max<br>Rate         | Modulation    | Application                          |

|---------------------------|------------------------|---------------|---------------------|---------------|--------------------------------------|

| Bluetooth                 | 2.4 GHz                | 10m           | 3 Mbit/s            | FHSS/GFSK     | Headsets, audio, sensor data         |

| GPS/GNSS                  | 1.57 GHz               | Several<br>km | 50 bit/s            | DSSS/BPSK     | Navigation /Geolocation              |

| GSM                       | 900, 1800,<br>1900 MHz | Several<br>km | 384 kbps<br>(EDGE)  | GMSK          | Cellular phone                       |

| UMTS                      | 1.9 – 2.1 GHz          | Several<br>km | 2 Mbit/s            | QPSK          | Cellular phone                       |

| UWB                       | 3.1 – 10.6<br>GHz      | 10 m          | 480 Mbit/s          | OFDM          | Video transfer                       |

| WiFi<br>802.11 a/b/g/n/ac | 2.4 and 5GHz           | 100 m         | 11 to 800<br>Mbit/s | DSSS/OFDM     | WLAN                                 |

| WiMAX                     | 2.3, 2.5 GHz           | 50 km         | 25 Mbit/s           | OFDM/ 64QAM   | WMAN, broadband inter-<br>net access |

| WirelessHD                | 60 GHz                 | 10 m          | 3 Gbit/s            | OFDM/ 16QAM   | Video                                |

| WirelessUSB               | 2.4 GHz                | 10 m          | 480 Mbit/s          | OFDM/<br>QPSK | USB, video                           |

| ZigBee<br>802.15.4        | 2.4 GHz                | 100 m         | 250 kbit/s          | OQPSK         | Sensor networks                      |

All these fast evolutions, resulted in the continuous development of wireless standards, as illustrated in Table 1.1, each of them aiming to address a specific requirement: geolocation (GPS,GNSS), wireless sensor networks (WSN), metropolitan area networks (WMAN), wireless local area networks (WLAN), wireless personal area network (WPAN), to name a few. Short or long range, low or high data rate, the power consumption and cost remain the key factors for any standard adoption and success.

#### 1.1 A BRIEF STORY OF WIRELESS STANDARDS

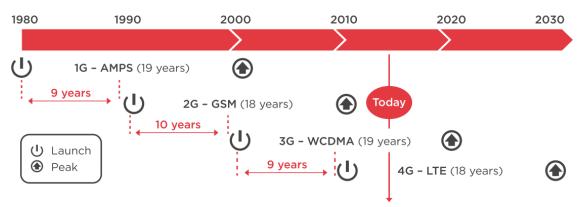

A new telephony technology generation has appeared approximately every 10 years and reached its peak 20 years after launch, as shown in Figure 1.1. Each generation typically refer to non-backward-compatible cellular standard, meaning that it shall use different infrastructure and spectrum. The first generation (1G), represented mostly by the Analog Mobile Phone System (AMPS) standard, operating in the 850 MHz band, featured heavy and expensive devices, with only voice capability. The AMPS employed Frequency-Division Multiple Access (FDMA) and paved the

way to commercial cellular systems allowing a large number of user throughout the deployment of cells and the local frequency reuse.

Figure 1.1 – Evolution of mobile technology by generation Source: (GSMA, [s.d.])

By the early 1990s the 2G emerged, with Global System for Mobile Communication (GSM) in the Europe, in the 900 MHz band, and later the Interim Standard 95 (IS-95) in the USA, in the 850 MHz. With the development of GSM, the DCS and PCS subsystems emerged, including the 1800 and 1900 MHz bands. These standards employed different access schemes to increase the number of simultaneous users, the Time-Division Multiple Access (TDMA) in combination with FDMA with 200kHz channel, and the Code division Multiple Access (CDMA), with 1.25 MHz channel width, respectively. These standards initially provided voice and very low data rates services only. Later with the development of the Internet and the increasing need for data communications, extensions to the GSM and IS-95 were released. The General Packet Radio Service (GPRS) and the Enhanced Data Rates for GSM Evolution (EDGE), on the GSM side, increased the data rates of 2G up to 40 times.

The 3G began in the early 2000s with the evolutions of 2G standards, Universal Mobile Telecommunication System (UMTS) and CDMA2000 were developed to replace GSM and IS-95 respectively. Operating on the 1900 MHz to 2100 MHz band, both standards use CDMA based access method, the UMTS employed Wideband CDMA (W-CDMA) with a pair of 5 MHz wide channels, while the CDMA2000 used one or more available 1.25 MHz channels for each direction of communication. On the 3G, the data rates were increased a ten-fold from the 2G.

In 2004 a 4G standard was developed by the 3GPP and standardized by the ETSI. The Long Term Evolution (LTE), introduced in 2008, is the access part of the

Evolved Packet System (EPS). The LTE was developed as a natural evolution of UMTS and CDMA2000 systems. The main requirements for the new access network are: high spectral efficiency, high peak data rates, short round trip time, as well as flexibility in frequency and bandwidth (3GPP, [s.d.]). The EPS is purely IP based, where both real time services (voice and video) and data communication services are carried by the IP protocol. The new access method is based on Orthogonal Frequency Division Multiple Access (OFDMA). In combination with higher order modulation (up to 64QAM), large bandwidths (up to 20 MHz), and spatial multiplexing in the downlink (up to 4x4), it achieves high data rates. The highest theoretical peak data rate on the transport channel is 75 Mbps in the uplink, while in the downlink, the rate can be as high as 300 Mbps.

The 5G is expected to be launched in the early 2020s. However, there is a significant debate on what 5G is and what is not. According to GSMA (GSM Association) there are two possible visions of the technology (GSMA, [s.d.]):

- 1. The hyper-connected vision: Mobile operators would create a blend of pre-existing technologies covering 2G, 3G, 4G, WiFi and others to allow higher coverage and availability, and higher network density in terms of cells and devices. Where the key differentiator is the greater connectivity, which would enable Machine-to-Machine (M2M) services and the Internet of Things (IoT). This vision may include a new radio technology to enable low power, low throughput field devices with long duty cycles of ten years or more.

- 2. Next-generation radio access technology: With specific targets for data rates and latency being identified, such new radio interfaces can be assessed against such criteria. This in turn makes a clear demarcation between a technology that meets the criteria for 5G, and another that does not.

Both of these approaches are important for the progression of the industry, but they are distinct sets of requirements associated with specific new services. To address this issue, many industry initiatives have worked on identifying a set of eight basic requirements for this generation:

- 1-10Gbps connections to end points in the field (i.e. not theoretical maximum)

- 1 ms end-to-end round trip delay (latency)

- 1000x bandwidth per unit area

- 10-100x number of connected devices

- (Perception of) 99.999% availability

- (Perception of) 100% coverage

- 90% reduction in network energy usage

- Up to ten year battery life for low power, machine-type devices

Because these requirements are specified from different perspectives, they do not make an entirely coherent list – it is difficult to conceive a new technology that could meet all of these conditions simultaneously.

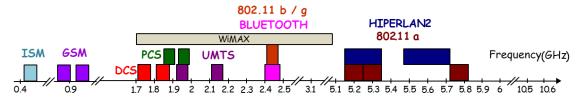

Parallel to the development of mobile cellular communication systems, other wireless standards focusing on data transfer were developed and gain importance in the telecommunication domain. Among them, the most successful are the shortrange Bluetooth and medium range WLAN (WiFi) standards. Initiated in the late 1980s and standardized in 1999, the Bluetooth standard was developed with focus on low cost, low power consumption and up to 10 m range. Operating in the 2.4 GHz ISM band, it used Frequency Hopping Spread Spectrum (FHSS) access method with 1 MHz channel width, GFSK modulation, it achieves up to 1 Mbit/s. In 1997, the IEEE established the 802.11 WLAN standard, with 22 MHz channel width, operating at the 2.4 GHz ISM band, it used the Direct Sequence Spread Spectrum (DSSS) modulation and reached up to 2 Mbit/s in a range of 100 m. Recent revisions of this standard as 802.11n and 802.11ac, operate at 2.4 GHz and 5 GHz bands, with channels up to 160 MHz wide, Multi-Input Multi-Output (MIMO) OFDM modulation, reaching 800 Mbit/s over a range of 35 m. Besides these standards, other systems emerged, such as the long range Worldwide Interoperability for Microwave Access (WiMAX or IEEE 802.16). Initially designed to reach 30 Mbit/s and deliver last-mile broadband services, WiMAX yields 1Gbit/s in short distances, or a few of MBit/s up to 50 km. The IEEE 802.16m revision of the standard, was developed for use in ITU's IMT-Advanced recommendation and is a competitor of LTE-Advanced on the 4G.

All these wireless data standards are considered as complementary to cellular ones, and there is a strong need for interoperability between them. Multifunction terminals, gathering a maximum of standards in an optimized way, have emerged over the last decade. Such hyper-connected devices are expected to provide a seamless connectivity anywhere at any time. Nowadays a smartphone is supposed to cover more than 15 standards located in a 0.4 GHz to 6 GHz band, as illustrated in Figure 1.2.

Figure 1.2 – Continuous development wireless standards

The increasing demand for higher data rates, wider bandwidths, higher integration and lower power consumption draw the canvas of this thesis work.

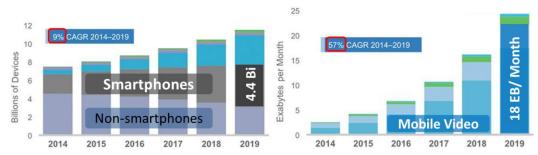

# 1.2 RADIO CONCEPT IN SMARTPHONE: OVERVIEW AND LIMITATION FOR THE FUTURE

Nowadays we find many connected devices in our environment. By 2019, 5 billion of them, including smartphones, tablets and laptops, are expected to co-exist with a 9% yearly growth. Such a huge number of devices will broaden the service and the quality of service (QOS), the data traffic will grow by 57% per year, reaching almost 25 Exabytes per month. As shown in Figure 1.3, mobile video will represent about 80% of this traffic. This demand for more data rate, calls for more bandwidth, higher complexity modulation schemes, MIMO and carrier aggregation techniques.

Figure 1.3 – Number of smart devices and mobile video expected growth Source: Adapted from (CISCO, 2016)

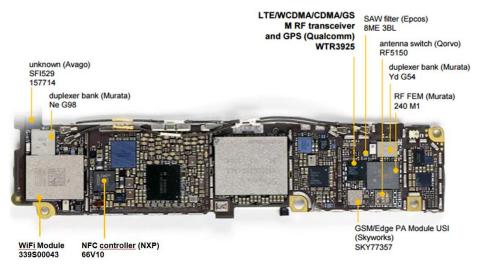

To address this purpose multi-standard Tx/Rx architectures are actually implemented with several single band/standard transceivers on the same chip as illustrated in Figure 1.4, for the WiFi/Bluetooth chip of iPhone 5S (Apple). However, the

competitive market of smartphone pushes harder toward low cost developments, low power consumption and high quality systems. These restrictions put strict challenges on the development of future radio that the basic concept of current transceivers cannot address. Some of these points are first introduced and discussed now.

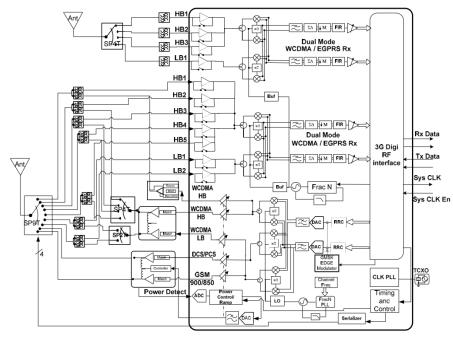

Figure 1.4 – Apple iPhone 6S board showing the multi-chip RF design. Source: (CHIPWORKS INC., 2015)

Recent smartphones are still implemented with multi-chip architectures. Where each group of standards, with defined and fixed frequency bands, is implemented in a different chip as illustrated in Figure 1.4, for the case of a 2.4/5GHz WiFi. This strategy is expensive, and do not allow upgrading, since the processing of a new standard or frequency band, not originally planned, requires the design of a new circuit and the sale of a new device, hindering flexibility. (MOY; PALICOT, 2015). Furthermore, redundant low noise amplifiers, mixers and frequency synthesis modules significantly increase the overall power consumption of such devices. Therefore, the multi-chip/multi-front-end solution is not sustainable over the long term. Even a recent work, shown in Figure 1.5 (GEORGANTAS et al., 2015), with integrated power amplifiers, and variable gain LNAs, still do not cover geolocation or data standards, so one or more chips are needed to cover all the needed standards.

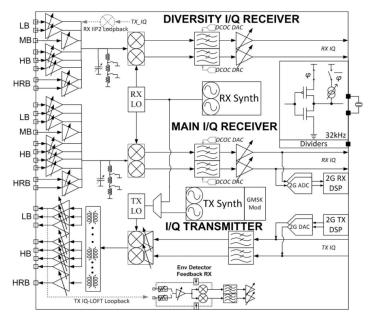

Figure 1.5 – Broadcom 13mm<sup>2</sup> 40nm GSM/EDGE/HSPA+/TDSCDMA/LTE Transceiver Source: (GEORGANTAS et al., 2015)

These transceivers features multiple receiving paths and are placed on the single die, with a fair number of external passive devices such as SAW filters and switches scattering off-chip, as shown in Figure 1.6. Passive devices can be integrated with the silicon die using 3-D stack-up packaging to save the board area. However, the cost of System-In-Package (SiP) is still prohibitively high for wide adoption (CHEN, 2009).

Figure 1.6 – Skyworks Digital RF 3G transceiver Source:(SOWLATI et al., 2009)

The power consumption of such chips is not optimized, as their radio performances, at system level, are designed and fixed for the worst-case scenario (LOLIS et al., 2015). For example, if a phone is close to a base station, the signal would be strong but the receiver would amplify it expending the same amount of power as it would if the signal were weak, wasting battery energy.

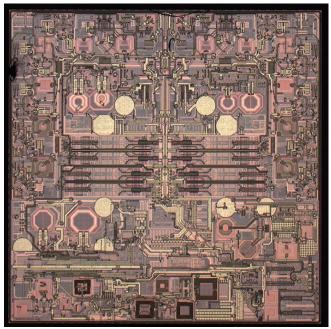

Figure 1.7 – Qualcomm WTR3925 die. 28 nm RF transceiver used in Samsung Galaxy S6 and Apple iPhone 6S

Source: (TECHINSIGHTS INC., 2015)

These RF blocks use many inductances, which are implemented on silicon for cost saving and a reduction of footprint. However, the size of the integrated inductors remains large compared to active devices that significantly limit the density of integration of RF systems as illustrated in Figure 1.7. Whereas the speed of transistor directly benefits from technology shrink, the quality of passive devices, and especially inductors, does not improve at all. The analog performance of MOS devices degrade with the reduction of the gate length. Short channel effects, DIBL, velocity saturation, flicker noise and linearity deteriorate for each new CMOS generation. Moreover, the radio specifications of modern devices become more stringent at each generation. A new approach in RF circuits and systems is required to address the challenge of future radio implementation in advanced CMOS Process.

#### 1.3 A BRIEF ON RX ARCHITECTURES

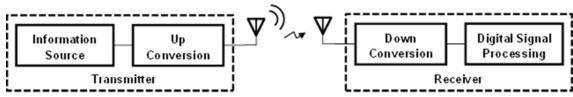

A wireless communication system uses electromagnetic waves propagation properties to transmit information over the air (Figure 1.8). After radiation by the antenna, the modulated signal travels away from transmitter being subject to several perturbations (attenuation, distortion) due to scattering, fading, multipath interference, and other propagation effects.

Figure 1.8 - Wireless communication system, transmitter and receiver

The signal received by the antenna shall be transposed back to a low frequency range so the information can be extracted. This is the down-conversion process or demodulation, which is carried out by the RF receiver chain.

#### 1.3.1 Conventional Receivers and Limitations

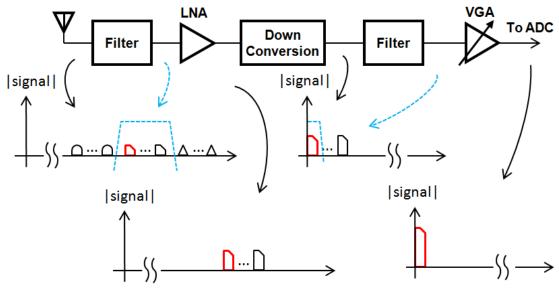

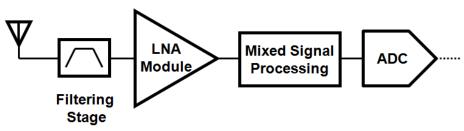

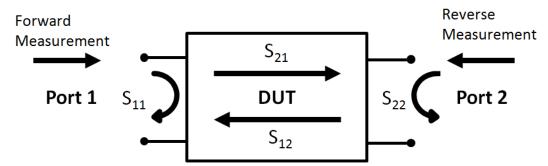

Over the years, several RF receiver architectures were proposed. They are all derived from one of the 3 most popular solutions which are: the heterodyne, the homodyne and the low-IF architecture. These 3 basic architectures are based on a same concept of RF analog signal processing represented in Figure 1.9. The signal collected by the antenna is first filtered by a high-Q pass band filter to select the standard of communication. The Low Noise Amplifier (LNA) is responsible for the sensitivity of the receiver, and a part of the RF gain. The frequency down conversion embedding a mixer and a frequency synthesis shifts the RF band to low frequency. This operation enables the channel selection by filtering. The Voltage Gain Amplifier (VGA) adapts the signal dynamic to the scale of the Analog to Digital Converter (ADC).

Figure 1.9 - Conventional RF Analog Signal processing in a receiver

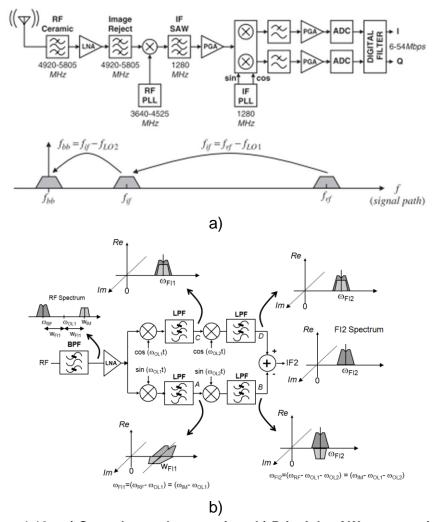

The heterodyne class of receivers features a two-step frequency down conversion as illustrated in Figure 1.10.a). The first mixer in Figure 1.10 shifts the signal to an intermediate frequency (IF) equals to 1.28 GHz. It is further filtered out by the Surface Acoustic Wave (SAW) and amplified by the PGA before the second, and final, frequency down conversion. The IF step generates the folding of the image frequency which requires a high-Q pass-band filter before the first mixer to attenuate the image. The problem of image rejection was lately solved with the Weaver architectures presented in Figure 1.10.b). The processing of the RF signal with parallel and quadratic paths cancels out the image. The image rejection filter is no longer needed which improves the integration and flexibility of heterodyne receiver. The large number of high-Q pass band filter remains a limitation in terms of integration, sensitivity, reliability and flexibility.

Figure 1.10 – a) Super-heterodyne receiver. b) Principle of Weaver receiver. Source: (BEHZAD, 2007)

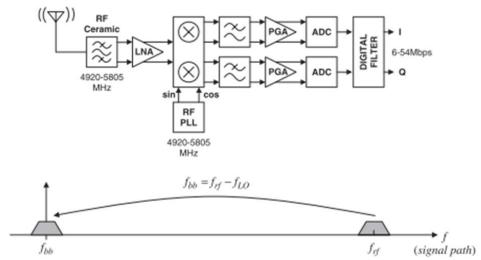

The problem of image rejection does not occur in the homodyne receiver, Figure 1.11. Indeed the RF signal is directly down converted to base band by selecting a local oscillator (RF PLL in Figure 1.11) at the same frequency of the RF signal, hence the image is the signal itself. The high integration and low power consumption of homodyne receiver makes it interesting for radio implementation. However, it has several drawbacks among them are: the sensitivity to flicker noise, the desensitization due to DC-offset, the need for high linearity to name a few.

Figure 1.11 – Homodyne 802.11a receiver Source: (BEHZAD, 2007)

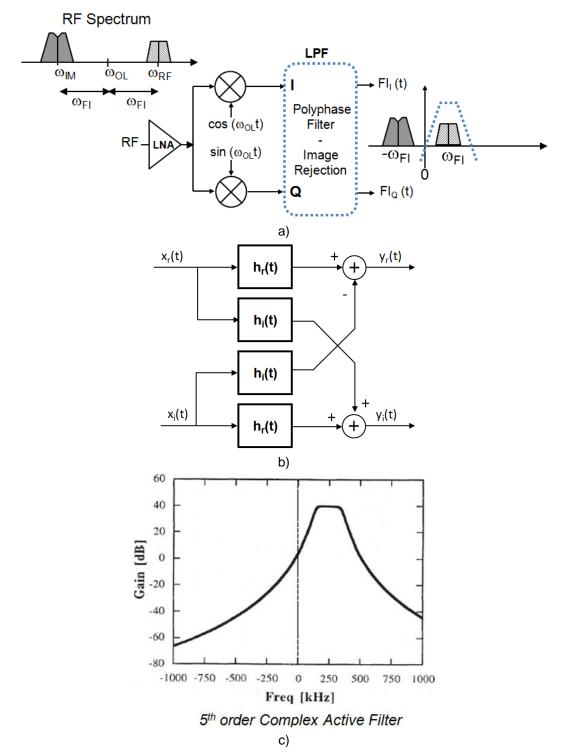

The concept of the Low IF receiver is close to the principle of the direct-conversion architecture: the signal is directly translated to baseband to be filtered and demodulated after analog to digital conversion. However, the IF is not zero, it is equals to 2 or 3 time the channel bandwidth. This frequency plan makes the low IF receiver less sensitive to flicker noise and DC offset generation. However, this architecture reintroduces the problem of image rejection inherent in heterodyne receivers. To solve it a poly-phase pass band filter is introduced after the complex down-conversion, Figure 1.12.a). It allows for image rejection and channel selection. Indeed the combination of I/Q paths, Figure 1.12.b), in the polyphase filter yields a complex processing of the signal which results in a filtering of the negative frequency attenuating the image, as illustrated in Figure 1.12.c). Nowadays the low IF receiver is a very popular architecture since it features the best trade-off in terms of performance, cost and integration compared to heterodyne and homodyne receivers.

Figure 1.12 – a) Low IF receiver. b) General description of a polyphase filter. c) frequency response of a 5th order active band-pass complex filter.

The conventional receivers described in this section, and their derived versions, feature the radio module of our wireless devices. The principle of frequency down conversion by RF mixing with a local oscillator is narrowband by nature. To address a multi-band operation several receivers are parallelized as illustrated in Fi-

gure 1.6. This approach is definitely suited to address the challenge of a wideband, adaptive and low cost radio. The next section reports on some new approaches of RF signal processing which circumvent most of the standard architecture issues.

#### 1.3.2 Multi-standard/multi-band receiver Rx Architectures attempts

Figure 1.13 - The concept of an adaptive radio receiver

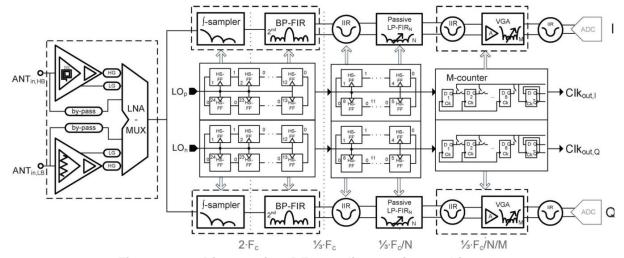

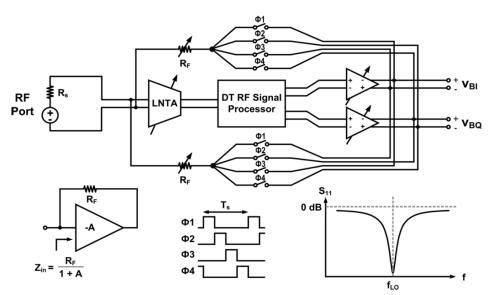

The Software Radio (SR), a concept introduced by Mitola (MITOLA, 1995), is actively being researched as a promising solution to address the challenge of multiband/multi-standard flexible radio. This concept, illustrated in Figure 1.13, is to replace the standard RF analog signal processing – implemented with RF mixers, frequency synthesizer, base-band filters and automatic gain control loops - by a high frequency mixed-signal processing module. As SR applications are still in their infancy, many solutions are being developed in current literature to perform digital/mixed signal processing. To name a few: a) the subsampling track-and-hold architecture (DEVRIES; MASON, 2008). Using a sample and hold circuit clocked at a lower frequency than the incoming RF carrier signal, it allows the use of a much lower power synthesizer compared to a direct conversion or low-IF receiver, which requires an RF PLL. Targeted to the 900 MHz band, it consumes 7.7 mW, has a NF of 8 dB, with image frequency attenuation of 25 dB. b) The RF-sampling architecture, shown in Figure 1.14 (GEIS et al., 2010), where the output of a gain programmable multiband LNA is sampled at full Nyquist rate of the signal's carrier. After the sampling process a strong shaped band-pass FIR filter, is applied before the signal is down-converted by means of subsampling. Consuming 115 mW, it covers the GSM, UMTS and WiMAX (3GHz) standards, with BW selection from 200 kHz to 20 MHz. It reaches NF of 5.1 dB, with gain in the -2 dB to 60 dB range. It also presents in-band IIP3 of +1 dBm and out-of-band (OOB) IIP3 of -3 dBm. c) The N-path filter receiver of Figure 1.15 (CHEN; HASHEMI, 2014), (ZHU; KRISHNASWAMY; KINGET, 2015) exploits a discrete time switched capacitor array to achieve High-Q filtering at RF frequency

together with a down conversion over a wide frequency range. Consuming up to 600 mW, it covers the 0.5 to 3 GHz frequency range, has NF of 6.8 dB, maximum gain of 35 dB, IB IIP3 of -12 dBm and OOB IIP3 of +11 dBm.

Figure 1.14 – Discrete-time RF-sampling receiver architecture Source: (GEIS et al., 2010)

Figure 1.15 – Software-Defined Radio Receiver Using Discrete-Time RF Signal Processing Source: (CHEN; HASHEMI, 2014)

More solutions based on very different approaches are reported in the literature. None of them clearly dominates because they cannot achieve a complete set of performance in terms of: bandwidth/resolution bandwidth, blocker tolerance/Linearity, dynamic range and power consumption due to system complexity. Interestingly, they all features a low noise amplification module before digital/mixed signal processing to adjust, at least, the dynamic of the signal and the signal-to-noise ratio.

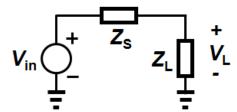

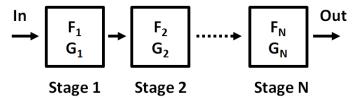

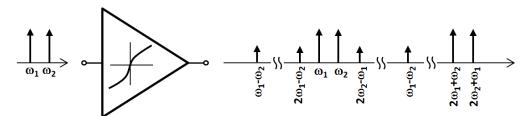

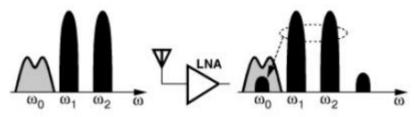

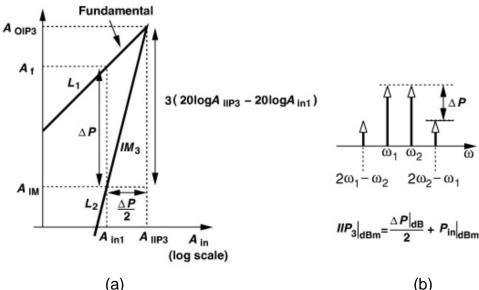

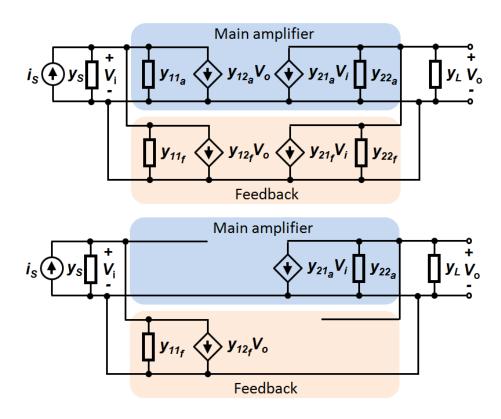

#### 1.4 LNA BASICS: FROM SYSTEM APPROACH TO CIRCUIT METRICS

The low noise amplifier (LNA) is the first active block of the receiver chain. It is placed after the band selection filter. Its function is to amplify the signal received by the antenna, which is usually very weak (in the range of -100 dBm), with minimum distortions (moderate 3th order Intermodulation Point (IP3)), and without introducing too much noise (low Noise Figure) to preserve the signal to noise ratio. The gain of the LNA must be large enough to minimize the noise contribution of the subsequent stages (see Appendix A). Together with the topology choice, the noise matching and the input matching contribute to achieve a large gain and a low noise figure. The linearity is supported by the architecture of the LNA.

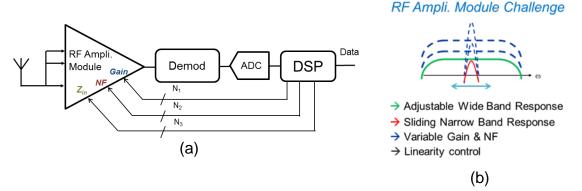

To cope with a low power consumption, a small silicon footprint and the increasing number of wireless standards, the research efforts currently focus on the development of broadband, highly linear and reconfigurable LNA for the concept of SR receiver presented in Figure 1.16.a). This reconfigurable low noise amplification module is expected to achieve the behavioral response proposed in Figure 1.16.b) which includes:

- An adjustable wideband response

- A sliding/tunable narrow-band response

- Allow a variation of the voltage gain and the noise figure

- A control of the linearity

Figure 1.16 – Reconfigurable receiver and the adaptive RF amplifier challenge

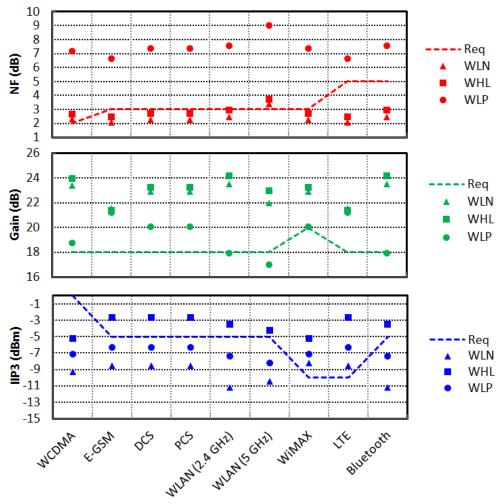

This work aims the development of a generic, wideband LNA, with a digital tuning of the performance. To reduce the silicon footprint, and the cost of implementation, an inductorless architecture is preferred. The LNA will address at least 8 different communication standards: WCDMA, E-GSM, DCS, PCS, WLAN (2.4GHz and 5GHz), Bluetooth, WiMAX and LTE. The specifications, in terms of voltage gain, noise figure (NF) and linearity (IIP3), required for each standard (ATALLAH et al., [s.d.]; BRANDOLINI et al., 2005; INIEWSKI, 2007), are summarized in Table 1.2, and are referred to the worst-case scenario for the radio link – i.e. maximum sensitivity and high linearity. A power saving can be obtained if the receiver does not need to demodulate all the standards at the same time, or if the radio link conditions improve. For instance, if the level of the blockers is low, the IP3 can be reduced, or if the level of desired signal is higher than the minimum required for sensitivity (high SNR<sub>in</sub>), the NF specification can be relaxed. In such scenarios, the LNA is able to be adapted to the radio link conditions, and to operate with reduced power consumption.

Table 1.2 - LNA requirements by wireless standard Frequency Band (MHz) Requirement

| . requestey Dania (iiii iz) |      |      |           |         |           |

|-----------------------------|------|------|-----------|---------|-----------|

| Standard                    | Low  | High | Gain (dB) | NF (dB) | IIP3 (dB) |

| WCDMA                       | 1920 | 2170 | 18        | 2       | 0         |

| E-GSM                       | 880  | 960  | 18        | 3       | -5        |

| DCS                         | 1710 | 1800 | 18        | 3       | -5        |

| PCS                         | 1850 | 1990 | 18        | 3       | -5        |

| WLAN (2.4GHz)               | 2400 | 2483 | 18        | 3       | -5        |

| WLAN (5 GHz)                | 5150 | 5850 | 18        | 3       | -5        |

| WiMAX                       | 1700 | 5000 | 20        | 3       | -10       |

| Bluetooth                   | 2400 | 2480 | 18        | 5       | -5        |

| LTE                         | 700  | 3800 | 18        | 5       | -10       |

#### 1.5 RESEARCH GOAL AND THESIS ORGANIZATION THIS

This research focuses on the design of low-power, low-area and wideband reconfigurable CMOS LNA suitable for adaptive multi-standard/multi-band radios. Even if the design methodology for inductor based narrowband LNA has been well explored in the literature for the last two decade, the correlation between low noise, linearity and broadband impedance matching of inductorless LNA, still needs to be

investigated to work out the right tradeoff. Moreover, the wideband operation of the LNA, in a multi-standard/multi-band scenario, requires higher linearity performance than the conventional specifications defined for each standard. This constraint calls for advanced and new circuit techniques. Furthermore, the orthogonal control of the LNA characteristics would give more flexibility to the receiver. All these considerations draw the framework of this thesis that is organized as follows:

- Chapter 2 reviews inductorless LNAs and reconfiguration techniques.

Two solutions are proposed and analyzed through the derivation of the LNA characteristics.

- Chapter 3 introduces the design guide proposed to explore the LNA design space, and to define the device sizes with respect to a set of specifications.

- Chapter 4 exposes the measurement results of the two inductorless reconfigurable LNA prototypes developed in 130nm CMOS technology. Through a large set of measurement in different mode of operation, the optimum configurations are worked out and discussed. Besides some specific scenario are proposed to test the circuit tolerance to concurrent standard blockers.

- Chapter 5 draws conclusions of this research and discussions for future investigations.

#### 2 PROPOSED TOPOLOGY

This chapter introduces the state of the art on wideband and reconfigurable LNAs. Next, the proposed topology is presented with a detailed analysis of the performance. Due to the low cost requirement presented in Chapter 1, only inductorless wideband solutions are discussed.

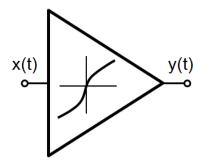

#### 2.1 WIDEBAND INDUCTORLESS LNA TOPOLOGIES

The impedance matching presents a crucial step in LNA design to guarantee a good trade-off between gain and noise factor (GIRLANDO; PALMISANO, 1999). The challenge is to achieve a high voltage gain  $(A_V)$  and a good input matching  $(Z_{in})$  over the band of interest, with a low power consumption  $(P_{DC})$ . The state of the art of wideband LNA topologies will be discussed focusing on the basic configurations shown in Figure 2.1. In this section, the existing wideband LNA families will be presented along with a comparison of the different advantages and disadvantages of each structure.

Figure 2.1 – Inductorless LNA structures. a) Common-gate b) Resistive SFB c) Current-reuse d) Active SFB.

In the state of the art, single-ended inductorless LNAs are based on either common-gate (CG) topology (Figure 2.1.a), or shunt-feedback (SFB) architectures (Figure 2.1.b, Figure 2.1.c, Figure 2.1.d).

Common-gate (CG) amplifiers, Figure 2.1.a), enable both high gain and low input impedance as  $g_{m1}$  increases:

$$A_V = +g_{m1}(R_L||r_{01}) (1)$$

$$Z_{in} = \frac{1}{g_{m1}} \tag{2}$$

Input matching is achieved over a wide frequency range when  $g_{m1}=R_S^{-1}$ , which results in  $g_{m1}=20~mS$  for a source impedance of  $50\Omega$ . The power consumption  $P_{DC}$  is basically fixed by the source impedance and is still large for low power applications. Some  $g_m$ -boosted solutions have successfully alleviated this compromise by exploiting the complementary nature of differential topologies (BELMAS; HAMEAU; FOURNIER, 2012; HAN; JUNG; KIM, 2015; SOBHY et al., 2011). Unfortunately, this approach makes the design of the antenna and front-end RF filter difficult, and sensitive to mismatching.

Figure 2.1.b) shows the resistive shunt feedback amplifier (SFB) (CHEN; LIU, 2012; PERUMANA et al., 2008). Applying the KCL in the loop we find

$$g_{m1}V_{in} = \left(\frac{-V_{out}}{R_L}\right) + \left(\frac{V_{in} - V_{out}}{R_F}\right) \tag{3}$$

The voltage gain found solving (3) for  $V_{out}$  and  $V_{in}$ ,

$$A_V = \frac{V_{out}}{V_{in}} = -G_m R_{out} \tag{4}$$

where, the effective transconductance is  $G_m = \left(g_m - \frac{1}{R_F}\right)$  and the output resistance is  $R_{out} = (R_F || R_L)$ , or accounting for channel length modulation  $R_{out} = R_F || R_L || r_o$ . The input impedance  $Z_{in}$  is defined by the ratio of the feedback resistance  $R_F$  and the voltage gain  $A_V$ . The input matching is achieved when  $R_F = R_S(1 + |A_V|)$  according (5).

$$Z_{in} = \frac{V_{in}}{I_{in}} = \frac{V_{in}}{\left(\frac{V_{in} - A_V V_{in}}{R_F}\right)} = \frac{R_F}{1 - A_V} = \frac{R_F}{1 + |A_V|} \approx \frac{R_F}{|A_V|}$$

(5)

This structure presents a trade-off between  $V_{DD}$  and  $A_V$ , as a higher value of  $R_L$  requires a higher value of  $V_{DD}$  for the same drain current. It also presents a compromise between  $A_V$  and  $R_F$  as the latter shunts the output thus reducing the output resistance. Lower values of  $R_F$  reduces the effective transconductance and reduces  $A_V$  (TARIS; BEGUERET; DEVAL, 2007).

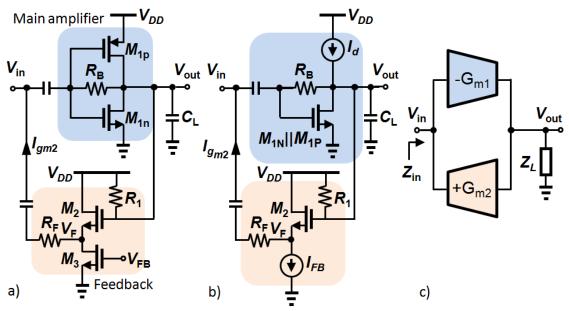

To circumvent this problem, the resistive load  $R_L$  in Figure 2.1.b) is replaced by a PMOS transistor  $M_2$  in the current-reuse (CR) structure Figure 2.1.c) (EL-NOZAHI et al., 2011).  $M_1$  and  $M_2$  biased with the same DC current act as a current source for the other, and the configuration of Figure 2.2.a) is equivalent to the two half circuit of Figure 2.2.b). For small signal analysis the current reuse stage is modeled as a resistive SFB stage biased by a single current source as illustrated in Figure 2.2.c).

Figure 2.2 – CR small signal model. a) CR b) Superposition of two ideal resistive SFB c) Final model of the resistive SFB with a single transistor combining M1 and M2 in parallel driven by a ideal current source.

The voltage gain is the same as the resistive SFB with:

$$G_m = g_{m1} + g_{m2} - 1/R_F \tag{6}$$

and

$$R_{out} = R_F ||r_{o1}|| r_{o2} \tag{7}$$

Neglecting the channel length modulation and assuming  $R_F\gg 1/(g_{m1}+g_{m2})$ , it yields:

$$A_V \approx -R_F(g_{m1} + g_{m2}) \tag{8}$$

The magnitude of the voltage gain is proportional to  $R_F$ , capable of reaching very high values. The matching criterion, further defined in Table 2.1, imposes  $g_{m1}+g_{m2}=\frac{1}{R_S}$ , which leads to :

$$A_V \approx -\frac{R_F}{R_S} \tag{9}$$

In practice, channel length modulation reduces the output resistance and the maximum achievable gain. The input impedance is highly capacitive due to the gate

to source capacitors of M1 and M2, and the bandwidth is limited. Still, this topology achieves the highest  $A_V/P_{DC}$  ratio of any single stage amplifier configuration, which makes it interesting for low power applications.

Another approach to minimize the trade-off between  $A_V$  and  $Z_{in}$  is the active SFB which introduces a source follower along with  $R_F$ , as illustrated in Figure 2.1.d) (BELOSTOTSKI; MADANAYAKE; BRUTON, 2012; CHEN et al., 2008; RAMZAN; ANDERSSON, 2007; WANG; ZHANG; YU, 2010). The trade-off between  $A_V$  and  $R_F$  is relaxed as the feedback transistor  $M_2$  does not drain current from the output. The voltage gain is the same as the resistive SFB with:

$$G_m = g_{m1} \tag{10}$$

and,

$$R_{out} = R_L || r_o \tag{11}$$

And,

$$A_V = -g_{m1}R_L \tag{12}$$

The input impedance is the ratio of  $R_F$  and the resistance viewed at the source of  $M_2$  over the voltage gain:

$$Z_{in} = \frac{1 + g_{m2}R_F}{g_{m2}(1 + |A_V|)} = \frac{\left(\frac{1}{g_{m2}} + R_F\right)}{1 + |A_V|} \approx \frac{\left(\frac{1}{g_{m2}} + R_F\right)}{|A_V|},\tag{13}$$

The input matching is completed if

$$g_{m2} = \frac{1}{R_S(1 + |A_V|) - R_F} \tag{14}$$

The active SFB of Figure 2.1.d) achieves good performance in terms of gain, NF and input matching over a wide bandwidth. Unfortunately the combination of active feedback with a resistive common source amplifier introduces some distortions which significantly degrade the linearity of the LNA (BORREMANS et al., 2008).

Table 2.1 summarizes the voltage gain, input impedance and matching conditions of each basic inductorless topology in the state of the art.

Table 2.1 - Indutorless LNA summary

|               | $R_{out}$ $A_V$         |                                             | $Z_{in}$                                  | Matching condition                        |  |

|---------------|-------------------------|---------------------------------------------|-------------------------------------------|-------------------------------------------|--|

| Resistive SFB | $R_L   R_F   r_{o1}$    | $-\left(g_{m1}-\frac{1}{R_F}\right)R_{out}$ | $\frac{R_F}{1+ A_V }$                     | $R_F = R_S(1 +  A_V )$                    |  |

| Active SFB    | $R_L    r_{o1}$         | $-g_{m1}R_{out}$                            | $\frac{1 + g_{m2}R_F}{g_{m2}(1 +  A_V )}$ | $g_{m2} = \frac{1}{R_S(1 +  A_v ) - R_F}$ |  |

| Common-Gate   | $R_L    r_{o1}$         | $+g_{m1}R_{out}$                            | $\frac{1}{g_{m1}}$                        | $g_{m1}=rac{1}{R_S}$                     |  |

| Current-Reuse | $R_F   r_{o1}   r_{o2}$ | $-\left(G_m-\frac{1}{R_F}\right)R_{out}$    | $\frac{R_F}{1+ A_V }$                     | $g_{m1} + g_{m2} = \frac{1}{R_S}$         |  |

Table II sums up the discussion about the pros and cons of the basic configurations for the implementation of wideband low power and highly linear LNA.

Table 2.2 - Classical LNA topologies comparison.

| Topology              | Gain     | NF       | Linearity | Consump-<br>tion | Integra-<br>tion | Bandwidth | High<br>frequency<br>impedance<br>matching |

|-----------------------|----------|----------|-----------|------------------|------------------|-----------|--------------------------------------------|

| Resistive termination | Moderate | High     | High      | High             | High             | wide      | Low                                        |

| Common-gate           | Moderate | Moderate | High      | Moderate         | High             | wide      | Moderate                                   |

| Resistive SFB         | Moderate | Moderate | Moderate  | High             | High             | wide      | Moderate                                   |

| Current-reuse         | High     | Moderate | High      | Low              | High             | wide      | Moderate                                   |

| Active SFB            | Moderate | Moderate | Moderate  | Moderate         | High             | wide      | High                                       |

The resistive termination architecture responds to the high integration requirements as it embeds few passive components. However, it is not suited for wideband operation due to the significant degradation of the noise figure at high frequencies. The same argument holds for the resistive feedback architecture, which also exhibits a large power consumption. These two topologies are finally not relevant since they achieve average performance and do not comply with the low power requirement.

The common-gate architecture is interesting in terms of linearity and gain. However, the minimum noise figure is limited to 3.5 dB, which is too large for some standards.

The current-reuse architecture achieve high gain, low power consumption but its noise performance and impedance matching pose as limiting factor to meet higher frequency standards requirements. The active feedback topology, however, shows

good balance among most of the characteristics being limited by its linearity and gain.

In this work, we combined the current-reuse and active shunt feedback topologies, taking advantage of the positive aspects of each one, creating a novel LNA architecture, called from now on Gyrator-like architecture (DE SOUZA; MARIANO; TARIS, 2015). This structure is used as the core of all 3 prototypes fabricated and is used to demonstrate the feasibility of a compact, low-power, performance reconfigurable LNA.

#### 2.2 RECONFIGURABLE LNA TECHNIQUES

Chapter 1 shows that an adaptive receiver needs a LNA that enables the reconfiguration of its Gain, NF, IIP3 and operating frequency. In the state of the art, most of the solutions address at most two of these parameters, generally in a nonorthogonal manner, as will be shown next.

# 2.2.1 Biasing control

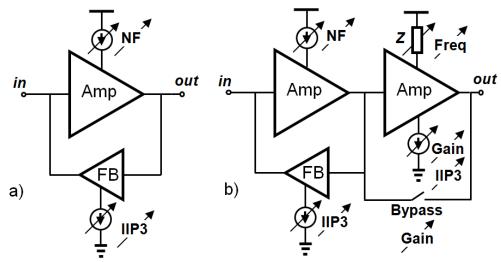

Figure 2.3 - LNA reconfiguration: Bias control.

The first approach exploits the control of bias conditions through current steering and, or, V<sub>DD</sub> variation to reconfigure the LNA performance.

A generic 2-stage LNA is represented in Figure 2.3 with some solutions of bias control of the state of the art. The variation of bias current/V<sub>DD</sub> only concerns the reconfiguration of the gain and the linearity.

A variable gain LNA featuring a two stage stacked cascade in common-source configuration is presented in (WANG; LU, 2005). These stages reuse the same bias current, achieving a high  $A_V/P_{DC}$ , thus enabling power saving. The circuit

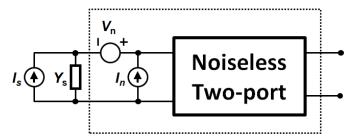

is implemented in 180 nm CMOS technology and the gain control is achieved by the bias voltage of the second stage. The prototype reaches 8 dB gain control range, with maximum gain of 16.4 dB, 1 GHz bandwidth, NF of 3.5 dB and  $P_{DC}$  of 3.2 mW.