# Compact modeling and circuit design based on spin injection

Qi An

#### ▶ To cite this version:

Qi An. Compact modeling and circuit design based on spin injection. Electronics. Université Paris Saclay (COmUE), 2017. English. NNT: 2017SACLS240. tel-01720258

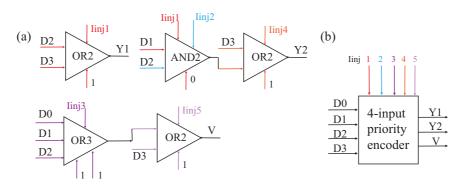

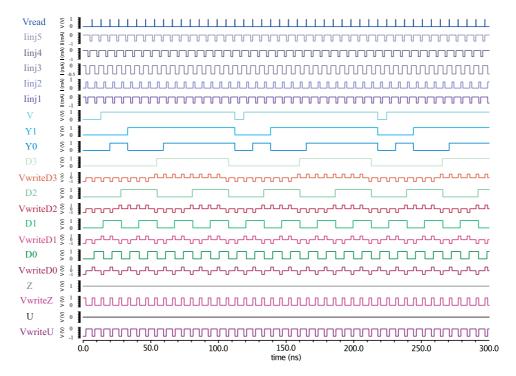

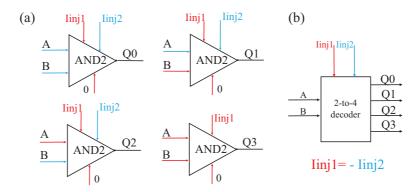

## HAL Id: tel-01720258 https://theses.hal.science/tel-01720258

Submitted on 1 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

NNT: 2017SACLS240

## Thèse de doctorat de l'Université Paris-Saclay préparée à l'Université Paris-Sud

Ecole doctorale n°575 Electrical, Optical, Bio-physics and Engineering (EOBE) Spécialité de doctorat : PHYSIQUE

par

## MLLE QI AN

Modélisation compacte et conception de circuit à base d'injection de spin

Compact modeling and circuit design based on spin injection

Thèse présentée et soutenue à Orsay , le 05 Octobre 2017.

#### Composition du Jury:

| Μ.  | Arnaud Bournel        | Professeur                  | (Président du jury)  |

|-----|-----------------------|-----------------------------|----------------------|

|     |                       | Université Paris-Sud        |                      |

| Μ.  | LIONEL TORRES         | $\mathbf{Professeur}$       | (Rapporteur)         |

|     |                       | Université Montpellier      |                      |

| Mme | Cristell Maneux       | Professeure                 | (Rapporteur)         |

|     |                       | Université de Bordeaux      |                      |

| Μ.  | IAN O'CONNOR          | $\mathbf{Professeur}$       | (Examinateur)        |

|     |                       | Ecole Centrale de Lyon      |                      |

| Μ.  | Sébastien Le Beux     | Maître de conférences       | (Examinateur)        |

|     |                       | Ecole Centrale de Lyon      |                      |

| Μ.  | Weisheng Zhao         | $\operatorname{Professeur}$ | (Examinateur)        |

|     |                       | Beihang Université          |                      |

| Μ.  | Jacques-Olivier Klein | $\operatorname{Professeur}$ | (Directeur de thèse) |

|     |                       | Université Paris-Sud        |                      |

## Acknowledgements

I would like to thank all the people that helped and supported me in the research and the life during the past three years. This work would not have been achieved without their help and support.

Before the acknowledgment, I want to tell you some stories. In 2013, I was able to come to France to study through the China government scholarship, based on the thesis subject provided by Sébastien Le Beux and Ian O'Connor at Ecole Centrale de Lyon. After finishing the study of Master, I was supposed to continue my doctoral study in Lyon. However, due to the check of "Fonctionnaire de Sécuritde Défense (FSD)", I could not continue my research at Ecole Centrale de Lyon. Under this circumstance, Sébastien Le Beux and Ian O'Connor, whom I should really thank to, help me contact Jacques-Olivier Klein, who became my advisor in the past three years, and Weisheng Zhao, who helps me and discusses with me a lot. Thanks to all of them, I am able to continue my research in France and work on this topic in this laboratory. Except for the opportunity they offered me, I also would like to thank them for their help in my research. I want to express my grateful gratitude to Jacques-Olivier Klein, for his patience, the fruitful discussions and invaluable advice that inspired me on the subject. I felt encouraged by his trust and also have learned what a doctor/researcher really is from him. I am also thankful for my co-advisor, Sébastien Le Beux. He always keeps patient and communicates with me on every detail of my work plans, the subject, and the paper manuscripts. I was influenced a lot by his preciseness in doing research. I also want to thank Weisheng Zhao, for his guidance and fruitful discussions during my thesis. I am also thankful for Ian O'Connor, for his patience, the fruitful discussions on my papers and felt encouraged by his confidence in my ability.

I am very grateful to the members of my thesis committee. I want to thank Prof. Lionel Torres and Prof. Cristell Maneux, for their agree to report this thesis. Similarly, I want to thank Prof. Arnaud Bournel, Prof. Ian O'Connor, Prof. Sébastien Le Beux and Prof. Weisheng Zhao to accept to be the examiners. It is my honor to have this thesis reviewed by such a significant committee. Thank you very much for having accepted this charge.

I would like to thank Prof. Nicolas Vernier, for his help in understanding the magnetic fundamental, and his kindness. I am also thankful to Prof. Arnaud Bournel, for the discussions in material physics. My sincere thanks to all the members of NANOARCHI group: Damien Querlioz, Christopher Benett, Nicolas Locatelli, Adrien Vincent, Alice Mizrahi, Damir Vodenicarevic...I also want to thank Dr. Zhaohao Wang, who helps me a lot in technical problems and understanding the fundamental of magnetism.

I also thank the administration members: Mme Lydia Pactole, Mme Marie-Pierre Garon, Mme Florence Gomez...It has been a pleasure to work in such a kind laboratory. Also thanks to Prof. Eric Cassan, Mme. Sophie Bouchoule and Mme. Laurence Stephen from Doctoral School, for their patience and their assistance in the registration and thesis defense procedure.

To all other friends that made my stay in Paris enjoyable: Erya Deng(thank a lot for your encouragement), Li Su(appreciate your help in my first year), Gefei Wang, Xueying Zhang, Yu Zhang, You Wang, Ping Che, Jiaqi Zhou, Boyu Zhang, Men Su, Lu Lu, Ming Wu, Xiaoyi Yang, Yiyi Li, Hao Zhang, Zheng Yang, Si Chen, Jiating Luo, Weilong Li...

A few lines to my dearest friends: Changhui Zhuang, who has always been close to me and provides me with spiritual power to confront the problems with life; Chenying Gan, who influences me with your optimism and humor on life; Rui Sun, grateful for your concerns

and support and Lingfei Wan, ...you pushed me to like life and gave me optimism.

A special gratitude to my family for their continuous support and encouragement especially to my dearest parents. Thanks for your selfless love and tolerance on me, which helps me live through all the difficulties and gives me hope in my life. Thanks a lot and I love you all!

The last but not the least, I would like to thank China Scholarship Council (CSC) for the financial support.

## Abstract

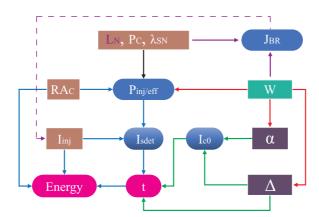

The Complementary Metal Oxide Semi-conductor (CMOS) technology has tremendously affected the development of the semi-conductor industry. However, as the technology node is scaled down, the CMOS technology faces significant challenges set by the leakage power and the short channel effects. To cope with this problem, researchers pay their attention to the spintronics in recent years, considering its possibilities to allow smaller-size fabrication and lower-power operations. The Magnetic Tunnel Junction (MTJ) is one of the most important spintronic devices which can store binary data based on Tunnel MagnetoResistance (TMR) effect. Except for the non-volatile memory, MTJ can be also used to combine with or replace the CMOS circuits to implement a hybrid circuit, for the potential to achieve low-power consumption and high-speed performance. However, the problem of frequent spin-charge conversion in a hybrid circuit may cause large power consumption, which diminishes the advantage of the hybrid circuits. Therefore, the ASL concept which uses a pure spin current to transport the information is proposed for fewer charge-spin conversions, thus for less power consumption. The design of All-Spin Logic (ASL) device-based circuits leads to numerous challenges related to the heterogeneity they introduce and the large design space to explore. Hence, this thesis focus on filling the gap between application requirements at the system level and the device fabrication at the device level.

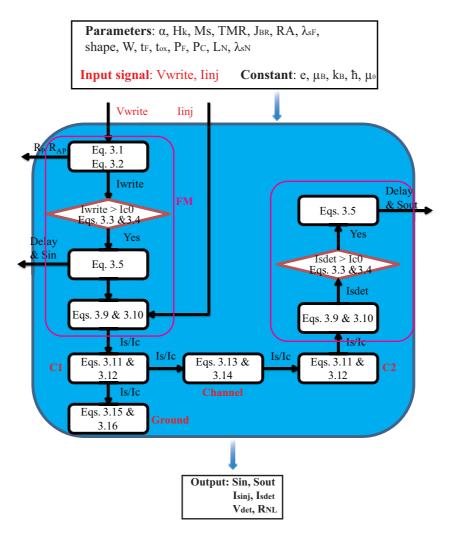

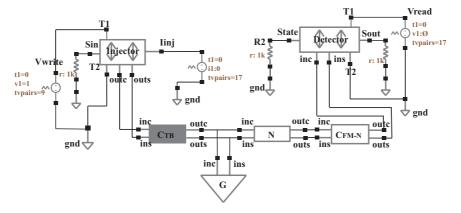

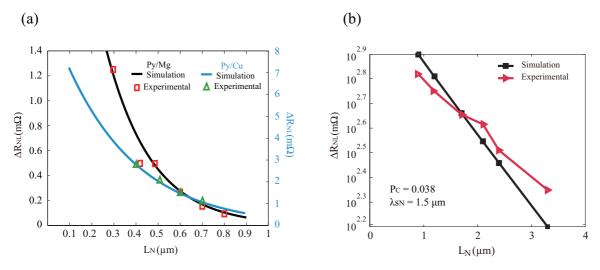

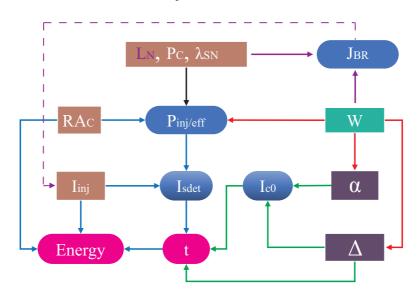

In device level, we developed a compact model integrating the Spin-Transfer Torque (STT), the TMR, the spin injection/accumulation effects, the channel breakdown current and the spin diffusion delay. Validated by comparing with experimental results, this model allows exploring fabrication-related device parameters such as channel lengths and MTJ sizes and help designers to prevent from device damages. Moreover, programmed with Verilog-A on Cadence and divided into several blocks: injector, detector, channel and contact devices, this model allows the independent design and cross-layer optimization of ASL-based circuits, that eases the design of hierarchical, complex circuits. Furthermore, the spin injection/accumulation expressions for the considered ASL device are derived, enabling to discuss the experimental phenomena of the ASL device.

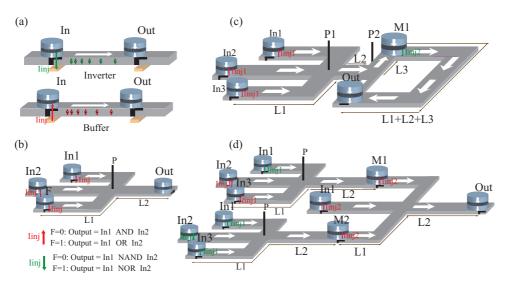

In circuit level, we developed a circuit/system design methodology, taking into account the multi-channel distribution, the gate interconnection and the different injection current ratios caused by the spin diffusion. With circuit/system specifications and constraints, the boolean functions of a circuit are synthesized based on the developed synthesis methods and fabrication-level parameters: channel lengths, MTJ sizes are specified. Based on this developed methodology, basic combinational circuits that form a circuit library are designed and evaluated by using the developed compact model.

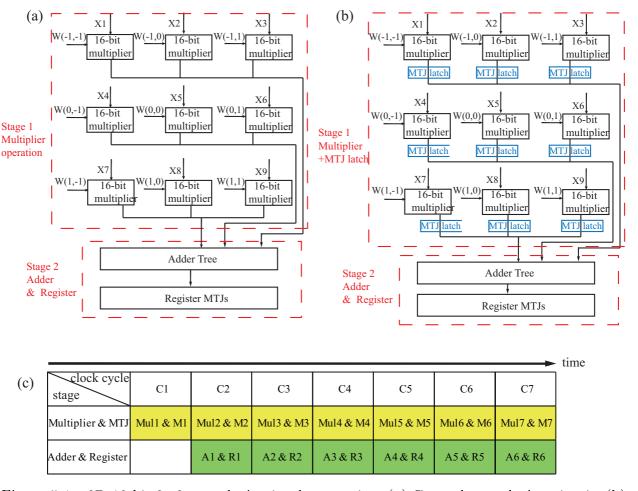

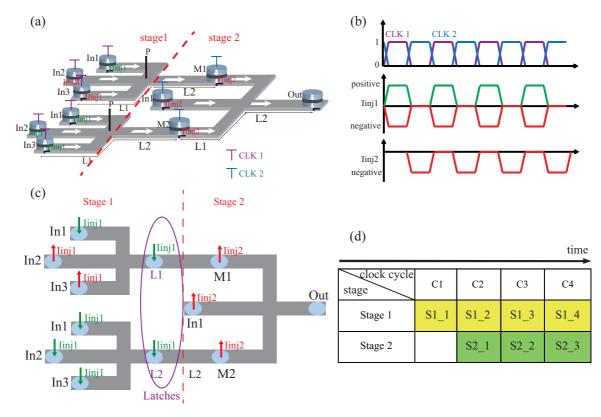

In system level, a convolution circuit and an Intel i7 system are evaluated exploring the interconnection issues: interconnection distribution between gates and inserted buffer count. With theoretical parameters, results show that ASL-based circuit/system can outperform CMOS-based circuit/system. Moreover, the pipelining schema of the ASL-based circuit is discussed with MTJ as latches inserted between stages. The reconfigurability caused by the injection current polarities/values and the control terminal states of ASL-based circuits are also discussed with the reconfigurable exploration of basic logic circuits.

**Keywords**: All spin logic, compact modeling, design methodology, pipelining, reconfigurability

## Résumé

La technologie CMOS a considérablement contribué au développement de l'industrie des semi-conducteurs. Cependant, au fur et à mesure que le nœud technologique est réduit, la technologie CMOS fait face à des défis importants liés à la dissipation dûe aux courants de fuite et aux effets du canal court. Pour résoudre ce problème, les chercheurs se sont intéressés à la spintronique ces dernièeres années, compte tenu de la possibilité de fabriquer des dispositifs de taille réduite et d'opérations de faible puissance. La jonction tunnel magnétique (MTJ) est l'un des dispositifs spintroniques les plus importants qui peut stocker des données binaires grâce à la Magnétorésistance à effect tunnel (TMR). En dehors des applications de mémoire non volatile, la MTJ peut également être utilisée pour combiner ou remplacer les circuits CMOS pour implémenter un circuit hybride, de façon à combiner une faible consommation d'énergie et des performances à grande vitesse. Cependant, le problème de la conversion fréquente de charge en spin dans un circuit hybride peut entraîner une importante consommation d'énergie, ce qui obère l'intérêt pour des circuits hybrides. Par conséquent, le concept ASL qui repose sur un pur courant de spin comme support de l'informaition est proposé pour limiter les conversions entre charge et spin, donc pour réduire la consommation d'énergie. La conception de circuits à base de dispositifs ASL entraîne de nombreux défis liés à l'hétérogénéité qu'ils introduisent et à l'espace de conception étendu à explorer. Par conséquent, cette thèse se concentre sur l'écart entre les exigences d'application au niveau du système et la fabrication des nanodispositifs.

Au niveau du dispositif, nous avons développé un modèle compact intégrant le couple de transfer de spin (STT), la TMR, les effets d'injection/accumulation de spin, le courant de breakdown des canaux et le délai de diffusion de spin. Validé par comparaison avec les résultats expérimentaux, ce modèle permet d'explorer les paramètres du dispositif liés à la fabrication, tels que les longueurs de canaux et les tailles de MTJ, et aide les concepteurs à éviter leur destruction. De plus, ce modèle, décrit avec Verilog-A sur Cadence et divisé en plusieurs blocs: injecteur, détecteur, canal et contact, permet une conception indépendante et une optimisation des circuits ASL qui facilitent la conception de circuits hiérarchiques et complexes. En outre, les expressions permettant le calcul de l'injection/accumulation de spin pour le dispositif ASL utilisé sont dérivées. Elles permettent de discuter des phénomènes expérimentaux observés sur les dispositifs ASL.

Au niveau circuit, nous avons développé une méthodologie de conception de circuit/système, en tenant compte de la distribution des canaux, de l'interconnexion des portes et des différents rapports de courant d'injection provoqués par la diffusion de spin. Avec les spécifications et les contraintes du circuit/système, les fonctions booléennes du circuit sont synthétisées en fonction de la méthode de synthèse développée et des paramètres de niveau de fabrication: longueur des canaux, et tailles MTJ sont spécifiées. Basé sur cette méthodologie développée, les circuits combinatoires de base qui forment une bibliothèque de circuits sont concus et évalués en utilisant le modèle compact développé.

Au niveau du système, un circuit de convolution et un système Intel i7 sont évalués en explorant les problèmes d'interconnexion: la répartition de l'interconnexion entre les portes et le nombre de tampons inséré. Avec des paramètres théoriques, les résultats montrent que le circuit/système ASL peut surpasser le circuit/système basé sur CMOS. De plus, le schéma de pipeline du circuit basé sur ASL est discuté avec MTJ comme tampons insérés entre les étapes. La reconfigurabilité provoquée par les polarités/valeurs du courant d'injection et les

états des terminaux de control des circuits ASL sont également discutés avec l'exploration reconfigurable des circuits logiques de base.

${f Mots\text{-}{\bf cl\acute{e}s}}$ : logique à pur courant de spin, modélisation compacte, méthodologie de conception, pipeline, reconfigurabilité

## Contents

| A            | cknov | ledgements                                            | i            |

|--------------|-------|-------------------------------------------------------|--------------|

| $\mathbf{A}$ | bstra | et i                                                  | ii           |

| Re           | ésum  | ş                                                     | $\mathbf{v}$ |

| 1            | Intr  | oduction                                              | 1            |

|              | 1.1   | Background                                            | 1            |

|              |       | 1.1.1 Device                                          | 1            |

|              |       | 1.1.2 Circuit and system                              | 2            |

|              | 1.2   | Motivation                                            | 3            |

|              | 1.3   | Objectives and Methods                                | 4            |

|              | 1.4   | Research Contributions                                | 5            |

|              |       | 1.4.1 Compact modeling of All Spin Logic (ASL) device | 5            |

|              |       | 1.4.2 ASL based circuit design method                 | 5            |

|              |       | 1.4.3 System design & evaluation method               | 5            |

|              | 1.5   |                                                       | 6            |

|              |       | 0.9                                                   |              |

| <b>2</b>     | Stat  | e-of-the-art                                          | 7            |

|              | 2.1   | MTJs                                                  | 7            |

|              |       | 2.1.1 Structure and working principle                 | 7            |

|              |       | 0 <b>1</b>                                            | 7            |

|              |       | r                                                     | 1            |

|              | 2.2   |                                                       | 4            |

|              |       | 1 0 ( )                                               | 4            |

|              |       |                                                       | 5            |

|              |       | ī                                                     | 8            |

|              |       | 0                                                     | 9            |

|              | 2.3   |                                                       | 22           |

|              | ۷.5   |                                                       | - 2          |

| 3            | Con   | pact Modeling of ASL Device 2                         | 3            |

|              |       | -                                                     | 24           |

|              | J     | ·                                                     | 25           |

|              |       |                                                       | 27           |

|              |       | ·                                                     | 1            |

|              | 3.2   |                                                       | 3            |

|              | 0.2   |                                                       | 3            |

|              |       |                                                       | 3            |

|              |       | <u> </u>                                              | 3            |

|              |       |                                                       | 4            |

|              | 3.3   | <u>.</u>                                              | 55           |

|              | ა.ა   |                                                       |              |

|              |       |                                                       | 6            |

|              |       | i v                                                   | 7            |

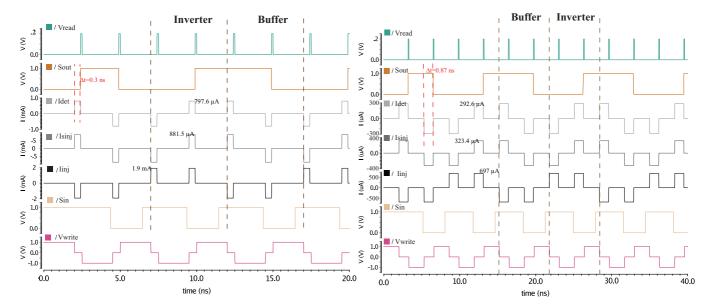

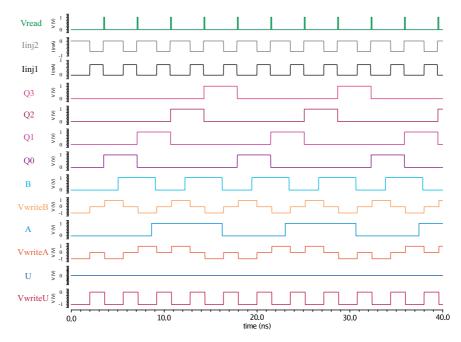

|              |       | 3.3.3 Inverter/Buffer simulation                      | 2            |

|                  | 3.4                                     | Summary                                       | 43             |

|------------------|-----------------------------------------|-----------------------------------------------|----------------|

| 4                | Circ                                    | cuit Design and Simulations                   | 15             |

|                  | 4.1                                     | 8                                             | 45             |

|                  |                                         | 9                                             | 45             |

|                  |                                         | v v i                                         | 46             |

|                  |                                         | v                                             | $\frac{1}{49}$ |

|                  | 4.2                                     | 0                                             | 50             |

|                  | 4.3                                     | 0                                             | 52             |

|                  | 1.5                                     |                                               | 52             |

|                  |                                         | 0                                             | 59             |

|                  |                                         | 9                                             | 75             |

|                  |                                         |                                               | 86             |

|                  | 4.4                                     | v                                             | 30<br>87       |

|                  | 4.5                                     | 9                                             | 31<br>88       |

|                  | 1.0                                     |                                               | 50             |

| 5                | $\mathbf{S}\mathbf{v}\mathbf{s}^{_{1}}$ | tem Level Design                              | 93             |

|                  | 5.1                                     |                                               | 93             |

|                  |                                         |                                               | 93             |

|                  |                                         | O v                                           | 95             |

|                  |                                         |                                               | 96             |

|                  | 5.2                                     |                                               | 98             |

|                  | J                                       | 1 9 , v                                       | 98             |

|                  |                                         |                                               | 00             |

|                  | 5.3                                     |                                               | 03             |

|                  | 0.0                                     |                                               |                |

| 6                | Con                                     | clusions and Perspectives 10                  | )5             |

|                  | 6.1                                     | Conclusions                                   | <b>)</b> 5     |

|                  |                                         | 6.1.1 Global conclusions                      | 35             |

|                  |                                         |                                               | 05             |

|                  |                                         |                                               | 06             |

|                  |                                         |                                               | 06             |

|                  | 6.2                                     | Perspectives                                  | 06             |

|                  |                                         | <del>-</del>                                  | 06             |

|                  |                                         |                                               | 07             |

|                  |                                         |                                               | 07             |

|                  |                                         |                                               |                |

| $\mathbf{R}_{0}$ | efere                                   | nces 10                                       | )8             |

|                  |                                         |                                               |                |

| $\mathbf{A}$     | ppen                                    | dix A ASL Performance Equations Derivation 12 | 29             |

| ۸.               |                                         | dix B Source Code of ASL Compact Model        | า              |

| $\mathbf{A}$     | -                                       | <u>.</u>                                      |                |

|                  | -                                       | O                                             | 33<br>33       |

|                  |                                         | 0                                             |                |

|                  |                                         |                                               | $\frac{37}{2}$ |

|                  |                                         |                                               | 38             |

|                  | Cha                                     |                                               | 39             |

|                  |                                         |                                               | 39             |

|                  | $\sim$                                  |                                               | 40             |

|                  | Gro                                     | and model                                     | 41             |

| $\mathbf{Li}$    | st of                                   | Figures 14                                    | 13             |

|                  |                                         |                                               | 1              |

| Li               | st of                                   | Tables 15                                     | ıΙ             |

| List of Acronyms                                               | 153 |

|----------------------------------------------------------------|-----|

| List of Publications                                           | 155 |

| Synthèse en Français                                           | 157 |

| Chapitre 1 Introduction générale                               | 157 |

| Chapitre 2 État de l'art                                       | 158 |

| Chapitre 3 Modélisation compacte de ASL                        | 159 |

| Chapitre 4 Conception et simulation des circuits à base de ASL | 161 |

| Chapitre 5 Modélisation et évaluation niveau système           | 162 |

| Conclusions et perspectives                                    | 165 |

## Chapter 1

## Introduction

| 1.1   | Backgro<br>.1 Dev | vice                                                          |      |

|-------|-------------------|---------------------------------------------------------------|------|

| 1.3   |                   | rcuit and system                                              |      |

| 1.2 N | Iotivati          | ion                                                           | <br> |

| 1.3   | bjectiv           | ves and Methods                                               | <br> |

| 1.4 H | tesearch          | h Contributions                                               | <br> |

| 1 4   | .1 Cor            | mpact modeling of All Spin Logic (ASL) device                 | <br> |

|       |                   |                                                               |      |

|       | .2 ASI            | L based circuit design method                                 | <br> |

| 1.4   |                   | L based circuit design method stem design & evaluation method |      |

### 1.1 Background

#### 1.1.1 Device

The CMOS technology has tremendously affected the development of semi-conductor industry in the past decades. Its ability to scale electronic devices to ever-smaller dimensions has been the primary driver of the increased performance leading to this development. For over 40 years, the industry has been able to pack twice as many CMOS Field-Effect Transistor (FET) onto a chip every 18 months, which is known as "Moore's Law" [1]. Moore's prediction proved accurate for several decades and has been used in the semiconductor industry to guide long-term planning and to set targets for research and development. However, as device scaling continues into the  $21^{st}$  century, it turns out that past trends in growth, doubling circuit density and increasing performance by around 40% for each new technology generation cannot be maintained by conventional scaling. The CMOS technology faces significant challenges and will slow down the growth of semiconductor industry, according to the International Technology Roadmap for Semiconductors (ITRS) [2], one of the leaders in the fields of semiconductor research and industry.

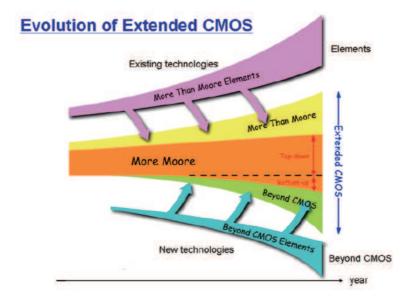

The limitations are found in three aspects: performance, lithography and economic. When scaled down to nano-scale, Short Channel Effect (SCE) becomes increasingly dominant, lowering the threshold voltage and making the devices more vulnerable to variability. Moreover, increasing leakage current [3] during scaling down leads to higher power consumption. From the lithographic point of view, scaling down to sub-50 nm requires several innovations in terms of design and equipment: optical proximity correction, high output power laser light sources, off-axis illumination, short wavelength, etc. These will increase the manufacturing costs. Due to these observations, the way out for semiconductor industry is, either finding a way to continue the scaling of CMOS technology ("More Moore"

and "More-than-Moore" [4]), or finding other replaced technologies promising more scaling opportunities ("Beyond-CMOS" [2]), as shown in Fig. 1.1.

Figure 1.1 – Hierarchical organization and opportunites for CMOS and emerging technologies [5].

"Beyond CMOS" is the name of one of the seven focus groups in ITRS 2.0 and refers to the possible future digital logic technologies beyond the CMOS scaling limits, such as spin-based devices, ferromagnetic logic, and atomic switch. Until now, various kinds of "Beyond-CMOS" devices, including memory devices (MTJ [6–33], Ferroelectronic Field-Effect Transistor (FeFET) [34,35], Resistive Random-Access Memory (ReRAM) [36–38], Molecular memory [39,40], etc) and logic devices (Spin Field-Effect Transistor (Spin-FET) [41–43], Spin Wave Device (SWD) [44], Spin torque majority gate [45], All-Spin Logic (ASL) [46–59], Spin Torque Oscillator (STO) [60–62], etc), have been proposed, for their potential to overcome the power and performance limitations.

Among emerging memory devices, MTJ, which can store binary data based on Tunnel MagnetoResistance (TMR) effect [6,31,63], has been studied a lot since the main source of static power consumption in a computational system is the memory which must be maintained by an ongoing power supply. Besides being used as Magnetoresistance Random Access Memory (MRAM) [15, 16, 64, 65], MTJ is also used to combine with CMOS to establish hybrid MRAM/CMOS circuits [8, 24, 25, 66]. This type of circuits is proved to have high power efficiency. Moreover, the hybrid circuit overcomes the bottleneck of communications between memory and logic. Nevertheless, it is difficult to manage the power consumption caused by the frequent conversion between spin and charge. Moreover, from the perspective of design method, the hybrid circuits still belong in the category of CMOS design. Hence, to better exert the advantage of spintronic devices, some ASL devices are proposed, which use the pure spin current to transport information and thus lower power consumption caused by charge-spin commutation. It has been argued that ASL device could potentially lead to ultra low power switches since a stable nanomagnet with an activation barrier of 40  $k_BT$  could be switched with less than 1 aJ [57]. Under this circumstance, this thesis focus on the study of the ASL device.

### 1.1.2 Circuit and system

Speaking of the possible applications of emerging research memory and logic device, the envisioned applications can take many forms, according to ITRS 2011 [4]:

• as a drop-in replacement for conventional circuits,

- as supplemental devices that complement and coexist with CMOS devices,

- as devices whose unusual properties can provide unique functionality for selected information processing applications.

The aforementioned hybrid MRAM/CMOS circuits belong to the second possible application. The future trend will possibly focus on the first and the third possible applications, considering the scaling limitation of CMOS technology. ASL devices, which integrates the function of memory and logic, have the possibility to be used for new circuit/system design. Furthermore, the current superposition and switching threshold of ASL device impel their research in neuromorphic application [29,30,52,55,56,67–98], which is different with traditional Von Neumann machines [99,100] and attracts growing interest due to their potential to achieve human-like intelligence and low-power operation. Along with zero static power, low power consumption, high density, and non-volatility, ASL could provide a dominant implementation for future circuits and systems.

#### 1.2 Motivation

ASL device is first proposed in [46]. It is an emerging device that uses a pure spin current to transport information and can realize both memory and logic functions. It is argued that ASL device shows five essential characteristics for logic applications: concatenability, non-linearity, feedback elimination, gain and a complete set of Boolean operations [46]. Hence, along with the possibility to allow low-power and high-density operations, these advantages prompt the discussion of the ASL device in new Boolean computing and neuromorphic computing.

Nevertheless, the ASL research is still in its infancy. Its physical fundamentals – the spin injection/transport experiments begin at the end of the 20th century [101,102]. Most of these experiments prove the spin injection/transport phenomena and explore the enhancement of the injection/transport efficiency by using different materials and structures of single ASL device [22, 103–145]. By the time of debut of this thesis, there is few article exploring the possible applications of ASL on circuits and systems. While as an emerging device and different with CMOS, ASL needs to be explored to system level with a new design paradigm. This situation prompts us to study ASL in three levels: device, circuit, and system.

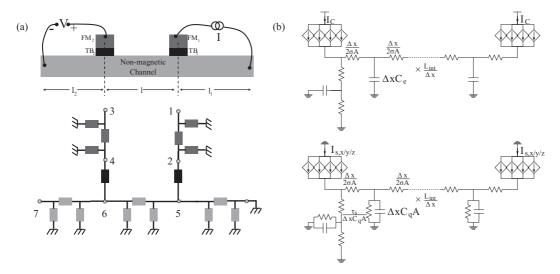

First and most basic, an electrical model is necessary to explore its possibility in circuits and systems, to fill the gap between application requirements at the system level and the circuit fabrication at the device level. Currently, some electrical models are proposed based on the spin-circuit concept by using MatLab [51, 54, 146–151]. However, these approaches are not scalable and cannot be used for complex circuits. Some electrical models [152, 153] use Verilog-A as the modeling language, yet cannot be used for circuit simulation because of the integration of the whole device into one block [152], or does not take into account the STT effect, the channel diffusion and breakdown current effects which are essential for delay calculation in circuit design [153]. Hence, an electrical model of ASL device, that allows the independent design of different parts, needs to be developed for circuit simulation and analysis.

In circuit level, the current addition or subtraction of ASL device shows the majority property [154]. The ASL circuit design is based on majority principle, which means a new design/synthesis method, unlike the AND/OR/Inverter (AOI) method [155], needs to be developed exploring the majority property. Moreover, to evaluate the performance of the circuits even the systems and to compare with CMOS based circuits, the benchmarking of ASL based circuits [156] also needs to be developed based on this new synthesis design method. Unlike the CMOS technology, which is fairly straightforward, the circuit design and the benchmarking of ASL are far more complicated. Many of the devices may perform computation utilizing different architectures, so it requires looking at not just the device but also the circuit implementation and in some cases even the specific application or computation

algorithm being implemented. Moreover, finding a quantitative set of metrics that can be used to contrast the devices and architectures is also necessary for circuit/system evaluation.

Moreover, as it is said that ASL device prompts the investigations of new computing, new computational architecture and relevant optimization methods need to be explored. How ASL device provides unique functionality in information processing applications is also one of the most promising topics.

## 1.3 Objectives and Methods

This section focus on the objectives and methods of our research, which aims to make progress of the synthesis methodology used in the framework of emerging computing technologies, here the ASL device. We approach this objective in three steps/levels: compact modeling for ASL device, ASL-based circuit design and system design/evaluation.

Based on the above-mentioned motivations, our goal of this thesis is divided into three parts: device, circuit and system level.

First, in device level, a compact model of ASL device needs to be developed in order to fill the gap between application requirements at the system level and the circuit fabrication at the device level. This compact model should achieve these following goals:

- Accurate simulations of spin injection/detection effects are needed to estimate the MTJ switching time, spin diffusion delay and the spin accumulation according to material properties.

- A scalable approach that allows the independent design of different parts, is mandatory to investigate the design of complex and hierarchical circuits. It is worth noticing that, to be adopted by the designer community, the approach should be compliant with current standardized CMOS-based design techniques and should be implemented in an existing commercial environment.

- The models should be generic to allow exploring fabrication-related device parameters such as channel lengths and MTJ sizes. Such exploration should allow investigating not only performances tradeoffs but should also help designers to prevent from device damages.

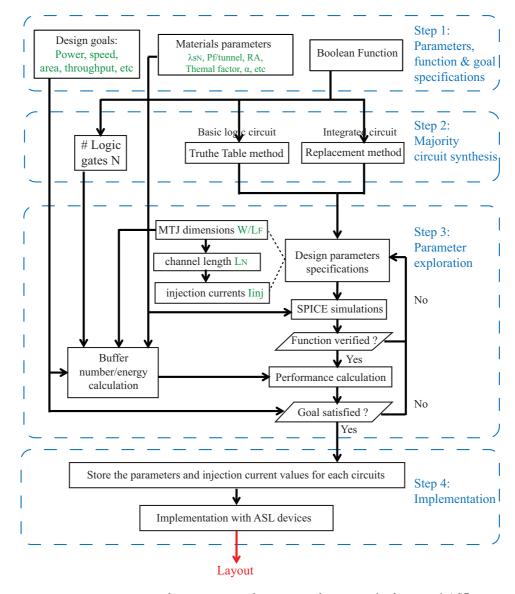

In circuit level, since ASL device follows the majority principle, this demands an entirely different design/synthesis method with that of CMOS. Hence, the most important is developing a methodology for ASL-based circuit design, approaching the circuit layout to the greatest extent possible. Moreover, considering the design/evaluation in system level and the comparison with CMOS technology, the benchmarking of these circuits is needed.

In system level, the main goal is to develop a method to evaluate the system performance based on the circuit benchmarking and to study the advantages of ASL devices and the possible optimizations compared with CMOS technology. The exploration in new computing, new computational architecture and relevant optimization methods is also inevitable.

The development of the compact model is the core of this thesis and is the foundation for circuit/system design and evaluation. According to our objective for ASL compact model, we use Verilog-A language [157], which is compatible with standard circuit simulation tools, to program our model. With Cadence platform, this model provides an easy parameter interface and can be divided and reorganized to implement different circuits. This allows cross-layer optimization of ASL-based circuits and eases the design of hierarchical circuits. The validation of this model is achieved by comparing with the experimental results extracted from published literatures.

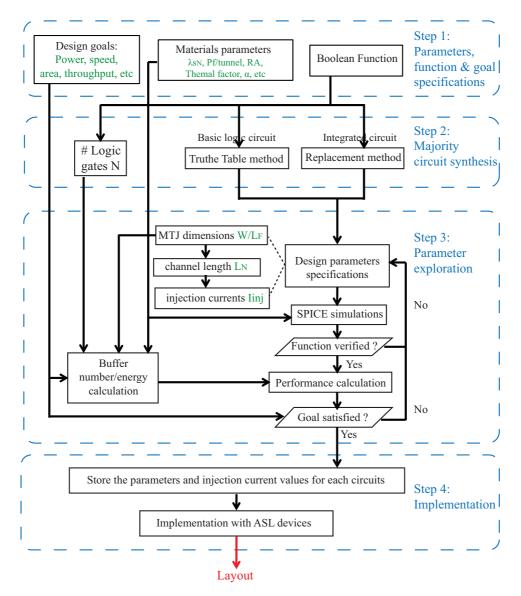

A circuit/system design methodology is developed combining with the majority synthesis methods. With circuit specifications and constraints, the circuit is implemented specifying the channel lengths and MTJ sizes, and its functional behavior is verified based on the

developed compact model. Moreover, basic circuits are implemented and benchmarked to build a library for system design/evaluation.

The system design and evaluation are based on the benchmarked circuit library, considering the gate interconnection distributions and the inserted buffer count. Moreover, the pipelining of ASL-based circuit/system is discussed to improve the performance, namely the throughout. Finally, the unusual property of ASL device induced by the majority functions, the reconfigurability, is introduced and prompts the application of ASL device in new computational architectures.

### 1.4 Research Contributions

In accordance with the goals of this thesis, the contributions have been made at three levels from the device modeling to the system architecture/application. The compact modeling of ASL device and circuit design methodology based on ASL are the cores of this thesis. The reconfigurability of ASL devices are discussed using the developed basic logic circuits. Based on the designed circuits and benchmarking, system design/evaluation methodology is developed, as well as the pipelining method.

#### 1.4.1 Compact modeling of All Spin Logic (ASL) device

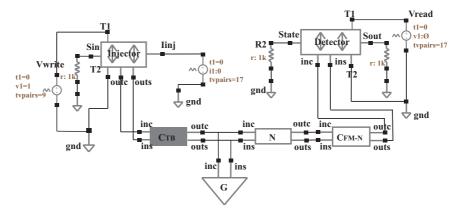

On the device level, this thesis develops a compact model of ASL device based on the spin-circuit concept with Verilog-A language on Cadence platform, which has an easy parameter interface. This compact model integrates the STT effect, the TMR effect, the spin injection/diffusion/accumulation effects and the channel breakdown current effect, which allows the investigation of the performance tradeoffs and also help designers to prevent from device damages. Furthermore, divided into six blocs: injector/detector F1/F2, channel N, ground G, interface C1/C2, this model allows the independent design of different parts and eases the design of hierarchical circuits.

Except for the compact modeling of ASL device, we also derived the equations of different performance criteria from the fundamental Maxwell's equations in the spin domain [148]. This would provide an insight into the circuit optimization and enables to discuss the experimental phenomena of the ASL device.

### 1.4.2 ASL based circuit design method

In circuit level, a circuit design methodology is developed. With the given parameters, the circuit specifications and constraints, the circuit is synthesized, implemented and laid out with optimized performance. The synthesis method defines the majority functions of the circuit: the "truth table" method in [154], or the "AOI replacement" method in [158]. With determinate majority functions, the circuit topology that yields minimum possible area is determined by exploring all possible layout topologies. Based on the chosen topologies, the MTJ sizes, the channel lengths and the injection currents are explored to implement the circuit and optimize the performance. Based on this methodology, combinational circuits are implemented and benchmarked, which form a circuit library for system design and evaluation. It is worth mentioning that for integrated circuit design, gate interconnection distribution and inserted buffer are considered to evaluate the performance more preciously.

### 1.4.3 System design & evaluation method

The design and evaluation of ASL device in system level are still in its infancy and there is not a suitable methodology for ASL-based system design. In this thesis, we use a cell-library approach to evaluate the ASL-based system. The system functionality is realized by replacing with the basic ASL-based combinational circuits; gate interconnection distribution

and inserted buffer count are calculated. With knowing the numbers and types of different basic circuits, the system performance can be calculated and optimized with different parameters of basic circuits. Moreover, for system optimization, we consider this from the original point of view of CMOS-based system: the pipelining and reconfigurability. A possible pipelining method is developed for the ASL-based system, by adding registers (MTJs) as latches between each stage like that in CMOS-based system. The reconfigurability is an inherent property of ASL device. By modifying the values and the polarities of the injected currents, the function of one ASL-based circuit can be changed.

## 1.5 Organization of the Thesis

The present thesis is divided into six chapters as follows.

This chapter presented the background, motivation, objectives and methods, and our contributions.

Chapter 2 reviews the state-of-the-art of MTJs and ASL devices. The basic principle, milestones in the development and the circuits/applications related to our work will be introduced.

Chapter 3 is the modeling part of our work. The physical and electrical models of MTJs and ASL device are presented. Moreover, the dependence of the performance criteria on different device parameters are derived and simulated, which helps the ASL-based optimization. The developed compact model is validated by comparing with the experiments of different materials and structures.

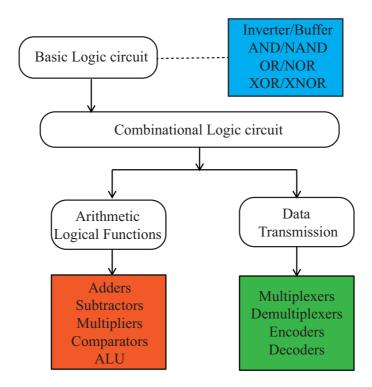

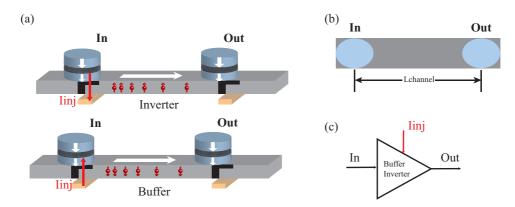

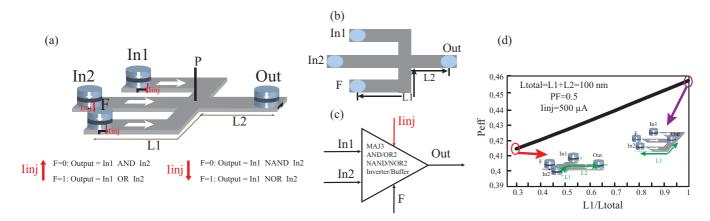

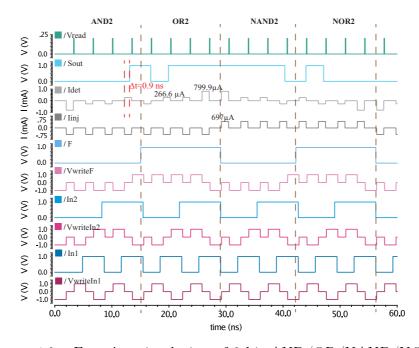

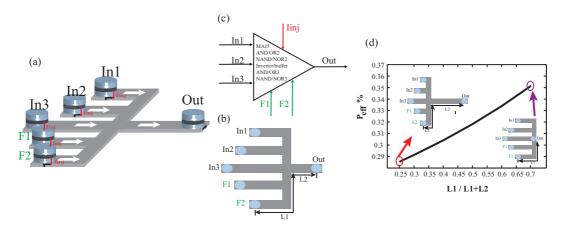

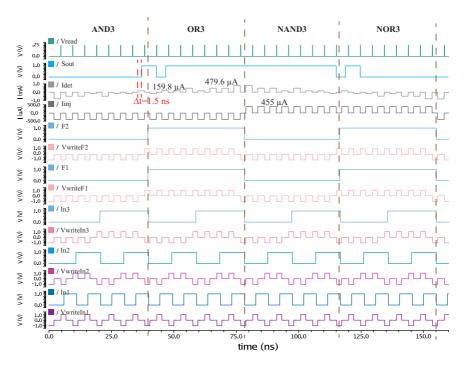

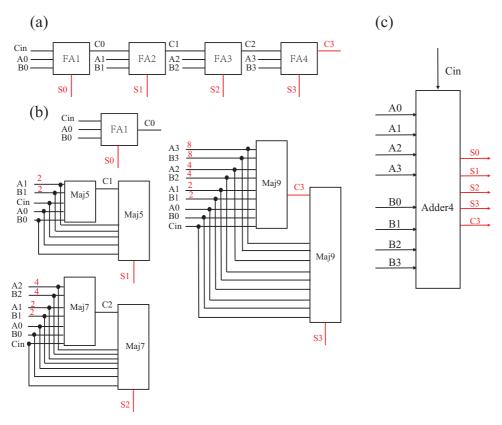

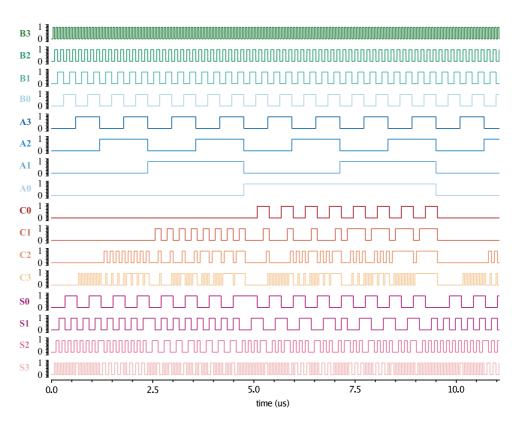

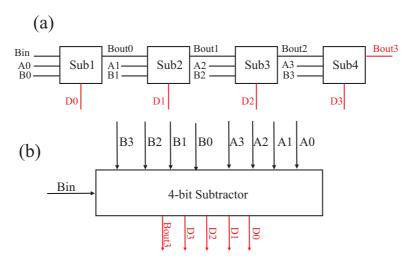

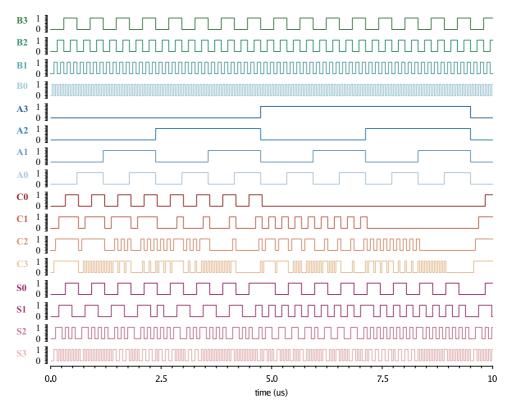

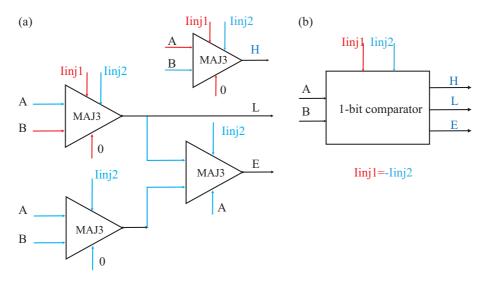

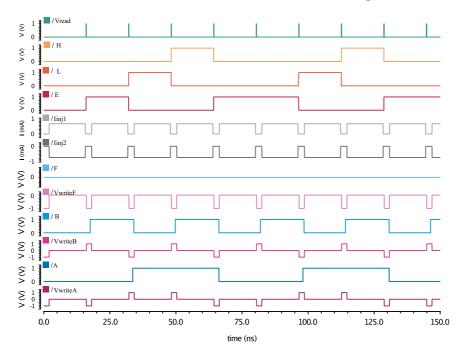

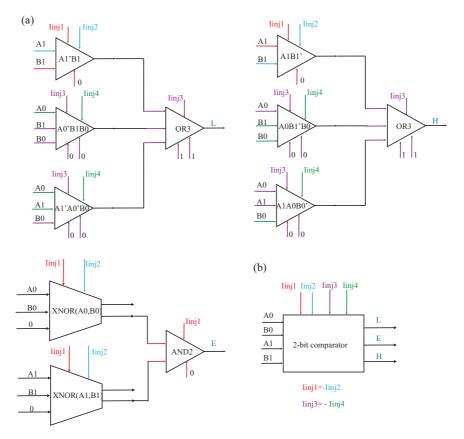

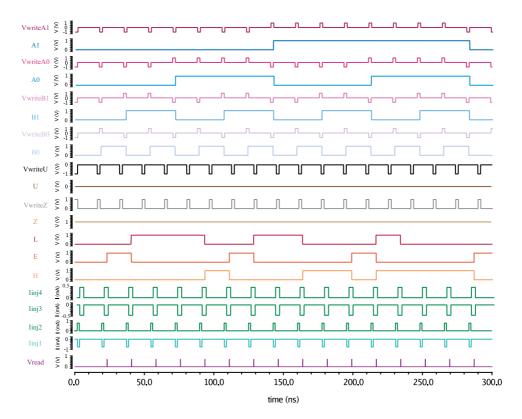

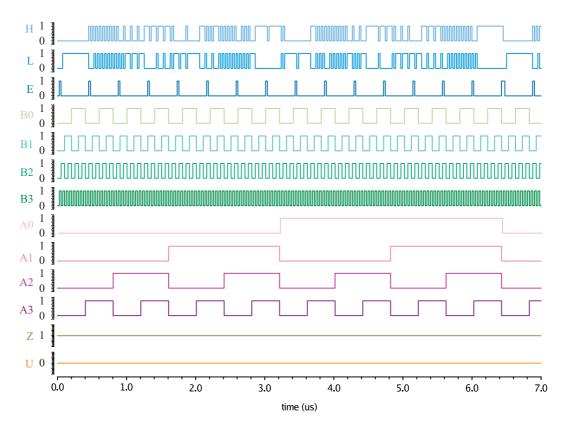

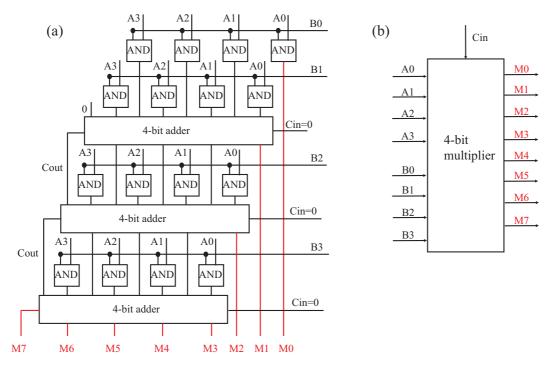

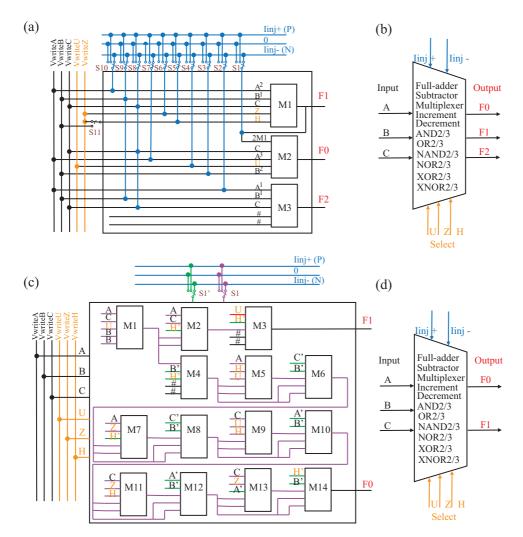

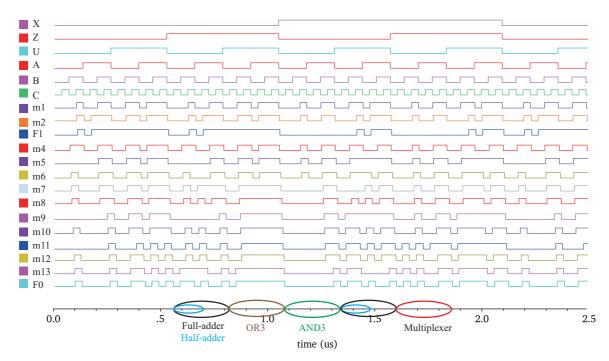

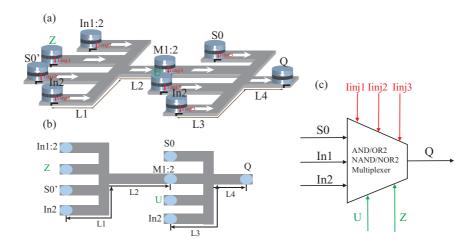

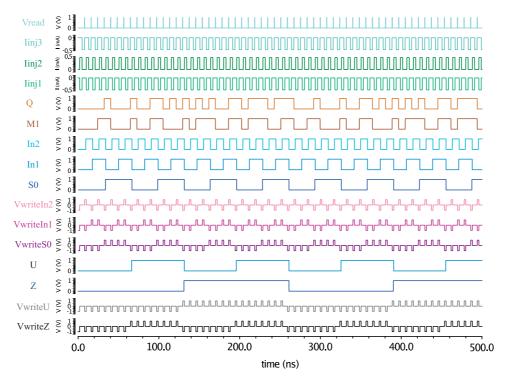

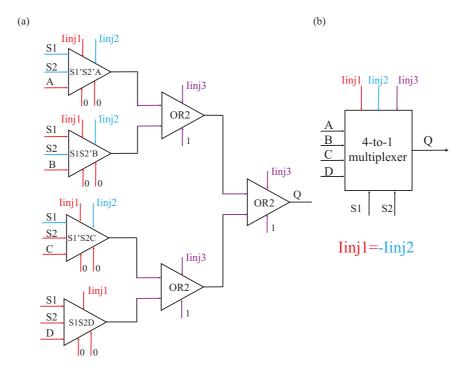

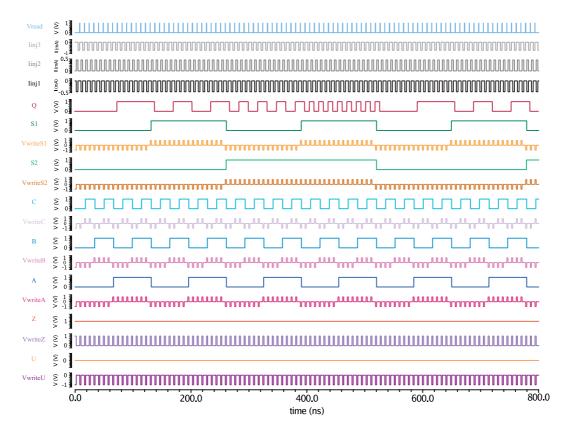

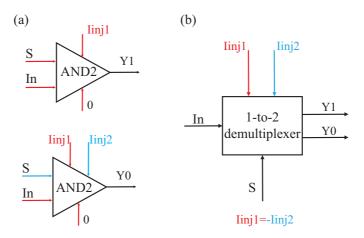

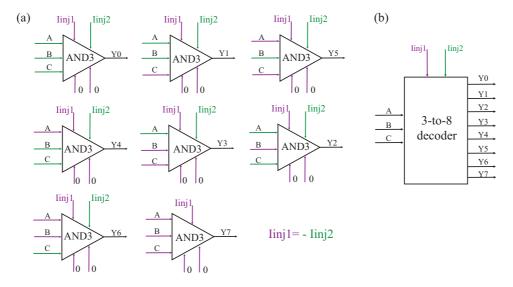

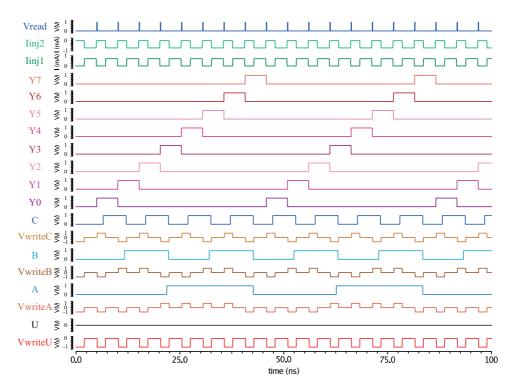

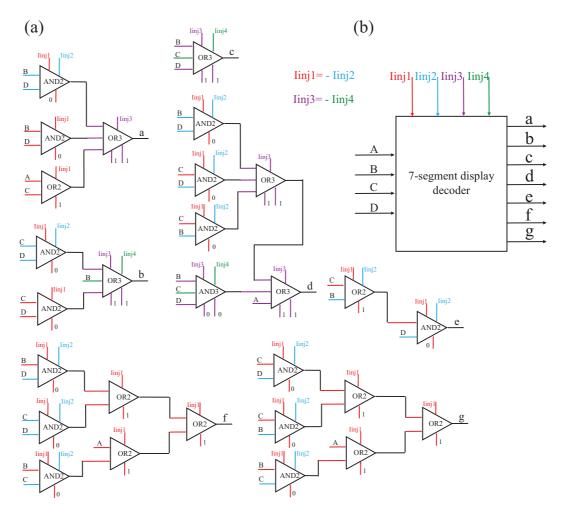

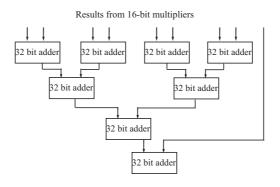

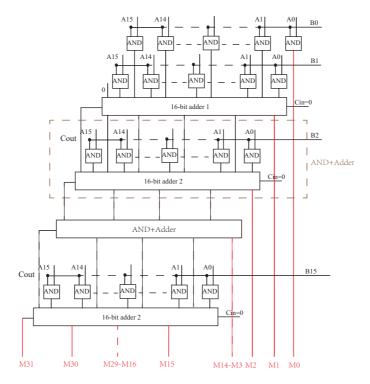

In chapter 4, we presents the ASL-based circuit design. A methodology of ASL based circuit design is developed, considering the current diffusion problems. Basic circuits, including Inverter/Buffer, AND/OR(NAND/NOR), Adder, Multiplexer (MUX) and Multiplier, and some combinational circuits are implemented and analysed based on this methodology. The benchmarking of these circuits are also evaluated, which is used for system evaluation.

Chapter 5 focus on the system level design and evaluation. The system performance is evaluated by using the cell-library approach based on the benchmarked circuit library in Chapter 4. Three high-level computing/system circuits: convolution circuit, and i7 system, are designed and evaluated as the examples. Moreover, we also initiate the research of the pipelining method and re-configurable properties of ASL-based circuits/systems, which are essential for performance optimization of a system.

Chapter 6 concludes the thesis and presents some perspectives.

## Chapter 2

## State-of-the-art

| 2.1.   | Structure and working principle    |

|--------|------------------------------------|

| 2.1.2  | MTJ fundamental and development    |

| 2.1.   | Memory and circuit applications    |

| 2.2 Al | Spin Logic (ASL) Device            |

| 2.2.   | Structure and working principle    |

| 2.2.2  | ASL fundamental and development    |

| 2.2.   | ASL modeling and benchmarking      |

| 2.2.4  | ASL circuit and system application |

|        | mmary                              |

#### 2.1 MTJs

### 2.1.1 Structure and working principle

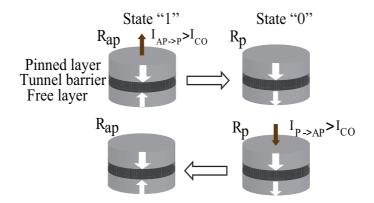

The basic structure of MTJ is shown in Fig. 2.1. It is composed of an insulating barrier sandwiched by two Ferromagnetic (FM) layers. The insulating barrier can be CuO [159], CoO [160], ZnO [161], NiO [162,163],  $TiO_2$  [164], MgO [21,165,166],  $Al_2O_3$  [167,168],  $SiO_2$ , or manganites [169,170], and needs to be enough thin to guarantee the electron tunneling effect. One FM layer is magnetically pinned, called pinned layer, whereas the other one, is called free layer, whose magnetization can be switched by a magnetic field or an enough large current based on the STT effect [171,172]. Depending on the relative magnetization orientations of these two FM layers, i.e. Parallel (P) or Anti-parallel (AP), one MTJ can have two resistance states:  $R_P$  or  $R_{AP}$  where  $R_P < R_{AP}$ , which is also named Tunnel MagnetoResistance (TMR). The relative change of these two resistances is the primary performance metric of an MTJ. It is usually named TMR ratio and defined as:

$$TMR \quad ratio = \frac{R_{AP} - R_P}{R_P} = \frac{G_P - G_{AP}}{G_{AP}} \tag{2.1}$$

### 2.1.2 MTJ fundamental and development

In this subsection, we will present the fundamental effects of MTJ: TMR effect and STT effect and outline some crucial progress in their enhancements, including the scaling effect. Moreover, two types of Multi-Level (ML) MTJs are presented, which will enlighten the research on neural network.

Figure 2.1 – Two Magnetic Tunnel Junction (MTJ) states with different resistances based on Tunnel MagnetoResistance (TMR) effect: Parallel ( $R_P$ , state "0") and Antiparallel ( $R_{AP}$ , state "1"); If the current flows from the free layer to the pinned layer and is larger than the critical current  $I_{c0}$ , the state will be switched to Parallel; on the contrary, the state will be switched to Anti-parallel.

#### 2.1.2.1 TMR effect

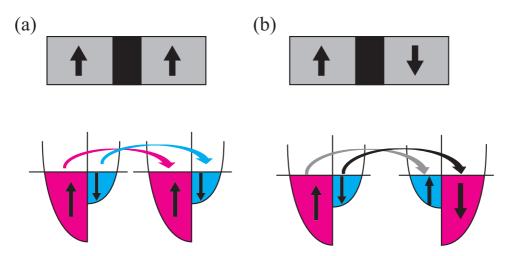

The origin of TMR arises from the difference in the electronic density of states (DOS) at the Fermi level  $E_F$  between spin-up  $N_{\uparrow}$  and spin-down  $N_{\downarrow}$  electrons. The tunnel conductance is proportional to the product of DOS of the two FMs with same spin orientation, and is given by  $N_{1\uparrow}N_{2\uparrow} + N_{1\downarrow}N_{2\downarrow}$ .

An intuitive figure of tunneling process explained above is shown in Fig. 2.2. As shown in this figure, an electron tunnels to the spin subband of the same spin orientation, i.e. spin-up to spin-up and spin-down to spin-down. A change from the parallel configuration (2.2(a)) to the antiparallel configuration (2.2(b)) of the magnetizations of two FM layers results in an exchange of the spin subband, causing a corresponding change in resistance/conductance and thus giving rise to TMR ratio.

Figure 2.2 – A schematic of tunneling process of MTJ, electron spin orientation is preserved while traveling from one FM layer to another. (a) Parallel configuration; (b) Anti-parallel configuration.

To calculate the TMR ratio, the resistance/conductance of parallel and anti-parallel states need to be calculated based on Eq. 2.1.

The MTJ resistance/conductance depends on the relative magnetic orientations of two FM layers. Supposing that the angle between these two magnetization orientations is  $\theta$ , the conductance of MTJ is given by [173]:

$$G(\theta, T, V) = G_T(T, V)(1 + P_1 P_2 cos\theta) + G_{ie}(T)$$

(2.2)

where  $G_T$  is the tunnel conductance [12,174–176], which depends on the bias voltage V of the junction and on its temperature T;  $G_{AP}$  and  $G_P$  correspond with  $\theta = 180^{\circ}$  and  $\theta = 0^{\circ}$ .  $P_1$  and  $P_2$  are the polarizations of the first and second FM layer and defined as:

$$P = \frac{N_{\uparrow} - N_{\downarrow}}{N_{\uparrow} + N_{\downarrow}} \tag{2.3}$$

The dependence of  $G_T$  upon the temperature T is given by Stratton model [174]:

$$G_T(T, V) = G_T(0, V) \frac{\lambda T}{\sin(\lambda T)} + G_{ie}(T)$$

(2.4)

where the constant  $\lambda$  is given by  $\lambda = (\pi t_{ox} k/)$ ,  $t_{ox}$  is the oxide thickness, k the Boltzmann constant, h the reduced Plank constant,  $m_e$  the electron mass and e its charge,  $G_{ie}(T)$  is a second term of inelastic conductance to describe the thermal variations in the conductance and is given by  $G_{ie}(T) = \tau_n T^{\beta}$ ,  $\tau_n$  is a material dependent constant and  $\beta$  depends on the number of states occupied by the electrons when traversing the tunnel barrier. For a second order system,  $\beta = \frac{4}{3}$ .

The voltage dependence of the conductance is given by Brinkman model [175] and Simmons model [177]:

$$G_T(0, V) = G_T(0, 0)(1 - 2\beta V + 3\delta V^2)$$

$$G_T(0, 0) = k_0 k_1 A \frac{\sqrt{\phi}}{2t_{ox}} e^{-k_1 t_{ox} \sqrt{\phi}}$$

(2.5)

where  $G_T(0, V)$  is the tunnel conductance at 0 K and  $G_T(0, 0)$  is the tunnel conductance at 0 V, 0 K.  $\beta$  is given by  $e\sqrt{2m_e}t_{ox}d\phi/(24\hbar\phi^{3/2})$ ,  $\delta$  is given by  $e^2m_et_{ox}^2/(12\hbar\phi)$ ,  $k_0=e^2/(2\pi h)$ ,  $k_1=4\pi\sqrt{2m_e}e/h$ ,  $\phi$  is the height of the tunnel barrier,  $d\phi$  the barrier asymmetry and A the surface of the junction.

TMR effect is first measured by Julliere in 1975 [173], with a maximum measured value of 14% in Fe-Ge-Co junctions at 4 K. The observed value, however, were rather small and cannot be applied in practice. The above equations show that the TMR depends on the DOS or the spin polarization coefficient P. This means realistic electronic structures and disorder at interfaces exert a large effect on TMR. Hence, over the following decades, researches on these factors flourish to get a larger TMR. In 1995, a large TMR of 18% at room temperature was reported for  ${\rm Fe}/Al_2O_3/{\rm Fe}$  [178]. Then the research on aluminum oxide barrier yields a steady increase in TMR ratio by improving the spin polarization and fabrication. In 2004, a TMR of 70.4% measured at room temperature is reported in [179] using a  ${\rm CoFeB}/AlO_x/{\rm CoFeB}$  junction. In 2001, a series of theoretical calculations predicted high TMR ratios for  ${\rm Fe}/{\rm MgO}/{\rm Fe}$  MTJs [180] [181], where the tunnel barrier is a crystalline MgO layer with (001) texture. The MgO has attracted new research attention. So far, TMR ratio as high as 604% has been reported in a  ${\rm CoFeB}/{\rm MgO}/{\rm CoFeB}$  MTJ [182]. There is no doubt that the research on improving TMR ratio will continue by exploring different materials/structures like the half-metals [43, 183] with extremely high spin polarization.

#### 2.1.2.2 STT effect

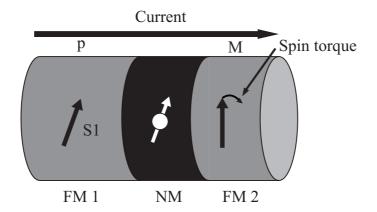

As said above in subsection 2.1.1, the magnetization orientation of FM free layer can be switched by applying a magnetic field or a current based on STT effect. As shown in Fig. 2.3, when a current is passing through this device, electrons are first polarized with the magnetization orientation of FM1 and then injected into FM2 through NM. The spins of the injected electrons interact with that in FM2 by exchange interaction and exert torque. If there is enough torque, the magnetization orientation in FM2 will be reversed. The dynamic of the magnetic switching can be explained by Landau-Lifschitz-Gilbert (LLG) equations [184], which includes a STT term:

$$\frac{d\overrightarrow{M}}{dt} = \overbrace{-\gamma_0 \overrightarrow{M} \times \overrightarrow{H_{eff}}}^{EffectiveFieldTorque} + \overbrace{\frac{\alpha}{M_s} \overrightarrow{M} \times \frac{d\overrightarrow{M}}{dt}}^{GilbertDamping} + \overbrace{\frac{STT}{T_{CIP/CPP}}}^{STT}$$

$$T_{CIP} = -(\mu \cdot \nabla)M + \frac{\beta}{M_s} \times [(\mu \cdot \nabla)M]$$

$$T_{CPP} = g(\theta) \frac{\sigma I}{M_s} M \times (p \times M)$$

(2.6)

where the first term is the effective field torque; the second is Gilbert damping; and the third is the spin-transfer torque, which is different depending on the geometries: Current In Plan (CIP) or Current Perpendicular to plan (CPP).

Figure 2.3 – Schematic illustration of Spin Transfer Torque (STT) effect in a magnetic nanopillar consisting of two Ferromagnetic (FM) layers (FM1/2) switching a non-magnetic layer (NM).

Compared to CIP, CPP has several advantages, which is the main research point of MTJ in recent years. First, the magnetic anisotropy of the MTJ is directly related to the thermal stability and data retention. In-plan anisotropy mainly originates from the shape anisotropy. Thereby an elongated cell surface and a thin thickness are required to provide enough thermal stability. With the shrinking of the MTJ size, the in-plan-anisotropy MTJ has difficulty in maintaining the satisfying thermal stability. The perpendicular anisotropy MTJ has no requirement for the elongated shape and thus can overcome this issue. Second, the perpendicular MTJ is more suitable for the STT switching than the in-plan MTJ. It is explained as follows. The critical current  $(I_{c0})$  for the STT switching can be derived from the LLG equation.

For in-plan MTJ, it is expressed as:

$$I_{c0\parallel} \simeq \alpha \frac{\gamma \mu_0 e}{\mu_B P} M_s V_F [H_{k\parallel} + \frac{M_s}{2}]$$

(2.7)

where  $\mu_B$  is the Bohr magneton,  $V_F$  is the free layer volume,  $H_{K\parallel}$  is the uniaxial in-plan anisotropy field. The energy barrier of thermal stability (E) of the in-plan MTJ is given by:

$$E_{\parallel} = \frac{\mu_0 M_s H_{K\parallel} V_F}{2} \tag{2.8}$$

The comparison between Eqs. 2.7 and 2.8 indicates that the STT must overcome additional field  $M_s/2$  which makes no contribution to the thermal stability. But in a perpendicular MTJ, the critical current is proportional to the thermal stability, expressed as:

$$I_{c0\perp} \simeq \alpha \frac{\gamma \mu_0 e}{\mu_B P} M_s V_F H_{k\perp} = 2\alpha \frac{\gamma e}{\mu_B P} E_{\perp}$$

(2.9)

Therefore perpendicular MTJ requires lower write current given the same thermal stability, thus lower power consumption.

The perpendicular MTJ was experimentally demonstrated for the first time in 2002, with a TbFeCo/CoFe/ $Al_2O_3$ /CoFe/GdFeCo structure and a TMR ratio of 55% [185]. In the past decade, much effort has been made to get higher TMR, lower power consumption and higher density, either in new materials research or dimension scaling [13,15,16,32,33,65,186–190]. Now high TMR ratio (120%), small area and low write current (49  $\mu$ A) can be achieved [22].

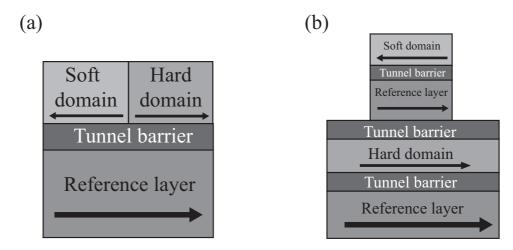

#### 2.1.2.3 Multi-layer MTJs

To improve the storage density and scalability of MTJs in STT-RAM, ML MTJ is proposed [10,11], which can store multi-bit data per cell. Two types of ML MTJ structures are proposed: parallel and series, as shown in Fig.2.4. A 2-bit parallel ML MTJ is shown in Fig. 2.4(a). It is composed of one single MTJ whose free layer has two domains. These two domains switch at different spin-polarized currents and form different resistance levels with the reference layer. For the 2-bit series ML MTJ shown in Fig. 2.4(b), it is composed of two vertically stacked single MTJs that have different TMR ratios. Multiple resistance levels can be achieved with different magnetization configurations of the two MTJs.

Figure 2.4 – Two different structures of 2-bit Multi-layer MTJ (ML MTJ). (a) parallel ML MTJ; (b) series ML MTJ.

So far, the two structures are designed and fabricated and the spin transfer switching is demonstrated [11, 191, 192] by using different currents based on the access scheme [10, 193]. The impacts of the process variations and the thermal fluctuations on the performance and reliability are also analyzed [10] and prove their feasibility. Now, ML MTJs are used as a processor's caches [194, 195] or for fast local checkpointing in computing systems [196].

Another possible application domain of ML MTJs is neuromorphic. Theoretically, arbitrary numbers of bits, if we stack multiple MTJs vertically and carefully chose the switching currents, can be stored in one ML MTJ cell. This prompts its possibility as synapse in a deep neural network, combined with a learning diagram with integer weights. The compact modeling developed in [27] will further facilitate this possible application.

### 2.1.3 Memory and circuit applications

Due to its non-volatility, MTJs provide a new route to the next generation memories and logic circuits. So far, MTJ-based memory, i.e. MRAM, has been widely explored and produced commercially. Moreover, its possible application in neuromorphic is also explored based on its memristive property and two-states representation. This subsection will review these applications.

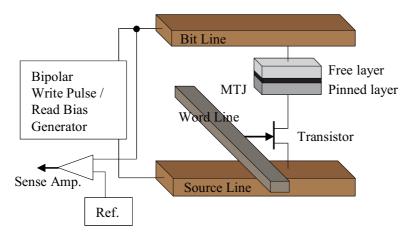

#### 2.1.3.1 Memory

The discovery of TMR at room temperature and higher value prompts MTJ in memory applications. One of the first working MRAMs, using the magnetic field for writing, was developed at IBM in 2000 [197]. Then the development of spin transfer switching represented a huge step forward for MRAM perspective. One schematic of STT-RAM is presented in Fig. 2.5 as 1T1R (one transistor and one resistor) form. The word line is connected to the gate of a transistor which is used to select the MTJ to be written or read. The writing is done through spin transfer switching by applying either a positive or a negative voltage pulse between the source line and the bit line. The reading is done by applying a weaker voltage to the bit line to sense the resistance of MTJ.

Figure 2.5 – Schematic of 1T1R memory cell [198].

Recently, a 64 Mb SPI/DDR4 chip is fabricated by Avalanche Technology using 55 nm CMOS technology, achieving a read raw (Bit Error Rate (BER)) below 10<sup>-7</sup> [64]. Many studies on the failure analysis [199, 200], stability [200], power and delay [14, 201] have been carried on.

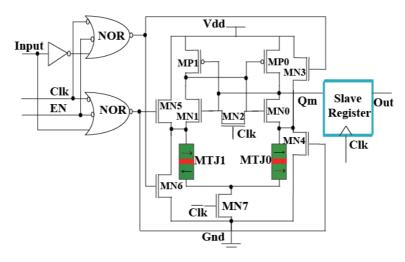

#### 2.1.3.2 Logic circuits

Another possibility of MTJ is the application for logic circuits. The most mature one is the hybrid MRAM/CMOS circuit [202]. Such a circuit contains both MTJs and CMOS transistors. The logic functions are still provided by CMOS transistors, but the MTJs provide enhanced functionalities such as instant on/off or enhanced radiation hardness. The realized hybrid circuits contain the flip-flop [203,204](Fig. 2.6), full-adder [20,205], sensing amplifier [66] and magnetic FPGA [206, 207]. The other approach for logic circuits is using magnetic interactions between magnetic nanostructures. Full logic functions (AND, OR, NAND, NOR, XOR, and XNOR) can be realized [28, 208, 209].

#### 2.1.3.3 Neural network

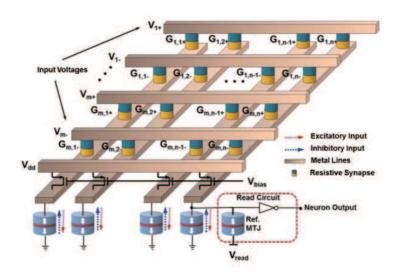

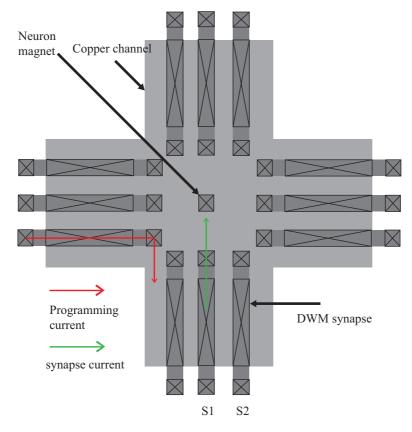

Neuromorphic computing has emerged as a future computing architecture due to its possibility of allowing low power consumption. CMOS based neural networks have been studied. However, the complexity of neural network prompts the research on nanodevices, considering the scaling limit of CMOS technology. MTJ is one of the possible devices, which can act both synapses and neurons in a neural network.

The neuron property originates from the thresholding operation during the switching of MTJ states [210]. Fig. 2.7 shows a crossbar neuromorphic architecture consisting of programmable resistive synapses and the MTJ neuron [29]. The synapses generate the excitatory/inhibitory charge current, inputting to the MTJ neuron and switching the neuron states.

Figure 2.6 – Schematic of Spin-MTJ based Non-Volatile Flip-Flop [203].

Figure 2.7 – Neuromorphic architecture based on "STT-Neuron" [29].

A MTJ can be a synapse in three ways: intrinsic non-volatile memory property representing integral weights, stochastic [211] and memristive [73,98,212,213] properties representing continuous weights. To represent integral synaptic weights, single MTJ can be used to represent binary (0, 1) [80,82,214,215] or ternary number (-1, 0, +1) [216] by adjusting the MTJ states and the input current values. The recent discovery of ML MTJ provides the possibility of representing arbitrary integral numbers even floating numbers if the function of each MTJ is well defined. The single MTJ with intrinsic stochastic property is proposed [211] to implement learning-capable synapses, giving an insight into a new way to use memory nanodevices. The most popular way of using MTJ as synapse is as a memristor, with the discovery of simultaneous occurrence of TMR and Resistive Switching (RS), a displacement of oxygen vacancies located at the interface. By applying several voltage pulses, the resistance of the AP or P state will be periodically switched between a High Resistance State (HRS) and a Low Resistance State (LRS). The resistance depends on the flux  $\Phi$ , which is defined as  $\Phi(t) = \sum_{i=0}^{n} v_i t_i$ , with  $v_i$  and  $t_i$  the voltage and duration of the *i*th pulse, respectively. Many oxides can exhibit memristive switching behavior, including Magnesia (Mg) [213,217], Barium Titanate (BTO) [218] and Tantalum Oxide  $(Ta_xO_x)$  [219]. Researches on new materials keep going to improve the resistance change and to improve the reliability and the robustness.

## 2.2 All Spin Logic (ASL) Device

#### 2.2.1 Structure and working principle

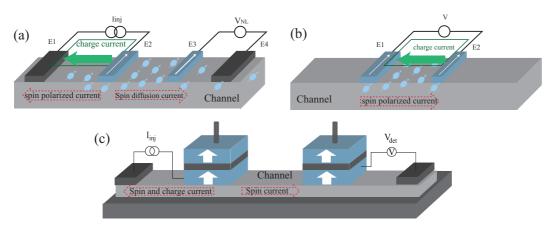

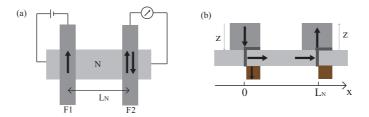

The fundamental of the ASL device is the spin injection/detection. To perform electrical spin injection into spin channel, two types of measurement known as "non-local" [101, 102, 117, 220, 221] and "local" [220, 222, 223] have been commonly used, as shown in Fig. 2.8 (a) and (b). For non-local measurement, a current source is applied between the electrodes E1 and E2, where E2 serves as the injector where charge current injected spin current through. After spin injection, the spin current in the channel underneath E2 is able to diffuse in both directions, towards E1 (as a spin current with a charge current) and E3 (spin current mostly). The spin is then detected by measuring the voltage across E3 and E4, where E3 (FM) is the spin detector. This measurement is called non-local because the voltage probe lies outside the charge current loop; This geometry allows the voltage to detect the spin density at E3 arising from the pure spin current of diffusion of spin-polarized electrons. The measured voltage  $V_{NL}$  is positive or negative depending on whether the magnetization configurations of E2 and E3 are parallel or antiparallel to each other. The difference between these two voltages is the non-local spin signal, and it is often converted to units of resistance by dividing out the injection current,  $I_{inj}$ , as  $\Delta R_{NL} = (V_{NL}^P - V_{NL}^{AP})/I_{inj}$ .

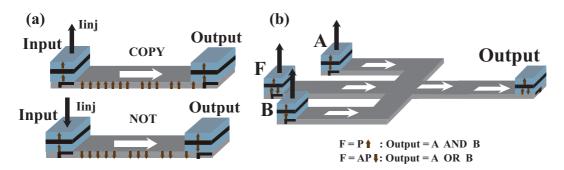

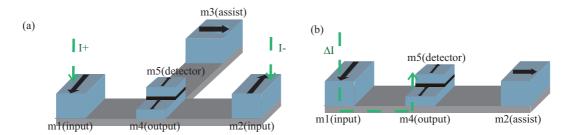

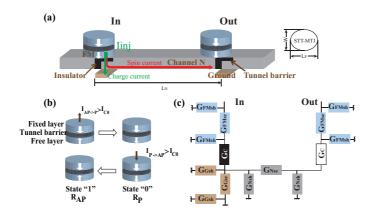

Figure 2.8 – Spin valve structure. (a)non-local spin valve; (b) local spin valve; (c) Schematic of All Spin Logic with perpendicular MTJs.

The local measurement directly measures the standard two-terminal resistance across two FM electrodes (E1 and E2) as shown in Fig. 2.8(b). Spin-polarized electrons are injected from one electrode, transported across the channel, and detected by the second electrode. The difference in the resistance between the parallel and antiparallel magnetization alignments of the two electrodes is the local magnetoresistance which is the signal of spin transport.

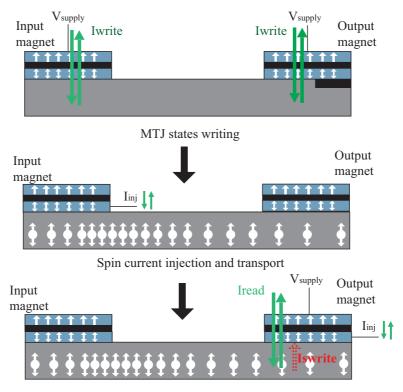

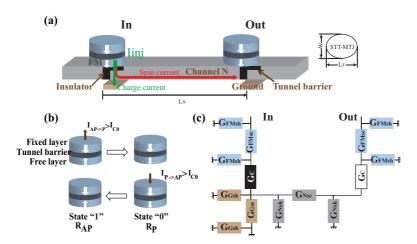

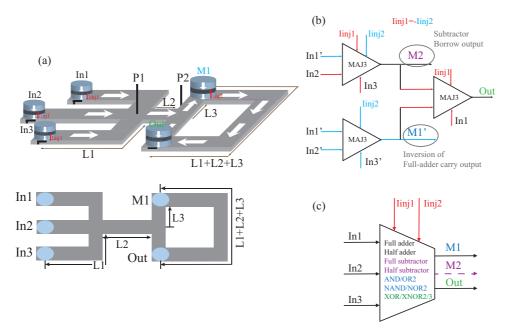

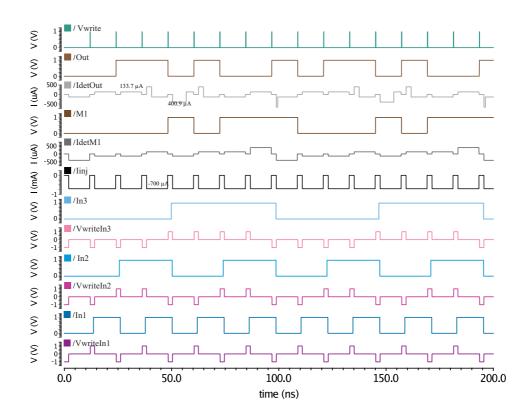

ASL device is a non-local spin valve device which can perform logic functions by combinations. There are several types of ASL devices: ASL with No Clock (ASLNC), ASL with Clock (ASLC), ASL with Clock with Biaxial anisotropy (ASLCB) [58] and Graphene based All Spin Logic Gate (G-ASLG) [152]. Fig. 2.8 (c) shows a typical ASL device. It is composed of two MTJs as the memories and injector/detector, and one channel for spin transport. Fig. 2.9 shows the working flow of the ASL device. First, a voltage/current source  $V_{supply}/I_{write}$  is applied to the write the MTJs. When the writing process finished, a charge current  $I_{inj}$  is injected into the channel through the free layer of MTJ injector, and polarized into spin currents whose magnetization orientation depends on the MTJ free layer magnetization orientation and the injection current polarity. The spin current in the channel diffuses in both directions: MTJ detector and input electrode. The spin current flowing into the MTJ detector will switch the state of the detector if enough torque is applied according to STT effect. The switched state can be read by applying a read voltage/current  $I_{read}$  and depends on the MTJ free layer magnetization orientation and the injected current polarity.

Spin current detection and MTJ state switching/reading

Figure 2.9 – ASL working flow. Step 1 : MTJ states writing with an applied voltage/current  $I_{write}$ ; Step 2: Spin current injected with a charge current  $I_{inj}$  injected and polarized through the MTJ free layer to the channel; Step 3: Output MTJ state switched with the injected and diffusive spin current; MTJ state read with an applied voltage/current  $I_{read}$

#### 2.2.2 ASL fundamental and development

#### 2.2.2.1 Spin injection/detection and transport

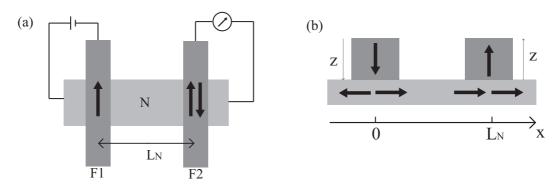

To describe the spin injection/detection fundamental [148], we use the non-local structure in Fig. 2.10. Two ferromagnetic magnets are on top of a nonmagnetic conductor, separated by a distance of  $L_N$ . Spin is injected into N from F1 and a part of spin current flows towards F2, which is indicated in Fig.2.10(b).

In this case, we suppose that the spin current in F1, F2 and N are one-dimensional. The boundary conditions in infinities are:

$$\mu_{sN}(\pm \infty) = \mu_{sF1}(-\infty) = \mu_{sF2}(\infty) = 0$$

(2.10)

Figure 2.10 – (a) Non-local geometry for spin injection and detection. (b) Cross view of the non-local geometry.

The charge and spin currents are presented in spin domain and expressed as:

$$j = j_{\uparrow} + j_{\downarrow} = \sigma \nabla \mu + \sigma_s \nabla \mu_s$$

$$j_s = j_{\uparrow} - j_{\downarrow} = \sigma_s \nabla \mu + \sigma \nabla \mu_s$$

(2.11)

where  $j_{\uparrow/\downarrow}$  is the electric current carried by spin up/down electrons,  $\mu(\mu_s)$  is the quasichemical charge(spin) potential,  $\sigma(\sigma_s)$  is the charge(spin) conductivity and are expressed as:

$$\begin{aligned}

\sigma &= \sigma_{\uparrow} + \sigma_{\downarrow} \\

\sigma_{s} &= \sigma_{\uparrow} - \sigma_{\downarrow}

\end{aligned} (2.12)$$

Based on Eqs. 2.11 and 2.12, the spin currents at the contact and through the spin-polarizing contact C1 are:

$$j_{sF1}(0) = jP_{\sigma F1} + \frac{1}{R_{F1}}\mu_{sF1}(0)$$

$$j_{sC1} = jP_{\Sigma 1} + \frac{1}{R_{C1}}[\mu_{sN}(0) - \mu_{sF1}(0)]$$

(2.13)

where  $P_{\sigma F1/\Sigma 1}$  is the conductivity spin polarization in F1/C1 and expressed as  $P_{\sigma} = \frac{\sigma_{\uparrow} - \sigma_{\downarrow}}{\sigma_{\uparrow} + \sigma_{\downarrow}} = \frac{\sigma_{s}}{\sigma}$ ,  $R_{F1/C1}$  is the spin resistance of F1/C1 and expressed as  $\frac{\sigma}{4\sigma_{\uparrow}\sigma_{\downarrow}}$ .

The spin current at x = 0 diffuses towards two directions, and expressed as:

$$j_{sN}(0+) = \frac{1}{R_N} \left[ -\mu_{sN}(0) \coth(L_N/\lambda_{sN}) + \frac{\mu_{sN}(L_N)}{\sinh(L_N/\lambda_{sN})} \right]$$

$$j_{sN}(0-) = \frac{1}{R_N} \mu_{sN}(0)$$

(2.14)

where  $R_N$  is the spin resistance of the channel,  $L_N$  is the channel length,  $\mu_{sN}(0/L_N)$  is the spin quasichemical potential at  $x = L_N$  and  $\lambda_{sN}$  is the spin diffusion length of the channel.

The continuity of the spin current in the injector gives:

$$j_{sN}(0+) = j_{sN}(0-) + j_{sC1} = j_{sN}(0-) + j_{sF1}$$

(2.15)

The same procedure for the detector, the spin currents at the contact and the channel, the continuity of spin currents are expressed as:

$$j_{sF2}(0) = -\frac{1}{R_{F2}} \mu_{sF2}(0)$$

$$j_{sC2} = \frac{1}{R_{C2}} [\mu_{sF2}(0) - \mu_{sN}(L_N)]$$

$$j_{sN}(L_N -) = \frac{1}{R_N} [-\frac{\mu_{sN}(0)}{\sinh(L_N/\lambda_{sN})} + \mu_{sN}(L_N) \coth(L_N/\lambda_{sN})]$$

$$j_{sN}(L_N +) = -\frac{1}{R_N} \mu_{sN}(L_N)$$

(2.16)

The continuity of spin currents in the detector is:

$$j_{sN}(L_N -) = j_{sN}(L_N +) + j_{sC2} = j_{sN}(L_N +) + j_{sF2}(0)$$

(2.17)

The detected voltage  $V_{det}$  is expressed as:

$$V_{det} = \mu_N(\infty) - \mu_{F2}(\infty)$$

$$= -(R_{C2}P_{\Sigma 2} + R_{F2}P_{\sigma 2}) \frac{\mu_{sN}(L_N)}{R_{C2} + R_{F2}}$$

(2.18)

where  $\mu_{sN}(L_N)$  can be extracted from Eqs. 2.15 and 2.17.

The detected voltage  $V_{det}$  is in general positive for parallel and negative for antiparallel magnetization orientations. Often what is detected is the nonlocal resistance  $\Re_{nl}$ , which is expressed as:

$$\Re_{nl} = V_{det}/j \tag{2.19}$$

or the corresponding difference in the nonlocal resistance for parallel and antiparallel orientations of F1 and F2:

$$\Delta \Re_{nl} = \Re_{nl}^{\uparrow\uparrow} - \Re_{nl}^{\uparrow\downarrow} \tag{2.20}$$

#### 2.2.2.2 ASL development

Johnson and Silsbee [101] first reported that nonequilibrium spin injected from a ferromagnet diffuses into an Al film over the spin diffusion length of the order of 1  $\mu m$  in 1985. During the following two decades, researchers mainly devoted to finding an efficient way to inject and detect the spin signal and the fabrication of spin valve devices. Only until 2010 [46], the application of spin valve in logic, is proposed by Behtash Behin-Aein, with a device named as All Spin Logic Device. In this proposal, the in-plan MTJs are used as the injector/detector. In the previous section, we have explained that the perpendicular MTJ consumes less power. Due to this advantage, the structure with perpendicular MTJs is proposed in [152].

As we explained in the previous subsection, the charge current will be injected into the channel and be polarized into a spin current, which will switch the MTJ state if enough torque is applied. Hence, the value of spin current into the detector is the most important criterion of an ASL device, which is directly related to the spin injection efficiency and the detected non-local resistance. Hence, to improve the detected spin current, the spin injection efficiency and the non-local resistance should be improved.

One way to improve the spin injection efficiency focus on the materials, which could once more be divided into two directions: finding new materials and improving the material quality. The researches on new materials concerns about both FM electrodes and channel. The basic idea for FM electrode material research is looking for a material with high spin polarization, since it is related to how many spins will be polarized into the channel. The halfmetallic material [183] is an interesting topic since its spin polarization is nearly 100%. The materials for channel, including metals (Cu, Mg) [54,108,114,117,131,224-226], semiconductors(silicon) [48, 227] and new materials like graphene [111, 124–127, 134, 138, 152, 228–232], are also explored. Their spin diffusion lengths influence directly spin detection current. Theoretically, long spin diffusion length is better for spin transport and thus for spin detection current. The graphene, whose spin diffusion length could be as long as 100  $\mu m$  [233], is studied a lot in recent years. Another research on material concerns how to improve the spin diffusion length of each material. The temperature and the extrinsic scattering with impurities, defects and boundaries, are the two important factors which are related to. The temperature dependence of spin relaxation process can be studied by means of nonlocal spinvalve measurements. Based on this study, the maximum spin diffusion length can be given at a specific temperature [122]. The extrinsic scattering will reduce the spin diffusion length of the material and increase the delay and energy consumption. To reduce this scattering, advanced fabrication methods, proper surface manipulation (such as oxidation [108]), the use of smaller junction area [123] and looking for new structure (e.g. suspended graphene device [133]) are the feasible ways.

Another way to improve the spin injection efficiency focus on overcoming the conductance mismatch problem between the ferromagnet and the channel. Because of the conductance mismatch, most of the spin-polarization of the current in FM relaxes at the interface. Therefore it is difficult to inject spins into the channel. This problem is first revealed by G.Schmidt [234] in 2000. In the same year, many groups began their researches on how to eliminate this problem and found that insertion of a spin-polarized interface(e.g. tunnel contact) between the FM and channel can remedy it [46, 109, 114, 139, 235–237]. Except for insertion of a tunnel barrier, another way reported in [103] uses ultra-fast optical excitation

instead of electrical spin injection. The amount of injected spin is constrained by the amount of excited electrons in the FM. With a femtosecond laser pump pulse, a population of excited electrons and hole in FM is created and a spin polarization of 80% is obtained in Ni-Si interface.

Except for the injection efficiency enhancement of ASL, researchers also made efforts for low power consumption and high density. 3-D ASL design constituting of multiple ASL layers [238] stacked vertically and the scaling down of ASL device [239] can achieve effective power savings and area benefit. The design method, the clocking for 3D stacking and the scaling limits (e.g. dipole coupling between input and output) and material targets are presented in [238] and [51, 239, 240], respectively.

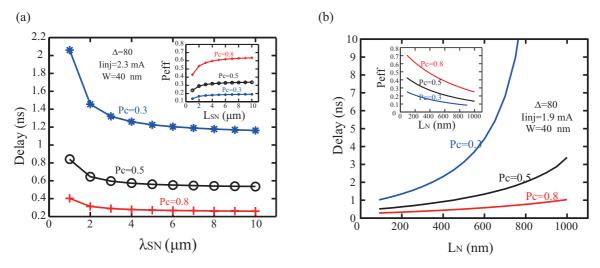

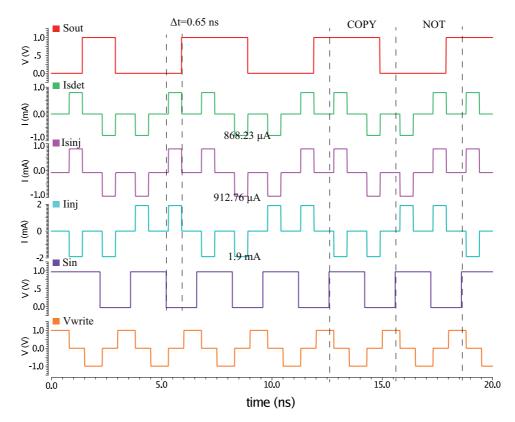

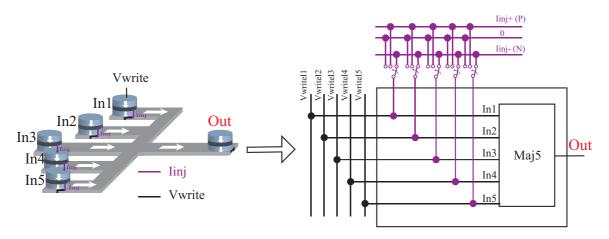

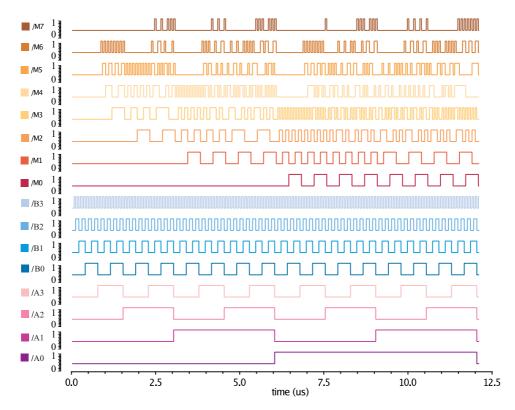

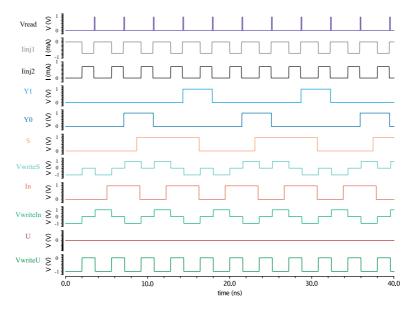

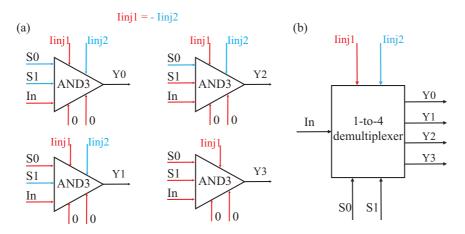

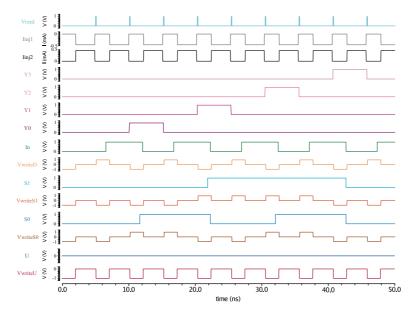

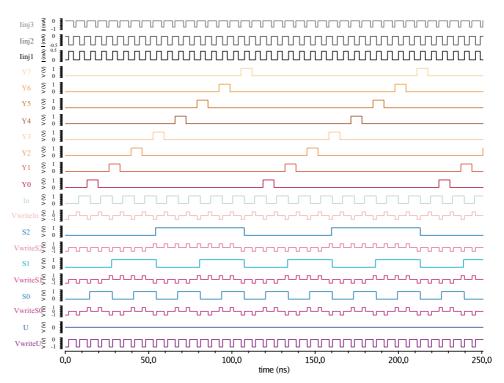

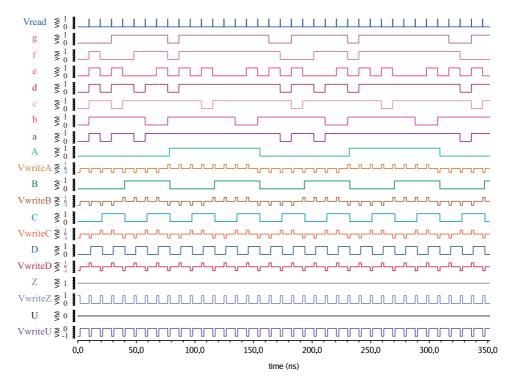

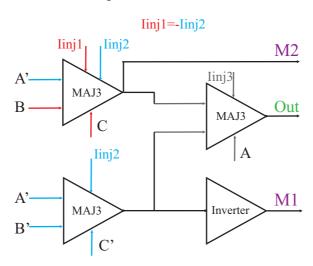

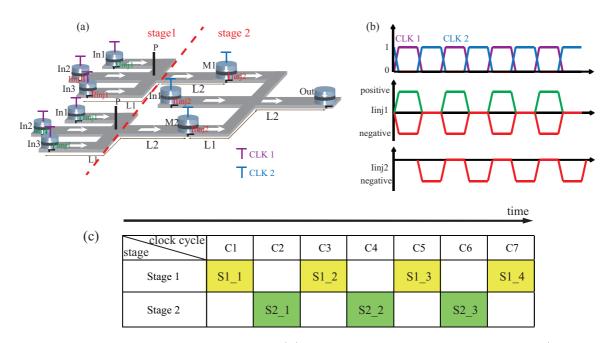

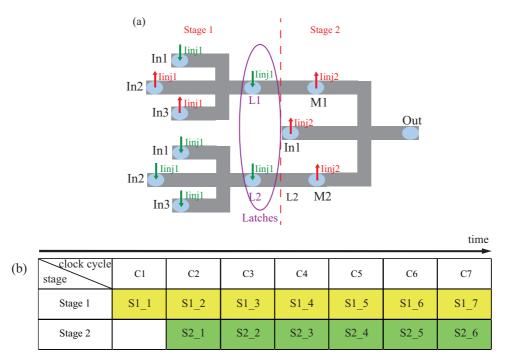

#### 2.2.3 ASL modeling and benchmarking