## Design, Parallel Simulation and Implementation of High-Performance Fault-Tolerant Network-on-Chip Architectures

Mohamed El Amir Charif

#### ► To cite this version:

Mohamed El Amir Charif. Design, Parallel Simulation and Implementation of High-Performance Fault-Tolerant Network-on-Chip Architectures. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2017. English. NNT: 2017GREAT075. tel-01743726

### HAL Id: tel-01743726 https://theses.hal.science/tel-01743726v1

Submitted on 26 Mar 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Communauté UNIVERSITÉ Grenoble Alpes

## THÈSE

Pour obtenir le grade de

#### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES Arrêté ministériel : 25 mai 2016

Présentée par

## Mohamed El Amir CHARIF

Thèse dirigée par **Michel NICOLAIDIS**, Directeur de Recherche , , et

codirigée par Nacer-Eddine ZEIRGAINOH

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés

dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

### Conception, Simulation Parallèle et Implémentation de réseaux sur puce hautes performances tolérants aux fautes

### Design, Parallel Simulation and Implementation of High-Performance Fault-Tolerant Network-on-Chip Architectures

Thèse soutenue publiquement le **17 novembre 2017**, devant le jury composé de :

Monsieur Nacer-Eddine ZERGAINOH Maître de Conférences, Université Grenoble Alpes, CoDirecteur de these Monsieur Frédéric PETROT Professeur, TIMA, Président Monsieur Ian O'CONNOR Professeur, Ecole Centrale de Lyon, Rapporteur Monsieur Bruno ROUZEYRE Professeur, Université Montpellier 2, Rapporteur

#### Abstract

Networks-on-Chip (NoCs) have proven to be a fast and scalable replacement for buses in current and emerging many-core systems. They are today an actively researched topic and various solutions are being explored to meet the needs of emerging applications in terms of performance, quality of service, power consumption, and fault-tolerance. This thesis presents contributions in two important areas of Network-on-Chip research:

- The design of ultra-flexible high-performance deadlock-free routing algorithms for any topology.

- The design and implementation of parallel cycle-accurate Network-on-Chip simulators for a fast evaluation of new NoC architectures.

While aggressive technology scaling has its benefits in terms of delay, area and power, it is also known to increase the vulnerability of circuits, suggesting the need for fault-tolerant designs. Fault-tolerance in NoCs is directly tied to the degree of flexibility of the routing algorithm. High routing flexibility is also required in some irregular topologies, as is the case for TSV-based 3D Network-on-Chips, wherein only a subset of the routers are connected using vertical connections. Unfortunately, routing freedom is often limited by the deadlock-avoidance method, which statically restricts the set of virtual channels that can be acquired by each packet.

The first part of this thesis tackles this issue at the source and introduces a new topologyagnostic methodology for designing ultra-flexible routing algorithms for Networks-on-Chips. The theory relies on a novel low-restrictive sufficient condition of deadlock-freedom that is expressed using the local information available at each router during runtime, making it possible to verify the condition dynamically in a distributed manner. A significant gain in both performance and fault-tolerance when using our methodology compared to the existing static channel partitioning methods is reported. Moreover, hardware synthesis results show that the newly introduced mechanisms have a negligible impact on the overall router area. In the second part, a novel routing algorithm for vertically-partially-connected 3D Networkson-Chips called First-Last is constructed using the previously presented methodology. Thanks to a unique distribution of virtual channels, our algorithm is the only one capable of guaranteeing full connectivity in the presence of one TSV pillar in an arbitrary position, while requiring a low number of extra buffers (1 extra VC in the East and North directions). This makes First-Last a highly appealing cost-effective alternative to the state-of-the-art Elevator-First algorithm.

Finally, in an aim to speed up the evaluation of new Network-on-Chip designs, the third and last part of this work presents the first detailed and modular parallel NoC simulator design to run fully on Graphics Processing Units (GPUs). First, a flexible task decomposition approach, specifically geared towards high parallelization is proposed. Our approach makes it easy to adapt the granularity of parallelism to match the capabilities of the host GPU. Second, all the GPU-specific implementation issues are addressed and several optimizations are proposed. Our design is evaluated through a reference implementation, which is tested on an NVidia GTX980Ti graphics card and shown to speed up 4K-node NoC simulations by almost 280x.

## Résumé

#### Introduction

Grâce à une réduction considérable dans les dimensions des transistors, les systèmes informatiques sont aujourd'hui capables d'intégrer un très grand nombre de coeurs de calcul en une seule puce (System-on-Chip, SoC). Faire communiquer les composants au sein d'une puce est aujourd'hui assuré par un réseau de commutation de paquets intégré, communément appelé Network-on-Chip (NoC). Cependant, le passage à des technologies de plus en plus réduites rend les circuits plus vulnérables aux fautes et aux défauts de fabrication. Le réseau sur puce peut donc se retrouver avec des routeurs ou des liens non-opérationnels, qui ne peuvent plus être utilisés pour le routage de paquets. Par conséquent, le niveau de flexibilité offert par l'algorithme de routage n'a jamais été aussi important.

La première partie de cette thèse consiste à proposer une méthodologie généralisée, permettant de concevoir des algorithmes de routage hautement flexibles, combinant tolérance aux fautes et hautes performances, et ce pour n'importe quelle topologie réseau. Cette méthodologie est basée sur une nouvelle condition suffisante pour l'absence d'interblocages (deadlocks) qui, contrairement aux méthodes existantes qui imposent des restrictions importantes sur l'utilisation des buffers, s'évalue de manière dynamique en fonction de chaque paquet et ne requiert pas un partitionnement stricte des canaux virtuels (virtual channels). Il est montré que ce degré élevé de liberté dans l'utilisation des buffers a un impact positif à la fois sur les performances et sur la robustesse du NoC, sans pour autant augmenter la complexité en termes d'implémentation matérielle.

La seconde partie de la thèse s'intéresse à une problématique plus spécifique, qui est celle du routage dans des topologies tri-dimensionnelles partiellement connectées, qui vont vraissemblablement être en vigueur à cause du coût important des connexions verticales, réalisées en utilisant la technologie TSV (Through-Silicon Via). Cette thèse introduit un nouvel algorithme de routage pour ce type d'architectures nommé "First-Last". Grâce à un placement original des canaux virtuels, cet algorithme est le seul capable de garantir la connectivité totale du réseau en présence d'un seul pilier de TSVs de coordonnées arbitraires, tout en ne requérant de canaux virtuels que sur deux des ports du routeur. Contrairement à d'autres algorithmes qui utilisent le même nombre total de canaux virtuels, First-Last n'impose aucune règle sur la position des piliers, ni sur les piliers à sélectionner durant l'exécution. De plus, l'algorithme proposé ayant été construit en utilisant la méthode décrite dans la première partie de la thèse, il offre une utilisation optimisée des canaux virtuels ajoutés.

L'implémentation d'un nouvel algorithme de routage implique souvent des changements considérables au niveau de la microarchitecture des routeurs. L'évaluation de ces nouvelles solutions requiert donc une plateforme capable de simuler précisément l'architecture matérielle du réseau au cycle près. De plus, il est essentiel de tester les nouvelles architectures sur des tailles de réseau significativement grandes, pour s'assurer de leur scalabilité et leur applicabilité aux technologies émergentes (e.g. intégration 3D). Malheureusement, les simulateurs de réseaux sur puce existants ne sont pas capables d'effectuer des simulations sur de grands réseaux (milliers de coeurs) assez vite, et souvent, la précision des simulations doit être sacrifiée afin d'obtenir des temps de simulation raisonnables. En réponse à ce problème, la troisième et dernière partie de cette thèse est consacrée à la conception et au développement d'un modèle de simulation générique, extensible et parallélisable, exploitant la puissance des processeurs graphiques modernes (GPU). L'outil développé modélise l'architecture d'un routeur de manière très précise et peut simuler de très grands réseaux en des temps records.

Dans ce qui suit on décrit plus en détail chacune des solutions proposées.

# Contribution I: Une nouvelle théorie pour la prévention d'interblocages dans les réseaux

Certaines parties de cette contribution ont fait l'objet de publications dans des conférences internationales Charif et al. [2016], Charif et al. [2017b].

Une approche très souvent adoptée pour augmenter le degré d'adaptabilité d'un algorithme de routage sans provoquer d'interblocages (deadlocks) consiste à introduire plusieures files de paquets par canal physique. Ces files d'entrée sont appelées canaux virtuels, ou Virtual Channels (VC). Une majeure partie des algorithmes adoptés dans les NoCs aujourd'hui Bahmani et al. [2012], Salamat et al. [2016b] sont conçus suivant d'anciennes théories telles que celle de Dally Dally and Seitz [1988], ou des méthodologies basées sur ces théories Ebrahimi and Daneshtalab [2017]. Dans ces approches, les canaux virtuels servent à diviser le réseau en plusieurs sous-réseaux (Sub-Networks), de manière à ce que les paquets présents dans chaque sous-réseau utilisent un algorithme de routage sans dépendances cycliques (cycle-free).

On identifie plusieurs problèmes avec cette approche. Premièrement, puisque la méthode même est basée sur la séparation stricte des différents sous-réseaux, les canaux qu'un paquet peut occuper à une étape donnée sont définis de manière statique. Cela signifie qu'un paquet ne peut utiliser un canal virtuel qui n'appartient pas à son sous-réseau actuel, même si ce canal est disponible. Sans cette restriction, les canaux virtuels pourraient être utilisés pour réduire le blocage des paquets et augmenter la bande passante du réseau. Deuxièmement, pour garantir l'absence de dépendances cycliques, cette méthode impose un ordre strict sur la traversée des différents sous-réseaux. Cela implique qu'un paquet ne peut jamais visiter le même sous-réseau deux fois, ce qui réduit la flexibilité du routage, et donc la tolérance aux fautes.

Ces limitations sont principalement dues au fait que dans toutes ces théories, des "sousfonctions" de routage sont associées à un ensemble précis de canaux virtuels. Un paquet ayant besoin d'une sous fonction particulière pour atteindre sa destination est donc obligé d'occuper le bon canal virtuel.

On propose une nouvelle vision du routage sans interblocages qui permet de résoudre toutes ces limitations à la fois. Au lieu d'associer une fonction de routage aux canaux, on les associe à des "classes" ou "groupes" de paquets. Chaque paquet du réseau transporte l'identifiant de son groupe et est routé en fonction de cet identifiant. Aucun partitionnement des canaux virtuels n'est effectué, et les paquets peuvent occuper, à priori, n'importe quel canal virtuel sur le canal physique sélectionné par leur fonction de routage.

On définit alors la condition suffisante à l'absence d'interblocages comme suit: Un paquet doit sélectionner un canal physique qui comporte au moins un canal virtuel occupé par un paquet d'une classe égale ou supérieure à sa classe. Intuitivement, cela peut être expliqué de la manière suivante: si chaque paquet dans le réseau suit des paquets de son groupe, et sachant que les paquets d'un même groupe sont routés suivant la même fonction de routage qui ne contient pas de cycles, au moins un chemin de dépendances ne contenant aucun cycle existe pour chaque paquet du réseau, ce qui suffit pour prévenir les interblocages.

On présente alors une méthodologie généralisée, comprenant étapes de construction et règles de routage à différents niveaux de complexité, permettant la construction systématique d'algorithmes qui satisfont la condition minimum d'absence d'interblocages, et ce pour n'importe quelle topologie réseau. En effet, on s'appuyera sur cette méthodologie pour construire les algorithmes présentés dans la seconde partie de la thèse pour les réseaux 3D.

En plus d'être très peu restrictive par rapport aux conditions d'absence d'interblocages utilisées jusque là, notre condition permet de déduire des propriétés très puissantes. Par exemple, étant donné que la classe de routage de chaque paquet est connue, il est possible de savoir, au cas par cas, les paquets qui peuvent se suivre au sein d'un même canal virtuel. Des canaux virtuels non-vides peuvent alors être réalloués du moment que la condition d'absence d'interblocages n'est pas violée. Ceci n'est pas possible dans les autres théories qui permettent les dépendances cycliques telles que Duato [1995], où il faut attendre qu'un canal virtuel soit complètement vide avant de le réallouer à un nouveau paquet. Un gain significatif en performances a été démontré par les simulations effectuées. De plus, contrairement aux approches classiques qui ne permettent les données dynamiques sur les classes des paquets, prévoit les changements de classe dans les deux sens, sans risque d'interblocages. Les résultats de simulation montrent que cela se traduit par un niveau accru de fiabilité qui n'est pas atteignable suivant les méthodes classiques qui ne permettent le changement de sous-réseau que dans un seul sens.

On montre que notre approche, en plus d'être utile pour la construction de nouveaux al-

gorithmes, permet également d'expliquer et de prouver les algrorithmes existants de manière plus intuitive. La reconstruction de ces algorithmes en utilisant notre méthodologie introduit une amélioration systématique au niveau de l'utilisation des canaux virtuels, et donc des performances.

Tous les mécanismes nécessaires à l'implémentation matérielle de notre méthode sont expliqués en détail, et on montre de plus que leur impact sur la surface totale du routeur est négligeable.

# Contribution II: Une nouvelle solution de routage économique et robuste pour les NoCs tri-dimensionnels partiellement connectés

Une version préliminaire de ce travail a été publiée dans Charif et al. [2017c].

Le TSV (Through-Silicon-Via) est une technologie prometteuse permettant de faire communiquer des composants en passant par la troisième dimension. Pour ce qui est du NoC, cela permet d'envisager des topologies tri-dimensionnelles à faible latence pouvant inclure un très grand nombre de noeuds.

Cependant, le coût élevé des TSV ne permet pas d'assurer des connexions verticales pour tous les noeuds, et les topologies 3D partielles, où seuls certains noeuds sont verticalement connectés, ont été regardés de très près ces dernières années. En effet, ce type de topologies irrégulières qui serait à priori inévitable en pratique, pose un certain nombre de challenges en matière de routage sans interblocages.

On constate que parmi les solutions proposées jusqu'à présent, certaines requièrent l'ajout d'un canal virtuel dans toutes les directions du plan Bahmani et al. [2012], ce qui implique un surcout considérable, alors que d'autres nécessitent moins de canaux additionnels Salamat et al. [2016b], voire même pas de canaux additionnels du tout Lee et al. [2015], mais posent des restrictions importantes soit sur le placement des TSVs, c'est à dire que les TSVs doivent être placés à des endroits spécifiques du réseau afin d'en garantir la connectivité, soit sur la sélection des TSVs à utiliser durant le routage, ce qui peut forcer l'emprunt de chemins trop longs et avoir

un impact négatif sur la performance.

En réponse à ces différents compromis, on introduit une nouvelle méthode de routage pour ce type de topologies possédant les caractéristiques suivantes:

- La connectivité est garantie en présence d'un seul pilier de TSVs placé n'importe où dans le réseau. Il n'y donc pas de restrictions sur le placement des piliers.

- N'importe quel pilier du réseau peut être sélectionné par l'algorithme de routage. Aucune restriction sur l'emprunt des TSVs.

- Un canal virtuel est requis dans seulement deux directions du plan.

On utilise donc le même nombre de canaux virtuels que Salamat et al. [2016b] mais notre méthode ne souffre pas des restrictions sur le placement des piliers et leur sélection.

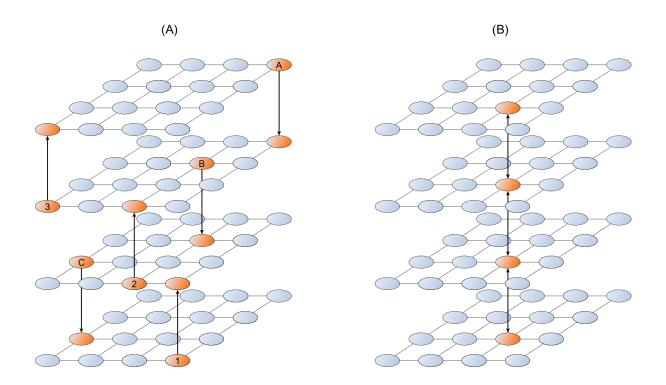

De manière générale, l'approche proposée peut être décrite comme suit:

- Diviser le plan (Est, Ouest, Sud, Nord) en deux ensembles de directions, de sorte à ce que le second ensemble + les deux directions Haut et Bas (la dimension Z) ne permettent pas la formation de cycles.

- Lors du routage, si un mouvement vertical est nécessaire, utiliser les directions du premier ensemble, puis celles du second ensemble pour atteindre n'importe quel TSV. Puisque toutes les directions sont incluses, il est toujours possible d'atteindre n'importe quel TSV.

- Utiliser les direcitons du second ensemble + haut et bas pour atteindre l'étage (le niveau) où se trouve la destination.

- 4. A l'étage de destination, utiliser les directions du second ensemble puis ceux du premier ensemble pour atteindre la destination. Là encore, toutes les directions sont incluses, et par conséquent, la destination peut être atteinte quelle que soit sa position.

- Les directions du premier ensemble étant utilisées au niveau source comme au niveau destination, un canal virtuel est requis uniquement dans ces directions pour prévenir les interblocages.

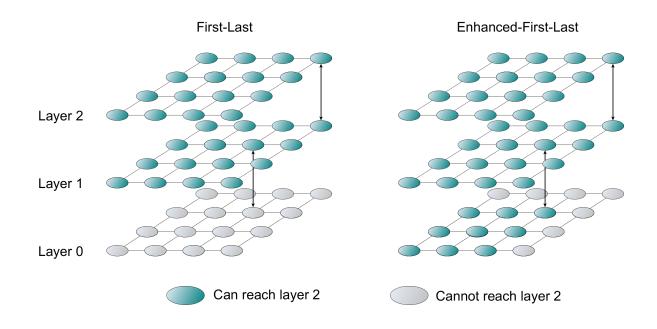

On montre que cette méthode, appelée "First-Last" du fait que les premières directions utilisées sont aussi les dernières, est réalisable en utilisant les directions positives (Est, Nord) comme premier ensemble et les directions négatives (Ouest, Sud) comme second ensemble. Cela signifie que des canaux virtuels sont nécessaires uniquement dans les directions Est et Nord.

Notre algorithme est le premier à permettre une telle distribution de canaux virtuels. En effet, les propositions existantes ne considèrent que les configurations où le nombre de canaux virtuels est le même le long d'une même dimension. Par exemple, l'algorithme East-then-West Salamat et al. [2016b] rajoute un canal virtuel le long de la dimension Y (Nord et Sud), conformément à ce qui a historiquement été fait dans le cas du routage 2D Schwiebert and Jayasimha [1993]. On a démontré que cette règle n'était pas nécessaire et ne faisait que limiter les solutions possibles.

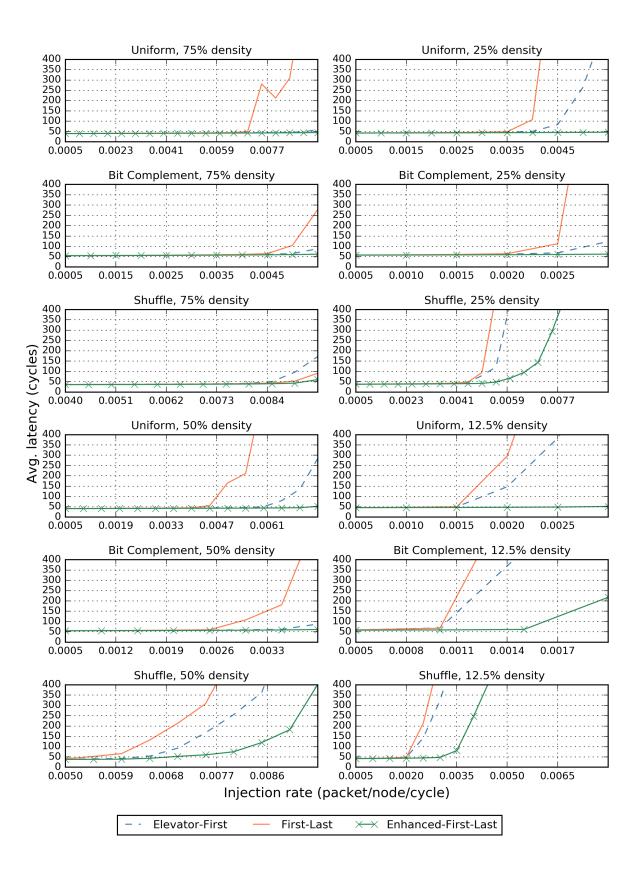

Les résultats de simulations et de synthèse matérielle montrent que nous arrivons non seulement à réduire considérablement le coût d'implémentation (d'environ 15%) par rapport à l'algorithme de référence Elevator-First Bahmani et al. [2012], mais aussi à offrir des performances bien supérieures grâce à une bonne exploitation des ressources disponibles.

Notre contribution au routage 3D ne se limite pas à l'algorithme First-Last. Afin de proposer une solution de routage complète et scalable, nous explorons également plusieurs méthodes de sélection de TSV. Chacune des méthodes proposées comporte un algorithme hors-ligne permettant d'assigner à chaque routeur un TSV et de configurer des registres de taille fixe pour pointer vers le TSV sélectionné, et un algorithme de routage capable d'exploiter ces données pour trouver un TSV lors de l'exécution. La recherche de TSV étant effectuée de manière distribuée, il est nécessaire de garantir que chaque paquet finit forcément par atteindre un TSV. Nous élaborons une preuve formelle qui stipule que si les TSVs sont assignés en fonction de leur distance par rapport aux noeuds, et quel que soit le critère utilisé pour départager des TSVs à équi-distance, chaque paquet finit toujours par atteindre un TSV, et ce en parcourant l'un des chemins de distance minimale à partir de la source. Cette preuve est très importante car elle implique que l'algorithme de routage (implémenté en hardware) n'a pas besoin d'être modifié pour éviter qu'un paquet ne cherche un TSV indéfiniment, comme d'autres solutions proposent de faire Niazmand et al. [2016].

# Contribution III: Simulation parallèle et précise de NoCs sur GPU

Cette contribution a fait l'objet d'une publication à ASP'DAC 2017 Charif et al. [2017a].

Les simulateurs de NoCs précis au cycle près (cycle-accurate) sont très souvent utilisés pour la validation de nouvelles architectures. Cependant, comme les puces émergentes sont capables d'accueillir de plus en plus de routeurs, les nouvelles solutions doivent être validées sur des réseaux de plus en plus grands (centaines voire milliers de routeurs). Les simulateurs populaires comme Garnet Agarwal et al. [2009] ou Booksim Jiang et al. [2013] ne parviennent pas à effectuer ce genre de simulations en des temps raisonnables.

Une solution évidente à ce problème consiste à paralléliser les simulations sur des machines multicoeurs Eggenberger and Radetzki [2013], Eggenberger et al. [2016], Ren et al. [2012]. Cependant, à cause des temps de synchronisation non-négligeables dans le cas des CPUs, et étant donné que la précision des simulations requiert une synchronisation globale après chaque cycle simulé, des compromis doivent être faits et souvent, la précision des résultats doit être sacrifiée pour obtenir des accélérations décentes Ren et al. [2012].

Les GPUs (Graphics Processing Units) sont par ailleurs devenus l'un des supports de calcul parallèle les plus prisés. Bien qu'ils n'offrent pas une solution miracle au problème de synchronisation, ils contiennent un grand nombre de ressources de calcul et permettent la création d'un grand nombre de threads, pouvant compenser le temps passé dans les synchronisations. On se propose donc de concevoir et d'implémenter un simulateur cycle-accurate de NoCs capable d'exploiter au mieux les ressources du GPU sans pour autant demander à l'utilisateur des efforts d'optimisation.

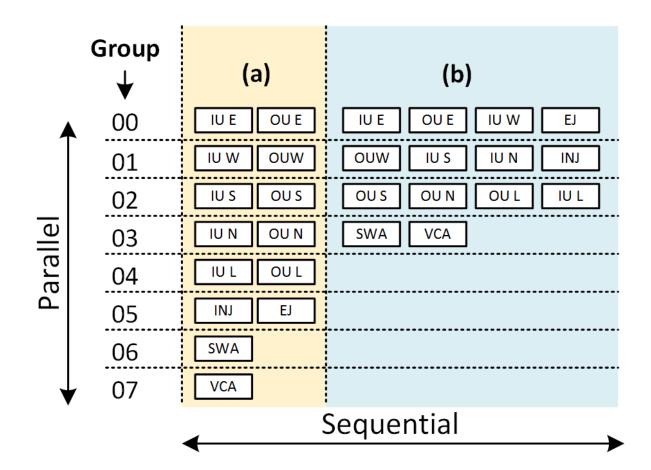

Le design proposé se base sur une décomposition des tâches qui n'est pas définie en terme de routeurs Eggenberger and Radetzki [2013] ou de ports Zolghadr et al. [2011], mais de groupements personnalisés de modules. Un modèle de programmation où tous les modules définis peuvent s'exécuter en parallèle est proposé. Les modules communiquent à travers des registres, où chaque registre se compose de deux cases (odd, even). Selon la parité du cycle simulé, les modules lisent et écrivent dans des cases différentes du registre. Cela assure que les modules ne lisent pas les valeurs trop tôt et préserve la fidélité au matériel simulé. On peut définir autant de modules que l'on veut, pouvant effectuer des tâches complètement distinctes et de complexités différentes (code divergent) et les organiser dans des groupes. La composition des groupes se fait par l'utilisateur sans aucune contrainte sur le nombre de modules ou leur type. Ce sont alors les groupes de modules qui sont considérés comme des tâches parallélisables. Cette indirection est très importante car on peut ajuster la granularité de la parallélisation comme on le souhaite. Le même design (mêmes modules, même code) peut être simulé sur un GPU à faibles ressources en changeant simplement le groupage pour contenir moins de groupes (et donc moins de threads). Sur un bon GPU, cela permet de simuler des NoCs de tailles très grandes (plus de 4000 routeurs ont été simulés sur un GTX980Ti).

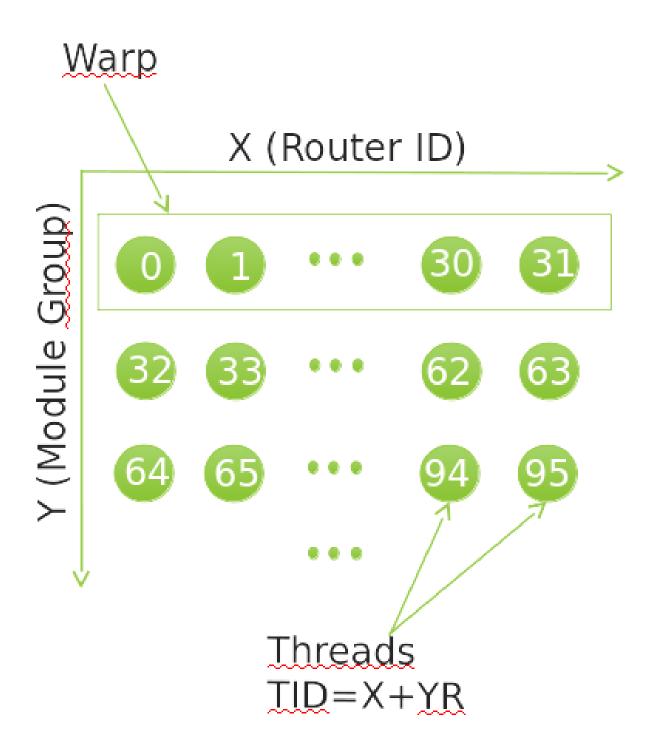

Au niveau de l'implémentation, on propose plusieurs optimisations sur l'utilisation de la mémoire ainsi que la synchronisation globale. Le point le plus important est le mapping des tâches, qui doit être réalisé de sorte à ce que la divergence de code soit minimale. Bien que les groupes de modules contiennent des codes complètement hétérogènes, on observe que tous les routeurs comportent les mêmes groupes. La stratégie de mapping doit donc exploiter ce parallélisme inhérent à l'architecture du NoC afin de minimiser, voire supprimer la divergence de code. On arrive à accomplir cela en identifiant chaque thread par deux coordonnées g, r (Groupe et Routeur). Sachant que tous les W threads (typiquement 32) doivent exécuter le même code (modèle SIMT Single Instruction Multiple Theeads), on propose de définir l'identifiant de thread comme suit ID = g \* R + r, où R est le nombre total de routeurs. Ainsi, au sein de W threads (appelés Warp), on change de routeur, avant de changer le groupe de modules, ce qui permet de garantir, en s'assurant que R est multiple de W, que les threads d'un warp exécutent le même code (même groupe).

En s'appuyant sur ce design, on a développé un outil de simulation ultra-rapide appelé GNoCS, qui a servi entre autres à la réalisation de toutes les simulations présentées le long de cette thèse. Des détails sur son implémentation (API, modèle de programmation, etc.) sont présentés dans l'Annexe B.

# Contents

| Contents<br>List of Figures |      |         |                                                                     |   |

|-----------------------------|------|---------|---------------------------------------------------------------------|---|

|                             |      |         |                                                                     |   |

| Ι                           | IN   | TROD    | UCTION                                                              | 1 |

| 1                           | Intr | oductio | n                                                                   | 3 |

|                             | 1.1  | Introd  | uction                                                              | 3 |

|                             |      | 1.1.1   | Contribution I: A New Methodology for the Design of Highly Flexible |   |

|                             |      |         | Deadlock-Free Routing Algorithms                                    | 4 |

|                             |      | 1.1.2   | Contribution II: A Cost-Effective Routing Solution for TSV-Based 3D |   |

|                             |      |         | Networks-on-Chips                                                   | 5 |

|                             |      |         | 1.1.2.1 Scalable TSV assignment strategies                          | 6 |

|                             |      |         | 1.1.2.2 The First-Last routing algorithm                            | 6 |

|                             |      | 1.1.3   | Contribution III: Ultra-fast GPU-Based Parallel Simulation of NoCs  | 6 |

|                             | 1.2  | Experi  | imental setup                                                       | 7 |

|                             |      | 1.2.1   | Hardware implementation                                             | 7 |

|                             |      | 1.2.2   | Simulation                                                          | 7 |

#### **II ON THE DESIGN OF DEADLOCK-FREE ROUTING ALGORITHMS**

### FOR WORMHOLE NETWORKS

| 2 | A Dynamic Sufficient Condition of Deadlock-Freedom for Highly Flexible Routing |         |                                                         |    |  |  |

|---|--------------------------------------------------------------------------------|---------|---------------------------------------------------------|----|--|--|

|   | in W                                                                           | ormho   | le Networks                                             | 11 |  |  |

|   | 2.1                                                                            | Introd  | uction                                                  | 11 |  |  |

|   | 2.2                                                                            | State-o | of-the-art                                              | 13 |  |  |

|   |                                                                                | 2.2.1   | VC-based deadlock avoidance                             | 13 |  |  |

|   |                                                                                | 2.2.2   | Necessary and sufficient conditions of deadlock-freedom | 13 |  |  |

|   |                                                                                | 2.2.3   | Routing algorithm design frameworks                     | 14 |  |  |

|   | 2.3                                                                            | Routin  | ng algorithm design methodology                         | 15 |  |  |

|   |                                                                                | 2.3.1   | Switch model                                            | 15 |  |  |

|   |                                                                                | 2.3.2   | Fault model                                             | 17 |  |  |

|   |                                                                                | 2.3.3   | Example design: Fault-tolerant routing in 2D mesh NoCs  | 17 |  |  |

|   |                                                                                | 2.3.4   | Upgrades and Downgrades                                 | 21 |  |  |

|   | 2.4                                                                            | Impler  | mentation details                                       | 22 |  |  |

|   |                                                                                | 2.4.1   | Without downgrades                                      | 23 |  |  |

|   |                                                                                | 2.4.2   | With downgrades                                         | 25 |  |  |

|   |                                                                                | 2.4.3   | Repeating route computation                             | 26 |  |  |

|   |                                                                                | 2.4.4   | Negative tag back-propagation                           | 26 |  |  |

|   | 2.5                                                                            | Forma   | l generalization                                        | 27 |  |  |

|   |                                                                                | 2.5.1   | Preliminary definitions                                 | 27 |  |  |

|   |                                                                                | 2.5.2   | Generic routing algorithm                               | 28 |  |  |

|   |                                                                                | 2.5.3   | Proof of deadlock-freedom                               | 28 |  |  |

|   |                                                                                | 2.5.4   | Livelock-freedom and termination                        | 30 |  |  |

|   | 2.6                                                                            | Flow c  | control                                                 | 31 |  |  |

|   | 2.7                                                                            | A fres  | h look at fully adaptive routing algorithms             | 31 |  |  |

|   | 2.8                                                                            | Experi  | imental results                                         | 33 |  |  |

|   |                                                                                | 2.8.1   | Simulation setup                                        | 33 |  |  |

|   |                                                                                | 2.8.2   | Simulation methodology                                  | 33 |  |  |

|   |                                                                                | 2.8.3   | Evaluating the fault-tolerant algorithm                 | 34 |  |  |

9

|    |      | 2.8.4   | The impact of flow control and dynamic masking                        | 37  |

|----|------|---------|-----------------------------------------------------------------------|-----|

|    |      | 2.8.5   | Hardware synthesis                                                    | 37  |

|    | 2.9  | Conclu  | usions                                                                | 39  |

|    |      |         |                                                                       |     |

| II | I R  | OUTI    | ING IN TSV-BASED THREE-DIMENSIONAL NETWOR                             | KS- |

| 0  | N-C  | HIPS    |                                                                       | 41  |

| 3  | A fr | amewo   | rk for scalable distributed TSV assignment                            | 43  |

|    | 3.1  | Introd  | uction                                                                | 43  |

|    | 3.2  | State-o | of-the-art                                                            | 44  |

|    | 3.3  | Target  | architecture                                                          | 46  |

|    |      | 3.3.1   | NoC architecture                                                      | 46  |

|    |      | 3.3.2   | Routing                                                               | 47  |

|    | 3.4  | Manha   | attan-distance-based elevator selection                               | 50  |

|    |      | 3.4.1   | Elevator location bits                                                | 50  |

|    |      | 3.4.2   | Safe Selection Algorithm (md-safe)                                    | 50  |

|    |      | 3.4.3   | Randomized Selection Algorithm (md-random)                            | 51  |

|    | 3.5  | Proof   | of reachability for Manhattan-Distance-Based approaches               | 55  |

|    | 3.6  | Optim   | istic elevator selection                                              | 60  |

|    |      | 3.6.1   | Elevator location bits                                                | 61  |

|    |      | 3.6.2   | Routing algorithm (optimistic)                                        | 61  |

|    | 3.7  | Experi  | imental results                                                       | 62  |

|    |      | 3.7.1   | Hardware synthesis results                                            | 62  |

|    |      | 3.7.2   | Performance evaluation                                                | 65  |

|    | 3.8  | Conclu  | usions                                                                | 69  |

| 4  | The  | First-L | ast routing algorithm: A cost-effective alternative to Elevator-first | 70  |

|    | 4.1  | Introd  | uction                                                                | 70  |

|    | 4.2  | State-o | of-the-art in 3D Routing                                              | 71  |

|    | 4.3  | The Fi  | rst-Last routing algorithm                                            | 73  |

|    |      | 4.3.1   | General approach                                                      | 73  |

|    |      |          | 4.3.1.1 Identifying cycle-free routing classes                        | 73   |

|----|------|----------|-----------------------------------------------------------------------|------|

|    |      |          | 4.3.1.2 Step 2: Assigning virtual channels                            | 74   |

|    |      | 4.3.2    | Enhanced-First-Last: Boosting network performance and resilience with |      |

|    |      |          | vertical VCs                                                          | 75   |

|    |      | 4.3.3    | Flow control                                                          | 76   |

|    |      |          | 4.3.3.1 First-Last                                                    | 77   |

|    |      |          | 4.3.3.2 Enhanced-First-Last                                           | 77   |

|    | 4.4  | Deadlo   | ock-freedom, livelock-freedom, and connectivity                       | 78   |

|    |      | 4.4.1    | Deadlock-freedom                                                      | 78   |

|    |      | 4.4.2    | Livelock-freedom                                                      | 78   |

|    |      | 4.4.3    | Condition of connectivity                                             | 78   |

|    | 4.5  | Hardw    | vare implementation details                                           | 80   |

|    |      | 4.5.1    | Scalable TSV assignment                                               | 81   |

|    |      | 4.5.2    | Route computation logic                                               | 82   |

|    | 4.6  | Experi   | mental results                                                        | 85   |

|    |      | 4.6.1    | Hardware synthesis                                                    | 85   |

|    |      | 4.6.2    | Performance evaluation                                                | 86   |

|    | 4.7  | Conclu   | usion                                                                 | 87   |

| •• | 7 •  |          |                                                                       | TN / |

| I  |      |          | A-FAST GPU-BASED PARALLEL CYCLE-ACCURATE S                            |      |

| U  | LAL  | ION C    | OF NETWORKS-ON-CHIPS                                                  | 91   |

| 5  | Higl | nly Para | allelizable Cycle-Accurate Network-on-Chip Simulation                 | 93   |

|    | 5.1  | Introdu  | uction                                                                | 93   |

|    | 5.2  | State-o  | of-the-art                                                            | 94   |

|    | 5.3  | Generi   | c Task Decomposition                                                  | 95   |

|    |      | 5.3.1    | Modules                                                               | 96   |

|    |      | 5.3.2    | Module groups                                                         | 99   |

|    |      | 5.3.3    | Tasks                                                                 | 99   |

|    | 5.4  | GPU-ł    | based implementation                                                  | 100  |

|   |             | 5.4.1   | Overview   | on the GPU architecture                                                                    | 101 |

|---|-------------|---------|------------|--------------------------------------------------------------------------------------------|-----|

|   |             | 5.4.2   | Warp-frie  | endly task mapping                                                                         | 101 |

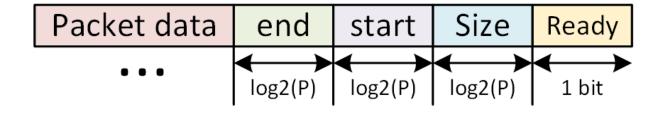

|   |             | 5.4.3   | Compact    | flit queue implementation                                                                  | 102 |

|   |             | 5.4.4   | Simulatin  | ng large networks                                                                          | 104 |

|   |             | 5.4.5   | Simulatio  | on kernel and final notes                                                                  | 105 |

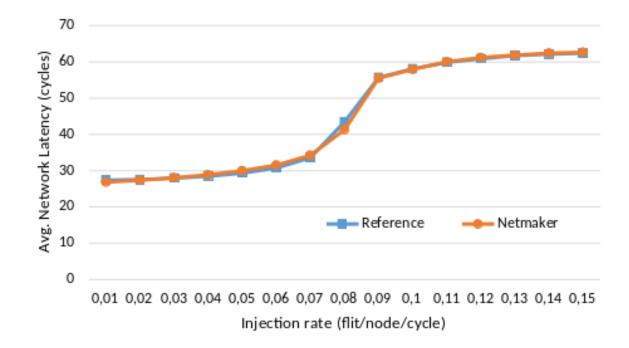

|   | 5.5         | Experi  | mental res | ults                                                                                       | 106 |

|   |             | 5.5.1   | Speedup    |                                                                                            | 106 |

|   |             | 5.5.2   | Hardware   | e fidelity                                                                                 | 108 |

|   | 5.6         | Conclu  | usions     |                                                                                            | 108 |

|   |             |         |            |                                                                                            |     |

| V | C           | ONCL    | USIONS     | 5 1                                                                                        | 12  |

| 6 | Con         | clusion | and Futu   | re works                                                                                   | 114 |

|   | 6.1         | Conclu  | usions     |                                                                                            | 114 |

|   | 6.2         | Future  | directions |                                                                                            | 116 |

|   |             |         |            |                                                                                            |     |

| V | [ A         | PPEN    | DICES      | 1                                                                                          | 19  |

| A | Con         | gestion | metrics fo | r adaptive routing                                                                         | 122 |

|   | A.1         | Introdu | uction     |                                                                                            | 122 |

|   | A.2         | Generi  | c congesti | on management unit description                                                             | 123 |

|   |             | A.2.1   | Router ev  | vents                                                                                      | 123 |

|   |             | A.2.2   | Updating   | the congestion value                                                                       | 124 |

|   |             | A.2.3   | Congesti   | on metric description                                                                      | 124 |

|   |             |         | A.2.3.1    | The free_buf metric $\ldots$                                                               | 124 |

|   |             |         | A.2.3.2    | The free_vc metric $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 125 |

|   |             |         | A.2.3.3    | The x_bar metric                                                                           | 125 |

|   |             |         | A.2.3.4    | The fr metric                                                                              | 126 |

|   | A.3         | Introdu | ining now  | · · · ·                                                                                    | 126 |

|   | <b>A</b> .3 | muou    | lenig new  | congestion metrics                                                                         | 120 |

|    |             | A.3.2        | The NAFAE congestion metric                                                                    | 127 |

|----|-------------|--------------|------------------------------------------------------------------------------------------------|-----|

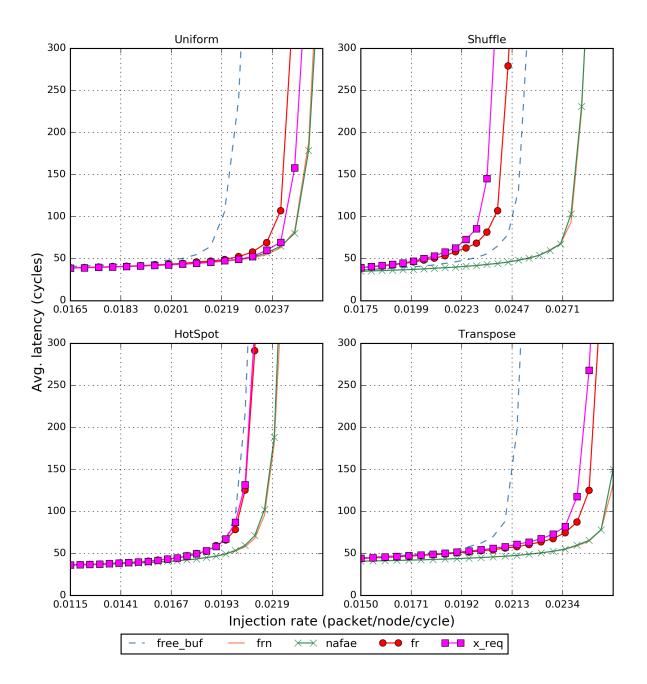

|    | A.4         | Experi       | mental results and conclusions                                                                 | 127 |

| B  | GNo         | oCS: A l     | nighly-extensible GPU-based parallel network-on-chip simulator                                 | 130 |

|    | <b>B</b> .1 | Introdu      | ction                                                                                          | 130 |

|    | B.2         | Basic d      | lata types and API                                                                             | 130 |

|    |             | B.2.1        | Integer API                                                                                    | 130 |

|    |             | B.2.2        | Registers                                                                                      | 131 |

|    |             | B.2.3        | Flit queue                                                                                     | 131 |

|    | B.3         | Program      | mming model                                                                                    | 133 |

|    |             | <b>B.3.1</b> | Example module: Credit manager                                                                 | 134 |

|    | B.4         | Simula       | tion automation                                                                                | 136 |

|    |             | <b>B.4.1</b> | Structure of a simulation description file                                                     | 136 |

|    |             | B.4.2        | The _except directive                                                                          | 138 |

|    |             | B.4.3        | SSH Support: The $\_nodes$ directive $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 138 |

| Bi | bliogr      | aphy         |                                                                                                | 141 |

# **List of Figures**

| 2.1 | Router architecture                                                            | 16 |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | Physical channels used by the two classes of the example algorithm. $\ldots$ . | 18 |

| 2.3 | An example packet configuration.                                               | 20 |

| 2.4 | Static vs. Dynamic masking. (a) Static: class 0 packets always mask the same   |    |

|     | channel during VC allocation. (b) Dynamic: The mask changes every time a       |    |

|     | class 1 packet acquires a VC                                                   | 24 |

| 2.5 | Physical channels used by the two classes of FT-CAR.                           | 32 |

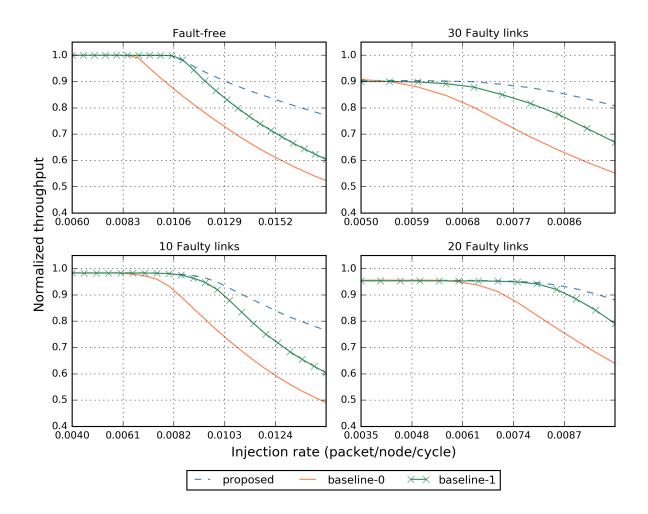

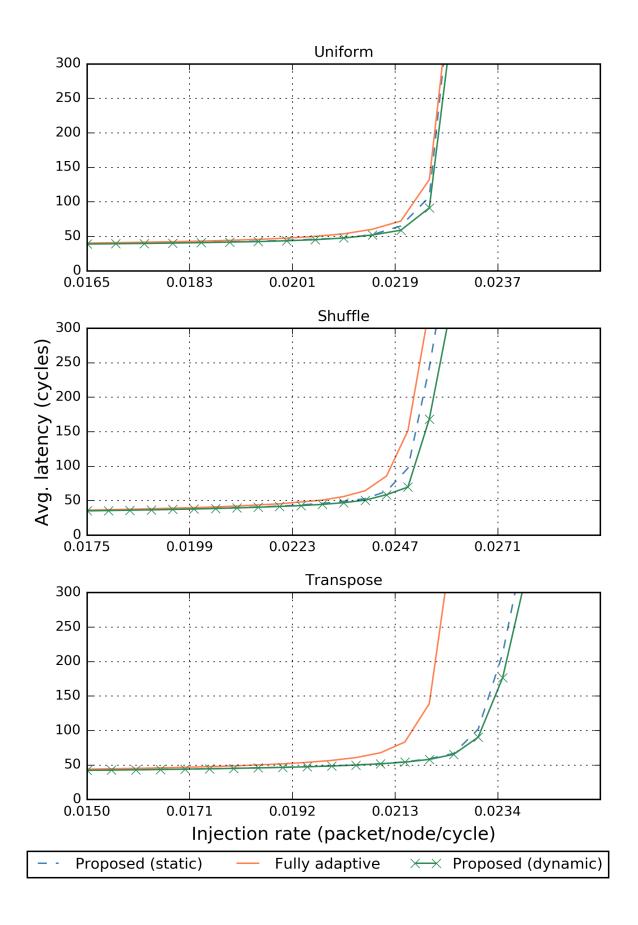

| 2.6 | Throughput results.                                                            | 35 |

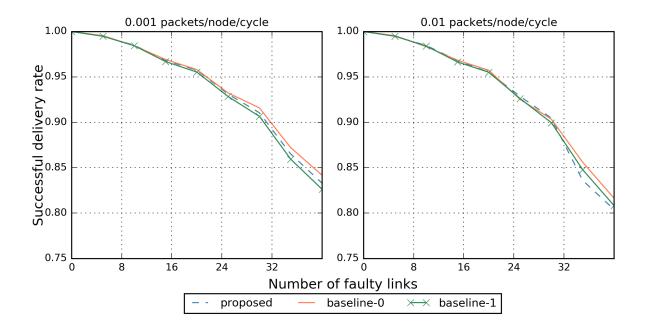

| 2.7 | Delivery success rate                                                          | 36 |

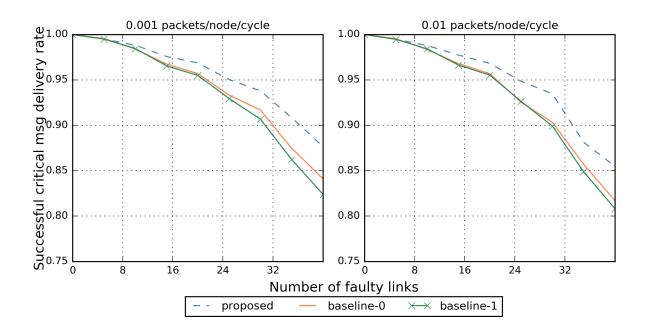

| 2.8 | Critical packet delivery success rate.                                         | 36 |

| 2.9 | Impact of flow control and dynamic masking on average latency                  | 38 |

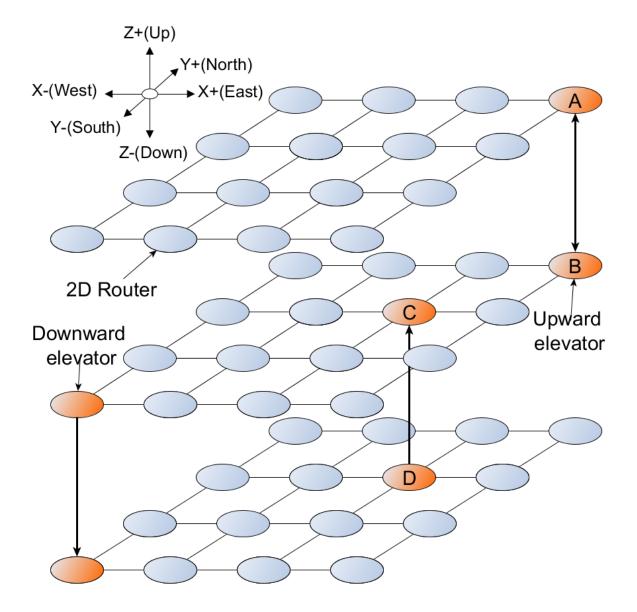

| 3.1 | Overview of the partially connected 3D-NoC Topology.                           | 48 |

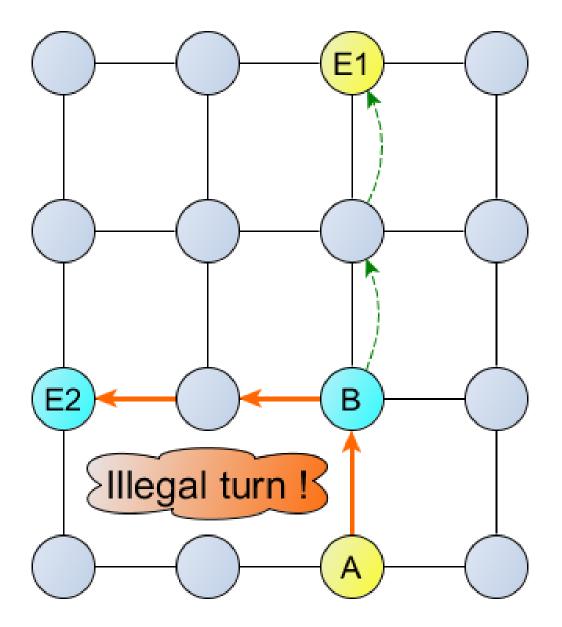

| 3.2 | Illustration of a potential deadlock scenario.                                 | 53 |

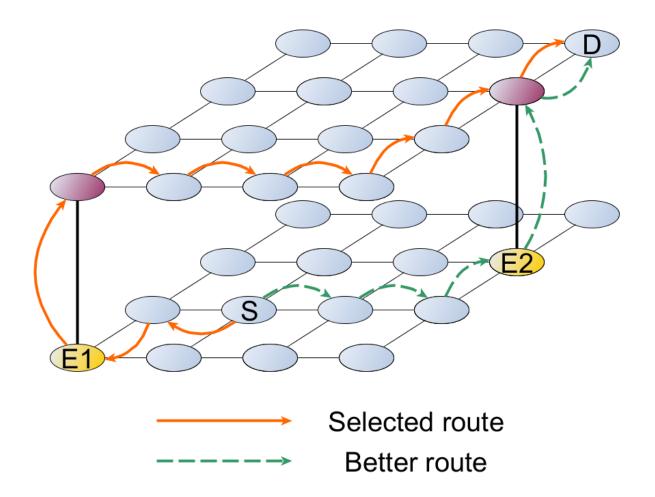

| 3.3 | Example of an inefficient route when using MD-based algorithms                 | 60 |

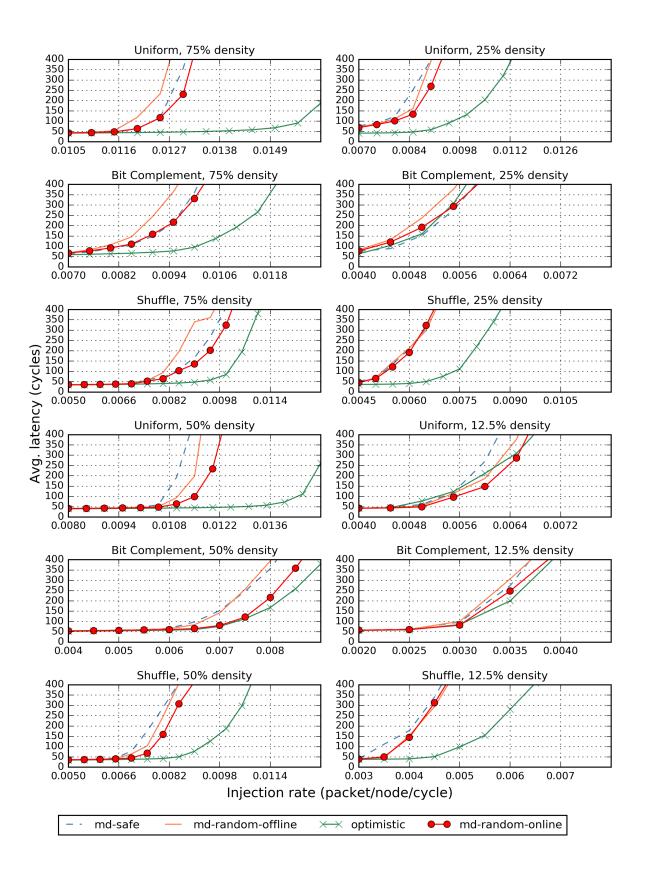

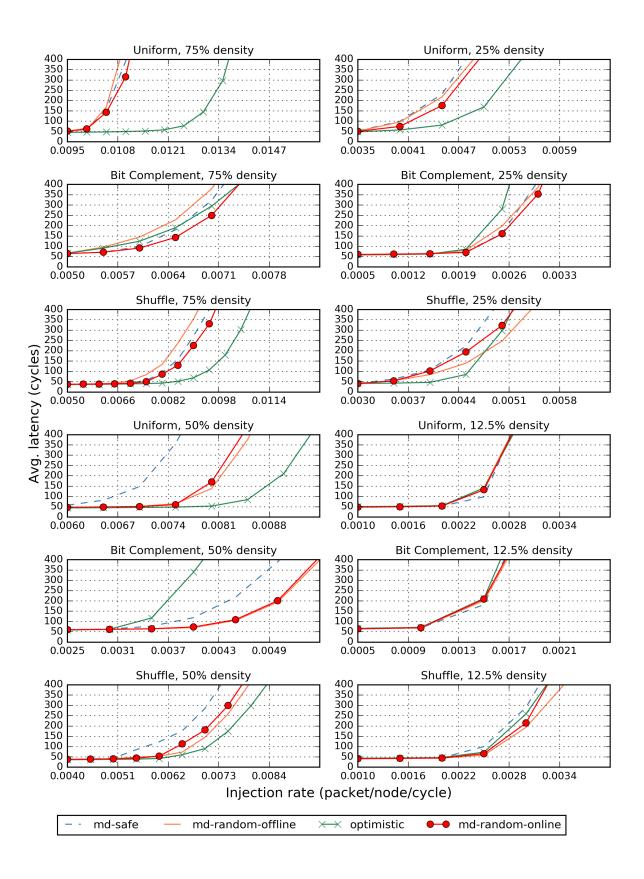

| 3.4 | Average packet latency for an 8x8x2 NoC                                        | 66 |

| 3.5 | Average packet latency for an 8x8x4 NoC                                        | 67 |

| 4.1 | The 3 routing classes of First-Last.                                           | 75 |

| 4.2 | The routing classes of Enhanced-First-Last.                                    | 76 |

| 4.3 | An example in which Enhanced-First-Last improves the connectivity of the net-  |    |

|     | work                                                                           | 77 |

| 4.4 | Examples of connected networks using First-Last.                               | 80 |

| 4.5 | Average packet latency.                                           | 88  |

|-----|-------------------------------------------------------------------|-----|

| 5.1 | Module groups.                                                    | 100 |

| 5.2 | Mapping of tasks onto threads.                                    | 103 |

| 5.3 | Compact flit queue representation.                                | 104 |

| 5.4 | Average Network Latency (RTL vs. GPU)                             | 109 |

| A.1 | Average packet latency obtained with different congestion metrics | 128 |

# **List of Tables**

| 2.1 | Hardware synthesis results                                    | 39 |

|-----|---------------------------------------------------------------|----|

| 3.1 | Hardware synthesis results                                    | 55 |

| 3.2 | Simulation parameters                                         | 58 |

| 4.1 | Hardware synthesis results                                    | 36 |

| 4.2 | Simulation parameters                                         | 36 |

| 5.1 | Simulation parameters                                         | )7 |

| 5.2 | Speedup results (1)                                           | )7 |

| 5.3 | Speedup results (2). (*) Injectors evicted from shared memory | )8 |

Part I

# **INTRODUCTION**

# Chapter 1

# Introduction

### **1.1 Introduction**

The ever-growing need for processing power in modern digital systems has led to a significant increase in the number of Intellectual Properties (IPs) integrated in a single chip. This was partly enabled by the aggressive scaling of transistor feature sizes, which, along with the many benefits it brings in terms of area, delay and power consumption, is known to pose some serious concerns about reliability. In this context, Networks-on-Chips (NoCs) Dally and Towles [2001] have emerged as the new paradigm of choice for on-chip communication, and are today widely used in many-core systems, as well as Graphics Processing Units (GPUs) Bakhoda et al. [2010], Wentzlaff et al. [2007]. In addition to being a power-efficient and scalable replacement for traditional buses, they contribute greatly to the chip's fault-tolerance and performance thanks to the path diversity that is inherent to the widely adopted NoC topologies. They are today an actively researched topic and various solutions are being explored to meet the needs of emerging applications in terms of performance, quality of service, energy, and fault-tolerance. This thesis presents contributions in two important areas of Network-on-Chip research:

- The design of flexible deadlock-free fault-tolerant routing algorithms for different topologies.

- The design and implementation of parallel cycle-accurate Network-on-Chip simulators for a fast evaluation of new NoC architectures.

4

These contributions are summarized in the remainder of this section.

## 1.1.1 Contribution I: A New Methodology for the Design of Highly Flexible Deadlock-Free Routing Algorithms

While aggressive technology scaling has its benefits in terms of delay, area and power, it is also known to increase the vulnerability of circuits, suggesting the need for fault-tolerant designs. Fault-tolerance in NoCs is directly tied to the degree of flexibility of the routing algorithm. High routing flexibility is also required in some irregular topologies, as is the case for TSV-based 3D Network-on-Chips, wherein only a subset of the routers are connected using vertical connections. One challenging aspect in the design such flexible algorithms is the risk of deadlock formation, which can occur if cyclic dependencies are formed between packets.

Many existing routing solutions make use of virtual channels (VCs), which consist in several disjoint input queues, to avoid deadlocks while offering enough routing flexibility to avoid faulty and congested areas in a NoC. However, most of the current solutions rely on an overly restrictive, static partitioning of VCs, which results in an under-utilization of their throughput enhancement capabilities Ebrahimi et al. [2013a], Chaix et al. [2011]. In effect, VCs can also be used to reduce Head-of-Line (HOL) blocking and greatly reduce the transmission delays Dally [1992].

To overcome the limitations of such approaches, Chapter 2 introduces a new sufficient condition of deadlock-freedom that greatly relaxes the restrictions imposed by the classic VC-based deadlock-avoidance methods. The strength of our condition lies in the fact that it is imposed on packets at runtime and does not require any partitioning of virtual channels, which makes it possible to fully exploit them to reduce packet blocking and boost performance. Based on this condition, we present a generic, topology-agnostic routing algorithm design methodology that can be used to construct highly flexible routing algorithms in only a few steps. Several examples are presented to showcase the usefulness of our approach for the construction of fault-tolerant routing algorithms, as well as the enhancement and the proof of existing routing algorithms. The implementation of all the required mechanisms in hardware is also described in detail, thereby demonstrating its feasibility in an on-chip environment. A significant gain in both performance and fault-tolerance when using our methodology compared to the existing static channel partitioning methods is reported. Moreover, hardware synthesis results show that the newly introduced mechanisms have a negligible impact on the overall router area. This methodology is subsequently used in the rest of the thesis to construct new routing algorithms for 3D NoCs.

We have published some parts of this work in Charif et al. [2016] and Charif et al. [2017b].

## 1.1.2 Contribution II: A Cost-Effective Routing Solution for TSV-Based 3D Networks-on-Chips

The emergence of 3D integration can greatly benefit future many-cores by enabling low-latency three-dimensional network-on-chip (3D-NoC) topologies Feero and Pande [2009], Pavlidis and Friedman [2007]. However, due to the high cost, low yield, and frequent failures of Through-Silicon Via (TSV) Benini [2008], 3D-NoCs are most likely to include only a few vertical connections Bartzas et al. [2007], resulting in partially connected topologies that pose new challenges in terms of deadlock-free routing and TSV assignment.

With a limited number of vertical connections, the routers of such networks require a way to locate the nodes that have vertical connections, commonly known as elevators, and select one of them in order to be able to reach other layers when necessary. Both the strategy used to select which elevator to take, and the routing algorithm used to reach the destination, have a critical impact on the cost and performance. However, most existing solutions either require too many VCs, which significantly impacts the cost Dubois et al. [2013], or poses too many restrictions on the placement and selection of TSVs Salamat et al. [2016b], Lee et al. [2015]. The goal of our second contribution is to provide a full routing solution for partially connected 3D-NoCs that not only reduces the number of required virtual channels, but offers increased flexibility compared to the state-of-the-art algorithms. This contribution consists of two parts presented in two different chapters:

#### 1.1.2.1 Scalable TSV assignment strategies

In Chapter 3, we explore, for the first time, various strategies for assigning TSVs to routers both offline and during runtime. All the solutions that we propose use a fixed number of re-configurable bits per router (scalability), and every assignment algorithm is formally proven to guarantee reachability and deadlock-freedom.

Many of the proposed strategies are generic and do not depend on a specific routing algorithm, resulting in a reusable framework for scalable TSV assignment in 3D-NoCs.

#### 1.1.2.2 The First-Last routing algorithm

Chapter 4 presents a novel routing algorithm targeting 3D-NoCs. Thanks to a unique distribution of virtual channels, our algorithm is the only one capable of guaranteeing full connectivity in the presence of one TSV pillar in an arbitrary position, while requiring a low number of extra buffers (only 1 extra VC in the East and North directions). Moreover, because it is based on the deadlock-avoidance approach presented in Chapter 2, it attains a high level of performance with respects to the state-of-the-art Elevator-First algorithm, in spite of using less virtual channels. We further exploit the efficient TSV assignment framework from Chapter 3 to implement a full, highly cost-effective routing solution for partially-connected 3D-NoCs.

A preliminary version of the First-Last routing algorithm was published in Charif et al. [2017c].

#### 1.1.3 Contribution III: Ultra-fast GPU-Based Parallel Simulation of NoCs

In order to speed up the evaluation of new Network-on-Chip designs, the last chapter of this thesis (Chapter 5) presents the first detailed and modular parallel NoC simulator design to run fully on Graphics Processing Units (GPUs). First, a flexible task decomposition approach, specifically geared towards high parallelization is proposed. Our approach makes it easy to adapt the granularity of parallelism to match the capabilities of the host GPU. Second, all the GPUspecific implementation issues are addressed and several optimizations are proposed. Our design is evaluated through a reference implementation, which is tested on an NVidia GTX980Ti graphics card and shown to speed up 4K-node NoC simulations by almost 280x. Part of this work was previously published in Charif et al. [2017a].

### **1.2** Experimental setup

#### **1.2.1 Hardware implementation**

Although our contributions introduce novel approaches that are interesting from the theoretical standpoint, it is important to make sure that the presented solutions are feasible in terms of hardware.

For this reason, all the new algorithms and mechanisms introduced throughout this manuscript are implemented and synthesized. We present both details about the implementation and synthesis results for every proposal. SystemVerilog was used for all hardware implementations. Full router implementations were based on the Netmaker on-chip router library Mullins [2009], whereas other implementations were written from scratch.

The syntheses were performed using Synopsys Design Compiler and the nangate 45nm library Nangate [2017].

#### **1.2.2** Simulation

For performance and reliability assessment, we use an in-house cycle-accurate simulator based on the design presented in Chapter 5. In addition to being very fast, it models the simulated router very accurately and in compliance with the hardware implementation. Moreover, the outputs of every single module are thoroughly checked throughout the simulations, giving us great confidence in the correctness of the presented results. It is worth mentioning that the simulation process is fully automated (see Appendix B) and that the figures were generated by the simulator and presented with no alterations.

## Part II

# ON THE DESIGN OF DEADLOCK-FREE ROUTING ALGORITHMS FOR WORMHOLE NETWORKS

### Chapter 2

# A Dynamic Sufficient Condition of Deadlock-Freedom for Highly Flexible Routing in Wormhole Networks

#### 2.1 Introduction

A convenient and widely adopted method for avoiding routing deadlocks is to make use of virtual channels Dally [1990], which consist in independent input queues added at each input port, allowing many packets to be multiplexed on the same physical channel. VCs are partitioned into several virtual networks (VNs), such that no cycles can form with-in each VN. Typically, packets of one VN cannot acquire virtual channels from another virtual network, the idea being the suppression of cyclic dependencies between virtual networks. Although this approach has proven to be a simple and effective deadlock-avoidance solution for fault-tolerant systems as well as emerging topologies Chaix et al. [2010], Dubois et al. [2013], its main drawback is that it underutilizes the available virtual channels. In fact, virtual channels are an expensive resource, and if we were able to use them for their performance boosting potential instead of reserving them for the sole purpose of deadlock-avoidance, it would make the extra cost worthwhile.

From a theoretical point of view, while the strict partitioning of virtual channels is sufficient to avoid deadlocks, it is not necessary. In effect, necessary and sufficient conditions of deadlock-freedom Duato [1995], Schwiebert and Jayasimha [1995], Fleury and Fraigniaud [1998] suggest that the absence of cyclic dependencies between channels is not necessary for deadlock avoidance. Moreover, by adding virtual channels the chances of deadlock formation are significantly decreased as explained in Pinkston and Warnakulasuriya [1999]. The currently adopted approaches are therefore overly restrictive, and the resulting resource waste can definitely be avoided.

In this first chapter, we propose a general solution to this issue by introducing a very lowrestrictive sufficient condition of deadlock-freedom that has the major advantage of being formulated using the locally available runtime information in each router. This means that the condition can be verified by the hardware online, and no static reservation of virtual channels for deadlock-avoidance is necessary, allowing for ultra-flexible high-performance routing algorithms to be designed.

Based on this condition, an intuitive, topology-agnostic routing algorithm design framework comprising the minimum set of rules that routing algorithms should fulfill to satisfy our deadlock-freedom condition is presented.

We provide details on the implementation of our approach in hardware, and highlight its wide range of applicability through several case studies. In addition to fault-tolerant routing, which we showcase in the first part of this chapter, we also demonstrate that the presented condition of deadlock-freedom can be used to enhance the performance of existing routing algorithms by relaxing the restrictions on their virtual channel usage. Finally, we show how our condition can provide a more intuitive understanding of already existing routing algorithms, as we easily reconstruct a maximally adaptive routing algorithm for the 2D topology, which was previously proven deadlock-free using channel dependency graphs and classic necessary and sufficient conditions of deadlock-freedom.

#### 2.2 State-of-the-art

#### 2.2.1 VC-based deadlock avoidance

The vast majority of routing algorithms that require virtual channels for deadlock avoidance have been adopting a conservative approach, which consists in a strict partitioning of virtual channels at design time such that each virtual channel has its own routing rules that packets must follow. Usually, blocked packets can only request one of the two virtual channels at a time. When fault-tolerance is required, moving from one virtual channel to the other is permitted only in one direction (e.g. in increasing order).

Example of recent fault-tolerant routing algorithms using this same approach include Ebrahimi et al. [2012], Chaix et al. [2010]. This method has also been employed in the context of 3D-NoCs Dubois et al. [2013], Salamat et al. [2016b], where there is always a strict separation between Upward and Downward packets Dubois et al. [2013], Eastward and Westward packets Salamat et al. [2016b], etc.

The issue with this approach is that the virtual channels are underutilized because packets have to wait for one specific VC at all times, even when other VCs are idle. In context of fault-tolerance, in order to provide all packets with enough flexibility to route around faults, some algorithms require that all packets start routing in the first VC, so that they get a chance to move to a higher VC when necessary Ebrahimi et al. [2012]. This means that the second VC remains entirely idle in the absence of faults, which is a waste of resources.

However, because the classic method simply consists in splitting the network into two disjoint deadlock-free networks that use familiar routing algorithms Glass and Ni [1992], it makes it easy to build new routing solutions by combining several previously known deadlock-free turn models. In this thesis, we aim at improving VC utilization without jeopardizing this important property.

#### 2.2.2 Necessary and sufficient conditions of deadlock-freedom

It has long been known that the suppression of cyclic dependencies is not necessary for deadlockfreeness Pinkston and Warnakulasuriya [1999]. Several necessary and sufficient conditions of deadlock-freedom have been proposed in the context of wormhole routing Verbeek and Schmaltz [2011], Duato [1995], Duato [1997], Fleury and Fraigniaud [1998]. These are all excellent for proving the deadlock-freedom of an existing algorithm and even for building formal verification tools Taktak et al. [2008].

However, they can hardly be used to construct new algorithms. For instance, the authors in Kumar et al. [2014] have recently proposed a routing algorithm for NoCs that aims at reducing the restrictions on the VCs that can be used. The algorithm uses Duato's necessary and sufficient condition Duato [1995] to prove the network deadlock-free despite the presence of cyclic dependencies. The resulting algorithm is highly flexible, but it can be difficult to have an intuitive understanding of how it works without thinking in terms of dependency graphs. There is therefore a clear need for a design methodology that makes it possible to systematically build such algorithms.

Using our design methodology, we will reconstruct the routing algorithm in Kumar et al. [2014] from scratch, and show how our approach can help explain it in a more intuitive way.

#### 2.2.3 Routing algorithm design frameworks

Our methodology is based on a sufficient condition of deadlock-freedom that is expressed using local information, which is made available through a virtual channel tagging mechanism during runtime. This makes our condition verifiable by the hardware dynamically, allowing for a high degree of flexibility.

The idea of using runtime information for deadlock avoidance is not new. Early works on adaptive routing, such as Dally and Aoki's algorithm Dally and Aoki [1993], also make use of a similar labeling mechanism. More notably, in Boppana and Chalasani [1996], the authors propose a framework for designing adaptive routing algorithms. The terminology as well as many of the concepts they propose are quite similar to our proposal. However, there are fundamental differences between our methodology and these works. First, both Dally and Aoki [1993] and Boppana and Chalasani [1996] avoid deadlocks by suppressing cyclic dependencies from the packet wait-for graphs. Our condition is less restrictive and allows the presence of cyclic dependencies both in the channel dependency graph and the packet wait-for graph. In

this regard, our deadlock-freedom condition is closer to the necessary and sufficient condition as formulated in Schwiebert and Jayasimha [1995]. Like Boppana and Chalasani [1996], our methodology supports class upgrades to further increase routing flexibility and enhance virtual channel utilization. However, our framework also supports class downgrades, pushing the level routing freedom even further. More importantly, our formulation is specifically tailored for on-chip networks, and can use the already available deadlock-free routing algorithms as building blocks. We also provide several details on the implementation of our deadlock-avoidance mechanisms in hardware.

More recently, in Ebrahimi and Daneshtalab [2017], the authors have introduced a new theory for designing deadlock-free routing algorithms. It is a formal generalization of the method used to construct several routing algorithms such as Ebrahimi et al. [2013a]. Because it is based on the partitioning of network channels as in Dally and Seitz [1988], it requires the absence of cyclic dependencies between channels for deadlock-freedom, limiting the utilization of VCs compared to the approach that we propose.

#### 2.3 Routing algorithm design methodology

In this section, we introduce the proposed routing methodology by example. After defining the network architecture, we design a new fault-tolerant routing algorithm for 2D Mesh NoCs and highlight the differences with the traditional static approaches.

#### 2.3.1 Switch model

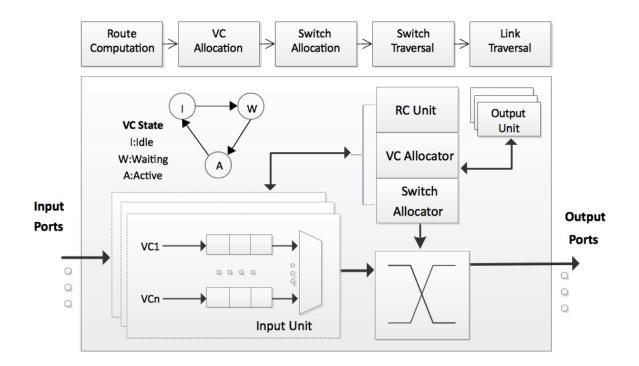

We consider a typical input-buffered wormhole router such as the one shown in fig. 2.1. Several Virtual Channels (VCs) may be available per input port. Routing a packet is performed in 5 steps. When the first (head) flit of a packet is read from an input port, it is buffered in the input VC that was allocated to it by the upstream router and, in the same cycle, the Route Computation Unit selects the next output port to which the packet should be forwarded. The input VC, which was in "Idle" state, moves to "Waiting" state and waits until the VC Allocator grants it an Idle VC in the downstream router. When a downstream VC is acquired, the input VC enters the "Active" state. Each flit of the packet then waits for the Switch Allocator to grant it permission

Figure 2.1: Router architecture.

to traverse the Crossbar and reach the output port, provided that there are enough free buffers to store the flit in the downstream VC. When a flit acquires the switch, a credit signal is sent to the upstream router, indicating that there is a newly available buffer in this VC. Finally, the flit traverses the link to reach the next router. When the last (tail) flit of a packet leaves the router, the input VC goes back to the "Idle" state and becomes ready to receive new packets.

The output unit (fig. 2.1) maintains a structure representing the status of each downstream VC. The structure representing one downstream VC has the following fields:

- State: Idle or Active.

- Credits: Number of free buffers.

- Tag: A signed integer used by the algorithm. Its usage will be explained later.

It is important to note that the only strict assumption that we make on the router's architecture is that the output port is selected before VC allocation is performed. All the other aspects, such as the allocator types, pipelining, speculative switch allocation, have no affect on the validity of our routing approach.

#### 2.3.2 Fault model

A faulty network is modeled by a set of permanently faulty unidirectional links. This model is often used to evaluate fault-tolerant routing algorithms as it demonstrates their ability to route packets in a maze-like irregular topology.

In practice, this can correspond to either a link actually failing, or input and output ports being disabled due to faults in their control logic, e.g. stuck-at faults. We consider that in the presence of faults in the central logic (allocators, crossbar, etc.) the router simply disables all of its input and output ports, so the same model can be employed to model node failure as well.

#### 2.3.3 Example design: Fault-tolerant routing in 2D mesh NoCs

We consider, as an example, that the routers are interconnected in a 2D Mesh topology. Therefore, each router has four input/output ports connecting it to at most four neighboring routers (North, South, East, West), and one input/output ports (Local) connecting it to a network interface (NI).

The first step in designing a routing algorithm using our methodology is to identify a set of **routing classes**, such that each routing class is associated with one cycle-free routing function. The routing function supplies a set of physical channels (output ports) that the packet can occupy. It can achieve cycle-freedom in two different ways: Either the set of physical channels supplied by the routing function cannot form a cycle (e.g. take only the physical channels of one dimension) as in Ebrahimi and Daneshtalab [2017], or the physical channels can form a cycle but they are supplied in a specific order (e.g. the turn models Glass and Ni [1992]).

In Section 2.7, we will present an algorithm that uses the former approach. In this example, however, because we want to maximize the routing options within each class, we use the turn model Glass and Ni [1992] as a routing function.

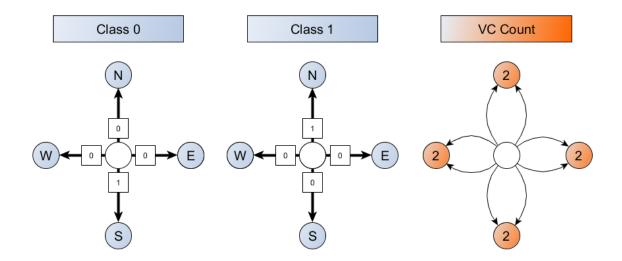

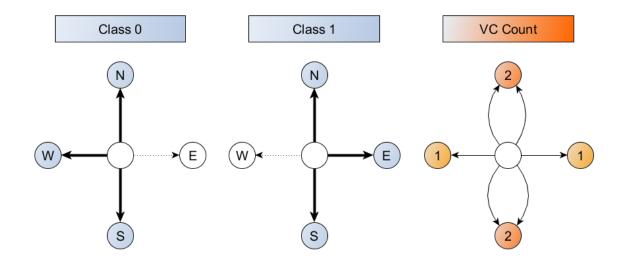

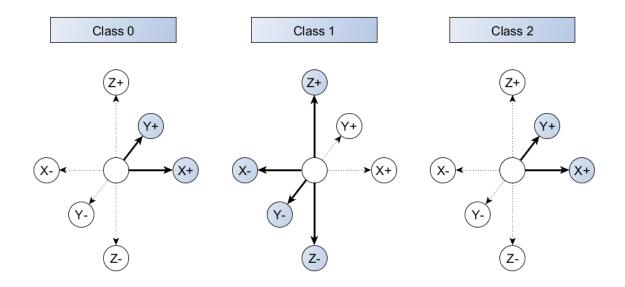

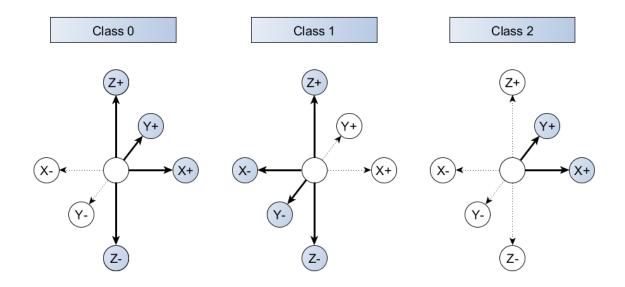

Here, we chose to use the non-minimal South-last and North-last turn models to be assigned to routing classes 0 and 1 respectively. Fig. 2.2 shows the physical channels used within each class, along wih the numbering that indicates the order in which the physical channels must be traversed to suppress cycles, as per Glass and Ni [1992]. We can see that all four physical channels are used by both classes.

Figure 2.2: Physical channels used by the two classes of the example algorithm.

From the set of physical channels, we can deduce the minimum number of virtual channels that are required in each direction. The VC count in one physical channel, as shown in Fig. 2.2, simply corresponds to the number of classes that use the same physical channel. Our algorithm will require two VCs in all directions.

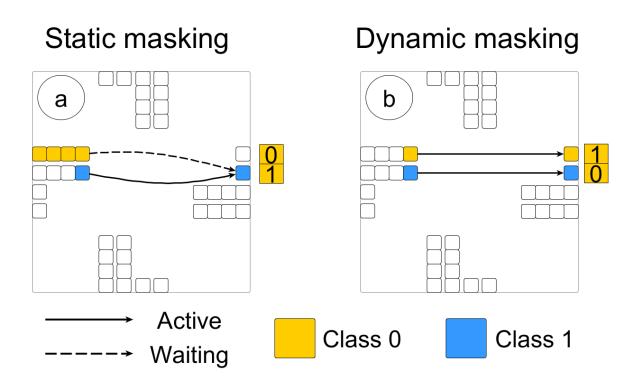

Thus far the setup is analogous to that uses by many related works, such as Chaix et al. [2010]. We intentionally chose similar routing functions to make it easier to highlight the differences. The first key difference is that unlike the classic approach, the routing functions are not assigned to specific virtual channels. Instead, each packet carries its class number, and this class number is used by the route computation unit to select the appropriate routing function, regardless of which virtual channel the packet is currently occupying. This also means that the virtual channels that packets can occupy are never known a priori, which is the main factor in achieving a higher throughput than the classic approaches. The VC acquisition rules are determined dynamically following the rules described in the rest of this section.

When a packet acquires a downstream VC, it must set the corresponding *Tag* field in the output unit to its class number. The following rule, which corresponds to our sufficient condition of deadlock-freedom, is enough to guarantee deadlock-free operation.

**Rule 2.1.** "A packet may not request an output port unless at least one of the virtual channels associated with that port is either free, or tagged with a number higher than or equal to its class

#### number".

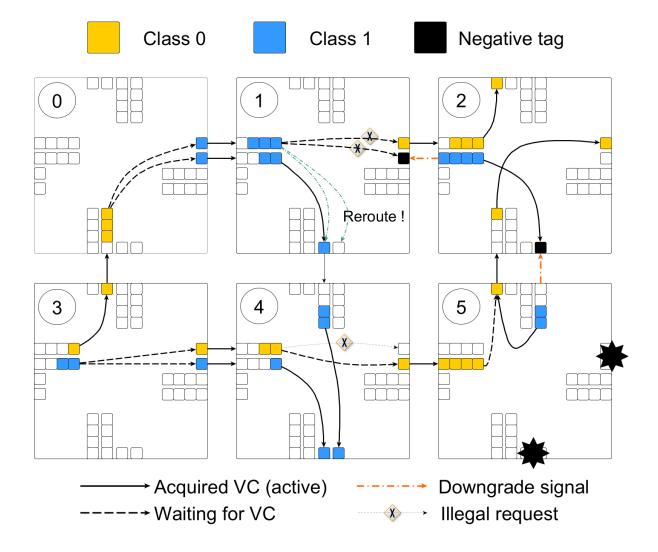

For our example case, this means that packets of class 1 cannot wait for an output port in which all the channel tags are less than 1. Consider the class 1 packet coming from the west port of router 3 in Fig. 2.3. It is able to request the east port because there is one VC tagged with "1" in that port. Similarly, the packet coming from the south port of router 0 can legally request the east port because it is occupied by packets of class 1, which is higher than class 0. The intuition behind this rule is simple. By ensuring that packets of class 1 always have a dependency in class 1, and knowing that all the packets in class 1 are routed using an acyclic turn model, we guarantee that packets of class 1 dynamically form an acyclic dependency chain. Packets of class 0 either have all their dependencies in class 0, in which case they cannot form cycles because the South-last turn model is cycle-free, or they may have class 1 dependencies, leading forcibly to the dynamic escape path formed by class 1 packets.

Therefore, the first rule guarantees at least one escape for every packet in the network.

It is very important to understand that while only one of the virtual channels of the requested port needs to have a higher or equal tag, nothing is done to force the packet to wait for that one VC specifically. Going back to our example in Fig. 2.3, the class 1 packet coming from the west port of router 3 may very well acquire the top-most VC, which is held by a class 0 packet about to leave router 4, even though the port was selected because of the second VC from the top, which is tagged with "1". This means that the packet was not waiting for only one VC, but for both VCs, including the one tagged with a lower class number. This is a crucial point in achieving high performance.

While rule 2.1 ensures deadlock-freedom, there are a few issues that need to be addressed. In fig. 2.3, there is a packet coming from the west port of router 4 and requesting the east port, which has one free VC. If this free VC is granted to this packet, the port will be full of class 0 tags. Consequently, if a class 1 packet arrived at router 4 and wanted to go east, it would not be able to request the east port, because otherwise it would violate rule 2.1. Rule 2.2 imposes one restriction on the VC requests to alleviate this issue.

**Rule 2.2.** "In every output port, there must be at least one free virtual channel for every class higher than the greatest tag in that port".

Figure 2.3: An example packet configuration.

In other words, the VC allocator should not grant all the virtual channels of a port to class 0 packets. Therefore, the 2-flit class 0 packet in the west port of router 4 (fig. 2.3) cannot request the free VC at the east port and has to wait for the class 0 packet to leave the router. However, note that router 0 has allocated all the virtual channels of its east port to class 1 packets. This does not violate the rule since there are 0 classes higher than 1, and therefore 0 VCs need to be kept free. We will show how this rule can be implemented in the next section.

#### **2.3.4 Upgrades and Downgrades**

To provide packets with even more routing freedom, our framework also supports class changing. Packets may prefer to change their class for various reasons. The most obvious use case is when their current class can no longer provide the necessary output channels to make progress towards the desitnation, either because of faults, or because they are not supplied by the routing function.

This feature is therefore a great contributor to fault-tolerance, as packet can either upgrade or downgrade to possibly get access to more physical channels and route around faults. A second case where packets may decide to move to another class is when all the physical channels they need to reach their destination are provided by a higher class. In this case, they may as well upgrade, as they will gain access to more virtual channels, as per rule 2.2.