# Balancing energy, security and circuit area in lightweight cryptographic hardware design

Rodrigo Portella

## ▶ To cite this version:

Rodrigo Portella. Balancing energy, security and circuit area in lightweight cryptographic hardware design. Cryptography and Security [cs.CR]. Université Paris sciences et lettres, 2016. English. NNT: 2016PSLEE036. tel-01743786

# HAL Id: tel-01743786 https://theses.hal.science/tel-01743786v1

Submitted on 26 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT

de l'Université de recherche Paris Sciences et Lettres PSL Research University

Préparée à l'Ecole normale supérieure de Paris

Balancing Energy, Security and Circuit Area in Lightweight Cryptographic Hardware Design

Ecole doctorale n° 386

SCIENCES MATHEMATIQUES DE PARIS CENTRE

Spécialité INFORMATIQUE

Soutenue par Rodrigo PORTELLA le 27 Octobre 2016

Dirigée par David NACCACHE

#### **COMPOSITION DU JURY:**

M. GUILLEY Sylvain

TELECOM-ParisTech, Rapporteur

M. CLAVIER Cristophe Université de Limoges, Rapporteur

M. GOUBIN Louis Université de Versailles-St-Quentin-en-Yvelines, Membre du jury

M. VUILLEMIN Jean École normale supérieure, Membre du jury

M. KOCHER Paul Cryptography Research, Membre du jury

Mme. TRICHINA Elena Cryptography Research, Membre du jury

# Balancing Energy, Security and Circuit Area in Lightweight Cryptographic Hardware Design

# Thèse de Doctorat

en vue de l'obtention du grade de

# Docteur de l'École normale supérieure (spécialité informatique)

présentée et soutenue publiquement le 27 octobre 2016 par

### RODRIGO PORTELLA DO CANTO

## devant le jury composé de :

Directeur de thèse : David Naccache (École normale supérieure)

Rapporteurs: Christophe Clavier (University of Limoges)

Sylvain Guilley (Télécom ParisTech)

Examinateurs: Louis Goubin (University of Versailles-Saint-Quentin-en-Yvelines)

Paul Kocher (Rambus Cryptography Research) Elena Trichina (Rambus Cryptography Research)

Jean Vuillemin (École normale supérieure)

# Balancing Energy, Security and Circuit Area in Lightweight Cryptographic Hardware Design

# Thèse de Doctorat

en vue de l'obtention du grade de

# Docteur de l'École normale supérieure (spécialité informatique)

présentée et soutenue publiquement le 27 octobre 2016 par

### RODRIGO PORTELLA DO CANTO

## devant le jury composé de :

Directeur de thèse : David Naccache (École normale supérieure)

Rapporteurs: Christophe Clavier (University of Limoges)

Sylvain Guilley (Télécom ParisTech)

Examinateurs: Louis Goubin (University of Versailles-Saint-Quentin-en-Yvelines)

Paul Kocher (Rambus Cryptography Research)

Elena Trichina (Rambus Cryptography Research)

Jean Vuillemin (École normale supérieure)

# **ACKNOWLEDGEMENTS**

First and foremost I want to express my sincere gratitude to Prof. *David Naccache*, for his support, dedication and patience. *David* has always been an incentive to me. He never let me lose focus and always made sure I kept on top of my work, which taught me how to become a better researcher. Without the encouragement of Prof. Naccache, this work would not have been completed.

I am mostly grateful to *Louis Goubin*, *Paul Kocher*, *Elena Trichina*, and *Jean Vuillemin* for agreeing to serve in this thesis committee. I express my particular gratitude to my thesis referees *Christophe Clavier* and *Sylvain Guilley* for their availability and dedication. I am very honored to have such a prestigious committee.

I would like to thank my colleagues at Rambus and Cryptography Research for having always encouraged me to continue with my research. A special thanks to *Elke De Mulder* for creative time off discussing innovative projects and supporting me to pursue this thesis. I would like to show my appreciation to *Roberto Rivoir* and *Pankaj Rohatgi* whose understanding gave me the confidence to finish this work. A very special thank you to *Craig Hampel*, who continuously believed in my work and was always eager to help.

I would also like to show my appreciation to the co-authors of the publications I worked with. All colleagues I had the pleasure to collaborate with were truly cooperative and my exchange with them was very constructive. A special thanks to *Diana Ştefania Maimuţ* and *Roman Korkikian* who were always available to support and contribute to my research. More than colleagues, *Diana* and *Roman* have become dear friends.

I would like to dedicate this work to some very special people who provided endless support and understanding throughout the development of this work. To my mother *Sônia Portella do Canto* who always believed in me and encouraged me to pursue my Ph.D. studies. Your endless dedication made me the man I am today. You are the bravest person I have ever met. The least I could do to pay you back a small fraction of the love, understanding and guidance you gave me was to make you proud. I hope I succeeded in doing so. Thank you for all your dedication and love. To my second mother *Natacha Laniado*, I cannot express how grateful I am of having you as a friend. Without you this thesis would have not been possible to complete. All the support you gave me, and all the issues you dealt with were outstanding. You are the most authentic and energetic person I have ever met and I love sharing good times with you.

To my beautiful and cheerful wife *Daiane Oakes*, I am thankful to eternity and beyond for having you in my life. You make me a better man every day. The grace in your eyes and the delight of your smile makes me the happiest person alive. Thank you for all your love and support, I love you. To my sisterin-law *Rachel Oakes* and to my mother-in-law *Leonilda Ferreira*, thank you for being a family to me and loving me as one of yours.

Last but not the least, I express all my gratitude to *Crégolas*, for being a true companion and for always sharing love and attention.

Rodrigo Portella do Canto

Nada é por acaso.

– Daiane Oakes

# **C**ONTENTS

| 1 | Intr | oductio |           |                                     | 13 |

|---|------|---------|-----------|-------------------------------------|----|

|   | 1.1  | Termi   | nology .  |                                     | 14 |

|   | 1.2  | Hardy   | vare Syst | em Security                         | 17 |

|   | 1.3  | Notati  | ions and  | Conventions                         | 18 |

|   | 1.4  | Finite  | Fields A  | rithmetic                           | 19 |

|   | 1.5  | Thesis  | Outline   |                                     | 22 |

|   | 1.6  | Public  | cations . |                                     | 23 |

|   |      |         |           |                                     |    |

| 2 | Fron |         |           | o a Cryptosystem                    | 26 |

|   | 2.1  | Integr  |           | ruit and Logic Design               | 27 |

|   |      | 2.1.1   |           | ction                               | 27 |

|   |      | 2.1.2   |           | esign                               | 27 |

|   |      | 2.1.3   | The CM    | IOS Transistor                      | 30 |

|   |      | 2.1.4   | CMOS 1    | Logic                               | 31 |

|   |      |         | 2.1.4.1   | The Inverter                        | 32 |

|   |      |         | 2.1.4.2   | The NAND Gate                       | 33 |

|   |      |         | 2.1.4.3   | Compound Gates                      | 34 |

|   |      |         | 2.1.4.4   | Tri-state Buffers                   | 34 |

|   |      | 2.1.5   | CMOS I    | I-V Characteristics                 | 35 |

|   |      |         | 2.1.5.1   | CMOS Electrical Properties          | 35 |

|   |      |         | 2.1.5.2   | Non-Ideal I-V Effects               | 37 |

|   | 2.2  | Hardy   | vare-Base | ed Cryptosystems                    | 41 |

|   |      | 2.2.1   | Introdu   | ction                               | 41 |

|   |      | 2.2.2   | Definiti  | ons                                 | 42 |

|   |      | 2.2.3   | Hardwa    | are Design Architecture             | 42 |

|   |      |         | 2.2.3.1   | Throughput and Latency              | 43 |

|   |      |         | 2.2.3.2   | Area                                | 43 |

|   |      | 2.2.4   | Cryptog   | graphic Hardware Design             | 44 |

|   |      |         | 2.2.4.1   | Iterative Looping                   | 45 |

|   |      |         | 2.2.4.2   | Loop Unrolling                      | 45 |

|   |      |         | 2.2.4.3   | Pipelining                          | 46 |

|   |      |         | 2.2.4.4   | Sub-Pipelining                      | 48 |

|   |      |         | 2.2.4.5   | Pseudo-Random Sequences in Hardware | 49 |

|   | 2.3  | Privat  | e-Kev Cr  | yptosystems                         | 50 |

|   |      | 2.3.1   |           | ta Encryption Standard              | 50 |

|   |      | 2.3.2   |           | vanced Encryption Standard          | 50 |

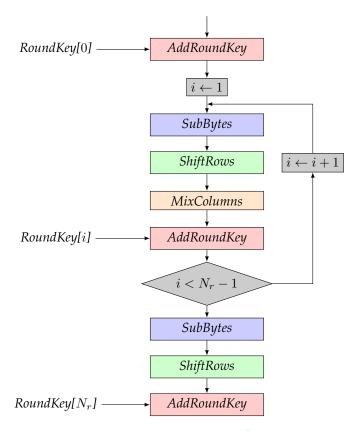

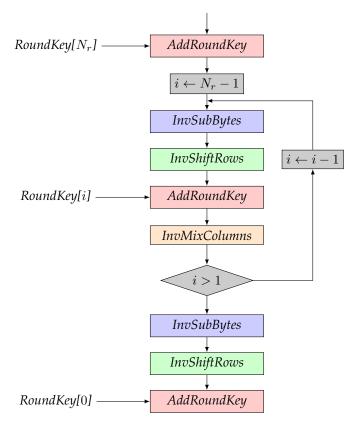

|   |      |         | 2.3.2.1   | AES Rounds                          | 51 |

|   |      |         | 2.3.2.2   | AES in Hardware (FPGA and ASIC)     | 53 |

|   | 2.4  | Crypt   |           | Hash Functions                      | 57 |

|   |      | 2.4.1   | U 1       | ction                               | 57 |

|   |      | 2.4.2   |           | Requirements of Hash Functions      | 58 |

|   |      |         | 2.4.2.1   | Preimage Resistance                 | 58 |

|   |      |         | 2.4.2.1   | Second Preimage Resistance          | 58 |

|   |      |         | 2.4.2.2   | Collision Resistance                | 59 |

|   |      |         | 2.4.2.3   | Overview of Hash Algorithms         | 60 |

|   |      | 2.4.3   |           | ure Hash Algorithm 1                | 60 |

|   |      | 4.4.3   | 1116 260  | uie nash Aigunull I                 | UU |

|   |      | 2.4.4          |               | ure Hash Algorithm 2 $\dots \dots \dots \dots \dots $ 6                    |                      |

|---|------|----------------|---------------|----------------------------------------------------------------------------|----------------------|

|   |      | 2.4.5          | <b>Implem</b> | entation Tradeoffs and Design Methodologies 6                              | 52                   |

|   |      | 2.4.6          |               |                                                                            | 62                   |

|   |      | 2.4.7          | FPGA-E        | Based Cryptography $\overset{\circ}{}_{\cdot}$ $\overset{\circ}{}_{\cdot}$ | 53                   |

|   |      | 2.4.8          |               |                                                                            | 53                   |

|   |      |                |               |                                                                            |                      |

| 3 | Cry  | ptograp        | hic Hard      | lware Acceleration and Power Minimization 6                                | 66                   |

|   | 3.1  | BCH v          | with Barr     | ett Polynomial Reduction                                                   | 57                   |

|   |      | 3.1.1          |               |                                                                            | 67                   |

|   |      | 3.1.2          |               |                                                                            | 67                   |

|   |      |                | 3.1.2.1       |                                                                            | 58                   |

|   |      | 3.1.3          |               |                                                                            | 59                   |

|   |      | 0.1.0          | 3.1.3.1       |                                                                            | 59                   |

|   |      |                | 3.1.3.2       |                                                                            | 59                   |

|   |      |                |               |                                                                            | 70                   |

|   |      |                | 3.1.3.3       |                                                                            |                      |

|   |      |                | 3.1.3.4       |                                                                            | 71                   |

|   |      |                | 3.1.3.5       |                                                                            | 73                   |

|   |      | 3.1.4          |               |                                                                            | 75                   |

|   |      |                | 3.1.4.1       |                                                                            | 75                   |

|   |      |                | 3.1.4.2       |                                                                            | 75                   |

|   |      |                | 3.1.4.3       | BCH Decoding                                                               | 76                   |

|   |      |                | 3.1.4.4       | Syndrome                                                                   | 77                   |

|   |      |                | 3.1.4.5       | Error Location                                                             | 77                   |

|   |      |                | 3.1.4.6       | Peterson's Algorithm                                                       | 77                   |

|   |      |                | 3.1.4.7       |                                                                            | 77                   |

|   |      | 3.1.5          | Implem        |                                                                            | 78                   |

|   |      |                | 3.1.5.1       |                                                                            | 78                   |

|   |      |                | 3.1.5.2       |                                                                            | 79                   |

|   |      |                | 3.1.5.3       | 1                                                                          | 79                   |

|   |      |                | 3.1.5.4       |                                                                            | 30                   |

|   | 3.2  | Mana           |               |                                                                            | 31                   |

|   | J.2  | 3.2.1          |               |                                                                            | 31                   |

|   |      | 3.2.2          |               |                                                                            | 31                   |

|   |      |                |               |                                                                            | 32                   |

|   |      | 3.2.3          |               |                                                                            | 34                   |

|   |      | 3.2.4<br>3.2.5 |               |                                                                            | 54<br>34             |

|   |      | 3.2.3          | riobabi       | listic Strategies                                                          | )4                   |

| 4 | Side | -Chan          | nel Attac     | ks and Hardware Countermeasures                                            | 36                   |

|   | 4.1  |                |               |                                                                            | 37                   |

|   | 4.2  |                |               |                                                                            | 38                   |

|   | 4.3  |                |               |                                                                            | 39                   |

|   | 4.4  |                |               |                                                                            | 93                   |

|   | 2.1  | 4.4.1          |               |                                                                            | 93                   |

|   |      | 4.4.2          |               |                                                                            | 93                   |

|   |      | 4.4.3          |               |                                                                            | 94                   |

|   |      | 1.1.5          | 4.4.3.1       |                                                                            | )4                   |

|   |      |                | 4.4.3.2       |                                                                            | )4                   |

|   |      |                |               |                                                                            | 9 <del>4</del><br>97 |

|   |      |                | 4.4.3.3       |                                                                            |                      |

|   |      |                | 4.4.3.4       |                                                                            | 97                   |

|   |      |                | 4.4.3.5       |                                                                            | 98                   |

|   |      | 4.4.4          | _             | $\Gamma$                                                                   | 99                   |

|   |      | 4.4.5          |               | entation Results                                                           |                      |

|   | 4.5  |                | 0 1           | ally Secure On-Chip Firewalling                                            |                      |

|   |      | 4.5.1          |               | ction                                                                      |                      |

|   |      | 4.5.2          | -             | ing Attack Surfaces on NoCs                                                |                      |

|   |      |                | 4.5.2.1       | Request Path                                                               |                      |

|   |      |                | 4.5.2.2       | Firewall Reprogramming Path                                                | )3                   |

|   |      |                | 4.5.2.3       | Firewall State at Rest                                                     | )4                   |

|   |     | 4.5.3      | Integration of Security Resources into an SoC                                                   |     |

|---|-----|------------|-------------------------------------------------------------------------------------------------|-----|

|   |     |            | 4.5.3.1 Securing the Request Path                                                               |     |

|   |     |            | 4.5.3.2 Securing the Firewall                                                                   |     |

|   |     | 4.5.4      | Access Control Firewalling to On-Chip Resources                                                 |     |

|   |     |            | 4.5.4.1 Endpoint versus NoC Firewalling                                                         |     |

|   |     |            | 4.5.4.2 Cryptographically Secure Access Control                                                 |     |

|   |     |            | 4.5.4.3 CSAC Synthesis Results                                                                  |     |

|   |     |            | 4.5.4.4 FPGA Implementation                                                                     |     |

|   | 4.6 |            | cal Instantaneous Frequency Analysis Experiments                                                |     |

|   |     | 4.6.1      | Introduction                                                                                    |     |

|   |     | 4.6.2      | Preliminaries                                                                                   |     |

|   |     |            | 4.6.2.1 The Hilbert Huang Transform                                                             |     |

|   |     |            | 4.6.2.2 AES Hardware Implementation                                                             |     |

|   |     | 4.6.3      | Hilbert Huang Transform and Frequency Leakage                                                   |     |

|   |     |            | 4.6.3.1 Why Should Instantaneous Frequency Variations Leak Information?                         |     |

|   |     |            | 4.6.3.2 Power consumption of one AES round                                                      |     |

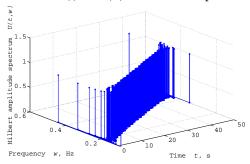

|   |     |            | 4.6.3.3 Hilbert Huang Transform of an AES Power Consumption Signal                              |     |

|   |     | 4.6.4      | Correlation Instantaneous Frequency Analysis                                                    |     |

|   |     |            | 4.6.4.1 Correlation Instantaneous Frequency Analysis on Unprotected Hardware                    |     |

|   |     |            | 4.6.4.2 Correlation Instantaneous Frequency Analysis in the Presence of DVS                     | 124 |

| _ | 7   | Vector     | dodgo Duotogolo and Authorticated Engagemtion                                                   | 126 |

| 5 | 5.1 |            | <b>Ledge Protocols and Authenticated Encryption</b> -Key Based Lightweight Swarm Authentication |     |

|   | 5.1 | 5.1.1      |                                                                                                 |     |

|   |     |            | Introduction                                                                                    |     |

|   |     | 5.1.2      | Preliminaries                                                                                   |     |

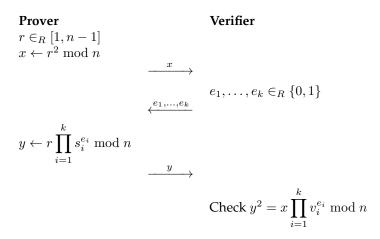

|   |     |            | 5.1.2.1 Fiat-Shamir Authentication Protocol                                                     | 12/ |

|   |     | 5.1.3      | 5.1.2.2 Topology-Aware Distributed Spanning Trees                                               | 128 |

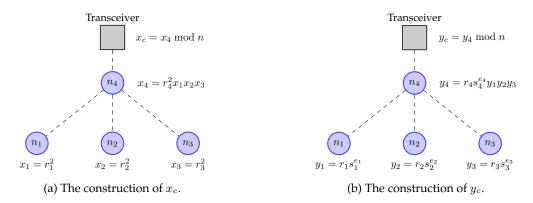

|   |     | 5.1.3      | Distributed Fiat-Shamir Authentication                                                          |     |

|   |     |            | 5.1.3.1 The Approach                                                                            |     |

|   |     | F 1 4      | 5.1.3.2 Back-up Authentication                                                                  |     |

|   |     | 5.1.4      | Security                                                                                        |     |

|   |     |            | 5.1.4.1 Soundness                                                                               |     |

|   |     |            | 5.1.4.2 Zero-knowledge                                                                          |     |

|   | г о | Tl O       | 5.1.4.3 Security Analysis                                                                       |     |

|   | 5.2 |            | ffset Merkle-Damgård Authenticated Cipher                                                       |     |

|   |     | 5.2.1      | Introduction                                                                                    |     |

|   |     | 5.2.2      | Preliminaries                                                                                   |     |

|   |     |            | 5.2.2.1 Security Definitions and Goals                                                          |     |

|   |     |            | 5.2.2.2 Quantitative Security Level of OMD-SHA256                                               |     |

|   |     |            | 5.2.2.3 Quantitative Security Level of OMD-SHA512                                               |     |

|   |     |            | 5.2.2.4 Security Proofs                                                                         |     |

|   |     |            | 5.2.2.5 Generalization of OMD Based on Tweakable Random Functions                               |     |

|   |     | <b>500</b> | 5.2.2.6 Instantiating Tweakable RFs with PRFs                                                   |     |

|   |     | 5.2.3      | Specification of OMD                                                                            |     |

|   |     |            | 5.2.3.1 The OMD Mode of Operation                                                               |     |

|   |     |            | 5.2.3.2 OMD-SHA256: Primary Recommendation for Instantiating OMD                                |     |

|   |     |            | 5.2.3.3 OMD-SHA512: Secondary Recommendation for Instantiating OMD                              |     |

|   |     |            | 5.2.3.4 Compression Functions of SHA-256 and SHA-512                                            | 149 |

| 6 | Con | clusion    |                                                                                                 | 154 |

| A | Cod | e: Barro   | ett's Algorithm for Polynomials                                                                 | 177 |

| P | •   |            | The Contract                                                                                    | 150 |

| В | Com | pressio    |                                                                                                 | 179 |

|   | R.I |            |                                                                                                 | 179 |

|   |     | B.1.1      | The Compression Function of SHA-256                                                             |     |

|   |     | B.1.2      | The Compression Function of SHA-512                                                             | 180 |

# LIST OF FIGURES

| 1.1  | The hierarchical diagram of the different fields of cryptography                                | 14  |

|------|-------------------------------------------------------------------------------------------------|-----|

| 1.2  | The broad fields of cryptography [MvV97]                                                        | 15  |

| 1.3  | The hierarchical diagram of the different fields of cryptanalysis [PP09]                        | 17  |

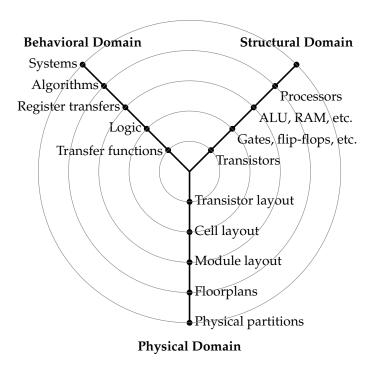

| 2.1  | Gajski-Kuhn <i>y</i> -chart [GK83]                                                              | 28  |

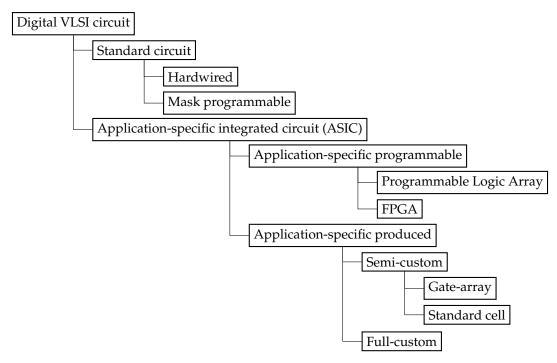

|      | The different design styles of a digital VI CI singuit [CPC+06]                                 | 29  |

| 2.2  | The different design styles of a digital VLSI circuit [GBC+96]                                  |     |

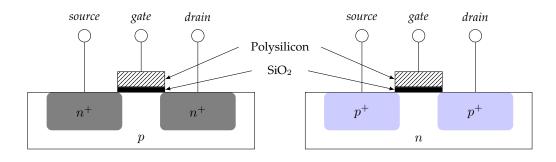

| 2.3  | The two types of CMOS devices.                                                                  | 31  |

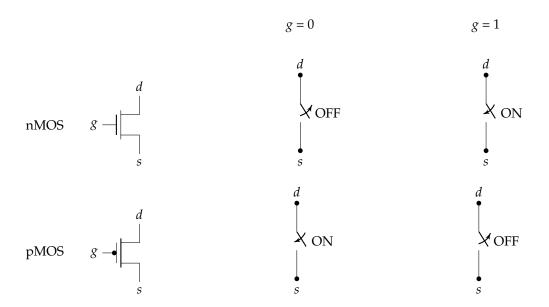

| 2.4  | CMOS transistor symbols and switch levels.                                                      | 32  |

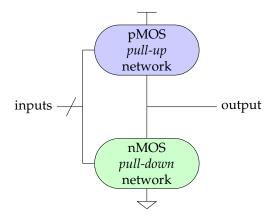

| 2.5  | General logic gate using <i>pull-up</i> and <i>pull-down</i> networks                           | 32  |

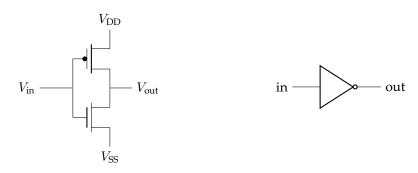

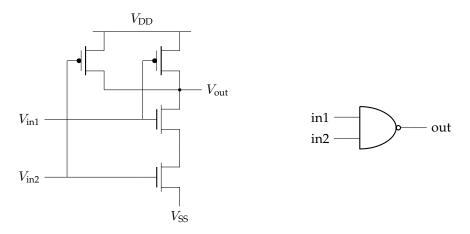

| 2.6  | CMOS inverter gate schematic and symbol                                                         | 33  |

| 2.7  | CMOS NAND gate schematic and symbol                                                             | 33  |

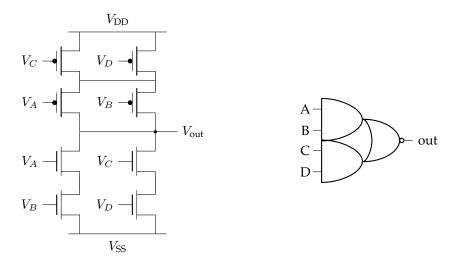

| 2.8  | CMOS AND-OR-INVERTER-22 schematic and symbol                                                    | 34  |

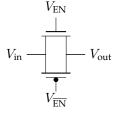

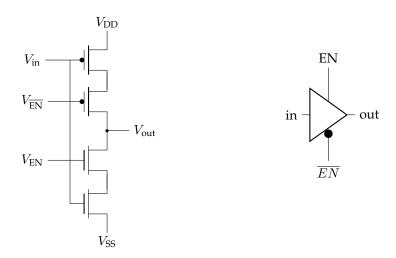

| 2.9  | CMOS transmission gate                                                                          | 34  |

| 2.10 | CMOS tri-state buffer schematic and symbol                                                      | 35  |

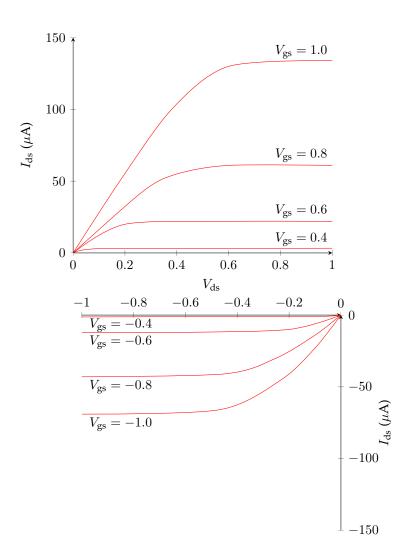

| 2.11 | I-V characteristics of ideal nMOS (upper graph) and pMOS (lower graph) transistors              |     |

|      | [WH10]                                                                                          | 38  |

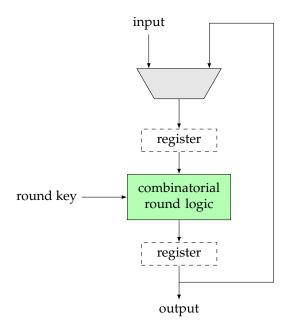

| 2.12 | General Iterative Looping architecture                                                          | 45  |

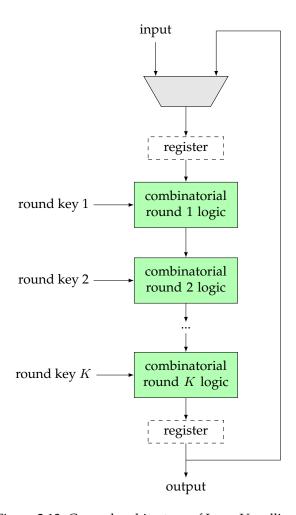

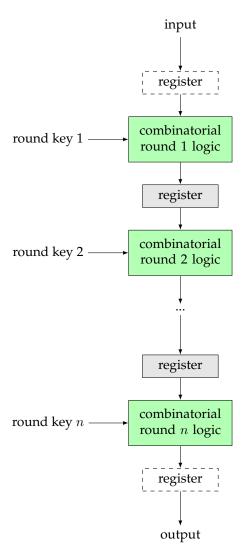

|      | General architecture of Loop Unrolling                                                          | 46  |

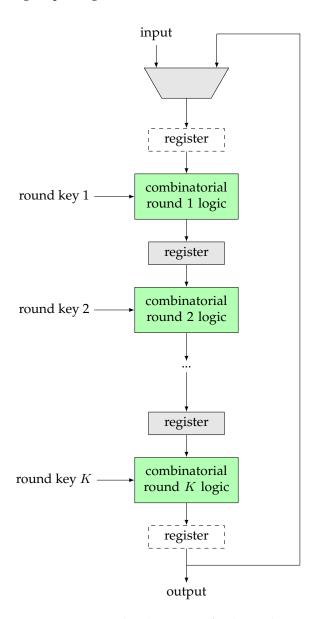

|      | General architecture of Pipelining.                                                             | 47  |

|      | General architecture of Sub-Pipelining                                                          | 48  |

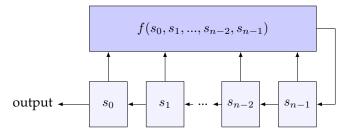

|      | General architecture of a Feedback Shift Register (FSR).                                        | 49  |

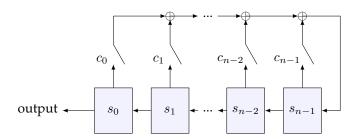

|      | General architecture of a Linear Feedback Shift Register (LFSR).                                | 49  |

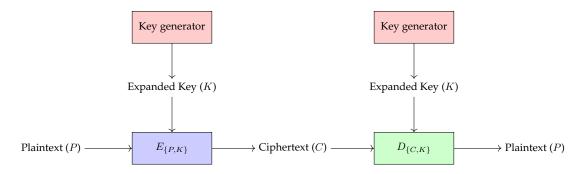

|      | Secret-key cryptography (overview)                                                              | 50  |

|      | The AES state.                                                                                  | 51  |

|      | The AES encryption flowchart.                                                                   | 52  |

|      |                                                                                                 | 52  |

|      | The AES decryption flowchart.                                                                   |     |

|      | Application of <i>SubBytes</i> transformation to the <i>state</i>                               | 53  |

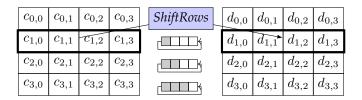

|      | Application of ShiftRows transformation to the state.                                           | 53  |

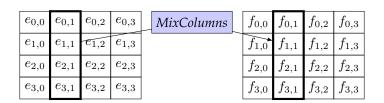

|      | Application of <i>MixColumns</i> transformation to the <i>state</i>                             | 53  |

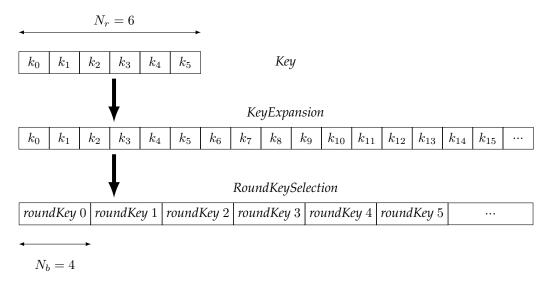

| 2.25 | Decomposition of key scheduling into KeyExpansion and RoundKeySelection for $N_k=6$             |     |

|      | (192-bit key) and $N_b = 4$ (128-bit data block). In the figure, $k_i$ is a word of 32 bits     | 54  |

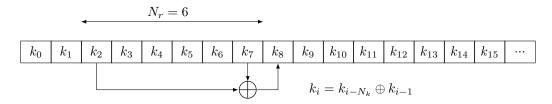

|      | <i>KeyExpansion</i> formula for $i \mod N_k \neq 0$                                             | 54  |

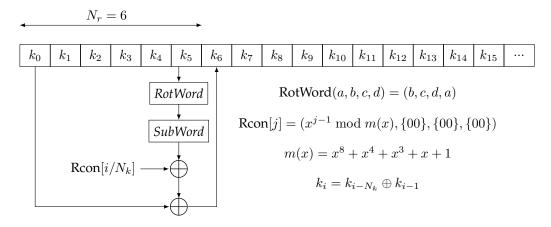

|      | <i>KeyExpansion</i> formula for $i \mod N_k = 0$                                                | 54  |

| 2.28 | Basic protocol for digital signatures with a hash function                                      | 57  |

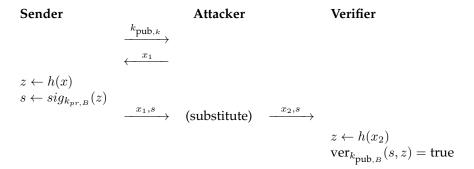

|      | Substitution attack on a hash scheme without second preimage resistance                         | 59  |

| 2.30 | Attack on a hash scheme without second collision resistance                                     | 59  |

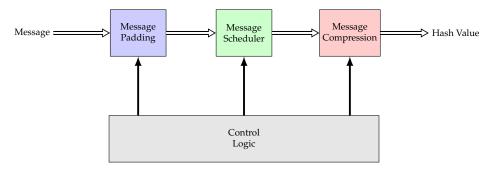

| 2.31 | General block diagram of the hardware SHA-2 implementation                                      | 61  |

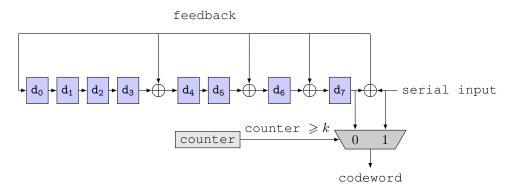

| 3.1  | Standard LFSR architecture block diagram. (Design BCH-LFSR)                                     | 79  |

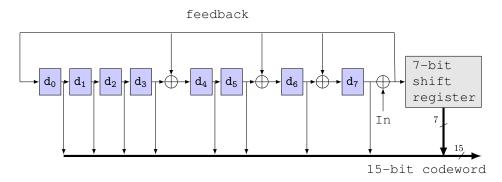

| 3.2  | Improved LFSR architecture block diagram. In denotes the module's serial input. (De-            | • • |

| 0.2  | sign BCH-LFSR-improved)                                                                         | 79  |

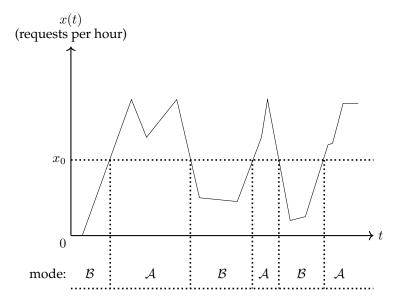

| 3.3  | Example of a request function $x(t)$ with a threshold $x_0$ . When $x(t) \geq x_0$ , it is more | ,,  |

| 5.5  | advantageous to be in $A$ -mode. Otherwise $S$ should better go into $B$ -mode                  | 92  |

| 2 /  |                                                                                                 | 83  |

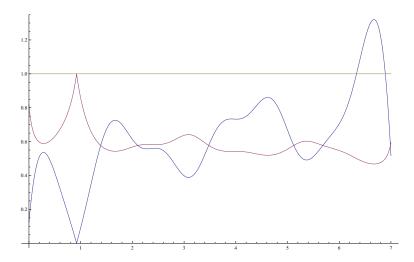

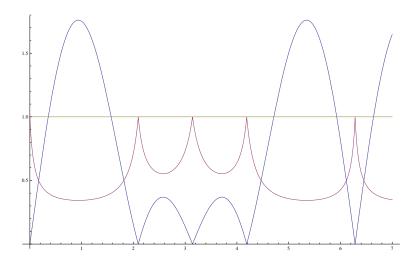

| 3.4  | Example of $v(t)$ (purple) for an example function $x(t)$ (blue)                                | 85  |

| 3.5  | Example of $v(t)$ (purple) for $x(t) =  \sin(x) + \sin(2x) $ (blue)                             | 85  |

| 4.1  | Power trace of an RSA exponentiation                                                            | 89  |

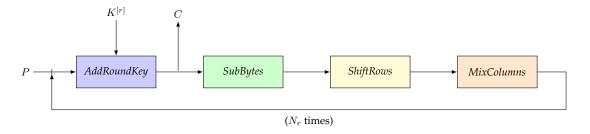

| 4.2  | AES encryption flowchart                                                                        | 93  |

|      |                                                                                                 |     |

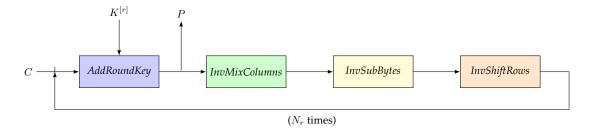

| 4.3          | AES decryption flowchart                                                                                                                                                 | 94  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

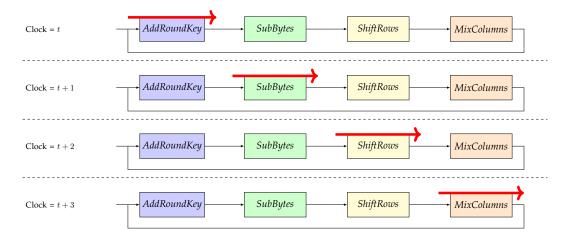

| 4.4          | Flow of computation in time                                                                                                                                              | 95  |

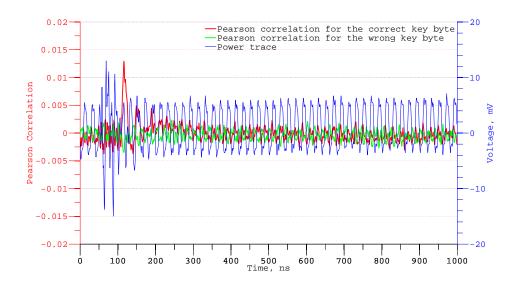

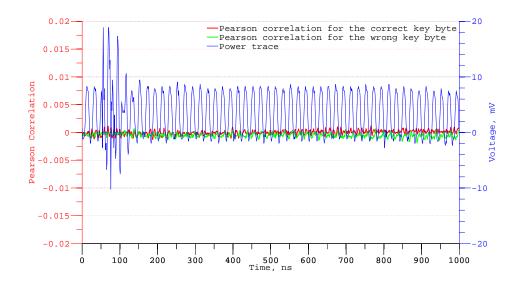

| 4.5          | Unprotected implementation: Pearson correlation value of a correct (red) and an incor-                                                                                   |     |

|              | rect (green) key byte guess. 500,000 power traces.                                                                                                                       | 95  |

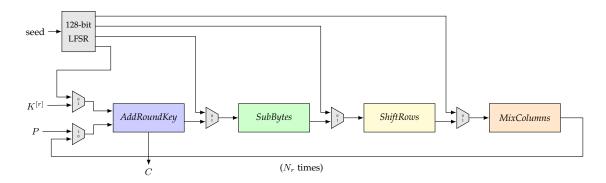

| 4.6          | Power scrambling with a PRNG                                                                                                                                             | 96  |

| 4.7          | LFSR implementation: Pearson correlation value of a correct (red) and an incorrect (green)                                                                               |     |

|              | key byte guess. 1,200,000 power traces.                                                                                                                                  | 96  |

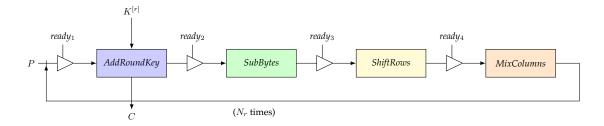

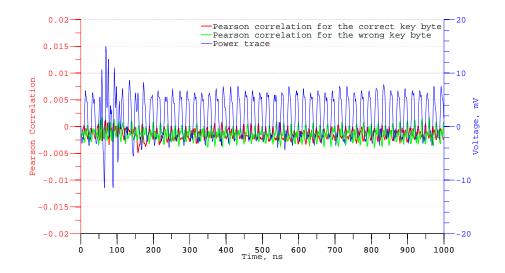

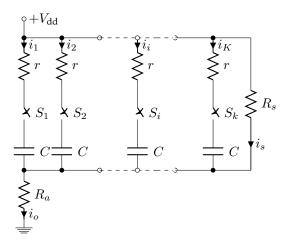

| 4.8          | Power scrambling with tri-state buffers                                                                                                                                  | 97  |

| 4.9          | Tri-state buffers implementation: Pearson correlation value of the correct key byte (green)                                                                              |     |

|              | and a wrong key byte guess (red). 800,000 power traces                                                                                                                   |     |

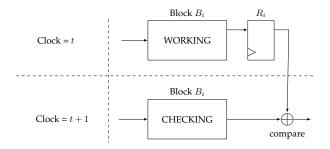

|              | Transient fault detection scheme for AES                                                                                                                                 |     |

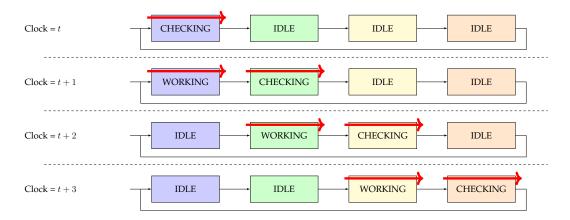

|              | Permanent fault detection scheme for AES                                                                                                                                 |     |

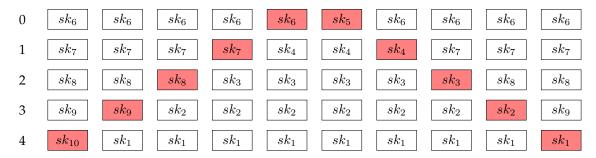

|              | Memory halving for AES decryption when $N_r = 10$                                                                                                                        |     |

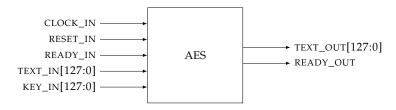

|              | AES design's inputs and outputs                                                                                                                                          |     |

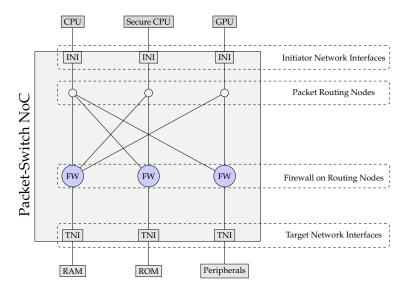

|              | Firewalling in an SoC based on NoC interconnect                                                                                                                          |     |

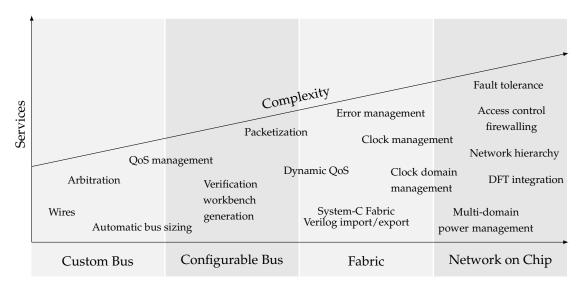

| 4.15         | Evolution of NoC integration services                                                                                                                                    | 103 |

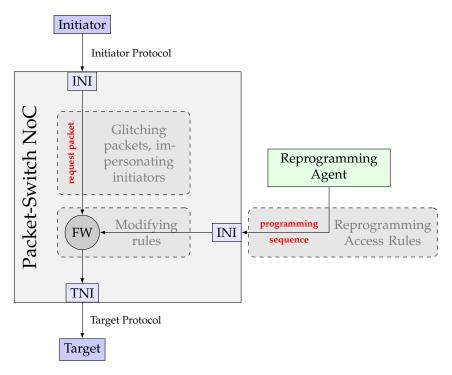

| 4.16         | Different attack surfaces on a NoC firewall                                                                                                                              | 104 |

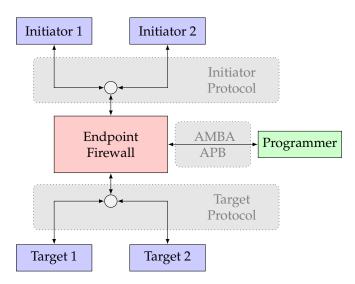

|              | Simple firewall partitioning of an address space covering two targets                                                                                                    |     |

|              | Endpoint firewall controlling access from initiators to a targets                                                                                                        |     |

|              | Content of a complex CSAC region.                                                                                                                                        |     |

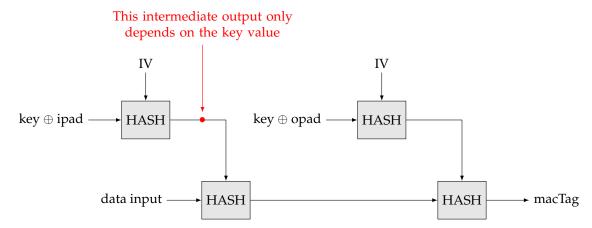

|              | HMAC intermediate used for key integrity checks                                                                                                                          |     |

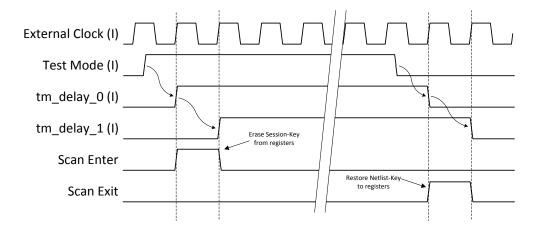

|              | Timing diagram of reset-on-scan block                                                                                                                                    | 109 |

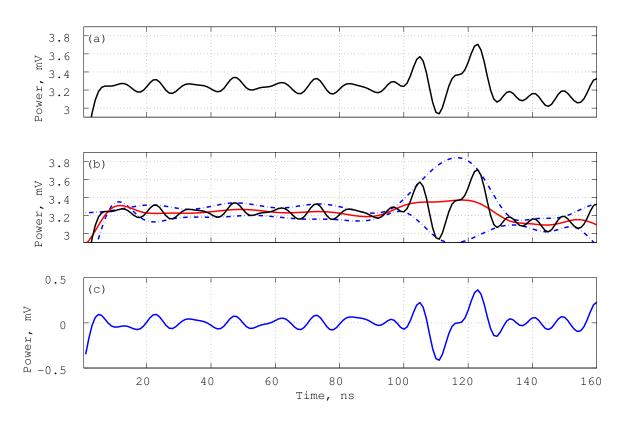

| 4.22         | Illustration of the EMD: (a) is the original signal $u(t)$ ; (b) $u(t)$ in thin solid black line,                                                                        |     |

|              | upper and lower envelopes are dot-dashed with their mean $m_{i,j}$ in thick solid red line;                                                                              |     |

|              | (c) shows the difference between $u(t)$ and the envelope's mean. $\dots \dots \dots \dots$                                                                               |     |

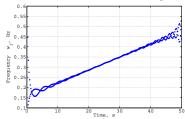

|              | The increasing frequency function $\cos((a+bt)t)$                                                                                                                        |     |

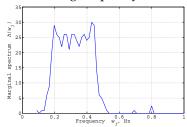

|              | Analysis of the function $\cos((a+bt)t)$ : Marginal Hilbert spectrum of Fig. 4.23                                                                                        |     |

|              | Analysis of the function $cos((a + bt)t)$ : Hilbert's amplitude spectrum contour of Fig. 4.23.                                                                           |     |

|              | Analysis of the function $cos((a+bt)t)$ : Hilbert's amplitude spectrum contour of Fig. 4.23.                                                                             |     |

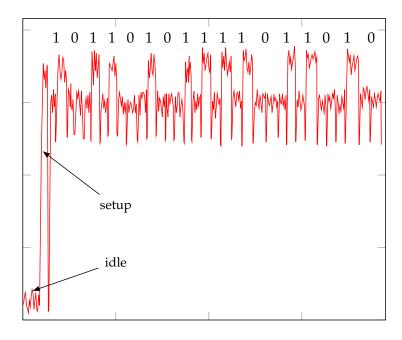

|              | Inverters switch simulation                                                                                                                                              |     |

|              | Four AES last rounds                                                                                                                                                     | 119 |

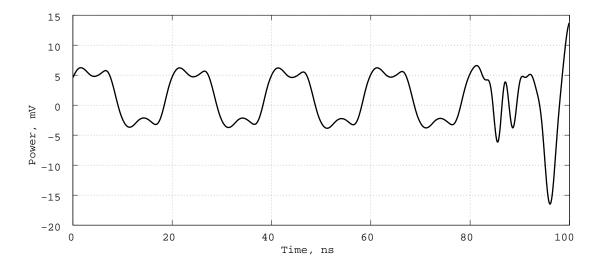

| 4.29         | AES last round power consumption for 55 (red), 65 (blue) and 75 (black) register's flip-flops: Full voltage range.                                                       | 120 |

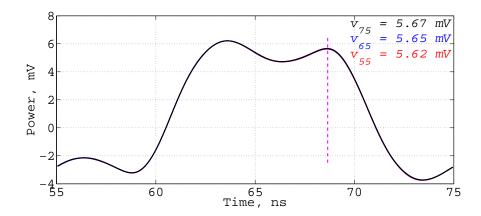

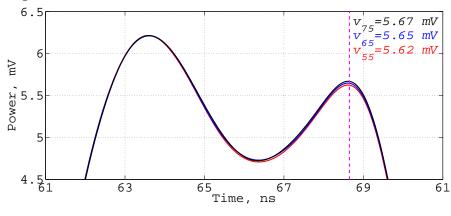

| 4 30         | AES last round power consumption for 55 (red), 65 (blue) and 75 (black) register's flip-                                                                                 | 120 |

| 1.00         | flops: Zoomed voltage range                                                                                                                                              | 120 |

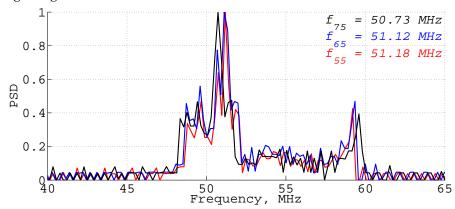

| 4.31         | AES last round power consumption for 55 (red), 65 (blue) and 75 (black) register's flip-                                                                                 | 1_0 |

|              | flops: Power spectra density for the signals shown on Fig. 4.29                                                                                                          | 120 |

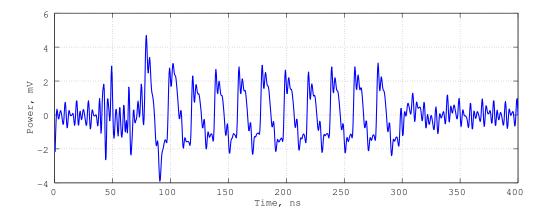

| 4.32         | Power consumption of our experimental AES-128 implementation: initial signal $u(t)$                                                                                      |     |

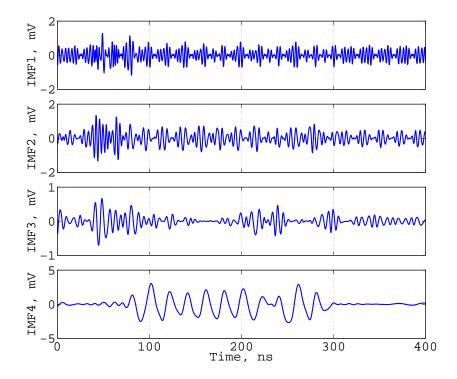

|              | Power consumption of our experimental AES-128 implementation: The Empirical Mode                                                                                         |     |

|              | Decomposition of signal $u(t)$                                                                                                                                           | 121 |

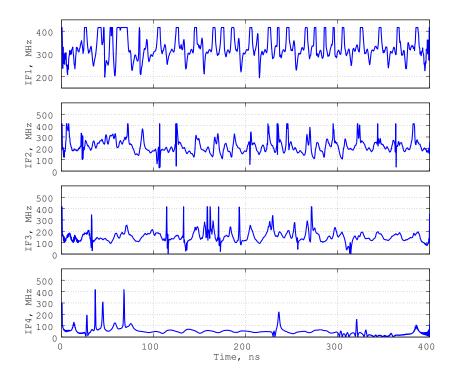

| 4.34         | Power consumption of our experimental AES-128 implementation: IF distribution over                                                                                       |     |

|              | time for the different IMFs of Fig. 4.33                                                                                                                                 |     |

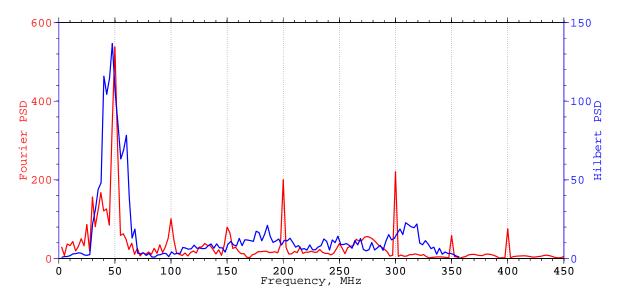

|              | Fourier and Hilbert power spectrum density of Fig. 4.32                                                                                                                  | 122 |

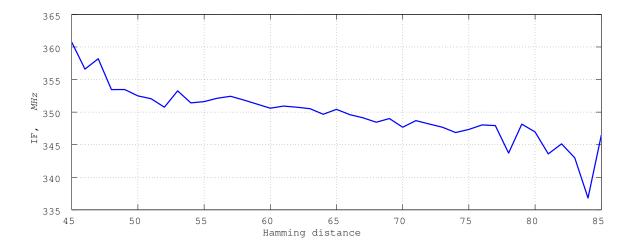

| 4.36         | Dependency between the Hamming distance of 9th and 10th AES round states and the                                                                                         |     |

|              | IF of the first IMF component at time 276 ns (corresponding to the beginning of the last                                                                                 | 100 |

| 4.07         | AES round).                                                                                                                                                              | 123 |

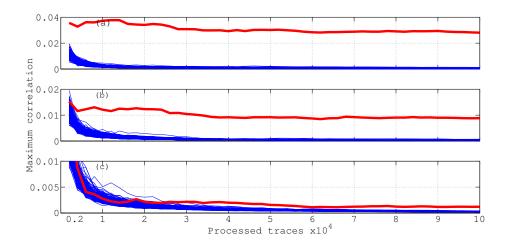

| 4.37         | Maximum correlation coefficients for a byte of the last round AES key in an unprotected implementation. Although the three attacks eventually succeed CPA>CSBA>CIFA. (a) |     |

|              | CPA (b) CSBA (c) CIFA                                                                                                                                                    | 122 |

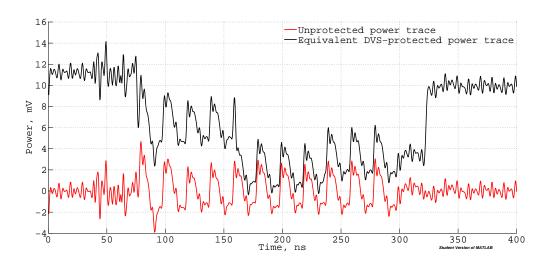

| 1 20         | Power traces of the FPGA AES implementation. The unprotected signal is shown in red.                                                                                     | 123 |

| <b>±.</b> 30 | The DVS-protected signal is shown in black.                                                                                                                              | 124 |

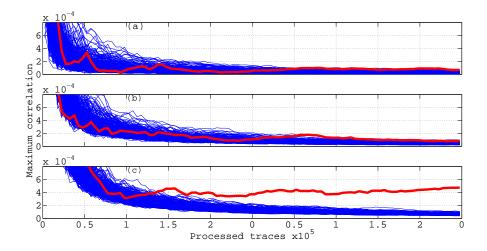

| 4 30         | Maximum correlation coefficient for a byte of the last round AES key with simulated                                                                                      | 144 |

| <b>4.</b> J7 | DVS. (a) CPA (b) CSBA (c) CIFA                                                                                                                                           | 125 |

|              | υτο. (a) CITI (b) CODII (c) CIIII.                                                                                                                                       | 120 |

| 5.1          | Fiat-Shamir authentication round                                                                                                                                         | 128 |

| 5.2          | The proposed algorithm running on a network. Each parent node aggregates the values                                                                                      |     |

|              | computed by its children before transmitting it upwards to the base station                                                                                              | 130 |

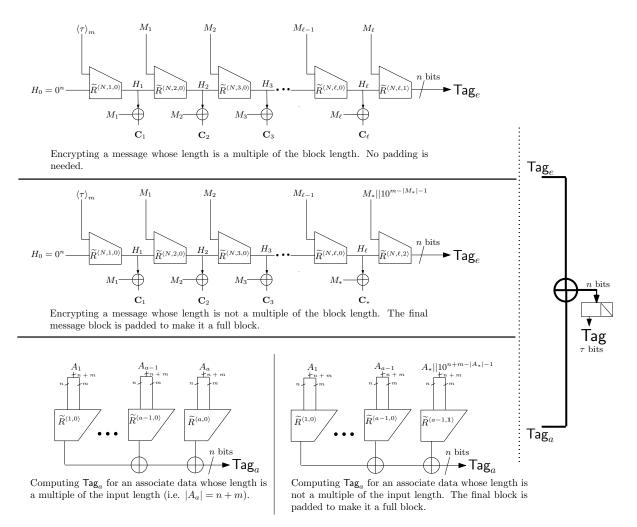

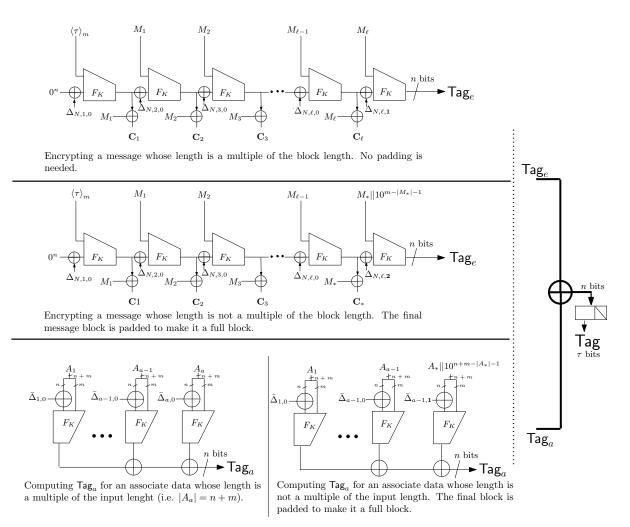

| 5.3 | The $\mathbb{OMD}[\widetilde{R}, \tau]$ scheme using a tweakable random function $\widetilde{R}: \mathcal{T} \times (\{0,1\}^n \times \{0,1\}^m) \to \mathbb{R}$                                                                                                                                                                                                                                                        |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | $\{0,1\}^n$ (i.e., $\widetilde{R} \stackrel{R}{\leftarrow} \operatorname{Func}^{\mathcal{T}}(n+m,n)$ ). The tweak space $\mathcal{T}$ consists of five mutually exclusive sets of tweaks, namely $\mathcal{T} = \mathcal{N} \times \mathbb{N} \times \{0\} \cup \mathcal{N} \times \mathbb{N} \times \{1\} \cup \mathcal{N} \times \mathbb{N} \times \{2\} \cup \mathbb{N} \times \{0\} \cup \mathbb{N} \times \{1\}$ , |     |

|     | where $\mathcal{N} = \{0, 1\}^{ \mathcal{N} }$ is the set of nonces, $\mathbb{N}$ is the set of positive integers                                                                                                                                                                                                                                                                                                       | 141 |

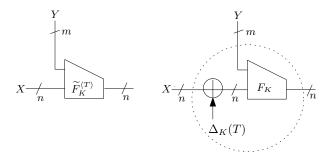

| 5.4 | Building a tweakable PRF $\widetilde{F}_K^{\langle T \rangle}: \{0,1\}^n \times \{0,1\}^m \to \{0,1\}^n$ using a PRF $F_K: \{0,1\}^n \times \{0,1\}^m \to \{0,1\}^n$ . There are several efficient ways to define the masking function $\Delta(T)$                                                                                                                                                                      |     |

|     | [Rog04a, CS07, KR11]. We use the method of [KR11]                                                                                                                                                                                                                                                                                                                                                                       | 144 |

| 5.5 | The encryption process of OMD[ $F$ , $\tau$ ] using a keyed compression function $F_K$ : $(\{0,1\}^n \times$                                                                                                                                                                                                                                                                                                            |     |

|     | $\{0,1\}^m$ ) $\to \{0,1\}^n$ with $m \le n$ . ( <b>Top</b> ) The encryption process when the message length                                                                                                                                                                                                                                                                                                            |     |

|     | is a multiple of the block length $m$ and no padding is required. (Middle) The encryption                                                                                                                                                                                                                                                                                                                               |     |

|     | process when the message length is not a multiple of the block length and the final block                                                                                                                                                                                                                                                                                                                               |     |

|     | $M_*$ is padded to make a full block $M_*  10^{m- \hat{M}_* -1}$ . ( <b>Bottom, Left</b> ) Computing the in-                                                                                                                                                                                                                                                                                                            |     |

|     | termediate value $T_a$ when the bit length of the associated data is a multiple of the <b>input</b>                                                                                                                                                                                                                                                                                                                     |     |

|     | length $n+m$ . ( <b>Bottom, Right</b> ) Computing $T_a$ when the bit length of the associated data is not a multiple of $n+m$ and the final block is padded to make a full block $A_*  10^{n+m- A_* -1}$                                                                                                                                                                                                                |     |

|     | is needed. The output ciphertext is $C  \text{Tag. For operation } \oplus \text{ see our convention in Sec-}$                                                                                                                                                                                                                                                                                                           |     |

|     | tion 5.2.2. Five types of key-dependent masking values (corresponding to five mutually                                                                                                                                                                                                                                                                                                                                  |     |

|     | exclusive tweak sets) are used; these are denoted by $\Delta_{N,i,0}, \Delta_{N,i,1}, \Delta_{N,i,2}, \bar{\Delta}_{i,0}$ and $\bar{\Delta}_{j,1}$ , for $i \geq 1$ and $j \geq 0$ , where $N$ is the nonce. Note that the masks used in computing $T_a$ do                                                                                                                                                             |     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                         | 147 |

| 5.6 | Definition of OMD[ $F$ , $\tau$ ]. The function $F: \mathcal{K} \times (\{0,1\}^n \times \{0,1\}^m) \to \{0,1\}^n$ is a keyed                                                                                                                                                                                                                                                                                           | 14/ |

|     | compression function with $\mathcal{K} = \{0,1\}^k$ and $m \leq n$ . The tag length is $\tau \in \{0,1,\cdots,n\}$ .                                                                                                                                                                                                                                                                                                    |     |

|     | Algorithms $\mathcal{E}$ and $\mathcal{D}$ can be called with arguments $K \in \mathcal{K}$ , $N \in \{0,1\}^{\leq n-1}$ , and $A, M, \mathbb{C} \in \mathcal{C}$                                                                                                                                                                                                                                                       |     |

|     | Algorithms $\ell$ and $\ell$ can be called writt arguments $K \in \mathcal{K}, N \in \{0,1\}^*$ . And $A, M, C \in \{0,1\}^*$ . $\ell_{\text{max}}$ is the bound on the maximum number of blocks in any input to the encryp-                                                                                                                                                                                            |     |

|     | tion or decryption algorithms                                                                                                                                                                                                                                                                                                                                                                                           | 148 |

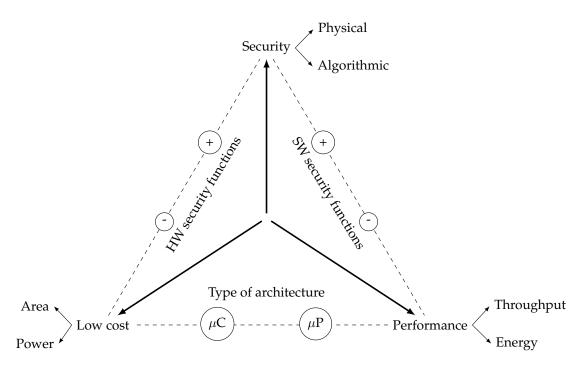

| 6.1 | Tradeoffs in cryptography                                                                                                                                                                                                                                                                                                                                                                                               | 155 |

# LIST OF TABLES

| 2.1 | Trends in microelectronics in the past decades [WH10]                                                     | 27  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of VLSI design methodologies [WH10]                                                            |     |

| 2.3 | Comparison of different AES implementations                                                               | 55  |

| 2.4 | Comparison of different pipelined AES implementations                                                     | 56  |

| 2.5 | Comparison of different pipelined AES implementations                                                     | 65  |

| 2.6 | Comparison of different SHA-2 implementations                                                             | 65  |

| 3.1 | Synthesis results of the four BCH designs                                                                 | 80  |

| 3.2 | Increase $\Delta P$ of the power consumption function in a short time period $\Delta T$                   | 82  |

| 3.3 | Increase $\Delta P$ of the power consumption function in a short time period $\Delta T$ . $(r_A + r_B)/2$ |     |

|     | represents the average rate due to the alternation of modes ${\cal A}$ and ${\cal B}$ during the request  | 84  |

| 4.1 | 29 possible configurations                                                                                | 99  |

| 4.2 | Number of configurations                                                                                  | 99  |

| 4.3 | Unprotected AES, LFSR and tri-state buffer designs synthesized to the 45nm FreePDK                        |     |

|     | open-cell library                                                                                         | 101 |

| 4.4 | Spartan3E-500 utilization summary report.                                                                 |     |

| 4.5 | Synthesis results of five CSAC designs (4 regions, 6 initiators, 4GB of address space) on a               |     |

|     | 45nm technology node                                                                                      | 109 |

| 4.6 |                                                                                                           |     |

|     | a 45nm technology node                                                                                    | 110 |

| 4.7 | CSAC (4 regions, 6 initiators, 4GB of address space) synthesis on Zynq-7000 board                         |     |

| 4.8 | CSAC (8 regions, 14 initiators, 64GB of address space) synthesis on Zynq-7000 board                       |     |

# LIST OF ALGORITHMS

| 1  | AES algorithm description                                |

|----|----------------------------------------------------------|

| 2  | Barrett's algorithm                                      |

| 3  | Polynomial Barrett algorithm                             |

| 4  | Peterson's algorithm                                     |

| 5  | Standard modular division (BCH-standard) 78              |

| 6  | Computation of an RSA signature (modular exponentiation) |

| 7  | Dynamic Voltage Scrambling (DVS) simulator               |

| 8  | Mooij-Goga-Wesselink algorithm, basic part               |

| 9  | Compression function of SHA-256                          |

| 10 | Compression function of SHA-512                          |

# CHAPTER 1

# Introduction

Cryptography is an ancient art. The word comes from the Greek  $\kappa\rho\pi\tau\delta\varsigma$ , that means hidden, and  $\gamma\rho\delta\phi\epsilon\iota\nu$ , that means writing. It is therefore the science of writing secrets, and has started thousands of years ago. The advent of cryptography is sometimes linked with the origin of written language [Vau05]. An example of that are the hieroglyphs, a written language based on symbols, created by the Egyptians. The scribes were usually the only ones who mastered it. They used to transmit their knowledge from father to son 1 until the Egyptian society fell apart and collapsed. For this reason, hieroglyphs remained a secret to humanity until Jean-François Champollion broke the code, in 1822 [Cha24].

Many historical personalities like Julius Caesar, Francis Bacon, Louis XIV, and Napoleon invented their own ciphers and used them for their secret correspondence [MM03]. During the American War of Independence, spies employed a code system where words were replaced with numbers extracted from a codebook. Around 1900, the French military employed a ciphering machine called the *Bazeries cylinder*. In the World War II, the German military bought the *Enigma machine*, perhaps the most famous cryptosystem.

Early cryptographic schemes focused on converting language into symbols, or mixing language characters, to carry the message from one place to another. Until late 19<sup>th</sup> century, cryptographic algorithms lacked rigorous and formal security proofs, and were seen as an art rather than science. It was only in the early 20<sup>th</sup> century that more sophisticated encryption means, using mechanical and electromechanical machines, such as the *Enigma machine*, were created, and cryptography increased in complexity. This development happened in parallel with cryptanalysis, the study of breaking such codes and ciphers. The *Enigma*, for example, was reversed engineered several times by Polish, French and British military intelligence, changing the course of World War II [Vau05].

A broader concept, cryptology, is the science of secure communications or, in other words, the study of cryptosystems. The word stems from Greek roots  $\kappa\rho\pi\tau\delta\varsigma$  and  $\lambda\sigma\gamma\iota\alpha$ , meaning hidden and word, respectively. Cryptology basically subdivides into two introduced disciplines, cryptography and cryptanalysis, since these two topics are closely related. When implementing a cryptosystem, one needs to prove its strength by actually attacking it (or proving the infeasibility of the attack). In other words, cryptanalysis assures that a cryptosystem is secure.

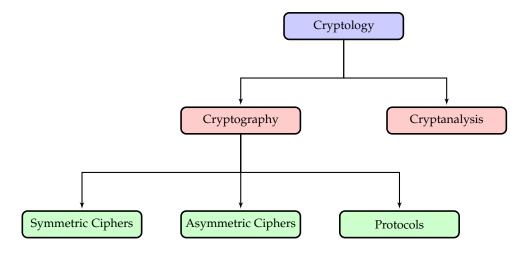

Fig. 1.1 depicts the three main building blocks of cryptography [PP09]:

**Symmetric Algorithms** Two parties have an encryption and decryption method for which they share a secret key. All cryptography from ancient times until 1976 was exclusively based on symmetric methods. Symmetric ciphers are still in widespread use, especially for data encryption and message integrity checks;

**Asymmetric (or Public-Key) Algorithms** In 1976 an entirely different type of cipher was introduced by Whitfield Diffie, Martin Hellman and Ralph Merkle [DH76, Mer78]. In public-key cryptography, a user possesses a secret key as in symmetric cryptography but also a public key. Asymmetric

<sup>1.</sup> Although some craftsmen were able to get their sons into the school for scribes, it was very rare.

Figure 1.1: The hierarchical diagram of the different fields of cryptography.

algorithms can be used for applications such as digital signatures and key establishment, and also for classical data encryption;

**Cryptographic Protocols** Also called security protocols, they are abstract or concrete protocols that perform security-related functions applying cryptographic methods or primitives. Cryptographic protocols describe how the algorithms should be used, with details about data structures, key establishment, authentication between parties, secret sharing methods, secure multi-party computation, etc.

The early usage of cryptography was to enable governmental and military applications. Nowadays it is used everywhere and is taken for granted by most people. We use underlying cryptography embedded in cryptosystems to surf the internet, purchase online and communicate using the cellphone. It is a powerful and important tool that enables fundamental operations in our modern society. Modern cryptology appeared somewhere in the mid-1970s, when academic research started to mature this discipline. Although before, in 1949, Claude Shannon published a paper [Sha49] linking cryptography to information theory, discussing the foundations of modern cryptography and providing a comprehensive theory of secrecy systems. His work proved the unconditional security of the *one-time pad* cipher, earlier published by Gilbert Vernam in 1926 [Ver].

Apart from the groundbreaking work of Claude Shannon, two other contributions mark the 1970s as the beginning of a new era: First, in 1973, Horst Feistel published a work [Fei73, Fei74] of an iterative symmetric block-cipher called Lucifer, based on the Feistel construction. This algorithm was submitted to the National Bureau of Standards and was accepted in 1976 as the Data Encryption Standard (DES), becoming the first standardized cryptographic algorithm. Secondly, in 1976, the concept proposed by Whitfield Diffie and Martin Hellman [DH76] defined the basis of a new paradigm: public-key cryptography. They showed that secret communication was possible without any transfer of secrets.

# 1.1 Terminology

Cryptography has developed an extensive vocabulary. This section lists some definitions that will be encountered in the rest of this thesis.

The basic security requirements are defined as the following properties [Til99]:

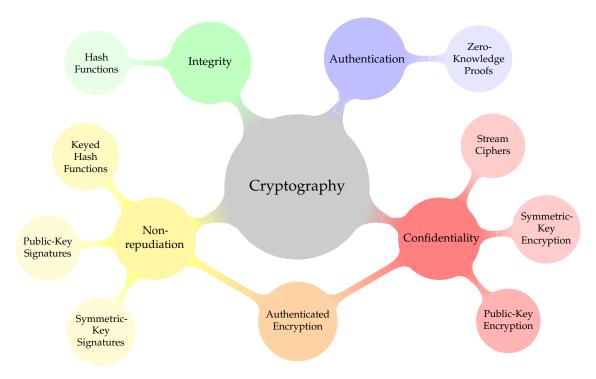

**Confidentiality** is a service used to keep the content of information hidden from all but those authorized to have it. *Secrecy* is a term synonymous to confidentiality and privacy. There are numerous approaches to providing confidentiality, ranging from physical protection to mathematical algorithms which render data unintelligible.

1.1 Terminology 15

**Data integrity** is a service which addresses the unauthorized alteration of data. To ensure data integrity, one must have the ability to detect data manipulation by unaccredited parties. Data manipulation includes such operations as insertion, deletion, and substitution.

**Authentication** is a service related to identification. This function applies both to entities and to information itself. Two parties entering into a communication should identify each other. Information delivered over a channel should be authenticated as to origin, date of origin, data content, time sent, etc. For these reasons this aspect of cryptography is usually subdivided into two major classes: entity authentication and data origin authentication. Data origin authentication implicitly provides data integrity (for if a message is modified, the source has changed).

**Nonrepudiation** is a service which prevents an entity from denying previous commitments or actions. When disputes arise due to an entity denying that certain actions were taken, a means to resolve the situation is necessary. For example, one entity may authorize the purchase of property by another entity and later deny that such authorization was granted. A procedure involving a trusted third party is needed to resolve the dispute.

Encryption is the first basic cryptographic operation to ensure *secrecy* or *confidentiality* of data transmitted across an insecure communication channel. Basically, encryption takes an information element (often called the *message*, *message block*, or *plaintext*) and translates it into a *cryptogram* (usually referred of as the *codeword* or *ciphertext*) using a cryptographic *secret key*. Decryption is the reverse operation, where the *ciphertext* is translated to a *plaintext* under a *secret key*. The step-by-step description of an encryption (or decryption) scheme is called the *encryption algorithm* (or *decryption algorithm*). Denominations such as *ciphers*, *cryptoalgorithms* or *cryptosystems* are often used without the need to differentiate encryption from decryption.

Figure 1.2: The broad fields of cryptography [MvV97].

A fundamental goal of cryptography is to adequately address these four areas in both theory and practice. Cryptography is about the prevention and detection of cheating and other malicious activities. Many of these will be briefly introduced in this chapter, with the detailed discussion being left to later chapters. These primitives should be evaluated with respect to various criteria such as:

**Security Level.** This is usually difficult to quantify. Often it is given in terms of the number of operations required (using the best methods currently known) to defeat the intended target. Typically the security level is defined by an upper bound on the amount of work necessary to defeat the objective. This is sometimes called the *work factor*.

**Functionality.** Primitives will need to be combined to meet various information security objectives. Which primitives are most effective for a given objective will be determined by the primitives' basic properties.

**Methods of operation.** Primitives, when applied in various ways and with various inputs, will typically exhibit different characteristics; thus, one primitive could provide very different functionalities depending on its mode of operation or usage. In other words, *methods of operation* means how different characteristics the protocol exhibits when applied in various ways and with various inputs.

**Performance.** Refers to the efficiency of a primitive in a particular mode of operation. (For example, an encryption algorithm may be rated by the number of bits per second which it can encrypt.)

**Ease of implementation.** Refers to the difficulty of realizing the primitive in a practical instantiation. This might include the complexity of implementing the primitive in either software or hardware.

**Cryptanalysis** Cryptanalysis is the art of breaking cryptosystems. Breaking a cipher does not necessarily mean finding a practical way to recover the plaintext from the ciphertext. Instead, breaking a cipher involves finding weaknesses in the cipher that can be exploited with complexity less than a brute-force attack [Sch00], in which every possible key is tested in sequence until the correct one is found. A cryptanalysis is also considered successful when it breaks a reduced-round variant of the cipher — 8-round AES versus the full 10-round AES (for 128-bit key), for example. Academic publications usually start out with a reduced-round variant cryptanalysis that eventually escalates to all the cipher rounds.

Modern cryptanalysis is fundamentally based on *Kerckhoffs's principle* [Ker83], which states that a cryptosystem should remain secure even if everything about the system, except the key, is public knowledge. Kerckhoffs's article, published in 1883 and entitled "The Military Cryptography", states the following design principles:

- The system must be practically, if not mathematically, indecipherable.

- The system must not be required to be secret, and it must be able to fall into the hands of the enemy without inconvenience.

- The system's key must be communicable and retainable without the help of written notes, and changeable or modifiable at the will of the correspondents.

- The system must be applicable to telegraphic correspondence.

- Apparatus and documents must be portable, and its usage and function must not require the concourse of several people.

- Finally, it is necessary, given the circumstances that command its application, that the system be easy to use, requiring neither mental strain nor the knowledge of a long series of rules to observe.

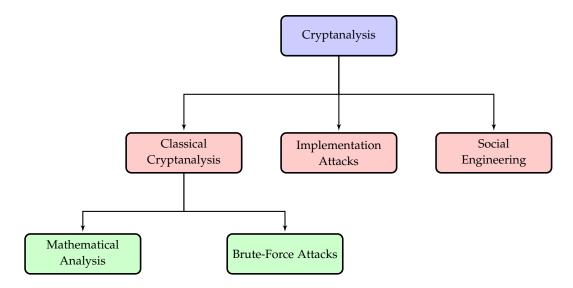

We can depict the field of cryptanalysis as shown in Fig. 1.3. The first subfield of cryptanalysis, Classical cryptanalysis, is the study of how to break the cryptosystem by means of recovering the secret key from the ciphertext or, alternatively, recovering the plaintext from the ciphertext. It is divided in Mathematical Analysis and Brute-Force Attacks. The first exploits algorithmic weaknesses to break the cipher and therefore discovers the secret key; the second treats the cipher as a black-box and tries all the possible key combinations, until the correct one is found.

Implementation attacks are a subfield of cryptanalysis exploiting implementation weaknesses rather than algorithmic mathematical properties. An unprotected implementation of a block cipher may leak information through the power being consumed or the time necessary to perform internal operations, and this side-channel information can be used by a cryptanalyst to break the cipher. Implementation attacks are most common when the attacker has physical access to cryptosystem.

The third cryptanalysis subfield, social engineering, uses blackmailing, espionage, bribing or other illegal practices to retrieve information that can lead to the discovery of the secret key. The more cryptosystem and secure protocols evolve, the more social engineering is used to trick people into disclosing sensitive information.

Cryptanalysis attacks are alternatively divided into passive and active attacks. A passive attack occurs when the communication is being eavesdropped and the information confidentiality is therefore

1.2 Hardware System Security 17

Figure 1.3: The hierarchical diagram of the different fields of cryptanalysis [PP09].

threatened. An active attack, on the other hand, occurs when the attacker attempts to modify the communication information, thus compromising the message's confidentiality, integrity and authenticity. In either way, the attack objective is to determine the key [Sti95].

The most common passive attacks include:

**Ciphertext-Only** The attacker has only access to the ciphertext.

**Known-Plaintext** The attacker has access to both the plaintext and the corresponding ciphertext.

**Chosen-Plaintext** The attacker has gained access to the encryption process of a cryptosystem and therefore, has the ability to input plaintext and observe the corresponding ciphertext.

**Chosen-Ciphertext** This is the reverse of a chosen plaintext attack. The attacker has access to the decryption process and is able to input ciphertexts and observe the original plaintext.

Three well-known active attacks are:

**Man-in-the-Middle (MITM)** Here the attacker controls the communication channel between two parties. The attacker can then retrieve information and send on altered messages without the other party being aware of it. Passwords are easily compromised in a MITM attack. Typically, hash functions are used to thwart such attacks.

**Timing Attacks** Cryptographic algorithms' inputs and internal data vary in the time it takes to process. By carefully measuring the amount of time required to perform certain operations, information can be retrieved and indeed, secret keys can even be uncovered [Koc96].

**Power Analysis** This technique involves interpreting power consumption measurements of various cryptographic operations to retrieve information [KJJ99]. Features such as DES permutation and shift operations can be easily spotted, as their power consumption traces are visibly different. Differential Power Analysis (DPA) is an even more powerful method of attack, in which statistical analysis and error correction techniques are also used to deduce information.

The science of cryptology is continually driven forward by the constant battle between cryptographers trying to secure information and cryptanalysts attempting to break cryptosystems.

# 1.2 Hardware System Security

Cryptographic engineering blends theory and practice of engineering a cryptosystem. A cryptographic engineer is thus responsible for translating the mathematical and formal descriptions of cryptographic algorithms to hardware or software systems. After designing and coding the encryption and

decryption modules, authentication blocks, digital signature schemes or any other cryptographic methods, a cryptography engineer is, nowadays, interested in cryptanalyzing the system for the purpose of checking its robustness and strength against attacks. In the past, cryptographic engineering relied on the mathematical strength of a cryptographic algorithm as a blind proof that the cryptosystem was therefore unbreakable. New cryptanalysis techniques have completely torn apart this belief.

Classical and theoretical cryptanalysis consider attack scenarios where adversaries access the cryptosystem as a black box, i.e., its inputs and outputs. For example, in a chosen ciphertext attack, it is assumed that the attacker can choose the ciphertext input into the decryption black-box and also that he can read the plaintext at the black box output. In real life, though, attackers might be even more powerful. For example, an adversary may monitor side-channel information that leaks out of the black-box, such as execution time or power consumption. The basic idea behind side-channel analysis is to infer secret information from this extra information.

Secure protocols, cryptographic algorithms and primitives do not specify how they should be implemented in hardware or software. Instead, they focus on describing their mathematical operations and transformations. The specification of a secure protocol disregards by which physical device it will be executed. For example, the target application could be a software running on a general purpose processor or a custom integrated circuit. Besides, each target platform leaks side-channel information in a different way.

The first attack of this kind was published by Paul Kocher in 1996 [Koc96]. Kocher showed how different RSA [Jr.96] operations could be tracked down by the actual time they take to compute. By doing so, Kocher demonstrated that it was possible to differentiate the multiplication and the squaring steps, therefore exposing the secret key. In 1999, Kocher *et al.* also presented a technique to infer the DES secret key by recording the power consumption of the device [KJJ99], called Differential Power Analysis (DPA). Power attacks proved to be so powerful that new academic publications rapidly demonstrated how to apply DPA to break the newly symmetric cipher approved by NIST, the Advanced Encryption Standard (AES). Although AES had been selected in the early 2000 to overcome security issues with DES, presenting a bigger key space and a more complex mathematical structure, it was not less vulnerable to DPA attacks than any other block-cipher.

Other side-channel attacks exploit electromagnetic emanations [AARR03,GMO01,QS01], optical [Kuh02] and acoustic [LU02,BWY06] leakage. In fact, side-channel analysis proved to be so powerful that the majority of techniques applied use only a portion of the side-channel information. Even if the acquired power traces present a considerable amount of noise, the idea behind differential analysis is to run and record several iterations of the device's power profile such that information can be averaged over a large number of samples.

# 1.3 Notations and Conventions

In this thesis we introduce the following notations and conventions:

If S is a finite set,  $x \overset{\$}{\leftarrow} S$  means that x is chosen from S uniformly at random.  $X \leftarrow Y$  is used for denoting the assignment statement where the value of Y is assigned to X. The set of all binary strings of length n bits (for some positive integer n) is denoted as  $\{0,1\}^n$ , the set of all binary strings whose lengths are variable but upper-bounded by L is denoted by  $\{0,1\}^{*L}$  and the set of all binary strings of arbitrary but finite length is denoted by  $\{0,1\}^*$ . For two strings X and Y we use X||Y and XY equivalently to denote the string obtained by concatenating Y and X. For an m-bit binary string  $X = X_{m-1} \cdots X_0$  we denote the left-most bit by  $msb(X) = X_{m-1}$  and the right-most bit by  $lsb(X) = X_0$ ; let  $X[i\cdots j] = X_i\cdots X_j$  denote a substring of X, for  $0 \le j \le i \le (m-1)$ . Let  $1^n0^m$  denote concatenation of n ones by m zeros. For a non-negative integer i let  $\langle i \rangle_m$  denote binary representation of i by an m-bit string.

For a binary string  $X = X_{m-1} \cdots X_0$ , let  $X \ll n$  denote the left-shift operation, where the n left-most bits are discarded and the n vacated right bits are set to 0; that is,  $X \ll n = X_{m-n-1} \cdots X_0 0^n$ . We let  $X \gg n$  denote the (unsigned) right-shift operation where the n right-most bits are discarded and the n vacated left bits are set to 0, i.e.,  $X \gg n = 0^n X_{m-1} \cdots X_n$ . We let  $X \gg_s n$  denote the signed right-shift

1.4 Finite Fields Arithmetic 19

operation where the n right-most bits are discarded and the n vacated left bits are filled with the left-most bit (which is considered as the sign bit); for example,  $1001100 \gg_s 3 = 1111001$ . If the left-most bit of X is 0 then we have  $X \gg_s n = X \gg n$ .