### Smart power management silicon integrated interfaces for capacitive vibration energy harvesters

Mohammed Bedier

#### ▶ To cite this version:

Mohammed Bedier. Smart power management silicon integrated interfaces for capacitive vibration energy harvesters. Emerging Technologies [cs.ET]. Université Pierre et Marie Curie - Paris VI, 2017. English. NNT: 2017PA066376. tel-01746118

### HAL Id: tel-01746118 https://theses.hal.science/tel-01746118v1

Submitted on 29 Mar 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE DE DOCTORAT DE l'UNIVERSITÉ PIERRE ET MARIE CURIE

Spécialité

#### Informatique

École doctorale Informatique, Télécommunications et Électronique (Paris)

Présentée par

#### Mohammed BEDIER

Pour obtenir le grade de

Docteur de l'Université Pierre ET Marie Curie

Sujet de la thèse :

Circuits d'interface intégrés sur silicium pour une gestion optimale de la puissance dans les récupérateurs d'énergie vibratoire à transduction capacitive

Soutenue le 20 December 2017

devant le jury composé de :

| M. Robert SOBOT,    | Rapporteur         | Professeur des universités |

|---------------------|--------------------|----------------------------|

| M. Mickaël LALLART, | Rapporteur         | Maître de conférences HDR  |

| M. Elie LEFEUVRE,   | Examinateur        | Professeur des universités |

| M. Zhuoxiang REN,   | Examinateur        | Professeur des universités |

| M. Philippe BASSET, | Invité             | Enseignant-chercheur HDR   |

| M. Dimitri GALAYKO, | Directeur de thèse | Maître de conférences HDR  |

## Ph.D. THESIS OF THE UNIVERSITY OF PIERRE AND MARIE CURIE

Electronics, Telecommunications and Computer science departement (Paris)

A dissertation presented by

#### Mohammed BEDIER

In partial fulfilment of the requirement for the degree Doctor of Philosophy in the school of Pierre and Marie Curie

Thesis title:

# Smart power management silicon integrated interfaces for capacitive vibration energy harvesters

On 20 December 2017

#### in front of the jury:

| Prof. Robert SOBOT,    | Reviewer         | Professeur              |

|------------------------|------------------|-------------------------|

| Prof. Mickaël LALLART, | Reviewer         | Associate Professor HDR |

| Prof. Elie LEFEUVRE,   | Examiner         | Professeur              |

| Prof. Zhuoxiang REN,   | Examiner         | Professeur              |

| Prof. Philippe BASSET, | Invited          | Research Engineer HDR   |

| Prof. Dimitri GALAYKO, | Thesis Directeur | Associate Professor HDR |

### Abstract

Vibrational energy is an attractive power source for self-powered wireless sensors. A mainstream harvesting technique for vibrational energy is electrostatic MEMS harvesters (e-VEH). Various circuit architectures have already been introduced with many successful implementation, yet a load interface that efficiently manages the harvested energy has rarely been reported.

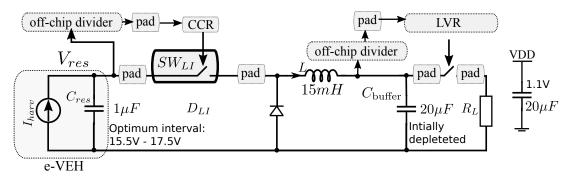

In this work a load interface is proposed which is suited for any condition circuit (CC) implementing rectangular QV cycles. In general, a rectangular QV conditioning circuit has an optimum interval of which the energy harvested is maximised, thus the harvested energy should be periodically removed to maintain maximising the harvested energy. This is achieved through the load interface (LI). The LI proposed is a switched inductor capacitive architecture with a LI controller allowing the extraction of the energy in a multiple energy shot fashion. The LI controller incorporate an ultra low power clock for switching events, as well as low power comparator for switching decision. Power consumption is reduced by operating at a low supply voltage (1.1V).

The proposed load interface is implemented in AMS0.35HV technology with a mixed high voltage and low power control blocks. It takes into account the harvester operation to maximise the energy extracted from the harvester. It overcomes the constrained limited biasing power, and tackles resistive losses and power handling transistor long channels by transferring the energy in a multiple shots fashion. A complete CMOS implementation is proposed along with the simulation results with an average consumed power of the controller less than 100nW allowing the system to operate with input power levels as low as few hundreds of nanowatts.

**Keywords:** vibration, vibrational energy, power management, integrated circuit, high voltage, controller, voltage regulation, switch, MEMS, capactive transducer.

## Abstract - French

Les vibrations ambiantes représentent une source potentielle d'énergie pour alimentation des capteurs sans fil autonomes. La transduction électrostatique est une des techniques utilisées pour la conversion de l'énergie des vibrations en électricité. De nombreuses réalisations des transducteurs et leurs circuits de conditionnement ont déjà été présentées dans la littérature. Pour transmettre l'énergie convertie vers une charge utile (par exemple, une batterie), des interfaces spécifiques doivent être conçues. Ce dernier sujet a été peu abordé dans la littérature.

Ce travail étudie une interface avec la charge dans un dispositif de récupération d'énergie vibratoire. L'architecture proposée au cours de cette étude est particulièrement adaptée aux circuits de conditionnement de type pompe de charge, qui fonctionne selon un cycle charge-tension rectangulaire. L'interface proposée accomplit deux tâches. Premièrement, il permet de transférer l'énergie électrique du circuit de conditionnement vers une charge tout en abaissant la tension d'une manière adiabatique, c.a.d., en minimisant les dissipations. Deuxièmement, il permet de réguler le débit d'extraction d'énergie du circuit de conditionnement en ajustant dynamiquement la puissance de ce transfert. Cela est réalisé avec un circuit intégrée en technologie 0.35 um CMOS haute tension dont l'architecture est inspirée d'un convertisseur DC-DC de type Buck fonctionnant en régime discontinu. La consommation de l'interface est minimisée grâce à l'utilisation du régime sous le seuil des transistors MOS pour pratiquement tous les blocs, grâce à une alimentation réduite à 1.1 Volt. L'interface consomme en dessous de 100 nanoWatts, et est capable de gérer des sources d'énergie à puissance en dessous de 1 microWatt.

- "But man is not made for defeat" he said. "A man can be destroyed but not defeated".

- Ernest Hemingway, The Old Man and the Sea

## Acknowledgements

I would like to thank all the people who have directly or indirectly supported me and contributed to my work during the last few years of my PhD.

Firstly, I would like to express my sincere gratitude to my supervisor and thesis director Prof. **Dimitri Galayko**. His knowledge and expertise have guided me through my research and writing of this thesis. He has always pushed me towards always improving the quality of my work.

Besides, I would like to thank the members of the dissertation jury for accepting my invitation. I am particularly honoured by their presence. I appreciate the dissertation reviewers Prof.Rober SOBOT and Prof. Mickäel LALLART for their insightful helpful feedback on my manuscript. I also thank the dissertation examiners Prof.Elie LEFEUVRE and Prof.Zhuoxiang REN for their time and for agreeing to be part of the committee. Special thanks to Prof. Philippe BASSET for his continuous support throughout my PhD.

I grateful to Prof. Marie-Minerve Louerat who provided me with the possibility to join their team at LIP6-CIAN, and who gave me access to their laboratory facilities. Without her support, it would not be possible to conduct this research.

I would like to thank all the professors at UPMC who have always had time to guide me. I am particularly grateful to Prof. **Hassan ABOUSHADY** and for Prof. **Gérard SOU** for their guide, help and support. For my friend at LIP6 Alhassan, Islam, Tamer, Imen and Armin for being supportive and thoughtful. Their knowledge and advice have contributed to this thesis in so many ways.

I would like to thank my family for their endless love. Being away from them for more than 4 years has not been easy, if it was for their understanding and encouragements, I would not have had the strength to go through it. Thank you!

Last but not least, I am thankful to all of my friends in Paris Anna, Lorijn, Ali and Hanen. You have made this journey worth it.

## Contents

| Al | bstra           | $\operatorname{\mathbf{ct}}$                          | iii |

|----|-----------------|-------------------------------------------------------|-----|

| Al | ostra           | ct - French                                           | v   |

| A  | cknov           | vledgements                                           | ix  |

| Al | bbrev           | viations                                              | xx  |

| 1  | $\mathbf{Intr}$ | oduction                                              | 1   |

|    | 1.1             | Overview                                              | 1   |

|    | 1.2             | Thesis Outline                                        | 3   |

|    | 1.3             | Harvestable Energy Sources                            | 3   |

|    | 1.4             | Vibration Energy Harvesting                           | 4   |

|    | 1.5             | Vibrational energy transduction methods               | 5   |

|    | 1.6             | Electrostatic vibrational energy harvesters           | 7   |

|    | 1.7             | Electrostatic Transducers                             | 8   |

|    | 1.8             | Energy conversion using variable capacitor            | 10  |

|    | 1.9             | Conditioning circuit                                  |     |

|    |                 | 1.9.1 Basic conditioning circuit                      | 14  |

|    |                 | 1.9.2 Charge constrained CC                           | 14  |

|    |                 | 1.9.3 Rectangular Q-V CC                              | 15  |

|    | 1.10            | Necessity of load interfaces                          | 20  |

|    | 1.11            | Thesis contribution                                   | 20  |

|    | 1.12            | Chapters summaries                                    | 21  |

|    | 1.13            | Summary                                               | 23  |

| 2  | Stat            | e of the Art for E-VEHs                               | 25  |

|    | 2.1             | Overview                                              | 25  |

|    | 2.2             | Electrostatic transducer                              | 26  |

|    |                 | 2.2.1 Electret-Free transducers                       | 26  |

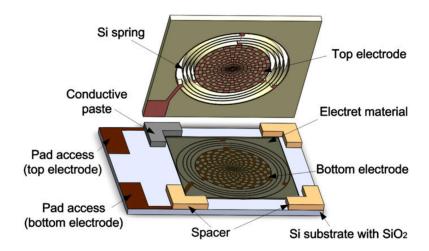

|    |                 | 2.2.2 Electret-based transducers                      | 28  |

|    | 2.3             | E-VEH with energy management interfaces               | 33  |

|    |                 | 2.3.1 E-VEH Step 1: Primitive transducer              | 34  |

|    |                 | 2.3.2 E-VEH Step 2: Synchronised transducer           | 34  |

|    |                 | 2.3.3 E-VEH Step 3: Synchronised conditioning circuit | 35  |

|    |                 | 2.3.4 E-VEH Step 4: Complete energy harvester system  | 36  |

#### CONTENTS

|   | 2.4 | Summary                                                | 3 |

|---|-----|--------------------------------------------------------|---|

| 3 | Loa | d Interface for E-VEH                                  | 9 |

|   | 3.1 | Overview                                               | 9 |

|   | 3.2 | Review of DC-DC Interfaces                             | Э |

|   |     | 3.2.1 Resistive interface                              | 1 |

|   |     | 3.2.2 Buck-Boost DC-DC Load Interfaces                 | 2 |

|   |     | 3.2.3 Buck DC-DC Load Interface                        | 3 |

|   | 3.3 | Buck Converters as Load Interface for CCs              | 5 |

|   |     | 3.3.1 Reservoir voltage regulation                     | 6 |

|   |     | 3.3.2 Load Voltage Regulation                          | 6 |

|   | 3.4 | Reservoir Voltage regulation Strategies                | 7 |

|   |     | 3.4.1 Defining $V_{res}$ Regulation Interval           | 7 |

|   |     | 3.4.2 Load Interface Control                           | 9 |

|   | 3.5 | DTVC Control                                           | Э |

|   |     | 3.5.1 Reservoir Voltage Regulation Operating Phases 50 | Э |

|   |     | 3.5.2 DTVC Sampling Clock                              | 1 |

|   |     | 3.5.3 Conduction losses                                | 1 |

|   | 3.6 | Multiple Energy-shot transfer                          | 2 |

|   | 3.7 | Load Interface Behavioural Model                       | 4 |

|   | 3.8 | Strategy of CMOS implementation                        | 4 |

|   | 3.9 | Summary                                                | 5 |

|   |     |                                                        |   |

| 4 |     | st Implementation of Load Interface System 57          |   |

|   | 4.1 | Overview                                               |   |

|   | 4.2 | AMS $0.35\mu m$ CMOS Technology                        |   |

|   | 4.3 | First implementation of Load Interface                 |   |

|   | 4.4 | Structure of the implemented load interface            |   |

|   | 4.5 | Switch Decision Block                                  |   |

|   |     | 4.5.1 Voltage Divider                                  |   |

|   |     | 4.5.2 6T Comparator overview                           |   |

|   |     | 4.5.3 6T Comparator Analysis                           |   |

|   | 4.0 | 4.5.4 Adjustable 6T Schmitt Trigger Comparator         |   |

|   | 4.6 | The clock generator                                    |   |

|   | 4.7 | Switch Control Block                                   |   |

|   |     | 4.7.1 Power Switch - $SW_{LI}$                         |   |

|   |     | 4.7.2 Dynamic flip-flop level shifter                  |   |

|   | 4.0 | 4.7.3 Switch Driver                                    |   |

|   | 4.8 | Simulation Results: First Implementation               |   |

|   | 4.9 | Summary                                                | 7 |

| 5 | Sec | ond Implementation of Load Interface System 79         | 9 |

|   | 5.1 | Overview                                               | 9 |

|   | 5.2 | Second implementation modification                     | 1 |

|   | 5.3 | Comparator Modification                                | 1 |

|   |     | 5.3.1 RS-Trigger based Hysteresis Comparator           | 2 |

| В | Seco         | ond im  | plementation schematic                                      | 113     |

|---|--------------|---------|-------------------------------------------------------------|---------|

| A | Ana          | dysis c | of Current and Energy for dc-dc buck load interface         | 109     |

|   | 6.3          | Public  | ations                                                      | <br>107 |

|   |              | 6.2.4   | Self-adjustability threshold                                |         |

|   |              | 6.2.3   | Integration of CC                                           | <br>105 |

|   |              | 6.2.2   | Diode losses                                                |         |

|   |              | 6.2.1   | Start-up circuit                                            |         |

|   | 6.2          |         | ectives and Future work                                     |         |

|   | 6.1          |         | isions                                                      | <br>103 |

| 6 | Sun          | ımarv.  | conclusions and perspectives                                | 103     |

|   | 5.10         | Summ    | ary                                                         | <br>102 |

|   |              | 5.9.3   | Discussions                                                 |         |

|   |              | 5.9.2   | Connection between on-chip and off-chip components of the L |         |

|   | 0.0          | 5.9.1   | Autonomous energy management system setup                   |         |

|   | 5.9          |         | omy of second implementation                                |         |

|   | 5.8          |         | voltage Regulator LVR                                       |         |

|   | $5.0 \\ 5.7$ |         | lock gating block                                           |         |

|   | 5.5<br>5.6   |         | side power switch - $SW_{LI}$                               |         |

|   | 5.4          |         | CR comparator                                               |         |

|   | - 1          | 5.3.5   | Adjustable RS-Trigger comparator                            |         |

|   |              | 5.3.4   | Comparing 6T and RS-trigger comparators                     |         |

|   |              | 5.3.3   | RS-trigger comparator design                                |         |

|   |              | 5.3.2   | RS-trigger hysteresis comparator operation                  |         |

|   |              |         |                                                             |         |

## List of Figures

| 1.1  | Thesis chapters and outline                                       | 2  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Harvested energy range and application                            | 4  |

| 1.3  | Vibration spectrum of varrious sources                            | 5  |

| 1.4  | Illustration of transduction methods                              | 6  |

| 1.5  | Electrostatic vibrational energy harvester systems                | 8  |

| 1.6  | Different transducer geometries                                   | 9  |

| 1.7  | General vibration energy harvester system                         | 10 |

| 1.8  | Charge constrained Q-V diagram energy conversion cycle            | 12 |

| 1.9  | QV diagrams for voltage constrained and Rectangular               | 13 |

| 1.10 | Basic conditioning circuit                                        | 14 |

|      | Charge constrained CC                                             | 15 |

|      | Charge Pump Conditioning Circuit                                  | 16 |

|      | Charge-pump CC simulation                                         | 17 |

|      | Charge-Pump CC with flyback                                       | 18 |

| 1.15 | Series-Parallel charge pump CCs                                   | 19 |

| 2.1  | E-VEH progress steps                                              | 27 |

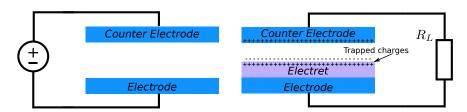

| 2.2  | Electret free and Electret transducers                            | 28 |

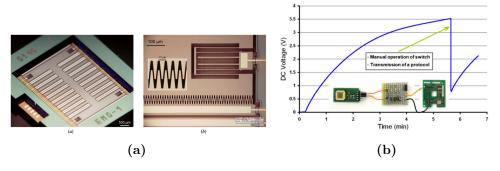

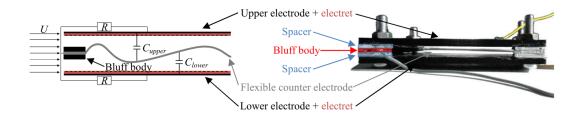

| 2.3  | E-VEH presented by Hoffmann et al; in 2011                        | 28 |

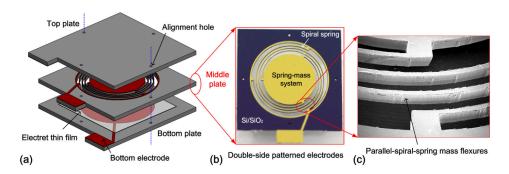

| 2.4  | Energy harvester presented by Lo et al; in 2008                   | 29 |

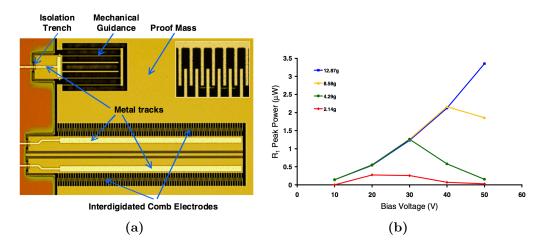

| 2.5  | Electrostatic harvester presented by Hoffmann et al; in 2009      | 30 |

| 2.6  | Proposed device by Choi et al; 2011                               | 30 |

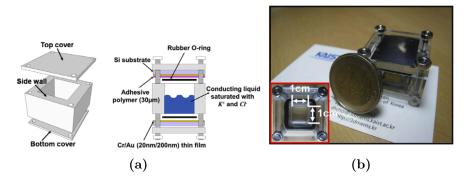

| 2.7  | Proposed devices by Altena et al; 2013                            | 31 |

| 2.8  | Proposed harvesters by Chiu et al; in 2013                        | 31 |

| 2.9  | Proposed device by Tao et al; in 2014                             | 31 |

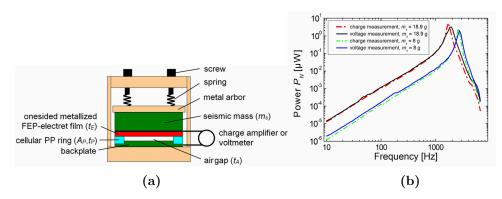

|      | Proposed devices by Hillenbrand et al; in 2015                    | 32 |

|      | Device proposed by Perez et al; in 2015                           | 32 |

|      | Proposed device by Tao et al; in 2017                             | 33 |

|      | Proposed deviced by Basset el al; in 2011                         | 34 |

|      | Proposed energy extraction by Meninger in 2001 and Torres in 2009 | 35 |

|      | Self-Synchronized energy extraction mechansim                     | 36 |

| 2.16 | E-VEH system by Kempitiyia in 2012 and Stanzione in 2015          | 37 |

| 3.1  | Overview of the system Blocks for a e-VEH                         |    |

| 3.2  | Load interfaces architectures                                     |    |

| 3.3  | Buck-Boost DC-DC Load interface                                   | 43 |

#### LIST OF FIGURES

| 3.4  | Buck converter interface                                                | 45              |

|------|-------------------------------------------------------------------------|-----------------|

| 3.5  | Series-Parallel Charge Pump CC measurements                             | $\frac{45}{47}$ |

| 3.6  | Buck Converter as LI of CCs                                             | 48              |

| 3.7  | LI control stratesiges                                                  | 49              |

| 3.8  | Discrete Time Voltage Control model                                     | 50              |

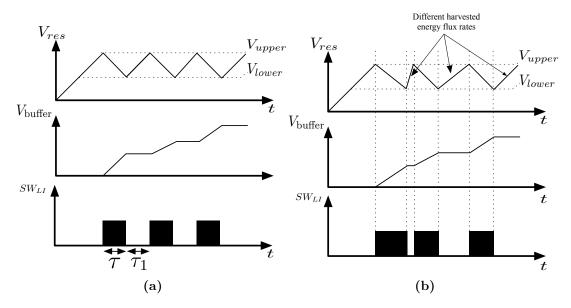

| 3.9  | Discrete Time Voltage Control Simulink model                            | 51              |

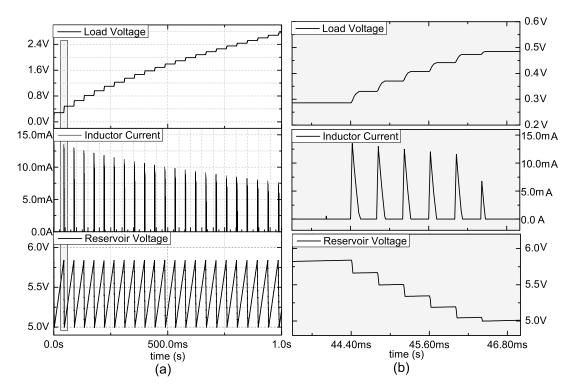

| 3.10 |                                                                         | 53              |

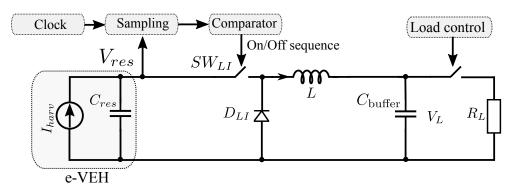

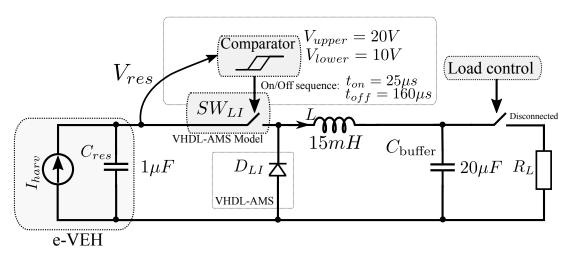

|      | Multiple Energy-Shot transfer LI VHDL-AMS model                         | 54              |

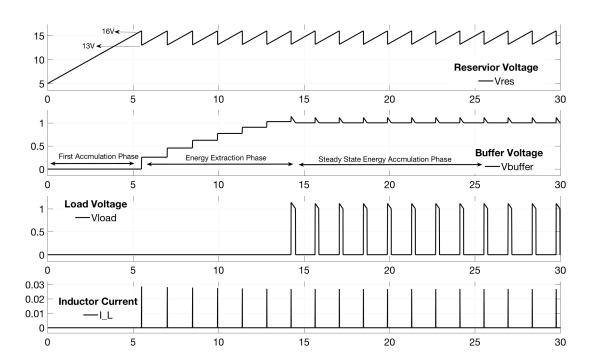

|      | VHDL-AMS model of multiple shot energy transfer                         | 55<br>55        |

| 3.12 | VIDL-AMS model of multiple shot energy transfer                         | 55              |

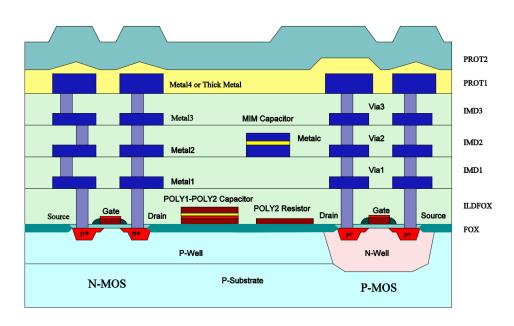

| 4.1  | Cross section of AMS technology                                         | 58              |

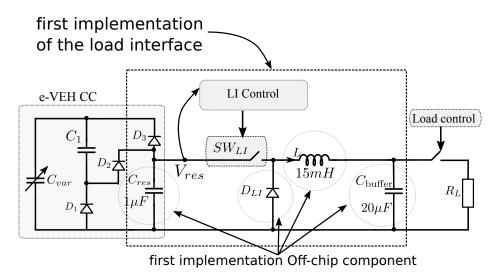

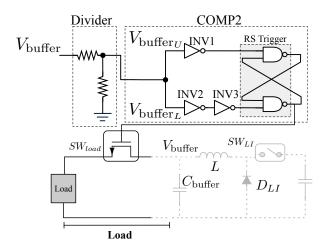

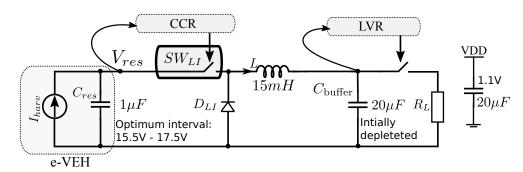

| 4.2  | Load Interface showing off chip blocks                                  | 60              |

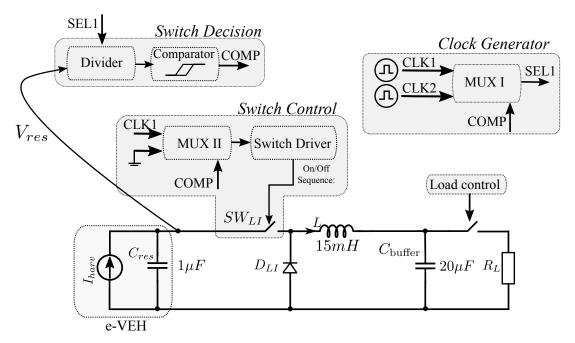

| 4.3  | Load interface architecture implementing the $V_{res}$ regulation       | 61              |

| 4.4  | Energy Transfer Modes                                                   | 62              |

| 4.5  | Switching Decision block                                                | 63              |

| 4.6  | Voltage Divider Current DC analysis                                     | 64              |

| 4.7  | 6T Comparator schematic                                                 | 65              |

| 4.8  | 6T comparator Upper threshold                                           | 66              |

| 4.9  | Transition of $V_x$ with $V_{in}$ increases                             | 67              |

| 4.10 |                                                                         | 68              |

| _    | 6T comparator thresholds with 1.1V VDD                                  | 69              |

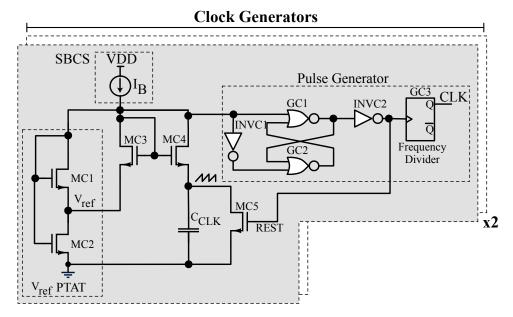

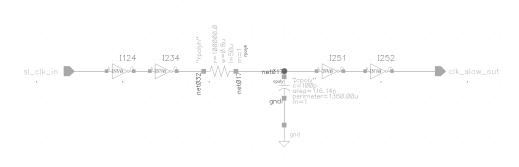

|      | Ultra low power clocks                                                  | 70              |

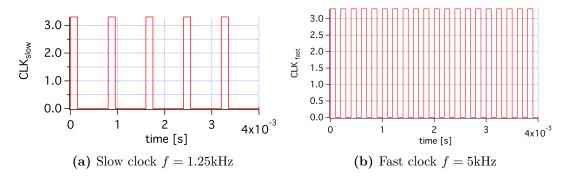

|      | Fast and Slow clock outputs                                             | 71              |

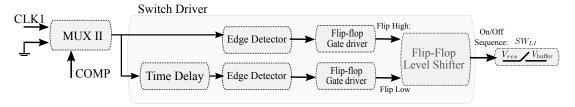

|      | Switch Control Block                                                    | 72              |

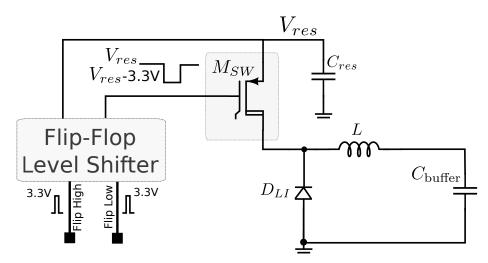

|      | Power switch with a level shifter to operate its gate commands          | 72              |

|      | Dynamic flip-flop voltage level shifter                                 | 74              |

|      | High Side power switch developed in AMS $0.35\mu m$ technology          | 74              |

|      | Switch Driver command to $SW_{LI}$                                      | 75              |

|      | Rise-edge detection circuit for $SW_{LI}$ command generation;           | 76              |

|      | Level shifter gate drivers for MN1 and MN2                              | 76              |

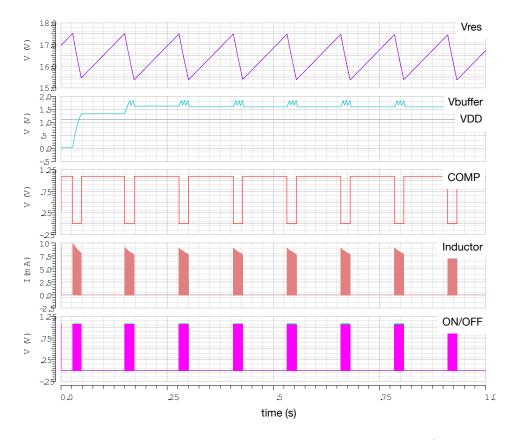

|      | CMOS Load interface simulation with multiple energy shot transfer       | 78              |

|      | The average power of each LI block simulated over 5 seconds             | 78              |

| 4.22 | The average power of each Li block simulated over 5 seconds             | 10              |

| 5.1  | First implementations drawbacks                                         | 80              |

| 5.2  | Modified Load Interface system blocks                                   | 81              |

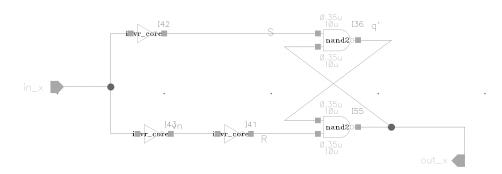

| 5.3  | RS trigger comparator                                                   | 82              |

| 5.4  | Simulation of 6T comparator simulation transient response               | 84              |

| 5.5  | Transient response for RS-trigger comparator                            | 85              |

| 5.6  | Adjustable inverter switching point                                     | 86              |

| 5.7  | Adjustable lower threshold switching point                              | 87              |

| 5.8  | RS-trigger comparator transient response simulation                     | 88              |

| 5.9  | Hysteresis comparator schematic - COMP1                                 | 88              |

|      | Power Switch with zero-static current level shifter                     | 89              |

|      | Characteristic of MN1 and MN2 showing $V_{ds}$ vs $I_d$                 | 90              |

|      | Safe-clock gating schematic $\dots \dots \dots \dots \dots \dots \dots$ | 91              |

|      |                                                                         |                 |

| 0.19 | Modified Load Interface system blocks                                   | $g_Z$           |

#### LIST OF FIGURES

| 5.14 | Second implementation LI energy transfer simulation                                |

|------|------------------------------------------------------------------------------------|

| 5.15 | Load voltage regulator                                                             |

| 5.16 | Schematic of first step simulation                                                 |

| 5.17 | Simulation of the first step                                                       |

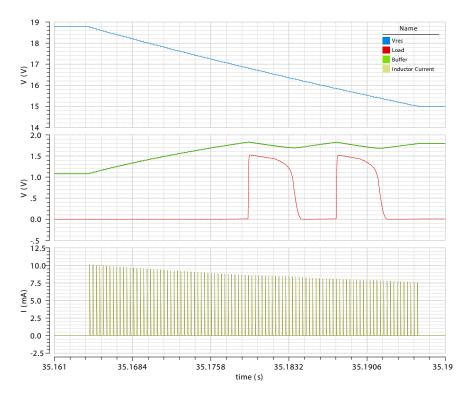

| 5.18 | An energy shot transfer showing $V_{res}$ , $V_{buffer}$ , $V_{load}$ and $I_L$ 97 |

| 5.19 | Schematic of step simulation with pads                                             |

| 5.20 | Second implemention simulation with Pads - part 1                                  |

| 5.21 | Second implemention simulation with Pads - part 2                                  |

| 5.22 | Second implemention simulation with Pads - part 3                                  |

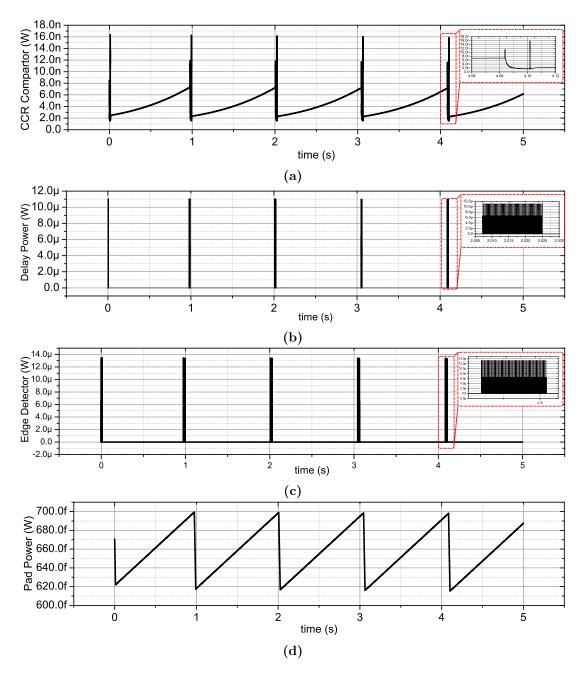

| 5.23 | Instantaneous power consumption of CCR, delay and edge detector $101$              |

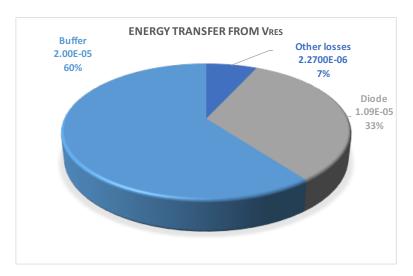

| 5.24 | Diagram showing each block received energy precentage during an en-                |

|      | ergy transfer                                                                      |

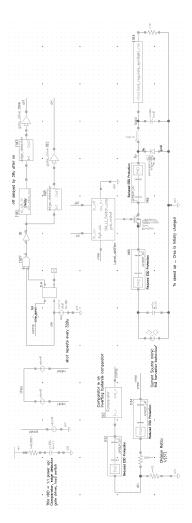

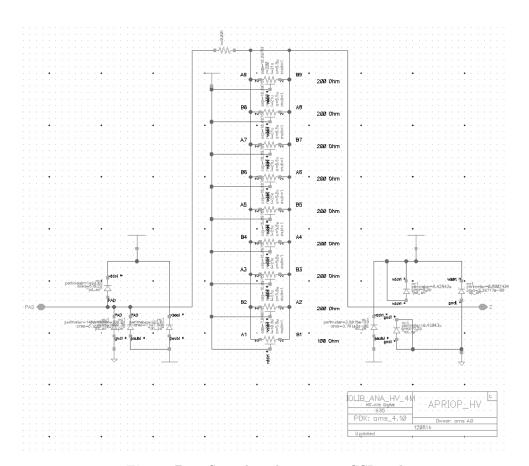

| B.1  | Second implementation schematic overview                                           |

| B.2  | Second implementation comparator                                                   |

| B.3  | Second implementation $30\mu s$ delay                                              |

| B.4  | Second implementation CCR pad                                                      |

## List of Tables

| 1.1 | Estimated harvestable power density                             |

|-----|-----------------------------------------------------------------|

| 1.2 | Vibration spectrum of different vibrating source                |

| 1.3 | Comparison between PE, EM and ES transduction methods           |

| 2.1 | State-of-art for electret-free electrostatic transducer         |

| 2.2 | State-of-art for electret-based electrostatic transducer        |

| 4.1 | CMOS $0.35\mu m$ H35B4D3 technology specifications              |

| 4.2 | High voltage transistor parameters of AMS H35B4D3 60            |

| 4.3 | Design parameters of the load interface first implementation 60 |

| 4.4 | Design parameters for the two clock generators                  |

| 5.1 | 6T comparator transistor sizing                                 |

| 5.2 | RS-Trigger CMOS sizing                                          |

| 5.3 | Energy for Single ON and OFF switching                          |

| 5.4 | Adjustable Inverter Sizing                                      |

| 5.5 | Adjustable $V_{lower}$                                          |

| 5.6 | Average Power Consumption modified LI                           |

| 5.7 | RS-Trigger comparator COMP2                                     |

| 5.8 | CCR comparator consumed energy per transfer                     |

| 6.1 | Comparison with similar work                                    |

## Abbreviations

**CC** Conditioning Circuit

**RF** Radio Frequency

$\mathbf{EM} \quad \text{Electromagnetic} \quad$

**ES** Electrostatic

PE Piezoelectric

VEH Vibration Energy Harvesters

e-VEH Electrostatic Vibration Energy Harvesters

${\bf MEMS} \ \, {\bf Micro-Electro-Mechanical-System}$

**CCR** Conditioning circuit Regulator

LVR Load voltage Regulator

MPPT Maximum power point tracking

TC Time Control

VC Voltage Control

$\mathbf{DTVC}$  Discrete-Time Voltage Control

## Chapter 1

## Introduction

| Contents                                        |          |

|-------------------------------------------------|----------|

| 1.1 Overview                                    | <br>. 1  |

| 1.2 Thesis Outline                              | <br>. 3  |

| 1.3 Harvestable Energy Sources                  | <br>. 3  |

| 1.4 Vibration Energy Harvesting                 | <br>. 4  |

| 1.5 Vibrational energy transduction methods     | <br>. 5  |

| 1.6 Electrostatic vibrational energy harvesters | <br>. 7  |

| 1.7 Electrostatic Transducers                   | <br>. 8  |

| 1.8 Energy conversion using variable capacitor  | <br>. 10 |

| 1.9 Conditioning circuit                        | <br>. 13 |

| 1.9.1 Basic conditioning circuit                | <br>. 14 |

| 1.9.2 Charge constrained CC                     | <br>. 14 |

| 1.9.3 Rectangular Q-V CC                        | <br>. 15 |

| 1.10 Necessity of load interfaces               | <br>. 20 |

| 1.11 Thesis contribution                        | <br>. 20 |

| 1.12 Chapters summaries                         | <br>. 21 |

| 1.13 Summary                                    | <br>. 23 |

#### 1.1 Overview

ERGY harvesting has been around since hundreds, if not thousands, of years. Whether it was windmills, waterwheels or even the simple concept of storing the energy from heat and vibrations. In fact, before the electrical era, energy harvesting was the only possible way to get any useful form of energy.

Fast forward to today, the term Energy Harvesting is used to refer to extracting energy from surrounding environment. The research behind energy harvesting has grown wide recently and its driven by the need for autonomously power embedded systems. Traditionally Li-ion batteries have been the go-to method for powering such system, yet they impose certain limitations such as their lifespan and maintenance. In

these applications, batteries proved to be inadequate and unpractical for applications such wearable gadgets and implantable medical devices.

With the gap between the energy required to operate such devices and the functionality expected out of it is closing more and more with each year (mirco-watts range), energy harvesting presents a solution to power such application. This said, energy harvesting raises some issues that need to be addressed before it can be used. These includes:

- Capture and transform the energy efficiently.

- How to accumulate, store and condition the harvested energy.

The issue of efficiently capturing the energy is introduced and studied extensively within the energy harvesting community[1]. This PhD project is concerned with how to manage the captured energy. However, before discussing our approach of how to tackle this issue, a brief introduction to energy harvesting fundamentals is presented in this chapter.

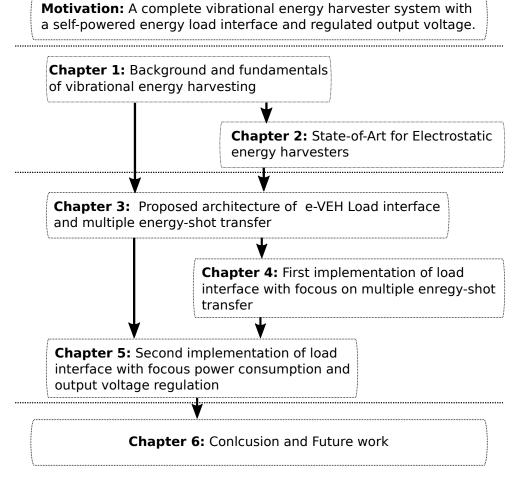

Figure 1.1: Thesis chapters and outline

#### 1.2 Thesis Outline

The thesis outline, shown in Figure 1.1, is as follows: Chapter 1 presents the fundamentals of Vibration Energy Harvesters (VEH) and especially Electrostatic Vibration Energy Harvesters (e-VEH) as well as the motivation for this PhD project. Chapter 2 highlights the recent reported vibrational harvesters and energy management interfaces. The methodology we present to tackle the problem of load interfacing with the vibrational energy harvester is discussed in Chapter 3. A first approach towards a smart energy management interface for e-VEH is proposed in Chapter 4, while an improved version of the load interface addressing how to make the management interface work autonomously is presented in Chapter 5. This work conclusion and future work are summarised in Chapter 6.

#### 1.3 Harvestable Energy Sources

Our surrounding environment is filled with various sources of energy that await to be harvested. These sources share few common features such as being abundant, and available yet free. The sources that are of interest for energy harvesting applications can be classified by the nature of the energy harvested. These types include:

- <u>Mechanical energy</u> where vibration or mechanical stress/strain sources exists. These sources could be a factory engine or a truck on a bridge.

- <u>Thermal energy</u> where sources of heater exists. These include industrial machinery, furnaces and friction.

- <u>Light energy</u> this is usually implemented by solar panels that make use of direct sunlight or even ambient light sources.

- <u>Electromagnetic energy</u> where source of Radio Frequency (RF) waves are used to wireless transfer energy. This is commonly used for RFID and wireless charging of electronic devices.

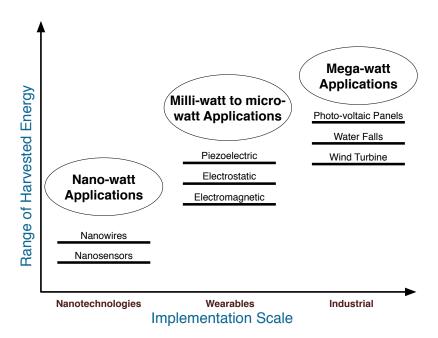

The sources of energy can also be classified by the amount of energy available to be harvested. By defining the scale of application they can be classified into nano-watt, milli-watt and Mega-watt applications as shown in Figure 1.2. For the application that requires megawatt power range waterfalls and wind turbines as well as solar cell panels are appropriate. For mid range power applications (milli to micro watts) piezo-electric, electrostatic and electromagnetic energy harvesters from sources like vibration are proven to be sufficient. For nano watt application the technology bound needed to be pushed a little further towards piezoelectric nanowires and Nano-sensors. To put this into perspective, Table 1.1 summarises the power density for each energy source. This PhD project is concerned with micro-scale energy harvesting that is derived from Micro-Electro-Mechanical-System (MEMS) devices. Targeted applications include health monitoring wearables where a typical case is to harvest a user's vibrational energy and then use it to monitor and transmit data without the need for a battery <sup>1</sup>. In the next section, vibrational energy is introduced as well as its transduction to electrical energy methods.

<sup>&</sup>lt;sup>1</sup>The health monitoring wearable is not the scope of this thesis whereas the energy management interface is the main focus of this work.

Figure 1.2: Harvested energy range and application

| Energy Source   | Characteristics  | Harvestable Power  |  |  |

|-----------------|------------------|--------------------|--|--|

| Vibration       | Hz - Human       | $4\mu W/cm^2$      |  |  |

| Vibration       | kHz - Industrial | $800\mu W/cm^3$    |  |  |

| Thermal         | Human            | $60\mu W/cm^2$     |  |  |

| Thermai         | Industrial       | $1 - 10\mu W/cm^2$ |  |  |

| Light           | Outdoor          | $100mW/cm^2$       |  |  |

| Ligit           | Indoor           | $100\mu W/cm^2$    |  |  |

| Radio Frequency | GSM 900 MHz      | $0.1\mu W/cm^2$    |  |  |

| requency        | WiFi             | $0.001/muW/cm^2$   |  |  |

Table 1.1: Estimated harvestable power density

### 1.4 Vibration Energy Harvesting

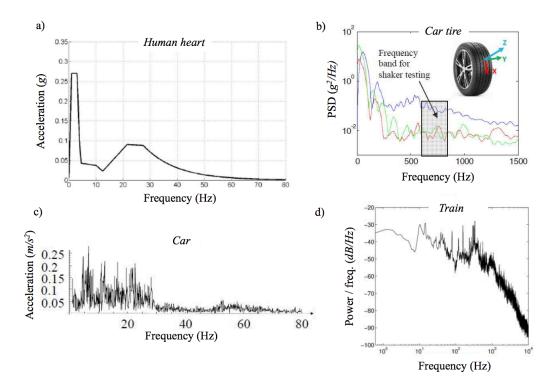

The source of vibration energy could be any ambient kinetic energy in the surrounding environment. It could be a car engine, a washing machine or simply a running man. The frequency and amplitude of such source vary since they vary in their nature. Figure 1.3 shows some selected vibration spectrum from different ambient sources while Table 1.2 presents the amplitude and peak frequency of vibrations in some ambient sources.

As can be seen from Figure 1.3 the vibration spectrum spread over a range of frequencies yet most of its power is concentrated in a narrow band of frequencies. Moreover, Table 1.2 it is clear that the ambient vibration sources in the low frequency range.

**Figure 1.3:** Vibration spectrum of (a) human heart blood acceleration[2] (b) tire inner surface @60 km/h[3] (c) car acceleration[4] (d) train acceleration[5]

Vibration source Peak acceleration Peak frequency  $[m/s^2]$  $F_{peak}$  [Hz] 12 200 Car engine compartment 121 Kitchen blender casing 6.4Clothes dryer 3.5 121 HVAC vents in office building 60 0.5 Wooden deck with foot traffic 1.3 385 External window of a busy street 0.7100 Washing machine 0.5109 Refrigerator 0.1 240

**Table 1.2:** Vibration spectrum of different vibrating source [6]

#### 1.5 Vibrational energy transduction methods

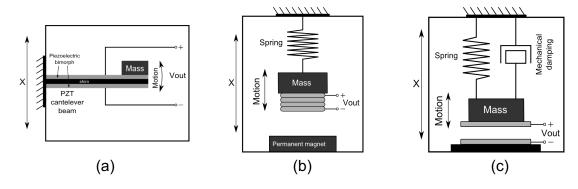

This section presents the common methods of converting vibration energy into electrical energy with an emphasise what is called *electrostatic energy harvesting*. These methods of converting mechanical energy into electrical energy exits, cf. Figure 1.4, includes: Electromagnetic (EM), Electrostatic (ES) and Piezoelectric (PE) [7–9].

<u>Piezoelectric (PE)</u>: Consider a clamped cantilever made of two bimorph layers and separated by a thin dielectric film and a proof mass attached its tip, cf. Figure 1.4a.

The mass is allowed to move freely with an external vibration are exerted on it. This creates a strain on the piezoelectric material and separates charges across it. If the movement of the mass is caused by a periodic vibration, an alternating voltage is created. With rectification stage, this voltage can be captured and stored in a battery [10, 11]. Some successful implementation of PE transducers was presented [12–15]

<u>Electromagnetic (EM)</u>: They are based on electromagnetic induction and ruled by Lenz's law where an electromotive force is generated from a relative motion between a coil and a magnet [16]. Assuming a movable coil attached to proof mass which resonates with an external vibrating source, cf. Figure 1.4b. As the movable coil cuts through the permanent magnetic flux it induces a current in the coil<sup>2</sup>. Electromagnetic transduction usually requires a boost converter stage to provide sufficient voltage for standard rectification techniques [17]. Some practical implementation was presented in [18, 19]

<u>Electrostatic (ES)</u>: vibration transducer is implemented by a variable MEMS capacitor, cf. Figure 1.4c. A proof mass is attached to one of the electrodes and is allowed to resonate <sup>3</sup>. The principle of energy conservation states that for the transducer to transform the mechanical energy into electrical energy, an electrically-originated damping force on the moving mass should be applied to purposely reduce its kinetic energy.

Electrostatic transduction usually features high voltage with relatively low output power (typically less than  $10\mu W$  [1]). It is easier to integrate with power electronics compared to other transduction methods [6], since it uses MEMS silicon technology. This allows implementing the transducer along with its driving CMOS electronics on the same wafer. A detailed survey of electrostatic energy transducers state-of-the-art will be presented in Chapter 2.

Figure 1.4: Illustration of (a) Piezoelectric (b) Electromagnetic (c) Electrostatic transduction

Each of the mentioned methods of transduction has its advantages and disadvantages as summarised in Table 1.3. In most cases, PE and ES devices are more appropriate for small scale energy harvesters (<1-10 cm<sup>3</sup>) while EM converters are better for larger devices[16]. Moreover, ES converters show more potential when it comes to monolithic integration. Electrostatic converters feature low output power levels, yet with power electronics shifting towards ultra low power consumption, they

<sup>&</sup>lt;sup>2</sup>The moving part can be either the movable coil or the permanent magnet.

$<sup>^3</sup>$ Electrostatic transducers can be non-resonators, yet in this context they are assumed resonant structures.

now can be introduced as a valuable power source. This PhD project is concerned with electrostatic transduction and thus the next section is dedicated to discussing its fundamentals.

| Table 1.3: | Comparison | between PE, | EM and | ES | transduction | $_{ m methods}$ |

|------------|------------|-------------|--------|----|--------------|-----------------|

|------------|------------|-------------|--------|----|--------------|-----------------|

| Method          | Advantages and Disadvantages of conversion methods   |

|-----------------|------------------------------------------------------|

|                 | _Advantages:                                         |

|                 | - high output power density[6]                       |

| Piezoelectric   | - no separate pre-charging voltage source            |

|                 | - no need to control any gap [16]                    |

|                 | $\underline{Disadvantages:}$                         |

| (PE)            | - expensive material[20]                             |

| (1 L)           | - hard to integrate with CMOS technology[6]          |

|                 | Advantages:                                          |

|                 | - high output current[20]                            |

| Electromagnetic | - long lifetime[16]                                  |

|                 | - robustness[16]                                     |

|                 | $\underline{Disadvantages:}$                         |

| (EM)            | - low output voltages [16]                           |

| (12111)         | - low efficiency in low frequencies[16]              |

|                 | Advantages:                                          |

|                 | - high output voltage[21]                            |

| Electorstatic   | - low cost[16]                                       |

|                 | - easy to integrate with CMOS[6]                     |

|                 | <u>Disadvantages:</u>                                |

| ()              | - requires a separate pre-charging voltage source[6] |

| (ES)            | - high impact of parasitic[16]                       |

|                 | - need to precisely define $\mu m$ -dimensions[16]   |

#### 1.6 Electrostatic vibrational energy harvesters

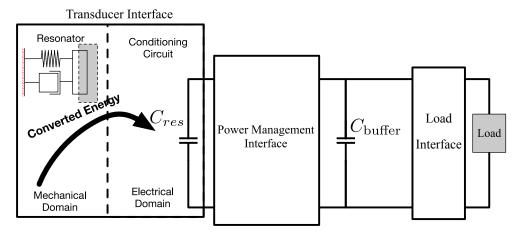

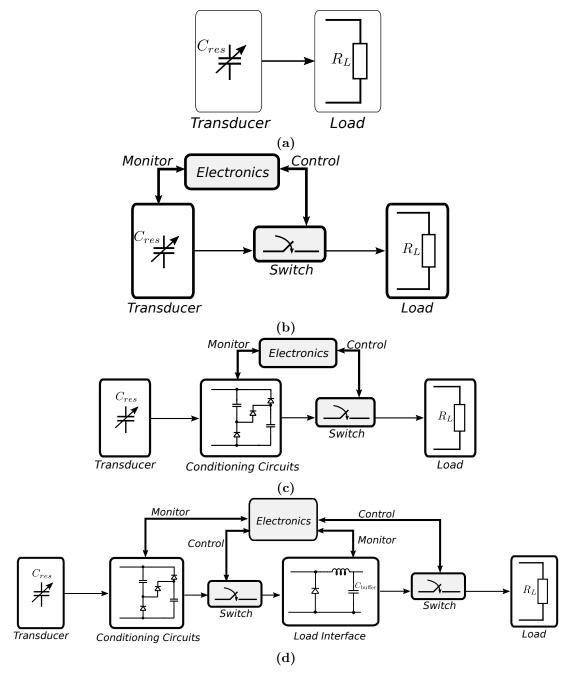

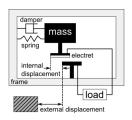

Electrostatic Vibrational Energy Harvester e-VEH systems refer to a wide array of architectures that aims to manage the energy harvesting process and prove a stable constant DC voltage to a load or a buffer. In fact, a vibrational energy harvester system can be break up into:

– <u>The transducer interface</u> which is the system input where the source vibration energy is applied. This part of the system is responsible of regulating the energy transduction process and accumulating the energy on to a reservoir. This part of the system includes variable MEMS capacitors as transducers, see section 1.7, and conditioning circuit CC, see section 1.9, section , which synchronise the energy conversion with the capacitor variation.

This stage is chosen according to the nature of the transducer - whether it is piezoelectric, electromagnetic or electrostatic - different implementation of these interfaces are used. For example, piezoelectric transducer requires an AC-to-DC rectification as the piezoelectric transducer provides an AC output voltage. Electromagnetic transducers on the other hand require a boost dc-dc converter and rectification stages as its transducers usually provide low AC output voltage. For electrostatic VEH the transducer is accompanied by a conditioning circuit (CC), that synchronises the energy conversion with the movement of the variable capacitor, such as [6, 22–25].

- <u>Power management interface</u> This block controls the energy flow between the transducer interface and the load interface blocks. For electrostatic vibrational harvesters this block is usually rarely address with most of the community research focusing on the transducer interface block (either the transducer itself or its synchronising electronics and the CCs).

- <u>Load interface</u> This is the output of the system, where the electrical energy is consumed by a load. This block aims to provide the load with a stable regulated DC voltage.

In chapter 2, the recent progress of energy management interfaces is described in details. Moreover, this PhD work is concerned with developing and implementing a whole system of e-VEH with focus on the energy management interface and the load regulation.

Figure 1.5: Electrostatic vibrational energy harvester systems

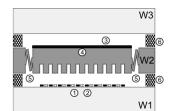

#### 1.7 Electrostatic Transducers

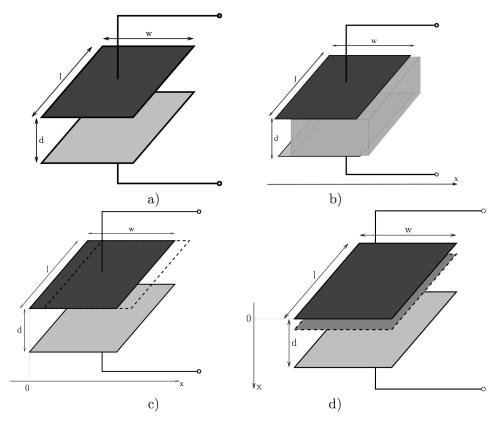

Electrostatic transducers are usually based on Micro-Electro-Mechanical-System (MEMS) capacitors [1]. These capacitors are two terminal devices with one terminal attached to a mobile proof mass while the other is fixed to a non inertial reference frame. The variable MEMS capacitor response is described according to the direction of motion of the external vibration exerted on the proof mass. This leads to a change in one of the capacitor parameters, cf. Figure 1.6a, where the capacitance  $C_{var}$  is expressed as,

$$C_{var} = \epsilon \frac{W \cdot l}{d} \tag{1.1}$$

where  $\epsilon$  is the permittivity of the medium between the two plate ( $\epsilon = \epsilon_r \epsilon_0$  where  $\epsilon_r$  is the relative permittivity and  $\epsilon_0$  is vacuum permittivity), W and l are the width and

the length of the parallel plates while d is the distance between the parallel plates.

It can be seen the geometry variation can be classified into: parallel movable plate, movable dielectric and gap closing capacitor Figure 1.6. The movable dielectric geometry depends on varying the effective area of the dielectric material by sliding it between the capacitor's plate. The out-of-plan parallel electrodes geometry refers to the type of variable capacitor where the effective parallel plate area varies. A gap-closing capacitor operates by varying the gap between the capacitor two plates.

The most common geometry of the variable plate capacitor in the context of energy harvesting is the gap varying capacitor [6]. For a gap-varying capacitor, equation 1.1 is reduced to,

$$C_{var} = \epsilon \frac{W \cdot l}{d_0 \pm x} \tag{1.2}$$

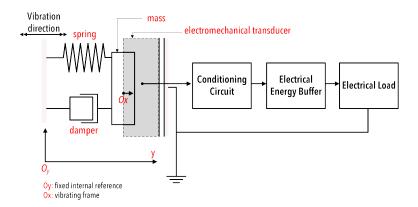

where x is the displacement of the movable plate as illustrated in Figure 1.6. As the gap moves towards closer the capacitance increases. The translation of the source vibration into a displacement of the variable capacitor movable plate can be simplified with the aid of two frames of reference, cf Figure 1.7. First the inertial reference (global frame)  $(0_Y)$  of which the vibration source occurs, while the second reference is a non-inertial reference frame  $(0_X)$  of attached to the source of the external vibrations.

Figure 1.6: Different transducer geometries (a) parallel plate (b) a movable dielectric (c) out-of-plan parallel electrodes (d) gap-closing capacitors.

As the global reference accelerates with  $a_{ext}$ , one can write the 2nd Newtonian law

Figure 1.7: General vibration energy harvester system

for the non-inertial (second) reference frame, where the movable mass is subject to an apparent force equal  $-ma_{ext}$ . The principle of energy conservation states that in an isolated system the energy remains constant over time. This means that for the transducer to transform the mechanical energy into electrical energy an electrically-originated damping force on the moving mass is applied to purposely reduce its kinetic energy. In the case of parallel plate capacitor, such force is an electrostatic force which is expressed by,

$$F_{elec} = \frac{1}{2}V^2 \frac{dC_{var}}{dx} \tag{1.3}$$

Where V is the voltage across the parallel plate capacitor and  $\frac{dC_t}{dx}$  is the space gradient of the capacitance. Plugging in Eq.1.2 into Eq. 1.3,

$$F_{elec} = \frac{1}{2} \epsilon V^2 \frac{W \cdot l}{(d \pm x)^2} \tag{1.4}$$

This shows that the electrostatic force does not scale down with the device dimensions, since both  $W \cdot l$  and  $(d_0 \pm x)^2$  scale quadratically, whereas mechanical forces are proportional to the linear dimensions of the spring and to the cube for the mass inertia which means that electrostatic forces are too weak to be useful at the macroscale[1]. Moreover, it can be seen that this force is dependent on the voltage V and thus the transducer mechanical behaviour can be controlled by changing biasing voltage.

#### 1.8 Energy conversion using variable capacitor

This section discusses the energy conversion from the mechanical domain into the electrical domain using a variable capacitor. Capturing the external vibration using a resonator with the aid of interface circuit to induce an electromechanical feedback force acting on the variable capacitor. For example, consider a gap-closing variable MEMS capacitor which is exposed to an external vibration, the vibration is captured and translated into a force acting on the capacitor movable plate. This changes the capacitor "physical" parameter, in this case the gap, which in turn changes the stored energy in the capacitor. For all cases of the variable capacitors geometries the energy

stored in the capacitor is defined as,

$$U = \frac{QV}{2} = \frac{Q^2}{2C_{var}} \tag{1.5}$$

It can be seen that the stored energy is controlled by either the amount of the charges or the induced voltage difference. Allowing vibrations to decrease the capacitance of a variable capacitor while keeping its voltage or charge constant produces energy in the form of charge or voltage, respectively[23]. These are indeed the two conversion schemes which are used to transducer the mechanical energy into electrical energy using a variable capacitor. The energy conversion process can either be charge-constrained or voltage constrained. Constraining the charge generates high voltages (up to 250V) that easily exceed the breakdown limits of standard CMOS technologies [26]. However, constraining the voltage while allowing the variable capacitor to make use of the already existing energy source to drive and to sink the harvested energy into it [23].

<u>Charge-constrained</u>: Let us consider the scenario where the charges Q on the variable capacitor is forced to be fixed. Also, let us assume that the rest position of that capacitor is where the x=0.

The proof mass attached to the movable plate induced a displacement due to the external vibration exerted on it. The new displacement  $d_1$  is the maximum allowed displacement for the movable plate. This will force the capacitance of  $C_{var}$  to decrease which in turns will increase the voltage across the plate according to Q = CV. The converted energy can be calculated as the difference between the capacitor's final energy state and the initial energy state as follows,

$$\Delta U = \frac{1}{2} (C_{max} V_0^2 - C_{min} V_{max}^2) \tag{1.6}$$

where  $C_{max}$  is the initial capacitance value with an initial voltage of  $V_0$  while  $C_{min}$  is the final capacitance reach by the capacitor corresponding to the maximum voltage of  $V_{max}$  is reached. Given that constant charge  $Q_0$  is assumed at all time,

$$C_{max}V_0 = Q_0 = C_{min}V_{max} (1.7)$$

then the converted energy can be expressed as,

$$\Delta U = \frac{1}{2} V_0^2 C_{max} (\frac{C_{max}}{C_{min}} - 1)$$

(1.8)

<u>Voltage-constrained</u>: This conversion scheme assumes that the voltage is fixed during the movement of the movable plate. Considering the rest position is when the gap is  $d_0$  and the capacitance is at its local maximum. As the capacitance starts to decreases the charges Q decreases following Q = CV. The converted energy can be expressed as,

$$\Delta U = \frac{1}{2} (C_{max} V_{const}^2 - C_{min} V_{const}^2) = \frac{1}{2} V_{const}^2 C_{min} (\frac{C_{max}}{C_{min}} - 1)$$

(1.9)

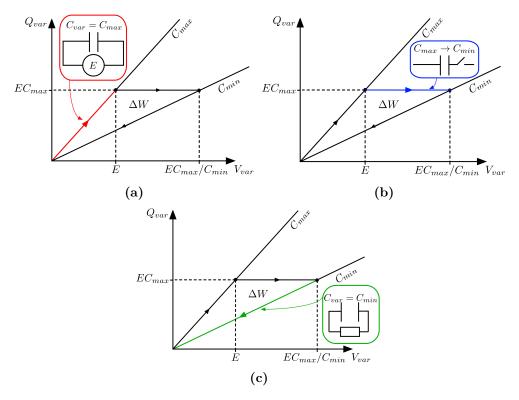

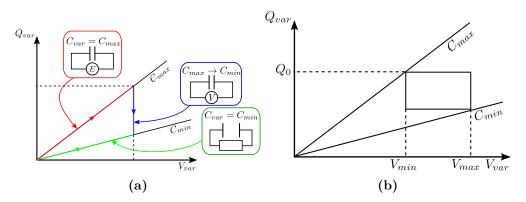

# Q-V diagrams

The Q-V diagrams present the states of the variable capacitor at different moment in time. This representation allows to easily estimate the converted energy per capacitance variation cycle. The converted energy is given by the enclosed area of the Q-V diagram. It is intuitive to use Q-V diagram as a graphical tool to analyse these two conversion schemes, constant voltage and constant charge.

<u>Charge-constrained Q-V diagram</u>: The Q-V diagram of charge constrained scheme is shown in Figure 1.8. The states of the variable capacitor are as follows:

- First, the capacitor  $C_{var}$  is connected to a reservoir, cf. Figure 1.8a.

- Next the capacitor decreases from  $C_{max}$  to  $C_{min}$  forcing the voltage to increases the energy stored in the capacitor from E to  $E\frac{C_{max}}{C_{min}}$ . During this stage the variable capacitor is isolated from the load, cf. Figure 1.8b.

- Finally, the variable capacitor is connected to a reservoir allowing to discharge the harvested energy, cf. Figure 1.8c.

Figure 1.8: Charge constrained Q-V diagram energy conversion cycle

<u>Constant Voltage Q-V diagram:</u> Figure 1.9a shows the capacitor states in a constant voltage scheme. Theses states are as follows,

- First the capacitor  $C_{var}$  is connected to an energy source charging it with its initial energy until maximum capacitance  $V_{res}$  is reached.

- Next,  $C_{var}$  is allowed to decrease while fixing the voltage using a voltage source.

- Finally, the variable capacitor is connected to a reservoir allowing to discharge the harvested energy.

Figure 1.9: Q-V diagram for (a) Voltage constrained (b) Rectangular

For both conversion schemes the harvested energy is numerically equivalent to the area enclosed by the QV diagram. It should be mentioned that practical implementation of these schemes is hard to be achieved precisely. This is as it requires a synchronisation between the charge flow and the capacitance variation. In most implementations, a modified Q-V cycle is adopted which is called rectangular Q-V cycle, cf. Figure 1.9b.

To decide which scheme - charge or voltage constrained- is better, certain hypotheses using the Q-V diagram must be considered. If the voltage source available initially is greater than the achievable voltage then constant charge scheme will produce more energy than the constant voltage. However, if the voltage equally limited in both schemes, then the constant voltage will provide more energy.

In the previous conversation schemes, it is assumed that a certain control is imposed to fix the charge, for fixed charge conversion, or the voltage, for fixed voltage conversion. In reality this is achieved through what is called Conditioning Circuit (CC). The conditioning circuits fundamentals and their requirements as electrostatic CC are discussed in the next section.

# 1.9 Conditioning circuit

This section presents different conditioning circuits as well as their implementation. First a basic conditioning circuit is introduced, then a primitive rectangular Q-V conditioning circuit. This section concludes with what is called a series-parallel charge pump CC, which is used for this project.

To study the conditioning circuits CC, the variation of transducer capacitance C(t) is must be defined and fully characterised as a function of time. A main hypothesis of the transducer capacitance is periodic with period T and having only one local maximum and minimum ( $C_{max}$  and  $C_{min}$ ) over this period should be emphasised [1]. In reality, because of the electromechanical coupling, the C(t) depends on the electrical operation of the conditioning circuit can be non-periodic. However, assuming a predetermined C(t) is a necessary step in the to present CC operation and will be assumed as such in the rest of this context.

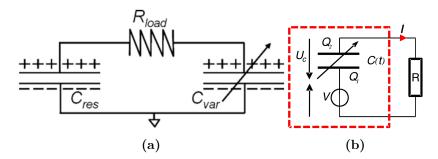

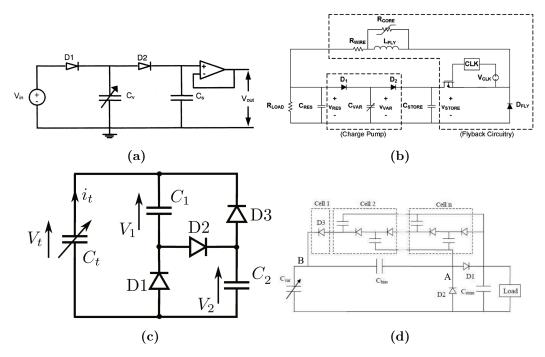

#### 1.9.1 Basic conditioning circuit

This CC is regarded as the simplest implementation of a CC where the transducer is connected in series with a load and a large capacitor reservoir  $C_{res}$ , cf. Figure 1.10. This implementation is first described in [27] to characterise an electret based transducer see chapter 2. In this arrangement a change in capacitance will always cause a charge transfer between the two capacitors through the load resistance imposing work on the load [28]. As the capacitor's movable plate moves due to the external vibration, its

Figure 1.10: Basic conditioning circuit

charges vary resulting in a current flow i(t) between the two capacitors through  $R_L$  which is expressed as,

$$i(t) = \frac{dQ_{var}(t)}{dt} \tag{1.10}$$

where Q is the instantaneous charge on the capacitance. This current dissipates power on the resistance, and this power can only come from the mechanical domain, not from the initial charge of  $C_{res}$ . Indeed, the system goes back to its initial electrical state after each periodic cycle of  $C_{var}$  since the charges on  $C_{var}$  and  $C_{res}$  are constant.

The drawback of this CC is that the load experiences an AC current with each capacitor cycles which would require a rectification step to supplying DC loads[20]. Moreover, this CC is unable to increase its internal energy [1].

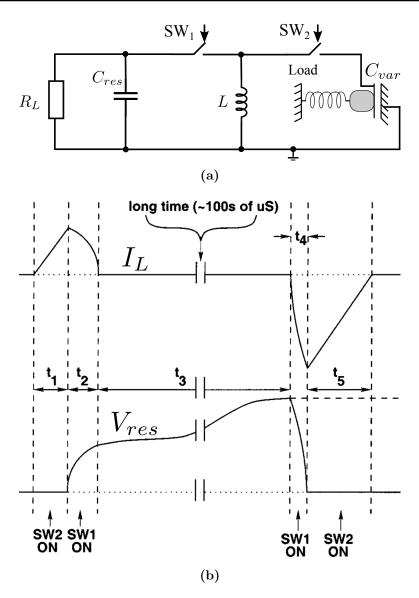

#### 1.9.2 Charge constrained CC

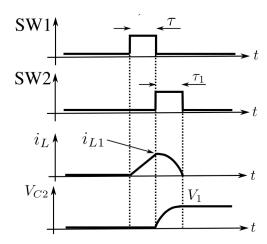

Another conditioning circuit implementation which is called charge constrained CC is shown in Figure 1.11a. This CC requires precise switching mechanism to insure proper energy extraction as shown in Figure 1.11b <sup>4</sup>. Charge-constrained CC operates as follows:

- Assuming initially  $C_{var} = C_{max}$  and with charge of  $Q_0$ . With the switches SW1 and SW2 are turned off. As the  $C_{var}$  decreases by separating the plates of the capacitor due to the external vibration source, the voltage increases as the charges are forced to be constant.

- When the capacitance on  $C_{var} = C_{min}$  reaches its local minimum, the switch SW2 is turned on, removing some charges <sup>5</sup> from  $C_{var}$  and moving its energy into the

<sup>&</sup>lt;sup>4</sup>Figure adopted from [29]

<sup>&</sup>lt;sup>5</sup> The time constant of when the capacitors is connected to the inductor is much shorter than the vibration period.

Figure 1.11: Charge-constrained CC (a) schematic (b) switching timing

inductor in the form of an inductor current  $i_L$ .

- Afterwards when  $V_{res}$  drops to zero and  $i_L$  is maximised, the switch SW1 is turned on and the charges removed from  $C_{var}$  are placed on  $C_{res}$  without losses. The capacitor  $C_{var}$  moves back to its maximum value.

- The process is repeated with the overall system energy increasing.

One of the first realisations of the charge-constrained cc was introduced in 2001 by Meninger et al; [29]. Another implementation was proposed later in 2005 by Despesse et al; [4]. This CC requires precise switching mechanism for the CC be able to function. In [29] a digital control was proposed with a counter and a delay line to achieve this precise switching mechanism, see Chapter 2.

# 1.9.3 Rectangular Q-V CC

Rectangular Q-V CC has two advantages over the two previous CC (i) rectangular Q-V cc allow self-increasing of the accumulation of converted energy starting from initially small bias. (ii) they can be implemented without external electronics to synchronise the charge from the transducer with the mobile mass[1]. Two variations of rectangular Q-V CC will be presented in this subsection: Charge-Pump CC and Series-Parallel Charge Pump CC.

#### Charge-Pump CC

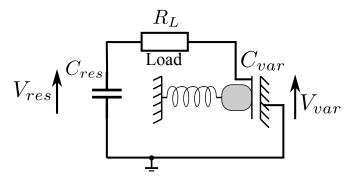

The first implementation of rectangular QV CC was introduced by [6]. It is based on the traditional charge pump architecture and was implemented as shown in Figure 1.12.

Figure 1.12: Charge Pump Conditioning Circuit

Assuming initially  $V_{var} = V_{res} = V_{store}$ ,  $C_{var} = C_{max}$  and both diodes D1 and D2 are turned off. The charge-pump CC operates as follow:

- As  $C_{var}$  decreases,  $V_{var}$  increases since the charge is kept constant.

- When  $V_{var}$  is high enough to turn D2 ON,  $V_{store}$  is connected.

- The charges are removed from  $C_{var}$  into  $C_{store}$ , dropping the voltage on  $C_{var}$ . In other words, the charges are pumped from  $C_{var}$  into  $C_{store}$ .

- The charges are pumped until D2 no longer is forward biased, and  $C_{var}$  moves from its local minimum value to its local maximum value, which decreases the voltage on  $C_{var}$ .

- As  $C_{var}$  decreases further D1 is forward biased allowing charges to move from  $C_{res}$  into  $C_{var}$ .

- As  $V_{var}$  increases reaching D1 is no forward biased, stopping the charge transfer.

- This process is repeated as  $C_{var}$  cycles between its maximum and minimum local values.

In sum, the mechanical vibrations have done a work on the  $C_{var}$  increasing the total energy stored in the system.

#### Practical implementation of charge-pump CC

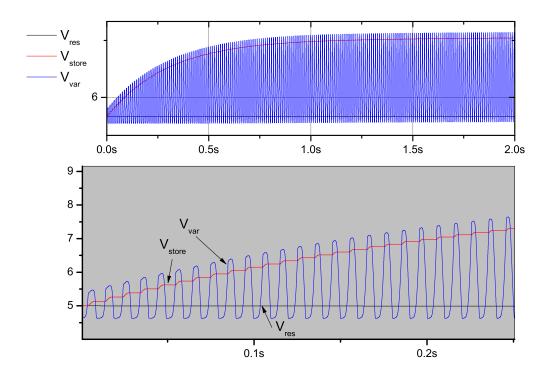

To illustrate the charge-pump conditioning circuit, a VHDL-AMS model is used to simulate its behaviour as shown in Figure 1.13. The Charge Pump CC simulated had the following parameters similar to the one presented in [21]:

- Initial voltage on  $C_{res}$  equal to  $V_{res} = 5V$

- Variable capacitor  $C_{var}$  varying between 100-200F.

- Reservoir capacitor was  $C_{res} = 1\mu F$

- Storage capacitor of  $C_{store} = 3n$ F.

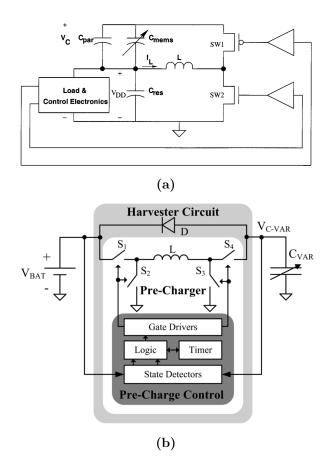

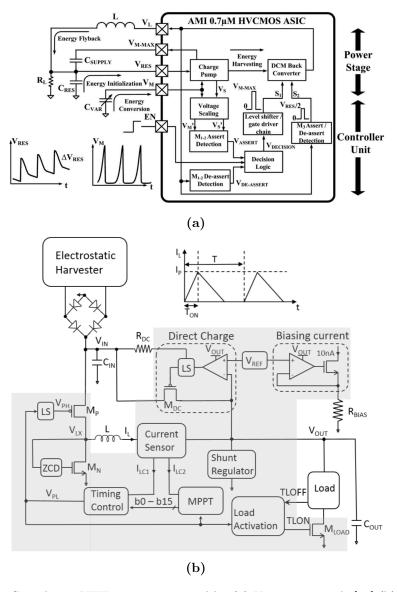

The simulation shows that after few cycles of energy harvesting and increasing of  $C_{store}$  voltage, a saturation state is reached. To ensure continuous energy harvesting process a mechanism by which charges from  $C_{store}$  is extracted is removed from the CC is needed. Most practical implementations of charge pumps conditioning circuits implement some sort of feedback mechanism, where after few energy harvesting cycles the charges are removed from  $C_{store}$  and placed on  $C_{res}$ . This could be a resistive flyback such as in [30] and [31], or an inductive flyback such as in [21].

Figure 1.13: Charge-pump CC simulation

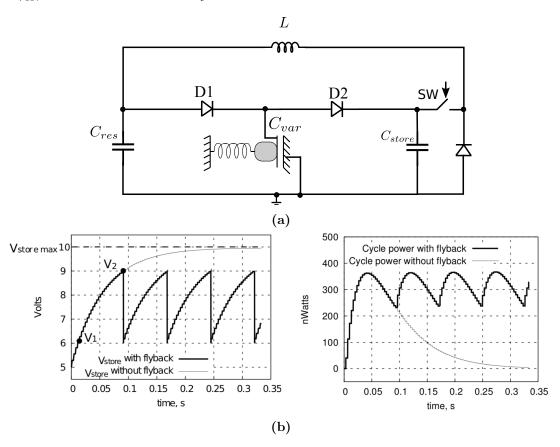

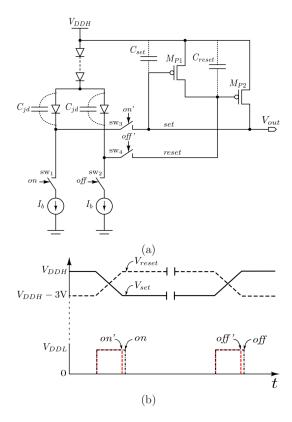

An example of the flyback mechanism is shown in Figure 1.14 where an *inductive flyback mechanism* is proposed. The flyback switching mechanism was defined by two voltages an upper and lower bound voltages. When the upper bound is reached flyback is activated while when the lower bound is reached flyback is turned off. The voltage on  $C_{strore}$  is periodically compared with these two voltages.

The charge-pump with inductive flyback mechanism simulated with and presented

in [21]. The flyback is activated at  $V_2 = 9V$  and deactivated at  $V_1 = 6V$  using the freewheeling diode and 15mH inductor with  $31\Omega$  winding resistance. As can be seen from the simulation, cf. Figure 1.13, the charge-pump with the flyback mechanism is able to maintain continuous harvesting process with self-increasing internal voltage on  $C_{res}$ , unlike the CC without flyback mechanism.

Figure 1.14: Charge-Pump CC with flyback (a) schematic (b) behaviour simulation[20]

This CC raises some issues when considering practical implementation such as:

- The voltage on  $C_{res}$  is increasing with time, and would eventually require regulation to ensure that maximum energy flux is extracted with the flyback mechanism.

- Without  $C_{res}$  regulation, the switching events which is supplied by  $C_{res}$  will vary as the voltage  $V_{res}$  slowly increases. This is due to the flyback mechanism slowly, but gradually, increases the biasing conditions of the CC when charges are removed from  $C_{store}$  into  $C_{res}$ . In practical implementations such as [21] a periodic re-calibration phase was proposed. In this implementation a semi-empirical calculation is achieved to deduce and update the two switching voltages.

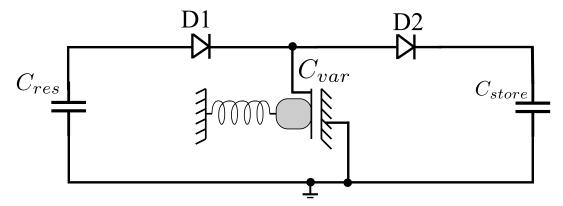

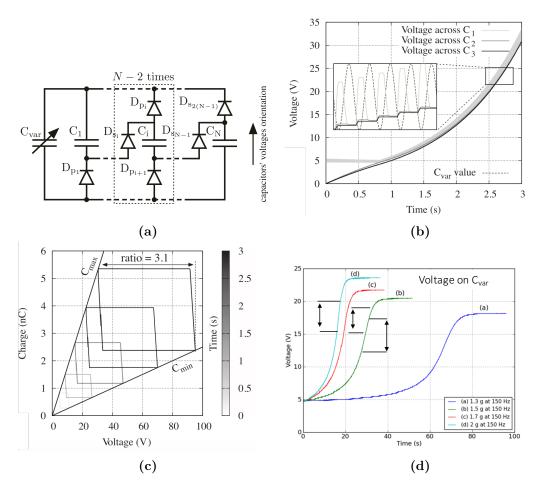

#### Series-Parallel Charge Pump

The series-parallel charge pump conditioning circuit is a modified architecture from what is called Bennet's doubler, which was first introduced by Queriroz et al. [32] in 2014. It gained the interest of the electrostatic energy harvesting community as

it is well suited with CMOS integration when the variable macroscale capacitor is replaced by microscale MEMS capacitors. It is a new family of CCs that is capable of exponentially increasing their internal accumulated harvested energy and the energy converted at each cycle [1]. These CC are capable of continuous harvesting operation through self-increasing their internal voltage.

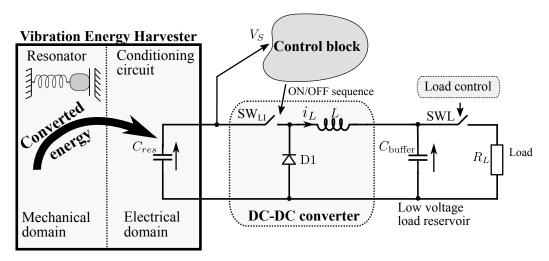

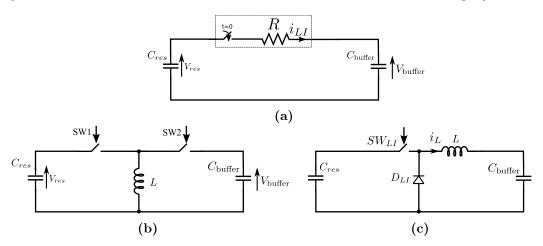

A generic topology for series-parallel charge-pump conditioning circuits can be seen in Figure 1.15a. It is composed of the variable MEMS capacitor  $C_{var}$  and number of voltage doubling cell. A details description of the series-parallel charge pump behaviour is found in [1, 33–35] It is worth to mention that in practical implementation this self-increasing of the internal voltage process actual reach a stopping point when the electromechanical coupling becomes dominant [33, 34].

#### Practical implementation of series-parallel charge-pump CC

A simulation of series-parallel charge pump CC behaviour can be seen in Figure 1.15b and 1.15c. These simulation are for a CC with  $C_{var}$  varying between  $C_{min} = 100 \text{pF}$ ,  $C_{max} = 180 \text{pF}$ , N=2, C1 = 1 nF, C2 = 10 nF and  $V_{var_0} = 5 \text{V}$ . As can be seen starting from initial low voltage invested on  $C_{var}$ , the internal voltage of the harvester exponentially increases as the variable MEMS capacitor transducer the mechanical energy from vibration into an electrical energy. Moreover, the area enclosed in the QV diagram with every cycle of the transducer increases with time indicating an increase in the harvested energy.

The drawback of the series-parallel charge pump is that after few cycles the electromechanical coupling forces become dominant stopping the converted energy from increasing. As can be seen in Figure 1.15d this behaviour of exponentially self increasing the internal voltage of the CC is not exhibited in real implementation, see Chapter 3. It is evident that to keep the energy harvesting process going on in the CC, part of the energy captured in has to be periodically extracted from the conditioning circuit.

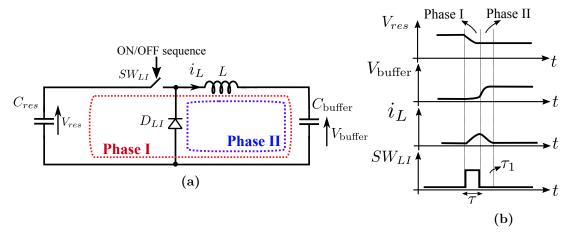

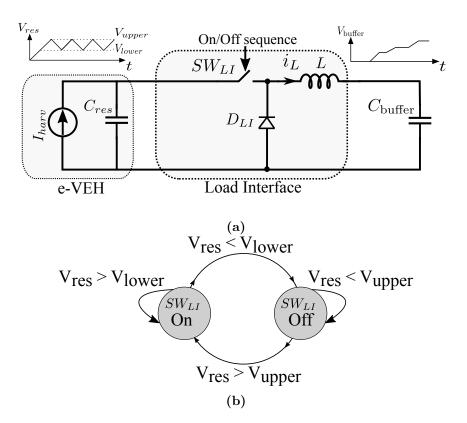

# 1.10 Necessity of load interfaces

In e-VEH the harvested energy is accumulated on a reservoir capacitor, however without regulation of the internal voltage of the harvester's CC, a saturation state will occur. If part of the reservoir capacitor energy is periodically removed this will ensure that the harvesting process will not reach the saturation state. The removed energy from  $C_{res}$  is temporarily stored onto a buffer capacitor. This buffer capacitor is necessary for two reasons:

- First, the reservoir capacitor can not directly supply the loads as it has to sustain sufficient energy across it to allow the harvester to properly function.

- Second, the voltage across the reservoir capacitor is usually high to directly interface with the load, so a step down voltage converter needs to be used.

For these reasons we proposed a load interface that transfers the energy from the reservoir capacitor into a buffer capacitor. This interface is able to maintain maximum energy flux from the energy harvester. It defines the amount of energy needed to be extracted from the harvester without compromising its efficiency and transfer this

**Figure 1.15:** Series-parallel charge-pump CC (a) Generic topology (b) output voltage simulation (c) Q-V diagram with time (d) measurement of  $V_{var}$  for different excitation[34]

energy to a temporary storage to be later used to supply a low voltage load. This interface is responsible for the following requirements to be fulfilled:

- Regulating the reservoir voltage to its optimal mode.

- A stabilised load voltage around a nominal low voltage.

# 1.11 Thesis contribution

This thesis is concerned with rectangular Q-V CC. It addresses the implementation of a complete vibrational energy harvesting system as imagined in Figure 1.5. As mentioned earlier in sections 1.9.3 and 1.10, a part of the energy accumulated on the CC needs to be removed and stored temporarily onto a buffer capacitor.

This PhD work tackles this problem using the starting point of an optimum interval to extract the energy from  $C_{res}$  [34]. We propose a method of energy extraction without impacting the efficiency of the energy harvester. The amount of energy extracted as well as when this energy is extracted impact on the harvesting process will be discussed see Chapter 3. However, this function is achieved with what we call a load interface.

This thesis introduces Conditioning Circuit Regulator (CCR) which interfaces the rectangular Q-V CC to buffer capacitor. This CCR periodically extracting part of CC harvested energy into a buffer capacitor. The next step is Load Voltage Regulation (LVR) block which is responsible for regulating the output voltage within a nominal low voltage. This thesis manuscript reports the following:

- Proposed a new ultra low power architecture for e-VEH with rectangular Q-V

CC load interface that is based on DC-DC buck converter.

- Provided an optimised mixed-signal load interface controller operating with an input power at least  $2\mu W$ .

- Proposed a low output voltage regulator for the load in conjunction with the proposed load interface enabling a load to be periodically supplied by the e-VEH.

# 1.12 Chapters summaries

Chapter 1 This chapter presents the fundamentals of energy harvesting in general. It focuses on vibrational energy harvesting and more specifically electrostatic energy harvester. First we summarise the different methods of transduction of vibrational energy. Then electrostatic transduction ES advantages over other types of transduction methods are listed. These include: the high output voltage of ES, relatively low cost, and ease of integration with CMOS. Afterwards, the three main blocks of any smart electrostatic vibrational energy harvesters (e-VEH) is highlighted. These blocks are the transducer interface, the power management interface and the load interface. The transducer interface is responsible for transduction the vibrational energy into electric energy as well as conditioning the output voltage from the transducer using a conditioning circuit. Afterwards, the power management interface ensures that the conditioning circuit is operating at its maximised output energy flux rate. This is achieved by maintaining the internal voltage of the CC within its optimum interval through periodically extracting part of the CC energy and temporary store onto a buffer storage. The proposed buffer storage can be a rechargeable battery of a capacitor. The last block of the e-VEH is the load interface, which is responsible for the regulated low output voltage and supplying the load the harvested energy when available.

The rest of the chapter is dedicated to discussing the fundamentals of the electrostatic transducer, conditioning circuits and the necessity of load interfaces for e-VEHs. For the conditioning circuit, this work incorporates rectangular QV cycle CC. Even though the interface we propose can work with any rectangular QV cycle CC, yet the design of interface targeted series-parallel charge pump. This is a new family of CC with a key feature of its capability of self-increasing of the CC internal voltage starting from relatively low voltage.

Chapter 2 In this Chapter the state-of-the-art of electrostatic energy harvesters is discussed. An overview of the practical implementations in the last decade is presented, distinguishing between four main steps towards what can be called a complete e-VEH. The main characteristic to differentiate between these steps was the control electronics.

With the research in the community shifting from developing a simple transducer, to incorporating synchronised and self-synchronised conditioning circuit to a full system that takes into account the optimum operating conditions of the CC as well as the load interface. This chapter highlights the fact that a mature and smart e-VEH with both load and energy management interfaces is still not explorer within the community. The goal of this PhD work is to tackle this problem for a particular type of e-VEH CC namely series-parallel charge pump CC.

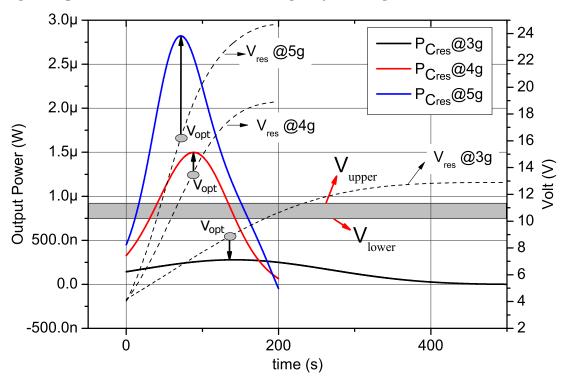

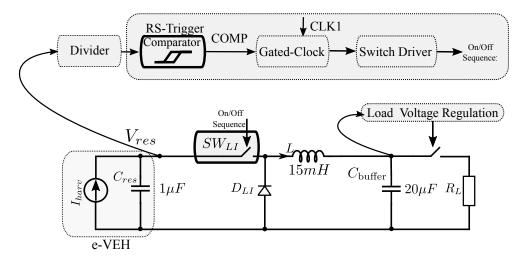

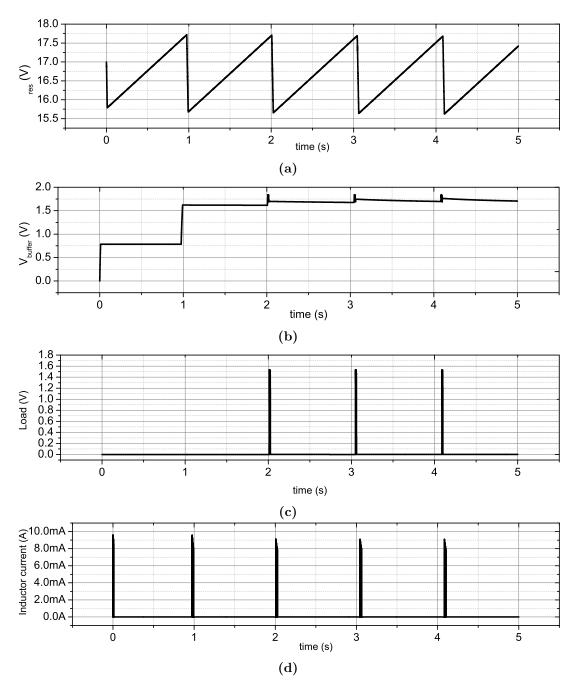

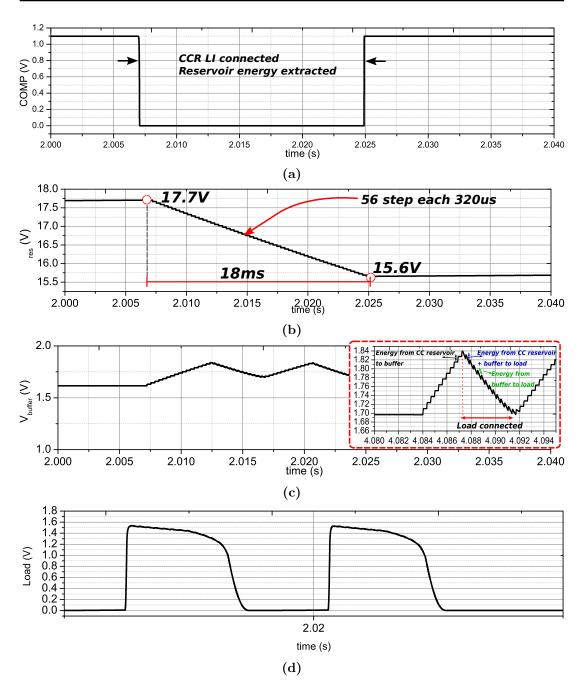

Chapter 3 In Chapter 3, we describe the architecture developed within the frame of this work. First different mechanisms which are used to transfer and manage the energy extraction between two capacitor storage is discussed. These include dc-dc interfaces that are capable of transferring the energy with minimum losses between capacitors. A justification for using buck dc-dc converter is explained with the two regulation processes that dictated by the e-VEH. The regulation process is the reservoir voltage regulation and the load voltage regulation. The reservoir voltage regulation is necessary to keep the harvesting processing from reaching saturation, while the load voltage regulation is necessary for the low output regulated voltage for the load. The reservoir voltage regulation strategies are proposed through first defining the optimum interval of the CC internal voltage. Afterwards, the load interface control technique is explained. For this work, the load interface control is achieved through a discretetime voltage control which is explained by the aide of behaviour model simulation. Finally, one major type of losses is identified, namely condition losses. To overcome such issue, multiple energy-shots transfer is proposed. In such scheme the energy extraction from the energy reservoir to a buffer reservoir through a number of small shot instead of a single shot. This maintains the interface inductor current within an upper bound and helps mainly minimal losses during the transfer. This chapter concludes with a VHDL-AMS behaviour model for the multiple energy-shot load interface. In chapter 4 a transistor level implementation is proposed while in chapter 5 an improved implementation of the LI addressing the power consumption is addressed.

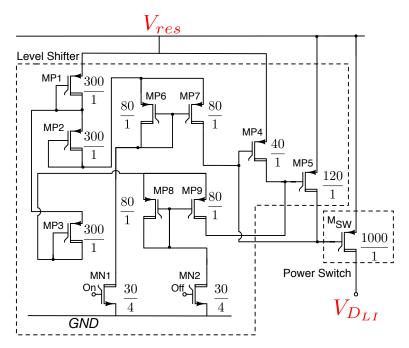

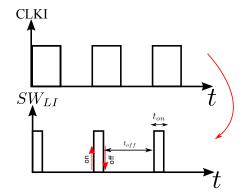

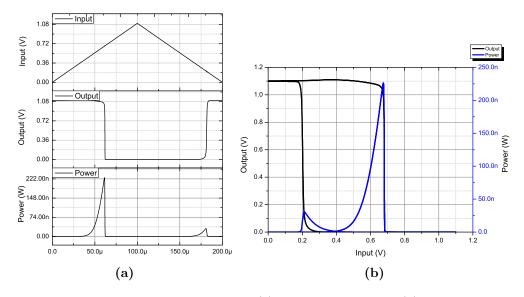

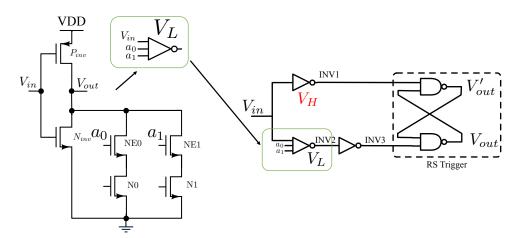

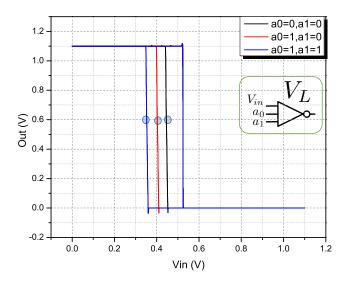

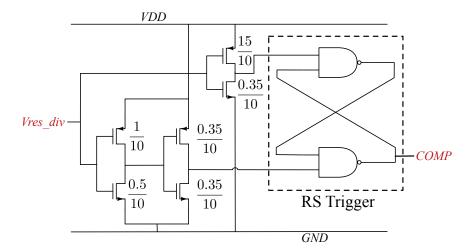

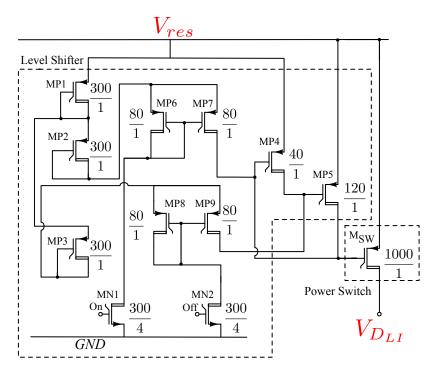

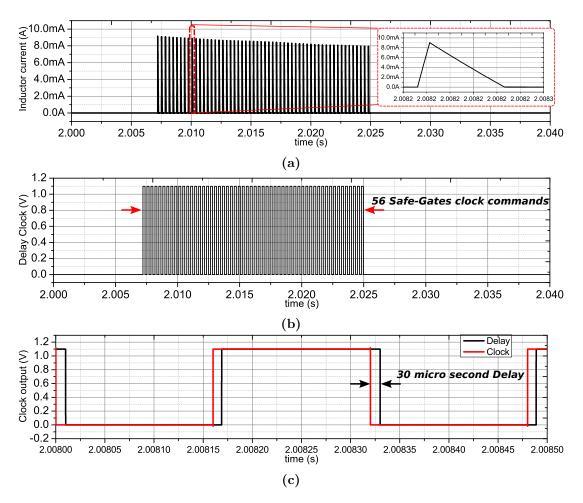

Chapter 4 In this chapter the multiple energy-shot transfer is implemented in transistor level for e-VEH load interface. This implementation promises an adequate energy transfer technique regardless of the maximum inductor current limit dictated by the LT switch. Moreover, a degree of modification for the switching thresholds is proposed using an adjustable Schmitt trigger comparator that can be used to autonomously adjust with the change of the optimum reservoir voltage caused by dynamics of the harvester. This chapter begins by describing the technology of which the transistor level implementation is proposed in. Justification for choosing such technology is listed. Next, the structure of the load interface implementation is described. This implementation had three main blocks including switching decision block, clock generator block and the switch control block. Each of the proposed blocks is described in details through out this chapter. At the core of the LI controller is a low power hysteresis comparator which is used to generate the required logical commands for the LI switch, activating/deactivating the energy extraction according to the state of the system. A sampled scaled down version of the CC internal voltage is applied to the comparator allowing this logical command generation. Other blocks include an ultra low power clock generator, zero-static current level shifter and a power switch. The chapter concludes with a complete transistor level implementation of the reservoir

voltage regulator and summary of the average power consumption of each of the LI controller blocks.

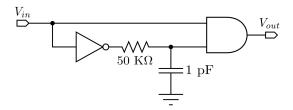

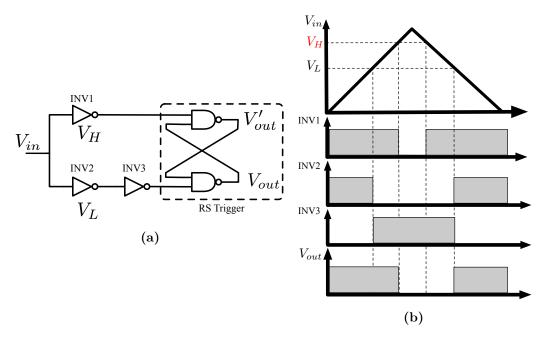

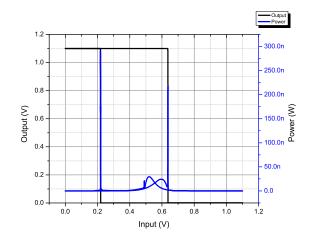

Chapter 5 A second low power load interface is proposed in this chapter. Similar to the first implementations it makes use of series-parallel charge pump CC as a conditioning circuit and a mix of high voltage interface with an ultra low power control block to maintain maximum energy harvested from e-VEH. The main focus of this implementation was to reduce the average power consumption of the LI controller and provide low output voltage regulation for the load. This required a modified LI controller architectures with a new hysteresis comparator based on RS triggers. All necessary modification required for the LI controller was carried out to reduce to reduce the power consumption. Simulated results show that the second implementation LI controller power overhead is less than 100nW thanks to an ultra low power RS-trigger based comparator.

# 1.13 Summary

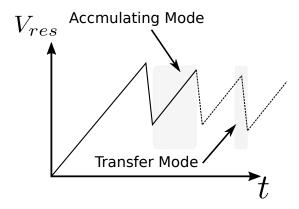

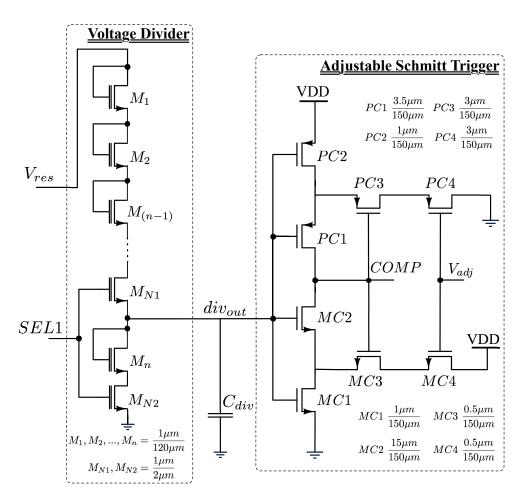

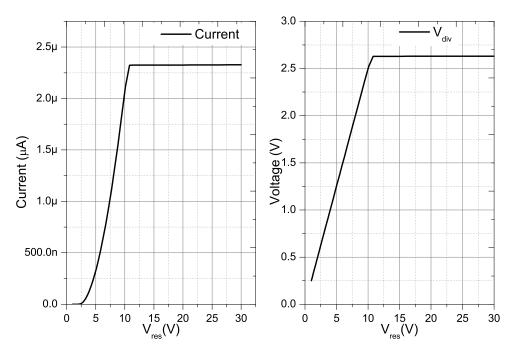

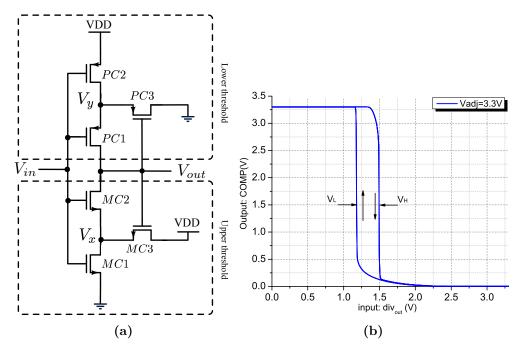

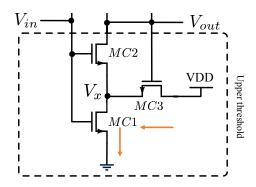

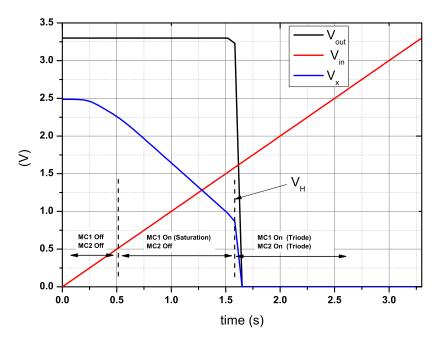

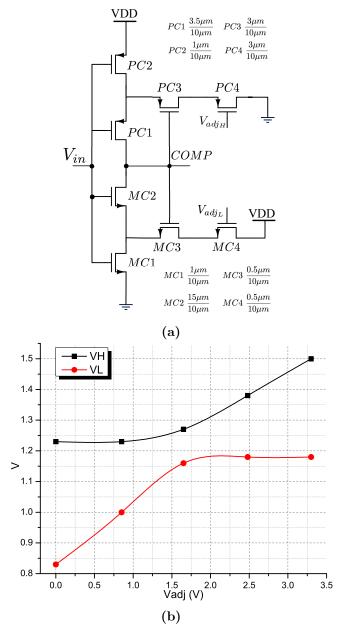

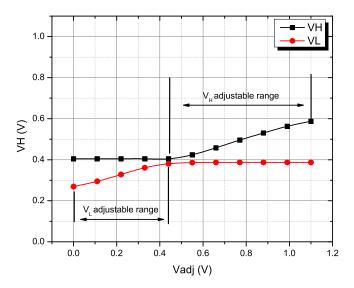

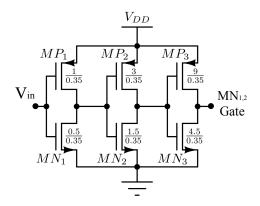

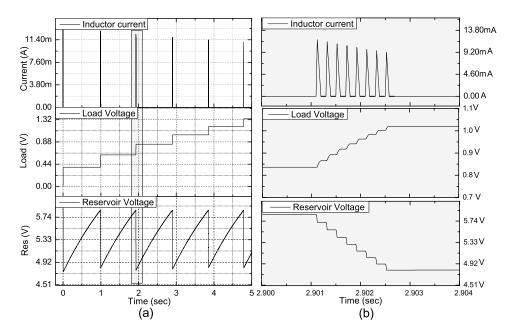

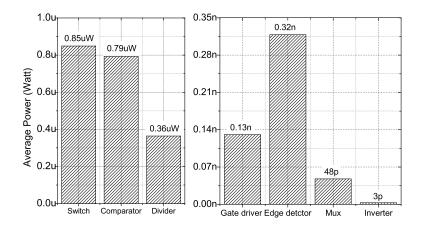

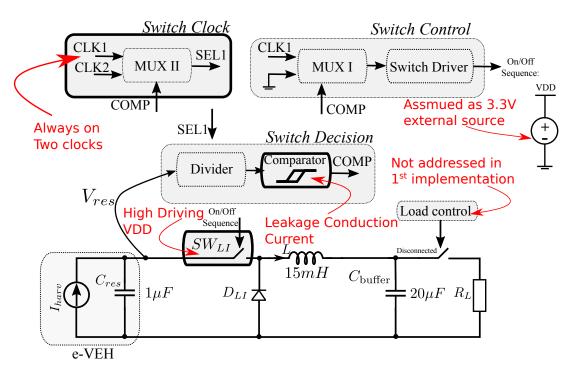

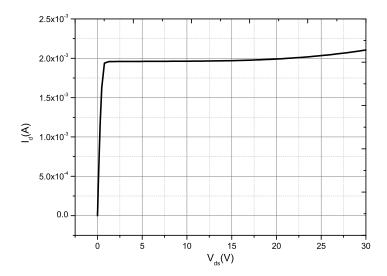

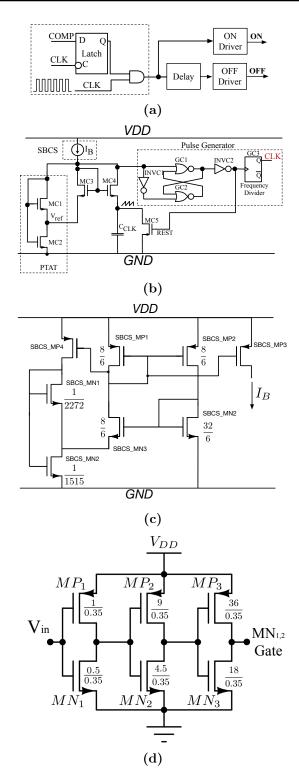

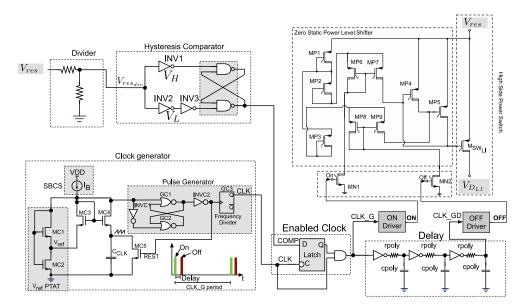

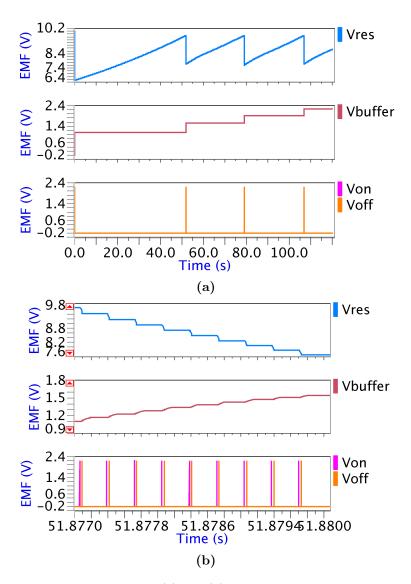

In this chapter, the fundamental of energy harvesting was introduced. A general model of vibrational energy harvesters is presented before discussing the types of conditioning circuits. With the main focus of this PhD project around electrostatic vibrational energy harvester e-VEH, a complete e-VEH system is introduced with three main blocks clearly distinguished. These main blocks general purpose is indicated, with the target of implementing a transistor level e-VEH in the subsequent sections of this thesis.