# Parallelization of iterative methods to solve sparse linear systems using task based runtime systems on multi and many-core architectures: application to Multi-Level Domain Decomposition methods

Adrien Roussel

### ▶ To cite this version:

Adrien Roussel. Parallelization of iterative methods to solve sparse linear systems using task based runtime systems on multi and many-core architectures: application to Multi-Level Domain Decomposition methods. Numerical Analysis [cs.NA]. Université Grenoble Alpes, 2018. English. NNT: 2018GREAM010. tel-01753992v2

# HAL Id: tel-01753992 https://theses.hal.science/tel-01753992v2

Submitted on 16 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITÉ DE GRENOBLE

Spécialité : **Informatique** Arrêté ministérial : 25 mai 2016

Présentée par

### Adrien ROUSSEL

Thèse dirigée par **Thierry Gautier** et co-encadrée par **Jean-Marc Gratien**

préparée au sein de l' INRIA Rhône-Alpes et de IFP Energies Nouvelles et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

Parallélisation sur un moteur exécutif à base de tâches des méthodes itératives pour la résolution de systèmes linéaires creux sur architecture multi et many cœurs : application aux méthodes de types décomposition de domaines multi-niveaux

Thèse soutenue publiquement le **06.02.2018**, devant le Jury composé de :

### M. Pierre Manneback

Professeur, Université de Mons, Rapporteur, Président du Jury

#### M. Joel Falcou

Maitre de conférence HDR, LRI, Université Paris Sud, Rapporteur

### M. Bruno Raffin

Directeur de recherche INRIA, LIG, Université de Grenoble, Examinateur

### M. Raymond Namyst

Professeur, INRIA, LaBRI, Université de Bordeaux, Examinateur

### M. Thierry Gautier

Chargé de Recherche INRIA, LIP, ENS-Lyon, Directeur de thèse

### M. Jean-Marc Gratien

Ingénieur de recherche, IFP Energies Nouvelles, Co-Encadrant de thèse

### Remerciements

Enfin! Cette page de remerciements représente l'aboutissement de près de 3 ans et demi de thèse. Toutes ces années m'ont apporté un grand enrichissement, aussi bien sur le plan professionnel que personnel. Avec ces quelques mots, je tiens à remercier tous ceux qui, de près ou de loin, m'ont permis de m'épanouir, de progresser et de cloturer cette expérience.

Tout d'abord, je tiens à remercier IFP Energies Nouvelles et INRIA Rhone-Alpes pour avoir soutenu les travaux de recherche de cette thèse. Je voudrais également remercier les membres du Jury de soutenance pour avoir accepter d'évaluer mes travaux. Tout d'abord, je tiens à remercier Joel Falcou et Pierre Manneback, qui m'a également fait l'honneur de président le jury de soutenance, pour leur rapport détaillé sur mon mémoire. Je voudrais également remercier chaleureusement Bruno Raffin et Raymond Namyst qui m'ont fait le plaisir d'accepter de participer à mon Jury de soutenance en tant qu'examinateurs. Enfin, je tiens à remercier Jean-Marc Gratien et Thierry Gautier de m'avoir encadré durant ces travaux, et de leur conseils sur toute la durée de ma thèse. Leur aide m'a beaucoup apporté durant ma thèse. Je tiens particulièrement à remercier Thierry qui, malgré la distance, m'a beaucoup conseillé et encouragé. Durant nos échanges, j'ai été particulièrement admiratif de ta grande culture scientifique et de la pertinence des échanges que l'on a pu avoir tout au long de cette thèse. Dorénavant, je ne vais plus surcharger ta boite mail!

Je voudrais remercier le Laboratoire d'Informatique du Parallélisme (LIP) de l'ENS-Lyon et l'équipe AVALON de l'INRIA pour leur accueil et l'accès aux machines qu'ils m'ont garanti pour faire certaines de mes expériences. Plus particulièrement, merci à Simon Delamare pour son aide dans la configuration du KNL et les installations logicielles!

Je n'aurais jamais pu commencer cette expérience de thèse sans Ani Anciaux et Thomas Guignon qui, alors que j'étais encore en Master à l'Université de Reims Champagne-Ardenne (URCA), m'ont permis de rencontrer Jean-Marc afin de postuler pour ce projet. A ceci, j'aimerais ajouter mes remerciements à Michael Krajecki, Arnaud Renard, Christophe Jaillet et Hervé Deleau de l'URCA pour m'avoir donné l'envie et la curiosité de poursuivre mes études en thèse, et également de m'avoir présenter à Ani et Thomas dans le cadre du stage de fin d'études de M2.

La thèse n'est pas qu'un travail académique, c'est aussi une expérience humaine. J'en profite donc pour remercier l'ensemble des membres du département d'Informatique Scientifique de l'IFPEN (R114), avec qui j'ai passé de très bons moments de rire et d'enrichissement professionnel : Ani, Thomas Guignon, Bruno, Christophe Cornet, Thomas Crabie, Laurent Astart, Christophe Delage, Jacques, Sylvie, Jean-Yves, Jean-Louis, Elsie, Vincent, Henry, Olivier et enfin Pierre Fery-Forgues.

Mention toute particulière aux thésards R114-R115 d'IFPEN. Je commence par les plus anciens, avec lesquels j'ai passé une première partie de thèse agréable en leur compagnie : Aboubacar et Huong. J'ai débuté cette expérience en même temps de Riad, et par la suite Mohamed, avec qui j'ai également de très bons moments. Bon courage à vous deux dans la poursuite professionnelle, nos chemins nous amèneront peut-être un jour à nous recroiser! Et enfin, bon courage à ceux pour qui l'aventure continue encore un peu : Nicolas, Zakariae, Karine, Julien et Bastien. Je garderais encore pour longtemps en mémoire ces quelques moments de pauses passés avec vous tous. L'ambiance du groupe des thésards était vraiment top, et j'espère vous revoir très vite!

Enfin, je tiens à remercier les différentes personnes avec qui j'ai partagé mon environnement de travail, et avec qui j'ai eu l'occasion de beaucoup discuter et d'échangers sur divers sujets : Pierre, Youness, Jose Martin Lozano Aparicio (alias le péruvien chanteur), à nouveau Nicolas, et Olivier.

Je tiens à remercier Caroline, qui a réussi à me supporter au quotidien durant toute cette période de thèse. Je ne pourrais jamais exprimer suffisamment à quel point ta présence à mes côtés m'a permis de relever ce défi. Pour finir, je tiens également à remercier ma famille qui m'a apporté tout leur soutient inconditionnel dans l'élaboration de ce projet qu'a été ma thèse.

# Contents

| K | esume                                               | I                |

|---|-----------------------------------------------------|------------------|

| 1 | Introduction  1.1 Context and motivation            | 7<br>7<br>8<br>9 |

| 2 |                                                     |                  |

| 2 | Background                                          | 11               |

|   | 2.1 Sparse linear algebra                           |                  |

|   | 2.1.1 Linear Solvers                                |                  |

|   | 2.1.1.1 Direct solver                               |                  |

|   | 2.1.1.2 Iterative Methods                           | 13               |

|   | 2.1.2 Preconditioners                               | 14               |

|   | 2.1.2.1 Generalities                                | 14               |

|   | 2.1.2.2 Polynomial                                  | 15               |

|   | 2.1.2.3 ILU(0)                                      | 15               |

|   | 2.1.2.4 AMG                                         | 16               |

|   | 2.2 Parallel Computers                              | 17               |

|   | 2.2.1 Generalities                                  | 17               |

|   | 2.2.1.1 Classification                              | 17               |

|   | 2.2.1.2 Levels of parallelism                       | 18               |

|   | 2.2.2 Processors Architecture                       | 19               |

|   | 2.2.2.1 General purpose processors                  | 19               |

|   | 2.2.2.2 Graphic Processing Units (GPU)              | 20               |

|   | 2.2.2.3 Intel <sup>®</sup> Xeon Phi Coprocessor     | 20               |

|   | 2.2.3 Memory Systems                                |                  |

|   | 2.2.3.1 Shared Memory                               |                  |

|   | 2.2.3.2 Distributed Memory                          |                  |

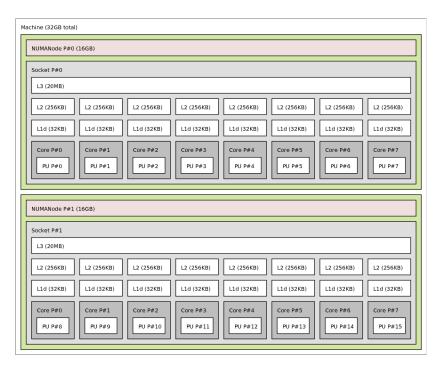

|   | 2.2.4 Topology discovery                            |                  |

|   | 2.3 Parallel Programming Models and Runtime Systems | 23               |

|   | 2.3.1 Parallel Programming Models                   | 24               |

|   | 2.3.1.1 Fork-Join Model                             | 24               |

|   | 2.3.1.2 Message Passing Model                       | 25               |

|   | 2.3.1.3 Data flow Model                             | 25               |

|   | 2.3.2 Runtime Systems                               | 25               |

|   | 2.3.2.1 Cilk                                        | 26               |

|   | 2.3.2.2 OpenMP                                      | 26               |

|   | 2.3.2.3 OmpSs                                       | 27               |

|   | 2.3.2.4 X-Kaapi                                     | 28               |

|   | 2.3.2.5 StarPŪ                                      | 29               |

|   | 2.3.2.6 HARTS                                       | 30               |

| 2.4 Discussion on HPC Trend                                                          |

|--------------------------------------------------------------------------------------|

| 2.4.1 Hardware                                                                       |

| 2.4.2 Runtime Systems                                                                |

| 2.4.3 Parallel Linear algebra                                                        |

| 2.5 Conclusion                                                                       |

| 2 Design and Evaluation of an Abstract Linear Algebra ADI on top of a worting        |

| 3 Design and Evaluation of an Abstract Linear Algebra API on top of a runtime system |

| 3.1 An Abstract Sparse Linear Algebra API                                            |

| 3.1.1 A sequential semantic to describe numerical methods                            |

| 3.1.2 Internal creation and representation of parallelism                            |

| 3.1.2.1 Data Partitioning using Graph partitioning                                   |

| 3.1.2.2 Task Decomposition                                                           |

| 3.1.2.3 Dependencies between tasks                                                   |

| 3.1.3 Translation from the API to runtime system                                     |

| 3.1.3.1 From the API to the runtime system                                           |

| 3.1.3.2 Declaration of dependencies                                                  |

| 3.1.4 DAG execution                                                                  |

| 3.1.5 Preliminary evaluations                                                        |

| 3.1.5.1 Instantiation and management of tasks                                        |

| 3.1.5.2 Efficiency on a single NUMA node                                             |

| 3.1.5.3 Impact of over decomposition                                                 |

| 3.2 Managing data locality computations                                              |

| 3.2.1 NUMA aware policy and runtime systems                                          |

| 3.2.2 Locality-aware computations in HARTS                                           |

| 3.2.2.1 Transparency at the initialization                                           |

| 3.2.2.2 Work pushing strategy                                                        |

| 3.2.2.3 Dynamic strategy at the execution                                            |

| 3.2.2.4 Positioning with related works                                               |

| 3.3 Monitoring and performance tools in HARTS                                        |

| 3.3.1 Monitoring in HARTS                                                            |

| 3.3.2 First analysis                                                                 |

| 3.3.2.1 Overhead of Instrumentation                                                  |

| 3.3.2.2 Iterative method analysis                                                    |

| 3.3.2.3 Work inflation in a NUMA system                                              |

| 3.4 API Evaluation on various preconditioners                                        |

| 3.4.1 Polynomial preconditioner                                                      |

| 3.4.2 Incomplete LU Factorization (ILU) preconditioner                               |

| 3.5 Conclusion                                                                       |

| 4 Efficient programming on Many-Core architectures                                   |

| 4.1 Knights Landing architecture Overview                                            |

| 4.1.1 Core design and Cache levels                                                   |

| 4.1.2 High Bandwidth Memory (HBWM)                                                   |

|   |     | 4.1.3 2D Mesh interconnect                                                    | 72  |

|---|-----|-------------------------------------------------------------------------------|-----|

|   | 4.2 | Programming Challenges                                                        | 73  |

|   |     | 4.2.1 Multi-versioning of kernels for vectorization                           | 74  |

|   |     | 4.2.1.1 Implementation                                                        | 74  |

|   |     | 4.2.1.2 Data Structure                                                        | 75  |

|   |     |                                                                               | 75  |

|   | 4.3 | Various vectorized implementation for standard kernels: example with the BLAS |     |

|   |     |                                                                               | 76  |

|   |     | 4.3.2 Various implementations proposal in the API                             |     |

|   |     | 4.3.3 Experiment on <i>Axpy</i> kernel                                        |     |

|   | 4.4 |                                                                               | 80  |

|   |     |                                                                               | 80  |

|   |     |                                                                               | 82  |

|   |     | 0 1                                                                           | 82  |

|   |     | 1                                                                             | 84  |

|   |     | 1                                                                             | 85  |

|   | 4.5 |                                                                               | 86  |

|   | 2.0 |                                                                               | 86  |

|   |     |                                                                               | 87  |

|   |     |                                                                               | 88  |

|   | 4.6 | -                                                                             | 89  |

|   |     | 1                                                                             | 90  |

|   |     |                                                                               | 90  |

|   |     | 4.6.1.2 Cluster mode impact                                                   | 91  |

|   |     | *                                                                             | 92  |

|   |     |                                                                               | 92  |

|   |     | J I                                                                           | 93  |

|   | 4.7 |                                                                               | 94  |

|   |     |                                                                               | 95  |

|   |     | J                                                                             | 96  |

|   |     | 4.7.3 Preconditioners                                                         |     |

|   |     |                                                                               |     |

| 5 | Do  | main Decomposition Methods                                                    | 97  |

|   | 5.1 | Overview and motivations                                                      | 98  |

|   |     | 5.1.1 Multi-Level Domain Decompositon method                                  | 98  |

|   |     | 5.1.1.1 1-level method Additive Schwarz Method                                | 98  |

|   |     | 5.1.1.2 2-level Additive Schwarz Method                                       | 99  |

|   |     | 5.1.2 Numerical performances                                                  | .00 |

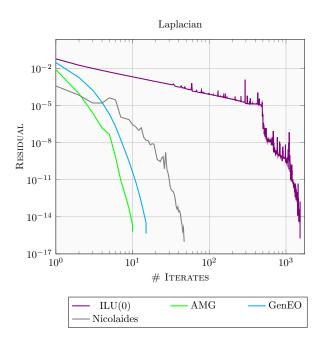

|   |     | 5.1.2.1 Laplacian systems                                                     | 01  |

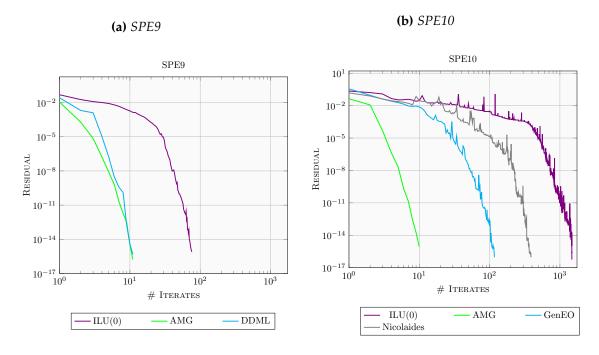

|   |     | 5.1.2.2 Oil reservoir simulations                                             | 01  |

|   | 5.2 | Parallel task-based implementation of DD methods                              |     |

|   |     | 5.2.1 Task Decomposition                                                      |     |

|   |     | 5.2.2 Bottleneck identification                                               | 03  |

|   |     | 5.2.3 Experiments                                                             | .04 |

| 6 | Conclusion                                     | 113 |

|---|------------------------------------------------|-----|

|   | 5.5 Discussion                                 | 112 |

|   | 5.4 Experiments on the KNL many-core processor | 109 |

|   | 5.3.2 Oil reservoir simulation's case          | 109 |

|   | 5.3.1 2-level ASM method performances          | 107 |

|   | 5.3 Experiments on multi-core based systems    | 107 |

# **List of Figures**

| 2.1  | Intel®Xeon Phi architecture                                   | 21 |

|------|---------------------------------------------------------------|----|

| 2.2  | UMA system with bus interconnection                           | 22 |

| 2.3  | System with 2 NUMA nodes with 8 processors                    | 22 |

| 2.4  | Hwloc illustration on a dual-socket machine                   | 24 |

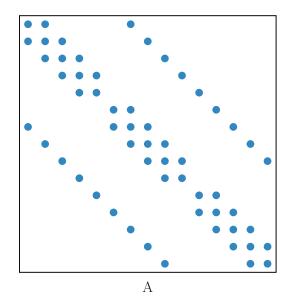

| 3.1  | Sparsity pattern                                              | 40 |

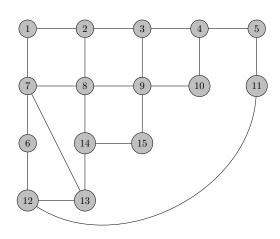

| 3.2  | Graph representation                                          | 40 |

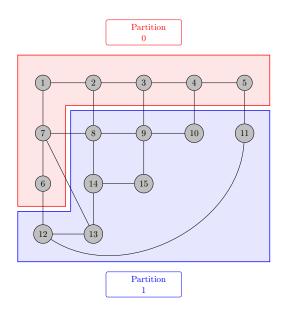

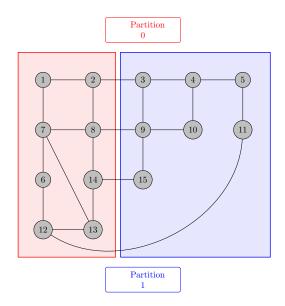

| 3.3  | Row partitioning                                              | 41 |

| 3.4  | Custom partitioning                                           | 41 |

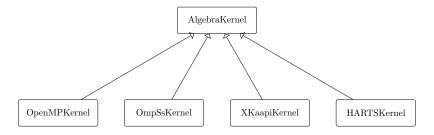

| 3.5  | AlgebraKernel diagram class                                   | 44 |

| 3.6  | Direct Acyclic Graph of BiCGStab sequence (see Listing 3.2)   | 48 |

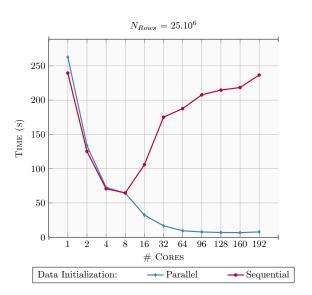

| 3.7  | Cost Evaluation of tasking model                              | 50 |

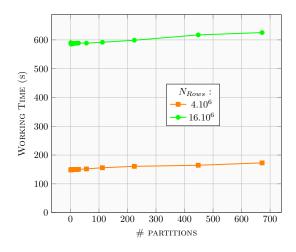

| 3.8  | Work inflation over partitioning                              | 51 |

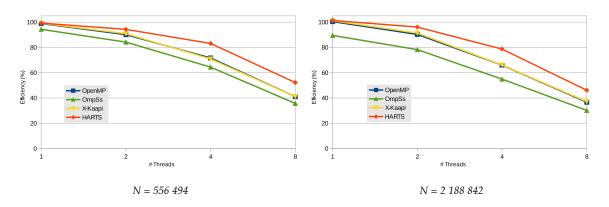

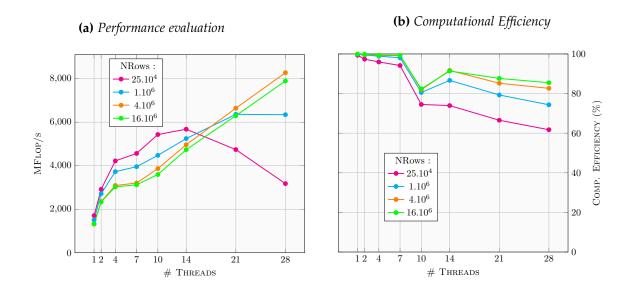

| 3.9  | SpMV on 24 NUMA nodes                                         | 54 |

| 3.10 | BiCGStab on 24 NUMA nodes                                     | 55 |

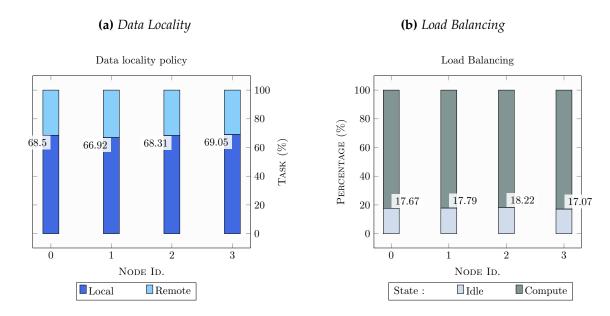

|      | SPE10 – BiCGStab with Diagonal preconditioner                 | 56 |

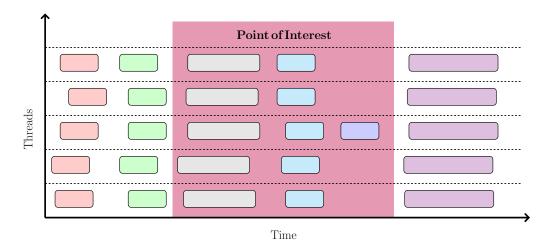

|      | Gantt chart example                                           | 58 |

| 3.13 | Counters' overhead evaluation                                 | 60 |

|      | BiCGStab with Diagonal preconditioner                         | 61 |

| 3.15 | 2000 x 2000 mesh – BiCGStab with Diagonal preconditioner      | 62 |

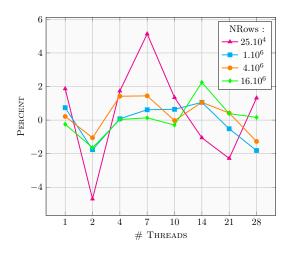

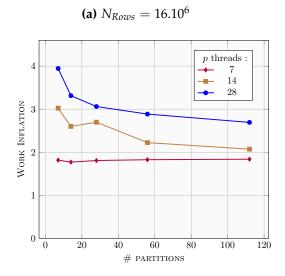

| 3.16 | Work inflation of BiCGStab with Diagonal preconditioner       | 63 |

| 3.17 | BiCGStab with Polynomial preconditioner parallel performances | 64 |

| 3.18 | BiCGStab with Polynomial preconditioner parallel performances | 65 |

| 3.19 | Incomplete LU Facto. DAG                                      | 66 |

| 3.20 | BiCGStab with ILU preconditioner parallel performances        | 66 |

| 3.21 | BiCGStab with ILU preconditioner parallel performances        | 67 |

| 3.22 | Thread activity per NUMA node ( $p = 28$ ) for ILU precond    | 68 |

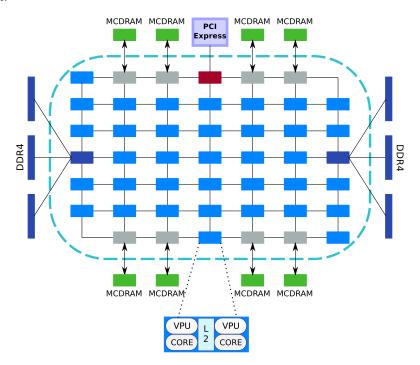

| 4.1  | Intel <sup>®</sup> Knights Landing processor architecture     | 73 |

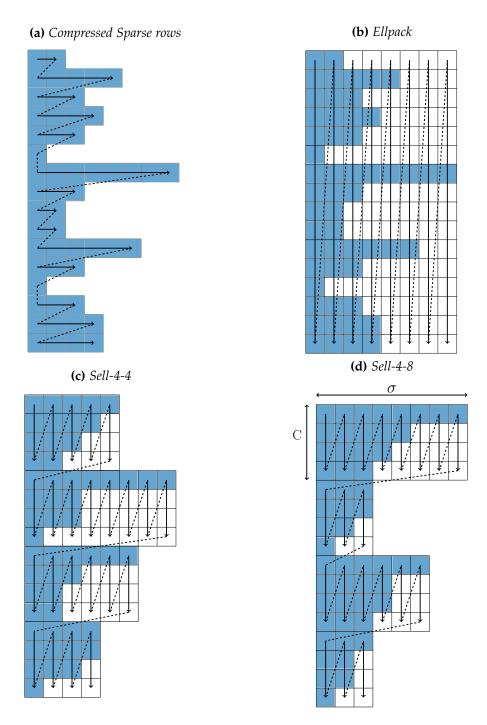

| 4.2  |                                                               | 82 |

| 4.3  | Various sparse matrix format for vector processors            | 83 |

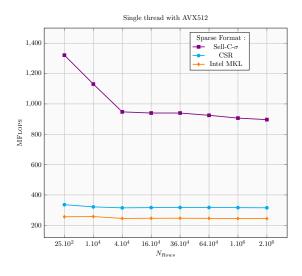

| 4.4  | Performances on SpMV implementations on 1 thread              | 84 |

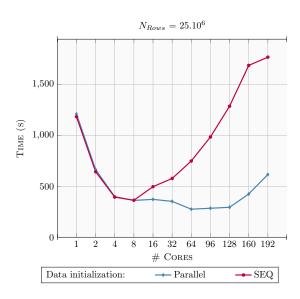

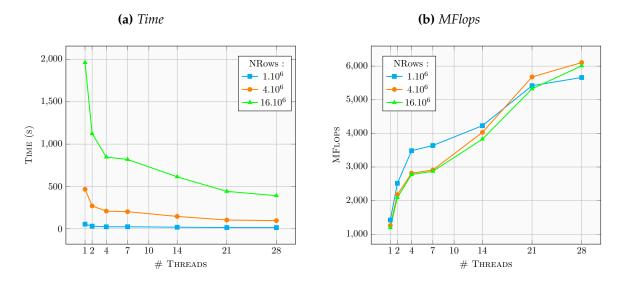

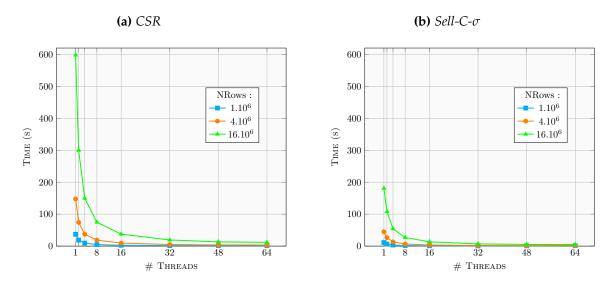

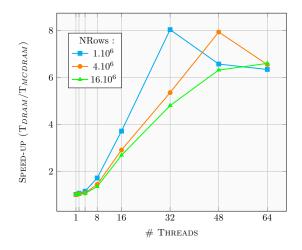

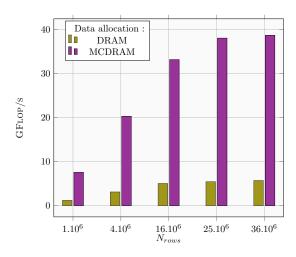

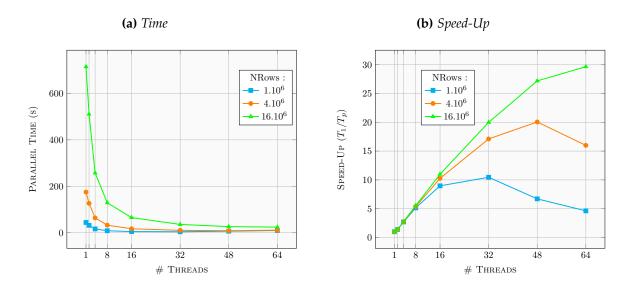

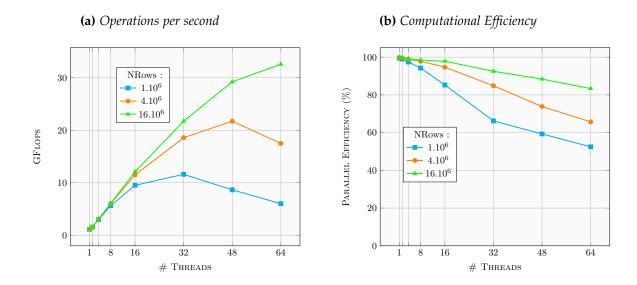

| 4.5  | SpMV's time results                                                       |

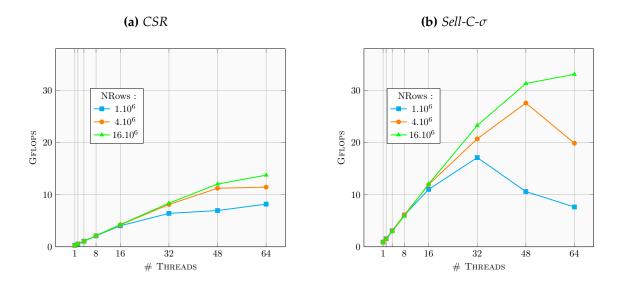

|------|---------------------------------------------------------------------------|

| 4.6  | SpMV's Flops                                                              |

| 4.7  | SpMV performances using the two memory banks of the KNL processor         |

| 4.8  | Performances on SpMV benchmarks using KNL memory banks                    |

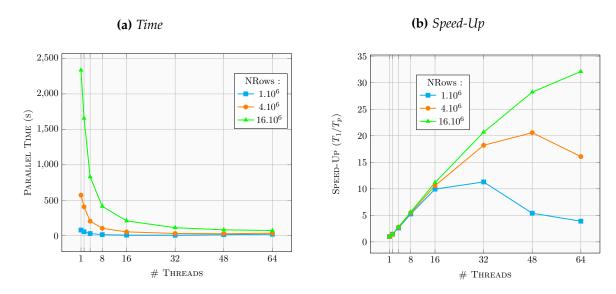

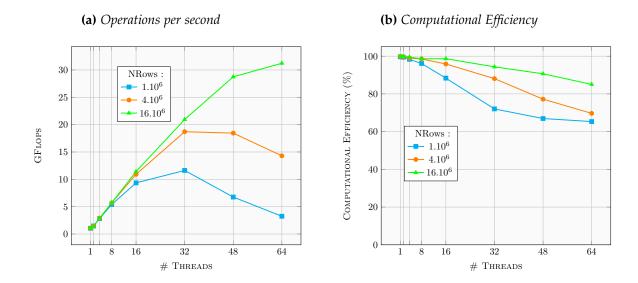

| 4.9  | BiCGStab parallel performances                                            |

| 4.10 | BiCGStab parallel performances                                            |

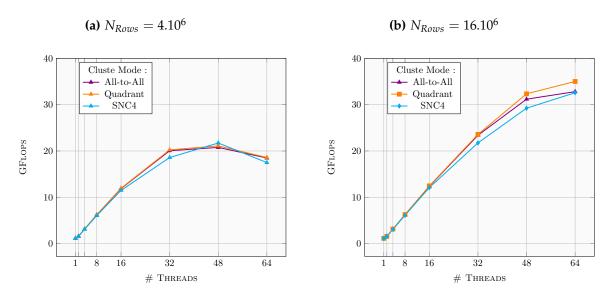

|      | Comparison between cluster modes of the KNL on a BiCGStab algorithm       |

| 4.12 | BiCGStab w. polynomial precon. parallel performances on a KNL processor   |

| 4.13 | BiCGStab w. polynomial precon. performance counters on a KNL processor    |

| 4.14 | BiCGStab w. ILU precon. parallel performances                             |

| 4.15 | BiCGStab w. ILU precon. parallel performances                             |

| 5.1  | LP Homogeneous                                                            |

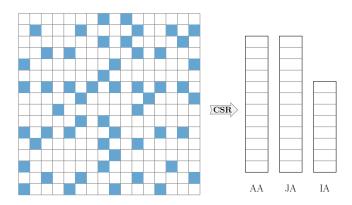

| 5.2  | SpMV with CSR format                                                      |

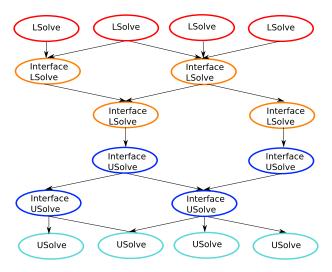

| 5.3  | 2-level ASM DAG                                                           |

| 5.4  | Partitioning information                                                  |

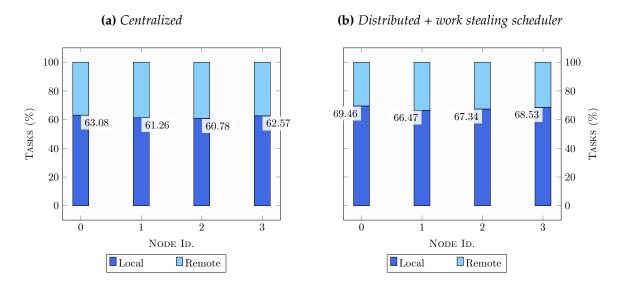

| 5.5  | DDML's tasks percentage                                                   |

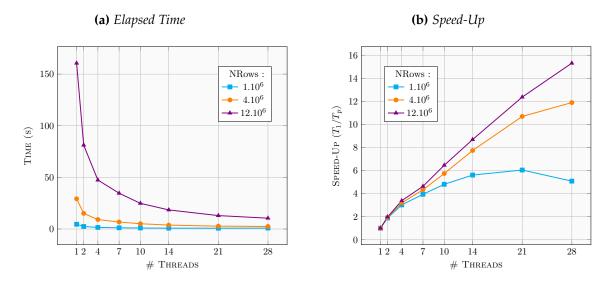

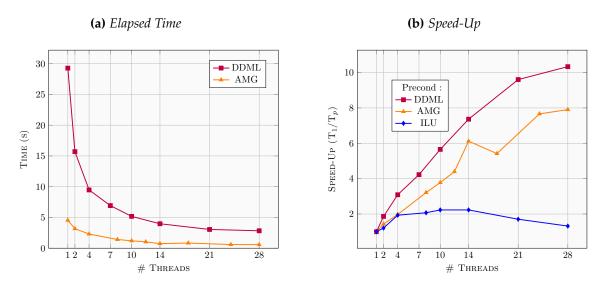

| 5.6  | 2-level AS preconditioner on Laplacian matrices                           |

| 5.7  | 2-level AS preconditioner on the SPE10 system                             |

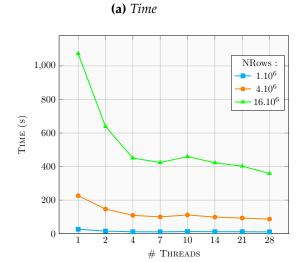

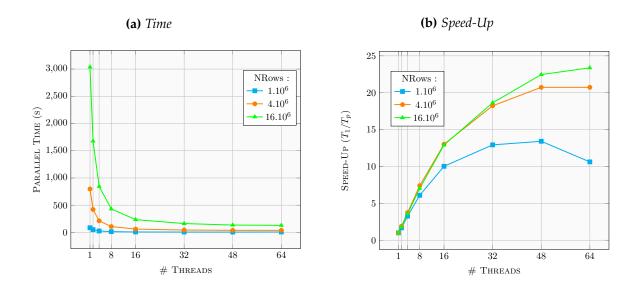

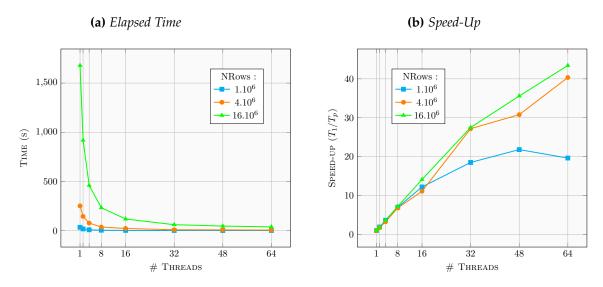

| 5.8  | 2-level AS preconditioner with various Laplacian systems on KNL processor |

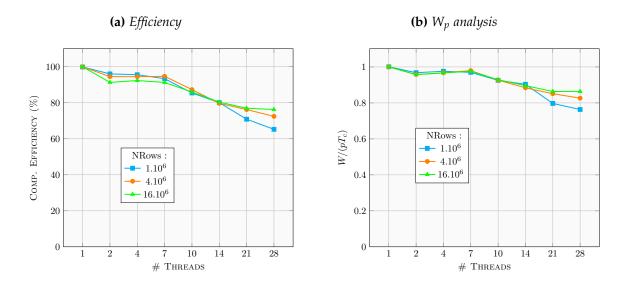

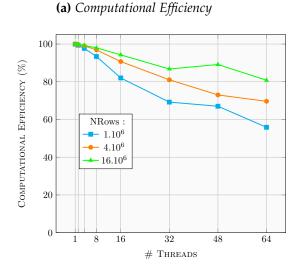

| 5.9  | Computational Efficiency of the DDML method on a KNL processor            |

| 5.10 | DDML's tasks percentage on KNL processor                                  |

# **List of Tables**

| 3.1 | Cost Evaluation of tasking model (%) – N = 2 188 842 | 50 |

|-----|------------------------------------------------------|----|

| 3.2 | Input matrices overview                              | 63 |

| 4.1 | Various vectorized ways for Axpy kernel (GFlops)     | 80 |

| 4.2 | Sparse Format summary                                | 81 |

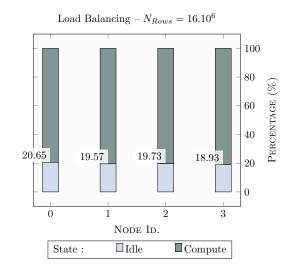

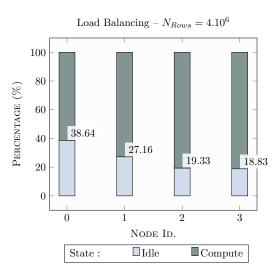

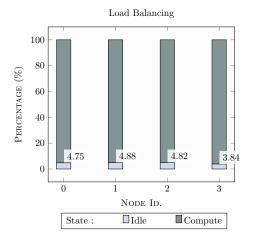

| 5.1 | Load Balancing analysis                              | 07 |

# **List of Algorithms**

| 2.1 | BiCGStab Algorithm                    | 14         |

|-----|---------------------------------------|------------|

| 2.2 | Incomplete LU Factorization Algorithm | 16         |

| 3.1 | BiCGStab Algorithm                    | 37         |

| 5.1 | ASM Algorithm                         | <b>9</b> 9 |

| 5.2 | 2-level ASM Algorithm                 | 00         |

# Résumé

### **Contexte et Motivation**

La simulation numérique de réservoirs de pétrole conduit à la résolution d'équations aux dérivées partielles (EDP). Les schémas numériques aux Volumes Finis amènent à résoudre ces EDP via la résolution d'un système non-linéaire. La solution de ce système est approchée par une méthode de Newton, où à chaque itération ce dernier est linéarisé. Ce système linéaire, creux et de grande taille, doit être ensuite résolu grâce à un solveur linéaire. Cumulées, les phases de résolution de systèmes linéaires représentent jusqu'à 80% du temps total d'exécution des simulateurs de réservoirs à IFPEN.

Bien que robustes et précises, les méthodes de résolution directes ne conviennent pas aux systèmes de grandes tailles car elles nécessitent trop de mémoire. De plus, elles sont difficiles à paralléliser à cause de leur structure algorithmique. Dans ces conditions, les méthodes dites itératives sont donc privilégiées, bien que donnant une solution approchée et dépendent de la structure du système. Pour accélérer la vitesse de convergence de ces méthodes, on applique un préconditionneur sur le système. Un préconditionneur comme *Algebraic Multi-Grid* (AMG), bien que adapté numériquement à nos problèmes, se révèle cependant difficile à paralléliser à un niveau suffisamment fin pour les architectures parallèles possédant un grand nombre d'unités de calcul.

En revanche, les préconditionneurs de type Décomposition de Domaine sont eux adaptés aux architectures parallèles modernes. Se basant sur une stratégie « diviser pour mieux régner », la structure algébrique de ces méthodes est naturellement parallèle. En revanche, ces méthodes ne sont pas assez robustes numériquement pour des problèmes mal conditionnés comme ceux rencontrés en simulation réservoir. Néanmoins, avec l'ajout d'un second niveau, et notamment l'opérateur grossier GenEO introduit par les travaux de N. Spillane [Spillane et al., 2014] puis parallélisé par P. Jolivet [Jolivet et al., 2013] sur une machine à mémoire distribuée, ces méthodes regagnent d'intérêt dans notre domaine d'application. Pour autant, la construction de cet opérateur repose sur une discrétisation selon un schéma aux éléments finis, ce qui diffère d'un schéma aux volumes finis utilisés dans nos applications.

Actuellement, les architectures informatiques parallèles à mémoire partagée se basent sur le modèle « Non Uniform Memory Access » (NUMA). En plus d'une mémoire qui est segmentée, ces systèmes ont tendance à accroître leur nombre de cœurs de calculs. De plus, la hiérarchie mémoire qui règne dans ces machines est également importante. Ces caractéristiques font émerger des problèmes de latence d'accès à la mémoire et de la contention des bus mémoire. Le nombre d'unités de calculs par socket explose en passant par une simplification des cœurs. Ces processeurs many-cœurs apportent une complexité de programmation supplémentaire, comme la nécessité de vectorisation.

Une partie de la complexité de programmation engendrée par ces architectures migre de plus en plus d'une programmation bas niveau à un niveau supérieur. Des problématiques telles que la gestion des données ou l'ordonnancement des tâches parallèles sur les différentes ressources de calculs se retrouvent dorénavant gérées au travers d'un support exécutif. L'utilisation de nouveaux modèles de programmation parallèle a déjà été adopté en algèbre linéaire dense. En revanche, des problèmes épineux restent à surmonter lors de la parallélisation de méthodes algébriques telles que celles employées dans les simulateurs numériques.

### Objectifs et contributions

L'objectif global de ces travaux est de fournir un préconditionneur de type Décomposition de Domaines qui exploite au mieux les capacités des architectures multi-cœurs. Cet objectif est en réalité double, il devra à la fois être robuste numériquement sur les cas de simulation réservoir et devra bénéficier également d'une implémentation parallèle efficace sur les architectures émergentes. Il est donc nécessaire de mettre en place les briques numériques et logicielles pour atteindre un tel niveau d'efficacité.

La première contribution de ce travail est d'évaluer une parallélisation de méthodes itératives via un modèle de programmation de type data-flow avec tâches. La parallélisation a été réalisée à travers une interface de programmation (i.e. API) qui permet à l'utilisateur de s'abstraire de l'implémentation sous-jacente et de se focaliser uniquement sur les aspects algorithmiques de la méthode. Cette API a été développée au-dessus de plusieurs supports d'exécution, tels que OpenMP 4.0, OmpSs, X-Kaapi et HARTS. L'interface de programmation s'articule autour de plusieurs principes, tels que la notion d'itération ou le découpage en tâches selon le graphe d'adjacence de la matrice des coefficients. Ces travaux ont fait l'objet d'une communication lors de la conférence nationale Compas [Roussel, 2016].

Après une première étude publiée dans [Virouleau et al., 2016b] sur la parallélisation de la multiplication d'une matrice creuse par un vecteur grâce au moteur exécutif XKaapi, nous avons intégré dans HARTS une manière de gérer l'exécution des tâches sur architectures NUMA en gérant de bout en bout la distribution des données jusqu'à l'exécution. Cette fonctionnalité est initialisée avant le début des sections parallèles car elle prend uniquement en compte le partitionnement des données, qui est connu qu début de l'exécution. A l'exécution, c'est l'ordonnanceur, basé sur un algorithme de type vol de tâche,

qui chargera alors le thread voleur de dérober une tâche opérant sur des données les plus proches possible.

Nous avons mis en place un système d'évaluation de performances à l'intérieur du support d'exécution HARTS. A l'aide de ces outils, nous avons la possibilité d'observer avec minutie le comportement de nos applications. Nous pouvons par exemple retracer le cours des évènements à travers la génération de diagramme de Gantt. A une échelle plus fine, nous pouvons faire des mesures au niveau d'une tâche, pour connaître aussi bien son temps d'exécution, sa granularité et même sur quelle unité de calculs elle s'est exécutée. Post-mortem, ces évènements sont utilisés pour aider à l'analyse des performances des exécutions. Par exemple par le calcul du chemin critique, du temps de travail, des temps d'inactivité par thread, etc.

Nous avons adapté nos méthodes pour les architectures de processeurs many-cœurs. Nous avons mis en évidence l'importance de la vectorisation des codes existants et l'utilisation de la mémoire à haute vitesse que nous propose le processeur Intel Xeon Phi Knights Landing. Bénéficiant du fait que nos données tiennent intégralement dans la mémoire à bande passante élevée, nous montrons la performance de nos applications sur ce type d'architecture.

Enfin, nous avons développé au dessus de l'API précédemment évoquée le préconditionneur de type Décomposition de Domaine 2-niveaux, basé sur l'opérateur grossier GenEO. Ainsi, nous avons pu attester de la performance numérique de ce préconditionneur sur des cas réservoirs qui, à ce niveau, permet d'être concurrent face à d'autres méthodes plus connues comme AMG. Nous avons aussi pu, à travers les travaux cités précédemment, mettre en place des implémentations multi-cœurs et many-cœurs efficaces du préconditionneur. Une étude préliminaire des performances du préconditionneur sur architecture multi-cœurs a été publiée dans la revue OGST [Roussel et al., 2016].

# Résumé des chapitres

Dans le **premier chapitre**, nous introduisons le contexte de nos travaux et les objectifs attendus. Nous présentons également les contributions que nous avons apportées tout au long de cette thèse, avant d'introduire le plan du mémoire.

Dans le **second chapitre**, nous replaçons le contexte du problème qui nous a été posé ainsi que les difficultés rencontrées. Dans ce cadre, nous rappelons aussi bien les enjeux dans les domaines du numérique et de l'informatique dont découlent les problématiques alors posées tout au long de ces travaux.

Dans le **troisième chapitre**, nous introduisons une API d'algèbre linéaire creuse qui permet à ses utilisateurs de pouvoir écrire des algorithmes itératifs de haut niveau avec une sémantique séquentielle. La parallélisation est implicite, et repose sur le paradigme de programmation par tâches. L'API est construite autour du concept de *Sequence* qui représente une suite d'opérations. Une *Sequence* est une structure persistante, encapsulant les différentes opérations à effectuer sous forme de tâches. A l'exécution, les *Sequence*

peuvent être rejouées plusieurs fois, ce qui permet de les encapsuler à l'intérieur de boucles itératives. Les tâches sont construites à partir du partitionnement du graphe d'adjacence représentant la matrice donnée en entrée du solveur, *i.e.* le système linéaire à résoudre. Lors du déclenchement de l'exécution de la *Sequence*, les tâches ainsi que leurs dépendances sont alors traduites puis envoyées à un support executif. Jusqu'à présent, notre API supporte les supports d'exécution suivants : OpenMP 4.0, OmpSs, X-Kaapi et HARTS. Lors d'une étude préliminaire, nous avons fait un comparatif d'exécutions en utilisant différents supports exécutifs.

Constatant que la plupart des machines multi-cœurs repose sur une architecture mémoire de type NUMA, nous avons cherché un moyen de prendre en compte la localité des données lors de l'exécution de nos méthodes. Nous avons alors mis en place un système de tâches d'initialisation dans HARTS pour pouvoir bénéficier d'une politique de type First-touch et ainsi distribuer nos données sur l'ensemble des bancs NUMA disponibles. En contrôlant l'ordonnancement des tâches et grâce à l'utilisation d'une queue distribuée sur chaque thread, nous garantissons que les tâches d'initialisation possédant un même numéro de partition sont exécutées par la même unité de calcul. Par conséquent, des données différentes seront distribuées de la même manière selon le partitionnement du graphe de la matrice d'entrée. Nous remplissons la queue appropriée lors de l'instanciation des tâches. Lors de l'équilibrage de charge, garanti par un algorithme de type vol de travail et grâce à la connaissance de la distribution des données, un thread inactif va pouvoir voler une tâche à un autre thread, tout en essayant de minimiser la distance NUMA qui le sépare de sa victime. Grâce à cette stratégie, nous arrivons à diminuer les accès sur des données distantes. Afin d'avoir une meilleure analyse de nos performances, nous avons mis en place un système de monitoring à l'intérieur du support exécutif HARTS. Grâce à des métriques collectées tout au long de l'exécution, nous pouvons alors analyser les données une fois l'exécution parallèle terminée. Par ce biais, nous pouvons tracer aussi bien des courbes d'activités de threads, diagrammes de Gantt, ou des analyses sur le chemin critique. Pour finir, nous analysons les performances que nous obtenons sur des méthodes itératives implémentées au dessus de notre API sur les machines multi-cœurs.

En l'état, notre API ne nous permet pas de pouvoir tirer parti efficacement des processeurs many-cœurs car elle ne tient pas en compte d'optimisations spécifiques qui sont requises pour ce type d'architecture. Le propos du **quatrième chapitre** est donc de proposer des extensions à l'API afin de pouvoir gérer un autre type d'architecture que celle que nous avons étudié par avant, tout en gardant la portabilité des performances à notre approche. Pour ce faire, nous concentrons nos travaux sur les processeurs many-cœurs Knights Landing d'Intel. Ceux-ci proposent une architecture particulière, basée notamment sur un réseau d'interconnexion des cœurs sous forme de maillage 2D. Grâce à une simplification des cœurs de calcul, le processeur peut alors posséder jusqu'à 64 unités de calculs. De plus, il embarque une mémoire à bande passante élevée appelée *MCDRAM* qui a pour but de réduire le coût des communications mémoire. De là, il en découle deux challenges de programmation que sont la gestion de la vectorisation des codes de calculs et une gestion efficace de la MCDRAM. Par le biais de notre API et les solveurs précédemments développés au-dessus de celle-ci, nous avons pu montrer que les

performances de nos méthodes continuent d'augmenter malgré l'augmentation du nombre de coeurs de calculs. A travers différents préconditionneurs, nous avons pu établir une évaluation de performances montrant que nous arrivons à obtenir de bonnes performances parallèles pour nos méthodes itératives, sur une architecture basée sur le processeur many-cœurs Knights Landing. Pour arriver à ce niveau de performances, nous avons dû étendre notre API pour permettre de prendre en considération la vectorisation des méthodes, mais également de pouvoir tirer avantage de la mémoire MCDRAM embarquée sur le processeur KNL. Ces extensions ont été faites dans le respect de la portabilité des performances de l'API sur différentes architectures. Ces choix d'optimisations pour une architecture spécifique se font à la compilation, sans altérer la manière dont on écrit nos méthodes itératives. Par exemple, nous montrons dans ces travaux comment nous permettons la vectorisation d'une opération de type produit matrice creuse par un vecteur (SpMV) grâce au changement de structure de la matrice en entrée. A l'arrivée, cette opération nous permet alors d'accroître les performances de nos solveurs écrits au-dessus de notre API.

Bien que nous pouvons proposer dorénavant une parallélisation des méthodes numériques employées en simulation réservoir, aussi bien sur architectures multi-cœurs que many-cœurs, les méthodes développées jusqu'ici s'avèrent inefficaces sur le plan numérique face à des système mal conditionnés. Pour palier à ce problème, dans le cinquième chapitre nous proposons alors l'implémentation d'un préconditionneur de type décomposition de domaine multi-niveaux. Après une rapide présentation des méthodes de type Additive Schwarz, nous rappelons que l'ajout d'un opérateur grossier tel que GenEO permet de palier à la robustesse et l'extensibilité des préconditionneurs de type décomposition de domaine sur des cas provenant de simulations numériques réelles. Nous retrouvons ces résultats à travers les mesures expérimentales que nous avons effectuées sur notre implémentation. L'ajout d'un second niveau nous amène alors à la résolution d'un système linéaire de petite taille. Cette résolution, dite grossière, nous permet alors de synchroniser l'ensemble des sous-domaines pour favoriser la communication entre eux et accélérer la convergence de la méthode. Nous proposons dans un second temps une parallélisation par tâches de cette méthode à l'aide de notre API. Expérimentalement, nous montrons qu'il existe un compromis à faire entre deux tailles de systèmes à résoudre à chaque itération. En effet, en fonction du nombre de sous-domaines la taille des systèmes locaux tend à diminuer, alors qu'à l'inverse la taille du système grossier augmente. Un compromis est alors de mise pour trouver le meilleur équilibre en termes de performances, pour ne pas que chacune des opérations ne freine les performances globales. Nous évaluons par la suite notre implémentation sur des systèmes de diverses tailles sur une machine de type multi-cœurs. Notre implémentation présente de bonnes performances, indépendamment de la taille du système. Comparée à la référence AMG, notre application se montre un peu moins efficace, mais bien plus que le préconditonneur ILU(0). Sur architecture many-cœurs, les performances ne sont pas en reste et présente une bonne efficacité de calculs. De même que sur la précédente machine, notre implémentation présente un niveau de performance un peu en retrait par rapport au code de référence AMG. Nous expliquons cette différence par une analyse de la répartition des temps de calculs à l'exécution qui montre que des tâches restent très consommatrices en temps de calculs et nécessitent encore d'être vectorisées à court terme. En définitif, les

performances actuelles du préconditionneur DDML sont en deçà de ce qui pourrait être obtenu. Une fois ce problème d'optimisation résolu nous pouvons espérer de meilleures performances sur ces machines car nous avons mesuré que le facteur d'accélération de notre code est plus important par rapport à la version séquentielle du même code. Toute amélioration séquentielle sera bénéfique.

Enfin, le **sixième et dernier chapitre** permet de conclure ce mémoire de thèse. Nous rappelons alors l'ensemble des travaux effectués ainsi que les différents résultats obtenus. Nous profitons également de ce chapitre pour donner des perspectives pour la suite de ces travaux.

# Introduction

| Contents | Contents                     |   |  |

|----------|------------------------------|---|--|

| 1.1      | Context and motivation       | 7 |  |

| 1.2      | Objectives and contributions | 8 |  |

| 1.3      | Outline                      | 9 |  |

### 1.1 Context and motivation

Numerical simulations in reservoir engineering lead up to the resolution of Partial Differential Equations (PDE), which are then discretized with a finite volume scheme. We solve it thanks to a Newton solver, in which the system is linearized at each step. The given linear system is generally large and sparse, and has to be solved via a linear solver method. This part is time consuming because of the large amount of computations, and it represents up to 80% of the total simulation time.

Direct resolution methods are accurate and robust algorithms to solve linear systems. However, it is unsuitable for large system because of the memory requirements and the lack of parallelism. Iterative methods are thus favored, despite the fact that they give approximate solutions and depend on the matrix structure. Preconditioners are applied on the system in order to increase their convergence rates. The *Algebraic Multi-Grid* (AMG) preconditioner presents good numerical qualities for the problems encountered in reservoir simulations. However, an efficient parallel implementation of a such method requires a significant programming effort.

On the other hand, *Domain Decomposition methods* are well-suited for modern parallel architectures. Its design relies on the "divide and conquer" strategy. Hence, its algorithmic structure naturally fits on parallel computers and enables a parallelization at a fine granularity. This later advantage is particularly interesting with the increase in number of computational units per socket. However, these methods are not robust enough for our case study. Recently, the problem was fixed with the advent of 2-level decomposition domain methods and the GenEO coarse operator [Spillane et al., 2014]. This

method already benefits from an efficient parallel implementation on a distributed memory computer [Jolivet et al., 2013].

Parallel computer architectures based on a shared memory model actually rely on the Non Uniform Memory Access (NUMA) design. Such systems are characterized by a segmented physical memory and an increase in the number of cores per chip. In addition of that, memory hierarchy that rules memory transfers impacts the application performances. In such designs, data latency problems arises from memory bus contention. Nowadays, the number of cores per socket massively increases because of the simplification of the core design. Programming efficiently these many-core processors is an additional challenges. Performances enhancement often involves vector processing and a good memory management.

A part of programming complexity moves from a low-level programming to a higher layer. Runtime systems are tools that helps data management and work scheduling among computational resources. The use of emergent parallel programming models is already adopted in dense linear algebra. However, complex challenges still require much more investment in the parallel design of the methods used in the reservoir simulation field.

### 1.2 Objectives and contributions

The main objective of this work is to develop a Domain Decomposition preconditioner which efficiently exploits the capacities of multi-core and many-core systems. It can be viewed as the combination of two derived objectives. The first one is to design a robust preconditioner that can be used in oil reservoir simulation. The second is to provide a parallel implementation of numerical methods on emerging architectures. We thus need to prepare beforehand main concepts, both numerical and software, on which our work will rely on. This preconditioner has to be integrated in the MCGSolver library [Anciaux-Sedrakian et al., 2014], developed at IFPEN, which aims to provide efficient parallel linear solvers for numerical methods' developers.

The first contribution of this work is to propose an efficient parallel implementation of iterative methods. It relies on a data-flow programming model, and is packed within an abstract linear algebra programming interface (i.e. API). By this way, users do not see parallel implementation and can focus on the algorithm. This API has been developed over several runtime systems among OpenMP, OmpSs, X-Kaapi and HARTS. The interface was build around the iterative pattern of the methods while the tasks were created according to the adjacency graph of the matrix. This work has been presented in [Roussel, 2016].

Within the X-Kaapi's OpenMP interface, we also highlight the importance of data locality scheduling policy on NUMA architecture. It enables to collect information on data at run time to place tasks among computational units. We expose the case of a sparse matrix vector product on a large scale NUMA machine in [Virouleau et al., 2016b]. Thanks to HARTS, we implement a data locality aware scheduling policy based on graph partitioning information provided by the API. By this way, tasks are pushed in a distributed

1.3. Outline

queue according to partition information. It enables to distribute data among memory nodes thanks to *first-touch* NUMA policy and allocating tasks of the API. At run time, when a thread is idle, a work stealing scheduler selects a victim according to the initial data distribution.

Moreover, we enhance our understanding of application behavior with the implementation of performances analysis tools inside HARTS. This model allows users to collect information at run time time, which enable to build application analysis after the execution. For example, it enables to build a time line from events records (e.g. beginning and end of tasks) gathered in a Gantt chart. At a lower scale, measurements can be collected at a task level to know its granularity or which resource performs it. After an execution, we also can analyze critical path which can give us an hint to a parallelism default.

Afterward, we adapt our numerical methods on many-core processors. On Intel Knights Landing processor, we highlight the importance of code vectorization and effective usage of high bandwidth memory. However, the performances of the API have to be portable whatever the architecture in use. We thus need to extend the API while keeping the same semantic. In order to enhance performances by code vectorization we enable the developers to write kernels with multiple implementations and a multiple structures management. Moreover, we extend the API with memory management unit to enhance applications with high bandwidth memory when it is available (depending on the architecture). We illustrate the performances we obtained with this architecture with various numerical methods we implemented.

Eventually, we develop a 2-level Domain Decomposition preconditioner with the GenEO coarse operator. This work was achieved within the abstract linear algebra API. We validate the robustness of such a preconditioner on benchmarks coming from oil reservoir simulations. By this way, we evaluate its numerical performance that is close to other widespread methods as AMG. Thanks to the work previously described, we develop both multi-core and many-core efficient parallel implementations. A preliminary study of this preconditioner on multi-core architecture was published in [Roussel et al., 2016].

### 1.3 Outline

In the second chapter, we introduce the challenges that leads to high performance computing in the sparse linear solver context. From algorithmic to the parallel implementation, there are many issues to overcome. This chapter aims to review them from algorithmic to computer architectures, while discussing on the implementation between them.

In the third chapter, we describe a way to write efficient parallel numerical methods on multi-core architectures. We present the framework we set up, and the required optimization to maximize performances. This chapter is devoted to the evaluation of parallel performances of iterative methods.

Many-core architecture is one alternative to multi-core processors in order to increase computing performances. However, these architectures introduce new programming

challenges. We review these challenges in the fourth chapter, and propose solutions for sparse linear algebra methods.

We propose an efficient parallelization of a 2-level domain decomposition preconditioner in the fifth chapter. We gather the various points we raised up in the previous chapters. By this way, we develop a preconditioner which is robust and efficient on both multi-core and many-core systems.

We conclude this thesis with the last chapter, on which we review our contribution and the results we obtained all along this work.

# **Background**

| Contents |                                                 |

|----------|-------------------------------------------------|

| 2.1      | Sparse linear algebra                           |

|          | 2.1.1 Linear Solvers                            |

|          | 2.1.2 Preconditioners                           |

| 2.2      | Parallel Computers                              |

|          | 2.2.1 Generalities                              |

|          | 2.2.2 Processors Architecture                   |

|          | 2.2.3 Memory Systems                            |

|          | 2.2.4 Topology discovery                        |

| 2.3      | Parallel Programming Models and Runtime Systems |

|          | 2.3.1 Parallel Programming Models               |

|          | 2.3.2 Runtime Systems                           |

| 2.4      | Discussion on HPC Trend                         |

|          | 2.4.1 Hardware                                  |

|          | 2.4.2 Runtime Systems                           |

|          | 2.4.3 Parallel Linear algebra                   |

| 2.5      | Conclusion                                      |

In basin modelization or oil reservoir simulation, multi-phase flow in porous media models lead to solve complex *Partial Differential Equations* (PDEs) systems. These PDEs are discretized with a cell-centered Finite Volume scheme in space and an Euler implicit method in time, leading to a nonlinear system which is solved with an iterative Newton's method [Kelley, 2003]. At each Newton step, the system is linearized then solved using a linear solver.

The equation reads Ax = b, where x is the vector of unknowns, A the input matrix and b the right-hand side vector. The resolution of such systems is the most expensive part among the simulator's workflow. It may represent up to 80% of the simulation time. Moreover, the generated linear system is ill-conditioned, large and sparse. As it is a bottleneck for application performance, parallel computing is thus a necessity to enhance

simulator's performances. Hence, methods must be adapted, or sometimes re-designed, for efficient parallel computations. In addition of that, parallel computers become more complex and programming them efficiently is challenging.

This chapter aims to review the challenges that parallel linear algebra algorithms have to overcome at several levels of complexity.

At the top level, we have linear solver algorithmic which aims to find a feasible solution in a reasonable time. Different classes of methods exist, which are designed from various classes of problems. These methods are reviewed in the first section.

At the lowest level, there is the computer hardware on which we eventually address parallel numerical methods. Parallel architectures are complex, and their understanding is a first step to face challenges we encounter. In the second section, we thus review widespread parallel computer designs in the high performance computing field.

Between these two levels, programming sparse linear algebra methods on parallel architectures remains challenging. A way to address the work flow is given by a parallel programming model to abstract the underlying architecture. Then, runtime systems tools implement it to manage the computations between the processing units. We review programming challenges in the third section.

Eventually, we discuss on the HPC trends in parallel sparse linear algebra field.

## 2.1 Sparse linear algebra

### 2.1.1 Linear Solvers

There are two ways to solve linear systems. The most intuitive one is direct method to obtain an exact solution of the system. Another way is to use an iterative method which refines an initial guess within a loop, until it reaches convergence to an approximate solution. We here aim to review both methods.

### 2.1.1.1 Direct solver

A method which allows the computation of the unknowns vector x in a finite number of operations is named a direct method for solving the the linear system Ax = b.

One of the most famous direct method consist to process a Gaussian elimination method. It reduces any linear system to a triangular one. It is then trivial to obtain the exact solution x.

Other methods [Ciarlet, 1998] rely on the factorization of the matrix A as a product of two other matrices such that A = BC. The solution of the system will be replace by the solution of two easily invertible systems as the matrices B and C are triangular or orthogonal. Common factorization methods are LU or QR decomposition.

Direct methods provide a robust and accurate way to solve linear systems. Robustness

property come from the fact that they do not depend on the shape of the linear system. However, such methods are greedy in memory. Moreover, the computation of the exact solution is time consuming and highly depends on the shape of the system to solve. Hence, these methods are not used to solve large linear systems.

#### 2.1.1.2 Iterative Methods

Given an initial guess, an iterative method will refine the approximate solution until convergence is reached. This method modifies one or a few components of the solution at each step, and stops when the convergence criterion is satisfied under a certain desired precision  $\varepsilon$ . It can be theoretically proved that these methods converge to the exact solution.

At the *k*-th iteration, error estimation is given by the formula:

$$e_k = x_k - x \tag{2.1}$$

The iterative method converges if and only if  $e_k$  converges to 0. As x is unknown we cannot compute it. It is pretty much easier to compute the residual vector at the k-th step, which is given by :

$$r_k = b - Ax_k \tag{2.2}$$

and then convergence criterion is evaluated to satisfy  $||b - Ax_k|| \le \varepsilon$ . In practice, we prefer to refer to a relative error to be sure that the criterion is not misleading, and it is given by:

$$\frac{\|b - Ax_k\|}{\|b - Ax_0\|} \le \varepsilon \tag{2.3}$$

Iterative methods are less accurate than direct methods because of the computation of an approximate solution to the problem, but the error is controlled. As a lack of robustness, the distinction between structured and unstructured matrices may affect iterative methods.

Some of them are based of coordinates relaxation. These basic iterative methods are algorithms like *Jacobi*, *Gauss-Seidel* or *Successive Over Relaxation* (SOR) methods. But these techniques are rarely good alternatives for solving large and sparse systems.

Another way is the use of methods based on projection techniques. In this case, the most popular ones are Krylov subspace methods. Common algorithms used for unstructured systems are the *Generalized Minimum Residual Method* (GMRES) [Saad and Schultz, 1986] and the *Biconjugate Gradient Stabilized* (BiCGStab) [van der Vorst, 1992] algorithms (illustrated in Algorithm 3.1). In our work, we mainly focus on the BiCGStab algorithm because

of its efficiency on unstructured linear systems arising in oil reservoir simulations.

### Algorithm 2.1: BiCGStab Algorithm

```

1 Compute r_0 = b - Ax_0;

2 r_0^* arbitrary;

3 p_0 = r_0;

4 j = 0;

5 do

\alpha_i = (r_i, r_0^*)/(Ap_i, r_0^*);

6

s_i = r_i - \alpha_i A p_i;

7

\omega_i = (As_i, s_i)/(As_i, As_i);

x_{i+1} = x_i + \alpha_i p_i + \omega_i s_i;

r_{j+1} = s_j - \omega_j A s_j;

10

\beta_j = \frac{(r_{j+1},r_0^*)}{(r_j,r_0^*)} \times \frac{\alpha_j}{\omega_j};

11

p_{i+1} = r_{i+1} + \beta_i(p_i - \omega_i A p_i);

12

j = j + 1;

13

14 while! convergence;

```

### 2.1.2 Preconditioners

### 2.1.2.1 Generalities

In scientific computing, there is no exact computations. Real numbers are represented in computer under a certain precision degree (representation with 32 bits for a single precision, or with 64 bits for a double precision). A slight modification of matrix entries may have a significant impact on the final computed solution. A numerical method which does not amplify errors is said to be *stable*. Because of their recursive nature, stability property for iterative methods is a way to not propagate and amplify error over iterations. Otherwise, computed solution may be far away from the expected result.

To measure how sensitive is the solution to the problem of rounding error, we now introduce the notion of *matrix conditioning*. It helps to measure the sensitivity of the solution x of the linear system Ax = b to perturbations of the data A and b. The condition number cond(A) quantify the conditioning or the sensitivity of the problem Ax = b to perturbations in the data A or b. Condition number of a singular matrix (i.e invertible) A is given by

$$cond(A) = ||A||.||A^{-1}||. (2.4)$$

Even if the relative error of the data is small, the impact on the solution x can be huge if the condition number of A is large. In other words, the condition number cond(A) measures the amplification of errors in A and b. A matrix A is said to be well conditioned if  $cond(A) \simeq 1$ , and conversely a matrix is said to be ill conditioned if  $cond(A) \gg 1$ .

Due to the complexity to compute the matrix  $A^{-1}$  when A is large, we generally

compute condition number by approximations which is enough to predict the amplification of errors in data.

Highly heterogeneous geological data and complex studied geometry lead to ill-conditioned linear systems solved with iterative methods. To prevent the propagation of errors, preconditioning methods transform a system to another while reducing its condition number. However, it does not change the solution of the problem. A left preconditioned system is given by

$$M^{-1}Ax = M^{-1}b, (2.5)$$

in which *A* is an ill-conditioned matrix, and *M* a non-singular matrix named a *preconditioner*, or a preconditioning matrix. There is also a right preconditioned system, given by

$$AP^{-1}y = b$$

with

$$x = P^{-1}y,$$

(2.6)

such that P is a non singular and easily invertible matrix. An important property of a preconditioned system is that  $cond(M^{-1}A) < cond(A)$ . The problem is now to find a matrix M which is easily invertible so that M-1A is close to the identity matrix (whose conditioning is equal to 1). Computing  $A^{-1}$  is a problem at least as difficult as to solve the linear system. So we have to find a matrix M which is close to A. Another important property of a preconditioner is that is easy to apply. Indeed, we will apply this preconditioner at each iteration of an iterative method, so it has to be not too expensive to apply it on A.

Ill-conditioned system fails to converge in a reasonable time because of the error propagation. Improving conditioning of a matrix with a preconditioner is so important to enhance linear solver's convergence rate. Indeed, it reduces number of iteration required to converge. Linear systems arising from oil reservoir simulation are generally ill-conditioned.

### 2.1.2.2 Polynomial

The idea of such a preconditioner is to define  $M^{-1} = p(A)$ , where p is a polynomial such that  $cond(C^{-1}A) < cond(A)$ . A good choice is to take for p(x), a truncation of the expansion in power series of  $A^{-1}$ , given by  $p(x) = 1 + \sum_{k \ge 1}^d (1-x)^k$ . Although it is easy to built, this preconditioner is most of the time not efficient for complex problems arising from oil reservoir simulations.

### 2.1.2.3 ILU(0)

Given a factorization of a large sparse matrix A such that

$$A = LU, (2.7)$$

where L is a lower triangular matrix, and U an upper triangular matrix. It is well known that usually in the factorization procedure, the matrices L and U have more non zero entries then A. These extra entries are called fill-in entries. The  $Incomplete\ LU\ factorization\ (ILU)\ [Varga, 1960]\ consists in dropping some of these elements. Incomplete factorization preconditioners consist in taking <math>M=\bar{L}\bar{U}\approx A$ , where  $\bar{L}$  and  $\bar{U}$  stand for the incomplete LU factors of A. Let S be a subset of  $n\times n$  positions of the original matrix generally including the main diagonal, and  $\forall (i,j)$  such as  $a_{i,j}\neq 0$ . An incomplete LU factorization of A only allows fill-in positions which are in S, which is designated by the elements to drop at each step. S has to be specified in advance in a static way by defining a zero pattern which must exclude the main diagonal. Therefore, for any zero pattern P, such that

$$P \subset \{(i,j)|i \neq j; 1 \leq i, j \leq n\}$$

$$(2.8)$$

an Incomplete LU Factorization, ILU, can be computed as in Algorithm 2.

Algorithm 2.2: Incomplete LU Factorization Algorithm

```

1 for i = 2, ..., n do

2 | for k = 1, ..., i - 1 and (i, k) \notin P do

3 | a_{ik} = a_{ik}/a_{kk} for j = k + 1, ..., n and (i, j) \notin P do

4 | a_{ij} = a_{ij} - a_{ik}a_{kj}

5 | end

6 | end

7 end

```

For an incomplete factorization with no-fill, named ILU(0), we define the pattern P as the zero pattern of A. However, more accurate factorization can be obtained by allowing some fill-in, denoted by ILU(p) where p stands for the desired level of fill. This class of preconditioner has some difficulties to converge in a reasonably number of iterations on ill-conditioned systems.

#### 2.1.2.4 AMG

Algebraic MultiGrid (AMG) [Brandt et al., 1984] method solves linear systems based on multigrid principles. It is a complex algorithm which is widely spread in simulation area because of its robustness property on large sparse and unstructured systems. The setup phase is non-negligible in the total solving time because of the determination, at each coarse grid level, of the coarse grid, interpolation and coarse grid operators. The setup time may be longer than the solving time as the solver requires only a few iterates to converge. The solving phase is composed of two complementary operations, also called the smoothing and the coarse grid correction steps. The first one attempt to reduce high-frequency error by the application of a smoother, also called relaxation method. Coarse grid correction eliminates low-frequency error. It performs a transfer of information to a coarser grid (also called restriction operator), then a coarse-grid operator is solved and at last the solution is send back to the fine grid (also called the interpolation). The major improvements of such

a method is that it operates on smaller problems, and the computational cost is therefore smaller. Moreover, it requires no information on the problem geometry. The number of iterations needed to converge only depends on the system size. In addition to that, coarsening and smoothing strategies may be tuned to affect convergence rates.

### 2.2 Parallel Computers

Moore's law [Moore, 1965] states that the number of transistors on a chip is multiplied by 2 every 18 months. This law shows its limits because of the downsizing of the hardware components is not enough to reach high performances regarding actual challenges of scientific computing. Since the rise of multi-core processors, parallel computing is an increasing need to take advantage of these architectures. Nowadays, processor's frequency tends to converge because of the heat dissipation induced by hardware limitations.

Since the multiplication of processors on a chip, the Admahl's law defines the theoretical speed-up obtained on an application. An application can be split in a part that is parallelizable, and another which is not. Let  $T_p$  be the execution time on p processors, and S the time to compute the serial part. The sequential time to compute the parallel part, denoted by B, is so deduced by  $B = T_1 - S$ . On p processors, a lower bound is so given by  $T_p = S + (B/p)$ . However, some overheads occur and factors such as data latency or memory bandwidth make the theoretical time slightly different.

The aim of this section is to describe parallelism from hardware to programmer's point of view. In the first sub-section, we describe a way for parallel architectures and parallelism classification. We then describe each significant hardware device which composes an actual architecture and its hierarchy. In the third section, we detail the programming models that help the developer to efficiently take advantage of parallel computers.

### 2.2.1 Generalities

The rise of multi-processors systems increases the complexity of programming. Several types of parallel computers exist, and there is a need to find a classification to describe any machine according to hardware features. There are several ways to classify parallel computers, and we first present the most used in parallel architectures: the Flynn taxonomy [Flynn, 1972]. This classification is based on instruction and data streams. In a second time, we present memory types encountered on parallel machines.

### 2.2.1.1 Classification

On a sequential computer, executing model is the same as the Von Neumann machine [Von Neumann, 1945]. There is a unique instructions stream in which one instruction is process per processor cycle on a single data item. In parallel computing area, an application can be viewed as one or several instructions streams acting on one or several data streams.

The classification proposed by Flynn [Flynn, 1972] is based on it. It deals with both instruction and data streams, and enables to store any computer in one of the four following categories:

- Single Instruction stream, Single Data stream (SISD) It refers to the uniprocessor category. Developers see it as a sequential computer.

- Single Instruction stream, Multiple Data stream (SIMD) The same instruction is processed by multiple processors on multiple data in parallel. Such computers own a single control unit. Exploiting this type of architectures needs sufficient amount of data. Vector architectures and data parallel architectures are placed in this computer class.

- Multiple Instruction stream, Single Data stream (MISD) Until now, there is no computer of this class.

- Multiple Instruction stream, Multiple Data stream (MIMD) Each processor executes its own instruction stream on its own data stream. Programming such architecture is more flexible, and imposes a significant grain size to efficiently exploit parallelism.

For example, a common architecture in clusters are nodes composed of two processors. Such a computational node can be classified in the MIMD category. A single single processor includes several computing units (cores) which have SIMD capabilities.

There are several other models which extend the classification presented above. For example, Single Program Multiple Data (SPMD) and Multiple Program Multiple Data (MPMD) take care of a running program which can be distributed on one or several computational nodes, and process local data at the same time.

### 2.2.1.2 Levels of parallelism

Parallelism is a meaning to divide a problem in smaller pieces processed by some computational units. There are several ways and different levels to express parallelism. In this part, we gradually review each level of parallelism.

**Instruction Level Parallelism (***ILP***)** in which instructions can be grouped or reorganized to be processed in parallel if dependencies between data allow it, without changing the result. Instruction level parallelism can be exploited by two major ways. The first one is at hardware level with a dedicated logic on a chip. The second one is at software level with the use of compiler.

**Data Level Parallelism (***DLP***)** is the ability to divide a problem by splitting processed data which are related to its resolution. Data are then distributed among working threads or processes which operate on it the same instructions. Efficient data parallelism requires a large amount of data to process. In this case, the amount of data processed is known as the work's granularity.

**Task Level Parallelism (***TLP***)** is the ability to divide the whole work in several tasks that can be performed simultaneously on different data. Tasks may be different from each other, and the completion of all of them lead to the final result of the problem.

### 2.2.2 Processors Architecture

The processor is the hardware unit responsible to perform computations. Nowadays, computing processors handle several execution units to enable parallel computing. Classical multi-processor chips are equipped with few but powerful execution units, also named as cores. On the other hand, compared to classical processors, computing accelerators generally handle much more cores which are less powerful. However, massive parallelism induced by these accelerators may increase performances.

Computational accelerators may take several forms, and we aim in this subsection to review some of the most popular ones. The first one, Graphical Processing Units (*GPUs*), refers to a widespread component in computer systems which are now used for achieving high performance computing. The second one is the Many Integrated Cores (MIC) introduced by Intel to provide huge number of simplified cores to make computations.

### 2.2.2.1 General purpose processors

Current processors in a computer refer to multi-processors chips or multi-core processors. A multi-core processor is composed of several processors, also called cores, on the same die. It means that these chips contain several independent processing units, which collaborate in parallel to achieve better performances than a single core processor. The set of instructions that a processor can process is called the Instruction Set Architecture (*ISA*). One of the most popular ISA is the x86 instruction set. Instructions represent data transfers, arithmetic, conditional, branches and logical operations. A register is the fastest memory location and is used to store temporary variables. There are some extensions to classical ISAs to SIMD instructions like Streaming SIMD Extension (*SSE*) instructions and also Advanced Vector Extension (*AVX*) support.

Current generation of multi-processors chips contains a cache memory hierarchy of three levels of cache, from the closest to the farthest. Cache memory avoids a processor to retrieve data each time from main memory, and so reduces latency by this means. At the top level, there is the L1 cache which is private to a core. This is the fastest and the closest cache level to the core but the size is highly limited. The L2 cache level is slightly bigger, and local to core but data access has higher latency. In some cases, L2 may also be shared (e.g. AMD Buldozer has shared L2 cache between 2 cores). The L3 cache level is the largest cache level, and is generally shared between all the cores. Nowadays, this is the last cache level to store data on current generation of processors. If after all, the data is not store in one of the three levels of cache, the core request data from main memory and the latency is therefore higher.

### 2.2.2.2 Graphic Processing Units (GPU)

GPUs are no longer exclusively used for graphical applications. General Purpose processing on GPU (GPGPU) refers to the fact that now GPUs are used as computational accelerators for general purpose computations. They provide a massively parallel architectures composed of a huge number of cores which have a simplified design. The most used architectures for GPGPU are provided by the Nvidia company, and are named CUDA-aware architectures. In Kepler architecture, cores are grouped in streaming multiprocessors (SMX), where each one shares a L2 cache memory. Each SMX owns its own memory hierarchy which is shared by all the cores of this SMX. For instance, each one shares a L1 cache between all the cores, and a constant cache memory. GPU computing introduces Single Instruction Multiple Threads (SIMT) execution model. Threads are grouped in a set called warp (generally equals to 32 threads). Each SMX also handles a quad warp scheduler, which allows to process the same instruction concurrently on four threads of different warps. Such data transfers between host (CPU side) and device (GPU device) are processed through the PCI Express bus. If an application processes too many data transfers, it could be a bottleneck for application performances. Designing a good scheduler that reduce data transfers and balance the work load is challenging. More details can be found in the Kepler architecture white paper [Nvidia Corporation, 2012].

### 2.2.2.3 Intel<sup>®</sup> Xeon Phi Coprocessor

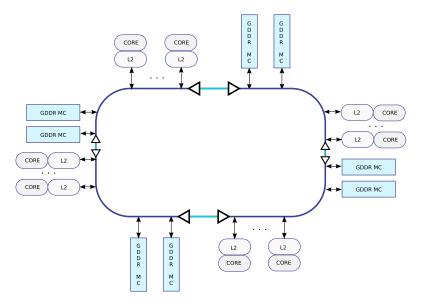

The accelerator proposed by Intel<sup>®</sup> is based on a Many Integrated Core (MIC) architecture, named Intel<sup>®</sup> Xeon Phi [Jeffers and Reinders, 2013]. The coprocessor is known under the name Knights Corner (KNC) product. The board is composed of more or less 60 x86 cores, linked by a bi-directional ring interconnect. Each core owns its own memory hierarchy with L1 cache which is closer to the core, and L2 cache which is still closer but in direct link with the interconnect. There are 8 memory controllers on the ring interconnect to dispatch data around the ring from external memory device. The key feature of such an architecture is that each core contains a vector processing unit to process vector instructions. Difficulties come from the code optimization to take care of vector processing, hyperthreading and multi-level parallelism. The hardware architecture of the KNC coprocessor board is illustrated in Fig. 2.1.

### 2.2.3 Memory Systems

It is also important to distinguish which type of memory is used on parallel computers. The reduction of both latency and bus contention is a determinant factor in memory systems. The latency defines the time from the request to a data access to the answer. Bus contention refers to the fact that more than one device attempt to simultaneously access to memory.

Nowadays, multi-processors chips handle several layers of memory hierarchy to reduce latency. There are memory blocks, called caches, very closed to processing units to reduce time to data retrieval. On the other hand, there is a need to handle memory

Figure 2.1 – Intel®Xeon Phi architecture

coherency between all the layers of the memory hierarchy. There are specific protocols to ensure the validity of the data between all the layers of the cache hierarchy of all the cores. Such a protocol is named a cache coherence protocol. An architecture which is not cache coherent is not easy to program.

We review here the two main categories of memory systems space. A shared memory system relies on a centralized memory shared between the processors. In the other hand, distributed memory is located at different locations such that each processor has not a direct hardware access to this memory bank.

### 2.2.3.1 Shared Memory

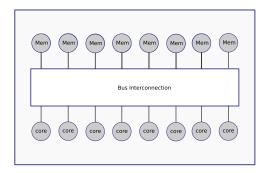

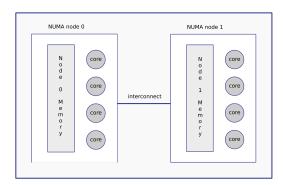

In shared memory systems, a set of processors is linked to a memory system through an interconnection network, and a processor can access to each memory location without any software support. The interconnect can either connect all the processors to the main memory, or each processor has its own local memory and can access to other memory locations. So the main categories of shared memory systems are the Uniform Memory Access (*UMA*) and Non-Uniform Memory Access (*NUMA*) architectures.

### **Uniform Memory Access (UMA)**

UMA architectures are characterized by the fact that each processor has the same path length to any memory address. In this case, bus contention may be a bottleneck for application when several cores have to access the centralized memory at the same time. An example of an UMA architecture with 8 threads is given in Fig.2.2. Systems which use UMA architecture are Symmetric Multi-Processors (SMP) and the first multi-core processors.

Figure 2.2 – UMA system with bus interconnection

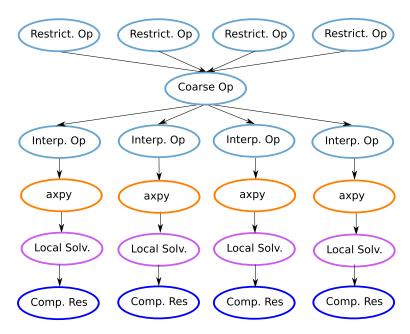

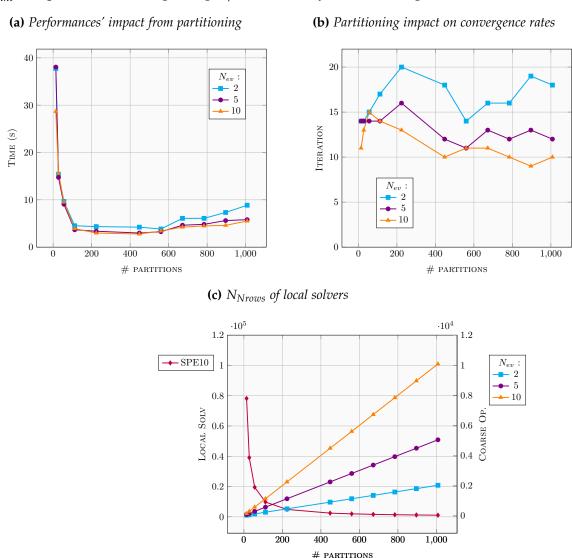

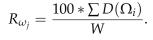

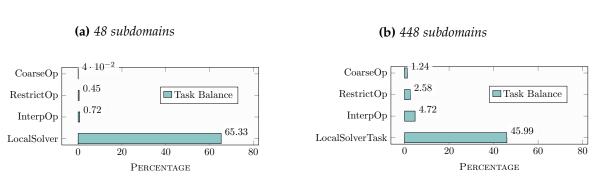

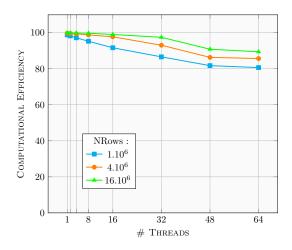

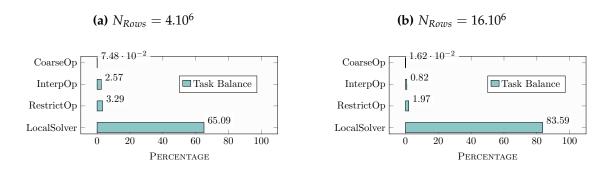

# Non Uniform Memory Access (NUMA)