# Testing Techniques for Detection of Hardware Trojans in Integrated Circuits of Trusted Systems

Leonel Acunha Guimarães

### ▶ To cite this version:

Leonel Acunha Guimarães. Testing Techniques for Detection of Hardware Trojans in Integrated Circuits of Trusted Systems. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2017. English. NNT: 2017GREAT080. tel-01754790

### HAL Id: tel-01754790 https://theses.hal.science/tel-01754790

Submitted on 3 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano Électronique & Nano Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

### Leonel ACUNHA GUIMARÃES

Thèse dirigée par Laurent FESQUET et co-encadreée par Rodrigo POSSAMAI BASTOS

réparée au sein du Laboratoire TIMA dans l'École Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal (E.E.A.T.S)

# Testing Techniques for Detection of Hardware Trojans in Integrated Circuits of Trusted Systems

Thèse soutenue publiquement le **1 décembre 2017**, devant le jury composé de :

#### M. Guy GOGNIAT

Professeur, Université de Bretagne du Sud, Président

#### M. Giorgio DI NATALE

Directeur de Recherche, LIRMM-CNRS, Rapporteur

### M. Lilian BOSSUET

Professeur, Université Jean-Monnet de Saint-Etienne, Rapporteur

### M. Laurent FESQUET

Maître de Conférences, Université Grenoble Alpes, Directeur de thèse

### M. Rodrigo POSSAMAI BASTOS

Maître de Conférences, Université Grenoble Alpes, Co-Encadrant de thèse

# Acknowledgement

I would like to dedicate a few words to acknowledge some people who were essential for the accomplishment of this work.

Firstly, I would like to express my sincere gratitude to my advisors Dr. Laurent Fesquet and Dr. Rodrigo Possamai Bastos who gave me the chance to work with them and guided me through this harsh road. Their guidance surely helped me to improve my research and mitigate all the insecurities a PhD student may have. I wish to express my special thanks to Prof. Guy Gogniat, Dr. Giorgio Di Natale, and Prof. Lilian Bossuet who accepted being part of my examining board. Their valuable and constructive feedback certainly counted for improving the quality of this manuscript and the dissertation defense.

I would like to thank all the staff of TIMA Laboratory, EEATS, and CIME Nanotech who always helped me somehow with uncountable issues, specially Alejandro Chagoya. I would like to name a few researchers, PhD and former PhD students who were great fellows whose collaboration impacted decisively in the result of this work: Thiago, Otto, Rodrigo Iga, Jean, Tugdual, Chadi, Amani, Raphael, Matheus, Ricardo, Assia, Karim, Sophie, Grégoire, Sylvain, Arthur, Alexandre, and Ali. Their feedbacks, friendship, and numerous rubber duck debbuging were essential for the final result of this work. I would like to also address special thanks to all my friends I had the pleasure to meet in Grenoble.

I wish to thank my loved ones who I had to stay apart since I decided to move to France: my aunts, uncles, cousins, grandmother, godfather, and all friends in Brazil.

I would like to extend great thanks to my dear Vó Cléia, Vó Joana, and Dinda Nadir who I dedicate this thesis to. I am grateful for your teaching, love, kindness, and affection. I would change everything to pass more time with you.

I would especially like to thank my parents Leonel and Ivana for everything they have done for me, they are the best parents I could have. This work would be nothing without them.

Finally, I wish to thank my beloved girlfriend Natália for her love, friendship, support, and inspiration.

# **Table of Contents**

| Al | ostrac         | et       |                                                       | XV   |  |  |  |

|----|----------------|----------|-------------------------------------------------------|------|--|--|--|

| Re | ésumé          | 3        |                                                       | xvii |  |  |  |

| 1  | 1 Introduction |          |                                                       |      |  |  |  |

| 2  | Har            | dware T  | Trojan Insertion and Detection                        | 5    |  |  |  |

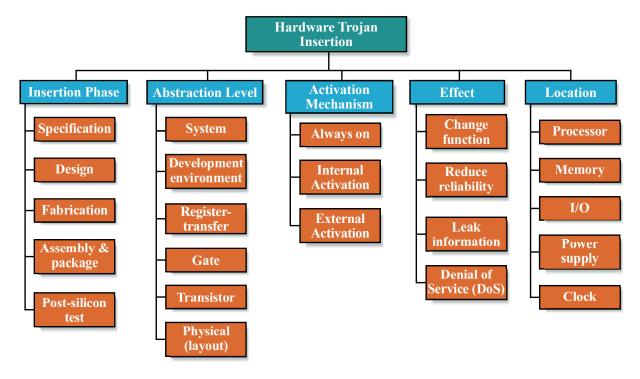

|    | 2.1            | Trojan   | Insertion                                             | . 5  |  |  |  |

|    |                | 2.1.1    | Trojan Model                                          | . 7  |  |  |  |

|    |                | 2.1.2    | Trojan Taxonomy                                       | . 8  |  |  |  |

|    |                | 2.1.3    | Case Studies: Trojans at Different Abstraction Levels | . 12 |  |  |  |

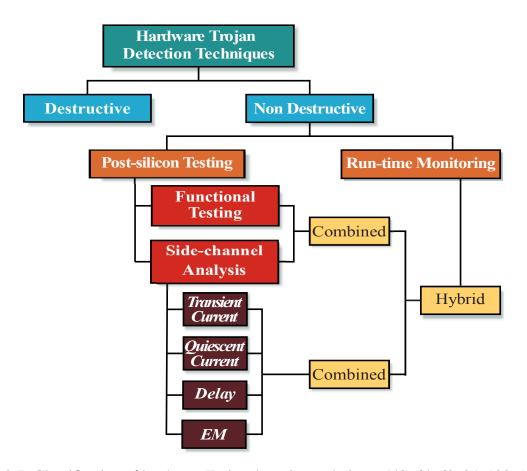

|    | 2.2            | Trojan   | Detection                                             | . 15 |  |  |  |

|    |                | 2.2.1    | Destructive: Physical Inspection                      | . 17 |  |  |  |

|    |                | 2.2.2    | Functional (Logic) Testing                            | . 17 |  |  |  |

|    |                | 2.2.3    | Side-Channel Analysis                                 | . 18 |  |  |  |

|    |                | 2.2.4    | Run-time Monitoring                                   | . 24 |  |  |  |

|    |                | 2.2.5    | Combined and Hybrid Methods                           | . 24 |  |  |  |

|    |                | 2.2.6    | Trojan Prevention                                     | . 26 |  |  |  |

|    |                | 2.2.7    | Overall Analysis                                      | . 26 |  |  |  |

|    | 2.3            | Conclu   | usion                                                 | . 27 |  |  |  |

| 3  | Ana            | lysis of | Transistor-Level Trojans in Ring Oscillators          | 29   |  |  |  |

|    | 3.1            | Motiva   | ation: Attack in RO-based TRNG                        | . 30 |  |  |  |

|    | 3.2            | Tri-Sta  | ate Trojans on Ring Oscillators                       | . 30 |  |  |  |

|    |                | 3.2.1    | Capacitor Trojan                                      | . 31 |  |  |  |

|    |                | 3.2.2    | Double-Switch Trojan                                  | . 32 |  |  |  |

|    |                | 3.2.3    | Transmission-Gate Trojan                              | . 32 |  |  |  |

|    | 3.3            | Trojan   | results in Ring Oscillators                           | . 33 |  |  |  |

|    |                | 3.3.1    | RO Frequency Analysis                                 | . 34 |  |  |  |

|    |                | 3.3.2    | Power Consumption Analysis                            | . 36 |  |  |  |

|    |                | 3.3.3    | Jitter x Frequency Analysis                           | . 36 |  |  |  |

|      | 3.3.4               | Case study                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4  | Conclu              | asions                                                                                                                                                                                                                                                                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bulk | . Built-i           | n Current Sensors For Detection of Transient Faults                                                                                                                                                                                                                                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

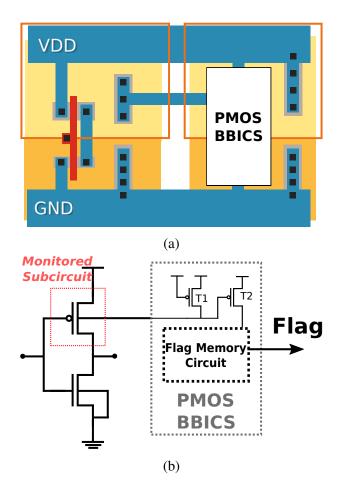

| 4.1  | Archite             | ectures of Built-In Current Sensors                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

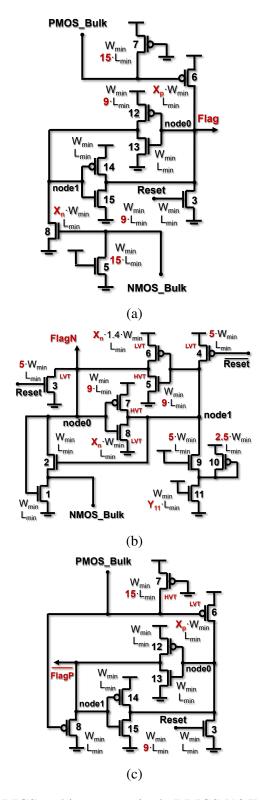

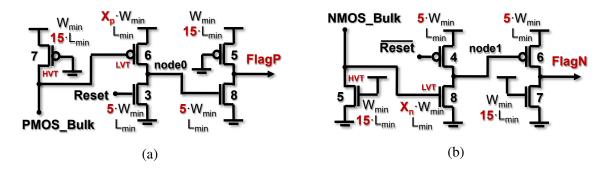

|      | 4.1.1               | Single BBICS architectures                                                                                                                                                                                                                                                                        | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.1.2               | BBICS architectures of Neto et al                                                                                                                                                                                                                                                                 | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.1.3               | BBICS architectures of Zhang et al                                                                                                                                                                                                                                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

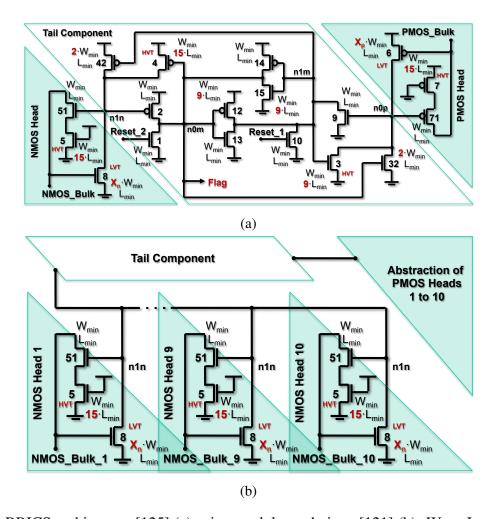

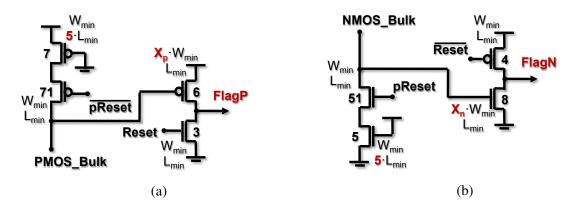

|      | 4.1.4               | Modular BBICS architectures                                                                                                                                                                                                                                                                       | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.1.5               | Dynamic BBICS architectures of Simionovski and Wirth                                                                                                                                                                                                                                              | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

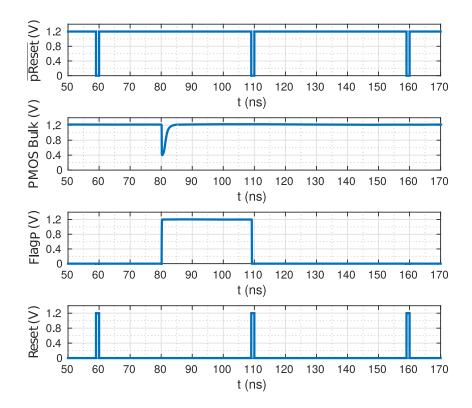

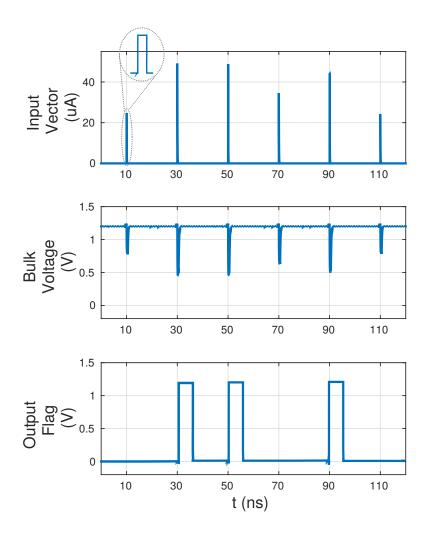

| 4.2  | New D               | ynamic BBICS Architecture                                                                                                                                                                                                                                                                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.3  | Sensiti             | vity of a Flip-Flop in Detecting Transient Faults                                                                                                                                                                                                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.3.1               | Experiments                                                                                                                                                                                                                                                                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.3.2               | Results and analysis                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.4  | Results             | s and Analysis of BBICS Sensitivities in Detecting Transient Faults                                                                                                                                                                                                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.4.1               | Experiments for sizing BBICS architectures                                                                                                                                                                                                                                                        | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.4.2               | Experiments for analyzing the sensitivities of BBICS architectures                                                                                                                                                                                                                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

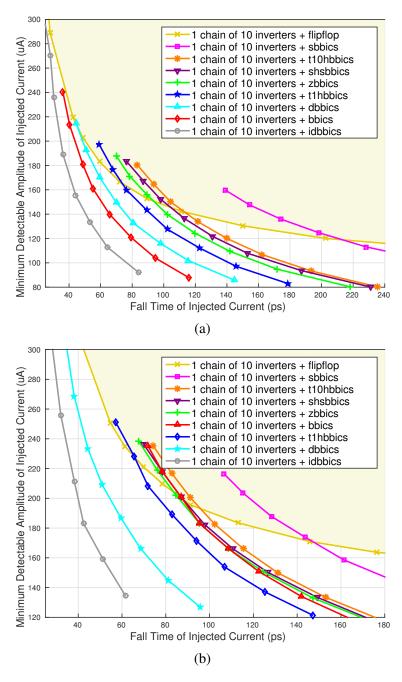

|      | 4.4.3               | Comparative analysis of BBICS detection sensitivities                                                                                                                                                                                                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

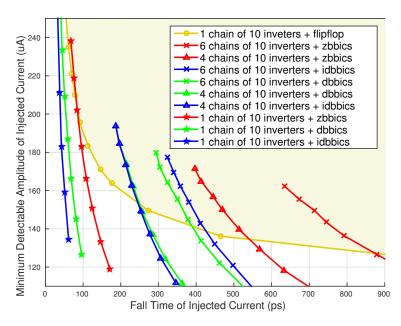

|      | 4.4.4               | Influence of the monitored area size                                                                                                                                                                                                                                                              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

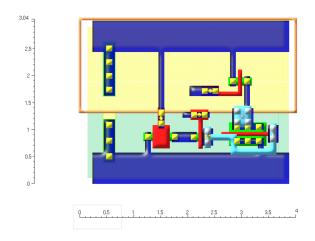

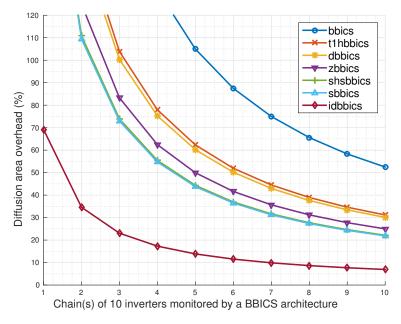

|      | 4.4.5               | Estimation of the area overhead imposed by BBICS architectures                                                                                                                                                                                                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.4.6               | Corner analysis of BBICS architectures                                                                                                                                                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.5  | Conclu              | isions                                                                                                                                                                                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

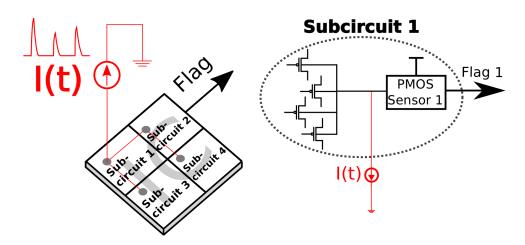

| Reus | se of Bu            | lk Built-in Sensors for Detection of Trojans                                                                                                                                                                                                                                                      | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.1  | Built-ii            | n Current Sensors for Generating Signatures of Subcircuit Substrate                                                                                                                                                                                                                               | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.2  | Propos              | ed HT Detection Method                                                                                                                                                                                                                                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.2.1               | Injection of Current Pulses into MOSFET Body Terminals                                                                                                                                                                                                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.2.2               | Monitoring of Current Sensors Built in System Subcicuits                                                                                                                                                                                                                                          | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

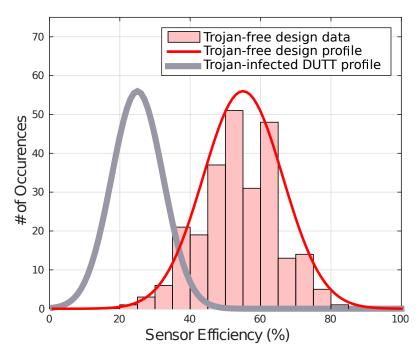

|      | 5.2.3               | Compilation of Signatures Collected from Subcircuit Substrate                                                                                                                                                                                                                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.2.4               | Statistical Analysis for Detecting HTs in System Subcircuits                                                                                                                                                                                                                                      | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3  | Simula              | ation Results and Analysis                                                                                                                                                                                                                                                                        | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.3.1               | Description of Simulation Experiments                                                                                                                                                                                                                                                             | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.3.2               | Targeted HT Implanted in DUTTs                                                                                                                                                                                                                                                                    | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.3.3               | DUTTs Used to Generate Simulation Results                                                                                                                                                                                                                                                         | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

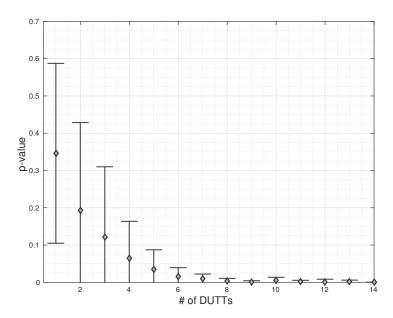

|      | 5.3.4               | System Area Overhead and Number of Required Samples                                                                                                                                                                                                                                               | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4  | Conclu              | sions and Perspectives                                                                                                                                                                                                                                                                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.2 4.3 4.4 5.1 5.2 | 3.4 Conclusion  Bulk Built-i  4.1 Archite  4.1.1  4.1.2  4.1.3  4.1.4  4.1.5  4.2 New D  4.3 Sensiti  4.3.1  4.3.2  4.4 Results  4.4.1  4.4.2  4.4.3  4.4.4  4.4.5  4.4.6  4.5 Conclusion  Reuse of Built-ii  5.2 Propose  5.2.1  5.2.2  5.2.3  5.2.4  5.3 Simulation  5.3.1  5.3.2  5.3.3  5.3.4 | Bulk Built-in Current Sensors For Detection of Transient Faults 4.1 Architectures of Built-In Current Sensors 4.1.1 Single BBICS architectures 4.1.2 BBICS architectures of Neto et al. 4.1.3 BBICS architectures of Zhang et al. 4.1.4 Modular BBICS architectures 4.1.5 Dynamic BBICS architectures of Simionovski and Wirth 4.2 New Dynamic BBICS architecture 4.3 Sensitivity of a Flip-Flop in Detecting Transient Faults 4.3.1 Experiments 4.3.2 Results and analysis 4.4 Results and Analysis of BBICS Sensitivities in Detecting Transient Faults 4.4.1 Experiments for sizing BBICS architectures 4.4.2 Experiments for analyzing the sensitivities of BBICS architectures 4.4.3 Comparative analysis of BBICS detection sensitivities 4.4.4 Influence of the monitored area size 4.4.5 Estimation of the area overhead imposed by BBICS architectures 4.4.6 Corner analysis of BBICS architectures 4.5 Conclusions  Reuse of Bulk Built-in Sensors for Detection of Trojans 5.1 Built-in Current Sensors for Generating Signatures of Subcircuit Substrate 5.2 Proposed HT Detection Method 5.2.1 Injection of Current Pulses into MOSFET Body Terminals 5.2.2 Monitoring of Current Sensors Built in System Subcircuits 5.2.3 Compilation of Signatures Collected from Subcircuit Substrate 5.2.4 Statistical Analysis for Detecting HTs in System Subcircuits 5.3.3 Duscription of Simulation Experiments 5.3.4 System Area Overhead and Number of Required Samples |

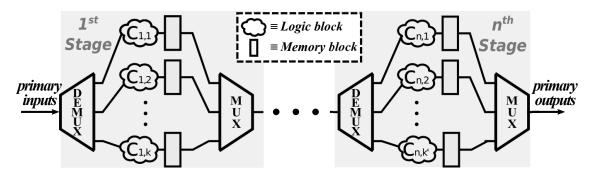

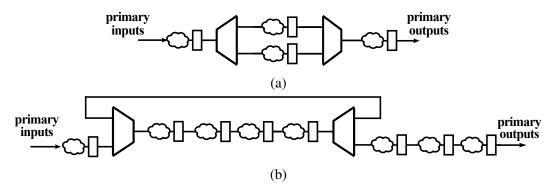

| 6  | Dete                                  | ection o | f Trojans in Asynchronous Circuits                           | <b>73</b> |  |

|----|---------------------------------------|----------|--------------------------------------------------------------|-----------|--|

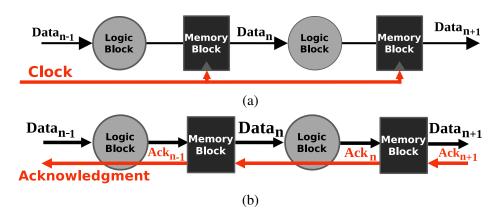

|    | 6.1                                   | Funda    | mentals of QDI Asynchronous systems                          | 74        |  |

|    | 6.2                                   | Side C   | Channel Analysis Applied to QDI Asynchronous Circuits        | 75        |  |

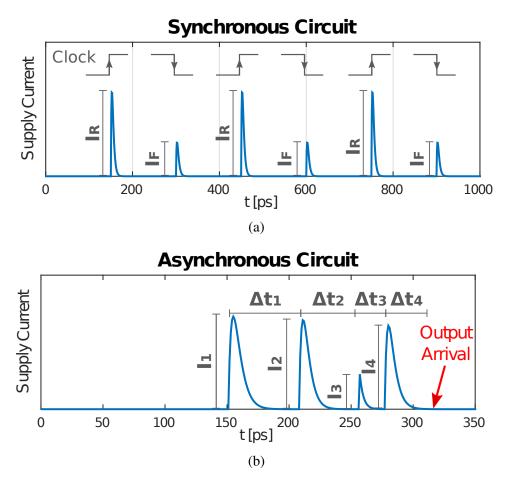

|    |                                       | 6.2.1    | Exploiting Side-Channel Signals in QDI Asynchronous Circuits | 75        |  |

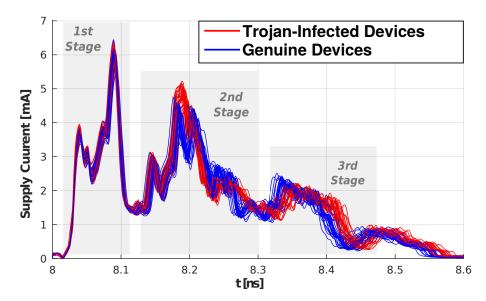

|    |                                       | 6.2.2    | Trojan Impacts on Side-Channel Signals                       | 77        |  |

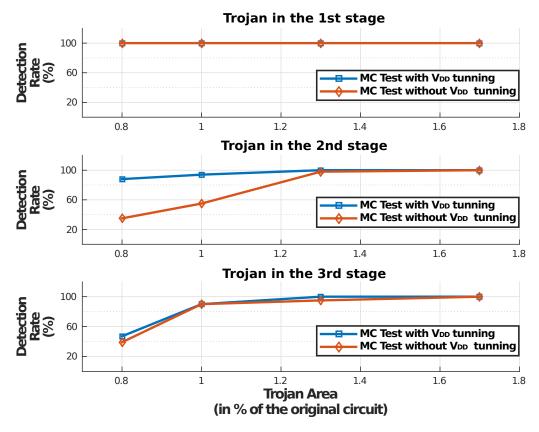

|    | 6.3                                   | Propos   | sed HT-Detection Technique for QDI Asynchronous Circuits     | 78        |  |

|    |                                       | 6.3.1    | Test Procedure: Collecting $I_{DDT}$ and $\Delta t$          | 78        |  |

|    |                                       | 6.3.2    | Voltage Tunning to Increase PV Compensation                  | 79        |  |

|    |                                       | 6.3.3    | Minimum Necessary Test Vectors                               | 79        |  |

|    | 6.4                                   | Experi   | ments, Results, and Analysis                                 | 80        |  |

|    |                                       | 6.4.1    | Target Case-Study: An 8-bit ALU                              | 80        |  |

|    |                                       | 6.4.2    | Target Hardware Trojan                                       | 81        |  |

|    |                                       | 6.4.3    | Test Description                                             | 81        |  |

|    |                                       | 6.4.4    | Results and Analysis                                         | 81        |  |

|    | 6.5                                   | Conclu   | usions                                                       | 83        |  |

| 7  | Con                                   | clusion  | s and Perspectives                                           | 85        |  |

| Gl | Glossary 8                            |          |                                                              |           |  |

| Bi | Bibliography of Author's Publications |          |                                                              |           |  |

| Re | References 93                         |          |                                                              |           |  |

# **List of Figures**

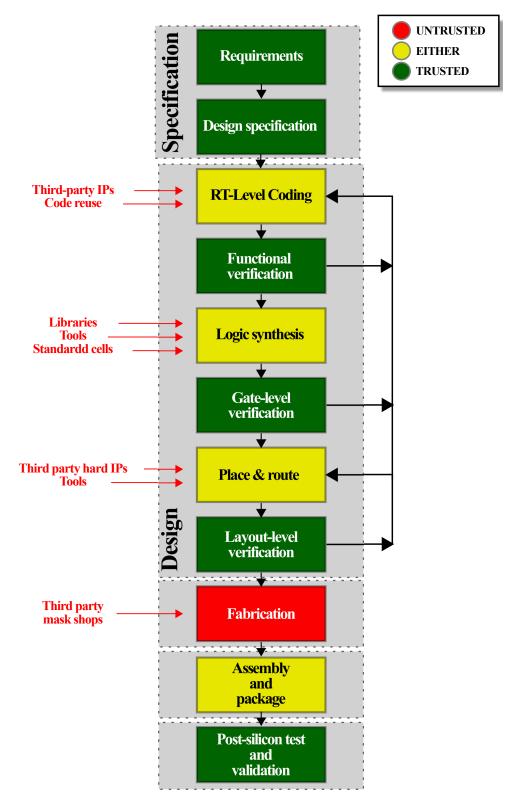

| 2.1  | Vulnerable steps of a modern IC production chain and their levels of trust taking         |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | into account: the adversary's information about the design, the difficulty of             |    |

|      | tampering with the system, and the facility of detecting modifications [24, 48,           |    |

|      | 61, 132]                                                                                  | 6  |

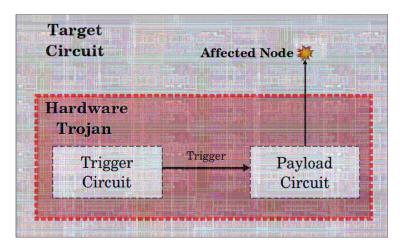

| 2.2  | Architecture of a Trojan inserted on a target circuit                                     | 8  |

| 2.3  | Trojan insertion taxonomy [24, 63, 79, 118, 120, 130, 131, 132, 137]                      | 8  |

| 2.4  | Architecture of the Trojan-infected AES-T2000 benchmark [120]                             | 13 |

| 2.5  | Architecture of the gate-level Trojan implemented in the Wishbone bus in the              |    |

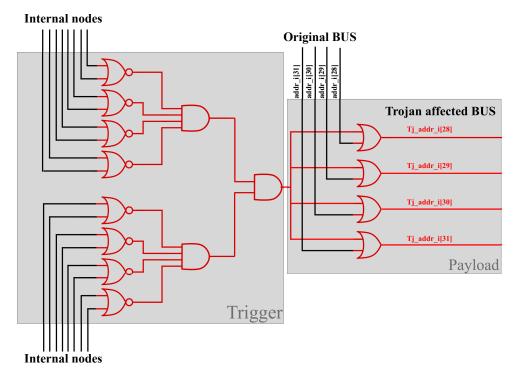

|      | benchmark <i>wb_conmax-T100</i> [118, 120]                                                | 14 |

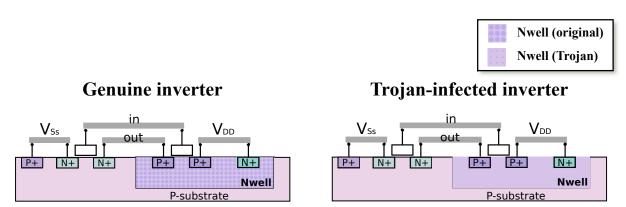

| 2.6  | Layout of an inverter with the dopant Trojan presented in [72]                            | 15 |

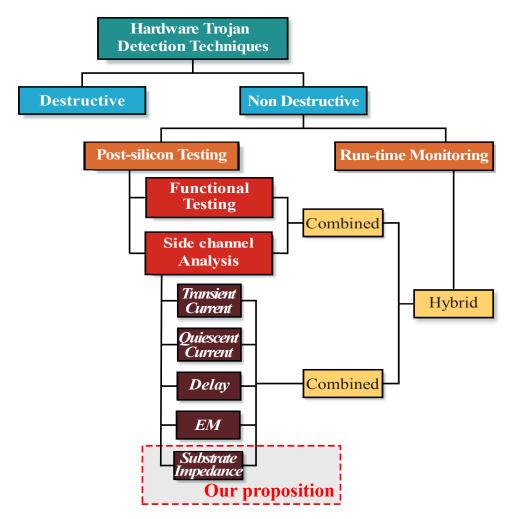

| 2.7  | Classification of hardware Trojan detection techniques [48, 64, 69, 94, 130, 132].        | 16 |

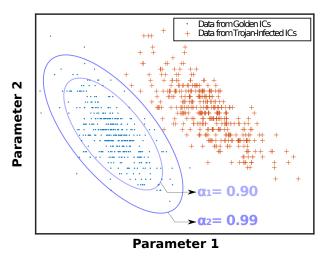

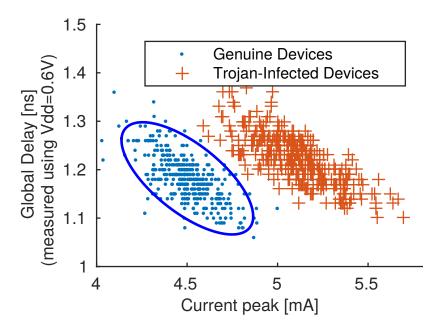

| 2.8  | Space of parameters generated by the data obtained from golden devices – error            |    |

|      | ellipses with difference significance levels $\alpha_1=0.90$ and $\alpha_2=0.99$ surround |    |

|      | it –, and from Trojan-infected DUTTs                                                      | 19 |

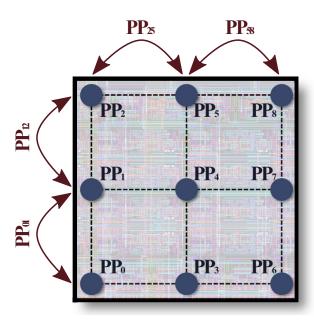

| 2.9  | Chip partition approach based on the measurement of multiple power supply                 |    |

|      | pins for Trojan isolation [114, 115]                                                      | 20 |

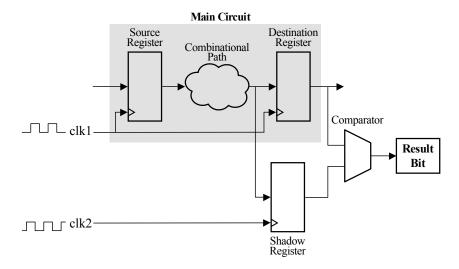

| 2.10 | Delay characterization with negative-skewed shadow registers [80]                         | 22 |

| 2.11 | EM emission maps generated considering a Trojan free DUTT (a); and a Trojan-              |    |

|      | infected DUTT (b). For each pixel, blue shades represents low difference be-              |    |

|      | tween EM emission from golden device and DUTT, and red shades denotes                     |    |

|      | considerable discrepancies [14, 129]                                                      | 23 |

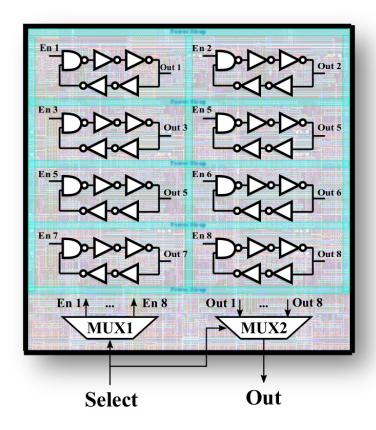

| 2.12 | A basic RON structure [149] with 8 ROs distributed in the circuit layout                  | 25 |

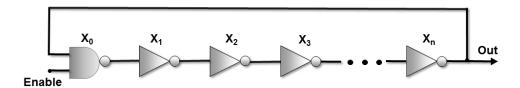

| 3.1  | A Trojan-free (n+1)-stage ring oscillator (RO)                                            | 30 |

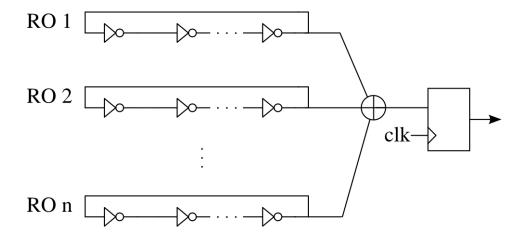

| 3.2  | The RO-based TRNG design                                                                  | 31 |

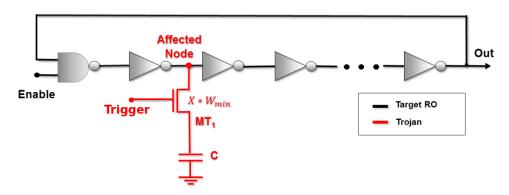

| 3.3  | Capacitor Trojan isolable by high impedance from the RO                                   | 32 |

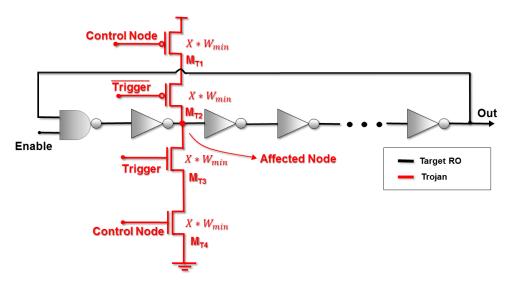

| 3.4  | Double-switch Trojan isolable by high impedance from the RO                               | 33 |

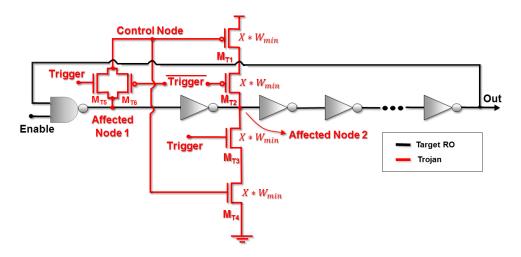

| 3.5  | Transmission-gate Trojan isolable by high impedance from the RO                           | 33 |

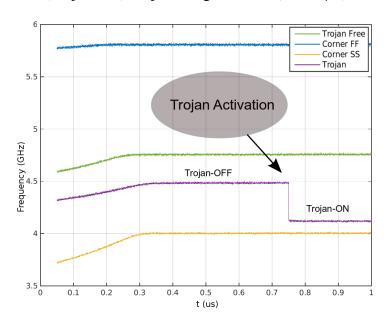

| 3.6  | Possible scenarios of Trojan insertion: Trojan-Free, Trojan-OFF, Trojan-ON                |    |

|      | and FF and SS corners of Trojan-Free circuit                                              | 34 |

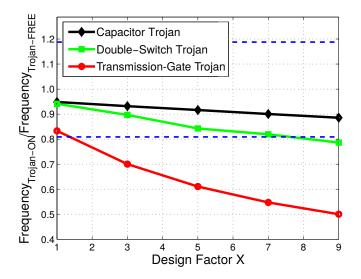

| 3.7  | Ratio of Trojan-ON frequency to Trojan-Free frequency vs. factor X of Trojan versions and corners FF and SS of the circuit Trojan-Free in a 7-stage RO                                                                                                                                                                                                                                                                          | 35 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

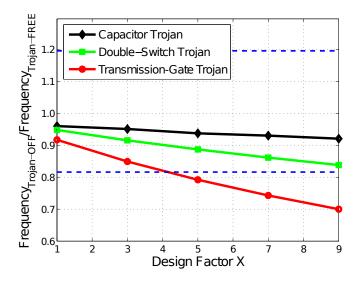

| 3.8  | Ratio of Trojan-OFF frequency to Trojan-Free frequency vs. factor X of Trojan versions and corners FF and SS of the circuit Trojan-Free in a 7-stage RO                                                                                                                                                                                                                                                                         | 36 |

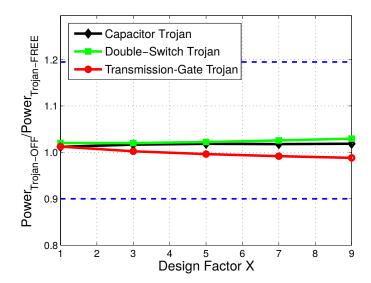

| 3.9  | Ratio of Trojan-OFF power consumptions to Trojan-Free power consumptions vs. factor X of Trojan versions and corners FF and SS of the circuit Trojan-Free in a 7-stage RO                                                                                                                                                                                                                                                       | 37 |

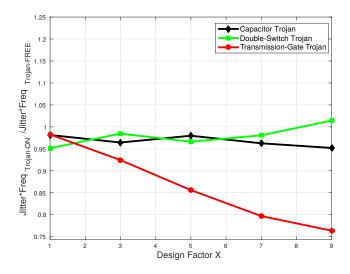

| 3.10 | Ratio proportional to jitter-frequency product of Trojan-ON / Trojan-Free vs. factor X of Trojan versions in a 7-stage RO                                                                                                                                                                                                                                                                                                       | 37 |

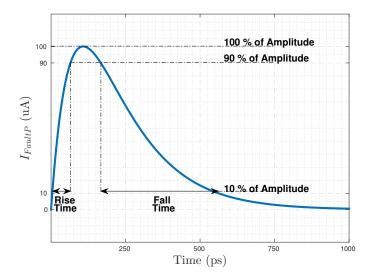

| 4.1  | Typical double-exponential profile of a transient fault, which is defined as a transient current generated on the circuit by a external perturbation such as radiation sources or laser beams                                                                                                                                                                                                                                   | 41 |

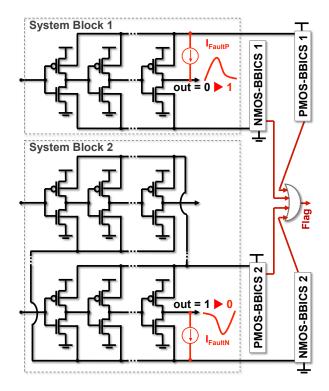

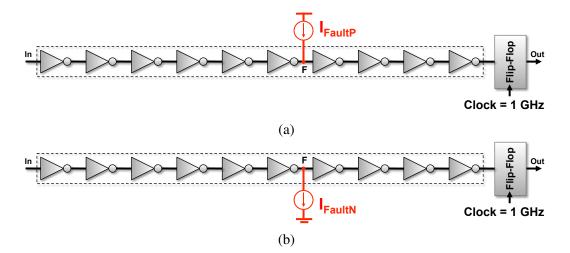

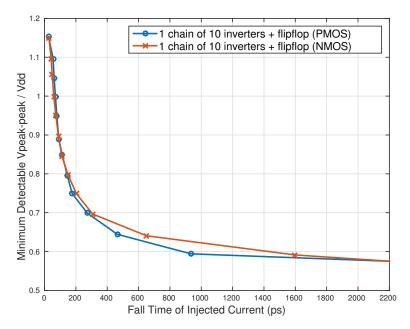

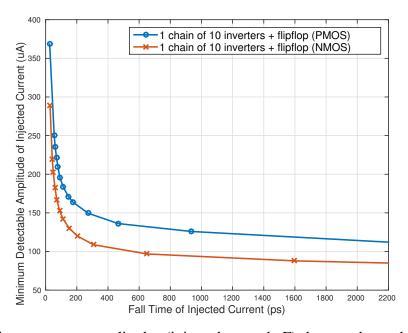

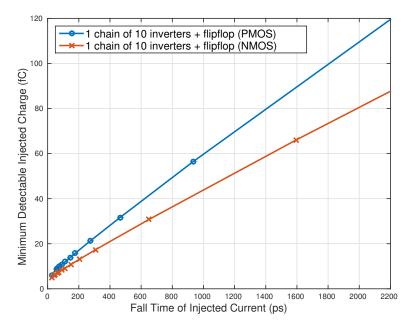

| 4.2  | Basic illustrations of BBICS monitoring two system blocks. $I_{FaultP}$ and $I_{FaultN}$ are current sources acting as external perturbations that produce abnormal current effects on the circuit defined as transient faults                                                                                                                                                                                                  | 42 |