## Efficient Hardware Implementations of LDPC Decoders, through Exploiting Impreciseness in Message-Passing Decoding Algorithms

Thien Truong Nguyen Ly

### ▶ To cite this version:

Thien Truong Nguyen Ly. Efficient Hardware Implementations of LDPC Decoders, through Exploiting Impreciseness in Message-Passing Decoding Algorithms. Networking and Internet Architecture [cs.NI]. Université de Cergy Pontoise, 2017. English. NNT: 2017CERG0904. tel-01783859

### HAL Id: tel-01783859 https://theses.hal.science/tel-01783859v1

Submitted on 2 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

présentée

à l'Université de Cergy Pontoise École Nationale Supérieure de l'Électronique de ses Applications

pour obtenir le grade de :

Docteur en Science de l'Université de Cergy Pontoise Spécialité : Sciences et Technologies de l'Information et de la Communication

Par

## Thien Truong NGUYEN LY

Équipes d'accueil :

Équipe Traitement des Images et du Signal (ETIS) – CNRS UMR 8051 Laboratoire des Systèmes sans fil Haut Débit (LSHD) – CEA/LETI

Titre de la thèse

### Efficient Hardware Implementations of LDPC Decoders, through Exploiting Impreciseness in Message-Passing Decoding Algorithms

Soutenue le 03/05/2017 devant la commission d'examen composée de :

| Prof. | Emmanuel Boutillon   | Lab-STICC, Université Bretagne Sud        | Président          |

|-------|----------------------|-------------------------------------------|--------------------|

| Prof. | Christophe Jégo      | IMS, Institut Polytechnique de Bordeaux   | Rapporteur         |

| Prof. | Charly Poulliat      | INP-ENSEEIHT, Université de Toulouse      | Rapporteur         |

| Dr.   | Oana Boncalo         | University Politehnica Timisoara, Romania | Examinateur        |

| Dr.   | Fakhreddine Ghaffari | ENSEA, Université de Cergy-Pontoise       | Examinateur        |

| Dr.   | Valentin Savin       | CEA-LETI, MINATEC, Grenoble               | Encadrant          |

| Prof. | David Declercq       | ENSEA, Université de Cergy-Pontoise       | Directeur de thèse |

To my parents, my two sisters and my sweetheart

## Acknowledgment

This thesis could not have been completed without the kind help of the following people to whom I would like to express my special thanks.

First, I would like to express my deepest gratitude to my two advisors, Prof. David DECLERCQ and Dr. Valentin SAVIN for their whole-hearted guidance, invaluable support, helpful advice, useful suggestions, and encouragement throughout my PhD work. Especially, I have no words to describe how thankful I am to Valentin SAVIN for everything he has done for me. He not only gave me professional knowledge but also helped me improve the soft skills. I could never forget the period when he helped me correct the articles, as well as my PhD manuscript. I will always remember the long discussions, and the rehearsals for my presentations. He has listened carefully and given me invaluable comments. To be honest, I would not be able to complete my PhD defense without his help. Besides, he helped me improve my speaking and writing skills. I also learned a lot from him, especially his enthusiasm, dedication, thoughtfulness, and meticulosity. I am sure that once I come back to Vietnam, I will also treat my students as he has done for me. In all sincerity, I would like to say thank Valentin again.

Second, my special thanks go to Prof. Christophe JEGO, and Prof. Charly POULLIAT for their acceptance as my PhD reviewers. Thank you so much for your comments on my PhD manuscript. I also would like to thank Prof. Emmanuel, Oana, and Fakhreddine for their acceptance as my PhD committee members.

Third, I would like to express my thanks to all the colleagues at Laboratoire des Systèmes sans fil Haut Débit (LSHD) – CEA/LETI for their friendship, support, encouragement, and fun, especially Minh, Quynh, Mickael, Yoann, Ludovic, Réda, Gourab, Moisés, Remun, Ioan-Sorin, Florian, Jimmy, Valerian, Robin, David, Luiz, Elodie, Rida, Antonio, Luc, Nicolas, Benoît, François, Sylvie, Jean-Baptiste, Manuel, and Xavier. I also would like to thank Lam, and Khoa, my colleagues, as well as my best friends at Équipe Traitement des Images et du Signal (ETIS). Thank you so much for all your help and support during my PhD work. I am also very grateful to Annick BERTINOTTI, Sandrine BERTOLA for helping me with administrative procedures, and Dimitri KTENAS, Fabien CLERMIDY for supporting me attend to the conferences.

Fourth, I would like to express my sincere gratitude to Bach Khoa University (BKU), Vietnam, especially Prof. Dinh-Thanh VU, Prof. Hong-Tuan DO, and Prof. Trang HOANG for giving me the opportunity to carry out my PhD study in France.

Last but not least, I am warmly grateful to my parents, Van-Chanh NGUYEN, and Thi-Kim LY, my two sisters, Nhu-An NGUYEN, and Ngoc-Khang NGUYEN, and my sweetheart, Kim-Anh NGUYEN for their love, moral support, and encouragement throughout my life. They have inspired me strength, shared with me moments of stress, disappointment, and encouraged me overcome all difficulties and challenges. Thank you very much.

# Author's publications

#### **Published** papers

- [A1] T. Nguyen-Ly, K. Le, F. Ghaffari, A. Amaricai, O. Boncalo, V. Savin, and D. Declercq, "FPGA design of high throughput LDPC decoder based on imprecise offset min-sum decoding", *IEEE 13th International New Circuits and Systems Conference (NEWCAS)*, pages 1-4, Grenoble, France, June 2015.

- [A2] T. T. Nguyen-Ly, K. Le, V. Savin, D. Declercq, F. Ghaffari, and O. Boncalo, "Non-surjective finite alphabet iterative decoders", *IEEE International Conference on Communications (ICC)*, pages 1-6, Kuala Lumpur, Malaysia, May 2016.

- [A3] Z. Mheich, T. Nguyen-Ly, V. Savin, and D. Declercq, "Code-aware quantizer design for finite-precision min-sum decoders", *IEEE International Black Sea Conference on Communications and Networking (BlackSeaCom)*, Varna, Bulgaria, June 2016.

- [A4] T. T. Nguyen-Ly, T. Gupta, M. Pezzin, V. Savin, D. Declercq, and S. Cotofana, "Flexible, cost-efficient, high-throughput architecture for layered LDPC decoders with fully-parallel processing units", *Euromicro Conference on Digital System Design (DSD)*, pages 230-237, Limassol, Cyprus, September 2016.

- [A5] T. T. Nguyen-Ly, V. Savin, X. Popon, and D. Declercq, "High throughput FPGA implementation for regular non-surjective finite alphabet iterative decoders", *IEEE International Conference on Communications Workshops (ICC)*, Paris, France, May 2017.

#### Submitted papers

[A6] T. T. Nguyen-Ly, V. Savin, K. Le, D. Declercq, F. Ghaffari, and O. Boncalo, "Analysis and design of cost-effective, high-throughput LDPC decoders", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 2017, submitted.

#### Participation to research projects

[DIAMOND] The author participated to the research project "Message Passing Iterative Decoders based on Imprecise Arithmetic for Multi-Objective Power-Area-Delay Optimization" (DIAMOND), supported by the Franco-Romanian (ANR-UEFISCDI) Joint Research Programme "Blanc-2013".

## Résumé

Les codes correcteurs d'erreurs sont une composante essentielle de tout système de communication, capables d'assurer le transport fiable de l'information sur un canal de communication bruitè. Les systèmes de communication de nouvelle génération devront faire face à une demande sans cesse croissante en termes de débit binaire, pouvant aller de 1 à plusieurs centaines de gigabits par seconde. Dans ce contexte, les codes LDPC (pour Low-Density Parity-Check, en anglais), sont reconnus comme une des solutions les mieux adaptées, en raison de la possibilité de paralléliser massivement leurs algorithmes de décodage et les architectures matérielles associées. Cependant, si l'utilisation d'architectures massivement parallèles permet en effet d'atteindre des débits très élevés, cette solution entraine également une augmentation significative du coût matériel.

L'objectif de cette thèse est de proposer des implémentations matérielles de décodeurs LDPC très haut débit, en exploitant la robustesse des algorithmes de décodage par passage de messages aux imprécisions de calcul. L'intégration dans le décodage itératif de mécanismes de calcul imprécis, s'accompagne du développement de nouvelles approches d'optimisation du design en termes de coût, débit et capacité de correction.

Pour ce faire, nous avons considéré l'optimisation conjointe de (i) le bloc de quantification qui fournit l'information à précision finie au décodeur, et (ii) les unités de traitement imprécis des données, pour la mise à jour des messages échangés pendant de processus de décodage. Ainsi, nous avons tout d'abord proposé un quantificateur à faible complexité, qui peut être optimisé par évolution de densité en fonction du code LDPC utilisé et capable d'approcher de très près les performances d'un quantificateur optimal. Le quantificateur proposé a été en outre optimisé et utilisé pour chacun des décodeurs imprécis proposés ensuite dans cette thèse.

Nous avons ensuite proposé, analysé et implémenté plusieurs décodeurs LDPC imprécis. Les deux premiers décodeurs sont des versions imprécises du décodeur « Offset Min-Sum » (OMS) : la surestimation des messages des noeuds de contrôle est d'abord compensée par un simple effacement du bit de poids faible (« Partially OMS »), ensuite le coût matériel est d'avantage réduit en supprimant un signal spécifique (« Imprecise Partially OMS »). Les résultats d'implémentation sur cible FPGA montrent une réduction importante du coût matériel, tout en assurant une performance de décodage très proche du OMS, malgré l'imprécision introduite dans les unités de traitement.

Nous avons ensuite introduit les décodeurs à alphabet fini non-surjectifs (NS-FAIDs, pour «Non-Surjective Finite Alphabet Iterative Decoders», en anglais), qui étendent le concept d'« imprécision » au bloc mémoire du décodeur LDPC. Les décodeurs NS-FAIDs ont été optimisés par évolution de densité pour des codes LDPC réguliers et irréguliers. Les résultats d'optimisation révèlent différents compromis possibles entre la performance de décodage et l'efficacité de la mise en oeuvre matérielle. Nous avons également proposé trois architectures matérielles haut débit, intégrant les noyaux de décodage NS-FAID. Les résultats d'implémentation sur cible FPGA et ASIC montrent que les NS-FAIDs permettent d'obtenir des améliorations significatives en termes de coût matériel et de débit, par rapport au décodeur Min-Sum, avec des performances de décodage meilleures ou très légèrement dégradées.

## Abstract

The increasing demand of massive data rates in wireless communication systems will require significantly higher processing speed of the baseband signal, as compared to conventional solutions. This is especially challenging for Forward Error Correction (FEC) mechanisms, since FEC decoding is one of the most computationally intensive baseband processing tasks, consuming a large amount of hardware resources and energy. The conventional approach to increase throughput is to use massively parallel architectures. In this context, Low-Density Parity-Check (LDPC) codes are recognized as the foremost solution, due to the intrinsic capacity of their decoders to accommodate various degrees of parallelism. They have found extensive applications in modern communication systems, due to their excellent decoding performance, high throughput capabilities, and power efficiency, and have been adopted in several recent communication standards.

This thesis focuses on cost-effective, high-throughput hardware implementations of LDPC decoders, through exploiting the robustness of message-passing decoding algorithms to computing inaccuracies. It aims at providing new approaches to cost/throughput optimizations, through the use of imprecise computing and storage mechanisms, without jeopardizing the error correction performance of the LDPC code. To do so, imprecise processing within the iterative message-passing decoder is considered in conjunction with the quantization process that provides the finite-precision information to the decoder. Thus, we first investigate a low complexity code and decoder aware quantizer, which is shown to closely approach the performance of the quantizer with decision levels optimized through exhaustive search, and then propose several imprecise designs of Min-Sum (MS)-based decoders. Proposed imprecise designs are aimed at reducing the size of the memory and interconnect blocks, which are known to dominate the overall area/delay performance of the hardware design. Several approaches are proposed, which allow storing the exchanged messages using a lower precision than that used by the processing units, thus facilitating significant reductions of the memory and interconnect blocks, with even better or only slight degradation of the error correction performance.

We propose two new decoding algorithms and hardware implementations, obtained by introducing two levels of impreciseness in the Offset MS (OMS) decoding: the Partially OMS (POMS), which performs only partially the offset correction, and the Imprecise Partially OMS (I-POMS), which introduces a further level of impreciseness in the checknode processing unit. FPGA implementation results show that they can achieve significant throughput increase with respect to the OMS, while providing very close decoding performance, despite the impreciseness introduced in the processing units.

We further introduce a new approach for hardware efficient LDPC decoder design, referred to as Non-Surjective Finite-Alphabet Iterative Decoders (FAIDs). NS-FAIDs are optimized by Density Evolution for regular and irregular LDPC codes. Optimization results reveal different possible trade-offs between decoding performance and hardware implementation efficiency. To validate the promises of optimized NS-FAIDs in terms of hardware implementation benefits, we propose three high-throughput hardware architectures, integrating NS-FAIDs decoding kernels. Implementation results on both FPGA and ASIC technology show that NS-FAIDs allow significant improvements in terms of both throughput and hardware resources consumption, as compared to the Min-Sum decoder, with even better or only slightly degraded decoding performance.

# Contents

| 1        | Intr | oducti | on        |                                                                                           | 1  |

|----------|------|--------|-----------|-------------------------------------------------------------------------------------------|----|

|          | 1.1  |        |           | ptivations                                                                                | 1  |

|          | 1.2  | Main ( | Contribut | ions and Thesis Outline                                                                   | 3  |

| <b>2</b> | Low  | -Densi | ity Parit | y-Check Codes and Message-Passing Decoders                                                | 7  |

|          | 2.1  |        |           |                                                                                           | 8  |

|          | 2.2  | LDPC   | Codes     |                                                                                           | 9  |

|          |      | 2.2.1  |           | on, Tanner graphs                                                                         | 9  |

|          |      | 2.2.2  | Quasi-C   | yclic LDPC codes                                                                          | 11 |

|          | 2.3  | Decod  |           | thms                                                                                      | 13 |

|          |      | 2.3.1  | Message   | -Passing algorithms                                                                       | 13 |

|          |      | 2.3.2  |           | copagation decoding                                                                       | 14 |

|          |      | 2.3.3  |           | n decoding                                                                                | 14 |

|          |      | 2.3.4  | Min-Sun   | n-based decoding                                                                          | 16 |

|          |      |        | 2.3.4.1   | Normalized and Offset Min-Sum decoding                                                    | 17 |

|          |      |        | 2.3.4.2   | Self-Corrected Min-Sum decoding                                                           | 18 |

|          | 2.4  | •      |           | Sum decoding                                                                              | 20 |

|          |      | 2.4.1  |           | phabet Min-Sum decoding                                                                   | 20 |

|          |      | 2.4.2  |           | evolution analysis                                                                        | 21 |

|          |      |        | 2.4.2.1   | Expression of the input pmf $G$                                                           | 23 |

|          |      |        | 2.4.2.2   | Expression of $B^{(\ell)}$ as a function of $A^{(\ell-1)}$                                | 23 |

|          |      |        | 2.4.2.3   | Expressions of $A^{(\ell)}$ and $\tilde{G}^{(\ell)}$ as functions of $B^{(\ell)}$ and $G$ | 24 |

|          |      |        | 2.4.2.4   | Asymptotic error probability and noise threshold $\ .$ .                                  | 25 |

|          | 2.5  |        | 0         | tegies                                                                                    | 27 |

|          |      | 2.5.1  |           | scheduling                                                                                | 27 |

|          |      | 2.5.2  |           | scheduling                                                                                | 28 |

|          | 2.6  |        | 0         | algorithms to their hardware implementation                                               | 33 |

|          |      | 2.6.1  | ~         | mic choices                                                                               | 33 |

|          |      |        | 2.6.1.1   | Decoding algorithm                                                                        | 33 |

|          |      |        | 2.6.1.2   | Quantization                                                                              | 34 |

|          |      |        | 2.6.1.3   | Scheduling strategy                                                                       | 35 |

|          |      |        | 2.6.1.4   | Number of iterations                                                                      | 36 |

|          |      | 2.6.2  |           | the-art on hardware implementations                                                       | 38 |

|          |      |        | 2.6.2.1   | LDPC decoder architectures                                                                | 38 |

|          |      |        | 2.6.2.2   | High-throughput optimizations                                                             | 39 |

|          |                      | $2.6.2.3  \text{Cost optimizations}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                    | 40 |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |                      | 2.6.2.4 Cost/power/throughput trade-offs in state of the art                                                                             |    |

|          |                      | designs                                                                                                                                  | 41 |

|          | 2.7                  | Conclusion                                                                                                                               | 45 |

| 3        |                      | de-Aware Quantizer Design for Finite-Alphabet Min-Sum De-                                                                                |    |

|          | $\operatorname{cod}$ |                                                                                                                                          | 47 |

|          | 3.1                  | Introduction                                                                                                                             | 48 |

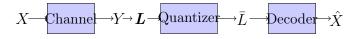

|          | 3.2                  | System model                                                                                                                             | 49 |

|          | 3.3                  | Code-Independent Quantizers                                                                                                              | 50 |

|          |                      | 3.3.1 $\operatorname{MI}_{X\bar{L}}$ : the quantizer which maximizes $I(X;\bar{L})$                                                      | 50 |

|          |                      | 3.3.2 $\operatorname{MI}_{\boldsymbol{L}\bar{\boldsymbol{L}}}$ : the quantizer which maximizes $I(\boldsymbol{L}; \bar{\boldsymbol{L}})$ | 51 |

|          | <b>.</b> (           | 3.3.3 Others                                                                                                                             | 52 |

|          | 3.4                  | Code-aware quantizers                                                                                                                    | 53 |

|          |                      | 3.4.1 Decision levels quantizer (DL)                                                                                                     | 53 |

|          |                      | 3.4.2 Gain factor quantizer (GF)                                                                                                         | 53 |

|          |                      | 3.4.3 Summary and remarks                                                                                                                | 54 |

|          | 3.5                  | Performance evaluation                                                                                                                   | 55 |

|          |                      | 3.5.1 (Semi-) Regular LDPC codes                                                                                                         | 55 |

|          |                      | 3.5.2 Irregular LDPC codes                                                                                                               | 56 |

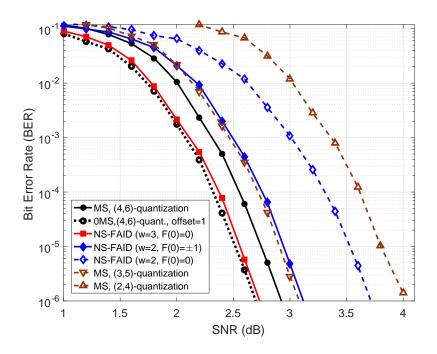

|          |                      | 3.5.3 Finite length performance of GF quantizer                                                                                          | 59 |

|          |                      | 3.5.4 Irregular LDPC code design for finite-alphabet Min-Sum de-                                                                         | 01 |

|          | 9 C                  | coder                                                                                                                                    | 61 |

|          | 3.6                  | Conclusion                                                                                                                               | 64 |

| 4        |                      | sign of High Throughput LDPC Decoder based on Imprecise                                                                                  |    |

|          |                      | set Min-Sum Decoding                                                                                                                     | 65 |

|          | 4.1                  | Introduction                                                                                                                             | 66 |

|          | 4.2                  | Proposed Partially Offset Min-Sum Decoding                                                                                               | 67 |

|          | 4.3                  | Hardware Architecture for QC-LDPC Decoders with Layered Schedul-                                                                         |    |

|          |                      | ing                                                                                                                                      | 69 |

|          |                      | 4.3.1 Hardware Architecture for Min-Sum Based Decoders                                                                                   | 69 |

|          |                      | 4.3.2 Hardware Architecture for Proposed POMS Decoder                                                                                    | 72 |

|          | 4.4                  | Imprecise Partially Offset Min-Sum Decoder                                                                                               | 74 |

|          | 4.5                  | Implementation Results                                                                                                                   | 75 |

|          | 4.6                  | Conclusion                                                                                                                               | 77 |

| <b>5</b> | Noi                  | n-Surjective Finite Alphabet Iterative Decoders                                                                                          | 79 |

|          | 5.1                  | Introduction                                                                                                                             | 80 |

|          | 5.2                  | Non-Surjective Finite Alphabet Iterative Decoders                                                                                        | 82 |

|          |                      | 5.2.1 Non-Surjective FAIDs                                                                                                               | 83 |

|          |                      | 5.2.2 Examples of NS-FAIDs                                                                                                               | 84 |

|          |                      | 5.2.3 Irregular NS-FAIDs                                                                                                                 | 85 |

|          |                      | 5.2.4 Density Evolution Analysis                                                                                                         | 86 |

|          | 5.3                  | Density Evolution Optimization of NS-FAIDs                                                                                               | 88 |

|    |                  | 5.3.1  | Optimization of Regular NS-FAIDs               | 88  |

|----|------------------|--------|------------------------------------------------|-----|

|    |                  | 5.3.2  | Optimization of Irregular NS-FAIDs             |     |

|    |                  |        | 5.3.2.1 Optimization procedure                 |     |

|    |                  |        | 5.3.2.2 Density Evolution evaluation           |     |

|    | 5.4              | Conclu | ision                                          |     |

| 6  | Low              | -Cost, | High-Throughput Hardware Architectures         | 95  |

|    | 6.1              | Introd | uction                                         | 96  |

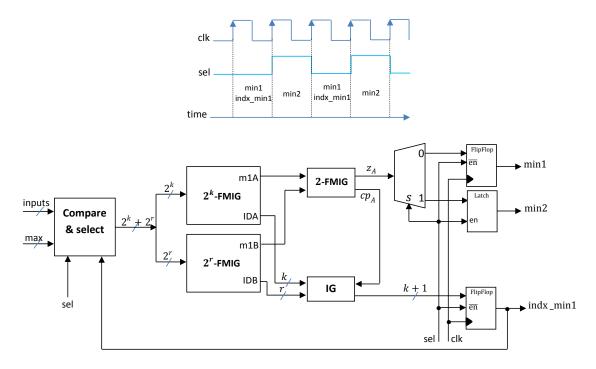

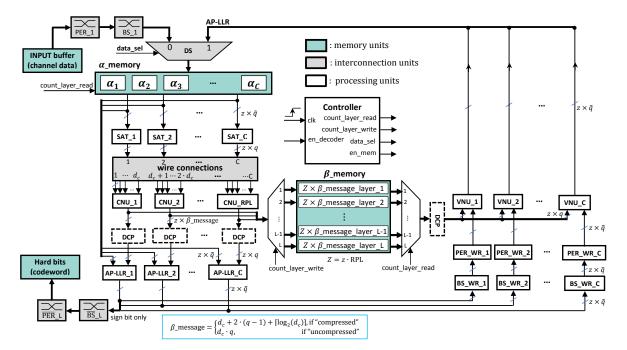

|    | 6.2              | Hardw  | vare reusing architecture                      | 97  |

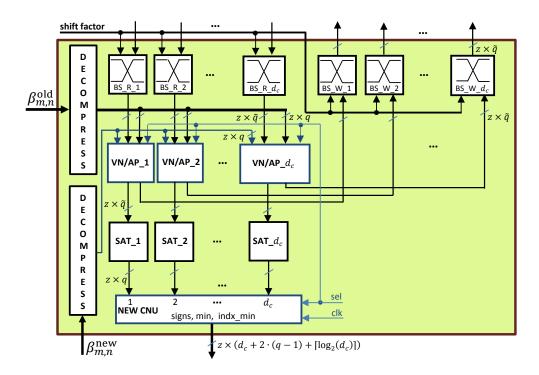

|    |                  | 6.2.1  | Description of the proposed enhancements       | 98  |

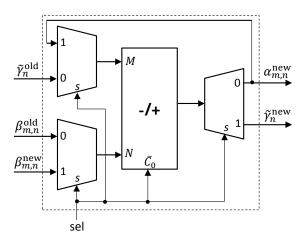

|    |                  |        | 6.2.1.1 VNU/AP-LLR Unit                        | 98  |

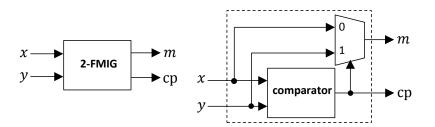

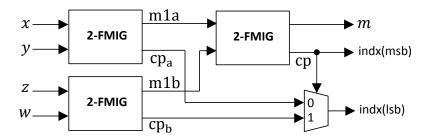

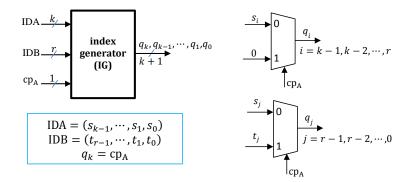

|    |                  |        | 6.2.1.2 CNU Unit                               | 100 |

|    |                  |        | 6.2.1.3 Layer Processing Split                 | 102 |

|    |                  | 6.2.2  | Case of Check-Node Irregular Codes             | 102 |

|    |                  | 6.2.3  | Implementation results                         | 103 |

|    | 6.3              | Hardw  | vare architectures with MS and NS-FAID kernels | 106 |

|    |                  | 6.3.1  | Pipelined architecture                         | 106 |

|    |                  |        | 6.3.1.1 Regular NS-FAID kernel                 | 109 |

|    |                  |        | 6.3.1.2 Irregular NS-FAID kernel               | 109 |

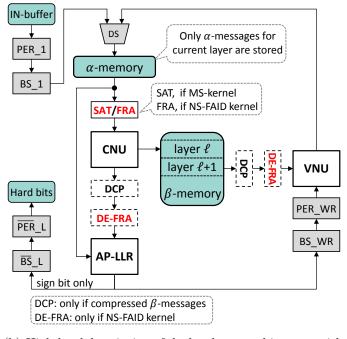

|    |                  | 6.3.2  | Full layers architecture                       | 110 |

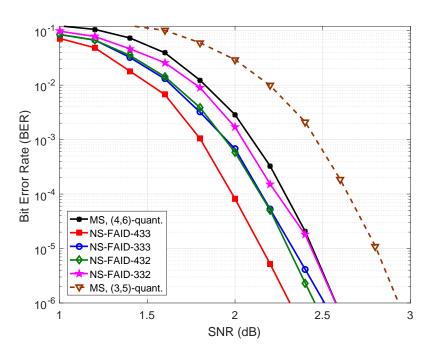

|    |                  | 6.3.3  | Implementation results                         |     |

|    |                  |        | 6.3.3.1 Regular NS-FAIDs                       | 113 |

|    |                  |        | 6.3.3.2 Irregular NS-FAIDs                     | 116 |

|    | 6.4              | Conclu | asion                                          | 119 |

| 7  | Con              | clusio | n and Perspectives                             | 121 |

|    | 7.1              | Genera | al Conclusion                                  | 121 |

|    | 7.2              | Perspe | ectives                                        | 123 |

| Bi | Bibliography 134 |        |                                                | 134 |

# List of Figures

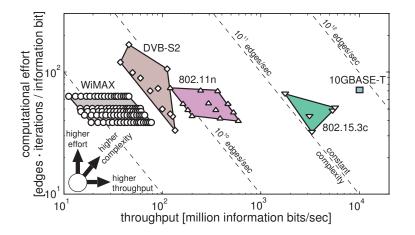

| 1.1  | Wireless roadmap [32] $\ldots$                                                                       | 1  |

|------|------------------------------------------------------------------------------------------------------|----|

| 2.1  | Example of parity-check matrix and corresponding Tanner graph                                        | 9  |

| 2.2  | Example of irregular Tanner graph                                                                    | 10 |

| 2.3  | Base matrix of QC-LDPC code                                                                          | 12 |

| 2.4  | Base matrix of WiMAX QC-LDPC code with rate of $1/2$                                                 | 12 |

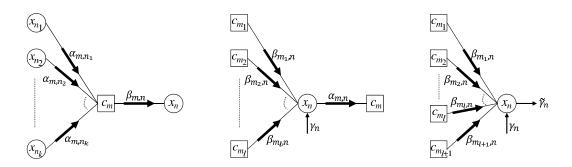

| 2.5  | Computation of extrinsic messages and of the a posteriori information                                | 14 |

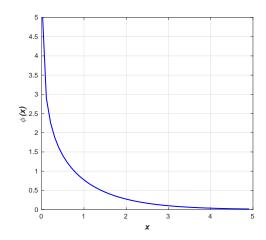

| 2.6  | $\Phi$ function, where $\Phi(x) = -\log(\tanh \frac{x}{2}), \ \forall x > 0 \ \dots \ \dots \ \dots$ | 16 |

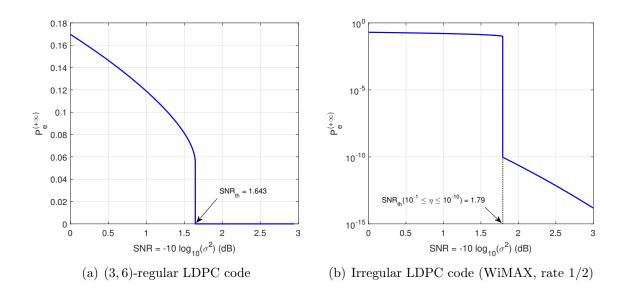

| 2.7  | Asymptotic error probability $P_e^{(+\infty)}$ as function of the SNR                                | 26 |

| 2.8  | Message-passing decoding with flooded scheduling                                                     | 28 |

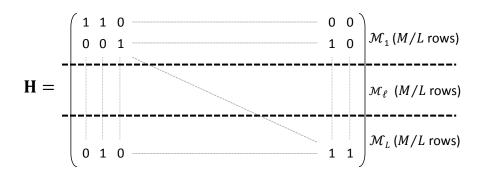

| 2.9  | Parity-check matrix with layered scheduling                                                          | 29 |

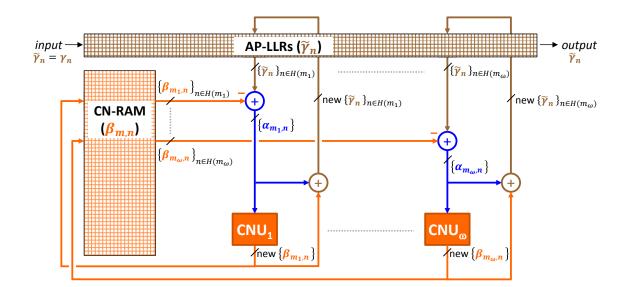

| 2.10 | Message-passing decoding with layered scheduling                                                     | 30 |

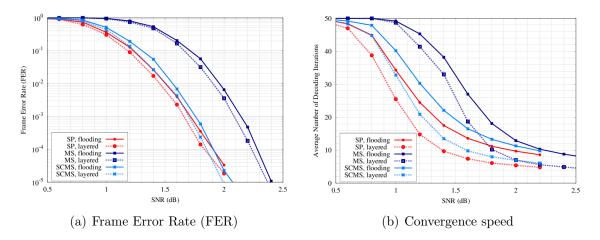

| 2.11 | Error correction performance and convergence speed of various MP                                     |    |

|      | decoder, with flooded and layered scheduling                                                         | 31 |

| 2.12 | BER performance of various decoding algorithms for $(3, 6)$ -regular                                 |    |

|      | QC-LDPC code, with code-length $N = 1296$                                                            | 34 |

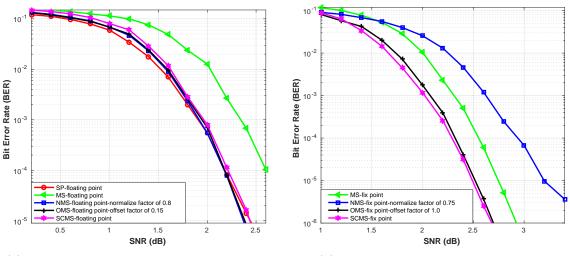

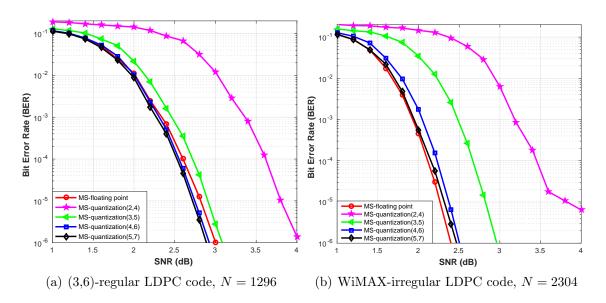

|      | Impact of the quantization to BER of LDPC decoders                                                   | 35 |

|      | Impact of the scheduling strategy to BER of LDPC decoders                                            | 36 |

|      | Impact of the number of iterations to BER of LDPC decoders                                           | 37 |

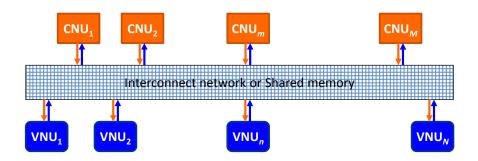

|      | General hardware architecture of an LDPC decoder                                                     | 38 |

| 2.17 | Computational effort (assuming 10 iterations) and throughput overview                                |    |

|      | of several standards employing LDPC codes [84]                                                       | 41 |

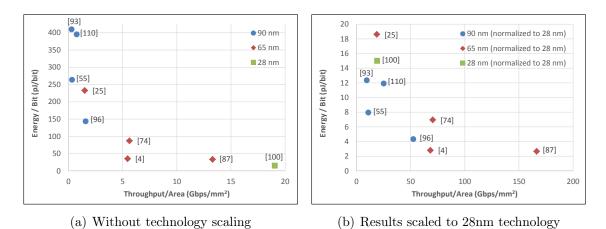

| 2.18 | Throughput vs. energy consumption trade-offs for state-of-the-art                                    | 40 |

|      | ASIC designs                                                                                         | 43 |

| 3.1  | Point to point communication system with quantized-input decoder .                                   | 49 |

| 3.2  | Decision levels of DL and GF quantizers                                                              | 58 |

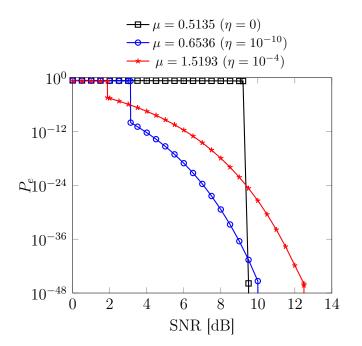

| 3.3  | Error probability $P_e$ obtained via DE using the GF quantizer                                       | 58 |

| 3.4  | BER curves for the GF quantizer with finite and infinite length codes                                |    |

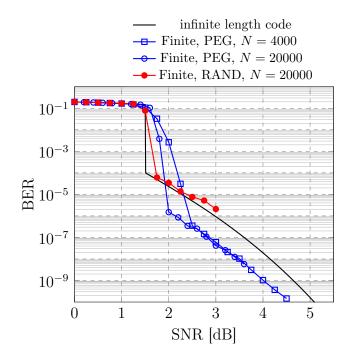

|      | when $q = 4$ , $\eta = 10^{-4}$ ( $\mu = 3.8010$ )                                                   | 60 |

| 3.5  | BER curves for the GF quantizer with finite and infinite length codes                                |    |

|      | when $q = 4$ , $\eta = 10^{-5} (\mu = 2.9582)$                                                       | 61 |

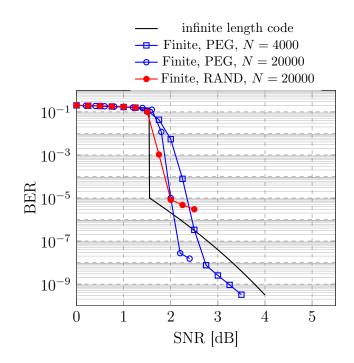

| 3.6  | Error probability $P_e$ obtained via density evolution using the GF                                  |    |

|      | quantizer as a function of the channel SNR for $\eta = 10^{-10}$ and $q \in$                         |    |

|      | $\{2,3,4\}$                                                                                          | 63 |

| 4.1  | Base matrix of the (3,6)-regular QC-LDPC code                                      | 69  |

|------|------------------------------------------------------------------------------------|-----|

| 4.2  | Block diagram for $(3, 6)$ -regular QC-LDPC decoder                                | 70  |

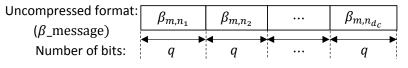

| 4.3  | Uncompressed $\beta$ -message                                                      | 70  |

| 4.4  | Compressed $\beta$ -message                                                        | 71  |

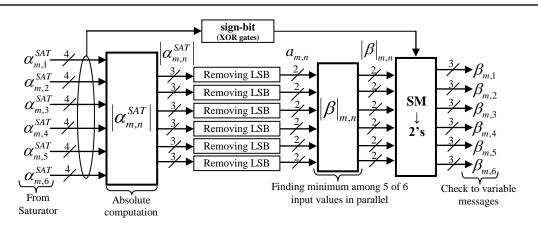

| 4.5  | Proposed CNU architecture for POMS $(d_c = 6)$                                     | 72  |

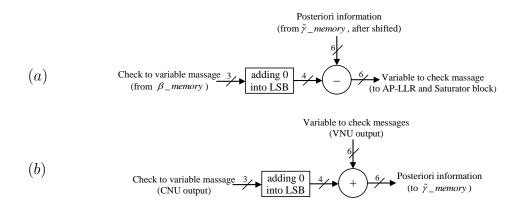

| 4.6  | VNU $(a)$ and AP-LLR $(b)$ architectures for POMS decoder                          | 73  |

| 4.7  | Diagram circuit for computing $ \beta _{m,n}$ messages in parallel $(d_c = 6)$ for |     |

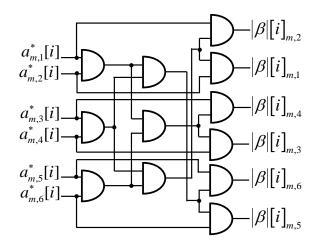

|      | I-POMS decoder                                                                     | 74  |

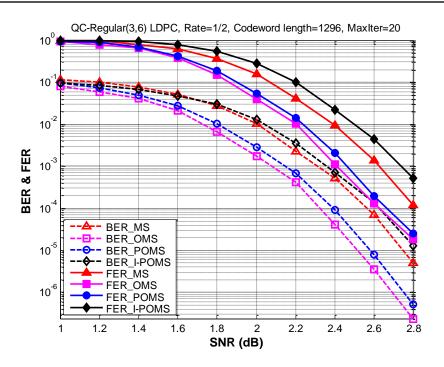

| 4.8  | Decoding performance for proposed algorithms (AWGN channel)                        | 76  |

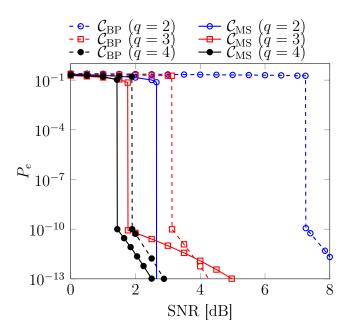

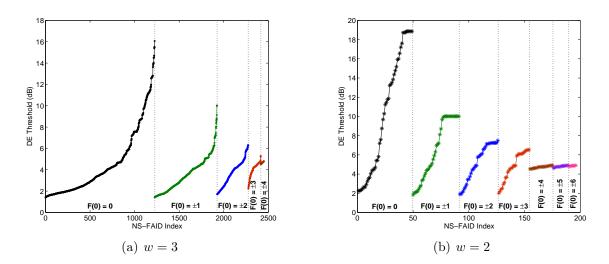

| 5.1  | Density evolution thresholds of regular $q = 4$ -bit NS-FAIDs with                 |     |

|      | w = 3 and $w = 2$                                                                  | 89  |

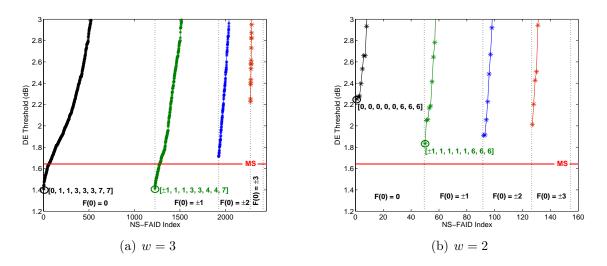

| 5.2  | Density evolution thresholds of best regular $q = 4$ -bit NS-FAIDs with            |     |

|      | w = 3 and $w = 2$                                                                  | 89  |

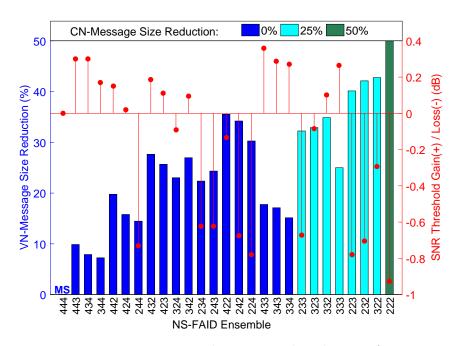

| 5.3  | Memory size reduction vs. decoding performance                                     | 93  |

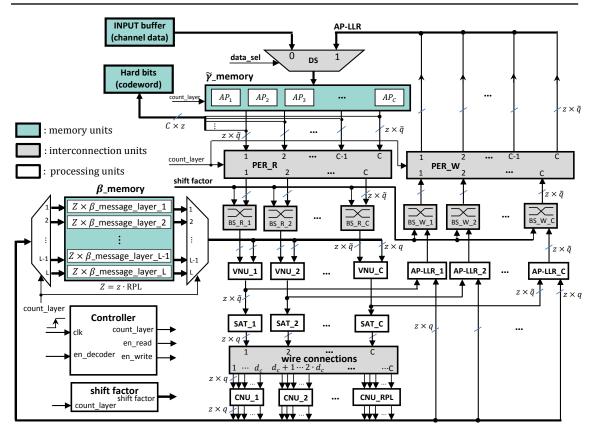

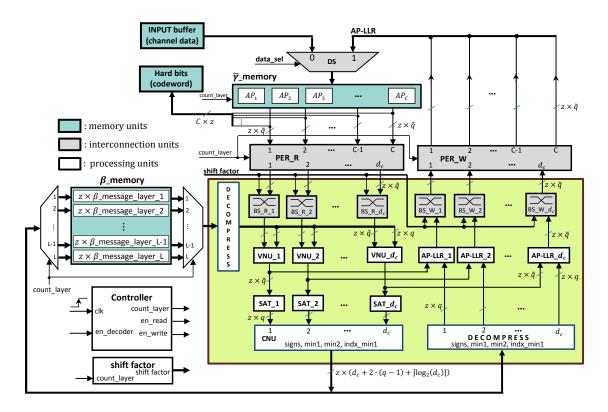

| 6.1  | Block diagram of the baseline layered MS decoder architecture                      | 98  |

| 6.2  | New processing units for the layered MS decoder architecture                       | 99  |

| 6.3  | Proposed VNU/AP-LLR processing unit                                                | 99  |

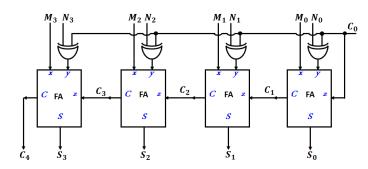

| 6.4  | Adder/subtractor block used within the VNU/AP-LLR unit $\ldots$                    |     |

| 6.5  | Block diagram of the proposed CNU architecture                                     |     |

| 6.6  | 2-FMIG architecture                                                                |     |

| 6.7  | 4-FMIG architecture                                                                |     |

| 6.8  | IG (Index Generator) architecture                                                  | 101 |

| 6.9  | Modified VNU/AP-LLR to accommodate variable check-node degree                      |     |

|      | (example for $d_{\rm cmin} = d_{\rm cmax} - 1$ )                                   | 102 |

| 6.10 | Modified CNU to accommodate variable check-node degree (example                    |     |

|      | for $d_{\rm cmin} = d_{\rm cmax} - 1$ )                                            |     |

|      | Block diagram of the proposed pipelined architecture                               | 107 |

| 6.12 | Modified base matrix of the irregular WiMAX code, rate of $1/2$ , with             |     |

|      | rows reordered [112]                                                               |     |

|      | Mapping between variable-nodes and VNUs                                            |     |

|      | Proposed full layers architecture with MS and NS-FAID kernels                      |     |

|      | BER performance of optimized NS-FAIDs for (3,6)-regular LDPC code                  | 114 |

| 6.16 | BER performance of optimized NS-FAIDs for WiMAX irregular LDPC                     |     |

|      | code                                                                               | 117 |

# List of Tables

| 2.1          | Factors impact to hardware complexity and decoding performance                                                                                                                                                                    | 37  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2          | Main characteristics of decoder architectures                                                                                                                                                                                     | 39  |

| 2.3          | Comparison of state-of-the-art ASIC designs for LDPC decoders                                                                                                                                                                     | 42  |

| 3.1          | Parameters of the quantizers under study                                                                                                                                                                                          | 54  |

| 3.2          | DE threshold of some independent-code quantizers and code-aware<br>quantizers for the family of (semi-)regular LDPC codes. The a priori                                                                                           | ~ ~ |

| 3.3          | information and the exchanged messages are quantized on $q = 2$ bits .<br>DE threshold of some independent-code quantizers and code-aware<br>quantizers for the family of (semi-)regular LDPC codes. The a priori                 | 55  |

|              | information and the exchanged messages are quantized on $q = 3$ bits .                                                                                                                                                            | 55  |

| 3.4          | DE threshold of some independent-code quantizers and code-aware quantizers for the family of irregular LDPC codes                                                                                                                 | 57  |

| 3.5          | $\eta$ -threshold of some independent-code quantizers and code-aware quan-<br>tizers for the family of irregular LDPC codes. The a priori information                                                                             |     |

| 9.0          | and the exchanged messages are quantized on $q = 2$ bits                                                                                                                                                                          | 57  |

| 3.6          | $\eta$ -threshold of some independent-code quantizers and code-aware quan-<br>tizers for the family of irregular LDPC codes. The a priori information<br>and the exchanged messages are quantized on $q = 3$ bits $\ldots \ldots$ | 57  |

| 3.7          | $\eta$ -threshold of some independent-code quantizers and GF quantizer<br>for the family of irregular LDPC codes                                                                                                                  | 59  |

| 3.8          | Good degree distribution pairs of rate one-half with variable node degrees fixed to 2, 3, 4 and 11 for $q = 2$ , 3 and 4, when $\eta = 10^{-10}$ .                                                                                | 62  |

| 4.1          | CNU hardware resources for MS, OMS ( $\delta = 1$ ), POMS, and I-POMS decoders ( $d_c = 6$ )                                                                                                                                      | 75  |

| 4.2          | Implementation results for MS, OMS ( $\delta = 1$ ), POMS, and I-POMS                                                                                                                                                             |     |

|              | decoders                                                                                                                                                                                                                          | 75  |

| 5.1          | Examples of 4-bit framing functions of weight $W = 4$                                                                                                                                                                             | 84  |

| $5.2 \\ 5.3$ | Best NS-FAIDs for (3, 6)-regular LDPC codes                                                                                                                                                                                       | 89  |

| 0.0          | mized Irregular NS-FAIDs                                                                                                                                                                                                          | 92  |

| 5.4          | LUTs used by NS-FAIDs in Table 5.3                                                                                                                                                                                                | 92  |

| 6.1          | Parameters of the QC-LDPC codes                                                                                                                                                                                                   | 103 |

| 6.2 | Comparison between enhanced and baseline architectures for $(3, 6)$ -   |

|-----|-------------------------------------------------------------------------|

|     | regular and WiMAX QC-LDPC codes                                         |

| 6.3 | Comparison between the proposed enhanced architecture and state-        |

|     | of-the-art implementations for the WiMAX QC-LDPC code $\ldots$ . 105    |

| 6.4 | FPGA Post-PAR Implementation Results on Zynq-7000                       |

| 6.5 | Comparison of FPGA implementations for $(3, 6)$ -regular LDPC codes 115 |

| 6.6 | ASIC post-synthesis implementation results on 65nm-CMOS technol-        |

|     | ogy for optimized (3,6) regular NS-FAIDs                                |

| 6.7 | ASIC post-synthesis implementation results on 65nm-CMOS technol-        |

|     | ogy for optimized irregular NS-FAIDs                                    |

| 6.8 | Comparison between the proposed NS-FAID and state-of-the-art im-        |

|     | plementations for the WiMAX QC-LDPC code                                |

# Glossary

| AP             | A Posteriori                                               |

|----------------|------------------------------------------------------------|

| AP-LLR         | A Posteriori Log-Likelihood Ratio                          |

| ASIC           | Application-Specific Integrated Circuit                    |

| AWGN           | Additive White Gaussian Noise                              |

| BEC            | Binary Erasure Channel                                     |

| BER            | Bit Error Rate                                             |

| $\mathbf{BF}$  | Bit-Flipping                                               |

| <b>BI-AWGN</b> | Binary-Input Additive White Gaussian Noise                 |

| BP             | Belief-Propagation                                         |

| BPSK           | Binary Phase-Shift Keying                                  |

| BRAM           | Block RAM                                                  |

| BSC            | Binary Symmetric Channel                                   |

| CLA            | Carry Lookahead Adder                                      |

| CMOS           | Complimentary Metal Oxide Semiconductor                    |

| $\mathbf{CN}$  | Check Node                                                 |

| CNU            | Check Node Unit                                            |

| DE             | Density Evolution                                          |

| DL             | Decision Level                                             |

| DVB-S2         | Digital Video Broadcasting - Satellite - Second Generation |

| EE             | Energy Efficiency                                          |

| FAID           | Finite Alphabet Iterative Decoder                          |

| FEC            | Forward Error Correction                                   |

|                |                                                            |

| FER            | Frame Error Rate                                 |

|----------------|--------------------------------------------------|

| FMIG           | First Minimum and Index Generator                |

| FPGA           | Field-Programmable Gate Array                    |

| $\mathbf{GF}$  | Gain Factor                                      |

| HUE            | Hardware Usage Efficiency                        |

| HW             | Hardware                                         |

| IG             | Index Generator                                  |

| I-POMS         | Imprecise Partially Offset Min-Sum               |

| LDPC           | Low-Density Parity-Check                         |

| LLR            | Logarithmic Likelihood Ratio                     |

| LSB            | Least Significant Bit                            |

| LUT            | Look-Up Table                                    |

| MAP            | Maximum A Posteriori                             |

| MI             | Mutual Information                               |

| ML             | Maximum Likelihood                               |

| MP             | Message-Passing                                  |

| $\mathbf{MS}$  | Min-Sum                                          |

| MSB            | Most Significant Bit                             |

| NEE            | Normalized Energy Efficiency                     |

| NMS            | Normalized Min-Sum                               |

| NS-FAID        | Non-Surjective Finite Alphabet Iterative Decoder |

| NTAR           | Normalized Throughput to Area Ratio              |

| OMS            | Offset Min-Sum                                   |

| PAR            | Place-and-Route                                  |

| $\mathbf{pdf}$ | Probability density function                     |

| PEG            | Progressive Edge Growth                          |

| $\mathbf{pmf}$ | Probability mass function                        |

| POMS          | Partially Offset Min-Sum                        |

|---------------|-------------------------------------------------|

| $\mathbf{QC}$ | Quasi-Cyclic                                    |

| RAM           | Random Access Memory                            |

| RPL           | Rows Per Layer                                  |

| SCMS          | Self-Corrected Min-Sum                          |

| SIPO          | Serial Input Parallel Output                    |

| SNR           | Signal-to-Noise Ratio                           |

| SP            | Sum-Product                                     |

| TAR           | Throughput-to-Area Ratio                        |

| $\mathbf{TS}$ | Tree Structure                                  |

| $\mathbf{VN}$ | Variable Node                                   |

| VNU           | Variable Node Unit                              |

| WiFi          | Wireless Fidelity                               |

| WiGig         | WIreless GIGabit                                |

| WiMAX         | WorldWide Interoperability for Microwave Access |

| WPAN          | Wireless Personal Area Network                  |

## Notation

#### [Related to parity-check matrix and Tanner graphs]

H: parity-check matrix

M: number of rows of  $\mathbf{H}$

N: number of columns of  $\mathbf{H}$

$K = N - \operatorname{rank}(\mathbf{H})$ : dimension of  $\mathbf{H}$

$$r = \frac{K}{N}$$

: coding rate

**B**: base matrix (used for QC-LDPC codes)

R: number of rows of  ${\bf B}$

C: number of columns of **B**

RPL: number of rows per layer

- L = R/RPL: number of decoding layers

- z: expansion factor of  $\mathbf{B}$

- $Z = z \times \text{RPL}$ : number of parity checks within one decoding layer, and reffered to as the parallelism degree (of the hardware architecture)

$\mathcal{H}$ : Tanner graph associated with  $\mathbf{H}$

$n \in \{1, 2, \ldots, N\}$ : a variable-node of  $\mathcal{H}$

$m \in \{1, 2, \ldots, M\}$ : a check-node of  $\mathcal{H}$

- $\mathcal{H}(n)$ : a set of check-nodes connected to the variable-node n, also referred to as the set of neighbor check-nodes of n

- $\mathcal{H}(m)$ : a set of variable-nodes connected to the check-node m, also referred to as the set of neighbor variable-nodes of m

- $d_n = |\mathcal{H}(n)|$ : number of check-nodes connected to n also referred to as the degree of the variable-node n

$d_m = |\mathcal{H}(m)|$ : number of variable-nodes connected to m also referred to as the degree of the check-node m

#### [Related to channel and transmitted/received words]

$\sigma^2$ : noise variance (BI-AWGN model)

$\mathcal{X}$ : channel input alphabet

$\mathcal{Y}$ : channel output alphabet

$\underline{x} = (x_1, \ldots, x_N) \in \mathcal{X}^N$ : transmitted

$\hat{\boldsymbol{x}} = (\hat{x}_1, \dots, \hat{x}_N)$ : estimated codeword

$\boldsymbol{y} = (y_1, \dots, y_N) \in \mathcal{Y}^N$ : received word

$P_n = \Pr(x_n = 1 \mid y_n)$ : probability of the transmitted bit  $x_n$  being equal to 1, conditional on the received value  $y_n$

$$\boldsymbol{L}_n = \log \frac{\Pr(x_n = 0 \mid y_n)}{\Pr(x_n = 1 \mid y_n)} = \log \frac{1 - \boldsymbol{P}_n}{\boldsymbol{P}_n} : \text{LLR of the transmitted bit } x_n, \text{ conditional on the received value } y_n$$

#### [Related to message-passing decoding]

$\gamma_n$ : a priori information of the decoder concerning variable-node n

$\tilde{\gamma}_n$ : a posteriori information provided by the decoder, concerning variable node n

$\alpha_{m,n}$ : message sent from variable-node n to check-node m

$\beta_{m,n}$ : message sent from check-node m to variable-node n

$\nu \in ]0,1[$ : normalization (scaling) factor used for Normalized Min-Sum decoding

$\delta > 0$ : offset factor used for Offset Min-Sum decoding

#### [Related to quantization]

$\varphi :$  quantization map

$\mu > 0$ : gain factor used to scale the received signal

q: number of bits for representation of a priori information and exchanged messages

$\tilde{q}$ : number of bits for representation of a posteriori information

- $\mathcal{M} = \{-Q, \ldots, -1, 0, +1, \ldots, +Q\}$ , where  $Q = 2^{q-1} 1$ , is the alphabet of the a priori information and exchanged messages.

- $\tilde{\mathcal{M}} = \{-\tilde{Q}, \dots, -1, 0, +1, \dots, +\tilde{Q}\}$ , where  $\tilde{Q} = 2^{\tilde{q}-1} 1$ , is the alphabet of the a posteriori information.

#### F: framing function used for NS-FAIDs decoding

W: weight of F, *i.e.*, the number of distinct entries in the vector  $[|F(0)|, F(1), \ldots, F(Q)]$

$w = \lceil \log_2(W) \rceil + 1$ : framing bit-length

## Chapter 1

## Introduction

### 1.1 Context and Motivations

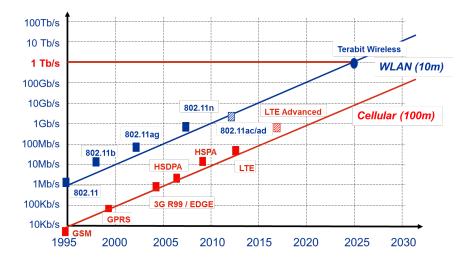

There has been a significant growth in the volume of mobile data traffic in recent years. This is due to proliferation of smart phones and other mobile devices that support a wide range of broadband applications and services. It is projected in [23] that the volume of the so called smart traffic will be 96% of the global data traffic by 2018, and among this more than 50% data will be routed using the WiFi access points or femtocells, while the remaining will be covered by the cellular networks. This tendency is confirmed by the multi-Gigabit/s data rate target of the current evolution of WLAN standards (IEEE802.11ac/ad), or of the 5th generation of cellular networks (5G). Moreover, short range communications in the extremely high frequency spectrum (from 30 to 300 Gigahertz) are expected to reach throughput from 100 Gigabit/s to 1 Terabit/s (Figure 1.1).

Figure 1.1: Wireless roadmap [32]

The increasing demand of massive data rates in wireless communications, supported by the use of very large bandwidths, will result in stringent, applicationspecific, requirements in terms of both throughput and latency. They will necessitate significantly higher processing speed of the baseband signal, as compared to conventional solutions, which is especially challenging for the Forward Error Correction (FEC) mechanism. Indeed, due to the erroneous nature of communication channels, FEC mechanisms are essential to any communication system, no matter the way the information is transported, for instance using a point-to-point, multicast, or broadcast technology, a wired or wireless link, and a terrestrial, satellite-based or hybrid infrastructure. However, these error-correction mechanisms require intensive computing tasks, consuming a large amount of hardware resources and energy.

The conventional approach to increase throughput is to use massively parallel architectures. In this context, Low-Density Parity-Check (LDPC) codes are recognized as the foremost solution, due to the intrinsic capacity of their decoders to accommodate various degrees of parallelism. They have found extensive applications in modern communication systems, due to their excellent decoding performance, high throughput capabilities, and power efficiency, and have been adopted in several communication standards, such as IEEE 802.11n (WiFi), IEEE 802.16e (WiMAX), IEEE 802.15.3c (WPAN), ETSI DVB-S2/T2/C2. More recently, to support increasing throughput requirements in wireless standards, LDPC codes have been adopted by IEEE 802.11ac (WiFi evolution) and IEEE 802.11ad (WiGig), as well as by the 3rd Generation Partnership Project (3GPP) for enhanced Mobile BroadBand (eMBB) 5G data channels [2].

In this context, the main objective of this thesis is to contribute to the development of very high-throughput, yet cost-effective, LDPC decoder designs, so that to address in the most suitable way the new generation of communication systems, requiring increased data rates and reduced energy footprint. The approach proposed in this thesis, is to exploit the robustness of message-passing LDPC decoders to computing inaccuracies. The idea is actually inspired by the approximate computing paradigm: the computation returns a possibly inaccurate result, for a situation where an approximate result is sufficient for a specific purpose [70]. Another closely related parading is the one of approximate storage: instead of storing data values exactly, they are stored approximately, e.g., by truncating the lowest significant bits. In this thesis, the use of approximate computing and storage in message passing LDPC decoders is seen as an enabler for throughput and cost optimization. By modeling such approximations in a specific way, we are actually able to address the multi-objective optimization of the design, with respect to cost, throughput, and error correction performance. The main contributions of the thesis will be outlined in the next section.

### **1.2** Main Contributions and Thesis Outline

This thesis targets the design of cost-effective, high-throughput LDPC decoders, so as to enable a smooth transition towards the new generation of multi-Gigabit/s communication systems. The main novelty of the research comes from the expansion of the design space, so as to harness the potential of approximate computing and storage. In this line of research, the thesis is aimed at (i) designing novel decoder architectures based on the integration of approximate computing and storage units, while still providing reliable error protection, and (ii) providing new approaches for the multi-objective optimization of the design with respect to cost, throughput, and error correction performance.

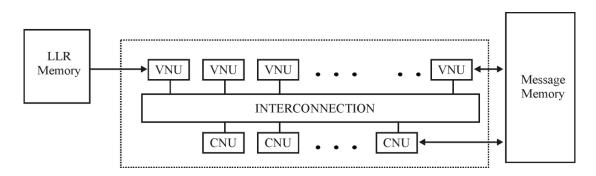

Typical LDPC decoder architectures consist of three main building blocks: memory, interconnects, and processing units. One important characteristic of LDPC decoders is that the memory and interconnect blocks usually dominate the overall area/power/delay performance of the hardware design. This emphasizes the potential benefits of approximate storage techniques, as they may significantly reduce the memory size requirements. Besides, as a side benefit, such mechanisms may also reduce the footprint of the routing network, which carries messages from the memory to the processing units.

To avoid degrading the error correction performance of the decoder, approximate storage techniques should be investigated along with the use of novel processing units, capable to compensate the information loss due to approximate storage. Such processing units are necessarily "approximate versions" of the conventional ones, but they can be subject to further circuit-level approximations, *e.g.*, by removing some specific signals from the implementing circuit.

Finally, it appears clear that approximate computing and storage techniques must be investigated in conjunction with the quantization rules for computing the finite-alphabet information supplied to the decoder, which actually determines the starting point of the iterative decoding process.

The main contributions of this thesis are summarized below, along with the thesis outline.

#### Chapter 2: Low-Density Parity-Check Codes and Message-Passing Decoders

Chapter 2 provides a brief introduction to LDPC codes and Message-Passing (MP) decoders. We first introduce the bipartite graph representation of LDPC codes and the principle of iterative MP decoding algorithms. Then we focus on some specific decoding algorithms that will be used in this thesis, namely the Min-Sum (MS) and several MS-based algorithms. The asymptotic analysis of finite alphabet MS decoders, based on the density evolution method, is also discussed.

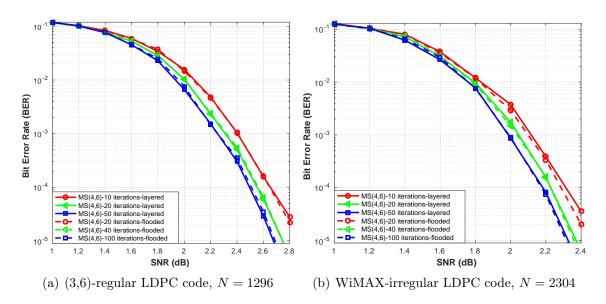

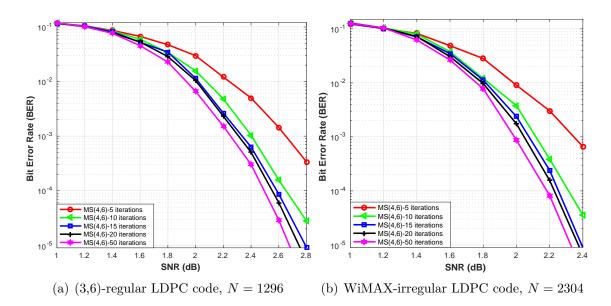

We further investigate the main algorithmic and architectural choices that impact the decoding performance and the hardware complexity of LDPC decoders. In particular, we discuss different scheduling strategies for MP decoders and their impact on the hardware architecture. Finally, several state-of-the-art approaches on low-cost, high-throughput hardware implementations are also reviewed in this chapter.

#### Chapter 3: Code-Aware Quantizer Design for Finite-Alphabet Min-Sum Decoders

Classically, the quantization of the soft information supplied to a finite-alphabet decoder is chosen to optimize a certain criterion which does not depend on the characteristics of the existing code. Chapter 3 investigates quantizers that are both code and decoder aware: such quantizers optimize the density evolution noise threshold of a given decoder and a given ensemble of LDPC codes. Throughout this chapter the LDPC decoder under consideration is the finite-alphabet MS decoder, and thus we shall simply refer to such quantizers as code-aware quantizers.

We propose a code-aware quantizer with lower complexity than that obtained by optimizing all decision levels and approaching its performance, for few quantization bits. We show that code-aware quantizers outperform code-independent quantizers in terms of noise threshold for both regular and irregular LDPC codes. To overcome the error floor behavior of LDPC codes, we propose the design of the quantizer for a target error probability at the decoder output. The results show that the quantizer optimized to get a zero error probability could lead to a very bad performance for practical range of signal to noise ratios.

We further propose to design jointly irregular LDPC codes and code-aware quantizers for the finite-alphabet MS decoder. We show that they achieve significant decoding gains with respect to LDPC codes designed for infinite-alphabet belief propagation decoding, but decoded by finite-alphabet MS.

Finally, we note that the proposed code-aware quantizer can easily be adapted to the MS-based decoders investigated in the next chapters of this thesis. This will allow the optimization of the code-aware quantizer jointly with the integration of approximate computing and storage techniques into the MS decoder.

#### Chapter 4: Design of High Throughput LDPC Decoder based on Imprecise Offset MS Decoding

Chapter 4 proposes two new decoding algorithms and hardware implementations, obtained by introducing two levels of impreciseness in the Offset MS (OMS) decoding: the Partially OMS (POMS), which performs only partially the offset correction, and the Imprecise Partially OMS (I-POMS), which introduces a further level of impreciseness in the check-node processing unit. We show that they allow significant reduction in the memory (25% with respect to the conventional OMS) and interconnect, and we further propose a cost-efficient check-node unit (CNU) architecture, yielding a cost reduction of 56% with respect to the conventional CNU architecture.

We further implement FPGA-based layered decoder architectures using the proposed algorithms as decoding kernels, for a (3,6)-regular Quasi-Cyclic LDPC code of length 1296 bits, and evaluate them in terms of cost, throughput and decoding performance. Implementation results on Xilinx Virtex 6 FPGA device show that they can achieve a throughput between 1.95 and 2.41 Gbps for 20 decoding iterations (48% to 83% increase with respect to OMS), while providing decoding performance close to the OMS decoder, despite the impreciseness introduced in the processing units.

#### Chapter 5: Non-Surjective Finite Alphabet Iterative Decoders

Chapter 5 introduces a new family of Non-Surjective Finite Alphabet Iterative Decoders (NS-FAIDs), characterized by specific processing rules, which can be theoretically analyzed and optimized for different trade-offs between hardware cost and error correction performance. The proposed approach builds upon the approximate storage technique, and allows storing the exchanged messages using a smaller precision than the processing units. It is also shown to provide a unified approach for several designs previously proposed in the literature.

NS-FAIDs are optimized by density evolution for regular and irregular LDPC codes, and are shown to provide different trade-offs between hardware complexity and decoding performance. In particular, we show that optimized NS-FAIDs may yield significant reductions of the memory size requirements, while providing even better or only slightly degraded error correction performance with respect to other MS-based decoders.

#### Chapter 6: Low-Cost, High-Throughput Hardware Architectures

Chapter 6 proposes three Quasi-Cyclic (QC)-LDPC decoder architectures targeting low-cost, high-throughput and efficient use of the hardware resources. All of the proposed architectures implement layered scheduled decoding with fully parallel processing units.

The first architecture is an enhanced version of the architecture introduced in Chapter 4. It is based on a specific design of the datapath processing units (VNUs, CNUs, and AP-LLR units) that allow an efficient reuse of the hardware resources, thus yielding significant cost reduction.

In the second architecture, efficient use of the hardware resources is ensured by pipelining the datapath, which also allows increasing the operating frequency, thus increasing the achieved throughput. However, the use of pipelining imposes specific constraints on the decoding layers, in order to ensure proper execution of the layered decoding process. Finally, the third architecture does not make use of pipelining, but allows maximum parallelism to be exploited through the use of full decoding layers, thus resulting in significant increase in throughput.

The second and third architectures may accommodate both MS and NS-FAID decoding kernels. Thus, to validate the promises of the NS-FAID approach, both MS and NS-FAID decoding kernels are integrated into each of these architectures, and compared in terms of throughput and resources consumption. Implementation

results on both FPGA and ASIC platforms show that regular and irregular NS-FAIDs allow significant improvements in terms of both throughput and hardware resources consumption, as compared to the conventional MS solution, with even better or only slightly degraded decoding performance.

We use the Throughput to the Area Ratio (TAR) metric, expressed in Gbps/mm<sup>2</sup>, to capture the performance of the proposed designs in terms of both throughput and cost. ASIC synthesis results targeting a 65nm CMOS technology, for our designs achieving the highest TAR performance, are summarized below:

- For irregular QC-LDPC codes, with rate 1/2 and code-length 2304 bits, specified by the IEEE 802.16e (WiMAX) standard, proposed designs achieve a TAR metric up to 2.7 Gbps/mm<sup>2</sup> at 20 decoding iterations, corresponding to a Normalized TAR of 54 Gbps/mm<sup>2</sup>/iteration (Normalized TAR corresponds to the TAR value for one decoding iteration).

- For (3, 6)-regular QC-LDPC codes, with rate 1/2 and code-length 1296 bits, proposed designs achieve a TAR metric up to 6.1 Gbps/mm<sup>2</sup> at 20 decoding iterations, corresponding to a Normalized TAR of 122 Gbps/mm<sup>2</sup>/iteration.

#### **Chapter 7: Conclusion and Perspectives**

Chapter 7 summarizes the results obtained in this thesis, and provides perspectives for future works.

## Chapter 2

# Low-Density Parity-Check Codes and Message-Passing Decoders

This chapter provides a brief introduction to Low Density Parity Check (LDPC) codes and Message-Passing (MP) decoders. We first introduce the bipartite graph representation of LDPC codes and the principle of iterative MP decoding algorithms. Then we focus on some specific decoding algorithms that will be used in this thesis, namely the Min-Sum (MS) and several MS-based algorithms. The asymptotic analysis of finite alphabet MS decoders, based on the density evolution method, is also discussed.

We further investigate the main algorithmic and architectural choices that impact the decoding performance and the hardware complexity of LDPC decoders. In particular, we discuss different scheduling strategies for MP decoders and their impact on the hardware architecture. Finally, several stateof-the-art approaches on low-cost, high-throughput hardware implementations are also reviewed in this chapter.

# 2.1 Introduction

This chapter aims to answer three main questions such as What are LDPC codes? Why are we interested in them? and How do they work? LDPC codes have been introduced by Gallager in his doctoral thesis in 1962 [35, 36], as a class of linear Forward Error Correction (FEC) codes defined by sparse parity-check matrices, which can be advantageously decoded by iterative message-passing (MP) decoders. Unlike other linear codes introduced at that time (e.g., Hamming, BCH, Reed-Solomon, etc.), which are short codes, based on algebraic constructions and with known error correction capacity, LDPC codes are usually long and often constructed pseudo-randomly, with only a probabilistic notion of their expected error correction performance [50]. Because of the computational effort in implementing encoder and decoder at that time, LDPC codes were mostly ignored for a long time. In 1996, they were rediscovered by Mackay [65], after the power of iterative decoding techniques had been also confirmed by the discovery of Turbo codes [6]. Since then, they have been developed rapidly and attracted a lot of research interest, especially focused on the analysis of iterative decoding algorithms [20, 22, 28, 58, 82, 83], as well as techniques developed for code construction and optimization [34, 42, 53].

Nowadays, LDPC codes have found extensive applications in modern communication systems due to their excellent decoding performance [21, 82, 83], as well as their advantages related to hardware implementations, such as low-cost [8, 10, 29], high-throughput capabilities [49, 52, 110, 111], and power efficiency [66, 75, 103]. Thus, LDPC codes are gradually replacing other well-established FEC schemes [84]. For instance, they have been adopted in several recent communication standards, such as 802.11n (Wi-Fi) [44], 802.11ad (WiGig) [43], 802.16e (WiMAX) [46], 802.15.3c (WPAN) [45], and DVB-S2 [31], and are being considered for a range of application areas, from optical networks to digital storage [50]. Moreover, LDPC codes have been proposed as a potential candidate for 5G cellular system [68].

# 2.2 LDPC Codes

### 2.2.1 Definition, Tanner graphs

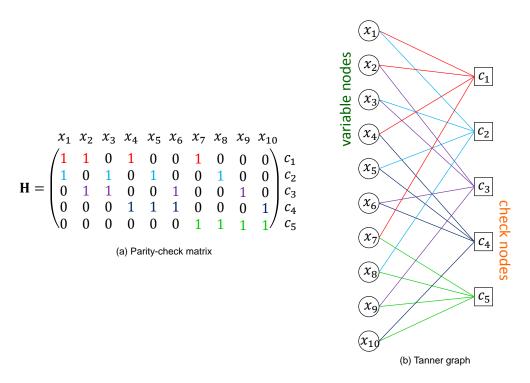

An LDPC code is a linear block code defined by a (M, N) sparse parity-check matrix denoted by **H**. As their name suggests, sparse or low-density means that the paritycheck matrix contains only a few 1's in comparison to the amount of 0's. This sparseness of **H** is essential for an iterative decoding complexity that increases only linearly with the code length. Figure 2.1(a) illustrates an example of parity-check matrix. Of course, the matrix in this example cannot be really called low-density. In order to satisfy low-density property, the size of parity-check matrix should usually be very large, of several hundreds of thousands of columns.

Figure 2.1: Example of parity-check matrix and corresponding Tanner graph

The N columns of the parity-check matrix **H** correspond to coded bits, and the M rows correspond to parity-check equations. A vector  $\underline{\boldsymbol{x}} = (x_1, \ldots, x_N) \in \{0, 1\}^N$  is a codeword if and only if:

$$\mathbf{H}\underline{\boldsymbol{x}}^{\mathbf{T}} = \mathbf{0} \pmod{2} \tag{2.1}$$

where **0** is the length-*M* all zeros vector and  $\underline{x}^T$  denotes the transpose of  $\underline{x}$ .

Assuming that the parity-check matrix  $\mathbf{H}$  is full rank (*i.e.*, rank( $\mathbf{H}$ ) = M) and the code is systematic, then any length-N codeword is comprised of K = N - M information bits and M parity bits. The fraction r = K/N is called the *coding rate* of the code. In other words, it characterizes the amount of redundancy added by the error correction code.

Figure 2.2: Example of irregular Tanner graph

The parity-check matrix can also be represented by a bipartite graph, denoted by  $\mathcal{H}$ , introduced by Tanner [94], and therefore usually referred to as *Tanner graph* of the code. The bipartite graph consists of two sets of nodes, namely the set of variable-nodes, corresponding to coded bits (or columns of **H**), and the set of checknodes correspond to parity-check equations (or rows of **H**). The edges connecting variable and check nodes correspond to the 1's entries of **H**. This bipartite graph representation is very useful for describing the message-passing decoding algorithms (see Section 2.3). Figure 2.1(b) shows the bipartite Tanner graph representation of the parity-check matrix from Figure 2.1(a).

Now, we will answer the question why we are interested in LDPC codes. The main reason comes from the fact that they are able to achieve excellent decoding performance. In 2001, Richardson and co-authors showed that irregular LDPC codes can be optimized such that to approach the Shannon limit [82, 83]. They showed that it is possible to construct irregular LDPC codes, with decoding performance at only 0.0045 dB from the Shannon limit [21].

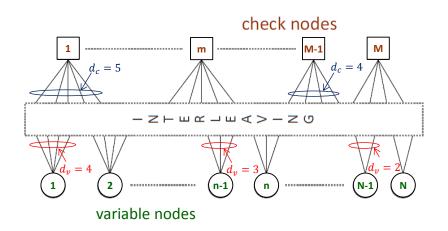

It is worth noting that LDPC codes can be regular and irregular, depending on their variable and check node degrees. The node degree is defined as the number of adjacent edges connected to that node. Variable-node degrees will be denoted by  $d_v(n)$ , and check-node degrees by  $d_c(m)$ . An example is shown in Figure 2.2. It can be easily seen that variable node-1 has 4 edges connected to, so it is of degree 4. Similarly, variable node-(n - 1) and variable node-(N - 1) have degrees equal to 3 and 2, respectively. In the same manner, for check-nodes, it can be observed that check node-1 is of degree 5, and check node-(M - 1) is of degree 4.

An LDPC code is said to be regular if all variable-nodes have the same degree  $d_v$ , and all check-nodes have the same degree  $d_c$ . Otherwise, the code is said to be irregular. It is worth noticing that most of the practical constructions of irregular LDPC codes are actually irregular on variable-node degrees, but regular or semi-regular in check-node degrees (semi-regular means that all check-node degrees take on two consecutive values). The irregularity of an LDPC code can be defined by the edge perspective degree-distributions polynomials, given in Eq. (2.2).

$$\lambda(x) = \sum_{d>1} \lambda_d x^{d-1}, \quad \rho(x) = \sum_{d>1} \rho_d x^{d-1}$$

(2.2)

where  $\lambda_d$  denotes the fraction of edges connected to variable-nodes of degree d, and  $\rho_d$  denotes the fraction of edges connected to check-node of degree d.

Finally, it is important to mention that irregularity allows more degree of freedom for code design, and carefully designed irregular LDPC codes have better decoding performance than their regular counterparts, as long as the decoding performance in the waterfall region is concerned (assuming the same codeword length). However, they also exhibit higher error floors compared to regular LDPC codes, usually attributed to fact that irregular graphs are more prone to the occurrence of small topological structures, discussed below, and known to be responsible for the failures of iterative message passing decoders.

The waterfall region corresponds to the Signal to Noise Ratio (SNR) region where the Bit Error Rate (BER) curve steadily decreases with increasing SNR. However, graph-based iteratively decodable codes, such as LDPC codes, there is a point after which the BER curve does not fall as quickly as before, in other words, there is a region in which the BER performance flattens. This region is referred to as the error floor region. The error floor phenomenon is directly attributed to small topological structures in the bipartite graph, such as stopping sets [28] (BEC channel) or trapping sets [80], near codewords [64], pseudo codewords [97] (BSC and AWGN channel). Irregular LDPC codes are more prone to such structures, mainly due variable-nodes of low degree. Besides, quantization effects also cause the error floor [113].

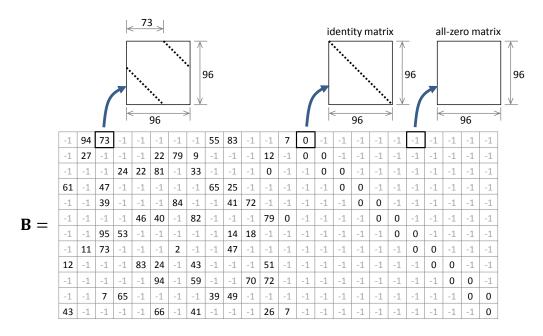

### 2.2.2 Quasi-Cyclic LDPC codes

Quasi-cyclic (QC) LDPC codes [34] are a class of structured LDPC codes, widely used in practical applications. They are defined by a base matrix **B** of size  $R \times C$ , with integer entries  $b_{i,j} \ge -1$ , where  $i \in \{1, \ldots, R\}$  and  $j \in \{1, \ldots, C\}$ , as shown in Figure 2.3. The parity-check matrix **H** is obtained by expanding the base matrix **B** by an expansion factor z. Thus, each entry of **B** is replaced by a square matrix of size  $z \times z$ , defined as follows:

- entries  $b_{i,j} = -1$  are replaced by the all-zero matrix,

- entries  $b_{i,j} \ge 0$  are replaced by a circulant matrix, obtained by right-shifting the identity matrix by  $b_{i,j}$  positions.

It follows that the parity-check matrix **H** is of size  $M \times N$ , with  $M = z \times R$  rows and  $N = z \times C$  columns.

Figure 2.4 gives an example of base matrix of size  $R \times C = 12 \times 24$ , and expansion factor z = 96 for WiMAX QC-LDPC code with rate of 1/2.

$$\mathbf{B} = \begin{pmatrix} b_{1,1} & b_{1,2} & \cdots & b_{1,C} \\ b_{2,1} & b_{2,2} & \cdots & b_{2,C} \\ \vdots & \vdots & \ddots & \vdots \\ b_{R,1} & b_{R,2} & \cdots & b_{R,C} \end{pmatrix}$$

Figure 2.3: Base matrix of QC-LDPC code

Figure 2.4: Base matrix of WiMAX QC-LDPC code with rate of 1/2

The main advantages of the quasi-cyclic structure are as follows:

- QC-LDPC codes can provide comparable error correction performance compared with random-LDPC codes, while allowing simple and structured construction [34],

- QC-LDPC codes are well-suited to hardware implementations, with parallelizable architecture and simple interconnection network, due to the specific structure of the parity-check matrix [98, 110],

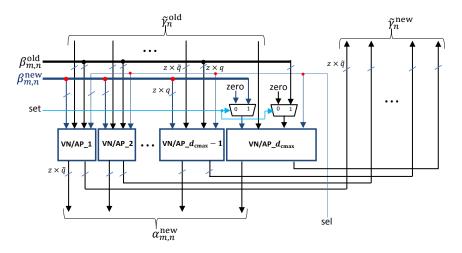

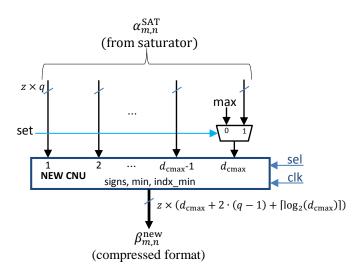

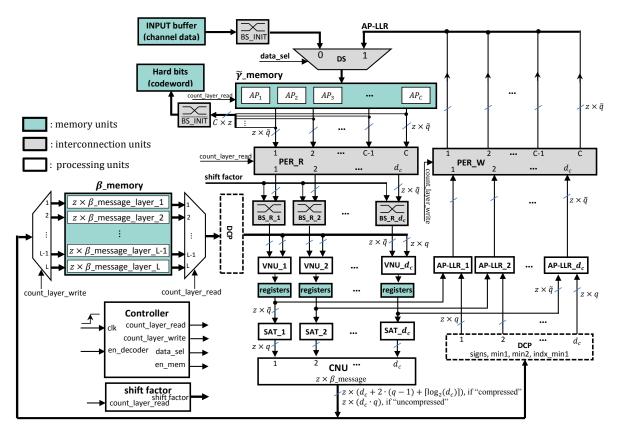

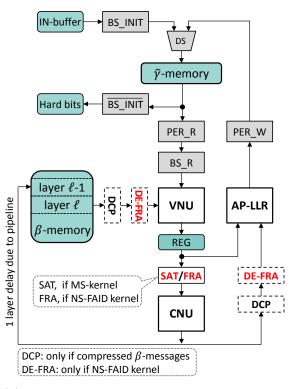

- QC-LDPC codes can support for flexible block lengths, by considering different expansion factors z [10, 111]