# Characterization and design of high-switching speed capability of GaN power devices in a 3-phase inverter Rémi Perrin

## ▶ To cite this version:

Rémi Perrin. Characterization and design of high-switching speed capability of GaN power devices in a 3-phase inverter. Electronics. Université de Lyon, 2017. English. NNT: 2017LYSEI001. tel-01784868

# HAL Id: tel-01784868 https://theses.hal.science/tel-01784868

Submitted on 3 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT : 2017ISAL001

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON opérée au sein de Laboratoire AMPERE

#### Ecole Doctorale N° ED160 Electrotechnique Electronique Automatique

Spécialité/ discipline de doctorat : Génie Electrique

Soutenue publiquement le 09/01/2017, par : Rémi PERRIN

# Characterization and Design of High-Switching Speed Capability of GaN Power Devices in a 3-Phase Inverter

Devant le jury composé de :

Lambeye, Yves, Professeur, Université Joseph Fourier Examinateur Wicht, Bernhard, Professeur, Université de Reutlingen Rapporteur Prodic, Aleksander, Professeur, Université de Toronto Rapporteur Radoslava, Mitova, Docteur, Schneider Electric Examinateur Allard, Bruno, Professeur, Insa de Lyon Directeur de Thèse

#### Département FEDORA - INSA Lyon - Ecoles Doctorales - Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                          | NOM ET COORDONNEES DU RESPONSABLE                                                      |

|-----------|----------------------------------------------------------|----------------------------------------------------------------------------------------|

|           |                                                          |                                                                                        |

| CHIMIE    | <u>CHIMIE DE LYON</u>                                    | M. Stéphane DANIELE                                                                    |

| CHIMIE    | http://www.edchimie-lyon.fr                              | Institut de Recherches sur la Catalyse et l'Environnement de Lyon<br>IRCELYON-UMR 5256 |

|           | Sec : Renée EL MELHEM                                    | Équipe CDFA                                                                            |

|           | Bat Blaise Pascal 3 <sup>e</sup> etage                   | 2 avenue Albert Einstein                                                               |

|           | secretariat@edchimie-lyon.fr                             | 69626 Villeurbanne cedex<br>directeur@edchimie-lyon.fr                                 |

|           | Insa : R. GOURDON                                        | directedi@edefinine-iyon.ii                                                            |

|           | ELECTRONIQUE,                                            | M. Gérard SCORLETTI                                                                    |

| E.E.A.    | ELECTROTECHNIQUE, AUTOMATIQUE<br>http://edeea.ec-lyon.fr | Ecole Centrale de Lyon                                                                 |

|           | http://edeca.ee-iyon.m                                   | 36 avenue Guy de Čollongue<br>69134 ECULLY                                             |

|           | Sec : M.C. HAVGOUDOUKIAN                                 | Tél : 04.72.18 60.97 Fax : 04 78 43 37 17                                              |

|           | Ecole-Doctorale.eea@ec-lyon.fr                           | <u>Gerard.scorletti@ec-lyon.fr</u>                                                     |

|           | EVOLUTION, ECOSYSTEME,                                   | M. Fabrice CORDEY                                                                      |

| E2M2      | MICROBIOLOGIE, MODELISATION                              | CNRS UMR 5276 Lab. de géologie de Lyon                                                 |

|           | http://e2m2.universite-lyon.fr                           | Université Claude Bernard Lyon 1                                                       |

|           | Sec : Sylvie ROBERJOT                                    | Bât Géode<br>2 rue Raphaël Dubois                                                      |

|           | Bât Atrium - UCB Lyon 1                                  | 69622 VILLEURBANNE Cédex                                                               |

|           | 04.72.44.83.62                                           | Tél: 06.07.53.89.13                                                                    |

|           | Insa : H. CHARLES<br>secretariat.e2m2@univ-lyon1.fr      | <u>cordey@univ-lyon1.fr</u>                                                            |

|           |                                                          |                                                                                        |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-<br>SANTE                    | Mme Emmanuelle CANET-SOULAS                                                            |

| 22100     | http://www.ediss-                                        | INSERM U1060, CarMeN lab, Univ. Lyon 1<br>Bâtiment IMBL                                |

|           | lyon.fr                                                  | 11 avenue Jean Capelle INSA de Lyon                                                    |

|           | Sec : Sylvie ROBERJOT<br>Bât Atrium - UCB Lyon 1         | 696621 Villeurbanne<br>Tél : 04.72.68.49.09 Fax :04 72 68 49 16                        |

|           | 04.72.44.83.62                                           | Emmanuelle.canet@univ-lyon1.fr                                                         |

|           | Insa : M. LAGARDE                                        |                                                                                        |

|           | secretariat.ediss@univ-lyon1.fr<br>INFORMATIQUE ET       | Mme Sylvie CALABRETTO                                                                  |

| INFOMATHS | MATHEMATIQUES                                            | LIRIS – INSA de Lyon                                                                   |

|           | http://infomaths.univ-lyon1.fr                           | Bat Blaise Pascal                                                                      |

|           | Sec :Renée EL MELHEM                                     | 7 avenue Jean Capelle<br>69622 VILLEURBANNE Cedex                                      |

|           | Bat Blaise Pascal                                        | Tél : 04.72. 43. 80. 46 Fax 04 72 43 16 87                                             |

|           | 3 <sup>e</sup> etage                                     | Sylvie.calabretto@insa-lyon.fr                                                         |

|           | infomaths@univ-lyon1.fr                                  |                                                                                        |

|           | MATERIAUX DE LYON                                        | M. Jean-Yves BUFFIERE                                                                  |

| Matériaux | http://ed34.universite-lyon.fr                           | INSA de Lyon                                                                           |

|           | Sec : M. LABOUNE                                         | MATEIS<br>Bâtiment Saint Exupéry                                                       |

|           | PM: 71.70 -Fax: 87.12                                    | 7 avenue Jean Capelle                                                                  |

|           | Bat. Direction                                           | 69621 VILLEURBANNE Cedex                                                               |

|           | Ed.materiaux@insa-lyon.fr                                | Tél : 04.72.43 71.70 Fax 04 72 43 85 28<br>jean-yves.buffiere@insa-lyon.fr             |

|           |                                                          |                                                                                        |

| MEGA      | MECANIQUE,ENERGETIQUE,GENIE<br>CIVIL,ACOUSTIQUE          | M. Philippe BOISSE                                                                     |

| MIZOR     | http://mega.universite-lyon.fr                           | INSA de Lyon<br>Laboratoire LAMCOS                                                     |

|           |                                                          | Bâtiment Jacquard                                                                      |

|           | Sec : M. LABOUNE<br>PM : 71.70 -Fax : 87.12              | 25 bis avenue Jean Capelle                                                             |

|           | Bat. Direction                                           | 69621 VILLEURBANNE Cedex<br>Tél : 04.72 .43.71.70 Fax : 04 72 43 72 37                 |

|           | mega@insa-lyon.fr                                        | Philippe.boisse@insa-lyon.fr                                                           |

|           | ScSo*                                                    | M. Christian MONTES                                                                    |

| ScSo      | http://recherche.univ-lyon2.fr/scso/                     | M. Christian MONTES<br>Université Lyon 2                                               |

|           |                                                          | 86 rue Pasteur                                                                         |

|           | Sec : Viviane POLSINELLI                                 | 69365 LYON Cedex 07                                                                    |

|           | Brigitte DUBOIS<br>Insa : J.Y. TOUSSAINT                 | Christian.montes@univ-lyon2.fr                                                         |

|           | Tél : 04 78 69 72 76                                     |                                                                                        |

| 1         | viviane.polsinelli@univ-lyon2.fr                         |                                                                                        |

$* ScSo: Histoire, G\acute{e}ographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie and Science politique, Sociologie, Content and Science politique and Science poli$

« Ce n'est pas parce que les choses sont difficiles que nous n'osons pas, c'est parce que nous n'osons pas que les choses sont difficiles. » (Sénèque)

## Contents

| т, |       | P. Freuder                                         |     |

|----|-------|----------------------------------------------------|-----|

| Ы  | IST O | F FIGURES x                                        | ix  |

| Lı | IST O | F TABLES XX                                        | xii |

| Lı | IST O | F ACRONYMS xx                                      | iv  |

| R  | EMER  | RCIEMENTS X                                        | xv  |

| D  | ISSEM | AINATION XX                                        | vii |

| A  | BSTR. | ACT XX                                             | ix  |

| R  | ÉSUM  | lÉ xx                                              | xi  |

| R  | ÉSUM  | ié en Français xxx                                 | iii |

| 1  | 0     | Martin Contraction                                 |     |

| 1  | -     | ARACTERIZATION AND MODELING OF 600 V E-GAN         | -   |

|    |       | MTs                                                | 1   |

|    | 1.1   |                                                    | 1   |

|    | 1.2   | GAN POWER DEVICES                                  | 7   |

|    |       | 1.2.1 GaN Rectifier                                | 7   |

|    |       | 1.2.2 The lateral GaN power device                 | 9   |

|    | 1.3   | Characterization of an Enhancement and Cascode     |     |

|    |       | GAN DEVICES                                        | 20  |

|    |       | 1.3.1 Static Characterization                      | 21  |

|    |       | 1.3.2 Dynamic Characterization                     | 24  |

|    | 1.4   | Contribution to modeling of an Enhancement GaN de- |     |

|    |       | VICE                                               | 31  |

|    |       | 1.4.1 SPICE Model Improvement                      | 31  |

|    |       | 1.4.2 Turn-On transient behavior                   | 39  |

|    | 1.5   | Conclusion                                         | 45  |

| 2 | Isoi | LATION       | OF CONTROL SIGNAL USING A CORELESS TRANS-                       |           |

|---|------|--------------|-----------------------------------------------------------------|-----------|

|   | FOR  | MER          |                                                                 | <b>47</b> |

|   | 2.1  | Intro        | DUCTION                                                         | 47        |

|   |      | 2.1.1        | Galvanic Isolation Solutions                                    | 50        |

|   | 2.2  | HIGH-        | TEMPERATURE CORELESS TRANSFORMER ISOLATION                      |           |

|   |      | Barri        | ER                                                              | 56        |

|   |      | 2.2.1        | Characterization and Modelization                               | 57        |

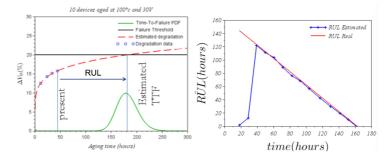

|   |      | 2.2.2        | Aging Test                                                      | 59        |

|   |      | 2.2.3        | Design of a High-temperature Control Signal Isolation $\ . \ .$ | 61        |

|   |      | 2.2.4        | Aging of the coreless-transformer board $\ . \ . \ . \ .$ .     | 63        |

|   | 2.3  | A $dV_{\mu}$ | /dt Generator for an Accurate evaluation of                     |           |

|   |      | TRANS        | SIENT IMPACT                                                    | 64        |

|   |      | 2.3.1        | dV/dt Generator                                                 | 64        |

|   |      | 2.3.2        | Dynamic Characterization of Isolation Solutions                 | 67        |

|   | 2.4  | Mode         | ling a Galvanic Isolation in a Power Stage                      | 73        |

|   |      | 2.4.1        | SPICE Simulation                                                | 74        |

|   | 2.5  | Conci        | LUSION                                                          | 76        |

| 3 | GAT  | e Dri        | VER POWER SUPPLY DEDICATED FOR HIGH-SWITCHIN                    | G         |

|   | Pov  | VER ST       | TAGE                                                            | 79        |

|   | 3.1  | Switc        | CHED-MODE POWER SUPPLY (SMPS) DEDICATED FOR                     |           |

|   |      | Gate         | DRIVER                                                          | 80        |

|   |      | 3.1.1        | Low Power and High-Temperature Soft-Switching topologies        | 82        |

|   |      | 3.1.2        | Magnetic material for High-Temperature Application              | 87        |

|   |      | 3.1.3        | EMI                                                             | 93        |

|   |      | 3.1.4        | High-Temperature Capacitor Selection                            | 94        |

|   |      | 3.1.5        | Power Supply Integration Challenges                             | 96        |

|   |      | 3.1.6        | Conclusion                                                      | 100       |

|   | 3.2  | HIGH-        | TEMPERATURE GAN ACTIVE-CLAMP FLYBACK CON-                       |           |

|   |      | VERTE        | R WITH RESONANT OPERATION INTERVAL                              | 101       |

|   |      | 3.2.1        | Resonant interval of Operation                                  | 102       |

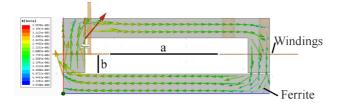

|   | 3.3  | TRANS        | SFORMER PARASITIC CAPACITANCE OPTMIZATION                       | 115       |

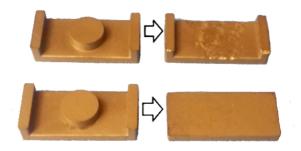

|   |      | 3.3.1        | Transformer Geometry Optimization                               | 115       |

|   |      | 3.3.2        | Transformer Optimization through FEM                            | 120       |

|   |      | 3.3.3        | Analytic Transformer Optimization                               | 122       |

|   |      | 3.3.4        | Conclusion                                                      | 123       |

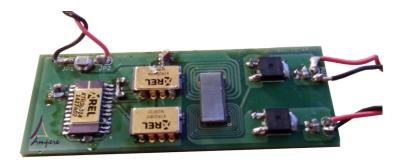

|   | 3.4  | PCB          | INTEGRATION OF A 2 W POWER-SUPPLY IN HIGH-                      |           |

|   |      | TEMPI        | ERATURE APPLICATIONS                                            | 124       |

|   |      | 3.4.1        | PCB Selection                                                   | 124       |

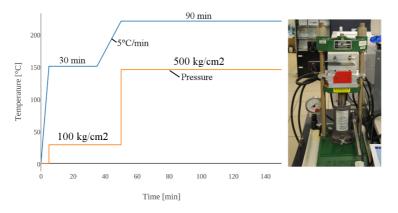

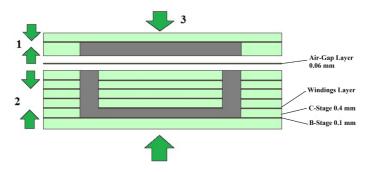

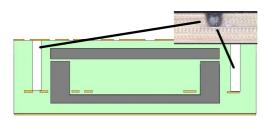

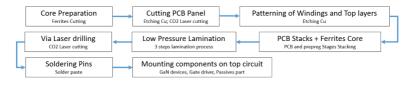

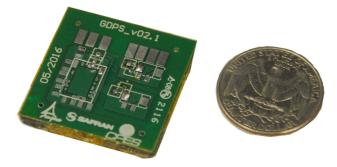

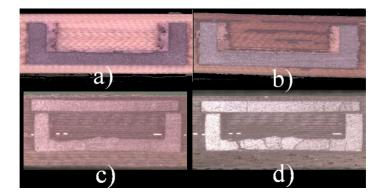

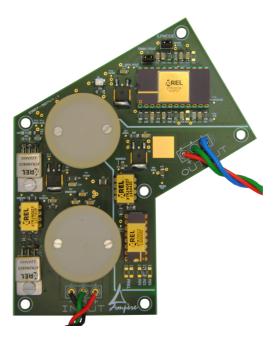

|   |      | 3.4.2        | PCB Lamination Process                                          | 125       |

|   |      | 3.4.3        | Thermal Cycling of PCB Embedded Transformer                     | 130       |

|   |     | 3.4.4         | Conclusion                                                                  |

|---|-----|---------------|-----------------------------------------------------------------------------|

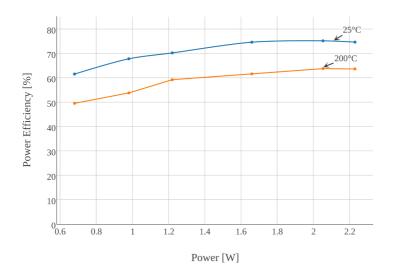

|   | 3.5 | Exper         | RIMENTAL RESULTS                                                            |

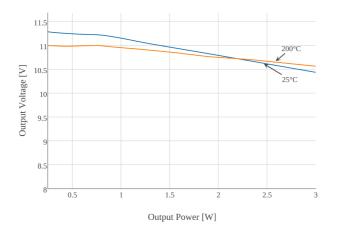

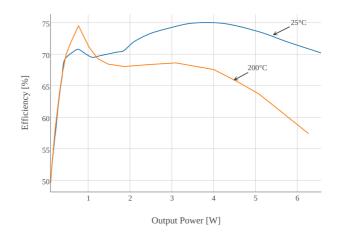

|   |     | 3.5.1         | High-Temperature Flyback Power Supply $\ldots \ldots \ldots \ldots 132$     |

|   |     | 3.5.2         | High-Temperature Active-Clamp Flyback Power Supply $134$                    |

|   |     | 3.5.3         | A High-Temperature Regulated Solution: Isolated Buck<br>Power Supply        |

|   | 3.6 | Conci         | LUSION                                                                      |

|   |     |               |                                                                             |

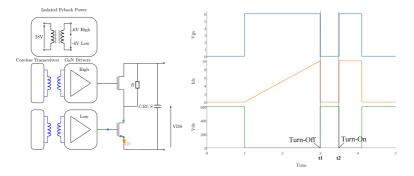

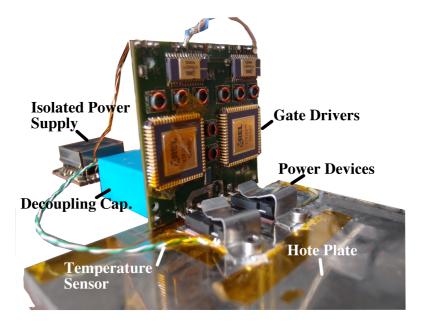

| 4 |     | VARDS<br>TION | HIGH-TEMPERATURE GAN POWER MODULE INTE- 151                                 |

|   | 4.1 | TRENI         | DS IN WBG GATE DRIVER                                                       |

|   |     | 4.1.1         | High-temperature GaN Phase-leg Switching                                    |

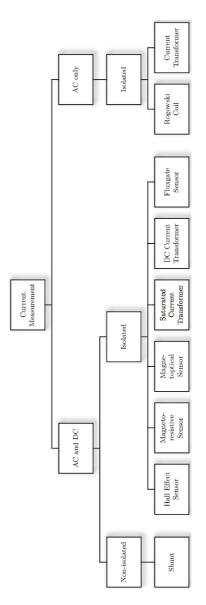

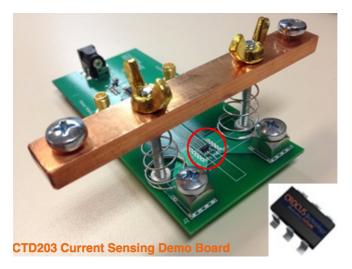

|   |     | 4.1.2         | Current Sensors in the Power Module                                         |

|   |     | 4.1.3         | Physical Health Monitoring                                                  |

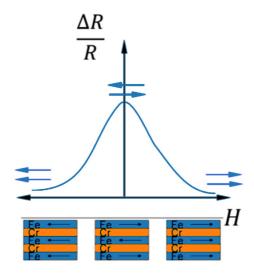

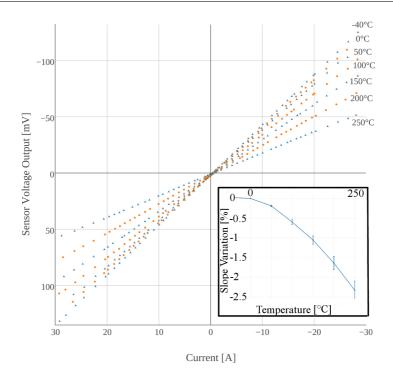

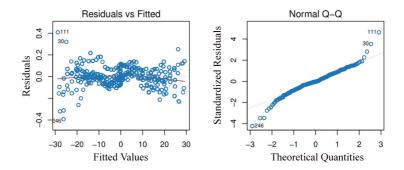

|   | 4.2 |               | TEMPERATURE CURRENT SENSOR SOLUTION BASED ON<br>EL MAGNETORESISTANCE EFFECT |

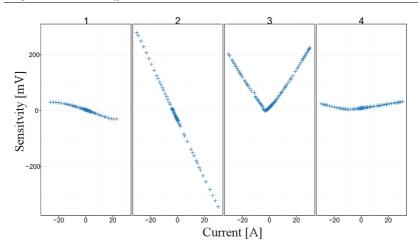

|   |     | 4.2.1         | TMR Selection and Evaluation                                                |

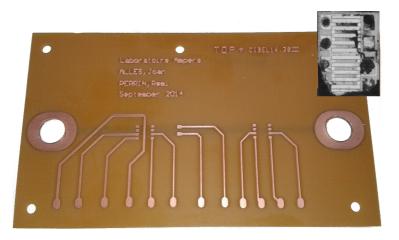

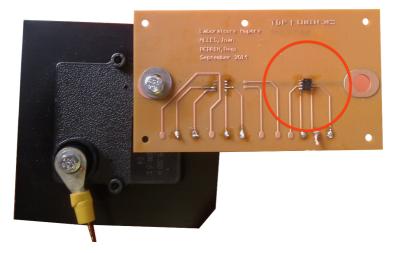

|   |     | 4.2.2         | TMR Current Sensor Design and Test                                          |

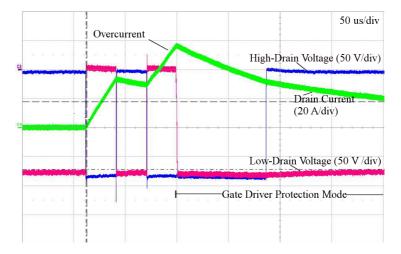

|   |     | 4.2.3         | TMR Current Sensor in a Overcurrent Protection Function . $170$             |

|   | 4.3 | Four-<br>FETs | LEVEL INTELLIGENT GATE DRIVER FOR E-MODE GAN                                |

|   |     | 4.3.1         | Principle of Operation of a Four-Level Driving Circuit for the              |

|   |     |               | eGaN FETs                                                                   |

|   |     | 4.3.2         | Experimental Results and Analysis 176                                       |

|   | 4.4 | HIGH-         | TEMPERATURE GAN PHASE-LEG DESIGN 180                                        |

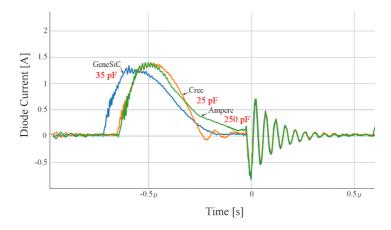

|   |     | 4.4.1         | Selection and Modeling of External Circuit Components 180                   |

|   |     | 4.4.2         | SPICE Module Simulation                                                     |

|   | 4.5 | Conci         | LUSION                                                                      |

| 5 | Gen | IERAL         | CONCLUSION 193                                                              |

|   | 5.1 | SUMM          | ARY OF CONTRIBUTIONS                                                        |

|   | 5.2 | Persp         | PECTIVES                                                                    |

|   |     | 5.2.1         | Short-term Challenges                                                       |

|   |     | 5.2.2         | Long-term Challenges                                                        |

| Appeni | DICES                                      | 197 |

|--------|--------------------------------------------|-----|

| .1     | GAN HEMT GS66508 Modified Model            | 199 |

| .2     | Coreless Isolation Capacitance Matlab Code | 205 |

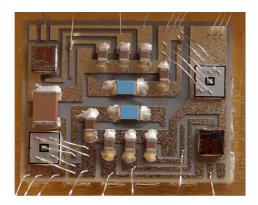

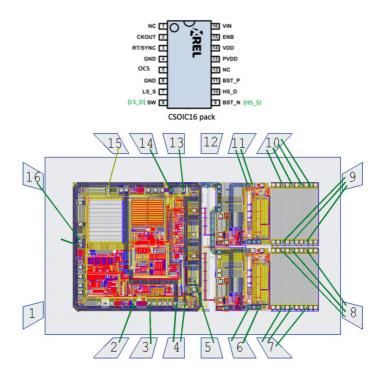

| .3     | XTR39020 SOI CMOS CHIP LAYOUT              | 207 |

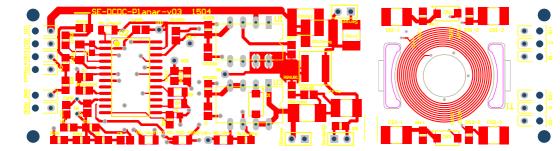

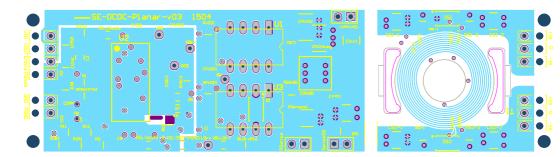

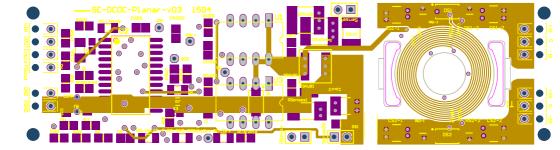

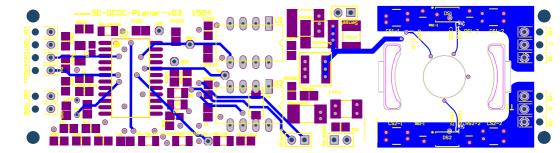

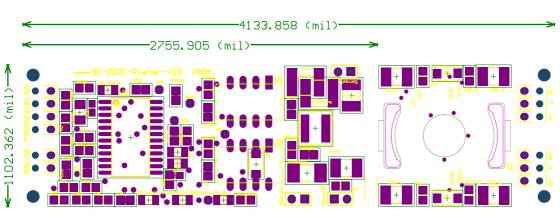

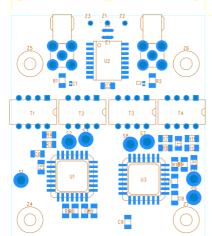

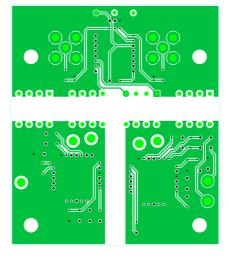

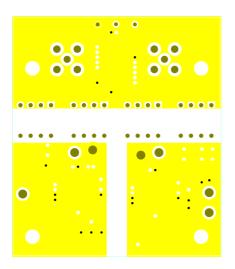

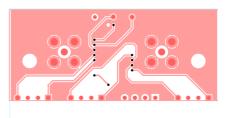

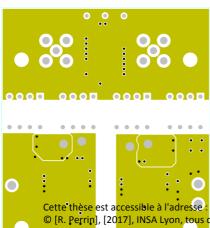

| .4     | ISOLATED BUCK CONVERTER LAYOUT             | 207 |

| .5     | 800 kHz Gan Active Clamp Flyback Layout    | 213 |

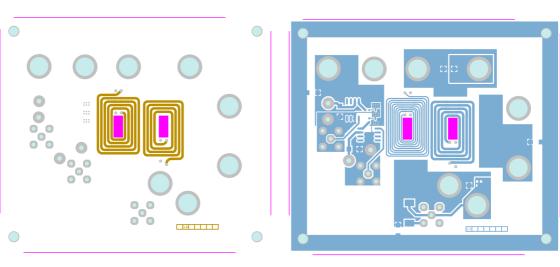

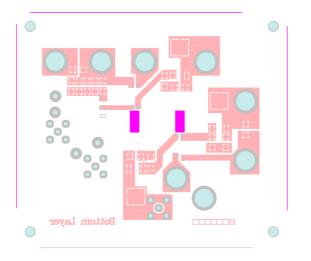

| .6     | MEGAN GATE DRIVER LAYOUT                   | 215 |

## List of Figures

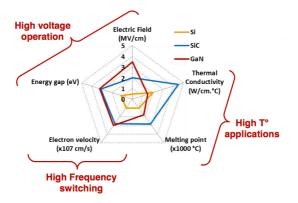

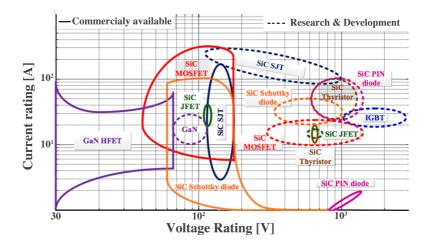

| 1.1  | Comparison of SiC and GaN devices against Si for Power          |    |

|------|-----------------------------------------------------------------|----|

|      | applications [189].                                             | 2  |

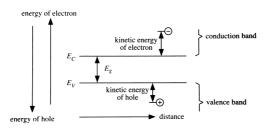

| 1.2  | Band diagram after an atom has been ionized [119]               | 2  |

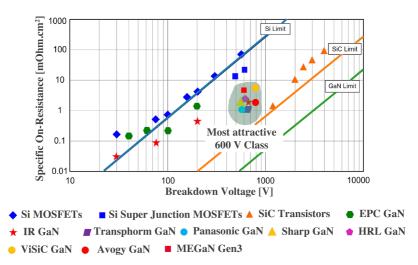

| 1.3  | Specific On-resistance vs. breakdown voltage for commercially   |    |

|      | SI, SiC and GaN devices [122]                                   | 3  |

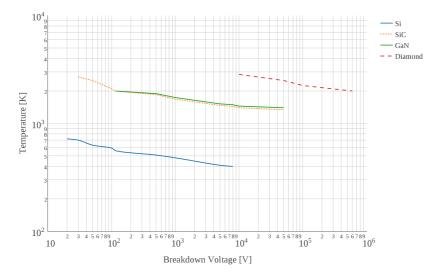

| 1.4  | Limited operation temperature for different semiconductor ma-   |    |

|      | terials [177]                                                   | 4  |

| 1.5  | Timeline of the development of the power semiconductor [100].   | 6  |

| 1.6  | Rating of selected research and commercial power devices [250]. | 7  |

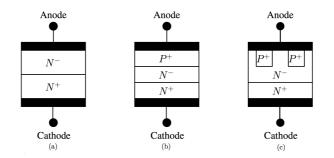

| 1.7  | Main diode structures                                           | 8  |

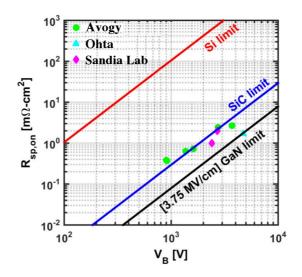

| 1.8  | Baliga figure of merit for GaN diodes state of the art (Sandia  |    |

|      | lab: [59]; Ohta: [152]; Avogy: [108])                           | 9  |

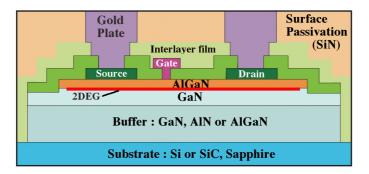

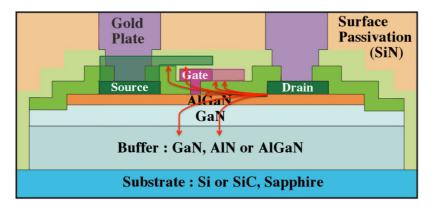

| 1.9  | Cross-section of a basic lateral GaN HEMT or HFET struc-        |    |

|      | ture [91]                                                       | 10 |

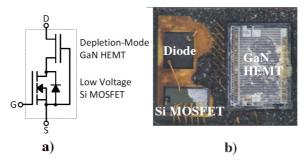

| 1.10 | Normally-Off Cascode structure a); Package view of a Transphorm |    |

|      | TPH3002PS Cascode GaN, 600 V 17 A b) [22]                       | 11 |

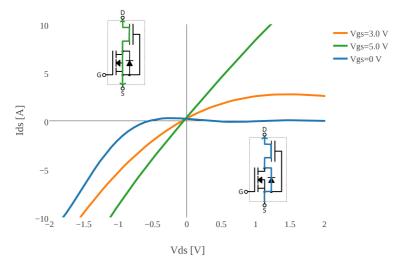

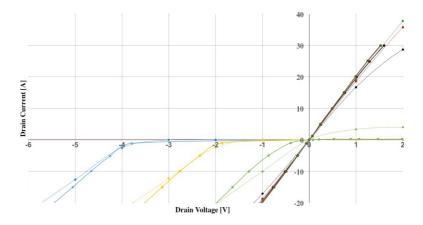

| 1.11 | Conduction principle of a cascode GaN HEMT and it is Vd-Id      |    |

|      | characteristics.                                                | 12 |

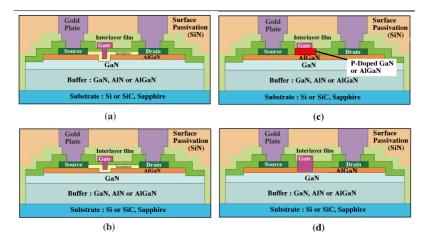

| 1.12 | Normally Off device gate structures, MIS-HFET (a), Insulated    |    |

|      | recessed gate (b), P-doped GaN or AlGaN (c), Recessed gate (d). | 14 |

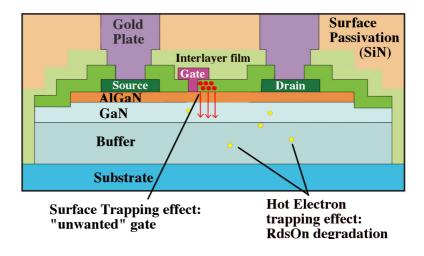

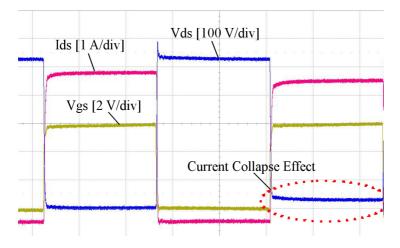

| 1.13 | Current collapse phenomena: surface charge trapping and hot     |    |

|      | electron trapping                                               | 15 |

| 1.14 | Current collapse effect on drain voltage with a Normally-Off    |    |

|      | MEGaN HEMT.                                                     | 16 |

| 1.15 | Current collapse limitation by the field plates structure       | 16 |

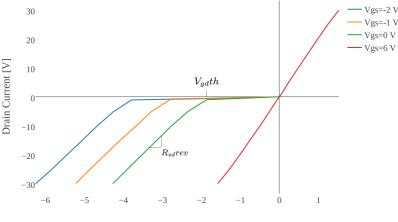

| 1.16 | Enhancement GaN device reverse conduction I-V characteristic.   | 17 |

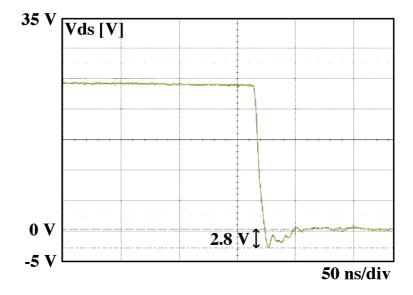

| 1.17 | Drain voltage drop of an enhancement GaN device, EPC2012        | 18 |

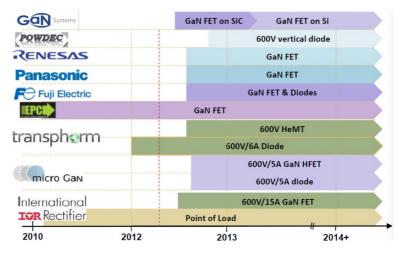

| 1.18 | GaN production roadmap, Yole [86]                               | 19 |

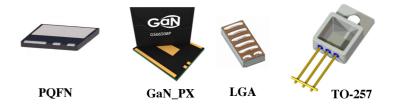

| 1.19 | Different packages for each GaN devices                         | 21 |

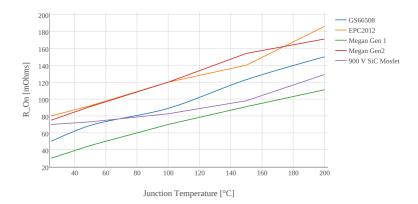

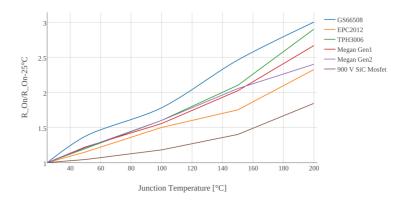

| 1.20 | Enhancement GaN devices and SiC MOSFET On resistance vs.               |          |

|------|------------------------------------------------------------------------|----------|

|      | temperature measured with the curve tracer.                            | 21       |

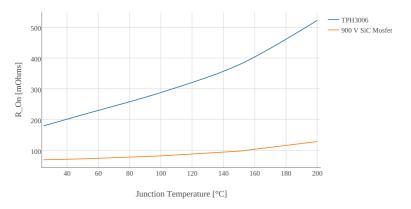

| 1.21 | Cascode device and SiC MOSFET device On resistance value               |          |

|      | vs. temperature measured with the curve tracer.                        | 22       |

| 1.22 | Normalized On-resistances vs. temperature for GaN and SiC              |          |

|      | MOSFET devices measured with the curve tracer.                         | 23       |

| 1.23 | Threshold Voltages vs. temperature for GaN and SiC MOS-                |          |

|      | FET devices measured during switching and with curve tracer.           | 23       |

| 1.24 | Typical double pulse test circuit with the typical waveform            | 24       |

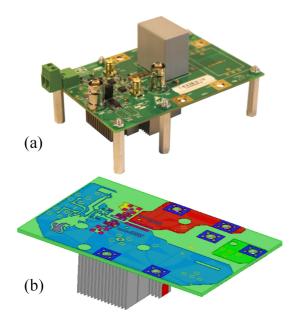

| 1.25 | Double pulse tester setup.                                             | 25       |

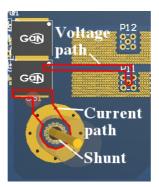

| 1.26 | Optimized voltage and current pathes for the GaN Systems               |          |

|      | GaN HEMT lab DPT board.                                                | 26       |

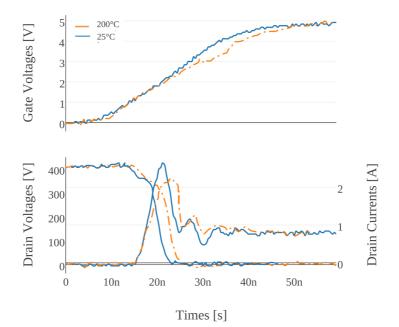

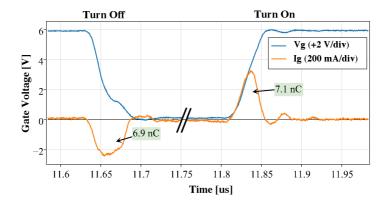

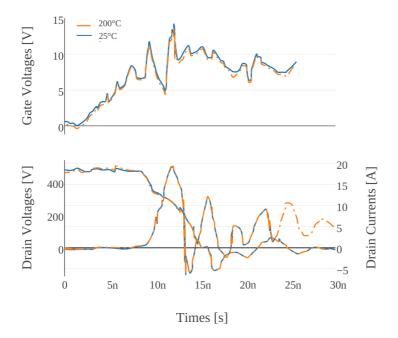

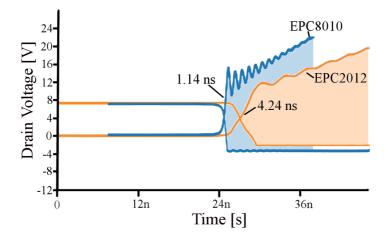

| 1.27 | Experimental turn On transient waveforms of the bottom de-             |          |

|      | vice at 400 V and 1 A at 25 and 200°C from Figure 1.25                 | 27       |

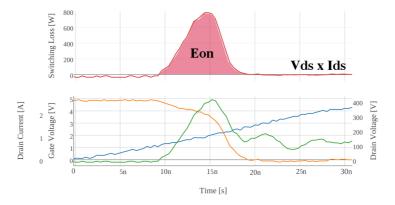

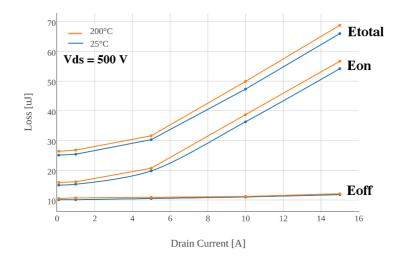

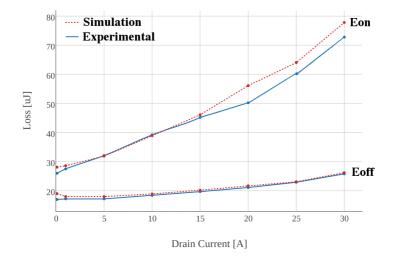

| 1.28 | Evaluation of turn-On energy                                           | 28       |

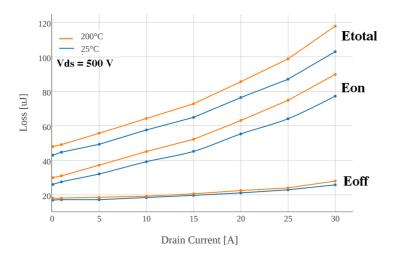

| 1.29 | Experimental turn-On and turn-Off losses at 25 and 200 $^{\circ}C$ at  |          |

|      | $V_{ds} = 500V$ from Figure 1.25                                       | 28       |

| 1.30 | Gate voltage and gate current during turn-On and turn-Off states.      | 29       |

| 1.31 | Experimental turn-On transient waveforms of the bottom de-             |          |

|      | vice on the board at 500 V and 5 A at 25 and $200^{\circ}C$            | 30       |

| 1.32 | Experimental turn-On and turn-Off losses for 25 and 200 $^{\circ}C$ at |          |

|      | $V_{ds} = 500V.$                                                       | 31       |

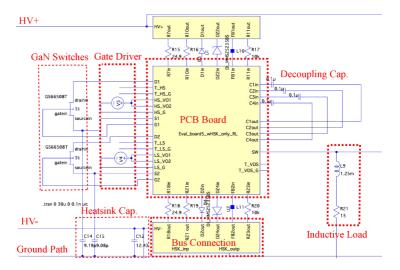

| 1.33 | Experimental (orange) and simulation (blue) comparative                |          |

|      | waveforms.                                                             | 32       |

| 1.34 | Experimental (plain) and simulation (dashed) comparative               |          |

|      | drain voltage and current characteristic.                              | 33       |

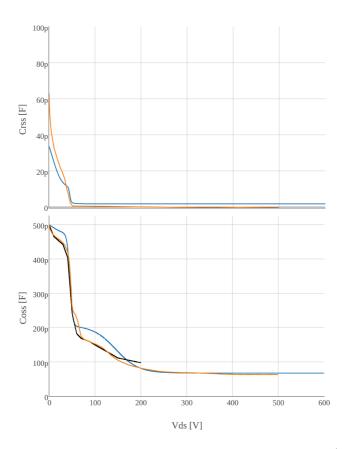

| 1.35 | GaN device $C_{rss}$ and $C_{oss}$ characteristic with datasheet (or-  |          |

|      | ange), simulation (blue) and experimental value (black) from [101].    | 34       |

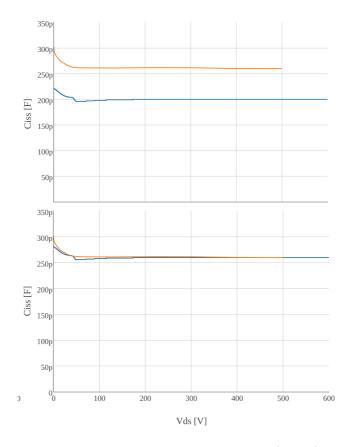

| 1.36 | GaN device $C_{iss}$ capacitance datasheet (orange), simulation        | ~ ~      |

| 1.05 | (blue) value before (top) and after modification (bottom)              | 35       |

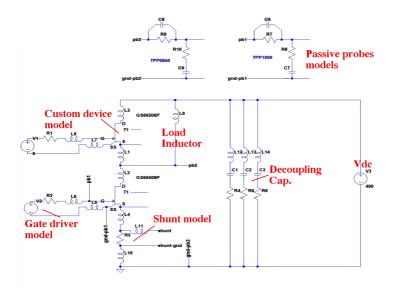

| 1.37 | Simulation circuit of the board in the double-pulse test config-       | 0.0      |

| 1.00 | uration.                                                               | 36       |

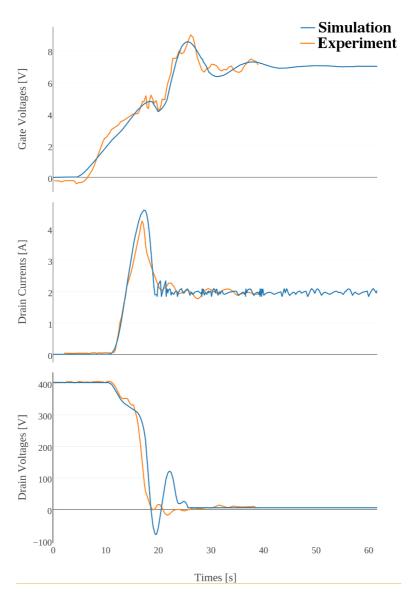

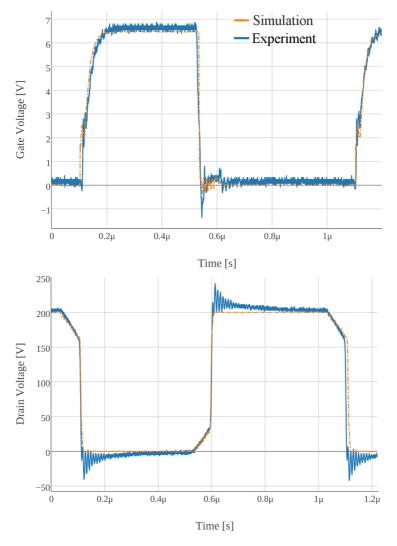

| 1.38 | Simulated and experimental turn-On switching waveforms of              | 07       |

| 1.90 | the bottom GaN device at 400 V, 2 A with $R_g = 0 \ \Omega$            | 37       |

| 1.39 | Simulation and experimental $E_{On}$ and $E_{Off}$ losses from GS66508 | 90       |

| 1 40 | modified model.                                                        | 38       |

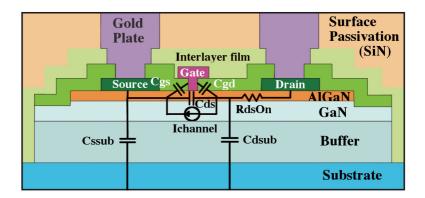

|      | Equivalent circuit model for an enhancement GaN device                 | 39<br>40 |

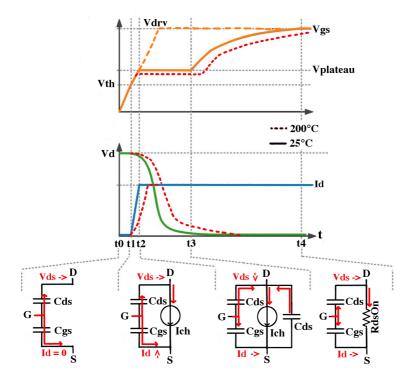

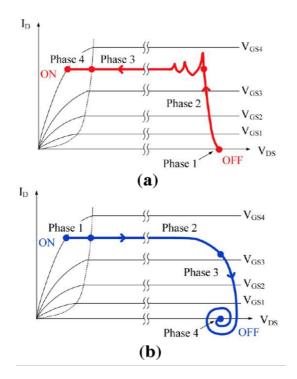

|      | Theoretical turn-On process of GaN HFET                                | 40       |

| 1.42 | Spice Simulation of the turn-On waveforms with $R_g = 100 \Omega$      | 49       |

|      | (top) and $R_g = 1 \Omega$ (bottom)                                    | 43       |

| 1.43 | Non-ideal switching trajectories for turn-On (a) and turn-Off<br>(b) from [46] | 44 |

|------|--------------------------------------------------------------------------------|----|

| 2.1  | Maximum experimental $dV/dt$ for different drain voltages and                  |    |

|      | a 2 $\Omega$ gate resistor.                                                    | 48 |

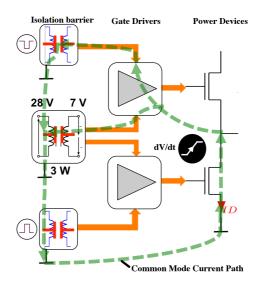

| 2.2  | Simplified schematic of the circulating common-mode current                    |    |

|      | in an inverter phase leg                                                       | 49 |

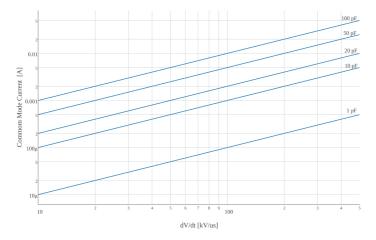

| 2.3  | Common-mode current for different isolation capacitances and                   |    |

|      | dV/dt                                                                          | 50 |

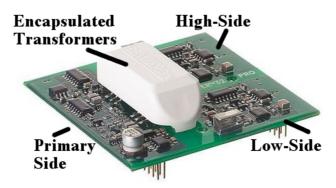

| 2.4  | Semikron IGBT gate driver with magnetic core isolation [1]                     | 51 |

| 2.5  | High-temperature solution for a control signal isolation with a                |    |

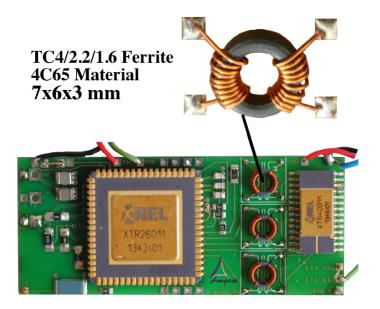

|      | toroidal ferrite [166]                                                         | 52 |

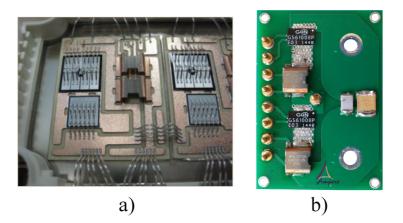

| 2.6  | Coreless transformer application, a) data isolation single trans-              |    |

|      | former [147]; b) and a DC/DC converter with signal isolation                   |    |

|      | in a iCoupler product [38]                                                     | 53 |

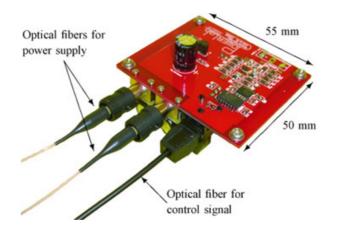

| 2.7  | Resonant gate driver optically isolated and supplied [76]                      | 54 |

| 2.8  | Isolated gate driver solution with PCB integrated capacitor [242].             | 54 |

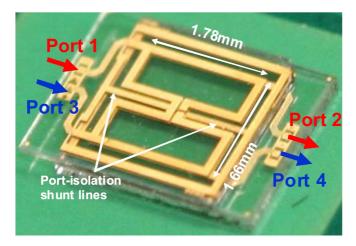

| 2.9  | Butterfly coupler on a sapphire substrate [145]                                | 55 |

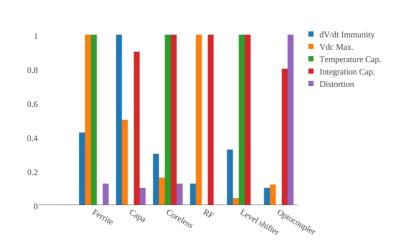

| 2.10 | Comparison of some isolation solutions previously presented.                   | 56 |

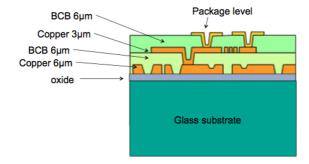

| 2.11 | Simplified cross-section of the technology used for the coreless               |    |

|      | transformer. With Courtesy of STMicroelectronics                               | 57 |

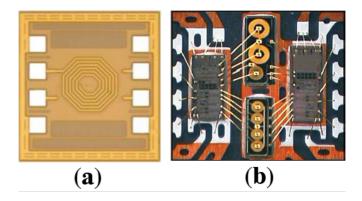

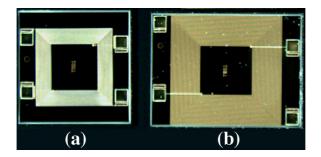

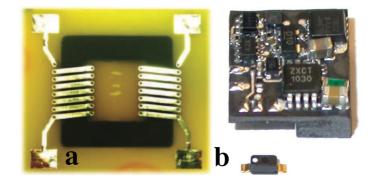

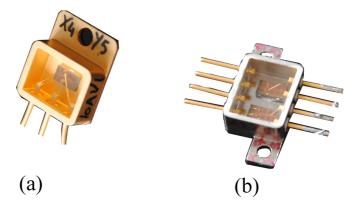

| 2.12 | Coreless transformer structures (a)TRD1 (3x3x0.2 mm) (b)TRS1                   |    |

|      | (4x3x0.2  mm)                                                                  | 58 |

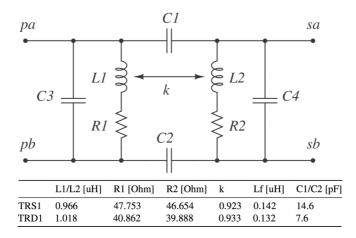

| 2.13 | Electrical model of the coreless-transformers in Figure 2.12 with $\hfill = 1$ |    |

|      | identified parameters [30]                                                     | 58 |

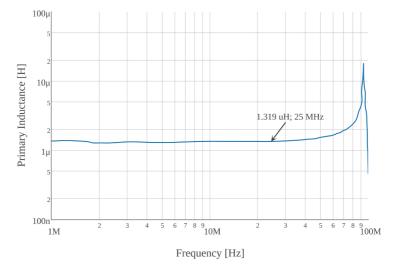

| 2.14 | Experimental primary inductance measurement.                                   | 59 |

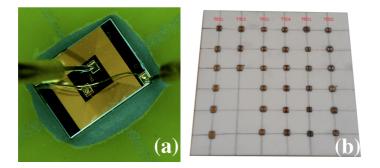

| 2.15 | 4 points probes for static measurement (a); Ceramic substrate                  |    |

|      | and the 6 different coreless transformer types with Parylene                   |    |

|      | coating (b)                                                                    | 60 |

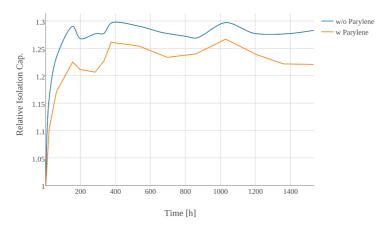

| 2.16 | TRS1 Isolation capacitance variation under $200^\circ C$ with and              |    |

|      | without Parylene                                                               | 60 |

| 2.17 | TRD1 Isolation capacitance variation under $200^\circ C$ with and              |    |

|      | without Parylene                                                               | 61 |

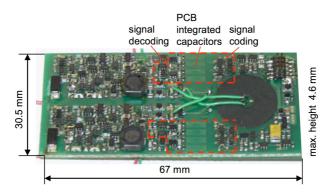

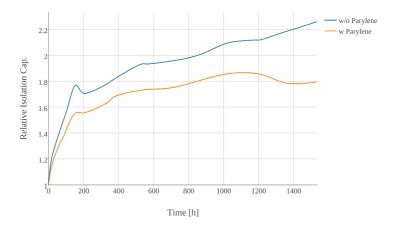

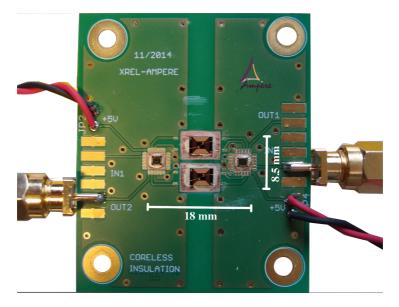

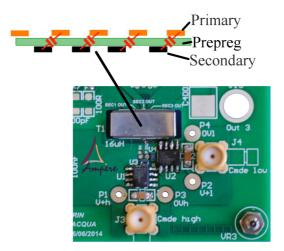

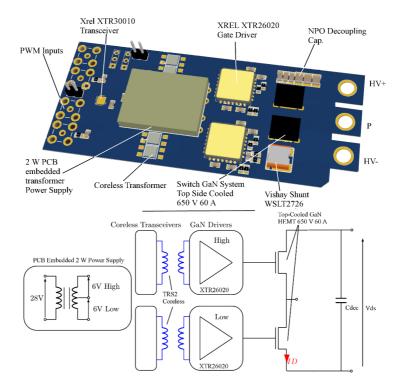

|      | Coreless-transformer Isolated board under testing                              | 62 |

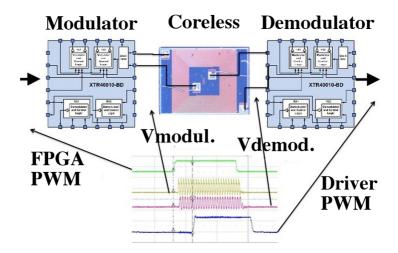

| 2.19 | Modulation and demodulation principle with two Xrel XTR40010                   |    |

|      | Transceiver.                                                                   | 63 |

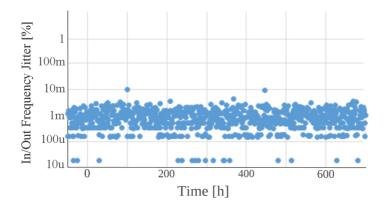

|      | Input/output frequency Jitter at $200^{\circ}C$ .                              | 64 |

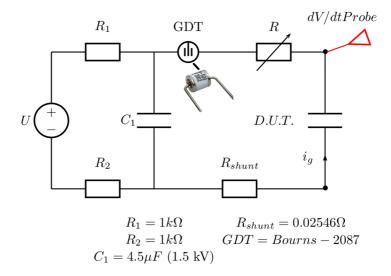

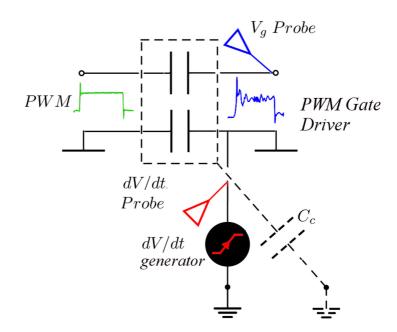

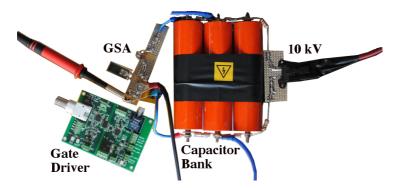

|      | dV/dt generator based on a Gaz Surge Arrester                                  | 65 |

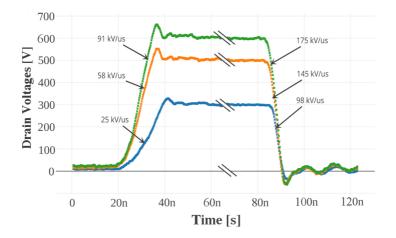

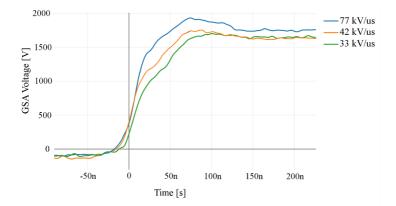

|      | Different $dV/dt$ values generated by the Gaz Surge Arrester                   | 66 |

| 2.23 | Simplified equivalent circuit of the characterization setup with               |    |

|      | the parasitic capacitance of the DUT                                           | 67 |

| 2.24 | Experimental setup.                                                | 68 |

|------|--------------------------------------------------------------------|----|

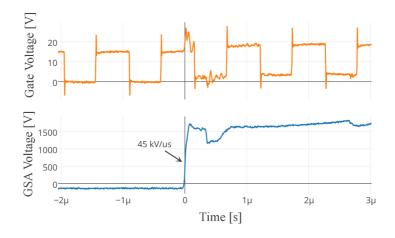

| 2.25 | 45 $kV/\mu s$ transient impact on an optocoupler barrier isolation |    |

|      | logic signal.                                                      | 69 |

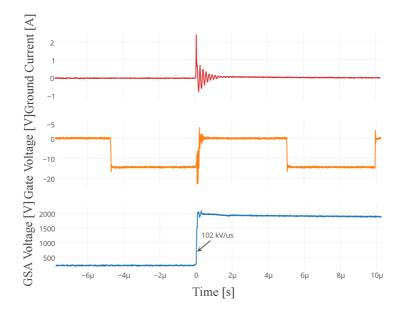

| 2.26 | 100 $kV/\mu s$ transient impact on an capacitive barrier isolation |    |

|      | ISO721 logic signal and generated common mode current              | 70 |

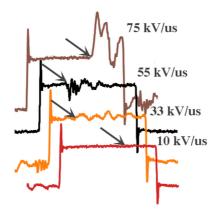

| 2.27 | Different $dV/dt$ impact values on the gate voltage logic signal   | 70 |

| 2.28 | Oscilloscope ground coupling capacitance discharging after a       |    |

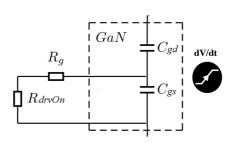

|      | dV/dt.                                                             | 71 |

| 2.29 | Simplified model of the gate driver and the power device during    |    |

|      | a positive $dV/dt$                                                 | 72 |

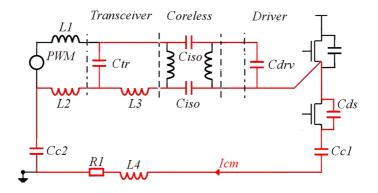

| 2.30 | Simplified model of a coreless-transformer isolation in a power    |    |

|      | stage configuration                                                | 74 |

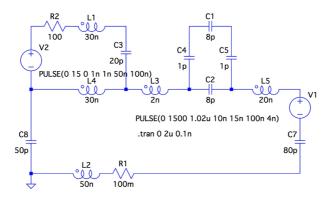

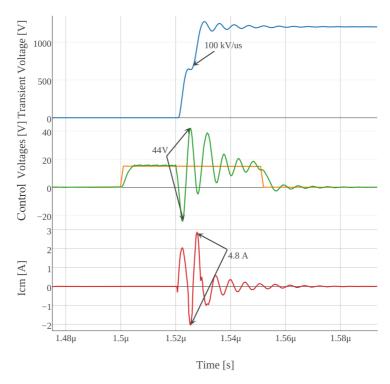

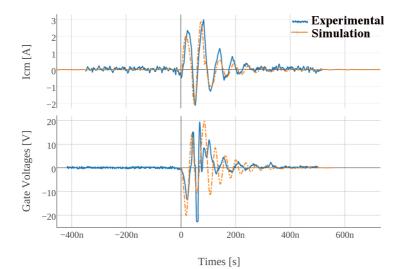

| 2.31 | LTspice circuit according to the schematic Figure 2.30             | 74 |

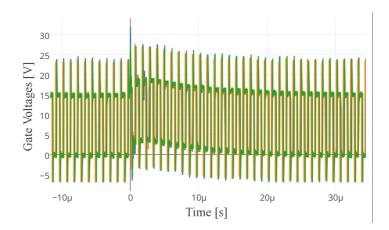

| 2.32 | Transient voltage, control signal voltages and common mode         |    |

|      | current                                                            | 75 |

| 2.33 | Gate voltage and common-mode current experimental and sim-         |    |

|      | ulatted waveforms for a 100 $kV/\mu s$                             | 76 |

|      |                                                                    |    |

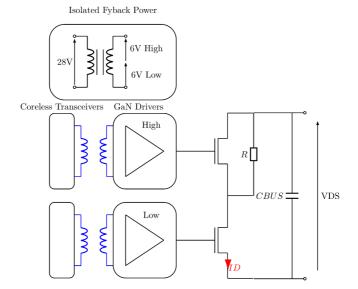

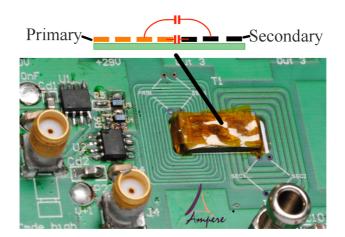

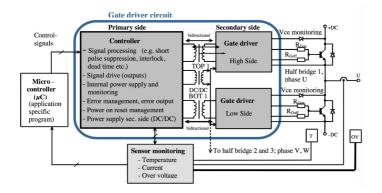

| 3.1  | A One-phase power stage block diagram                              | 81 |

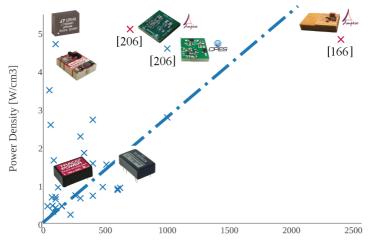

| 3.2  | Power density vs. switching frequency for commercial available     |    |

|      | low-power (< 5 W) converters and best lab-scale prototypes $$      |    |

|      | (including this work).                                             | 82 |

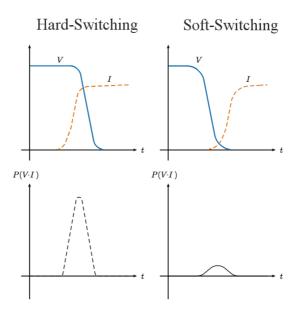

| 3.3  | Comparative hard and soft switching current and voltage wave-      |    |

|      | forms                                                              | 83 |

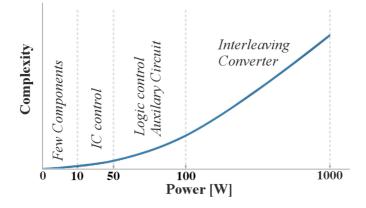

| 3.4  | Complexity of the power supply vs. power level.                    | 84 |

| 3.5  | LLC topology.                                                      | 85 |

| 3.6  | Quasi-resonant Flyback topology.                                   | 85 |

| 3.7  | Active-clamp Flyback topology.                                     | 86 |

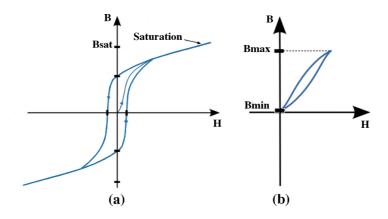

| 3.8  | B - H characteristics [67]                                         | 88 |

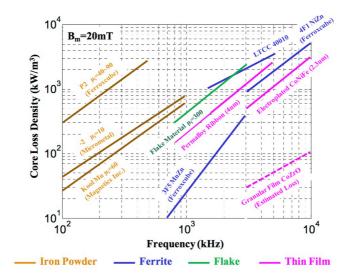

| 3.9  | Core loss chart for high frequency material [139]                  | 89 |

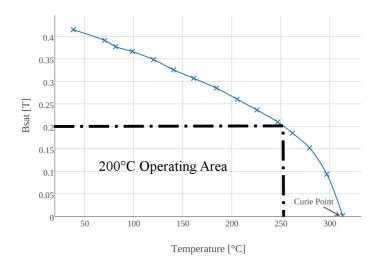

| 3.10 | 1                                                                  | 89 |

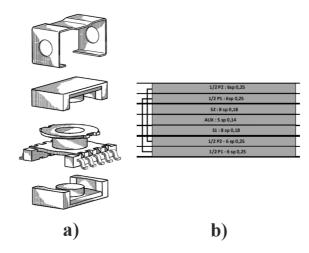

| 3.11 | EFD15 core transformer and ER14.5 core planar transformer          |    |

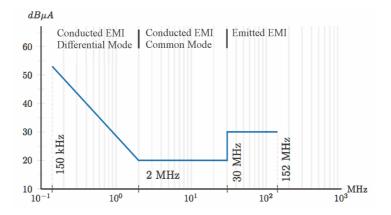

|      | for a 3 W, $200^{\circ}C$ power supply                             | 92 |

|      | Maximum EMI noise level from the DO160 standard [4]                | 93 |

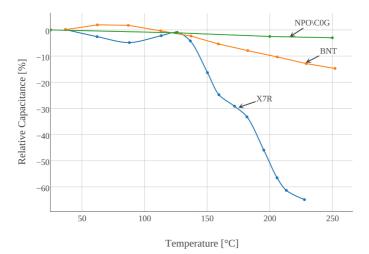

| 3.13 | Relative variation of the capacitance for a ceramic X7R (PCI-      |    |

|      | X7R), BNT and NPO at 10 kHz [182, 166, 8, 149]                     | 95 |

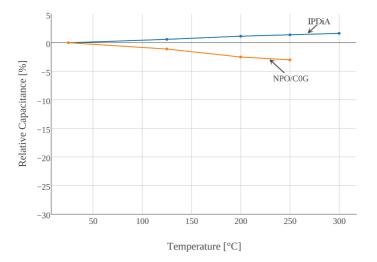

| 3.14 | Relative variation of the capacitance for a silicon IPDiA XTSC     |    |

|      | capacitor [36, 218]                                                | 96 |

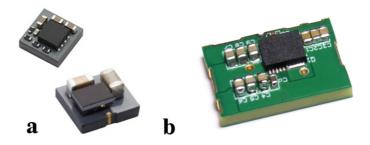

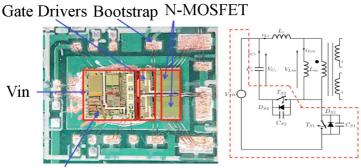

| 3.15 | Non-isolated LTCC inductor integrated POL converters a) Mu-        |    |

|      | rata LTCC power supply [143]; b) CPES POL module with              |    |

|      | LTCC [245]                                                         | 97 |

| 3.16 | a) PCB integrated EMI Filter with coupled inductor [16]; b) In-<br>tegrated flyback dc-dc converter built using ferrite-based LTCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | materials [184]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97  |

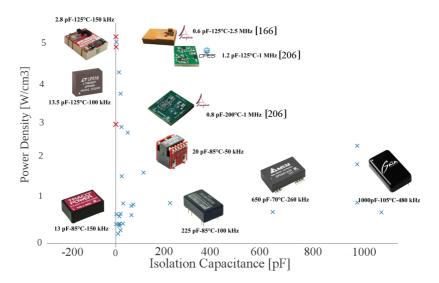

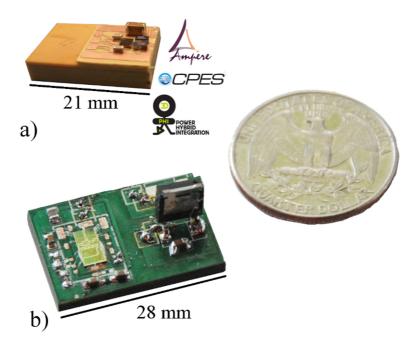

| 3.17 | Power density vs. isolation capacitance for commercial avail-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | able low-power (< 5 W) converters and best lab scale proto-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | types (including this work); Isolation capacitance, max. junc-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | tion temperature and switching frequency are given for each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99  |

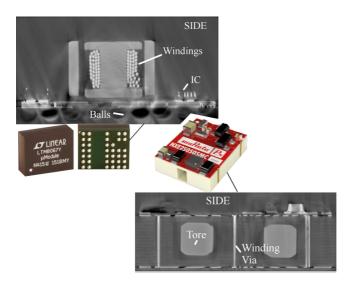

| 3.18 | Xray picture of the side and top cross-section of the LTM8068 $\hfill \hfill \$ |     |

|      | and NXE2 power supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |

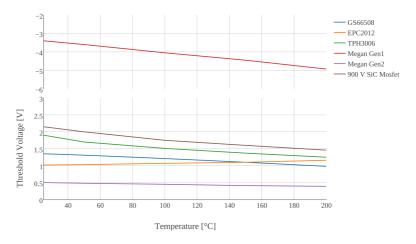

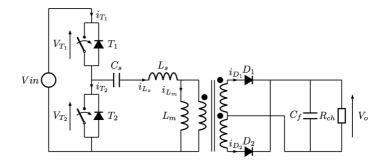

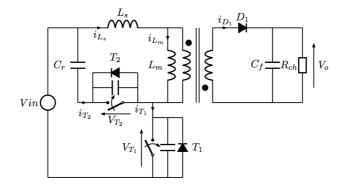

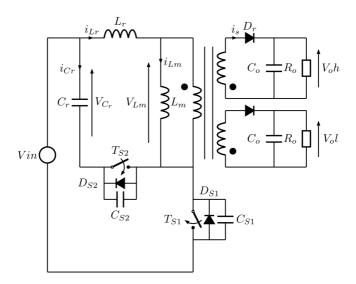

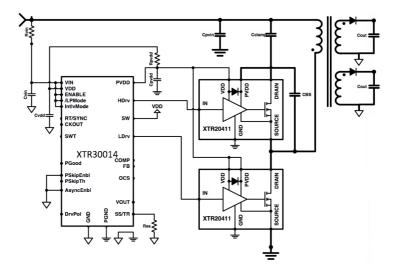

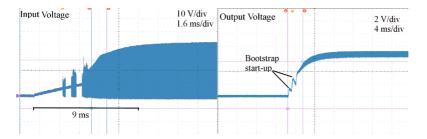

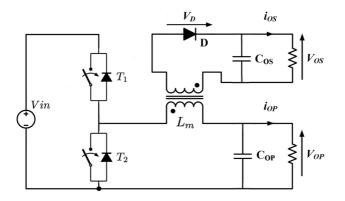

| 3.19 | Double-output Active-clamp flyback power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101 |

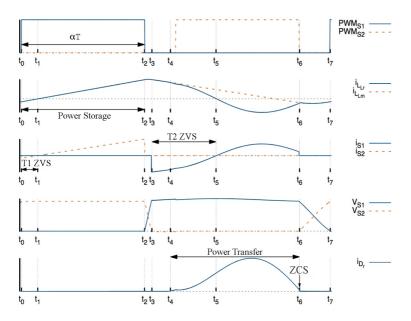

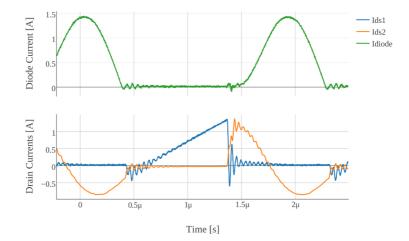

| 3.20 | Active-clamp Flyback main ideal waveforms in steady-state op-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | eration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 103 |

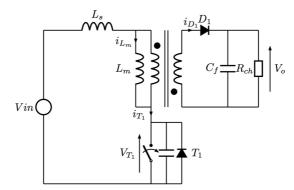

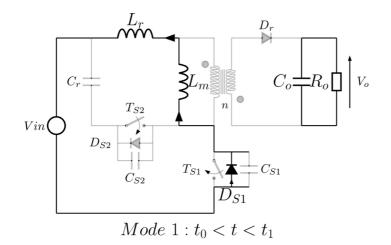

| 3.21 | Interval 1 of Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104 |

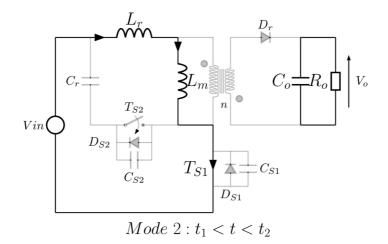

| 3.22 | Interval 2 of Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104 |

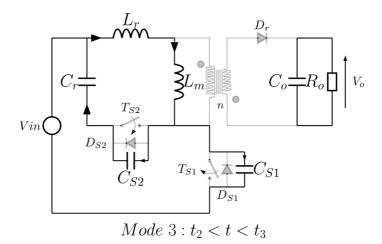

| 3.23 | Interval 3 Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 105 |

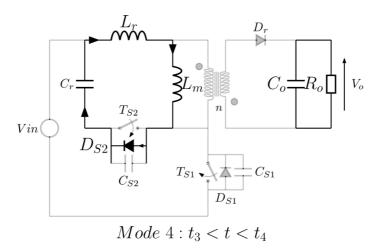

| 3.24 | Interval 4 Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106 |

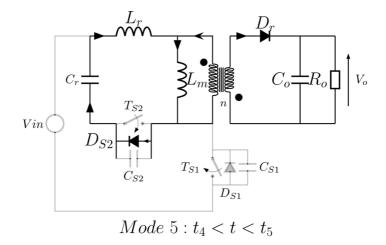

| 3.25 | Interval 5 Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 107 |

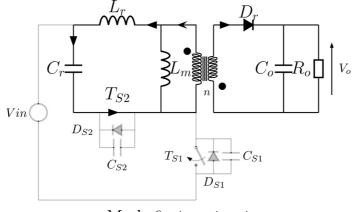

| 3.26 | Interval 6 Active-Clamp Flyback topology operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

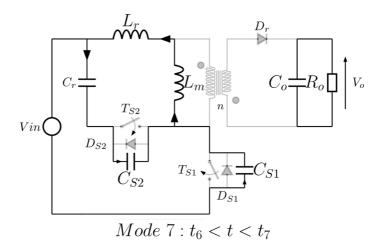

| 3.27 | Interval 7 Active-Clamp Flyback operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109 |

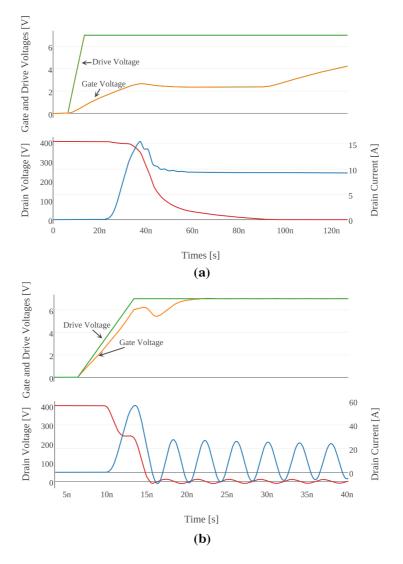

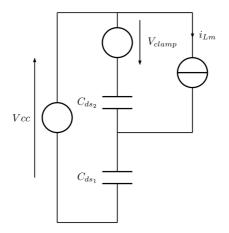

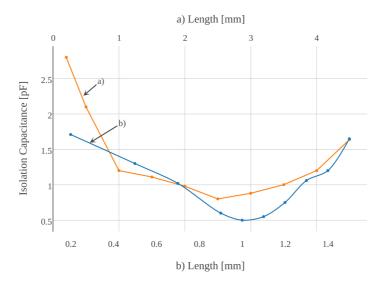

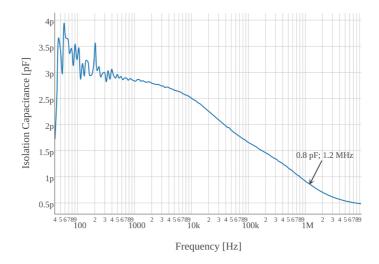

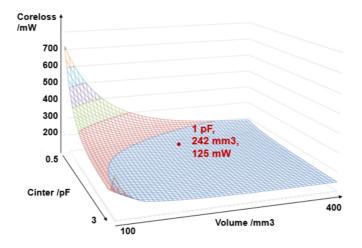

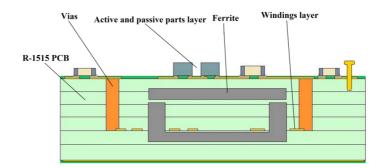

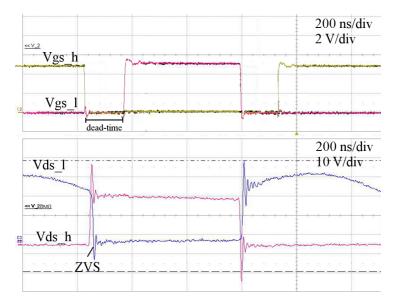

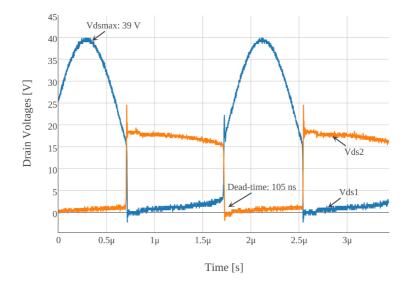

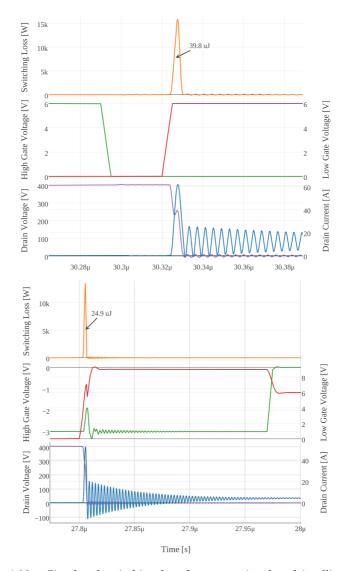

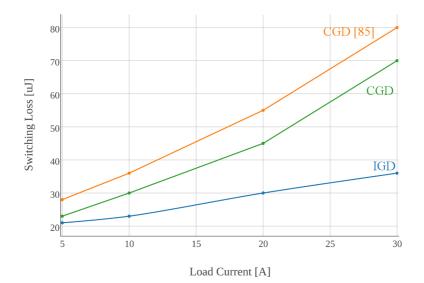

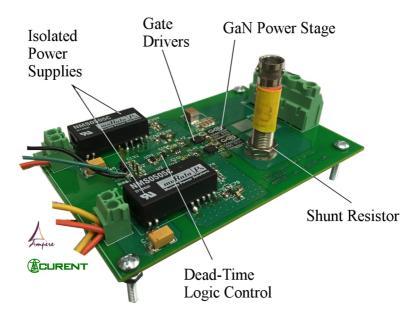

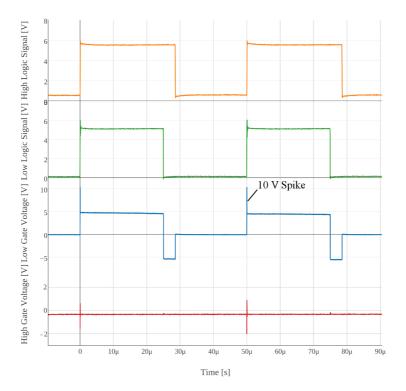

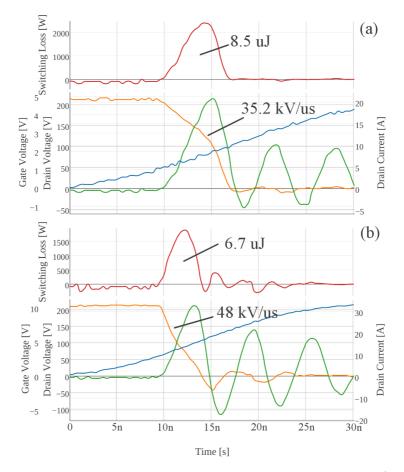

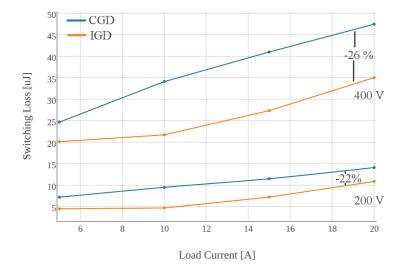

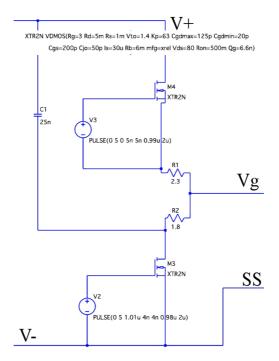

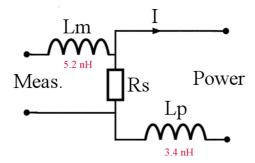

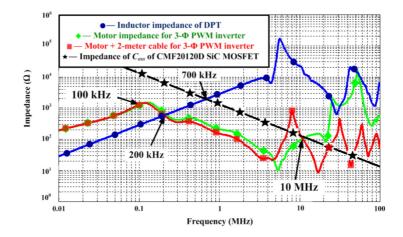

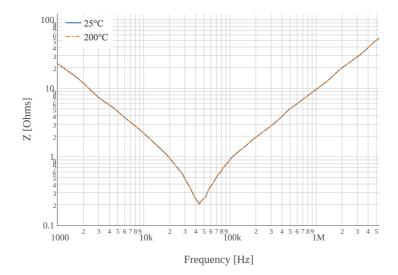

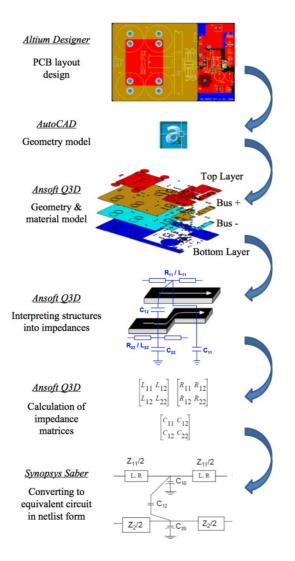

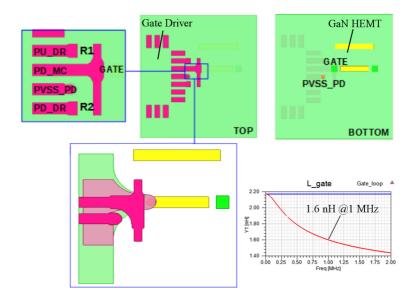

| 3.28 | Equivalent circuit of the GaN half-bridge during dead-time, in-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |