# Evaluation of DC supply protection for efficient energy delivery in low voltage applications

Thi Thuong Huyen Ma

# ▶ To cite this version:

Thi Thuong Huyen Ma. Evaluation of DC supply protection for efficient energy delivery in low voltage applications. Electric power. Universit\'e de Lyon, 2018. English. NNT: 2018LYSE1055. tel-01797803

# HAL Id: tel-01797803 https://theses.hal.science/tel-01797803

Submitted on 22 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2018LYSE1055

# THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de

l'Université Claude Bernard Lyon 1

Ecole Doctorale N° 160

Électronique, Électrotechnique, Automatique de Lyon (EEA)

Spécialité de doctorat : Génie electrique

Soutenue publiquement le 05 april 2018, par:

Thi Thuong Huyen MA

# Evaluation of DC supply protection for efficient energy delivery in low voltage applications

# Devant le jury composé de:

| M. SECHILARIU Manuela | Professeure, Université de Technologie de Compiègne           | Rapporteur         |

|-----------------------|---------------------------------------------------------------|--------------------|

| M. PHAN Xuan Minh     | Professeure, Institut Polytechnique de Hanoï                  | Rapporteur         |

| M. LU Guo Neng        | Professeur, Université Claude Bernard Lyon 1                  | Examinateur        |

| M. YAHOUI Hamed       | Maître de Conférences-HDR Université Claude Bernard<br>Lyon 1 | Directeur de thèse |

| M. HERVÉ Morel        | Directeur de Recherche CNRS, Ampere                           | Invité             |

# UNIVERSITE CLAUDE BERNARD - LYON 1

Président de l'Université M. le Professeur Frédéric FLEURY

Président du Conseil Académique M. le Professeur Hamda BEN HADID

Vice-président du Conseil d'Administration M. le Professeur Didier REVEL

Vice-président du Conseil Formation et Vie Universitaire M. le Professeur Philippe CHEVALIER

Vice-président de la Commission Recherche M. Fabrice VALLÉE

Directrice Générale des Services Mme Dominique MARCHAND

# COMPOSANTES SANTE

Directeur: M. le Professeur G.RODE Faculté de Médecine Lyon Est – Claude Bernard

Faculté de Médecine et de Maïeutique Lyon Sud - Charles Directeur : Mme la Professeure C. BURILLON

Mérieux

Directeur: M. le Professeur D. BOURGEOIS Faculté d'Odontologie

Directeur: Mme la Professeure C. VINCIGUERRA Institut des Sciences Pharmaceutiques et Biologiques

Directeur: M. X. PERROT

Institut des Sciences et Techniques de la Réadaptation Directeur: Mme la Professeure A-M. SCHOTT

Département de formation et Centre de Recherche en Biologie

Humaine

# COMPOSANTES ET DEPARTEMENTS DE SCIENCES ET TECHNOLOGIE

Faculté des Sciences et Technologies Directeur: M. F. DE MARCHI

Département Biologie Directeur: M. le Professeur F. THEVENARD

Directeur: Mme C. FELIX Département Chimie Biochimie

Directeur: M. Hassan HAMMOURI Département GEP

Directeur: M. le Professeur S. AKKOUCHE Département Informatique Département Mathématiques Directeur: M. le Professeur G. TOMANOV Département Mécanique Directeur: M. le Professeur H. BEN HADID

Département Physique Directeur: M. le Professeur J-C PLENET

UFR Sciences et Techniques des Activités Physiques et Sportives Directeur: M. Y.VANPOULLE

Observatoire des Sciences de l'Univers de Lyon Directeur: M. B. GUIDERDONI

Polytech Lyon Directeur: M. le Professeur E.PERRIN

Ecole Supérieure de Chimie Physique Electronique Directeur: M. G. PIGNAULT

Institut Universitaire de Technologie de Lyon 1 Directeur: M. le Professeur C. VITON

Ecole Supérieure du Professorat et de l'Education Directeur: M. le Professeur A. MOUGNIOTTE

Institut de Science Financière et d'Assurances Directeur: M. N. LEBOISNE

# **ABSTRACT**

Currently, there is a drop in the price of distributed energy resources, especially solar PVs, which leads to a significant growth of the installed capacities in many countries. On the other hand, policies encouraging energy efficiency have promoted the development of DC loads in domestic areas, such as LEDs lighting, computers, telephones, televisions, efficient DC motors and electric vehicles. Corresponding to these changes in sources and loads, DC microgrid distribution system becomes more attractive than the traditional AC distribution system. The main advantages of the DC microgrid are higher energy efficiency, easier in integrating with distributed energy sources and storage systems.

While many studies concentrate on the control strategies and energy management in the DC microgrid, the protection still receives inadequate attention and lack of regulations and experiences. Protection in DC grids is more complex than AC grids due to the continuous arc, higher short circuit current value and fault rate of rising. Furthermore, the DC distributed grids are composed of many electronic and semiconductor switching devices, which only sustain the fault currents of some tens of microseconds. Mechanical circuit breakers, which have a response time in tens of milliseconds, seem not to meet the safety requirement of DC microgrids. The lack of effective protection devices is a barrier to the development of DC microgrids in the distributed systems.

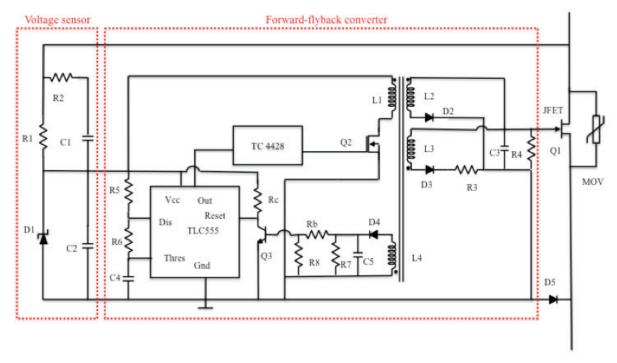

This thesis proposes a self-power solid-state DC circuit breaker using normally-on SiC JFET, which offers a great protection device for DC microgrids due to its fast response time and low on-state losses. The design of the solid state DC circuit breaker aims to meet two objectives: fast response time and high reliability. The designed specifications and critical energies that result in the destruction of the circuit breaker are identified on the basis of the experiments of a commercial normally-on JFET. In addition, a very fast and reliable protection driver based on a forward-flyback converter topology is employed to generate a sufficient negative voltage to turn and hold off the SiC JFET. The converter will be activated whenever short-circuit faults are detected by sensing the drain-source voltage, then creating a negative voltage applied to the gate of JFET. To avoid gate failure by overvoltage at the gate of JFET, the output voltage of the forward-flyback converter is regulated using Primary Side Sensing technique. Experimental results validated the working principle of the proposed solid state DC circuit breaker with fault clearing time less than 3 µs.

Additionally, a model of the normally-on JFET in Matlab/Simulink environment is built for exploring the behaviors of the solid-state DC circuit breaker during short-circuit faults. The agreement between the simulation and experimental results confirms that this JFET model can be appropriately used for the investigation of solid state DC circuit breaker operations and DC microgrids in general during fault evens and clearing fault processes.

**Keywords:** DC circuit breaker, DC microgrid, normally-on SiC JFET, protection in DC microgrid, robustness of SiC JFET, short circuit protection, solid-state DC circuit breaker.

# RESUME

Actuellement, il y a une baisse du prix des ressources énergétiques distribuées, en particulier l'énergie solaire photovoltaïque, conduisant à la croissance significative de leur capacité d'installation dans de nombreux pays. D'autre part, les politiques encourageant l'efficacité énergétique ont favorisé le développement de charges DC dans les zones domestiques, telles que l'éclairage LED, les ordinateurs,, les téléphones, les téléviseurs, les moteurs DC efficaces et les véhicules électriques. Grace àce changement, le système de distribution de microgrid DC devient plus attractive que le système de distribution à courant alternatif traditionnel. Les avantages principaux du microgrid DC sont l'efficacité énergétique plus élevée, plus facile à intégrer avec les sources d'énergie distribuées et le système de stockage.

Alors que de nombreuses recherches se concentrent sur les stratégies de contrôle et la gestion de l'énergie dans le microgrid DC, sa protection reçoit une attention insuffisante et un manque de réglementation et d'expériences. La protection dans les réseaux DC est plus difficile que dans le réseau AC en raison de l'arc continu, de la valeur plus élevée du courant de court-circuit et du taux de défaut de montée. En outre, dans les réseaux distribués à courant continu sont composés de nombreux dispositifs de commutation électroniques et semi-conducteurs, qui ne supportent le courant de défaut que quelques dizaines de microsecondes. Les disjoncteurs mécaniques, qui ont un temps de réponse de quelques dizaines de millisecondes, ne semblent pas satisfaire aux exigences de sécurité du microréseau à courant continu. L'absence d'un dispositif de protection efficace constitue un obstacle au développement du microgrid DC dans le système distribué.

Cette thèse propose un disjoncteur DC auto-alimenté à courant continu utilisant normalement JFET SiC, qui offre un excellent dispositif de protection pour les microgrids DC grâce à son temps de réponse rapide et ses faibles pertes à l'état passant. La conception du disjoncteur DC à semi-conducteurs vise à répondre à deux objectifs: temps de réponse rapide et fiabilité. Les spécifications conçues et les énergies critiques qui entraînent la destruction du disjoncteur sont identifiées sur la base des résultats mesurés d'un JFET populaire dans le commerce. Un pilote de protection très rapide et fiable basé sur une topologie à convertisseur flyback avant est utilisé pour générer une tension négative suffisante pour tourner et maintenir le JFET SiC. Le convertisseur sera activé chaque fois que le disjoncteur détecte des défauts de court-circuit en détectant la tension de drain-source de JFET et crée une tension négative s'applique à la porte de JFET. Pour éviter une défaillance de la porte par surtension au niveau de la grille du JFET, la tension de sortie du convertisseur de retour vers l'avant est régulée à l'aide de la mesure coté primaire. Les résultats expérimentaux sur le prototype du disjoncteur DC ont validé les principes de fonctionnement proposés et ont confirmé que le disjoncteur DC à semi-conducteurs proposé peut interrompre le défaut en 3 µs.

D'un autre côté, un modèle du JFET normalement activé dans l'environnement Matlab/Simulink est construit pour étudier les comportements du SSCB pendant une durée de court-circuit. L'accord entre la simulation et les résultats expérimentaux confirment que ce modèle JFET peut être utilisé pour simuler le fonctionnement d'un disjoncteur DC et dans l'étude du fonctionnement du microgrid DC pendant le processus de défaut et de compensation.

**Mots-clés**: Disjoncteur DC, microgrid DC, JFET SiC normally-on, protection en microgrid DC, robustesse du JFET SiC, protection contre les courts-circuits, disjoncteur à semi-conducteurs.

# **ACKNOWLEDGEMENTS**

This doctoral thesis concludes the major part of the work, which I have carried out at the Laboratory Ampere, Claude Bernard Lyon 1 University since November 2015. I would never have had the strength to pursue this work successfully without the guidance, encouragement, help, and support of various persons.

First of all, I would like to express my sincere gratitude to my supervisor, Assoc. Prof Hamed Yahoui, for his patient guidance, enthusiastic encouragement and useful advice of this research work. His wide knowledge and his way of thinking have been of great value to me. Without him, being my supervisor, this thesis would never be a complete piece of work. I also would like to express my great appreciation to Dr. Hervé Morel for the immense contribution to the success of this work. Under his supervision, I have gained a lot of knowledge and experience in semiconductor devices and methods to investigate their characteristics. From him, I have learned how to work as a research scientist. Special thanks go to Dr. Hoang Giang VU from Electric Power University, Vietnam. He is not only my supervisor but also a good friend, and a colleague. Without his precious support, it would not be possible to conduct this research. I also would like to give many thanks to Dr. Nicolas Siauvé for his supporting on various fields at the laboratory. It was a pleasure to work under the supervision of all four of you.

I would like to express my sincere gratitude to Glink project-Erasmus Mundus program for supporting and providing the funding for the work. A very special gratitude goes to GENOME project for allowing me using the short circuit and avalanche test bench, hence I can quickly complete the complex tests with JFET.

My grateful thanks are also extended to the labmates and staff at the Ampere laboratory and the Genie Electric department. Thank you for the great working environment and your assistance. A special thank goes to Fedia Baccar El Boubkari and Thanh Kha Tran for the great collaboration. I also want to particularly thank Lea Chancelier and Ewelina Bolimowska for all the assistance during the time preparing and staying in Lyon.

My time at Lyon was enriched due to many Vietnamese friends who are like me living away from home. I am grateful for the time we share the happiness, sadness, and difficulty with each other during last three years.

Last but not least, I would like to thank my family for all their love, encouragement and support. Most of all I want to thank my husband and our beloved daughters who are the biggest supporters and motivation for me to complete this work.

Lyon, December 2017

MA Thi Thuong Huyen

# TABLE OF CONTENTS

| Abstract                                                                      | i   |

|-------------------------------------------------------------------------------|-----|

| Résumé                                                                        | ii  |

| Acknowledgements                                                              | iii |

| Table of contents                                                             | iv  |

| List of figures                                                               | vii |

| List of abbreviations                                                         | xi  |

| General introduction                                                          | 1   |

| Energy consumption in domestic field                                          | 1   |

| Current status of energy consumption in buildings                             |     |

| Policies to promote energy efficiency                                         | 1   |

| The increase of renewable energy sources                                      | 2   |

| The development of DC Loads                                                   |     |

| Why a DC microgrid?                                                           |     |

| Motivations                                                                   |     |

| Research objectives and approach                                              |     |

| Link with the ANR C3μ project                                                 |     |

| Research Objectives and Thesis Outline                                        | 5   |

| CHAPTER 1: State of the art in dc microgrid protection                        | 7   |

| 1.1 Introduction                                                              |     |

| 1.2 Short circuit and protection in DC microgrids                             | 7   |

| 1.2.1 Concept and structures of DC microgrids                                 | 7   |

| 1.2.2 Challenges of short circuits in DC microgrid                            |     |

| 1.2.2.1 Characteristics of short circuit in DC microgrid                      |     |

| 1.2.2.2 Interruption of short circuit current in DC grid                      |     |

| 1.2.3 Requirements of a DC Circuit Breaker in the DC Microgrid                |     |

| 1.2.4 Comparison of protective devices technologies for DC grid               |     |

| 1.3 Solid state DC circuit breakers                                           |     |

| 1.3.1 Topologies for solid state DC circuit breakers                          |     |

| 1.3.2 Power Semiconductor Devices in Solid-State Circuit Breakers             |     |

| 1.3.2.1 Electrical properties                                                 |     |

| 1.3.2.2 Comparison of semiconductor materials                                 |     |

| 1.3.2.3 Structure of SiC devices                                              |     |

| 1.3.3.1 Destruction mechanisms of SiC semiconductor devices                   |     |

| 1.3.3.2 Robustness of SiC devices in avalanche mode                           |     |

| 1.3.3.3 Robustness of SiC device in short circuit mode                        |     |

| 1.3.3.4 Aging of SiC devices under short circuits                             |     |

| 1.3.4 The advantages of normally-on SiC JFETs for Solid-State circuit breaker | 52  |

| applications                                                                  | 34  |

| 1.4 Conclusions                                                               |     |

|                                                                               |     |

| CHAPTER 2: Characteristics of normally-on SiC JFETs                           |     |

| 2.1 Introduction                                                              |     |

| 2.2.1 Power device analyzer for parameter identification                      |     |

| 2.2.2 Static characteristics                                                  |     |

| 2.2.3 Transfer characteristics                                                |     |

|                                                                               |     |

| 2.2.4 On-state resistance                                                         | 41       |

|-----------------------------------------------------------------------------------|----------|

| 2.2.5 Leakage current measurement                                                 | 42       |

| 2.2.6 Dynamic characteristics                                                     | 42       |

| 2.2.7 Switching characteristics                                                   | 46       |

| 2.3 Robustness of normally-on SiC JFET                                            | 48       |

| 2.3.1 Short Circuit and Avalanche Breakdown Test Bench                            | 48       |

| 2.3.2 Robustness of SiC JFET in the short-circuit mode                            |          |

| 2.3.2.1 Description of short-circuit test bench                                   |          |

| 2.3.2.2 Drive signal in short circuit operations                                  |          |

| 2.3.2.3 Calculation of critical energy in short circuit mode                      |          |

| 2.3.2.4 Failure modes of SiC JFET in short-circuit tests                          |          |

| 2.3.3 Robustness of SiC JFET in the avalanche mode                                |          |

| 2.3.3.1 Description of the avalanche test bench.                                  |          |

| 2.3.3.2 Failures of normally-on SiC JFET in avalanche mode                        |          |

| 2.4 Conclusions                                                                   | 61       |

| CHAPTER 3: Solid state DC circuit breaker based on normally-on SiC JFETs          | 63       |

| 3.1 Introduction                                                                  |          |

| 3.2 Topologies and main components of the solid state DC circuit breaker base     | d on     |

| normally-on SiC JFETs                                                             |          |

| 3.3 Operating principle                                                           |          |

| 3.3.1 Concept of self-powered solid-state circuit breaker                         |          |

| 3.3.2 The operation of the protection driver                                      |          |

| 3.3.3 Gate voltage limitation principle                                           |          |

| 3.4 Simulations of normally-on SiC JFET and protective function                   |          |

| 3.4.1 Mathematical model of the normally-on SiC JFET                              |          |

| 3.4.1.1 Static model                                                              |          |

| 3.4.1.2 Dynamic model                                                             |          |

| 3.4.1.3 Temperature dependence                                                    |          |

| 3.4.1.4 Extraction of parameters                                                  |          |

| 3.4.2 Matlab/Simulink model                                                       |          |

| 3.4.3 Validation of the SiC JFET model                                            |          |

| 3.4.3.1 Validation of static characteristic                                       |          |

| 3.4.3.2 Validation of dynamic characteristic                                      |          |

| 3.4.4 Application in DC circuit breaker with normally-on SiC JFET                 |          |

| 3.5 Prototype design of the solid-state circuit breaker based on SiC JFETs        |          |

| 3.5.1 Design of forward-flyback converter for self-powered solid-state circuit by | reaker   |

| 81                                                                                | 0.1      |

| 3.5.1.1 Design specifications of the forward-flyback converter                    |          |

| 3.5.1.2 Design of forward-flyback transformer                                     |          |

| 3.5.2 Selection of components of voltage sensor                                   |          |

| 3.6 Experimental validation                                                       |          |

| 3.6.1 Gate voltage limitation function of the forward-flyback converter           |          |

| 3.6.2 Operation of the voltage sensor                                             | 80<br>20 |

| 3.6.3 Operation of the converter driving the JFET                                 |          |

| 3.7 Conclusions                                                                   |          |

| Conclusions and perspectives                                                      |          |

| Conclusions                                                                       |          |

| Perspectives                                                                      |          |

| The affection of the temperature to the operation of solid-state circuit breaker  |          |

| Challenges regarding parallel connection of SiC JFETs.                            | 91       |

| Publications                                                                      | 92       |

| . 93 | 3  |

|------|----|

| •    | 93 |

# LIST OF FIGURES

| Figure 0-1 Final energy consumption breakdown into sectors in the EU-27, 2010 [2] 1                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 0-2 Final electricity consumption breakdown into sectors in the EU-27, 2010 [2] 2                                                     |

| Figure 1-1 Unipolar single bus DC microgrid [22]                                                                                             |

| Figure 1-2 A bipolar single bus DC microgrid [22]                                                                                            |

| Figure 1-3 A typical DC microgrid configuration utilizes DC circuit breakers                                                                 |

| Figure 1-4 Ring bus DC microgrid [22]9                                                                                                       |

| Figure 1-5 Two types of short circuit faults in DC systems: (a) pole-to-ground fault, (b) pole-to-pole fault                                 |

| Figure 1-6 Equivalent short circuit diagram of one DC source                                                                                 |

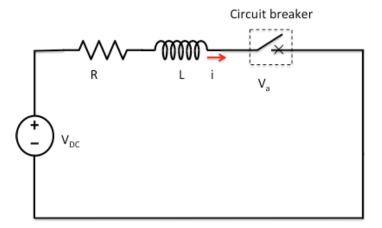

| Figure 1-7 Basic DC circuit containing a circuit breaker with short circuit fault                                                            |

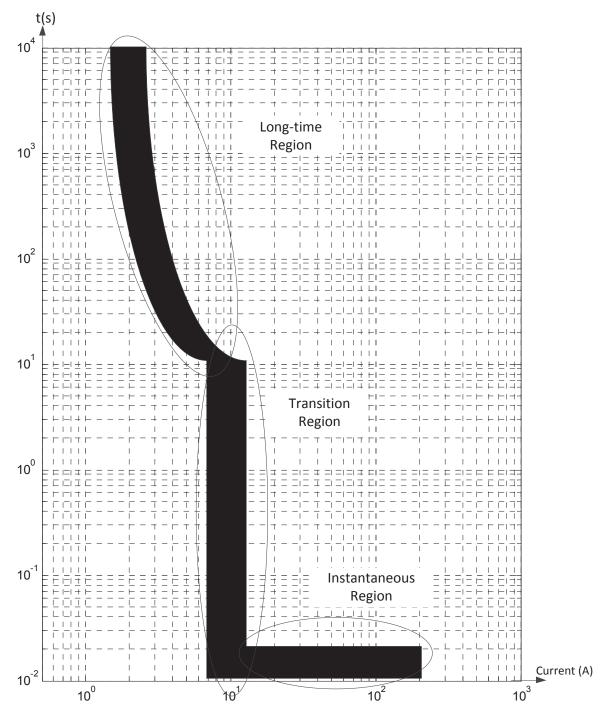

| Figure 1-8 Example of a typical time-current characteristic curve of a thermal-magnetic trigger system for a mechanical circuit breaker [33] |

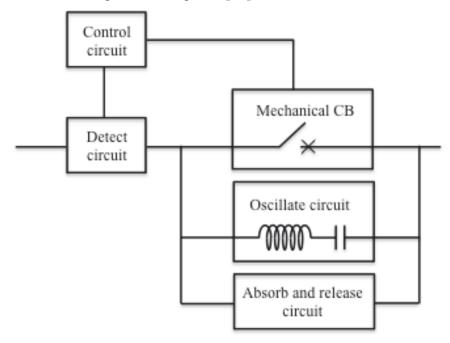

| Figure 1-9 Basic structure of the mechanical DC circuit breaker [37]                                                                         |

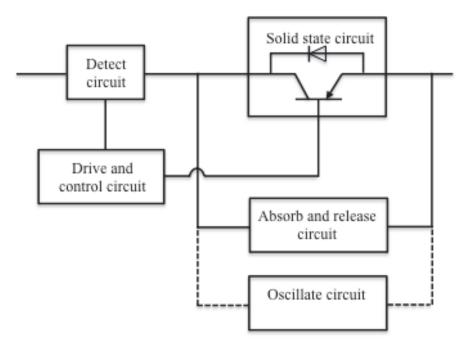

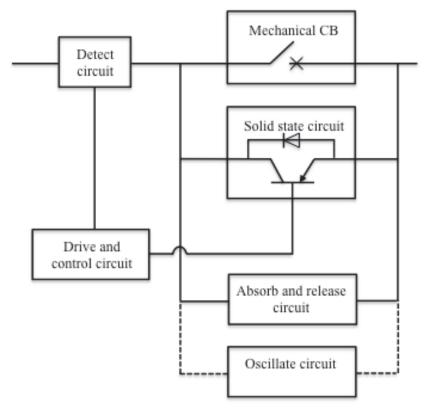

| Figure 1-10 Basic structure of solid state DC circuit [37]                                                                                   |

| Figure 1-11 Basic structure of hybrid DC circuit [37]                                                                                        |

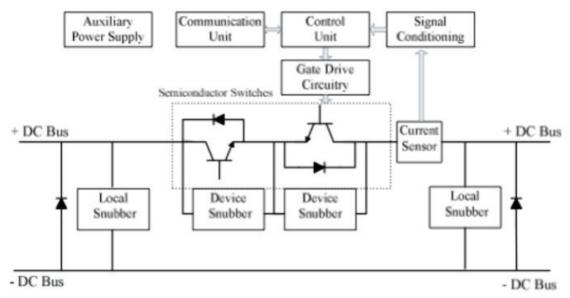

| Figure 1-12 A generic bidirectional solid state DC breaker schematic diagram [36]                                                            |

| Figure 1-13 Unidirectional self-power SSCB using normally-on SiC JFET [40]                                                                   |

| Figure 1-14 Bidirectional self-power SSCB using normally-on SiC JFET [41]                                                                    |

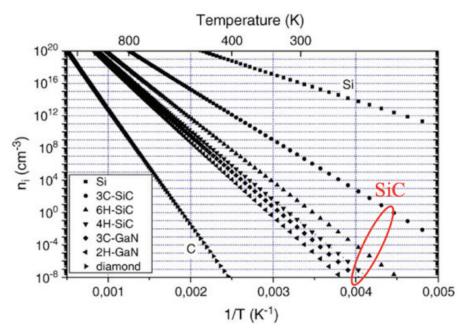

| Figure 1-15 Intrinsic carrier for various semiconductors VS reciprocal temperature [44] 20                                                   |

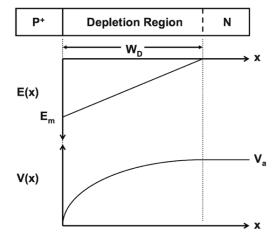

| Figure 1-16 Electric field and potential distribution for an abrupt parallel-plane $P^+/N$ junction                                          |

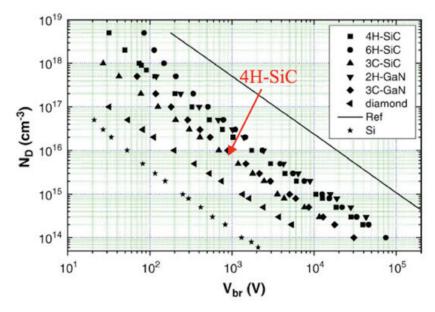

| Figure 1-17 Maximal doping level vs. theoretical breakdown voltage for several semiconductor materials [43], [44]                            |

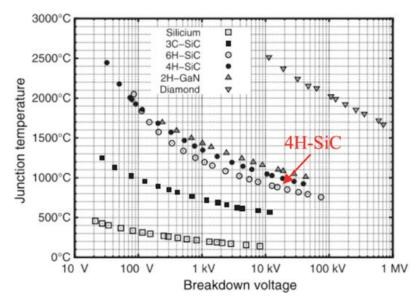

| Figure 1-18 Thermal runaway limits for various semiconductor materials [45]                                                                  |

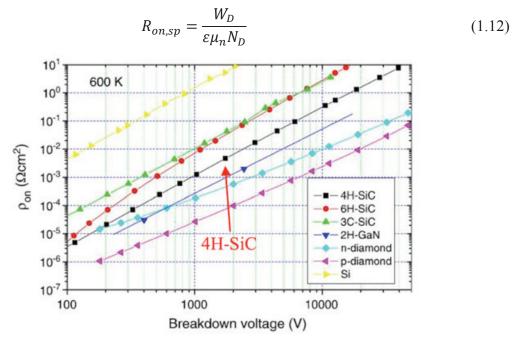

| Figure 1-19 Theoretical specific resistance of the epilayer as a function of breakdown voltage at 600 K [44]                                 |

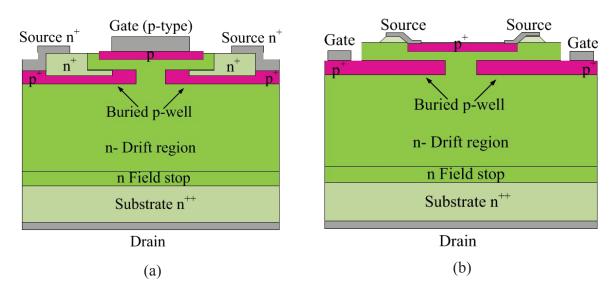

| Figure 1-20 SiCED Normally-on LVJFET (a) optimized for fast switching (b) optimized for low on-state resistance [47]                         |

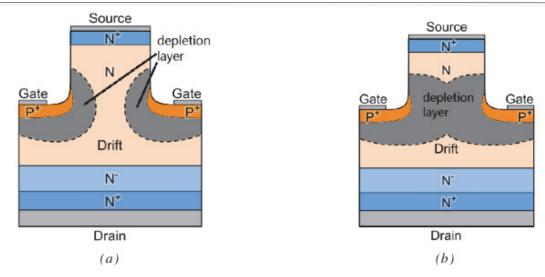

| Figure 1-21 SemiSouth (a) normally-on and (b) normally-off V-JFET [50]                                                                       |

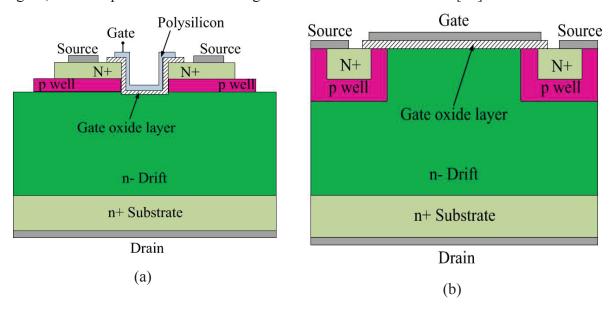

| Figure 1-22 (a) Cross-section of U-MOSFET and (b) Cross-section of D-MOSFET [47] $\dots$ 25                                                  |

| Figure 1-23 Simplified device cross section of a SiC power BJT with a two-zone etched [52]                                                   |

| Figure 1-24 Schematic of Unclamped Inductive Switching test for Avalanche mode [52] 27                                                       |

| Figure 1-25 $V_{DS}$ and $I_{D}$ of normally-off JFET in avalanche mode [52]                                                                 |

| Figure 1-26 Destructive test of normally-on SiC JFET in avalanche mode [52]                                                                  |

| Figure 1-27 $V_{DS}$ and $I_{DS}$ of MOSFET in avalanche mode [52]                                                                           |

| Figure 1-28 Destructive test of BJT in avalanche mode: (a) collector-emitter voltage and                                                     |

| collector current, (b) base-emitter voltage and base current [52]                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-29 Schematic of short-circuit test [53]                                                                                                                                                                         |

| Figure 1-30 Destructive test for normally-on JFET in current limitation mode ( $V_{DC}$ =400 V $T_{CASE}$ =25 $^{0}$ C) [54]                                                                                             |

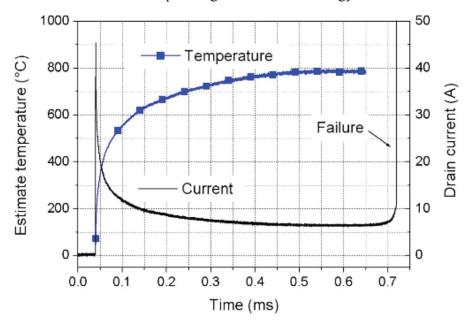

| Figure 1-31 Estimation of the temperature during a long term short circuit phase ( $V_{DC}$ =400 V $T_{CASE}$ =25 $^{0}$ C) [54]                                                                                         |

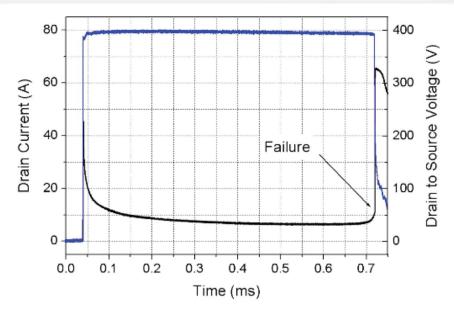

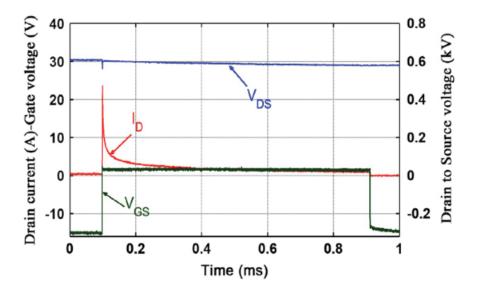

| Figure 1-32 Robustness of normally-off JFET under long-term short-circuit test [55] 3                                                                                                                                    |

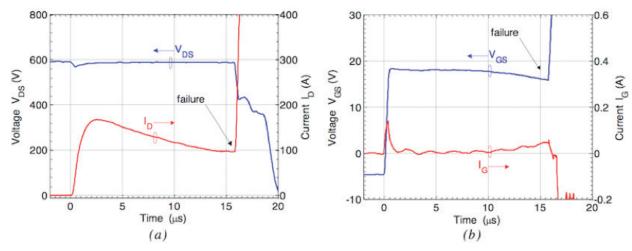

| Figure 1-33 Destructive test of a CMF20120D MOSFET (a) Drain and (b) Gate waveform fo $V_{DC}$ =600V and T=25 $^{0}$ C [56]                                                                                              |

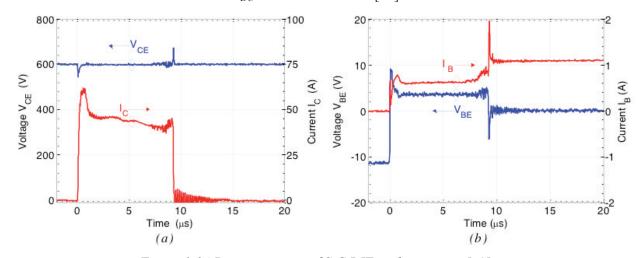

| Figure 1-34 Destructive test of SiC BJT in short circuit [52]                                                                                                                                                            |

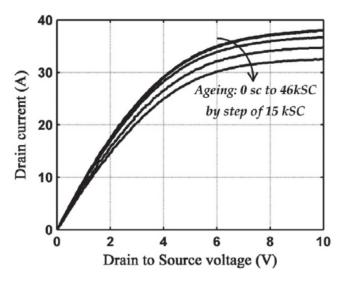

| Figure 1-35 Evolution of drain current with drain-source voltage for $V_{GS}$ =0 V, during aging of 100 m $\Omega$ SiC JFET (aging test conditions: $E = 540$ V, $T_{sc} = 100$ $\mu s$ , $T_{C} = 25$ $^{0}$ C) [58] 32 |

| Figure 1-36 Evolution of drain current with drain - source voltage ( $V_{GS}$ =0V) during aging o 300 m $\Omega$ SiC JFET (aging test conditions: E = 540 V, $T_{sc}$ = 200 $\mu s$ , $T_{C}$ = 25 $^{0}$ C) [58] 33     |

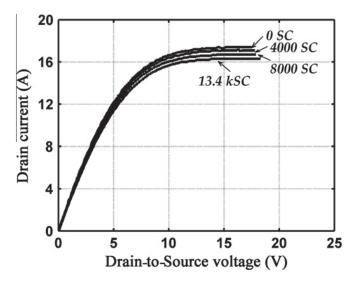

| Figure 1-37 (a) Gate current, (b) room in gate current (c) gate-source voltage and (d) drain current of SiC MOSFET during repetitive short circuit, with $t_{sc} = 3 \mu s$ , $T_C = 25  ^{0}C$ [52]33                   |

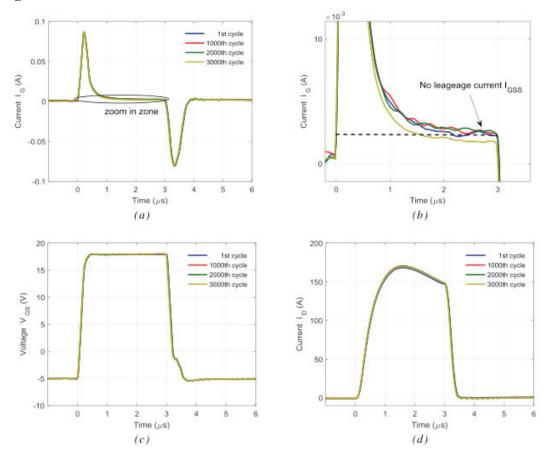

| Figure 1-38 (a) Gate current, (b) room in gate current (c) gate-source voltage and (d) drain current of SiC MOSFET during repetitive short circuit, with $t_{sc} = 7 \mu s$ , $T_C = 25  ^{0}C$ [52]34                   |

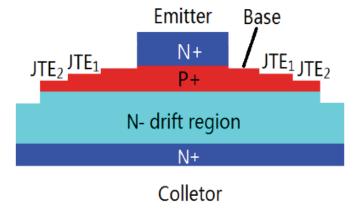

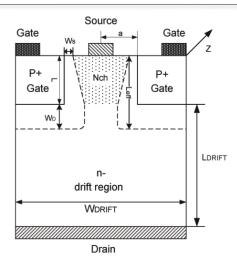

| Figure 2-1 Cross section of the normally-on vertical SiC JFET [62]                                                                                                                                                       |

| Figure 2-2 Photograph of B1506A power device analyzer for circuit design from Keysigh Technology [64]                                                                                                                    |

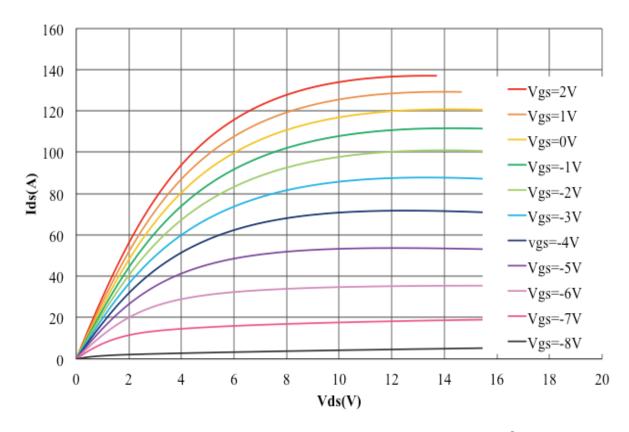

| Figure 2-3 Static characteristics of UJN 1205K JFET at $T_{CASE} = 25$ $^{0}C$                                                                                                                                           |

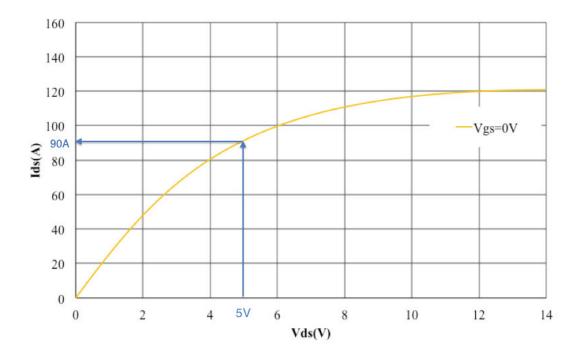

| Figure 2-4 Identify the current limiting value for solid state circuit breaker                                                                                                                                           |

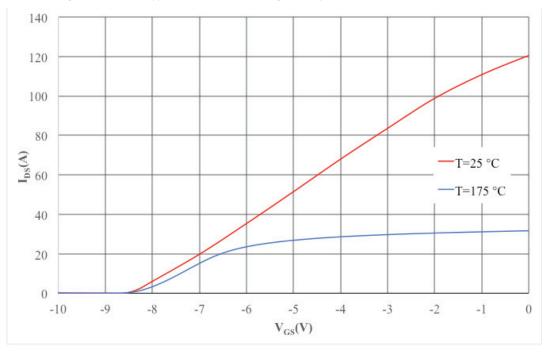

| Figure 2-5 Transfer characteristics of UJN 1205K JFET at $V_{DS}$ = 5 V, $T_{CASE}$ = 25 $^{0}$ C and $T_{CASE}$ = 175 $^{0}$ C                                                                                          |

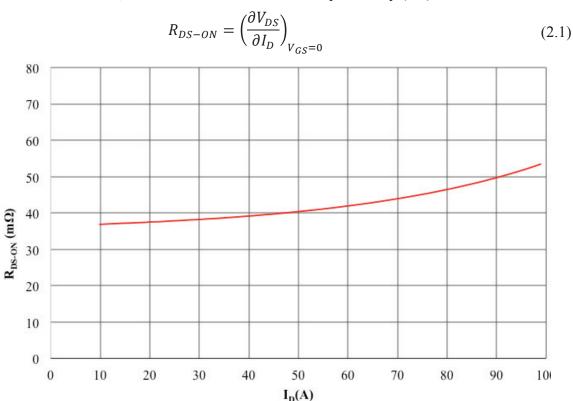

| Figure 2-6 Typical drain-source resistance of UJN 1205K JFET at $V_{GS} = 0$ V, $T_{CASE} = 25^{\circ}$ C 4                                                                                                              |

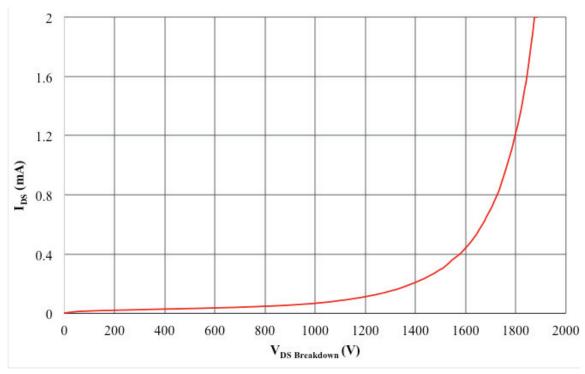

| Figure 2-7 Typical drain-source leakage current of UJN 1205K JFET at $V_{GS}$ = -20 V, $T_{CASE}$ = 25 $^{0}C$                                                                                                           |

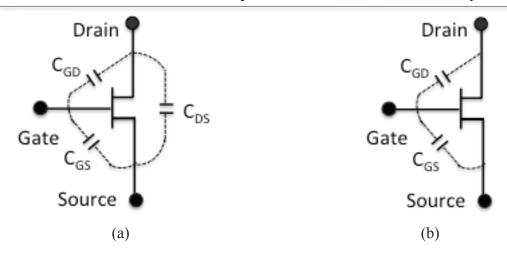

| Figure 2-8 Schematic diagram of a normally-on SiC JFET (a) with drain-source capacitance and (b) without drain-source capacitance                                                                                        |

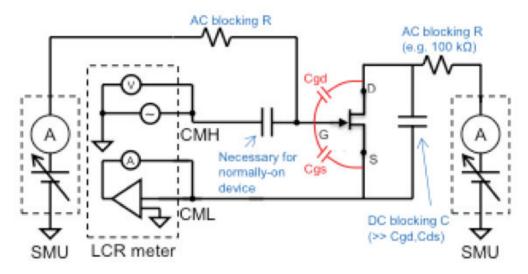

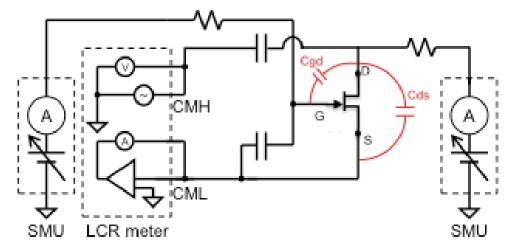

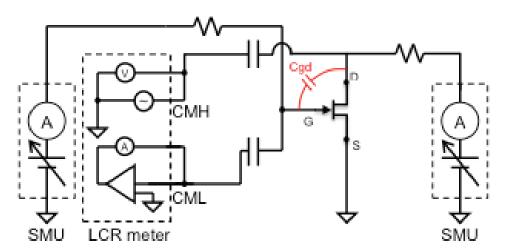

| Figure 2-9 Circuit diagram to measure Ciss                                                                                                                                                                               |

| Figure 2-10 Circuit diagram to measure Coss                                                                                                                                                                              |

| Figure 2-11 Circuit diagram to measure Crss                                                                                                                                                                              |

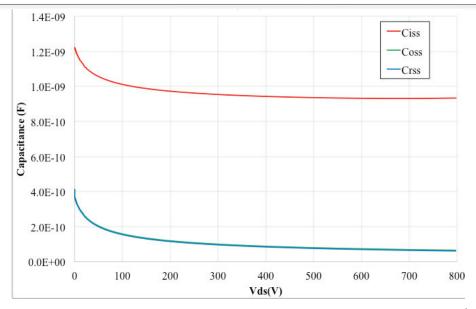

| Figure 2-12 Typical capacitances of UJN 1205K JFET at 100 kHz, $T_{CASE} = 25$ $^{0}C$ 4:                                                                                                                                |

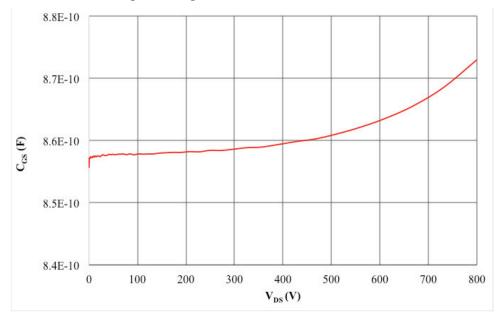

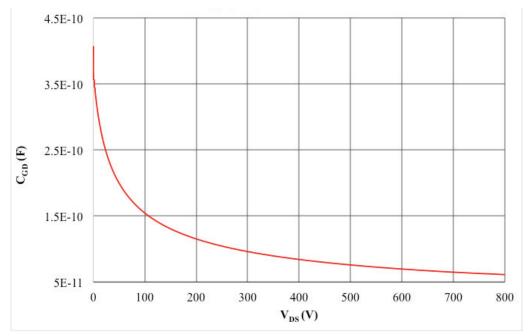

| Figure 2-13 Variation of gate-source capacitance to drain-source voltage of UJN 1205K JFE at $f = 100$ kHz, $T_{CASE} = 25$ $^{0}C$                                                                                      |

| Figure 2-14 Variation of gate-drain capacitance to drain-source voltage of UJN 1205K JFE at $f = 100$ kHz, $T_{CASE} = 25$ $^{0}C$                                                                                       |

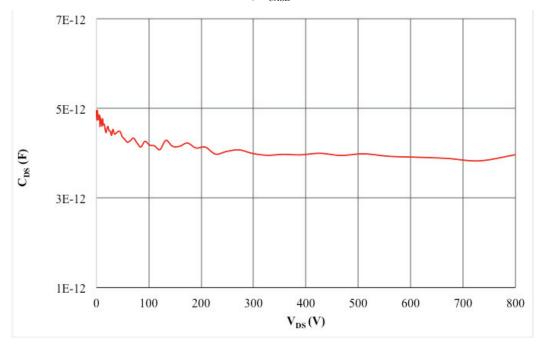

| Figure 2-15 Variation of drain-source capacitance to drain-source voltage of UJN 1205F JFET at $f = 100 \text{ kHz}$ , $T_{CASE} = 25  ^{0}\text{C}$                                                                     |

| Figure 2-16 Unclamped Inductive Switching test circuit                                                                                                                             | 47         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 2-17 Unclamped Inductive Switching test bench                                                                                                                               | 47         |

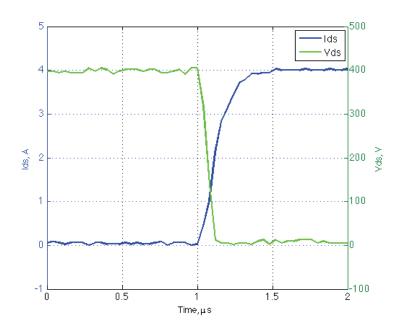

| Figure 2-18 Turn off UJN 1205K JFET under single pulse unclamped inductive swit                                                                                                    | _          |

| Figure 2-19 Turn on UJN 1205K JFET under single pulse unclamped inductive swit                                                                                                     | ching test |

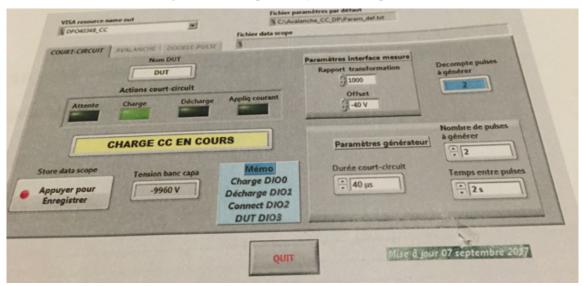

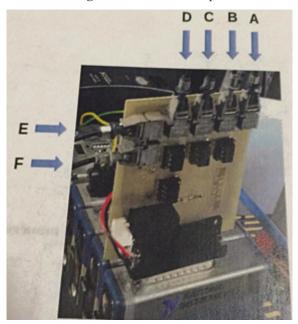

| Figure 2-20 The picture of SCAB components                                                                                                                                         | 49         |

| Figure 2-21 Control desktop                                                                                                                                                        | 49         |

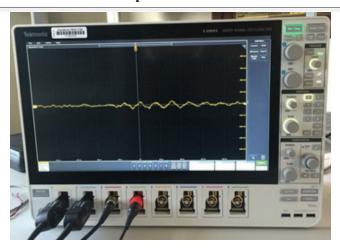

| Figure 2-22 Oscilloscope                                                                                                                                                           | 50         |

| Figure 2-23 Optical fiber connections                                                                                                                                              | 50         |

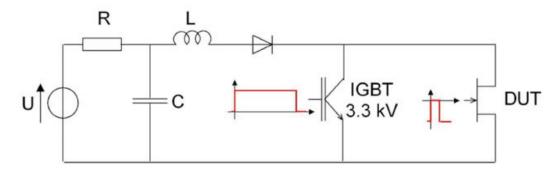

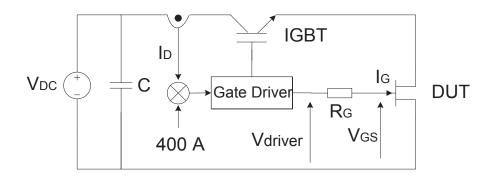

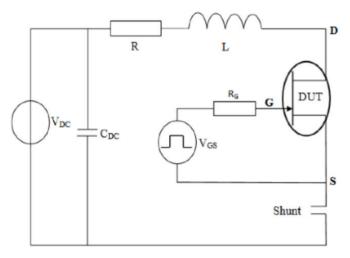

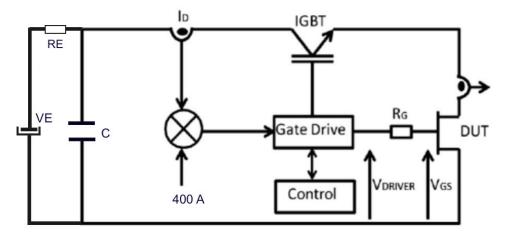

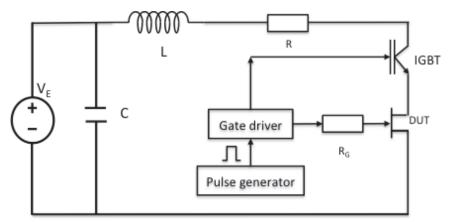

| Figure 2-24 Test circuit for short-circuit analysis                                                                                                                                | 51         |

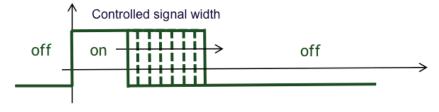

| Figure 2-25 Controlled signal during short circuit test                                                                                                                            | 51         |

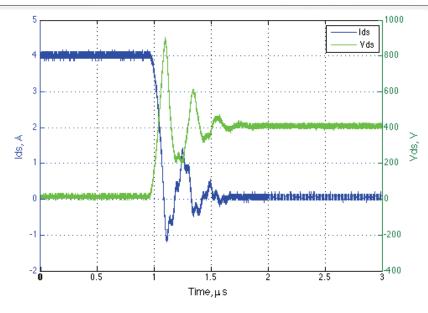

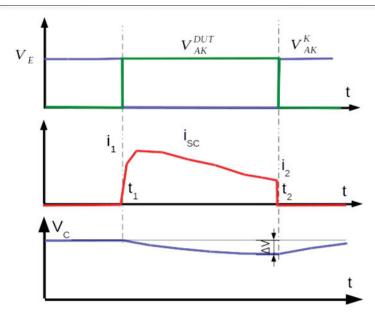

| Figure 2-26 Waveforms of voltage and current during short circuit test                                                                                                             | 52         |

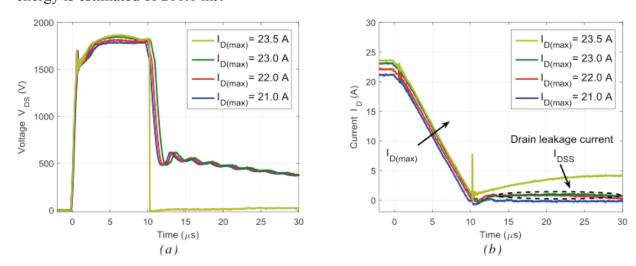

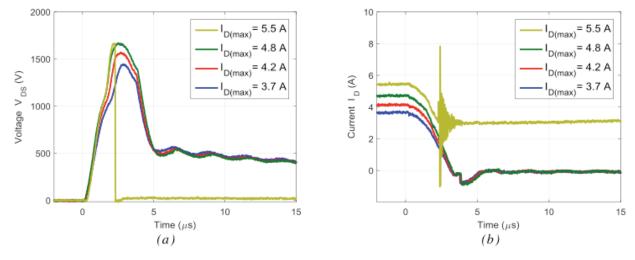

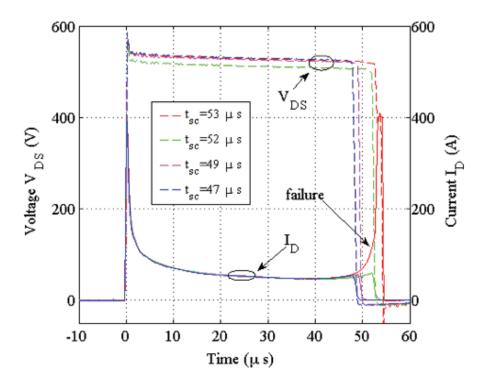

| Figure 2-27 Short-circuit behavior of 1200 V SiC JFET at $V_{supply} = 520$ V, $T_{CASE} = 2.0$                                                                                    |            |

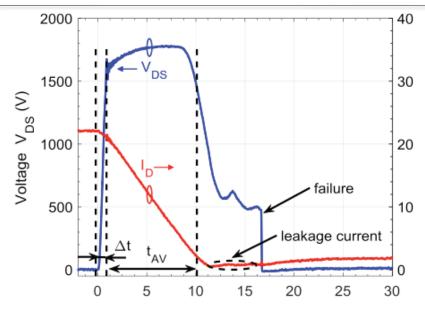

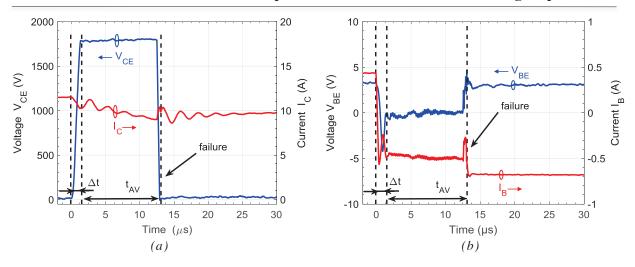

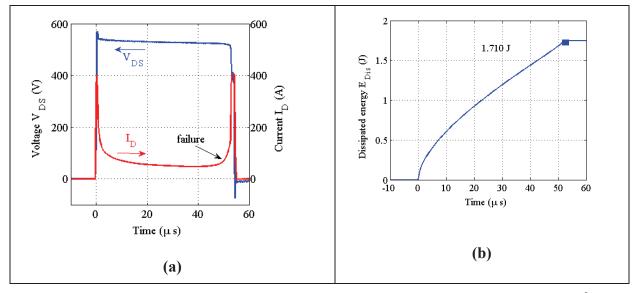

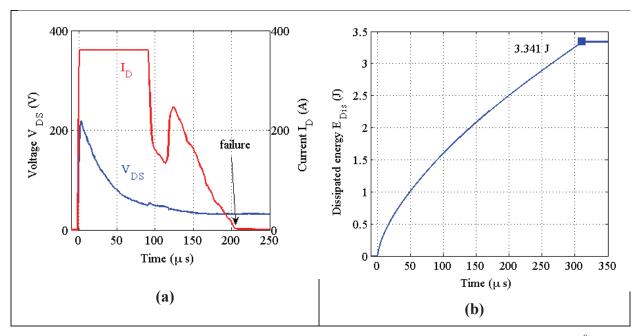

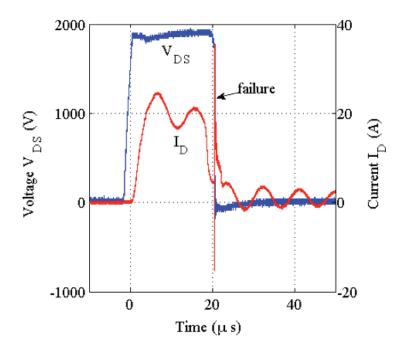

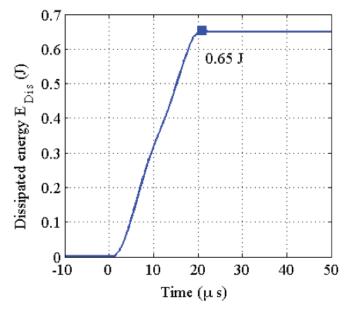

| Figure 2-28 (a) Failure voltage and current of 1200 V SiC JFET at $V_{supply} = 520$ V, T $^{0}$ C, $t_{sc} = 53$ $\mu s$ and (b) the dissipated energy at $t_{sc} = 52$ $\mu s$   |            |

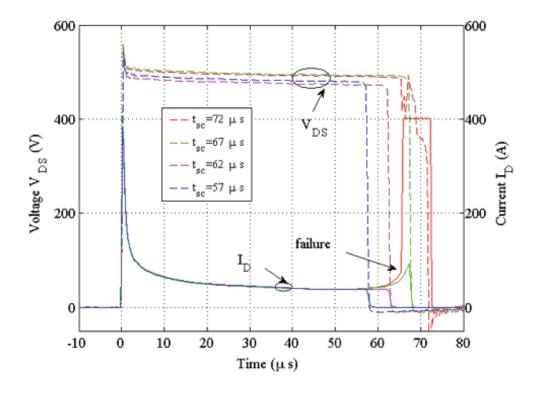

| Figure 2-29 Short circuit behavior of 1200 V SiC JFET at $V_{supply}$ = 477 V, $T_{CASE}$ = 25                                                                                     | 5 °C 54    |

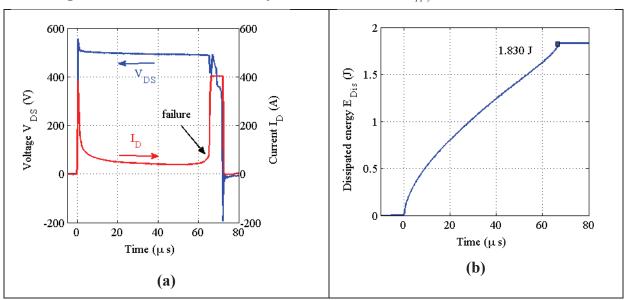

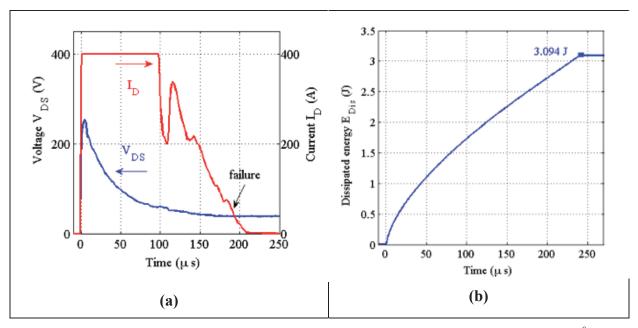

| Figure 2-30 (a) Failure voltage and current of 1200 V SiC JFET at $V_{supply} = 477$ V, T $^{0}$ C, $t_{sc} = 72$ $\mu s$ and (b) the dissipated energy at $t_{sc} = 67$ $\mu s$   |            |

| Figure 2-31 Short-circuit behavior of 1200 V SiC JFET at $V_{supply} = 340$ V, $T_{CASE} = 2.0$                                                                                    | 5 °C 55    |

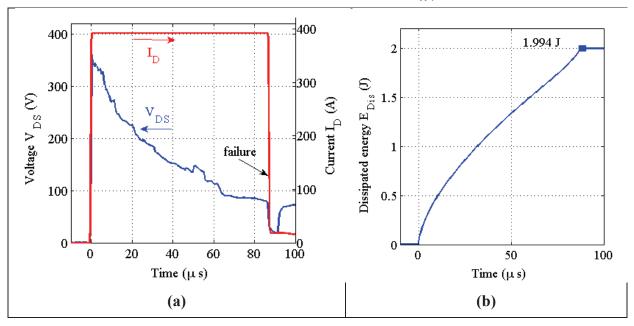

| Figure 2-32 (a) Failure voltage and current of 1200 V SiC JFET at $V_{supply} = 340$ V, T $^{0}$ C, $t_{sc} = 72$ $\mu s$ and (b) the dissipated energy at $t_{sc} = 87$ $\mu s$   |            |

| Figure 2-33 Short-circuit behavior of 1200 V SiC JFET at $V_{supply} = 250$ V, $T_{CASE} = 2.0$                                                                                    | 5 °C 56    |

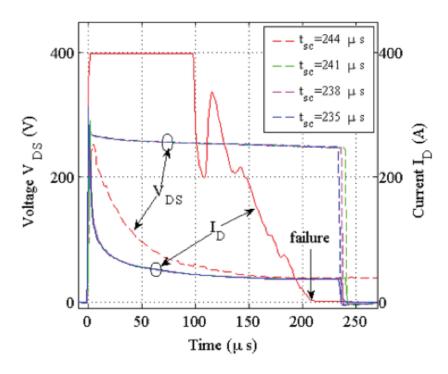

| Figure 2-34 (a) Failure voltage and current of 1200 V SiC JFET at $V_{supply} = 250$ V, T $^{0}$ C, $t_{sc} = 244$ $\mu s$ and (b) the dissipated energy at $t_{sc} = 241$ $\mu s$ |            |

| Figure 2-35 Short-circuit behavior of 1200 V SiC JFET at $V_{supply} = 210$ V, $T_{CASE} = 2.0$                                                                                    | 5 °C 57    |

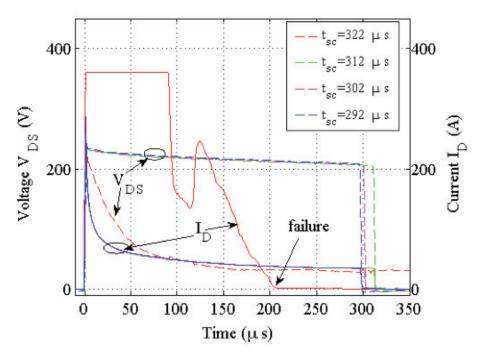

| Figure 2-36 (a) Failure voltage and current of 1200 V SiC JFET at $V_{supply} = 210$ V, T $^{0}$ C, $t_{sc} = 322$ $\mu s$ and (b) the dissipated energy at $t_{sc} = 312$ $\mu s$ |            |

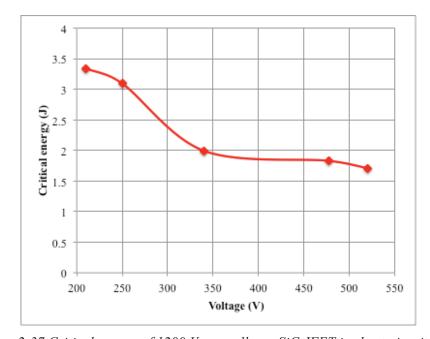

| Figure 2-37 Critical energy of 1200 V normally-on SiC JFET in short-circuit mode                                                                                                   | 58         |

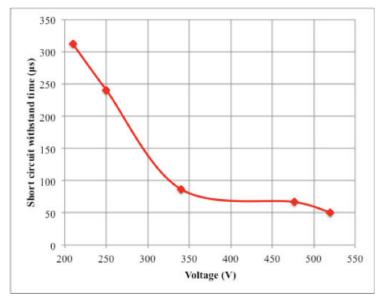

| Figure 2-38 Short circuit withstand time of 1200 V normally-on SiC JFET in sho                                                                                                     |            |

| Figure 2-39 Schematic of avalanche test circuit for 1200 V normally-on SiC JFET                                                                                                    | 59         |

| Figure 2-40 Typical voltage and current waveform in avalanche mode [69]                                                                                                            | 60         |

| Figure 2-41 $V_{DS}$ and $I_D$ of 1200 V normally-on SiC JFET in avalanche mode                                                                                                    | 61         |

| Figure 2-42 Dissipated energy of 1200 V normally-on SiC JFET in avalanche mode .                                                                                                   | 61         |

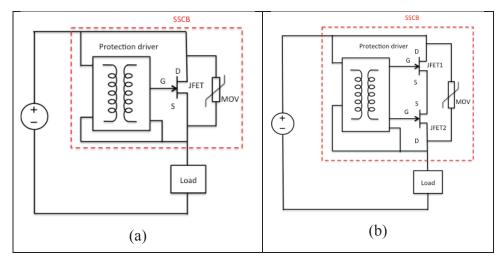

| Figure 3-1 (a) Unidirectional and (b) Bidirectional self-power solid state DC circuit b                                                                                            | reaker65   |

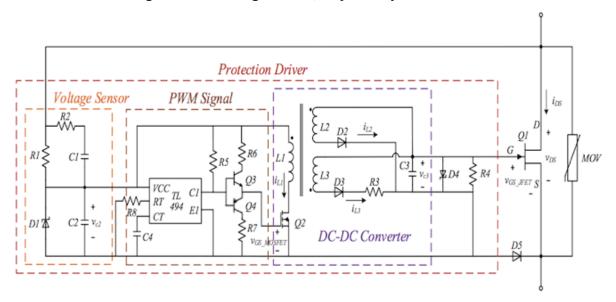

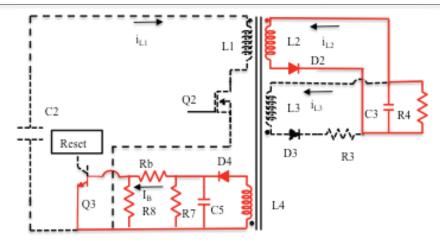

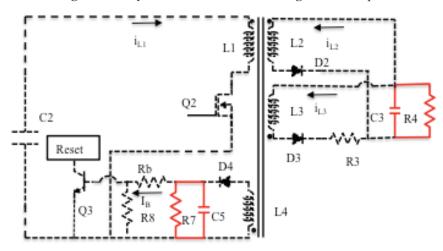

| Figure 3-2 Unidirectional solid state DC circuit breaker topology                                                                                                                  |            |

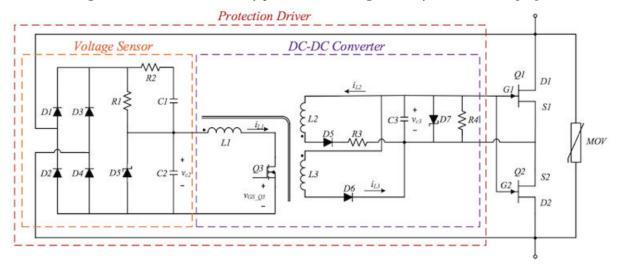

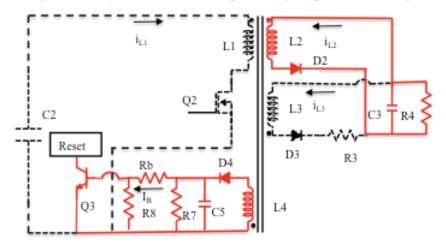

| Figure 3-3 Bidirectional solid state DC circuit breaker topology                                                                                                                   | 66         |

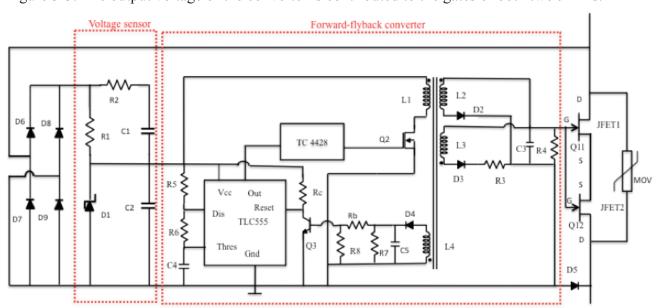

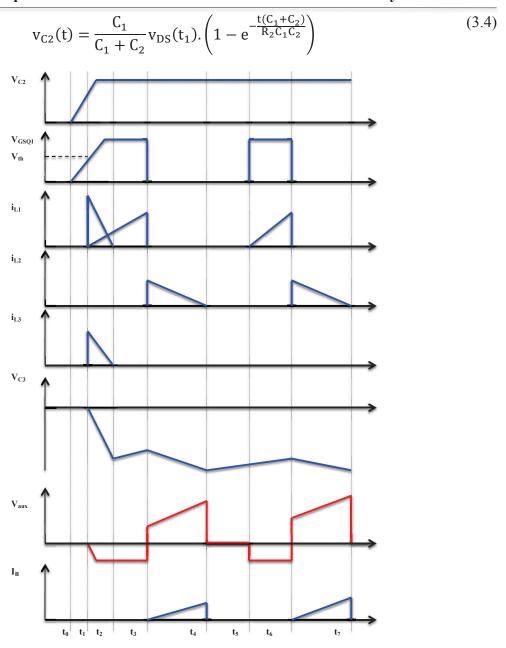

| Figure 3-4 The waveform of voltages and currents of the forward-flyback converter                                                                                                  | 68         |

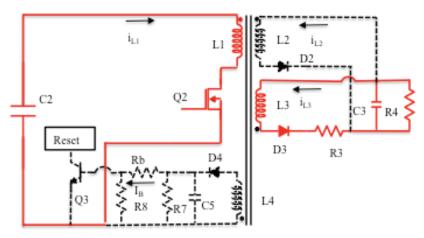

| Figure 3-5 Forward mode of forward-flyback converter                                                                                                                                       | 70 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

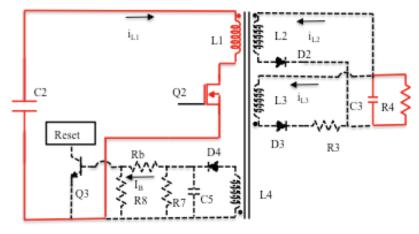

| Figure 3-6 Period both forward and flyback winding of the converter does not work                                                                                                          | 70 |

| Figure 3-7 Flyback mode with output voltage in permission range                                                                                                                            | 71 |

| Figure 3-8 Flyback mode with overvoltage at the output                                                                                                                                     | 71 |

| Figure 3-9 Idle mode                                                                                                                                                                       | 71 |

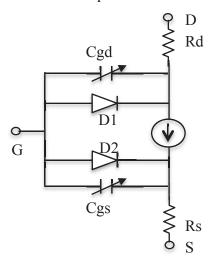

| Figure 3-10 – Equivalent circuit of SiC JFET model                                                                                                                                         | 73 |

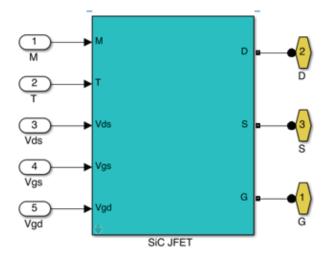

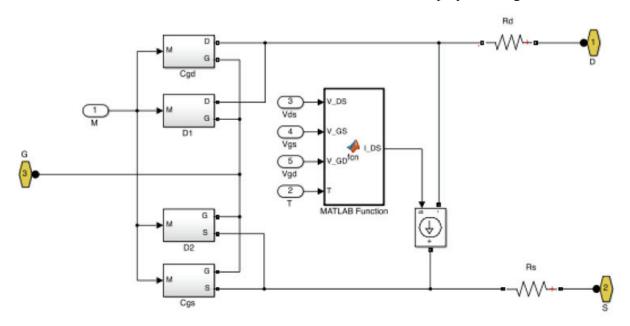

| Figure 3-11 SiC JFET block                                                                                                                                                                 | 76 |

| Figure 3-12 SiC JFET model                                                                                                                                                                 | 76 |

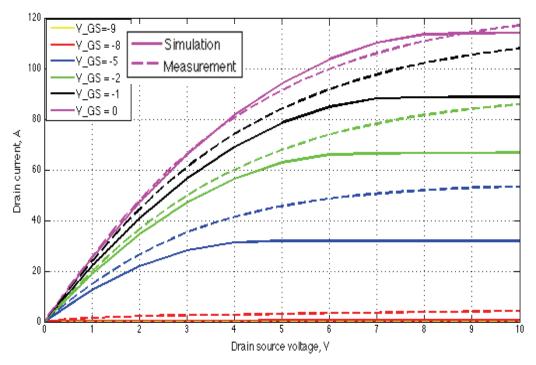

| Figure 3-13 Static characteristic, simulation results VS experimental results for a normal JFET                                                                                            |    |

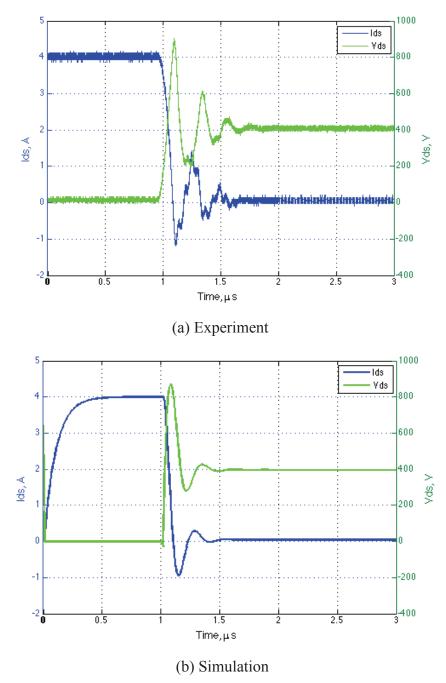

| Figure 3-14 Turn off JFET under single pulse unclamped inductive switching test                                                                                                            | 78 |

| Figure 3-15 Turn on JFET under single pulse unclamped inductive switching test                                                                                                             | 79 |

| Figure 3-16 Short circuit diagram                                                                                                                                                          | 80 |

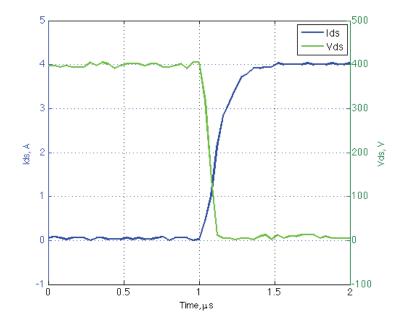

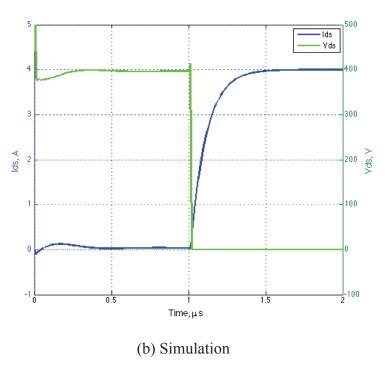

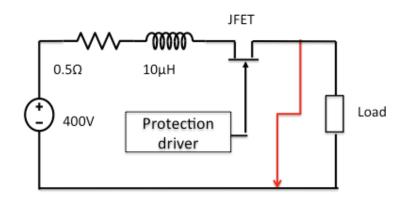

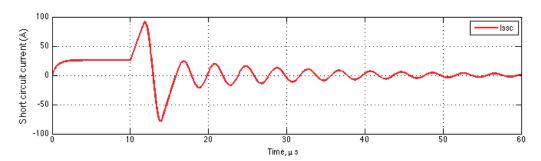

| Figure 3-17 Short circuit current                                                                                                                                                          | 80 |

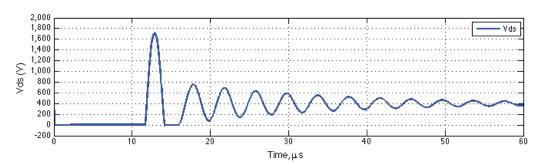

| Figure 3-18 Drains-source voltage during time JFET clearing short circuit fault                                                                                                            | 80 |

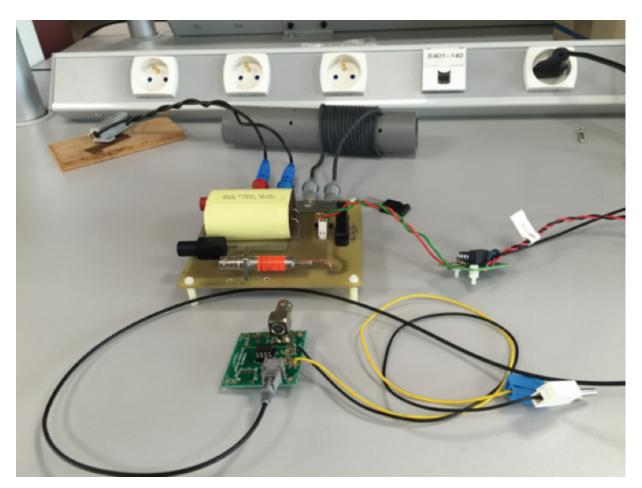

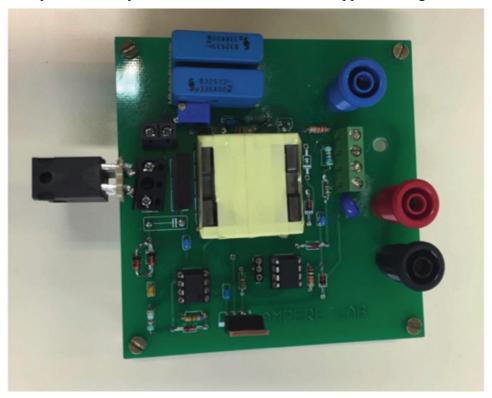

| Figure 3-19 SSCB prototype                                                                                                                                                                 | 85 |

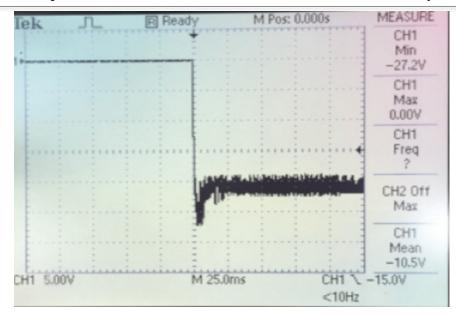

| Figure 3-20 Output voltage of the forward-flyback converter in case without voltage limitation (5 V/div)                                                                                   | _  |

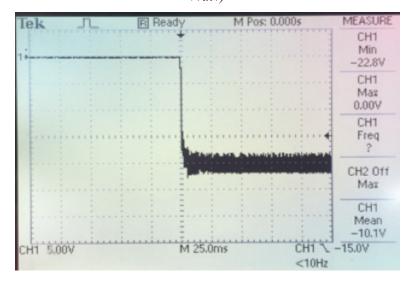

| Figure 3-21 Output voltage of forward-flyback converter with gate voltage limitation V/div)                                                                                                | `  |

| Figure 3-22 Waveform of voltage of C <sub>2</sub> (BLUE 2 V/div), voltage of C <sub>1</sub> (GREEN 0.5 V output voltage (PINK 5 V/div) and drain current (YEALLOW 1 A/div)                 |    |

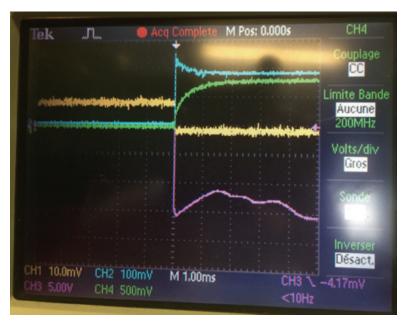

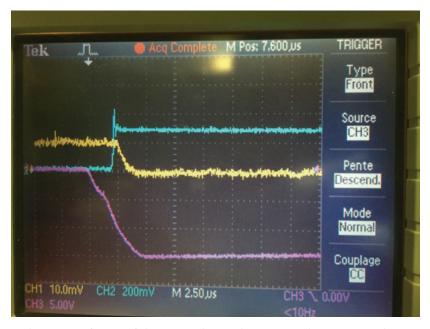

| Figure 3-23 Switching waveforms of the JFET driven by proposed protection driver. BLV $V_{DS}$ (4 V/div), YELLOW is $I_{DS}$ (0.1 A/div), PINK is $V_{GS}$ (5V/div), Time (2.5 $\mu$ s/div |    |

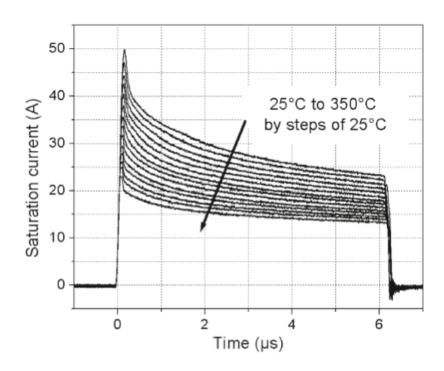

| Figure 4-1 Decrease of saturation current with temperature (E = 400 V) [54]                                                                                                                | 90 |

# LIST OF ABBREVIATIONS

6LoWPAN IPv6 over Low Power Wireless Personal Networks

AC Alternating Current

ANR The French National Research Agency

BJT Bipolar Junction Transistor

CBs Circuit Breakers

COAP Constrained Application Protocol

DC Direct Current

DSP Digital Signal Processor

DUT Device Under Test

EU European Union

EVs Electric Vehicles

GaN Gallium Nitride

GTO Gate Turn-Off thyristor

ICT Information and Communication Technologies

IEDs Intelligent Electronic Devices

IGBT Insulated Gate Bipolar Transistor

IGCT Integrated Gate-Commutated Thyristor

JFET Junction Field-Effect Transistor

JTE Junction Termination Extension

LCIS Laboratoire de Conception et d'Intégration des Systèmes

LEDs Light-Emitting Diode

LVDC Low Voltage Direct Current

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOV Metal-Oxide Varistor

PHEVs Plug-in Hybrid Electric Vehicles

PSS Primary Side Sensing

PWM Pulse Width Modulation

RPL Routing Protocol for Low Power and Lossy Networks

SCAB Short Circuit and Avalanche Breakdown Test Bench

SiC Silicon Carbide

SSCB Solid-state Circuit Breaker

UIS Unclamped Inductive Switching

# GENERAL INTRODUCTION

# **Energy consumption in domestic field**

# Current status of energy consumption in buildings

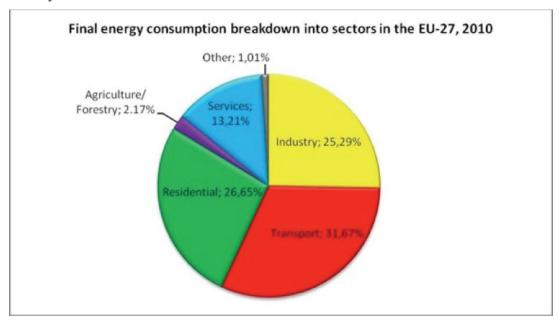

Energy consumption in buildings is divided into two categories, residential buildings and service buildings (or tertiary buildings). According to the report of ODYSSEE-MURE [1], buildings account for about 40% of total final energy consumption and around 55% of electricity consumption in the European Union (EU) in 2012. Buildings are the largest enduse sector with around two-thirds of the buildings consumptions for residential and one-third left for service as shown in Figure 0-1 and Figure 0-2. Reducing demand through the improved efficiency of devices and procedures in buildings would get a great benefit not only in the economy but also in ensuring stable energy future. By improving the energy efficiency of buildings, we could reduce total EU energy consumption by 5% to 6% and lower CO2 emission by about 5%.

Figure 0-1 Final energy consumption breakdown into sectors in the EU-27, 2010 [2]

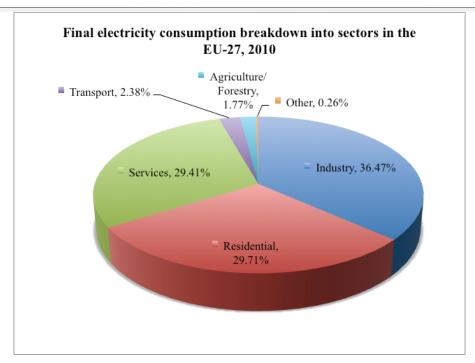

The electricity intensity is clearly increasing in most countries in services, because of the growing number of new appliances, such as IT devices, linked to the development of the internet and of new telecommunication types, as well as a spread of air conditioning. At the EU level, the increase of electricity consumption in services between 2008 and 2012 is mainly due to structural changes, and to a lesser extent, to increase comfort and productivity increases due to the diffusion of ICT and air conditioning.

# Policies to promote energy efficiency

Energy efficiency and renewable energy entail multiple benefits beyond energy savings and CO2 emission reductions. In recent years, EU countries have many policies to promote energy efficiency and renewable energy.

Figure 0-2 Final electricity consumption breakdown into sectors in the EU-27, 2010 [2]

The 2010 Energy Performance of Buildings Directive and the 2012 Energy Efficiency Directive [2] are the EU's main legislation when it comes to reducing the energy consumption of buildings.

Under the Energy Performance of Buildings Directive:

- Energy performance certificates are to be included in all advertisements for the sale or rental of buildings;

- EU countries must establish inspection schemes for heating and air conditioning systems or put in place measures with equivalent effect;

- All new buildings must be nearly zero-energy buildings by 31 December 2020 (public buildings by 31 December 2018);

- EU countries must set minimum energy performance requirements for new buildings, for the major renovation of buildings and for the replacement or retrofit of building elements (heating and cooling systems, roofs, walls, etc.);

- EU countries have to draw up lists of national financial measures to improve the energy efficiency of buildings;

Under the Energy Efficiency Directive:

- EU countries make energy efficient renovations to at least 3% of buildings owned and occupied by central government;

- EU governments should only purchase buildings which are highly energy efficient;

- EU countries must draw-up long-term national building renovation strategies which can be included in their National Energy Efficiency Action Plans.

The policies as presented above lead to a big change in domestic loads and rapidly in distributed generations as following.

# The increase of renewable energy sources

The rapid depletion of the conventional fossil fuels, energy crisis, and environmental pollution are agents to promote the development of many distributed generations in recent years. These distributed generations make use of renewable energy sources such as solar,

wind, biomass, fuel cells etc. to generate electricity or heat. The cost of renewable energy technologies is on a falling trend and is expected to reduce further as demand and production increases, and becomes competitive with classical generations. Almost renewable energy generators are intrinsically DC sources, for example, photovoltaic panels (PVs), small wind turbines or fuel cells. Therefore DC-AC inverters are used to in order to integrate these generators into the power system. These renewable energy sources could replace the using of fossil fuels as oil and coal, reduce the CO2 emissions, ensure security energy and sustainable development.

# The development of DC Loads

The DC loads are growing rapidly nowadays. The policies to promote energy efficiency, typically low-energy buildings and zero-energy buildings, of many countries in the world are the first reason [3]. The second, many works have shown the fact that new DC loads have energy efficient higher than AC loads and most of the tertiary building electric loads could be fed directly with DC power [4]. DC appliances include communication technologies and all consumer electronics, such as computers, telephones, televisions, compact fluorescent lighting with electronic ballasts, light-emitting diodes (LEDs), and efficient DC motors. Fluorescent and LED lighting uses one-quarter of the power consumption, or less than the traditional incandescent lighting. It is replacing in the residential and commercial sectors. Brushless DC permanent magnet motors can save 5-15% of the energy used by traditional AC induction motors, and up to 30-50% in variable-speed applications for pumping, ventilation, refrigeration, and space cooling. DC-motor-driven heat pump technologies for water and space heating can also displace conventional resistance heating with a savings of 50% or more. In addition to DC-internal appliances, electric vehicles (EVs) and plug-in hybrid electric vehicles (PHEVs) are expected to constitute a rapidly growing pure DC load in the foreseeable future.

# Why a DC microgrid?

Currently, most of available architectures for electrical energy distribution are mainly centralized with AC topologies due to the fact that simple AC transformers can step up and down voltages to facilitate power system. The DC grid mainly applies for high-voltage transmission system to transport electricity in a very long distance. In low voltage system, DC only exists in ships, aircrafts, or railway applications. However, the significant change in both domestic loads, and renewable energy sources make the electrical manager consider DC as a viable alternative to improve energy efficiency and reliability of the electric system. In addition, the advances in power electronic technology recently make DC distribution become more attractive than AC system. The first reason is challenges the operating of the electric power system. The intermittent and unpredictable nature of renewable energy sources, such as wind turbine and photovoltaic, remains an issue for their integration into the public grid resulting in fluctuations of voltage and/or frequency, harmonic pollution, difficult in load management. The second, in traditional AC power system, PV generators produce DC power that is converted to AC to supply electric power system; then, this power has to be inverted to DC for many end users as mentioned above. This requires multi-stage DC-AC and AC-DC conversions, causing great amount of power losses, due to the AC reactive power consumption, and the converter losses. In order to increase the integration level of renewable energies and energy efficiency, the DC microgrid is proposed. The main difference of the microgrid from a conventional power generation is that the power generators are usually small and they are distributed and located in close proximity to the energy users. The major advantages of a DC microgrid in comparison with AC grid are:

- DC grid maximizes the energy efficiency by avoiding multi-state converters and reducing conversion losses by using DC-DC converters.

- DC grid is simple in integrating with renewable energy sources without regard to matching phases, only voltage needs to be stable.

- DC grid is easy in coupling with electricity storage systems like batteries, supercapacitorsn, and DC load.

The DC microgrid can be applied in various fields, for example, commercial and office buildings, smart homes, data centers, shipboards, and aircraft, etc.

#### **Motivations**

While many research concentrates on the control strategies and energy management in the DC microgrids [5]–[8]the protection issue receives inadequate attention and lack of regulations and experiences. Protection in DC grids is more difficult than that in AC grid due to the continuous arc, higher short circuit current value and fault rate of rising. Furthermore, the DC distributed grids are composed of many electronic and semiconductor switching devices, which should withstand the overcurrent from 3 to 5 times rated values in some microseconds. In order to ensure the safety of these systems, the protection devices have to interrupt the faults in a very short time (some tens of microseconds). Mechanical circuit breakers, which have a response time in tens of milliseconds, seem not to meet the safety requirements of DC microgrid. The lack of efficient protection device is one of barriers to develop DC microgrid in the distributed system. Recent studies have indicated that solid-state DC circuit breaker (SSCB), which uses semiconductor device as main switch instead of mechanical switch, offers a great protection device for DC microgrid due to its fast response time can solve this problem.

# Research objectives and approach

# Link with the ANR C3µ project

Ampere Laboratory cooperates with "Laboratoire de Conception et d'Intégration des Systèmes" (LCIS) carry out an ANR (The French National Research Agency) C3μ project in order to develop a meshed DC microgrid.

There exist numerous recommendations at the European or the National levels to improve the energy efficiency particularly in housings and buildings. DC microgrid or LVDC (Low Voltage Direct Current) was proposed some years ago for housing and office buildings to take advantage of the PV local production. Such smart grids increase the efficiency of the PV to user power chain due to the elimination of inverters and PFCs (Power Factor Corrector) needed in a classical AC-grid. Although most studies in the microgrids topic concern AC-grid because of the industrial standards, most of the modern office and housing equipment are DC loads or have DC voltage level, such as LED lightings, office automation devices, data centers, electric vehicle plugs, building elevators and the like. Power-line communication (including the high-speed Internet) is fully compatible with LVDC if twisted pairs of DC lines are used. However, most studies on DC-grid only concern point-to-point DC links. The meshed DC grid raises some problems to be investigated: voltage control, power flow control and stability of the grid. These meshed DC grids have rarely been investigated until now. A meshed DC grid may include loops. Nevertheless, the loops may be useful for controlling the power flows, enabling redundancy or simplifying the sizing. If such issues are difficult to be studied in super-grid and distribution grids, because of the cost of such demonstrators, they are much easier to test them on a DC microgrid. It includes a connection to the AC-grid with a circuit breaker, which may be a DC breaker or a standard AC breaker if placed between the

AC-grid and the inverter. The DC circuit breaker may be smart and used as the interface for the communication between the microgrid and the AC-grid. The AC-DC inverter is bidirectional, it serves to both rectify (AC-DC) power from the grid to the building distribution system and invert (DC-AC) excess power from the DC sources to the AC grid. The DC microgrid may include one or more energy sources like solar cells, batteries or generators. DC-DC devices that receive power directly from the photovoltaic arrays or other sources convert them to the DC voltage bus (400 V DC). Furthermore, the grid includes an Electric Vehicle (EV) plugged into the grid, which yields possible redundancy that may be studied by a breaker for fault emulations (break emulator). Some energy storages (batteries or supercapacitors) may also be included because of the interest in smoothing the PV generation. Finally, smart switches may control the LED lightings by sending signals into the grid. Few studies concern a decentralized control of the grid, even if such concept leads to very robust systems. Some issues also concerning the DC bus itself impact the efficiency, particularly at the life-cycle assessment level, because of the need for copper. The smart plugs and DC breakers have to manage the security of the connection in case of faults. Finally, such new DC microgrids represent a clear advantage in term of efficiency with respect to AC-grid. However numerous scientific issues have to be studied as listed above. The topic represents an advance research area and fits very well within the ANR Call.

As the electrical wiring is not similar to classical network architectures (bus, star or ring-shaped) but has a free topology, we will analyze the data exchanges suitable to meet the criteria for robust control and supervision both at the system and component levels. Nonetheless, to provide consistent IP network interfaces we propose to specify the 6LoWPAN protocol that provides robust control with a reduced bandwidth (COAP) and routing (RPL) regardless the network topology on AC and DC power line and already validated in the wireless use cases. The use of a DC plug with communication capacity as the unit element of the power network will allow an efficient management of the power and a more accurate measurement and dispatch of the energy flow.

The aim of the  $C3\mu$  project is to build a benchmark platform of a meshed DC microgrid for delivery of electrical energy in the interior of the buildings for tertiary, commercial or residential buildings, with a decentralized management system to distribute needs and to associate in the most efficient way intermittent renewable sources of energy. The project is investigating the energy-saving potential, benefits, barriers, and safety of using DC microgrid to use local renewable energy systems directly in their DC forms, rather than converting them to AC currents and finally used in DC loads. The project is composed of 5 tasks:

- Design and realization of elementary DC power management components;

- Consumption measure, transmission and data processing for exchange;

- Development the platform to estimate gains of DC microgrid solution;

- Design of protocol and communication electronics for the grid;

- Modeling energy management and reliability of the DC grid; this will be performed by building a Matlab/Simulink platform in order to simulate the meshed DC microgrid.

# **Research Objectives and Thesis Outline**

My work under the sponsor of Glink project Erasmus Mundus program is connected to the ANR C3µ project but concentrates on the protection in DC microgrid issue. The objectives of the thesis are composed of two main parts. The first is to propose a DC circuit breaker, which will be used to protect for a meshed DC microgrid from short circuit current. The second goal is to build a mathematical model of the JFET in order to simulate the operation of proposed

DC circuit breaker in Matlab/Simulink environment, which will be used in the simulation platform of the ANR C3µ project.

The thesis is divided into 3 main chapters as follows:

In chapter 1, the protection in DC microgrid in literature will be reviewed. The features of the short circuit in DC microgrid are analyzed in order to indicate the requirements for protection devices. Then short circuit detection methods and solid state DC circuit breaker topologies are evaluated to select the most suitable method for the DC circuit breaker application. At the last of this chapter, the thesis will compare semiconductor devices, which can be used as main switches in the DC circuit breakers (IGBTs, MOSFETs, JFETs), in on-state losses and robustness with the short circuit. The failure modes of semiconductor switches are also mentioned here. These analyses allow us to select the SiC JFET device as the most suitable for fast and robust DC breaker solution.

In chapter 2, characteristics of a commercial normally-on SiC JFET are investigated. Effectively, the mathematical model approaches are based on the electrical parameters of the semiconductor topology. To extract these parameters, static and dynamic measurements are implemented to select the rated parameters for the DC breaker. The tests with the JFET in short circuit and avalanche modes will be also performed; and the critical energy in each case will be calculated.

Chapter 3 will propose an original DC circuit breaker configuration, which can automatically break/interrupt when a short circuit occurs in a very fast time. The operation of protection driver, which is composed of a voltage sensor and a forward-flyback converter, is described clearly in this chapter. The requirement on safety and reliability in operation will be also considered during the design process. The simulations of the original SiC JFET model in Matlab Simulink environment will be carried out in order to investigate the behaviors of the DC circuit breaker when it operates to protect the DC grid again overcurrent faults. Then the selection of devices of protection driver will be described in detail. Lastly, the validation tests are performed to verify proposed principle of the solid state DC circuit breaker.

Finally, conclusions and perspectives are given.

# CHAPTER 1: STATE OF THE ART IN DC MICROGRID PROTECTION

# 1.1 Introduction

This chapter presents a brief overview of the protection in the DC microgrid. In the first part, the basic concept of a DC microgrid is defined; and main components, some typical topologies, and applications are also introduced. The functions of protection devices and locations they should be placed in each type of configurations are discussed. Then, the chapter addresses types of short circuit and the comparison between the short circuit in the DC system and that in AC system. Due to the fact that there is no zero current crossing, an arc that appears upon breaking DC current cannot be extinguished naturally, making the protection of DC microgrid a difficult problem. This challenge results in harder requirements for DC circuit breakers in comparison with the case of AC.

The main part of the chapter is devoted to describing solid state DC circuit breaker technology. The application of power semiconductor devices to overcome the limitations of the conventional mechanical circuit breaker is discussed. The comparisons among other kinds of available semiconductor devices are carried out in order to select the most appropriate switching device for the circuit breaker application. The reliability of the DC circuit breaker will be discussed in the failure modes of the system.

# 1.2 Short circuit and protection in DC microgrids

# 1.2.1 Concept and structures of DC microgrids

DC microgrids were originally introduced in 2004 through the work of Ito et al, which illustrated the simpler control, superior efficiency, and reliability in comparison with its AC counterpart [9]. Accompanied by improvements in semiconductor materials and advancements in power electronics technology, DC systems can be flexible usage for diversity fields. They are becoming an increasingly popular solution for many types of residential and industrial applications such as telecom systems [10], distributed renewable and storage plants [11], data centers [12], residential households and buildings [13]–[17], fast EV charging stations [18], [19], and hybrid energy storage system [20].

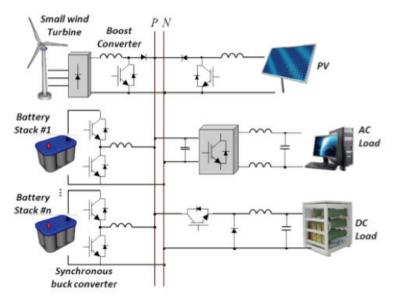

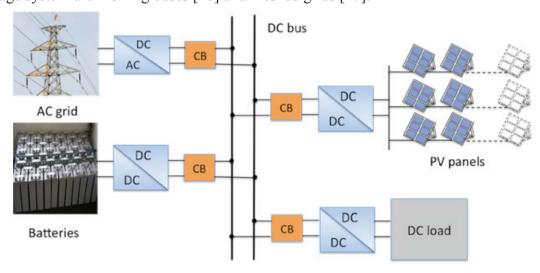

A DC microgrid can be defined as a modern distributed power system in which differently alternative renewable energy sources, energy storage systems, and DC or AC loads are connected to a common DC bus either directly or through power electronics converters [21], [22]. It can be operated in an isolated configuration without the presence of utility grid, as shown in Figure 1-1; or it can also be integrated with the AC grid by using a DC-AC inverter. The inverter is used to transfer surplus or shortage energy into the grid, as shown in Figure 1-2. DC-DC converters are usually used to link renewable energy sources such as PVs, fuel cells, or storage units with the DC bus in order to control the power balance and bus voltage. Depending on the type and capacity of loads, they can be directly fed by the DC bus, or through DC-DC converters in order to step down the voltage to lower levels those are suitable for the requirements of loads. It can be considered that the main components of a DC microgrid are: sources, converters, energy storage systems, and loads. The microgrid

technology in general and DC microgrid technology in particular commonly represents three important goals of a society: reliability, sustainability, and economics (cost optimizing, efficiency) [23].

Unfortunately, there has been a lack of regulation and standardization of LVDC distribution system. According to the literature, the DC microgrids can be classified into three categories i.e. single-bus, multi-bus and meshed topologies [22]. The most common single-bus topology usually deployed in practical applications is the unipolar system as can be seen in Figure 1-1. This configuration is simple, low-cost, and easy to the integration of renewable energy sources and storage systems. Nonetheless, using this configuration results in a decrease in transmission capacity of the system and also needs inverters capable of forming the zero potential level between the zero and phase conductors at the load point [24].

Figure 1-1 Unipolar single bus DC microgrid [22]

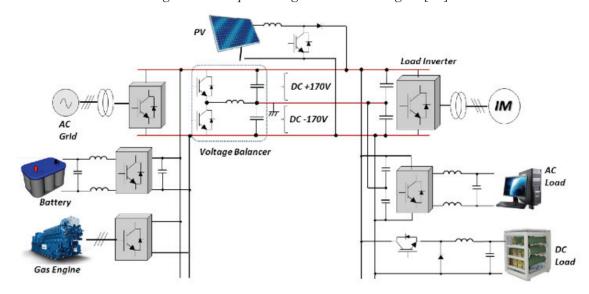

Figure 1-2 A bipolar single bus DC microgrid [22]

Another single-bus topology is bipolar, where the distribution in the system is made by a set of 3-wire lines including a positive, a negative and a neutral as illustrated in Figure 1-2. It can be easily appreciated that this concept reduces the voltage level with respect to ground, which makes the distribution system safer for the users. The system increases the reliability of the power supply, because, in case of a fault in one the lines, the energy can still be supplied

using the other two lines. In the bipolar system, the loads can be connected either between the current conductor and zero conductor or directly between the positive and negative conductors. Both of these solutions have their own problems. In the first-mentioned bipolar solution, the drawback is that the loads are not identical and the system falls into unbalance. In this case, there will be a continuous current flow in the zero conductor. The inverters required at the customer's end will also need more components because the zero potential level will have to be formed between the system zero and phase conductor for producing required alternative voltage. In the second case, the loads are connected directly between the positive and negative conductors, the problem is the increased costs of the power electronic devices due to the higher voltage level [24].

When some single-bus topologies link with each other through cables, creating a multi-bus topology or multiple DC microgrid cluster configuration. In this way, each DC microgrid is able to receive the shortage power from or inject surplus energy into the neighborhood DC microgrids [25]. Other DC microgrid architectures that feature high reliability and flexibility, which are usually used in high-voltage DC microgrid and can be applied to distribute low voltage system are DC ring buses [26] and meshed grids [27].

Figure 1-3 A typical DC microgrid configuration utilizes DC circuit breakers

Figure 1-4 Ring bus DC microgrid [22]

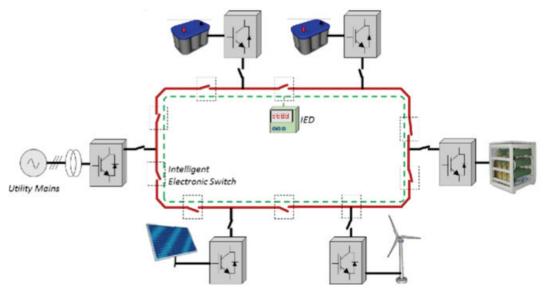

It is imperative to utilize circuit breakers (CBs) at nearly every single circuit branch in the DC microgrids to protect against short circuit faults and isolate the faulty parts from the healthy

section. An example of placing DC CBs in the DC microgrid is illustrated in Figure 1-3. Furthermore, CBs can operate as intelligent electronic devices (IEDs), which separate DC bus into segments in closed loop configurations. Therefore, the loads can be bi-directionally fed; and an alternative path is provided in a ring bus or a meshed grid in case of faults or maintenances as can be seen in Figure 1-4. Depending on the power flow direction in the branch, a CB needs to be either unidirectional or bidirectional. For instance, a CB connected to a rechargeable battery unit, or located between bus segments needs to be bidirectional while most other load and source branches only require unidirectional CBs. A DC CB model, which was implemented in a meshed DC microgrid as a complementary work for ANR C3µ project, has been mentioned in publication {2}.

# 1.2.2 Challenges of short circuits in DC microgrid

# 1.2.2.1 Characteristics of short circuit in DC microgrid

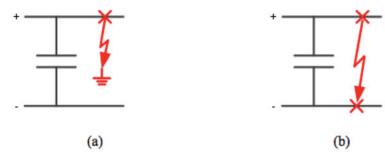

The short circuit is the most common cause of a fault current; and it may appear in all electrical systems. In DC power systems, there exist two basic types of short circuit faults: pole-to-ground and pole-to-pole faults, as illustrated in Figure 1-5 [28]. Pole-to-pole fault typically has low fault impedance, while pole-to-ground fault can have either low-impedance or high-impedance [29]. Pole-to-ground faults are less serious, but they are the most frequent ones appearing in DC distributed systems. However, pole-to-pole faults bring most serious fault currents to the DC system, short circuit currents are usually calculated in this case. The calculated results are deployed for issuing the interruption of a fault [30]. In addition, the fault position can be at various points, and each of them has different impacts on the system. While feeder faults can be rapidly isolated from the main bus, faults at main bus themselves present more danger since they will affect all sources and loads connected to the bus [29].

Figure 1-5 Two types of short circuit faults in DC systems: (a) pole-to-ground fault, (b) pole-to-pole fault.

It is not possible to eliminate short-circuit, but effects of short circuits and other faults in the distributed system can be minimized using good protection devices and well-designed protection system. Accurate short-circuit current calculation and fault-detection are the most important prerequisites for the good design of the protection system. It is important to identify the most dangerous fault location and to calculate the maximum fault current [30]. As mentioned above, the pole-to-pole short circuit at the DC bus is the most serious fault. All active sources connected to the short-circuit point contribute to the total fault current and their actual contributions depend on the equivalent impedance between the respective source and the fault location. Since the sources are connected in parallel, they can be dealt with separately, and the fault current at the short-circuit point is the sum of partial currents [31] based on superposition principle. Figure 1-6 is an equivalent short-circuit diagram proposed by the IEC Standard for a branch source.

The contribution of source ith connected to the common DC bus can be expressed as follows:

$$i_{Si}(t) = \frac{V}{R} \left( 1 - e^{-t/\tau_{eff}} \right)$$

(1.1)

where V is the equivalent voltage of the source ith at the time of the fault. It can be battery output voltage, PV open-circuit voltage or root-mean-square (RMS) line-to-line nominal voltage at the AC grid side corresponding to the type of the DC source. R and L are equivalent resistance and inductance, respectively, which are calculated from the source to the fault position.  $\tau_{eff} = L/R$  is the time constant of the equivalent branch.

Figure 1-6 Equivalent short circuit diagram of one DC source

The sustained value of the short-circuit current is equal to:

$$I_{Si} = \frac{V}{R} \tag{1.2}$$

The time constant  $\tau_{eff}$  is a measure of the rate of rise of the short-circuit current:

$$\frac{di}{dt} = \frac{V}{L} \tag{1.3}$$

It shows how fast the fault current rises to the stable value after the occurrence of a short circuit. It can be seen that due to the absence of high-value transformer inductance, the rate of rise of short-circuit current in DC microgrid is much higher than that in AC grid. In order to ensure safety when interrupting fault currents, protection devices must have a very fast response time. Similarly, the fault currents of other sources can be treated with corresponding their voltages and impedances.

On the other hand, battery banks and other types of sources are often connected to the DC bus through power electronics converter interfaces, which always employed filters to limit the ripple. When a fault occurs on the bus bar, the filter capacitors start to discharge with a very short time constant and contribute to high fault currents:

$$i_{cj}(t) = \frac{V_{dc}}{R_C} e^{-t/\tau_C}$$

(1.4)

where  $V_{dc}$  is the common DC-bus voltage at the time of the fault,  $R_C$  is the series resistance of the capacitor and  $\tau_c = C_c R_c$  is the time constant of the capacitor  $C_c$  circuit.

Total fault current can be calculated as a sum of currents provided by the sources and the converters connected to the common bus [28]:

$$i_{fault}(t) = \sum_{i=1}^{N} i_{Si}(t) + \sum_{j=1}^{M} i_{Cj}(t)$$

(1.5)

where N and M are the numbers of sources and converters connected to the fault point, respectively.

# 1.2.2.2 Interruption of short circuit current in DC grid

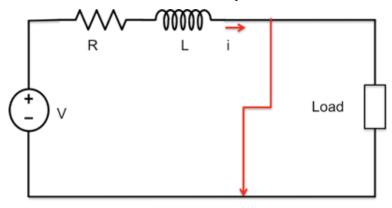

The interruption of high-value currents in DC grid is a challenging task due to the difficulty in extinguishing the arc. Contrary to AC grid in which alternating current passes through zero naturally at each half cycle and the extinction of the arc is implemented during the circuit opening, the current of DC grid always remains at the difference from zero. Therefore forcing the DC current to zero is required in order to guarantee the arc extinction. The protection devices like circuit breakers are commonly used in power system of all sizes to ensure the safety of the human and equipment. A circuit breaker is installed in the path of the current flow to protect the circuit from a pole-to-pole fault, which can be illustrated in Figure 1-7. When short circuit event occurs in this system, the impedance of the circuit is likely to be substantially reduced that leads to a large fault current. The magnitude of the fault current is dependent on voltage source and fault impedance. During the current interruption period, the opening of the circuit breaker causes a dynamic increase in the dielectric strength. This brings about an increase in the resistance of the insulating medium that forces a large voltage to develop across the circuit breaker to drive the fault current to zero.

Assuming R and L to be the total resistance and inductance of the circuit, the voltage and current relationship within the faulted circuit can be presented by the following equation:

$$V_{DC} = Ri + L\frac{di}{dt} + V_a \tag{1.6}$$

where  $V_{DC}$  is the DC equivalent voltage source,  $V_a$  is the voltage across the breaker or arc voltage and i is the current flowing in the circuit.

Figure 1-7 Basic DC circuit containing a circuit breaker with short circuit fault

Equation (1.6) can be rewritten as:

$$\frac{di}{dt} = \frac{1}{L} (V_{DC} - Ri - V_a) \tag{1.7}$$

It is shown in Equation (1.7) that in order to drive short circuit current to zero during circuit interruption, the arc voltage  $V_a$  must be greater than  $(V_{DC}-Ri)$  to produce the required negative rate of change in fault current [32], [33]. On the other hand, the rate of change of current is inversely proportional to the circuit inductance, therefore, the clearance time of a circuit breaker depends on both the acceptable magnitude of the breaker across voltage and the circuit inductance value. After forcing the current to zero, the circuit breaker should maintain its high dielectric strength in order to ensure the current is completely quenched. On the other hand, during normal operation, the voltage  $V_a$  should be as small as possible to minimize the on-state losses of the circuit breaker.

# 1.2.3 Requirements of a DC Circuit Breaker in the DC Microgrid