# Exploration of parallel graph-processing algorithms on distributed architectures

Julien Collet

#### ► To cite this version:

Julien Collet. Exploration of parallel graph-processing algorithms on distributed architectures. Other [cs.OH]. Université de Technologie de Compiègne, 2017. English. NNT: 2017COMP2391. tel-01800156

#### HAL Id: tel-01800156 https://theses.hal.science/tel-01800156

Submitted on 25 May 2018  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Par Julien COLLET

Exploration of parallel graph-processing algorithms on distributed architectures

Thèse présentée pour l'obtention du grade de Docteur de l'UTC

Soutenue le 6 décembre 2017 Spécialité : Technologies de l'Information et des Systèmes : Unité de recherche Heudyasic (UMR-7253)

D2391

### Thèse de doctorat de L'Université de Technologie de Compiègne

Département de Génie Informatique École doctorale 71, Sciences pour l'Ingénieur

Technologies de l'Information et des Systèmes

### Exploration of parallel graph-processing algorithms on distributed architectures

PAR Julien Collet

#### POUR OBTENIR LE GRADE DE DOCTEUR de L'Université de Technologie de Compiègne

Membres du jury:

Président du Jury : Dritan NACE, Professeur à l'Université de Technologie de Compiègne

Examinateur : Lorène ALLANO, Ingénieur-Chercheur, CEA-LIST

Rapporteur : Corinne ANCOURT, Professeur à l'Ecole des Mines de Paris

Rapporteur : Didier EL BAZ, Directeur de recherche LAAS-CNRS

Directeur de thèse : Jacques CARLIER, Professeur émérite, Université de Technologie de Compiègne

Co-Directeur de thèse : Renaud SIRDEY, Directeur de recherche, CEA-LIST

Encadrant : Tanguy SASSOLAS, Ingénieur-Chercheur, CEA-LIST

**Co-Encadrant :** Yves LHUILLIER, Ingénieur-Chercheur, CEA-LIST

Date de soutenance : 6 décembre 2017

Je dédie cette thèse à mon grand-père, Michel Cottonnet

### Remerciements

Ce manuscrit de thèse vient clore un chapitre couvrant trois années de travail — et quelque part, bien plus. Je voudrais ici prendre un peu d'espace pour remercier les personnes qui ont contribué à l'écrire. De par leur nombre, il m'est pratiquement impossible d'être absolument exhaustif. Ainsi, je voudrais commencer par remercier et présenter mes excuses à ceux qui ne se retrouveraient pas dans les quelques mots qui suivent.

Tout d'abord, j'aimerais exprimer ma gratitude envers le laboratoire LCE de l'institut LIST du CEA pour m'avoir accueilli en son sein et, en particulier, Raphaël DAVID et Nicolas VENTROUX, chefs successifs du LCE, pour leur bienveillance, leurs conseils avisés et leur sympathie.

Je voudrais ensuite remercier Corinne ANCOURT et Didier EL BAZ pour avoir accepté de rapporter ma thèse, ainsi que Dritan NACE pour avoir accepté de présider le jury de thèse. J'aimerais également adresser de chaleureux remerciements à Lorène ALLANO pour m'avoir permis d'accéder aux plateformes de calcul du LADIS et de découvrir le fascinant domaine de la génomique, ainsi que pour avoir accepté de prendre part au jury en qualité d'examinateur.

Aussi, j'aimerais dire ici toute ma reconnaissance à Jacques CARLIER, directeur de thèse, pour son aide continue et ses nombreux conseils avisés tout au long de ces trois années de dur labeur. J'adresse également mes plus francs remerciements à Renaud SIRDEY, directeur de thèse, pour sa disponibilité et sa bienveillance pendant les moments de doute, pour avoir apporté une hauteur de vue nécessaire et avoir été un précieux soutien tout au long de cette thèse.

Il m'est impossible de ne pas remercier ici Tanguy SASSOLAS et Yves LHUILLIER, encadrants de thèse, pour leur disponibilité, leurs conseils et leur implication, mais également leur sympathie, leur tolérance et leur sens de l'humour qui font qu'aujourd'hui la thèse se termine relativement paisiblement. Tanguy, si j'ai souvent pesté — à tort ! contre ton souci permanent du détail, force est de reconnaître que cette rigueur (dont je manquais probablement un peu en arrivant) m'aura été très précieuse, à chaque instant. Yves, merci de n'avoir jamais perdu patience pendant ces trois ans malgré les sollicitations incessantes — et pas toujours pertinentes, hélas ! —, ton expertise m'aura beaucoup fait progresser durant cette thèse. Enfin, travailler avec vous a été un vrai plaisir, que j'espère partagé. Pour ceci et pour beaucoup d'autres choses encore, je veux vous remercier à nouveau.

Au cours de ces trois ans, j'ai eu l'occasion de rejoindre l'ENSTA ParisTech en tant qu'enseignant-vacataire. À ce titre, je voudrais donc remercier sincèrement Omar HAM-MAMI pour sa confiance et pour cette belle opportunité, mais également pour m'avoir donné l'occasion d'exploiter des plateformes de calcul de l'ENSTA dans le cadre de cette thèse.

J'ai une pensée toute particulière pour mes collègues futurs docteurs — voire jeunes diplômés pour certains ! — avec qui j'ai l'impression d'avoir bien plus que simplement partagé un lieu de travail pendant plusieurs semaines, mois ou années. Pour commencer, je voudrais remercier Vincent pour les débriefings de réunions de thèses (souvent modérément animés et, parfois, un peu plus), pour l'aide apportée tout au long de ces quelques années et pour tous les bons souvenirs que je garde de ce temps-là — on démarrait nos thèses ensemble il y a trois ans et, malgré tout, on touche enfin au but : not bad. Je tenais également à remercier Joël, nouvellement promu à la meilleure place de l'openspace, celle du *chef* — nos réunions du lundi ainsi que les intermèdes philosophiques (et moins philosophiques aussi) me manquent déjà. De même, j'aimerais remercier Emna, qui est capable de rendre presque supportable une formation doctorale — je n'oublie pas non plus les pépites musicales que tu m'as fait découvrir et qui me hantent encore. J'aimerais également adresser mes remerciements à Johannes — je ne désespère pas d'un jour comprendre, grâce à toi, quelque chose aux réseaux de neurones — et à Jason qui, je l'espère, continuera à promouvoir l'usage unilatéral de *beamer*. Enfin, merci aussi à Mariam, pour notre correspondance très constructive pendant la quasi-totalité de la thèse — et toutes mes félicitations ! Je n'oublie pas non plus les anciens, Aziz et Alexandre, qui ont guidé mes premiers pas de thésard au laboratoire — merci pour les franches rigolades et pour avoir fait le déplacement le grand jour.

Je voudrais également adresser mes remerciements à David, pour ses analyses très objectives sur de multiples sujets (sport, cuisine et tourisme en particulier), à Benoit, en souvenir de cours d'anglais mémorables, à Mickaël, pour tous les soucis que j'ai pu te causer en salle serveur, à Thomas, pour les relectures toujours très pointues des chapitres qui composent le présent manuscrit, à Alexandre, pour ses conseils tout au long de la thèse, à Emmanuel, pour avoir toléré mon accent espagnol déplorable, à Mohammed et ses fameux *loupins*, et, enfin, à Gabriel et Enrique, à qui je souhaite également bonne route dans mon désormais ex-bureau. J'aimerais finalement remercier l'ensemble des membres des laboratoires LCE, L3S et L3A que j'ai pu côtoyer, pour l'atmosphère générale qui m'a permis de ne pas (trop) sombrer dans la folie pendant ces trois ans, mais également pour avoir supporté toutes mes obsessions, mes petites manies et mes prises de position — toujours très modérées — avec une grande patience et une certaine bienveillance. J'espère que vous garderez un aussi bon souvenir que moi de ces années.

Je voulais également remercier, sans ordre particulier et pour des raisons différentes, Florian, Faustine, Bastien, Camille, Etienne (si, si), Lucia, Mickael, Weronika, Alice, Norbert, Eleonore, Sophie, Lukàš *and all of you guys at the University of Ostrava*, les *embiddet people*, les amis lyonnais de CPE — quel que soit le côté de l'amphi qu'ils aient occupé d'ailleurs —, sans oublier toutes les personnes qui, par discrétion ou par inadvertance, ne sont pas citées ici. Chacun à votre manière, vous avez donné une belle couleur à ces trois années et je vous en suis reconnaissant. Bien sûr, je n'oublie pas Robin, complice infaillible depuis bien trop longtemps déjà — et pour combien de temps encore ? Last, but not least, je voudrais remercier ceux qui sont à mes côtés depuis le début, ma famille et, en particulier mes parents, Isabelle et Alain, et mon frère, Thomas. Je sais n'avoir pas toujours été *facile* pendant ces trois années et je veux vous dire encore merci de m'avoir accompagné de la meilleure des façons.

Je termine — enfin ! — sur ces quelques mots, qui prennent (en ce qui me concerne) un sens assez particulier après ces trois années.

Rien n'est plus difficile pour chacun d'entre nous que de situer ce qu'il a fait et de se situer soi-même à sa juste mesure

— Jean d'Ormesson

iv

## Contents

| A        | bstra | $\mathbf{ct}$ |                                                                                                      | 1         |

|----------|-------|---------------|------------------------------------------------------------------------------------------------------|-----------|

|          | Abs   | tract .       |                                                                                                      | 1         |

|          | Rési  | ımé .         |                                                                                                      | 2         |

| In       | trod  | uction        |                                                                                                      | 3         |

|          | Con   | text of       | the thesis $\ldots$ | 3         |

|          | Rese  | earch fo      | cus and problematic                                                                                  | 5         |

|          | Out   | line of t     | this manuscript                                                                                      | 7         |

| 1        | Hig   | h perf        | ormance computers and parallel programming paradigms                                                 | 9         |

|          | 1.1   | Lands         | cape of high performance parallel machines                                                           | 11        |

|          |       | 1.1.1         | Supercomputers and high-end architectures                                                            | 11        |

|          |       | 1.1.2         | Data-crunching many-cores                                                                            | 13        |

|          |       | 1.1.3         | Commodity clusters                                                                                   | 14        |

|          |       | 1.1.4         | Summary                                                                                              | 14        |

|          | 1.2   | Abstra        | actions and design models for parallel programming                                                   | 15        |

|          |       | 1.2.1         | Execution models                                                                                     | 16        |

|          |       | 1.2.2         | Memory models                                                                                        | 18        |

|          | 1.3   | Towar         | ds parallel computing for data-mining                                                                | 20        |

|          |       | 1.3.1         | Integrated Development Environment for data-mining                                                   | 20        |

|          |       | 1.3.2         | Language extension approaches                                                                        | 21        |

|          |       | 1.3.3         | Library-based approaches                                                                             | 23        |

|          | 1.4   | Conclu        | uding remarks                                                                                        | 24        |

| <b>2</b> | Gra   | ph-pro        | ocessing at scale on distributed architectures                                                       | <b>27</b> |

|          | 2.1   | Graph         | -processing: Programming models and state of the art                                                 | 29        |

|          |       | 2.1.1         | Programming models: from BSP to vertex-centric programming $\ .$ .                                   | 29        |

|          |       | 2.1.2         | Landscape of vertex-centric frameworks                                                               | 30        |

|          | 2.2   | Anato         | my of a GraphLab program                                                                             | 31        |

|          |       | 2.2.1         | Initialization and input file parsing                                                                | 32        |

|          |       | 2.2.2         | Partitioning of the graph structure                                                                  | 32        |

|          |       | 2.2.3         | Graph-processing using the GAS execution engine                                                      | 33        |

|          |       | 2.2.4         | Result output and execution termination $\ldots \ldots \ldots \ldots \ldots \ldots$                  | 36        |

|          |       | 2.2.5         | Synthesis                                                                                            | 37        |

|          | 2.3   | Perfor        | mance evaluation of GraphLab programs                                                                | 37        |

|          |       | 2.3.1         | Benchmarking off-the-shelf application against real-life performance                                 |           |

|          |       |               | tuning                                                                                               | 38        |

|          |       | 2.3.2         | Throughput metrics for operating performance benchmarking                                            | 39        |

|   | 2.4  | Availa  | ble distributed memory architectures                                                    | 40  |

|---|------|---------|-----------------------------------------------------------------------------------------|-----|

|   |      | 2.4.1   | Presentation of the compute clusters $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 40  |

|   |      | 2.4.2   | Comparing hardware approaches                                                           | 42  |

|   | 2.5  | Synthe  | esis                                                                                    | 43  |

| 3 | Pra  | ctical  | deployment of parallel graph applications                                               | 45  |

|   | 3.1  | Progra  | am trace analysis                                                                       | 46  |

|   |      | 3.1.1   | Algorithms and graph models of computation                                              | 47  |

|   |      | 3.1.2   | Vertex-centric implementation                                                           | 49  |

|   |      | 3.1.3   | Experimental protocol, materials and methods                                            | 52  |

|   |      | 3.1.4   | Experimental results                                                                    | 52  |

|   |      | 3.1.5   | Synthesis                                                                               | 58  |

|   | 3.2  | De Br   | uijn graph filtering for <i>de novo</i> assembly                                        | 59  |

|   |      | 3.2.1   | De novo assembly of short reads using de Bruijn graphs                                  | 60  |

|   |      | 3.2.2   | Problem modelization                                                                    | 64  |

|   |      | 3.2.3   | DBG preprocessing algorithm                                                             | 67  |

|   |      | 3.2.4   | Vertex-centric implementation of the algorithm $\ldots \ldots \ldots \ldots$            | 70  |

|   |      | 3.2.5   | Materials and methods                                                                   | 71  |

|   |      | 3.2.6   | Experimental results                                                                    | 72  |

|   |      | 3.2.7   | Synthesis                                                                               | 76  |

|   | 3.3  | Conclu  | uding remarks                                                                           | 78  |

| 4 | Dist | tribute | ed architecture exploration for efficient graph-processing                              | 81  |

|   | 4.1  | Assess  | sing performance and operating ranges                                                   | 82  |

|   |      | 4.1.1   | Operating ranges                                                                        | 82  |

|   |      | 4.1.2   | Targeting an efficient operating point                                                  | 83  |

|   |      | 4.1.3   | Experimental parameters                                                                 | 84  |

|   | 4.2  | Comp    | arison of distributed architectures for graph-processing                                | 84  |

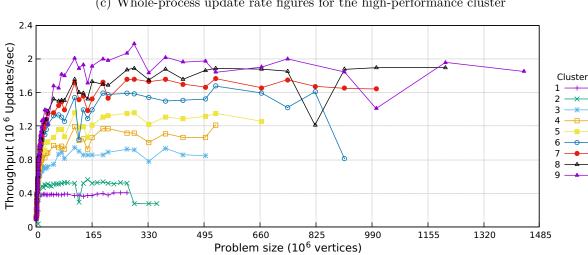

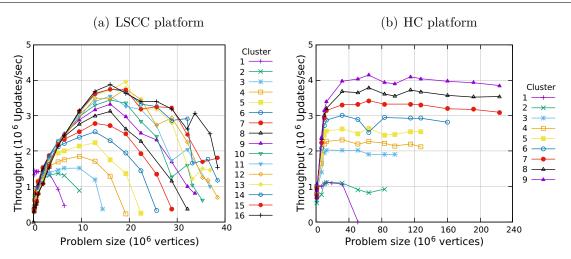

|   |      | 4.2.1   | Analysis of GraphLab program profiles                                                   | 84  |

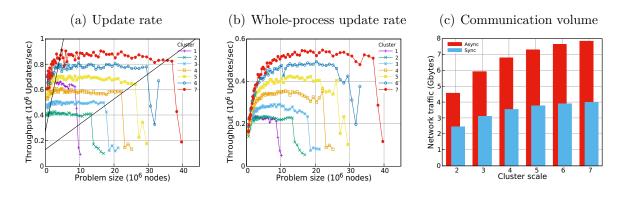

|   |      | 4.2.2   | Throughput-based analysis                                                               | 87  |

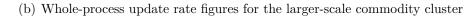

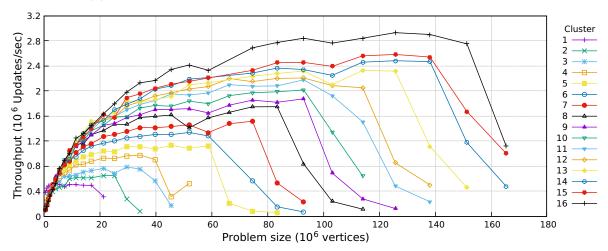

|   |      | 4.2.3   | Whole-process update rates                                                              | 90  |

|   |      | 4.2.4   | Asynchronous execution performances                                                     | 92  |

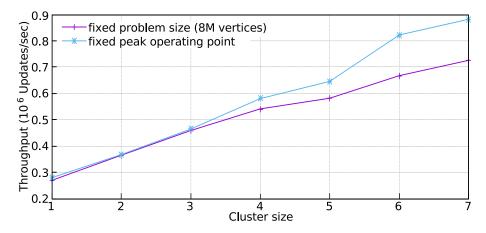

|   |      | 4.2.5   | Performance scalability                                                                 | 93  |

|   |      | 4.2.6   | Synthesis                                                                               | 95  |

|   | 4.3  | Throu   | ghput-oriented dimensioning of a cluster                                                | 96  |

|   |      | 4.3.1   | From operating ranges to machine capacity                                               | 96  |

|   |      | 4.3.2   | Replication factor                                                                      | 99  |

|   |      | 4.3.3   | Throughput-based methods for cluster dimensioning                                       | 99  |

|   | 4.4  | Conch   | usion and perspectives                                                                  | 101 |

| <b>5</b>     | Mo                                             | re effic                                                                        | ient graph-oriented cluster design                                              | 105                                                                                                                |

|--------------|------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|              | 5.1                                            | Flash-                                                                          | based victim swap towards graceful performance degradation $\ . \ . \ .$        | 106                                                                                                                |

|              |                                                | 5.1.1                                                                           | Motivations                                                                     | 106                                                                                                                |

|              |                                                | 5.1.2                                                                           | Evaluation of flash-based swap memory                                           | 107                                                                                                                |

|              |                                                | 5.1.3                                                                           | Perspectives in graph-processing cluster design                                 | 109                                                                                                                |

|              | 5.2                                            | Micros                                                                          | erver-based architectures for efficient graph-processing $\ldots \ldots \ldots$ | 109                                                                                                                |

|              |                                                | 5.2.1                                                                           | Motivations                                                                     | 110                                                                                                                |

|              |                                                | 5.2.2                                                                           | Hardware architecture                                                           | 110                                                                                                                |

|              |                                                | 5.2.3                                                                           | Using GraphLab on ARMv8 architectures                                           | 110                                                                                                                |

|              |                                                | 5.2.4                                                                           | Single-node operating performances                                              | 112                                                                                                                |

|              |                                                | 5.2.5                                                                           | Distributed operating performances                                              | 113                                                                                                                |

|              |                                                | 5.2.6                                                                           | Relevance of ARM-based platform for graph-processing                            | 115                                                                                                                |

|              | 5.3                                            | Conclu                                                                          | sion and perspectives                                                           | 116                                                                                                                |

| C            | nalu                                           | aiona d                                                                         | and perspectives                                                                | 110                                                                                                                |

| $\mathbf{U}$ | листи                                          |                                                                                 |                                                                                 |                                                                                                                    |

|              |                                                |                                                                                 |                                                                                 | 119                                                                                                                |

|              | Synt                                           | hesis                                                                           | · · · ·                                                                         | 119                                                                                                                |

|              | Synt                                           | thesis<br>pectives                                                              | <br>                                                                            | 119<br>122                                                                                                         |

|              | Synt                                           | hesis<br>pective<br>Short-                                                      | term                                                                            | <ol> <li>119</li> <li>122</li> <li>122</li> </ol>                                                                  |

|              | Synt                                           | hesis<br>pective<br>Short-                                                      | <br>                                                                            | <ol> <li>119</li> <li>122</li> <li>122</li> </ol>                                                                  |

| Pe           | Synt<br>Pers                                   | hesis<br>pectives<br>Short-<br>Longer                                           | term                                                                            | <ol> <li>119</li> <li>122</li> <li>122</li> </ol>                                                                  |

| Pe           | Synt<br>Pers<br>erson                          | hesis<br>pective<br>Short-<br>Longer<br><b>al pub</b>                           | s                                                                               | <ol> <li>119</li> <li>122</li> <li>122</li> <li>123</li> <li>125</li> </ol>                                        |

| Pe           | Synt<br>Pers<br>erson<br>Inter                 | chesis<br>pectives<br>Short-<br>Longer<br><b>al pub</b><br>rnations             | s                                                                               | <ul> <li>119</li> <li>122</li> <li>122</li> <li>123</li> <li>125</li> </ul>                                        |

| Pe           | Synt<br>Pers<br>erson<br>Inter<br>Post         | chesis<br>pectives<br>Short-<br>Longer<br><b>al pub</b><br>rnations<br>er prese | s                                                                               | <ul> <li>119</li> <li>122</li> <li>122</li> <li>123</li> <li>125</li> <li>125</li> <li>125</li> </ul>              |

| Pe           | Synt<br>Pers<br>erson<br>Inter<br>Post<br>Talk | chesis<br>pectives<br>Short-<br>Longer<br><b>al pub</b><br>mationa<br>er prese  | s                                                                               | <ul> <li>119</li> <li>122</li> <li>122</li> <li>123</li> <li>125</li> <li>125</li> <li>125</li> <li>125</li> </ul> |

## List of Figures

| 1    | TOP500 performances                                                                   | 4  |

|------|---------------------------------------------------------------------------------------|----|

| 1.1  | Fork-Join execution model                                                             | 16 |

| 1.2  | Message-passing execution model                                                       | 17 |

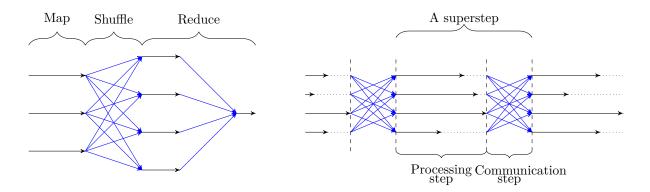

| 1.3  | MapReduce and BSP execution models                                                    | 17 |

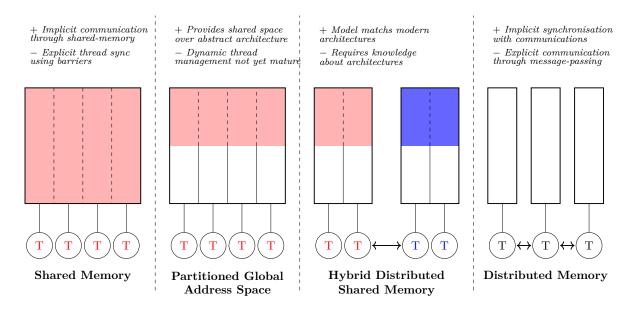

| 1.4  | Parallel memory models                                                                | 19 |

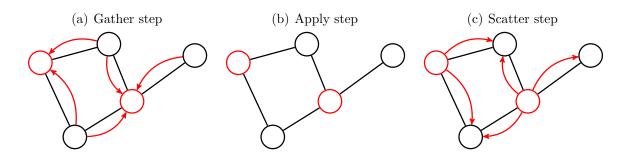

| 2.1  | GraphLab Gather-Apply-Scatter model                                                   | 34 |

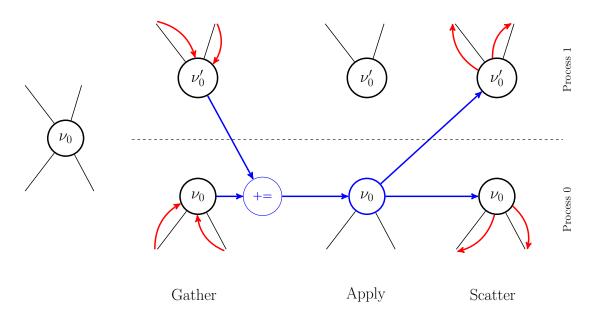

| 2.2  | Distributed GAS model                                                                 | 35 |

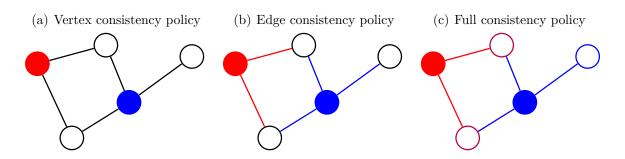

| 2.3  | GraphLab vertex consistency policies                                                  | 36 |

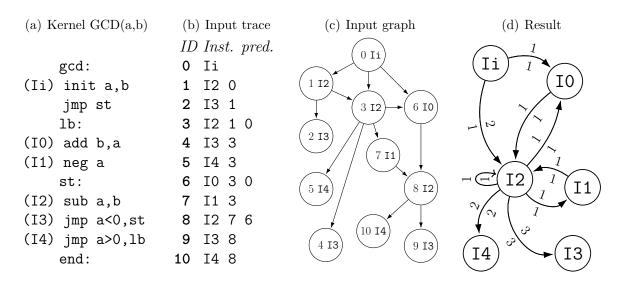

| 3.1  | Program trace analysis toy example                                                    | 48 |

| 3.2  | Input graph datasets characteristics                                                  | 51 |

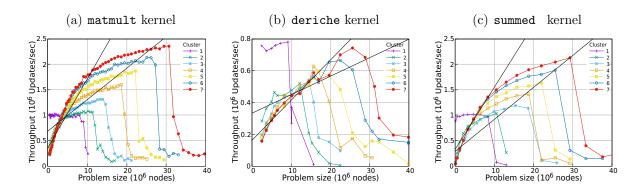

| 3.3  | Update rate figures for the three input kernels                                       | 53 |

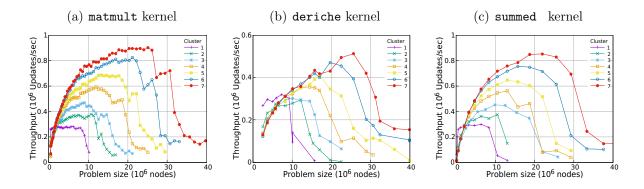

| 3.4  | Whole-process update rate figures for the three input kernels                         | 53 |

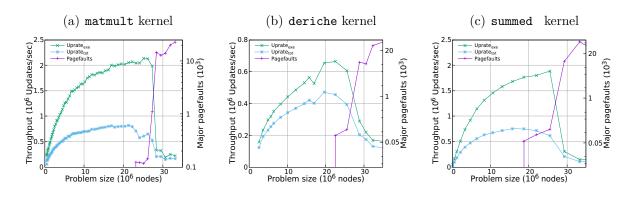

| 3.5  | Performances and pagefaults figures for the three input kernels                       | 54 |

| 3.6  | Timing analysis for matmult kernel                                                    | 55 |

| 3.7  | Operating performances scalability                                                    | 56 |

| 3.8  | Asynchronous engine execution performances                                            | 57 |

| 3.9  | Ingress method performance comparison                                                 | 58 |

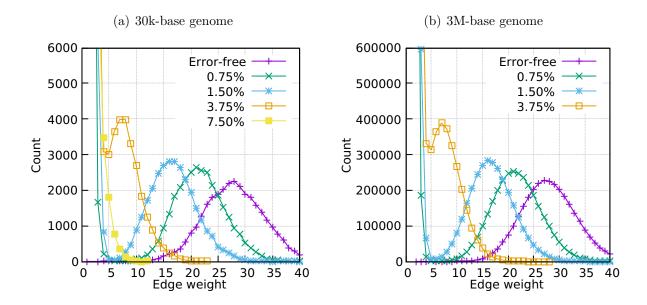

| 3.10 | Read errors in sequencer data                                                         | 61 |

| 3.11 | $k\text{-}\mathrm{mer}$ decomposition and associated de Bruijn graph of a sequence    | 61 |

| 3.12 | Typical sequencing experiment set-up                                                  | 62 |

| 3.13 | De Bruijn graph edge weight distribution                                              | 65 |

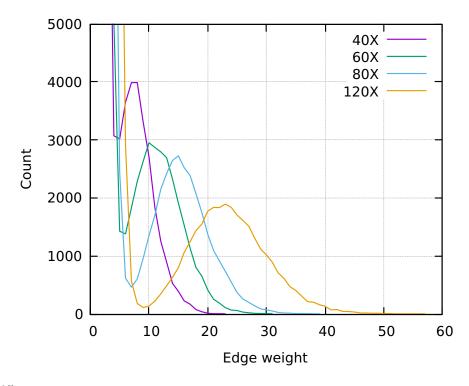

| 3.14 | Impact of the sequencing depth on the $k$ -mer spectrum $\ldots \ldots \ldots \ldots$ | 66 |

| 3.15 | $k$ -mer spectrum of the ID0_40X dataset                                              | 66 |

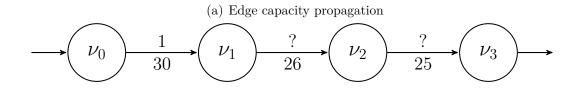

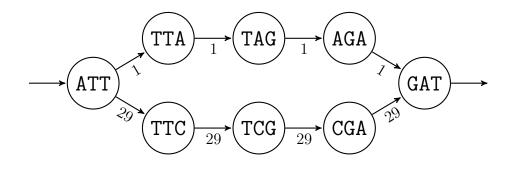

| 3.16 | Edge determination using capacity propagation                                         | 68 |

| 3.17 | Error-induced bubble in a 3-mer de Bruijn graph                                       | 68 |

| 3.18 | Edge capacity determination and dead-end branch removal                               | 69 |

| 3.19 | Impact of the algorithm parameters                                                    | 70 |

| 3.20 | Algorithm accuracy with varying error rates                                           | 73 |

| 3.21 | Impact of the tolerance interval and the sequencing depth on the accuracy             |    |

|      | of the algorithm                                                                      | 74 |

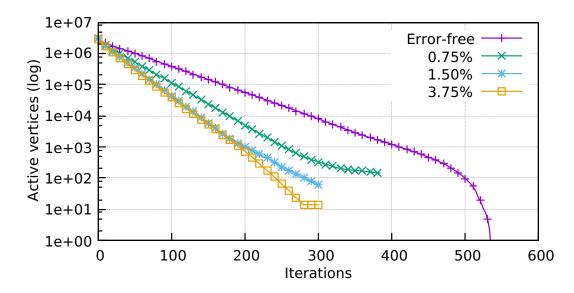

| 3.22 | Algorithm convergence for varying error rates                                         | 75 |

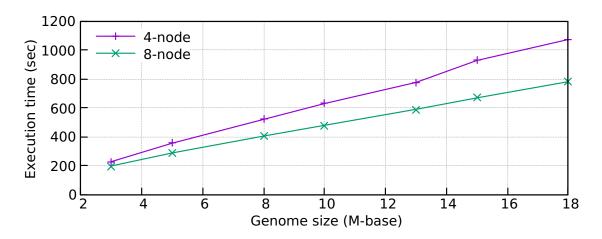

| 3.23 | Wall execution time for increasing input graphs                                       | 75 |

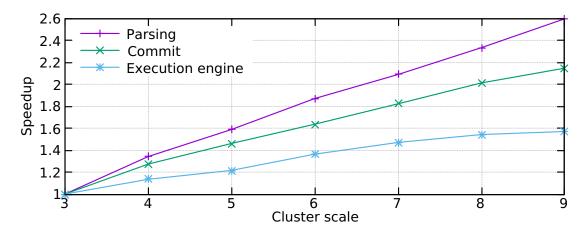

| 3.24 | Speedup observed for three parts of the program                                       | 76 |

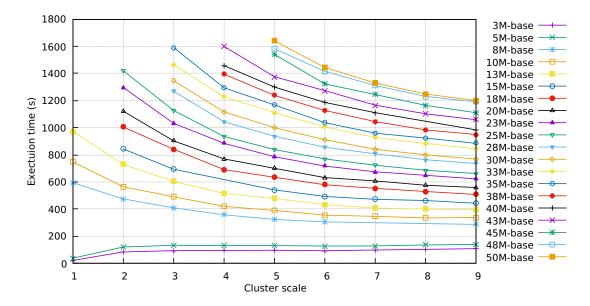

| 3.25 | Execution time with varying cluster configurations                                    | 77 |

| 3.26 | Performances of various distributed cluster configurations                            | 77 |

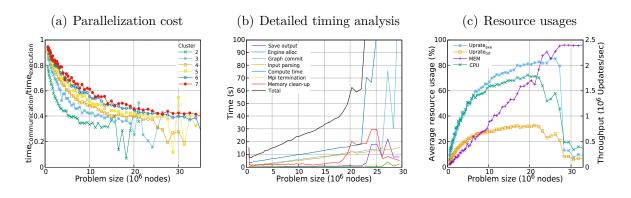

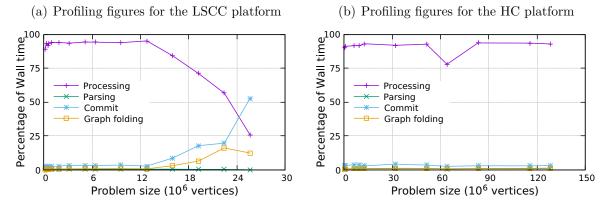

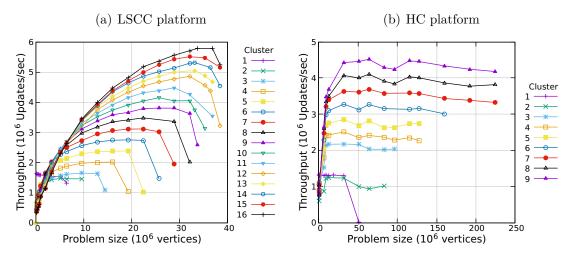

| 4.1  | Profiling figures for the program trace application                                                                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

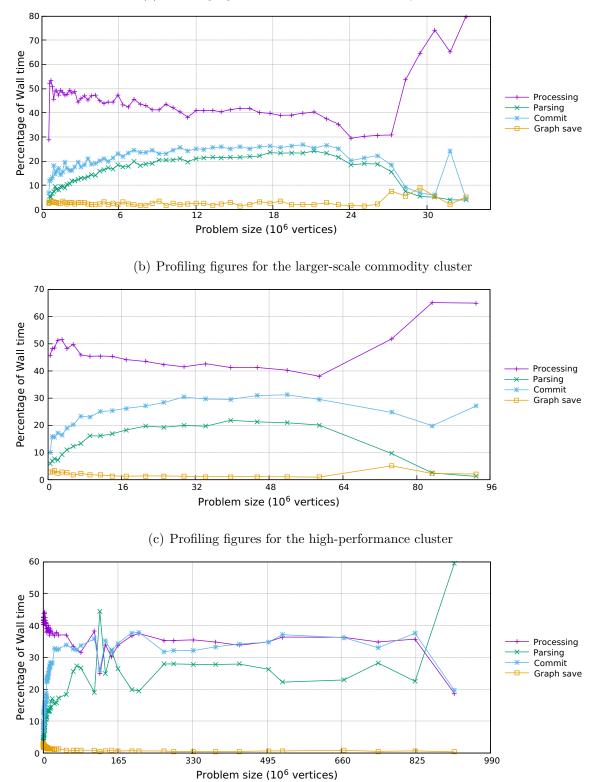

| 4.2  | Profiling figures for the DBG filtering algorithm                                                                                                                          |

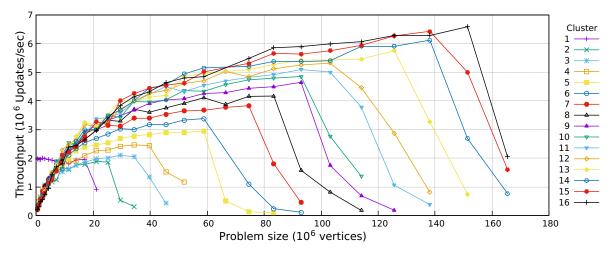

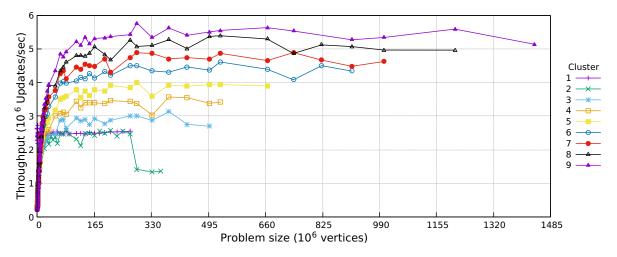

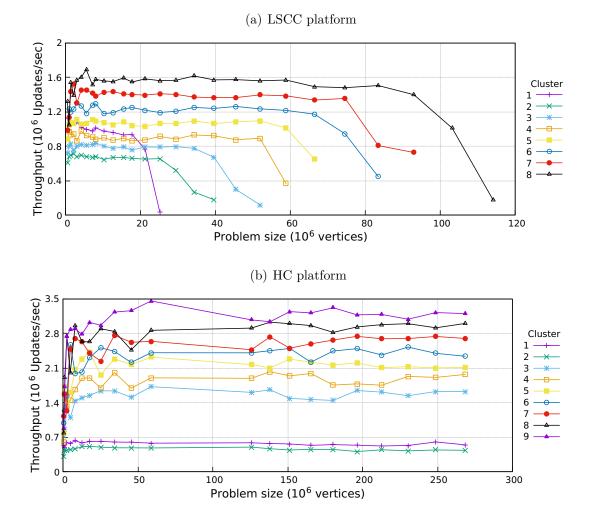

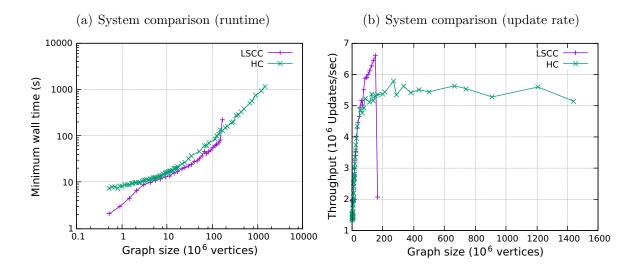

| 4.3  | Throughput performance comparison of the distributed clusters $\ldots \ldots 88$                                                                                           |

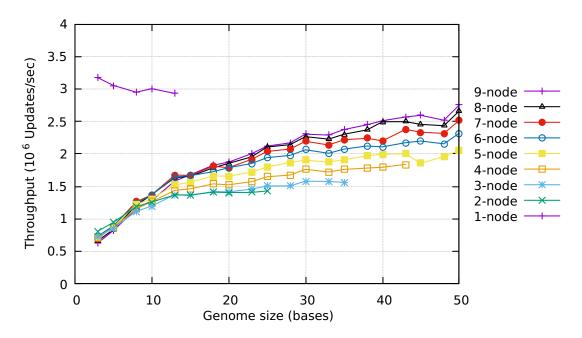

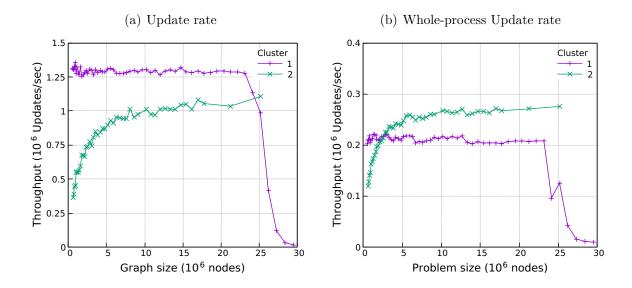

| 4.4  | Update rate figures for the DBG filtering algorithm $\ldots \ldots \ldots \ldots $ 89                                                                                      |

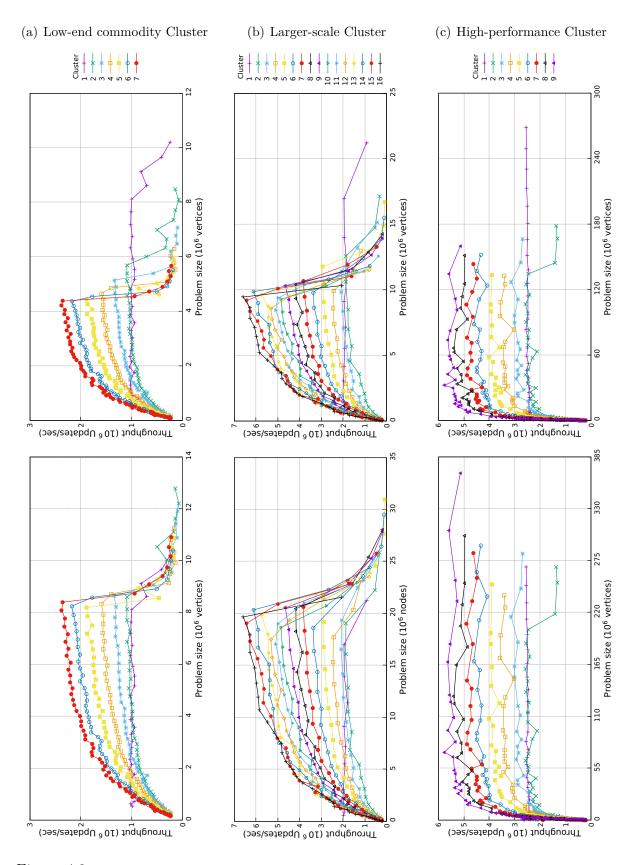

| 4.5  | Global performances comparison of three distributed clusters 91                                                                                                            |

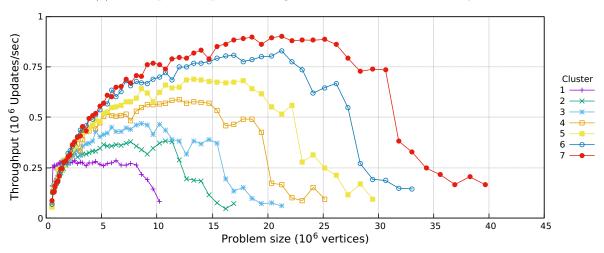

| 4.6  | Whole-process update rate figures for the DBG filtering algorithm 92                                                                                                       |

| 4.7  | Asynchronous throughput performances of the HC and LSCC platforms $93$                                                                                                     |

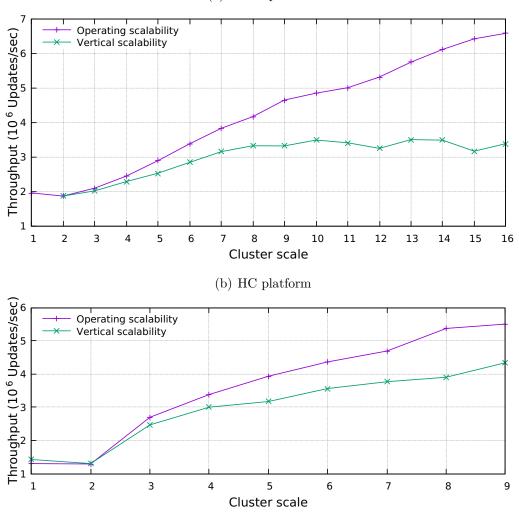

| 4.8  | Performance scalability of the LSCC and HC platforms for the trace anal-                                                                                                   |

|      | ysis use-case                                                                                                                                                              |

| 4.9  | Per machine update rate                                                                                                                                                    |

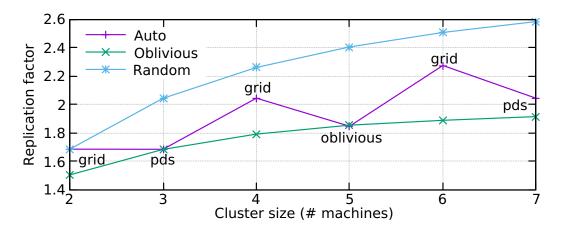

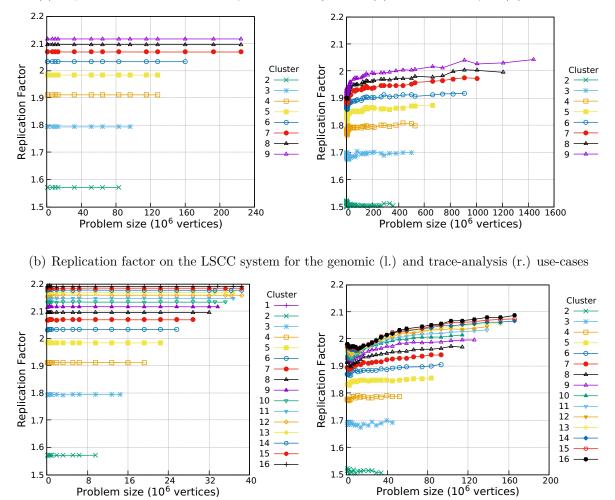

| 4.10 | Evolution of the replication factor $\ldots \ldots \ldots$ |

| 4.11 | System comparison (program trace analysis)                                                                                                                                 |

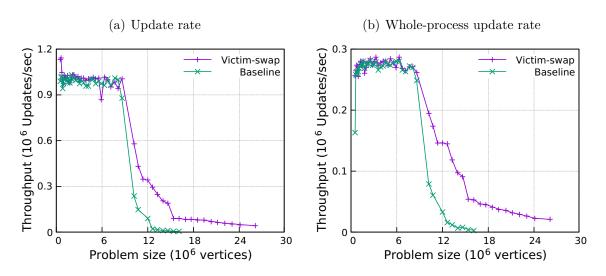

| 5.1  | Performance comparison of the victim-swap approach with the baseline $\ . \ . \ 107$                                                                                       |

| 5.2  | Comparison of wall-clock execution time of the victim-swap approach with                                                                                                   |

|      | the baseline $\hdots$                                                                                                                                                      |

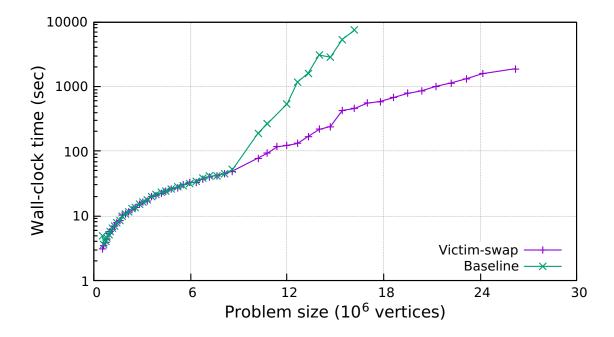

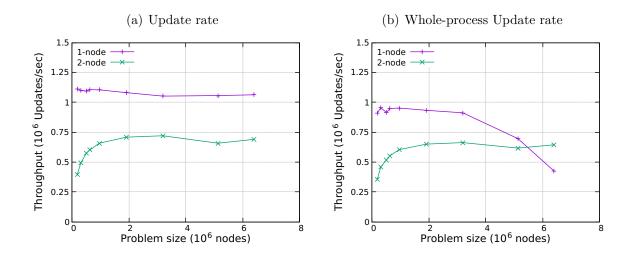

| 5.3  | Operating performance of the TX2 board on the trace analysis use-case $\ . \ . \ 113$                                                                                      |

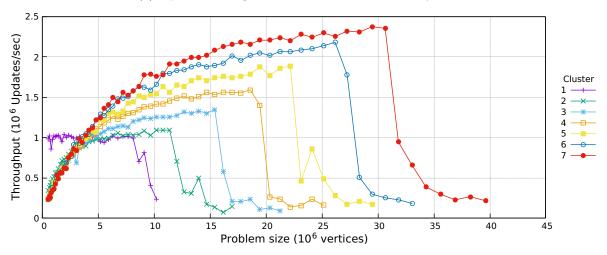

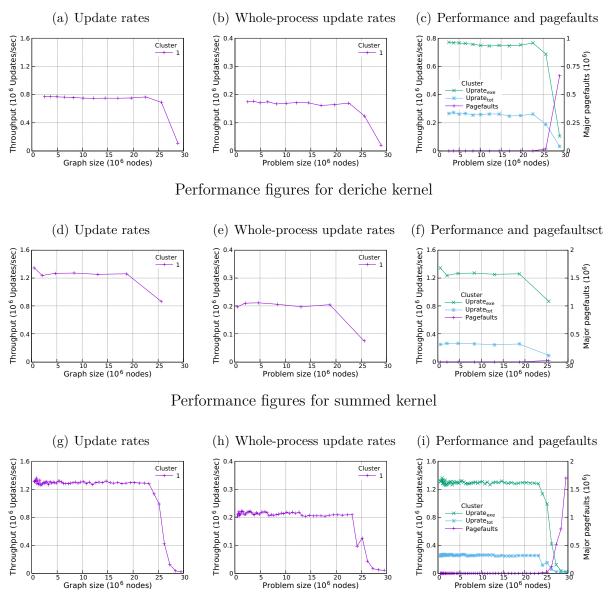

| 5.4  | Distributed performances of the TX2-based platform (trace analysis use-case) $114$                                                                                         |

| 5.5  | Distributed performances of the TX2-based platform (genomic use-case) 115                                                                                                  |

## List of Tables

| 1.1 | Evolution of supercomputer architectures                    | 12  |

|-----|-------------------------------------------------------------|-----|

| 1.2 | Architectural trends in embedded high-performance manycores | 13  |

| 2.1 | Comparison of vertex-centric frameworks                     | 30  |

| 2.2 | Description of the hardware architectures used              | 41  |

| 4.1 | Unit capacities of the three platforms                      | 99  |

| 5.1 | Description of the Nvidia Jetson TX2 hardware architecture  | 111 |

## List of Algorithms

| 1 | Algorithm of the parallel input file parser             | 49 |

|---|---------------------------------------------------------|----|

| 2 | Algorithm of the program trace analysis vertex-function | 50 |

### Abstract

#### Abstract

With the advent of ever-increasing graph datasets in a large number of domains, parallel graph-processing applications deployed on distributed architectures are more and more needed to cope with the growing demand for memory and compute resources. Though large-scale distributed architectures are available, notably in the High-Performance Computing (HPC) domain, the programming and deployment complexity of such graph-processing algorithms, whose parallelization and complexity are highly data-dependent, hamper usability. Moreover, the difficult evaluation of performance behaviors of these applications complexifies the assessment of the relevance of the used architecture.

With this in mind, this thesis work deals with the exploration of graph-processing algorithms on distributed architectures, notably using GraphLab, a state of the art graphprocessing framework. Two use-cases are considered. For each, a parallel implementation is proposed and deployed on several distributed architectures of varying scales. This study highlights operating ranges, which can eventually be leveraged to appropriately select a relevant operating point with respect to the datasets processed and used cluster nodes.

Further study enables a performance comparison of commodity cluster architectures and higher-end compute servers using the two use-cases previously developed. This study highlights the particular relevance of using clustered commodity workstations, which are considerably cheaper and simpler with respect to node architecture, over higher-end systems in this applicative context.

Then, this thesis work explores how performance studies are helpful in cluster design for graph-processing. In particular, studying throughput performances of a graphprocessing system gives fruitful insights for further node architecture improvements. Moreover, this work shows that a more in-depth performance analysis can lead to guidelines for the appropriate sizing of a cluster for a given workload, paving the way toward resource allocation for graph-processing.

Finally, hardware improvements for next generations of graph-processing servers are proposed and evaluated. A flash-based victim-swap mechanism is proposed for the mitigation of unwanted overloaded operations. Then, the relevance of ARM-based microservers for graph-processing is investigated with a port of GraphLab on a NVIDIA TX2-based architecture.

#### Résumé

Avec l'explosion du volume de données produites chaque année, les applications du domaine du traitement de graphes ont de plus en plus besoin d'être parallélisées et déployées sur des architectures distribuées afin d'adresser le besoin en mémoire et en ressource de calcul. Si de telles architectures larges échelles existent, issue notamment du domaine du calcul haute performance (HPC), la complexité de programmation et de déploiement d'algorithmes de traitement de graphes sur de telles cibles est souvent un frein à leur utilisation. De plus, la difficile compréhension, a priori, du comportement en performances de ce type d'applications complexifie également l'évaluation du niveau d'adéquation des architectures matérielles avec de tels algorithmes.

Dans ce contexte, ces travaux de thèses portent sur l'exploration d'algorithmes de traitement de graphes sur architectures distribuées en utilisant GraphLab, un framework de l'état de l'art dédié à la programmation parallèle de tels algorithmes. En particulier, deux cas d'applications réelles ont été étudiées en détails et déployées sur différentes architectures à mémoire distribuée, l'un venant de l'analyse de trace d'exécution et l'autre du domaine du traitement de données génomiques. Ces études ont permis de mettre en évidence l'existence de régimes de fonctionnement permettant d'identifier des points de fonctionnements pertinents dans lesquels on souhaitera placer un système pour maximiser son efficacité.

Dans un deuxième temps, une étude a permis de comparer l'efficacité d'architectures généralistes (type commodity cluster) et d'architectures plus spécialisées (type serveur de calcul hautes performances) pour le traitement de graphes distribué. Cette étude a démontré que les architectures composées de grappes de machines de type workstation, moins onéreuses et plus simples, permettaient d'obtenir des performances plus élevées. Cet écart est d'avantage accentué quand les performances sont pondérées par les coûts d'achats et opérationnels. L'étude du comportement en performance des ces architectures a également permis de proposer *in fine* des règles de dimensionnement et de conception des architectures distribuées, dans ce contexte. En particulier, nous montrons comment l'étude des performances fait apparaitre les axes d'amélioration du matériel et comment il est possible de dimensionner un cluster pour traiter efficacement une instance donnée.

Finalement, des propositions matérielles pour la conception de serveurs de calculs plus performants pour le traitement de graphes sont formulées. Premièrement, un mécanisme est proposé afin de tempérer la baisse significative de performance observée quand le cluster opère dans un point de fonctionnement où la mémoire vive est saturée. Enfin, les deux applications dévélopées ont été évaluées sur une architecture à base de processeurs basseconsommation afin d'étudier la pertinence de telles architectures pour le traitement de graphes. Les performances mesurés en utilisant de telles plateformes sont encourageantes et montrent en particulier que la diminution des performances brutes par rapport aux architectures existantes est compensée par une efficacité énergétique bien supérieure.

### Introduction

#### Contents

| Context of the thesis          | 3        |

|--------------------------------|----------|

| Research focus and problematic | <b>5</b> |

| Outline of this manuscript     | 7        |

#### Context of the thesis

In 1964 was released what is considered to be the very first supercomputer ever, the CDC 6600 [1], sold about \$8 million each and outperforming every other existing computing platforms. The handcrafted machine was able to execute an outstanding 500 thousand Floating Point Operations Per Seconds (FLOPS) and even reach approximately 1 mega-FLOPS. The core architecture was designed around a 10MHz 60-bit processor with 10 so-called parallel functional units, a very early superscalar-like design. This design also allowed the use of a reduced instruction set, which can be seen as a precursor to the RISC processors that followed.

Since the 6600, other supercomputers have been designed, notably to address the growing demand for computing power. In particular, the Cray 1 [2], released in 1976, brought numerous improvements which quickly promoted it as one of the most successful platform in supercomputer history. With the slightly slowing pace of frequency-related and microarchitectural improvements in processors, new orientations where explored to face the continuous increase in processing power requirements and eventually lead to the design of the first massively parallel computers. In particular, Fujitsu released in 1993 its Numerical Wind Tunnel [6] embedding 166 vector processors, later followed by the 2048-core Hitachi SR2201 [5] in early 1996. It was a dramatic contrast with previous platforms, whose core numbers were kept at a limited four to eight configuration, and a first step toward massively parallel computers.

ASCI Red [7], the first supercomputer to be built around off-the-shelf processors was released in 1996. This platform was the first supercomputer to overcome both the 1 TFLOPS and 1 Megawatt marks. This breakthrough set up the commoditization of supercomputers, with ordinary workstations beginning to be assembled in compute clusters to perform large-scale processing. In the early 2000's, thousand-core supercomputers were designed and eventually broke the 1-PFLOPS barrier, notably with the IBM Roadrunner [31]. Great focus was put at the time to improve networking, power consumption and heat management. Roughly ten years later, supercomputer performances reached

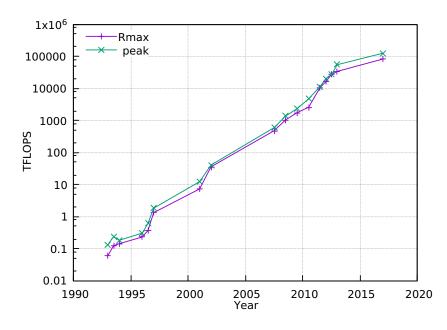

Figure 1: Peak and achieved performances (logarithmic scale) of TOP500's most powerful supercomputer over time.

more than 10 PFLOPS for an estimated consumption of 10MW, as visible in Fig. 1, showing the exponential growth in peak performances of the TOP500 [4] list leading supercomputers. Many of the supercomputers previously presented contributed to major advances in scientific computing, modeling and simulations. Indeed, a primary task of such platforms, especially in the 1960-1970 era, was modeling and simulation for the design of nuclear weapons. The range of applications was quickly extended to weather forecasting, aerodynamic computations and molecular dynamics modeling. However, primary customers were also limited in number due to the extensive initial and operating costs, the limited number of relevant applications at the time and the required programming effort. Indeed, to fully exploit such large installations of cores and memory, parallel programming techniques are needed. Hence, efficient development of applications over such platforms is achieved at the cost of a greater complexity.

Meanwhile, new competitors are entering the field of High-Performance Computing (HPC) with the emergence of large-scale data-mining, often referred to as High-Performance Data Analytics (HPDA) or Big Data computing. Indeed, though traditional scientific computing applications have matured along with supercomputers, new applications are joining in from the data-mining area. Data mining is a not so young scientific domain which mostly involves the processing of datasets using statistical or machine learning techniques to discover patterns or knowledge in it — finding a needle (the knowledge) in a haystack (the data). A particularly concrete example of the spreading of data analytics applications is shown by the fact that a growing number of companies nowadays leverage intensive data-mining algorithms to exploit customer data. As an example, exploiting business-related data can help companies to e.g. adapt their business to their customer base, improve their internal processes or plan a marketing campaign. Finally, though data analytics is considered a rather mature domain, the term Big Data has only been coined in the late nineties with the growing scale of datasets.

More recently, applications processing data modeled under the shape of graphs have been witnessed. This particular area of data-mining, more formally known as graphprocessing or graph analytics, has gained much interest in recent years, with the massive emergence of social networks. More broadly, graph algorithms have proven useful in an increasing number and variety of domains, such as web analysis, security or biomedical applications.

In particular, the ever-accelerating pace of data production has lately transformed data-mining applications into strong peers of legacy HPC applications. These new applications are challenging current architectures, notably due to the required memory amounts and the changing nature of their execution behaviors, which is contrasting with more traditional HPC workloads. Data mining applications — and even more strikingly, graph analytics — have long been known for being data-dependent, irregular and hardly predictable. This becomes a major issue when it is required to deploy them efficiently on distributed architectures at a large-scale.

A consequence of this shift in hardware architectures used in data-mining is the increased programming challenge. Indeed, it requires the end-user, presumably a data practitioner, to endorse multiple responsibilities at the same time, in addition to being a specialist in its field. In order to address the memory requirement, the user must be able to appropriately size its hardware platform, that is, choosing the appropriate amount of compute nodes and per-machine available memory. Then, in order to deploy the algorithm successfully, he must develop system administrator skills to be able to cope with tasks related to cluster management (e.g. handling node failure, network congestion, system update or process distribution), and finally, to fully benefit from the cluster, he should also be a parallel and distributed programming expert. Moreover, data analytic applications evolve at a fast pace and as a consequence, programmers seldom allocate time for the development of an "optimal parallelization" as lifecycles of such applications are shorter in comparison to those of the scientific computing domain. Indeed, data practitioners require a way to quickly implement their algorithms and deploy them seamlessly on a distributed architecture, while benefiting from the performance brought by ever-scaling cluster architectures.

#### Research focus and problematic

In this thesis work, we focus on large-scale graph analytics workloads deployed over distributed-memory architectures. With the advent of Big Data, HPC tools and architectures are more and more often necessary to match the processing/memory requirements of data-mining tasks, hence the term of High-Performance Data Analytics. As graph analytics algorithms are known for being particularly data-dependent, irregular and un-

structured, achieving a scalable parallel implementation on distributed architectures is a particularly challenging task. Though programming frameworks have been proposed to address this programming issue, their scalability and performance behaviors are nontrivially assessed. Moreover, the fast pace at which data-mining applications evolve makes traditional application/dataset benchmarking approaches hardly applicable. In such a situation, choosing an adequate hardware resource becomes challenging. However, being able to properly design a cluster architecture is extremely important to enable the efficient processing of large volume of data. Such ability can help as well, for a given problem, to optimize a cluster setting for maximum compute performances or energy efficiency. Thus, it is also crucial to have means to understand how performances evolve with increasing dataset and cluster sizes, as it gives user hints to appropriately design its cluster for its application needs. In view of those considerations, we hence address the points of understanding performance behaviors of distributed graph analytics workloads implemented using a dedicated library and propose an approach toward scalability/performance evaluation of such applications. The aim of this work is eventually to adumbrate guidelines for the appropriate design of clusters in the context of HPDA applications.

To achieve the aforementioned objectives, we decided to focus on two real-life graphrelated problems rather than numerous synthetic applications usually used for benchmarking purposes. Indeed, in the context of data-dependent performances (*i.e.* performances vary with data size and properties) leveraging well-known algorithms on random scalefree graphs may bring less genuine insights on the real-life performances of a system. For each problem, we provide an in-depth and practical presentation of the novel algorithm we propose, its distributed implementation and the measured performances using a dedicated benchmarking approach. We argue the contrasting natures of the considered problems make them relevant and enable, *in fine*, the gathering of more global insights on performances with respect to software aspects.

We also conducted a performance-oriented comparison of three different hardware platforms based on the use-cases we worked on. These studies highlight inefficiencies in current high-performance architectures, questioning their usage for such purposes notably when put in perspective with their cost. Finally, we propose some cluster design guidelines and architectural considerations to conceive the next generation of high-performance graphprocessing platforms. In particular, we evaluate the relevance of emerging low-power embedded computing platforms in such a context.

To conclude, we argue this work is of much relevance to the following audiences. Data practitioners, and in particular, programmers in the field of graph analytics may be interested by practical aspects of deploying GraphLab implementations, as presented in Chapters 2 and 3. We consider that the benchmarking approaches introduced in Chapter 2 and leveraged throughout this work in particular in Chapters 3 and 4, can be useful as well. Indeed, understanding the behavior of graph-processing applications is of much importance in a field such as graph-mining, where dataset sizes are increasing.

Additionally, being able to adequately design a cluster for a dedicated workload can bring numerous improvements in terms of compute resources availability or energy efficiency. Finally, we argue that the outcomes of the work provided in Chapters 4 and 5 can lead to visible improvements in the hardware architecture design of more efficient distributed clusters. On a more domain-specific point of view, both use-cases studied in this work constitute relevant and novel contributions to their relative fields and thus can be of interest for their applicative aspects.

#### Outline of this manuscript

This manuscript is constituted as follows. Chapter 1 starts with a state of the art in current architectural trends in High-Performance Computing. High-end compute servers, derived from large supercomputing installations seem a weapon of choice for any kind of large computations. However, their cost of ownership and operation may be out of reach, not mentioning the large programming gap required to fully exploit the complex hardware provided. On the other side, many-cores with hundreds of cores in a chip seem promising considering their processing power to energy figure, but they usually come with limited amount of memory and/or a high programming gap. In between, assembling clusters of inexpensive workstations is an interesting trend exhibiting promising performances with respect to its price. Mainstream programming models of interests are discussed and reviewed, as with parallel software tools for data-mining applications. A striking inadequacy between traditional HPC tools (complex, general-purpose) and data-mining requirements (shortened development time, domain-specific semantic) led to the emergence of new domain-specific programming paradigms of many forms. In the particular case of graph analytics, a large variety of approaches has been proposed and, amongst them, domain-specific libraries seem a fairly interesting compromise between ease of use and relevant performances.

As we focus on graph-mining tasks, Chapter 2 introduces mandatory notions in parallel graph-processing programming and details the experimental environment leveraged in this thesis work. In particular, vertex-centric frameworks are introduced and GraphLab, the library we use, is presented in details along with our experimental hardware platforms. This chapter addresses as well the critical issue of assessing and measuring performances of graph-processing systems. More precisely, metrics used in this work and benchmarking aspects of the experiments are discussed in this context. Indeed, graph-processing benchmarks are often constructed around a synthetic scale-free graph generator and a graph algorithm. Though this approach enables a performance comparison between architectures, it hardly gives hints on the behavior of real-life use-cases.

Thus, we decided to build our study on two real-life applications as we argue that the practical experience of implementing and deploying them is valuable. Then, Chapter 3 details the two real-life use-cases we developed and deployed on our experimental systems

using GraphLab. The first application presented is a program trace analysis algorithm, while the second application is a graph-filtering algorithm for genomic data. In particular, we study operating performances and scalability aspects, leveraging the experimental context and metrics previously presented.

Having presented the algorithms and compared their individual performance properties on relevant architectures, gathering software-related insights on performance behaviors, we conduct a comparison of all available hardware systems in Chapter 4. The goal of this chapter is to highlight the efficiency of the available platforms in order to provide more hardware-related insights on the assessed performances. Using performance figures and traditional metrics, we show how such analysis can help in tailoring cluster architectures to a particular workload, which is strikingly relevant in a domain where datasets vary in size and properties, hence affecting the system's throughput.

Chapter 5 discusses more general aspects and perspectives regarding distributed memory cluster design in the context of graph-mining. We propose in this chapter a hardware approach called victim-swap, towards the mitigation of the performance decrease observed when all the memory available in the node is saturated. Indeed, we observed notably that often, a particularly interesting operating point is set near the saturation point of the system memory, increasing the risk of observing swap in/out operations slowing down computations abruptly. We show that by leveraging such cost-effective approach, this risk can be mitigated, hence making it an interesting feature for the next-generation of servers for graph-analytics. Then, having previously studied the performances of wellestablished platforms and going further in hardware propositions, we provide a study of the relevance of emerging embedded computing platforms or microservers. Indeed, though we expect a performance degradation with respect to high-end processors, it is of particular relevance to assess if it can be mitigated by an unmatched energy efficiency in the context of graph analytics — a domain known to be rather memory-bound than compute-bound.

Finally, research perspectives of this work are detailed and presented after a general conclusion is provided.

## High performance computers and parallel programming paradigms

#### Contents

| 1.1 Lar | dscape of high performance parallel machines $\ldots$            | 11        |

|---------|------------------------------------------------------------------|-----------|

| 1.1.1   | Supercomputers and high-end architectures                        | 11        |

| 1.1.2   | Data-crunching many-cores                                        | 13        |

| 1.1.3   | Commodity clusters                                               | 14        |

| 1.1.4   | Summary                                                          | 14        |

| 1.2 Ab  | stractions and design models for parallel programming            | 15        |

| 1.2.1   | Execution models                                                 | 16        |

| 1.2.2   | Memory models                                                    | 18        |

| 1.3 Tov | vards parallel computing for data-mining                         | 20        |

| 1.3.1   | Integrated Development Environment for data-mining $\ . \ . \ .$ | 20        |

| 1.3.2   | Language extension approaches                                    | 21        |

| 1.3.3   | Library-based approaches                                         | 23        |

| 1.4 Co  | ncluding remarks                                                 | <b>24</b> |

The race for processing performances ignited the development of parallel machines and highly efficient parallel implementations. High-Performance Computing (HPC) has been gathering applications requiring large-scale resources such as clusters of computers since the sixties. The field of scientific computing has provided historical HPC applications, as for example physics simulations or partial differential equation solvers. Since, these optimized implementations have been developed and successfully deployed across largescale distributed architectures — a required burden in order to fulfill the compute power requirements of these applications.

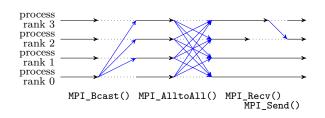

Programming a distributed computer raises substantial programming challenges, such as communication management or data placement which are parallelization-related issues. In particular, the efficient design of a parallel program requires an in-depth understanding of the underlying hardware and software architectures. The HPC community provided numerous approaches to address these parallelization problems. Amongst them, the Message-Passing Interface (MPI) [62] has emerged as the standard for parallel applications on distributed architectures using explicit message passing. An MPI program is usually constituted of many processes distributed across compute nodes performing computations on their private data, only communicating through explicit messages as needed. Though MPI grants the programmer full control over communications, manually handling communications within a program is a non-trivial task and requires an extensive programming effort.

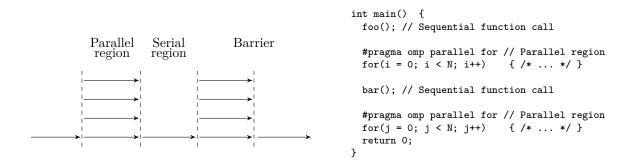

Orthogonal to MPI, another standard has appeared for the parallelization of programs, namely OpenMP [8]. OpenMP allows a fast, user-friendly parallelization of sequential programs by leveraging multithreading over a shared memory view. Indeed, a small set of pragmas are used to automatically parallelize loops in the code, thus hiding the complexity of thread management and allowing an incremental parallelization of sequential sources. An OpenMP program is organized around sequential and parallel regions. Within sequential regions, only the master thread is active. This thread is then forked in parallel region, where spawned workers communicate implicitly through shared objects. Despite being more user-friendly, OpenMP does not scale-out well over non-shared memory architectures due to the high cost of maintaining data consistency across physically separated memory spaces.

More recently, data-mining applications started to claim the title of HPC use-cases, as they require more and more frequently high-performance architectures to manage their ever-increasing dataset size, hence coining the term of High-Performance Data-Analytics (HPDA). In particular, with the rise of graph data in many domains including social networks, security or bioinformatics, graph analytics algorithms gained interests. Though these applications are considered being particularly difficult to deploy efficiently on parallel architectures — notably due to the irregular nature of graph data — data practitioners need now to scale-out their graph analytics workloads. Contrary to the scientific computing, which is now a relatively mature and resourceful domain having deployed fine-tuned distributed MPI applications at scale, the need for large-scale graph-processing implementations is more recent. Unfortunately, none of the aforementioned parallelization approaches (multithreading with OpenMP or message-passing with MPI) is a completely satisfying answer for HPC newcomers because of the scalability or the complexity issues. Indeed, data scientists need now to work at multiple levels to develop an efficient implementation of their algorithm: they need to understand the matching between their algorithm and their data but also, and perhaps more importantly, the underlying hardware. Moreover, these issues are emphasized by the fast pace at which data-mining applications evolve, which is in contrast with decade-long lifecycles of most scientific codes.

This chapter is organized as follows. In the first section, current architectural trends in the field of High-Performance Computing are discussed in order to understand to which extent they can be seen as a hardware platform of choice in the context of High Performance Data Analytics (HPDA) and, in particular, large-scale graph analytics. Then, in Section 1.2, mainstream parallel execution models are detailed, followed by a description of associated relevant memory models. Finally, programming frameworks for data-mining applications are introduced and discussed, before a conclusion is drawn at the end of the chapter.

#### **1.1** Landscape of high performance parallel machines

In this section, we review the main hardware trends in distributed parallel architectures. First, we explore architectures of extreme scale installations seen in HPC centers and high-end compute servers inspired by such machines. Then, massively parallel manycores are presented. Finally, the use of commodity desktop workstations linked in cluster is discussed with respect to large-scale distributed computations.

We focus particularly on node architecture in terms of processor micro-architecture, memory amount or hardware accelerators as it has fueled considerable amounts of specializations that impacted programming. In comparison, networks and interconnects are quite transparently interoperable from the point of view of the user. Hence, we take the assumption that the network is a uniform, reliable crossbar communication network.

#### **1.1.1** Supercomputers and high-end architectures

The study of the state of the art in the field of high-performance computer architecture shows a great deal of variety. Historically, High-Performance Computing started with the emergence of supercomputers, or large powerful computer infrastructures exhibiting astonishing performances at the cost of a staggering complexity and specificity of each architectural solutions. Hence, efficiently exploiting such installations implies a great programming challenge. Nowadays, most supercomputers are built with high-end generalpurpose multiprocessors featuring heterogeneous accelerators (such as co-processors [63] or GPU [86]). Still, such hardware accelerators have already proven useful with existing scientific computing applications, *e.g.* Monte-Carlo numerical simulations for stratospheric balloon enveloppe drift descent analysis [**Plazolles2017**], where the massive available hardware parallelism could be fruitfully wielded by the application. More rarely, some supercomputers rely on specific, off-the-track, computer hardware such as the Cray XMT system [29] with its massively multithreaded processors providing 128 hardware instruction streams where usual simultaneous multithreaded (SMT) cores usually provide up to 16 hardware threads each [21, 82, 86, 110].

IBM Bluegene's architectures — a successful example of a high-end architecture — often top supercomputing ranks on various lists such as Top500 [4], Green500 [28] and Graph500 [45], which evaluate respectively floating point, power-efficiency and graph-processing performances. Architecture-wise, a typical BlueGene/L node embeds two PowerPC440 running at 700MHz [21] and a more recent BlueGene/Q has a 16-core

|  | Chapter $1 - High$ | performance | computers | and | parallel | programming | paradigms |

|--|--------------------|-------------|-----------|-----|----------|-------------|-----------|

|--|--------------------|-------------|-----------|-----|----------|-------------|-----------|

| System                          | Nodes  | Cores      | Node architecture                                         | Memory (per-node)                                                                | Rank                                        |

|---------------------------------|--------|------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------|

| TaihuLight<br>(2016)            | 40,960 | 10,649,600 | 1x SW26010 260C                                           | 32GB                                                                             | Top500: 1<br>Graph500: 2<br>Green500: 17    |

| Tianhe-2<br>(2013)              | 16,000 | 3,120,000  | 2x 12-core Intel Xeon<br>Ivy Bridge 2.2GHz<br>3x Xeon Phi | 64GB<br>24GB (Xeon Phi)                                                          | Top500: 2<br>Graph500: 8<br>Green500: 147   |

| Titan (Cray)<br>(2012)          | 18,688 | 299,008    | 1x 16-core AMD<br>Opteron 6274 2.2GHz<br>1x Nvidia K20x   | $\begin{array}{c} 32 \mathrm{GB} \\ 6 \mathrm{GB} \ \mathrm{(K20x)} \end{array}$ | Top500: 4<br>Graph500: N/A<br>Green500: 109 |

| Sequoia<br>BlueGene/Q<br>(2012) | 98,304 | 1,572,864  | 1x 16-core PowerPC<br>A2 1.6GHz                           | 16GB                                                                             | Top500: 5<br>Graph500: 3<br>Green500: 100   |

| K Computer<br>(2011)            | 88,128 | 705,024    | 1x 8-core SPARC64<br>VIIIfx 2.0GHz                        | 16GB                                                                             | Top500: 8<br>Graph500: 1<br>Green500: 277   |

Table 1.1: Evolution of supercomputer architectures. Though recent installations have shown complex node architectures embedding co-processors and GPUs around a large-many cores, the leading Graph500's architecture shows a much simpler architecture, without hardware accelerators. Top500, Graph500 and Green500 lists as of June 2017.

PowerPC A2 running at 1.6 GHz. In comparison, a typical node from Tianhe-2 [82], one of China's largest supercomputers, embeds two Intel Xeon Ivy Bridge processors running at 2.2GHz and three Xeon Phi co-processors [82], a state of the art co-processor [63, 111] embedding dozens of x86 processors. This results in a grand total of 3, 120, 000 available cores in the full-scale Tianhe-2 installation. The Titan supercomputer from Cray in the National Oak Ridge Laboratory, another state of the art supercomputer, features a 16-core AMD Opteron plus a Nvidia Tesla K20 GPU per node [86].

More recently, for the first time, the TaihuLight [101], the June'17 TOP500 leading supercomputer, embeds chinese-design processor. Indeed, it features a considerably simpler architecture with a single 1.45GHz, 260-core SW26010 processor and 32GB of memory per node. Interestingly enough, supercomputer nodes seem to evolve towards such simpler architectures, a trend anticipated by IBM with its BlueGene machines or by the K-computer, as visible in Tab. 1.1. Such design choice is particularly relevant in the context of graph-processing, as highlighted by their Graph500 results, where the top three machines have straightforward architectures with no hardware accelerators or GPU.

Running and maintaining such heavy infrastructures involve high operational expenditures and may be out of reach for many. However other options are available such as renting compute time slots on open supercomputing centers or through research frameworks. PRACE [98], the European program for advanced computing is an example of such supercomputing center association granting access to high performance platforms.

Such supercomputers have also driven the evolution of high-end server architectures at a more moderate scale. Typical racks embed 2 to 16 high-end processors with terabytes of storage memory [103, 105] with, optionally, hardware accelerators or GPUs. Although more affordable than extreme-scale HPC installations, they usually come at a high cost of ownership, making them unsuitable if expected performances are not guaranteed as in data-dependent and irregular workloads. However, historical web hosting services also offer such dedicated HPC architectures for rent [97] at a more affordable cost, enabling performance benchmarking prior to any longer-term investment.

Even though these architectures can be accessed or built at a more moderate scale matching a smaller demand, the complexity of such clustered architecture is rather high. This complexity greatly increases the programming challenge that users are dealing with. Indeed, extracting the highest performances on such high-end nodes embedding accelerators is not easily reached in the context of data or graph analytics.

#### 1.1.2 Data-crunching many-cores

On the other side of this architectural spectrum, embedded distributed platforms are also available, featuring dozens of processing elements gathered on a single-chip distributed computer. Such platforms can be of huge interests for the processing of large datasets when taking into considerations their low power capabilities. Examples of such architectures include the MPPA many-core, Epiphany-IV and TileGx, detailed in Tab. 1.2.

The MPPA-256 [65] many-core from Kalray is dedicated to massively parallel embedded applications and features up to 256 32-bit cores in a chip, clustered in bulk of 16 cores. The MPPA2-256 (Bostan) [106] was later introduced, with up to 288 64-bit programmable cores. However, though promising, both architectures are more suitable for time-critical or networking applications [92] rather than large-scale data applications.

Adapteva's Epiphany IV [88] can scale from 64 to 4096 cores interconnected by a 2D grid network but processing elements are limited in terms of arithmetic operations and memory per core. Indeed, systems presented in [88] do not exceed 1GB per board, which shall be extended for larger scale data analytic workloads. Moreover, in this purely distributed architecture, the on-chip memory management is leaved entirely to the programmer, increasing the programming burden.

The TileGx processor family is another example of embedded architecture ranging from 9 to 72 processing elements. Conversely to the Kalray and Epiphany architectures, the TileGx provides full cache-coherency across the entire chip [77], at the expense of a more limited scalability.

| System                  | Number of cores | Cluster size | Core architecture | Memory management                  |

|-------------------------|-----------------|--------------|-------------------|------------------------------------|

| Kalray MPPA2            | 256             | 16 cores     | VLIW core, 800MHz | Explicit                           |

| Tilera<br>TileGx        | 9-72            | N/A          | VLIW core, 1.2GHz | Cache coherence<br>across the chip |

| Adapteva<br>Epiphany-IV | up-to 4096      | N/A          | RISC core, 800MHz | Explicit                           |

Table 1.2: Architectural trends in embedded high-performance manycores. The TileGx architecture, contrary to the others, provides cache coherence across the whole chip, but this capability explains its limited scalability with regards to the MPPA and Epiphany architectures.

Though all these architectures foster energy efficient parallel computing, they require dedicated development suites in order for programmers to be able to successfully deploy their implementations. Moreover, notwithstanding the effort required to master such specialized toolchains, it is also a tough task to understand how to adequately implement an application in order to fully exploit the architectural specificities of these platforms. Finally, not all libraries and software tools are fully supported by other processors than the traditional architectures encountered in servers or workstations and the porting task can be demanding and time-consuming.

#### **1.1.3** Commodity clusters

The previously presented architectural trends show that the high-end HPC world is quite heterogeneous and programming at a large-scale on these machines is a cumbersome task [70, 80]. Moreover, previously outlined architectures are either lacking library or compilation support (embedded-oriented many-cores) or unreachable for many due to their high cost of ownership (HPC supercomputers). Acknowledging this context, commodity cluster architectures are emerging in between these two trends, with in mind to leverage more processing power and memory at a more affordable cost. Indeed, desktop workstations nowadays embed 4 or 8 cores and sometimes up to 16 or even 32 Gigabytes of memory. Yet, some datasets may still not fit in their memory, thus requiring the clustering of workstations around, *e.g.* an Ethernet network to further expand memory and processing capabilities. In this context, commodity clusters can be seen as an intermediate solution of interest notably because their performance/price ratio can be significantly higher than traditional high-end clusters.

Such approach has been successfully adopted by Google [12] with an architecture combining thousands of desktop workstations linked across Ethernet networks. As explained by Barroso *et al* in [12], commodity clusters have many advantages such as *e.g.* the initial cost of ownership of compute nodes, which is orders of magnitude lower than high-end systems. Though reliability in commodity clusters is an issue compared with high-end architectures, it can be mitigated in software using dedicated monitoring systems. Moreover, at the scale of hundreds or thousands of machines, the burden of maintaining an architecture is equivalent regardless of the kind of architecture used (high-end or commodity). In the particular case illustrated in [12], reliability is actually software-managed and repair operations are batched in order to keep a low operating cost.

#### 1.1.4 Summary

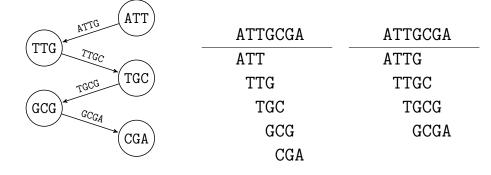

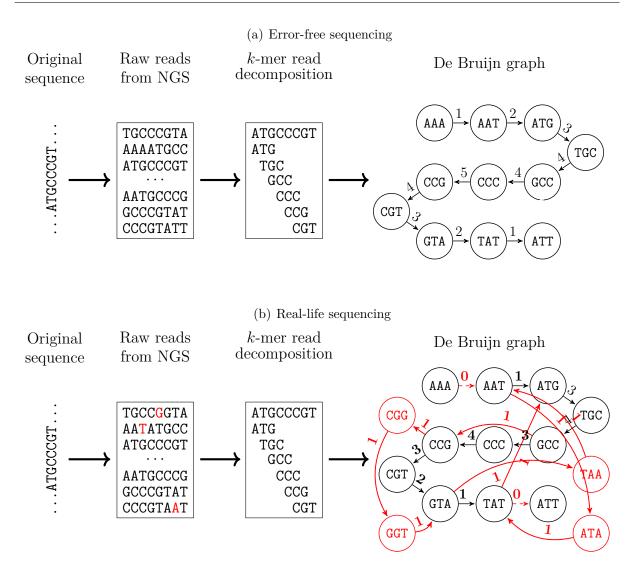

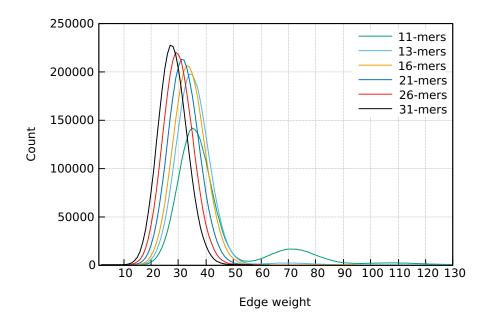

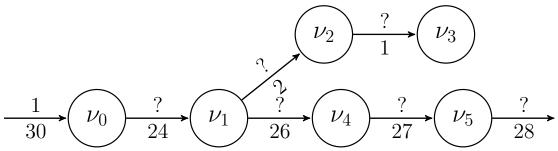

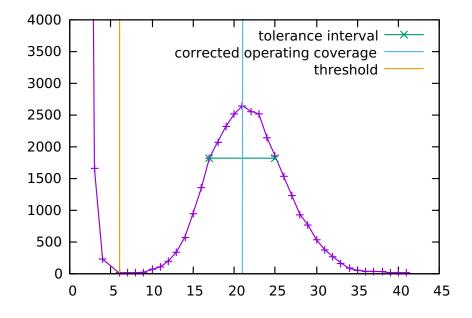

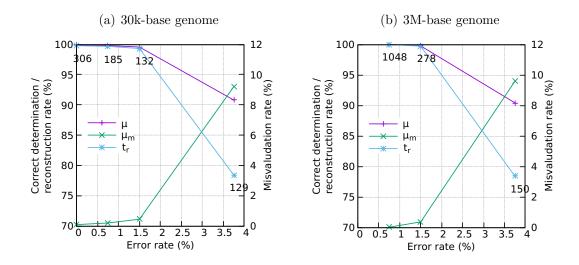

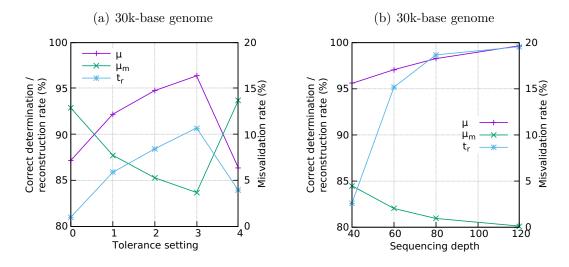

In this section, we detailed the three main architectural trends observed in large-scale distributed processing. Historically, large-scale systems based on dense high performance nodes have proven, despite striking peak performances, to be out of reach for many datamining applications with respect to the programming gap or the operating/acquisition cost wall. On the opposite side, clusters of embedded manycores can be a path of interest thanks to their relatively high energy efficiency which can make acceptable their relative computing performance decrease compared with high-end machines. However, a sufficient amount of memory as with a fair share of mainstream programming tools and libraries should be provided in order to make them hardware platforms of choice as large data analytics platforms.