# Tolerant GPS receiver circuit for electronics errors

Mohamed Mourad Hafidhi

# ▶ To cite this version:

Mohamed Mourad Hafidhi. Tolerant GPS receiver circuit for electronics errors. Signal and Image Processing. Université de Bretagne Sud, 2017. English. NNT: 2017LORIS458. tel-01803420

# HAL Id: tel-01803420 https://theses.hal.science/tel-01803420v1

Submitted on 30 May 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE BRETAGNE SUD

UFR Sciences et Sciences de l'Ingénieur sous le sceau de l'Université Européenne de Bretagne

Pour obtenir le grade de :

DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE SUD

Mention : STICC

École Doctorale SICMA

présentée par

# Mohamed Mourad HAFIDHI

Lab-STICC: Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la connaissance

# Un circuit de réception GPS tolérant aux erreurs de l'électronique

### Thèse soutenue le 16-11-2017,

devant la commission d'examen composée de :

## M. Jean-Didier Legat

Professeur, Université Catholique de Louvain / Président

# M. Patrick Girard

Directeur de Recherche CNRS, LIRMM Montpellier / Rapporteur

### M. Emmanuel Simeu

Maître de conférences, HDR, TIMA Grenoble / Rapporteur

### M. Arnaud Dion

Ingénieur de recherche, ISAE Toulouse / Examinateur

### Mme. Fabienne Uzel-Nouvel

Maître de conférences, HDR, INSA de Rennes / Examinatrice

### M. Emmanuel Boutillon

Professeur, Université de Bretagne-Sud / Directeur de thèse

**Résumé** — Avec l'avancée technologique, la minimisation des transistors et la réduction des tensions d'alimentation ont permis de concevoir des applications complexes à faible consommation. Cependant, en abordant les limites de l'intégration des transistors de faible tension d'alimentation, la fiabilité des circuits devient critique. Les circuits sont sujet des erreurs dues aux perturbations environnementales, défauts de fabrication et interférences. L'apparition de ces erreurs peut affecter le comportement du circuit et générer en sortie un dysfonctionnement du système. Par conséquent, il est de plus en plus important de considérer les effets de ces erreurs dans la conception des futurs circuits.

L'objectif de la thèse est de traiter la fiabilité des systèmes numériques et d'introduire de nouvelles techniques de tolérance aux pannes permettant de construire des applications de traitement de signal fiables sur un électronique peu fiable. Un exemple d'application a été considéré durant la thèse: les modules de poursuite dans un récepteur GPS. Ces modules contiennent un ensemble d'applications de traitement de signal avec des exigences de fiabilité différentes : fonction de corrélation, boucles fermées, machine d'état, générateurs de codes et de porteuses. À partir d'une version standard d'un récepteur GPS, des mécanismes de redondance ont été proposés et ajoutés pour concevoir un récepteur GPS plus tolérant aux erreurs. Un circuit intégré (ASIC) sera conçu en utilisant la technologie 28 nm pour valider les performances de ces techniques et faire les tests de mesures de consommation d'énergie. Au cours de la thèse, une plate-forme d'émulation a été conçue pour préparer l'environnement expérimental à utiliser une fois l'ASIC fondu.

**Abstract** — There is continual motivation to scale down transistors and reduce the supply voltage of circuits. However, by approaching the limits of transistor scaling and operating at a minimal supply voltage, circuit reliability has emerged as a critical concern. Circuits become more and more susceptible to errors due to Process, voltage and temperature (PVT) variations. Occurrence of errors can affect the behaviour of circuits and generate a permanent system failure. Therefore, it is increasingly important to deal with errors effects in order to keep future devices working properly.

The objective of the thesis is to address the reliability in digital systems and introduce new fault tolerant techniques to perform reliable signal processing applications on unreliable hardware. An example of application has been considered in the thesis: the tracking process of GPS receivers. It contains a very interesting set of different signal processing problem with different requirements of reliability: Correlation process, tracking loops (recursive operations), state machine, Gold and carrier generators. Starting from a noiseless GPS receiver, redundant mechanisms have been proposed and added to design a more resilient GPS receiver tolerant to errors. An Application-Specific Integrated Circuit (ASIC) will be designed, based on thesis results, using the 28 nm technology to validate the performances of the proposed techniques performances. During the thesis, an emulation platform was designed to prepare the experimental environment for the ASIC.

$N^{o}$  ordre: 458

Université de Bretagne Sud, Lab-STICC Centre de Recherche Christiaan Huygens - BP 92116, 56321 Lorient CEDEX Tél : + 33(0)2 97 87 45 62 Fax : + 33(0)2 97 87 45 27

# Acknowledgements

I would like to express my deepest gratitude to my thesis director, Prof. Emmanuel Boutillon. His encouraging attitude, profound guidance and invaluable advises helped keeping my research well directed. Also for his carefully reviewing this report which helped to improve the quality of the manuscript.

My sincere thanks also goes to Arnaud Dion, Guillaume Beaugendre and Benoit Priot, members of the Navigation team in the Institut Supérieur de l'Aéronautique et de l'Espace. Their support and valuable advices helped me resolve many problems during my research.

My grateful thanks are also extended to Prof. Chris Winstead for his generous welcome and his valuable and constructive suggestions during my stay in Utah State University for a collaborative research visit.

I would also like to acknowledge all my master students who provided me an opportunity to enrich my understanding through sharing my knowledge about the subject and also for their valuable contribution to my work.

Finally, none of this would have been possible without the love and patience of my family and my friends. Their constant support and strength has aided and encouraged me throughout this endeavour.

# Contents

| In | ntroduction 1 |                                                            |    |  |

|----|---------------|------------------------------------------------------------|----|--|

| 1  | Cor           | Context and Motivation                                     |    |  |

|    | 1.1           | Technology Scaling Challenges                              | 5  |  |

|    | 1.2           | Reliability Improvement Approaches                         | 7  |  |

|    |               | 1.2.1 Fault Avoidance                                      | 7  |  |

|    |               | 1.2.2 Fault Removal                                        | 8  |  |

|    |               | 1.2.3 Fault Tolerance                                      | 8  |  |

|    | 1.3           | Fault tolerant architectures                               | 11 |  |

|    |               | 1.3.1 Von Neumann Multiplexing Architectures               | 11 |  |

|    |               | 1.3.2 Triple Modular redundancy                            | 13 |  |

|    |               | 1.3.3 Restorative Feedback method                          | 14 |  |

|    |               | 1.3.4 Redundant Residue Number System                      | 16 |  |

|    |               | 1.3.5 Algorithmic Noise Tolerance                          | 19 |  |

|    |               | 1.3.6 Razor systems                                        | 20 |  |

|    | 1.4           | Hardware efficiency versus error probability               | 22 |  |

|    |               | 1.4.1 The Reliability Efficiency Criteria of the S-TMR     | 23 |  |

|    |               | 1.4.2 The Reliability Efficiency Criteria of the T-TMR     | 24 |  |

|    |               | 1.4.3 The Reliability Efficiency Criteria of the Razor II  | 24 |  |

|    |               | 1.4.4 Comparison results                                   | 25 |  |

|    | 1.5           | Summary                                                    | 26 |  |

| 2  | FT-           | -ECC and DSC: New fault tolerant schemes                   | 29 |  |

|    | 2.1           | Definitions                                                | 30 |  |

|    |               | Fault Tolerant based Error Code Correcting scheme (FT-ECC) | 31 |  |

iv Contents

|   |       | 2.2.1 The FT-Hamming scheme                                               | 31 |

|---|-------|---------------------------------------------------------------------------|----|

|   |       | 2.2.2 Application of the ANT in the FT-Hamming scheme                     | 34 |

|   |       | 2.2.3 Generalisation: FT-ECC scheme                                       | 35 |

|   | 2.3   | Principle of the Duplication with Syndrome based Correction (DSC) $$      | 36 |

|   |       | 2.3.1 The Three Duplication with Syndrome based Correction scheme (3-DSC) | 36 |

|   |       | 2.3.2 Generalisation: N-DSC scheme                                        | 38 |

|   | 2.4   | Evaluation of the FT-Hamming and 4-DSC schemes                            | 39 |

|   |       | 2.4.1 The normalised hardware efficiency                                  | 40 |

|   |       | 2.4.2 Robustness Performances                                             | 41 |

|   | 2.5   | Summary                                                                   | 45 |

| 3 | Inte  | roduction to the GPS navigation system                                    | 47 |

| J | 11101 |                                                                           | 41 |

|   | 3.1   | GPS system segments                                                       | 47 |

|   | 3.2   | GPS position measurements                                                 | 48 |

|   | 3.3   | GPS Satellite signals                                                     | 49 |

|   | 3.4   | GPS User Equipment                                                        | 50 |

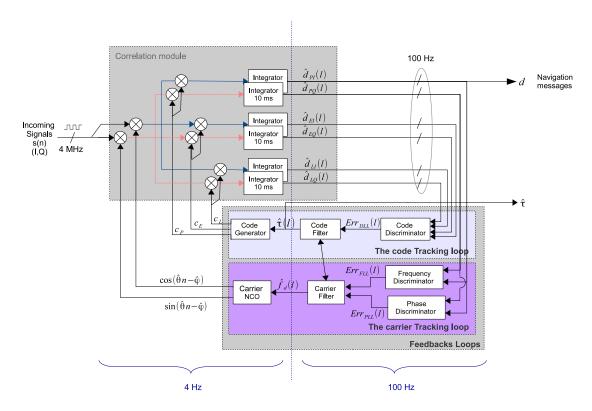

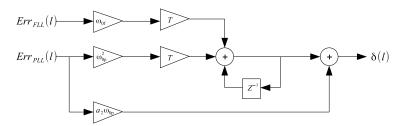

|   |       | 3.4.1 The carrier tracking loop                                           | 51 |

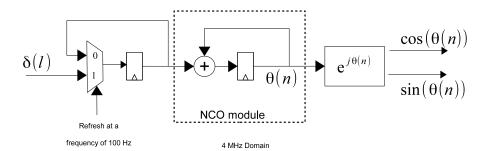

|   |       | 3.4.2 The code tracking loop                                              | 53 |

|   |       | 3.4.3 GPS Code Generation                                                 | 55 |

|   | 3.5   | Summary                                                                   | 55 |

| 4 | Cas   | e Study: Fault tolerance of the GPS tracking channel module               | 57 |

| * |       | ·                                                                         |    |

|   | 4.1   | Resilience of the tracking loop channel against faults                    | 58 |

|   | 4.2   | Robustness of the Correlation Function                                    | 61 |

|   | 4.3   | Reliable Code Generator                                                   | 63 |

|   |       | 4.3.1 The principle of GPS codes                                          | 64 |

|   |       | 4.3.2 Protection with TMR                                                 | 64 |

Contents

|   |     | 4.3.3  | Protection with FT-Hamming                                              | 67 |

|---|-----|--------|-------------------------------------------------------------------------|----|

|   |     | 4.3.4  | Protection with parity-check error detection                            | 68 |

|   |     | 4.3.5  | Evaluation                                                              | 71 |

|   | 4.4 | Reliab | cility of the carrier discriminator                                     | 72 |

|   |     | 4.4.1  | The linearised representation of the carrier tracking loop              | 72 |

|   |     | 4.4.2  | The proposed method                                                     | 73 |

|   |     | 4.4.3  | The standard deviation $\sigma_X(p)$                                    | 74 |

|   |     | 4.4.4  | The error induced Tracking Error Variance                               | 74 |

|   |     | 4.4.5  | Performances and results                                                | 74 |

|   | 4.5 | Reliab | ele NCO carrier Generator                                               | 76 |

|   |     | 4.5.1  | The Rendez-vous Checking method (RvC)                                   | 77 |

|   |     | 4.5.2  | Time Freezing Method (TF)                                               | 77 |

|   |     | 4.5.3  | Comparison results                                                      | 78 |

|   | 4.6 | Summ   | ary                                                                     | 79 |

| 5 | The | GPS    | Emulation platform                                                      | 81 |

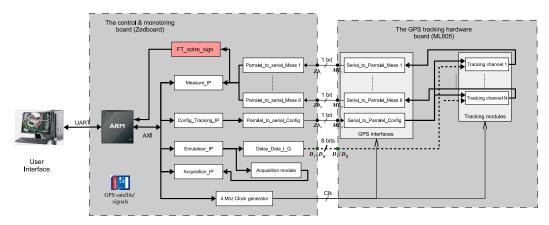

|   | 5.1 |        | PS Emulation platform                                                   | 82 |

|   |     | 5.1.1  | General description                                                     | 82 |

|   |     | 5.1.2  | Architecture of the platform                                            | 82 |

|   |     | 5.1.3  | Simulation flow inside the platform                                     | 84 |

|   | 5.2 | Contri | ibutions and modifications                                              | 86 |

|   |     | 5.2.1  | Adapt the design of the GPS tracking channels for $4\mathrm{MHz}$ clock | 86 |

|   |     | 5.2.2  | Isolate the tracking channels modules in a separate board               | 86 |

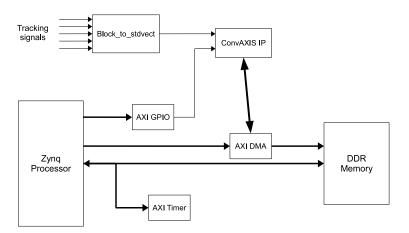

|   |     | 5.2.3  | Improving the GPS tracking observability                                | 88 |

|   |     | 5.2.4  | Include the robust version of the GPS tracking channels                 | 91 |

|   | 5.3 | Summ   | ary                                                                     | 92 |

|   |     |        |                                                                         |    |

| vi | i C | ont | ent | ts |

|----|-----|-----|-----|----|

|    |     |     |     |    |

| Co | Conclusion 95  |        |                                                            |     |  |

|----|----------------|--------|------------------------------------------------------------|-----|--|

| Ρŀ | PhD Summary 97 |        |                                                            |     |  |

| A  | Ann            | exe    |                                                            | 99  |  |

|    | A.1            | The ar | nalysis of the the robustness of Von Neumann architectures | 99  |  |

|    |                | A.1.1  | Reliability of the NAND Mux architecture                   | 100 |  |

|    |                | A.1.2  | Reliability of the Maj Mux architecture                    | 101 |  |

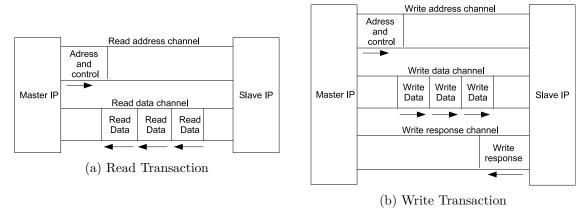

|    | A.2            | The X  | ilinx AXI protocol                                         | 102 |  |

|    | A.3            | The pl | latform functionality                                      | 103 |  |

|    |                | A.3.1  | Initiate the communication with the board                  | 103 |  |

|    |                | A.3.2  | Run the Emulator                                           | 104 |  |

|    |                | A.3.3  | Configure and initiate tracking channels                   | 105 |  |

|    |                | A.3.4  | Get tracking measurements                                  | 106 |  |

|    | A.4            | Pin Co | onnection for the Zedboard, the ML605 and the FMC Cards    | 108 |  |

|    | A.5            | Placen | ment constraint files                                      | 108 |  |

|    |                | A.5.1  | The Vertex-6 ML605 board                                   | 108 |  |

|    |                | A.5.2  | The ZedBoard                                               | 109 |  |

|    |                | A.5.3  | FMC Debug Cards                                            | 110 |  |

| Ri | hling          | rranhv |                                                            | 113 |  |

# List of Figures

| 1.1  | Transistor count and clock Feature size scaling trend over years              | 6  |

|------|-------------------------------------------------------------------------------|----|

| 1.2  | General scheme of error detection with error detecting codes                  | 9  |

| 1.3  | Duplication with Comparison scheme                                            | 10 |

| 1.4  | Two Von Neumann architectures                                                 | 12 |

| 1.5  | Maj Mux and NAND Mux performances                                             | 13 |

| 1.6  | Different configurations of the TMR                                           | 14 |

| 1.7  | TMR temporel configuration                                                    | 14 |

| 1.8  | The standard C-element circuit                                                | 15 |

| 1.9  | The modified C-element design                                                 | 15 |

| 1.10 | Implementation of the Retroactive FeedBack method                             | 15 |

| 1.11 | The two phases of the RFB method: the setup and the restoration phase $$ . $$ | 16 |

| 1.12 | Two ANT based schemes: (a) RPR technique, (b) ASET technique                  | 19 |

| 1.13 | Razor I system architecture to protect logics against timing faults           | 20 |

| 1.14 | A timing diagram of the Razor I system when a timing error occur in cycle $2$ | 21 |

| 1.15 | Recovery using the global clock gating                                        | 21 |

| 1.16 | A timing diagram where a short path is flagged as an error in cycle 3         | 22 |

| 1.17 | Description of the bubble Razor algorithm                                     | 22 |

| 1.18 | The RE-Criteria for S-TMR, BRRNS, Razor and ARQ architectures                 | 25 |

| 2.1  | Reliability improvement using TMR                                             | 31 |

|      |                                                                               |    |

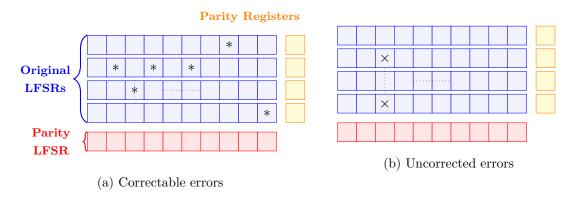

| 2.2  | Introduction to the FT-Hamming solution                                       | 32 |

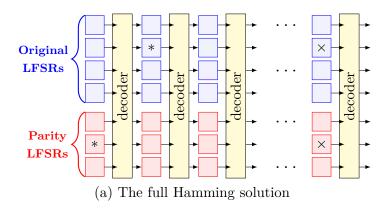

| 2.3  | Architecture of the FT-Hamming scheme                                         | 34 |

| 2.4  | ANT applied in the FT-Hamming scheme                                          | 35 |

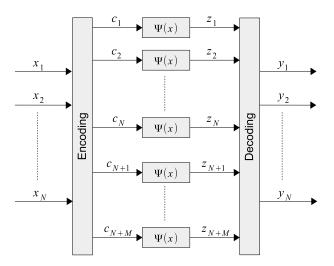

| 2.5  | Illustration of the FT-ECC solution                                           | 35 |

viii List of Figures

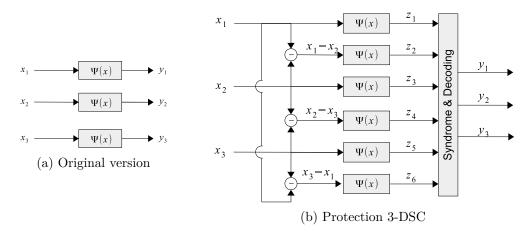

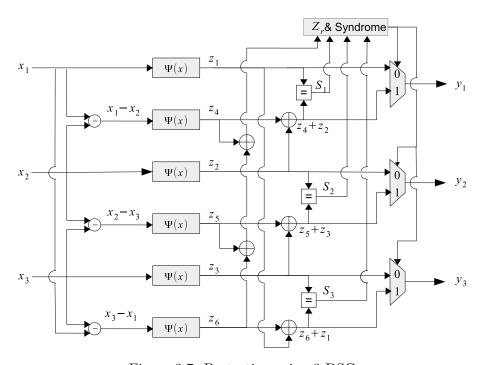

| 2 | 2.6  | Introduction to the 3-DSC concept                                                                 | 36 |

|---|------|---------------------------------------------------------------------------------------------------|----|

| 2 | 2.7  | Protection using 3-DSC                                                                            | 38 |

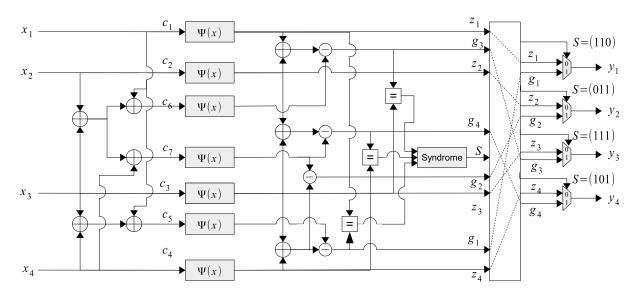

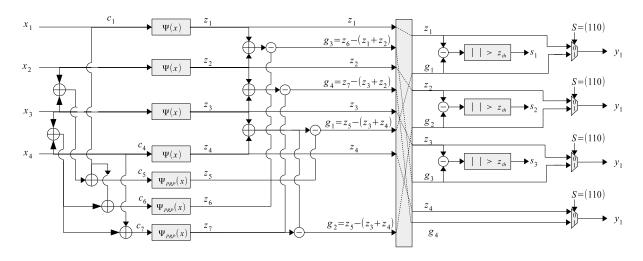

| 2 | 2.8  | Correction using Local syndromes for N-DSC scheme                                                 | 39 |

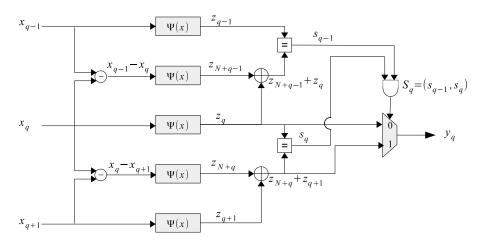

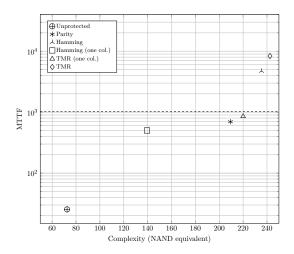

| 2 | 2.9  | Complexity comparison of the FT-Haming, 4-DSC and TMR scheme                                      | 41 |

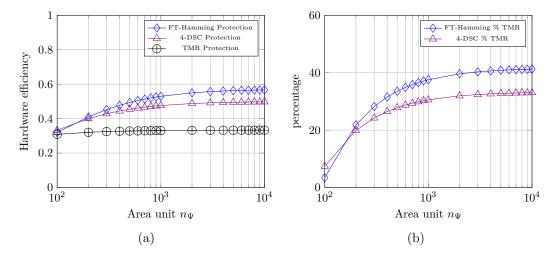

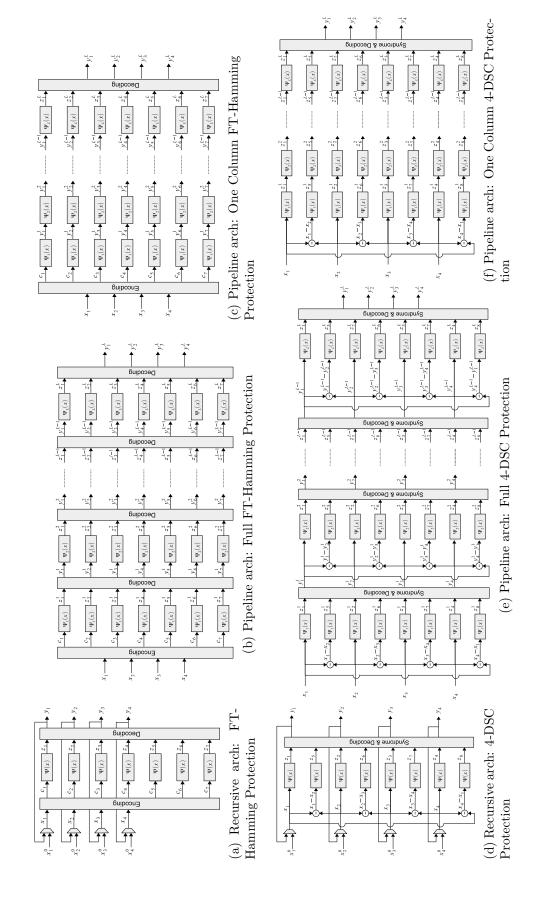

| 2 | 2.10 | Examples of application to explore fault tolerance                                                | 42 |

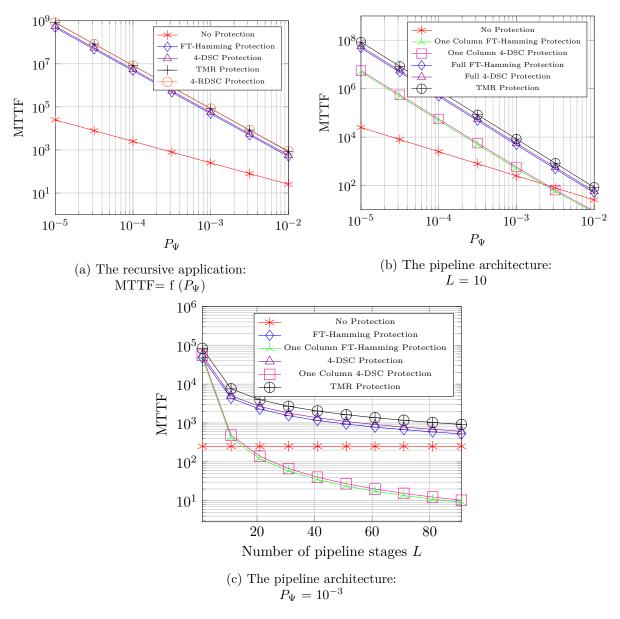

| 2 | 2.11 | Performance Results                                                                               | 44 |

| 2 | 2.12 | Application of the FT-Hamming and 4-DSC for recursive and pipeline applications                   | 46 |

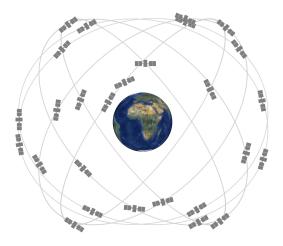

|   | 3.1  | $24\mbox{-}\mathrm{GPS}$ satellite constellation, as defined in the SPS Performance Standard $$ . | 48 |

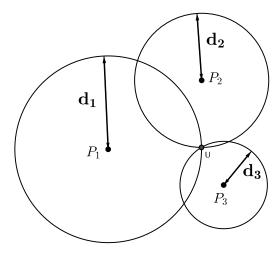

| ٠ | 3.2  | The GPS user position                                                                             | 49 |

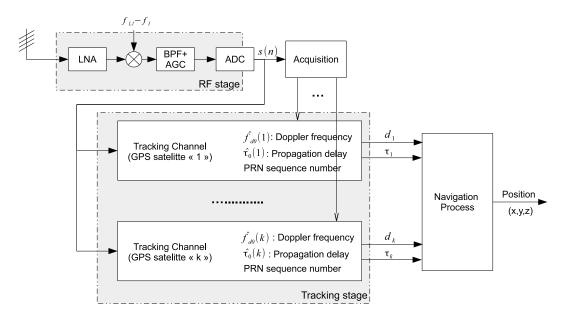

| ٠ | 3.3  | Generic GPS receiver block diagram                                                                | 50 |

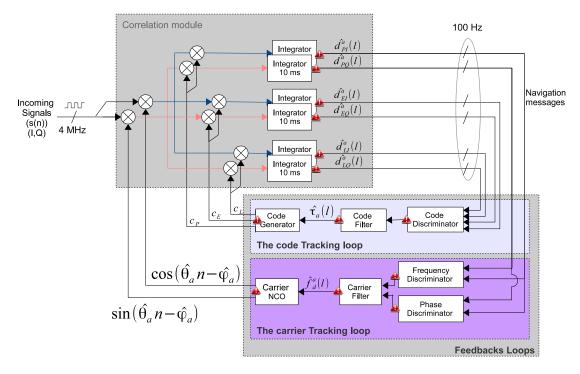

| ٠ | 3.4  | Generic digital receiver channel block diagram                                                    | 52 |

| ٠ | 3.5  | First order FLL assisted second order PLL                                                         | 53 |

| ٠ | 3.6  | NCO generator block diagram                                                                       | 53 |

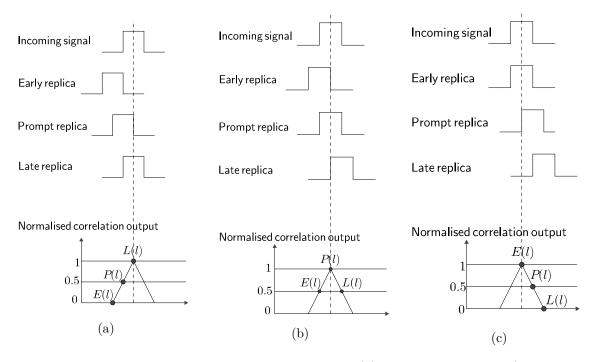

|   | 3.7  | Code correlation cases                                                                            | 54 |

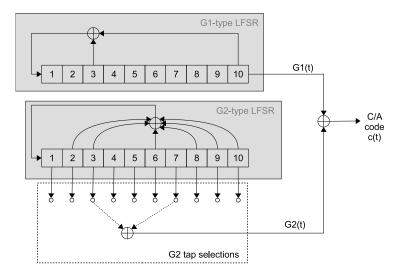

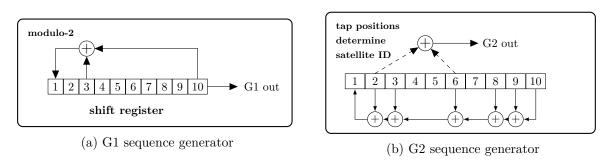

|   | 3.8  | C/A Code Generator                                                                                | 55 |

| 4 | 4.1  | Fault components of the top Level of the tracking channel                                         | 58 |

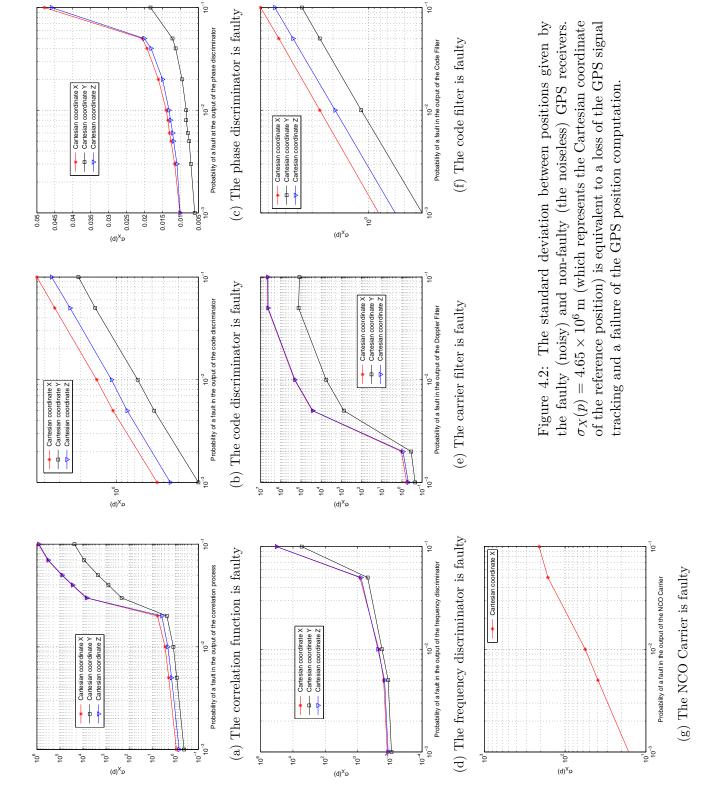

| 4 | 4.2  | The standard deviation between positions given by the faulty and non-faulty GPS receivers         | 60 |

| 4 | 4.3  | FFL and LCV hardware configurations                                                               | 62 |

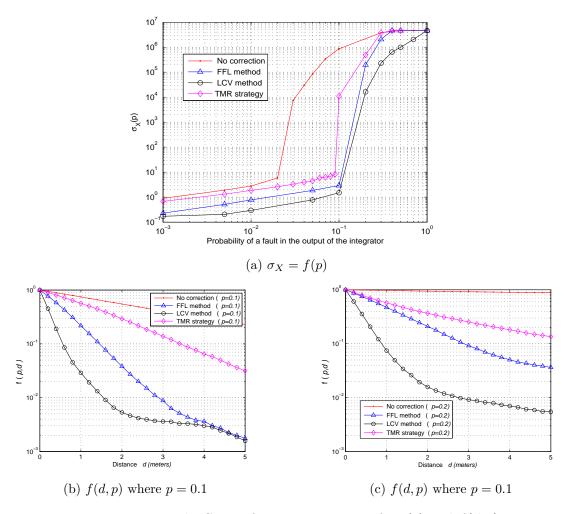

| 4 | 1.4  | FFL and LCV Performances in term of $\sigma_X(p)$ and $f(d,p)$                                    | 63 |

| 4 | 4.5  | Global Positioning System (GPS) codes generators                                                  | 64 |

| 4 | 4.6  | Shift register with TMR protection in each flip-flop                                              | 65 |

| 4 | 1.7  | Shift register with TMR protection in the $3^{thd}$ flip-flop                                     | 66 |

| 4 | 1.8  | Trellis graph describing error propagation in the one-column error correction solution            | 66 |

| 4 | 4.9  | Shift registers with FT-Hamming protection                                                        | 68 |

List of Figures ix

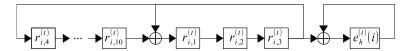

| 4.10 | New architecture of G1 LFSR with row parity                                          | 69  |

|------|--------------------------------------------------------------------------------------|-----|

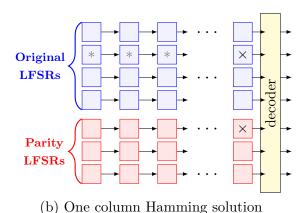

| 4.11 | The Parity checking method configuration                                             | 70  |

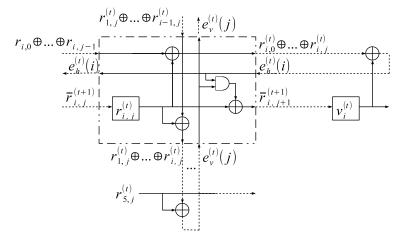

| 4.12 | Schematic for parity-based correction of the $j^{th}$ flip-flop in the $i^{th}$ LFSR | 70  |

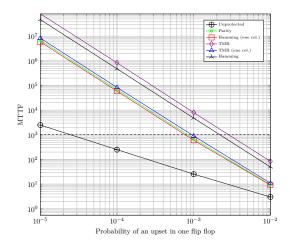

| 4.13 | Complexity and performance of the proposed methods                                   | 71  |

| 4.14 | Performance as a function of the upset probability                                   | 71  |

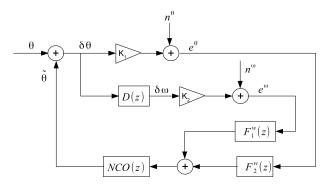

| 4.15 | Structure of the GPS carrier tracking loop                                           | 72  |

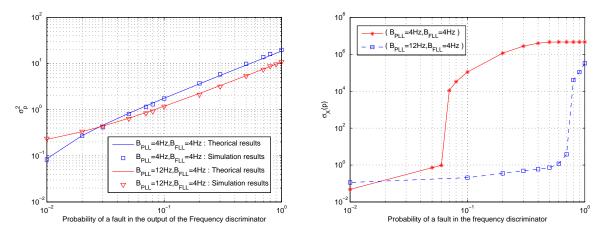

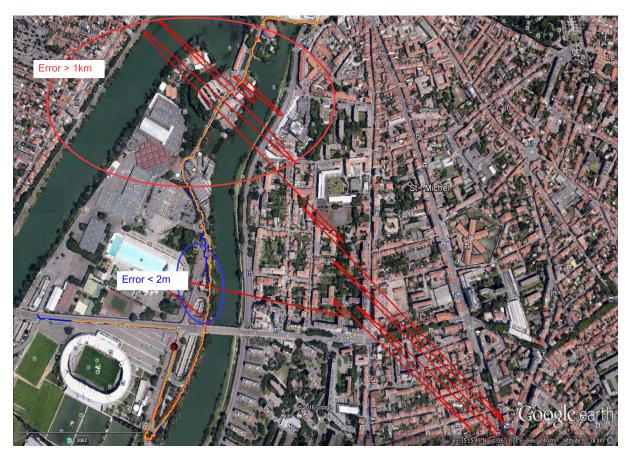

| 4.16 | Performance results of tuning filters bandwidths                                     | 75  |

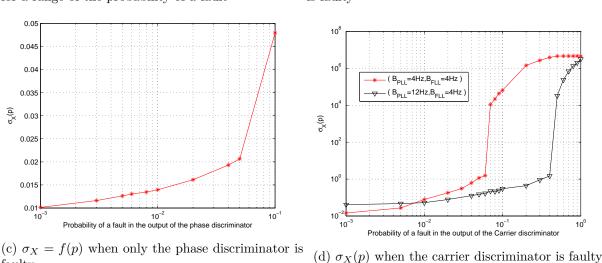

| 4.17 | Trajectories of the standard, faulty and resilient GPS receivers                     | 76  |

| 4.18 | Rendez-vous checking method's configuration                                          | 77  |

| 4.19 | Correction of errors in the RvC method                                               | 78  |

| 4.20 | Time Freezing Method's Configuration                                                 | 78  |

| 4.21 | The performances of the Rvc, TF and the TMR solutions in term of $\sigma_X(p)$       | 79  |

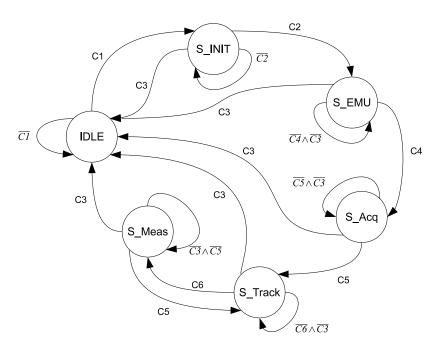

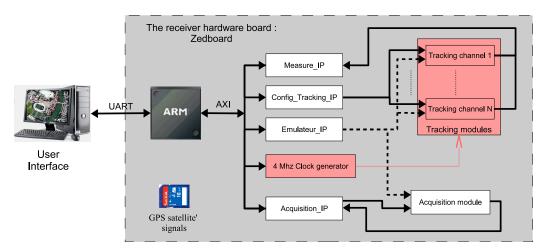

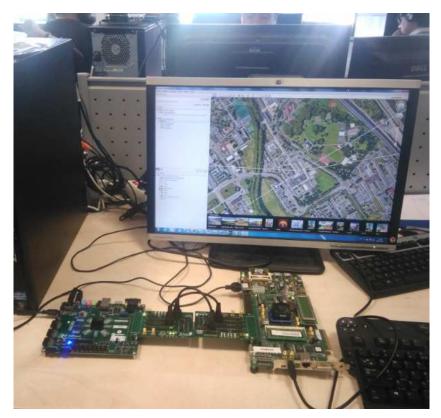

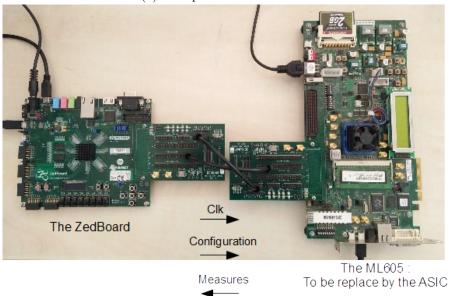

| 5.1  | A representation of the GPS emulation platform                                       | 83  |

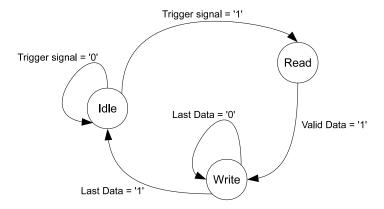

| 5.2  | An illustration of the state machine of the processor                                | 85  |

| 5.3  | An illustration of the first modification on the GPS emulation platform $$           | 86  |

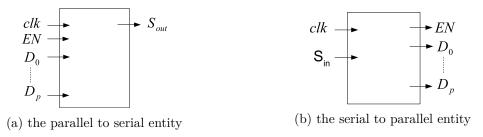

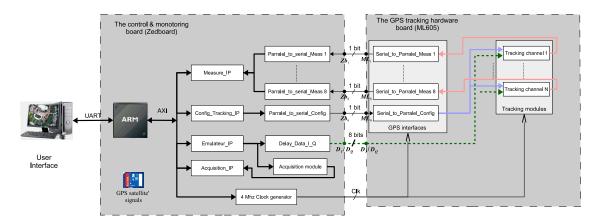

| 5.4  | Supplementary entities for the communication between boards $\dots \dots$            | 87  |

| 5.5  | Schematic of the GPS hardware platform modified                                      | 88  |

| 5.6  | Presentation of the new GPS hardware platform                                        | 89  |

| 5.7  | An illustration of the GPS emulation platform with the observability option $.$      | 90  |

| 5.8  | The diagram of the FT_sotre_sign module                                              | 90  |

| 5.9  | ConvAxis state machine                                                               | 91  |

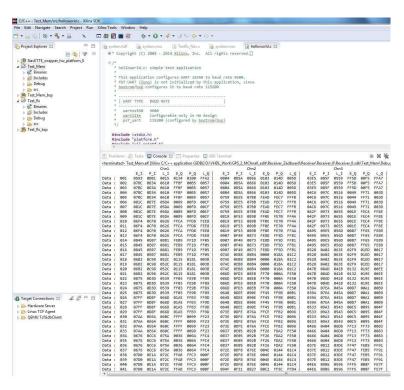

| 5.10 | Correlation output signals stored and displayed on the console of the SDK tool $$    | 92  |

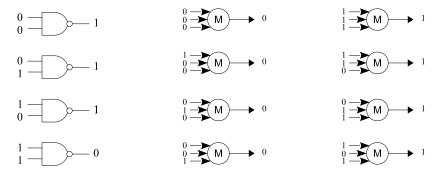

| A.1  | Majority and NAND gates configurations                                               | 100 |

| A.2  | The architecture of the AXI4 interface between slave and master IP cores $$ . $$     | 103 |

| A.3  | The FMC Card referred as the XM 105 board [1]                                        | 110 |

# List of Tables

| 1.1 | Logic synthesis results for the S-TMR                                                                                                        | 25  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Comparison of different fault tolerant architectures                                                                                         | 27  |

| 2.1 | The syndrome corresponding to each faulty module for the FT-Hamming method                                                                   | 34  |

| 2.2 | The syndrome corresponding to each faulty module                                                                                             | 37  |

| 2.3 | Logic synthesis results in term of number of NAND obtained by synthesising the designs with Synopsys Design compiler in the 28 nm technology | 41  |

| 3.1 | The syndrome corresponding to each faulty module for the FT-Hamming method                                                                   | 56  |

| 4.1 | Synthesis results for each method, showing total module counts and the equivalent number of NAND gates per LFSR                              | 70  |

| 5.1 | Principle Matlab Commands and Board Acknowledgements for the GPS platform                                                                    | 84  |

| A.1 | Corresponding Pin Connections of the Xilinx Vertex-6 ML605 board, the Zedboard and the FMC debug cards                                       | 108 |

# Glossary

AMBA Advanced Micro-controller Bus Architecture. 104

ANT Algorithmic Noise Tolerance. 1, 19, 20, 26

ARQ Automatic Repeat reQuest. 23, 25

**ASET** Algorithmic Soft Error Tolerance. 19

**ASIC** Application-specific integrated circuit. 2, 3

AXI Advanced eXtensible Interface. 84, 104, 105

BRRNS Bi-Directional Redundant Residue Number System. 17, 18, 23, 25

CMOS Complementary Metal Oxide Semiconductor. 2

CRT Chinese Remainder Theorem. 17, 18

**DSC** Duplication with Syndrome based Corrector technique. 2

**FFT** Fast Fourier transform. 23

FIR Finite Impulse Response. 25

FT-ECC Fault Tolerant Error Code Correcting based technique. 2

**GPS** Global Positioning System. vi, vii, 2, 3, 53, 59–63, 65, 66, 73–81

ISAE Institut Supérieur de l'Aéronautique et de l'Espace. 3, 81, 83, 84

LFSR Linear Feedback Shift Register. 66–71

MRC Mixed Radix Conversion. 18

MTTF Mean Time To Failure. 2

MWSCAS 2015 Midwest Symposium on Circuits and Systems. 74

**PVT** Process, Voltage and Temperatures. 2, 6

RE-Criteria Reliability Efficiency Criteria. 22, 23

RFB Restorative FeedBack. 14, 16, 26

RNS Residue Number System. 16, 17

xiv

${f RPR}$  Reduced Precision Redundancy. 19

$\textbf{S-TMR}\,$  Spatial TMR. 13, 23, 26

${f SDK}$  Software Development Kit. 93

**SEU** Single Event Upsets. 7

${f SNR}$  Signal to Noise Ratio. 86

**SOI** Silicon On Insulator. 7

T-TMR Temporal TMR. 13, 14, 23, 24

TMR Triple Modular Redundancy. 2, 13, 14, 16

# Introduction

During the past decades, transistor dimensions scaling has greatly lead to enhance computational capabilities of devices and build more and more complex system in one circuit, billions of transistors can now be integrated per square of centimetres in single chip [2]. As well as the huge performances improvements, supply voltage of circuits have also been reduced which has driven to a power savings of circuits. However, approaching the manufacturing nanoscale imperfections limits and by operating at a minimal supply voltage, technology scaling faces new challenges. The increase in integration density makes transistors performances varying under high temperatures and low voltage conditions. Therefore, the reliability of circuit is no longer guaranteed. Faults can appear in transistor outputs which can change the state of a gate, affect the performance of circuits and generate a permanent system failure. Hence, it is increasingly important to consider the reliability issue for the development of high performance and low power devices.

There are three general classes of faults than can affect the performances of a circuit: permanent fault, transient fault and timing fault. Permanent faults are an irreversible physical change that last on time: a stuck at a value of 0 or 1 in a gate output. Transient fault are a temporary change of the binary value of a signal while timing faults are momentary delay in the execution time of an operation. In the literature, a considerable amount of fault tolerant architectures have been proposed to improve reliability of systems in the presence of different type faults. It is John von Neumann that pioneered the idea of using redundancy, in the 1950's, to improve the reliability of systems in [3]. He proved the existence of an arbitrarily reliable architecture under constraint of a minimum reliability of the NAND gate and showed that the objective of making reliable computation on an unreliable architecture is realistic. The well-known Triple Modular Redundancy (TMR) appears as a similar approach with less complexity [4]. In a TMR system, the original module is replicated three times, and error correction is achieved by a majority vote operation. Predictions techniques, such as Algorithmic Noise Tolerance (ANT) technique [5], propose to increase the reliability of circuit by adding a reduced precision replica to the original function. This reduced precision replica consumes much less power than the original function. The final output is chosen between the original function output and the output of the replica. Error Correction Codes has also been proposed to protect memories, [6] and then applied for interconnect networks [7]. All these methods are based on the hardware redundancy to detect and eliminate faults. Another approach to detect faults is to repeat the execution of one operation multiple times and compares the outputs; it refers as the temporal redundancy based approach. The TMRtemporal is an example of temporal based techniques. Finally, Razor systems have been also proposed to deal with timing and transient faults. These systems are based on sampling the output of functions at different instants and detect occurrence of faults by observing the incoherence between the outputs at the two instants [8]. Razor systems don't deal with permanent faults.

2 Introduction

The thesis, part of the RELIASIC project, is funded by French government sponsors COMIN Labs<sup>1</sup>, the National Research Agency in the "Investing for the Future" program under reference ANR-10-LABX-07-01 and the Brittany Region. It addresses the reliability in digital systems and introduces new fault tolerant techniques to perform reliable signal processing applications on unreliable hardware. The robustness capacity in term of Mean Time To Failure (MTTF) and the hardware efficiency of the proposed fault tolerant techniques were solved first to study techniques improvements in general. Then, an example of digital application was considered to evaluate the quality of service of the protected application against faults. The application was the tracking process inside GPS receivers. It is a very interesting application since it contains a several signal processing problems with different requirements of reliability: Correlation process, tracking loops (recursive operations), state machine, Gold and carrier generators.... Starting from the standard version of the GPS application, redundant mechanisms have been proposed and added to design a more resilient GPS receiver tolerant to faults due to Process, Voltage and Temperatures (PVT) variations coupled with the Complementary Metal Oxide Semiconductor (CMOS) technology evolution. An Application-specific integrated circuit (ASIC) will be designed using the 28 nm technology to test the fault tolerant techniques in a real design case and validate by experiments and measurements the performances in terms of robustness and power consumption.

The following of the manuscript is organised as follow:

- Chapter 1 introduces the context and the motivation of the thesis research. It starts by discussing the reliability threat with the trend of technology scaling in integrated circuits. Then, it summarises the different approach of reliability improvement: Fault avoidance, fault removal and fault tolerance. The last section of the chapter provides a survey of the fault tolerant techniques proposed in the literature to improve reliability of circuits and compares the characteristics of their architectures.

- Chapter 2 presents two new fault tolerant techniques based on error correcting codes and duplication with syndromes computation. The two techniques are named the Fault Tolerant Error Code Correcting based technique (FT-ECC) and the Duplication with Syndrome based Corrector technique (DSC). The performances of the two techniques in term of resilience capacity and hardware efficiency are performed and compared to the performances of the classical Triple Modular Redundancy (TMR). This part of work was published in [10].

- Chapter 3 is a brief introduction of the GPS system. It describes first the different segments of the GPS navigation system. Then, it discusses how the GPS position is computed based the GPS satellites signal. Finally, we provide an overview of the GPS user equipment and we describe the structure of the GPS tracking modules.

- Chapter 4 addresses the fault tolerance of the tracking process of GPS receivers. It starts by defining elements of the tracking module that requires the high reliability concern. Then, we detail the fault tolerant techniques proposed to improve reliability

<sup>&</sup>lt;sup>1</sup>Acronym of COMmunication and INFormation sciences Laboratories [9]

Introduction 3

of each block in the GPS tracking process. This work is the summary of publications in [11], [12], [13] and [14].

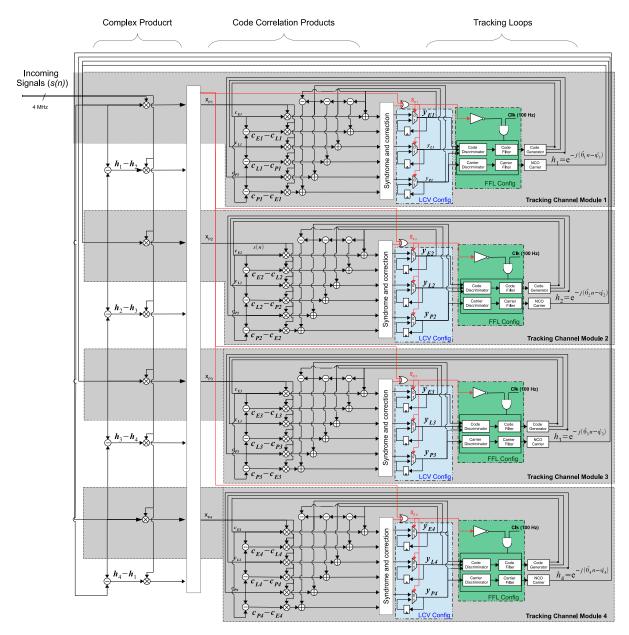

• Chapter 5 describes a GPS hardware emulation platform developed by the Institut Supérieur de l'Aéronautique et de l'Espace (ISAE) to study GPS system and improve navigation algorithms. Several modifications are made on this GPS platform to be exploited for ASIC experiences and measurements: we improved a key module of the tracking loop (i.e. carrier and code estimators) and we modified the whole architecture to isolate the part of the design that will be replace by the ASIC. This chapter details these modifications and presents the resilient version that will be designed in the ASIC.

Finally, the conclusion summarises contributions during the thesis and presents future perspectives.

# Context and Motivation

| Contents | S               |                                                     |

|----------|-----------------|-----------------------------------------------------|

| 1.1      | Tech            | nnology Scaling Challenges                          |

| 1.2      | $\mathbf{Reli}$ | ability Improvement Approaches                      |

|          | 1.2.1           | Fault Avoidance                                     |

|          | 1.2.2           | Fault Removal                                       |

|          | 1.2.3           | Fault Tolerance                                     |

| 1.3      | Faul            | t tolerant architectures                            |

|          | 1.3.1           | Von Neumann Multiplexing Architectures              |

|          | 1.3.2           | Triple Modular redundancy                           |

|          | 1.3.3           | Restorative Feedback method                         |

|          | 1.3.4           | Redundant Residue Number System                     |

|          | 1.3.5           | Algorithmic Noise Tolerance                         |

|          | 1.3.6           | Razor systems                                       |

| 1.4      | Har             | dware efficiency versus error probability           |

|          | 1.4.1           | The Reliability Efficiency Criteria of the S-TMR    |

|          | 1.4.2           | The Reliability Efficiency Criteria of the T-TMR    |

|          | 1.4.3           | The Reliability Efficiency Criteria of the Razor II |

|          | 1.4.4           | Comparison results                                  |

| 1.5      | Sum             | mary                                                |

# 1.1 Technology Scaling Challenges

The past five decades were marked by a huge evolution of semiconductor manufacturing technology where transistors were scaled down in order to improve their speed and decrease their cost and power dissipation. This growth helped to increase the number of transistors per area unit and to build more and more complex system in one chip. One of the first single chips was introduced by Intel in November 1971 and was named the Intel 4004. The chip had 2,300 transistors that ran at a clock speed of up to 740 KHz and dissipated in total 0.5 watts [15]. Today chips employ billions of transistors, include multiple processor cores on a single silicon die, run at clock speeds measured in gigahertz and deliver more than

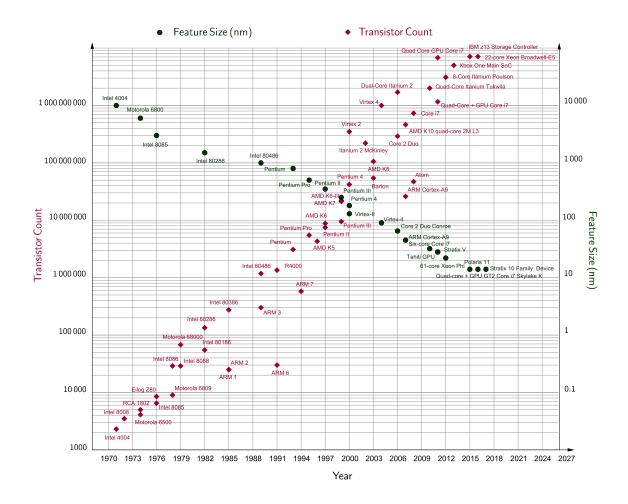

4 million times the performance of the original 4004 [15]. Fig. 1.1 illustrates the trend of technology advancements during the last four decades. Moreover, since power consumption is proportional to the square of the supply voltage  $V_{dd}$ , voltage scaling has been started in the late 80s in order to reduce the consumption of circuits. During the last decades,  $V_{dd}$  was scaled from 5V to 3.3V then to 2.5V and it is predicted to be reduced to 0.64V in 2028 [16].

Figure 1.1: Transistor count and clock Feature size scaling trend over years.

Clearly, the increase of integration density with technology scaling has offered the possibility for designers to build very complex system on a single chip. However, approaching the limits of integration, circuit reliability has emerged as a critical concern. Two main sources can affect the reliability of circuits: 1/ PVT variations and 2/ interference.

➤ PVT variations: Process variations are defined as the imperfections and the lack of precise control of equipment during the fabrication processes [18]. These imperfections appear as a variability of transistor characteristics such as random dopant fluctuation

<sup>&</sup>lt;sup>1</sup>Reliability is defined as the "ability for a system to continue delivering correct service, i.e., perform failure-free operation, for a specified period of time" [17].

and line edge roughness. Voltage variations can increase delays inside circuit when  $V_{dd}$  is lower than the transistor threshold voltage  $V_{th}$ . Chip power densities due to scaling can also lead to global temperature variations as well as local fluctuations in regions of high-activity, so called hot-spots. The temperature fluctuations affect the timing characteristics of circuits and can provoke the wear-out failure that limit the useful lifetime and performance of circuits.

➤ Interferences: Integrated circuits are more and more sensitive to interference such as electromagnetic influences, alpha particle radiation or cosmic radiation. A local creation of charges in the bulk can flip the output of a gate of a memory flip-flop.

Occurrence of faults leads to errors that can change the state of a gate, affect the behaviour of circuits and change the output of a system. Errors or faults can be classified into three main groups: permanent, transient and timing errors. Permanent errors are defined as irreversible physical changes: a stuck at the value 0 or 1 of a bit for a gate or a memory. They can be caused by manufacturing defects or device wear-out [19]. Transient errors are temporal malfunctions that manifest as a temporary change of the binary value of a bit. The other term used for transient errors is Single Event Upsets (SEU). Environmental changes, such as higher or lower temperature and voltage variation, are the essential sources of the occurrence of these errors [20]. Timing errors result when a input signal arrives too late and misses the reference arrival of the clock due to the size down-scaling process [21]. Appearance of faults can cause a system failure if they are not eliminated. Therefore, reliability improvement practises must be considered to guarantee correct system behaviour with the actual technological evolution of the semiconductor industry.

# 1.2 Reliability Improvement Approaches

In order to improve reliability of devices, reliability practices might be taken at different time in the overall development cycle of a system: design time, fabrication time and device lifetime. Reliability practises differ from one level of abstraction to another. In the following sections we describe the different reliability practices according to their chronology in the development cycle as defined in [22].

# 1.2.1 Fault Avoidance

Fault avoidance includes techniques and methods that aim to limit the introduction of faults during specification, design and fabrication phases. A typical example of fault avoidance at design phase is employing transistor resizing within critical gate to decrease the vulnerability to errors [23]. Fault avoidance may also include technology mitigation techniques that implicate modifications of conventional manufacturing processes, for example modern chips designs use Silicon On Insulator (SOI) technology that provides many advantages including

significantly reduced susceptibility to soft errors due to the smaller volume for charge collection [24]. Besides these, using radiation hardened components is another example of fault avoidance practise at design phase.

# 1.2.2 Fault Removal

Despite all best effort done during the manufacturing process to avoid faults, systems may still contain faults. Fault removal techniques are applied so to find and remove causes of faults that can exist in the fabricated device. It includes designs reviews, unit verification, and system testing... Improper fabricated devices can be suppressed.

### 1.2.3 Fault Tolerance

Neither fault avoidance nor Fault removal ensures that fabricated circuits are free of faults. Despite all effort, faults can appear during the lifetime of a system. Besides to that, the moment of the occurrence of faults is unpredictable. Fault-tolerance is the set of measures and techniques that aim to enable continuity of correct service delivered by a system even in presence of errors during its lifetime. They involve generally two essential and sequential steps: error detection and error recovery. Error detection during the normal life of a system is referred as On-Line detection or concurrent error detection. Error recovery mechanisms follow the error detection to eliminate the effect of the errors. This section discusses some well-known techniques for error detection and the main approaches for error recovery.

### 1.2.3.1 On line Error Detection

There exist various strategies for error detection but what they have in common is that they all use redundancies to detect different types of errors. Redundancy takes two forms: spatial and temporal. The spatial redundancy (also known as the hardware redundancy) refers as an addition of components, functions or data in a system. This type of redundancy is very costly in terms of area and power since it is involves extra hardware resources and power dissipation for redundant components. In the temporal redundancy, a computation or a transmission of information is repeated in time. It comes with a throughput penalties and a reduction of system performance. Each approach (temporal or spatial) has advantages and disadvantages in term of cost, performance and error coverage. The decision of which approach to choose depends on the application. For applications where the system cost is less important than its reliability, spatial redundancy is suitable while temporal redundancy is used for applications that tolerate spending extra time to recompute operations. Some known error detection mechanisms are presented in the following sections.

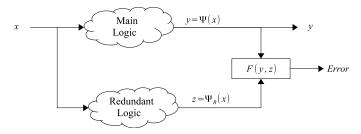

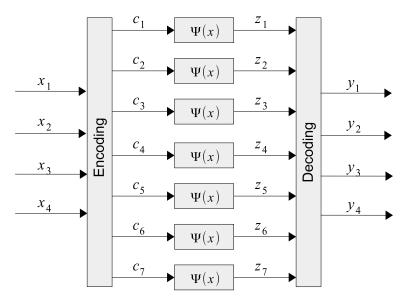

➤ Error detecting codes: The main concept of this technique is to add some hardware redundancy to the main logic to detect possible anomalies after operation. Fig.1.2

illustrates how error detecting codes can be used for fault tolerance. The result y is the output of a circuit logic that performs a function  $\Psi$  on the input x. The redundant logic processes the input x to output  $z = \Psi_R(x)$ . F(y,z) is a function that checks the characteristics that y and z must cater. Let consider the following two examples to illustrate this method.  $1/\Psi(x_1,x_2) = x_1 \times x_2$ ,  $\Psi_R(x_1,x_2) = (x_1 \mod 3) \times (x_2 \mod 3)$ , where mod is the modulo function. F(y,z) checks that  $y \mod 3 = z \mod 3$ . Let us take  $x_1 = 7$ ,  $x_2 = 8$ . If for example the main logic is faulty and y = 31 instead of 56 while the redundant module is fault free,  $z = (7 \mod 3) \times (8 \mod 3) = 2 \times 1 = 2$ . (31  $\mod 3$ ) = 1 \neq (2 \mod 3). An error is flagged in this case.  $2/y = \Psi(x) = \text{FFT}(x)$ ,  $z = \Psi_R(x) = ||x||^2$ . F(y,z) verifies if  $||y||^2 = ||x||^2$ .

The next section will present another example of error detecting codes based technique where the redundant logic is the replica of the original logic.

Figure 1.2: General scheme of error detection with error detecting codes.

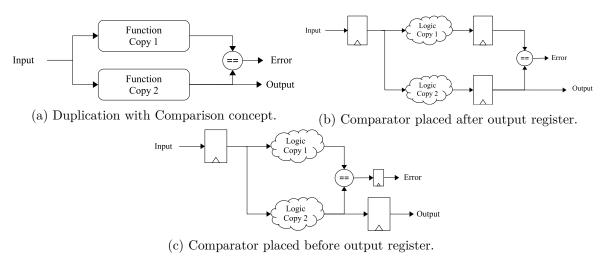

➤ Duplication with comparison: Duplication with comparison is a very popular error detection technique based on hardware redundancy. The original module is duplicated, outputs are compared and an error is flagged when there is an inequality in the result computed by the two copies as shown in Fig.1.3a. The block labelled as '==' represents the static comparator. Apart its simplicity to implement, the Duplication with comparison can detect all type of faults which include permanent, transient and timing faults. An important design decision for schemes that use duplication with comparison is the placement of the comparator.

The simplest way of placing the comparator is to insert it after the output register as shown in Fig.1.3b. It is true that the scheme reduces the power dissipation in the comparator since one transition per cycle is experienced for comparator inputs, but, this requires duplication in the same time of the logic and the output register. The comparator can also be inserted before the output register as shown in Fig.1.3c. The duplication of the output register is, thus, no more required with this comparator placement. However, since the comparator compares during the entire cycle, the comparator experiences an increased switching activity (thus higher power consumption) during the time where the logic outputs are unstable due to the difference in circuit path lengths. Moreover, the comparator output is an unstable signal and needs a latching mechanism to have a stable error signal. The additional path for signals to traverse the comparator has to be considered when choosing when to store the error signal because if the error signal is captured with the clock edge, i.e. at the same time as data is saved in the register, a timing fault may get latched in the output register but can possibly escape

getting latched in error FF. The work in [25] proposes a circuit-level implementation of a special comparator that offers about 30% reductions in power compared with a static comparator with a negligible area overhead.

Figure 1.3: Duplication with Comparison scheme.

➤ Double sampling: The main idea of this method is to observe the output signals of a given circuit at two instants. Incoherence is flagged as error. Compared to the duplication with comparison technique, the double sampling adds a register to the original design which is less costly than adding hardware redundancy in general. Nevertheless, double sampling requires carefully timing constraints related to the critical path of combinatorial logic (short path shouldn't be detected as errors) and is effective only to detect occurrence of transient and timing errors [26].

### 1.2.3.2 Error recovery

Error recovery is the action to transform the system faulty state into an error-free state. There are two main approaches for error recovery: Rollback Error Recovery and Forward Error Recovery.

➤ Rollback Error Recovery: In rollback recovery scheme, errors correction is achieved using the temporal redundancy: 1) system sate is saved periodically or occasionally, the saved state is called a checking point and refers as an error free state for the system, 2/ once an error is detected, the system is taken back to the error free state and operation(s) is (are) repeated. These rollbacks can be just for one cycle deep [27] or up to several thousands of cycles [28]. Although it is simple and independent of the nature fault, the roll-back error recovery has a few inherent drawbacks: First, a degradation of the area due to the overhead to store the error free system sates. Second, the re-execution affect the processing throughput of the design. Finally, there is no guarantee that error will not persist when the operation is repeated (for example with permanent faults).

➤ Forward Error Recovery: The Forward Error Recovery mechanism uses the spatial redundancy to compensate the error state by acting on the damaged part. Error masking is a typical example of forward error recovery scheme. Since no re-computation is needed, the forward error recovery is efficient in application with timing constraints. However, this recovery mechanism needs an accurate assessment of the damage in the system, so, the use of this technique is limited a pre-defined set of applications.

# 1.3 Fault tolerant architectures

The challenge in fabricating small size transistors operating in low supply voltage have resulted in a possible unexpected occurrence of faults in circuits and a loss of reliability of systems. To improve the reliability against faults that appear during the lifetime of a system, a considerable amount of fault tolerant architectures have been proposed until now. In this section, we discuss a set of the relevant fault tolerant architectures that represent most categories of architectures available in literature.

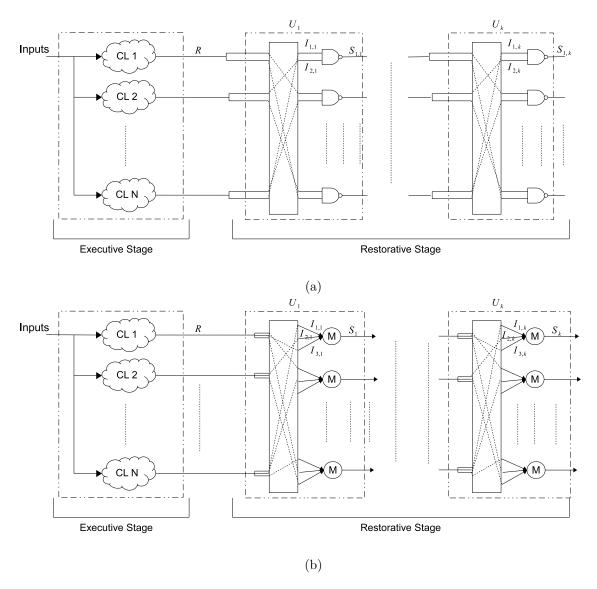

# 1.3.1 Von Neumann Multiplexing Architectures

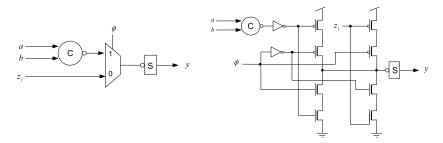

In 1952, Von Neumann addressed the problem of performing reliable computation on unreliable devices and introduced the first redundancy technique called multiplexing [29]. The main concept of the multiplexing technique is to replace the single processing module  $\Psi$  by the so-called "the multiplexing unit"  $(N \gg 1)$ . The design of the multiplexing unit involves two stages: the executive stage and the restorative stage. In the executive stage, the single processing module  $\Psi$  is replicated N times. Each replica processes the same inputs in parallel which gives N independent outputs. If the inputs and devices are reliable, the N outputs should be identical. However, if there are errors, incoherence between outputs is observed. To tackle these errors, outputs of the executive stage are duplicated (or triplicated) and used as inputs of the restorative stage. The restorative stage contains k blocks of N copies of a NAND or a majority gate. The multiplexing unit is called the NAND Mux (respectively Maj Mux) when the corresponding restorative stage is formed by NAND gates (respectively majority gates). Fig. 1.4 illustrates the two multiplexing units.

In the following, we demonstrate how increasing the number of stages (k) improves fault tolerance. To simplify our study, we chose a processing module  $\Psi$  that outputs a binary signal and we determinate  $\eta_{NAND}^{(j)}$  (and respectively  $\eta_{Maj}^{(j)}$ ) the probability that the NAND gate (respectively the majority gate) in the  $j^{th}$  block  $U_j$  of the restorative stage in the NAND Mux (respectively Maj Mux) as illustrate in Appendix. A.3. Let us consider  $\eta_{Maj}^{(1)}$  as defined in (A.25), p the failure probability of the module  $\Psi$  and  $\epsilon$  the failure probability of the NAND and the majority gate. The equation  $(\eta_{Maj}^{(1)} - p = 0)$  has three solutions:  $p_1 = 0.5, p_2 = \frac{1}{2}(1 + \sqrt{\frac{1-6\epsilon}{1-2\epsilon}}), p_3 = \frac{1}{2}(1 + \sqrt{\frac{1-6\epsilon}{1-2\epsilon}}).$   $p_2$  and  $p_3$  exist only if  $\epsilon < 1/6 = 0.16$ . With that, Von Neumann demonstrated that it is possible to build a fault tolerant multiplexing architecture

Figure 1.4: Two Von Neumann architectures: (a) NAND Mux (b) Maj Mux.

only if the failure probability of the basic element of the restorative stage is less than 0.16. Moreover, by increasing the number of blocks inside the restorative stage, the robustness of the multiplexing unit can be improved.

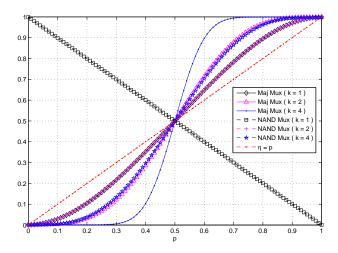

Fig. 1.5 shows the curves of  $\eta_{NAND}^{(k)}$  and  $\eta_{Maj}^{(k)}$  for k=1, 2 and 4 when  $\epsilon=10^{-3}$ . As we can see in this figure,  $\eta_{NAND}^{(1)}$  is an anti-monotone<sup>2</sup> function since NAND transforms an information to its opposite (the NAND gate brings two inputs equal to '0' to an output equal to '1' and vice versa). When p is close to 0, in most case the two inputs are the same, the output will take the opposite value which brings  $\eta_{Maj}^{(1)}$  near to 1. For this reason, the restorative operation needs to be iterated with a second block  $U_2$  in the NAND Mux. The figure demonstrates also that the error probability decreases as the number of blocks inside

<sup>&</sup>lt;sup>2</sup>An anti-monotone function f satisfies the property  $x \le y$  implies  $f(x) \ge f(y)$ ,

the restorative stage increases for both the Maj and the NAND Mux (when  $p \le 0.5$ ). For example, when p = 0.05,  $\eta_{Maj}^{(1)} = 0.0165$ ,  $\eta_{Maj}^{(2)} = 0.0024$ ,  $\eta_{NAND}^{(2)} = 0.0186$  and  $\eta_{NAND}^{(4)} = 0.0046$ .

This result of Von Neumann is a theorem that prove the existence of an arbitrarily reliable architecture under constraint of a minimum reliability of the NAND gate. It shows that the objective of the thesis of making reliable computation on an unreliable architecture is realistic. However, this theorem gives little indication on the hardware because the complexity of the Von Neumann architectures grows very quickly with the required level of reliability and its efficiency (number of operations per time unit and area unit) trends rapidly toward zero. This theorem is similar to the Shannon's second theorem that proves the basic existences of error-correcting codes without giving a practical method for constructing them.

Figure 1.5: Maj Mux and NAND Mux performances.

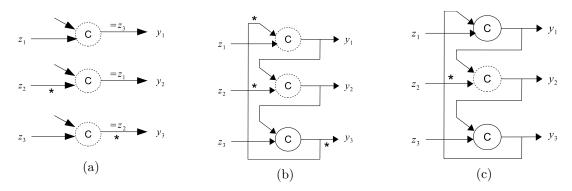

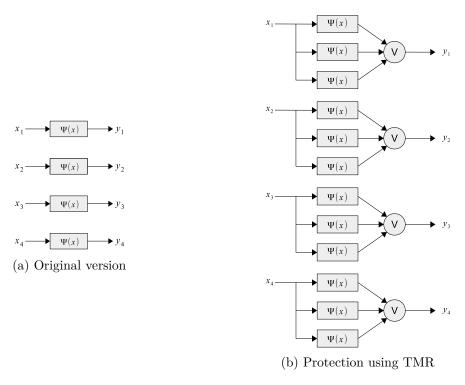

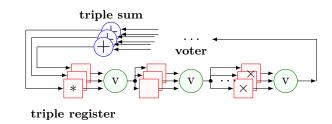

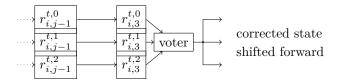

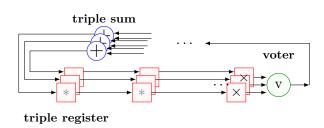

# 1.3.2 Triple Modular redundancy

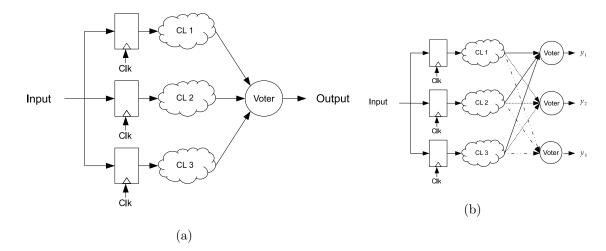

TMR is a classical solution developed in the 60's for fault tolerance in electronic systems [4]. Two versions of TMR exist: the Spatial TMR (S-TMR) and the Temporal TMR (T-TMR). In a standard S-TMR, the original logic module is replicate three times and error correction is achieved by a majority vote operation as shown in Fig. 1.6a. If a fault appears in any one of the three replicas module, the other two replica can correct and mask the fault. But once two of the three replicas fail, an uncorrectable failure results. Faults in the voter can cause the whole system to fail. To deal with these drawbacks, others alternative configurations were proposed, such as the triple-voter method or the restorative-feedback voter [30]. Fig. 1.6b illustrates the triple-voter configuration. All these configurations are costly in term of area and power consumption. As a consequence, the S-TMR is used in general for the robustness of extremely critical applications, such as space, avionics and healthy applications, where the system cost is less important than its reliability. In the T-TMR, the original logic module processes the same input three times during three successive clock cycles. Error correction

Figure 1.6: Two configurations for the TMR: (a) The simple TMR and (b) TMR with three voters.

is achieved by the majority vote between the outputs at the three clock cycles. The T-TMR doesn't tolerate permanent faults.

Figure 1.7: TMR temporel configuration.

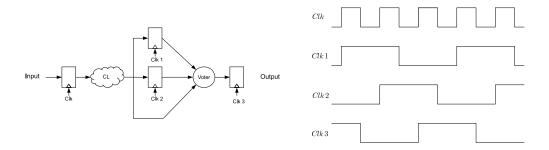

# 1.3.3 Restorative Feedback method

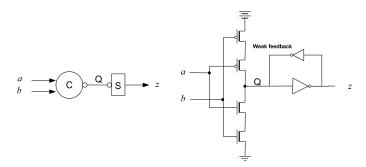

The Restorative FeedBack (RFB) method is logically identical to the TMR method but it relies on the use of C-Muller elements instead of majority gate. The C-element is a well-known gate that has long been used in asynchronous circuit design [31] and was more recently recognised for its inherent fault-compensating abilities. A standard binary C-element circuit is shown in Fig. 1.8. The C-element is logically defined as a two-input latch, a, b and output c. It is composed of C-not gate and S gate. The C-not gate output at the time step t,  $Q^t$ , is defined as,

$$Q^{t} = \begin{cases} \overline{a}, & \text{if } a = b \\ Q^{t-1}, & \text{otherwise} \end{cases}$$

(1.1)

When  $a \neq b$ , the state of S latch is maintained via weak feedback.

Figure 1.8: A standard C-element circuit; the C-not gate detects if the inputs are equal, the S gate acts as an inverting state memory [32].

Figure 1.9: The modified C-element design; phase  $\phi = 0$  active the setup process while  $\phi = 1$  enable the Restoration process [32].

Figure 1.10: Implementation of the Retroactive FeedBack method.

Figure 1.11: Two phases of the RFB method: the setup and the restoration phase. The dotted circles indicate C-elements which are not activated (feed-backs are not activated) while the star indicates the error location. (a) During the setup phase the outputs  $y_1$ ,  $y_2$  and  $y_3$  are initialised with replica signals  $z_1$ ,  $z_2$  and  $z_3$ . (b) In the restoration phase, feed-backs are activating. (c) After a propagation delay, errors are eliminated once C-elements are activated [30].

A modified C-Muller element is given in Fig. 1.9. The modified C-element operates in two phases, called initialisation (set-up) and restoration. During the initialisation phase, the C-not gate is disconnected and the multiplexer force the state of S to be set to a known initial value,  $z_i$ . During the restoration phase, the C-element is activated.

In the RFB scheme, the original module is replicated three times; the three independent output signals,  $z_1$ ,  $z_2$  and  $z_3$  are connected to three modified C-element as illustrate in fig. 1.10. Similar to the TMR, the RFB scheme is able to correct any single error that appears during the initialisation phase. For example, if  $z_2$  is erroneous, the initialized value of the last C-element is incorrect. During the restoration phase, feed-backs are activated. Errors are corrected once the output signal  $y_2$  and the input data  $z_3$  remain correct as shown in fig. 1.11. The RFB method yields an error probability similar to TMR when errors occur during the set-up phase. However, it suppresses most errors that occur during the restoration phase.

# 1.3.4 Redundant Residue Number System

# 1.3.4.1 Introduction and fundamentals

The Residue Number System (RNS) was introduced by Garner in [33]. A standard RNS is defined by a set of k pairwise relative prime positive integers,  $m_1$ ,  $m_2$ ,...,  $m_{k-1}$ ,  $m_k$ , i.e, greatest common divisor  $(m_i, m_j) = 1$  with  $i \neq j$ .  $m_1$ ,  $m_2$ ,...,  $m_{k-1}$ ,  $m_k$  are called moduli. The order of moduli is in increasing, i.e,  $m_1 < m_2 < ... < m_{k-1} < m_k$ . Their product represents the interval [0, M) called the legitimate range that defines the useful computational range of the number system, that is

$$M = \prod_{i=1}^{k} m_i. (1.2)$$

Every natural integer X in the legitimate range can be represented by a set of residues,  $r_1$ ,  $r_2$ , ...,  $r_{k-1}$ ,  $r_k$ , where

$$X \equiv r_i \pmod{m_i}, i.e. \exists \alpha \in \mathbb{N} / X = \alpha m_i + r_i; r_i < m_i.$$

(1.3)

It is frequently desirable to determine the natural number, X, associated with a particular residue representation  $m_i$ . The conversion technique is named the Chinese Remainder Theorem (CRT). According to the the CRT, X can be computed by

$$r_1 A_1 \frac{M}{m_1} + \dots + r_k A_k \frac{M}{m_k} \equiv X \pmod{M}, \tag{1.4}$$

where

$$A_i \frac{M}{m_i} \equiv 1 \pmod{m_i}. \tag{1.5}$$

**Example 1:** Consider a residue number system with bases ( $m_1=2$ ,  $m_2=3$ ,  $m_3=5$ ,  $m_4=7$ ). The legitimate range is equal to 210. The input data 173 is represented by the residue vector (1,2,3,5). The conversion formula for the residue system with base (2,3,5,7) is obtained by

$$105 \ A_1 \equiv 1 \pmod{2} \quad so \ A_1 = 1,$$

$70 \ A_2 \equiv 1 \pmod{3} \quad so \ A_2 = 1,$

$42 \ A_3 \equiv 1 \pmod{5} \implies 2 \ A_3 \equiv 1 \pmod{5} \quad so \ A_3 = 3,$

$30 \ A_4 \equiv 1 \pmod{7} \implies 2 \ A_4 \equiv 1 \pmod{7} \quad so \ A_4 = 4.$

The conversion formula can be used now to determine the natural number corresponding the residue vector (1,2,3,5) as follow

$$1 \times 1 \times 105 + 2 \times 1 \times 70 + 3 \times 3 \times 42 + 5 \times 4 \times 30 = X \pmod{M},$$

$$1223 \equiv X \pmod{210} => X = 173.$$

The great utility of RNS in the context of fault tolerance comes from the following theorem

$$(X * Y) \pmod{M} \equiv ((X(\text{mod } M)) * (Y(\text{mod } M))) \pmod{M}, \tag{1.6}$$

$$(x_1, x_2, ..., x_k) * (y_1, y_2, ..., y_k) = (z_1, z_2, ..., z_k) , z_i \equiv x_i * y_i \pmod{m_i}.$$

(1.7)

where \* denotes the three operations: addition, subtraction, multiplication. By checking this relation, errors in the  $(X^*Y)$  operation can be detected. The following section presents a RNS based system that permits the detection and correction of errors.

## 1.3.4.2 Bi-Directional Redundant Residue Number System (BRRNS)

The Bi-Directional Redundant Residue Number System (BRRNS) is an RNS based system. It is characterised by n pairwise relative prime positive moduli,  $m_1$ ,  $m_2$ ,...,  $m_{n-1}$ ,  $m_n$ , that are formed in increasing, i.e.,  $m_1 < m_2 < ... < m_{n-1} < m_n$  [32]. The first k moduli are called

the information moduli while the remaining n-k moduli are redundancies. Similar to the definition of moduli, the residue vector is composed of the information residues  $r_1$ ,  $r_2$ , ...,  $r_{k-1}$ ,  $r_k$  and the redundant residues  $r_{k+1}$ ,  $r_{k+2}$ , ...,  $r_{n-1}$ ,  $r_n$ . BRRNS codes satisfies the following constraints

$$M = \prod_{i=1}^{k} m_i \approx M_R = \prod_{i=k+1}^{n} m_i,$$

(1.8)

$$m_n < m_1 \times m_2. \tag{1.9}$$

The legitimate range of the BRRNS is  $Min(M, M_R)$  and any redundant modulus is smaller than the product of the two minimum redundant values as (1.9). Since the product of the redundant moduli is approximately equivalent to the product of the information moduli, any integer X belonging to the legitimate range can be restored through the information residue vector or from the redundant residue vector  $(r_{k+1}, r_{k+2}, ..., r_{n-1}, r_n)$ . BRRNS apply the Mixed Radix Conversion (MRC) for the conversion of residue vector to integer in place of the CRT. The MRC is expressed by the following equation

$$X = \sum_{i=1}^{n} \alpha_i \prod_{j=1}^{i-1} m_j, \tag{1.10}$$

where  $0 \le \alpha_i < m_i$  and  $\prod_{j=1}^0 m_j = 1$ . The digits  $\alpha_i$  are called the mixed radix radix digit. They can be obtained from a computation iteration, that is

$$\alpha_{1} = r_{1},$$

$$\alpha_{2} = (r_{2} - \alpha_{1}) \ m_{1,2}^{-1} \ (\text{mod } m_{2}),$$

$$\alpha_{3} = ((r_{3} - \alpha_{1}) \ m_{1,3}^{-1} - \alpha_{2}) \ m_{2,3}^{-1} \ (\text{mod } m_{3}),$$

$$\alpha_{4} = (((r_{4} - \alpha_{1}) \ m_{1,4}^{-1} - \alpha_{2}) \ m_{2,4}^{-1} - \alpha_{3}) \ m_{3,4}^{-1} \ (\text{mod } m_{4}),$$

$$\alpha_{5} = ((((r_{5} - \alpha_{1})m_{1,5}^{-1} - \alpha_{2}) \ m_{2,5}^{-1} - \alpha_{3}) \ m_{3,5}^{-1} - \alpha_{4}) \ m_{4,5}^{-1} \ (\text{mod } m_{4})...$$

$$(1.11)$$

These computations are performed in a serial way, thus, a pipe-lined architecture for the implementation of the mixed radix converter is mostly employed in digital filters [32]. The BRRNS codes with n-k redundant modulus detect errors if the condition  $\alpha_j \neq 0, j \in [k+1,\mathbf{n}]$ , is satisfied. The integer belonging to the legitimate range is restored through the redundant residue vector (if digits of the information residue vector are faulty) or from the information residue vector (if digits of the redundant residue vector are faulty).

**Example 2:** Let us consider the BRRNS composed of the moduli set  $(m_1=4, m_2=5, m_3=7, m_4=11, m_5=13)$ . The legitimate range is  $[0,4 \times 5 \times 7)=[0,140)$ , according to  $Min(M,M_R)$ . If the input data is X=125 is considered, then the corresponding residue values are X=(1, 0, 6, 4, 8). Assuming an error occurs in  $r_3$ , then the received BRRNS code word becomes (1, 0, 1, 4, 8). The first consistent checking involves  $r_1$ ,  $r_2$ ,  $r_3$  and  $r_4$ ,  $\alpha_4=5\neq 0$ . The second consistent checking involves  $r_1$ ,  $r_2$ ,  $r_3$  and  $r_5$ ,  $\alpha_5=7\neq 0$ . Hence, the corrupt digits are in the information residue vector. The integer is restored by  $r_4$  and  $r_5$ , the redundant residue set.

### 1.3.5 Algorithmic Noise Tolerance

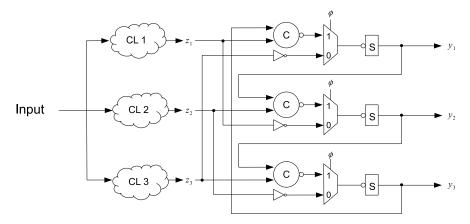

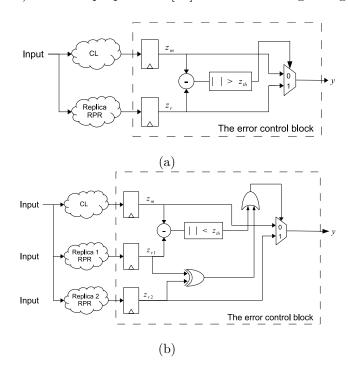

In the context of signal processing applications, the ANT technique proposes to add only one additional module to the original computation module. The additional replica provides a reduced precision estimation for the output of F and consumes less than the original one. By applying some criteria to make the decision, the final output is chosen between the output of the original module and the output of the replica. An ANT based system, the Reduced Precision Redundancy (RPR) is introduced in [5] and illustrated in Fig. 1.12a. It is composed of an error control block that calculates the Euclidean distance,  $d_e$ , between the original module output,  $z_m$ , and the RPR replica output,  $z_r$ , then decides which signals to feed. The final output can be described by

$$y = \begin{cases} z_m, & \text{if } d_e \le z_{th} \\ z_r, & \text{if } otherwise \end{cases}$$

(1.12)

where the  $z_{th}$  is a specified threshold. Since the reduced precision replica consumes much less power than the original function, the ANT technique achieves reliable low-power digital signal processing. However, the occurrence of errors in the estimator leads the output to be faulty. To tackle this drawback, another ANT based approach, called Algorithmic Soft Error Tolerance (ASET) has been proposed in [34]. Instead of using a single RPR estimator,

Figure 1.12: Two ANT based schemes: (a) RPR technique, (b) ASET technique.

ASET employs two RPR estimators to produce more reliable redundancy which help to make a more reliable decision after (see fig. 1.12b). Two differences are calculated:  $d_e(z_m, z_{r1})$  and  $d_h(z_{r1}, z_{r2})$ .  $d_e(z_m, z_{r1})$  is the Euclidean metric between  $z_m$  and  $z_{r1}$ , and  $d_h(z_{r1}, z_{r2})$  is the

Hamming distance between  $z_{r1}$  and  $z_{r2}$ . The error correction block is summarised as follow:

$$y = \begin{cases} z_m, & \text{if } d_e(z_m, z_{r1}) \le z_{th} \\ z_m, & \text{if } d_e(z_m, z_{r1}) > z_{th} \text{ and } d_h(z_{r1}, z_{r2}) \ge 1 \\ z_{r2}, & \text{if } d_e(z_m, z_{r1}) > z_{th} \text{ and } d_h(z_{r1}, z_{r2}) = 0 \end{cases}$$

$$(1.13)$$

Two drawbacks limit the based ANT method to be widely used. First, the reduced precision block should be constructed to provide the ability to detect and correct errors which it is feasible for signal processing application but not control application for example. Then, the ANT method requires that the decision block is reliable to perform a correct error-control.

### 1.3.6 Razor systems

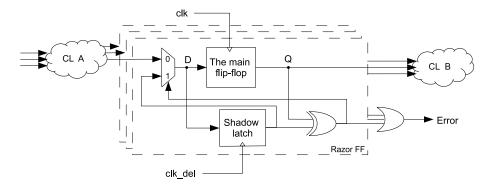

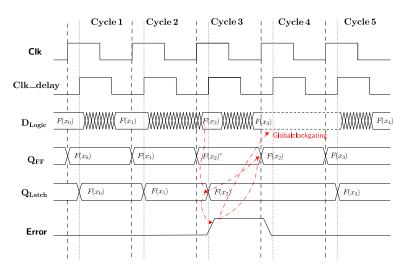

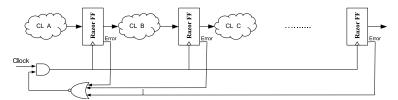

The main concept of Razor systems is to take advantage of the temporal nature of timing and transient faults and achieve faults detection by observing the output of a given circuit at two instants. Three versions of Razor system exist: Razor I, Razor II and bubble Razor. The architecture of Razor I system is illustrate in Fig.1.13; each flip-flop in a design is augmented with a shadow latch controlled with a delayed clock. An error is flagged when both outputs disagree. A timing diagram of the Razor concept is given in Fig.1.14. By the rising edge of the clock in cycle 1, both the main flip-flop and the shadow latch will latch the correct data. The error signal at the output of the comparator remains low. Let suppose that a timing fault occur and the operation in cycle 2 exceeds the intended delay. Data is not latched correctly by the main flip-flop, in cycle 3, it is the shadow latch that will successfully latch the correct data. An error signal is flagged so and the recovery phase starts.

Figure 1.13: Razor I system architecture to protect logics against timing faults [35].

One of the proposed mechanisms for the recovering phase is the global clock gating whose architecture is shown in fig.1.15. It involves a stalling of the entire circuit for one clock cycle and reloading of main Razors with correct values stored in shadow latches. Any previously erroneous data value in main flip-flops is replaced with the correct value from the shadow latches. Thus any number of timing faults can be tolerated in a single cycle. Since this technique is based on communicating the erroneous state to the entire circuit in one cycle, it cannot be used for circuits with aggressive clock periods and for large performance designs.

Figure 1.14: Example timing diagram of the Razor I system: A timing error occur in cycle 2 when the computation of  $F(x_2)$  exceeds the intended delay, An error is flagged in cycle when the FF and latch outputs disagree.

Another approach was proposed to deal with this drawback, named the counter-flow pipelining. More details are given in [8].

Figure 1.15: Recovery using the global clock gating.

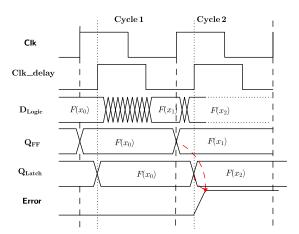

Energy savings and tolerance against transient faults were considered when designing the Razor II. This new version performs a timing and transient fault detection by a so called "transition detector", and achieve recovery by a replay mechanism from a Razor validated check pointed state [36]. Using the negative edge of the clock to samples data in the shadow latch reduces also overhead of using a second delayed clock [8]. However, short path can be flagged as an error in this version of Razor. In fact, when data arrives after the positive edge, it must guarantee to be from a long path launched from the previous clock edge. Fig .1.16 presents the case where a short path is flagged as an error. To deal with this drawback, the authors of [37] have proposed a new version of Razors referred as Bubble Razors.

The bubble Razors use a two phase latch based data path instead of a flip-flop based data path by breaking the flip-flops into their master and slaves latches. Since two neighbouring latches are not opening at the same cycle, there is no possibility that two successive input data are latched at the same time. This enables large speculation window up to one half a clock cycle [37]. Once errors are detected, bubble signals are propagated to neighbouring latches, causing a latch to skip its next clock phase. To prevent bubbles from propagating indefinitely in loops, a latch that receives a bubble from one or more of its neighbours, stalls

Figure 1.16: A timing diagram where a short path is flagged as an error in cycle 3.

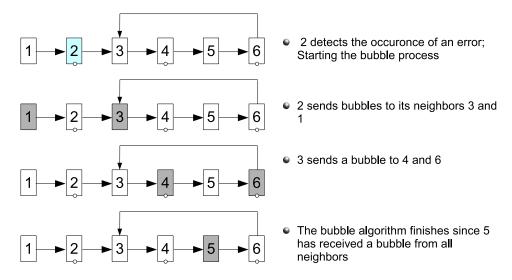

and sends a bubble to the other neighbours (input and output) one half cycle later; A latch that receives a bubble from all of its neighbours doesn't send out any bubbles. This algorithm remains the same in the presence of multiples errors during the same cycle and for high error rates. Bubble Razor reduces the throughput penalty to 1 cycle. Fig.1.17 describes the bubble Razor algorithm when the occurrence of an error was detected in second latch.

Figure 1.17: Description of the bubble Razor algorithm.

### 1.4 Hardware efficiency versus error probability

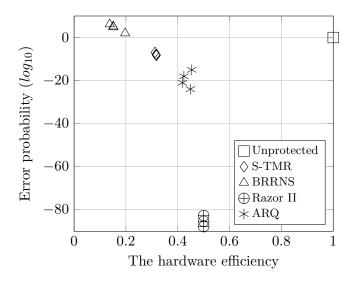

All state of the art techniques have in common that they requires extra hardware or/and throughput penalties (extra clock cycles needed for the recovery process). To compare architectures in unreliable hardware, the authors of [32, 38] define a novel metric called the Reliability Efficiency Criteria (RE-Criteria). The RE-Criteria consists on a couple ( $P_{Error}$ ,

$\gamma$ ) where  $P_{Error}$  is the error probability in the output of the architecture and  $\gamma$  represents the hardware efficiency of an architecture (defined as the normalised number of operation per unit area and time unit). To compute the hardware efficiency, the nature of the computation inside the area unit is not specified, it can be a simple multiplier or more complex operation like an Fast Fourier transform (FFT)... If we consider an operation  $\Psi$  that takes  $n_{\Psi}$  area units and  $m_{\Psi}$  area clocks to be executed, the efficiency is expressed as

$$\gamma_{\Psi} \triangleq \frac{1}{n_{\Psi} \times m_{\Psi}} \text{ operations/(area unit × time unit)}.$$

(1.14)

The RE-Criteria has already been used in [32, 38] to compare the performances of BRRNS, S-TMR and Automatic Repeat reQuest (ARQ)<sup>3</sup> architectures against faults. In this section, we first review the RE-Criteria of S-TMR and T-TMR (for the rest of architectures, the reader is invited to [32] for more details). Then we will investigate the RE-Criteria of the Razor II Architecture to be added to the comparison.

### 1.4.1 The Reliability Efficiency Criteria of the S-TMR

Let  $P_{\Psi}$  the error probability at the output of the function  $\Psi$  during one clock cycle,  $P_v$  the error probability of a voter, and  $n_v$  the area cost of the voter ( $m_v$  is the number of clock cycle to perform the voter is assummed to be equal to 0). We remind that one of the hypotheses made in [32] is that two successive errors cannot lead to a correct result. It is a simplification hypothesis that gives an upper band of the output error probability. The output of the S-TMR is wrong when at most one replica is faulty and the voter is faulty or at least two of the replicas are faulty. Let  $P_1$  the probability that at least two of the three replicas is correct. The resulting error probability of the S-TMR is expressed as

$$P_{S-TMR} = (1 - P_1) + P_1 P_v. (1.15)$$

$P_1$  is expressed as,

$$P_1 = (1 - P_{\Psi})^3 + 3 P_{\Psi} (1 - P_{\Psi})^2. \tag{1.16}$$

The efficiency of the S-TMR is determined by,

$$\gamma_{S-TMR} = \frac{1}{(3.n_{\Psi} + n_v).m_{\Psi}} \tag{1.17}$$

The normalised hardware efficiency is defined as,

$$\Gamma_{S-TMR} = \frac{\gamma_{TMR}}{\gamma_{\Psi}} = \frac{n_{\Psi}}{(3.n_{\Psi} + n_{v})} \tag{1.18}$$

<sup>&</sup>lt;sup>3</sup>The ARQ technique performs the error detection by adding hardware redundancy (modulo 4, modulo 8...). When an error occurs, the detector asks to restart the computation [39].

### 1.4.2 The Reliability Efficiency Criteria of the T-TMR

In the T-TMR, the computing function executes the same operation three clock cycles. The majority vote is performed between the outputs of the computing function at the three clock cycles. Registers are used to save outputs of the first and the second computations. Faults occur in these registers. Let  $P_f$  the probability that an error appear at the output of a register,  $R_1$ ,  $R_2$  and  $R_3$  the probability of a correct input of the voter.  $R_1 = (1 - P_R) \cdot (1 - P_f)^2$ ,  $R_2 = (1 - P_R) \cdot (1 - P_f)$  and  $R_3 = (1 - P_R) \cdot (1 - P_R)$  in this case is expressed as

$$P_1 = 1 - (R_1 \ R_2 \ R_3 + R_1 \ R_2 \ (1 - R_3) + R_2 \ R_3 \ (1 - R_1) + R_3 \ R_1 \ (1 - R_2)). \tag{1.19}$$

The resulting error probability of the T-TMR is,

$$P_{T-TMR} = (1 - P_1)(1 - P_v) + P_1 P_v. (1.20)$$

The efficiency of the T-TMR is determined by,

$$\gamma_{S-TMR} = \frac{1}{(3.n_{\Psi} + n_v + 2.n_R).m_{\Psi}} \tag{1.21}$$

where  $n_R$  is the area cost of a register. Since the register area cost is low compared to the area of the function  $\Psi$  ( $n_R \ll n_{\Psi}$ ), its error probability is much smaller than  $P_R$ . Hence, PT - TMR is approximate to  $P_{S-TMR}$  as well as its hardware efficiency [32].

### 1.4.3 The Reliability Efficiency Criteria of the Razor II

The Razor II technique performs complete transient and timing error detection by the double sampling approach (see Sec. 1.3.6). When an error occurs, the computation is restarted. The average number of time unit (or clock cycles) for the Razor II to output a correct data is given by,

$$M_{RazorII} = \sum_{k=0}^{\infty} (k+1) (m_{\Psi} + 1) P_{\Psi}^{k} (1 - P_{\Psi}) = \frac{m_{\Psi} + 1}{1 - P_{\Psi}}.$$

(1.22)

The efficiency of the Razor is determined by,

$$\gamma_{Razor} = \frac{1 - P_{\Psi}}{n_{\Psi} \cdot (m_{\Psi} + 1)} \tag{1.23}$$

The error probability of the Razor II is expressed as,

$$P_{Razor} = \sum_{i=2}^{\infty} P_{\Psi}^{i} \dots = \frac{P_{\Psi}^{2}}{1 - P_{\Psi}}$$

(1.24)

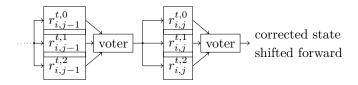

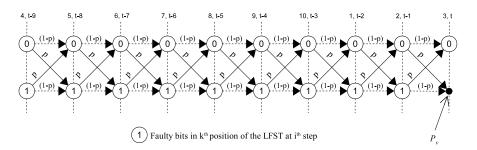

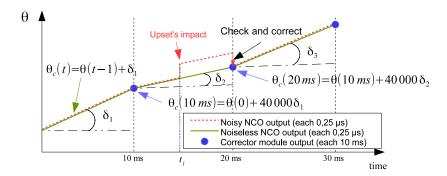

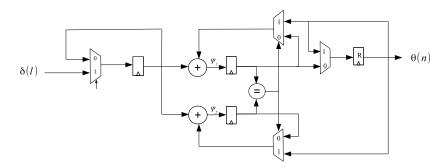

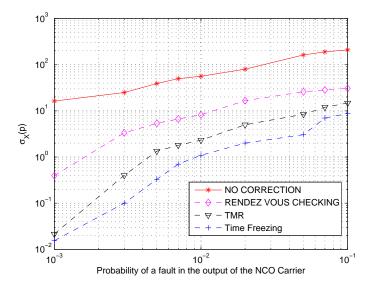

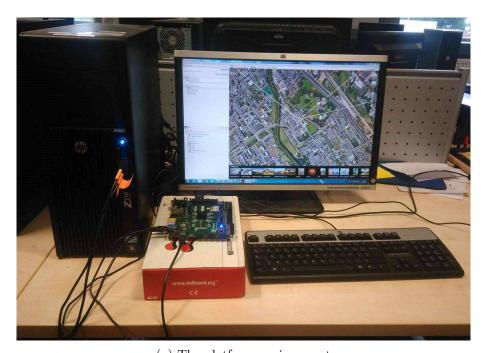

### 1.4.4 Comparison results