# Circuit and system fault tolerance techniques Imran Wali

### ▶ To cite this version:

Imran Wali. Circuit and system fault tolerance techniques. Electronics. Université Montpellier, 2016. English. NNT: 2016MONTT313 . tel-01807927

# HAL Id: tel-01807927 https://theses.hal.science/tel-01807927

Submitted on 5 Jun2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Délivré par l'Université de Montpellier

Préparée au sein de l'école doctorale **I2S** Et de l'unité de recherche **LIRMM**

Spécialité: SYAM

Présentée par Imran WALI

# Circuit and System Fault Tolerance Techniques

Soutenue le 30 Mars 2016, devant le jury composé de:

M. Fabrice MONTEIRO, Professeur, Université de Lorraine

Mme. Lirida NAVINER, Professeur, Telecom ParisTech

M. Matteo SONZA REORDA, Professeur, Politecnico di Torino

M. Alberto BOSIO, MCF HDR, Université de Montpellier

M. Arnaud VIRAZEL, MCF HDR, Université de Montpellier

M. Patrick GIRARD, DR CNRS, LIRMM

Rapporteur Rapporteur Examinateur Examinateur Directeur de thèse CoDirecteur de thèse

## Acknowledgements

First and foremost, I would like to thank my Lord, the Almighty, for being close and responsive throughout the course of my thesis. Only due to His countless gifts of sense, intellect, patience, health, family and many more, I could complete this task.

I would like to express my deepest gratitude to my thesis director, Prof. Arnaud Virazel. With his encouraging and supporting attitude, meeting him has always been a work-stress reliever for me. His profound guidance and invaluable advises helped keeping my research well directed and my progress on schedule while maintaining my autonomy.

My sincere thanks also goes to my co-director, Prof Patrick Girard, for his immense knowledge, motivation and support throughout the research. Also for his thought-provoking ideas and helpful criticism in improving the quality of this manuscript and other publications. I also appreciate Prof. Alberto Bosio's insightful comments and advises which helped me solve various problems during my research.

My grateful thanks are also extended to Prof. Matteo Sonza Reorda for his generous support and effort to actively maintain the collaborative partnership, LAFISI, and his valuable and constructive suggestions that helped me enrich my ideas.

I am also thankful to him for carefully reviewing my work at different stages of my thesis. I would like to thank the rest of my thesis committee members, Prof. Lirida Naviner and Prof. Fabrice Monteiro for reviewing this manuscript and providing positive feedback.

I would also like to acknowledge all my master students who provided me an opportunity to enrich my understanding through sharing my knowledge about the subject and also for their valuable contribution to my work. I wish to acknowledge the support received form my friends at LIRMM for the various discussions and brain storming sessions. Also for making the last three years memorable.

Finally, none of this would have been possible without the love and patience of my family. Their constant support and strength has aided and encouraged me throughout this endeavor.

### Abstract

Semiconductor is one of the most reliable inventions when engineered and used with longevity in mind. However, the increasing demand of fast and highly featured products has drastically changed the reliability realm in the recent years. The means of improving the reliability of nano-metric technology circuits encompass techniques that tackle reliability issues at the level of technology, design and manufacturing. Absolutely necessary but these techniques are almost inevitably imperfect. Therefore, it becomes essential to reduce the consequence of the "remaining" faults using fault tolerance techniques.

This thesis focuses on improving and developing new low-power fault tolerance techniques that combine the attractive features of different types of redundancies to tackle permanent and transient faults and addresses the problem of error detection and confinement in modern microprocessor cores. Our case study implementation results show that a power saving of up to 20% can be achieved in comparison with fault tolerance techniques that use only one type of redundancy, and offer lifetime reliability improvement.

With the objective to further improve the efficiency in terms of cost and fault tolerance capability we present a design space exploration and an efficient cost-reliability trade-off analysis methodology to selectively harden logic circuits using hybrid fault tolerant techniques. The outcome of the two studies establish that hybrid fault tolerant approaches provide a good foundation for building low-power reliable circuits and systems from future technologies, and our experimental results set a good starting point for further innovative research in this area.

# List of Acronyms

| <b>TMR</b> Triple Modular Redundancy xii                |

|---------------------------------------------------------|

| <b>DMR</b> Dual Modular Redundancy 31                   |

| <b>DVS</b> Dynamic Voltage Scaling                      |

| <b>DFS</b> Dynamic Frequency Scaling                    |

| HyFT Hybrid Fault Tolerant xiii                         |

| PHyFT Pipelined Hybrid Fault Tolerant                   |

| HyTFT Hybrid Transient Fault Tolerant xii               |

| HyTPFT Hybrid Transient and Permanent Fault Tolerantxii |

| BL Baseline xii                                         |

| PaS Pair-and-A-Sparexv                                  |

| <b>FD</b> Fault-Detection                               |

| CL Combinational Logic                                  |

| <b>FF</b> Flip-Flops                                    |

| SET Single Event Transient                                                                          |

|-----------------------------------------------------------------------------------------------------|

| SEU Single Event Upset1                                                                             |

| ID Instruction Decode                                                                               |

| IF Instruction Fetch                                                                                |

| EXE Execution                                                                                       |

| <b>MEM</b> Memory                                                                                   |

| <b>WB</b> Write-back                                                                                |

| STA Static Timing Analysis                                                                          |

| <b>RTL</b> Register Transfer Level                                                                  |

| HyFT-1a Original HyFT xiii                                                                          |

| <b>HyFT-1b</b> Hybrid Fault Tolerant (HyFT) Architecture with short <i>DC</i> xiii                  |

| <b>HyFT-2a</b> Hybrid Fault Tolerant (HyFT) Architecture with <i>CLK</i> enclosed <i>DC</i> xiii    |

| <b>HyFT-2b</b> Hybrid Fault Tolerant (HyFT) Architecture with <i>DC</i> across <i>CLK</i> edge xiii |

| ATPG Automatic Test Pattern Generator                                                               |

| CMOS Complementary Metal-Oxide-Semiconductor                                                        |

| SER Soft Error Rate                                                                                 |

| SDF Standard Delay Format                                                                           |

| VCD Value Change Dump                                                                               |

| <b>DOR</b> Dynamic OR xv                     |

|----------------------------------------------|

| <b>FSM</b> Finite State Machine xvii         |

| PaS Pair-and-A-Sparexv                       |

| SoC System on Chip                           |

| MTF Multiple Transient Fault                 |

| MET Multiple Event Transient                 |

| SPRA Signal Probability Reliability Analysis |

| MEPP Multiple Event Probability Propagation  |

| <b>BDD</b> Binary Decision Diagram           |

| VF Vulnerability Factor                      |

| SEE Single Event Effect                      |

| <b>FPGA</b> Field-Programmable Gate Array120 |

| <b>PVT</b> Process, Voltage and Temperature  |

# **Table of contents**

| Li | st of f | igures   |                                             | XV  |

|----|---------|----------|---------------------------------------------|-----|

| Li | st of t | ables    |                                             | xix |

| In | trodu   | ction    |                                             | 1   |

| 1  | Con     | text and | 1 Motivation                                | 5   |

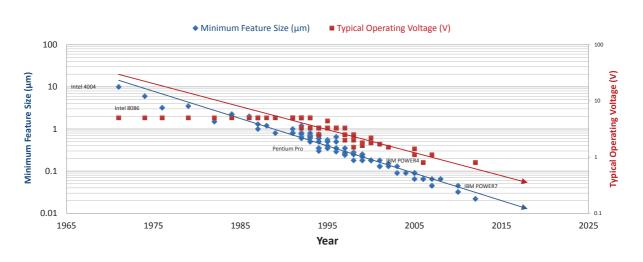

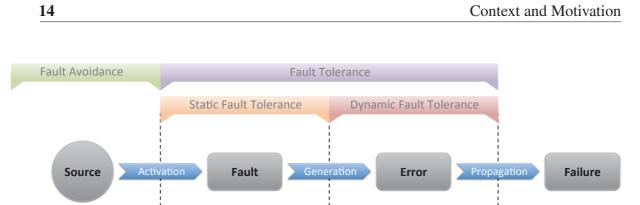

|    | 1.1     | Semico   | onductor Technology Evolution               | 5   |

|    | 1.2     | Reliab   | ility threats in nano-metric technologies   | 7   |

|    |         | 1.2.1    | Variability                                 | 7   |

|    |         | 1.2.2    | Manufacturing Defects                       | 8   |

|    |         | 1.2.3    | Wear-out                                    | 8   |

|    |         | 1.2.4    | Interference                                | 8   |

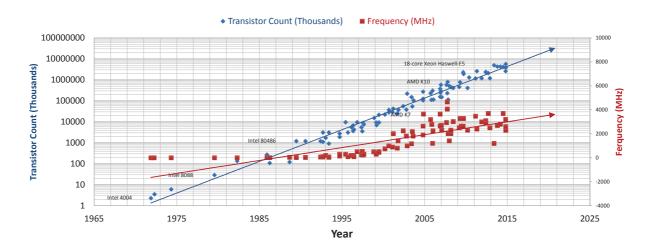

|    | 1.3     | Errors   | in Integrated Circuits                      | 9   |

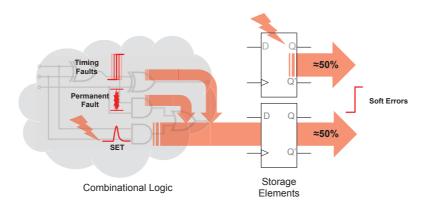

|    |         | 1.3.1    | Soft Errors                                 | 9   |

|    |         | 1.3.2    | Hard Errors                                 | 12  |

|    |         | 1.3.3    | Timing Errors                               | 13  |

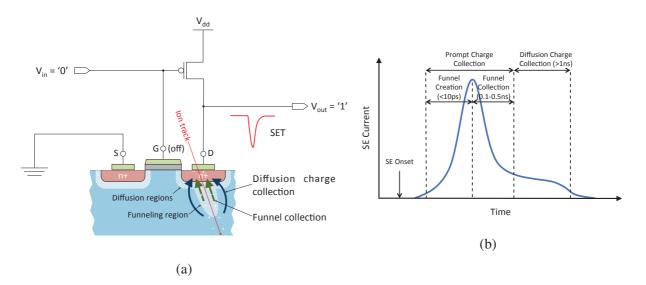

|    | 1.4     | Reliab   | ility Improvement Approaches                | 13  |

|    |         | 1.4.1    | Fault Avoidance                             | 13  |

|    |         | 1.4.2    | Fault Removal                               | 14  |

|    |         | 1.4.3    | Fault Tolerance                             | 14  |

|    |         | 1.4.4    | Fault Evasion                               | 15  |

|    | 1.5     | Resear   | ch Objectives                               | 16  |

| 2  | Faul    | t Tolera | ant Architectures and Assessment Techniques | 19  |

|    | 2.1     | Fault-7  | Folerance Techniques                        | 20  |

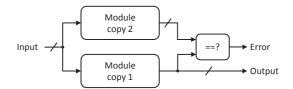

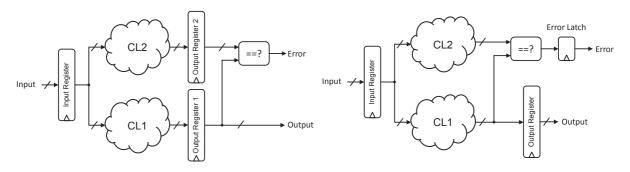

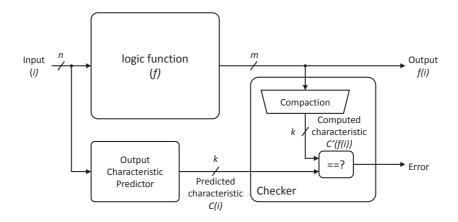

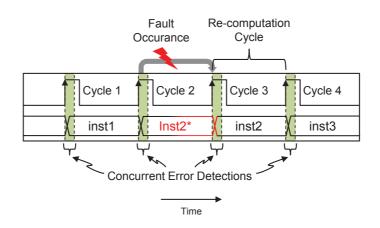

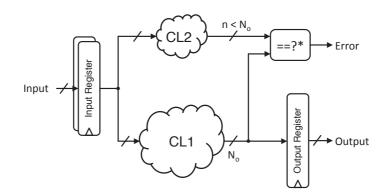

|    |         | 2.1.1    | Concurrent Error Detection                  | 20  |

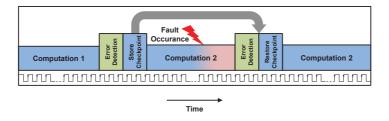

|    |         | 2.1.2    | Error Recovery                              | 26  |

|   | 2.2  | Fault to | olerant Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 |

|---|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |      | 2.2.1    | Pair-and-A-Spare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |

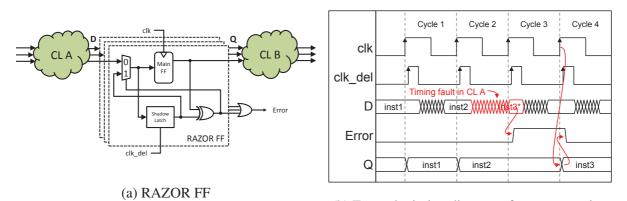

|   |      | 2.2.2    | Razor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 |

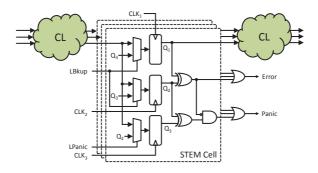

|   |      | 2.2.3    | STEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29 |

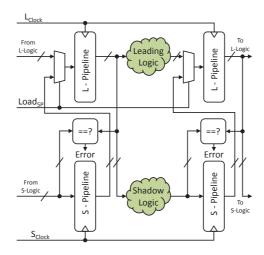

|   |      | 2.2.4    | CPipe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |

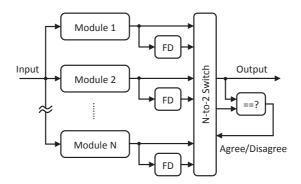

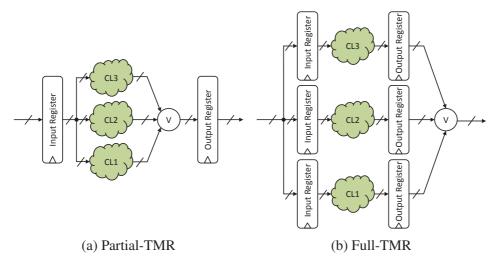

|   |      | 2.2.5    | TMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30 |

|   |      | 2.2.6    | DARA-TMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31 |

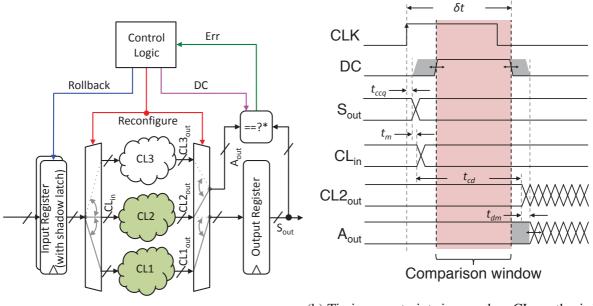

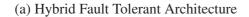

|   |      | 2.2.7    | Hybrid Fault-Tolerant Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32 |

|   | 2.3  | Robust   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

|   |      | 2.3.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35 |

|   |      | 2.3.2    | Empirical Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37 |

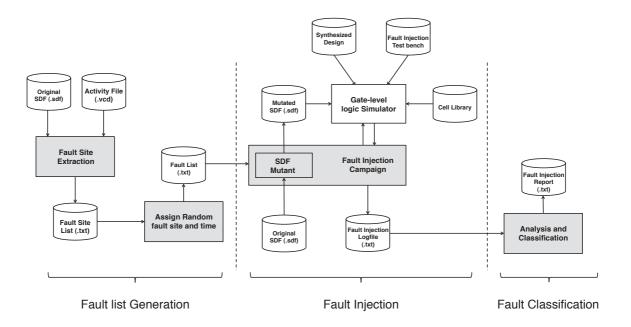

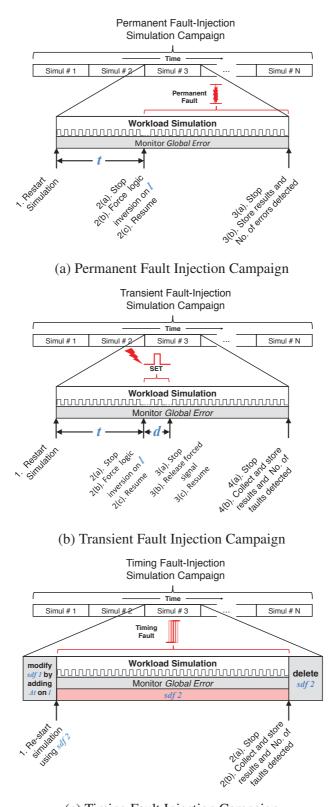

|   |      | 2.3.3    | A Gate-Level Fault Injection Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38 |

|   | 2.4  | Experi   | mental Comparative Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

|   |      | 2.4.1    | Experimental Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |

|   |      | 2.4.2    | I States and Stat | 43 |

|   | 2.5  | Summ     | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

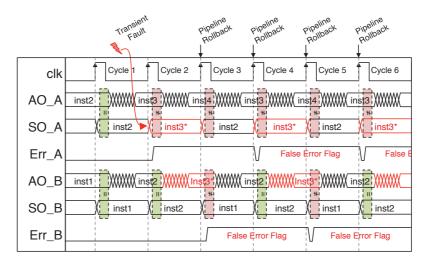

| 3 | Pipe | lined H  | ybrid Fault Tolerant Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |

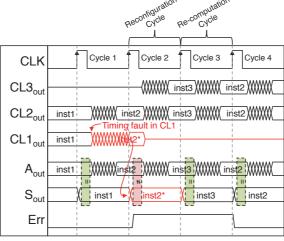

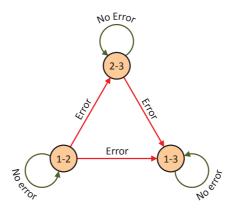

|   | 3.1  | Error H  | Propagation in Pipelined Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |

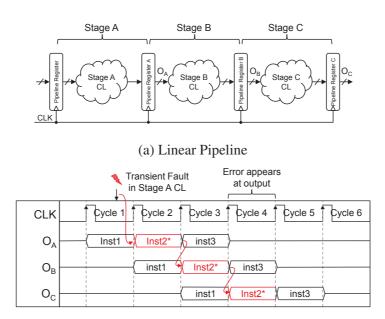

|   |      | 3.1.1    | Linear Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52 |

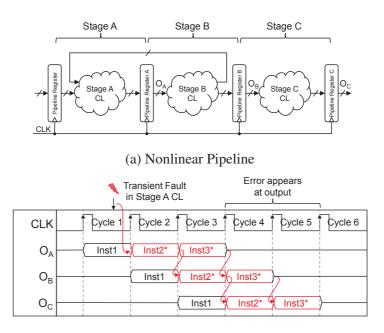

|   |      | 3.1.2    | Nonlinear Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53 |

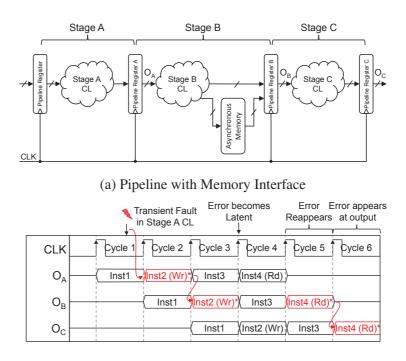

|   |      | 3.1.3    | Pipeline with Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

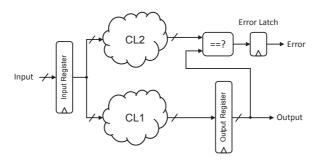

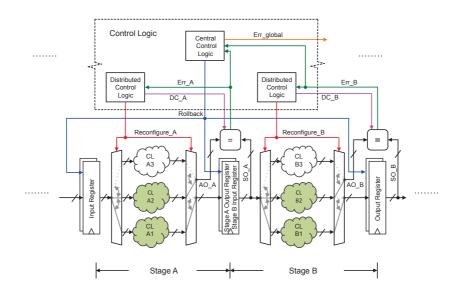

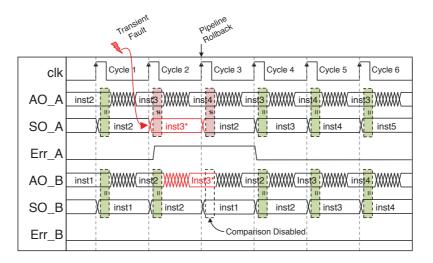

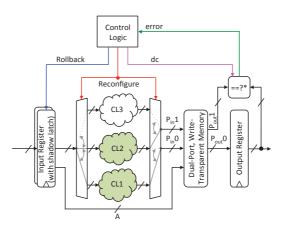

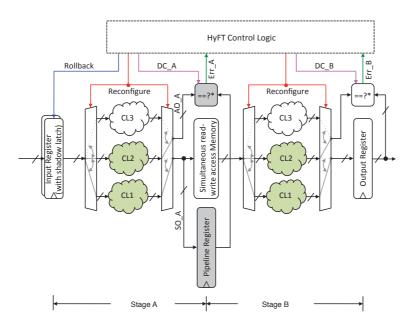

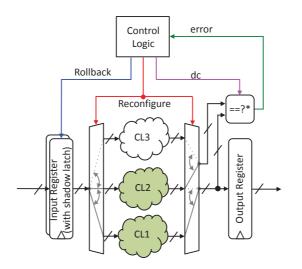

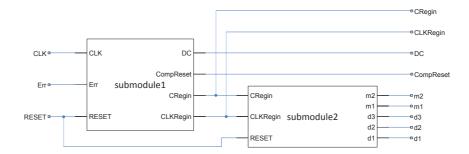

|   | 3.2  | Extens   | ion of HyFT Architecture to Pipelined Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54 |

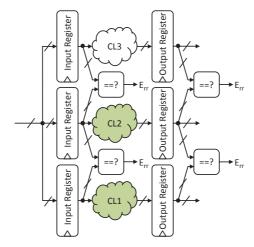

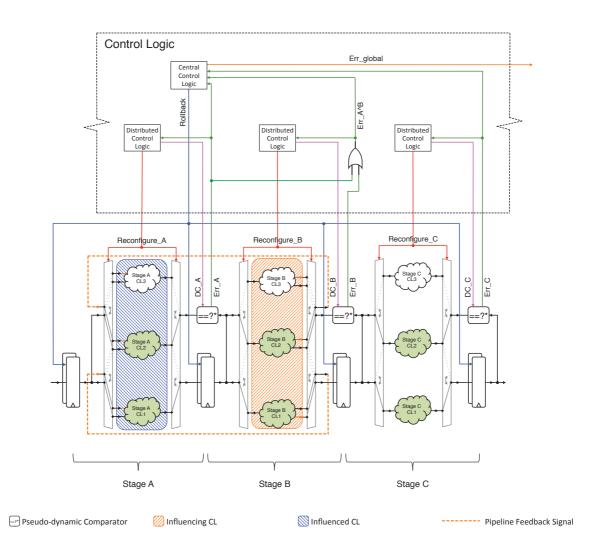

|   |      | 3.2.1    | Basic Pipeline Cascading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

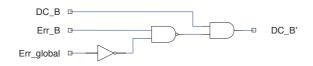

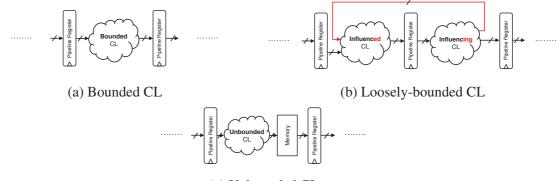

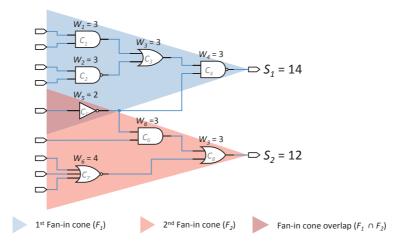

|   |      | 3.2.2    | Stage/Combinational Logic (CL) Classification and Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56 |

|   |      | 3.2.3    | Dealing with Error Propagation in Nonlinear Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59 |

|   |      | 3.2.4    | Error detection in Pipeline stages with memory interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59 |

|   | 3.3  | Case S   | tudy: Fault Tolerant Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63 |

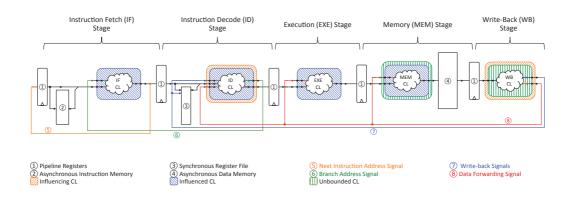

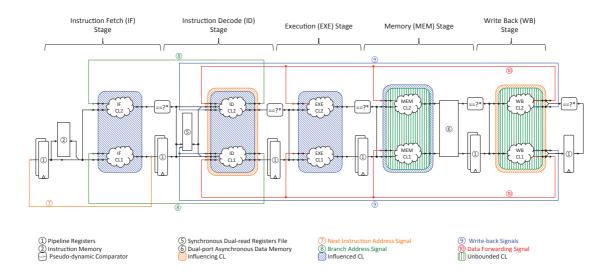

|   |      | 3.3.1    | Baseline (BL) Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

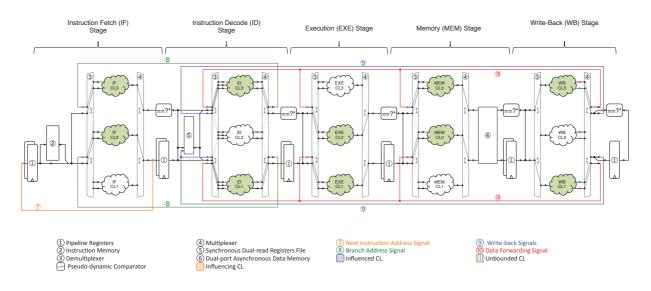

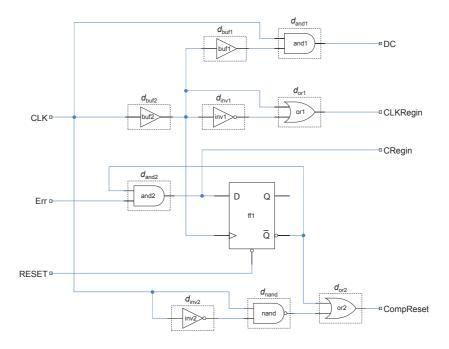

|   |      | 3.3.2    | Hybrid Transient Fault Tolerant (HyTFT) Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65 |

|   |      | 3.3.3    | Hybrid Transient and Permanent Fault Tolerant (HyTPFT) Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66 |

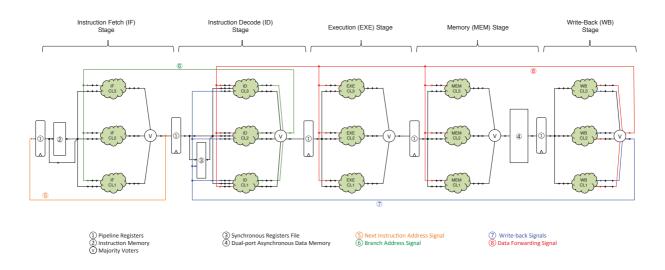

|   |      | 3.3.4    | Triple Modular Redundancy (TMR)-b Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

|   |      | 3.3.5    | TMR-w Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

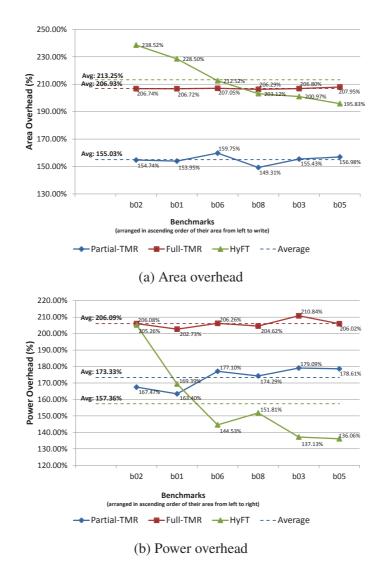

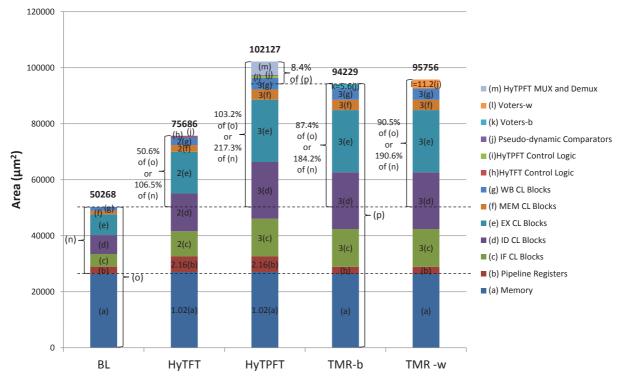

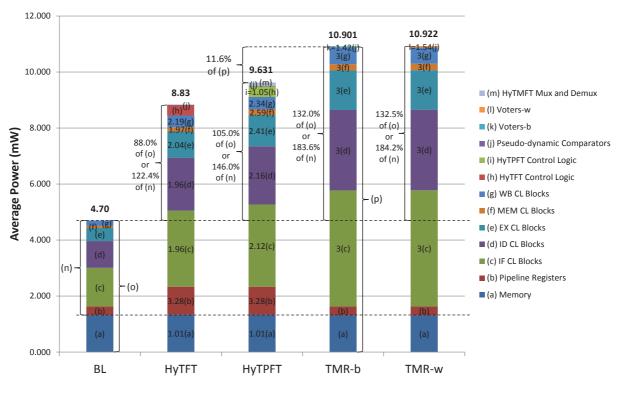

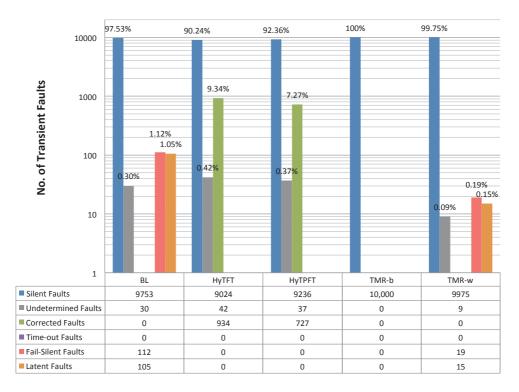

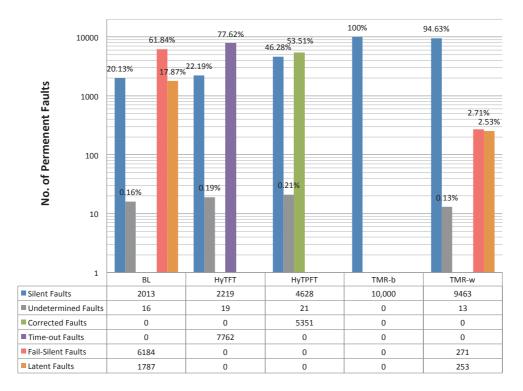

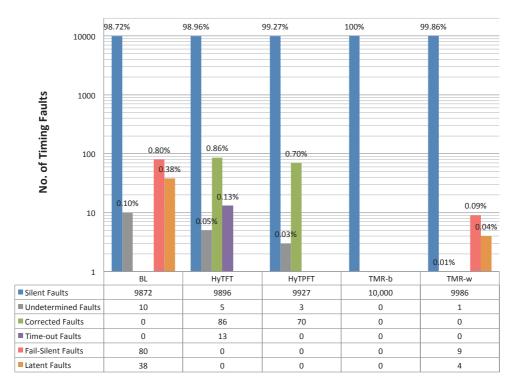

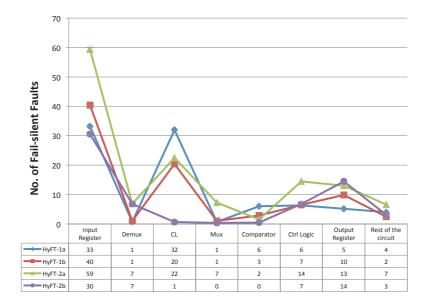

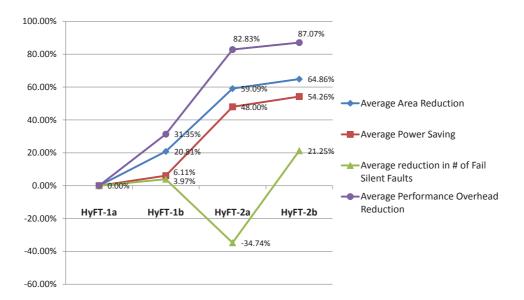

|   |      | 3.3.6    | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

|   |      | 3.3.7    | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78 |

|   |      | 5.5.7    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

| 4          | Desi   | ign Space Exploration and Optimization of HyFT Architecture                    | 81  |

|------------|--------|--------------------------------------------------------------------------------|-----|

|            | 4.1    | Limitations of Hybrid Fault Tolerant (HyFT) Architecture                       | 81  |

|            |        | 4.1.1 Contamination delay constraints                                          | 81  |

|            |        | 4.1.2 Asymmetric clock duty-cycle                                              | 82  |

|            | 4.2    | Design and Timing Optimization                                                 | 82  |

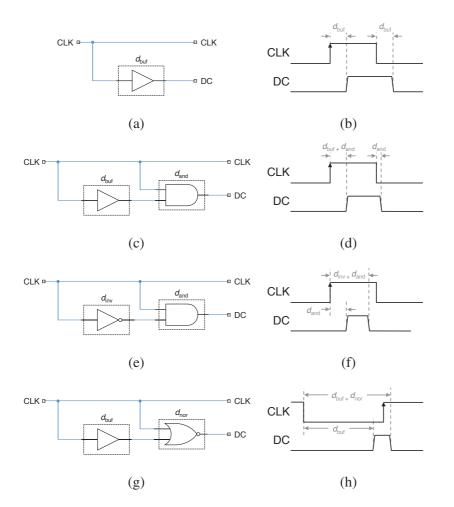

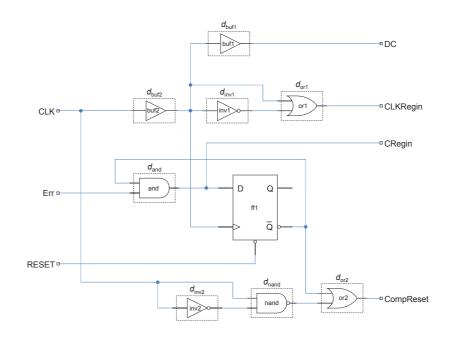

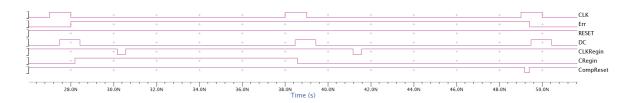

|            |        | 4.2.1 Original HyFT (HyFT-1a) Architecture                                     | 83  |

|            |        | 4.2.2 Hybrid Fault Tolerant (HyFT) Architecture with short <i>DC</i> (HyFT-1b) | 83  |

|            |        | 4.2.3 Hybrid Fault Tolerant (HyFT) Architecture with CLK enclosed DC           |     |

|            |        | (HyFT-2a)                                                                      | 83  |

|            |        | 4.2.4 Hybrid Fault Tolerant (HyFT) Architecture with DC across CLK edge        |     |

|            |        | (HyFT-2b)                                                                      | 85  |

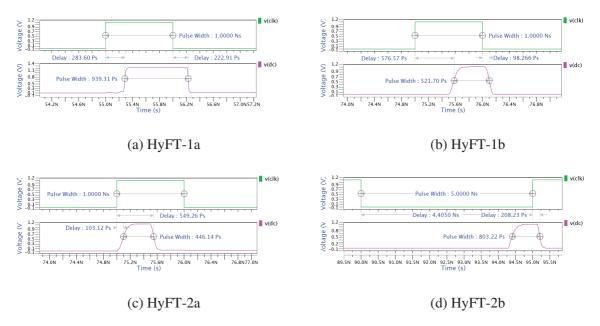

|            | 4.3    | Experimental Assessment of Improvements                                        | 86  |

|            |        | 4.3.1 Experimental Setup                                                       | 86  |

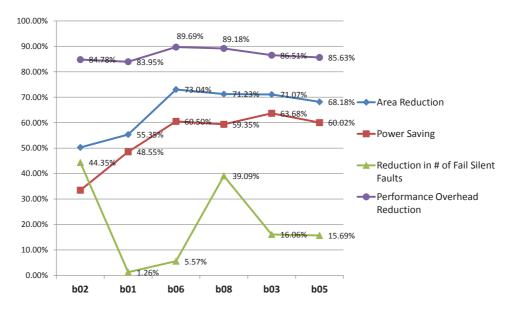

|            |        | 4.3.2 Experimental Results                                                     | 92  |

|            |        | 4.3.3 Discussion                                                               | 97  |

|            | 4.4    | Impact of circuit size on the evaluated metrics                                | 98  |

|            | 4.5    | Summary                                                                        | 99  |

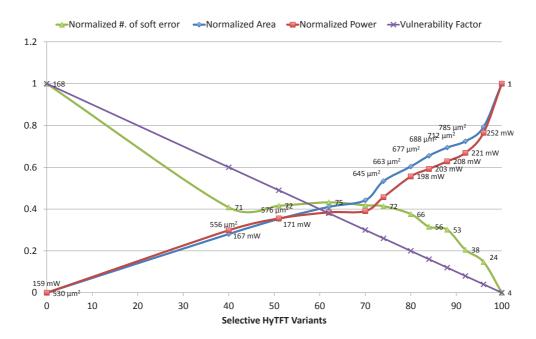

| 5          | Sele   | ctive Hybrid Fault Tolerance                                                   | 101 |

|            | 5.1    | Previous work                                                                  | 102 |

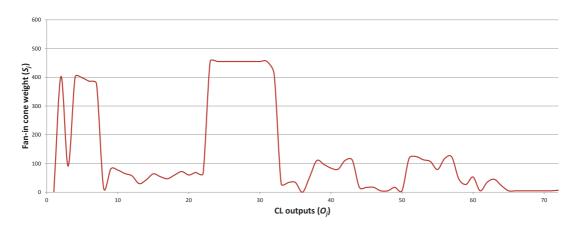

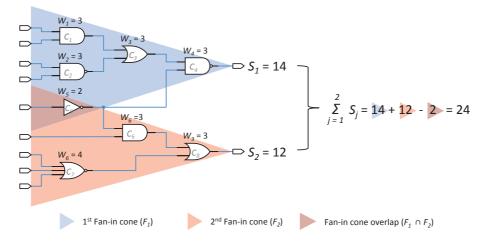

|            | 5.2    | A low-cost output susceptibility analysis                                      |     |

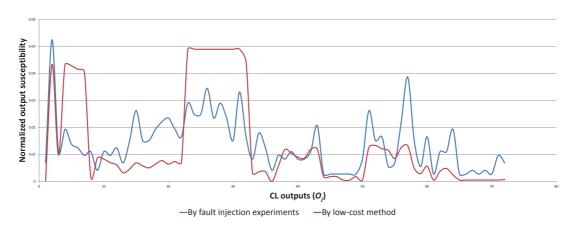

|            |        | 5.2.1 Results                                                                  |     |

|            | 5.3    | Validation of the approach                                                     |     |

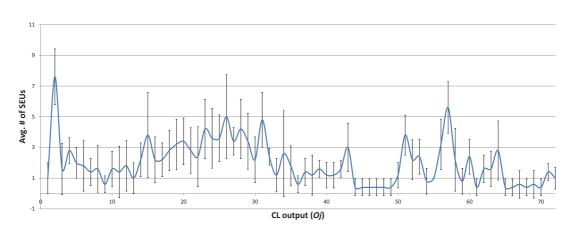

|            |        | 5.3.1 Fault injection based output susceptibility analysis                     | 107 |

|            |        | 5.3.2 Discussion                                                               | 108 |

|            | 5.4    | Selective HyTFT Architecture                                                   | 108 |

|            |        | 5.4.1 A low-cost HyTFT architectural reliability estimation                    | 110 |

|            | 5.5    | Experimental Validation and Results                                            | 112 |

|            |        | 5.5.1 Experimental Setup                                                       | 112 |

|            |        | 5.5.2 Experimental Results                                                     |     |

|            |        | 5.5.3 Discussion                                                               | 116 |

|            | 5.6    | Summary                                                                        |     |

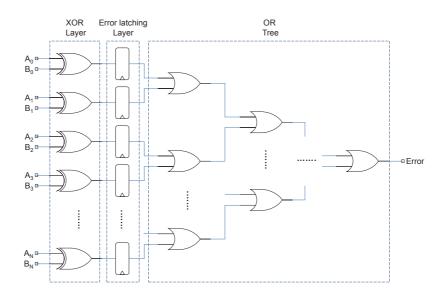

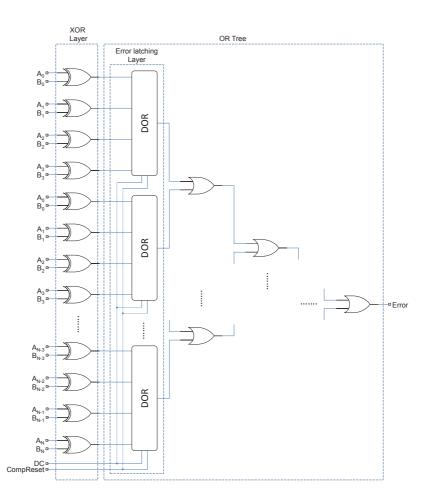

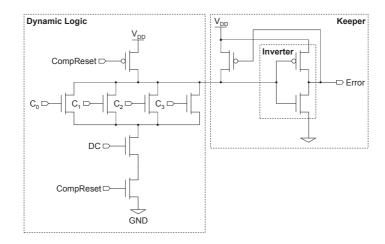

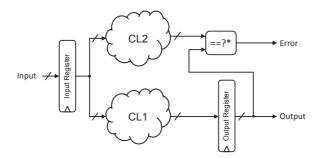

| C          | onclus | sion 1                                                                         | 119 |