# High efficiency S-Band vector power modulator design using GaN technology

Abhijeet Dasgupta

#### ▶ To cite this version:

Abhijeet Dasgupta. High efficiency S-Band vector power modulator design using GaN technology. Electronics. Université de Limoges, 2018. English. NNT: 2018LIMO0021. tel-01810140v2

### HAL Id: tel-01810140 https://theses.hal.science/tel-01810140v2

Submitted on 7 Jun 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THESE DE DOCTORAT

Université de Limoges - Faculté des Sciences et Techniques Ecole Doctorale nº 610 : Sciences et Ingénierie pour l'Information XLIM - CCSNL, UMR CNRS 7252

### Thése

Pour obtenir le grade de

### Docteur de l'Université de Limoges

Spécialité : "Électronique des Hautes Fréquences, Photonique et Systémes"

Présentée et soutenue publiquement par

### Abhijeet Dasgupta

le 27. Avril. 2018.

### High Efficiency S-Band Vector Power Modulator Design using GaN Technology

Directeurs de thèse : M. Jean-Michel NEBUS et M. Philippe BOUYSSE

### Jury:

| M. Raymond QUERE,        | Professeur Emérite, XLIM, Université de Limoges        | Président   |

|--------------------------|--------------------------------------------------------|-------------|

| Mme. Nathalie DELTIMPLE, | MCF-HDR, Université de Bordeaux                        | Rapporteur  |

| M. Alain PEDEN,          | Professeur, IMT Atlantique Bretagne                    | Rapporteur  |

| M. Philippe BOUYSSE,     | MCF, XLIM, Université de Limoges                       | Examinateur |

| M. Olivier JARDEL,       | Ingénieur, Thales Alenia Space, Toulouse               | Examinateur |

| M. Jean-Michel NEBUS,    | Professeur, XLIM, Université de Limoges                | Examinateur |

| M. Emmanuel GATARD,      | Ingénieur, Société WUPATEC, Limoges                    | Invités     |

| M. François TORRES,      | Chargé de Recherches CNRS, XLIM, Université de Limoges | Invités     |

## Droits d'auteurs / Copyright

Cette cration est mise disposition selon le Contrat : "Paternit - Pas d'Utilisation Commerciale - Pas de modification 3.0 France" disponible en ligne l'adresse suivante : http://creativecommons.org/licenses/by-nc-nd/3.0/fr/.

This work is licensed under the Creative Commons Attribution - Pas dUtilisation Commerciale - Pas de Modification 3.0 France License. To view a copy of this license, visit <a href="http://creativecommons.org/licenses/by-nc-nd/3.0/fr/">http://creativecommons.org/licenses/by-nc-nd/3.0/fr/</a> or send a letter to Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

| "You cannot teach a man anything; you can only he | elp him discover it in himself"  Galileo Galilei               |

|---------------------------------------------------|----------------------------------------------------------------|

|                                                   |                                                                |

|                                                   |                                                                |

|                                                   | To the young minds of India, To my Grandmother, To my Parents, |

### Acknowledgements

No one who achieves success does so without acknowledging the help of others.

The wise and confident acknowledge this help with gratitude.

Alfred North Whitehead

First of all, I would like to express my sincere gratitude to **M. Dominique Bail-largeat** (Director XLIM) and **M. Bernard Jarry** (responsible CCSNL) for allowing me to carry out my research work with axe CCSNL in XLIM laboratory, University of Limoges in France.

This research work has been accomplished with the constant support and motivation of several individuals, without whom, it would not have been possible. I would like to acknowledge all those people who have helped me in my journey of three years in XLIM laboratory, France. I would sincerely like to thank director and co-director of my thesis M. Jean-Michel Nébus and M. Philippe Bouysse for providing me with an opportunity to learn and grow under their supervision. Their constant guidance and passion towards high quality research has always been and will be a source of inspiration for me. My deepest gratitude to Mme. Nathalie Deltimple, MCF-HDR, Université de Bordeaux and M. Alain Peden, Professor, IMT Atlantique Bretagne for taking their time to be the reporters of my thesis and evaluating this work along with the president reporter 3 of the jury. I would like to thank M. Olivier Jardel, Engineer, Thales Alenia Space, M. Emmanuel Gatard, WUPATEC, Limoges, M. Raymond Quéré, Professor Emeritus, XLIM and M. François Torres, CNRS for being a part of the jury. Special acknowledgement to François for helping in the soldering procedure of the transistors.

I would also like to thank M. Julien Lintignat, Mme. Audrey Martin and M. Sébastian Mons for sharing their time with me outside the laboratory while travelling to New Delhi, Honolulu, Saint-Malo, Bordeaux and within Limoges. Many thanks to M.

**Tibault Reveyrand**, CNRS for not only sharing his knowledge on RF but also key life experiences in the United States and France and philosophy over coffee.

I would always be indebted to M. Raymond Quéré and M. Jean-Christophe Nallatamby for enabling me to make a smooth transition initially in my thesis work from the United Kingdom to France. I am extremely grateful to the departmental secretary, Mme. Marie-Claude Lerouge for always assisting me with the administrative work and for being a helping hand during tough times. Special thanks to M. Pierre Medrel (XLIM), M. Arnaud Delias and M. Lotfi Ayari (AMCAD Engineering, Limoges), M. Poornakarthik Nakkala (FOCUS Microwaves, Québec, Canada) for always sharing their knowledge and time.

Life in France would not have been easy without my friends who have always been there for me. I am fortunate to be in company of such friends and express my sincere thanks to M. Sylvain Lanzeray, M. Anthony Disserand, Mlle. Wafa Khelifi and M. Alexis Courty for sharing the office and for always maintaining a vibrant and a happy environment. I would like to thank my partner in crime, both in the UK and in France, M. Nandha Kumar Subramani (Global Foundries, Dresden, Germany), M. Jayanth Channagiri (Grenoble), M. Sudarshan Shinde (Paris), M. Sudip Kumar Saha (Kolkata), Mme. Shrabani Panigrahi (Lisbon), M. Santanu Jana (Lyon), M. Abhijit Bera (TU-Wien, Vienna), M. Muhammad Adnan, Mlle. Frédérique Simbelie, Mle. Emeline Broussard, M. Julien Couvidat and M. Clément Hallepee for their constant support and being part of good times. I have to thank few important persons in my life, M. Amlan Chakraborty (Monash University, Melbourne), Mlle. Taniya Mitra (University of Veterinary Medicine in Vienna), M. Arnab Jana (Lille), M. Erwan Capitaine, M. Matthew Jossent, M. Johann Sence, M. David Moreau, M. Patrick Cadroas and others.

Special gratitude to Mlle. Antara Ghosh Mazumder for sharing her time and life experiences, from Pune in India. I convey my best wishes to the current masters and PhD students, and my friends Morgane, friend Paul, Seif, Ayoube, Ouessama, Marwen and others. Last but not the least, I would like to dedicate this thesis work and express gratitude to my parents and my sister Mlle. Anushree Dasgupta for their unconditional love and support throughout my good and bad times and always backing my decisions in life.

## Contents

| List of figures                                                                         | X               |

|-----------------------------------------------------------------------------------------|-----------------|

| List of tables                                                                          | vii             |

| General Introduction                                                                    | 1               |

| Chapter I Challenges and Design Considerations in GaN based RF                          |                 |

| Power Generation                                                                        | 3               |

| General Context of RF Power Transmitters                                                | 4               |

| General Requirements for Modern RF Transmitters                                         | 4               |

| Microwave Power Transmitter Architecture                                                | 6               |

| Issues and challenges in RF Power Amplifiers                                            | 7               |

| Basic Architecture of an RF Power Amplifier                                             | 7               |

| General Design Considerations and Figures of Merit (FoM)                                | 14              |

| Power Characteristics and Power Budget                                                  | 15              |

| Linearity Criteria                                                                      | 20              |

| Transistor Technology: Gallium Nitride (GaN)                                            | 24              |

| Why Gallium Nitride?                                                                    | 24              |

| General Figure of Merits for GaN Device Selectivity                                     | 25              |

| Band Gap, Intrinsic Charge Density and Breakdown Field                                  | 25              |

| Thermal Conductivity                                                                    | 26              |

| Johnson's Figure of Merit (JFM) and Baliga's Figure of Merit (BFM) GaN Device Structure | 26              |

| GaN Device Structure                                                                    | 27<br>30        |

| DC-IV curves                                                                            | 31              |

| Maximum Available Gain (MAG) and Maximum Stable Gain (MSG)                              | $\frac{31}{32}$ |

| Conclusions                                                                             | $\frac{32}{33}$ |

| Chapter II High Efficiency RF Power Transmitter Architectures                           | 35              |

| Introduction                                                                            | 36              |

| Motivation                                                                              |                 |

| Basics of Modern Modulation Schemes                                                     | 36              |

| RF Modulation Scheme in Bandpass Radio Communication Channel                            |                 |

| Characteristic Features of Modern Modulated Signals                                     | 39              |

| Crest Factor and Peak to Average Power Ratio (PAPR)                                     | 40              |

| Average and Instantaneous Power for Modulated Signals                                   | 41              |

| Probability Density Function (PDF)                                                      | 43              |

| RFPA Spectral Regrowth and Adjacent Channel Power Ratio (ACPR) :                        |                 |

| Out-of Band Distortion                                                                  | 44              |

viii *CONTENTS*

|               | Error Vector Magnitude (EVM): In-band Distortion                  | . 46  |

|---------------|-------------------------------------------------------------------|-------|

|               | Noise Power Ratio (NPR)                                           | . 47  |

| High Efficier | ncy Power Transmitter Architectures for Modulated Signals         | . 48  |

| Load N        | Modulation Technique and Doherty Architecture                     | . 50  |

|               | Principle of Doherty Technique                                    | . 50  |

|               | Implementation of the Doherty Principle                           | . 52  |

|               | Limitations in Doherty Power Amplifier Implementation             | . 55  |

| Envelo        | pe Tracking Technique                                             | . 56  |

|               | Principle of Envelope Tracking Technique                          | . 56  |

|               | Implementation of Envelope Tracking Architecture                  | . 60  |

|               | Major Design Challenges in Conventional ET Implementation $$      | . 61  |

| Outph         | asing Technique                                                   | . 62  |

|               | Principle of Outphasing                                           | . 62  |

|               | Implementation of Outphasing Architecture                         | . 63  |

|               | Design Issues with Outphasing Architecture Implementation $\dots$ | . 65  |

| Envelo        | pe Elimination and Restoration (EER)                              | . 66  |

|               | Principle of operation of EER Technique                           | . 66  |

|               | Implementation of EER Technique                                   | . 67  |

|               | Major Design Challenges in Conventional EER Implementation $$ .   | . 68  |

| Conclusion.   |                                                                   | . 70  |

| Chapter III   | Design and Characterization of S-Band GaN RF Vector               | r     |

| Power Modul   |                                                                   | 71    |

|               |                                                                   |       |

| _             | the Vector Power Modulator                                        |       |

|               | d Architecture                                                    |       |

|               | ransistors and PCB Technology Selected                            |       |

|               | ew of the Design Methodology                                      |       |

|               | edure of the Power Stage                                          |       |

|               | ircuit Architecture and Stability Issue                           |       |

|               | ng Network Design                                                 |       |

|               | Load-Pull Analysis                                                |       |

|               | Design of Output Matching Network for the Power Stage             |       |

|               | Frequency and Power Characteristics of Power Stage                |       |

|               | Requirements of a Two-stage Circuit                               |       |

| _             | edure of the Two-stage Circuit                                    |       |

|               | ircuit Architecture and Stability Issue of the Driver Stage       |       |

| Matchi        | ng Network Design                                                 |       |

| _             | Load-Pull Analysis of the Driver Stage                            |       |

| Two-st        | age Saturated Variable Gain Power Modulator Circuit               |       |

|               | Frequency and Power Characteristics of the Driver Stage           |       |

|               | Two-stage GaN-HEMT Power Modulator : Simulation Results           |       |

|               | at Results                                                        |       |

|               | static Measurement Results of the Two-stage Power Modulator Circ  |       |

| Associa       | ation of the Supply Modulator and the Two-stage Circuit: The      |       |

|               | Vector Power Modulator                                            |       |

|               | The Vector Power Modulator Key building Blocks                    | . 108 |

CONTENTS ix

| Multi-level discrete GaN Based Hybrid Supply Modulator Circuit:            |

|----------------------------------------------------------------------------|

| Implementation and Working Principle 109                                   |

| Association of the Two-stage SVG and Supply Modulator Circuit $$ . 110     |

| Vector Power Modulator Dynamic Measurements                                |

| Application to 16-QAM Generation                                           |

| Prospectives and Conclusions                                               |

| Chapter IV Investigation of New Bias Architecture for Bandwidth En-        |

| hancement of Vector Power Modulator 119                                    |

| Motivation                                                                 |

| Presentation of the New Bias Circuit                                       |

| Proposed Architecture and Comparison with the First Version 120            |

| Vector Power Modulator Design with New Bias Circuit                        |

| Design of the New Vector Power Modulator Circuit                           |

| Performances of the New Vector Power Modulator Circuit                     |

| Comparison between Previous and the New Vector Power Modulator Circuit 129 |

| Comparison in terms of RF Bandwidths                                       |

| Conclusions                                                                |

| General Conclusions and Perspectives 136                                   |

| References 140                                                             |

## List of Figures

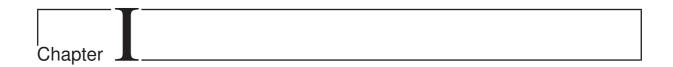

| I.1  | General Architecture of an RF Power Transmitter Chain (a) Linear case (b) Non-linear case and (c) General power characteristics of an RFPA                                                                                                                                                                                                                                                                | 4  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

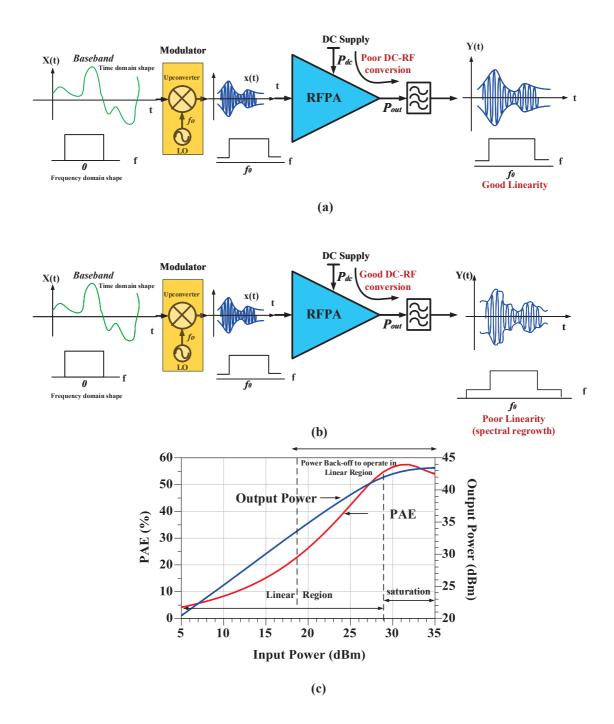

| I.2  | General Architecture of RF Power Transmitter Chain                                                                                                                                                                                                                                                                                                                                                        | 6  |

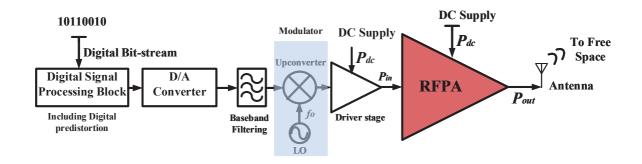

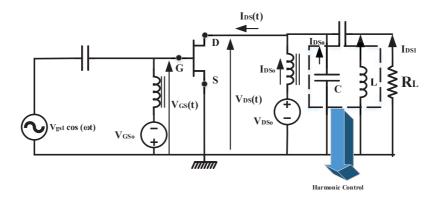

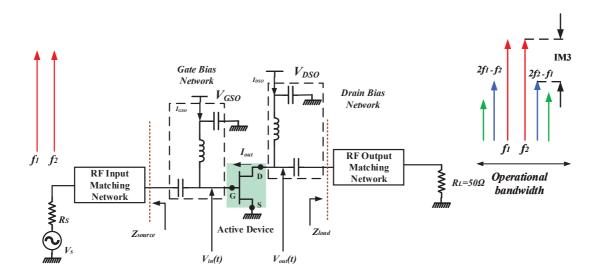

| I.3  | Block Diagram of RF power amplifier and simplified model of the transistor                                                                                                                                                                                                                                                                                                                                | 8  |

| I.4  | Static piecewise-linear DC-IV characteristics of a simplified power transis-                                                                                                                                                                                                                                                                                                                              |    |

| 1.1  | tor model                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |

| I.5  | Representation of different current flow within a simplified amplifier model                                                                                                                                                                                                                                                                                                                              | 10 |

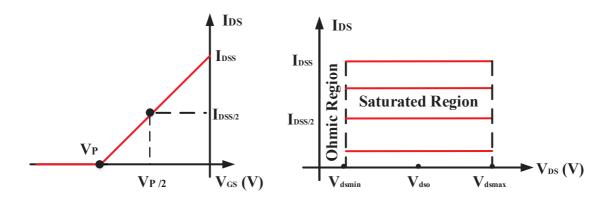

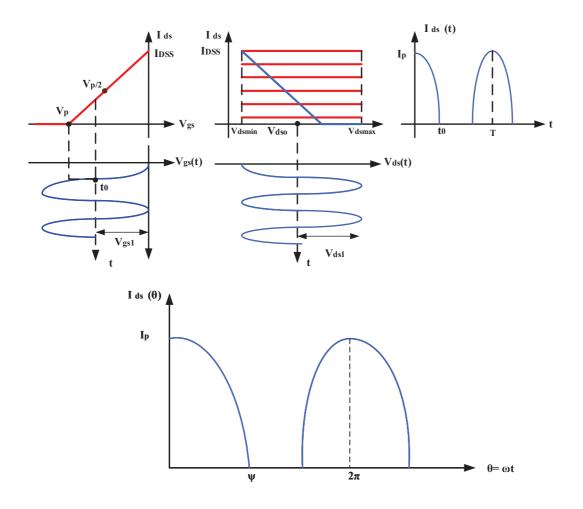

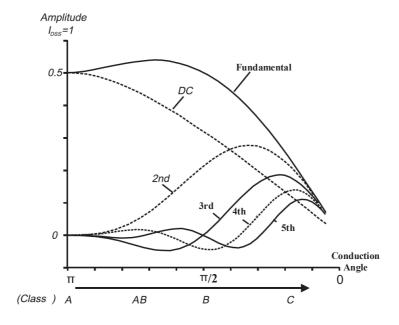

| I.6  | Illustration of the conduction angle phenomenon from simplified voltage-<br>current characteristics of a power transistor, $I_P = I_{DSS}$ and $V_{GSmax} =$                                                                                                                                                                                                                                              |    |

|      | 0                                                                                                                                                                                                                                                                                                                                                                                                         | 11 |

| I.7  | Illustration of the conduction angle phenomenon from simplified voltage-                                                                                                                                                                                                                                                                                                                                  |    |

|      | current characteristics of a power transistor                                                                                                                                                                                                                                                                                                                                                             | 13 |

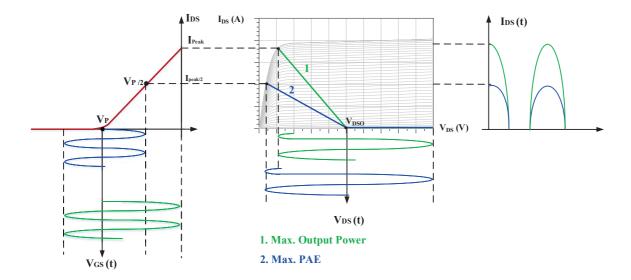

| I.8  | Transistor loadline illustration for maximum PAE (in blue) and output                                                                                                                                                                                                                                                                                                                                     |    |

|      | power (in green)                                                                                                                                                                                                                                                                                                                                                                                          | 15 |

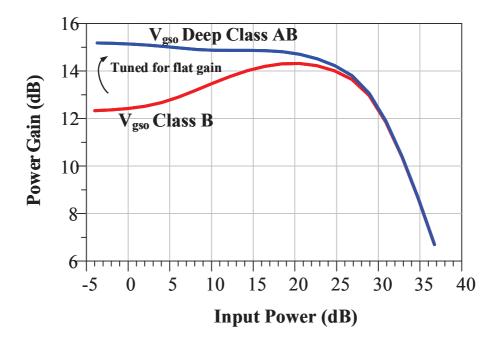

| I.9  | Gain characteristics of a conventional RF power amplifier                                                                                                                                                                                                                                                                                                                                                 | 16 |

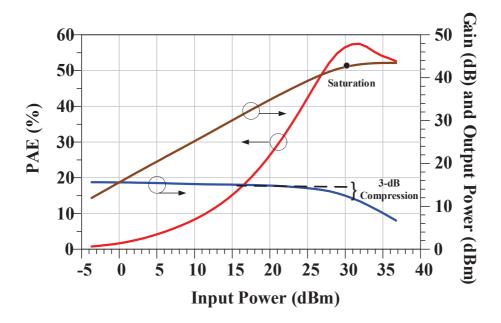

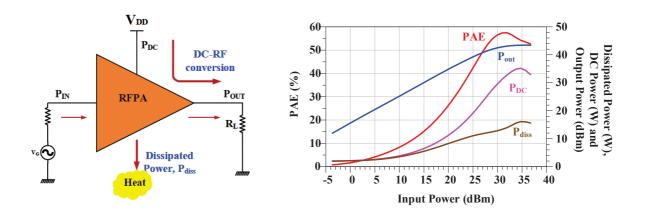

| I.10 | Power characteristics of a conventional GaN based RF power amplifier                                                                                                                                                                                                                                                                                                                                      | 17 |

| I.11 | Power Budget Analysis                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

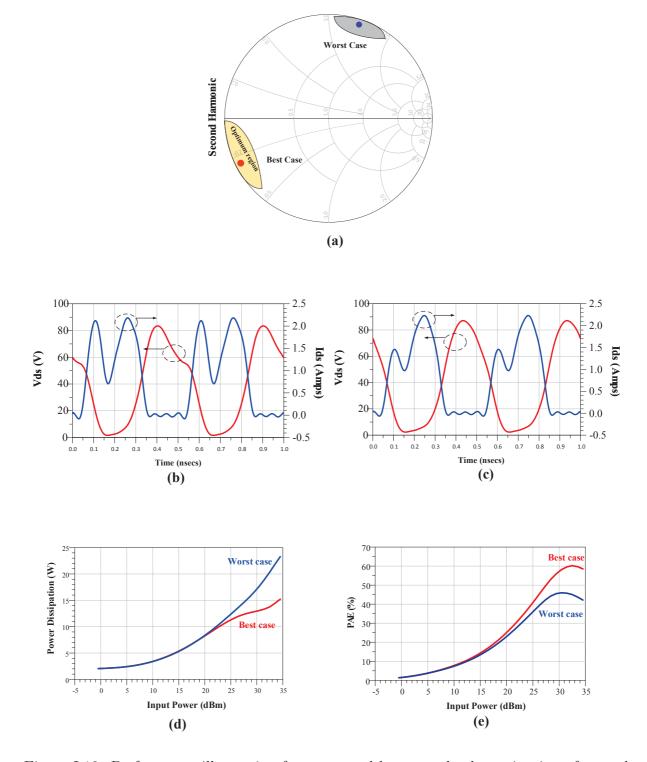

| I.12 | Performance illustration for worst and best case load termination of second harmonic (a) Worst and ideal regions of second harmonic load impedance (b) Intrinsic drain voltage and current waveforms in worst case (c) Intrinsic drain voltage and current waveforms in best case (d) Power dissipation comparison between best and worst case and (e) Efficiency comparison between best and worst case. | 19 |

| I.13 | General schematic of an RFPA indicating the input and output voltages .                                                                                                                                                                                                                                                                                                                                   | 20 |

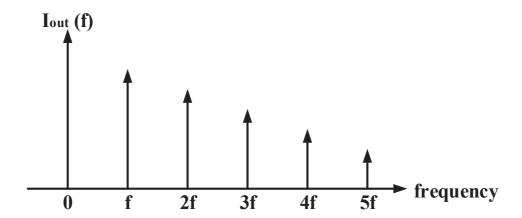

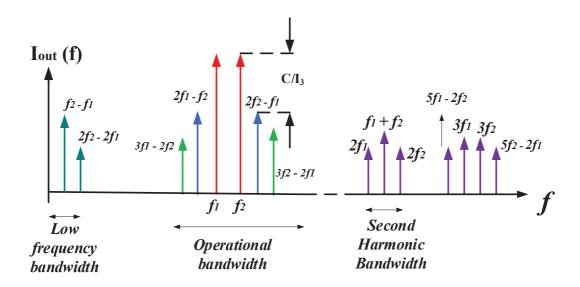

| I.14 | Shape of the output current spectrum for a single tone linear excitation                                                                                                                                                                                                                                                                                                                                  | 21 |

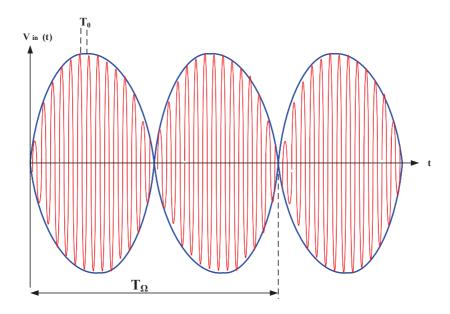

| I.15 | General shape of a modulated signal with two-tone excitation                                                                                                                                                                                                                                                                                                                                              | 22 |

| I.16 | Illustration of output current spectrum under a two tone excitation show-                                                                                                                                                                                                                                                                                                                                 |    |

|      | ing the intermodulation products                                                                                                                                                                                                                                                                                                                                                                          | 22 |

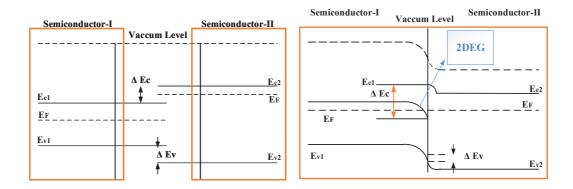

| I.17 | Energy band diagrams for narrow (I) and wide (II) band gap semiconductors (left) and also the discontinuities in bands after equilibrium in the heterostructure (right)                                                                                                                                                                                                                                   | 27 |

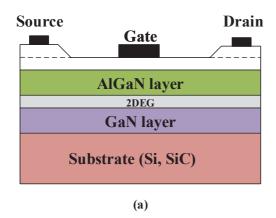

| I.18 | (a) Simplified cross-section of AlGaN/GaN-HEMT and (b) Cross-section                                                                                                                                                                                                                                                                                                                                      |    |

| 1.10 | of AlGaN/GaN-HEMT on a Silicon substrate seen with a scanning electron microscope.                                                                                                                                                                                                                                                                                                                        | 28 |

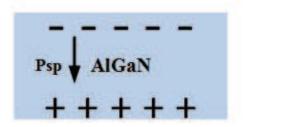

| I.19 | Spontaneous polarization induced surface charges in the AlGaN and GaN                                                                                                                                                                                                                                                                                                                                     |    |

| ŭ    | structure.([14])                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

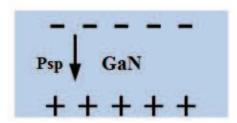

| I.20 | Strain induced piezoelectric polarization in the AlGaN/GaN heterostruc-                                                                                                                                                                                                                                                                                                                                   |    |

|      | ture ([14])                                                                                                                                                                                                                                                                                                                                                                                               | 29 |

LIST OF FIGURES xi

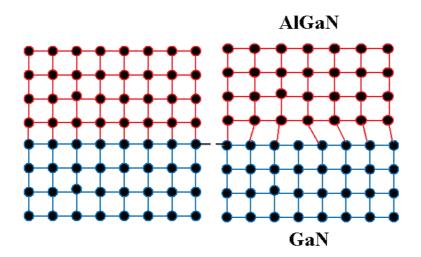

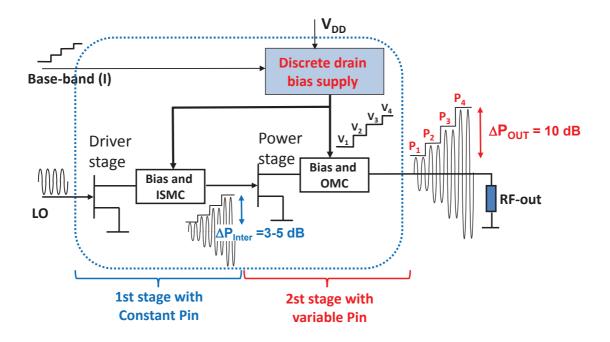

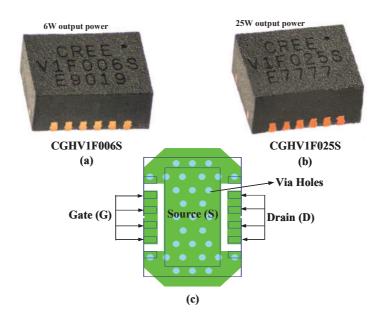

| I.21   | Packaged transistor technology used: (a) Cree CGHV1F006S (b) CGHV1F002 and (c) Transistor footprints indicating the different terminals      | 25S<br>31 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

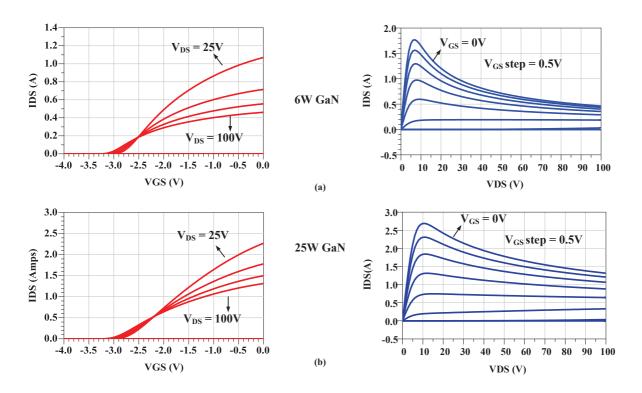

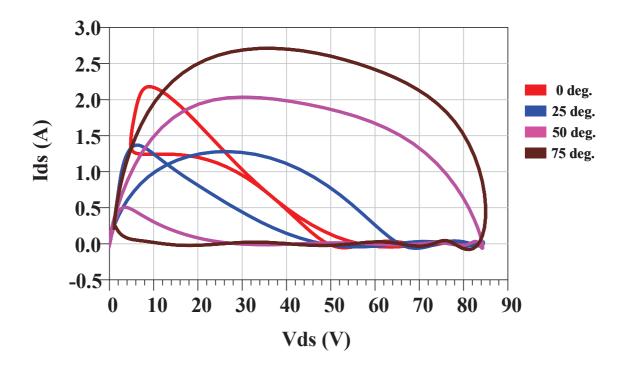

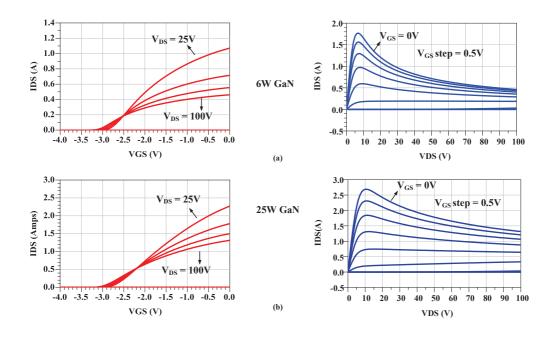

| I.22   | DC-IV characteristics: (a) Cree CGHV1F006S (b) CGHV1F0025S                                                                                   | 31        |

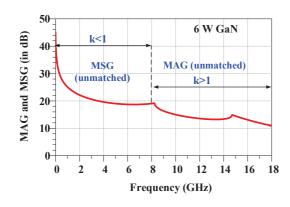

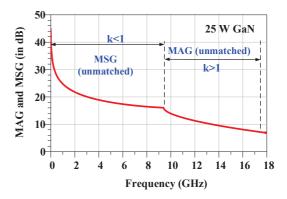

| I.23   | Simulated MAG and MSG capabilities of the 6 W (left) and 25 W (right)                                                                        | 01        |

|        | packaged GaN transistor alone                                                                                                                | 33        |

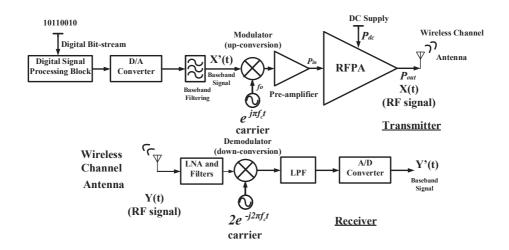

| II.1   | General Illustration of Communication Transceiver Chain                                                                                      | 37        |

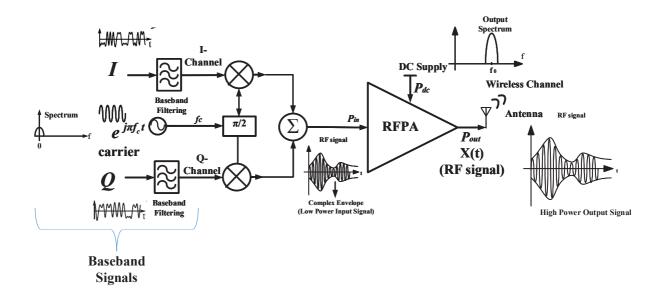

| II.2   | Ideal Quadrature Transmitter System                                                                                                          | 39        |

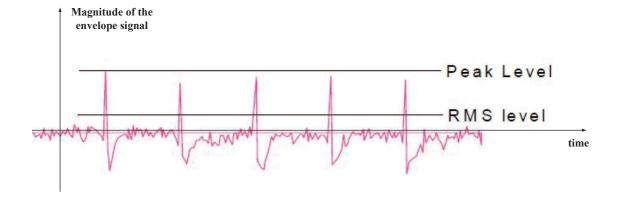

| II.3   | Crest Factor Representation for Complex Modulated Signal                                                                                     | 40        |

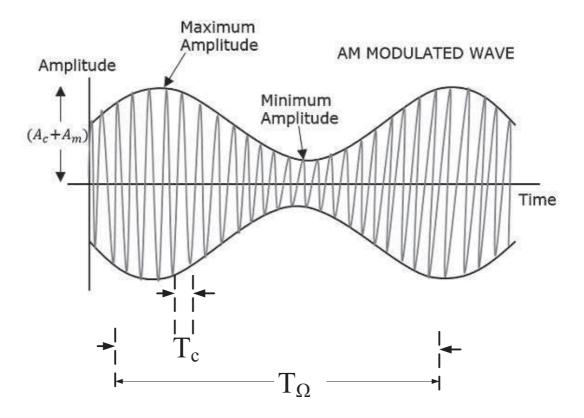

| II.4   | Simplified representation of an amplitude modulated signal with variable envelope                                                            | 41        |

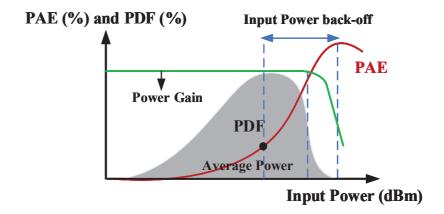

| II.5   | Typical RFPA efficiency with respect to input power. Probability density                                                                     |           |

|        | function for a high PAPR signal at an average output power level example                                                                     |           |

|        | is illustrated                                                                                                                               | 44        |

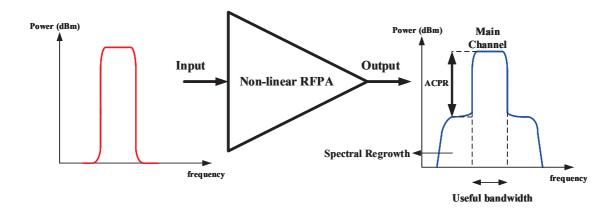

| II.6   | Graphical depiction of ACPR for Complex Modulated Signals, Input spectrum of the modulated signal (left, in red) and Output Spectrum (right, |           |

|        | in blue)                                                                                                                                     | 45        |

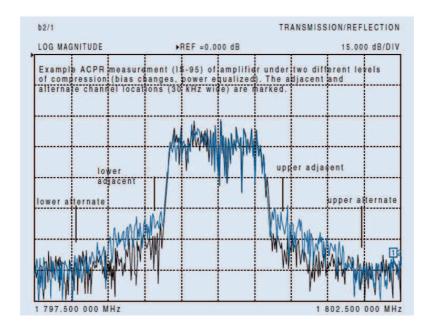

| II.7   | Example of a non-linear RFPA output spectrum illustrating spectral regrowth ([24])                                                           | 45        |

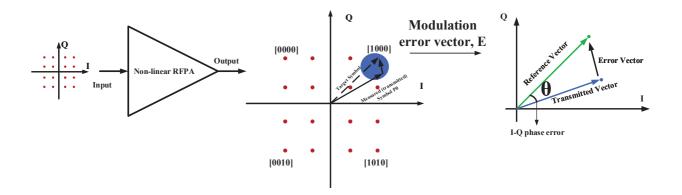

| II.8   | Demonstration of EVM principle for 16-QAM constellation example across                                                                       | 10        |

|        | RFPA output                                                                                                                                  | 46        |

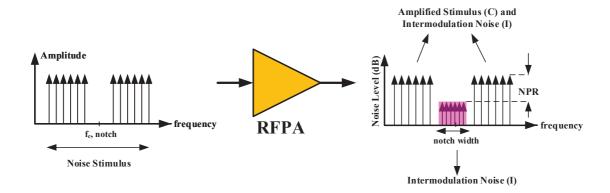

| II.9   | A digital NPR test stimulus with white noise source connected in cascade                                                                     |           |

|        | with a bandpass filter and a notch filter. The notch depth can be measured                                                                   |           |

|        | with a Spectrum Analyzer                                                                                                                     | 47        |

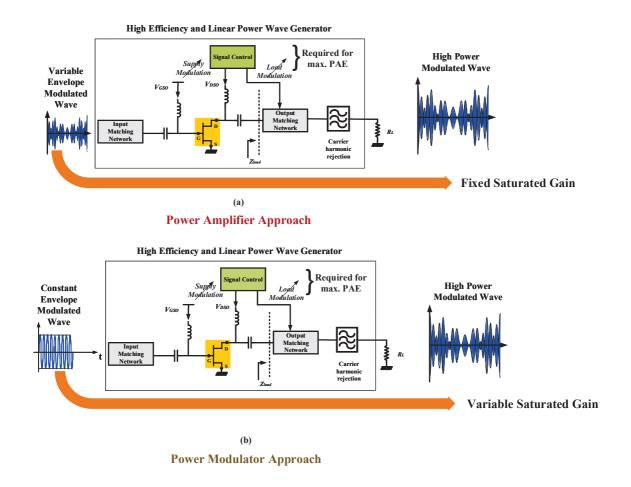

| II.10  | General architecture of a modulated power wave generating system for                                                                         |           |

|        | modulated signals (a) fixed saturated gain and (b) variable saturated gain.                                                                  | 49        |

| II.11  | General schematic of an RFPA with a load tuner demonstrating load vari-                                                                      |           |

|        | ation for three different input power levels                                                                                                 | 50        |

| II.12  | Power Added Efficiency as a function of output power for three different                                                                     |           |

| II 10  | load impedances A, B and C                                                                                                                   | 51        |

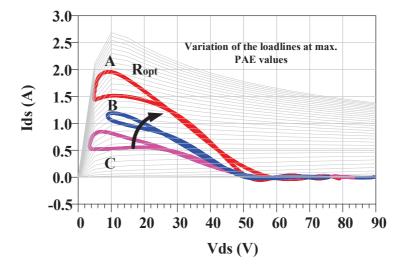

| II.13  | Intrinsic loadlines corresponding to three different load impedances A, B                                                                    | ۲1        |

| TT 1 / | and C.                                                                                                                                       | 51        |

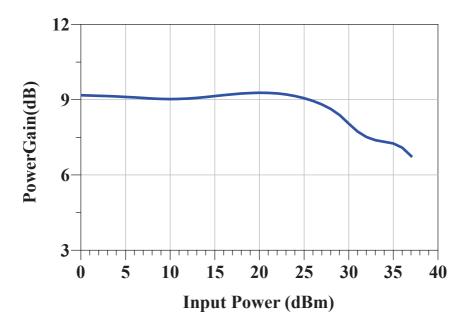

| II.14  | Gain shape for varied load impedances versus input power                                                                                     | 52        |

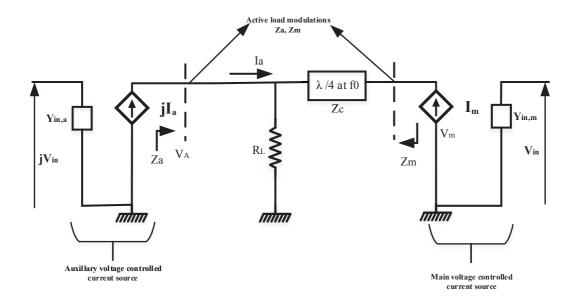

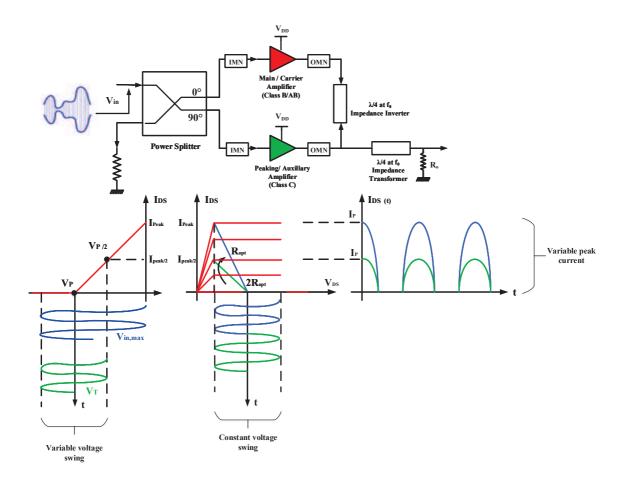

| II.15  | Principle of Active Load Pull in Doherty Technique                                                                                           | 53        |

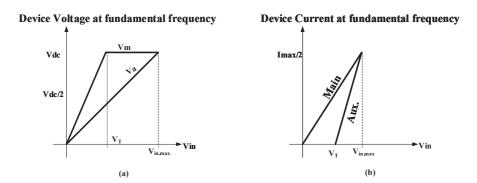

| II.16  | (a) Voltage and (b) current combination for the main and auxiliary transistors.                                                              | E 1       |

| II.17  | sistors                                                                                                                                      | 54        |

| 11.17  | teristics of the voltage controlled drain current source along with voltage                                                                  |           |

|        | and current waveforms and associated loadlines for the Main Amplifier                                                                        | 54        |

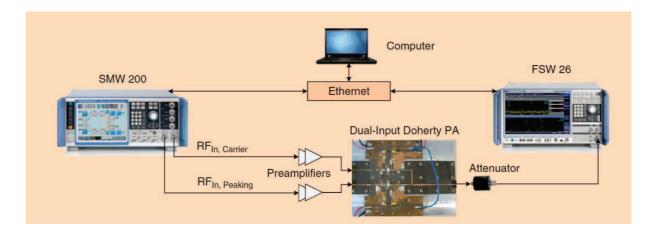

| II.18  | A mixed-signal demonstrator setup for the digitally equalized Doherty PA                                                                     | 94        |

| 11.10  | ([32])                                                                                                                                       | 56        |

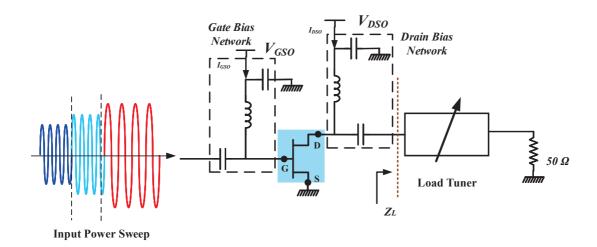

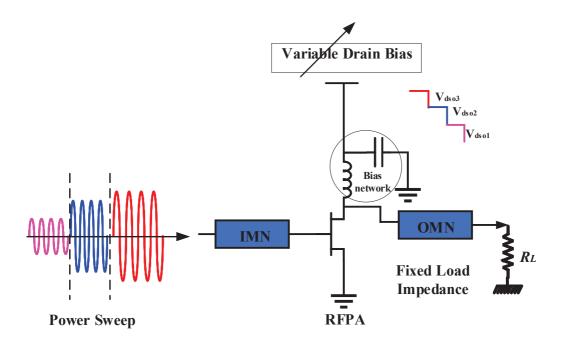

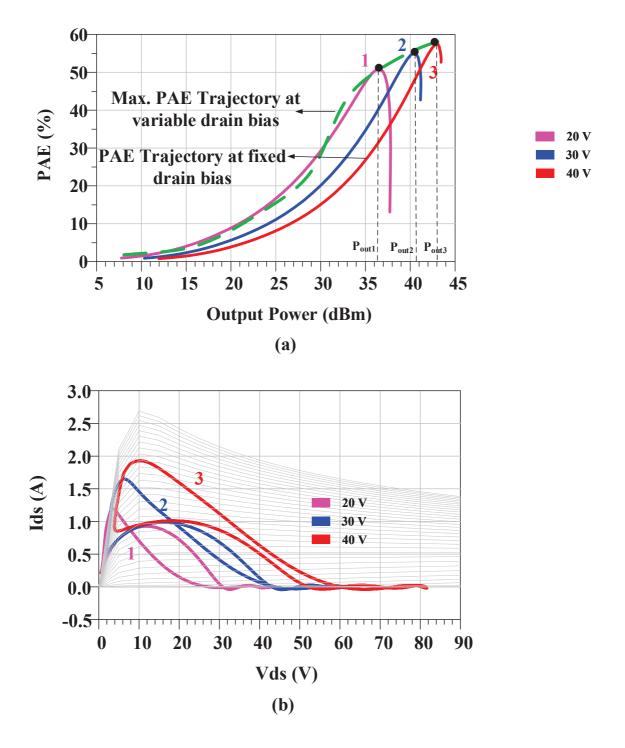

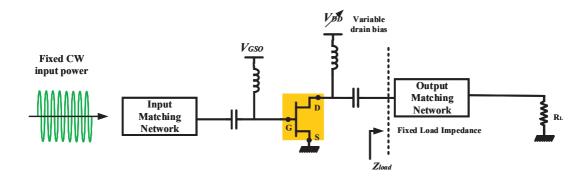

| II.19  | General schematic of a Wolfspeed packaged GaN 25 W transistor RFPA                                                                           |           |

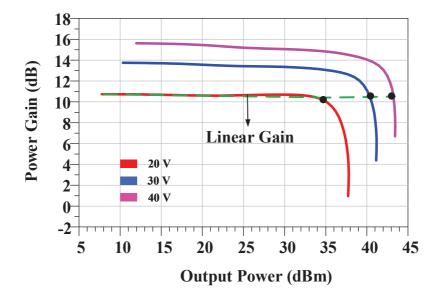

|        | with a fixed load impedance and variable drain bias voltage demonstrating                                                                    |           |

|        | envelope tracking principle for three different input power levels                                                                           | 57        |

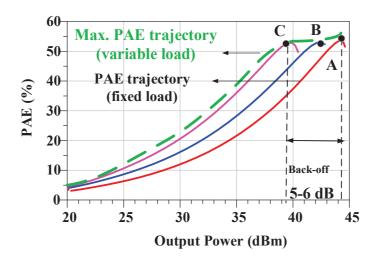

| II.20  | (a) Corresponding simulated PAE performances as a function of output                                                                         |           |

|        | power, indicating the optimum trajectory for maximum PAE and (b) In-                                                                         |           |

|        | trinsic loadlines for three drain bias voltage                                                                                               | 58        |

xii LIST OF FIGURES

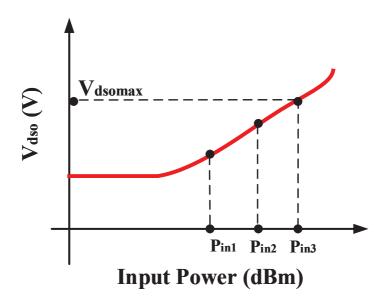

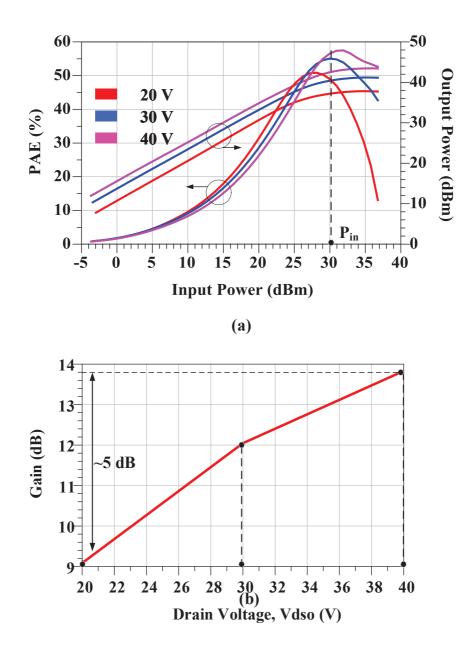

| II.21<br>II.22 | Drain bias law versus input power to get the maximum PAE trajectory<br>Simulated CW gain characteristics as a function of drain output power         | 59       |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 11.22          | with the optimum trajectory corresponding to linear gain at different drain                                                                          |          |

|                | voltages                                                                                                                                             | 59       |

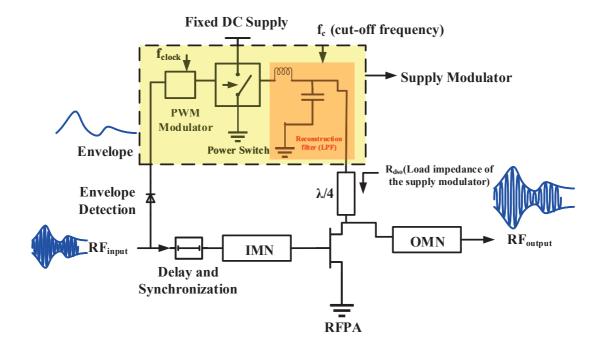

| II.23          | Simplified architecture of Envelope Tracking amplifier                                                                                               | 60       |

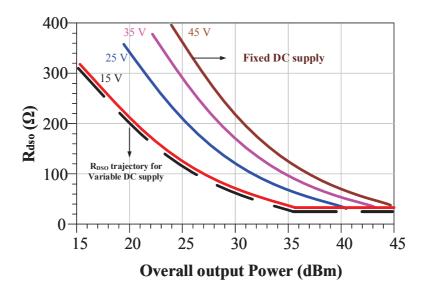

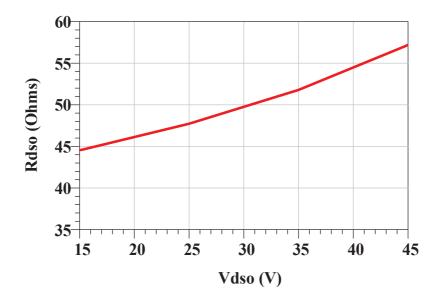

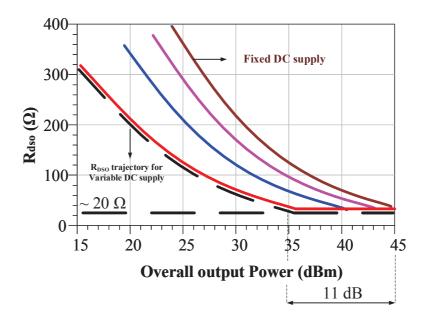

| II.24          | Simulated values of drain resistance $R_{dso}$ as a function of output power                                                                         | 61       |

| II.25          | Simplified block diagram of an outphasing transmitter architecture                                                                                   | 62       |

| II.26          | General schematic of an outphasing principle with a non-isolating power combiner                                                                     | 64       |

| II.27          | Intrinsic loadlines at maximum PAE and fixed input power for four different outphasing angles                                                        | 65       |

| II.28          | General Schematic of a 25 W GaN transistor based RFPA with fixed input                                                                               |          |

| II 90          | power and variable drain bias                                                                                                                        | 66       |

| II.29          | Simplified principle of operation for EER technique (a) PAE and output power as a function of input power and (b) Gain variation as a function       |          |

|                | of drain voltage                                                                                                                                     | 67       |

| II.30          | Architecture of Classical EER Transmitter with separate amplitude and                                                                                |          |

| II 01          | phase information                                                                                                                                    | 68       |

| II.31          | Variation of $R_{dso}$ versus $V_{dso}$                                                                                                              | 69       |

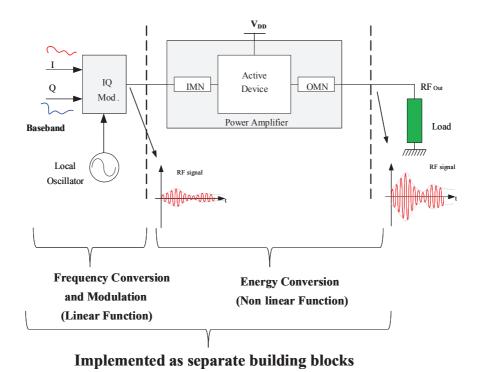

| III.1          | Conventional transmitter architecture                                                                                                                | 73       |

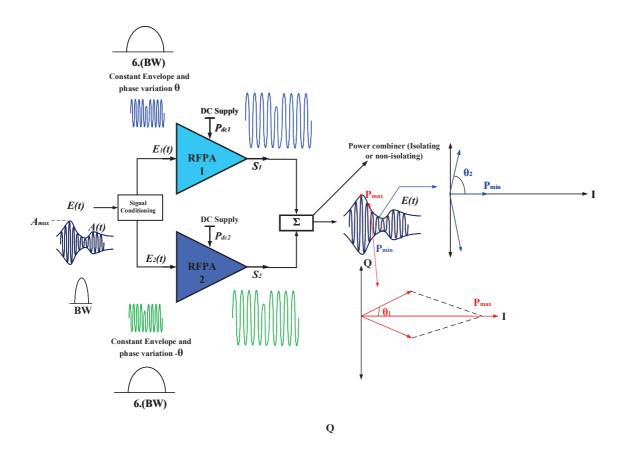

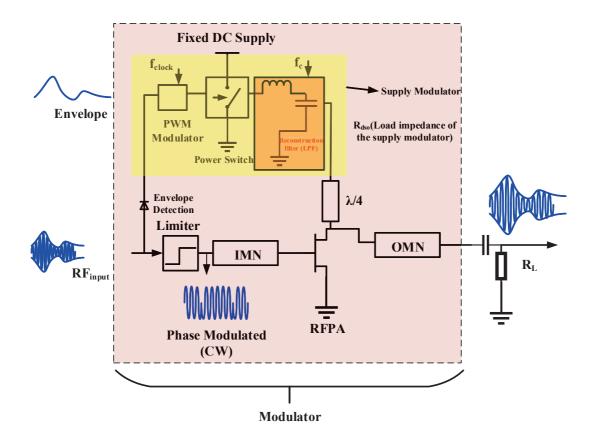

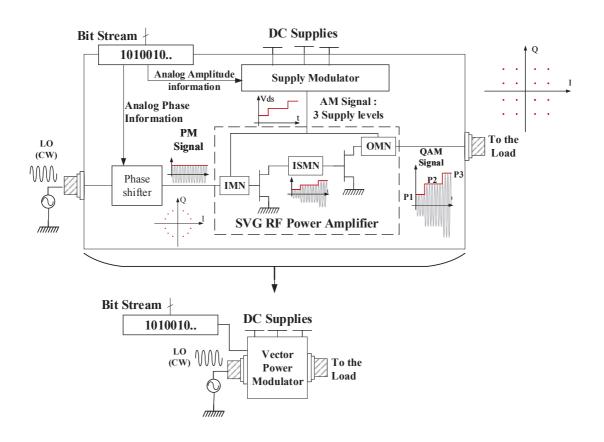

| III.2          | Proposed GaN based Vector Power Modulator                                                                                                            | 74       |

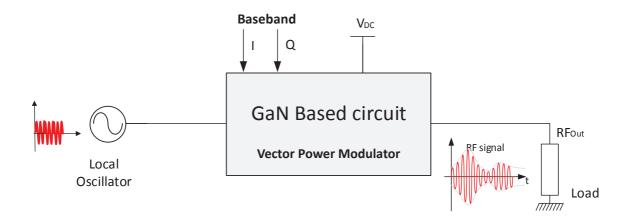

| III.3          | Working principle of the Vector Power Modulator                                                                                                      | 74       |

| III.4          | Packaged transistor technology used: (a) Cree CGHV1F006S (b) CGHV1F00                                                                                |          |

| III.5          | and (c) Transistor footprints indicating the different terminals                                                                                     | 76       |

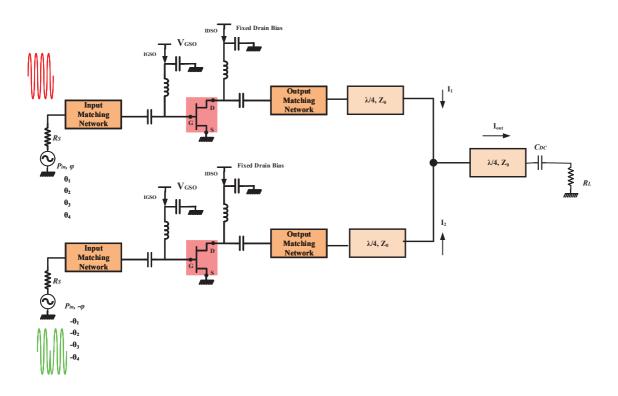

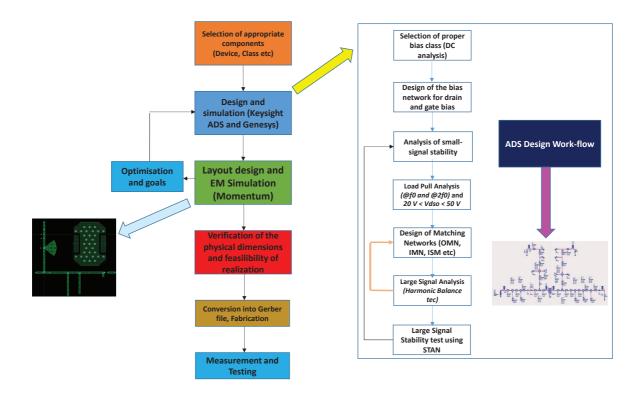

| III.6          | DC-IV characteristics of the GaN transistor (a) 6 W and (b) 25 W Design methodology steps for the overall two-stage circuit                          | 76<br>78 |

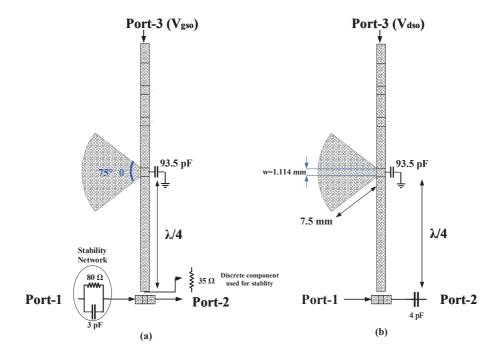

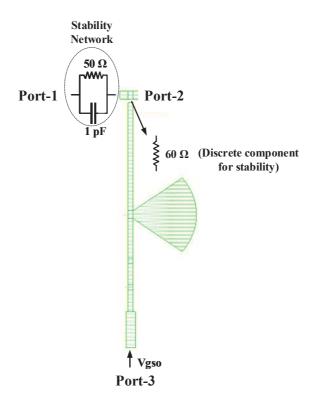

| III.7          | Topology of the biasing circuits along with the stability network for the                                                                            | 10       |

|                | power stage (a) gate bias circuit and (b) drain bias circuit                                                                                         | 79       |

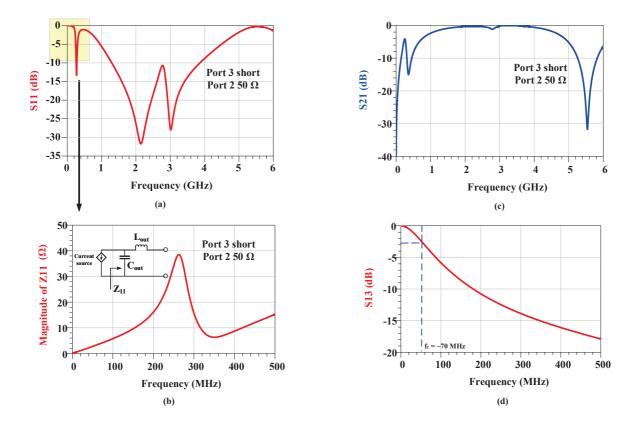

| III.8          | Simulated S-parameter results of the output bias network (a) $S_{11}$ response                                                                       |          |

|                | (b) Low frequency impedance $Z_{11}$ (c) $S_{21}$ response and (d) Isolation be-                                                                     |          |

|                | tween DC and RF ports                                                                                                                                | 80       |

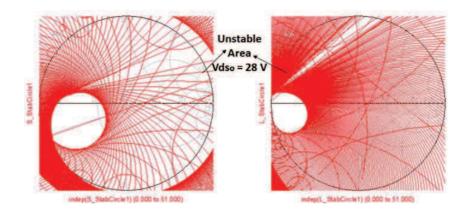

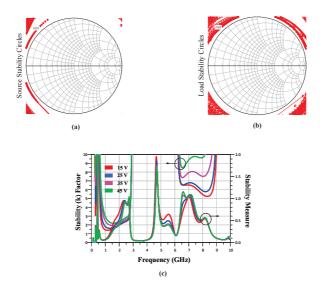

| III.9          | Simulated stability circles (left) Source stability circles (right) Load sta-                                                                        | 01       |

| III 10         | bility circles for determination of unconditional stability                                                                                          | 81       |

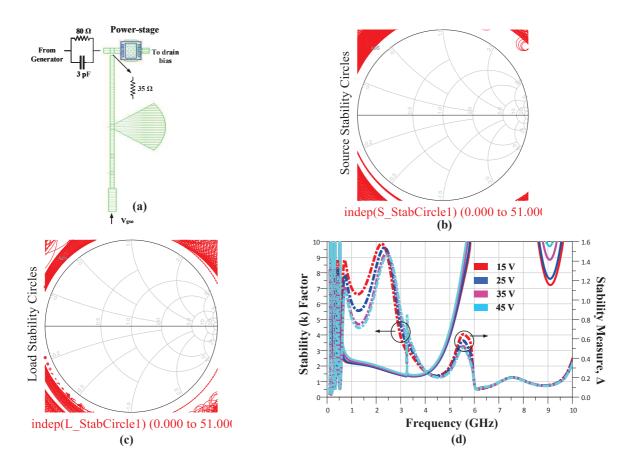

| III.10         | Unconditional Stability after the implementation of the stability network for the power-stage (a) Stability Network (b) Source Stability Circles (c) |          |

|                | Load Stability Circles and (d) Stability Factor, k and Stability Measure, $\Delta$ .                                                                 | 82       |

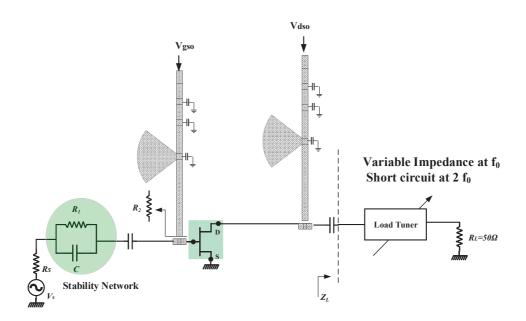

| III.11         | General schematic of initial loadpull analysis using load tuner with second                                                                          | 02       |

|                | harmonic as short                                                                                                                                    | 83       |

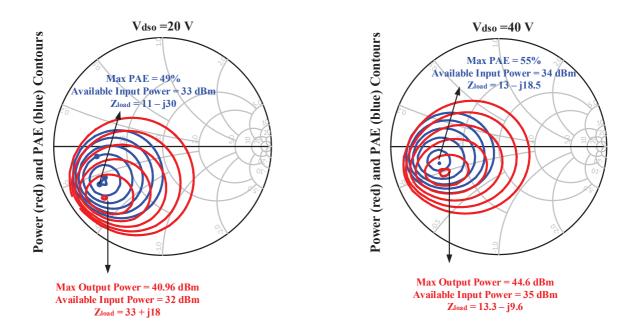

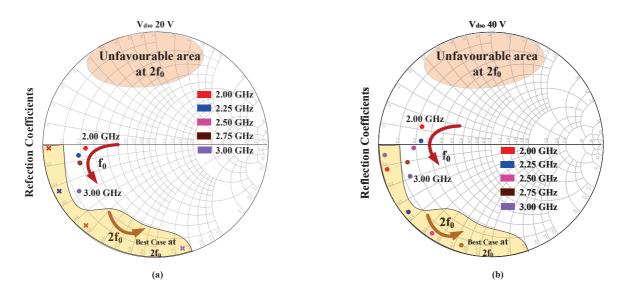

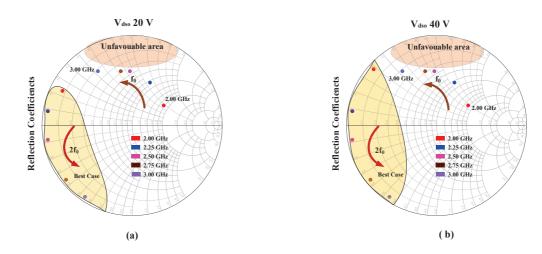

| III.12         | Initial loadpull contours for maximum output power and maximum PAE                                                                                   |          |

|                | at (a) $V_{dso}$ =20 V and (b) $V_{dso}$ =40 V optimized for maximum PAE when                                                                        |          |

| III 10         | $2f_0$ is short                                                                                                                                      | 84       |

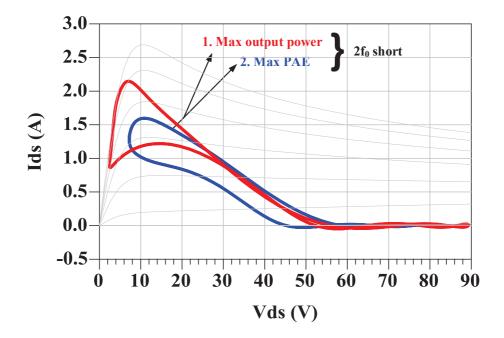

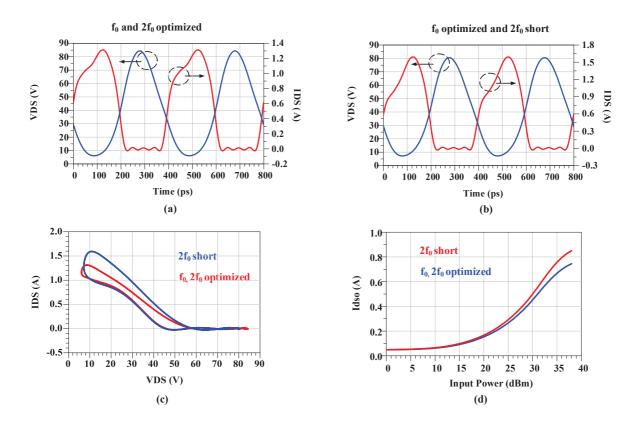

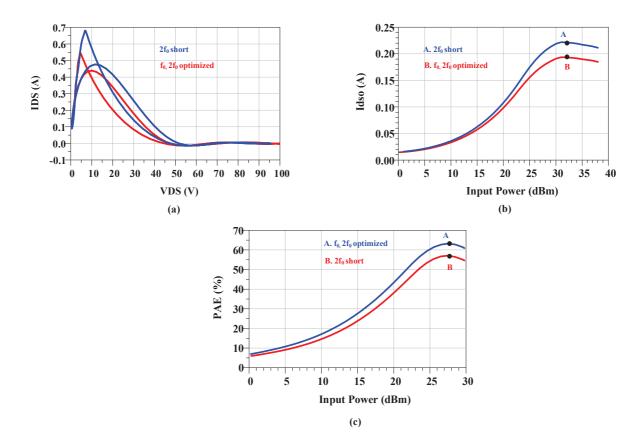

| III.13         | Loadlines for maximum output power (red) and maximum PAE (blue) at                                                                                   | 0.5      |

| III.14         | $f_0=2.5$ GHz and $V_{dso}=40$ V when $2f_0$ is short                                                                                                | 85       |

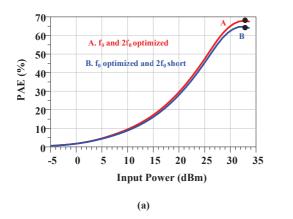

| 111.14         | monic is short and both fundamental and second harmonic are optimized                                                                                |          |

|                | at $f_0$ =2.5 GHz and $V_{dso}$ = 40 V                                                                                                               | 86       |

LIST OF FIGURES xiii

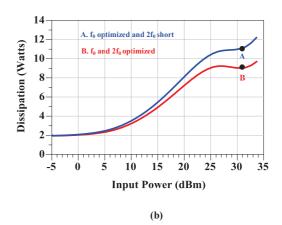

| 111.15           | Loadlines and voltage-current waveforms when the second harmonic is short and both fundamental and second harmonic optimized at saturation                                                                                                                                  | 0.6      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| III.16           | for $f_0=2.5$ GHz and $V_{dso}=40$ V                                                                                                                                                                                                                                        | 86       |

|                  | ( ) 400                                                                                                                                                                                                                                                                     | 87       |

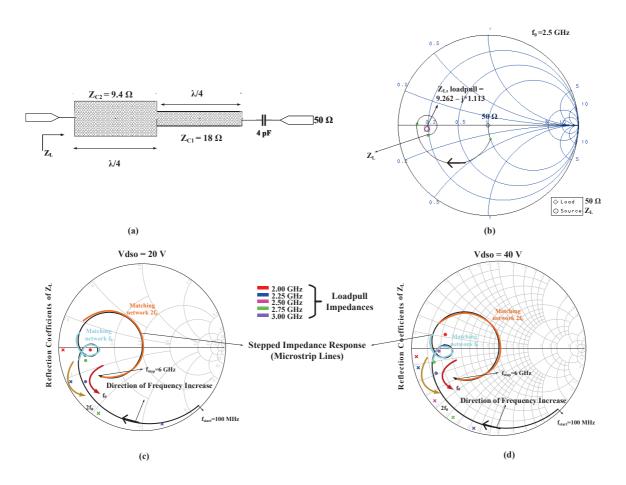

| III.17           | Stepped impedance output match topology for the power stage (a) layout (b) impedance transformation trajectory and comparison between stepped impedance response versus frequency with loadpull impedances at $V_{dso} = 20 \text{ V}$ (c) and $V_{dso} = 40 \text{ V}$ (d) | 88       |

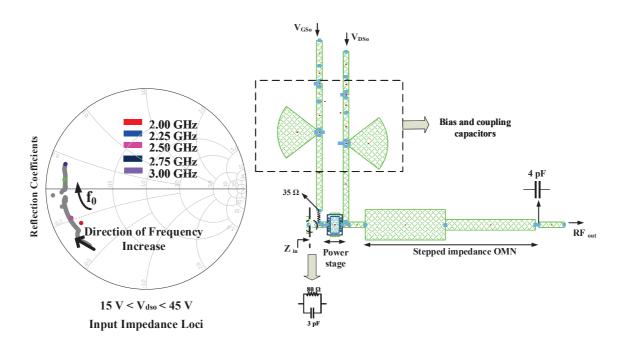

| III.18           | Layout of the power stage with stability and stepped-impedance output matching networks showing input impedance loci from loadpull at $V_{dso} =$                                                                                                                           | 89       |

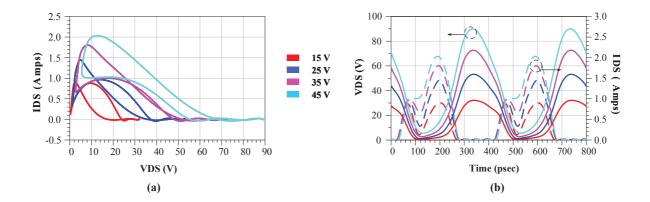

| III.19           | (a) Simulated intrinsic loadlines and (b) drain voltage and current wave-                                                                                                                                                                                                   | 90       |

| III.20           | 400                                                                                                                                                                                                                                                                         | 90       |

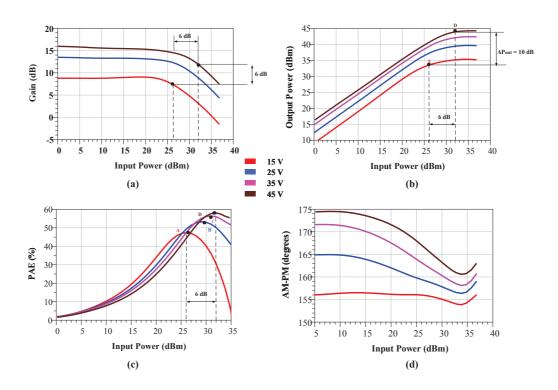

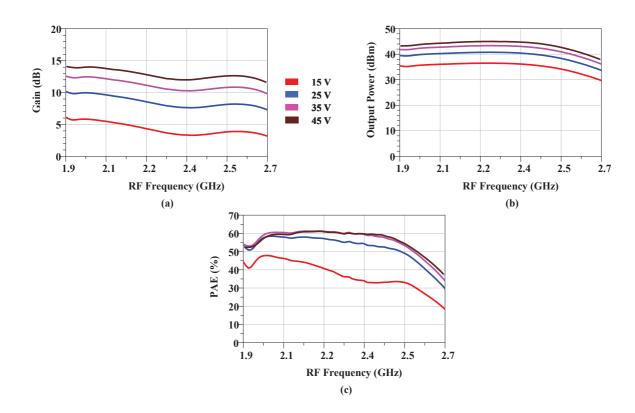

| III.21           | Simulated power characteristics of power stage RFPA alone as a function of RF frequency over the band of interest (a) Gain (b) Output Power and (c) PAE                                                                                                                     | 92       |

| III.22           | Simulated input and output power (a) and PAE characteristics (b) of the power stage, analysis is made for three different drain bias voltages for a                                                                                                                         | 93       |

| III.23           | Simulated input and output power (a) and PAE characteristics (b) of the power stage, analysis is made for three different drain bias voltages for a                                                                                                                         |          |

| III 0.4          |                                                                                                                                                                                                                                                                             | 93       |

| III.24<br>III.25 | Unconditional Stability after the implementation of the stability network for the driver-stage (a) Source Stability Circles (b) Load Stability Circles                                                                                                                      | 94<br>95 |

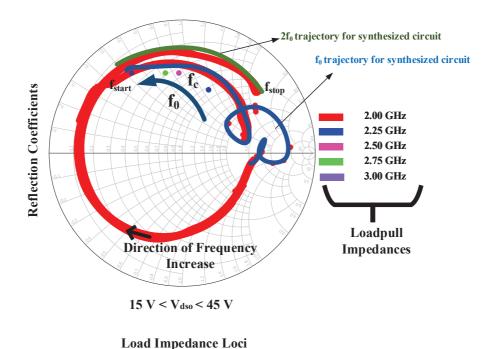

| III.26           | Optimal load impedance at fundamental and second harmonic favourable and unfavourable region for maximum PAE of the driver stage vs frequency.                                                                                                                              |          |

| III.27           | Example of power characteristics of 6 W transistor when the second harmonic is short and both fundamental and second harmonic optimized at                                                                                                                                  | 0.0      |

| 111.00           | 0 460                                                                                                                                                                                                                                                                       | 96<br>07 |

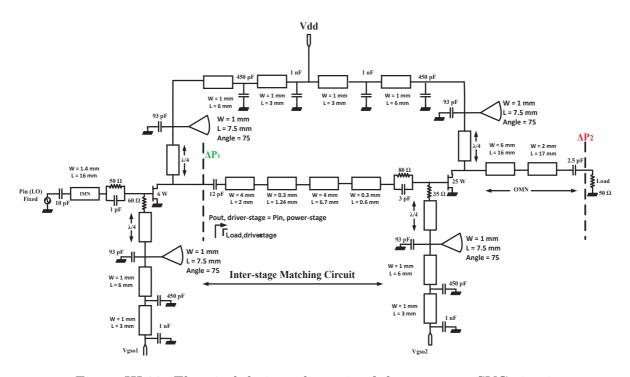

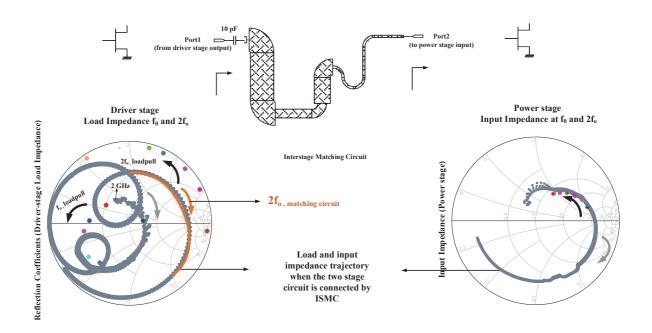

| III.28<br>III.29 | Optimum load impedance loci of the driver stage from loadpull and from the synthesized circuit at reference plane $\Delta P_1$ of fig. III.28. The impedance indicates clearly the $2f_0$ of the synthesized circuit is not well matched and                                | 97<br>98 |

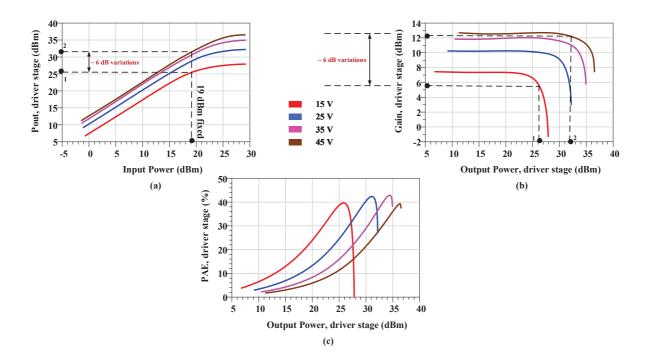

| III.30           | Simulated large signal CW power performances of the driver stage at 2.5                                                                                                                                                                                                     | 99       |

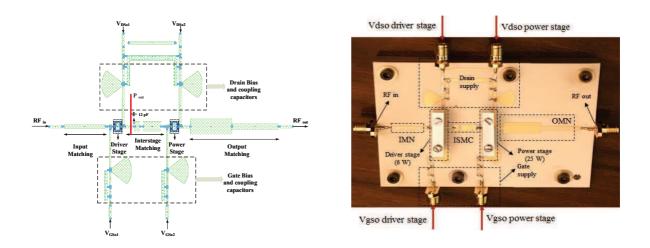

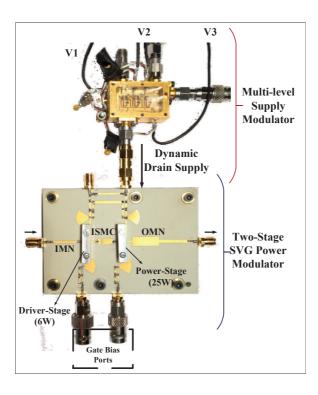

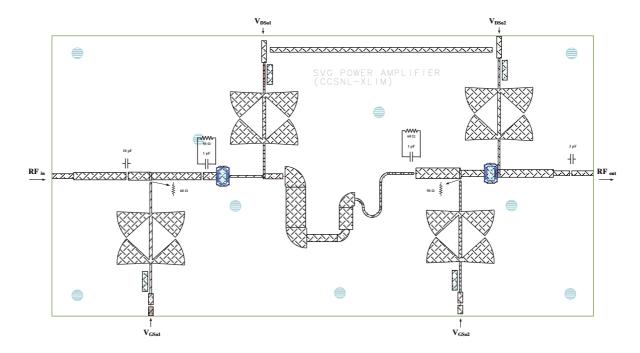

| III.31           | Layout (left) and fabricated (right) two-stage vector power modulator circuit. The circuit has been fabricated on Rogers RO4350 substrate with $\epsilon_r = 3.48$ ([70])                                                                                                   |          |

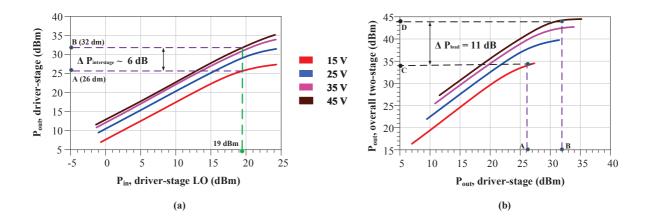

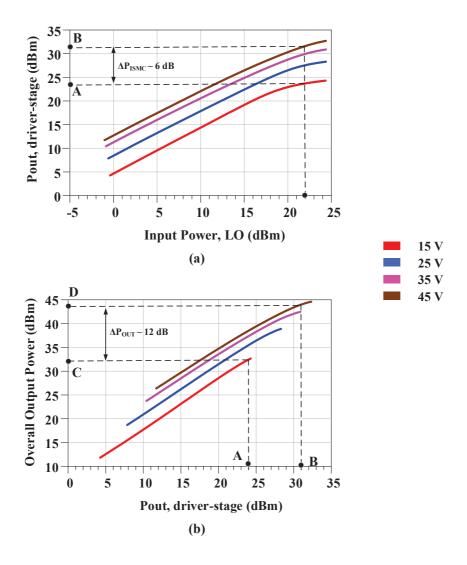

| III.32           | Input and output power characteristics of the (a) driver-stage and (b)                                                                                                                                                                                                      | 01       |

xiv LIST OF FIGURES

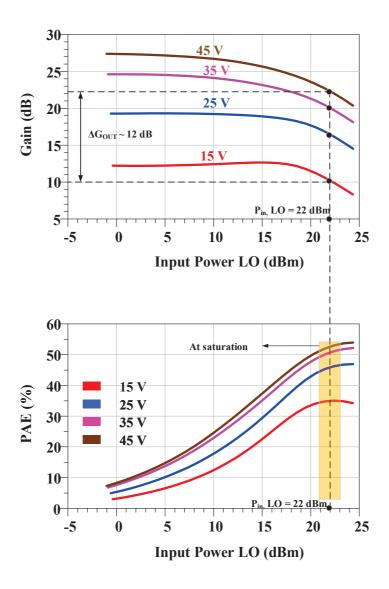

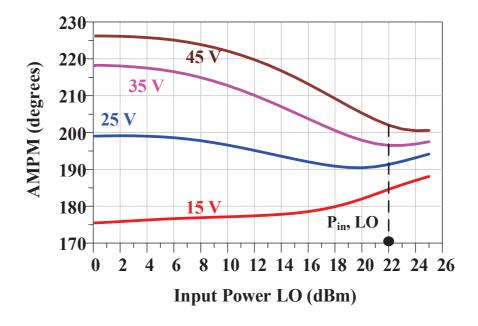

| 111.33 | Demonstration of gain transfer principle showing gain characteristics of<br>the (a) driver stage LO and (b) power stage respectively at 2.5 GHz 101          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

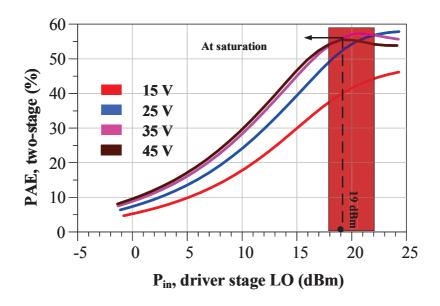

| III.34 | PAE as a function of input power LO of driver stage for the overall two-                                                                                     |

|        | stage power modulator circuit at 2.5 GHz                                                                                                                     |

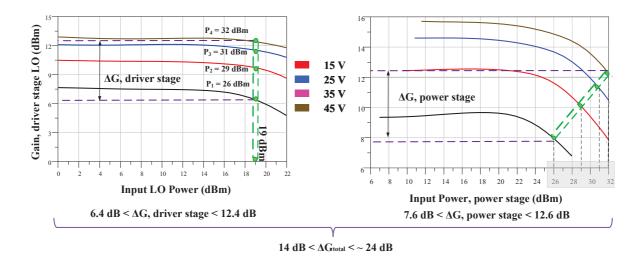

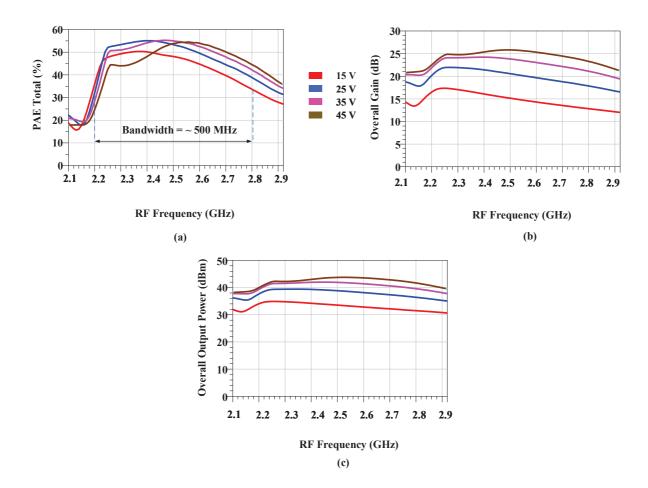

| III.35 | Simulated power characteristics of the two-stage power modulator circuit                                                                                     |

|        | as a function of RF frequency (a) PAE as a function of RF frequency and                                                                                      |

| 111.26 | (b) Overall two-stage circuit gain and (c) output power                                                                                                      |

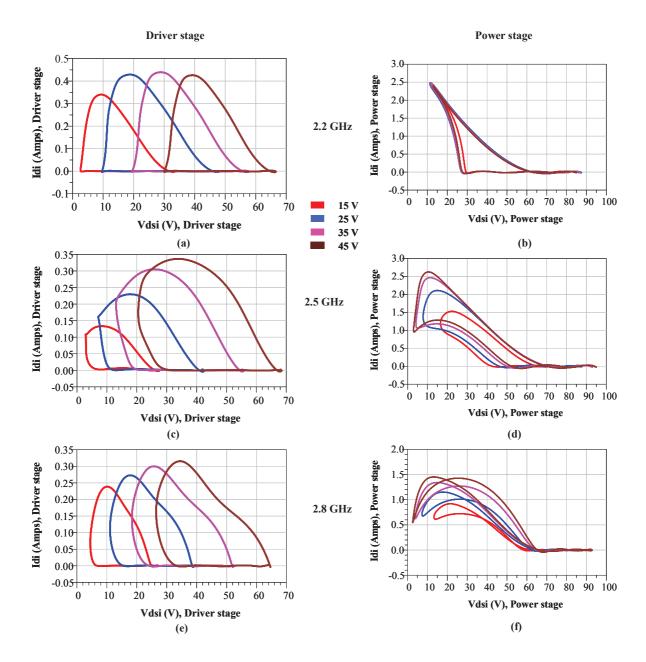

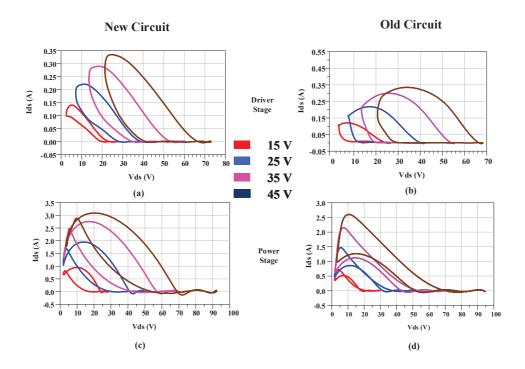

| III.36 | Simulated intrinsic loadlines for driver and power stages (a) -(b) at 2.2 GHz, (c) -(d) at 2.5 GHz and (e) -(f) at 2.8 GHz respectively 104                  |

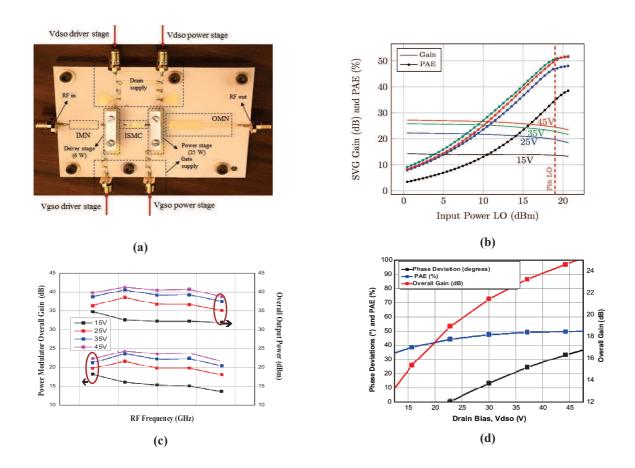

| III.37 | Measured CW quasi-static power performances of the two-stage circuit                                                                                         |

| 111.57 | alone (a) fabricated circuit (b) efficiency and gain variation demonstration                                                                                 |

|        | (c) power characteristics as a function of frequency and (d) phase deviation                                                                                 |

|        | and PAE as a function of drain supply voltage                                                                                                                |

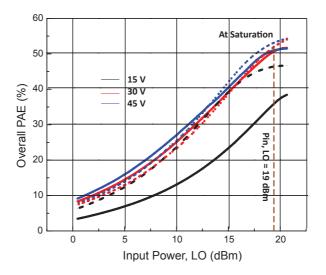

| III.38 | Measured (full lines) and simulated (dotted lines) PAE comparison of the                                                                                     |

|        | two-stage VPM circuit [71]                                                                                                                                   |

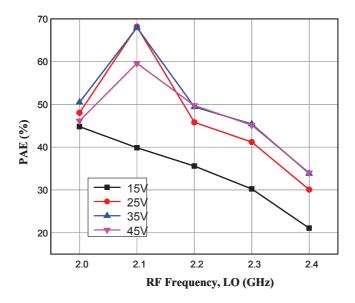

| III.39 | Measured PAE performances of the two-stage circuit as a function of RF                                                                                       |

|        | frequency                                                                                                                                                    |

| III.40 | Final schematic of the compact GaN based Vector Power Modulator circuit .108                                                                                 |

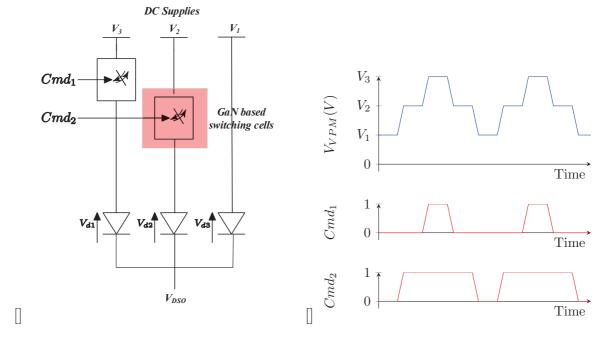

| III.41 | Function of Switching Cells (a) Diode OR logical function implementation                                                                                     |

|        | to the VPM output and (b) Associated output DC envelope corresponding                                                                                        |

|        | to different drain voltages                                                                                                                                  |

| III.42 | Integration of the Two-stage SVGA and architecture of the multi-level                                                                                        |

| III 49 | supply modulator                                                                                                                                             |

| III.43 | Simulated static resistance presented by the power modulator circuit to its drain access for different drain bias voltages with respect to output power. 111 |

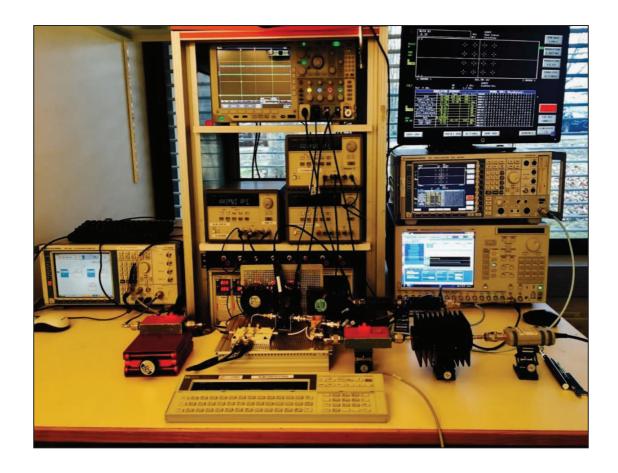

| III.44 | Photograph of the measurement test bench                                                                                                                     |

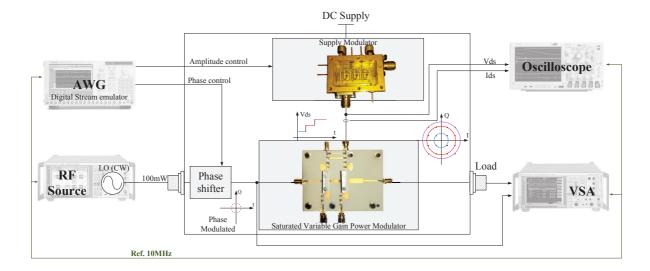

| III.45 | Photograph of the measurement setup and description of the measurement                                                                                       |

|        | bench                                                                                                                                                        |

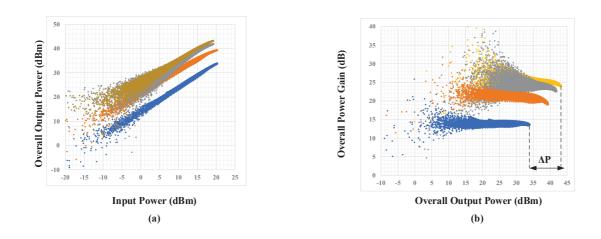

| III.46 | (a) Measured input and output power characteristics and (b) Envelope                                                                                         |

|        | gain variation as a function of output power at 2.2 GHz                                                                                                      |

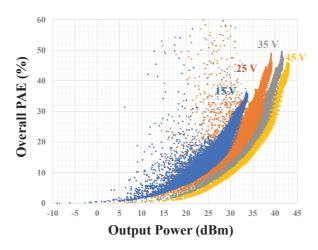

| III.47 | (a) Measured overall PAE at 19 dBm input power LO at $f_c=2.2$ GHz 114                                                                                       |

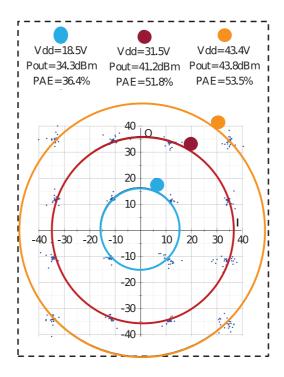

| III.48 | Measured 16-QAM output constellations at a symbol rate of 40 Msym/sec. 115                                                                                   |

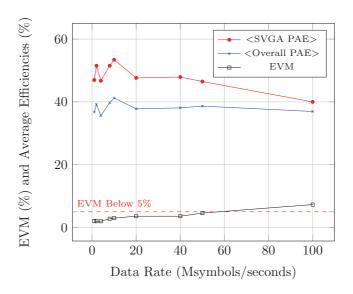

| III.49 | Measured overall average PAE, EVM and PAE of the SVG circuit at 19                                                                                           |

|        | dBm average input power LO at 2.2 GHz                                                                                                                        |

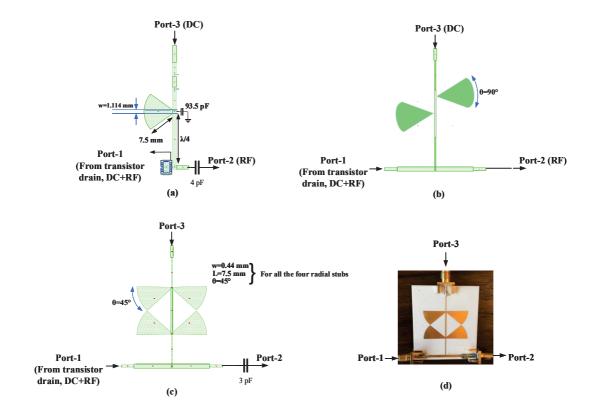

| IV.1   | Modifications of bias network topology (a) conventional bias architecture                                                                                    |

|        | (b) two-radial stub topology (c) modified two-radial stub topology with                                                                                      |

|        | size reduction (d) fabricated circuit                                                                                                                        |

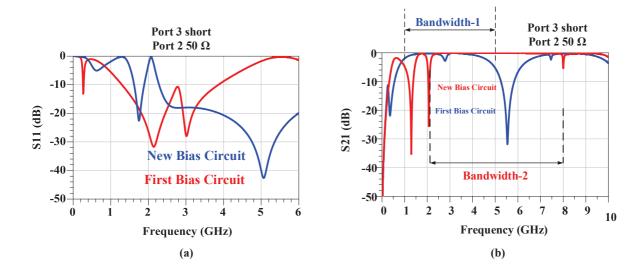

| IV.2   | Simulated S-parameters comparison between both the output bias archi-                                                                                        |

|        | tectures (a) Simulated $S_{11}$ of both the bias circuits (b) Simulated $S_{21}$                                                                             |

|        | response of both the bias circuits                                                                                                                           |

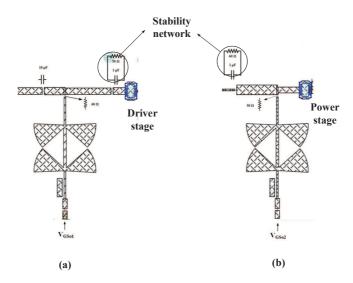

| IV.3   | Implementation of stability networks at the input of (a) driver stage and                                                                                    |

|        | (b) power stage respectively                                                                                                                                 |

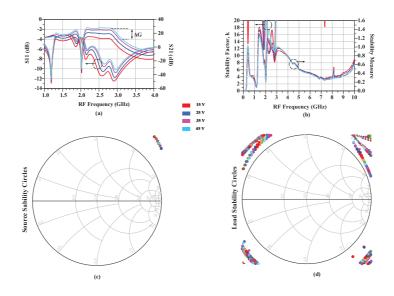

| IV.4   | S-parameters of the new vector power modulator circuit (a) $S_{11}$ and $S_{21}$                                                                             |

|        | (b) Stability factor, k and stability measure (c) Source stability circles                                                                                   |

|        | and (d) Load stability circles                                                                                                                               |

LIST OF FIGURES xv

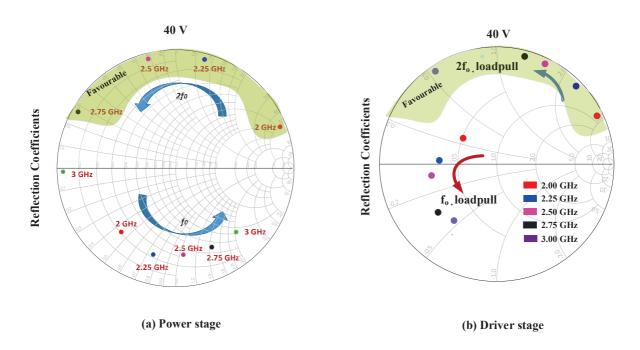

| IV.5         | Location of load impedances for the power and driver as a function of frequency obtained from loadpull simulations                                                                                                                                                                                                                                                     | 194 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TT C         | - v                                                                                                                                                                                                                                                                                                                                                                    |     |

| IV.6<br>IV.7 | Layout of the new two-stage power modulator circuit                                                                                                                                                                                                                                                                                                                    | 125 |

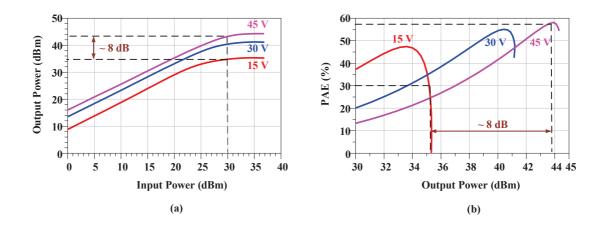

| IV.8         | impedances of the power stage as a function of frequency obtained from loadpull simulations and the impedance trajectory when the inter-stage matching circuit is connected to the two-stage circuit are highlighted Power characteristics of the driver and power stages respectively demonstrating the overall output power variation at center frequency of 2.5 GHz | 126 |

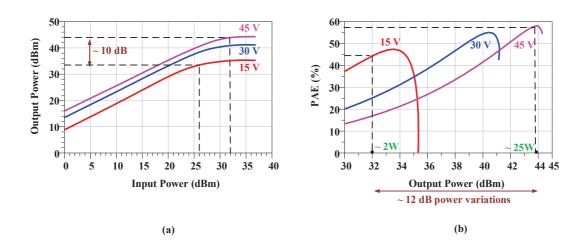

|              |                                                                                                                                                                                                                                                                                                                                                                        | 127 |

| IV.9         | Illustration of the Saturated Variable Gain (SVG) principle for the new power modulator circuit at input power of 22 dBm and at a center fre-                                                                                                                                                                                                                          | 121 |

|              | quency of 2.5 GHz                                                                                                                                                                                                                                                                                                                                                      | 128 |

| IV.10        | Dynamic loadlines of the drain current source of the driver and power                                                                                                                                                                                                                                                                                                  |     |

| TT T 4 4     | stages respectively for the old and new circuits                                                                                                                                                                                                                                                                                                                       | 129 |

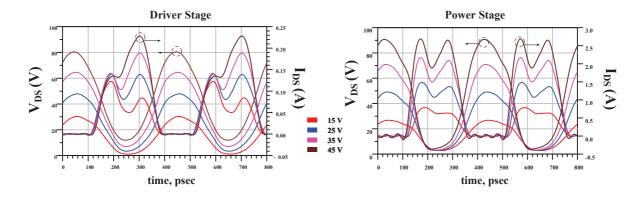

| IV.11        | Intrinsic time domain voltage and current waveforms at center frequency and $P_{in}=22$ dBm for the driver and power stages respectively                                                                                                                                                                                                                               | 130 |

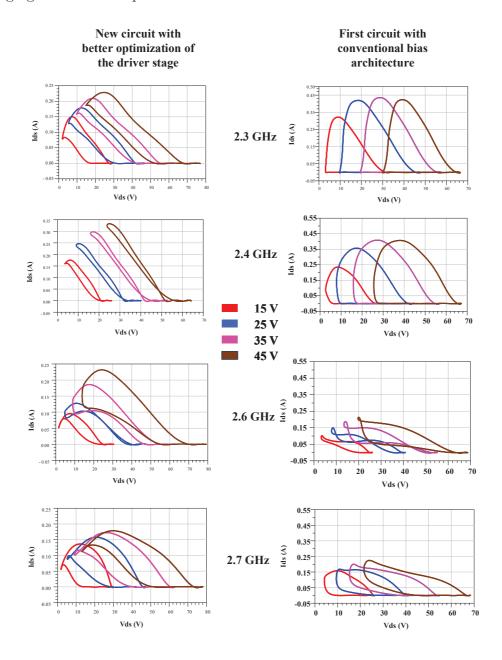

| IV.12        | Comparison of the driver stage current source dynamic loadlines at different frequencies for $P_{in}$ =22 dBm (new circuit), $P_{in}$ =19 dBm (first circuit)                                                                                                                                                                                                          |     |

|              | and 15 V $< V_{dso} < 45$ V                                                                                                                                                                                                                                                                                                                                            | 131 |

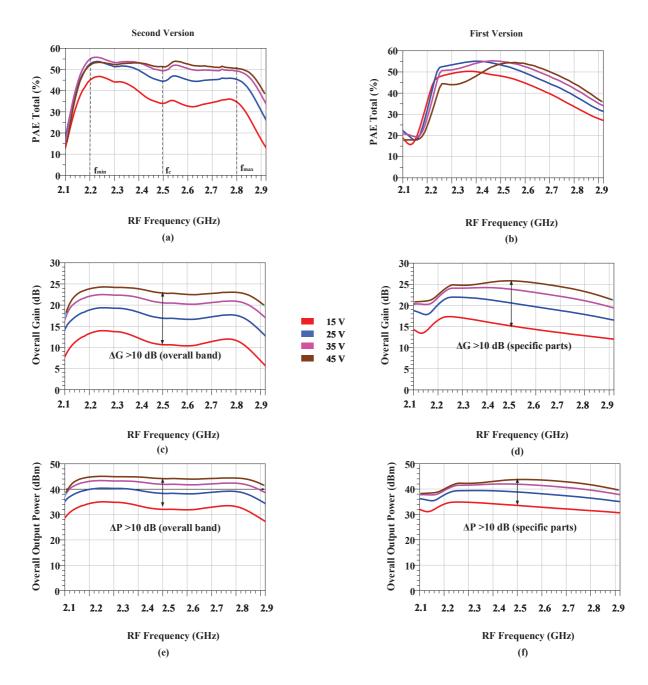

| IV.13        | Comparison of the simulated power characteristics as a function of frequency for the first and second power modulator circuits (a) PAE of the new circuit (b) PAE of the first circuit (c) Overall gain of the new circuit                                                                                                                                             |     |

|              | (d) Overall gain of the first circuit (e) Overall output power of the new                                                                                                                                                                                                                                                                                              |     |

|              | circuit and (f) Overall output power of the first circuit                                                                                                                                                                                                                                                                                                              | 132 |

| IV.14        | 1 1                                                                                                                                                                                                                                                                                                                                                                    |     |

|              | at $f_0=2.5$ GHz                                                                                                                                                                                                                                                                                                                                                       | 133 |

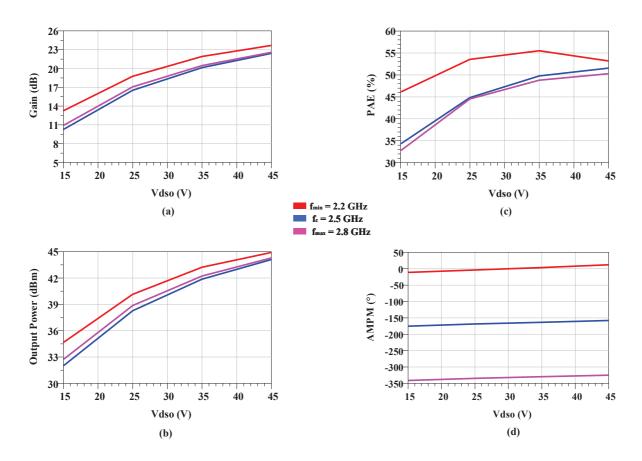

| IV.15        | Power characteristics at different frequency as a function of drain supply                                                                                                                                                                                                                                                                                             |     |

|              | voltage $V_{dso}$ (a) Gain (b) PAE (c) Output power and (d) AM-PM                                                                                                                                                                                                                                                                                                      | 134 |

## List of Tables

| I.1   | Comparison of principal material properties of Silicon, GaAs, GaN and SiC. | 25 |

|-------|----------------------------------------------------------------------------|----|

| I.2   | JFM and BFM values for Silicon and GaN                                     | 27 |

| III.1 | Key characteristics of the GaN transistors selected                        | 75 |

| III.2 | Principal Properties of Rogers RO4350B substrate                           | 77 |

### General Introduction

The process of communication has always been an integral part of the human society. The present era is dedicated to the evolution of modern communications (HDTV's, satellite communications etc) and information processing technologies which has also made human life pleasant and lot more easier. The need for human beings to continuously process information and communicate effectively over remote distances has tremendously led to the boost of mobile telecommunications and wireless industries leading to the rise of sophisticated communication standards over the years starting from GSM in the early 90's up to present research in LTE and beyond for 5G technologies. Due to the never ending demands of the subscribers for frequency flexibility, portability and above all greater wireless connectivity between devices, various communication standards and protocols and services beyond machine-machine learning has led to exponential increase of popularity for personal communications, internet and, recently, the so-called "Internet-of-Things (IoT's)" which is affecting human lives one way or the another.

The processing and transmission of such complex protocols, standards and constantly evolving signal schemes has imposed stringent requirements before the designers to address these issues and make innovative and efficient approaches towards transmitter architectures in terms of signal integrity, bandwidth and above all without compromising the performances in terms of power consumption and signal quality. In this regard, over a decade ago, there was a significant breakthrough in solid state RF power devices based on compound semiconductor technology such as SiC and GaN. Among the various available technologies, GaN because of its high power handling capabilities along with frequency flexibility and higher breakdown voltage has emerged as a very promising candidate for a wide variety of high power transmitter architectures. Several space industries and foundries such as Qorvo, Wolfspeed, Mitsubishi, Nitronex, NXP and UMS among others are constantly maturing in terms of improving the performances of such technologies to make it more viable for various commercial and defence related applications.

One of the most important part of any power transmitter is the RF power amplifier which suffers from the issues arising from the trade-offs between linearity, bandwidth and above all the DC power consumption. The main objective of this thesis work lies in the analysis of technical approaches that make use of signal conditioning and signal controlled power amplification to improve energy efficiency and flexibility of communication transmitters. To achieve this objective, a specific laboratory test bench developed in XLIM laboratory, University of Limoges has been used. Two new two-stage GaN based architectures have been proposed, design and presented that works on the principle of Saturated Variable Gain (SVG) using supply modulation technique. A new biasing architecture to improve bandwidth performances has also been presented as a part of this thesis work.

This thesis is divided into the following four chapters:

The **First chapter** highlights various design issues, challenges and Figures of Merit (FOM's) of communication transmitters. It also presents various potentialities of the GaN transistors used in the design procedure in this thesis and the simplified illustration of the transistor current source and its analysis and impact on communication transmitter design.

The **Second chapter** illustrates the properties of modern complex modulated signals with high PAPR and comments on various advanced transmitter architectures for their efficient amplification. This chapter also explains the limitations of conventional transmitter architectures based on supply modulation technique for the generation of high PAPR power waves and proposes an improvement on such architectures necessary for high power wave generation.

The **Third chapter** presents the design procedure of an high efficiency Vector Power Modulator (VPM) circuit and its simulated and measured performance analysis comparison. In this chapter, the designed circuit and its association with a high speed and efficient supply modulator has also been highlighted and the principle of Saturated Variable Gain (SVG) has been demonstrated.

The **Final chapter** proposes a new biasing architecture and an improved VPM version with investigations on bandwidth enhancement capabilities.

Finally, a general conclusion along with some interesting future perspectives for the extension of this work has been highlighted at the end of this thesis.

## Challenges and Design Considerations in GaN based RF Power Generation

### Contents

| 1 General Context of RF Power Transmitters                | <br>4  |

|-----------------------------------------------------------|--------|

| 1.1 General Requirements for Modern RF Transmitters       | <br>4  |

| 1.2 Microwave Power Transmitter Architecture              | <br>6  |

| 1.3 Issues and challenges in RF Power Amplifiers          | <br>7  |

| 2 Transistor Technology : Gallium Nitride (GaN) $\dots$   | <br>24 |

| 2.1 Why Gallium Nitride?                                  | <br>24 |

| 2.2 General Figure of Merits for GaN Device Selectivity . | <br>25 |

| 2.3 GaN Device Structure                                  | <br>27 |

| 2.4 General Overview of the GaN Devices used in this work | <br>30 |

| 3 Conclusions                                             | <br>33 |

### 1 General Context of RF Power Transmitters

### 1.1 General Requirements for Modern RF Transmitters

A general representation of an RF Power Transmitter chain is illustrated in fig. I.1.

Figure I.1: General Architecture of an RF Power Transmitter Chain (a) Linear case (b) Non-linear case and (c) General power characteristics of an RFPA

The continuous evolution of communication transmitter systems has always been governed by the increase in the complexity of communication signals (from constant-envelope to non-constant envelope signals) starting from GSM (2-G systems) in the beginning upto LTE (4-G systems) currently and beyond (5-G systems).

This has led to the investigations and development of spectral efficient complex modulation techniques like n-QAM. Such modulation techniques lead to non-constant envelope signals having large Peak to Average Power Ratio (PAPR). This main characteristic is the cause of higher sensitivity to different sources of distortions and more power consumption.

To maintain the signal integrity, conventional power amplifiers, PA (which are the most power consuming in a transmitter) are generally operated at power back-off levels which leads to poor average efficiency (case of fig. I.1 (a)). This implies that modern PAs must be specially designed for high PAPR signals for providing efficient operation at average power levels [1]. If power amplifiers operate in their saturation region to improve PAE performances (case of fig. I.1 (a)). Then the signal reaches its peak power and the non-linear behaviour of the RFPA leads to spectral regrowth and poor linearity performances. Basically a digital predistortion technique must be implemented to meet the linearity requirements. This has also forced the designers to put forward a cost-effective, reliable, portable and light weight equipment for efficient transmission with main focus on the compactness of the different analog segments, power and frequency flexibility, and minimizing the energy consumed under the stringent constraint of acceptable signal integrity (linearity).

The compactness and ease of integrating complex modulation and energy conversion functions and their co-design within the transmitting part of a communication system is the principle idea on which the development of this thesis is focused.

This idea is furthermore associated with three fundamental parameters that have to be accommodated as far as the designing aspect is concerned:

Efficient DC-RF energy conversion at average power levels over wide frequency bandwidth maintaining an acceptable amount of signal linearity with minimum DC power consumption for complex modulated signals.

The flexibility of a transmitter implies a relatively wide band functional operation to address multi-standard or multi-function applications. It induces the need to jointly take into account various functions such as amplification, filtering and signal conditioning for the design of the RF power generation function at the transmitter.

Miniaturization in the presence of high power levels (of the order of ten watts) induces an essential factor which is the power density of active devices and the increase in operating frequencies. Furthermore, wideband functions are required instead of multi-channel bands.

With extensive research over past few years, Gallium Nitride (GaN-HEMT) technology has emerged as a potential candidate for high frequency and high power applications because of numerous advantages over its existing counterparts such as Si-LDMOS like high power density, higher breakdown voltage. GaN technology is more attractive for wideband power amplifier design and can result in smaller circuits or design sizes for the same amount of output power.

In this general context, this chapter highlights the description and basic considerations in RF power generation process employing GaN devices suitable for RF power transmitters. The chapter also highlights the main characteristics and performance criteria of power transistors and power amplifiers. The issue of the trade-off between various figures of merit has also been addressed.

Finally, the chapter is concluded with the addressing of the main characteristics of GaN technology suitable for high efficiency and high power amplifier design.

#### 1.2 Microwave Power Transmitter Architecture

Fig. II.2 illustrates a basic block diagram of an RF power transmitter.

Figure I.2: General Architecture of RF Power Transmitter Chain

In the overall transmission chain, the RF power amplifier (RFPA) is the main source of DC power consumption. Any power amplifier converts the DC power supplied into output RF signal power. An ideal RF Power Amplifier can hence be defined as a transducer that converts DC power to useful RF power under the influence of an RF input signal. Traditionally, the design of power amplifiers predominantly focuses on the main power stage and the gain requirement is usually met by adding linear gain elements (drivers) before the amplifier (Fig. II.2). These driving stages are made linear in order to maintain the overall linearity of the power amplifier [2].

Concerning the RF power amplifier, if efficiency is not optimized, a great amount of DC consumption is dissipated into heat and thermal management of the system is more complex along with a significant increase in the cost of products.

Good efficiency is obtained when transistors operate at saturation which is prejudicial for linearity. A trade-off always exists between power efficiency performances and linearity when power back-off is applied. However, the most challenging aspect today is to propose solutions that enables the optimization of both efficiency and linearity rather than to find acceptable trade-offs. Moreover, PA operating over wide frequency bandwidths are required. All that makes PA design a major challenge in RF transmitter chain.

### 1.3 Issues and challenges in RF Power Amplifiers

### 1.3.1 Basic Architecture of an RF Power Amplifier