# Analysis and modeling methods for predicting functional robustness of integrated circuits during fast transient events

Rémi Bèges

# ► To cite this version:

Rémi Bèges. Analysis and modeling methods for predicting functional robustness of integrated circuits during fast transient events. Electromagnetism. Université Paul Sabatier - Toulouse III, 2017. English. NNT: 2017TOU30046 . tel-01811079

# HAL Id: tel-01811079 https://theses.hal.science/tel-01811079

Submitted on 8 Jun 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

Thèse CIFRE présentée et soutenue le 2 juin 2017 par : RÉMI BÈGES

Analysis and modeling methods for predicting functional robustness of integrated circuits during fast transient events

Geneviève Duchamp Pascal Nouet Alain Sauvage Frederic Lafon Fabrice Caignet Patrice Besse Marise Bafleur Patrick Austin JURY

Professeur d'Université Professeur d'Université Docteur Docteur Maitre de Conférence Docteur Professeur d'Université Professeur d'Université

Membre du Jury Membre du Jury

### École doctorale et spécialité :

GEET : Électromagnétisme et Systèmes Haute Fréquence

Unité de Recherche :

Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS-CNRS - UPR 8001) Entreprise CIFRE :

NXP Semiconductors Toulouse

## Directeurs de Thèse :

Fabrice Caignet, Patrice Besse et Marise Bafleur

#### **Rapporteurs** :

Mme. Geneviève Duchamp et Mr. Pascal Nouet

# Contents

| Introduction 7 |     |         |                                                                           |    |  |

|----------------|-----|---------|---------------------------------------------------------------------------|----|--|

| 1              | Rev | view of | ESD testing and functional analysis                                       | 13 |  |

|                | 1.1 | Conte   | xt                                                                        | 13 |  |

|                |     | 1.1.1   | Electrostatic discharge                                                   | 13 |  |

|                |     | 1.1.2   | Impact of ESD on electronic devices                                       | 14 |  |

|                |     | 1.1.3   | ESD protection                                                            | 17 |  |

|                | 1.2 | Review  | w of $\overrightarrow{\text{ESD}}$ testing                                | 20 |  |

|                |     | 1.2.1   | Transmission Line Pulsing (TLP)                                           | 20 |  |

|                |     | 1.2.2   | ESD Gun (IEC 61000-4-2 / ISO 10605)                                       | 24 |  |

|                |     | 1.2.3   | ISO 7637-2                                                                | 26 |  |

|                |     | 1.2.4   | IEC 61000-4-4                                                             | 30 |  |

|                |     | 1.2.5   | IEC 62215 standard                                                        | 31 |  |

|                | 1.3 | Review  | w of soft-failure silicon-level investigation                             | 33 |  |

|                |     | 1.3.1   | Case studies                                                              | 33 |  |

|                |     | 1.3.2   | Observation methods                                                       | 36 |  |

|                |     | 1.3.3   | Modeling methods of soft-failures for integrated circuits $\ldots \ldots$ | 40 |  |

| <b>2</b>       | Dev | velopm  | ent of investigation tools                                                | 43 |  |

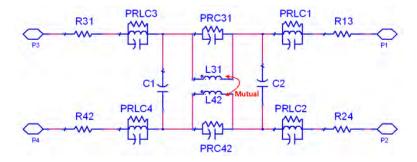

|                | 2.1 | System  | n-level ESD modeling method                                               | 43 |  |

|                |     | 2.1.1   | Transmission line                                                         | 44 |  |

|                |     | 2.1.2   | Passive devices                                                           | 50 |  |

|                |     | 2.1.3   | ESD protections                                                           | 52 |  |

|                |     | 2.1.4   | Common mode filter                                                        | 56 |  |

|                |     | 2.1.5   | Ferrite beads                                                             | 56 |  |

|                | 2.2 | Model   | ing method application to a TLP generator                                 | 58 |  |

|                | 2.3 | Develo  | opment of a new injection tool                                            | 62 |  |

|                |     | 2.3.1   | Motivation                                                                | 62 |  |

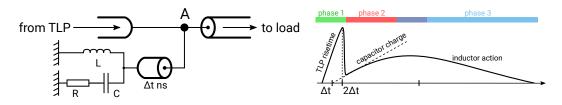

|                |     | 2.3.2   | Principle of operation of the TLP-HMM                                     | 64 |  |

|                |     | 2.3.3   | Validation of TLP-HMM models and standard compliance                      | 67 |  |

|                |     | 2.3.4   | Conclusion, limitations and future improvements                           | 72 |  |

|                | 2.4 | Near-f  | field sensor post-processing                                              | 72 |  |

|                |     | 2.4.1   | Time-domain integration method                                            | 72 |  |

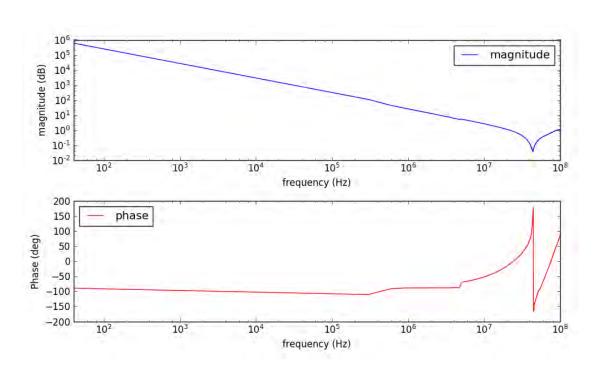

|   |                  | 2.4.2 Frequency-domain reconstruction method                   | $d \ldots \ldots 74$                                  |  |

|---|------------------|----------------------------------------------------------------|-------------------------------------------------------|--|

|   |                  | 2.4.3 Conclusion on near-field post-processing                 | g                                                     |  |

|   | 2.5              | Conclusion                                                     |                                                       |  |

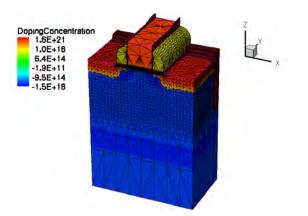

| 3 | $\mathbf{Stu}$   | y of soft-failures at silicon-level                            | 81                                                    |  |

|   | 3.1              | Study of a real product                                        |                                                       |  |

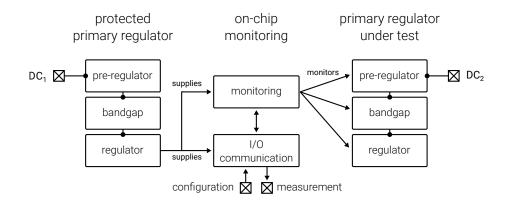

|   |                  | 3.1.1 Product description                                      |                                                       |  |

|   |                  | 3.1.2 Functional failure study                                 |                                                       |  |

|   | 3.2              | Test vehicle                                                   |                                                       |  |

|   |                  | 3.2.1 Test vehicle description                                 |                                                       |  |

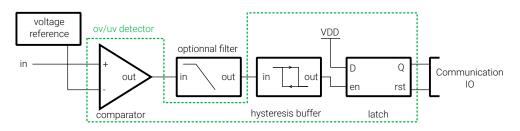

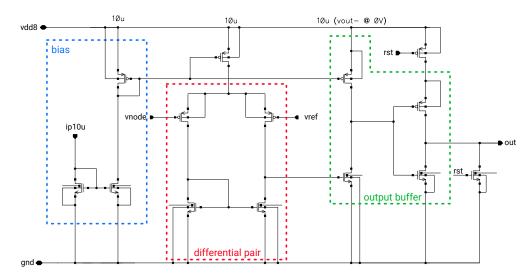

|   |                  | 3.2.2 Voltage monitoring                                       |                                                       |  |

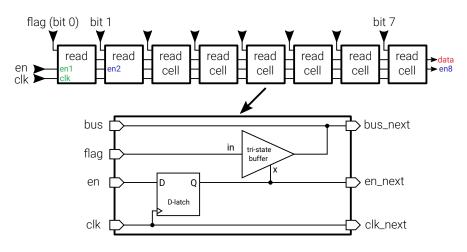

|   |                  | 3.2.3 Communication system                                     |                                                       |  |

|   |                  | 3.2.4 On-chip near-field current sensors                       |                                                       |  |

|   |                  | 3.2.5 Topcell                                                  |                                                       |  |

|   |                  | 3.2.6 Test boards $\ldots$                                     |                                                       |  |

|   |                  | 3.2.7 Test vehicle verification and testing afte               | er manufacturing 97                                   |  |

| 4 | Mo               | eling methods for functional robustness                        | prediction 101                                        |  |

|   | 4.1              | Intra-chip block modeling                                      | 103                                                   |  |

|   |                  | 4.1.1 Block failure characterization and mode                  | eling method $\ldots \ldots \ldots \ldots \ldots 103$ |  |

|   |                  | 4.1.2 Block models chaining                                    |                                                       |  |

|   |                  | 4.1.3 Application to the test vehicle                          | 109                                                   |  |

|   |                  | 4.1.4 Limitations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |                                                       |  |

|   |                  | 4.1.5 Proposed workaround                                      |                                                       |  |

|   |                  | 4.1.6 Final conclusion and follow-up work .                    |                                                       |  |

|   | 4.2              | Black box modeling approach                                    |                                                       |  |

|   |                  | 4.2.1 Function failure model                                   |                                                       |  |

|   |                  | 4.2.2 Electrical pin models                                    |                                                       |  |

|   |                  | 4.2.3 Conclusion on black-box modeling                         |                                                       |  |

| С | onclu            | sion                                                           | 135                                                   |  |

| A | ppen             | lices                                                          | 141                                                   |  |

| A | $\mathbf{TL}$    | modeling                                                       | 143                                                   |  |

|   |                  | Validation curves                                              |                                                       |  |

| В | Bot              | om-up block characterization and modeli                        | ing 147                                               |  |

|   | B.1              | Characterizations                                              |                                                       |  |

|   | B.2              | Improved model chain versus reference                          |                                                       |  |

| С |                  | k box modelling                                                | 153                                                   |  |

|   | C.1              | Additional validations                                         |                                                       |  |

| B | Bibliography 155 |                                                                |                                                       |  |

# Acronyms

# Introduction

Integrated circuits miniaturization is still ongoing nowadays allowing increasingly massive integration of electronic functions. An integrated technology is the definition of the dimensions and processes required to manufacture an integrated circuit and its fundamental conception bricks. The main characteristic of a technology is the feature size called  $\lambda$  that represents the smallest dimension for a transistor gate. Size reduction of integrated circuit is mainly accomplished by decreasing this feature size. All other dimensions of the technology are defined as an integer multiplication factor of  $\lambda$ . The value of  $\lambda$  determines the size, power consumption, switching speed, performance and many other properties of a chip. So far, Moore's law successfully predicted that technology dimensions will be reduced by a factor of two every 18 months. The automotive world follows this trend as well, moving recently to 16 nm technology nodes (see Fig. 1) [1] that are normally employed in less demanding applications.

Reduction of  $\lambda$  results in more massive integration on a given silicon surface. The area occupied by a function on silicon is the main cost factor. Reducing this area allows to diminish the unit manufacturing cost resulting in increased profits and margins. For the same area, integrated circuits in more recent technologies can pack more functionalities with higher performances. Weight reduction of electronic modules in automotive or aerospace lowers fuel consumption, and reduces the impact on the environment.

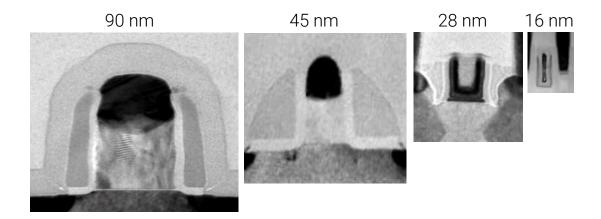

Figure 1: Recent evolution of NXP's automotive technology nodes [1]

The decrease of  $\lambda$  results in reduction of insulating material's thickness. Transistor gate oxide becomes thinner, tolerating lower electrical fields before breakdown. After breakdown, the oxide starts leaking significant amount of currents and the transistor becomes unusable. As a result, the technology provides more sensitive conception bricks and a larger silicon area must be dedicated to protecting the core circuitry [1].

New major trends are also emerging in the automotive field. The development of fully autonomous driving is seeing tremendous progress. This class of functionalities take decisions and perform critical actions such as braking or steering the wheel. Those features are developed to offer increased safety for the user. A side consequence is that electronic modules now have very high responsibilities. The real-time constraint is particularly important, meaning that electronic circuits must perform their duties without delay and operate correctly all the time. For instance, an airbag system must always be ready to trigger in case of car accident without any delay. Electric cars raise new challenges for safety as well, such as battery management. Those features require more computing power, more sensing capabilities and more data to exchange. As a consequence, the amount of Engine Control Unit (ECU)s and electronic modules in a car is growing quickly. Communication buses like the Controller Area Network (CAN) [2] or Local Interconnect Network (LIN) [3] are shared by multiple systems and new standards appear for supporting higher bandwidths. The CAN bus with Flexible Data rate (CAN-FD) is an example of this trend.

The automotive environment is quite harsh for electronic devices and equipments are exposed to a wide range of stresses. A running engine generates plenty of vibrations and mechanical stress. A lot of heat and thermal cycling is produced when the engine is on, and a vehicle is exposed to large temperature variations during its lifetime. Electrical contacts, solder joints and connections suffer from these stresses, and must be designed to withstand them. Electronic system are also exposed to a wide range of electrical stresses especially in the automotive field. Transient disturbances can be generated by natural phenomena or by the vehicle itself. When the engine is turned on, the battery voltage can drop very low due to the amount of current drawn by the ignition. This voltage drop can affect electronic systems and damage them. Another major source of electrical stress is called the Electro-Static Discharge (ESD).

An electrostatic discharge is the sudden flow of electricity between two objects of different charge. It is the result of a local accumulation of electrostatic potential. When a large enough potential difference is reached, a very rapid and large discharge occurs. It is common to record amplitudes in the range of thousands of volts and tens of amperes. A study by Renault car manufacturer [4] estimates that electronic devices are exposed 10000 times to ESDs during their lifetime. It has always been considered a very serious threat for electronic systems.

In terms of architecture, a vehicle is constituted by a multitude of electronic modules interconnected by cables. Interconnected electronic systems need to share a good ground reference for them to communicate and work properly. The car's metallic body is the ground reference for all electronic modules, because a good connection to Earth is impossible inside a vehicle. Electronic modules and the battery are all linked to the car's body using wires and cables. In D.C. and at low frequencies, this ground connection is good because the vehicle's body is a very large chunk of metal with a very low resistance. At high-frequencies though, those cables have an inductive behavior. They oppose to variations of currents and exhibit large potential differences. Local disturbances can shift the ground reference between one module an another. Electrostatic discharges are high frequency events of very large amplitude and can cause disturbances like this. Inside a vehicle, the discharges can propagate inside cables by conduction, or by coupling between cables through radiated emission. Electronic modules are designed to be robust but the complex architecture and the very harsh nature of ESD makes challenging to guarantee immunity.

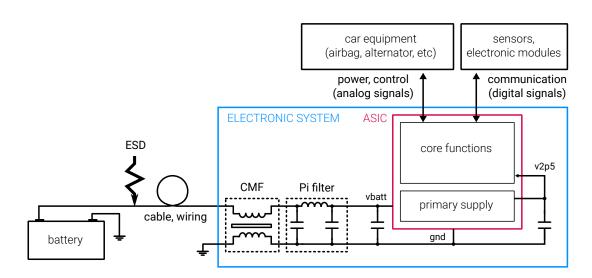

Figure 2: Architecture of electronic systems in a vehicle [5]

In summary, electronic devices must operate in severe automotive environment while using more sensitive conception bricks. Despite the robustness of modules, disturbances such as electrostatic discharges can cause failures. In the ESD field, there are two kinds of failures to consider. The hardware failure, or hard-failure, is when an electronic device is permanently damaged [6]. Destruction can occur through oxide breakdown, when a too large voltage is applied on an insulating material. It can also occur through thermal breakdown, when current through a structure is too high and causes a meltdown. Recently, a new class of failures is being studied. Soft-failure, or functional failure, is when an electronic device fails temporarily to perform its function, because of an electrical disturbance. Different levels of severity can be identified depending on the impact of the failure on the rest of the system. A module that is momentarily disturbed by a discharge but recovers immediately is less severe than a module that requires user intervention. Also, failures on the airbag system are much more severe than on the entertainment system, because user safety is put at risk in the first case. A first article on the topic was published by F. Caignet and N. Lacrampe in 2007 [7]. A large amount of research at the system level was published in EOS/ESD symposium 2012 [8, 9, 10] and 2013 [11, 12]. The draft standard IEC 62433-6 [13] aims to provide a base framework for soft-failures analysis and prediction. Analysis of the literature reveals that most studies are currently focused on system-level soft-failure analysis. There is currently no real work at the component level or studies performed inside the design of an integrated circuit.

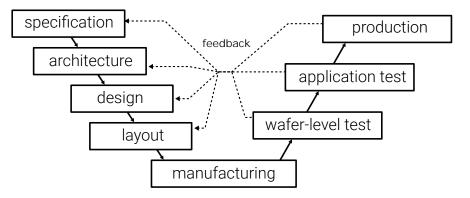

Beyond studying failures inside integrated circuits, it is important to keep in mind how chips are designed and developed. This is important to propose solutions that are actually implementable. This entire process from the specification to the manufacturing of a product is called the design flow (see Fig. 3). During this process, there are many teams and people involved. Modeling team creates electrical model of technology components. Design team assembles component together to create integrated functions that conform to the specification. Layout team translates the electrical schematic into the series of masks and layers required by manufacturing. The laboratory tests manufactured parts and runs investigations in case of failures. The ESD and Electro-Magnetic Compatibility (EMC) team has the particularity to interact will all teams because issues and solutions can be found in any step of the design flow. The main source of delay in this process is the manufacturing time which can be of several months. Designs are put on silicon but the parts are tested only after manufacturing, several months later. To gain time to market and be competitive, it is essential to reduce the number of design-manufacturing-testing cycles. Each additional manufacturing is very expensive, and increases further the development time of the product. This is why any simulation tool able to predict early any kind of failure (and functional failures among them) is very valuable for silicon design companies.

Figure 3: Simplified integrated circuit design flow

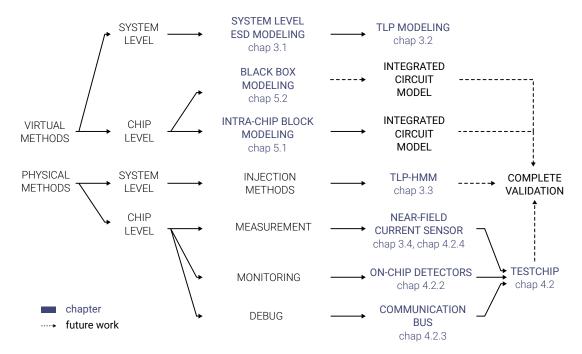

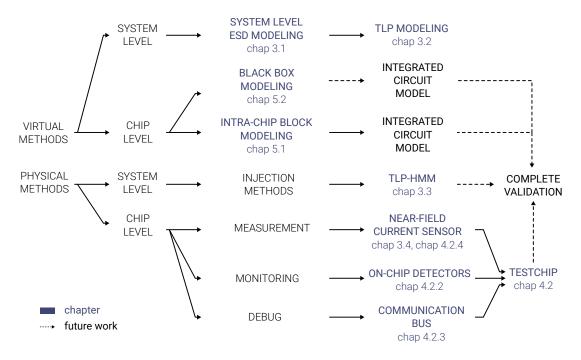

It was demonstrated that real-time electronic circuits have higher responsibilities yet they can be disturbed by disturbances such as electrostatic discharges. It is essential to understand how failures appear in order to fix them and prevent them prior to manufacturing. For this purpose, many approaches and methods were explored and detailed in this document. Fig. 4 shows the different paths taken during the research, all studied in parallel with the ultimate goal to develop and validate integrated circuit models for soft-failures. Among all proposed approaches, a modeling method of electronic systems exposed to electrostatic discharge is developed, improving prior work on the topic [14, 15]. It helps determining what fraction of an incoming discharge reaches the integrated circuit. Then, on-chip measurement methods have been designed and manufactured, in order to acquire more data inside the chip. Those methods comprise monitoring devices such as an on-chip current sensor, overvoltage and undervoltage detectors, and a communication chain for fast prototyping. Finally, modeling methods were experimented using simulation tools. The first method models each block function individually, then offer to chain and combine models together to deduce the robustness of a complete top-level function. The second method aims to build an electrical equivalent model of the integrated circuit, for system-level simulations. Black box modeling that abstract the internal design using only the external behavior is used. Finally, a concept of an assertion system is detailed, to identify quickly and efficiently during preliminary design phase the potential weakness of an integrated circuit.

Figure 4: Explored research paths for soft-failure investigation and prediction

Chapter 1 details what is an electrostatic discharge and how to reproduce it in laboratory conditions. This preliminary work highlights how functional failures appear and how they impact electronic devices. The literature about ESD-induced soft-failures is reviewed. It is demonstrated that so far that most of the studies are focused at the system level, and that it remains very challenging to identify failure root cause without access to the chip design.

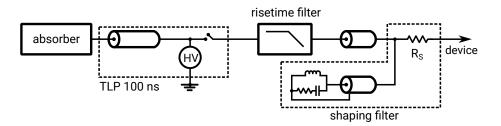

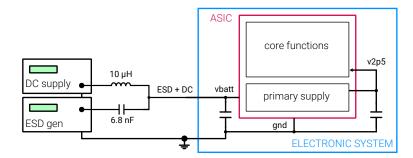

Chapter 2 presents a modeling method for simulating ESD waveforms up to the integrated circuit inputs. The first challenge for understanding soft-failures at siliconlevel is to determine what fraction of an incoming ESD actually reaches the integrated circuit. Between the injection point of a stress and the disturbed circuit, many devices are connected such as cables, discrete devices, etc. Each element interacts with the discharge, absorbs a part of its current or changes the waveform. A model library of common electrical elements found in ESD testing environment has been constructed and is detailed. The modeling method is applied to a complex pulse generator, and yields a highly accurate model. Finally, a new test generator was developed to overcome some issues met during the debug of silicon-level failures using system level ESD testers [16, 17]. The principle of operation and architecture of the generator is described. It produces the same compliant waveform than those standards, with some advantages such as increased testing reproducibility and zero radiated emission.

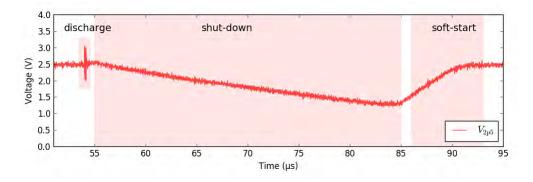

A case of soft-failure in an integrated circuit is explained in chapter 3. In a first phase, measurement data is obtained at the application board level and the failure is explained. Simulations are run to understand how failures appear, and more specifically how a short electrical event can disturb an integrated circuit for a long period of time. In a second phase, the integrated function is placed onto a custom testchip. Specific on-silicon structures were designed to gather measurement data on electrical nets that are not physically accessible. All these measurements are performed for the purpose of estimating the accuracy of integrated circuit ESD simulations. There are two main potential sources of error that are checked. Silicon technology device models are not designed to function for extremely fast transient transient disturbances. Also, standard simulations do not take parasitic devices into account, such as metal track resistances and parasitic couplings. Measurement data is confronted to simulations in order to verify the validity of models. Analysis of the failure led to the development of a testchip, to put on silicon the same failing function but with a more convenient environment for measurement and investigation.

When issues are discovered late in the testing lab, analysis is performed manually, by trial and error, searching inside the design why the function is failing. It is a complex and time-consuming process. The core research of this work focuses on proposing new analysis methods and tools for electrical simulations. It is detailed in chapter 4. The first method offers to study and model block functions individually, then connect the models together to deduce the robustness of a top-level function. The second method targets system-level simulations comprising integrated circuit. It focuses on modeling an integrated function with a behavioral model that is not aware of the internal design, in order to run powered ESD simulations. Finally, a concept is presented for easing the search of soft-failures during integrated circuit development. It is based on using a assertions inside the blocks to efficiently and quickly find which function or net is being disturbed due to an ESD.

The final conclusion summarizes the work achieved during the PhD, highlights the most notable discoveries, and identifies follow-up work and research topics that could be worth pursuing.

# Chapter 1

# Review of ESD testing and functional analysis

# 1.1 Context

#### 1.1.1 Electrostatic discharge

An electrostatic discharge (ESD) is the result of the accumulation of electrostatic potential. It is a very sudden current flow that propagates through metallic or non-metallic materials, electrical systems and sometimes even through the air. It is a very short electrical event, involving large currents, extremely high voltages, and durations in the range of a few hundred nanoseconds. Currents can reach tens of amperes and voltage levels several thousand of volts. The total discharge energy is small, somewhere near the millijoule (mJ). The power on the other hand is extremely high because the waveforms are changing extremely rapidly.

Objects can accumulate electrostatic potential by tribocharging or electrostatic induction. In the case of tribocharging, electrons are transferred from one object to the other when they are put into contact and then separated. One object becomes positively charged and the other negatively depending on the kind of material constituting each one. Nature of common materials in that regard is given in Table 1.1

Field induction, also called electrostatic induction, works differently but also results in accumulation of electrostatic potential. When a piece of material is placed inside an electric field, positive and negative charges of the material become spatially separated, at a macroscopic scale. If the object is temporarily grounded in one point, charges near that location are evacuated, in majority positive or negative. Similarly to tribocharging, electrostatic induction causes the material to loose its electrical neutrality.

Tribocharging happens constantly when a vehicle is in motion [19]. It occurs because of the friction of the tires on the road surface, which is a constant contact followed by separation mechanism. Therefore, static electricity accumulates constantly inside a vehicle, until a discharge happens.

Triboelectrification may also happen between a human body with clothing and the

| $\uparrow$ Positive   | Rabbit fur                   |

|-----------------------|------------------------------|

|                       | Glass                        |

|                       | Mica                         |

|                       | Human Hair                   |

|                       | Nylon                        |

|                       | Wool                         |

|                       | Fur                          |

|                       | Lead                         |

|                       | Silk                         |

|                       | Aluminum                     |

|                       | Paper                        |

|                       | Cotton                       |

|                       | Steel                        |

|                       | Wood                         |

|                       | Amber                        |

|                       | Sealing Wax                  |

|                       | Nickel, copper brass, silver |

|                       | Gold, platinum               |

|                       | Sulfur                       |

|                       | Acetate rayon                |

|                       | Polyester                    |

|                       | Celluloid                    |

|                       | Silicon                      |

| $\downarrow$ Negative | Teflon                       |

Table 1.1: Typical Triboelectric Series (Credit: ESDA [18])

seat fabric, eventually leading to an electrostatic discharge. The probability of discharge is rather low [19] and the phenomenon can be only be observed in rare situations when the human body leaves the vehicle.

Similarly, triboelectrification can also occur between the vehicle's body and the airflow generated by the motion. More specifically, it is not the air itself but the dirt particles carried in it that induce the contact and separation process. The ESDA indicates that virtually all materials can be triboelectrically charged [18] as long as the contact and separation process exists.

## 1.1.2 Impact of ESD on electronic devices

As detailed in the introduction, electrostatic discharges constitute a large threat for electronic devices. Failures can occur during manufacturing or normal operation. The manipulation of parts by manufacturing machines involves repeated contact and separation. Ultimately, triboelectrification and discharges happen and devices can get destroyed. Several standards exist to guarantee that devices can survive this manufacturing step.

The Human Body Model (HBM) reproduces the discharge of a human body into a device. It is standardized in Method 3015.9 of MIL-STD-883 [20] and JEDEC JS-001-2014 [21]. The charged human body is modeled by a 100 pF capacitor and a discharge resistor of  $1.5 \,\mathrm{k\Omega}$ . Charging voltages reach a maximum of  $8 \,\mathrm{kV}$ , although nowadays customers tend to ask for less than that.

The Charged Device Model (CDM) is a field-induced ESD test. The component under test is placed between two charging plates that generate an electric field. At some point, a grounded pin is brought near any of the pins of the component, forcing the charges to evacuate suddenly. This test is standardized in [22].

The Machine Model (MM) used to be another ESD testing specification that is now considered deprecated. The JEDEC committee recommended discontinuing use of this standard [23], because it is the result of a misunderstanding of real-world events in manufacturing environments. It does not help improving the reliability of devices against electrostatic discharges.

Those three tests (HBM, CDM, MM) aim to guarantee that the devices can survive their manufacturing environment qualified as Electrostatic Protected Area (EPA). An EPA area involves special hardware such as anti-static wrist wraps or special carpet materials to avoid the accumulation of electrostatic potential and electrostatic discharges.

Over the years, manufacturing processes and standards have been improved, reducing the requirements of discharge levels to sustain. In parallel, the factory environment has been studied extensively to identify actual levels devices are exposed to. Machine Model deprecation is the perfect illustration of increased community knowledge and experience. Those efforts aim to reduce the pressure on semiconductor manufacturers that are facing growing challenges to protect devices, because of the shrink of technologies and robustness.

After manufacturing, failures can happen with the device in its operating environment. Manipulation by electrically-charged humans is a major source of danger for commercial products like cellphones and cameras. The automotive environment is even harsher, with vehicles being a major source of electrostatic discharges.

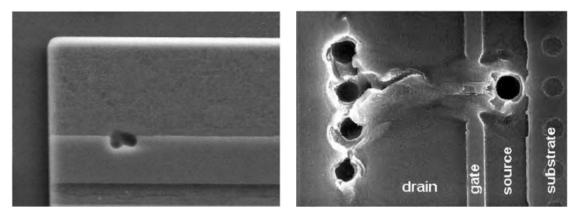

The electrical destruction of a device is called a hard-failure. A hard-failure corresponds to changes in the material structure or properties of a device to the point where it no longer fulfills at least part of its specification. ESD induce those failures because of the extremely large current densities, high voltages, and power levels involved. Different kinds of failure signatures can be observed. Pictures of destroyed devices, obtained with an electronic microscope, are provided in Fig. 1.1.

A first kind of common failure for integrated devices is the oxide breakdown. Oxide breakdown happens when an insulating material is exposed to a larger electric field than it can tolerate. A picture of the oxide of a device destroyed because of an electrostatic discharge is provided in Fig. 1.1. During an ESD, large voltage variations in a short amount of time result in very large electric fields. Oxide breakdown happens usually with the insulator constituting the gate of a Metal-Oxide Semiconductor (MOS) transistor.

# oxyde breakdown

# thermal breakdown

Figure 1.1: Example of ESD induced failures at silicon-level (From [24])

As technologies shrink, so does transistor gate oxide thickness. After the failure, the gate that is normally insulated from the rest of the device leaks significant amount of current. The transistor can no longer operate and is considered destroyed.

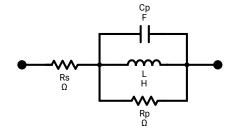

Thermal breakdown is another kind of ESD induced failure. It is the result of an elevation of temperature inside the silicon, above its melting point. It is caused for long discharges that can induce significant and very localized device heating. It results in a significant increase of leakage current or apparition of short-circuits.

Finally, metal melting is the last kind of failures observed after a discharge. Inside an integrated circuit, metal tracks are rather resistive because of their form factor. Resistivity sits in the range of  $10 \text{ m}\Omega \square^{-1}$  to  $100 \text{ m}\Omega \square^{-1}$ . When large currents are flowing, metal tracks and vias dissipate power and heat up. The elevation of temperature, if large enough, can melt the metal track and turn it into an open-circuit.

Integrated circuits are studied and protected against hard-failure since a few decades. Despite this experience of the ESD community, it remains challenging to perfectly protect an electronic system against hard-failures. Nowadays, a new class of failures appears. Instead of studying permanent failures, devices are studied for temporary failures affecting their functionality. These are called soft-failures or functional failures. ESD can cause them to happen, with diverse consequences. In less severe situations, functionality of a chip is disturbed just for the duration of the ESD and recovers immediately without noticeable consequence. The failure remains located inside the integrated circuit and does not impact the application above. Sometimes, the discharge is harmful enough to cause a circuit to restart because the ESD disturbed some critical nets or parameters. This is common when supply voltages go out of specification for instance. Startups or power-on reset functions can interpret overvoltage or undervoltage caused by disturbances as the signal for a regular power-up sequence. The device can also perform restarts to try a recovery because proper operations cannot be guaranteed, due to unexpected values on some nets. Most microcontrollers for instance monitor supply voltages of digital gates. If the voltage is too low, the noise margins of the gates cannot be guaranteed and proper operation either. At this point, the microcontroller restarts in an attempt to recover normal operation. Restarts are slow processes compared to the operation of a chip. For critical applications, this delay is highly unwanted because it impacts human safety. The availability of the chip that triggers airbags in a car is vital for instance. In a more severe scenario, the system gets completely frozen or stuck into an unwanted state because of the ESD. The only way to recover normal operation requires a user-intervention. User intervention can take the form of turning the key to shut down and restart the vehicle's engine. Finally, hard-failure can be seen as the next step immediately after the most severe soft-failure. The device is in a non-recoverable state and must be replaced. Hard-failures are not considered for functional robustness analysis.

In this context, soft-failures represent a risk just as important as hardware failures. To limit risks and costs inherent to upgrading a device after it was deployed in the field, these failures must be taken care of as early as possible. Ideally, the robustness of an electronic product should be studied, characterized or simulated during its design phase. The research conducted and presented in this document aims to develop new tools and techniques for studying and predicting functional failures.

To protect sensitive electronics against discharges, several options are available. The most common solution, presented in the next section, is the ESD protection.

#### 1.1.3 ESD protection

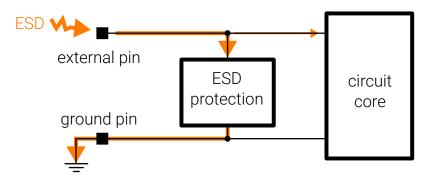

ESD protections divert discharge current before it reaches sensitive circuitry. By offering a low impedance path to ground, they clamp input voltages to avoid crossing the maximum accepted levels. Fig. 1.2 gives a simple example of ESD protection strategy. Current is routed into the ground before reaching the core circuitry. Protections have very low on-resistance, usually in the order of a few ohms. Even with a few amperes of current, voltage remains low. ESD protections can absorb significant amounts of current for very short periods of time, but they are not designed to sustain DC currents.

Figure 1.2: Classic ESD protection strategy

Inside an electronic circuit, ESD protections are found in two different locations. On-chip protections are integrated directly into silicon. External protections are discrete devices connected to inputs or outputs of integrated circuits. Historically, on-chip protections were designed for stresses generated during manufacturing. They were not aimed to protect against system-level discharges, i.e. discharges happening in the field during the normal product life. This task was fulfilled by external protections, such as transient voltage suppressors, diodes, capacitors, filters. Over the years, design techniques and simulations tools have improved, and more robust integrated protections could be designed. On the other hand, equipment manufacturer were always looking for means of reducing the bill of materials (BOM) or the cost of electronic systems. This led to a shift of responsibilities toward on-chip ESD protections for handling system-level stresses. The shrink of integrated technologies makes this tasks even more challenging. External protections are still very relevant, where an integrated solution would occupy too much silicon area, or when very harsh requirements are demanded.

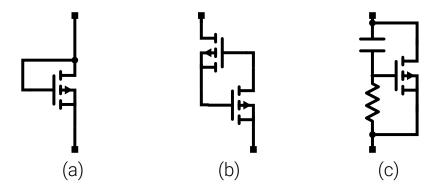

Figure 1.3: common ESD protections architectures - (a) Diode (b) Thyristor (c) RC-triggered MOS

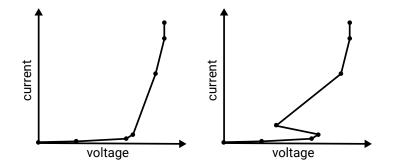

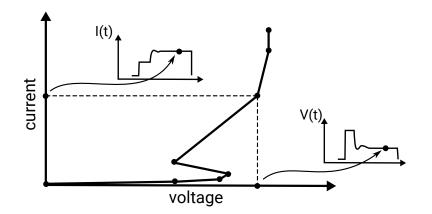

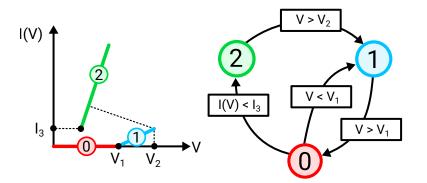

ESD protections can be designed in various ways (see Fig. 1.3). Diodes or thyristors are two main architectures used for designing a protection. Thyristors have typical snapback characteristics as shown in Fig. 1.4. RC-triggered MOS are frequently found for protecting low-voltage Input and/or Output (I/O) of Complementary Metal Oxide Semiconductor (CMOS) circuits. Basically, it is a power transistor activated during the discharge by a resistor-capacitor network. During a transient event, the capacitor acts as a short-circuit, rising the gate potential. The MOS switches on and absorbs current, deviating it into the ground.

A few key values are important for describing a protection.  $V_{t1}$  refers to the triggering voltage of the protection.  $I_{t1}$  corresponds the current absorbed by the protection immediately after triggering.  $V_{t2}$  and  $I_{t2}$  describe the coordinates where the protection is destroyed. A sudden increase of the leakage current (Fig. 1.4) is a good indicator of a damaged protection.

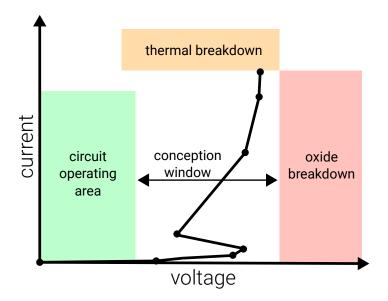

To design an efficient ESD protection, several requirements are to be fulfilled. This is called the conception window, illustrated in Fig. 1.5. In the absence of a discharge,

Figure 1.4: I(V) curves of typical ESD protections with snapback and no-snapback

protections must be transparent to the rest of the device. It corresponds to the area in green in Fig. 1.5. The protection must trigger above the operating voltage of the circuitry. For instance, if an input operates between 0 V and 5 V, and the protection switches on at 4 V, it will trigger during normal operation and be immediately destroyed. On the other hand, protections must clamp voltage (by absorbing current) before reaching the maximum voltage tolerated by the silicon gate oxide. It corresponds to the red area on Fig. 1.5. When absorbing large currents, the protection heats up very high locally. If the temperature exceeds the melting of silicon (1414 °C), the protection device gets destroyed through thermal breakdown, corresponding to the area in orange in Fig. 1.5. For demanding applications, protections must trigger at a given voltage accurately, independently of manufacturing process, mismatches and temperature variation. This reduces the conception window substantially and makes the design more challenging.

Figure 1.5: Conception window of an ESD protection

To design and validate protections, tools like Synopsys TCAD (Technology Computer Aided Design) [25] are employed to simulate semiconductor physics. Afterwards, an electrical model is constructed, to verify that the protection and the circuit cooperate as expected. Simulation is ran in a Simulation Program with Integrated Circuit Emphasis (SPICE) environment. Modeling of ESD protections for SPICE simulations is presented later in chapter 2.1.3.

# 1.2 Review of ESD testing

Electronic hardware robustness is tested against electrostatic discharges using different test methods and standards. Each method reproduces a specific discharge event in laboratory conditions. In this chapter, relevant ESD generators for this research work are detailed.

In ESD testing, a distinction is often made between so-called system-level level tests and Integrated Circuit (IC) level tests. System-level tests reproduce discharge events encountered by a system deployed in the field. Silicon-level tests target ESD events happening during IC manufacturing.

System-level tests involve higher voltage and current amplitudes, and are more harmful for electronic devices than IC level tests.

### 1.2.1 Transmission Line Pulsing (TLP)

The transmission line pulsing generator is an extremely popular tool in the ESD field. Over the years, it was employed in a variety of applications, from characterization of devices [26, 27], investigation of failures [28, 29] and correlation of failure levels with other generators [30]. It is a versatile tool, that was often modified to address larger testing conditions [31] or non-rectangular pulse waveforms [32, 33]. The technique was invented by T. Maloney and N. Nakamura [34]. It is standardized as part of ANSI/ESD STM 5.5.1-2016 [35] through the effort of the ESD Association (ESDA) [36]. It was extensively studied during the PhD thesis of N. Monnereau [15] and N. Lacrampe [14].

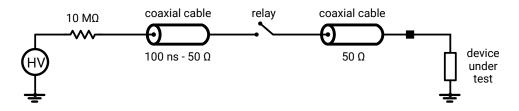

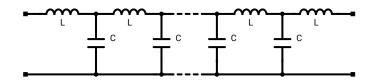

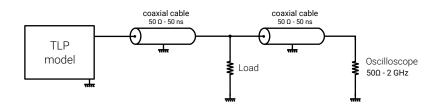

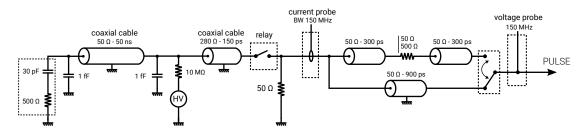

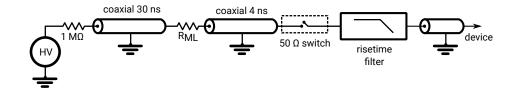

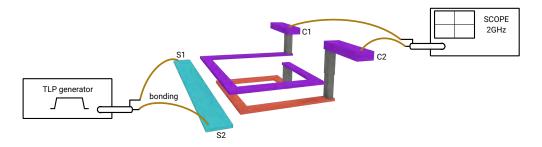

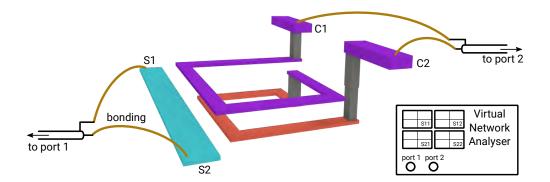

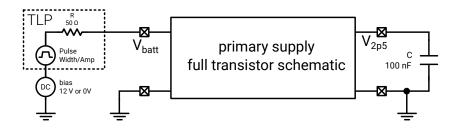

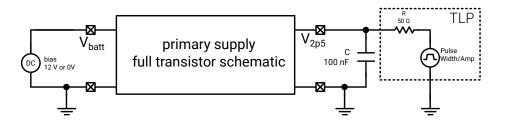

Transmission Line Pulsing (TLP) systems produce a short rectangular pulse, through the discharge of a coaxial cable (Fig. 1.6). The cable is initially charged with an highvoltage voltage supply through a high value resistor. This keeps the current small and avoids oscillations on the cable. When the voltage of the cable reaches the desired amplitude, a relay can be switched to trigger the discharge. The coaxial cable has usually a characteristic impedance of  $50 \Omega$  and a length of 10 m, corresponding to a 50 ns propagation delay. The generated pulse is twice that delay.

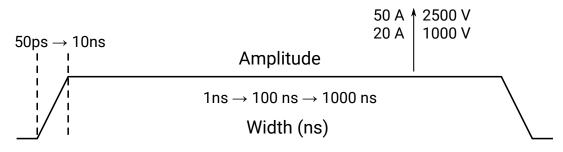

TLP systems constitute very well-controlled test generators. The pulse is generated inside a shielded environment. It is isolated from external radiated emissions and does not emit electromagnetic disturbances. The characteristic impedance of  $50 \Omega$  can be controlled up to the load, by using appropriate  $50 \Omega$  cables and hardware. Those properties result in clean and repeatable pulse waveforms without reflections. The main features of the generated pulse are given in figure 1.7.

Figure 1.6: Minimal example of a TLP system

Figure 1.7: Main characteristics of a TLP pulse on a resistive load

The waveform parameters are completely controlled and easily tunable. The charging voltage is set by the high-voltage source. The pulse width can be increased or decreased by changing the length of the coaxial cable. The risetime can be enforced with a 50  $\Omega$  matched risetime filter [37, 38]. Unlike most filters, they are specifically designed to work by absorption and not by reflection. They do not pollute the system with reflected waves.

TLP generators can also be employed as a measurement tool. Some configurations use Time-Domain Reflectometry (TDR) and others rely on more standard techniques for measuring electrical properties of a load.

Time-domain reflectometry is a measurement technique with a wide range of applications. With TDR, it is possible to determine electrical properties of a device by observing reflected waveforms. Application of time-domain reflectometry to TLP is described in the ANSI ANSI/ESD STM 5.5.1-2016 standard [35]. In this configuration, voltage and current measured at the output of the generator are equal to voltage and current waveforms inside the load.

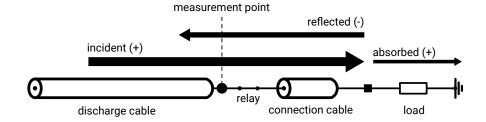

This is due to the superposition of the incident and reflected pulses during the discharge (see Fig. 1.8). When the relay is closed, an incident wave appears that propagates toward the load. The impedance mismatch between the load and the connection cable forces a part of the incident power to reflect back. The rest is absorbed and dissipated by the load. This reflected wave corresponds to the difference between the incident power and the absorbed power, but with a negative sign. At the measurement point, the incident wave and the reflected wave add up. Eq. 1.1 explains how this sum is equal

Figure 1.8: TDR measurement with incident and reflected waves superposition

to the value absorbed by the load, for the voltage.

$$V_{measured} = V_{incident} + V_{reflected} = V_{incident} + (-(V_{incident} - V_{absorbed})) = V_{absorbed}$$

(1.1)

The same equation applies for computing the current value. In summary, the measured voltage and currents at the output of the TLP are equal to the voltage and current inside the load, when incident and reflected waves are superimposed. An extensive analysis of Time-Domain Reflectometry (TDR) TLP is provided in [15].

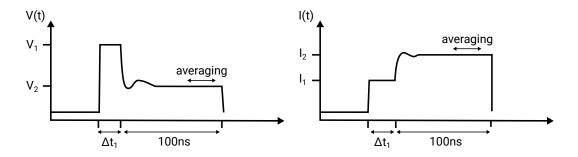

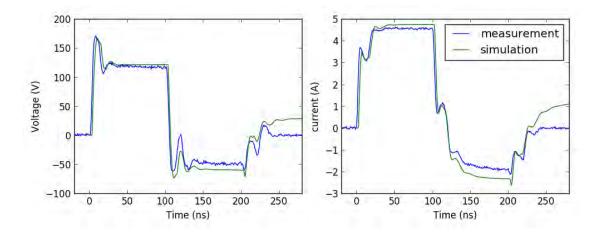

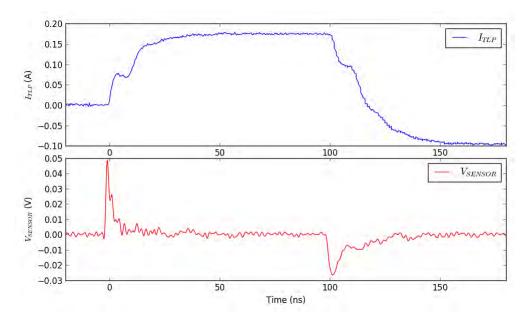

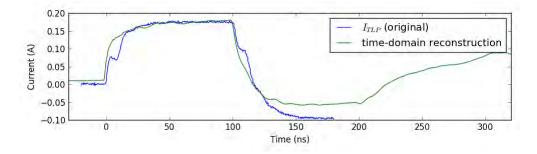

Fig. 1.9 provides an example of a typical waveform generated by a TLP injecting in an ESD protection. The recording is done in a TDR configuration. Voltage and current waveforms usually exhibit two steps. The first step is due to the connection cable that links the TLP to the load (see previously Fig. 1.6). Delay  $\Delta t_1$  corresponds to the delay of the connection cable. The ratio  $V_1/I_1$  is equal to the characteristic impedance of the connection cable, usually 50  $\Omega$ . The second step is the response of the tested load. The value  $V_2/I_2$  is the quasi-static resistance of the load.  $V_2/I_2$  is a function of the TLP charging voltage. By averaging each waveform during a few tens of nanosecond, the current and voltage value of the load can be accurately sampled.

Figure 1.9: TLP V(t) and I(t) example

The pulse ends when the main coaxial cable is fully discharged. The pulse lasts twice the delay of the discharge cable. At 0 ns the relay is closed. The cable starts discharging from the end closer to the relay. The other end starts discharging only 50 ns later because of the propagation delay. It takes another 50 ns delay for the discharge to completely propagate back to the relay side. This explain why the pulse length is twice the coaxial cable delay.

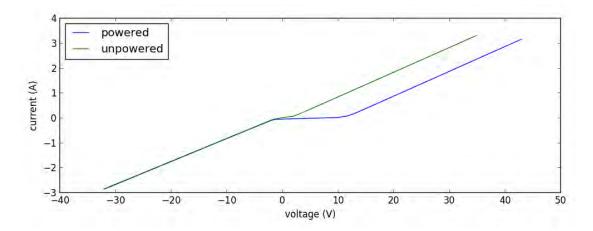

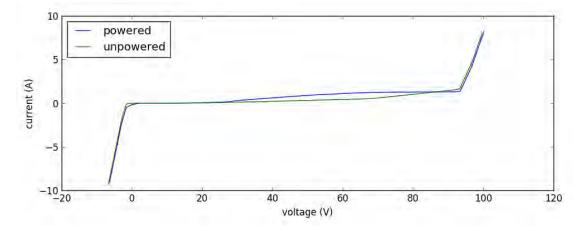

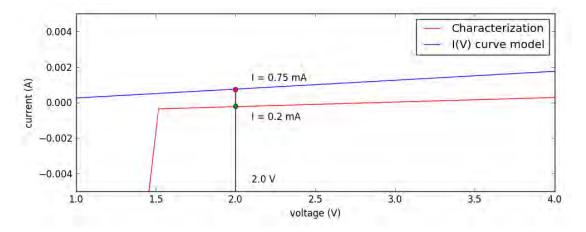

A very popular application of transmission line pulsers is the extraction of an I(V) curve 1.10 from a set of pulses and measurements. An I(V) represents the current versus voltage response of a device. They are called quasi-static because values are sampled during a short amount of time and cannot be entirely assimilated to a DC characterization. They are extracted at much larger levels than the device can withstand in DC. Quasi-static I(V) curves are particularly useful for characterization of ESD protections [26], that by nature work in transient regime and cannot be studied in DC.

Figure 1.10: TLP-extracted I(V) characteristic example

The I(V) curve is extracted point after point. Each point corresponds to a voltage and current measured by averaging the transient waveforms during the second step. A first pulse is injected, current and voltage are measured, and the coordinates of a first point are extracted. Then the process is repeated and the charging voltage is incremented after each new point (Fig. 1.10). Depending on the kind of tested device, snapback responses can sometimes be measured. A snapback response is a non-monotonous curve, where a single x-axis value (voltage) can correspond to multiple y-axis values (current). An example is provided in Fig. 1.10. Snapbacks are observed for devices with at least two different states of operation. In the off-state, it acts as a high-value resistance and current increases very slowly when voltage gets higher. When the device turns on, its resistance drops abruptly and becomes very small. Current suddenly increases and voltage falls. This transition corresponds to the discontinuity visible on the curve.

TLPs are also commonly used for testing the robustness of systems and devices [27, 7]. It is great for troubleshooting because the pulse is well repeatable. A rectangular waveform is also more desirable for investigation, it simplifies the analysis. However in some cases, it can be an issue for reproducing a failure observed with more time-varying waveforms like IEC 61000-4-2 [16] described after.

A few variations of the TLP exist to cover edge cases and specific characterization requirements. The very-fast TLP (vf-TLP) is one of them. It was designed by H. Gieser [39] to reproduce gate oxide breakdown. Basically, it is a TLP with a shorter pulse width, usually in the range of 1 ns to 10 ns.

vf-TLP requires more advanced calibration techniques for measuring load current and voltage, and stronger constraints on the quality and bandwidth of test elements and measurement systems. In this configuration, incident and reflected waves never superimpose and by default time-domain reflectometry cannot be employed as-is. However, E. Grund adapted the technique to vf-TLP in [40]. With this method, it is possible to analyze and calculate the impedance of all elements between the generator and the load.

To sum up, Transmission Line Pulsing is an extremely versatile and useful technique for the ESD field. It is not considered a qualification tester though because it does not reproduce any real-world electrostatic discharge events. Standards and other techniques dedicated to this task are described hereafter.

#### 1.2.2 ESD Gun (IEC 61000-4-2 / ISO 10605)

IEC 61000-4-2 [16] and ISO 10605 [17] standards define a system-level test waveform and test generator to reproduce the discharge of a human body through an electronic device. This test is used very extensively for qualification of products. Fig. 1.11 provides a picture of an ESD gun. The gun is composed of a metallic discharge tip to inject the pulse. The ground return is a long metallic ribbon a couple of meters long. Depending on the test configuration, it is connected to the product ground or the earth. Its shape impacts a lot recorded failure levels. Historically, ESD gun were famous for lacking some reproducibility on test results [41]. They have largely improved since then although radiated emissions and shape of the ground return still remain a very large factor of variation and uncertainty [42].

Figure 1.11: Picture of an ESD gun IEC 61000-4-2 compliant

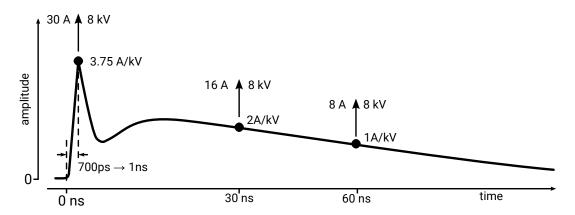

Fig. 1.12 presents the main properties of the generated stress. The standard defines this waveform for a  $2\Omega$  load. The pulse starts by a fast peak with a 1 ns risetime. It is followed by a slower slope of smaller amplitude but longer duration of about 200 ns. Voltage levels can reach 15 kV peak and 30 A of current.

Figure 1.12: Main properties of an IEC 61000-4-2 pulse on a  $2\Omega$  resistive load

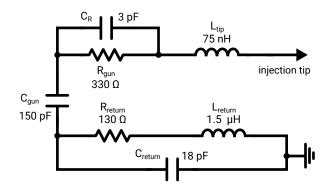

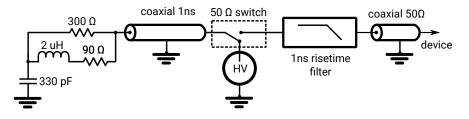

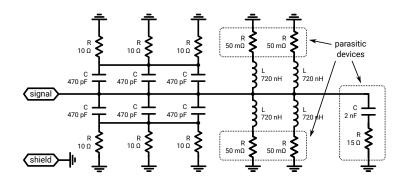

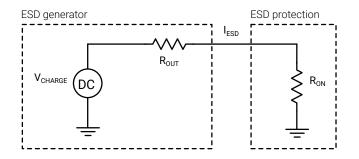

The generation of the ESD pulse is done with a  $330 \,\Omega$  resistor and  $150 \,\mathrm{pF}$  capacitor discharge network. The RC network alone though does not suffice to reproduce the waveform. Parasitic devices play an important part in shaping the waveform. Fig. 1.13 provides a physically-based ESD Gun model that helps understand the impact of parasitic devices. This model was originally written by Chiu [43] and is referenced in the PhD thesis of N. Monnereau [15]. It adds an RLC network to model the ground return. A series parasitic capacitance inductance model imperfections in the direct injection path.

Figure 1.13: ESD Gun model (from Chiu [43])

IEC 61000-4-2 [16] and ISO 10605 [17] are system-level standards, targeting different fields of application. IEC 61000-4-2[16] standard targets consumer electronics. ISO 10605[17] standard is intended for automotive equipment. It defines additional pulse

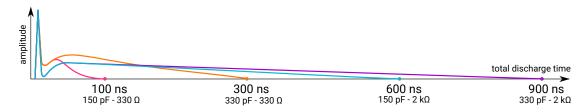

waveforms to cover a wider range of ESD events (See fig 1.14). Each pulse is generated with a different discharge network. Instead of the usual 150 pF and 330  $\Omega$  values, all combinations with 330 pF and 2 k $\Omega$  are also possible.

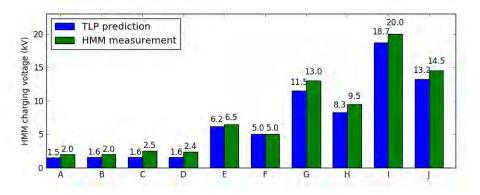

The Human Metal Model (HMM) [44] specification aims to adapt those system-level standards for component-level testing. The pulse waveform remains identical, but a few modifications concerning the injection setup are proposed. Most notably, the ground return of the gun is connected directly to the ground of the device, rather than the Earth. The specification is standardized under ANSI/ESD SP5.6-2009 [44].

Figure 1.14: Waveforms defined in ISO 10605 standard on a  $2\,\Omega$  resistive load

ISO 10605 introduces the concept of performance classes for categorizing the robustness of powered-on electronic systems in operation against electrical disturbances. Classes are defined from A to E, with A describing systems that are the more immune to the test. Class E corresponds to the worst severity, where the electronic device did not survive the test. Table 1.2 details the conditions specified for each class.

#### 1.2.3 ISO 7637-2

ISO 7637-2[45] is an automotive standard for testing immunity of electronic devices against transient electrical disturbances. It reproduces disturbances applied on supply lines, when the battery of a car is disconnected for instance. This standard defines several waveforms. Among them, pulses 2A and 3B are the closest to an electrostatic discharge.

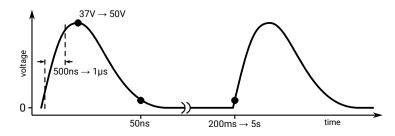

Pulse 2A simulates the sudden disconnection of a load placed in parallel with the device under test. In a car, it reproduces the switching of devices separated by inductive wiring harnesses. When a load is abruptly switched off, the inductance opposes to the sudden interruption of current. Instead of flowing through the load, the current is maintained and reported onto the Device Under Test (DUT) which can be damaged or disturbed in the process. These events can be quite harmful with peak voltages above 50 V during  $50 \,\mu\text{s}$ . This pulse can be an interesting testing waveform in the context of this entire document. The characteristics of pulse 2A are given in fig. 1.15.

The ISO 7637-2 standard does not enforce how stress generators must be constructed or modeled. A compliant generator can be implemented with a resistor-capacitor discharge network. By tuning both values, it is rather straightforward to produce the standardized waveform. It should be noted though that the behavior of an RC network is quite different from an actual inductive load disconnection. However, as long as the

| Immunity class | Definition                                                                                                                                                                                                                                                                        |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| А              | All functions of a device or system perform as designed during and after exposure to interference.                                                                                                                                                                                |

| В              | All functions of a device/system perform as designed during exposure;<br>however, one or more of them may go beyond the specified tolerance.<br>All functions return automatically to within normal limits after expo-<br>sure is removed. Memory functions shall remain class A. |

| С              | One or more functions of a device or system do not perform as designed<br>during exposure but return automatically to normal operation after<br>exposure is removed.                                                                                                              |

| D              | One or more functions of a device or system do not perform as designed<br>during exposure and do not return to normal operation until exposure<br>is removed and the device or system is reset by a simple "operator/use"<br>action.                                              |

| Е              | One or more functions of a device or system do not perform as designed<br>during and after exposure and cannot be returned to proper operation<br>without repairing or replacing the device or system.                                                                            |

Table 1.2: Electronic systems performance classes from ISO10605

Figure 1.15: Waveform 2A defined in ISO 7637-2 standard on a  $2\,\Omega$  resistive load

generated waveform follows the amplitude criteria defined in the standard the generator is considered compliant.

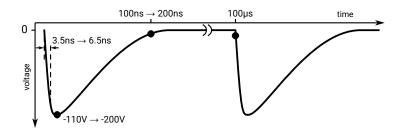

Figure 1.16: Waveform 3B defined in ISO 7637-2 standard on a  $50\,\Omega$  resistive load

Pulse 3B simulates the result of a switching process on a wiring harness, causing negative spikes on a DUT. Its waveform is given in fig. 1.16. Compared to pulse 2a, this waveform has a shorter duration and risetime and a higher amplitude. Interestingly, it is one of the rare ESD waveforms to be defined on a 50  $\Omega$  load.

A few papers [46, 47, 48] studied the impact of those waveforms on integrated ESD protections. Automotive equipment manufacturer are required to qualify products against ISO 7637-2, to guarantee they can survive the vicinity of other electrical modules in the car such as ignition systems. Therefore, it is relevant to test functional robustness of devices against this standard.

The VDA FAT-AK30 working group on simulation of mixed-systems with VHDL-AMS [49] has worked on modeling all ISO 7637-2 generators. They have provided opensource models of all pulses defined in the standard, as part of the *vdalib* library [50]. For instance, VHDL-AMS model of pulse 3B is provided in Listing 1.1.

```

architecture IDEAL of ISO_7637_PULSE3B is

constant UAO : REAL := 0.0;

constant D2 : REAL := LOG(10.0)/(TD-TR);

STATE_TYP is (S0, S1, S2, S3);

type

signal STATE : STATE_TYP := S0;

signal TSTART : REAL

:= 0.0;

signal ACTIVE : BOOLEAN

:= FALSE;

signal ACTIVE_CTRL : BOOLEAN;

quantity VSW across ISW through EL_1 to EL_2;

quantity V

across I

through EL_1 to EL_2;

begin

process is

begin

STATE <= SO;

TSTART <= NOW;

wait for INIT_DELAY;

loop

for I in 0 to INTEGER(T4/T1) loop

STATE <= S1;

TSTART <= NOW;

wait for TR/0.8;

STATE <= S2;

TSTART <= NOW;

wait for T1-TR/0.8;

end loop;

STATE <= S3;

TSTART <= NOW;

wait for T5;

end loop;

```

```

end process;

if ACTIVE use

case STATE use

when SO => V == UAO+RI*I;

when S1 => V == US*REALMAX(0.8/TR*(NOW-TSTART),1.0)+UA0+RI*I;

when S2 => V == US*EXP(-D2*(NOW-TSTART))+UAO+RI*I;

when S3 => V == UAO+RI*I;

when others => V == UAO+RI*I;

end case;

else

I == 0.0;

end use;

process (S_IN, STATE) is

begin

if (S_{IN} = '1' \text{ or } S_{IN} = 'H')

and (STATE = S0 or STATE = S3)

and ACTIVE = FALSE then

ACTIVE <= TRUE;

end if;

if not (S_IN = '1' or S_IN = 'H')

and (STATE = S0 or STATE = S3)

and ACTIVE = TRUE then

ACTIVE <= FALSE;

end if;

end process;

ACTIVE_CTRL <= not ACTIVE_CTRL when ACTIVE and STATE'event;

if ACTIVE use

ISW == 0.0;

else

VSW == 0.0;

end use;

break on ACTIVE, ACTIVE_CTRL;

end architecture IDEAL;

```

Listing 1.1: Open-source VHDL-AMS model of ISO7637 pulse 3B - Copyright VDA/FAT

#### 1.2.4 IEC 61000-4-4

The IEC 61000-4-4 standard [51], also called burst test, defines an electrical fast transient for ESD testing. It defines a test waveform, generator and procedures for assessing susceptibility of electronic devices subjected to transient disturbances such as interruption of inductive loads and relay contact bounce. It concerns all kinds of inputs such as supply, signal and control lines. This standard applies to any field of application and is not specific to one.

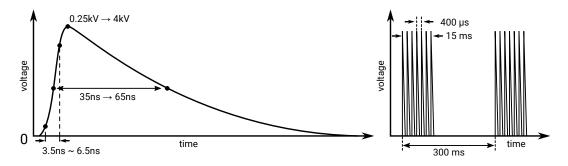

The defined waveform is a double exponential pulse 1.17 with a width of 50 ns at 50 % of the peak amplitude. Risetime is comprised between 3.5 ns and 6.5 ns. It is defined for a 50  $\Omega$  load, with a pulse period of 15 ms and a burst period of 300 ms.

Figure 1.17: IEC 61000-4-4 waveform on a  $50 \Omega$  resistive load

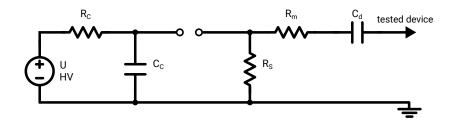

The standard defines a circuit diagram for the generator (Fig 1.18). The discharge is produced by a resistor-capacitor  $R_{\rm C}$ - $C_{\rm C}$  network and initiated by a spark-gap. A spark-gap consists in two conductive tips separated by a gap. When voltage across the gap becomes superior to the breakdown voltage, a spark appears and resistance of the spark gap suddenly drops, allowing discharge current to flow through. In Fig. 1.18,  $R_{\rm s}$ ,  $R_{\rm m}$  and  $C_{\rm d}$  shape the waveform.  $R_{\rm s}$  defines the duration of the pulse,  $R_{\rm m}$  performs an impedance matching and  $C_{\rm d}$  act as a D.C. block. The generator's output is a coaxial plug to prevent radiated emission during the discharge.

Figure 1.18: IEC 61000-4-4 generator circuit diagram

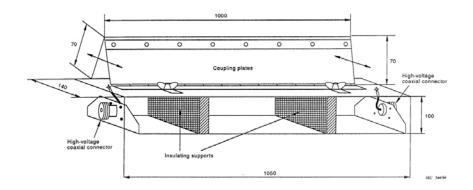

A particular injection method for powered lines called a *capacitive coupling clamp* (Fig. 1.19) is defined in this standard. This injection system is interesting for performing repeatable injection into powered supply lines. The clamp is constituted of two large

metallic plates. The upper plate has the shape of a tunnel, where the wires receiving go through. The discharge is injected in the upper plates. The bottom plate is connected to the ground of the discharge generator. Thanks to this design, the shape of the wires and the entire setup is well controlled. Although originally designed to work with the IEC 61000-4-4 waveform, the capacitive coupling clamp accepts coaxial cables and any kind of stress generator can be employed instead.

Figure 1.19: IEC 61000-4-4 capacitive coupling clamp

### 1.2.5 IEC 62215 standard

The IEC 62215 standard [52] defines a method for measuring the immunity of an integrated circuit to conducted electrical transient disturbances. It specifically targets testing of integrated circuits in operation. Instead of specifying test pulses, this standard defines a way to inject stresses suitable for integrated circuits. For automotive devices, the standard specifies the use of waveforms from ISO 7637-2 [45]. IEC 61000-4-4 [51] or IEC 61000-4-5 are required for industrial and consumer applications. Ultimately, the goal is to understand and classify interactions between a conducted disturbance and performance degradation induced in integrated circuits. The test method resembles the Direct radio-frequency Power Injection (DPI) technique defined in IEC 62132-4 [53]. The DPI standard focuses on frequency domain immunity, while this standard tests time-domain immunity.

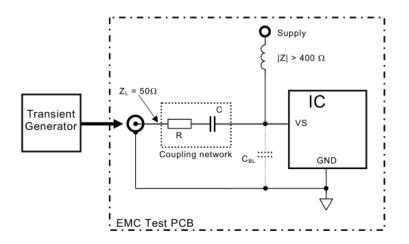

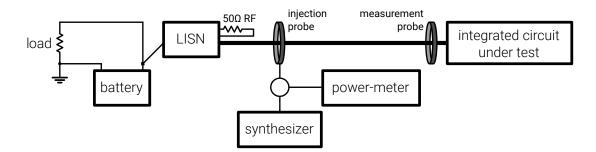

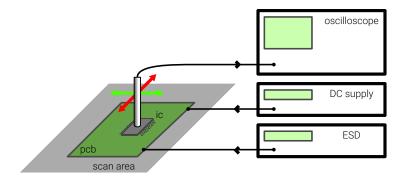

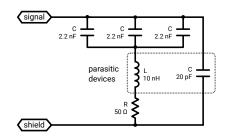

Disturbances are applied to the IC pins via a coupling network, that isolates the stress generator and the D.C. supply from one another. A typical pin injection setup is given in Fig. 1.20.

Beyond test setup and waveforms, the standard defines immunity classes (see Table 1.3) to categorize the behavior of integrated circuits exposed to disturbances. It is a direct adaptation of performance classes defined in Annex B of ISO10605 and presented previously in Table 1.2. Classes range from A to E. A describes devices that are completely unaffected by the testing procedure and maintain their entire functionality. B describes a short time degradation of internal signals. It is not applicable for integrated circuits, where internal signals are most of the time not accessible. C is identical to

Figure 1.20: Typical injection setup via a coupling network

A, with the difference that failures can occur internally inside the chip, as long as they remain internal to the circuit and do not affect the final application. Finally, D and E describe actual cases of failure, with E representing a hard-failure.

| Immunity class  | Definition                                                                                                                                                                                                                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>IC</sub> | All monitored functions of the IC perform within the defined tolerances during and after exposure to disturbance.                                                                                                                      |

| B <sub>IC</sub> | Short time degradation of one or more monitored signals during exposure to disturbance is not evaluable for IC only. Therefore this classification is not applicable for ICs.                                                          |

| C <sub>IC</sub> | All monitored functions of the IC are within the defined tolerances before and after exposure to disturbance.                                                                                                                          |

| D <sub>IC</sub> | At least one monitored function of the IC does not perform within<br>the defined tolerances during exposure and does not return to normal<br>operation by itself. The IC returns to normal operation by simple<br>action (e.g. reset). |

| E <sub>IC</sub> | At least one monitored function of the IC does not perform within the defined tolerances after exposure and can not be returned to proper operation.                                                                                   |

Table 1.3: IC performance classes from IEC62215

## 1.3 Review of soft-failure silicon-level investigation

In previous sections, major ESD standards used in laboratories were presented. The impact of electrostatic discharges on electronic devices has been detailed, highlighting two classes of failures. Hard-failures are well known and multiple protection strategies exists, from external devices and ESD protections, to distributed protection architectures and much more. Soft-failures are the kind of issue caused by electrical fast transients. When discharges propagate inside electronic equipments and reach integrated circuits, they can cause them to malfunction. For multiple reasons described in previous sections, it is essential to detect early functional weaknesses. This section is a review the literature of the current state of the art on ESD induced soft-failure analysis. Study cases, observation methods and modeling approaches are presented.

#### 1.3.1 Case studies

N. Lacrampe presents a functional failure case in [7]. Very-fast TLP is injected on an  $0.18 \,\mu\text{m}$  CMOS technology (1.8 V supply voltage) testchip. The chip contains 6 instances on the same logic core, differing only by their power-rails architecture. The injection on power rails is performed using a D.C. block 1 nF capacitor, similarly to the DPI standard [53]. An output signal of the logic core is monitored. The susceptibility criteria is the amplitude crossing a 20% threshold from the established logic level. Above this threshold, the core is supposed to no longer work reliably. It is proven that modeling the output buffer of the core logic is enough for reproducing with less than 20% error the waveform on the output. It is less accurate than a full-netlist simulation, but faster to simulate. VHDL-AMS and SPICE modeling are performed in this analysis.

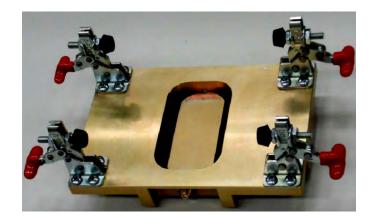

In [9], soft-failures are studied on a SDRAM memory in operation. The injection setup consists of a modified compact Transverse Electro-Magnetic (TEM) cell 1.21 with a reduced septum height. Reduced dimensions result in increased field strengths, to reach levels normally produced by an ESD gun. The discharge waveform, injected inside the cell, is generated by a filtered TLP and is similar in shape to IEC 61000-4-2 [16]. The SDRAM chip is mounted on a board. Data is written and read on the memory by a Field Programmable Gate Array (FPGA). Differences between incoming and outgoing data signifies a functional failure of the memory. Only the memory is exposed to the disturbance, the rest of the board's devices are located outside of the TEM cell, on the other side of the board. The main defect of this method is to only provide a global failure level. It does not allow to identify which particular net or pin is the most sensitive to disturbances.

B. Orr reports in [11] errors caused by electrostatic discharges on two different camera communication buses. Events of different severities are observed, depending on the discharge parameters. It is attempted to determine whether the sensor or the application processor is causing the error. The magnetic emission map is recorded with a near-field magnetic scanner to try to observe local variations in the emission spectrum because of the degradation of functionality. It was envisioned that soft-failure can induce significant variations in the emission spectrum of a disturbed component, and thus those variations

Figure 1.21: Modified TEM cell from [9]

could help localize them. In this particular case, the root cause of failures could not be determined.

An LCD display is studied in [54]. The device is tested with an IEC 61000-4-2 [16] generator, and non-destructive problems are observed due to the discharge. Electromagnetic disturbances cause stripes to appear on the display, optical parameters changes and black-lighting malfunctions. System-level testing waveforms were found too complex for identifying the root cause. A near-field injection is performed to identify which trace of the LCD's flex connector claims the lowest immunity. The lack of resolution of the near-field probe caused multiple traces to be disturbed at once, preventing this second approach to work. Finally, the individual track stressing was repeated with a capacitively-coupled TLP on each individual metal track. However, results were once more inconclusive and no metal trace could categorically be identified as more sensitive than the others. The conclusion for this paper is that silicon level soft-error models are required for standard investigation.

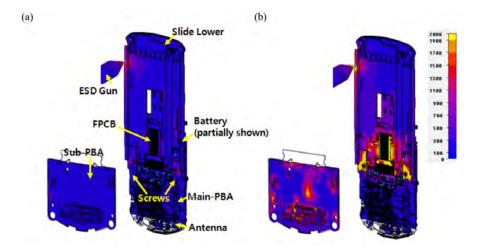

An investigation method is presented in [55] to search for discharge propagation paths responsible for soft-failures on a mobile phone. The IEC 61000-4-2 standard is chosen as testing waveform. Metallic parts are assumed to be the main propagation paths. To confirm this hypothesis, time-domain electromagnetic field 3D simulations of almost the entire phone are ran (see Fig. 1.22) After the failure location was determined, RC-networks are used as countermeasures to protect physical inputs and outputs, like buttons, LCD inputs and connectors.

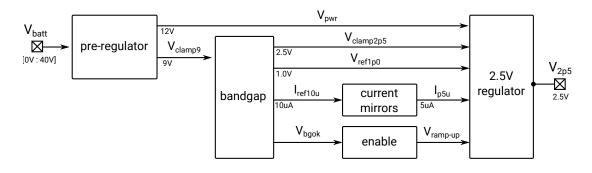

K. Abouda details in [56] a case of soft-failure on an integrated automotive regulator IC. The failure signature is a loss of the regulated voltage when exposed to Bulk Current Injection (BCI) ISO11452-4 [57]. The test setup is provided in Fig. 1.23. The product is investigated manually, by searching inside the design for coupling and propagation paths, and performing multiple simulations. Eventually, it was proven that a residue of the disturbance was coupling through the substrate on a current mirror inside the bandgap reference. During the disturbance, bandgap voltage was shifting from its nominal value. After some delay, the bandgap output was reaching an undervoltage threshold, causing

Figure 1.22: ESD Current Distribution on Mobile Phone and Backside sub-battery pack at (a) 1.0 ns and (b) 1.8 ns (Credit: [55])

the entire system to restart. To avoid it, a design fix was proposed by filtering at the appropriate spot inside the design to avoid the amplification of the disturbance.

Figure 1.23: Bulk Current Injection setup

In summary of the case studies, multiple soft-failures of integrated circuits were studied. They involved core CMOS logic, SDRAM memories, video processors or multimedia devices failing to work temporarily, detected by raising a flag, display issues and communication errors. Overall, it was demonstrated that it remains highly difficult to identify the root cause of the failure, especially without access to the design of the chip. A multitude of tools has been employed throughout the studies, such as near-field injection and scan, modified TEM cells, SPICE and electromagnetic simulations and modeling languages such as VHDL-AMS. Ultimately, it seems that access to the silicon design is essential to debug the problem and fix, as was shown successfully in [56]. All these conclusions call for new investigation methods at silicon level, and modeling method for enabling system level simulations without disclosing intellectual property. The new methods and tools presented in this document aim to solve exactly this kind of issues.

#### 1.3.2 Observation methods

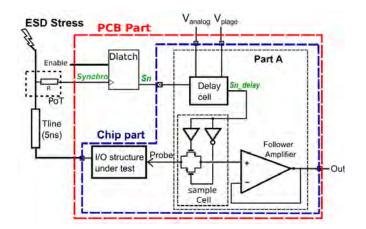

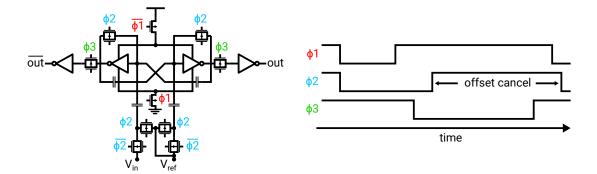

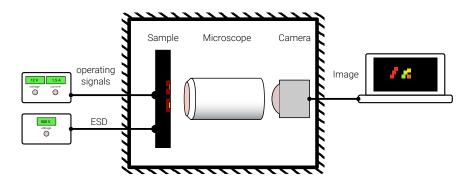

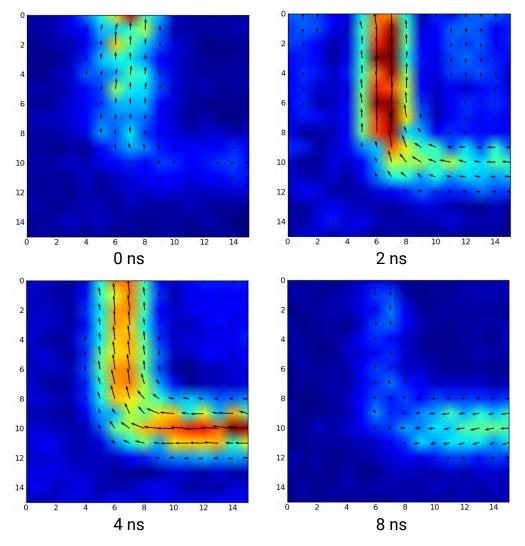

F. Caignet proposes in [58] an on-chip measurement technique capable of recording ESD waveforms with a 20 GHz bandwidth. It relies on equivalent-time sampling for measuring waveforms with a much larger bandwidth that real-time oscilloscopes. Equivalent timesampling works exclusively with repeatable or periodic signals. A real-time oscilloscope takes a complete waveform constituted of N samples in a single shot. On the other hand, a time-equivalent sampler measures waveforms point by point, and require Nrepetitions of the waveform to acquire the N samples. The process for acquiring the data is the following. A first waveform is shot, and the sampler only records its value at t = 0. A second waveform is shot, and the sampler records the value at  $t = \Delta t$ . At the third waveform, the recording is at  $t = 2\Delta t$ . The process is repeated while increasing the sampling delay by  $\Delta t$  at each step until enough points were acquired. This approach is interesting because it reduces a lot the constraints on the measurement system, while offering a huge bandwidth. The main disadvantage is that it requires as many measurements as the amount of points needed. In [58], the sampler was designed using a CMOS 65 nm technology and embedded into a testchip. Architecture is given in Fig. 1.24.

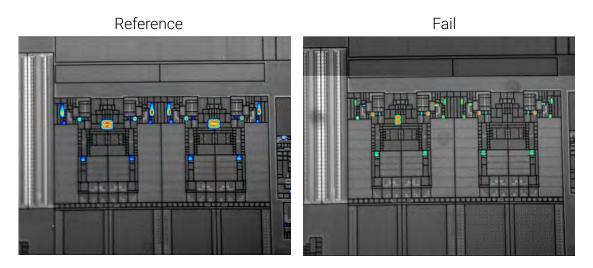

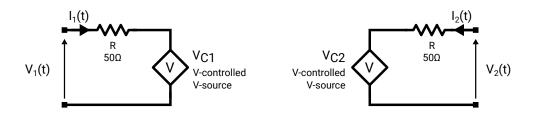

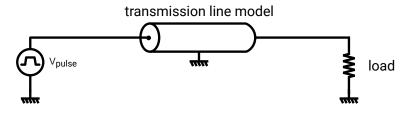

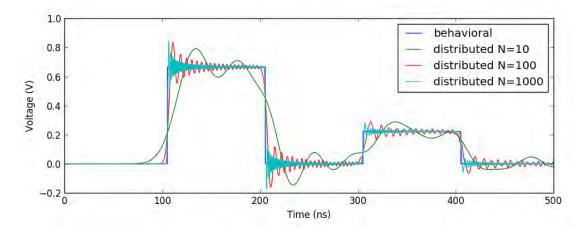

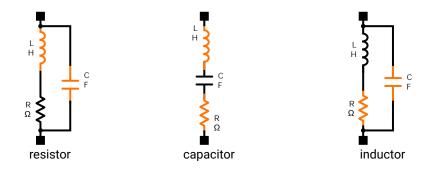

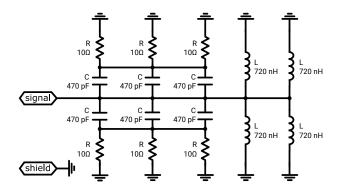

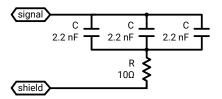

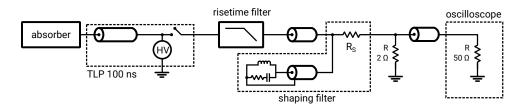

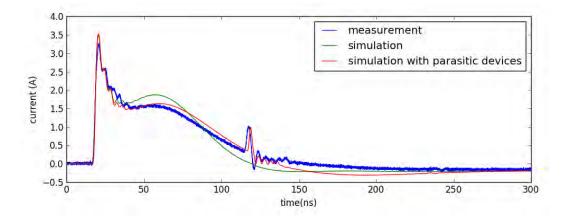

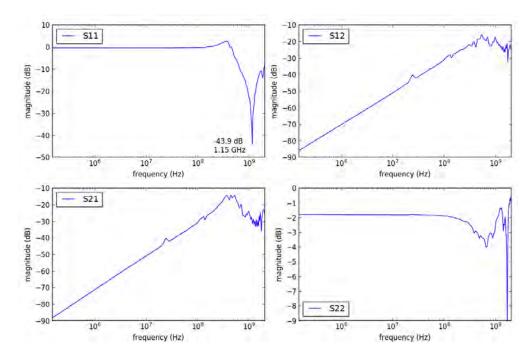

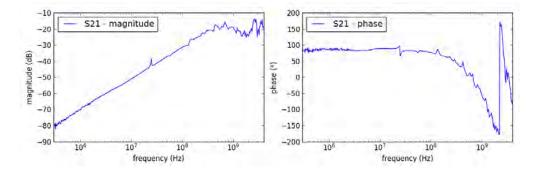

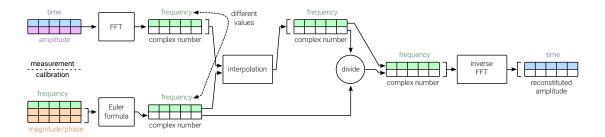

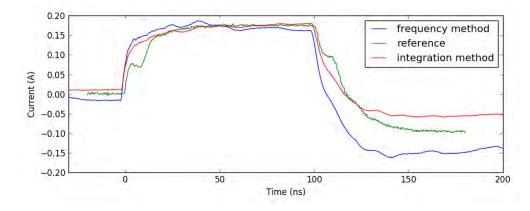

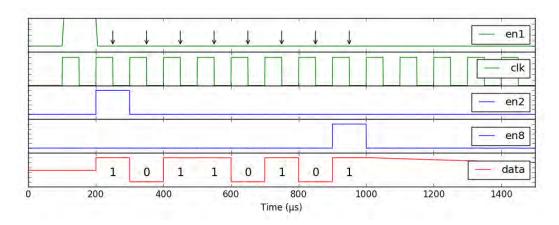

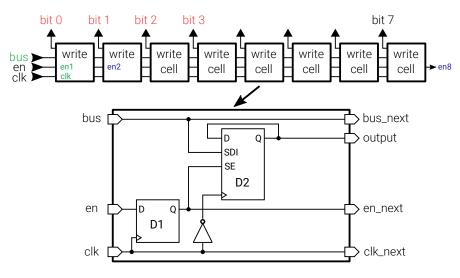

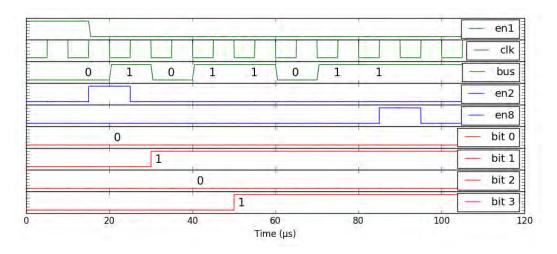

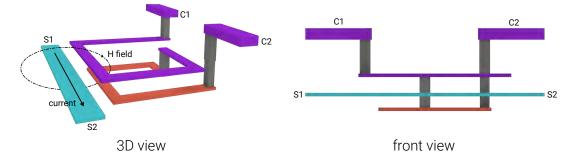

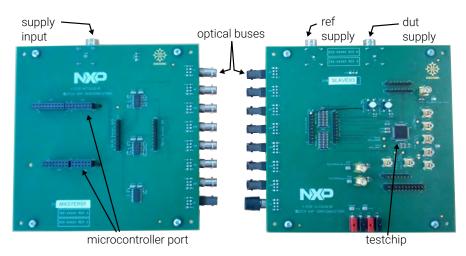

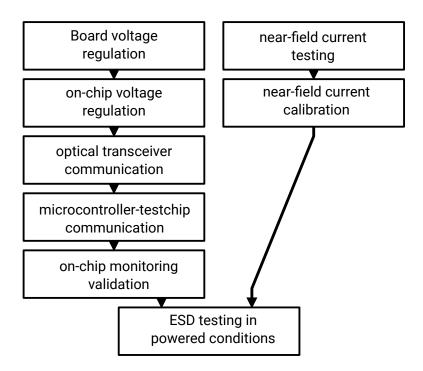

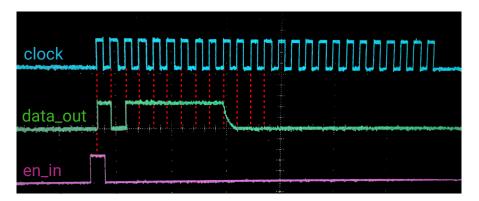

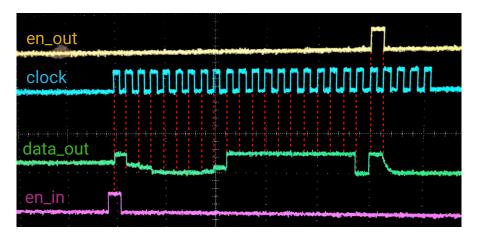

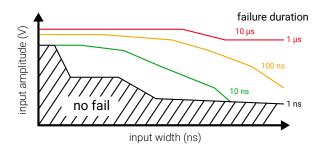

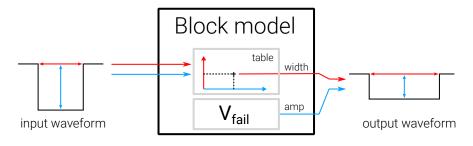

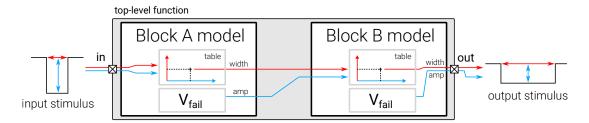

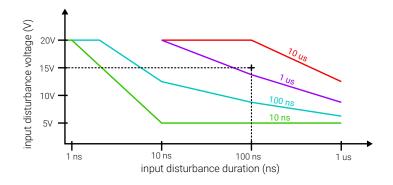

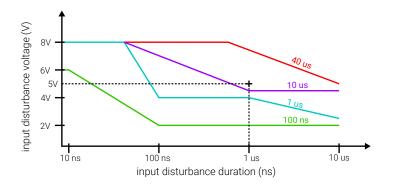

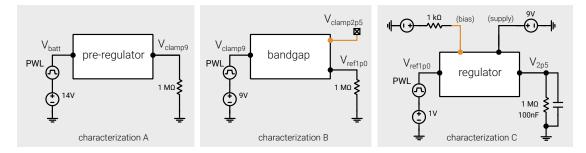

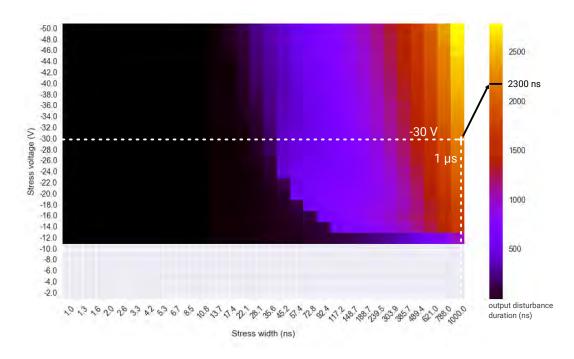

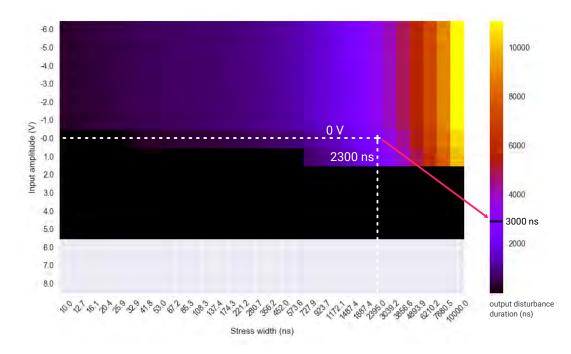

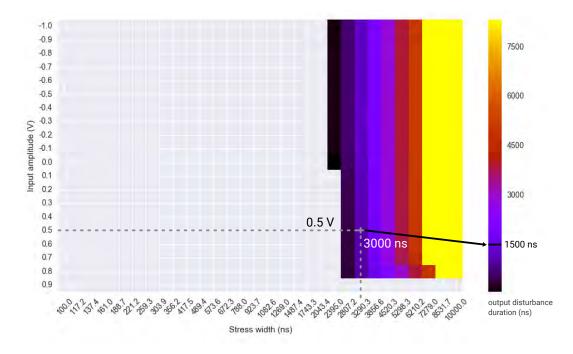

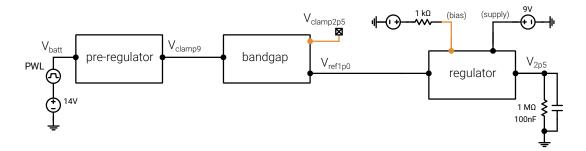

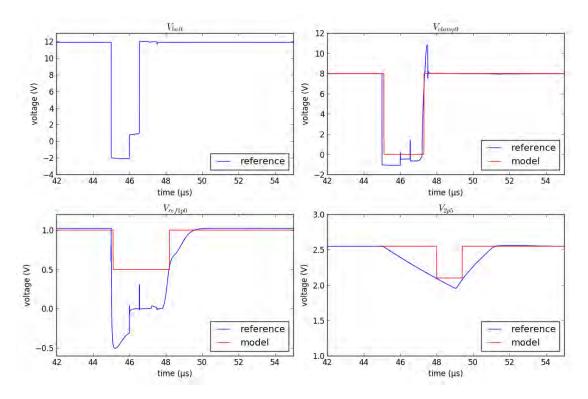

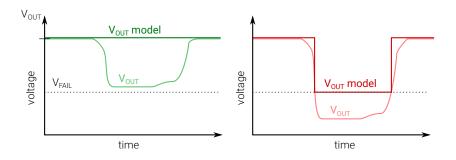

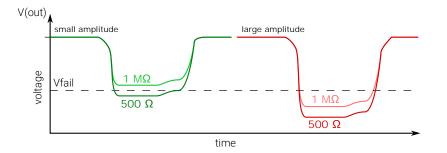

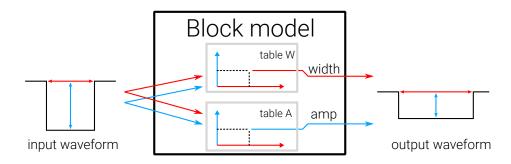

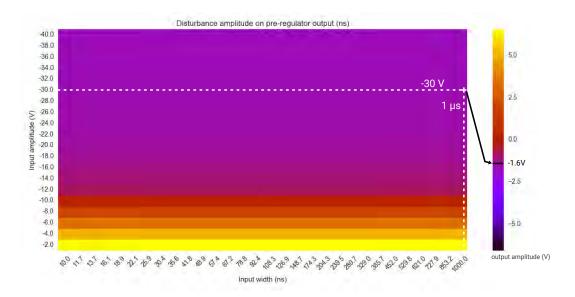

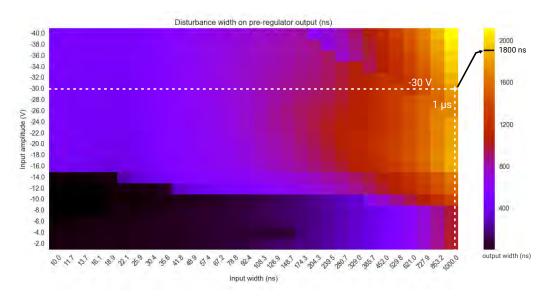

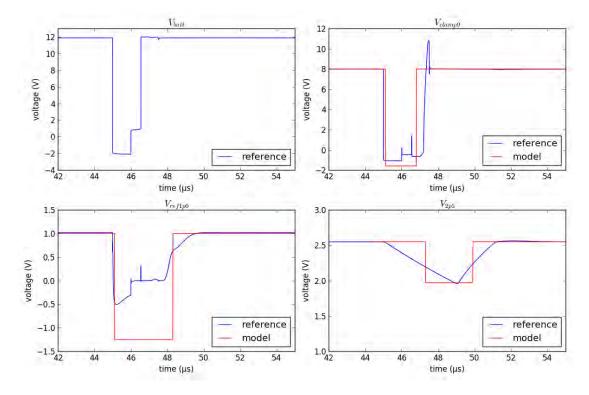

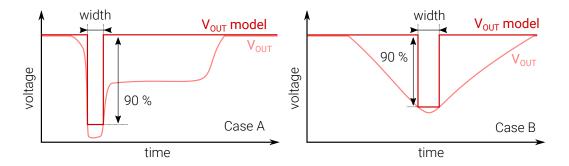

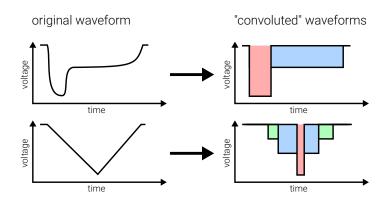

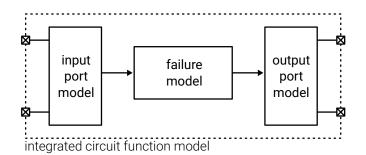

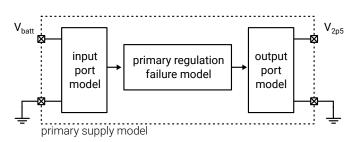

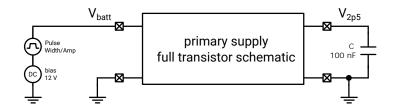

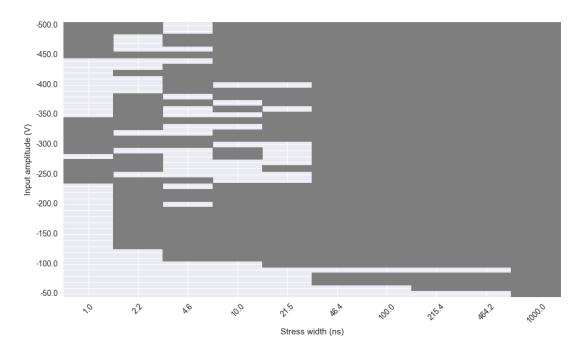

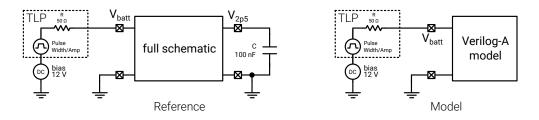

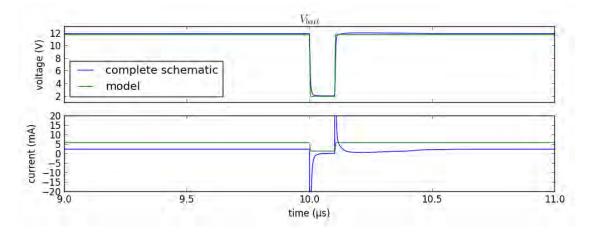

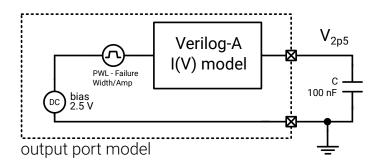

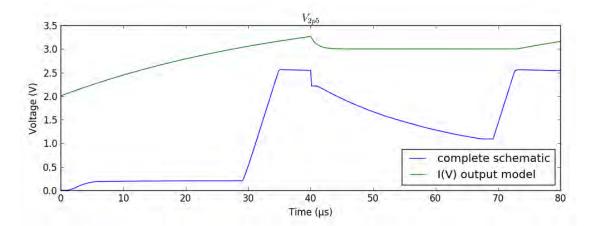

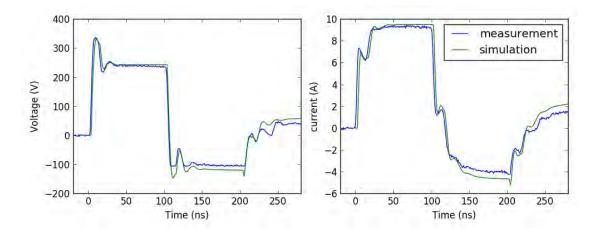

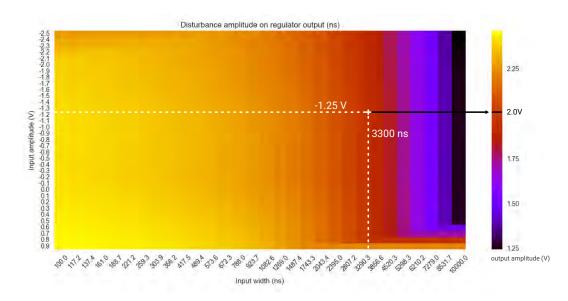

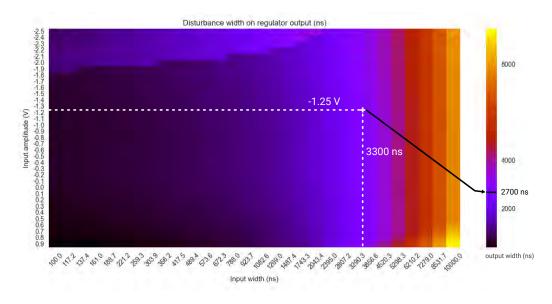

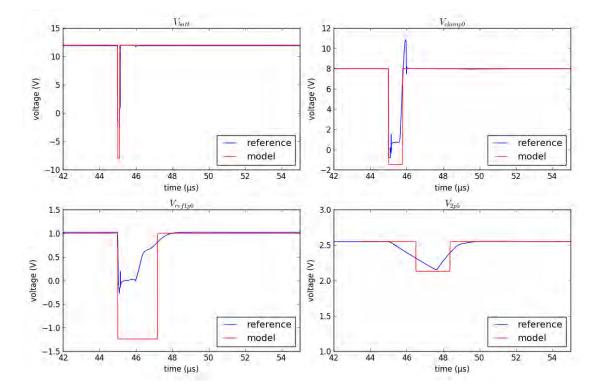

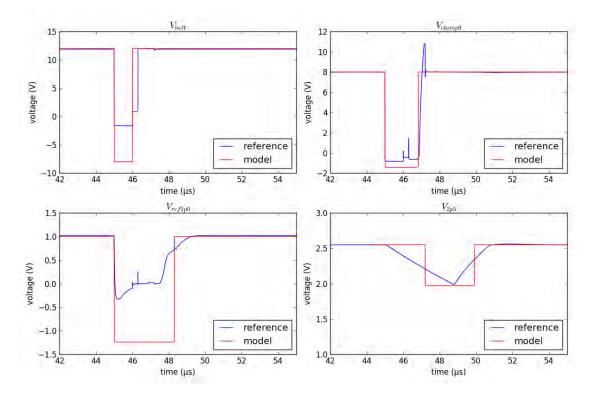

Figure 1.24: Equivalent time-sampler architecture from [58]