# Contribution à la continuité de service des convertisseurs statiques multiniveaux

Florent Becker

### ▶ To cite this version:

Florent Becker. Contribution à la continuité de service des convertisseurs statiques multiniveaux. Energie électrique. Université de Lorraine, 2017. Français. NNT: 2017LORR0202. tel-01813413

### HAL Id: tel-01813413 https://theses.hal.science/tel-01813413

Submitted on 12 Jun 2018

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **AVERTISSEMENT**

Ce document est le fruit d'un long travail approuvé par le jury de soutenance et mis à disposition de l'ensemble de la communauté universitaire élargie.

Il est soumis à la propriété intellectuelle de l'auteur. Ceci implique une obligation de citation et de référencement lors de l'utilisation de ce document.

D'autre part, toute contrefaçon, plagiat, reproduction illicite encourt une poursuite pénale.

Contact: ddoc-theses-contact@univ-lorraine.fr

### LIENS

Code de la Propriété Intellectuelle. articles L 122. 4

Code de la Propriété Intellectuelle. articles L 335.2- L 335.10

<a href="http://www.cfcopies.com/V2/leg/leg\_droi.php">http://www.cfcopies.com/V2/leg/leg\_droi.php</a>

<a href="http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm">http://www.culture.gouv.fr/culture/infos-pratiques/droits/protection.htm</a>

#### Université de Lorraine

Ecole Doctorale "Informatique – Automatique – Electrotechnique – Electronique – Mathématiques" Département de Formation Doctorale "Electrotechnique – Electronique"

### THESE

Présentée à

### L'Université de Lorraine

En vue de l'obtention du titre de

### DOCTEUR de l'Université de Lorraine Spécialité : Génie Electrique

Par Florent BECKER

## Contribution à la continuité de service des convertisseurs statiques multiniveaux

### Soutenue publiquement le 04 Décembre 2017

### Membres du Jury:

### **Rapporteurs:**

Eric Monmasson Professeur, SATIE – Université de Cergy-Pontoise

Mickael Hilairet Professeur, FEMSTO-ST - Université de Franche-Comté

### **Examinateurs:**

Betty Lemaire-Semail Professeur, L2EP – Université des Sciences et Technologies de Lille

Virginie Peron Ingenieur R&D – General Electric Renewable Energy - Nantes

Philippe Poure MDC-HDR, IJL - Université de Lorraine, Directeur de Thèse

Shahrokh Saadate Professeur, GREEN - Université de Lorraine, Co-directeur de Thèse

Thèse préparée au sein des Laboratoires IJL (Institut Jean Lamour) et GREEN (Groupe de Recherche en Electronique et Electrotechnique de Nancy) de l'Université de Lorraine.

### Remerciements

Les travaux de thèse présentés dans ce mémoire ont été effectués dans le cadre d'une collaboration entre l'Institut Jean Lamour (IJL) et le Groupe de Recherche en Electrotechnique et Electronique de Nancy (GREEN), tous deux laboratoires de l'Université de Lorraine. Je remercie M. Éric GAFFET et M. Bernard DAVAT, Professeurs à l'Université de Lorraine, respectivement Directeurs de l'IJL et du laboratoire GREEN, de m'avoir accueilli au sein de leurs laboratoires.

Je tiens, tout d'abord, à remercier et à exprimer ma profonde reconnaissance à Monsieur Philippe POURE pour avoir dirigé cette thèse. Ses précieux conseils, sa disponibilité ainsi que nos nombreuses discussions m'ont permis de progresser tout au long de ces travaux de thèse.

J'exprime mes sincères remerciements à Monsieur Shahrokh SAADATE, Professeur à l'Université de Lorraine, d'avoir bien voulu co-diriger ma thèse. Je le remercie également pour la confiance qu'il m'a constamment témoignée durant ces années.

Je tiens à exprimer ma profonde gratitude à Madame Betty LEMAIRE-SEMAIL, Professeur à Université des Sciences et Technologies de Lille, pour l'honneur qu'elle m'a fait, en acceptant de présider mon jury de thèse.

Je remercie également M. Eric MONMASSON et M. Mickael HILAIRET, respectivement Professeur à l'Université de Cergy-Pontoise et Professeur l'Université de Franche-Comté, d'avoir accepté d'être rapporteurs de cette thèse et pour l'intérêt qu'ils ont porté à l'évaluation de mes travaux de recherche.

Je tiens également à remercier Mme Virginie Peron, Ingénieur R&D chez General Electric Renewable Energy à Nantes d'avoir accepté d'examiner ma thèse et d'apporter sa vision industrielle sur mes travaux de recherche.

Un grand merci à tous mes collègues du GREEN, de l'IJL et de l'Université de Lorraine pour ces merveilleuses années passées à leurs côtés, aussi bien sur le plan recherche, avec nos nombreuses discussions, que sur le plan humain avec son lot de pause-café et de sorties. Merci à Michaël, Jimny, Nicolas, Julien, Eric, Ehsan, Mahmoud, Bashar, Rada, Lamia, Bastien, Raphael, Anis, Alex, Romain, Saima, Eber, Benjamin, Aina, Badr, Mohamed, Cihan, Stéphanie, Isabelle, Patrice, Pierre, Christine, Jean Leveque, Malika Hinaje, Smail Mezani, Bruno Douine, Thierry Lubin ,Gaëtan Didier, Kévin Berger, Hocine Menana, Francis Weinachter, Patrick Schweitzer, Djilali Kourtiche, Slavisa Jovanovic, Laouès Guendouz, Yves Berviller, Serge Weber, Etienne Tisserand. Merci également à tous ceux ce que j'aurais pu oublier.

Finalement, je tiens à remercier du plus profond de mon cœur mes parents, mes frères, ainsi que l'ensemble de ma famille et de mes amis proches pour leur soutien inconditionnel. La question " Tu soutiens quand ? " a enfin eu sa réponse. Merci à tous.

### Table des matières

| Table des matières                                                                          | iv |

|---------------------------------------------------------------------------------------------|----|

| Chapitre I - Convertisseurs multiniveaux : Structures et contrôle                           | 1  |

| 1. Introduction                                                                             | 2  |

| 2. Topologies de base des convertisseurs de tension                                         | 3  |

| 2.1. Le convertisseur deux niveaux                                                          | 3  |

| 2.2. Les Convertisseurs 3 niveaux                                                           | 4  |

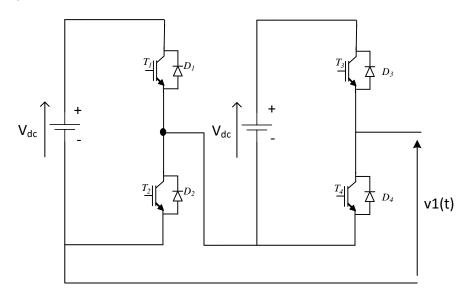

| 2.2.1. Structure basée sur deux demi-ponts en H                                             | 4  |

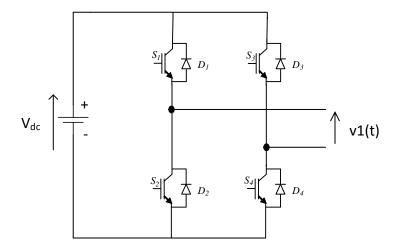

| 2.2.2. Structure Pont en H                                                                  | 5  |

| 2.2.3. Structure à capacité flottante                                                       | 6  |

| 2.2.4. Structure à fractionnement du bus continu                                            | 9  |

| 2.2.4.1. Structure Neutral Point Clamped ou NPC                                             | 9  |

| 2.2.4.2. Structure Active Neutral Point Clamped ou ANPC                                     | 12 |

| 2.2.4.3. Structure Neutral Point Piloted ou NPP                                             | 15 |

| 2.2.5. Étude comparative des différents convertisseurs étudiés                              | 19 |

| 3. Familles de convertisseurs multiniveaux                                                  | 21 |

| 3.1. Structures avec fractionnement du bus continu                                          | 21 |

| 3.1.1. Topologie NPC                                                                        | 22 |

| 3.1.2. Topologie FC                                                                         | 24 |

| 3.2. Structures type « Modulaire»                                                           | 25 |

| 3.2.1. Convertisseur Modulaire à base de Pont en H                                          | 25 |

| 3.2.2. Convertisseur Modulaire à base de Demi-ponts en H                                    | 27 |

| 4. Contrôle des convertisseurs multiniveaux                                                 | 28 |

| 4.1. PWM sinusoïdale ou sous-harmonique (PS-PWM)                                            | 29 |

| 4.2. PWM à sélection d'harmoniques à éliminer (SHE-PWM)                                     | 29 |

| 4.3. PWM vectorielle (SV-PWM)                                                               | 30 |

| 4.4. Level-shifted Modulation (LS-PWM)                                                      | 31 |

| 4.5. Conclusion                                                                             | 32 |

| Chapitre II : Contrôle à nombre minimal de commutations pour les structures HB-NPC et HB-T- |    |

| Type                                                                                        |    |

| 1. Introduction                                                                             |    |

| 2. Simulation d'un convertisseur HB-NPC à 5 niveaux, commandé en LS-PWM                     |    |

| 2.1. Description du système                                                                 | 36 |

| 2.2.    | Résultats de simulation                                                              | 39         |

|---------|--------------------------------------------------------------------------------------|------------|

| 2.3.    | Possibilité de réduction du nombre de commutations                                   | 40         |

| 2.3.1.  | Principe général de la minimisation des commutations                                 | 43         |

| 2.3.1.  | 1. Reconstitution du niveau de tension $V_0^*$                                       | 44         |

| 2.3.1.2 | 2. Recherche de la trajectoire à nombre minimal de commutations                      | 44         |

| 3. C    | Cas du HB-NPC à 5 niveaux avec minimisation des commutations                         | 46         |

| 3.1.    | Niveaux de tension et composants passants                                            | 46         |

| 3.2.    | Trajectoires à nombre minimal de commutations                                        | 47         |

| 3.3.    | Résultats de simulation avec optimisation du nombre de commutations                  | 53         |

| 3.4.    | Cas du HB-NPC à 5 niveaux avec minimisation des commutations – Résultats expe<br>56  | érimentaux |

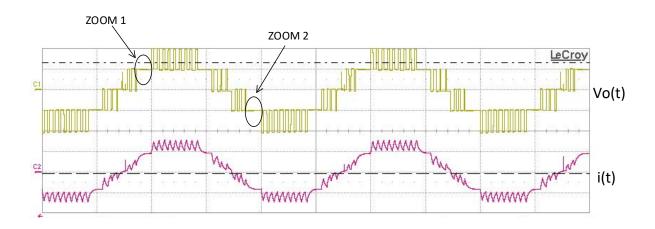

| 3.4.1.  | Résultats expérimentaux avec un contrôle LS-PWM                                      | 58         |

| 3.4.2.  | Résultats expérimentaux avec un contrôle OPT-PWM                                     | 60         |

| 4. C    | Cas du HB-T-Type à 5 niveaux avec minimisation des commutations                      | 63         |

| 4.1.    | Niveaux de tension et composants passants                                            | 63         |

| 4.2.    | Résultats de simulation                                                              | 67         |

| 4.2.1.  | Simulation du HB-T-Type avec une commande de type LS-PWM                             | 67         |

| 4.2.2.  | Simulation du HB-T-Type avec minimisation des commutations                           | 71         |

| 4.3.    | Résultats expérimentaux                                                              | 73         |

| 4.3.1.  | HB-T-Type commandé par LS-PWM                                                        | 73         |

| 4.3.2.  | HB-T-Type avec minimisation des transitions.                                         | 76         |

| 5. C    | Conclusion                                                                           | 79         |

| Cha     | apitre III : Continuité de service des convertisseurs multiniveaux – Etat de l'art   | 80         |

| 1. Ir   | ntroduction                                                                          | 81         |

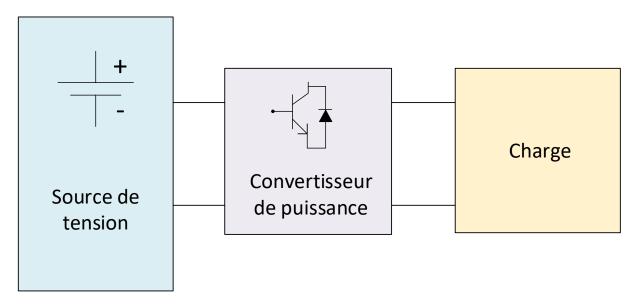

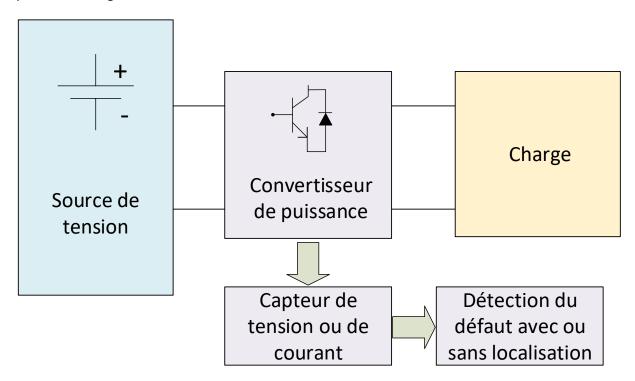

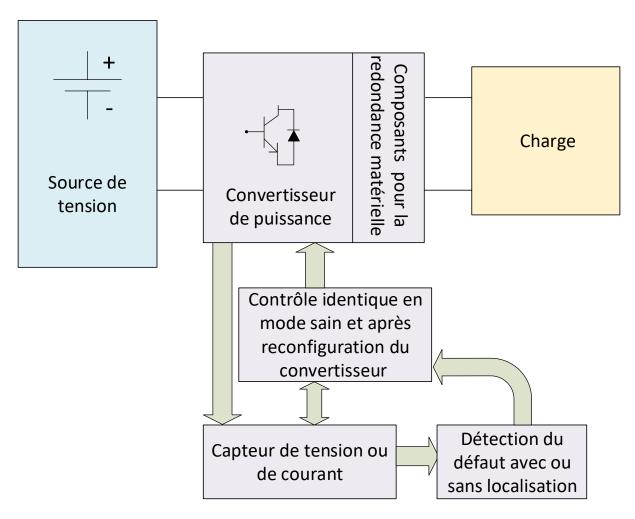

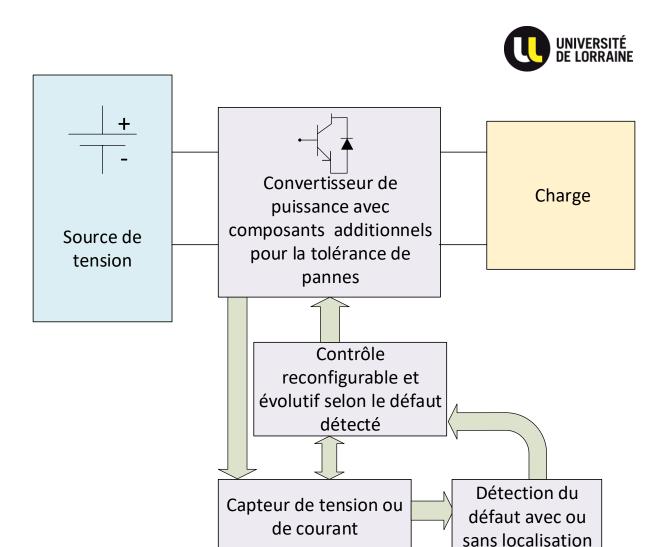

| 2. C    | Continuité de service des convertisseurs                                             | 81         |

| 2.1.    | Diagnostic                                                                           | 82         |

| 2.2.    | Reconfiguration                                                                      | 83         |

| 3. D    | Diagnostic de défauts dans les convertisseurs multiniveaux de types NPC, ANPC, NPP ( | T-Type).85 |

| 3.1.    | Détection de défaut se basant sur les courants                                       | 86         |

| 3.1.1.  | Algorithme de détection basé sur les courants de Park                                | 86         |

| 3.1.2.  | Détection sans utilisation des courants de Park                                      | 88         |

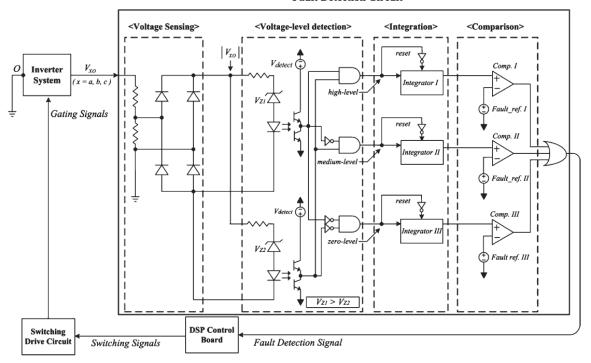

| 3.2.    | Détection de défaut se basant sur les tensions                                       | 89         |

| 3.2.1.  | Détection de défaut avec ajout de capteurs                                           | 89         |

| 3.2.2.  | Détection de défaut sans ajout de capteur                                            | 91         |

| 3.3.  | Conclusion                                                                                                    | 92    |

|-------|---------------------------------------------------------------------------------------------------------------|-------|

| 4.    | Topologies de convertisseurs multiniveaux NPC, ANPC et NPP (T-Type) à tolérance de panne                      | s. 92 |

| 4.1.  | Introduction                                                                                                  | 92    |

| 4.2.  | Structures NPC à tolérance de pannes sans IGBT additionnel                                                    | 93    |

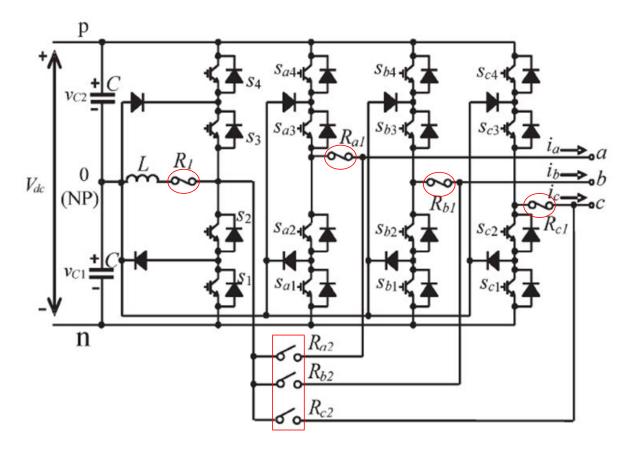

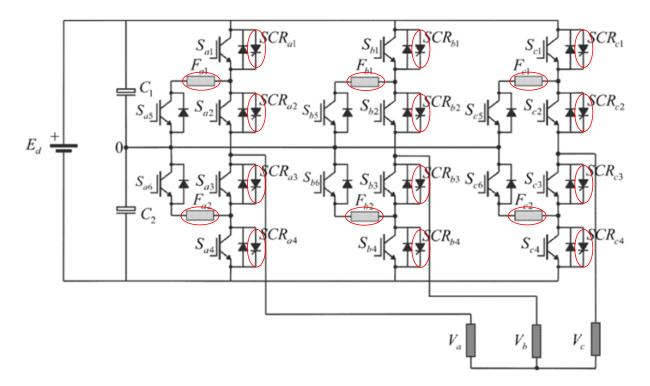

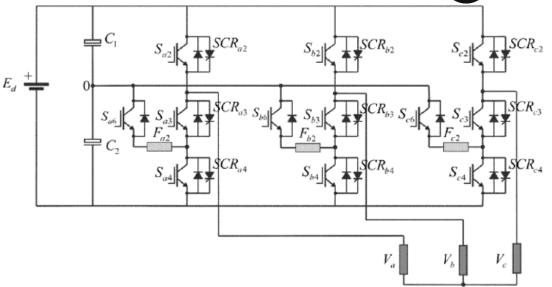

| 4.2.1 | 1. Utilisation de 3 paires de thyristors additionnels                                                         | 93    |

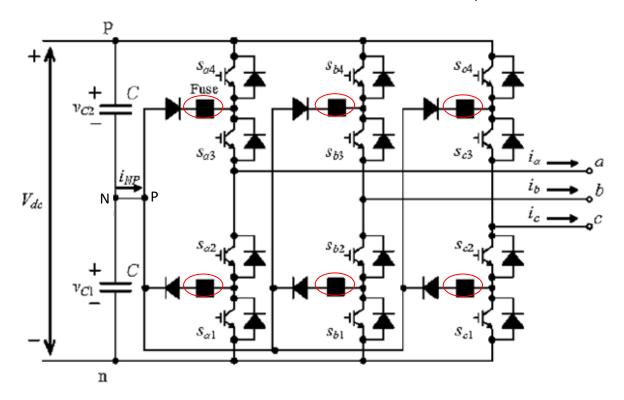

| 4.2.2 | 2. Utilisation de fusibles additionnels uniquement                                                            | 95    |

| 4.2.3 | 3. Utilisation de fusibles associés à des thyristors                                                          | 96    |

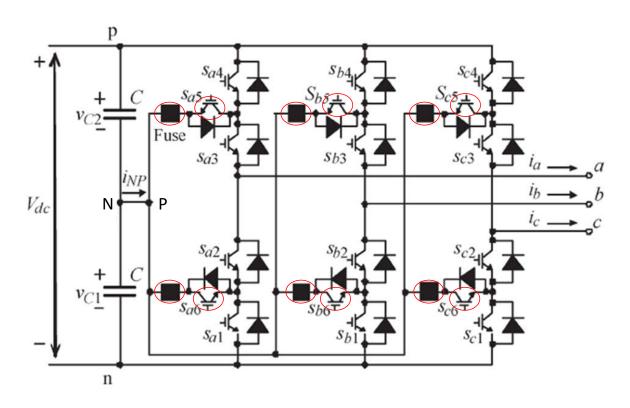

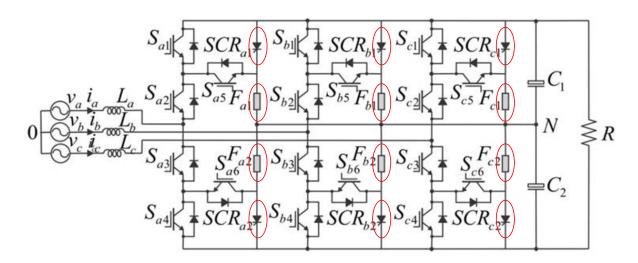

| 4.3.  | Structure NPC à tolérance de pannes avec ajout d'IGBT                                                         | 97    |

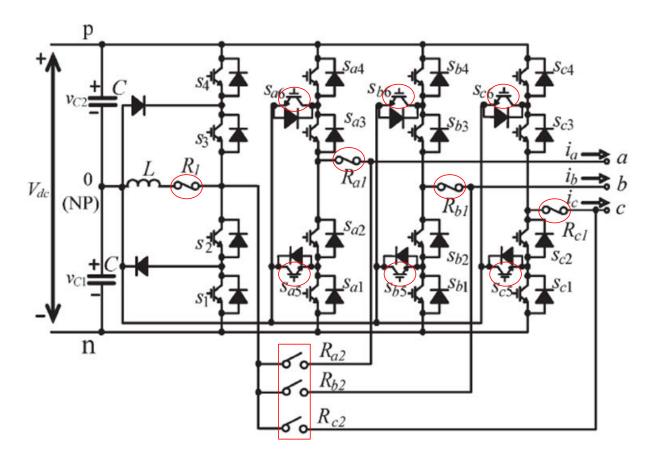

| 4.3.1 | 1. IGBT additionnel pour garantir un fonctionnement en mode nominal après défaut                              | 97    |

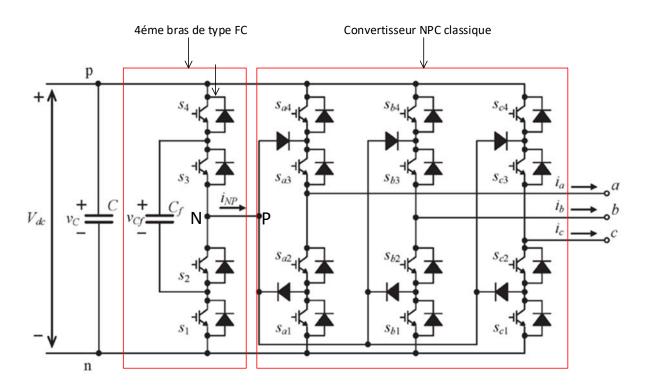

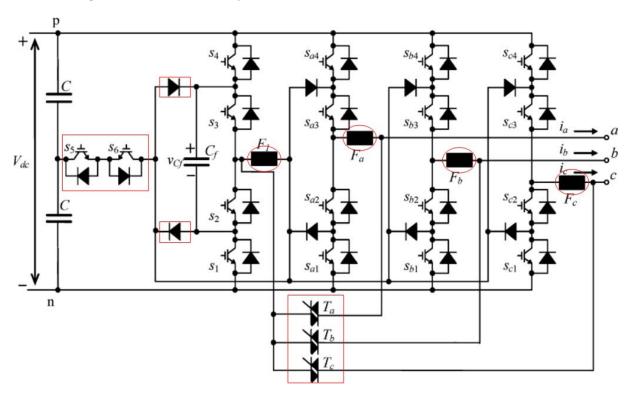

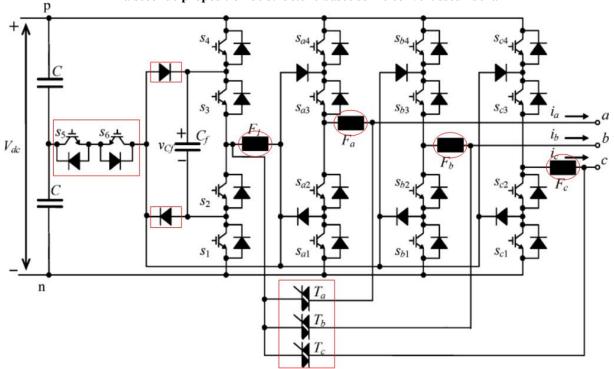

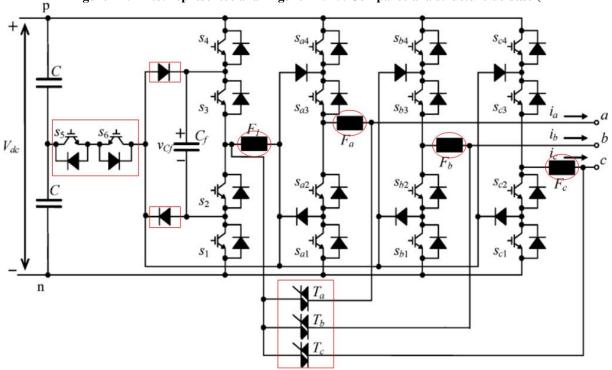

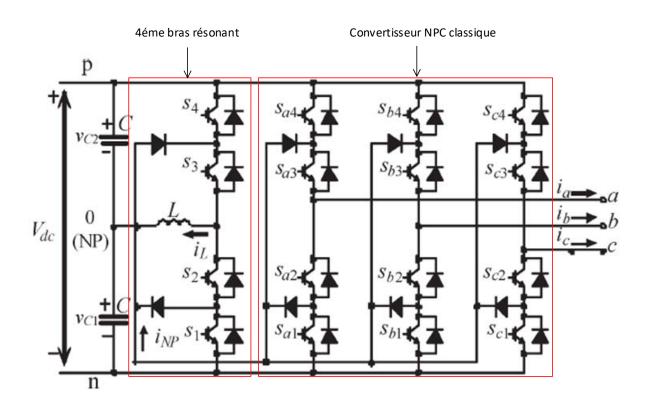

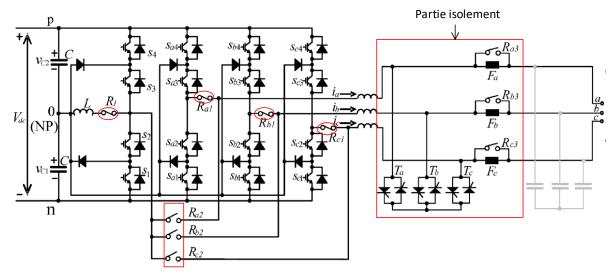

| 4.3.2 | 2. IGBT additionnels utilisés en mode sain comme 4 <sup>ème</sup> bras de type FC                             | 99    |

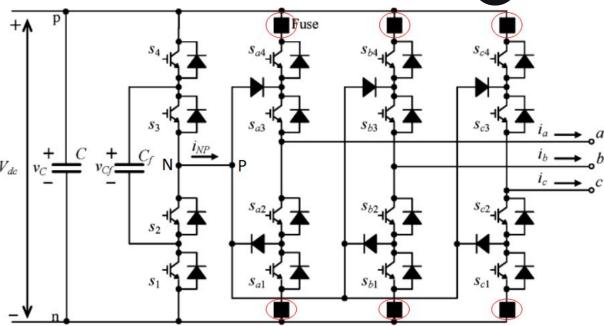

| 4.3.3 | 3. IGBT additionnels utilisés en mode sain comme 4 <sup>ème</sup> bras résonnant                              | . 103 |

| 4.3.3 | 3.1. Structures basées sur l'ajout de contacteurs                                                             | . 104 |

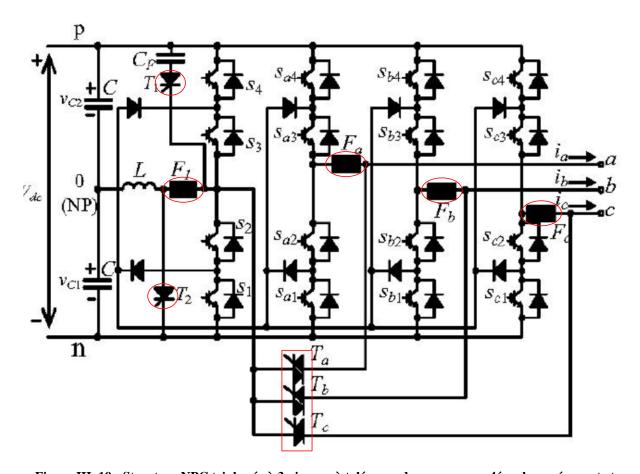

| 4.3.3 | 3.2. Structure basée sur l'ajout de fusibles et de thyristors                                                 | . 107 |

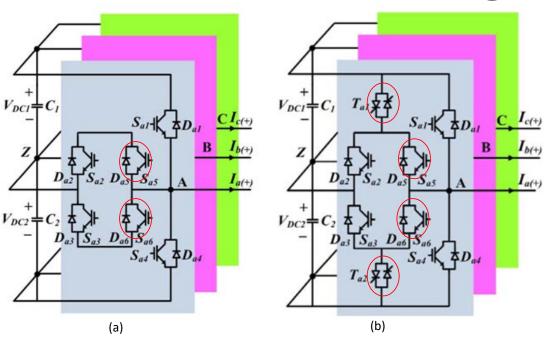

| 4.4.  | Structures ANPC et T-type à tolérance de pannes sans ajout d'IGBT                                             | . 108 |

| 4.4.1 | 1. Utilisation de fusibles associés à des thyristors                                                          | . 108 |

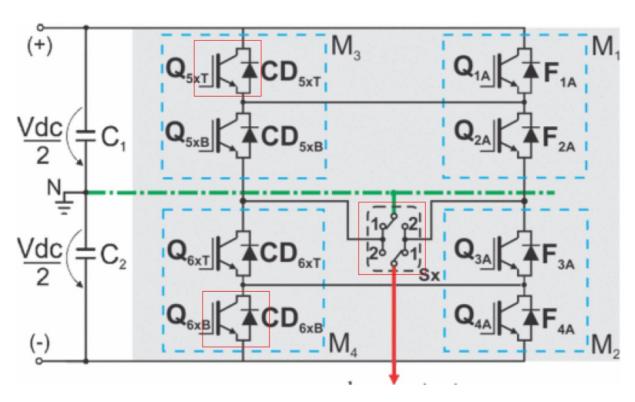

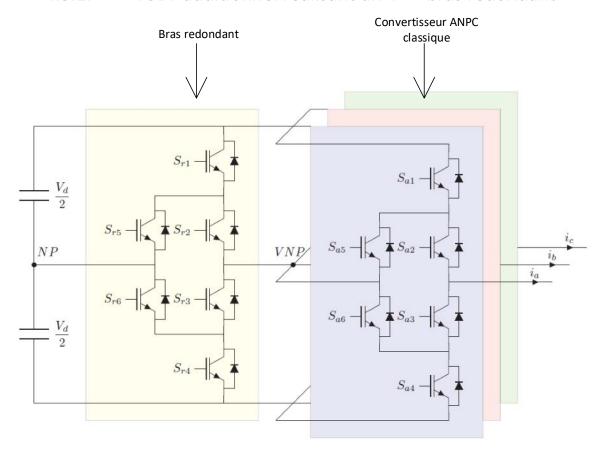

| 4.5.  | Structure ANPC et T-type à tolérance de pannes avec ajout d'IGBT                                              | . 110 |

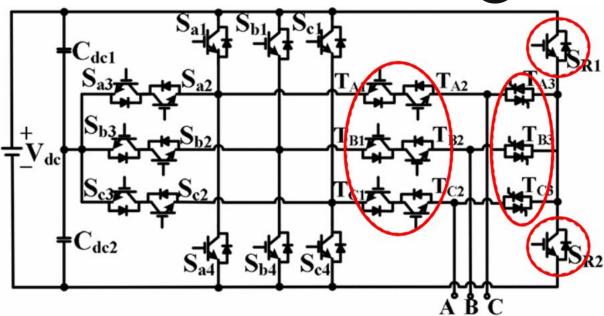

| 4.5.1 | 1. IGBT additionnels pour garantir le fonctionnement à puissance nominale après défaut .                      | . 110 |

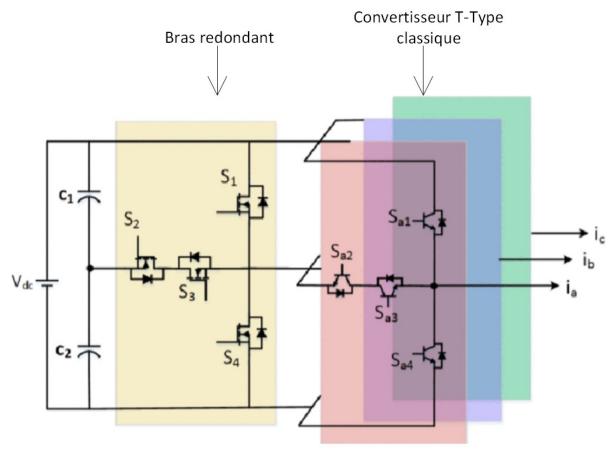

| 4.5.2 | 2. IGBT additionnel réalisant un 4 <sup>éme</sup> bras redondant                                              | . 113 |

| 4.6.  | Bilan des topologies à tolérance de pannes                                                                    | . 114 |

| 5.    | Conclusion                                                                                                    | . 117 |

|       | HAPITRE IV : Continuité de service de convertisseurs multiniveaux de type Pont en H, à struct<br>PP ou T-type |       |

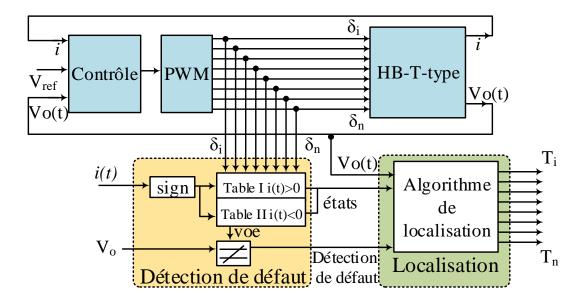

| 1.    | Introduction                                                                                                  | . 120 |

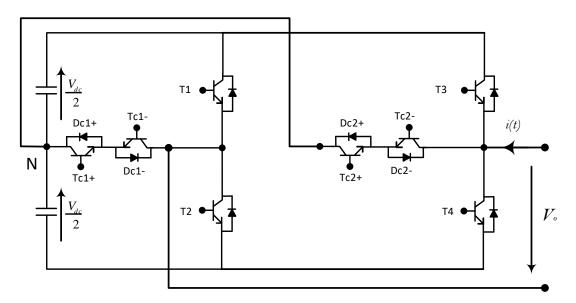

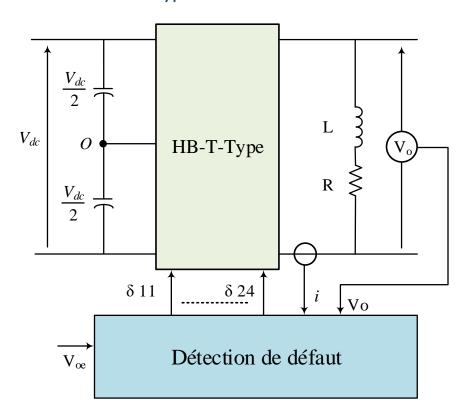

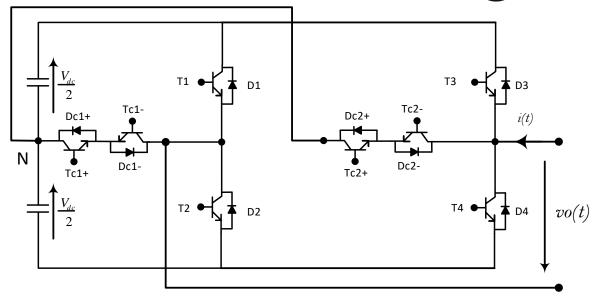

| 2.    | Convertisseurs étudiés                                                                                        | . 121 |

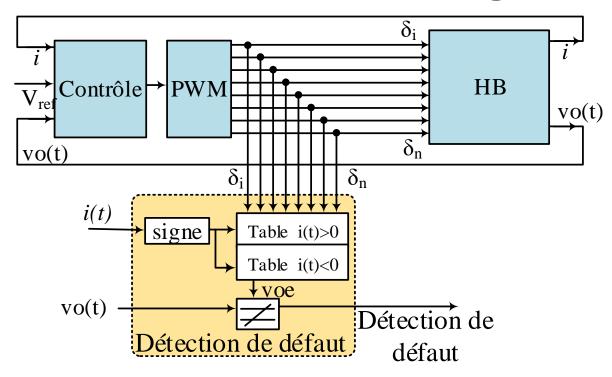

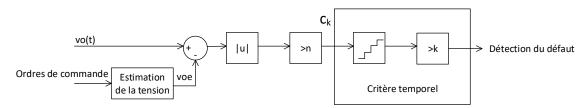

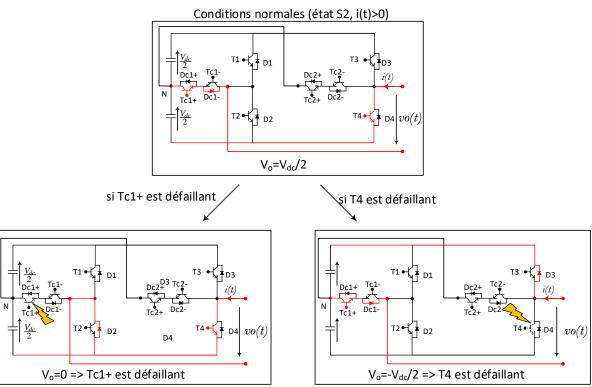

| 3.    | Détection d'un défaut de type circuit ouvert                                                                  | . 123 |

| 3.1.  | Principe général de la détection pour un « Pont en H »                                                        | . 123 |

| 3.2.  | Résultats de Modélisation/Simulation dans le cas du convertisseur HB-T-Type                                   | . 126 |

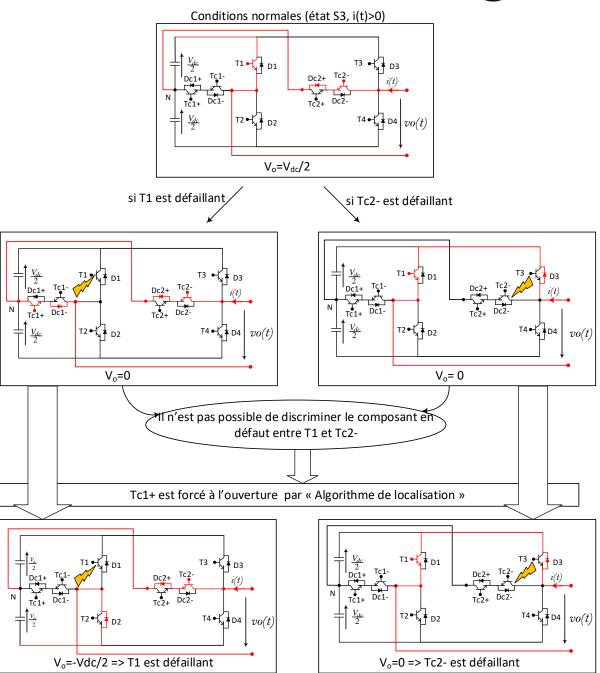

| 4.    | Localisation d'un défaut de type circuit ouvert dans le cas du convertisseur HB-T-Type                        | . 130 |

| 4.1.  | Méthode de localisation                                                                                       | . 130 |

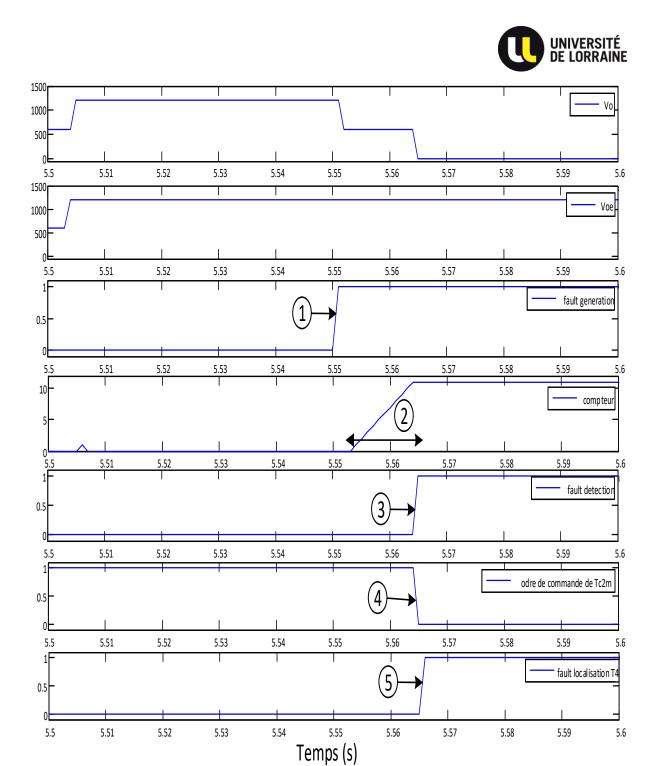

| 4.2.  | Résultats de Modélisation/Simulation                                                                          | . 136 |

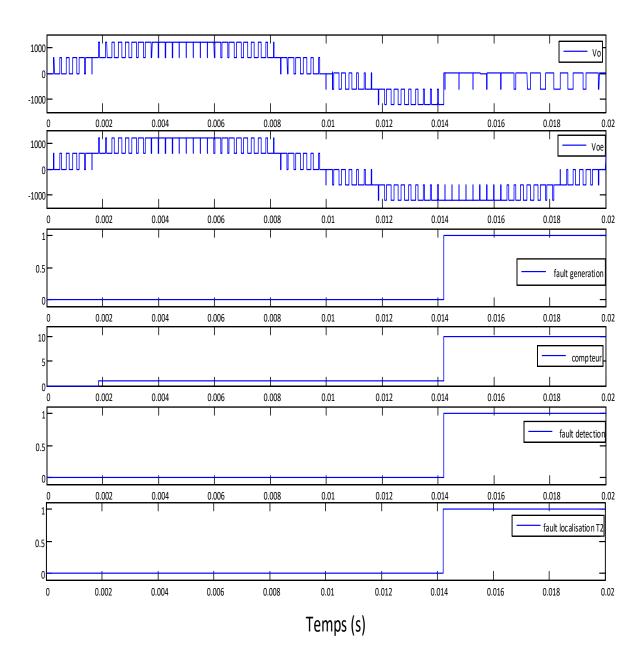

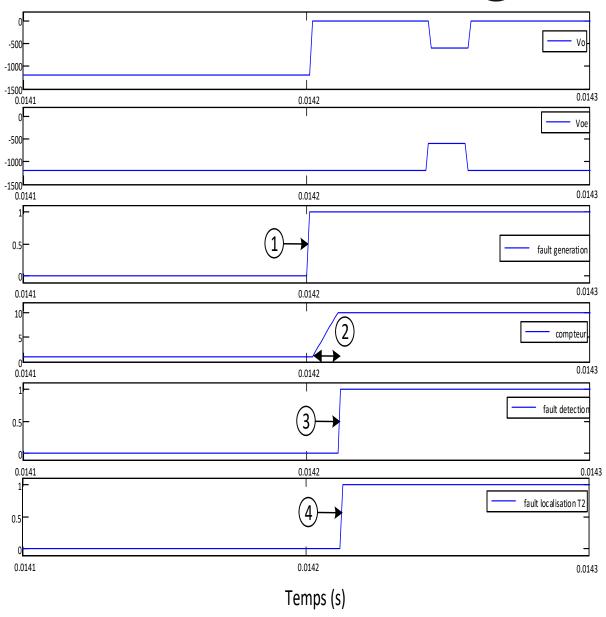

| 4.2.1 | 1. Défaut circuit ouvert dans l'état S3                                                                       | . 137 |

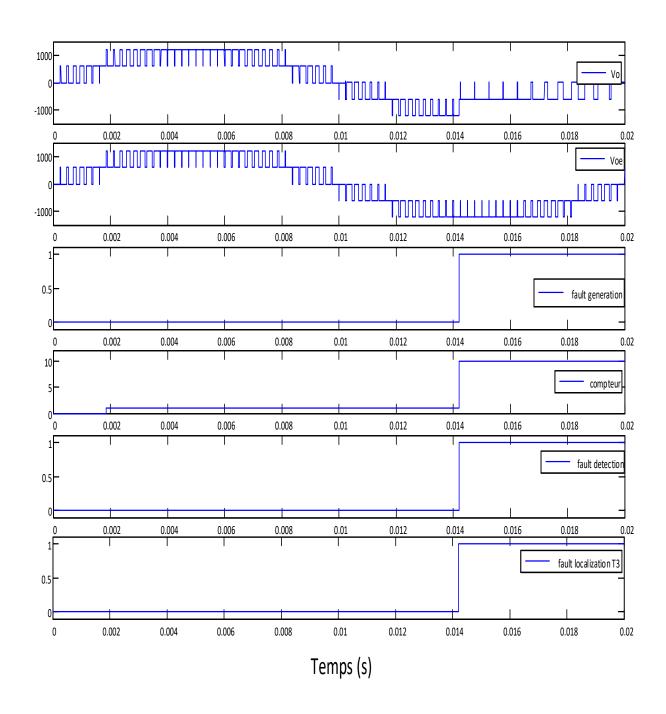

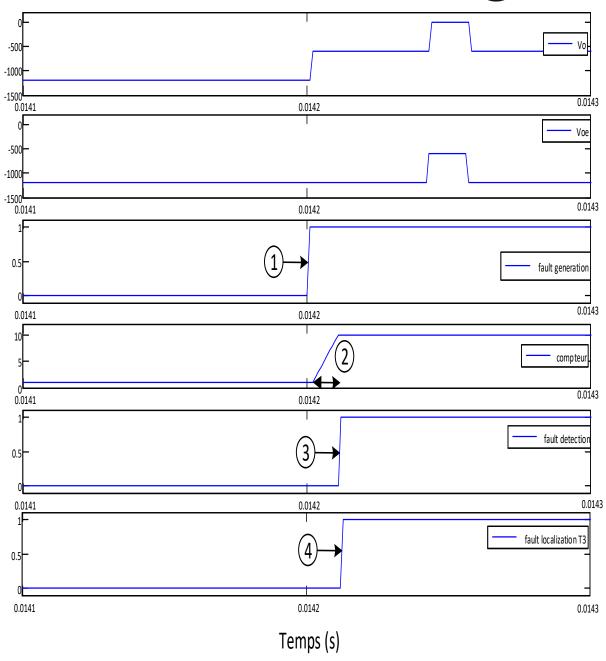

| 4.2.2 | 2. Défaut circuit ouvert dans l'état S18                                                                      | . 141 |

| 5.    | Garantie de la continuité de service par reconfiguration du convertisseur HB-T-type                           | . 146 |

| 5.1.  | Topologie de convertisseur HB-T-Type à tolérance de pannes et contrôle associé                                | . 146 |

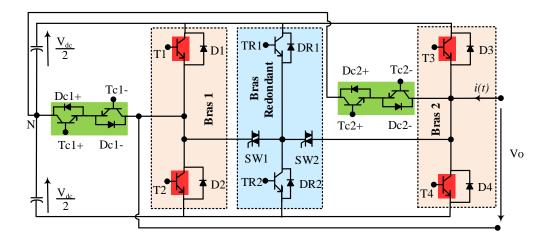

| 5.1.2         | L.         | Topologie HB-T-Type à tolérance de pannes                                                       | 146  |

|---------------|------------|-------------------------------------------------------------------------------------------------|------|

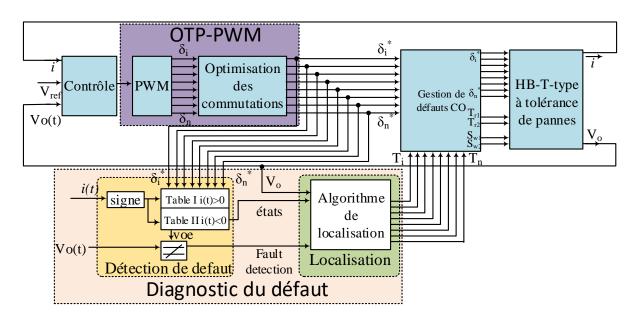

| 5.1.2         | 2.         | Contrôle et gestion des défauts                                                                 | 147  |

| 5.2.          | R          | ésultats de Modélisation/Simulation                                                             | 150  |

| 5.2.          | l.         | Exemple de reconfiguration de la commande lors du défaut CO d'un switch horizontal              | 150  |

| 5.2.2<br>vert |            | Exemple de reconfiguration matérielle du convertisseur lors du défaut CO d'un sw<br>152         | itch |

| 6.            | Con        | clusion                                                                                         | 154  |

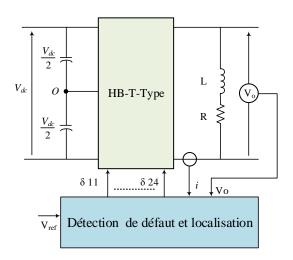

| CI            | HAPI       | TRE V : Validation expérimentale du convertisseur HB-T-Type à tolérance de pannes               | 158  |

| 1.            | Intr       | oduction                                                                                        | 159  |

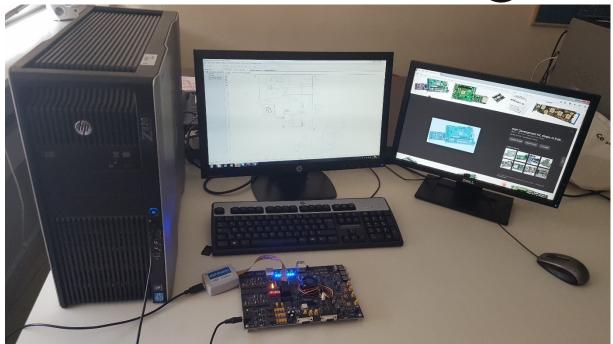

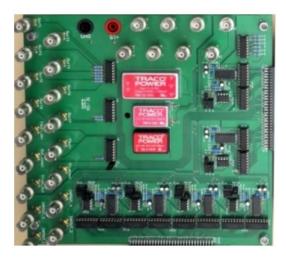

| 2.            | Cho<br>160 | oix technologiques pour l'implantation du contrôle, du diagnostic de défaut et de sa ges        | tion |

| 3.            | Mét        | thodologie de Prototypage de l'implantation sur cible FPGA                                      | 161  |

| 3.1.          | Р          | remière étape : simulation fonctionnelle                                                        | 163  |

| 3.2.          | D          | euxième étape : simulation mixte                                                                | 163  |

| 3.3.          | Т          | roisième étape : le Prototypage "FPGA in the loop"                                              | 163  |

| 3.4.          | С          | Quatrième étape : validation entièrement expérimentale                                          | 165  |

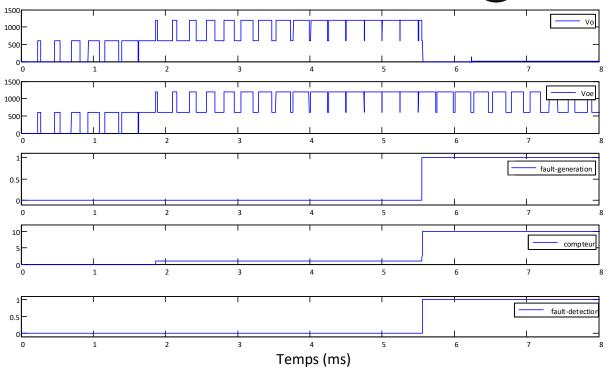

| 4.<br>tolé    |            | pe de validation intermédiaire par prototypage « FPGA in the loop » du HB-T-Type<br>e de pannes |      |

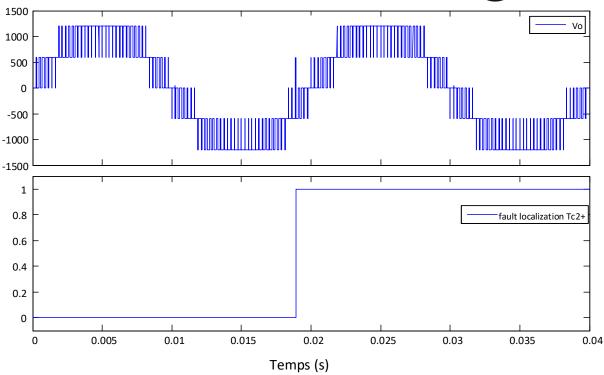

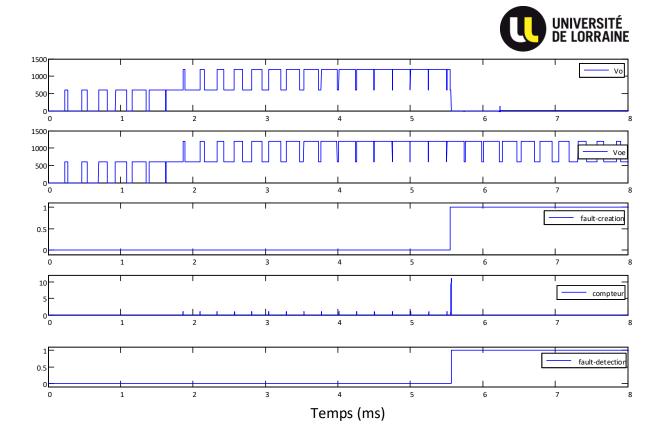

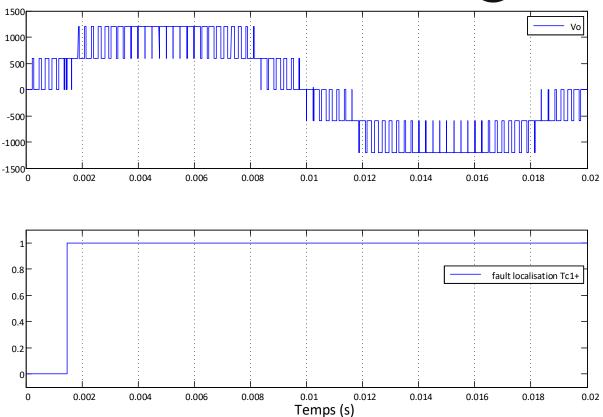

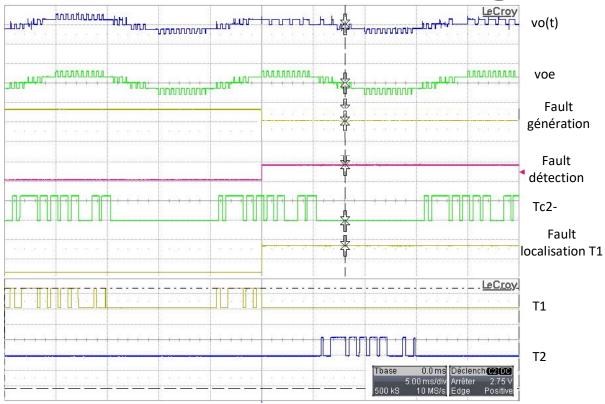

| 4.1.          | R          | ésultats de Prototypage "FPGA in the Loop"                                                      | 166  |

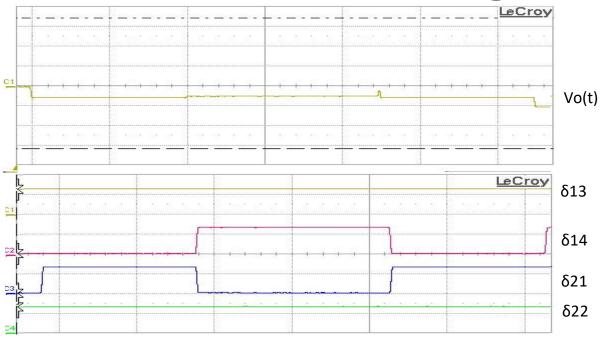

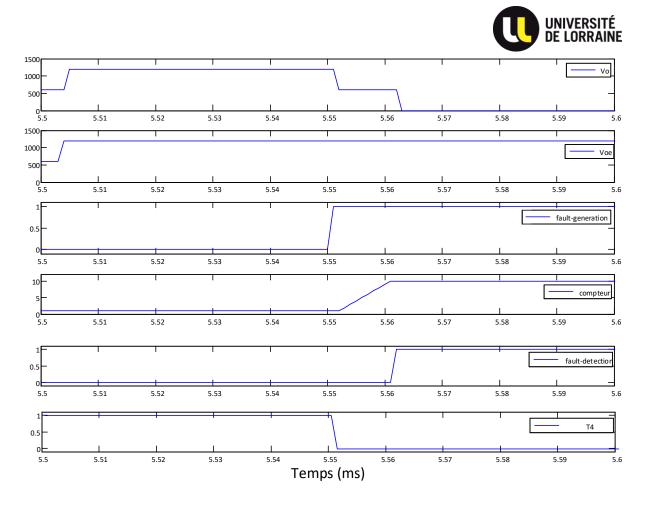

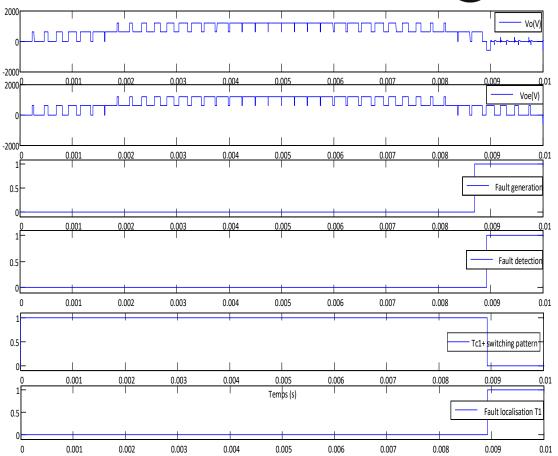

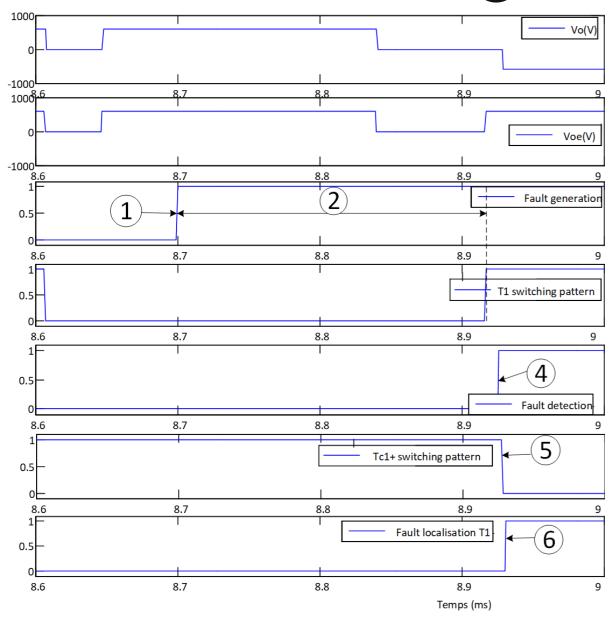

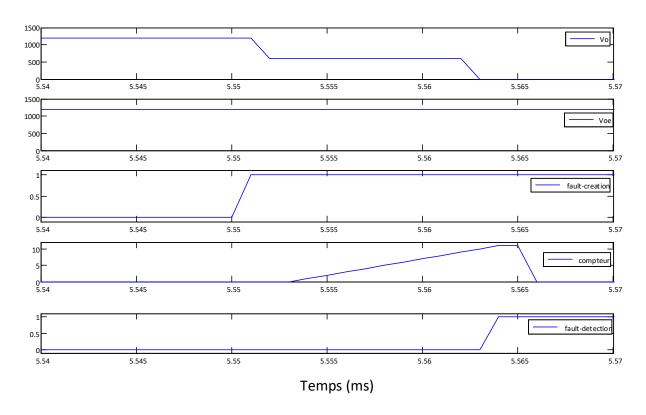

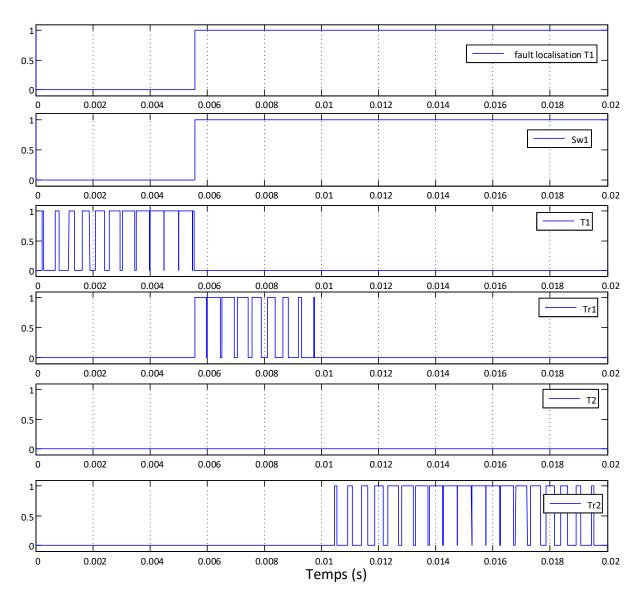

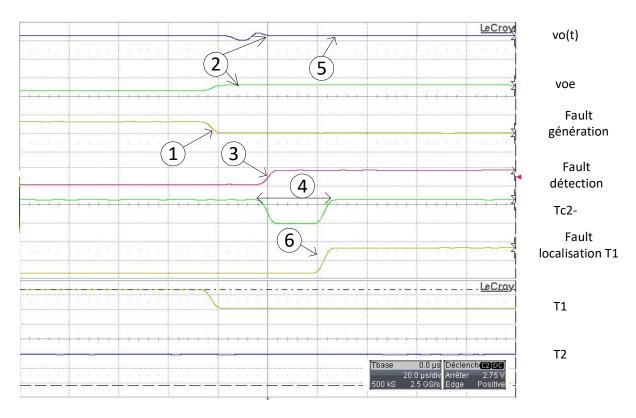

| 4.1.          | l.         | Résultats issu du Prototypage "FPGA in the Loop" pour la détection de défaut                    | 166  |

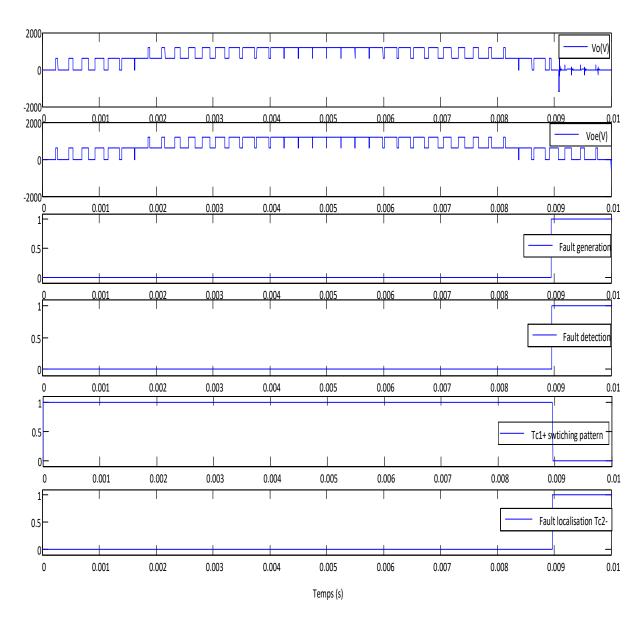

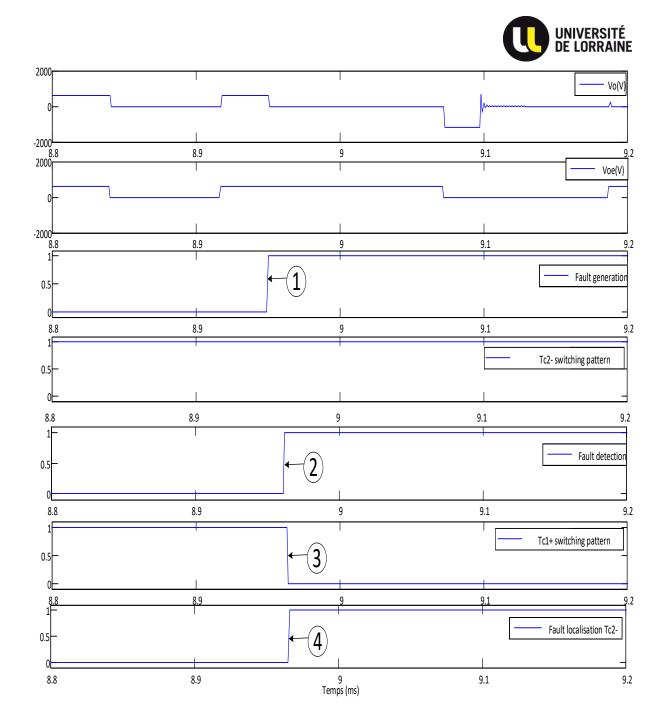

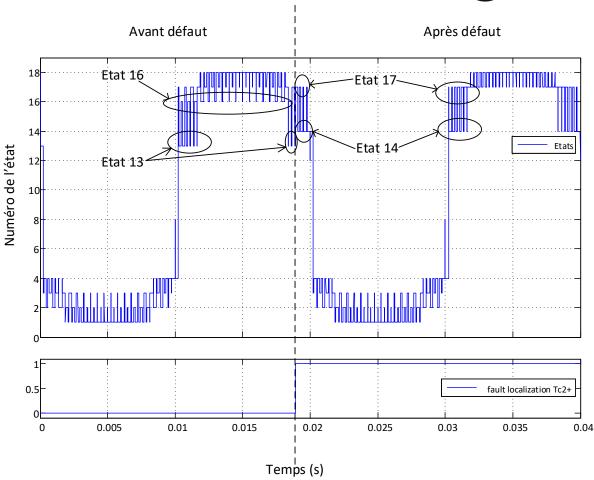

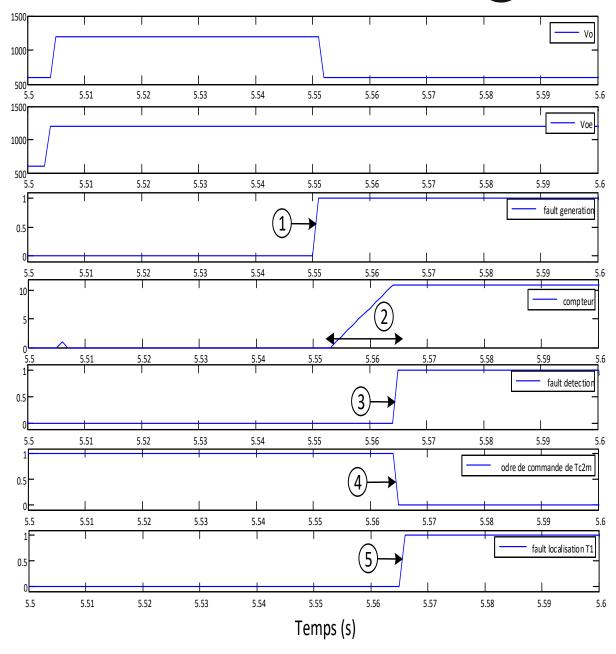

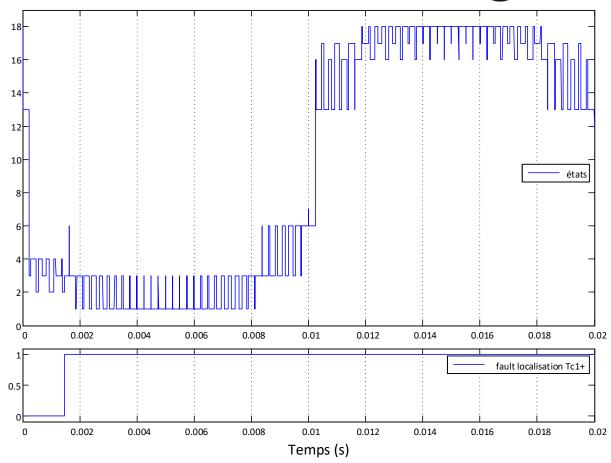

| 4.2.          | R          | ésultats issu du Prototypage "FPGA in the Loop" pour la localisation                            | 168  |

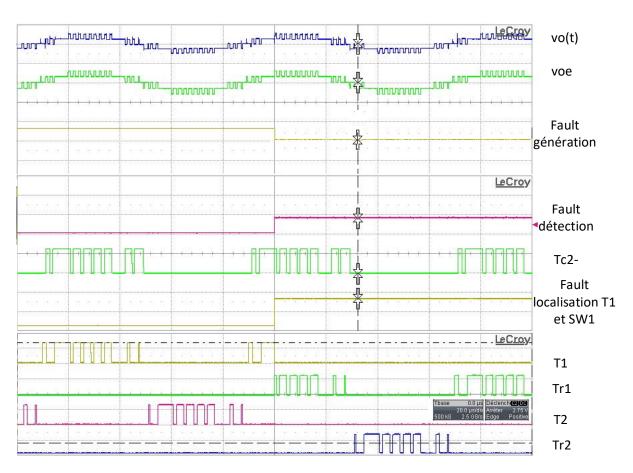

| 4.3.          | R          | ésultats issus du Prototypage "FPGA in the Loop" pour la reconfiguration                        | 171  |

| 4.3.2         | l.         | Reconfiguration avec redondance matérielle                                                      | 171  |

| 4.3.2         | 2.         | Reconfiguration sans redondance matérielle                                                      | 172  |

| 4.5           | С          | onclusion                                                                                       | 174  |

| 5.            | Rés        | ultats expérimentaux                                                                            | 175  |

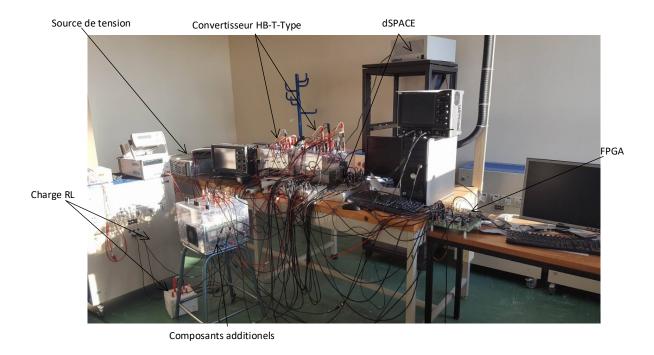

| 5.1.          | D          | escription du banc de test expérimental                                                         | 175  |

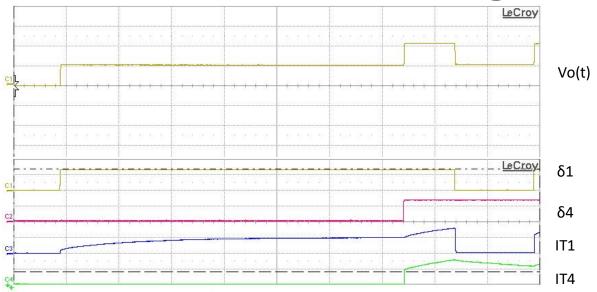

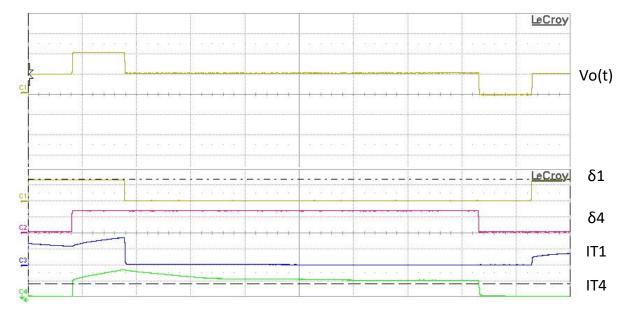

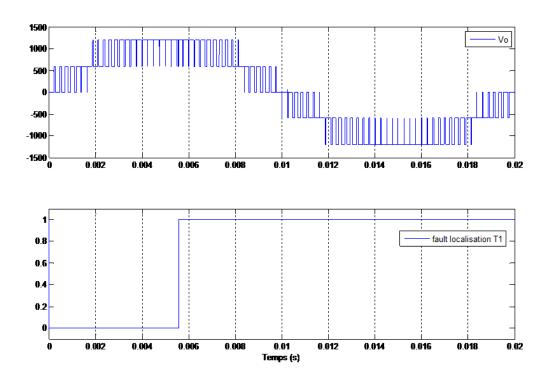

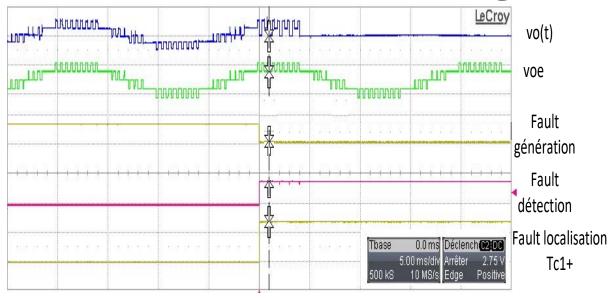

| 5.2.<br>reco  |            | ésultats expérimentaux suite à un défaut CO du switch horizontal TC1+ : diagnosti-<br>uration   |      |

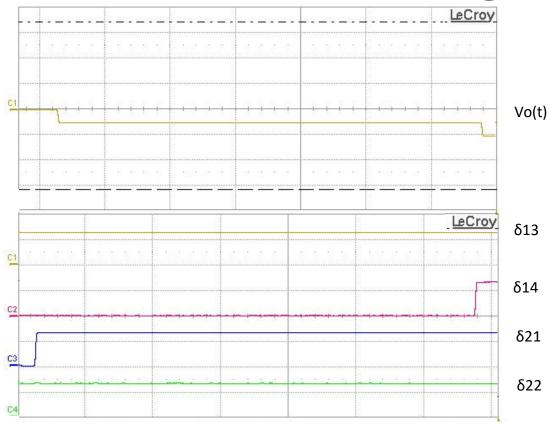

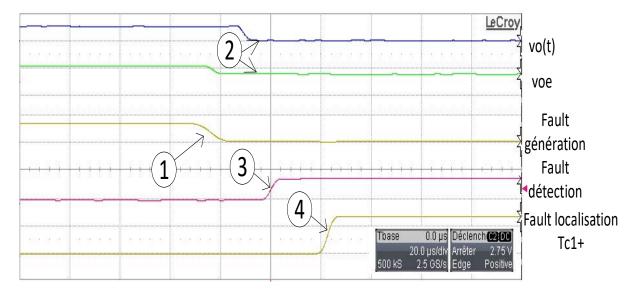

| 5.2.2         | l.         | Diagnostic d'un défaut CO du switch Tc1+                                                        | 177  |

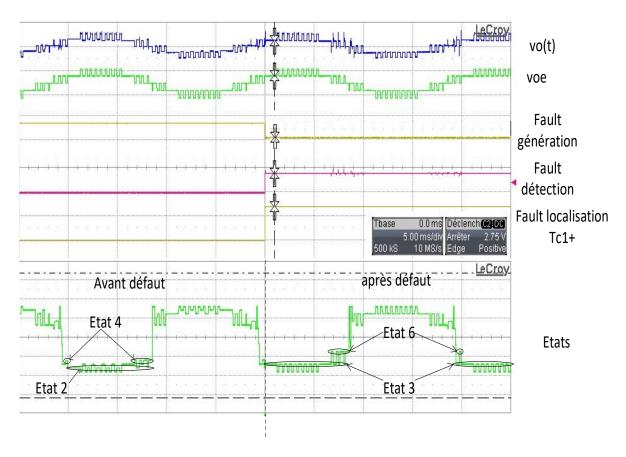

| 5.2.2         | 2.         | Reconfiguration suite à un défaut localisé sur TC1+                                             | 178  |

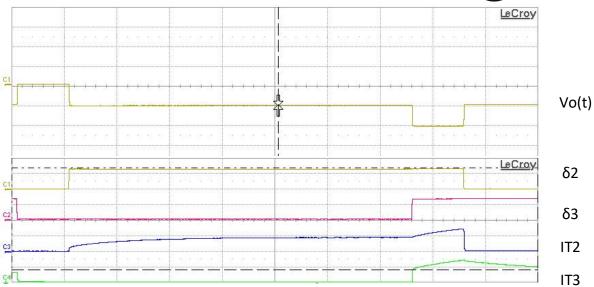

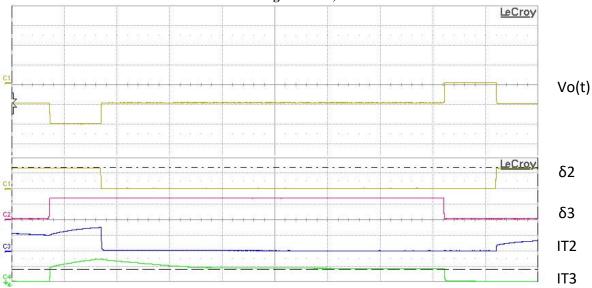

| 5.3.          | R          | ésultat expérimental : défaut CO d'un switch vertical                                           | 179  |

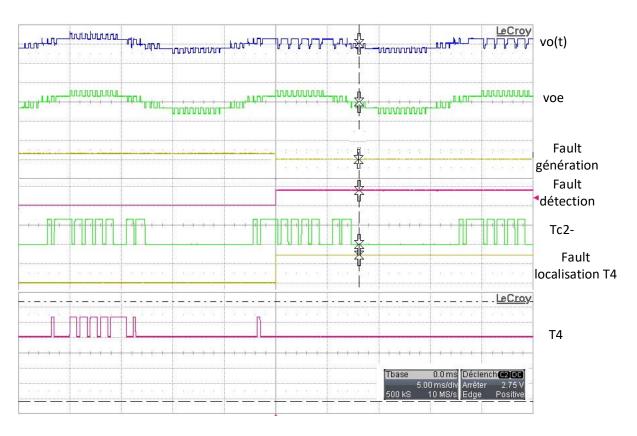

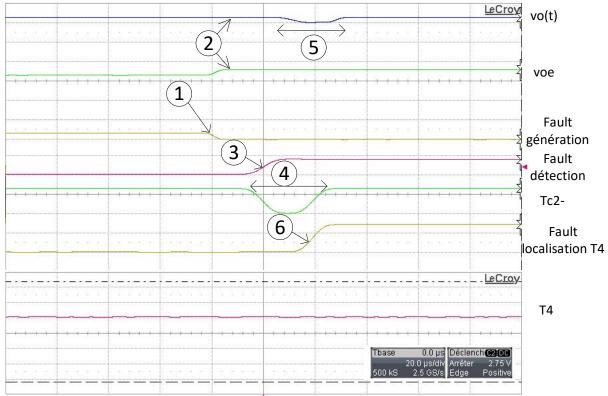

| 5.3.2         | l.         | Diagnostic d'un défaut CO du switch T4                                                          | 180  |

| 5.3.2         | 2.         | Diagnostic d'un défaut CO du switch T1                                                          | 181  |

| 5.3.3. | Reconfiguration du convertisseur su | iite à la détection | d'un défaut CO | du switch vertical T1 |

|--------|-------------------------------------|---------------------|----------------|-----------------------|

|        | 183                                 |                     |                |                       |

| 6. | . Conclusion                        | 184 |

|----|-------------------------------------|-----|

|    | Conclusion générale et perspectives | 185 |

|    | Ribliographie                       | 180 |

### **Nomenclature**

E, V<sub>dc</sub>: Tension aux bornes du bus continu

T<sub>ij</sub>: Transistor

$\delta_{ij}$ : Ordre de commande envoyé au transistor  $T_{ij}$

D<sub>ii</sub>: Diode

Vo(t): Tension instantanée en sortie d'un convertisseur

i(t): Courant instantané en sortie d'un convertisseur

C: Condensateur

NPC: Neutral Point Clamped (point neutre clampé)

ANPC: Active Neutral Point Clamped (point neutre clampé activement)

NPP: Neutral Point Piloted (point neutre piloté)

FC: Flying Capacitor (capacité flottante)

THD: Taux de Distorsion Harmonique

MMC: Modular Multilevel Converter (convertisseur modulaire multiniveaux)

PWM: Pulse Width Modulation (Modulation à largeur d'impulsions MLI)

LS-PWM: Level-Shifted Modulation (modulation pleine onde)

PS-PWM: Phase-Shited Modulation

SHE-PWM: Selective Harmonic Elimination Modulation (Modulation à élimination d'harmoniques)

SV-PWM: Space Vector Modulation (modulation à vecteur d'états)

OPT-PWM: modulation optimisée proposée dans ce mémoire

NOC : nombre de commutations

NOT : nombre de trajectoires

NOC<sub>total</sub>: Nombre total de commutations

### Table des illustrations

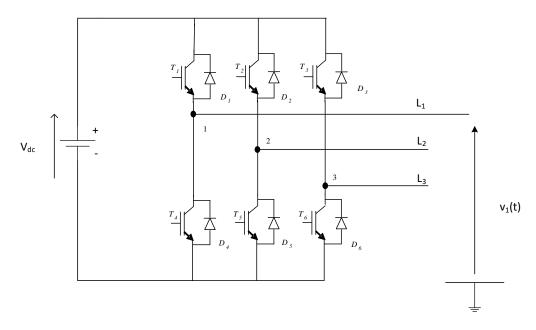

| Figure I.1 : Convertisseur 2 niveaux.                                                                                  | 3     |

|------------------------------------------------------------------------------------------------------------------------|-------|

| Figure I.2: Tension de sortie d'une phase d'un convertisseur 2 niveaux                                                 | 3     |

| Figure I.3: Mise en série de deux demi-ponts en H                                                                      | 4     |

| Figure I.4 : Convertisseur Pont en H                                                                                   | 5     |

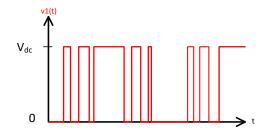

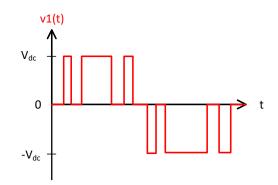

| Figure I.5 : Forme d'onde typique de la tension de sortie d'un pont en H                                               | 5     |

| Figure I.6: Structure triphasée 3 niveaux à capacités flottantes                                                       | 6     |

| Figure I.7: Représentation équivalente d'une phase du convertisseur 3 niveaux à capacités flottai                      | ntes  |

| par deux cellules de commutation                                                                                       | 7     |

| Figure I.8 : Séquences de conduction d'un FC 3 niveaux (cas de la phase a)                                             | 8     |

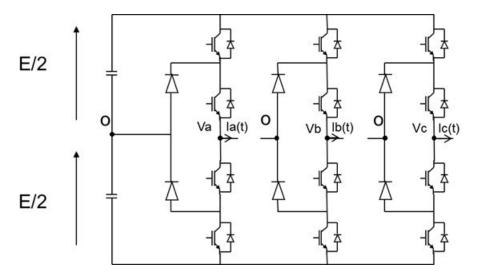

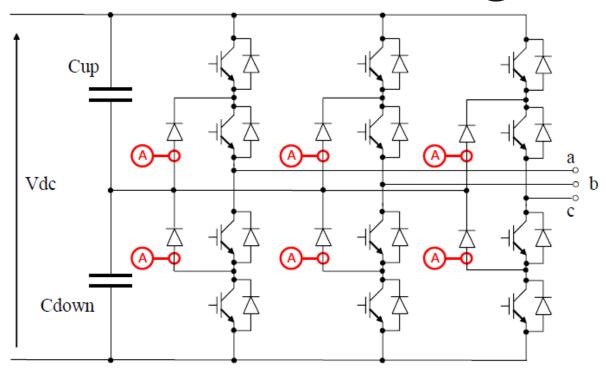

| Figure I.9: Convertisseur triphasé NPC à 3 niveaux                                                                     |       |

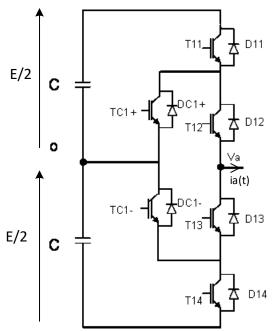

| Figure I.10 : Convertisseur NPC monophasé à 3 niveaux                                                                  | 10    |

| Figure I.11: Séquences de conduction d'un NPC 3 niveaux monophasés                                                     |       |

| Figure I.12: Convertisseur ANPC 3 niveaux triphasé.                                                                    |       |

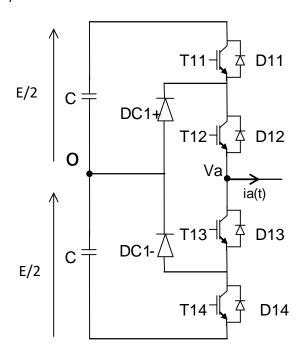

| Figure I.13 : Vue détaillée d'une phase du convertisseur ANPC à 3 niveaux                                              | 13    |

| Figure I.14 : Séquences de conduction pour un ANPC 3 niveaux monophasé                                                 | 14    |

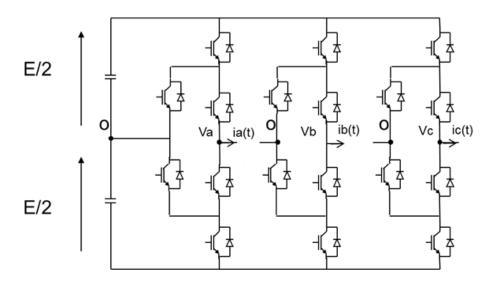

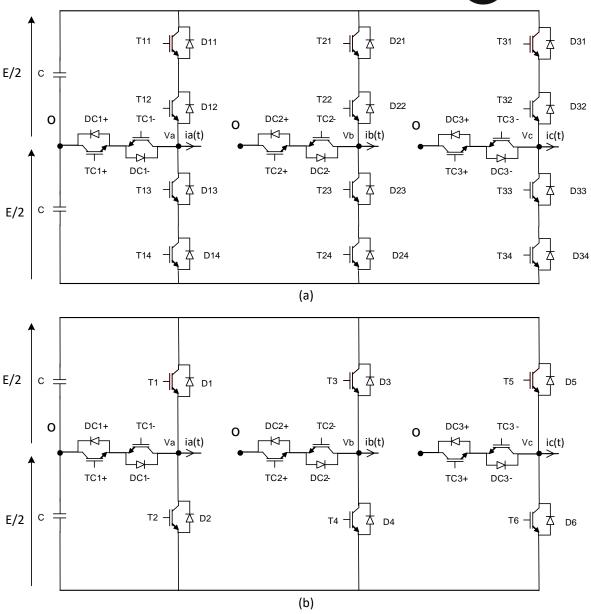

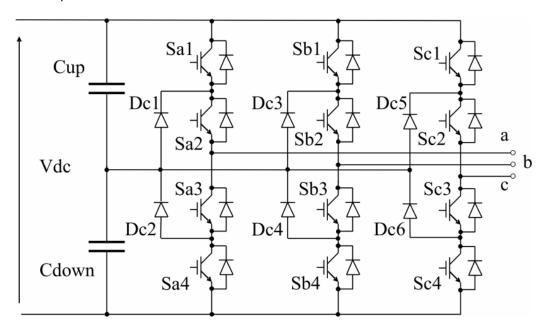

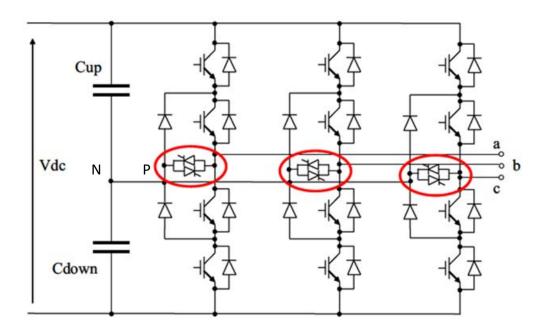

| Figure I.15 : (a) Convertisseur triphasé NPP 3 niveaux (b) Convertisseur triphasé T-type 3 niveaux                     | 16    |

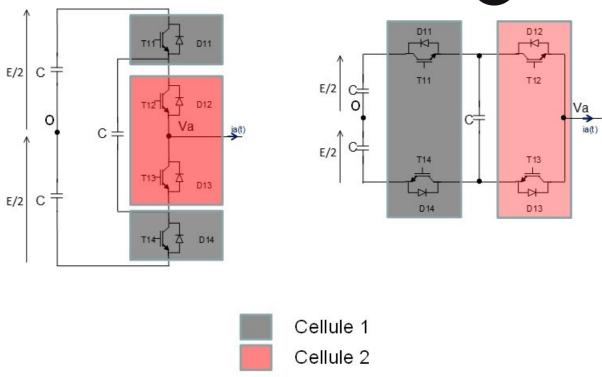

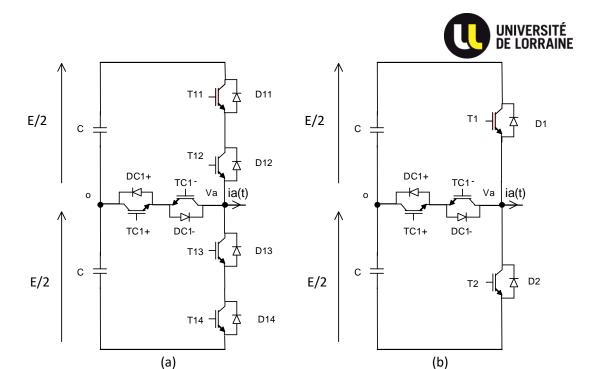

| Figure I.16: (a) Schéma détaillé d'une phase du convertisseur NPP à 3 niveaux (b) Schéma détaille                      | aillé |

| d'une phase du convertisseur T-type à 3 niveaux                                                                        | 17    |

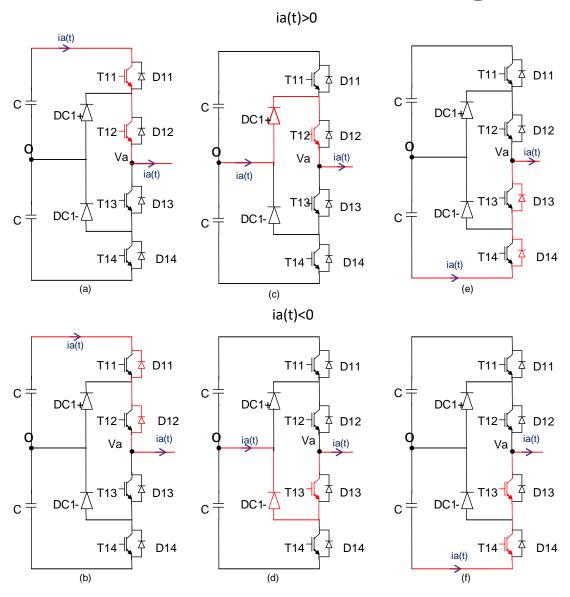

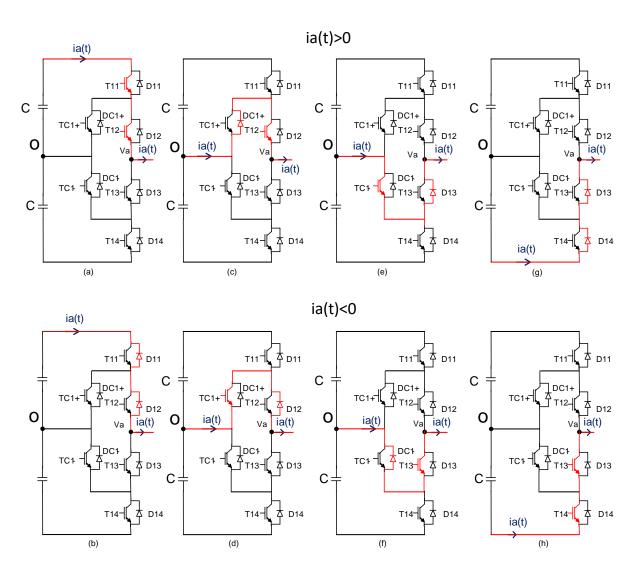

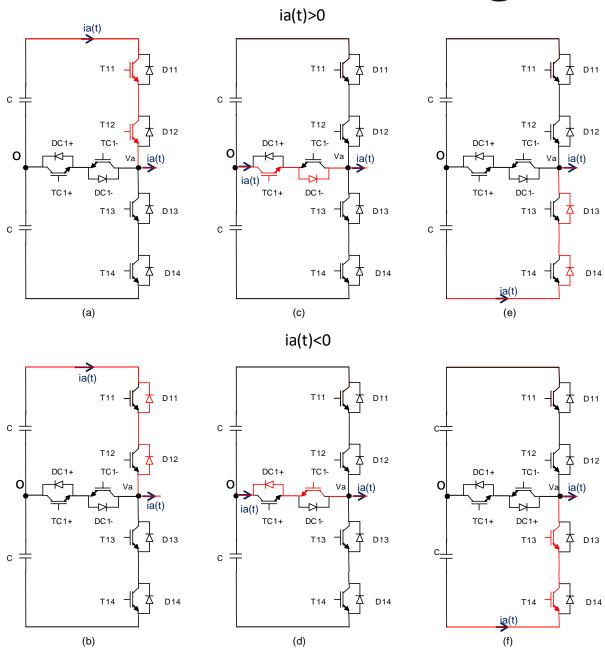

| Figure I.17 : Séquences de conduction d'un à NPP 3 niveaux selon le signe du courant ia(t)                             |       |

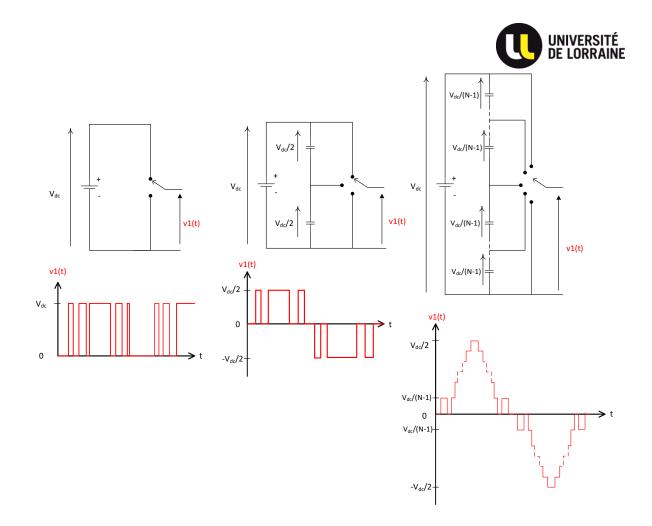

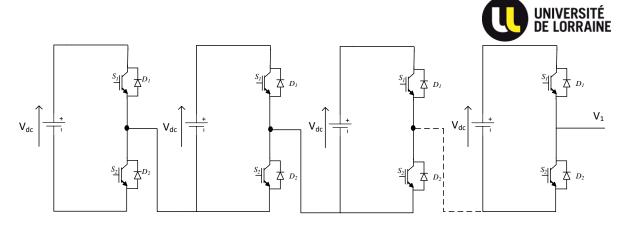

| Figure I.18 : Elaboration d'une structure à N niveaux                                                                  |       |

| Figure I.19 : Bras d'un convertisseur NPC à 5 niveaux.                                                                 | 23    |

| Table I.9: Séquences de conduction du NPC 5 niveaux Figure I.20                                                        | 23    |

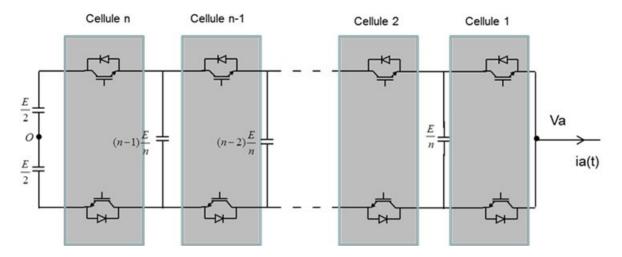

| Figure I.21 : Convertisseur FC à n cellules                                                                            | 24    |

| Figure I.22 : Mise en cascade de 2 convertisseurs de type pont en H                                                    | 25    |

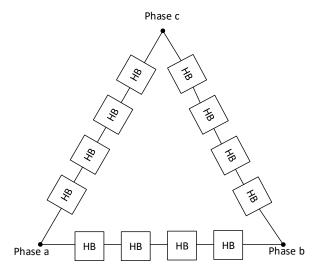

| Figure I.23 : Convertisseur modulaire basé sur une configuration triangle                                              | 26    |

| Figure I.24: Convertisseur modulaire basé sur une configuration étoile                                                 | 26    |

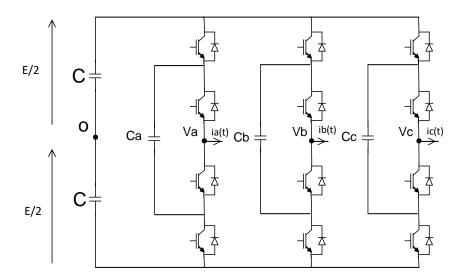

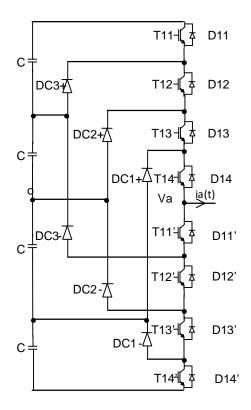

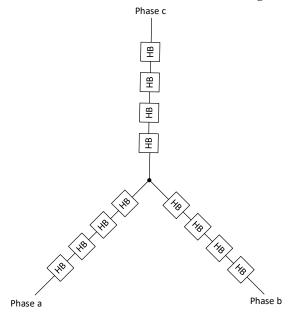

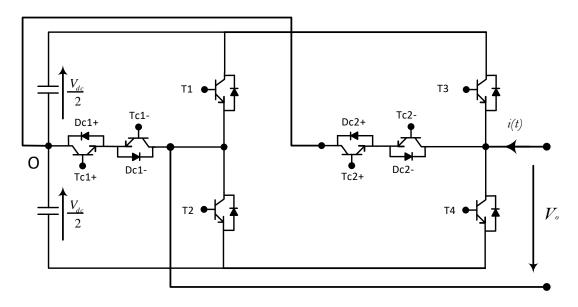

| Figure I.25 : Structure NPC Pont en H à 5 niveaux.                                                                     | 27    |

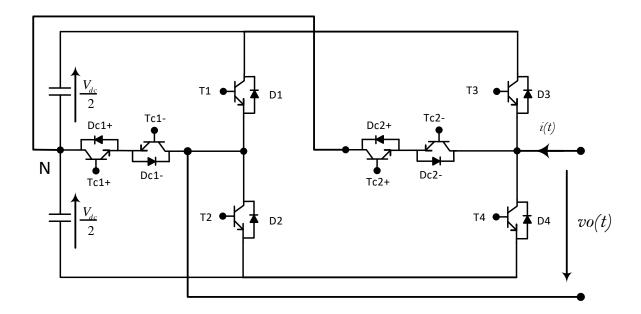

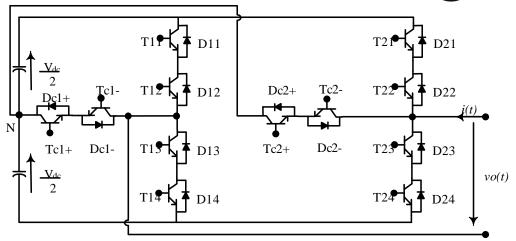

| Figure I. 26: Structure T-Type Pont en H à 5 niveaux                                                                   | 27    |

| Figure I. 27: Mise en cascade de convertisseurs de type demi-pont en H                                                 |       |

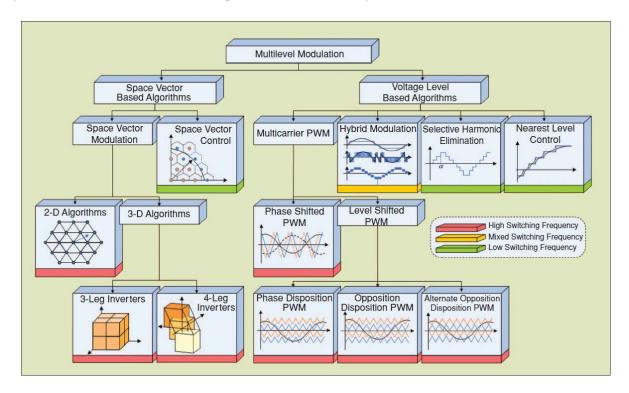

| Figure I.28 : Classification des méthodes de modulation pour convertisseurs multi-niveaux [21]                         | 28    |

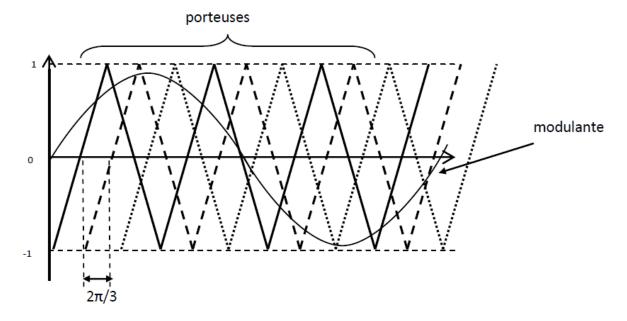

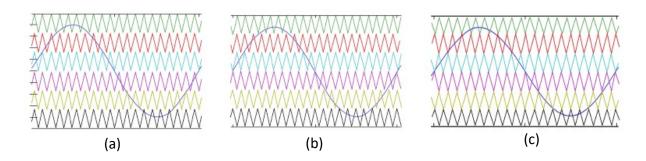

| Figure I. 29: Modulation de type PS-PWM avec 3 porteuses [22].                                                         | 29    |

| Figure I.30 : Exemple de commande MLI type SHE-PWM [22]                                                                | 30    |

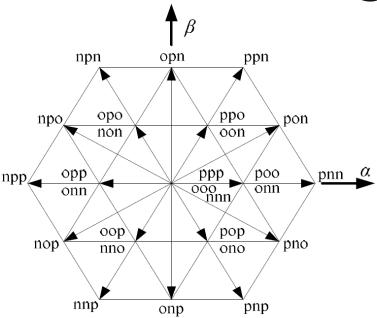

| Figure I.31: Commande MLI de type « SV-PWM » pour un convertisseur 3 niveaux [25]                                      | 31    |

| Figure I.32 : Différentes possibilités de commande MLI type « LS-PWM » : (a) PD-PWM (b) POD-PV                         | WM    |

| (c) APOD-PWM [26]                                                                                                      | 31    |

|                                                                                                                        |       |

| Figure II. 4 - Decemination du postème étudié hacé como IID NDC à Faireann                                             | 2.0   |

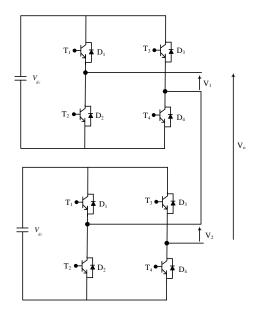

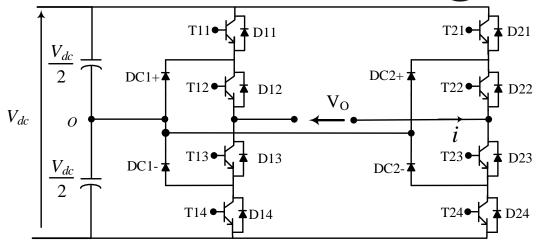

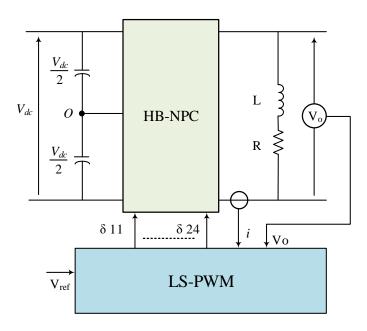

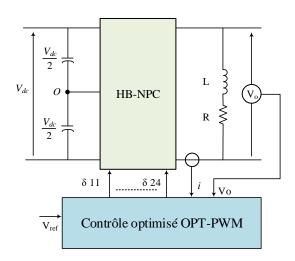

| Figure II. 1: Description du système étudié, basé sur un HB-NPC à 5 niveaux                                            |       |

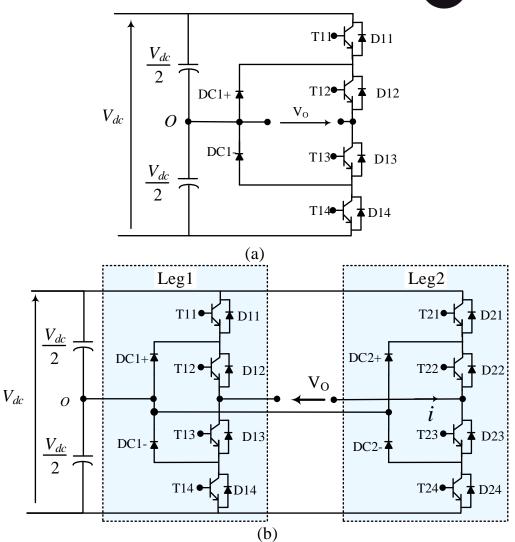

| Figure II.2: (a) Topologie NPC à 3 niveaux. (b) Topologie HB-NPC à 5 niveaux                                           |       |

| Figure II.3 : Génération des ordres de commande, interne au bloc LS-PWM                                                |       |

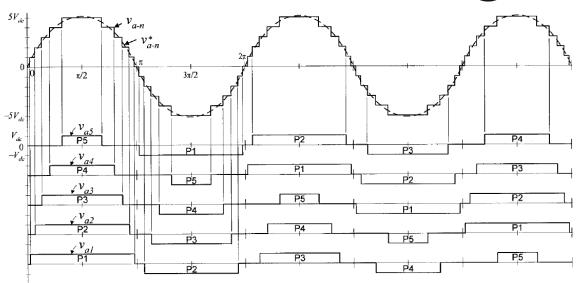

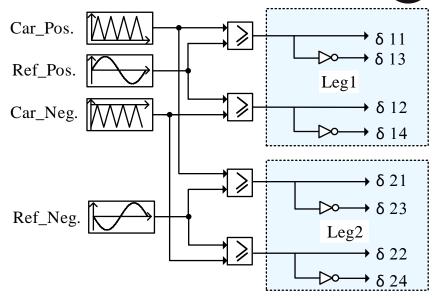

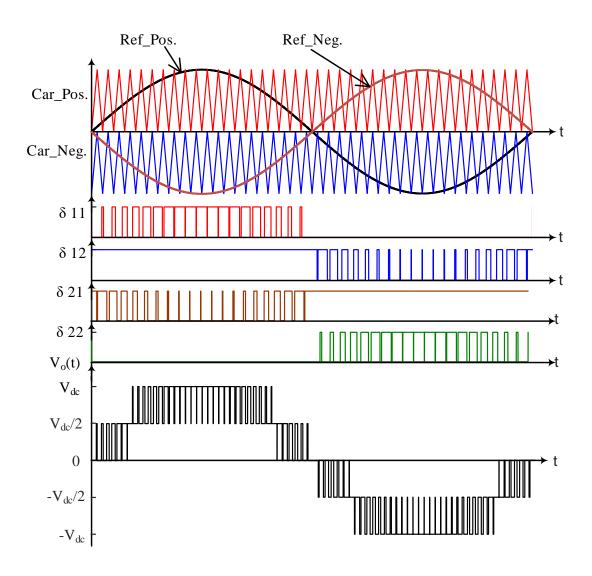

| Figure II.4: Formes d'ondes des signaux LS-PWM, ordres de commande et tension de sortie Vo(t).                         |       |

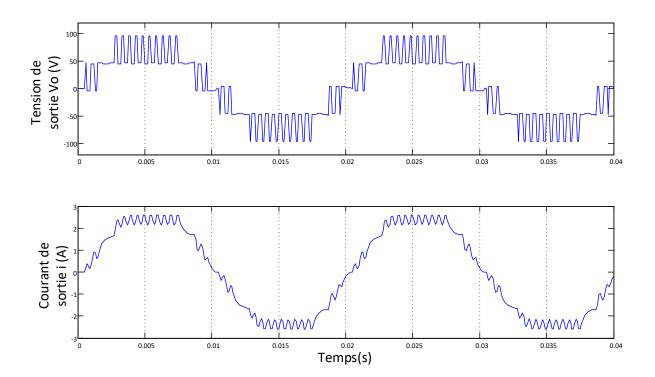

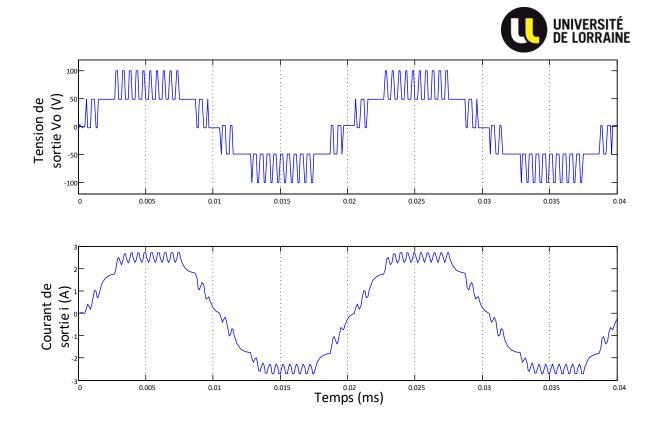

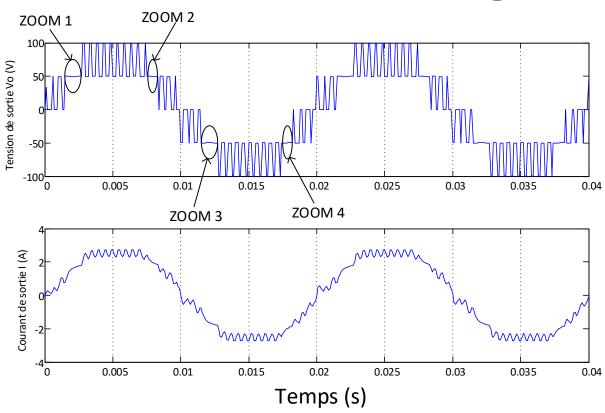

| Figure II. 5 : Résultats de simulation d'un convertisseur HB-NPC à 5 niveaux pour une comma rapprochée de type LS-PWM. |       |

| rapprocnee de type LS-PWIVI                                                                                            | 39    |

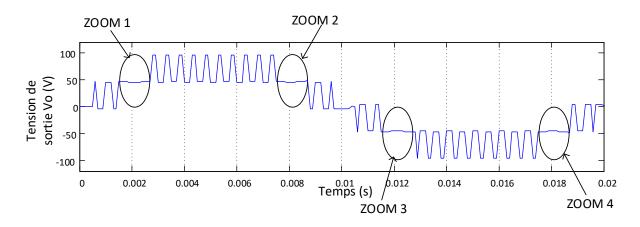

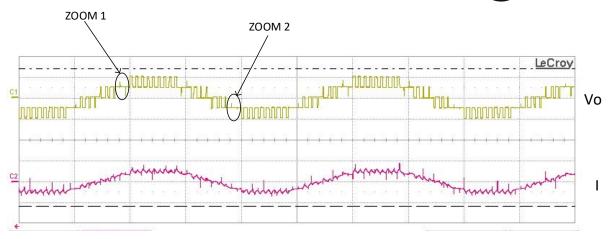

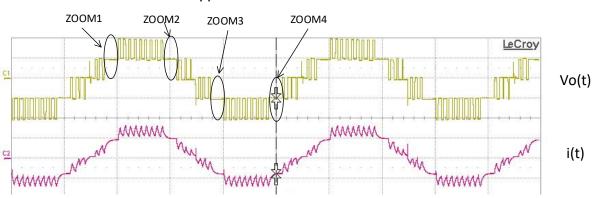

| Figure II. 6: Tension Vo(t) en sortie du HB-NPC 5 niveaux : zoom sur les faibles variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 40 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

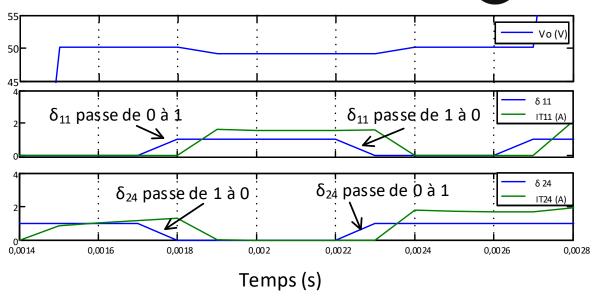

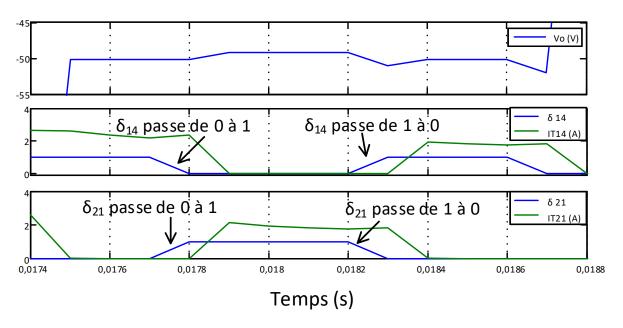

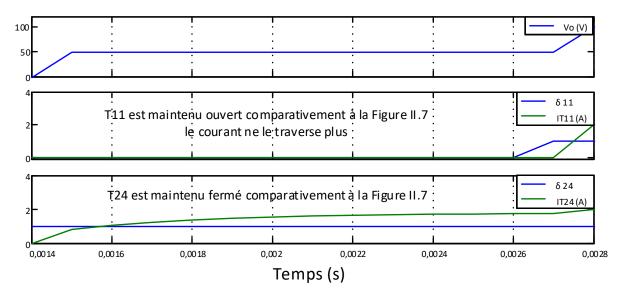

| Figure II.7 : Tension Vo(t), courants $i_{T11}$ et $i_{T24}$ et ordres de commande envoyés à T11 et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| (ZOOM 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

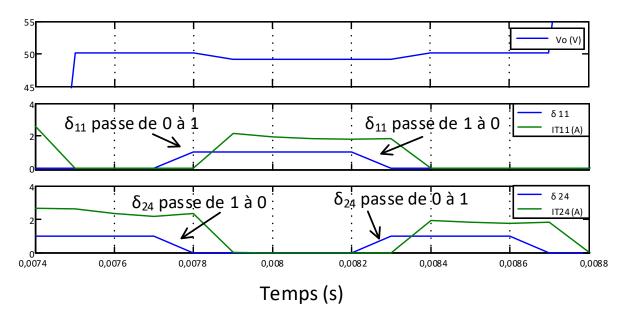

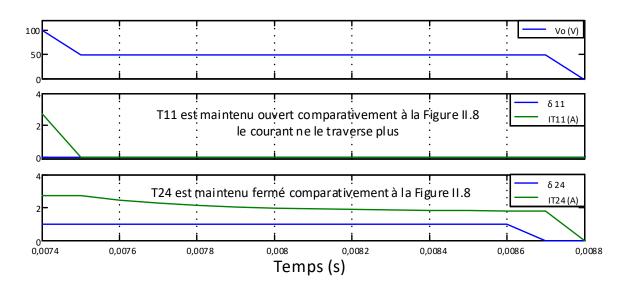

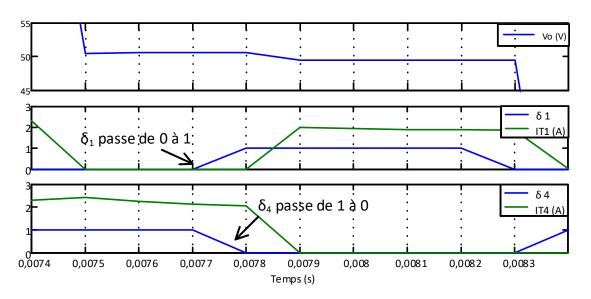

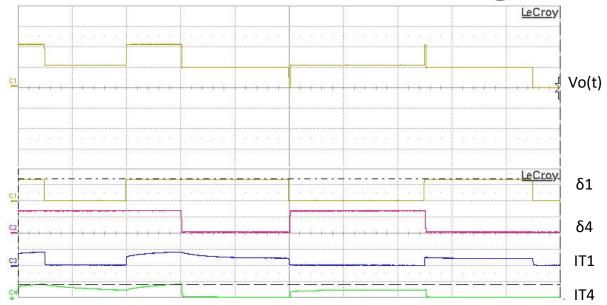

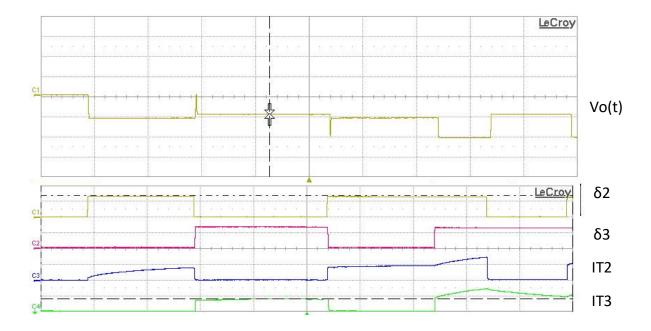

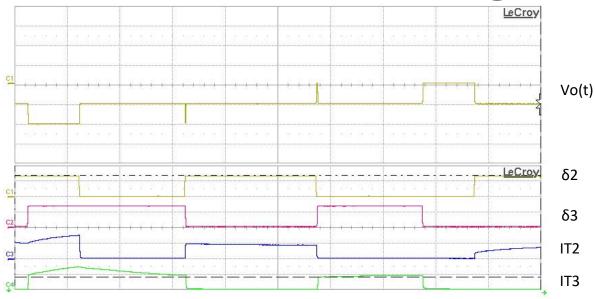

| Figure II.8 : Tension Vo(t), courants $i_{T11}$ et $i_{T24}$ et ordres de commande envoyés à T11 et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| (ZOOM 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

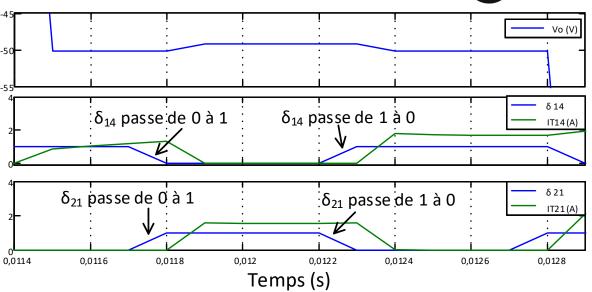

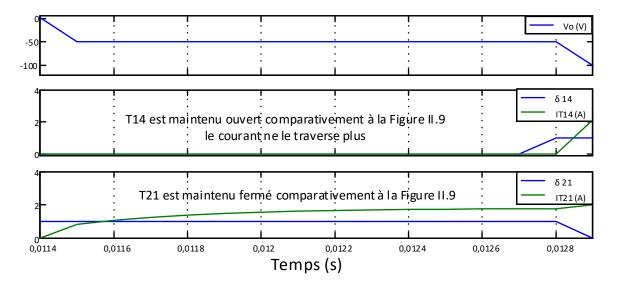

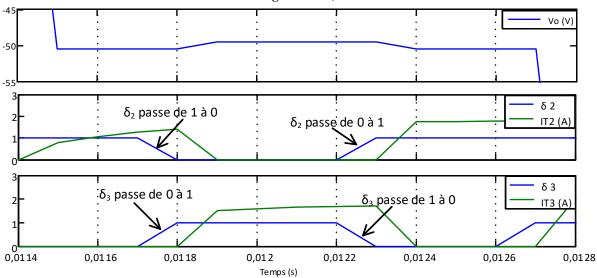

| Figure II.9: Tension Vo(t), courants $i_{T21}$ et $i_{T14}$ et ordres de commande envoyés à T21 et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| (ZOOM 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

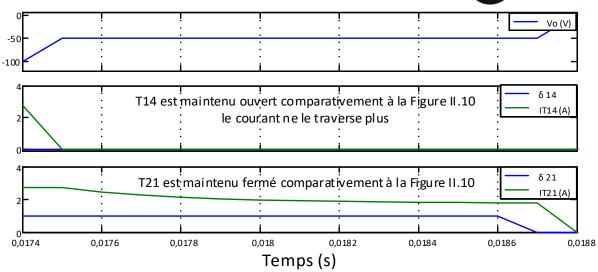

| Figure II. 10: Tension Vo(t), courants $i_{T21}$ et $i_{T14}$ et ordres de commande envoyés à T21 et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| (ZOOM 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

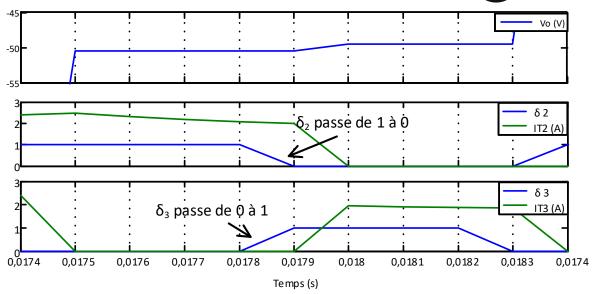

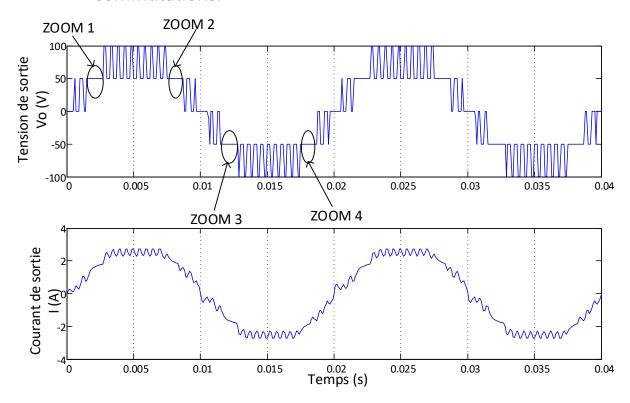

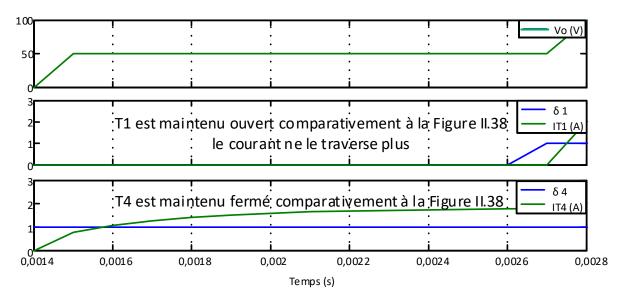

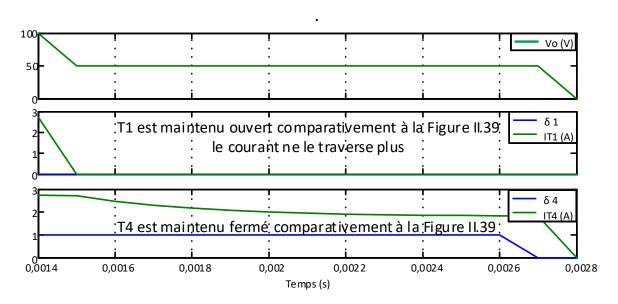

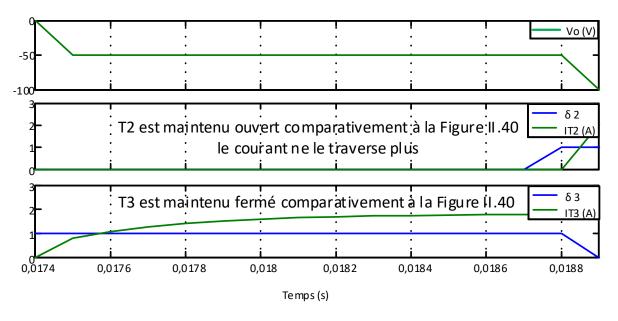

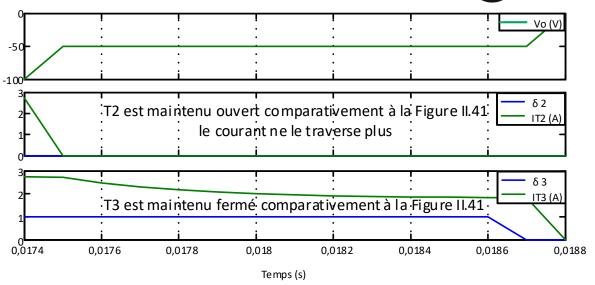

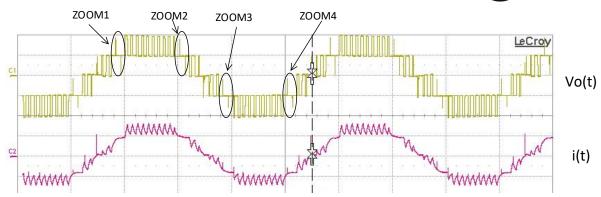

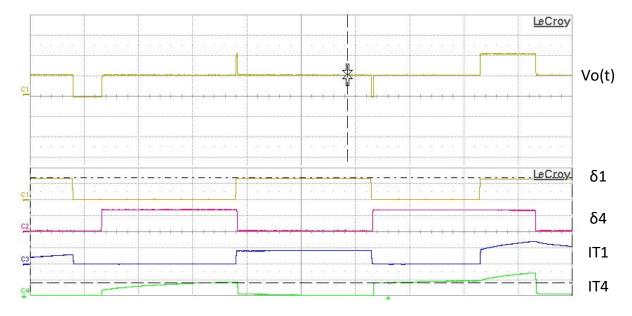

| Par ailleurs, nous avons analysé avec soin et sur une période tous les ordres de commande ainsi de la commande ain | -    |

| les courants des switches associés. Seules les régions que nous avions ciblées sur la Figure II.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| offraient une possibilité de réduction du nombre de commutations. Dans tous les autres cas,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| commutations étaient optimisées et il n'est pas possible de réduire leur nombre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

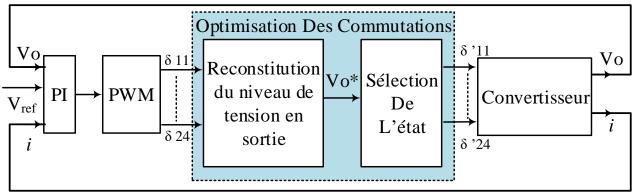

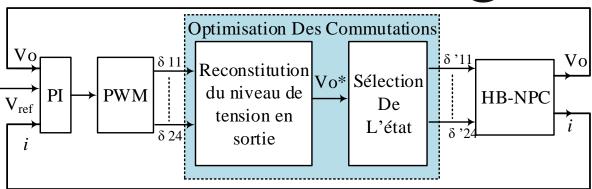

| Figure II.12: Principe général de la minimisation des commutations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

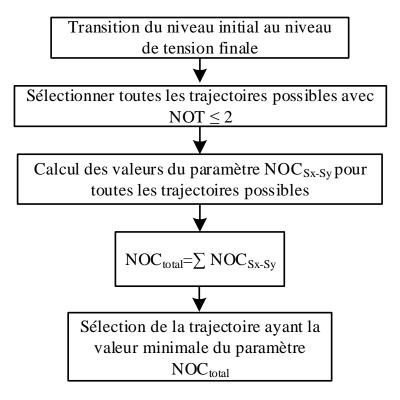

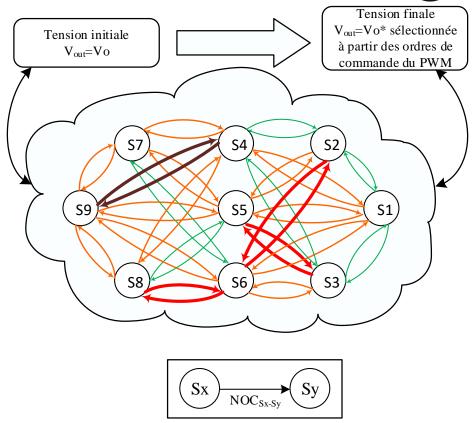

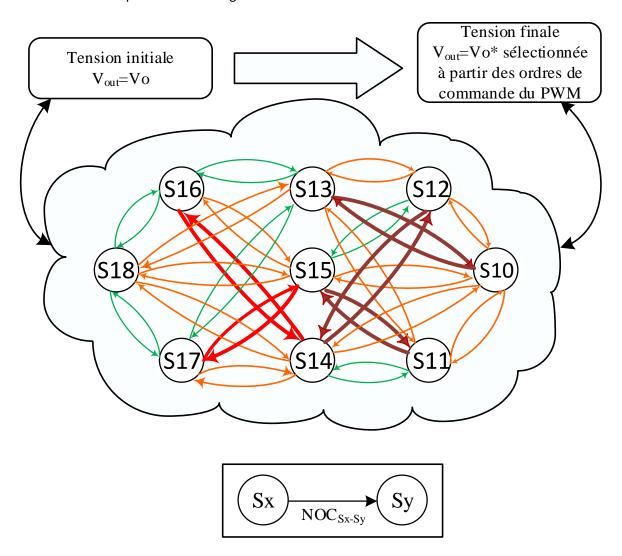

| Figure II.13 : Recherche des trajectoires à nombre minimal de commutations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

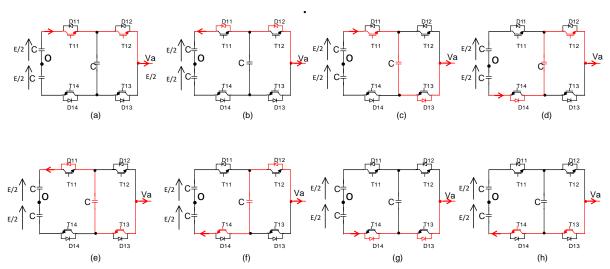

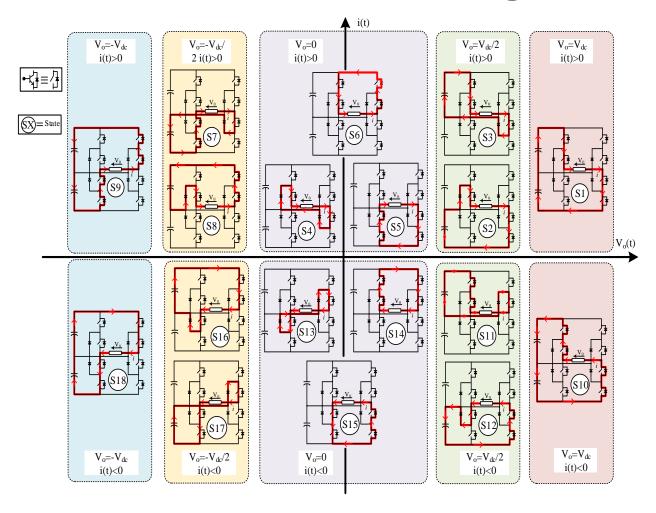

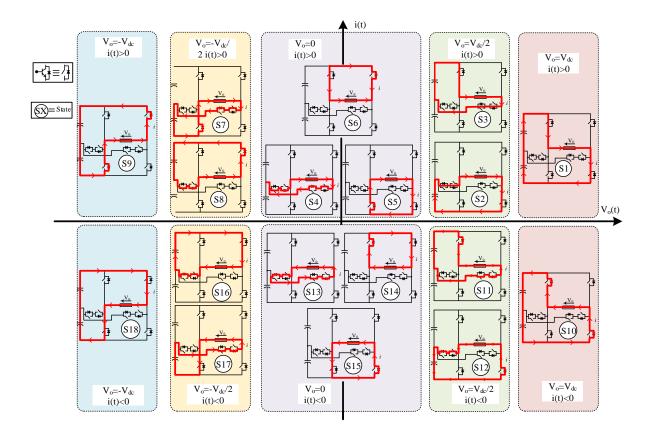

| Figure II.14: Configurations du convertisseur HB-NPC selon les 18 états de commutations possibles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

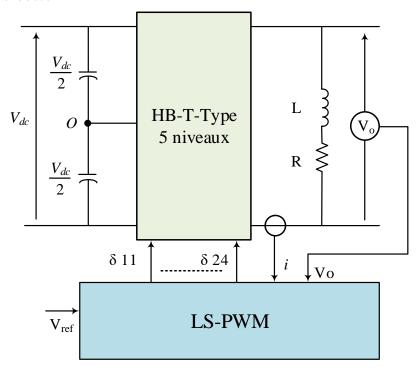

| Figure II.15 : Principe de contrôle du HB-NPC à 5 niveaux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

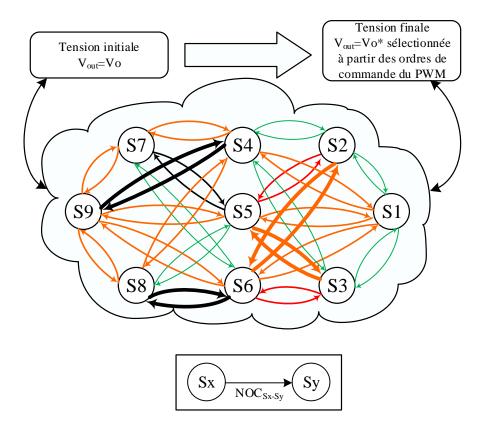

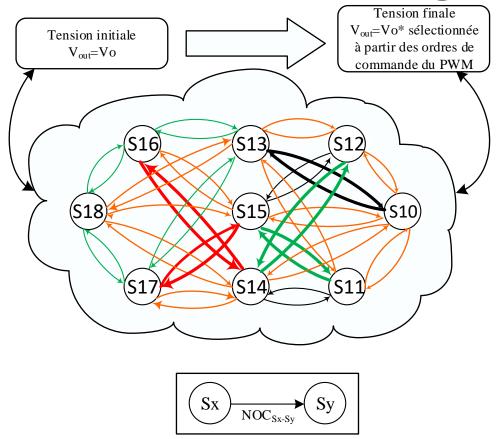

| Figure II.16 : Etat de commutations et trajectoires associées lorsque i(t) est positif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Figure II. 17 : Etats de commutations et trajectoires associées lorsque i(t) est négatif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

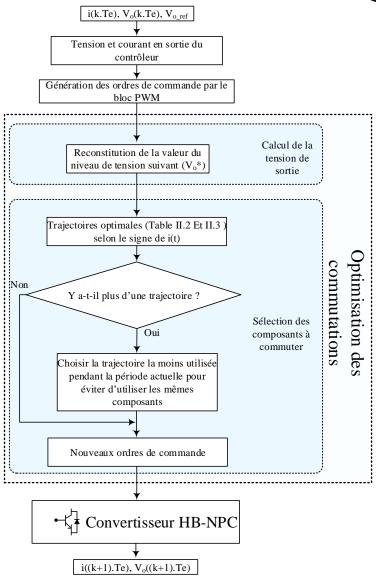

| Figure II.18 : Algorithme complet pour l'optimisation des commutations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Figure II.19: HB-NPC connecté à une charge RL avec contrôle OPT-PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 53 |

| Figure II. 20 : Tension et courant en sortie du convertisseur avec le contrôle OPT-PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 54 |

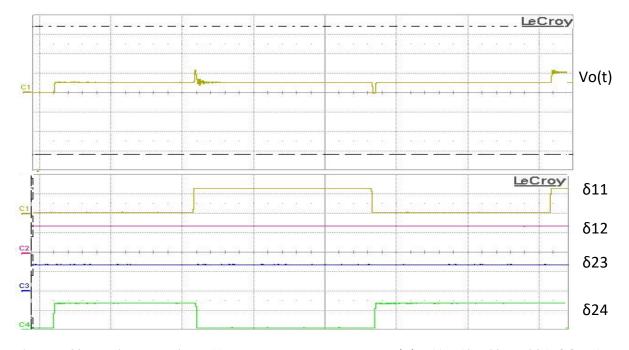

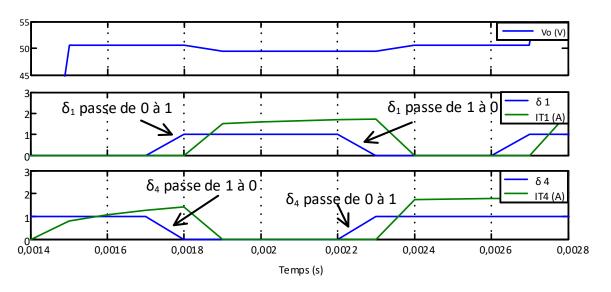

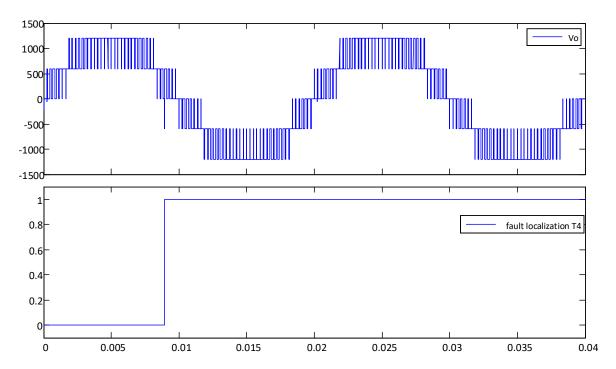

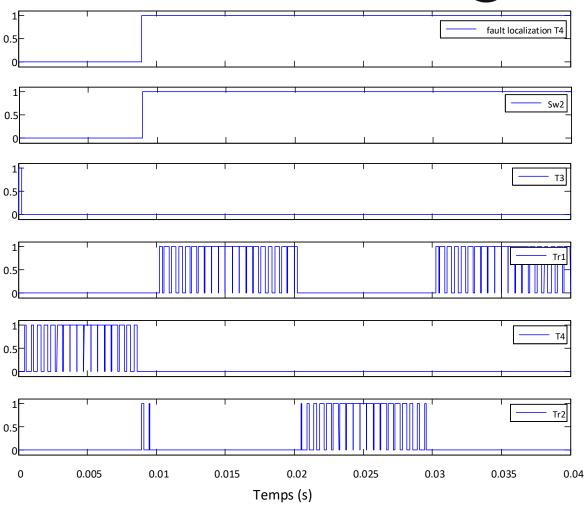

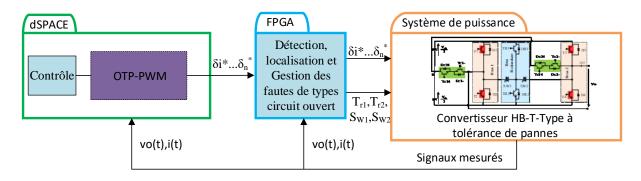

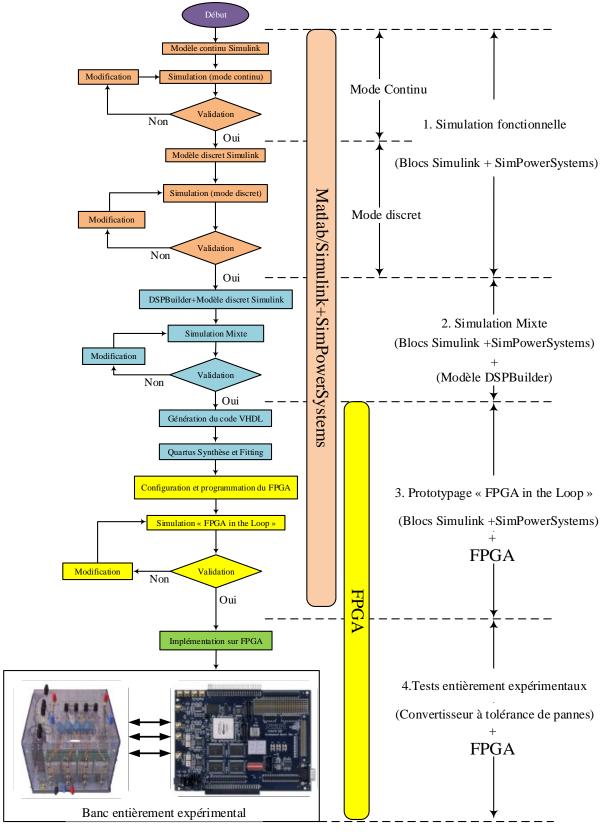

| Figure II.21 : Tension Vo, courants $i_{T11}$ et $i_{T24}$ et ordres de commande $\delta_{11}$ et $\delta_{24}$ (ZOOM 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 54 |