# Détection et prévention de Cheval de Troie Matériel (CTM) par des méthodes Orientées Test Logique

Papa-Sidy Ba

#### ▶ To cite this version:

Papa-Sidy Ba. Détection et prévention de Cheval de Troie Matériel (CTM) par des méthodes Orientées Test Logique. Cryptographie et sécurité [cs.CR]. Université Montpellier, 2016. Français. NNT: 2016MONTT271. tel-01816951

## HAL Id: tel-01816951 https://theses.hal.science/tel-01816951v1

Submitted on 15 Jun 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Délivré par l'Université de Montpellier

Préparée au sein de l'école doctorale I2S - Information, Structures, Systèmes Et de l'unité de recherche UMR 5506 - Laboratoire d'Informatique, Robotique et Micro-électronique de Montpellier

Spécialité: SYAM - Systèmes Automatiques et Micro-électroniques

Présentée par Papa-Sidy Ba

## Détection et Prévention de Chevaux de Troie Matériels par des Méthodes Orientées Test Logique

#### Soutenue le 02 Décembre 2016 devant le jury composé de

| M. Guy Gogniat          | Pr      | Université de Bretagne-Sud                 | Rapporteur         |

|-------------------------|---------|--------------------------------------------|--------------------|

| M. Paolo Prinetto       | Pr      | Politecnico di Torino                      | Rapporteur         |

| M. Bruno Rouzeyre       | Pr      | Université de Montpellier - LIRMM          | Directeur de thèse |

| M. Giorgio DI NATALE    | DR CNRS | CNRS - LIRMM                               | Examinateur        |

| Mme. Sophie DUPUIS      | MCf     | Université de Montpellier - LIRMM          | Examinatrice       |

| Mme. Marie-Lise FLOTTES | CR CNRS | CNRS - LIRMM                               | Examinatrice       |

| M. Julien Francq        | Dr      | Airbus Defence and Space- CyberSecurity    | Examinateur        |

| M. Jean-Baptiste RIGAUD | MCf     | École Nationale des Mines de Saint Etienne | Examinateur        |

|                         |         |                                            |                    |

## **Avant propos**

Remerciements

### Contexte de la thèse

Cette thèse s'est déroulée dans le cadre du projet FUI#14 HOMERE (Hardware TrOjans : Menaces et robustEsse des ciRcuits intEgrés).

Ce projet a été financé par le gouvernement français (BPI-OSEO) et supervisé par la Direction Générale de l'Armement (DGA). C'est le fruit de la collaboration entre instituts de recherche (LIRMM, Mines de Saint Étienne, CEA LETI et Télécom ParisTech), d'industriels (Gemalto, Cassidian et SECURE-IC S.A.S.) et d'institutions gouvernementales (ANSSI et DGA).

Cette thèse s'est déroulée au LIRMM (Laboratoire d'Informatique de Robotique et de Micro-électronique de Montpellier).

Le LIRMM est une unité mixte de recherche, dépendant conjointement de l'Université Montpellier (UM) et du Centre National de la Recherche Scientifique (CNRS). Il est situé sur le Campus Saint-Priest de l'UM.

Ses activités de recherche positionnent pleinement le LIRMM au coeur des sciences et technologies de l'information, de la communication et des systèmes.

Ainsi, de l'information aux systèmes, de la technologie à l'humain et aux usages, les activités de recherche du LIRMM concernent : la conception et la vérification de systèmes intégrés, mobiles, communicants, la modélisation de systèmes complexes à base d'agents, les études en algorithmique, bioinformatique, interactions homme-machine, robotique, etc.

Les travaux sont menés dans trois départements scientifiques de recherche, eux-mêmes organisés en « équipes-projet ».

Le département Microélectronique mène des recherches de pointe dans les domaines de la conception et du test de systèmes intégrés et microsystèmes en mettant l'accent sur les aspects architectures, modélisation et méthodologie.

## Table des matières

| A  | ant p  | propos                                           | 11   |

|----|--------|--------------------------------------------------|------|

| Ta | ıble d | les matières                                     | v    |

| Li | ste d  | es figures                                       | vii  |

| Li | ste d  | es tableaux                                      | viii |

| Li | ste d  | es acronymes                                     | X    |

| Re | ésum   | é et abstract                                    | 1    |

| 1  | Intr   | oduction générale                                | 3    |

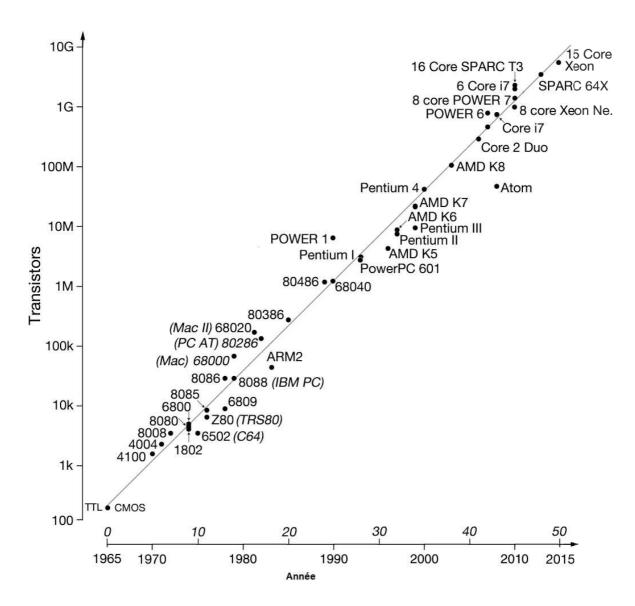

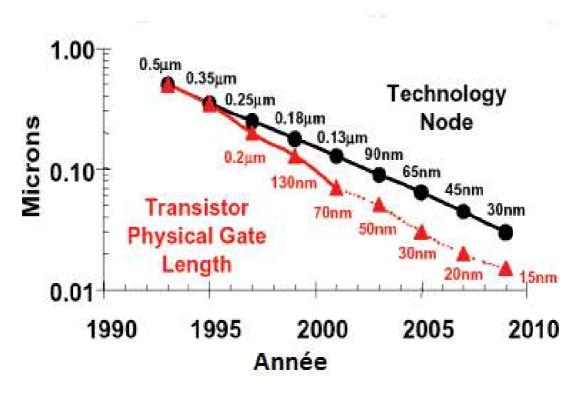

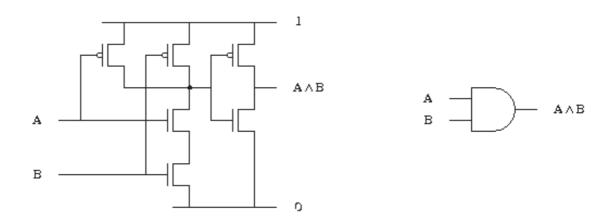

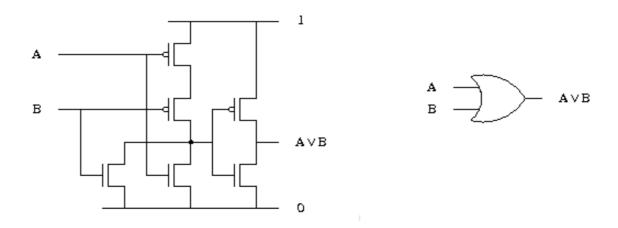

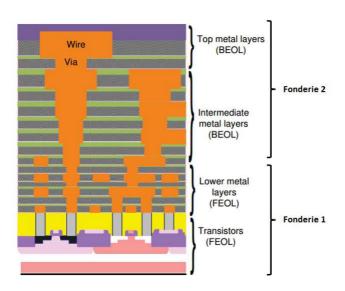

|    | 1.1    | Technologie CMOS                                 | 6    |

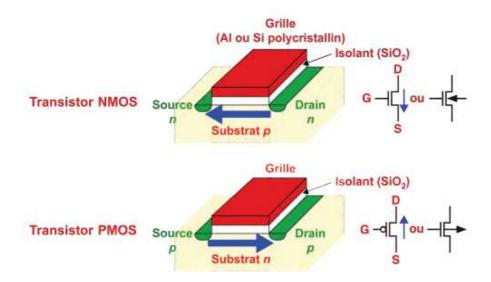

|    | 1.2    | Transistor MOS                                   | 6    |

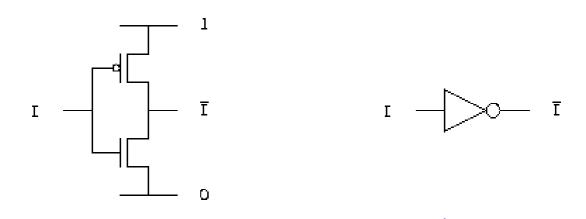

|    | 1.3    | Du transistor MOS aux cellules standards         | 7    |

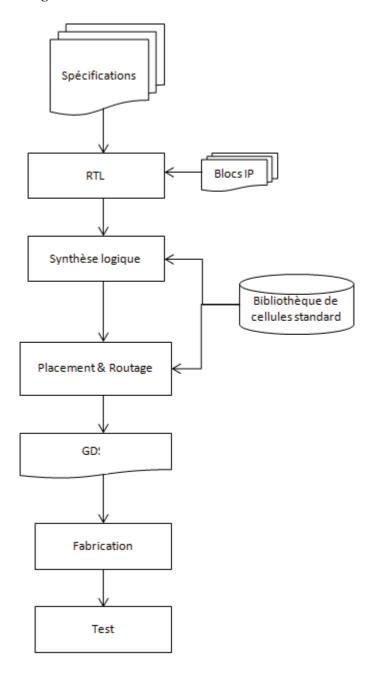

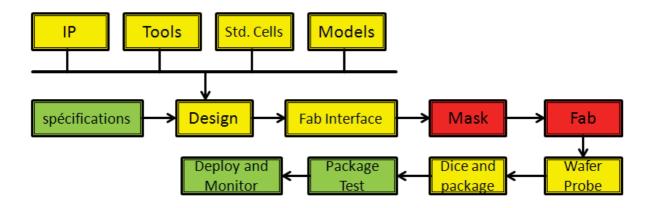

|    | 1.4    | Flot de conception VLSI                          | 9    |

|    | 1.5    | Étapes vulnérables du le flot VLSI               | 10   |

|    | 1.6    | Menaces potentielles                             | 12   |

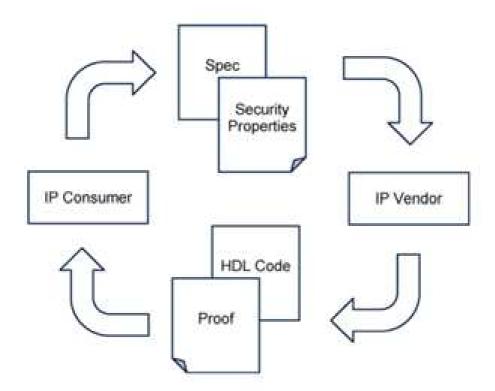

|    | 1.7    | Confiance matérielle                             | 14   |

|    | 1.8    | Contributions de cette thèse                     | 14   |

|    | 1.9    | Références                                       | 17   |

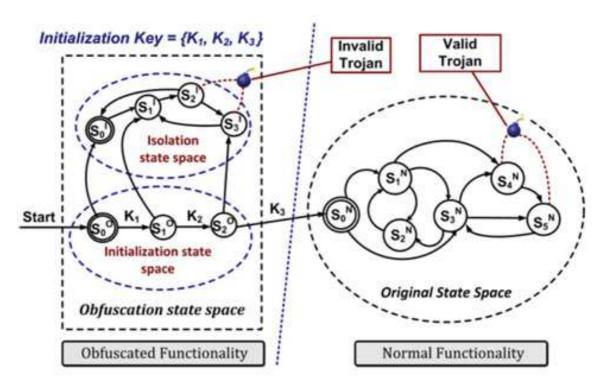

| 2  | Tax    | onomie et état de l'art de lutte contre les CTMs | 18   |

|    | 2.1    | Introduction                                     | 19   |

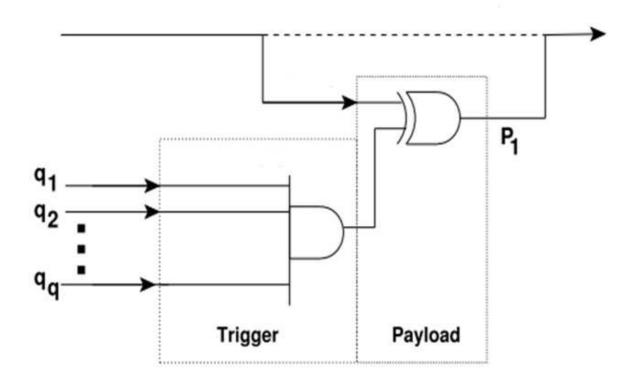

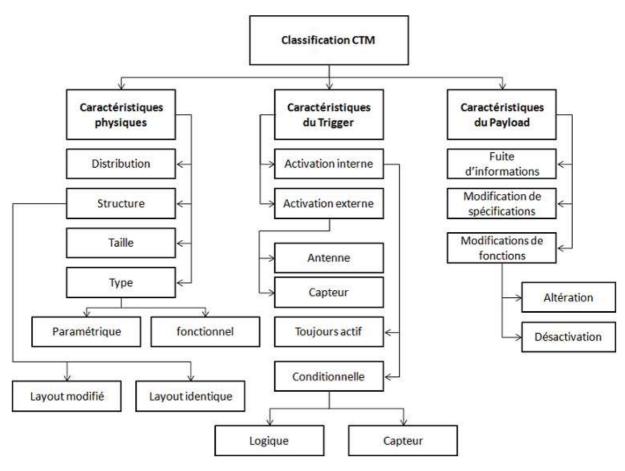

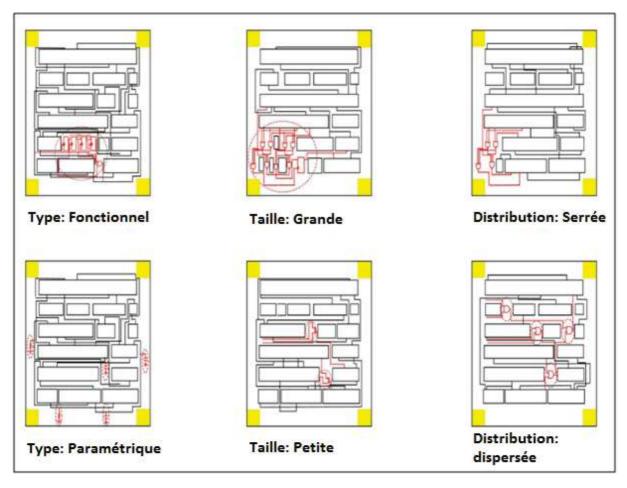

|    | 2.2    | Taxonomie des CTMs                               | 19   |

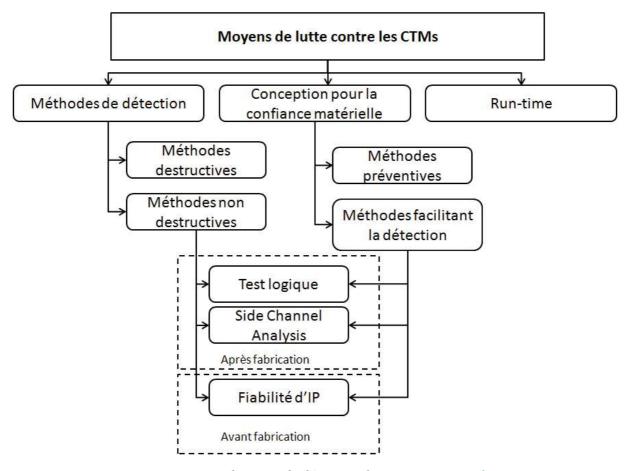

|    | 2.3    | Méthodes de détection                            | 23   |

|    | 2.4    | Méthodes de prévention                           | 31   |

|    | 2.5    | Conclusion                                       | 34   |

|    | 2.6    | Références                                       | 35   |

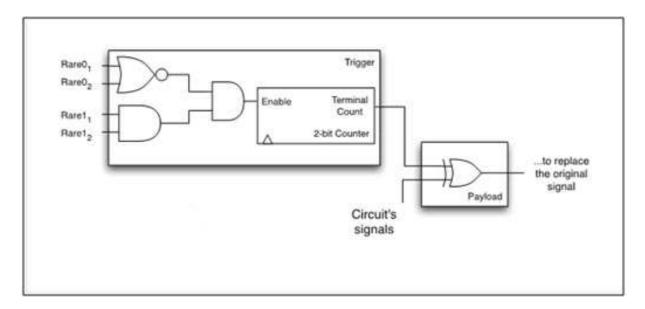

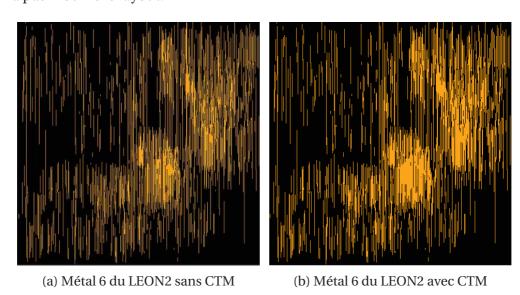

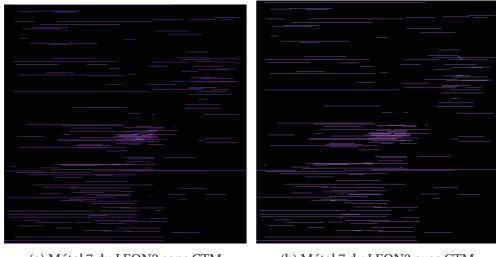

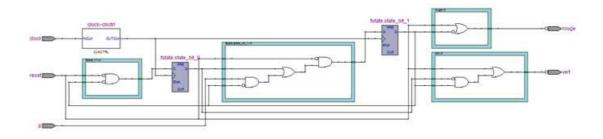

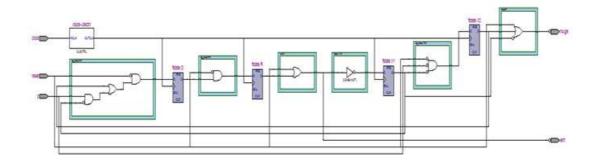

| 3  | Imp    | lémentations de CTMs dans l'AES et le LEON2      | 38   |

|    | 3.1    | Introduction                                     | 39   |

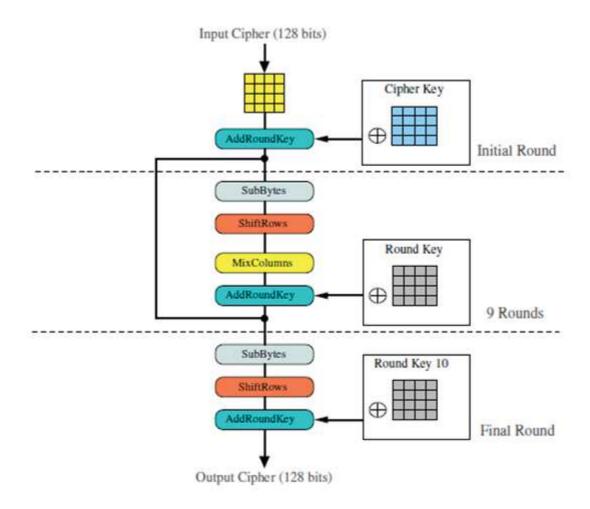

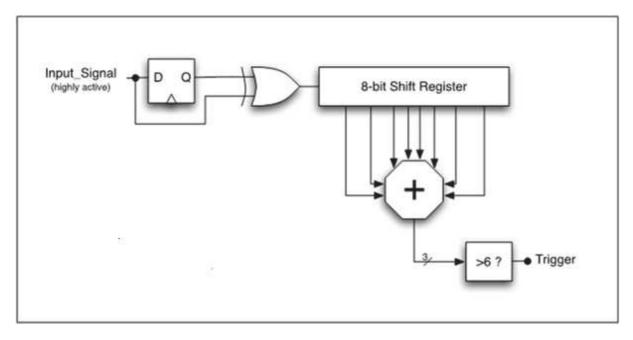

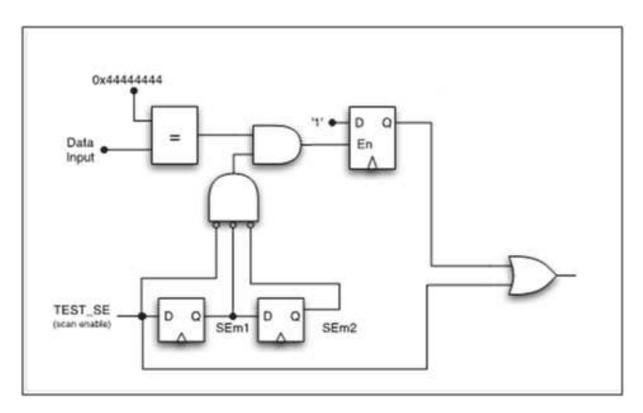

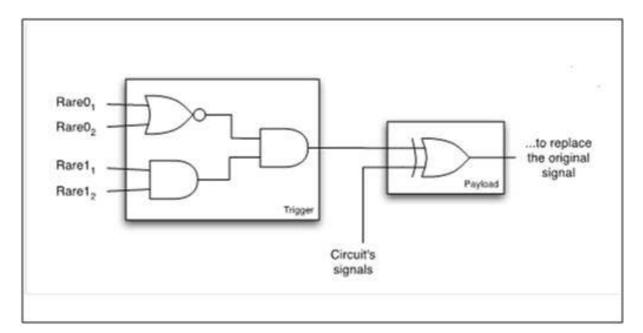

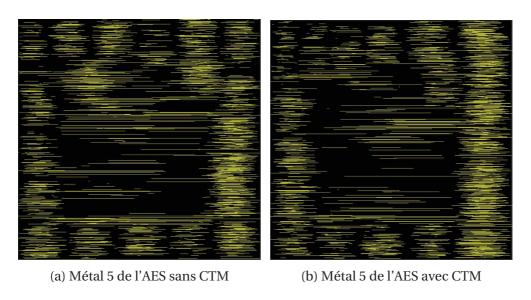

|    | 3.2    | Implémentation dans l'AES                        | 39   |

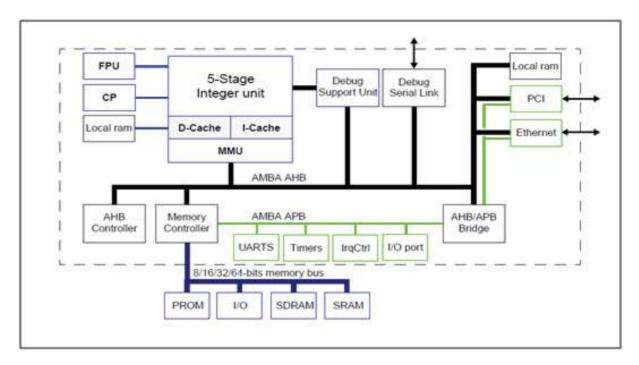

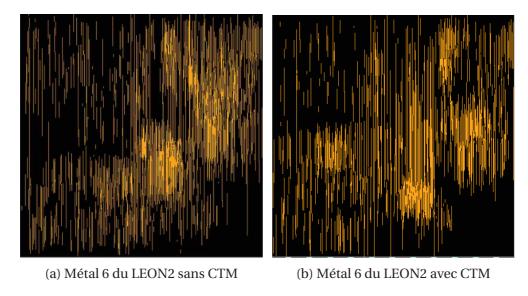

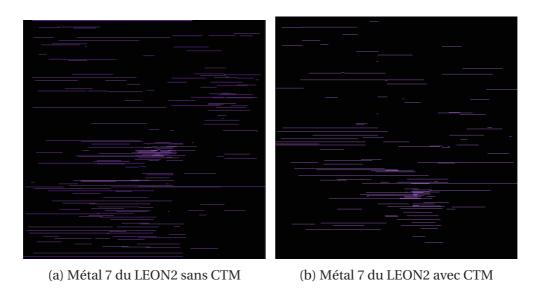

|    | 3.3    | Implémentation dans le processeur LEON2          | 48   |

|    | 3.4    | Conclusion                                       | 55   |

|    | 3.5    | Références                                       | 56   |

|   | Det                                                                                                   | I .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>57</b>                                                                     |

|---|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|   | 4.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58                                                                            |

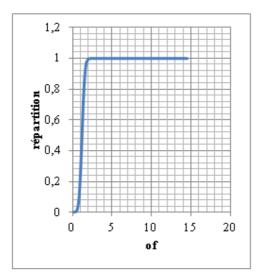

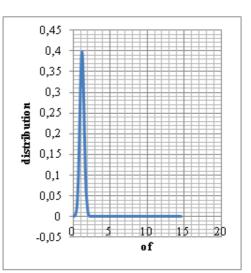

|   | 4.2                                                                                                   | 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60                                                                            |

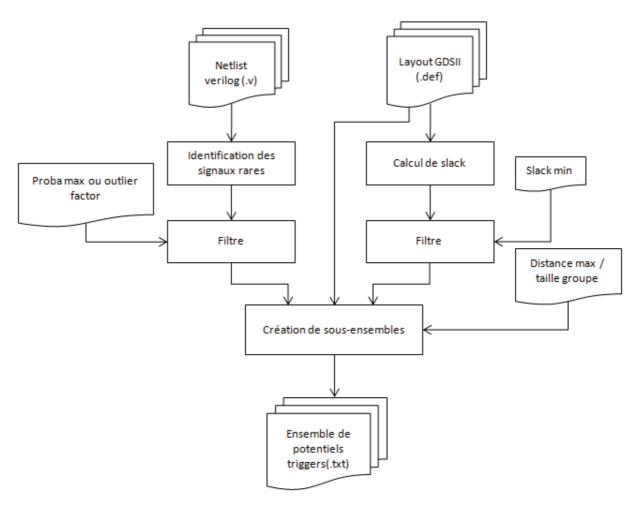

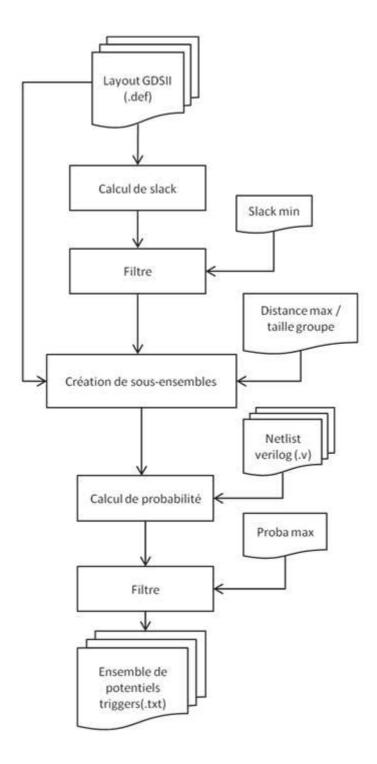

|   | 4.3                                                                                                   | Approche de détection proposée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                                            |

|   | 4.4                                                                                                   | O .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61                                                                            |

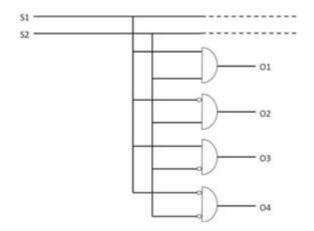

|   | 4.5                                                                                                   | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68                                                                            |

|   | 4.6                                                                                                   | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71                                                                            |

|   | 4.7                                                                                                   | Génération des vecteurs de déclenchement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                            |

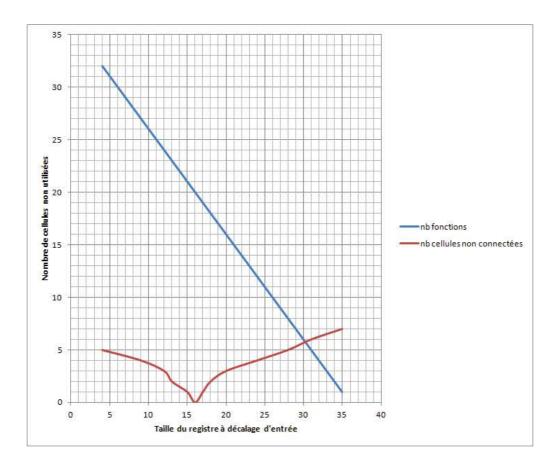

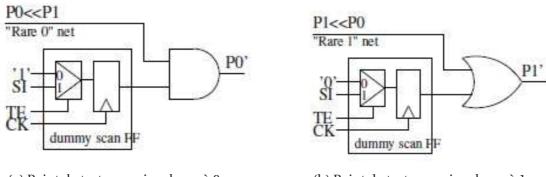

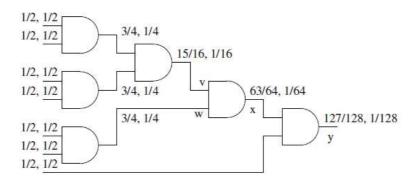

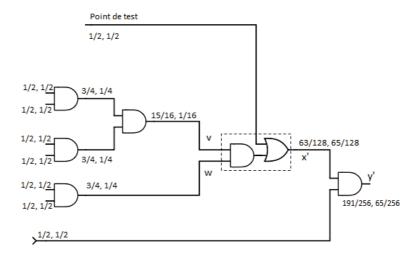

|   | 4.8                                                                                                   | Résultats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75                                                                            |

|   | 4.9                                                                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                                            |

|   | 4.10                                                                                                  | Références                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78                                                                            |

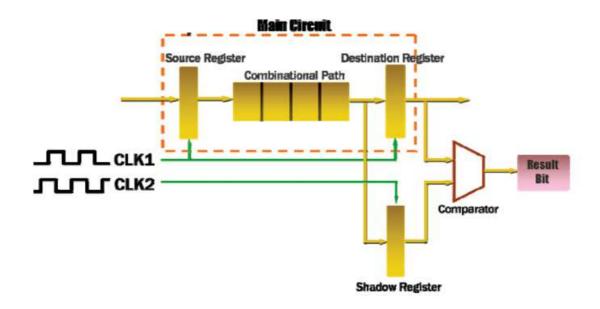

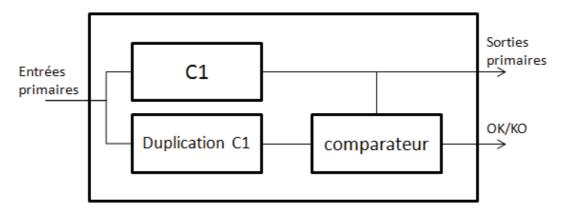

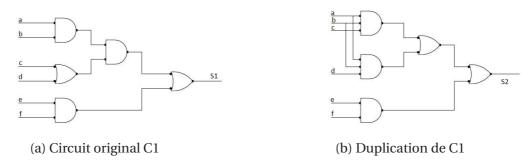

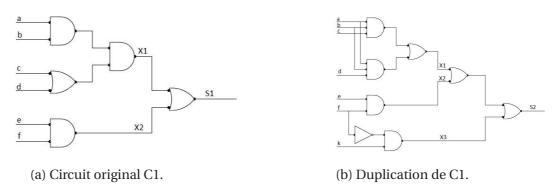

| 5 | Dét                                                                                                   | ection de CTMs en-ligne par duplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80                                                                            |

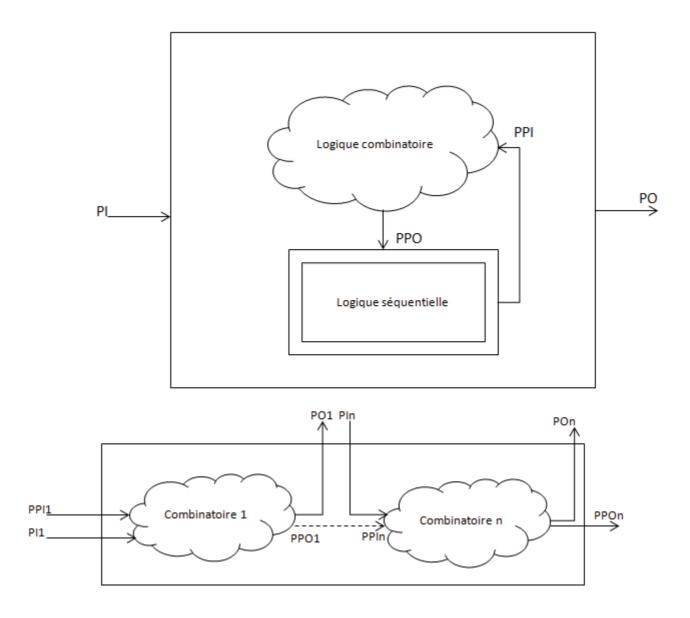

|   | 5.1                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81                                                                            |

|   | 5.2                                                                                                   | Étude bibliographique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81                                                                            |

|   | 5.3                                                                                                   | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 82                                                                            |

|   | 5.4                                                                                                   | <del></del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85                                                                            |

|   | 5.5                                                                                                   | Durcissement du système de monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85                                                                            |

|   | 5.6                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                                            |

|   | 5.7                                                                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                            |

|   | 5.8                                                                                                   | Références                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89                                                                            |

| G | Duá                                                                                                   | vention dincertion de CTM ner remuliesers du levert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90                                                                            |

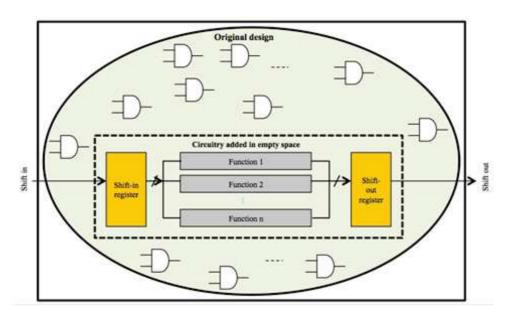

| 6 | Pre                                                                                                   | vention a insertion de CTM par remplissage du layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | JU                                                                            |

| O | 6.1                                                                                                   | 1 1 0 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91                                                                            |

| O |                                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                               |

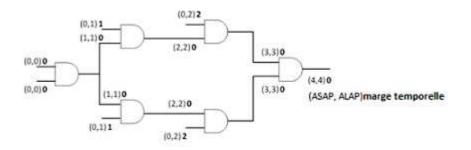

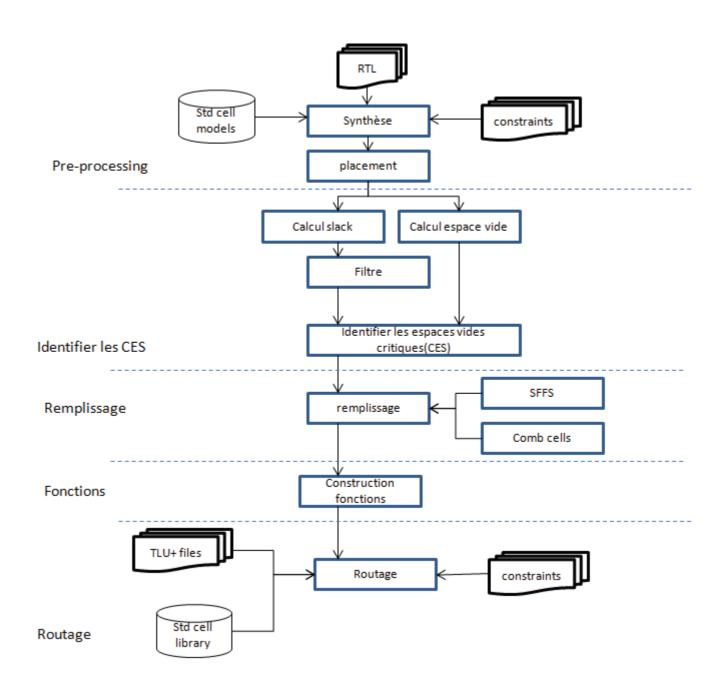

| O | 6.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91                                                                            |

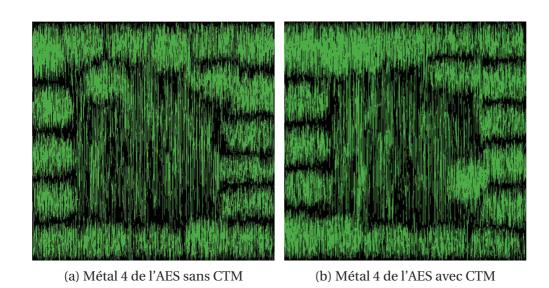

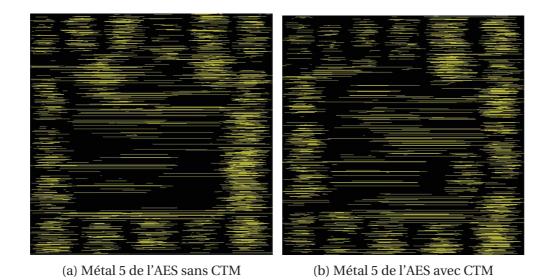

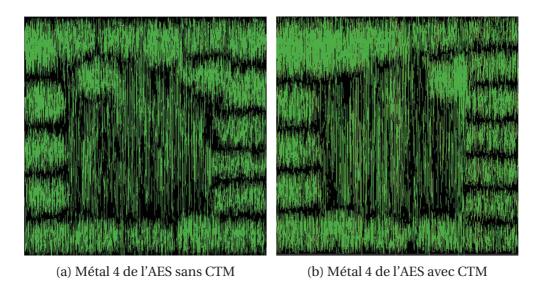

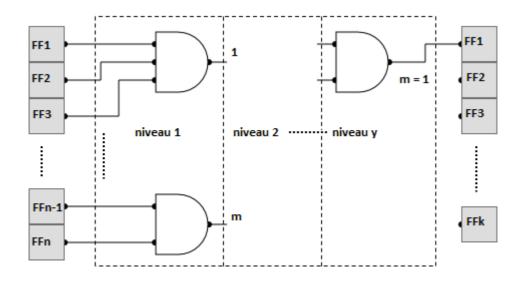

| O | 6.1<br>6.2                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91<br>91<br>92                                                                |

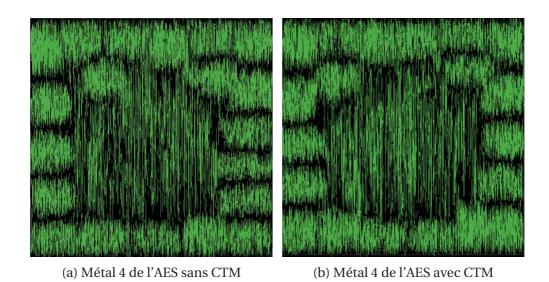

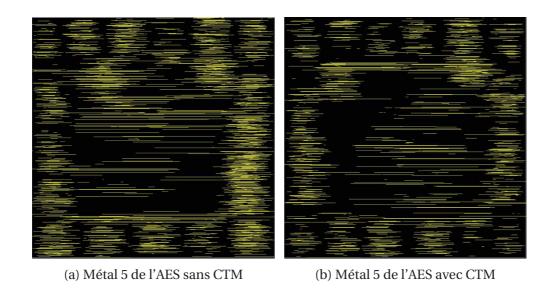

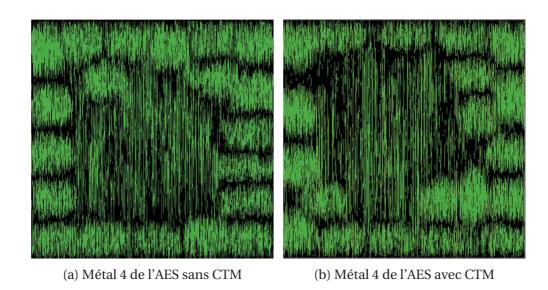

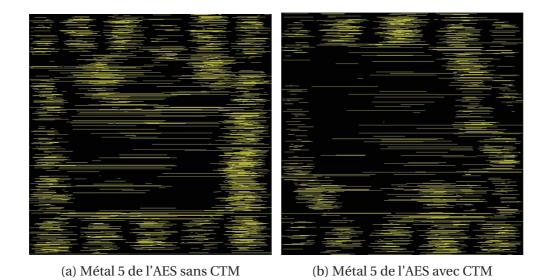

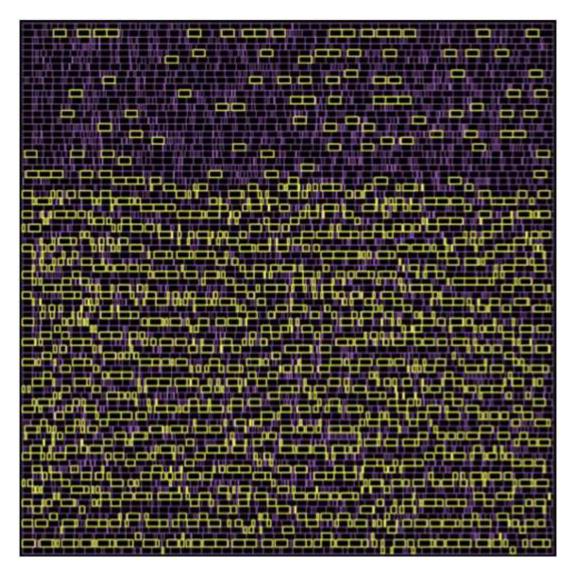

| O | 6.1<br>6.2<br>6.3                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91<br>91<br>92<br>97                                                          |

| O | 6.1<br>6.2<br>6.3<br>6.4                                                                              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91<br>91<br>92<br>97<br>101                                                   |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91<br>92<br>97<br>101<br>102                                                  |

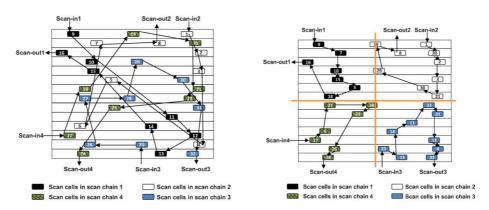

| 7 | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91<br>92<br>97<br>101<br>102                                                  |

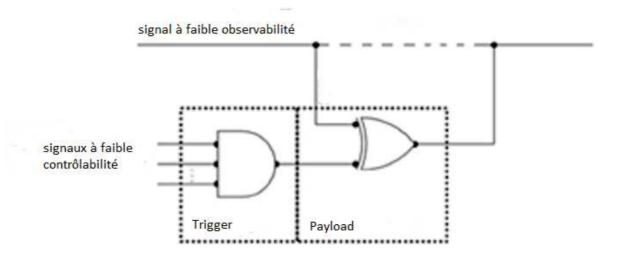

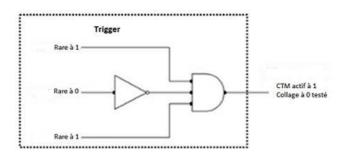

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br><b>Pré</b>                                                  | Introduction Étude bibliographique Approche Résultats Conclusion Références  Vention d'insertion de CTM par insertion de points de test Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91<br>92<br>97<br>101<br>102                                                  |