# Epitaxie en phase vapeur aux organométalliques de semiconducteurs III-As sur substrat silicium et formation de contacts ohmiques pour les applications photoniques et RF sur silicium

Reynald Alcotte

#### ▶ To cite this version:

Reynald Alcotte. Epitaxie en phase vapeur aux organométalliques de semiconducteurs III-As sur substrat silicium et formation de contacts ohmiques pour les applications photoniques et RF sur silicium. Micro et nanotechnologies/Microélectronique. Université Grenoble Alpes, 2018. Français. NNT: 2018GREAT005. tel-01844072

# HAL Id: tel-01844072 https://theses.hal.science/tel-01844072

Submitted on 19 Jul 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Nano Electronique et Technologie

Arrêté ministériel : 25 mai 2016

Présentée par

#### **Reynald Alcotte**

Thèse dirigée par **Thierry Baron** et codirigée par **Yann Bogumilowicz**

préparée au sein du **Laboratoire des Technologies de la Microélectronique (LTM-CNRS)**

dans l'École Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal (EEATS)

Epitaxie en phase vapeur aux organométalliques de semiconducteurs III-As sur substrat silicium et formation de contacts ohmiques pour les applications photoniques et RF sur silicium

Thèse soutenue publiquement le **02 Février 2018**, devant le jury composé de :

#### **Monsieur Thierry BARON**

Directeur de recherche, CNRS Délégation Alples, Directeur de thèse **Monsieur Fabrice SEMOND**

Directeur de recherche, CNRS Délégation Côte d'Azur, Rapporteur

**Monsieur Guillaume SAINT-GIRONS**

Directeur de recherche, CNRS Délégation Rhône Auvergne, Rapporteur

**Monsieur Jean DECOBERT**

Ingénieur, Nokia Bell Labs, Examinateur

**Madame Jumana BOUSSEY**

Directeur de recherche, CNRS Délégation Alples, Président

## Table des matières

| Introduction générale                                                                             | 9  |

|---------------------------------------------------------------------------------------------------|----|

| Chapitre I                                                                                        | 12 |

| Intégration des matériaux III-V sur une plateforme silicium                                       | 12 |

| 1.1 Propriétés des matériaux III-V                                                                | 12 |

| 1.1.1 Structure de bandes à gap direct                                                            | 13 |

| 1.1.2 Mobilité des porteurs de charge                                                             | 14 |

| 1.2 Pourquoi vouloir intégrer les matériaux III-V sur silicium ?                                  | 16 |

| 1.2.1 Interconnexions optiques                                                                    | 16 |

| 1.2.2 Enjeux écologique et économique                                                             | 18 |

| 1.3 Verrous technologiques à surmonter pour permettre la réalisation de composants V sur silicium |    |

| 1.3.1 Problématique de l'épitaxie de matériaux III-V sur Si                                       | 19 |

| 1.3.1.1 Stratégies possibles pour l'intégration de III-V sur silicium                             | 26 |

| 1.3.1.1.1 Croissance pleine plaque                                                                | 26 |

| 1.3.1.1.2 Croissance via des couches tampons                                                      | 27 |

| 1.3.1.1.3 Croissance directe sur silicium                                                         | 30 |

| 1.3.1.2 Collage III-V sur silicium                                                                | 32 |

| 1.3.1.3 Croissance sélective                                                                      | 34 |

| 1.3.1.3.1 Aspect Ratio Trapping (ART)                                                             | 35 |

| 1.3.1.3.2 Confined Lateral Selective Epitaxial Growth (CLSEG)                                     | 37 |

| 1.3.1.4 Comparatif des techniques d'intégration de III-V sur silicium                             | 40 |

| 1.3.2 Résistance de contacts                                                                      | 40 |

| 1.3.2.1 Contact Metal-Semiconducteur                                                              | 42 |

| 1.3.2.2 Mécanismes de transport                                                                   | 46 |

| 1.3.2.3 Contact Ohmique                                                                           | 48 |

| 1.3.2.4 Couche de contact                                                                         | 51 |

| 1.3.3 Dopage et croissance du III-V sur silicium à basse température                              | 52 |

| 1.4 Conclusion                                                                                    | 53 |

| 1.5 Objectif de la thèse                                                                          | 54 |

| Chapitre II                                                                                       | 56 |

| Epitaxie de GaAs et InAs sur silicium (100) à basse température                                   | 56 |

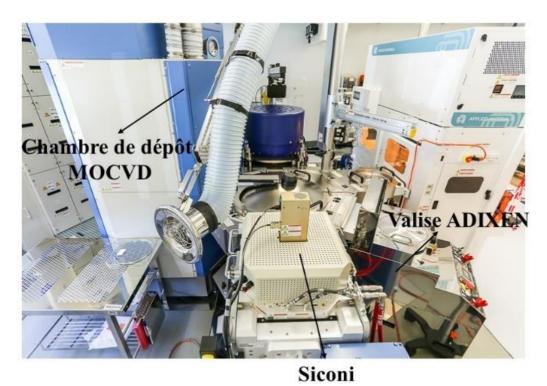

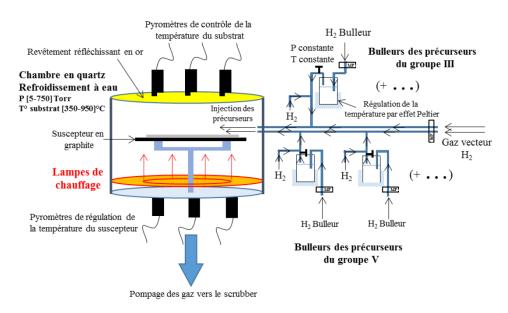

| 2.1 Bâti de croissance MOCVD                                                                      | 56 |

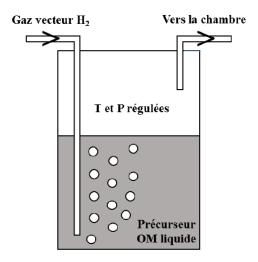

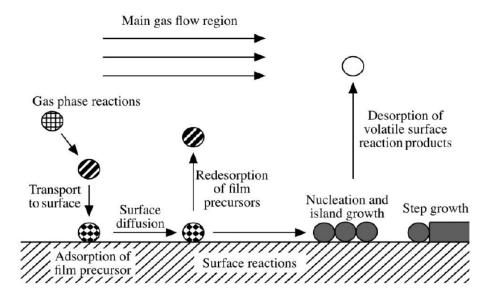

| 2.2 C         | roissance par MOCVD                                                                                    | . 58 |

|---------------|--------------------------------------------------------------------------------------------------------|------|

| 2.3 Pı        | réparation du substrat de silicium avant croissance                                                    | . 60 |

| 2.3.1         | Retrait de l'oxyde natif du silicium(100)                                                              | . 60 |

| 2.3.2         | Reconstruction de la surface du silicium (100)                                                         | . 60 |

| 2.3.          | 2.1 Effet de la pression sur la reconstruction de surface du silicium (100)                            | . 61 |

| 2.3.          | 2.2 Effet du temps de recuit sur la reconstruction de surface du silicium (100).                       | . 65 |

| 2.3.2<br>surf | 2.3 Effet de la direction de désorientation du substrat sur la reconstruction de ace du silicium (100) | . 66 |

| 2.4 C         | roissance de GaAs sur silicium sur (100)                                                               | . 66 |

| 2.4.1         | Etat de l'art de la croissance de GaAs                                                                 | . 66 |

| 2.4.2         | Croissance via des couches tampons                                                                     | . 67 |

| 2.4.          | 2.1 Croissance directe sur silicium                                                                    | . 68 |

| 2.5 C         | roissance du GaAs en deux étapes                                                                       | . 69 |

| 2.5.1         | Couche de nucléation                                                                                   | . 69 |

| 2.5.2         | Croissance à haute température                                                                         | .71  |

| 2.6 R         | ésultats expérimentaux sur la croissance de GaAs sur silicium (100)(100)                               | .71  |

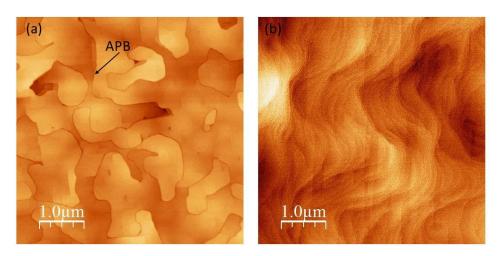

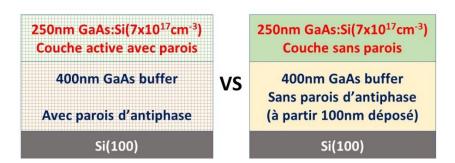

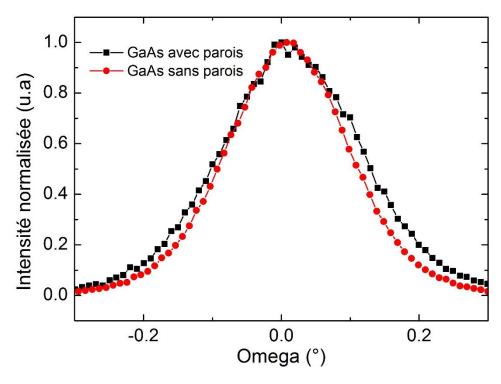

| 2.6.1         | Effet des parois d'antiphase sur les propriétés du GaAs                                                | . 73 |

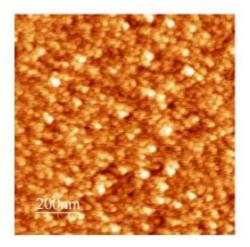

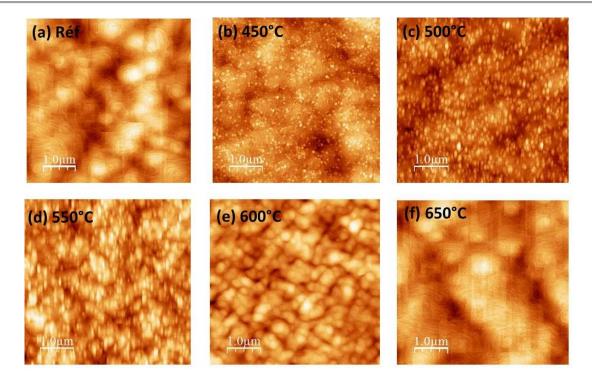

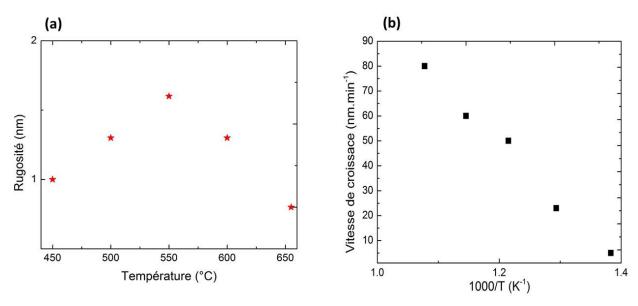

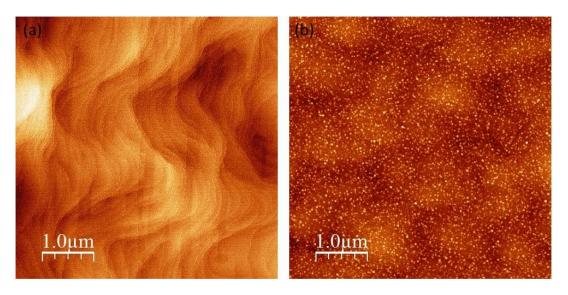

| 2.6.          | 1.1 Propriétés surfaciques des couches de GaAs                                                         | .73  |

| 2.6.          | 1.2 Propriétés électriques et optiques des couches de GaAs                                             | . 74 |

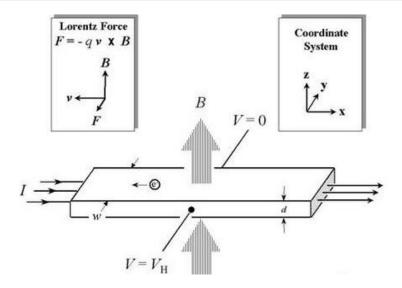

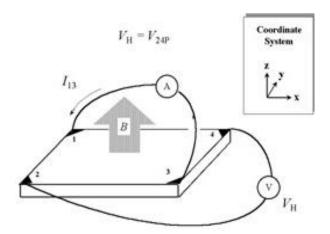

| 2.            | .6.1.2.1 Effet Hall                                                                                    | . 74 |

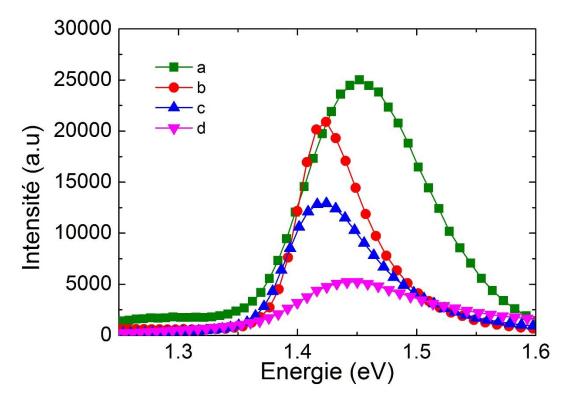

| 2.            | .6.1.2.2 Photoluminescence à température ambiante                                                      | . 77 |

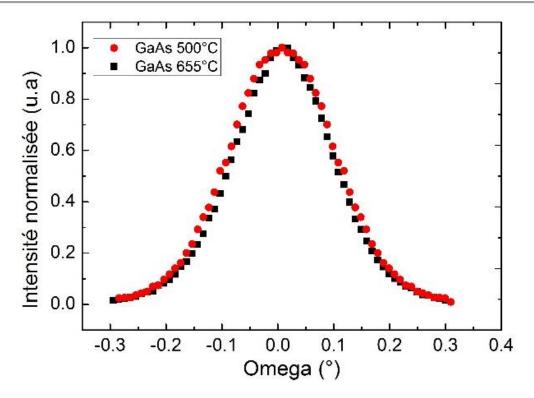

| 2.6.          | 1.3 Propriétés cristallines des couches de GaAs                                                        | . 80 |

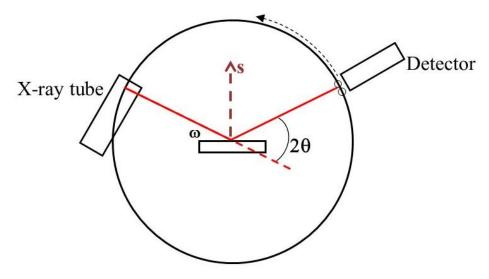

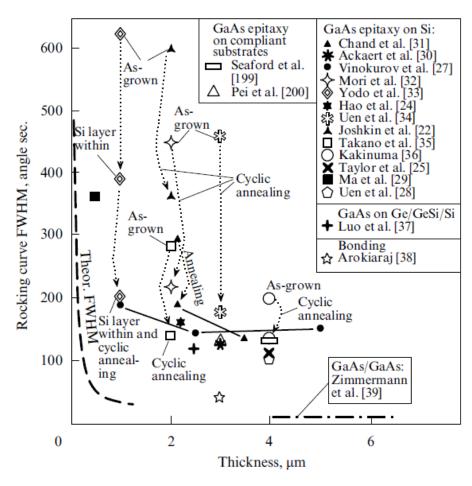

| 2.            | .6.1.3.1 Diffraction des rayons X                                                                      | . 81 |

| 2.7 R         | éduction des dislocations émergentes dans le GaAs                                                      | . 84 |

| 2.8 E         | ffet de la température sur la croissance du GaAs                                                       | . 87 |

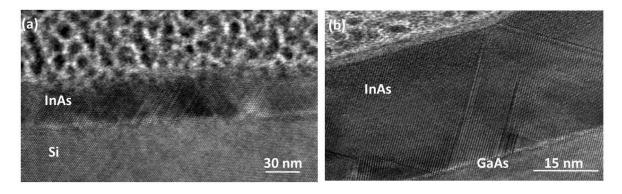

| 2.9 C         | roissance d'InAs sur silicium et GaAs                                                                  | . 90 |

| 2.9.1         | Etat de l'art de la croissance InAs sur silicium et sur GaAs                                           | .91  |

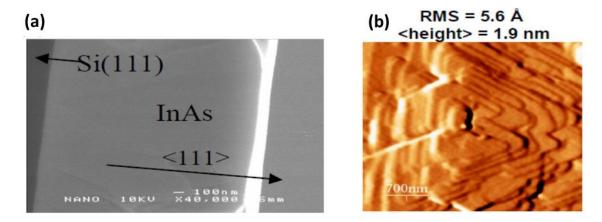

| 2.9.2         | Croissance InAs sur silicium                                                                           | .91  |

| 2.9.3         | Croissance InAs sur GaAs                                                                               | . 94 |

| 2.9.4         | Résultats expérimentaux sur la croissance d'InAs sur silicium                                          | . 95 |

| 2.9.          | 4.1 Croissance de la couche de nucléation                                                              | . 95 |

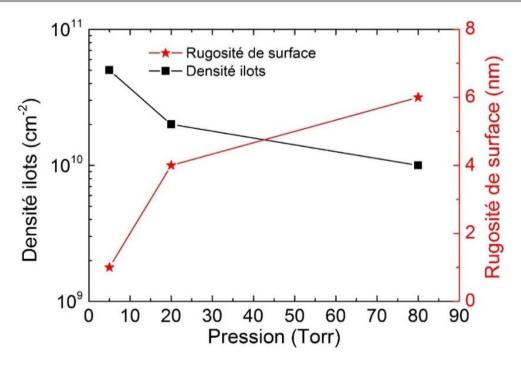

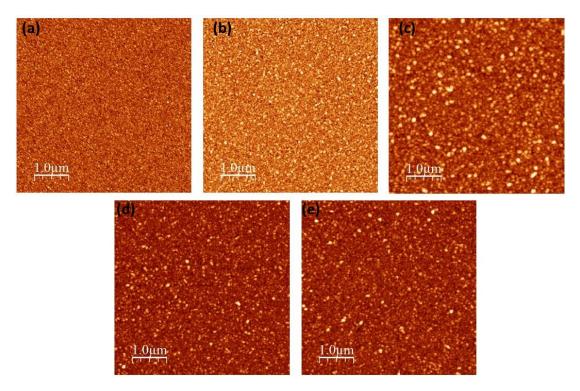

| 2.            | 9.4.1.1 Effet de la pression sur la croissance de la couche de nucléation                              | . 96 |

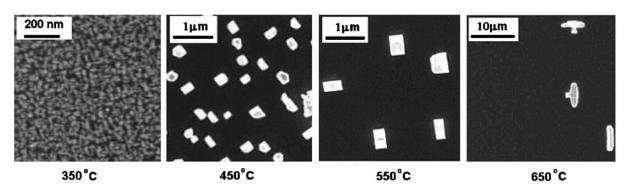

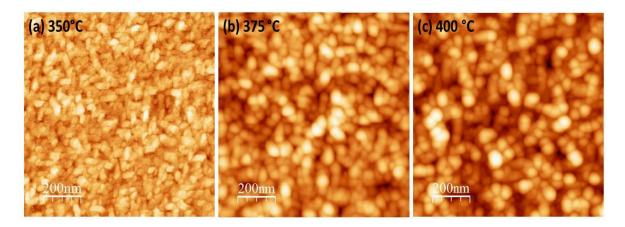

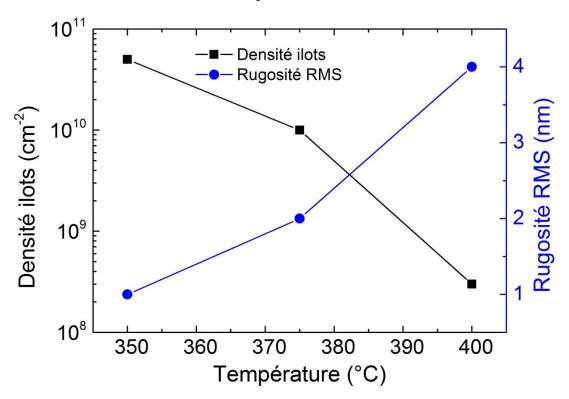

| 2.            | 9.4.1.2 Effet de la température sur la croissance de la couche de nucléation                           | . 97 |

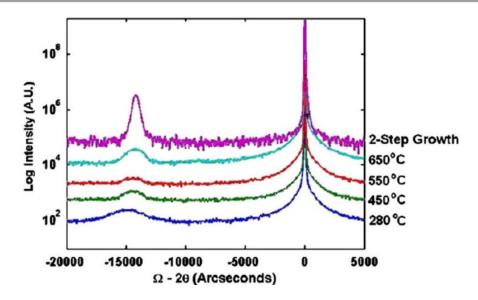

| 2.9.4         | 4.2 Croissance à haute température                                                                     | .98  |

| 2.9.4.3 Effet de la montée en température sur la couche de nucléation   | 99    |

|-------------------------------------------------------------------------|-------|

| 2.10 Conclusion                                                         | 103   |

| Chapitre III                                                            | 106   |

| Dopage GaAs et InAs                                                     | 106   |

| 3.1 Dopage des matériaux III-V                                          | 106   |

| 3.2 Dopage de type n du GaAs et de l'InAs                               | 107   |

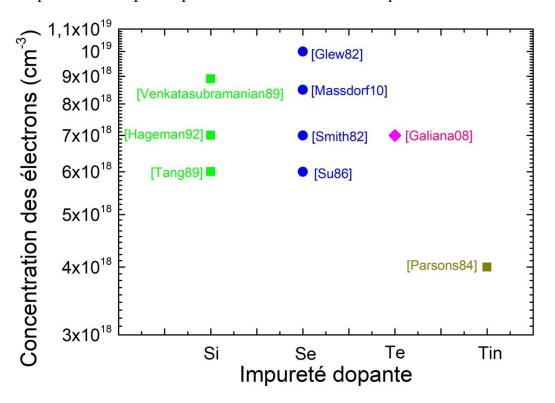

| 3.2.1 Etat de l'art du dopage de type n pour le GaAs et l'InAs          | 107   |

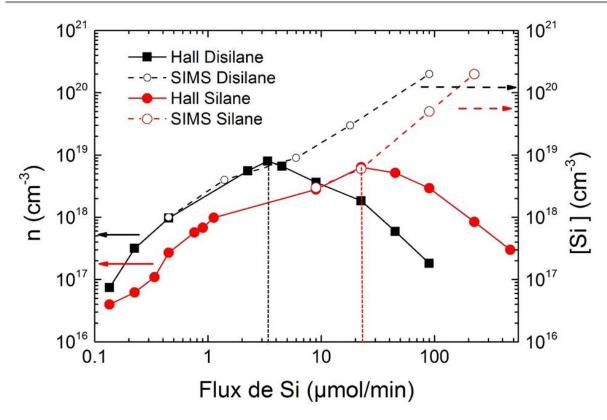

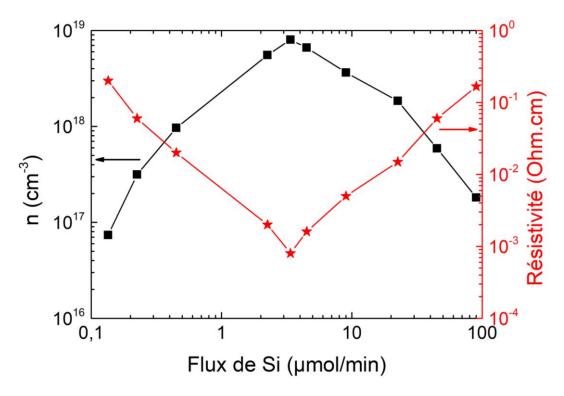

| 3.3 Etude du dopage de type n pour le GaAs avec du silicium             | 108   |

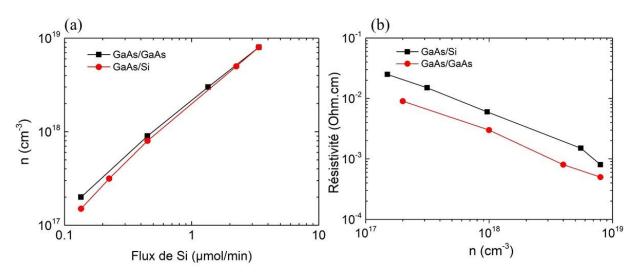

| 3.3.1 Propriétés électriques des couches de GaAs dopées n               | 108   |

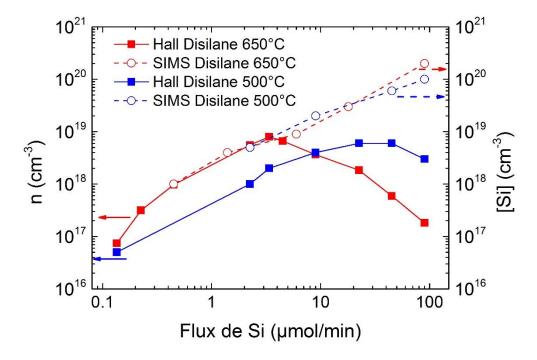

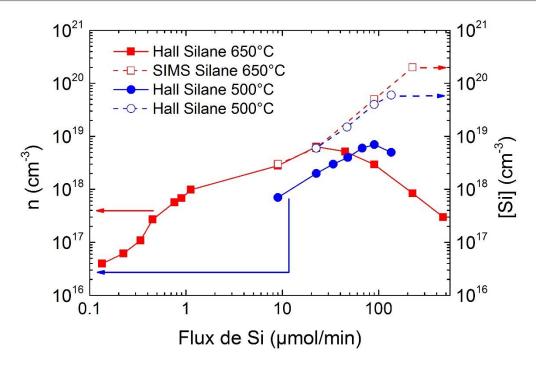

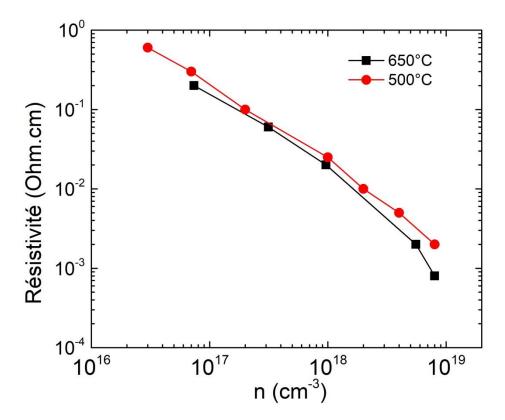

| 3.3.1.1 Effet de la température sur le dopage                           | 113   |

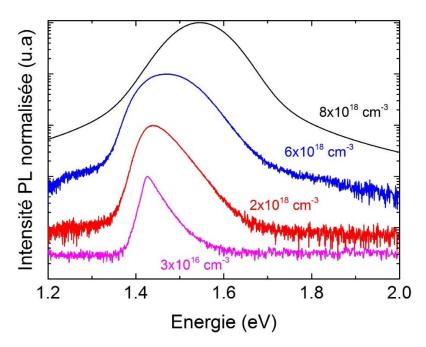

| 3.3.2 Propriétés optiques des couches de GaAs dopées n                  | 116   |

| 3.4 Etude structurale des couches de GaAs dopées n avec du silicium     | 117   |

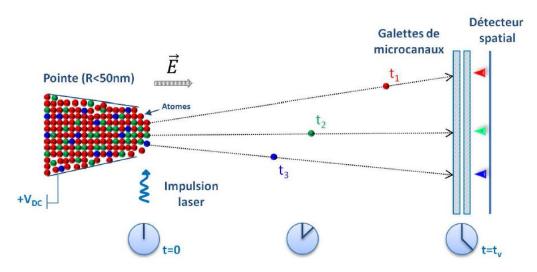

| 3.4.1 Sonde atomique tomographique                                      | 117   |

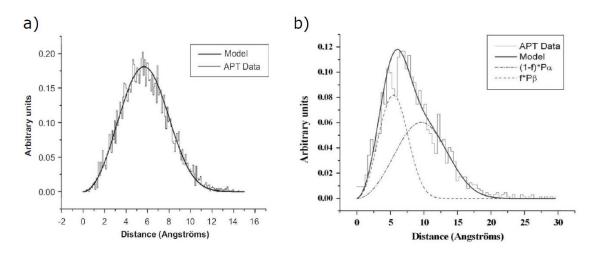

| 3.4.1.1 Méthode de traitement des données de la sonde atomique tomograp | hique |

| 3.4.1.1.1 Distribution spatiale des atomes du volume analysé            | 118   |

| 3.4.1.1.2 Distribution de distances aux premiers voisins (1NN)          | 119   |

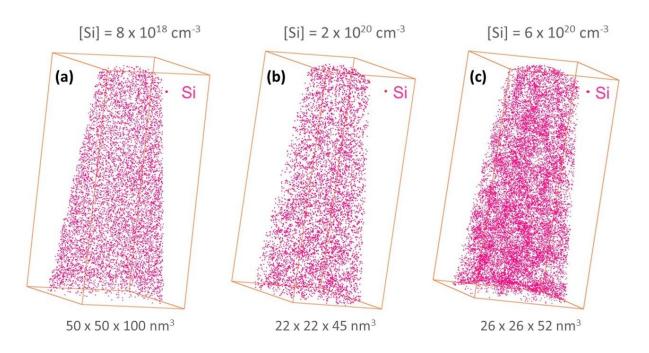

| 3.4.2 Evolution de la distribution des atomes de silicium dans le GaAs  | 120   |

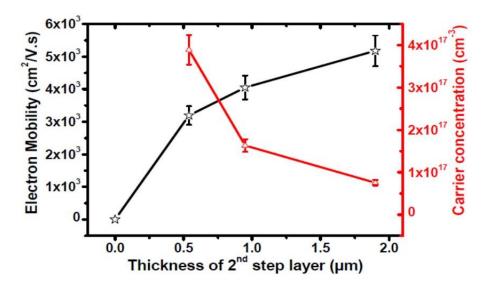

| 3.5 Etude du dopage de type n pour l'InAs avec du silicium              | 124   |

| 3.5.1 Propriétés électriques des couches d'InAs dopées n                | 124   |

| 3.6 Dopage de type p du GaAs                                            | 127   |

| 3.6.1 Etat de l'art du dopage de type p pour le GaAs                    | 127   |

| 3.6.2 Etude du dopage de type p pour le GaAs avec du zinc               | 128   |

| 3.6.2.1 Propriétés électriques des couches de GaAs dopées p             | 128   |

| 3.6.2.2 Effet de la température sur le dopage de type p                 | 130   |

| 3.7 Conclusion                                                          | 131   |

| Chapitre IV                                                             | 133   |

| Fabrication et caractérisation des contacts sur GaAs                    | 133   |

| 4.1 Caractérisation des contacts ohmiques par la méthode TLM            | 133   |

| 4.2 Détermination des propriétés du contact                             | 133   |

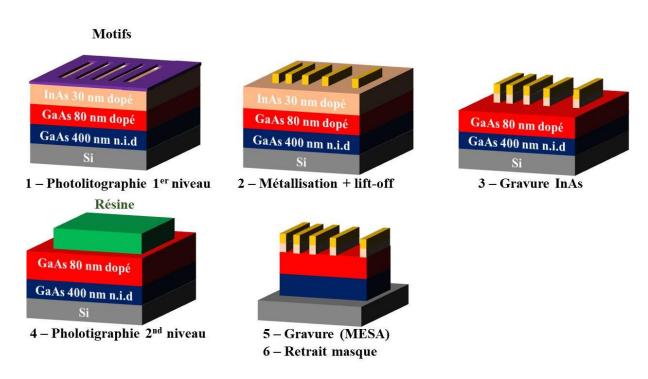

| 4.3 Fabrication des motifs TLM droits sur GaAs                          | 137   |

| 4.3.1 Contact sans InAs                                                 | 137   |

| 4.3.2 Contact avec InAs                                                 | 140   |

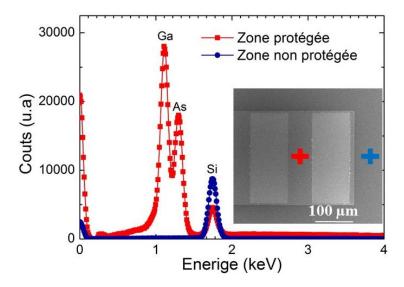

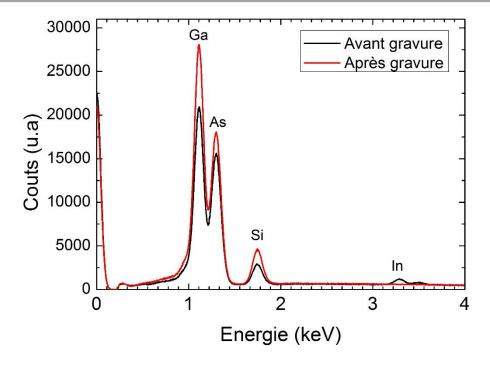

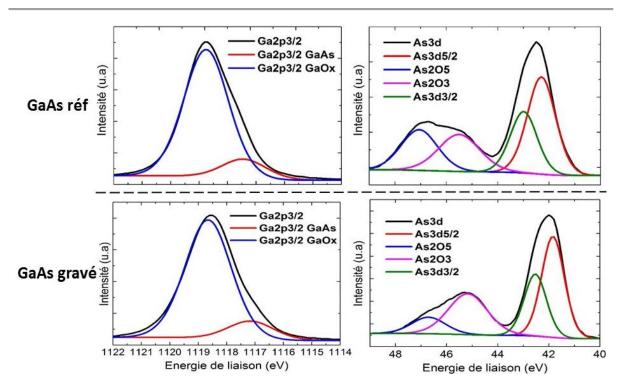

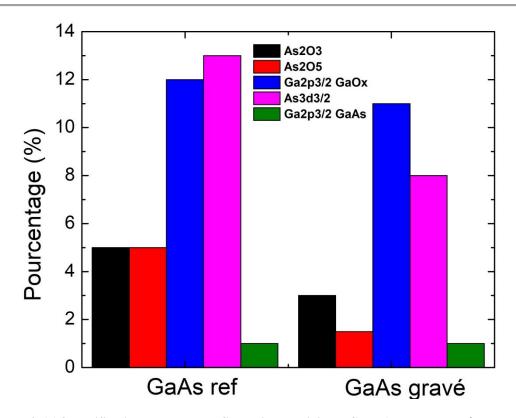

| 4.3.2.1 Gravure de la couche d'InAs                                     | 140   |

## Table des matières

| 4.4 Eta     | t de l'art sur la résistivité de contact sur GaAs                 | 144 |

|-------------|-------------------------------------------------------------------|-----|

| 4.4.1       | Etat de l'art pour les contacts de type n                         | 144 |

| 4.4.2       | Etat de l'art pour les contacts de type p                         | 145 |

| 4.5 Pro     | priétés électriques des contacts de type n et p réalisés sur GaAs | 146 |

| 4.5.1       | Caractérisation électrique des contacts de type n                 | 146 |

| 4.5.2       | Etude de la résistivité des contacts de type n sur GaAs           | 147 |

| 4.6 Car     | ractérisation électrique des contacts de type p                   | 154 |

| 4.6.1       | Etude de la résistivité des contacts de type p sur GaAs           | 155 |

| 4.7 Co      | nclusion                                                          | 157 |

| Conclusions | et perspectives                                                   | 159 |

| Références. |                                                                   | 163 |

# Introduction générale

Depuis les années 60, la miniaturisation des transistors, composants de base des circuits intégrés, a permis l'augmentation de la puissance de calcul des circuits intégrés ainsi que l'explosion du nombre de fonctions présentes au sein du circuit. Aujourd'hui, le développement futur de la microélectronique passe par l'intégration des semiconducteurs III-V sur la plateforme silicium afin de produire des composants à base de III-V à faible coût et pour remplacer les interconnexions électriques par des interconnexions optiques à base de lasers III-V.

Cependant d'un point de vue technologique l'intégration de matériaux III-V sur silicium représente un défi.

En effet, les matériaux III-V et le silicium présentent des incompatibilités qui complexifient la croissance cristalline des premiers sur le second. En premier lieu, la différence de paramètre de maille est la source de l'apparition de dislocations qui dégradent les propriétés de transport électronique et d'émission de photons du semi-conducteur III-V. Ensuite, l'écart de coefficient de dilatation thermique limite l'épaisseur totale qu'il est possible de déposer sur le silicium, sous peine de courbure du substrat, voire de rupture de la couche. Enfin, les matériaux III-V sont des composés polaires, à l'inverse du silicium qui lui est apolaire. Cette différence est la cause de la création de défauts cristallins particuliers, les parois d'antiphase.

De plus, outre l'intégration des matériaux III-V sur silicium, il est impératif de former des contacts (métal/semiconducteur) avec une faible résistivité afin d'assurer le fonctionnement optimal des composants à base de III-V fabriqués sur silicium.

Dans ce contexte, les travaux de thèse présentés dans ce manuscrit portent premièrement sur l'étude de la croissance par MOCVD (MetalOrganic Chemical Vapour Deposition) de GaAs et d'InAs sur substrats de silicium de 300 mm de diamètre puis sur la formation de contacts (type n et p) avec une faible résistivité sur GaAs. Ce document se divise en quatre chapitres distincts.

Le premier chapitre traite en détail de l'intérêt de l'intégration des matériaux III-V sur silicium. A travers celui-ci, nous mettrons en évidence les verrous communs (épitaxie des matériaux III-V sur silicium et formation de contacts avec une faible résistivité) à soulever pour permettre la réalisation de composants III-V (photoniques ou radiofréquence) sur silicium ainsi que les diverses solutions technologiques possibles pour lever ces verrous.

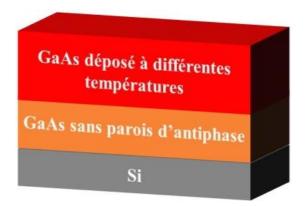

Au cours du chapitre II, nous présenterons la croissance du GaAs et d'InAs sur silicium. Dans un premier temps, nous étudierons la structuration de surface de silicium afin de former des marches biatomiques nécessaires à la croissance de matériaux III-V sans parois d'antiphase sur silicium. Après la préparation de surface du substrat, nous étudierons l'effet des parois d'antiphases sur les propriétés morphologiques, électriques et optiques du GaAs. Suite à cela,

une brève étude sur la réduction des dislocations au sein du GaAs sera faite. Pour finir, la croissance d'InAs sur silicium sera abordée.

Le chapitre III sera consacré au dopage de type n et p du GaAs et au dopage de type n de l'InAs. Au cours de ce chapitre, nous étudierons l'évolution de la concentration des porteurs de charge en fonction du flux de gaz précurseur, ainsi que l'effet de la température de dépôt sur le dopage des matériaux et l'évolution des propriétés du matériau en fonction de la concentration de porteurs.

Enfin, le chapitre IV sera consacré à la formation des contacts (type n et p) avec une faible résistivité sur GaAs. Nous étudierons au cours de ce chapitre l'effet de la métallisation et des dislocations émergentes sur la résistivité de contact.

# **Chapitre I**

# Intégration des matériaux III-V sur une plateforme silicium

Depuis la formulation de la loi de Moore dans les années 70 qui prévoit de doubler le nombre de transistors en silicium présent sur une puce tous les deux ans, l'informatique et les technologies liées à la microélectronique ont fortement évolué.

En effet, le suivi de cette loi a permis l'explosion du nombre de fonctionnalités électroniques présentes sur un circuit intégré, l'émergence, le développement et l'évolution de diverses technologies telles que les smartphones, les télévisions, les consoles de jeux, internet, les objets connectés et bien d'autres. Aujourd'hui, afin de poursuivre l'innovation et le développement de nouvelles technologies, l'industrie de la microélectronique s'intéresse fortement à l'intégration des matériaux III-V sur silicium.

Au travers de ce chapitre, nous commencerons par présenter les propriétés des matériaux III-V, leurs applications et les raisons qui poussent à vouloir les intégrer sur silicium tout en mettant en évidence les problématiques liées à cette intégration. Suite à cela, nous passerons en revue les différentes stratégies développées afin de s'affranchir de ces verrous et nous finirons ce chapitre par une présentation de l'objectif de cette thèse.

# 1.1 Propriétés des matériaux III-V

Les matériaux III-V sont des alliages obtenus en associant un ou plusieurs éléments de la colonne III du tableau de Mendeleïev (figure 1.1) avec un ou plusieurs éléments de la colonne V de ce tableau.

| 111    | IV     | V      |

|--------|--------|--------|

| 5      | 6      | 7      |

| В      | C      | N      |

| 10,81  | 12,01  | 14,01  |

| 13     | 14     | 15     |

| AI     | Si     | P      |

| 26,98  | 28,09  | 30,97  |

| 31     | 32     | 33     |

| Ga     | Ge     | As     |

| 69,74  | 72,59  | 74,92  |

| 49     | 50     | 51     |

| In     | Sn     | Sb     |

| 114,82 | 118,69 | 121,75 |

Figure 1. 1 Extrait des colonnes III, IV et V du tableau de Mendeleïev.

On peut les retrouver sous forme d'alliages binaires GaAs, InAs, InP, GaP ..., ternaires avec l'In<sub>x</sub>Ga<sub>1-x</sub>As ou l'InAs<sub>x</sub>P<sub>1-x</sub>, et quaternaire avec le Ga<sub>x</sub>In<sub>1-x</sub>As<sub>y</sub>P<sub>1-y</sub>. L'association de ces divers éléments entre eux confère aux III-V des propriétés qui diffèrent d'un composé à un autre. Certains matériaux tels que le GaAs et l'InP existent sous forme de substrats massifs et sont couramment utilisés dans l'industrie. L'intérêt suscité par ces semiconducteurs provient de deux propriétés à savoir une structure de bandes à gap direct et une forte mobilité pour les électrons.

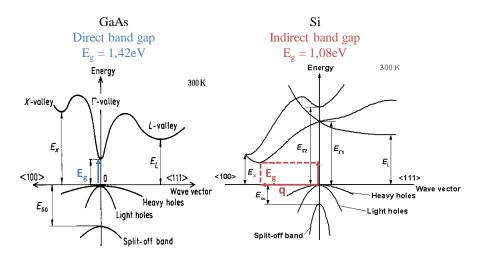

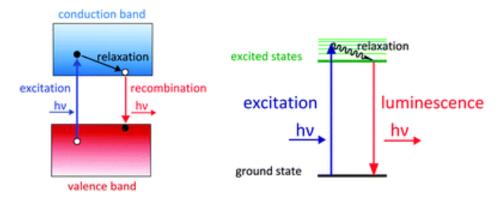

#### 1.1.1 Structure de bandes à gap direct

Contrairement au silicium qui possède une structure de bandes dite à « gap indirect », de nombreux III-V possèdent une structure de bandes à « gap direct » (figure 1.2). Un matériau semiconducteur possède un « gap direct » quand le minimum de la bande de conduction (BC) correspond au maximum de la bande de valence (BV) pour le même vecteur d'onde k comme illustré dans la figure (1.2) pour le GaAs. Cependant si le minimum de la BC ne correspond pas au maximum de la BV pour le même vecteur d'onde k, on parle alors de « gap indirect » (figure 1.2).

Figure 1. 2 Structure bandes du GaAs et du Si.

Pour un matériau à gap direct la relaxation d'une paire électron-trou donne lieu à la formation d'un photon dont l'énergie correspond à celle du gap (1.1).

$$\hbar\omega = E_g (1.1)$$

Avec : h la constante de Planck

$\omega$ : la pulsation

Eg: le gap du matériau

Alors que pour un matériau à « gap indirect », il faut satisfaire la conservation de l'énergie et du vecteur d'onde k. Ceci n'est possible que si un phonon d'énergie  $\hbar\omega(q)$  et de vecteur d'onde q participe à la transition. L'énergie d'un photon est définie par la relation (1.2) pour un matériau à gap indirect.

$$\hbar\omega = E_g + \hbar\omega(q) \, (1.2)$$

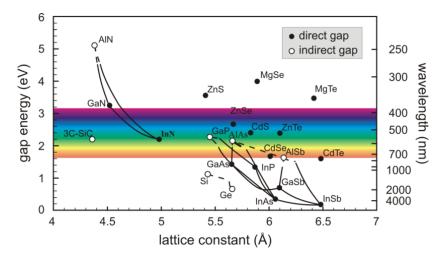

De plus, la création d'une paire électron-trou est moins rapide que pour un matériau à « gap direct ». Cette propriété rend les III-V plus attractifs que le Si pour la réalisation de dispositifs optiques. La figure (1.3) montre la gamme spectrale couverte par les matériaux III-V, celle-ci s'étend de l'ultra-violet à l'infrarouge. Les matériaux binaires InP et GaAs sont majoritairement utilisés en optoélectronique comme source électroluminescente pour les fibres optiques, les LED (Light Emitting Diode) émettant dans le spectre visible et infrarouge. Ces semiconducteurs sont utilisés au sein de diverses technologies comme les écrans de télévisions, de téléphones, l'éclairage, les lecteurs de CD, DVD, blu-ray et les cellules solaires à haut rendement (multijonctions).

Figure 1. 3 Paramètre de maille et énergie de bande interdite des matériaux III-V.

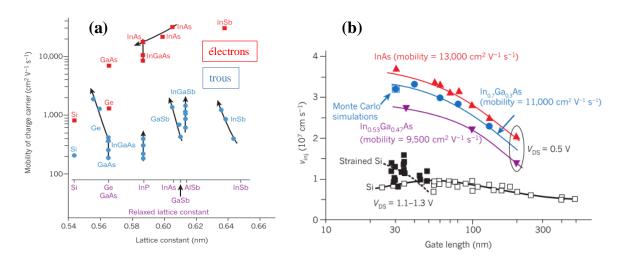

## 1.1.2 Mobilité des porteurs de charge

La mobilité électronique est présentée dans la figure (1.4 (a)). On remarque que certains semiconducteurs III-V (InGaAs, InAs et InSb) possèdent des mobilités électroniques dépassant la dizaine de milliers de cm².V-¹.s-¹. A titre de comparaison avec la mobilité des électrons du silicium, ces valeurs sont 10 à 100 fois supérieures. Actuellement, cette forte mobilité des III-V est exploitée dans des transistors HEMT (High Electron Mobility Transistor) pour les applications nécessitant le fonctionnement à des fréquences élevées (micro-ondes). A travers la figure (1.4 (b)), la vitesse d'injection des électrons dans les transistors HEMT (InAs, In<sub>0,53</sub>Ga<sub>0,47</sub>As et In<sub>0,7</sub>Ga<sub>0,3</sub>As) est comparée à celle des transistors MOSFET Si (Metal Oxyde Semiconductor Field Effect Transistor) et permet de voir qu'elle est plus importante pour les HEMT III-V que pour les MOSFET Si.

Figure 1. 4 (a) Mobilité des trous et des électrons pour différents III-V comparée avec le Si et le Ge. (b) Vitesse d'injection des électrons pour des HEMT III-V comparée au MOSFET en silicium pour différentes longueurs de grille [Del Alamo11]

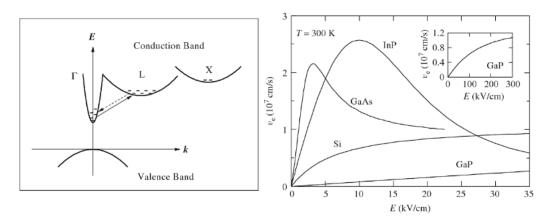

Une autre propriété intéressante de ces composés par rapport au Si, est leur tenue à haute fréquence. A très fort champ électrique, la vitesse des porteurs atteint une vitesse maximale appelée « vitesse de saturation » puis au-delà d'une certaine valeur pour le champ électrique la vitesse des porteurs commence à chuter. La figure (1.5) montre ce phénomène pour l'InP et le GaAs. La réduction de la vitesse avec l'augmentation du champ électrique est due au passage d'une partie des électrons dans la vallée L puis dans la vallée X [Adachis05][Howes85]. La masse effective des électrons dans la vallée L étant plus importante que dans la vallée  $\Gamma$  cela induit une diminution de la vitesse des électrons et de la vitesse moyenne.

Figure 1. 5 A gauche passage des électrons pour le GaAs de la vallée  $\Gamma$  vers la vallée L pour un fort champ électrique. A droite, évolution de la vitesse de saturation pour le GaAs, InP, GaP et Si [Adachi05].

Cette propriété appelée « l'effet Gunn » (mobilité à différentielle négative) couplée à la forte mobilité électronique du GaAs et de l'InP permet la réalisation de HEMT fonctionnant jusqu'à 300 GHz. Ces transistors sont principalement utilisés dans les systèmes de communication sans fil tel que le WIFI, le blueetooth, les réseaux mobiles (1G, 2G, 3G, 4G et prochainement 5G) ainsi que dans applications militaires (radars et satellites).

Au cours de cette partie nous avons mis en avant les propriétés des matériaux III-V et montré qu'ils sont présents dans diverses technologies que nous utilisons quotidiennement. Par conséquent une question nous vient à l'esprit 'pourquoi cherchons nous à intégrer ces matériaux sur silicium ?' La réponse à cette question sera apportée au cours de la partie suivante.

#### 1.2 Pourquoi vouloir intégrer les matériaux III-V sur silicium ?

Au cours de cette partie, nous allons mettre en évidence l'intérêt de l'intégration des matériaux III-V sur silicium.

#### 1.2.1 Interconnexions optiques

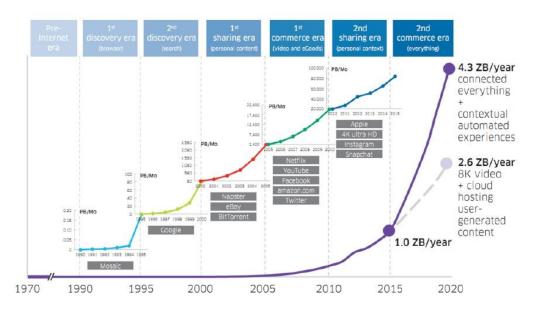

L'une des conséquences du développement des technologies numériques est l'évolution du volume de données échangées au sein d'un circuit intégré et à travers le monde. Ceci est dû à l'augmentation de la puissance de calcul des processeurs, à la fonctionnalisation des circuits intégrés, au développement d'internet, des applications sur mobiles, des réseaux sociaux ou encore des objets connectés (IoT) (figure 1.6).

Figure 1. 6 Evolution du trafic de l'information depuis 1970 avec une projection pour 2020 [Weldon16].

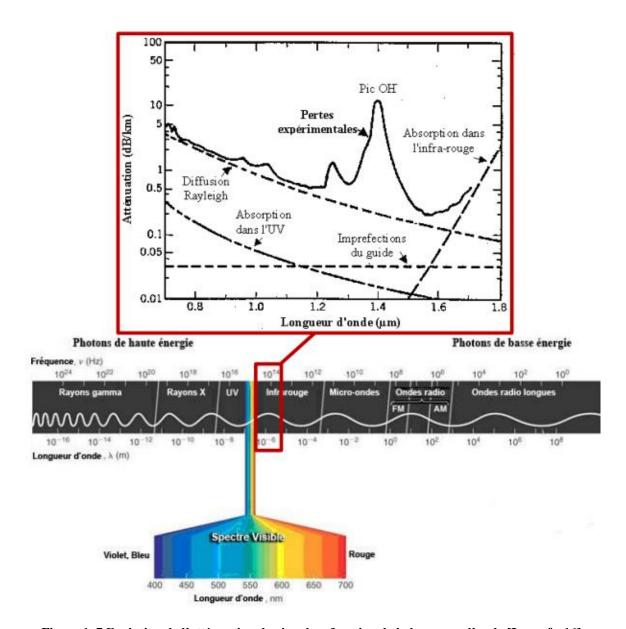

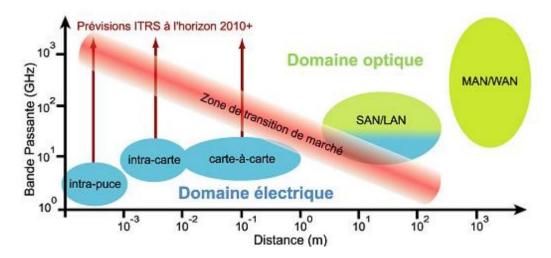

Avec l'augmentation de la demande globale en bande passante, les interconnexions électriques qui assuraient auparavant le transfert de l'information pour les réseaux télécoms ont été remplacées par des interconnexions optiques depuis les années 80 pour les applications longue distance (>10 km). La raison pour cela est que les interconnexions électriques souffrent de pertes de l'information d'environ 10 dB/km. Ces pertes liées à l'effet Joule induisent une atténuation du signal, des problèmes de latence et l'augmentation de la puissance dissipée du circuit. Par conséquent, afin de palier ces limitations, les efforts d'ingénierie ont conduit au remplacement des interconnexions électriques par des lasers à semiconducteurs et des fibres optiques car le transport de l'information est plus rapide et souffre de moins de pertes. En effet, avec les lasers et les fibres optiques la perte du signal est

de 0,22 dB/km pour un fonctionnement entre 1,3  $\mu m$  et 1,55  $\mu m$  (figure (1.7)) et les débits d'informations sont de l'ordre de 13 Tb/s sur 2500 km contre seulement 150 Mb/s sur 200 m pour les interconnexions électriques.

Figure 1. 7 Evolution de l'atténuation du signal en fonction de la longueur d'onde [Levaufre16].

Toutefois en ce qui concerne les petites et moyennes distances (<10 m), le transfert de l'information est toujours assuré par les interconnexions électriques (figure 1.8). Cette décision a été prise car les technologies optiques actuelles sont rentables pour les liaisons télécoms d'une distance supérieure à 10 m.

Figure 1. 8 Présentation du marché des interconnexions électriques et optiques.

Cependant à cause de l'évolution des technologies, de la mutation de nos réseaux de communications et des prochains besoins en bande passante (figure (1.6)), les experts de l'ITRS préconisent de remplacer les interconnexions électriques des circuits intégrés par des interconnexions optiques à base de III-V afin d'éviter les problèmes de latence, de pertes du signal et de forte puissance dissipée qui apparaitront à cause des futurs débits d'informations à gérer. Par conséquent afin de pouvoir opérer ce remplacement, il est envisagé d'intégrer directement les matériaux III-V (GaAs, InAs, InGaAs, InP et InGaAsP) sur la plateforme silicium afin de réaliser par la suite des lasers fonctionnant entre 1,3 µm et 1,5 µm. Ces longueurs d'onde ont été choisies car elles permettent d'avoir respectivement une dispersion chromatique nulle et une atténuation minimum à ces longueurs d'ondes.

## 1.2.2 Enjeux écologique et économique

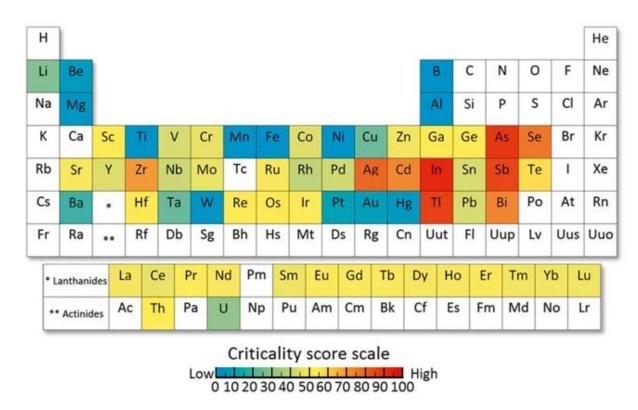

Outre l'aspect photonique, l'intégration des matériaux III-V sur silicium serait une solution pour produire des substrats III-V abordables et de grandes tailles. En effet, du fait de la rareté du gallium, de l'indium, ou bien encore de l'arsenic, les substrats de III-V commercialisés sont onéreux et disponibles uniquement en petites dimensions contrairement à ceux en silicium. A titre d'exemple, un substrat d'un diamètre de 300 mm de silicium vaut 25 dollars tandis qu'un substrat de GaAs avec un diamètre de 100 mm vaut environ 200 dollars. De plus, une étude menée par des chercheurs de l'université de Yale a montré que certains éléments couramment utilisés dans nos technologies tels que l'indium (In), le gallium (Ga), l'arsenic (As) ou encore l'antimoine (Sb) risquaient de ne plus être disponibles dans le futur (figure 1.9). Une pénurie de ces éléments aurait pour effet d'induire une hausse significative du prix de vente des substrats de GaAs et d'InP commercialisés. Par conséquent, afin d'éviter la pénurie des ressources naturelles nécessaires à la fabrication des substrats III-V, l'intégration des semiconducteurs III-V sur silicium est une solution.

Figure 1. 9 Tableau périodique des éléments mettant en avant les difficultés à fournir certains éléments [Graedel15].

# 1.3 Verrous technologiques à surmonter pour permettre la réalisation de composants III-V sur silicium

Afin de réaliser des composants photoniques ou radiofréquences à base de matériaux III-V performants sur silicium, divers verrous technologiques propres à chaque technologie doivent être franchis. Cependant trois de ces verrous sont communs à ces deux types de composants :

- Epitaxier un matériau III-V de bonne qualité sur silicium

- Former des contacts (métal/semiconducteur) avec une faible résistivité

- Respecter le budget thermique pour la croissance et le dopage des matériaux

Dans la suite de cette partie, nous discuterons de chacun de ces verrous en détail.

# 1.3.1 Problématique de l'épitaxie de matériaux III-V sur Si

L'intégration des matériaux III-V sur silicium représente un challenge en raison des nombreux défauts générés durant l'épitaxie. Ces défauts sont induits par des différences de propriétés intrinsèques entre le silicium et le III-V. Dans cette partie, nous mettrons en avant ces différences et leurs impacts sur la croissance du III-V. Celles-ci se divisent en trois catégories : la différence de coefficient de dilatation thermique, de paramètre de maille et de polarité.

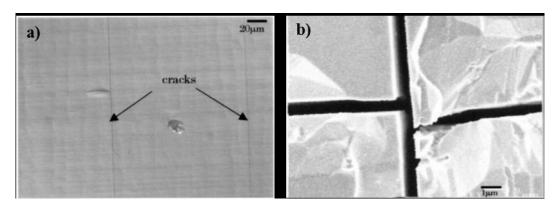

Différence de coefficient de dilatation thermique: Les III-V possèdent un coefficient de dilatation thermique différent de celui du silicium. Par exemple le GaAs, l'InAs, et l'InP possèdent respectivement un coefficient de dilatation thermique de 5,73 x 10<sup>-6</sup> °C <sup>-1</sup>, 4,52 x 10<sup>-6</sup> °C <sup>-1</sup> et 4,60 x 10<sup>-6</sup> °C <sup>-1</sup> tandis que pour le silicium celui-ci est de 2,6 x 10<sup>-6</sup> °C <sup>-1</sup>. Cette différence a tendance à induire des contraintes au sein du matériau épitaxié lorsqu'il est chauffé et refroidi. Les épitaxies de III-V se faisant généralement à haute température, lors de la phase de refroidissement des contraintes en tension se forment dans le matériau déposé. Cela se traduit par une augmentation de l'énergie élastique stockée par le matériau (relation 1.3). Si ces contraintes sont trop importantes, elles peuvent induire une déformation du substrat le rendant ainsi inutilisable par les robots des équipements [Zhu09]. Outre la courbure des substrats, des fissures peuvent aussi se produire comme le montre la figure (1.10) pour une énergie élastique très importante. Ces fissures sont à éviter car elles dégradent les propriétés du matériau et par conséquent les performances d'un dispositif.

Figure 1. 10 Fissures générées pour des couches de GaAs (a) de 2,8 µm (b) 8 µm [Yang03].

L'énergie élastique est définie par la relation (1.3).

$$E_e = 2t^2 G \frac{(1-v)}{(1+v)} f^2$$

(1.3)

Avec t: L'épaisseur de la couche epitaxiée

G : Le module de cisaillement de la couche v : Le coefficient de poisson de la couche

f: La déformation de la couche

Afin de déterminer l'épaisseur maximale qu'il est possible de déposer avant l'apparition de fissures, on considère l'énergie de formation d'une fissure (Ec) comme le double de l'énergie de surface (Es) d'un plan où apparaissent les dislocations, que multiplie l'épaisseur t de la couche (relation (1.4)).

$$E_c = 2tE_S (1.4)$$

Par exemple pour le GaAs, les fissurent apparaissent selon le plan (110) [Messmer81].

En faisant une égalité entre les relations (1.3) et (1.4), on peut déterminer l'épaisseur maximale  $t_C(1.5)$ :

$$t_C = \frac{E_S(1-v)}{G(1+v)f^2}$$

(1.5)

f représente la déformation induite par la différence de coefficient de dilation thermique entre le III-V et le silicium sur la gamme de température qui nous intéresse. Elle s'exprime selon la relation (1.6).

$$f = (\alpha_{III-V} - \alpha_{Si})\Delta T (1.6)$$

L'expression montre que l'épaisseur maximale que l'on peut déposer avant l'apparition des fissures diminue avec l'augmentation de l'écart entre la température de dépôt et celle à laquelle l'empilement refroidit en fin d'épitaxie. Dans le GaAs, des fissures apparaissent pour des croissances de 3 µm à 5,5 µm quand la croissance se passe entre 500°C et 700°C.

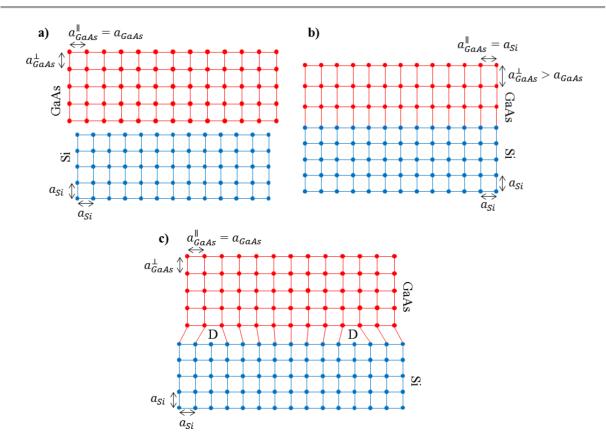

<u>Différence de paramètre de maille</u>: L'un des paramètres importants en ce qui concerne l'épitaxie de deux matériaux différents est la différence de paramètre de maille  $(\frac{\Delta a}{a})$  entre ces deux matériaux (figure 1.11 (a)). Elle est définie par la relation (1.7):

$$\frac{\Delta a}{a} = \frac{a_M - a_S}{a_S} \tag{1.7}$$

Avec a<sub>M</sub>: Le paramètre de maille du matériau déposé

as: Le paramètre de maille du substrat

Lors de la croissance d'un matériau A sur un matériau B, la contrainte générée par la différence de paramètre de maille modifie le paramètre de maille du matériau A dans le plan  $(a_{A//})$  afin de s'adapter à celui du substrat durant les premiers instants de la croissance. Cela produit une augmentation ou une diminution du paramètre de maille du matériau déposé dans la direction normale au plan de croissance  $(a_A \perp)$ . On parle dans ce cas de croissance pseudomorphique (figure 1.11 (b)). A cet instant, le matériau A est contraint. Il peut être en compression si  $a_A > a_B$  ou en tension si  $a_A < a_B$ . A mesure que la couche déposée sur le substrat s'épaissit, l'énergie élastique emmagasinée par le matériau évolue jusqu'à une énergie critique. Lorsque celle-ci est dépassée, des dislocations apparaissent dans le matériau afin de relâcher la contrainte. Cette relaxation permet au matériau de reprendre son paramètre de maille (figure 1.11 (c)). Le point de non-retour avant l'apparition des dislocations est appelé l'épaisseur critique ( $h_c$ ) et s'exprime selon la relation (1.8) [Matthews75].

$$h_c = \frac{b}{8\pi(1+v)\frac{\Delta a}{a}} \left( ln\left(\frac{h_c}{b}\right) + 1 \right) (1.8)$$

Avec b: La norme du vecteur de Burgers de la dislocation

v : Le coefficient de poisson du matériau épitaxié

Figure 1. 11 Représentation schématique de la croissance GaAs sur silicium à différentes étapes. (a) Matériaux massifs pris individuellement. (b) Croissance pseudomorphique ( $h < h_c$ ). (c) Croissance couche relaxée ( $h > h_c$ ).

Les matériaux tels que le GaAs, l'In<sub>0.53</sub>Ga<sub>0.47</sub>As, l'InP, l'InAs et le GaSb sont par exemple soumis à une compression lors de la croissance sur silicium car ils ont un paramètre de maille supérieur à celui du silicium. A titre d'exemple, la différence de paramètre de maille de ces matériaux avec le silicium est de 4%, 8%, 8% 12%, 13% respectivement pour les systèmes GaAs/Si, In<sub>0.53</sub>Ga<sub>0.47</sub>As/Si, InP/Si, InAs/Si et GaSb/Si. Dans le cas du système GaAs sur silicium, la relation (1.8) donne une épaisseur critique inférieure au nanomètre. Ces dislocations tout comme les fissures sont des défauts dont on cherche à s'affranchir car ils agissent comme des centres de diffusion et de recombinaison non radiatifs [Fang90]. Ce comportement contribue à la diffusion des porteurs de charge et à la dégradation des propriétés intrinsèques du matériau [Fang90]. Ces dislocations présentent la particularité de pouvoir se propager au sein de la couche épitaxiée jusqu'à la surface ainsi qu'à travers un empilement de différentes couches. Une épitaxie standard de GaAs sur silicium génère une densité de dislocations d'environ 10<sup>9</sup> cm<sup>-2</sup> pour une épaisseur de 100 nm [Yamaguchi91]. Ceci représente une différence de 5 ordres de grandeur avec un substrat massif commercial de GaAs (10<sup>4</sup> cm<sup>-2</sup>). Il est donc nécessaire de réduire drastiquement la densité de ces défauts pour pouvoir espérer intégrer ces matériaux sur silicium.

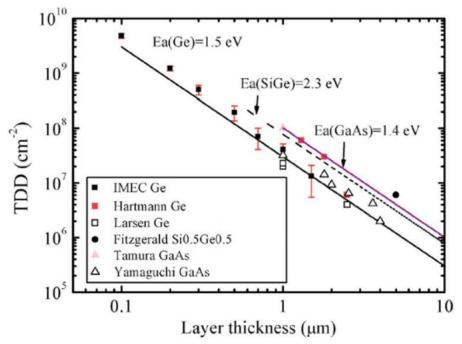

La figure (1.12) montre un modèle reliant l'évolution de la densité de dislocations dans le GaAs en fonction de l'épaisseur. A travers cette figure on remarque que pour atteindre une densité équivalente à celle des substrats massifs, une épaisseur supérieure à 10 µm est

nécessaire. Or, la croissance de couches épaisses de plusieurs microns est limitée par la formation des fissures.

Figure 1. 12 Evolution de la densité des dislocations (TDD) en fonction de l'épaisseur du GaAs sur Si [Wang09].

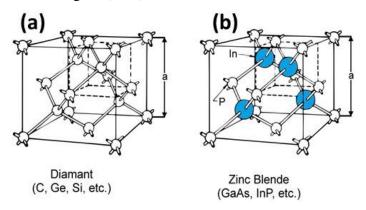

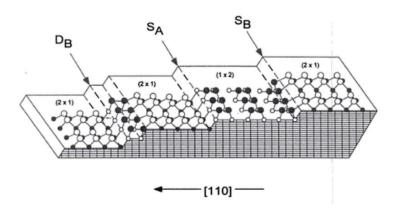

**<u>Différence de polarité</u>**: Au niveau cristallographie, une grande partie des matériaux III-V possèdent une structure cristallographique de type Zinc-Blende. Dans cette configuration les atomes III et V occupent chacun un sous-réseau décalé de a[1/4,1/4,1/4]. Le silicium lui possède une structure de type diamant. Cette structure est équivalente à la structure Zinc-Blende sauf que celle-ci est uniquement composée d'un seul type d'atome. Les deux structures sont représentées figure (1.13)

Figure 1. 13 Structure cristallographique (a) Diamant (b) Zinc Blende.

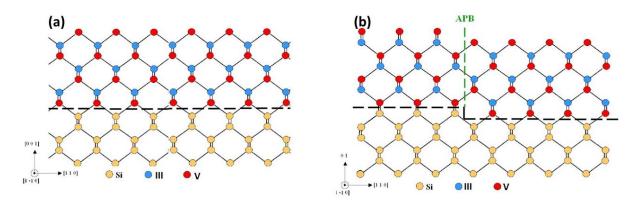

En raison de la présence de deux atomes différents dans la structure cristallographique d'un III-V, la croissance de ces matériaux se déroule selon un dépôt successif de monocouches d'éléments III et V. Dans un cas parfait où l'on possède une surface de silicium plane, l'épitaxie donne lieu à un empilement de type ABABABA... où A représente une monocouche d'un élément et B une monocouche de l'autre élément (figure 1.14 (a)). Toutefois dans la pratique, la surface du silicium est composée de marches monoatomiques

(figure 1.14 (b)). Lors de la croissance du III-V sur une telle surface, le passage d'une marche monoatomique à une autre induit une rupture de la continuité des monocouches déposées. Cela entraine la formation de liaisons homoatomiques III-III et/ou V-V.

Figure 1. 14 Croissance de GaAs (a) sur une surface de silicium idéale. (b) sur une surface présentant des marches monoatomiques [Chriqui05].

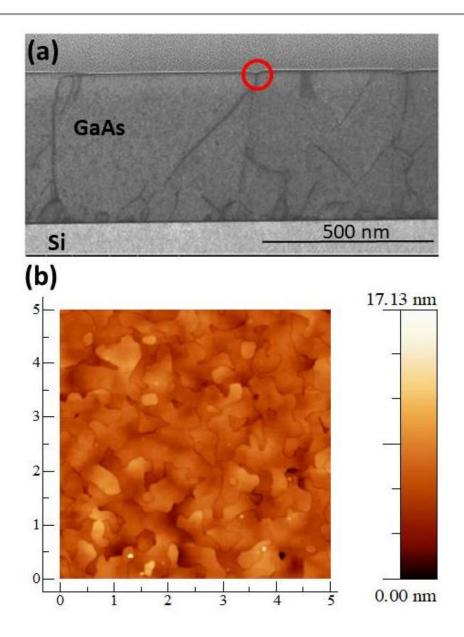

Ces liaisons appelées parois d'antiphase (APB pour antiphase boundaries en anglais) sont nuisibles à la bonne qualité cristalline du III-V. En effet, ces liaisons agissent comme des centres de recombinaisons non-radiatifs pour les porteurs [Fang90]. De plus, elles peuvent induire un dopage non intentionnel du matériau ce qui modifie ses propriétés intrinsèques. Pour finir, ces défauts peuvent se propager de l'interface III-V/Si à la surface du composé III-V entraînant la formation de sillons de quelques nanomètres de profondeur à la surface (figure 1.15).

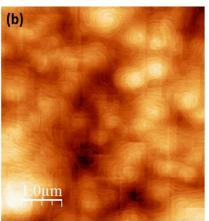

Figure 1. 15 (a) Image FIB-STEM d'une coupe de GaAs épitaxié sur Si. (b) Image AFM 5x5 um de la surface d'un GaAs sur Si montrant des sillons provoquéspar des parois d'antiphase.

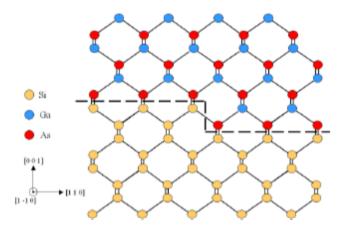

Une solution envisagée pour s'affranchir des parois d'antiphase est de faire la croissance sur un substrat de silicium ayant des marches non plus monoatomiques mais biatomiques. Avec ce type de marche, il a été montré que la croissance était exempte de parois d'antiphase (figure 1.16) car les éléments III et V n'intègrent pas le même sous-réseau.

Figure 1. 16 Croissance du GaAs sur une surface de silicium avec des marches biatomiques [Chriqui05].

Les substrats de silicium dit désorientés sont fréquemment utilisés pour générer des marches biatomiques et ainsi faire croître les composés III-V sans parois d'antiphase [Bolkhovityanov08][Deppe87][Choi91]. Ces substrats possèdent une surface qui forme un angle  $\theta$  de  $4^{\circ}$  à  $6^{\circ}$  avec le plan (100). La largeur des terrasses qui séparent deux marches atomiques est donnée par la relation (1.9).

$$L = \frac{a}{4tan(\theta)} (1.9)$$

Avec L: La largeur de la terrasse

a : Le paramètre de maille du matériau

Θ : L'angle formé avec le plan (100)

Un traitement thermique avant la croissance permet également la formation des marches biatomiques sur ces substrats. Cependant il n'est pas prévu de les utiliser car ils ne sont pas standards dans l'industrie de la microélectronique.

# 1.3.1.1 Stratégies possibles pour l'intégration de III-V sur silicium

Nous venons de voir que l'intégration des semiconducteurs III-V sur silicium nécessite de pouvoir réaliser une épitaxie de bonne qualité. Afin de s'affranchir des contraintes citées plus haut différentes stratégies de croissance ont été développées. Celles-ci peuvent être classées en deux catégories à savoir : la croissance pleine plaque et la croissance sélective.

#### 1.3.1.1.1 Croissance pleine plaque

Dans le cas d'une croissance pleine plaque, 3 approches sont possibles :

- L'épitaxie sur Si en utilisant des couches tampons aussi appelées « buffer »

- L'épitaxie directe sur Si en suivant un procédé de croissance en deux étapes

- Le report d'une épitaxie de III-V sur Si par collage

#### 1.3.1.1.2 Croissance via des couches tampons

Afin d'adapter la différence de paramètre de maille entre le III-V et le Si, il est possible d'utiliser des matériaux dont le paramètre de maille se situe entre celui du III-V et du Si. Ces couches appelées couches tampons permettent de réduire la densité de dislocations formée dans le matériau d'intérêt. Elles peuvent être classées en deux catégories : celles avec un paramètre de maille constant et celles dont le paramètre de maille peut évoluer.

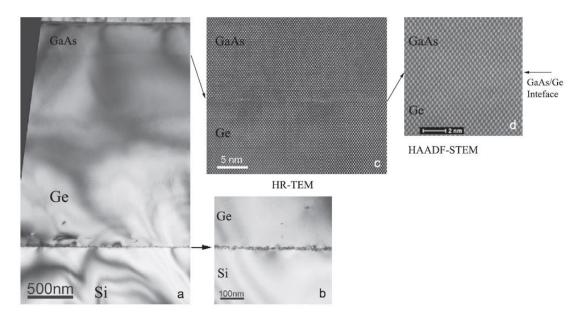

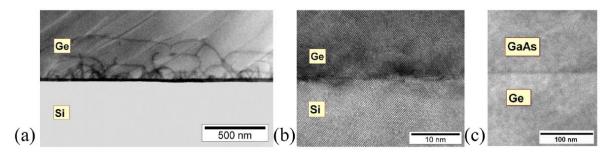

Couches tampons à composition constante : Dans la littérature, le germanium est souvent utilisé en tant que couche tampon pour la croissance de GaAs. En effet, ce matériau est un matériau de choix car il possède le même paramètre de maille que le GaAs et un coefficient de dilatation thermique proche de celui du GaAs. La figure (1.17) présente la croissance de GaAs d'une épaisseur de 400 nm sur une couche tampon de germanium de 2 μm réalisée par D. Choi et al [Choi09]. Un substrat de silicium désorienté de 4° est utilisé afin d'obtenir un matériau sans parois d'antiphase. Au travers de cette publication les auteurs ne donnent aucune valeur en ce qui concerne la densité de dislocations. Toutefois avec cette approche, ils obtiennent de la photoluminescence pour des puits quantiques In<sub>0,2</sub>Ga<sub>0,8</sub>As (10 nm) similaire à celle obtenue pour une croissance sur substrat GaAs.

Figure 1. 17 Couche de GaAs épitaxié sur silicium désorienté de 4° avec une couche tampon en germanium [Choi09].

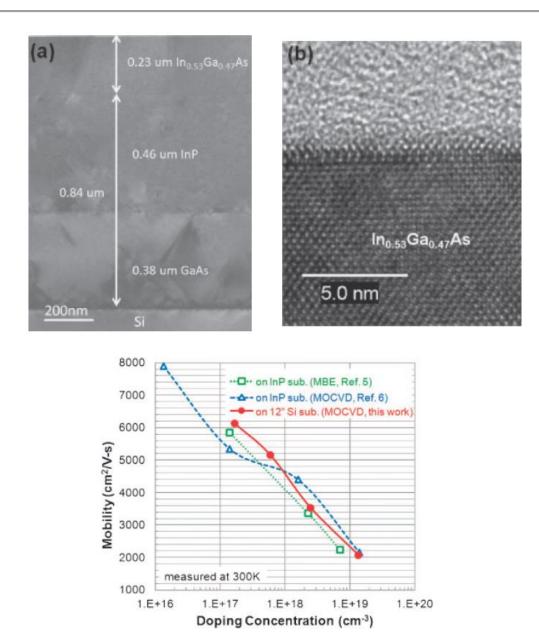

Un autre exemple est présenté figure (1.18). Cette fois il s'agit de la croissance d'In<sub>0,53</sub>Ga<sub>0,47</sub>As sur un substrat de silicium. Afin d'adapter la différence de paramètre de maille entre les deux matériaux, les auteurs ont utilisé un empilement InP(460 nm)/GaAs(380 nm) en tant que couche tampon. Dans cette publication, la désorientation du substrat n'est pas précisée toutefois l'In<sub>0,53</sub>Ga<sub>0,47</sub>As épitaxié a une épaisseur de 230 nm et possède une mobilité électronique équivalente à celle des épitaxies directes sur substrat InP (figure 1.18). La densité de dislocations des matériaux épitaxiés est de 10<sup>9</sup> cm<sup>-2</sup> [Lin14].

Figure 1. 18 Croissance d'une couche d'In<sub>0,53</sub>Ga<sub>0,47</sub>As sur silicium avec comme couche tampon un empilement InP/GaAs [Lin14].

<u>Couches tampons à composition variable</u>: Les couches tampons peuvent aussi être réalisées à l'aide d'alliage dont on fait varier la composition afin de se rapprocher du paramètre de maille de la couche d'intérêt. Cela permet d'obtenir une relaxation du matériau tout en réduisant l'apparition des dislocations. On peut retrouver dans la littérature l'utilisation des alliages suivants: GaAsP[Olson86][Takagi95][Tsuji04], SiGe [Luo07][Carlin00][Carlin00][Carlin00][Carlin01] pour la croissance du GaAs sur silicium ou encore InGaAs [Papanicolaou92][Gocalinska16] et InAlAs [Hill0][Datta07][Takagi17] pour la croissance d'InGaAs sur silicium.

Le SiGe en tant que couche tampon est fortement utilisé dans la littérature pour la croissance du GaAs. Les couches obtenues avec cette approche sont couramment employées pour les applications comme le photovoltaïque [Carlin00][Carlin00][Ting00][Carlin01]. En effet, les propriétés de ces couches sont proches de celles épitaxiées sur des substrats GaAs. On

peut citer par exemple la publication de J. A. Carlin et al **[Carlin01]**. Au travers de ces travaux ils obtiennent une couche de GaAs avec une densité de dislocations de  $10^6$  cm<sup>-2</sup> en utilisant une couche tampon en SiGe de  $10 \mu m$  (figure 1.19). Ils s'affranchissent des parois d'antiphases avec des substrats de silicium désorientés de  $6^{\circ}$ .

Figure 1. 19 Croissance de GaAs sur Si (a) avec un buffer graduel en SiGe de 10µm d'épaisseur. (b) avec une couche tampon en SiGe [Carlin01].

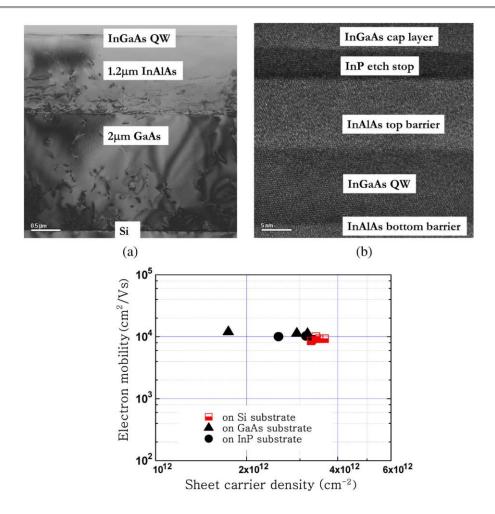

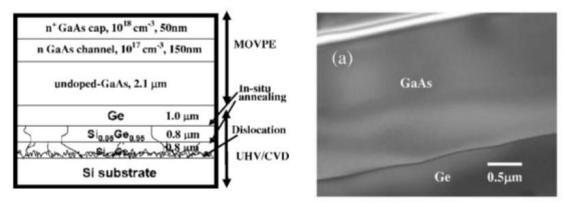

Un exemple de croissance d'InGaAs en utilisant une couche tampon en InAlAs sur un substrat désorienté de 4° est montré figure (1.20) [**Datta07**]. Dans ce papier les auteurs ont réalisé un transistor avec un canal fait avec des puits quantiques d'In<sub>0,7</sub>Ga<sub>0,3</sub>As. La croissance commence par un dépôt de 2 µm de GaAs puis 1,2 µm d'InAlAs est déposé en faisant varier sa concentration pour être en accord de maille avec l'InGaAs. Avec ces couches tampons, ils ont montré que des transistors fabriqués sur silicium avaient une mobilité électronique comparable à des transistors fabriqués sur des substrats GaAs et InP (figure 1.20).

Figure 1. 20 Croissance d'InGaAs sur silicium désorienté de 4° à l'aide d'une couche tampon en In<sub>x</sub>Al<sub>1-x</sub>As [Datta07].

De manière générale, l'utilisation de couches tampons est une solution pour réduire la densité de dislocations et obtenir des matériaux III-V avec de bonnes propriétés intrinsèques. Toutefois ce type de croissance nécessite de maitriser la croissance de divers matériaux. De plus, les travaux présentés ci-dessus ont tendance à utiliser de fortes épaisseurs pour la couche tampon. Ces fortes épaisseurs peuvent induire une courbure du substrat ainsi que la formation de fissures. Pour finir, la réalisation de ces couches tampons peut nécessiter l'emploi de plusieurs équipements d'épitaxie ce qui peux complexifier la fabrication des composants et les rendre inadaptés à l'échelle industrielle

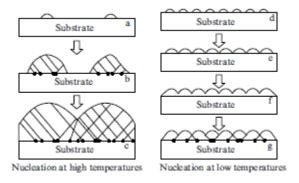

#### 1.3.1.1.3 Croissance directe sur silicium

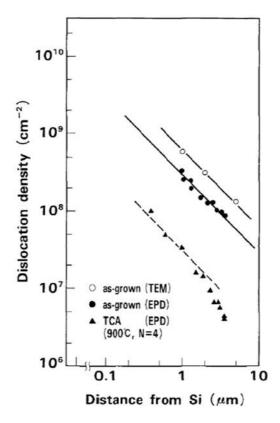

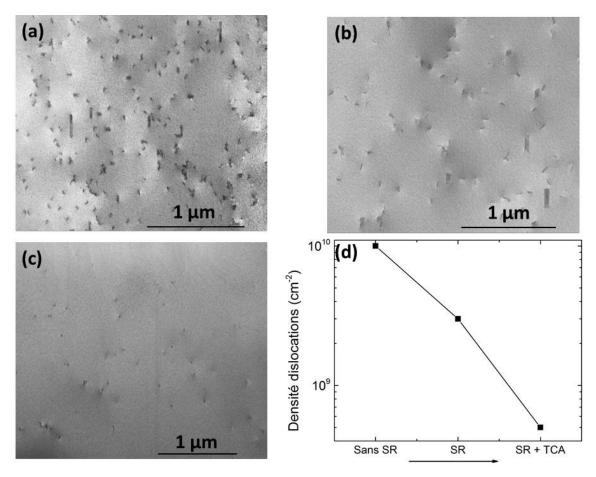

L'utilisation de couches tampons implique en général la croissance de couches épaisses ce qui peut induire une courbure du substrat. Dans le but de réduire les épaisseurs déposées et de s'affranchir de l'emploi de matériaux autres que le III-V, de nombreux groupes de recherche s'intéressent à la croissance direct de III-V sur silicium. Celle-ci se déroule selon un procédé dit en deux étapes. La première étape consiste à déposer à basse température une couche de nucléation puis de réaliser un second dépôt à haute température dans des conditions de croissance similaires à celle d'une homoépitaxie [Tachikawa93][Hao95][Akiyam84]. Cependant avec cette approche la densité de dislocations dans le matériau est relativement

élevée comparée à une croissance avec des couches tampons. Si on prend le cas du GaAs, elle est environ de 10<sup>9</sup> cm<sup>-2</sup> pour une épaisseur de 100 nm (figure 1.21). Afin de réduire cette valeur, la croissance en deux étapes est associée à la pratique de recuits cyclés (TCA en anglais pour Thermal Cycling Annealing) pendant et/ou après la fin de la croissance. En effet, l'utilisation de ces recuits permet d'obtenir un matériau avec moins de défauts grâce à l'apport en énergie thermique. Cet apport en énergie active la mobilité des dislocations et favorise l'annihilation de ces défauts par recombinaison [Yamaguchi91]. En combinant croissance en deux étapes et TCA, Yamaguchi et al [Yamaguchi91] (figures 1.21) ont montré qu'à épaisseur égale le GaAs avait une densité de dislocations inférieure à un dépôt sans recuit. Dans ces travaux, ils ont obtenu une valeur de 3-5x10<sup>6</sup> cm<sup>-2</sup> en pratiquant un TCA sur une couche de GaAs de 4 μm déposée sur silicium désorienté de 2°.

Figure 1. 21 Effet des recuits cyclées sur la densité de dislocations émergentes pour un GaAs sur Si [Yamaguchi91].

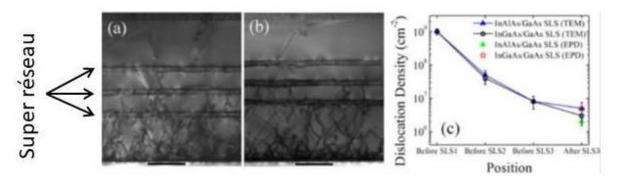

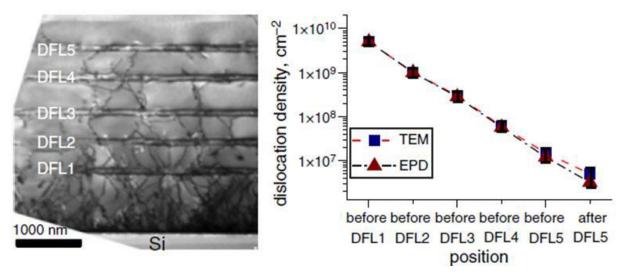

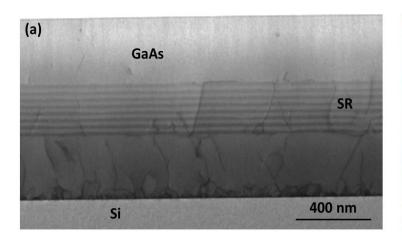

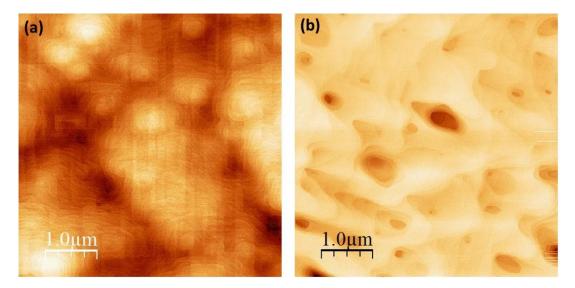

L'utilisation de filtres à dislocations (DFL en anglais pour Defects Filter layers) est aussi étudiée pour réduire la densité de dislocations [Tang14] [George15]. Ces filtres appelés aussi super réseaux sont composés d'une alternance de fines couches de matériaux contraints. Ils peuvent être réalisés par l'alternance de couches GaAs/InGaAs, GaAs/AlGaAs, GaAs/InAlAs etc. L'introduction d'un champ de contrainte au sein du matériau a pour effet de courber les dislocations, les empêchant ainsi d'atteindre la surface du matériau en favorisant leur annihilation. Un exemple de l'utilisation de ces filtres est visible figure (1.22). En utilisant des filtres à dislocations GaAs/InGaAs ou GaAs/InAlAs, les auteurs ont réussi à obtenir une couche de GaAs avec une densité de dislocations de 10<sup>6</sup> cm<sup>-2</sup> pour une épaisseur de 3 μm [Tang14].

Figure 1. 22 Image TEM d'une vue en coupe pour un super réseau (a) InGaAs/GaAs et (b) InAlAs/GaAs. (c) Réduction de la densité de dislocation en fonction du nombre de super réseaux [Tang14].

La croissance directe de III-V sur silicium permet de réduire l'épaisseur totale de matériau déposé sur le substrat. Par conséquent, cela limite l'apparition de la courbure du substrat et des fissures. De plus, il est possible d'obtenir des couches avec une faible densité de dislocations en utilisant un procédé de croissance en deux étapes, en utilisant des TCA ou bien des super réseaux.

# 1.3.1.2 Collage III-V sur silicium

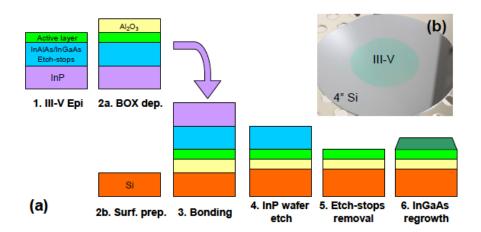

Dans l'optique d'obtenir un matériau III-V exempt de défauts cristallins sur silicium, le moyen le plus efficace est d'effectuer la croissance du matériau directement sur un substrat III-V tout en étant en accord de paramètre de maille puis de le reporter sur silicium par collage. Cette technique consiste à mettre en contact deux matériaux sans ajout de matière et sans compression [Rauer14]. Elle se fait grâce aux forces de Van Der Waals, aux liaisons hydrogène et forces de capillarité. Afin de rendre le collage irréversible, un traitement thermique est pratiqué afin de changer les liaisons de Van Der Waals en liaisons covalentes, car ces liaisons ont une énergie plus élevée. Une étape importante avant de réaliser le collage est qu'une couche d'adhésion, généralement un diélectrique (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> ou SiN par exemple) doit être déposée sur le matériau que l'on souhaite reporter car le collage direct III-V/Si n'est pas facile. Après collage, le substrat ayant servi pour la croissance du III-V est retiré par voie chimique ou mécanique. La figure (1.23) présente les différentes étapes nécessaires pour reporter sur silicium une couche d'InGaAs épitaxiée sur InP [Czornomaz13].

Figure 1. 23 (a) Etapes pour le report par collage d'une couche d'InGaAs sur un substrat en silicium. (b) Substrat en silicium sur lequel on a reporté un matériau III-V par collage [Czornomaz13].

L'inconvénient principal de cette technique réside dans la taille des substrats III-V reportés sur silicium ainsi que le nombre d'étapes technologiques qui doivent être effectuées. En effet, la taille du substrat III-V étant limité, les substrats Si 200 mm ou 300 mm ne seront pas exploités totalement.

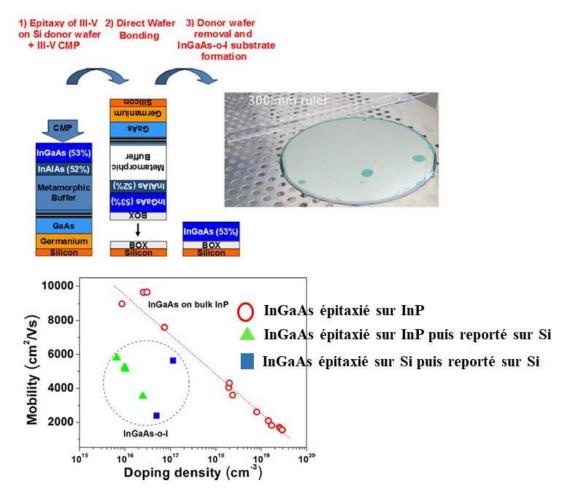

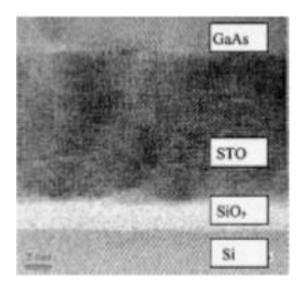

La solution pour pouvoir utiliser la totalité du substrat de silicium est de réaliser la croissance des matériaux III-V sur silicium, puis de reporter l'hétéroépitaxie sur le substrat en silicium. Des chercheurs d'IBM ont montré qu'une couche d'In<sub>0,53</sub>Ga<sub>0,47</sub>As avec une densité de dislocations de 10<sup>-9</sup> cm<sup>-2</sup> épitaxiée premièrement sur silicium désorienté de 6° puis reportée par collage sur silicium possédait une mobilité électronique similaire à une couche d'In<sub>0,53</sub>Ga<sub>0,47</sub>As épitaxiée sur InP puis reportée sur silicium (figure (1.24)) [**Daix14**].

Figure 1. 24 Comparaison de la mobilité des électrons entre des couches d'InGaAs épitaxiées sur silicium et sur substrat InP puis reportées sur silicium [Daix14].

Dans l'ensemble, l'utilisation du collage pour intégrer les III-V sur silicium est intéressante. La limite de l'exploitation du substrat en silicium peut être surmontée en utilisant des hétéroépitaxies sur silicium. Néanmoins, cela demande de savoir épitaxier diverses couches tampons avant la croissance de notre matériau d'intérêt. De plus outre la croissance du matériau, de nombreuses étapes technologiques sont requises pour faire le collage. La réalisation de toutes ces étapes demande d'utiliser différents équipements. Cela peut induire un coût de production important.

#### 1.3.1.3 Croissance sélective

La croissance sélective (ou localisée) consiste à faire croître des matériaux dans des motifs (trous ou tranchées) localisés sur un substrat. Ce mode de croissance permet de réduire la densité des défauts grâce à la géométrie des motifs, de réduire les épaisseurs des matériaux déposés et par conséquent le coût de l'étape de dépôt. Ils existent deux types de croissance sélective : la croissance par « Aspect Ratio Trapping (ART) » et la « Confined Lateral Selective Epitaxial Growth (CLSEG) ».

#### 1.3.1.3.1 Aspect Ratio Trapping (ART)

Cette méthode de croissance consiste à bloquer la propagation des dislocations formées en confinant la croissance du III-V entre des murs d'oxyde de silicium (SiO<sub>2</sub>). En faisant cela une partie des dislocations créées s'annihile sur les murs de SiO<sub>2</sub> (figure 1.25).

Figure 1. 25 Principe de la croissance localisée par ART. Les traits noirs représentent les défauts générés durant la croissance.

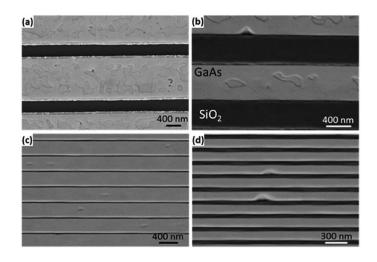

Grâce au confinement, le matériau III-V situé au sommet des motifs est de meilleure qualité. La figure (1.26) présente un cas de croissance de GaAs dans des cavités en SiO<sub>2</sub>.

Figure 1. 26 Vue en coupe d'une croissance de GaAs sur Si dans des cavités de SiO<sub>2</sub> [Li08].

L'efficacité de l'annihilation des dislocations est tributaire du rapport d'aspect de la cavité. Celui-ci est défini avec le rapport hauteur(H)/largeur(L) de la cavité. En faisant varier le rapport d'aspect, R. Cipro et al [Cipro14] ont montré qu'il était possible d'obtenir du GaAs sur silicium nominal sans parois d'antiphase à condition que le ratio d'aspect soit supérieur à 1,3 (figure 1.27).

Figure 1. 27 Vue du dessus d'une croissance en fonction du rapport d'aspect des cavités (a) 0,18 (b) 0,32 (c) 0,6 (d) 1,3 [Cipro14].

Des couches 2D peuvent aussi être obtenues avec une croissance sélective après coalescence du GaAs qui dépasse de la cavité (figure 1.28). Ce type de croissance est appelé ELOG pour (Epitaxial Lateral Over Growth). Les couches 2D formées avec cette approche ont une densité de défauts inférieure à celles directement épitaxiées sur silicium. Cependant, en raison du facettage des matériaux en sortie de cavités selon les plans (111) (figure 1.26), la coalescence peut causer l'apparition de fautes d'empilement ou de dislocations (figure 1.28).

Figure 1. 28 Vue en coupe d'une couche de GaAs sur Si obtenue après coalescence du matériau en sorti des cavités de SiO<sub>2</sub> [Li08].

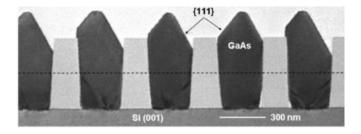

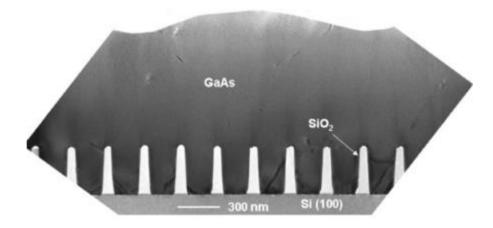

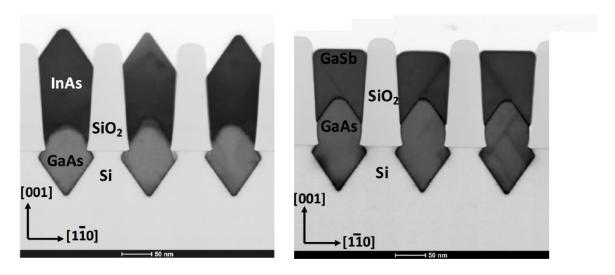

Afin d'améliorer la qualité du matériau déposé et obtenir des matériaux sans parois d'antiphase des équipes de recherches effectuent la croissance sur les plans (111) du silicium. Ces plans (111) sont révélés au fond des cavités par une gravure du substrat en amont du dépôt. Cette gravure induit une cavité en forme de V aussi appelée V-groove. Avec cette approche T. Orzali et al [Orzali16] ont épitaxié des empilements InAs/GaAs et GaSb/GaAs sans parois d'antiphase en combinant ART et révélation des plans (111) en fond de cavité (figure 1.29).

Figure 1. 29 Vues en coupe d'une croissance de matériaux d'empilement InAs/GaAs et GaSb/GaAs dans des cavités en SiO<sub>2</sub> avec un V-groove [Orzali16].

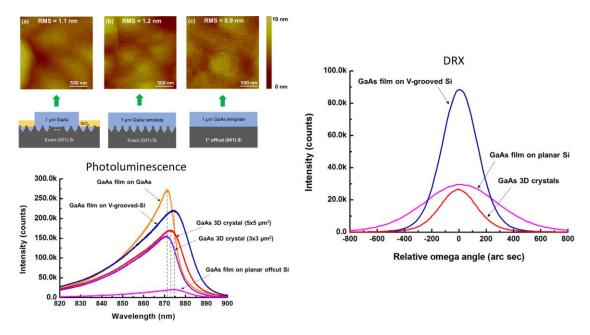

Toujours avec cette approche l'équipe de Kei May Lau [Li16] a montré que la formation de V-groove combinée à une croissance latérale du III-V permettait d'obtenir une couche 2D de

GaAs sur silicium nominal (100) sans parois d'antiphase (figure 1.30). Ils ont aussi montré grâce à de la diffraction par rayons X et de la photoluminescence que le GaAs obtenu était de meilleur qualité que celui directement épitaxié sur un substrat silicium désorienté de 1°.

Figure 1. 30 Comparaison de la qualité cristalline d'un GaAs épitaxié sur silicium selon différentes approches [Li16].

L'épitaxie localisée couplée à la révélation des plans (111) en fond de cavité est une solution intéressante pour pouvoir épitaxier des matériaux avec une faible densité de défauts et de bonnes propriétés physiques sur silicium. Cependant, cette approche nécessite de réaliser diverses étapes technologiques en amont du dépôt afin de structurer le substrat.

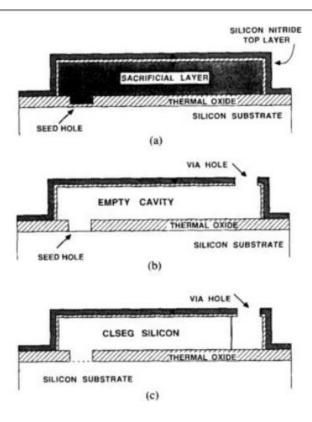

### 1.3.1.3.2 Confined Lateral Selective Epitaxial Growth (CLSEG)

Ce type de croissance est une version améliorée de la croissance par ART où le III-V est confiné totalement dans un moule d'oxyde. La croissance par « Confined Lateral Selective Epitaxial Growth » (CLSEG) consiste à faire croitre sélectivement un matériau au sein d'une cavité d'oxyde à partir d'un germe de Si. Les étapes de fabrication sont visibles sur la figure 1.31. Premièrement, un oxyde thermique est réalisé sur le substrat Si puis des ouvertures sur le substrat sont faites par photolitographie et gravure. Une couche sacrificielle de Si amorphe est ensuite déposée et gravée pour couvrir le trou sur le Si. L'épaisseur et la forme de la couche sacrificielle définiront les dimensions de la cavité. Cette couche sacrificielle est ensuite partiellement oxydée (figure 1.31 (a)). Une ouverture est créée sur le Si amorphe afin de le retirer sélectivement par rapport à l'oxyde (figure 1.31 (b)). La croissance du III-V peut être effectuée après désoxydation du Si.

Figure 1. 31 Etapes de fabrication pour la croissance CLSEG [Schubert90]

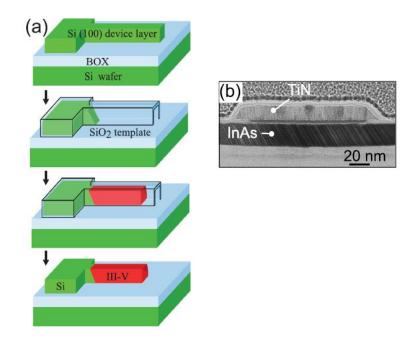

A partir de ce procédé de croissance, IBM a développé en 2015 l'intégration TASE (Template-Assisted Selective Epitaxy) pour la croissance de nanofils III-V sur oxyde. Cette technique de croissance consiste à définir une matrice 3D dans laquelle le semiconducteur III-V est épitaxié selon les plans (111) du silicium pour s'affranchir des parois d'antiphase (figure 1.32) [Schmid15]. Avec cette approche, les équipes de recherches d'IBM ont obtenu des nanofils d'InAs avec un diamètre de 20 nm et une mobilité de 5400 cm².V<sup>-1</sup>.s<sup>-1</sup>. Cependant, du fait que la croissance du III-V se déroule selon les plans (111), celui-ci contient une forte densité de fautes d'empilements (figure 1.31).

Figure 1. 32 (a) Principe de la croissance de III-V selon l'approche TASE. (b) Vue en coupe d'InAs épitaxié par la méthode TASE [Schmid15].

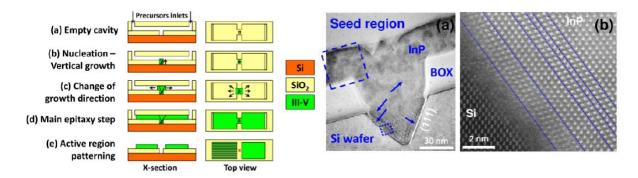

Outre l'approche TASE, IBM a aussi développé une technique de croissance appelée CELO (Confined Epitaxial Layer Overgrowth). Elle combine les avantages de la croissance par ART et CLESG [Czornomaz15][Czornomaz16]. La croissance du III-V débute sur silicium dans des cavités jusqu'à un mur d'oxyde situé en sortie de la cavité (figure 1.33). La rencontre avec ce mur induit une croissance latérale du matériau. A la fin de l'épitaxie, l'oxyde qui entraine la croissance latérale est retiré ce qui permet d'accéder au III-V. Il est aussi possible avec cette technique de garder uniquement le III-V qui a poussé latéralement hors de la cavité en gravant la partie défectueuse. Avec cette approche, les équipes d'IBM ont présenté la croissance d'InP et d'In<sub>0,7</sub>Ga<sub>0,3</sub>As dans des cavités longues de chaque côté de la zone de nucléation de 1,3 µm et épaisses de 30 nm. Toutefois, ils rapportent qu'il est difficile de contrôler la concentration de l'InGaAs le long du film.

Figure 1. 33 Croissance selon l'approche CELO et images de la croissance d'InP sur silicium [Czornomaz16].

1.3.1.4 Comparatif des techniques d'intégration de III-V sur silicium

Dans le tableau 1.1, nous listerons les avantages et inconvénients des différentes techniques d'intégration que nous venons de voir.

| Technique         | Inconvénients                        | Avantages                                                   |  |

|-------------------|--------------------------------------|-------------------------------------------------------------|--|

| Croissance direct | Forte densité de dislocations        | Rapide et simple                                            |  |

| sur Si            |                                      | Faible épaisseur                                            |  |

| Croissance avec   | Nombreuses étapes supplémentaires    | Densité de dislocations de 10 <sup>6</sup> cm <sup>-2</sup> |  |

| couches tampons   | Différents matériaux                 |                                                             |  |

|                   | Forte épaisseur                      |                                                             |  |

| Collage           | Nombreuses étapes supplémentaires    | Pas de dislocation si collage depuis                        |  |

|                   | Mobilité électronique similaire à    | III-V                                                       |  |

|                   | celle d'une croissance III-V/III-V   |                                                             |  |

| ART               | Etapes technologies pour obtenir les | Réduction de la densité de                                  |  |

|                   | motifs                               | dislocations                                                |  |

|                   | Fautes d'empilement                  |                                                             |  |

| CLSEG             | Composition des alliages difficile à | Faible densité de dislocations                              |  |

|                   | contrôler                            | Faible épaisseur                                            |  |

|                   | Nombreuses étapes technologiques     |                                                             |  |

|                   | pour préparer le substrat            |                                                             |  |

Tableau 1. 1 Comparaison des techniques d'intégration de matériaux III-V sur substrat Si.

#### 1.3.2 Résistance de contacts

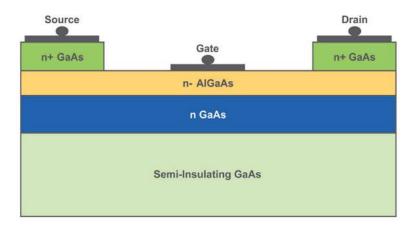

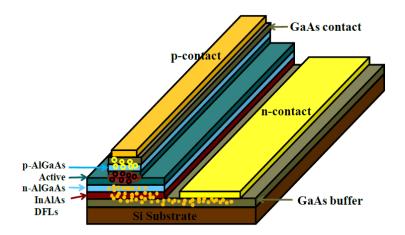

Afin de tirer profit des propriétés des III-V et d'améliorer les performances des transistors HEMT et des lasers, il est nécessaire d'obtenir de faibles résistivités au niveau des contacts. La valeur attendue pour un fonctionnement optimal dépend des dimensions du composant et des contacts. Dans le cas des transistors HEMT, les contacts sont formés sur des semiconducteurs dopés n (figure 1.34) et la valeur attendue selon l'ITRS (International Techonology Roadmap for Semiconductors) doit être inférieure à 10<sup>-8</sup> ohm.cm² en raison de la taille des composants (< 100 nm).

Figure 1. 34 Schéma d'un transistor HEMT en GaAs.

En ce qui concerne les dispositifs photoniques, les contacts sont formés à la fois sur des matériaux dopés n et p (figure (1.35)). Pour ces composants, une résistivité de contact de  $10^{-6}$  ohm.cm² est requise afin de fonctionner correctement car la taille des composants est de l'ordre du micron.

Figure 1. 35 Schéma d'un laser à base de GaAs avec émission entre 1,3 μm et 1,55 μm [Tang14].

Dans le but d'obtenir des contacts avec une faible résistivité diverses approches peuvent être utilisées telles que doper fortement le semiconducteur en contact avec le métal, choisir le métal adéquat, réaliser des alliages ou insérer des matériaux à petit gap tel que l'InAs ou le Ge en tant que couche de contact entre le métal et le semiconducteur [Rhoderick82][Shen92][Scozoni88].

Dans la suite de cette partie, nous présenterons en premier lieu la théorie sur le contact métalsemiconducteur puis nous nous intéresserons à la formation d'un contact avec une faible résistivité.

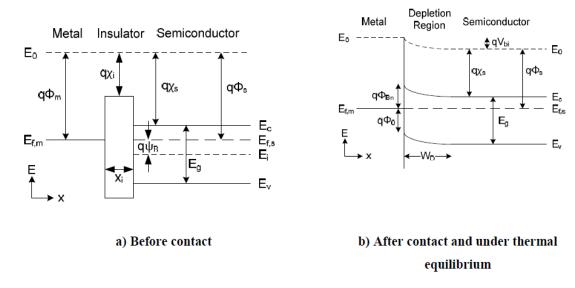

#### 1.3.2.1 Contact Metal-Semiconducteur

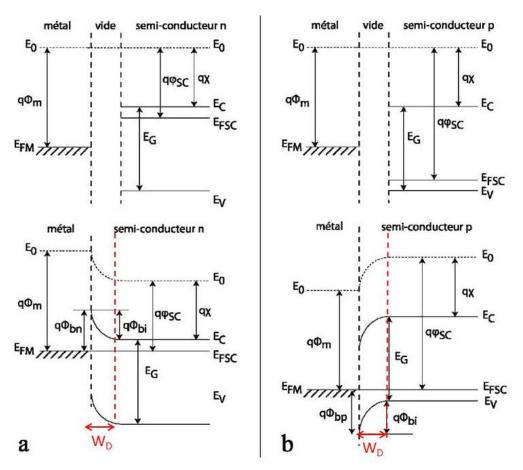

La figure (1.36) montre la structure de bandes entre un métal et des semiconducteurs dopés n (a) et p (b) avant et après leur mise en contact.

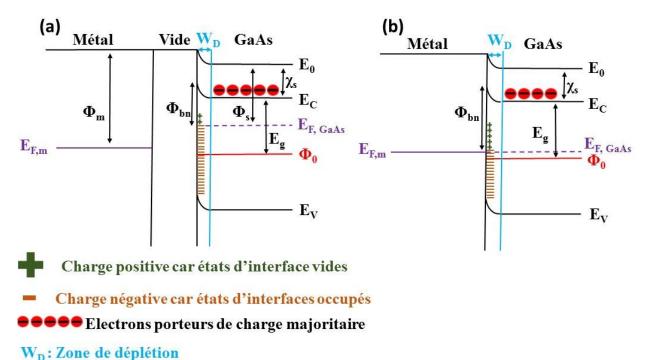

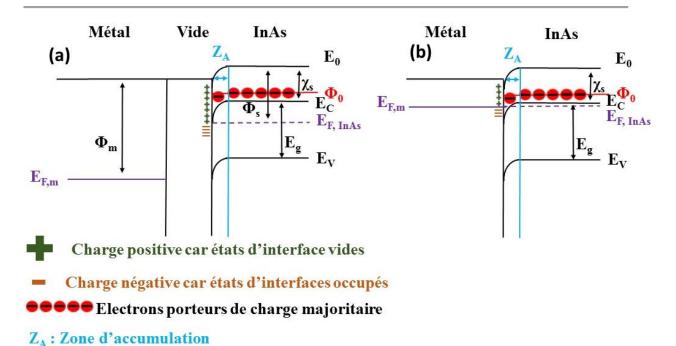

Figure 1. 36 Contact métal-semiconducteur dans un cas parfait.

Dans le cas d'un semiconduteur dopé n, avant la mise en contact les niveaux de Fermi du métal  $(E_{Fm})$  et du semiconducteur  $(E_{Fsc})$  ne sont pas alignés car les travaux de sortie du métal  $(\Phi_m)$  et du semiconducteur  $(\Phi_{sc})$  sont différents (figure 1.36). Lors de la mise en contact, les électrons du semiconducteur vont diffuser vers le métal afin d'atteindre l'équilibre et aligner les niveaux de Fermi entre eux. Cet alignement induit la courbure des bandes de valence et de conduction, l'apparition d'une zone de déplétion  $(W_D)$  dépourvue de porteurs de charge et la formation d'une barrière Schottky notée  $\Phi_{Bn}$  qui empêche le passage des électrons du semiconducteur vers le métal. Dans un cas parfait où le contact métal-semiconducteur est exempt d'états d'interface,  $\Phi_{Bn}$  est définie par la relation (1.10).

$$\Phi_{Bn} = (\Phi_m - \chi) (1.10)$$

Tandis que pour un type p, on a la relation (1.11).

$$\Phi_{Bp} = Eg - (\Phi_m - \chi) (1.11)$$

Avec  $E_g$  le gap du semiconducteur et  $\chi$  l'affinité électronique du semiconducteur qui s'exprime selon la relation (1.12) :

$$\chi = \Phi_{sc} - (E_c - E_{Fsc}) (1.12)$$

Avec E<sub>c</sub> le niveau de la bande de conduction.

$\Phi_m$  et  $\Phi_{sc}$  représentent respectivement pour un métal et un semiconducteur l'énergie nécessaire pour faire passer un électron du niveau de Fermi jusqu'au niveau du vide (E<sub>0</sub>). L'affinité électronique correspond à l'énergie dont un électron a besoin pour passer de la bande de conduction du semiconducteur au niveau du vide.

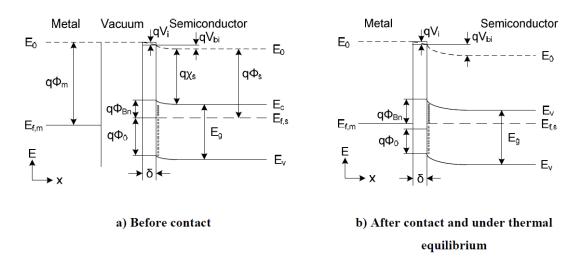

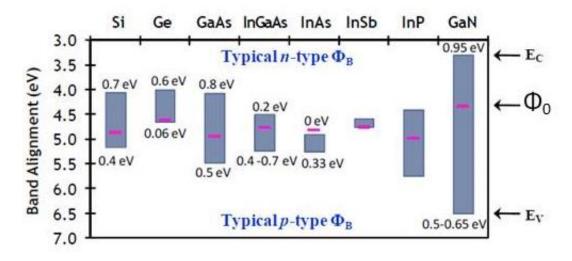

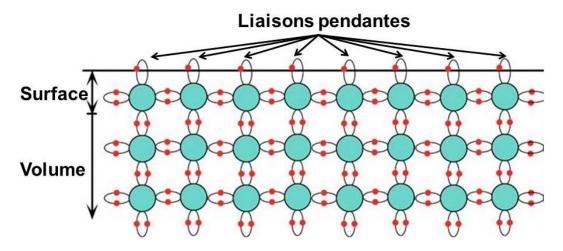

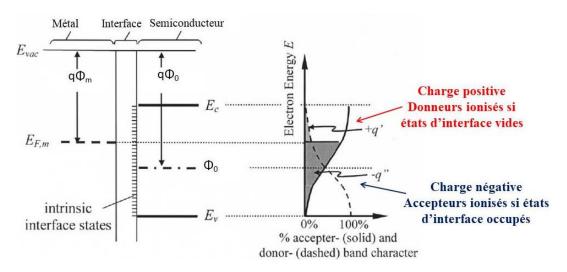

Cependant dans la pratique, l'interface entre le métal et le semiconducteur possède des états d'interface à cause des liaisons atomiques insatisfaites à la surface du matériau. En effet, contrairement aux liaisons dans le volume qui sont covalentes, celles à la surface ne le sont pas car les atomes ne possèdent qu'un seul voisin à savoir du côté du semiconducteur. L'absence de voisins du côté surface induit la formation de liaisons insatisfaites qui génèrent par la suite des états d'interfaces distribués en énergie dans le gap du matériau et caractérisés par un niveau d'énergie neutre  $(\phi_0)$ . Dans le cas de figure où la surface du semiconducteur est neutre,  $\phi_0$  correspond à l'énergie de Fermi et tous les états en dessous de  $\phi_0$  sont remplis avec des électrons alors que ceux situés au-dessus sont vides. Cependant, dans la pratique, ce cas de figure ne se produit pas, ce qui induit l'apparition d'une charge à la surface du semiconducteur. Celle-ci peut être négative ou positive en fonction du positionnement des états de surface par rapport à  $\phi_0$ . La charge à la surface induit la formation d'un champ électrique qui courbe les bandes de conduction et de valence, crée une zone de déplétion et fait apparaître une barrière Schottky avant la mise en contact avec le métal (figure 1.37(a)). Ce phénomène a pour conséquence de rendre les relations (1.10) et (1.11) inutilisables car les propriétés de la jonction métal/seminconducteur ne sont plus définies par les propriétés du matériau mais par l'interface [Rhoderick82][Cowley65][Bardeen47]. Dans cette configuration, la barrière Schottky est indépendante du métal.

Figure 1. 37 Diagramme de bandes d'un contact métal-Semiconducteur réel (a) avec un semiconducteur de type n avant (b) et après mise en contact

En prenant en compte la présence des états d'interface les barrières Schottky  $\Phi_{Bn}$  et  $\Phi_{Bp}$  s'écrivent selon les relations (1.13) et (1.14).

$$\Phi_{Bn} = \gamma (\Phi_m - \chi) + (1 - \gamma)(E_g - \Phi_0) (1.13)$$

$$\Phi_{Bp} = \gamma (E_g - \Phi_m + \chi) + (1 - \gamma) (\Phi_0) (1.14)$$

Avec  $\gamma$  définie par l'expression (1.15)

$$\gamma = \frac{\varepsilon_i}{\varepsilon_i + q\delta D_{it}}$$

(1.15)

Avec δ : l'épaisseur de la couche d'oxyde natif du matériau

$\varepsilon_i$ : la permitivité totale

Dit : la densité des états d'interface

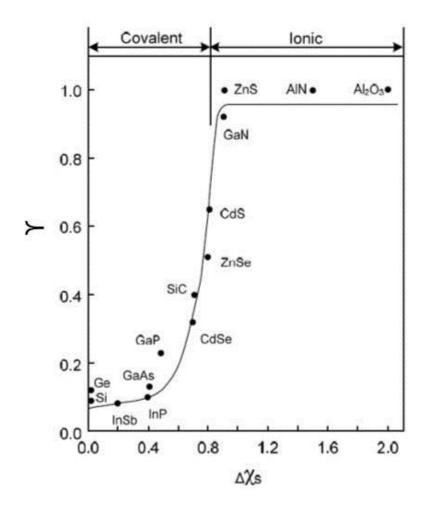

Les relations (1.13) et (1.14) montrent que la barrière Schottky est dépendante de  $\gamma$ . Dans le cas où  $\gamma$  vaut 0, la barrière Schottky est indépendante du travail de sortie du métal. Cependant, si  $\gamma$  est différent de 0, le travail de sortie du métal aura un impact sur la barrière Schottky. Il a été montré que ce paramètre est lié à la nature des liaisons (covalentes ou ioniques) [Sze98]. La figure (1.38) présente l'évolution de ce paramètre en fonction de l'électronégativité de différents matériaux. Dans le cas du GaAs,  $\gamma$  vaut environ 0,1 – 0,2. Par conséquent, une variation de la barrière est possible en fonction du métal déposé.

Figure 1. 38 Evolution du paramètre  $\gamma$  en fonction de la différence d'électronégativité ( $\Delta Xs$ ) des matériaux [Sze98].

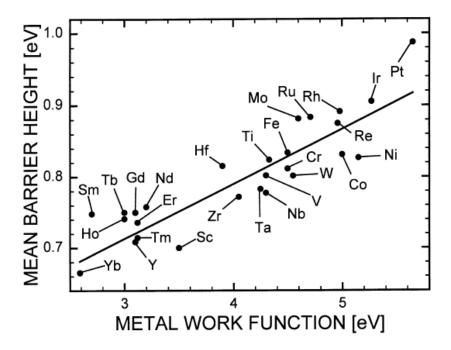

Après formation du contact métal-semiconducteur, celui-ci peut être « redresseur » synonyme de forte résistivité pour les contacts ou bien « ohmique » synonyme de faible résistivité de contact. En général un comportement redresseur est obtenu pour une importante barrière de potentiel tandis qu'un comportement ohmique est obtenu pour une faible barrière de potentiel permettant ainsi aux porteurs de charge de passer à l'interface métal-semiconducteur. Dans le cas d'un contact idéal, à partir des relations (1.10) et (1.11), une faible barrière de potentiel nécessite de choisir un métal dont le travail de sortie permet d'obtenir une barrière de potentiel nulle ou proche de zéro. Cependant comme nous l'avons dit précédemment, cette barrière est indépendante du travail de sortie du métal. Par conséquent, il est difficile d'obtenir une faible barrière Schottky. La figure (1.39) illustre l'évolution de la barrière de potentiel en fonction de divers métaux pour le GaAs dopé n [Myburg98]. Comme nous pouvons le voir, la valeur de la barrière se situe entre 0,7 eV et 0,9 eV. Afin d'améliorer le passage des porteurs de charge malgré une barrière de potentiel importante, il est recommandé de les faire passer par effet tunnel.

Figure 1. 39 Valeur de la barrière Schottky pour le GaAs pour différents métaux [Myburg98].

#### 1.3.2.2 Mécanismes de transport

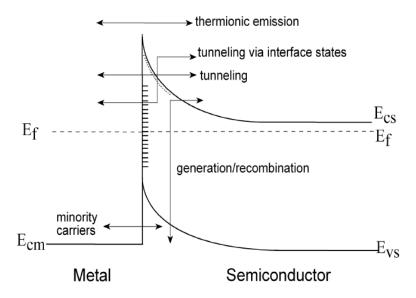

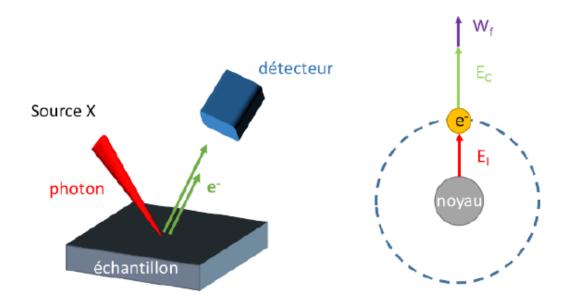

Le transport des porteurs de charge du semiconducteur vers le métal est assuré par 5 mécanismes de transport comme montré dans la figure (1.40).

- Passage par émission Thermo-ionique (effet de saut)

- Passage par effet tunnel

- Effet tunnel par les états d'interface

- Phénomène de génération et recombinaison dans la zone de charge d'espace

- Transport des porteurs minoritaires

Figure 1. 40 Mécanismes de transport des porteurs pour un contact métal-semiconducteur

Parmi tous ces mécanismes, les plus importants sont le passage par émission thermo-ionique et le passage par effet tunnel. A l'équilibre ces mécanismes dépendent de la concentration des porteurs de charge. Les autres mécanismes de transport tels que le transport des porteurs minoritaires et le phénomène de génération et recombinaison sont moins efficaces et par conséquent négligés.

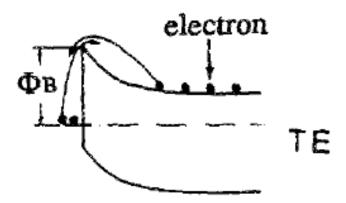

Emission Thermo-ionique (TE): Pour les faibles niveaux de dopage ( $< \sim 10^{17}$  cm<sup>-3</sup>), l'émission Thermo-ionique est dominante. Dans ces conditions la taille de la zone de déplétion définie par la relation (1.16) est trop importante pour permettre un passage par effet tunnel.

$$W_D \propto \frac{1}{\sqrt{N_{\rm d}}} (1.16)$$

Avec N<sub>d</sub> représente le nombre de porteurs de charges.

Figure 1. 41 Passage des électrons par effet de saut avec l'émission thermo-ionique [Shen92].

Le passage des porteurs de charge par effet thermo-ionique se fait en sautant par-dessus la barrière de potentiel comme présenté en figure (1.41). L'énergie nécessaire pour assurer le passage est en général apportée par la polarisation externe et la température [Rhoderick82][Cowley65][Shen92]. La densité de courant courant thermo-ionique pour un contact métal-semiconducteur est donnée par la relation (1.17).

$$J = A^* T^{2e^{-\left(\frac{q\Phi_B}{kT}\right)}} \left(e^{\left(\frac{qV}{kt}\right)} - 1\right) (1.17)$$

Avec  $A^*$  est la constante de Richardson du semiconducteur étudié, V la polarisation externe, T la température en kelvin et k la constante de Boltzmann.

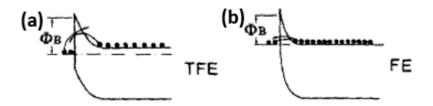

Emission par effet tunnel: L'augmentation du niveau de dopage du matériau induit une réduction de la zone de déplétion (1.16) et favorise le passage des porteurs de charge à travers la barrière par effet tunnel. Ce mécanisme commence à dominer pour des niveaux de dopage compris entre  $10^{18}$  cm<sup>-3</sup> et  $10^{19}$  cm<sup>-3</sup>. L'effet tunnel se produit pour des porteurs de charge dont l'énergie est comprise entre la barrière Schottky et le niveau de Fermi, ce

mécanisme de passage est appelé en anglais « Thermionic Field Emission (TFE)» [Shen92] (figure 1.42 (a)). Pour des niveaux de dopage plus importants la zone de déplétion est si fine que la plupart des porteurs de charge passent par effet tunnel près du niveau de Fermi. Dans ce cas, le mécanisme est appelé « Field Emission (FE) » en anglais [Shen92] (figure 1.42 (b)).

Figure 1. 42 Passage des électrons par (a) Thermionic Field Emission. (b) Field Emission [Shen92].

La densité de courant tunnel est déterminé par la relation suivante (1.18).

$$J \propto e^{\left(-A^* \frac{\Phi_B}{\sqrt{N_D}}\right)} \ (1.18)$$

Afin de distinguer le mécanisme de conduction prépondérant, le paramètre  $E_{00}$  a été défini (1.19) **[Padovani66]**.

$$E_{00} = \frac{q\hbar}{2\pi} \sqrt{\frac{N_d}{m^* \varepsilon_r}} (1.19)$$

q : la charge d'un électron

$\varepsilon_r$ : la constante diélectrique du semicondcuteur

m\*: la masse effective du semiconducteur

Quand on a  $kT \gg E_{00}$ , le mécanisme thermo-ionic domine

Quand on a kT  $\sim$  E<sub>00</sub>, le mécanisme thermo-ionic field emssion domine

Quand on a kT << E<sub>00</sub>, le mécanisme field emission domine

# 1.3.2.3 Contact Ohmique

Lors de la réalisation d'un composant on cherche à obtenir un contact ohmique entre le métal et le semiconducteur car il permet d'obtenir une faible résistivité de contact. Cette résistance est définie par le flux de porteurs de charge à travers l'interface metal-semiconducteur et est caractérisée par la résistivité du contact notée  $\rho_c$ . Cette résistivité de contact s'exprime selon la relation (1.20) [Shen92].

$$\rho_c = \left(\frac{\partial J}{\partial V}\right)^{-1} \text{ à V} = 0 \ (1.20)$$

Avec J: la densité de courant

Avec V : la tension à travers la barrière Schottky

Pour un contact ohmique elle s'exprime selon la relation (1.21) :

$$\rho_c \propto e(\frac{q\Phi_b}{E_{00}}) (1.21)$$

L'obtention d'un contact avec une faible résistivité nécessite 4 critères.

- Fort niveau de dopage pour le semiconducteur

- Le choix du métal

- La préparation de surface

- La stabilité thermique du contact

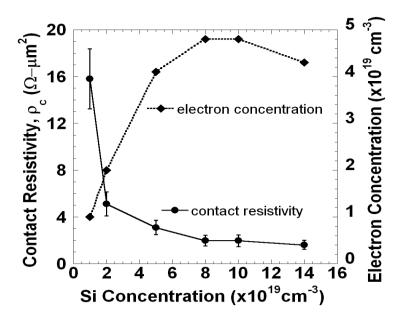

<u>Dopage des zones de contacts</u>: Pour obtenir une faible résistivité de contact, il est primordial de maximiser le nombre de porteurs de charge afin de favoriser un passage par effet tunnel. La figure 1.43 présente l'évolution de la résistivité de contact en fonction de la concentration en électron pour une couche d'InGaAs épitaxié sur InP et dopée avec du silicium [Baraskar11]. On peut ainsi voir que la résistivité du contact diminue à mesure que le niveau de dopage augmente dans le matériau.

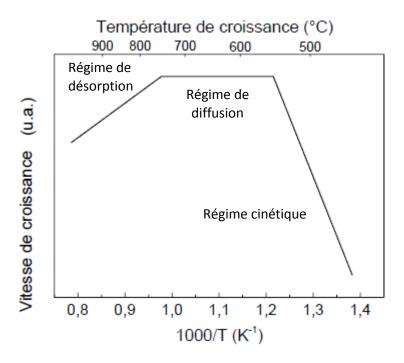

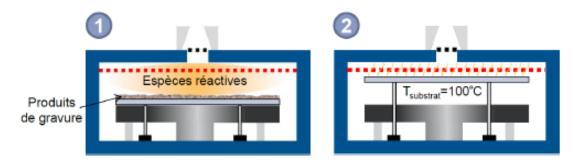

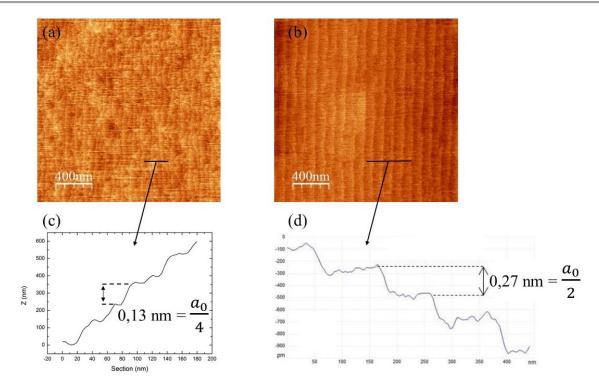

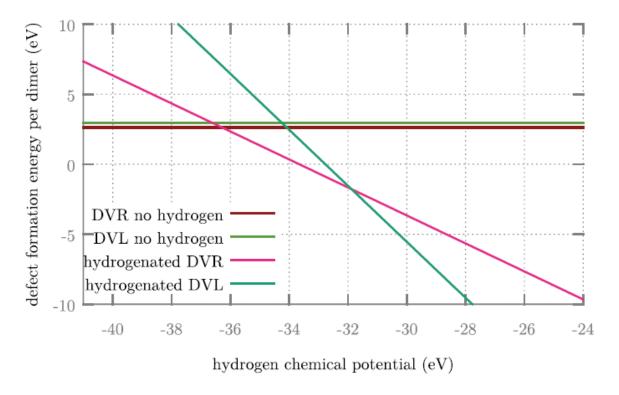

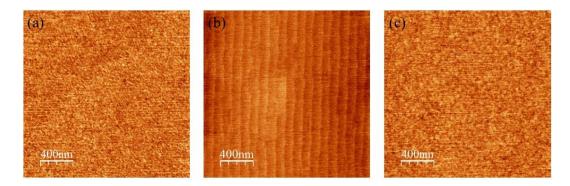

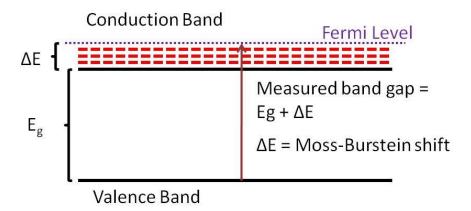

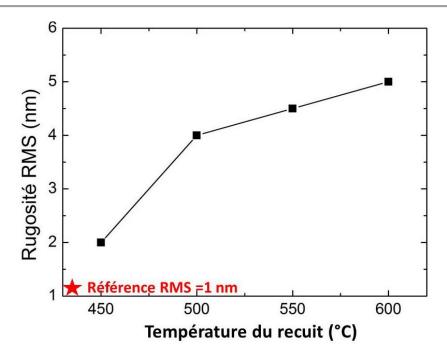

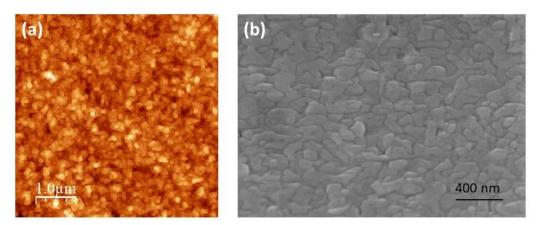

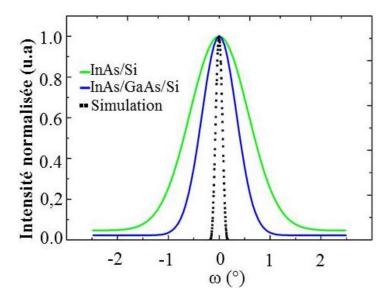

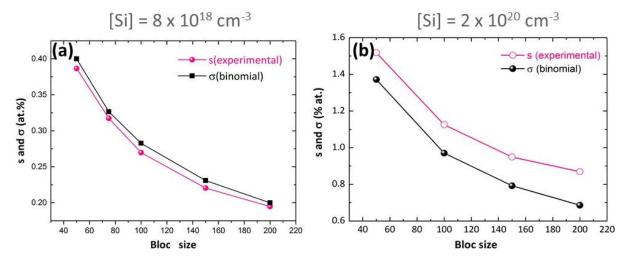

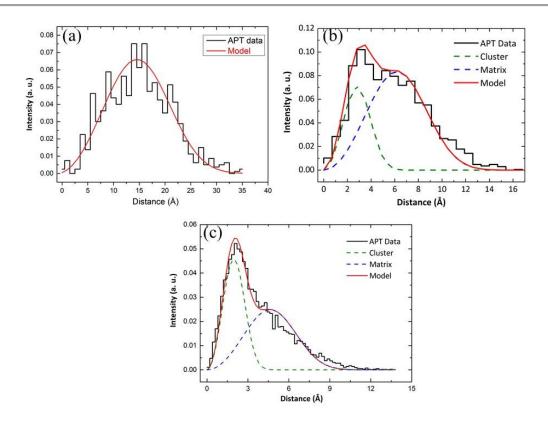

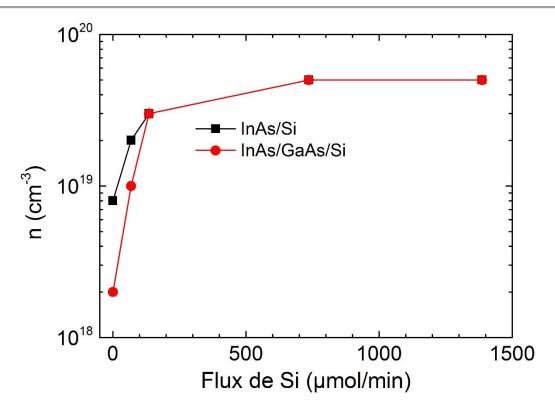

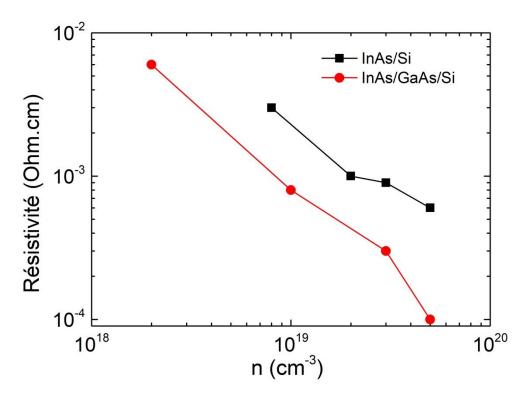

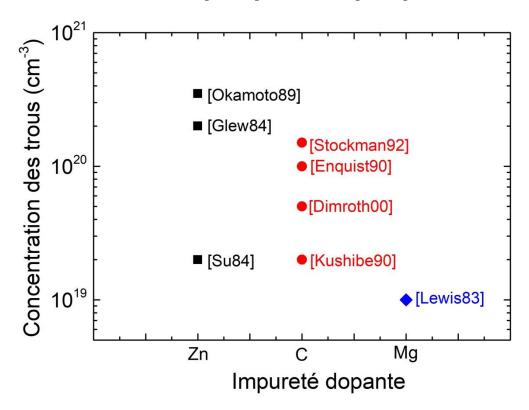

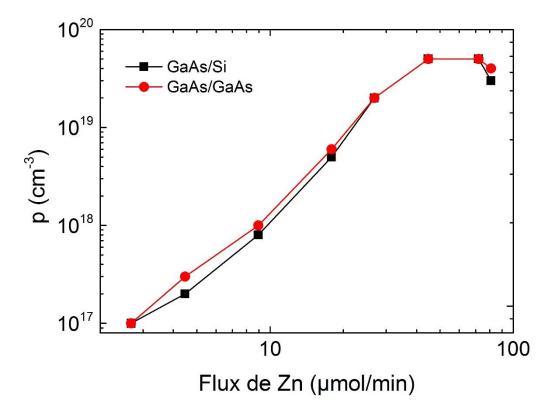

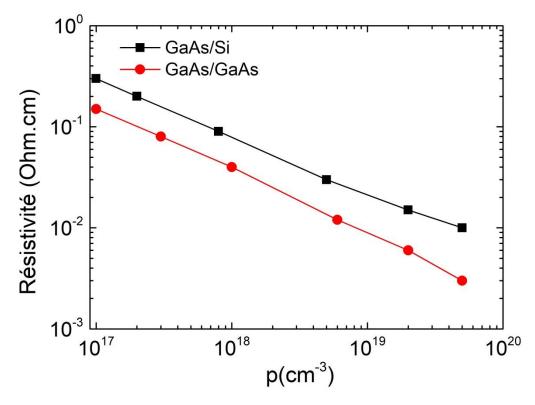

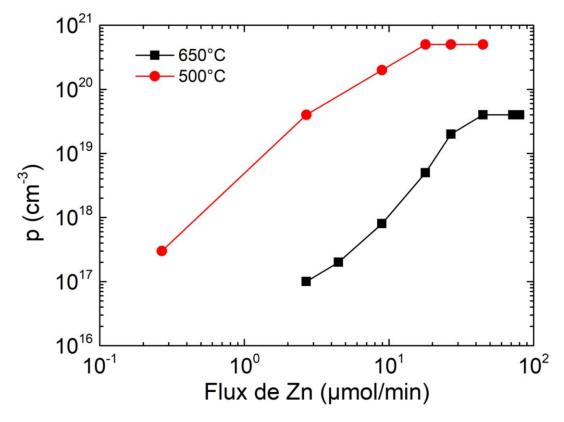

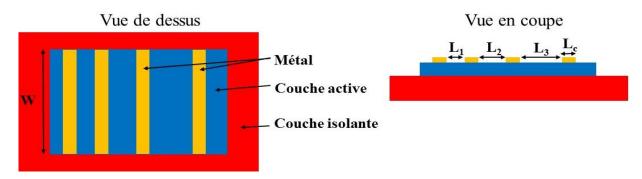

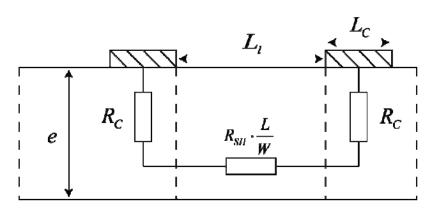

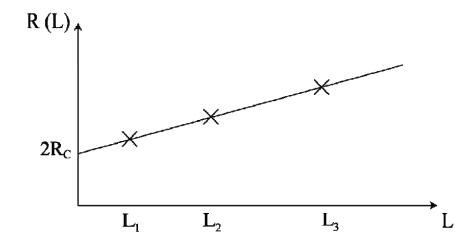

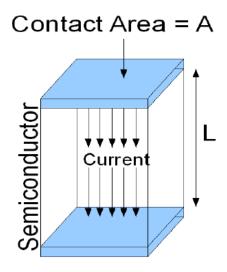

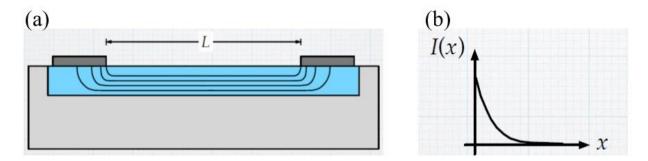

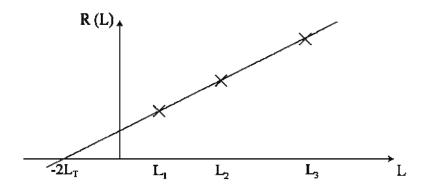

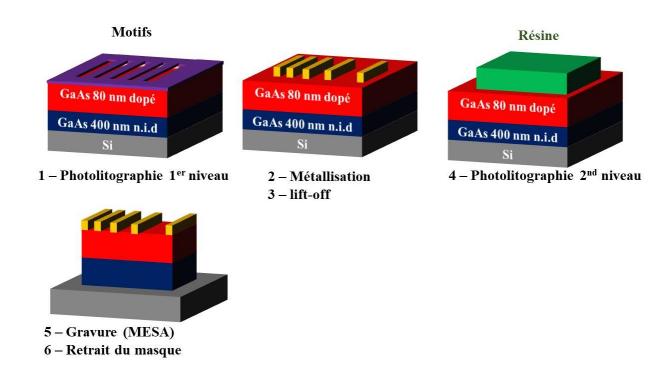

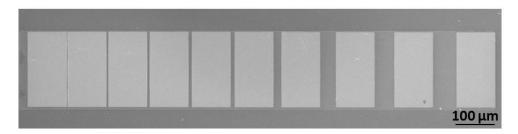

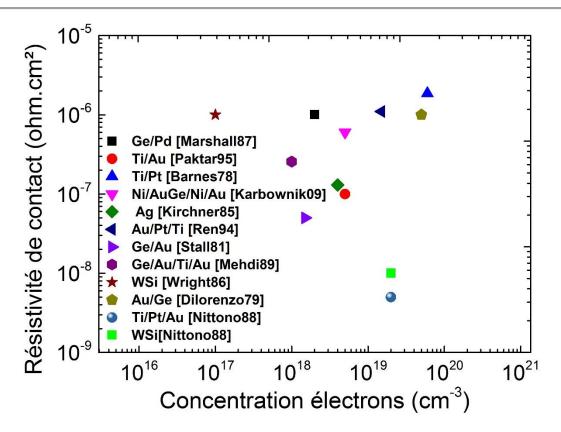

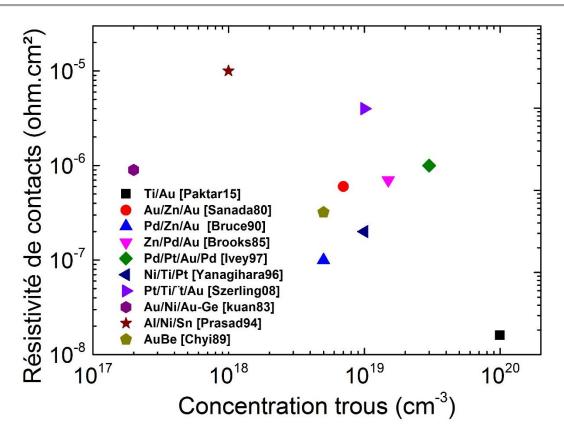

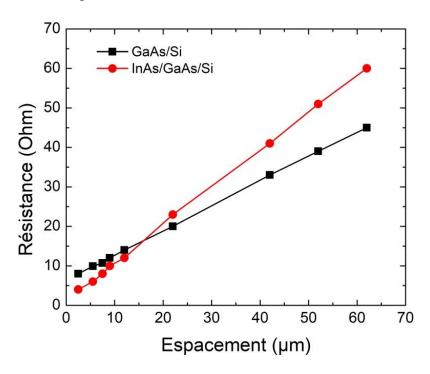

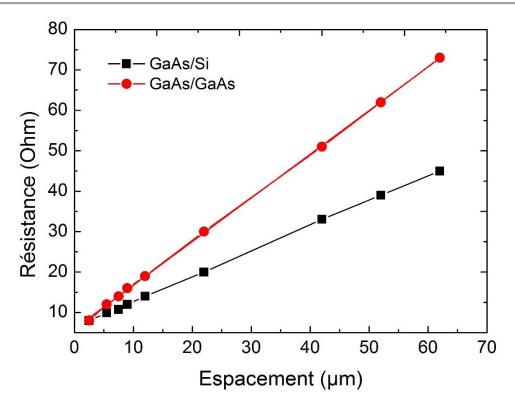

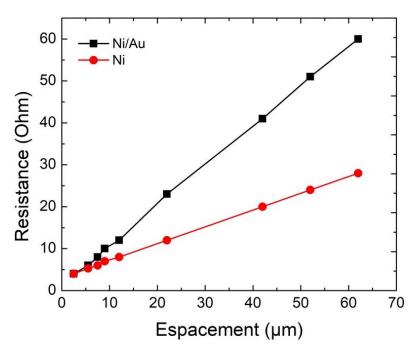

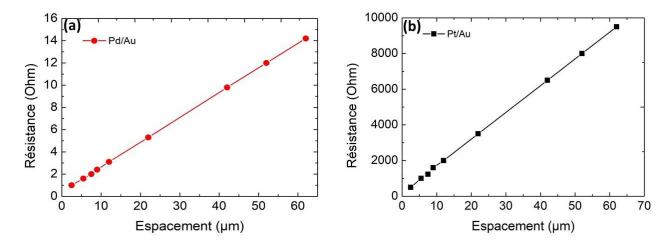

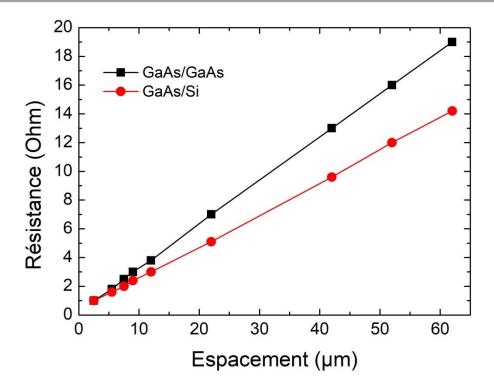

Figure 1. 43 Evolution de la résistivité de contact d'un InGaAs en fonction de la concentration en électron [Baraskar11].