## Building and analyzing processing graphs on FPGAs with strong time and hardware constraints

Ke Du

#### ► To cite this version:

Ke Du. Building and analyzing processing graphs on FPGAs with strong time and hardware constraints. Programming Languages [cs.PL]. Université Bourgogne Franche-Comté, 2018. English. NNT: 2018UBFCA005. tel-01865542

### HAL Id: tel-01865542 https://theses.hal.science/tel-01865542

Submitted on 31 Aug 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# SPIM Thèse de Doctorat

## Building and analyzing processing graphs on FPGAs under strong real-time environment and hardware constraints

KE DU

## SPIM Thèse de Doctorat

école doctorale sciences pour l'ingénieur et microtechniques UNIVERSITÉ DE TECHNOLOGIE BELFORT-MONTBÉLIARDA

#### N° 0 5

## Création et analyse de graphes de traitements sur FPGA, sous contraintes matérielles et contexte temps réel dur

présentée par

## Ke DU

pour obtenir le

## Grade de Docteur de Université Bourgogne Franche-Comté

Spécialité : Informatique

Dissertation Committee:

| Eric MONMASSON  | Rapporteur            | Professeur à l'Université de Cergy Pontoise |

|-----------------|-----------------------|---------------------------------------------|

| François AUGER  | Rapporteur            | Professeur à l'Université de Nantes         |

| Serge WEBER     | Examinateur           | Professeur à l'Université de Lorraine       |

| MICHEL LENCZNER | Directeur de thèse    | Professeur à l'Université Bourgogne         |

|                 |                       | Franche-Comté                               |

| Stéphane DOMAS  | Co-directeur de thèse | Maître de Conférences à l'Université        |

|                 |                       | Bourgogne Franche-Comté                     |

## ABSTRACT

## Building and analyzing processing graphs on FPGAs under strong real-time environment and hardware constraints

Ke Du University of Burgundy Franche-Comté, 2018

#### Supervisors: Michel Lenczner, Stéphane Domas

In recent years, embedded systems has been widely used in both scientific environment and daily lives of common people. For some applications with strong real-time constraints, FPGA chips constitute a good choice. Their sizes and capacities are increasing continuously, allowing to build more and more complex applications. Thus, it is harder and harder to manage the application designs manually. This problem has been addressed through several ways. One is to use a model that is a more or less realistic abstraction of the behavior of the design. Nevertheless, it introduces another problem, which is the efficient implementation of the model on real architectures, like FPGAs. For example, some model characteristics may lead to a waste of resources, which can even make a design infeasible for a particular target architecture.

In this dissertation, we focus on overcoming some limitations yield by unfaithful descriptions of hardware behaviors for some existing models and the drawbacks of available tools. The Static/Synchronous Data Flow (SDF) based models, especially the version with Access Patterns (SDF-AP), are investigated. From the analysis of the problems of the existing models and EDA tools, our researches yield a new model: Actors with Stretchable Access Patterns (ASAP), and a new EDA tool called BIAsT (Block Assembly Tool). The model shares some basic principles of SDF-AP model but with other semantics and goals, which allows to model a wider range of behaviors and to obtain greater analysis capacities. Indeed, we propose a complete framework to check whether a design processes the input data streams correctly and if it is not the case, to modify the graph automatically to obtain this correctness. It is verified by experiments carried out on the realistic cases that clearly point out the advantages of ASAP over SDF-AP model, notably in terms of resources consumption. The BIAsT proposes a graphical interface to create designs by putting functional blocks on a panel and connecting them. It integrates the analysis principles defined by ASAP. It is also able to produce the VHDL code for the whole design. Thus, BIAsT offers the possibility for users without any knowledge in VHDL to create designs for FPGAs and with the insurance that it will produce correct results.

**KEY WORDS:** Field Programmable Gate Arrays (FPGAs), Embedded Systems, System on Chips (SoC), Static Analysis and Scheduling, Synchronous Data Flow (SDF), Model Based Design, Electronic Design Automation (EDA).

## RÉSUMÉ

## Création et analyse de graphes de traitements sur FPGA, sous contraintes matérielles et contexte temps réel dur

Ke Du Université Bourgogne Franche-Comté, 2018

#### Encadrants: Michel Lenczner, Stéphane Domas

Ces dernières années, les systèmes embarqués ont envahit tant les environnements scientifiques que la vie quotidienne. Pour les applications avec des fortes contraintes temps réel, les FPGA sont un choix pertinent. Leur taille et leurs capacités évoluent constamment, ce qui permet de créer des applications de plus en plus complexe. Cependant, cette augmentation va de pair avec une difficulté croissante à créer le design de ces application à la main. Ce problème a été abordé de diverses façons. L'un d'entre elles consiste à élaborer un modèle qui abstrait le comportement d'un design de façon plus ou moins réaliste. Cependant, cela conduit à un autre problème, qui est la transposition du modèle sur une architecture réelle telle qu'un FPGA. Par exemple, certaines caractéristiques du modèle peuvent entraîner un gâchis de ressources logiques, au point de rendre le design inapplicable sur certaines architectures.

Dans cette thèse, nous nous intéressons à comment dépasser les limitations de certains modèles en terme d'expressivité de comportement. Nous abordons également celles des outils d'aide au développement de designs. Les modèles basés sur les flux de données synchrones (SDF) et plus spécialement la version avec patrons d'accès (SDF-AP) ont été pris comme référence. A partir de l'étude des limitations de ces modèles, nous avons produit un nouveau modèle nommé Acteurs avec patrons d'accès extensibles (ASAP), ainsi qu'un nouvel environnement d'aide au développement nommé BIAsT. Ce modèle a des caractéristiques communes avec SDF-AP mais en leur donnant des nouvelles définitions afin d'élargir le nombre de comportements modélisés et les possibilité d'analyse du design. En effet, nous proposons un cadre d'analyse complet qui vérifie si le design traite correctement les flux de données entrants et si ce n'est pas le cas, qui fait automatiquement les modifications minimales pour assurer des résultats corrects. Ce cadre a été testé sur une application réelle qui montre clairement les avantages que procure notre modèle comparé à SDF-AP, notamment en terme de consommation de ressources logiques. Quant au logiciel BIAsT, il propose une interface graphique pour créer un design, simplement en posant des blocs fonctionnels sur un panneau et en les connectant. Il intègre les principes d'analyse tels que définis par ASAP. Enfin, il permet de générer automatique le code VHDL d'un design. En conclusion, il offre la possibilité de créer des designs FPGA sans aucun connaissance sur VHDL, tout en ayant l'assurance d'obtenir un code fonctionnel.

**MOTS-CLÉS:** Réseaux de portes logiques programmables (FPGAs), Systèmes embarqués, Système sur copeaux (SoC), Analyse et ordonnancement statique, Flux de données synchrones (SDF), Modèle basé sur la conception, Automatisation de la conception électronique (EDA).

## CONTENTS

| Ał | ostrad  | ot      |            |                            | 1  |

|----|---------|---------|------------|----------------------------|----|

| Re | ésum    | é       |            |                            | 3  |

| Та | ble o   | f Conte | ents       |                            | 8  |

| Li | st of   | Figure  | S          |                            | 10 |

| Li | st of   | Tables  |            |                            | 11 |

| Li | st of . | Algorit | hms        |                            | 13 |

| Li | st of   | Notion  | s and Ab   | breviationss               | 13 |

| Ac | cknov   | vledge  | ments      |                            | 19 |

| 1  | Intro   | oductio | n          |                            | 21 |

|    | 1.1     | Gener   | al Introdu | lction                     | 21 |

|    | 1.2     | Motiva  | ation and  | Objectives                 | 22 |

|    | 1.3     |         |            | f this Thesis              |    |

|    | 1.4     |         |            |                            |    |

| I  | Scie    | entific | Backgro    | ound                       | 25 |

| 2  | Sum     | mary    | of Biblio  | yraphy                     | 27 |

|    | 2.1     | Introd  | uction     |                            | 27 |

|    | 2.2     | Field I | Programm   | nable Gate Arrays          | 28 |

|    |         | 2.2.1   |            | ents of FPGAs              |    |

|    |         |         | 2.2.1.1    | Flip-Flops                 |    |

|    |         |         | 2.2.1.2    | Lookup Tables (LUTs)       |    |

|    |         |         | 2.2.1.3    | Multipliers and DSP Slices |    |

|    |         |         |            | Block RAM                  |    |

|     | 2.2.2  | PGA Design and Tools                             |

|-----|--------|--------------------------------------------------|

|     |        | .2.2.1 The Design Flow                           |

|     |        | .2.2.2 Traditional Design Tools                  |

|     |        | .2.2.3 High-Level Synthesis Design Tools         |

|     | 2.2.3  | nalysis                                          |

| 2.3 | Model  | or Static Analysis                               |

|     | 2.3.1  | Synchronous Data Flow                            |

|     |        | .3.1.1 Principles                                |

|     |        | .3.1.2 Analysis                                  |

|     | 2.3.2  | Cyclo-Static Data Flow                           |

|     |        | .3.2.1 Principles                                |

|     |        | .3.2.2 Analysis                                  |

|     | 2.3.3  | Static Data Flow with Access Patterns            |

|     |        | .3.3.1 Principles                                |

|     |        | .3.3.2 Analysis                                  |

|     | 2.3.4  | Other Data Flow Based Models                     |

|     |        | .3.4.1 Some Efforts in Data Flow Based Models 43 |

|     |        | .3.4.2 Analysis                                  |

|     | 2.3.5  | Cheduling of Hardware Systems                    |

|     | 2.3.6  | Design Frameworks of Data Flow Based Models 46   |

|     | 2.3.7  | Remarks                                          |

| 2.4 | Conclu | ion                                              |

#### **II** Contributions

#### 51

| 3 | Acto | ors witl | n Stretchable Access Patterns | 53 |

|---|------|----------|-------------------------------|----|

|   | 3.1  | Introdu  | uction                        | 53 |

|   | 3.2  | Limita   | tions of SDF-AP Model         | 54 |

|   |      | 3.2.1    | Auto-concurrency              | 54 |

|   |      | 3.2.2    | Strict Pattern Conformance    | 55 |

|   |      | 3.2.3    | Infinite Buffering            | 56 |

|   |      | 3.2.4    | Mandatory Buffering           | 56 |

|   | 3.3  | Princip  | bles                          | 57 |

|   |      | 3.3.1    | Actor's Context and Structure | 57 |

|   |      | 3.3.2    | Actor's Behavior              | 59 |

|   |      |        | 3.3.2.1 Computation                                        | 59  |

|---|------|--------|------------------------------------------------------------|-----|

|   |      |        | 3.3.2.2 Execution and Concurrency                          | 59  |

|   |      |        | 3.3.2.3 Delay between Executions                           | 60  |

|   |      | 3.3.3  | Actor's Patterns and Schedules                             | 60  |

|   |      |        | 3.3.3.1 Execution                                          | 60  |

|   |      |        | 3.3.3.2 Consumption                                        | 61  |

|   |      |        | 3.3.3.3 Production                                         | 63  |

|   |      |        | 3.3.3.4 Output                                             | 64  |

|   |      |        | 3.3.3.5 Remarks                                            | 66  |

|   | 3.4  | Evalua | tion through Existing IPs                                  | 67  |

|   |      | 3.4.1  | Tests on the original version of FIR filter                | 67  |

|   |      | 3.4.2  | The AIX4-stream protocol                                   | 71  |

|   | 3.5  | Conclu | usion                                                      | 72  |

| 4 | Stra |        | for Design Analysis Based on ASAP Model                    | 75  |

| 7 | 4.1  | -      |                                                            | _   |

|   |      |        | inary Remarks about Graph Analysis                         |     |

|   | 1.6  | 4.2.1  | Additional Assumptions on the Graph of Actors              |     |

|   |      |        | Correct Processing Conditions Resulting from ASAP Modeling |     |

|   | 4.3  |        | gies for Design Analysis                                   |     |

|   | 1.0  | 4.3.1  | Sample Rate Checking                                       |     |

|   |      | 4.3.2  | Graph Traversal                                            |     |

|   |      | 4.3.3  | Ratio Checking and Resampling                              |     |

|   |      | 4.3.4  | Compatibility Checking                                     |     |

|   |      |        | 4.3.4.1 Admittance Pattern Generation                      |     |

|   |      |        | 4.3.4.2 Pattern Compatibility Checking                     |     |

|   |      | 4.3.5  | Pattern Modification                                       |     |

|   |      |        | 4.3.5.1 Synthesis on an Example Case                       | 93  |

|   |      |        | 4.3.5.2 Principles of Pattern Modification                 |     |

|   | 4.4  | Experi | ments and Analysis                                         | 96  |

|   | 4.5  | Conclu | usion                                                      | 100 |

|   |      |        |                                                            |     |

| 5 |      |        |                                                            | 103 |

|   | 5.1  |        |                                                            |     |

|   | 5.2  |        | Functionalities                                            |     |

|   |      | 5.2.1  | Project Management and Design Creation                     | 105 |

|     |     | 5.2.2   | Graph A   | nalysis and VHDL Generation | 106 |

|-----|-----|---------|-----------|-----------------------------|-----|

|     |     |         | 5.2.2.1   | The Reference File          | 107 |

|     |     |         | 5.2.2.2   | The Implementation File     | 108 |

|     |     |         | 5.2.2.3   | Analysis                    | 111 |

|     |     |         | 5.2.2.4   | VHDL Generation             | 111 |

|     | 5.3 | Examp   | ole Case  |                             | 113 |

|     | 5.4 | Conclu  | usion and | Perspectives                | 115 |

| 111 | Со  | nclusi  | on and I  | Perspectives 1              | 117 |

| 6   | Con | clusior | n and Per | spectives                   | 119 |

|     | 6.1 | Conclu  | usion     |                             | 119 |

|     | 6.2 | Perspe  | ectives . |                             | 120 |

|     |     |         |           |                             |     |

| -            |   |    |          |    |   |   |  |

|--------------|---|----|----------|----|---|---|--|

| Bi           | h | 10 |          | ro | n | h |  |

| $\mathbf{D}$ |   |    | <b>u</b> | ια | D |   |  |

|              |   |    |          |    |   |   |  |

## LIST OF FIGURES

| 2.1  | FPGA chips produced by Xilinx and Altera.                                                     | 28 |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | The different parts of an FPGA                                                                | 29 |

| 2.3  | The symbol of flip-flop                                                                       | 30 |

| 2.4  | An 4-input LUT.                                                                               | 30 |

| 2.5  | Boolean AND operation                                                                         | 30 |

| 2.6  | Multiply function.                                                                            | 31 |

| 2.7  | Schematic drawing of a 4-bit by 4-bit multiplier                                              | 31 |

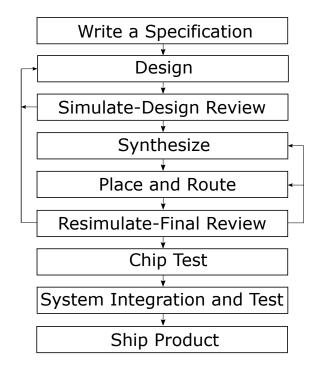

| 2.8  | The flow chart of FPGA design                                                                 | 33 |

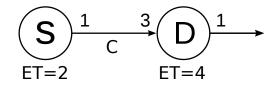

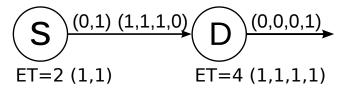

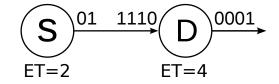

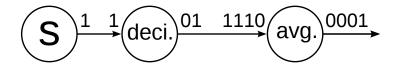

| 2.9  | A Source-Downsampler presented by SDF                                                         | 37 |

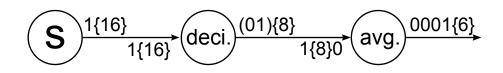

| 2.10 | A Source-Downsampler presented by CSDF                                                        | 39 |

| 2.11 | A Source-Downsampler presented by SDF-AP.                                                     | 41 |

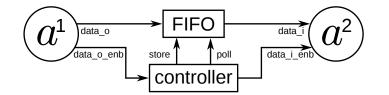

| 2.12 | General structure (FIFO+controller) to interconnect two actors in SDF-AP                      | 42 |

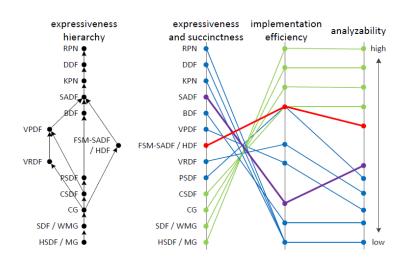

| 2.13 | Hierarchy graph of dataflow based models                                                      | 45 |

| 3.1  | A decimator connected to an average filter with fixed size data flows mod-<br>eled by SDF-AP. | 55 |

| 3.2  | A decimator connected to an average filter with an infinite data flow mod-<br>eled by SDF-AP. | 56 |

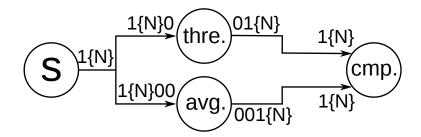

| 3.3  | An average filter and a threshold filter in parallel, feeding a comparator modeled by SDF-AP. | 56 |

| 3.4  | The process of computing output pattern.                                                      | 65 |

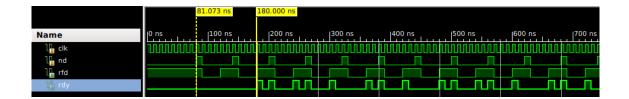

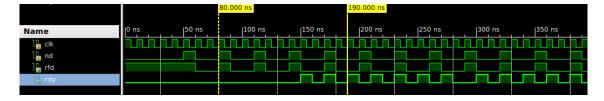

| 3.5  | Simulation 1 - 3 $\rightarrow$ 5 interpolator for $IP_{4cc}$ .                                | 68 |

| 3.6  | Simulation 2 - 3 $\rightarrow$ 5 interpolator for $IP_{5cc}$ .                                | 68 |

| 3.8  | Simulation 4 - 5 $\rightarrow$ 7 interpolator for $IP_{4cc}$ .                                | 68 |

| 3.7  | Simulation 3 - 3 $\rightarrow$ 5 interpolator for $IP_{6cc}$ .                                | 69 |

| 3.9  | Simulation 5 - 5 $\rightarrow$ 7 interpolator for $IP_{5cc}$                                  | 69 |

| 3.10 | Simulation 6 - 5 $\rightarrow$ 7 interpolator for $IP_{6cc}$ .                                | 69 |

| 3.11 | Simulation 7 - 5 $\rightarrow$ 8 interpolator for $IP_{4cc}$                                  | 69 |

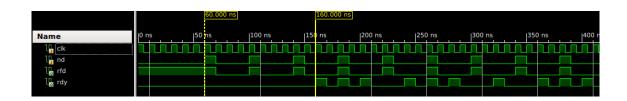

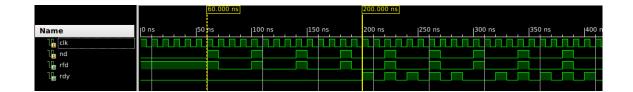

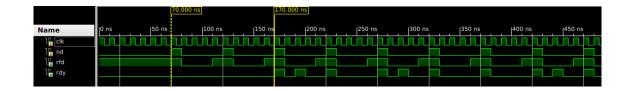

| 3.12 | Simulation 8 - 5 $\rightarrow$ 8 interpolator for $IP_{5cc}$                                  | 69 |

| 3.13 | Simulation 9 - 5 $\rightarrow$ 8 interpolator for $IP_{6cc}$ .                                | 70 |

| 3.14 | Simulation 10 - 5 $\rightarrow$ 7 interpolator v2, for $IP_{5cc}$ .              | 70 |

|------|----------------------------------------------------------------------------------|----|

| 3.15 | Simulation 11 - 5 $\rightarrow$ 7 interpolator for $IP_{3cc}$                    | 70 |

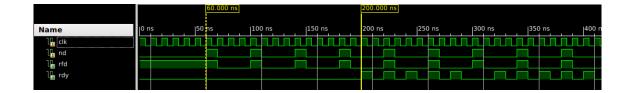

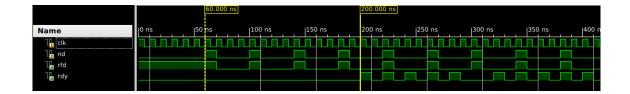

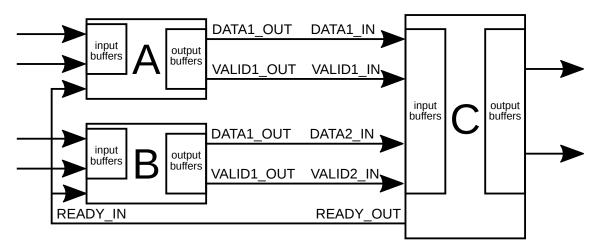

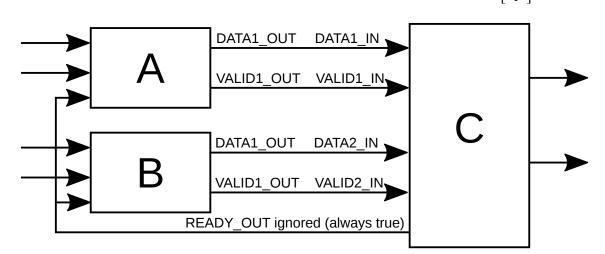

| 3.16 | AIX4-stream - IPs using the blocking mode                                        | 71 |

| 3.17 | AIX4-stream - IPs using the non-blocking mode.                                   | 72 |

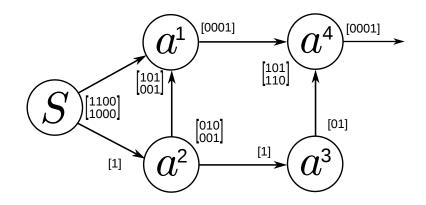

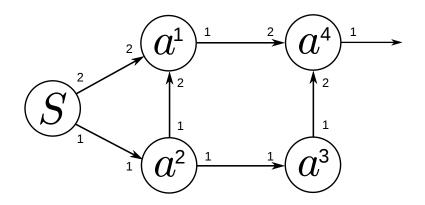

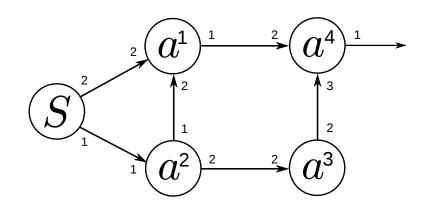

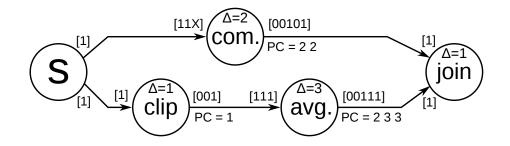

| 4.1  | An graph presented by ASAP model                                                 | 76 |

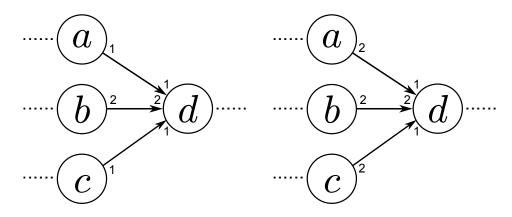

| 4.2  | An example of channels aggregation.                                              | 76 |

| 4.3  | Consumption rates: the most favorable case and the unfavorable case              | 77 |

| 4.4  | Consumption rates of an actor in different cases.                                | 78 |

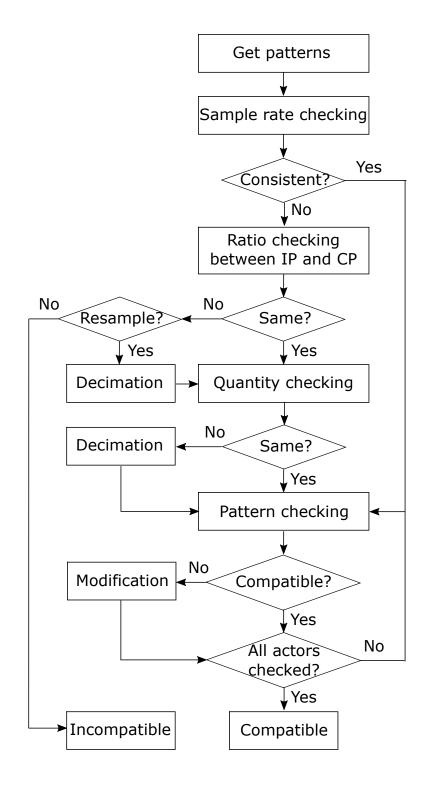

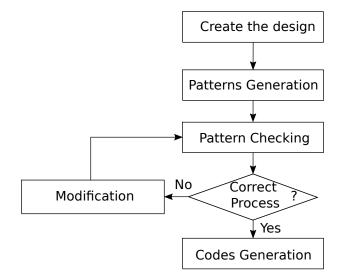

| 4.5  | The flow chart of conformance checking and modification                          | 79 |

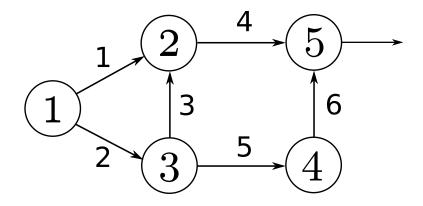

| 4.6  | A graph (consistent) presented in SDF model                                      | 81 |

| 4.7  | A labeled graph.                                                                 | 81 |

| 4.8  | A graph (inconsistent) presented in SDF model                                    | 82 |

| 4.9  | Building admittance pattern for Example 9                                        | 87 |

| 4.10 | Infinite number of choices when building an admittance pattern                   | 88 |

| 4.11 | Building admittance pattern for Example 11                                       | 91 |

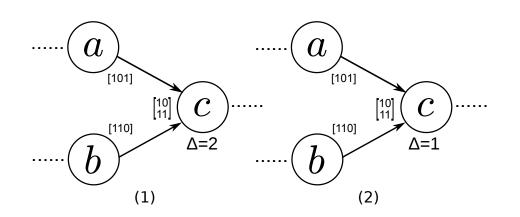

| 4.12 | An ASAP design: filtering a stereo signal.                                       | 93 |

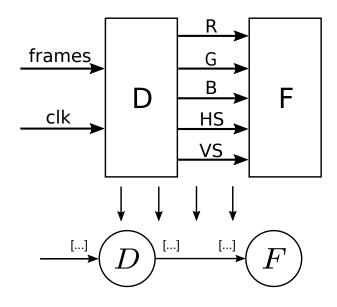

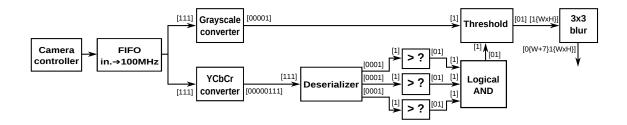

| 4.13 | Demonstration case: a graph of blocks for real-time image processing on an FPGA. | 97 |

| 5.1  | The flow chart of working process in BIAsT.                                      | 04 |

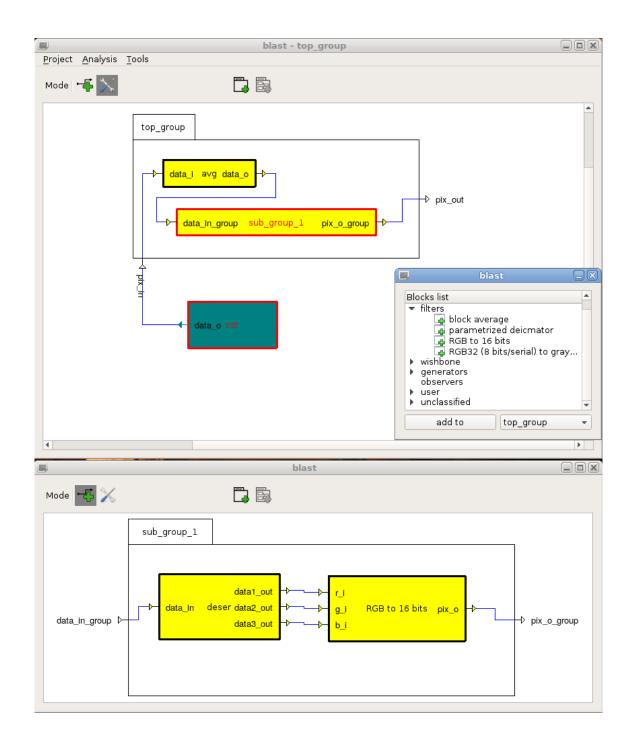

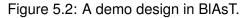

| 5.2  | A demo design in BIAsT                                                           | 06 |

| 5.3  | An example of reference file                                                     | 07 |

| 5.4  | Parameter setting in BIAsT                                                       | 08 |

| 5.5  | An example of implementation file                                                | 09 |

| 5.6  | An example of @for instruction in an implementation file                         | 10 |

| 5.7  | The patterns definition for a blur filter                                        | 10 |

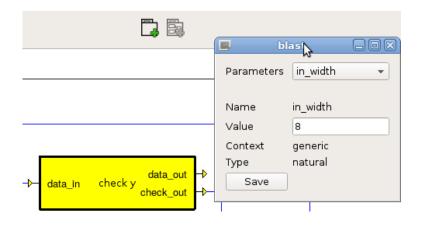

| 5.8  | An example of generated VHDL code for a top group.                               | 12 |

| 5.9  | An example of wheels detector design in BIAsT                                    | 13 |

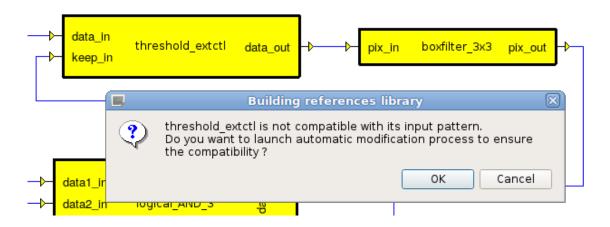

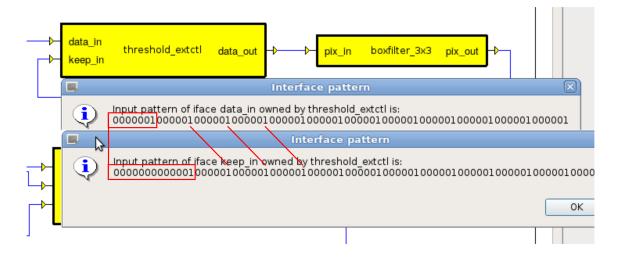

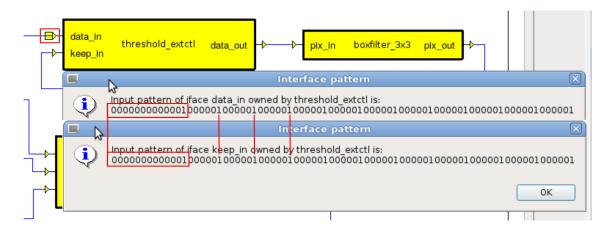

| 5.10 | Detection of an incompatible case                                                | 14 |

| 5.11 | Investigating an incompatible case                                               | 14 |

| 5.12 | Solving an incompatible case                                                     | 15 |

## LIST OF TABLES

| 2.1 | Truth table for boolean AND operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Characteristics of 5 $\rightarrow$ 7 and 5 $\rightarrow$ 8 interpolators $\hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \hfill \hfill \hfill \ldots \hfill \hfill \hfill \ldots \hfill \h$ | 68  |

| 4.1 | Production counters of blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98  |

| 4.2 | Production patterns for different camera clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 99  |

| 4.3 | Resources consumption with ASAP model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99  |

| 4.4 | Min. and max. combination of test parameters with SDF-AP model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 |

| 4.5 | Test results of two examples of timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

## LIST OF ALGORITHMS

| 1  | Transmutation from input pattern to input schedule.  | 58 |

|----|------------------------------------------------------|----|

| 2  | Transmutation from output pattern to output schedule | 58 |

| 3  | Transmutation from output schedule to output pattern | 58 |

| 4  | Output pattern generation.                           | 66 |

|    |                                                      |    |

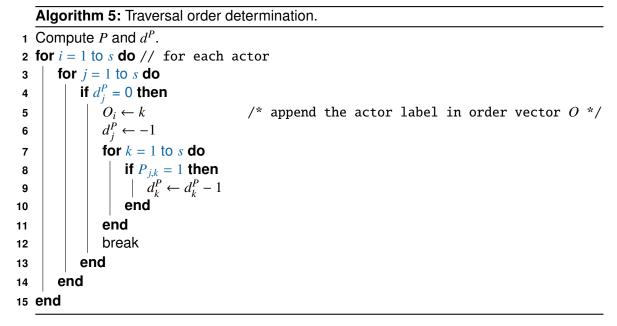

| 5  | Traversal order determination.                       | 83 |

| 6  | Ratio checking and resampling.                       | 85 |

| 7  | Admittance generation.                               | 90 |

| 8  | Compatibility checking.                              | 92 |

| 9  | Pattern modification and decimation.                 | 95 |

| 10 | Delays calculation                                   | 96 |

|    |                                                      |    |

## NOTIONS AND ABBREVIATIONS

In order to help the reader, the main notions and acronyms used in this manuscript are reported here, together with a short description in English and French. They are given in their approximate order of appearance.

• SDF graph: Static Data Flow graph (graphe à flux de données statiques).

SDF is a model that abstracts a design with a graph composed of actors linked by channels. An Actor represents a process that consumes and produces a fixed (i.e. static) number of data during each of its executions. Data are received/sent via the channels.

SDF est un modèle qui abstrait un design grâce à un graphe composé d'acteurs reliés par des canaux. Un acteur représente un processus qui consomme et produit un nombre fixe (d'où le mot statique) de données à chacune de ses exécutions. Les données sont reçues/envoyées via les canaux.

SDF-AP: Static Data Flow with Access Patterns (flux de données statiques avec schéma d'accès).

SDF-AP is a model that uses access patterns to describe at which clock cycles an actor consumes/produces data during a single execution. A pattern is a sequence of 1 and 0, with a length equal to the duration of the execution in clock cycles. For a given clock cycle, a 1 means that the actor consumes/produces a data.

SDF-AP est un modèle qui utilise des schémas d'accès pour décrire à quel cycle horloge un acteur consomme/produit une donnée lors de son exécution. Un schéma d'accès est une suite de 1 et 0, dont la longueur est celle d'une exécution en terme de cycles horloge. Pour un cycle donnée, un 1 signifie que l'acteur consomme/produit une donnée.

ASAP: Actors with Stretchable Access Patterns (Acteurs avec schéma d'accès extensible).

ASAP is a model also using access patterns. Nevertheless, patterns describe the maximum pace of consumption/production of an actor. When connected to other actors, it may receive/send data at a lower pace, which means that the pattern contains more 0 than expected: it is stretched. This model is the central contribution of this PhD.

ASAP est un modèle qui utilise également les schémas d'accès. Néanmoins, ces schémas décrivent le rythme maximum de consommation/production. Quand un acteur est connecté à d'autres, il peut recevoir/envoyer des données à un rythme plus lent. Cela implique que le schéma contient plus de 0 que prévu : il est donc étiré.

• *P<sub>I</sub>*, *P<sub>O</sub>*: Number of input/output ports (nombre de ports d'entrée/sortie).

For an actor within a graph,  $P_I$  is the number of its input channels, and  $P_O$  the number of output channels. The word "port" is a reference to the name used for inputs/outputs signals of a VHDL component.

Pour un acteur au seind d'un graphe,  $P_I$  est le nombre de canaux entrants et  $P_O$  celui des canaux sortant. Le mot "port" est une référence à celui utilisé pour les signaux d'entrée/sortie d'un composant VHDL.

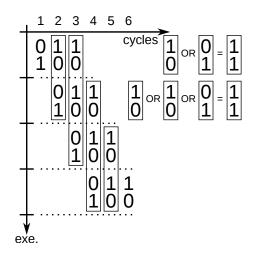

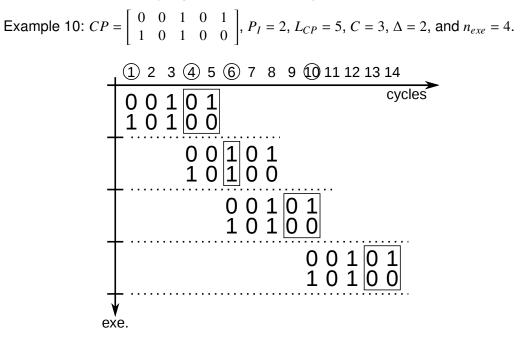

• CP, PP: Consumption/Production pattern (Schéma de consommation/production).

The consumption/production pattern represents the maximum pace of consumption/production of an actor, during one execution. For example, CP = [101] means that the actor can consume at most a data during the first and third clock cycle of its execution.

Le schéma de consommation/production représente le rythme maximal de consommation/production d'un acteur durant son exécution. Par exemple, CP = [101] signifie que l'acteur peut au mieux consommer une donnée lors des premier et troisième cycles horloge de son exécution.

•  $\delta$ : Production delay (délai de production).

It represents the latency of an actor, i.e. the number of clock cycles needed to produce the first result. It corresponds to the number of 0 at the beginning of PP.

Il représente la latence d'un acteur, c'est-à-dire le nombre de cycles horloge pour produire le premier résultat. Il correspond au nombre de 0 au début de PP.

• PC: Production counter (Compteur de production).

The production counter represents the number of data that must be consumed to produce a particular data. For example, PC = [2,3] means that the actor must consume 2 data to produce the first result, and one more (thus 3) to produce the second.

Le compteur de production représente le nombre de données qui doivent être consommées pour produire une donnée en particulier. Par exemple, PC = [2, 3] signifie que l'acteur doit consommer 2 données pour produire le premier résultat, et une de plus (donc 3) pour produire le second.

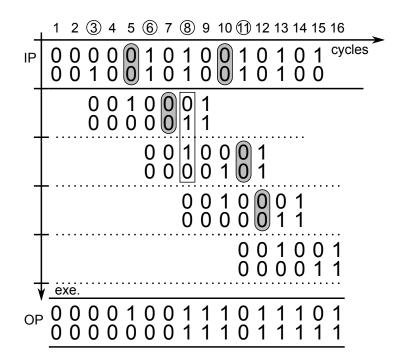

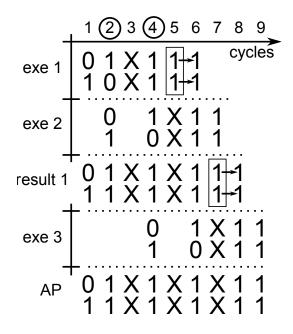

• IP, OP: Input/Output pattern (Schéma d'entrée/de sortie).

The input/output pattern represents what an actor really receives/produces all along its executions when it is connected to other actors. IP must be compatible with the admittance pattern (see below) so that the actor can consume and process the data correctly. In that case, OP is computed from IP, PP and PC.

Le schéma d'entrée/sortie représente ce qu'un acteur va réellement recevoir ou produire tout au long de ses exécutions, lorsqu'il est connecté à d'autres acteurs. IP doit être compatible avec le schéma d'admissibilité (voir ci-dessous) pour que l'acteur consomme et traite correctement les données. Dans ce cas, OP est calculé à partir de IP, PP et PC.

IS, OS, PS: Input, Output, Production Schedules (Timings d'entrée, sortie, production).

The input, output or production schedules are an alternative representation of the patterns. The schedule is the list of the clock cycles at which there is a 1 in the associated pattern.

Les timings d'entrée, sortie ou production sont une représentation alternative des schémas d'accès. Un timing est la liste de cycles horloge où apparaît un 1 dans le schéma associé.

• AP: Admittance pattern (Schéma d'admissibilité).

The admittance pattern is built from the consumption pattern. If removing some 0 in the input pattern leads to the admittance pattern, they are declared to be compatible. It means that the actor consumes and processes correctly the input data.

Le schéma d'admissibilité est créé à partir du schéma de consommation. Si en supprimant des 0 du schéma d'entrée, on obtient le schéma d'admissibilité, ils sont déclarés comme étant compatibles. Cela signifie que l'acteur consomme et traite correctement les données.

•  $\Delta$ : Delay between executions (délai entre les exécutions).

It describes the number of data that must be consumed by an actor before it can start another execution. Depending on its value and the number of 1 in the consumption pattern, it may lead to concurrent executions of the actor.

Il décrit le nombre de données qui doivent être consommées par un acteur avant qu'il ne puisse être exécuté une nouvelle fois. Selon sa valeur et le nombre de 1 dans le schéma de consommation, cela peut conduire à des exécutions concurrentes de l'acteur.

• Γ: Topology matrix (matrice de topologie).

It represents the relations between actors and their consumption/production on the channels of a graph. Assuming actors and channels are labeled with unique numbers,  $\Gamma_{i,j}$  is the number of data consumed/produced (depending on the sing value) by actor *j* on channel *i*.

Elle indique les relations entre les acteurs et leur consommation/production sur les canaux. En supposant que chaque acteur/canal reçoit un numéro unique,  $\Gamma_{i,j}$  donne le nombre de données consommées/produites (selon de signe de la valeur) par l'acteur *j* sur le canal *i*.

• q: Repetition vector (vecteur de répétition).

This vector only exists if all data produced by actors during a certain number of executions are finally consumed in a finite time. It expresses the existence of a cycle. Taking into account the same labels used for  $\Gamma$ ,  $q_i$  gives the number of executions of actor *i* to obtain that cycle.

Ce vecteur n'existe que si toutes les données produites par les acteurs durant un certain nombre d'exécutions sont consommés dans un temps fini. Cela exprime une notion de cycle. En se basant sur la même numération de  $\Gamma$ ,  $q_i$  indique le nombre d'exécution de l'acteur *i* pour obtenir ce cycle.

• O: Traversal order (ordre d'analyse).

This vector gives an order to analyze the actors, for example when input pattern compatibility is checked. It ensures that all the precursors of a given actor are analyzed before itself.

Ce vecteur indique un ordre pour analyser le graphe, par exemple afin de tester la compatibilité des schémas d'entrée. Cet ordre assure que tous les précurseurs d'un acteur sont évalués avant lui-même.

• *CM*, *PM*: Consumption/Production matrix (matrice de consommatio/production).

They give the number of data sent/receive between two given actors. They are used to check if sample rates of consumption/production are consistent between actors.

Elles indiquent le nombre de données envoyées/reçues entre deux acteurs donnés. Elles sont utilisées pour vérifier que les taux de consommation/production entre deux acteurs sont cohérents.

• D: Downsampling matrix (matrice de réechantillonage).

This matrix indicates the downsampling (i.e. the decimation rate) that must be applied between two actors so that their rates of consumtion/production are consistent.

Cette matrice indique le rééchantillonnage (c.a.d. le taux de décimation) à appliquer entre deux acteurs afin que leur taux de consommation/production soient cohérents.

• *DS* : Decimation schedule (Timings de décimation).

DS contains a vector for each input port of an actor. Each vector gives the clock cycles at which a decimation occurs (i.e. a valid data that is ignored).

DS contient un vecteur pour chaque port d'entrée d'un acteur. Chaque vector indique à quel cycles horloge une décimation doit avoir lieu (c.a.d. une donnée valide ingorée).

• DM: Delay matrix (Matrice des délais).

DM contains the delay that must be applied to each valid value received by an actor. It may be 0. These delays allows to enforce a corect processing.

DM contient le délai à appliquer pour chaque donnée valide reçue par un acteur. Cela peut être 0. Ces délais permettent d'assurer un traitement correct.

• BIAsT: Block Assembly Tool (Outil d'assemblage de blocs).

BIAsT is the software developped in the framework of this PhD. It allows to create FPGA designs graphically, to analyze and to modify them with the principles of ASAP. It also generates the VHDL code.

BIAsT est l'outil logiciel développé dans le cadre de cette thèse. Il permet de créer de façon graphique des designs pour FPGA, de les analyser et les modifier grâce aux principes d'ASAP. Il génère également le code VHDL.

## ACKNOWLEDGEMENTS

The long journey of my Ph.D. study has finished. It is with great pleasure to express my most sincere gratitude to Prof. Michel Lenczner and Assoc. Prof. Stéphane Domas, my supervisors, for giving me the opportunity to work on my dissertation, and for their dedicated guidance, thoughtful advices and endless patience during the course throughout the entire process of my study. During the past three years, They have been constantly available to discuss our results and provide insightful suggestions. Without their brilliant and illuminating instructions on my research and even about the writing, this dissertation could not reach its present form. This dissertation would never have been possible without their elaborative direction and meticulous corrections.

I wish also to acknowledge the members of AND(*Algorithmique Numérique Distribuée*) for the warm and friendly atmosphere in which they allowed me to work. Especially for the helps from Prof. Raphaël Couturier and my colleague Yousra Ahmed Fadil, Amor Lamar, Nesrine Khernane and Ali Kadhum Idrees both in life and study. I will never forget all the colleagues: Jean-François Couchot, Mourad Hakem, Gilles Perrot, Michel Salomon, Jean-Claude Charr, Karine Deschinkel, Arnaud Giersch, Abdallah Makhoul, Fabrice Ambert, Christophe Guyeux, Mohammed Bakiri, Joseph Azar, Gaby Boutayeh, Zeinab Fawaz, Christian Salim, Carol Habib, Anthony Nassar and Ahmed Badri Muslim Fanfakh.

I would further like to give my gratitude to the financial support from the program of China Scholarships Council (CSC), and to UBFC where I did my dissertation.

My sincere thanks also goes to my friends that I passed an amazing journey with them in France. I will never forget the beautiful moments I shared with you: Ruifeng Zhu, Yan Wang, Jie Qiu, Chunjie Huang, Chaoyue Chen, Hui Shang, Renfei Han, Zhao Zhang, Dongxue Lu, Chen Song, Jianding Guo, Yingchun Xie, Rongrong Liu, Jian Zhang, Tao Jiang, Hailong Wu, Mengli Yin, Lei Zhang, Daming Zhou, Bei Li, Yu Wu, Jinjian Li, Jin Wei.

I would also like to express my thanks to the high speed development of China and the fast growing of real estate prices, which have been encouraging me to non-stop hard working.

Finally, I wish to take this opportunity to express my appreciation and thanks to all my family for the emotional support. I would especially like to thank my parents who provide me the mental support and encouragement to explore the unknowns. Thanks especially to my wife Shuyi for her love. The future will be much better.

1

## INTRODUCTION

#### 1.1/ GENERAL INTRODUCTION

With the development of electronic industry, a growing number of projects require realtime streaming applications on embedded platforms. These comprise increasingly high hardware and timing constraints, which leads to the use of FPGAs (Field Programmable Gate Arrays). Usually, the designer should have a good knowledge of programming with VHDL or Verilog HDL. Unfortunately, only specialists can do it, because this needs a lot of training and practices to master the skill. Furthermore, even for specialists, the process of development is quite time consuming. Therefore, how to develop a tool to help non-expert users working on FPGA is a promising but challenging work.

In order to manage the ever-increasing size and complexity of designs, the abstraction is gradually more and more essential. As a result of a trend called "raising the level of abstraction", the developer can focus on the design at higher-level properties that matter most, which helps to avoid being bothered by the lower-level details. This is true in both software programming and hardware design, which have historically evolved toward higher-level languages and models. For software, programming languages have evolved from process-oriented assembly to object-oriented programming, such as C++ and Java. In the meanwhile, coming with the advances of chips and EDA tools functionalities, hardware design has evolved from basic logic elements transistor and gate layout to logic synthesis and high-level synthesis.

In another aspect, coping with large and complex systems, current hardware design practice often relies on integration of components. Although it makes hardware development much easier by allowing modularization and component reuse, because of a lack of support with rigorous methodologies, theories and tools are still managed in a mostly ad-hoc process. Some disturbing troubles or difficulties may be caused by the informal description documents of components. For example, designers can only get descriptions of structural but non-behavioral specifications in IP-XACT, which are usually incomplete. Moreover, the ability to read the files in English is a prerequisite.

Not only some models but also some tools have emerged in recent years, based on the concept of HLS (High Level Synthesis). They can make transformation in high-level languages, such as C and VHDL. These tools are increasingly effective but limited to low stress applications. Other tools exist, such as Simulink / HDL coder based chaining function blocks [65, 64]. This is the easiest way to create, debug and test a processing via simulation. Nevertheless, the results are seldom applicable when actually implemented

in FPGAs.

#### 1.2/ MOTIVATION AND OBJECTIVES

In general, the existing tools suffer from two flaws. One is that they do not take the physical characteristics of the target architecture of the application into account, including that of the selected FPGA. The other one is that they do not check whether a data stream is processed correctly by the chain, besides creating many test-benches, which is tedious and time consuming for the developer. In fact, these tools can neither analyze the process of a data stream when it passes through the processing graph nor test whether the blocks are actually able to produce the expected outcomes based on the entries and the selected target FPGA. Therefore, they are not suitable to produce applications in real-time environment and high hardware constraints.

These problems have been partially addressed in a previous thesis [32] that proposed a software environment named CoGen. It allows to create chains of blocks to process video streams (or similar ones), and check the capacity of each block to process the stream it receives. Finally, it was able to produce VHDL code for some FPGAs.

The primary objective of this dissertation is to generalize these results to an acyclic graph of blocks, by providing a model of them that allows to determine mathematically the correctness of the result, and thus without launching complex simulations. Every component used in FPGAs is regarded as a block. If the inputs and outputs of connected blocks can be approved compatible, the designed system can be implemented on an FPGA by hardware design languages (VHDL or Verilog HDL). But if the analysis result is negative, algorithms for modifying the design are needed. This is another objective of this thesis. After some modifications, some designs can be implemented on hardware and the correct designs can be derived from our approaches by algorithms. Otherwise, the designs are regarded as unable to be implemented correctly on FPGAs.

The final goal of this thesis is to develop a software tool which can produce VHDL code from a graph of functional blocks. It can do far more than existing ones based on the same concepts. One major new possibility, based on our models and algorithms, is to check whether the result will be correctly carried out by the proposed model and algorithms for a given input stream. The production of final VHDL code is made automatically by assembling previously developed components. This process is called block assembly. Then, the blocks are able to self-schedule their executions because they know the status of executions. Thus, users without VHDL programming skills are able to generate correct code by assembling blocks.

#### 1.3/ CONTRIBUTIONS OF THIS THESIS

In this dissertation, we concentrate on the study of the static analysis of block and graph models and the software tool that can help non-expert users for automatic design of FPGA implementations correctly. The main contributions are summarized as follows:

i) The limitations of existing SDF based models, in particular those of the SDF-AP model, are described and illustrated by the analysis of characteristic examples. The

#### 1.4. THESIS OUTLINE

two most common problems encountered in block assembly implementations are the production of incorrect results and the infinite growth of buffer size.

- ii) We propose a new model called Actors Stretchable Access Patterns (ASAP) that describes the hardware behaviors as efficiently and precisely as possible. This is a novel way to address the scheduling problem of actors dedicated for FPGA architectures. It opens the possibility to determine the execution correctness mathematically without launching complex simulations. It can not only model actors' behaviors properly, but also avoid the above mentioned drawbacks. Algorithms of transmutations of the patterns and corresponding schedules and output pattern generation are also provided.

- iii) We investigate strategies and related algorithms to analyze and schedule graphs of systems. The correctness of the designed systems can be analyzed by a series of algorithms, such as sample rate checking and pattern compatibility checking. Using the proposed ASAP model, the rate decimation and actor's input pattern modifications are applied when a correctness failure is detected. This increases the number of possible real FPGA implementations covered by the block assembly method.

- iv) A software tool based on the concept of functional block graph is also developed. It is called BIAsT (Block Assembly Tool) and aims to compensate the drawbacks of other tools based on the same concepts, as for example Simulink + HDL coder. In BIAsT, the proposed ASAP model and related algorithms are used to check that for a given input stream, whether the system can produce a correct result and finally generate VHDL code directly usable on a real FPGA-based board. Otherwise, the tool determines the required decimations and modifications on the graph automatically. It makes a user without any programming skills able to make designs on FPGAs thanks to the friendly graphic interface.

#### 1.4/ THESIS OUTLINE

The dissertation is organized as follows: the next chapter is a review of the related literature dedicated to models for static analysis and related tools oriented to FPGA implementation. A brief analysis of each model and tool is also discussed. Chapter 3 discusses the main limitations of the SDF-AP model and presents the principles of the proposed analysis model: Actors with Stretchable Access Patterns (ASAP). Both basic algorithms for pattern generation and transmutation are given together. Chapter 4 introduces the strategies to analyze a design modeled with the ASAP principles. Algorithms achieving this analysis are given in detail with examples. Furthermore, the proposed principles are verified to be feasible and efficient by some metrics and tests on realistic cases. Chapter 5 describes our EDA tool BIAsT developed based on the concept of block assembly, the proposed ASAP model and related approaches. Functionalities and the methods for using the tool are illustrated by a real application. Finally, the conclusions of the work and some perspectives are given in the last chapter.

# SCIENTIFIC BACKGROUND

2

## SUMMARY OF BIBLIOGRAPHY

#### 2.1/ INTRODUCTION

Hardware devices are widely used nowadays both in scientific environment and daily lives of common people. Among the different types of architectures, FPGAs have become indispensable choices for designers. Regardless of the relative high price, they really improve the reliability and the integration of systems, and they are especially suitable for small batch systems. Modern embedded systems often execute parallel applications. For instance smartphones have four or more processors and several applications can be run for different purposes simultaneously. Thus, there are many expectations for the systems, such as a robust behavior, stable performances and less resource consumption especially minimal energy cost for battery limitation, etc [19, 79]. Thanks to the high degree in integration, it is possible to design complex and large size systems. This leads to the conception of Multi-Processor Systems-on-Chips (MPSoCs). Some discussions about related theories and techniques can be found in [44, 78].

The abstraction of systems allows the designers to deal with large and complex systems. Cooperating with the abstraction, in the meanwhile, the reusable components work as functional blocks in different levels play an important role in hardware design. Both of them help a lot for FPGA design and yield more powerful FPGA applications. But programming MPSoCs is a challenging work, especially timing problems may be caused by the interaction between the components [63]. The design of the requisite communication and the control logic to connect the blocks are still made manually which is time consuming and error-prone. Designing hardware systems is usually done by taking system abstraction and usable components into account to meet the performance requirements. In practice, in order to chose the components to build a system correctly, the real-time environment and hardware constraints should be taken into consideration at the same time. Then, designers must deal with the interfaces of blocks in a manual way. Thus, they are usually faced with low-level control and timing artifacts. Even when all parts of systems are already built, designers still need to spend considerable time to debug [20]. Therefore, it is really hard to design MPSoCs on FPGAs. Some key issues regarding MPSoC design and programming is discussed in [62]. This includes the number of processors, interprocessor communications, concurrency, memory hierarchy, platform scalability, models of programming and control, etc. Although there are some commercial ESL and EDA tools which can provide help to designers, such as Xilinx ISE, they are still like the IP industry requiring to offer large components of the solution.

The question of whether it is possible to find a way to automatically reduce the

complexity of creating designs still remains. Many researchers have worked on it for a long time. With the efforts of researchers, series of models have been proposed. Nowadays, designing hardware often involves model based analysis and techniques [67, 82, 72, 61, 36, 10], and the related tools have also been developed, which can help to check the correctness of systems and give performance evaluations.

The basic problem is discussed in [88] with a vivid name as the glue design problem. An abstract model of hardware systems is provided to analyze the system correctness and performance properties. There are also other models dealing with the similar problems since 30 years ago, but surprisingly none of them described the hardware behavior precisely. Therefore, important information about system are omitted yielding rough system descriptions and resulting in either defensive or aggressive analysis results.

As for tools, there has been an increasing interest in the development and use of standard formats for system structure and IP configuration parameters. Among them, XML-based formats and data flow interchange format are widely used in the software tools development. But the core part to analyze the performance of the system is the model. Therefore, the analysis results of tools based on existing models can be seldom used directly and correctly.

It is promising to find a model that can describe the behaviors of hardware exactly and capture the properties of systems faithfully. If such a model is achieved, the related analysis results can be used in hardware design directly, especially for FPGAs. A software tool based on such a model will be more promising.

#### 2.2/ FIELD PROGRAMMABLE GATE ARRAYS

Field programmable gate arrays (FPGAs) are reprogrammable silicon chips. In 1985, the first FPGA was invented by Ross Freeman, the cofounder of Xilinx. In fact, FPGAs combine the best parts of application-specific integrated circuits (ASICs) and processor-based systems. This why FPGA chips are adopted across all industries. FPGAs provide hardware-timed speed and reliability, but they do not require high volumes to justify the large upfront expense of custom ASIC design. Figure 2.1 shows two FPGA chips produced by Xilinx (on the left) and Altera (on the right), which are the current FPGA market leaders and long-time industry rivals. Together, they control over 80 percents of the worldwide market.

Figure 2.1: FPGA chips produced by Xilinx and Altera.

Reprogrammable silicon has also the same flexibility of software running on a

processor-based system, but it is not limited by the number of available processing cores. Unlike processors, FPGAs are truly parallel in nature, so different processing operations do not have to compete for the same resources. This makes it possible for designers to get around the basic limitations of sequential processors. Each independent processing task is assigned to a dedicated section of the chip, and can function autonomously without any influence from other logic blocks. As a result, the performance of one part of the application is not affected when adding more processing.

#### 2.2.1/ COMPONENTS OF FPGAs

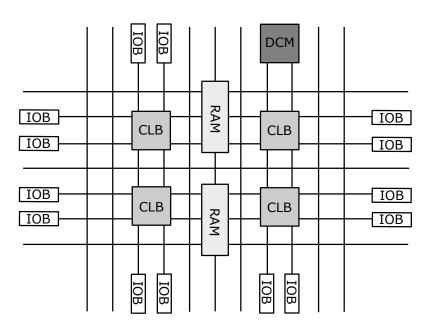

Until now, most of the FPGAs are based on look up tables (LUTs) technique. Every FPGA chip is made up of a finite number of predefined resources. Configurable logic blocks (CLB) are the basic unit of FPGAs. As shown in Figure 2.2, it works with programmable interconnects to implement a reconfigurable digital circuit, I/O blocks (IOB) to allow the circuit to access the outside world, embedded block RAM to make it more flexible in applications and digital clock management modules (DCM).

Figure 2.2: The different parts of an FPGA.

Generally, the metrics to evaluate FPGA resource specifications include the number of configurable logic blocks, the number of fixed function logic blocks such as multipliers and the size of memory resources like embedded block RAM. The parts shown in the above figure are typically the most important in FPGA chips. When selecting FPGAs for a particular application, these metrics must be taken into consideration.

The CLBs, sometimes referred to as slices or logic cells, are made up of two basic components: flip-flops and lookup tables (LUTs). Various FPGA families differ in the way flip-flops and LUTs are packaged together, so it is important to understand the principle of flip-flops and LUTs operation.

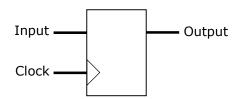

#### 2.2.1.1/ FLIP-FLOPS

Flip-flops are binary shift registers used to synchronize logic operations and save logical states between clock cycles within an FPGA circuit. On every clock edge, a flip-flop latches the 1 (TRUE) or 0 (FALSE) value on its input and holds that value constant until the next clock edge. As shown in Figure 2.3, a flip-flop has an input, an output and a clock signal.

Figure 2.3: The symbol of flip-flop.

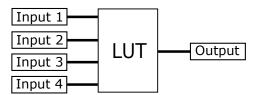

#### 2.2.1.2/ LOOKUP TABLES (LUTS)

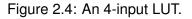

Much of the logic in a CLB is implemented using very small amounts of RAM in the form of LUTs. Figure 2.4 shows a 4-input LUT. It is easy to assume that the number of system gates in an FPGA refers to the number of NAND gates and NOR gates in a particular chip. But, in reality, all combinatorial logic (ANDs, ORs, NANDs, XORs, and so on) is implemented as truth tables within LUT memory. A truth table is a predefined list of outputs for every combination of inputs.

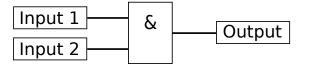

The Boolean AND operation, for example, is shown in Figure 2.5 and the corresponding truth table for the two inputs of an AND operation is shown in Table 2.1.

Figure 2.5: Boolean AND operation.

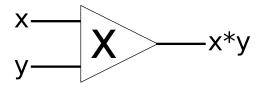

#### 2.2.1.3/ MULTIPLIERS AND DSP SLICES

Figure 2.6 shows a multiply function for the simple task of multiplying two numbers, which can get extremely resource intensive and complex to implement in digital circuitry. This

| Input1 | Input2 | Output |

|--------|--------|--------|

| 0      | 0      | 0      |

| 0      | 1      | 0      |

| 1      | 0      | 0      |

| 1      | 1      | 1      |

Table 2.1: Truth table for boolean AND operation

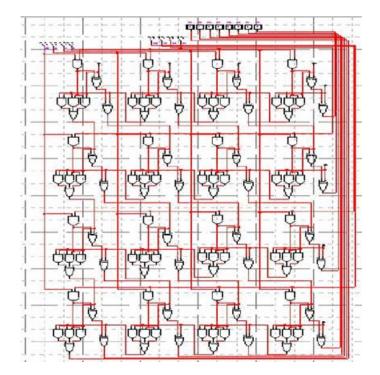

is illustrated in Figure 2.7 that shows the schematic drawing of one way to implement a 4-bit by 4-bit multiplier using combinatorial logic. When it comes to multiplying two 32-bit numbers, it ends up with more than 2000 operations. For this reason, FPGAs have prebuilt multiplier circuitry to save on LUT and flip-flop usage in math and signal processing applications.

Figure 2.6: Multiply function.

Figure 2.7: Schematic drawing of a 4-bit by 4-bit multiplier.

Many signal processing algorithms involve keeping the running total of numbers being multiplied, and, as a result, higher-performance FPGAs like Xilinx Virtex-5 FPGAs have

prebuilt multiplier-accumulate circuitry. These prebuilt processing blocks, also known as DSP48 slices, integrate a  $18 \times 18$  bits multiplier with adder circuitry.

# 2.2.1.4/ BLOCK RAM

Memory resources are another key specification to consider when selecting FPGAs. User-defined RAM, embedded throughout the FPGA chip, is useful for storing data sets or passing values between parallel tasks. Their size and number depends on the FPGA family and model. For example, a Spartan 6 LX100 integrates 536 RAM blocks of 9Kbits. There is still the option to implement data sets as arrays using flip-flops; however, large arrays quickly become expensive for FPGA logic resources. A 100-element array of 32-bit numbers can consume more than 30 percent of the flip-flops in a Virtex-II 1000 FPGA or take up less than 1 percent of the embedded block RAM. Digital signal processing algorithms often need to keep track of an entire block of data, or the coefficients of a complex equation, and without on-board memory, many processing functions do not fit within the configurable logic of an FPGA chip.

The inherent parallel execution of FPGAs allows for independent pieces of hardware logic to be driven by different clocks. Passing data between logic running at different rates can be tricky, and on-board memory is often used to smooth out the transfer using first-in-first-out (FIFO) memory buffers.

# 2.2.2/ FPGA DESIGN AND TOOLS

With the understanding of the fundamental FPGA components, the advantage of implementing a design in hardware circuitry can be seen clearly: it allows improvements in execution speed, reliability, and flexibility. However, in the process of FPGA design some trade-offs should be made based on an FPGA for the processing and I/O connectivity in a system.

For FPGA design, the designer defines digital computing tasks in software using development tools and then compile them down to a configuration file or bitstream that contains information on how the components should be wired together. Although there are many development tools, the challenge in the past with FPGA technology was that the low-level FPGA design tools could be used only by engineers with a deep understanding of digital hardware design. However, the rise of high-level synthesis (HLS) design tools, such as Simulink developed by MathWork and the NI LabVIEW system design software, changes the rules of FPGA programming in some degree.

# 2.2.2.1/ THE DESIGN FLOW

As the design is the main part of FPGA implementations, it is necessary to talk about the entire process. Figure 2.8 shows the design flow of hardware devices, not only for FPGA but also for others, such as ASIC and CPLD. Following the steps in the design flow can guarantee the best chance to get a correct prototype of the designed system.

# 2.2. FIELD PROGRAMMABLE GATE ARRAYS

Figure 2.8: The flow chart of FPGA design.

Writing a specification is the first step. This plays a quite important role as a guide for designers to understand the entire design and choose the proper devices. It allows to design the correct interface to the rest of the pieces of the chip. It also helps to save time and avoid misunderstanding. The following information should be included in a specification:

- An external block diagram showing how the chip fits into the system.

- An internal block diagram showing each major functional section.

- A description of the I/O pins, including output drive capability and input threshold level.

- Timing estimates, including setup and hold times for input pins, propagation times for output pins and clock cycle time.

- Estimated gate count.

- Package type.

- Target power consumption.

- Target price.

- Test procedures.

With the specification, the designer can find the best vendor with a technology and structure that best meets the requirements of the project. At this point, a design entry method should be chosen. Generally speaking, for small chips, schematic entry is used,

especially if the designer is familiar with the tools. But for large designs, a hardware description language (HDL) such as VHDL or Verilog HDL is used for its portability, flexibility, and readability. When using a high level language, synthesis software is required to "synthesize" the design. This means that the software creates low level gates from the high level description. Thus, at the same time, the designer should choose a synthesis tool, which is important since each synthesis tool has recommended or mandatory methods of designing so that it can work properly.