## Vieillissement accéléré de modules de puissance de type MOSFET SiC et IGBT Si basé sur l'analyse de profils de mission d'onduleurs photovoltaïques.

Mouhannad Dbeiss

#### ▶ To cite this version:

Mouhannad Dbeiss. Vieillissement accéléré de modules de puissance de type MOSFET SiC et IGBT Si basé sur l'analyse de profils de mission d'onduleurs photovoltaïques.. Energie électrique. Université Grenoble Alpes, 2018. Français. NNT: 2018GREAT020. tel-01869018

#### HAL Id: tel-01869018 https://theses.hal.science/tel-01869018

Submitted on 6 Sep 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : GENIE ELECTRIQUE

Arrêté ministériel : 25 mai 2016

Présentée par

#### **Mouhannad DBEISS**

Thèse dirigée par **Yvan AVENAS**, **Maître de Conférences HdR**, **Institut Polytechnique de Grenoble**

préparée au sein du CEA/INES dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Mission Profile-Based Accelerated Ageing Tests of SiC MOSFET and Si IGBT Power Modules in DC/AC Photovoltaic Inverters

Thèse soutenue publiquement le **14 Mars 2018**, devant le jury composé de :

#### M. Jean-Paul FERRIEUX

Professeur des Universités, Université Grenoble Alpes, Président

#### M. François FOREST

Professeur des Universités, Université Montpellier 2, Rapporteur

#### M. Hamid GUALOUS

Professeur des Universités, Université de Caen Normandie, Rapporteur

#### M. Laurent DUPONT

Chargé de Recherche, IFSTTAR, invité

#### M. Franck AI SHAKARCHI

Ingénieur, CEA, Co-encadrant, invité

#### M. Yvan AVENAS

Maître de Conférences HdR, Grenoble-INP, Directeur de thèse

First of all, Thank God Almighty, for having granted me the ability and strength to accomplish this thesis.

To my family, my source of love, self-confidence, encouragement and inspiration...

My father Gabriel, my mother Sosephine, my brother Barrak and my dear sisters Rayaly, Canadi and Amanie, it's to you that S dedicate my success, my doctorate degree and these years of challenging work spent far from you...

⊗ love you Mouhannad ⊗beiss

## **Acknowledgments**

The work presented in this thesis was financed by INES2 and ANR agency (MEMPHIS Project). It was carried out at CEA-INES (French Alternative Energies and Atomic Energy Commission- National Solar Energy Institute) in collaboration with CNRS-University of Grenoble Alpes, Grenoble INP, G2Elab.

I would like to warmly thank my thesis supervisor Dr. Yvan Avenas, for his dedication, his availability and his intelligence. I would also like to acknowledge the time he devoted correcting the manuscript and the articles, in addition to the time he spent educating me and answering my questions.

I would like to thank my colleagues in the power electronics team within CEA-INES for the help they provided in the experimental tests.

I would like to thank the CACHAN-SATIE laboratory, in particular Dr. Laurent Dupont, for his contribution, in addition to his useful and decisive advice throughout my thesis.

I would like to thank the chair of my committee Pr. Jean-Paul FERRIEUX (University of Grenoble Alpes) for examining this manuscript. I would equally like to thank my committee members, Pr. François FOREST (University of Montpellier 2) and Pr. Hamid Gualous (University of Caen Normandy) for having spent time evaluating and commenting on this manuscript.

I would like to thank all of my doctoral colleagues with whom I have shared wonderful memories.

Finally, in order not to forget anybody, I express my deepest thanks to all those who helped me carry out this work.

## **Abstract**

In the case of photovoltaic installations, the DC/AC inverter has the highest failure rate, and the anticipation of its breakdowns is still difficult, while few studies have been done on the reliability of this type of inverter. The aim of this PhD is to propose tools and methods to study the ageing of power modules in this type of application, by focusing on ageing phenomena related to thermo-mechanical aspects.

As a general rule, the accelerated ageing of power modules is carried out under aggravated conditions of current (Active Cycling) or temperature (Passive Cycling) in order to accelerate the ageing process. Unfortunately, when applying this type of accelerated ageing tests, some failure mechanisms that do not occur in the real application could be observed, while inversely, other mechanisms that usually occur could not be recreated.

The first part of the PhD focuses on the implementation of an accelerated ageing method of the semiconductor devices inside photovoltaic inverters. This is accomplished by analyzing the mission profiles of the inverter's output current and ambient temperature, extracted over several years from photovoltaic power plants located in the south of France. These profiles are used to study photovoltaic current dynamics, and are introduced into numerical models to estimate losses and junction temperature variations of semiconductors used in inverters, using the cycle counting algorithm "Rainflow".

This method is then performed in two experimental test benches. In the first one, the devices under test are IGBT modules, where the accelerated ageing profile designed is implemented using the opposition method. Moreover, an in-situ setup for monitoring ageing indicators (thermal impedance and dynamic resistance) is also proposed and evaluated. The second bench is devoted to study the ageing of SiC MOSFET power modules. The accelerated ageing test is carried out under the same conditions as for the IGBT modules with more monitored electrical indicators, but this time by disconnecting the semiconductor devices from the inverter. The results obtained allowed to determine several potential ageing indicators of IGBTs and SiC MOSFETs used in a photovoltaic inverter.

## Keywords

Photovoltaic Inverter - Mission profile - Silicon Carbide MOSFET - Accelerated ageing tests - Power cycling - Thermal cycling - Reliability - Condition monitoring - Failure indicators - Power losses estimation - Junction temperature estimation

## Résumé

Dans le cas des installations photovoltaïques, l'onduleur est le premier élément défaillant dont il est difficile d'anticiper la panne, et peu d'études ont été faites sur la fiabilité de ce type de convertisseur. L'objectif de cette thèse est de proposer des outils et méthodes en vue d'étudier le vieillissement des modules de puissance dans ce type d'application en se focalisant sur les phénomènes de dégradation liés à des aspects thermomécaniques.

En règle générale, le vieillissement accéléré des modules de puissance est effectué dans des conditions aggravées de courant (Cyclage Actif) ou de température (Cyclage Passif) pour accélérer les processus de vieillissement. Malheureusement, en appliquant ce type de vieillissement accéléré, des mécanismes de défaillances qui ne se produisent pas dans la vraie application peuvent être observés et, inversement, d'autres mécanismes qui se produisent habituellement peuvent ne pas apparaître.

La première partie de la thèse se focalise donc sur la mise en place d'une méthode de vieillissement accéléré des composants semi-conducteurs des onduleurs photovoltaïques. Cela est fait en s'appuyant sur l'analyse des profils de mission du courant efficace de sortie des onduleurs et de la température ambiante, extraits des centrales photovoltaïques situées au sud de la France sur plusieurs années. Ces profils sont utilisés pour étudier les dynamiques du courant photovoltaïque, et sont introduites dans des modèles numériques pour estimer les pertes et les variations de la température de jonction des semi-conducteurs utilisés dans les onduleurs, en utilisant l'algorithme de comptage de cycles "Rainflow".

Cette méthode est ensuite mise en œuvre dans deux bancs expérimentaux. Dans le premier, les composants sous test sont des modules IGBT. Les composants sont mis en œuvre dans un banc de cyclage utilisant la méthode d'opposition et mettant en œuvre le profil de vieillissement défini précédemment. Un dispositif in-situ de suivi d'indicateurs de vieillissement (impédance thermique et résistance dynamique) est également proposé et évalué. Le deuxième banc est consacré à l'étude de modules de puissance à base de MOSFET SiC. Le vieillissement est effectué dans les mêmes conditions que pour les modules IGBT et de nombreux indicateurs électriques sont monitorés mais, cette fois ci, en extrayant les composants de l'onduleur de cyclage. Les résultats obtenus ont permis de déterminer des indicateurs de vieillissement d'IGBT et de MOSFET SiC utilisés dans un onduleur photovoltaïque.

## Mots clés

Onduleur photovoltaïque - Profils de mission - MOSFET en Carbure de Silicium - Tests de vieillissement accéléré - Cyclage actif - Cyclage passif - Fiabilité du semi-conducteur - Suivi de l'état de santé - Estimation des pertes - Estimation de la température de jonction

## **Abbreviations**

AC Alternative Current

Al Aluminum

Al<sub>2</sub>O<sub>3</sub> Aluminum Oxide

AlN Aluminum Nitride

APC Active Power Cycling

BJT Bipolar Junction Transistor

BTI Bias Temperature Instability

CM Condition Monitoring CT Current Transformer

CTE Coefficient of Thermal Expansion

Cu Copper DC Direct Current

DCB Direct Copper Bonded DFT Discrete Fourier Transform

DMOS Double-diffused Metal-Oxide-Semiconductor

DPT Double Pulse Test

DUT Device Under Test

FFT Fast Fourier Transform

FIB Focused Ion Beam

FPGA Field Programmable Gate Array

FT Fourier Transform GaN Gallium Nitrade

HALT Highly Accelerated Life Test

HF Humidity Freeze

HMI Human Machine Interface

HTGB High Temperature Gate Bias

HTOB High Temperature Operating Bias

IDFT Inverse Discrete Fourier Transform

IGBT Insulated Gate Bipolar Transistor

JFET Junction Field Effect Transistor

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PCB Printed Circuit Board

PTC Passive Temperature Cycling

PV Photovoltaic

PWM Pulse Width Modulation RMS Root Mean Square

SAM Scanning Acoustic Microscopy

SEB Single-Event-Burnout

SEGR Single-Event-Gate-Rupture

SEM Scanning Electron Microscopy

Si Silicon

SiC Silicon Carbide SiO<sub>2</sub> Silicon Dioxide

TSCT Two Stage Current Transformer

TSEP Thermo-Sensitive Electrical Parameters

## **Notations**

PWM duty cycle α С Heat capacity

DC bus link capacitor  $C_{bus}$  $C_{cb}$ Collector-base capacitance Decoupling capacitors  $C_{dec}$  $C_{DS}$ Drain-source capacitance Gate-drain capacitance  $C_{GD}$ Gate-source capacitance  $C_{GS}$  $C_{i_{SS}}$ MOSFET's input capacitance

Cos  $\varphi$ Power factor

MOSFET's output capacitance  $C_{o_{SS}}$ MOSFET's reverse capacitance  $C_{r_{SS}}$

$C_{th}$ Thermal capacitance Cumulative damage

$D_i$ Device i

$\Delta I$ Current variation

$\Delta I/\Delta t$ Slope of a current's variation  $\Delta I_{min}$ Minimum current variation  $\Delta T_C$ Case temperature swing  $\Delta T_I$ Junction's temperature swing

Difference between the junction and the ambient temperatures  $\Delta T_{IA}$

$\Delta T_{J_D}$ Diode's  $T_I$  swing on a fundamental period  $\Delta T_{J_T}$ Transistor's  $T_I$  swing on a fundamental period

Time step  $\Delta t$

$D_w$ Diameter of the wire bonding  $dZ_{th}$ Derivative of the thermal impedance

Ε DC-link voltage  $E_{off}$ Turn-off energy losses Turn-on energy losses  $E_{on}$

Diode's reverse recovery energy losses  $E_{rec}$ IGBT's threshold forward voltage  $E_T$

Diode's threshold voltage  $E_0$

Flux density φ

$f_{out}$ Fundamental frequency Switching frequency  $f_{sw}$ Power Switch's total current

Current per wire bonding  $I_B$ Collector-emitter cut-off current  $I_{CE_S}$ Current produced during clear sky  $I_{Clear}$ IGBT's rated collector current

Drain current  $I_D$

$I_{C_r}$

Direct off-state current  $I_{D_D}$

MOSFET's rated drain current  $I_{Dr}$

Drain leakage current  $I_{DSS}$

Diode's mean forward current  $I_{f_M}$ IGBT's Gate leakage current  $I_{GE\varsigma}$ MOSFET's gate leakage current  $I_{GSS}$

Gate trigger current  $I_{GT}$

Low current injected during TSEP measurement  $I_m$ Maximum value of an RMS current's profile  $I_{MAX}$

Direct reverse current  $I_{RD}$ Transistor's current  $I_T$ J Current density L Load inductance Thermal conductivity  $\lambda_{th}$ PWM modulation depth mN Number of temperature cycles

P Power losses

p P power spectral density

Diode's total average conduction losses  $P_{condD}$

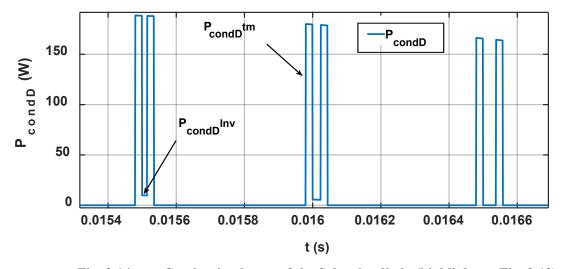

Diode's average conduction losses during MOSFET's conduction phase in  $P_{condD}Inv$

the 3<sup>rd</sup> quadrant

Diode's average conduction losses during dead time  $P_{condD}tm$

Transistor's average conduction losses  $P_{condT}$ Power losses at thermal equilibrium  $P_h$ Power losses during TSEP measurement  $P_m$

$P_{off}$ Turn-off power losses

$P_{off_l}$ Turn-off power losses of low side transistor

Turn-on power losses  $P_{on}$

Turn-on power losses of low side transistor  $P_{on_l}$ Reverse recovery losses of high side diode  $P_{rech}$

Diode's average switching losses  $P_{SWD}$  $P_{SWT}$ Transistor's average switching losses Diode's total average power losses  $P_{tot}$ Transistor's total average power losses  $P_{tot\, T}$

$r_d$ Dynamic resistance

$R_{DSon}$ Drain-source on-state resistance

Internal gate resistance  $R_{g_{on}}/R_{g_{off}}$ External gate resistances

$R_{th}$ Thermal resistance

$R_{th_{IC}}$ Junction-Case thermal resistance

Electrical conductivity

t Time

TTemperature

$T_a \over T_a T_a max$ **Ambient Temperature**  $T_a$  power spectral density

Maximum ambient temperature value  $T_amin$ Minimum ambient temperature value

Case temperature  $T_{\mathcal{C}}$ High side transistor  $T_h$  $T_H$ Heat sink's temperature Heat sink's time constant  $\tau_H$  $T_{J}$ Junction temperature  $T_I$  power spectral density

$T_{I_D}$  max Diode's maximum  $T_I$  on a fundamental period  $T_{J_D}min$ Diode's minimum  $T_I$  on a fundamental period  $T_{J_h}$ Junction temperature at thermal equilibrium

$T_{J_T} max$ Transistor's maximum  $T_I$  on a fundamental period  $T_{J_T}min$  Transistor's minimum  $T_J$  on a fundamental period

$T_{J_m}$  Instantaneous junction temperature estimated by measuring the TSEP

$T_{J_M}$  Mean junction temperature  $T_{J_{max}}$  T<sub>J</sub> of the hottest power module

$T_{J_{MAX}}$  Maximum  $T_J$  given in a power module's datasheet

$T_{J_{min}}$  Cycle's minimal value  $T_l$  Low side transistor

$t_m$  Dead time

$T_{off}$  Power-off-time during power cycling  $T_{on}$  Power-on-time during power cycling

T<sub>out</sub> Fundamental period

$t_p$  Time delay between two consecutive ageing profiles

$t_{rr}$  Reverse recovery time  $T_{sw}$  Switching period V Electrical potential

$V_{bus}$  Voltage measured across the DC bus

$V_C$  Blocking voltage rating  $V_{ce}$  Collector-emitter voltage

$V_{ce_{sat}}$  Collector-emitter saturation voltage  $V_{ce_{th}}$  Collector-emitter threshold voltage

V<sub>d</sub> PWM delta-shaped voltage

$\widehat{V_d}$  Fundamental amplitude of the PWM delta-shaped voltage

$V_{dr}$  Driver's voltage  $V_{DS}$  Drain-source voltage

$V_{DS_h}$  Drain-source voltage measured across high side transistor  $V_{DS_l}$  Drain-source voltage measured across low side transistor

$V_f$  Diode's forward voltage  $V_{ge}$  Gate-emitter voltage  $V_{GS}$  Gate-source voltage

$V_{GS_{th}}$  Gate-source threshold voltage

$V_{GT}$  Gate trigger voltage  $V_{isol}$  Isolation test voltage

V<sub>L</sub> Inverter's output AC voltage

$\widehat{V_L}$  Fundamental amplitude of the inverter's output AC voltage

$V_{ref}$  PWM Sinusoidal reference voltage

$\widehat{V_{ref}}$  Fundamental amplitude of the PWM sinusoidal reference voltage

$V_{SD}$  MOSFET's body diode forward voltage

$Z_{ii}$  Junction-Ambient self-heating thermal impedance of device  $D_i$   $Z_{ji}$  Mutual thermal coupling impedance between devices  $D_i$  and  $D_i$

$Z_{th}$  Thermal impedance

$Z_{th_{CH}}$  Case-Heat sink thermal impedance  $Z_{th_{JC}}$  Junction-Case thermal impedance  $Z_{th_{HA}}$  Heat sink-Ambient thermal impedance

## **Table of Contents**

| Introduction                                                                             | 29 |

|------------------------------------------------------------------------------------------|----|

| Chapter 1: State of art and proposed approach                                            | 34 |

| 1.1. Introduction                                                                        | 34 |

| 1.2. Semiconductor power modules' main failure mechanisms                                | 34 |

| 1.2.1. Semiconductor power module structure                                              | 34 |

| 1.2.2. Chip-related main failure mechanisms                                              | 36 |

| 1.2.2.1. Si IGBT                                                                         | 36 |

| 1.2.2.2. SiC MOSFET                                                                      | 37 |

| 1.2.2.2.1. Gate threshold voltage $V_{GS_{th}}$ instability                              | 37 |

| 1.2.2.2.2. Gate oxide cracks and breakdown                                               | 40 |

| 1.2.2.2.3. Single-event-gate-rupture (SEGR)                                              | 40 |

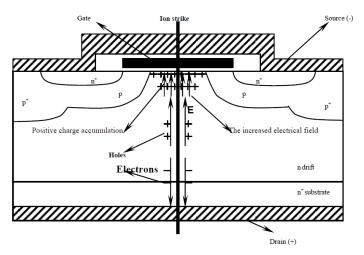

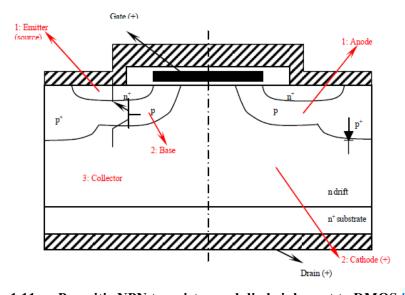

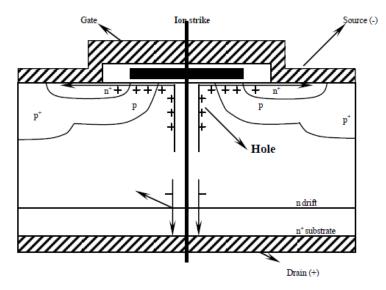

| 1.2.2.2.4. Activation of parasitic bipolar junction transistor (BJT) in SiC power MOSFET | 41 |

| 1.2.2.2.5. Single-event-burnout (SEB)                                                    | 42 |

| 1.2.2.2.6. Parasitic diode avalanche breakdown                                           | 43 |

| 1.2.2.2.7. Body diode switching failure                                                  | 43 |

| 1.2.3. Packaging-related main failure mechanisms                                         | 44 |

| 1.2.3.1. Bond wire fatigue                                                               | 44 |

| 1.2.3.1.1. Bond wire lift off                                                            | 44 |

| 1.2.3.1.2. Bond wire heel crack                                                          | 45 |

| 1.2.3.2. Aluminum metallization reconstruction                                           | 45 |

| 1.2.3.3. Corrosion of interconnections                                                   | 46 |

| 1.2.3.4. Solder fatigue                                                                  | 47 |

| 1.2.3.4.1. Solder fatigue in chip soldering                                              | 47 |

| 1.2.3.4.2. Solder fatigue on the base plate                                              | 48 |

| 1.2.3.5. Brittle cracking                                                                | 49 |

| 1.3. Main accelerated ageing tests                                                       | 50 |

| 1.3.1. Reliability tests categories                                                      | 50 |

| 1.3.2. AEC-Q101 and IEC 62093 Ed.2 stress based qualification tests                      | 50 |

| 1.3.3. SiC MOSFET VGS <sub>th</sub> instability testing                                  | 51 |

| 1.3.3.1. Static gate oxide ageing test applying high temperature steps                   |    |

| 1.3.3.2. HTGB test with increasing stress time                                           | 52 |

| 1.3.3.3. HTGB test with fix stress time                                         | 53 |

|---------------------------------------------------------------------------------|----|

| 1.3.4. A review of power cycling's state of art                                 | 53 |

| 1.3.4.1. Active Power Cycling (APC)                                             | 53 |

| 1.3.4.2. Control strategies                                                     | 54 |

| 1.3.4.3. Type of APC tests                                                      | 55 |

| 1.3.4.3.1. DC current source                                                    | 55 |

| 1.3.4.3.2. Full-bridge inverter with inductive load                             | 56 |

| 1.3.4.3.3. Inverter-inverter back-to-back                                       | 57 |

| 1.3.4.4. Review of APC tests                                                    | 58 |

| 1.4. Condition monitoring and failure indicators in APC tests                   | 59 |

| 1.4.1. Voltages                                                                 | 59 |

| 1.4.2. Thermal resistance and impedance                                         | 60 |

| 1.4.3. Currents                                                                 | 61 |

| 1.5. Conclusions and proposed approach                                          | 63 |

| Chapter 2: Power losses estimation                                              | 67 |

| 2.1. Introduction                                                               | 67 |

| 2.2. Intersective Pulse Width Modulation (PWM)                                  | 68 |

| 2.3. Conduction losses estimation                                               | 70 |

| 2.3.1. Case of IGBT power modules                                               | 70 |

| 2.3.1.1. Operation in the first quadrant (IL > 0 and $0 \le t \le \alpha Tsw$ ) | 70 |

| 2.3.1.2. Operation in the third quadrant (IL < 0 and $0 \le t \le \alpha Tsw$ ) | 71 |

| 2.3.1.3. IGBT's conduction losses                                               | 71 |

| 2.3.1.4. Diode's conduction losses                                              | 71 |

| 2.3.1.5. Electro-thermal coupling                                               | 72 |

| 2.3.2. Case of SiC MOSFET power modules                                         | 73 |

| 2.3.2.1. Operation in the first quadrant (IL > 0 and $0 \le t \le \alpha Tsw$ ) | 73 |

| 2.3.2.2. Operation in the third quadrant (IL < 0 and $0 \le t \le \alpha Tsw$ ) | 73 |

| 2.3.2.3. MOSFET's conduction losses                                             | 76 |

| 2.3.2.4. Diode's conduction losses                                              | 77 |

| 2.3.2.5. Electro-thermal coupling                                               | 78 |

| 2.4. Switching losses estimation                                                | 79 |

| 2.4.1. Extraction of datasheet's switching losses                               | 79 |

| 2.4.1.1. Transistor's turn-on and turn-off energy losses                        | 79 |

| 2.4.1.2. Diode's reverse recovery energy                                        | 80 |

| 2.4.2. Switching losses measurement using double pulse test                     | 81 |

| 2.4.2.1. Justification for the use                                      | 81  |

|-------------------------------------------------------------------------|-----|

| 2.4.2.2. Test's description                                             | 82  |

| 2.4.2.3. Test's application                                             | 83  |

| 2.4.2.3.1. Voltage probe's bandwidth                                    | 83  |

| 2.4.2.3.2. The current measurement method                               | 84  |

| 2.4.2.3.3. Eliminating the skew between probes                          | 85  |

| 2.4.2.3.4. The test bench                                               | 85  |

| 2.4.2.4. Results                                                        | 86  |

| 2.4.3. Case of a PWM voltage inverter                                   | 90  |

| 2.4.3.1. The transistor's switching losses                              | 90  |

| 2.4.3.2. The diode's losses                                             | 91  |

| 2.5. Validation                                                         | 91  |

| 2.5.1. Case of IGBT power modules                                       | 91  |

| 2.5.2. Case of MOSFET power modules                                     | 94  |

| 2.6. Conclusions                                                        | 95  |

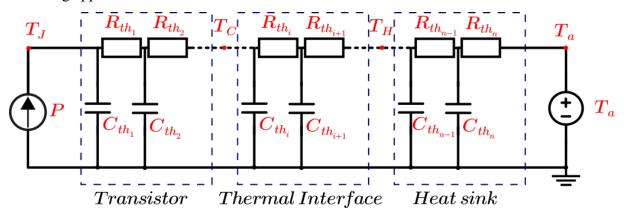

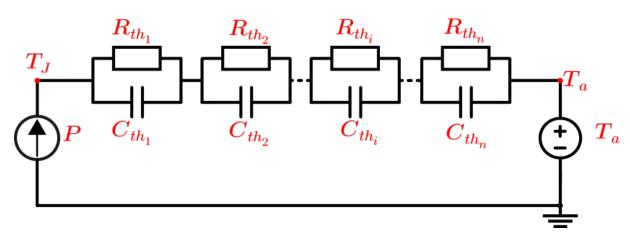

| Chapter 3: Construction, evaluation and identification of thermal model | s97 |

| 3.1. Introduction                                                       | 97  |

| 3.2. Basics of power assemblies' thermal modeling                       | 97  |

| 3.2.1. Equivalence between thermal and electrical parameters            | 97  |

| 3.2.2. Cauer and Foster networks                                        | 99  |

| 3.2.3. Thermal coupling between several chips                           | 102 |

| 3.3. Junction temperature calculation methods                           | 102 |

| 3.3.1. Time-Domain Estimation                                           | 103 |

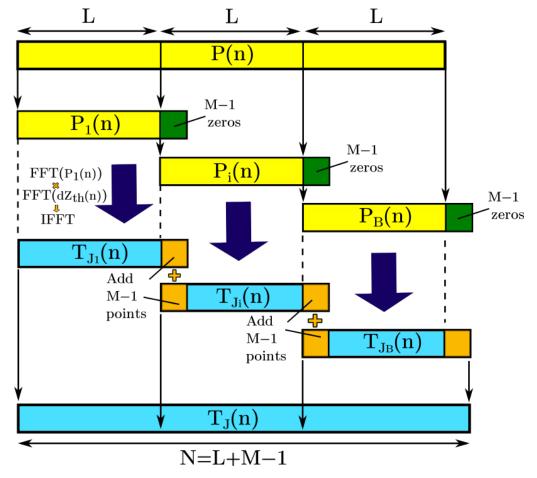

| 3.3.2. Fast Fourier Transform FFT                                       | 103 |

| 3.3.3. FFT with Overlap-Add method                                      | 104 |

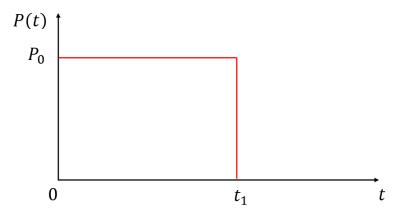

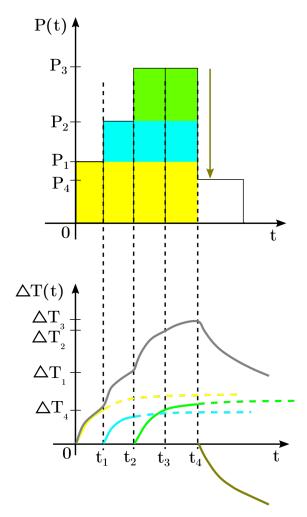

| 3.3.4. Breaking down the mission profile into single pulses             | 106 |

| 3.3.5. Analytical solution                                              | 108 |

| 3.3.6. Comparison between the methods                                   | 109 |

| 3.4. Models validation                                                  | 110 |

| 3.4.1. Case of IGBT power modules                                       | 110 |

| 3.4.2. Case of MOSFET power modules                                     | 113 |

| 3.5. Self-heating and mutual thermal coupling impedances measurements   | 114 |

| 3.5.1. Justification for measurement tests                              | 114 |

| 3.5.2. Choice of the measurement method                                 | 114 |

| 3.5.3. Choice of the TSEP                                               | 115 |

| 3.5.4. $Z_{th}$ measurement with TSEPs: methodology and tests               | 115 |

|-----------------------------------------------------------------------------|-----|

| 3.5.4.1. Calibration of the TSEP as a function of the temperature           | 115 |

| 3.5.4.2. High current injection and temperature measurement                 | 117 |

| 3.5.4.3. Temperature estimation during cooling                              | 120 |

| 3.5.5. Results                                                              | 121 |

| 3.5.5.1. Results of the thermal impedances measurements and fitting         | 121 |

| 3.5.5.2. Estimating the junction temperature                                | 122 |

| 3.6. Conclusions                                                            | 123 |

| Chapter 4: Accelerated ageing methodology: from mission profiles to semicon |     |

| accelerated ageing tests                                                    | 126 |

| 4.1. Introduction                                                           | 126 |

| 4.2. Methodology for accelerated ageing profiles generation                 |     |

| 4.2.1. Analysis of photovoltaics' mission profiles                          |     |

| 4.2.1.1. The shape of the current                                           | 128 |

| 4.2.1.2. The diffuse current                                                | 129 |

| 4.2.1.3. The slope of the current variations                                | 129 |

| 4.2.1.4. Delays between the current variations                              | 130 |

| 4.2.1.5. Seasons                                                            | 131 |

| 4.2.1.6. Ambient Temperature                                                | 133 |

| 4.2.2. 1 <sup>st</sup> method: Generating maximum variations                | 133 |

| 4.2.2.1. Building the accelerated ageing profile                            | 133 |

| 4.2.2.2. Determining the profile parameters                                 | 135 |

| 4.2.2.2.1. Case Study                                                       | 135 |

| 4.2.2.2.2. Power losses and thermal models                                  | 135 |

| 4.2.3. 2 <sup>nd</sup> method: Regenerating real variations                 | 136 |

| 4.3. Evaluation and comparison                                              | 138 |

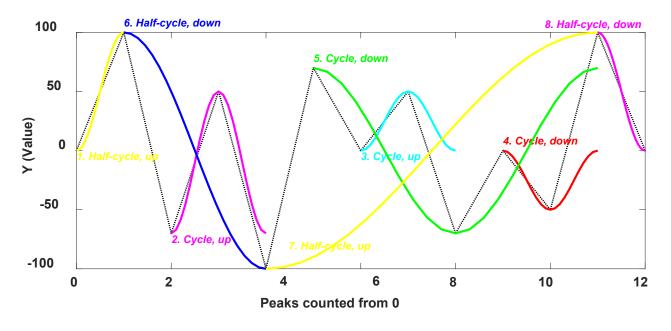

| 4.3.1. "Rainflow" counting algorithm                                        | 138 |

| 4.3.2. Comparison between different methods                                 | 141 |

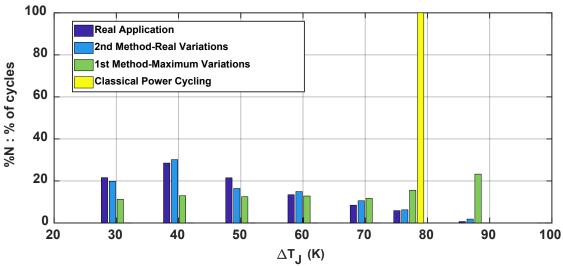

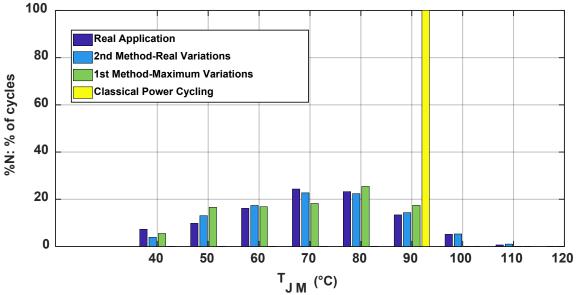

| 4.3.2.1. $\Delta TJ$ and $TJ_M$ distributions                               | 141 |

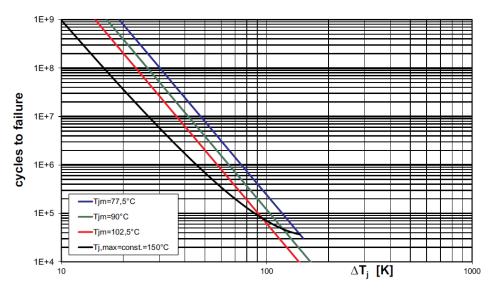

| 4.3.2.2. Tests duration and acceleration factors                            | 143 |

| 4.4. Design of the ageing tests profiles                                    | 144 |

| 4.4.1. Case of IGBT power modules                                           | 144 |

| 4.4.2. Case of SiC MOSFET power modules                                     | 147 |

| 4.5 Conclusions                                                             | 147 |

| Chapter 5: SiC MOSFET's accelerated ageing tests                               | 150     |

|--------------------------------------------------------------------------------|---------|

| 5.1. Introduction                                                              | 150     |

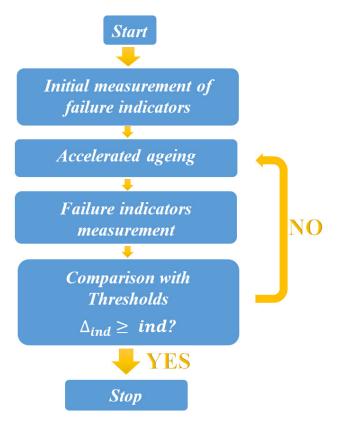

| 5.2. Tests' methodology                                                        | 150     |

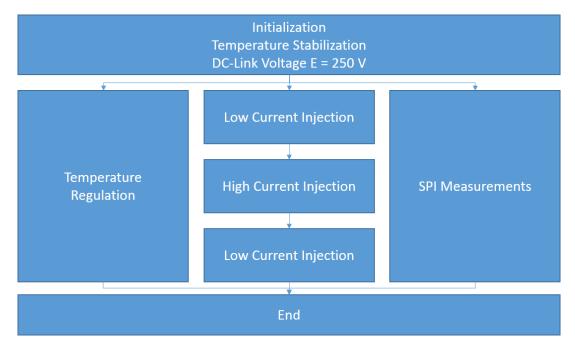

| 5.2.1. Accelerated ageing tests                                                | 150     |

| 5.2.2. Failure indicators measurement                                          | 151     |

| 5.2.2.1. Selection of failure indicators                                       | 151     |

| 5.2.2.2. Measurement methodology                                               | 152     |

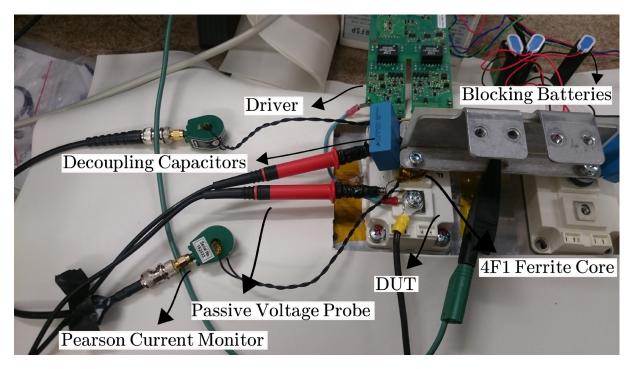

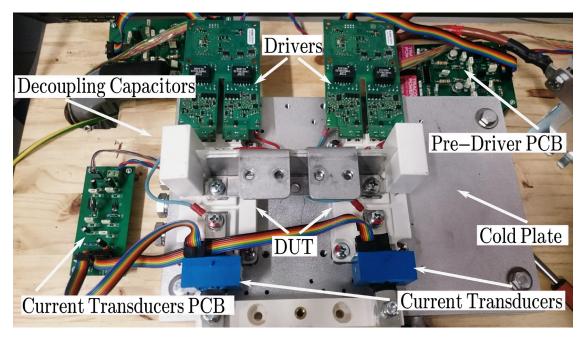

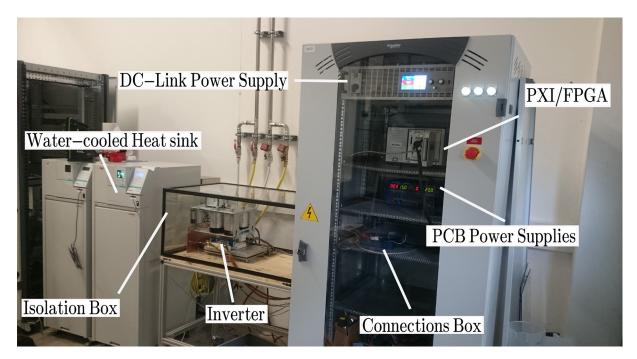

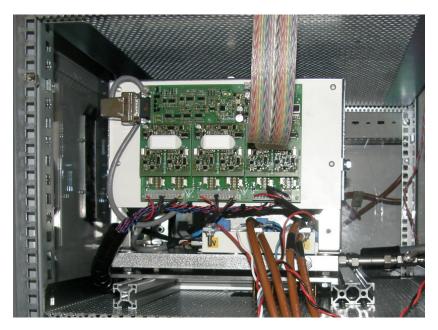

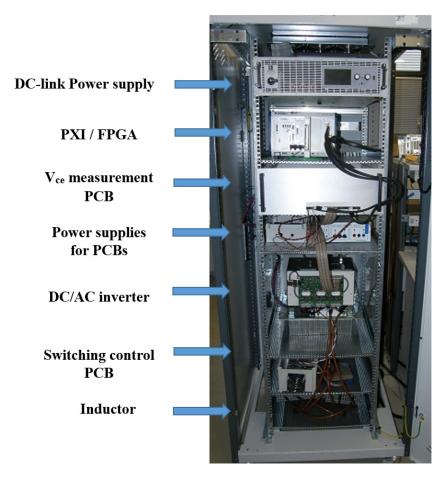

| 5.3. Test bench                                                                | 154     |

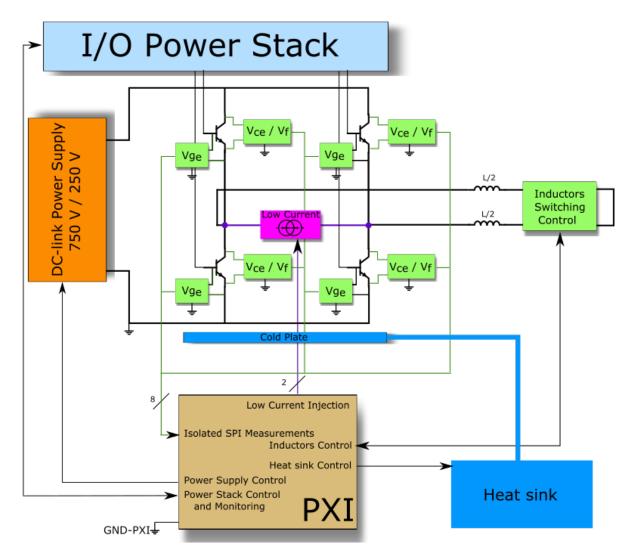

| 5.3.1. Power circuit                                                           | 154     |

| 5.3.2. PCBs design                                                             | 156     |

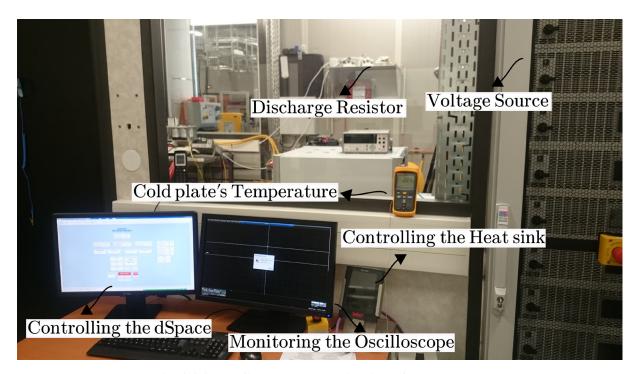

| 5.3.3. Temperature regulation system                                           | 157     |

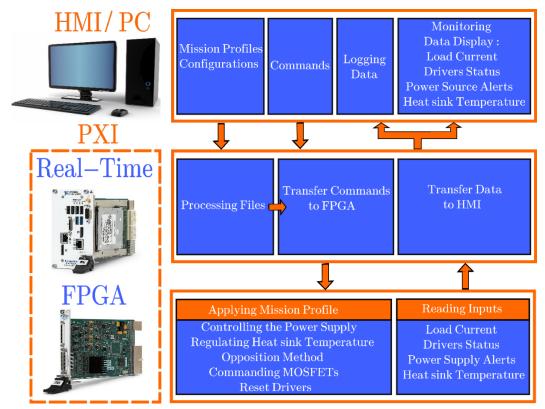

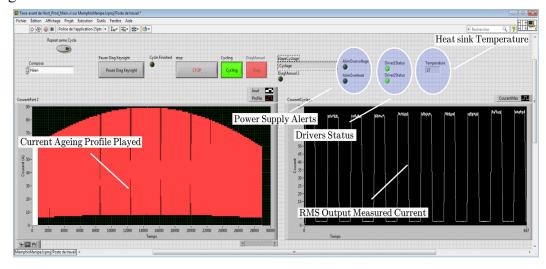

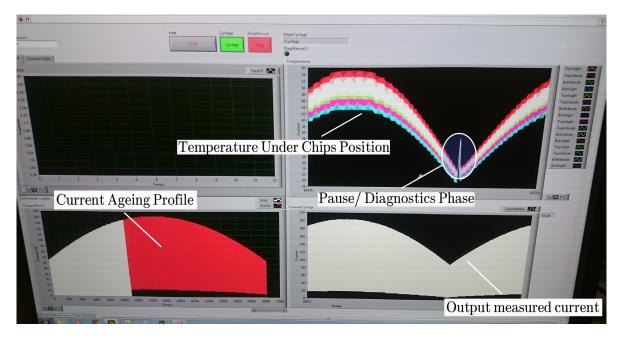

| 5.3.4. Control system                                                          | 158     |

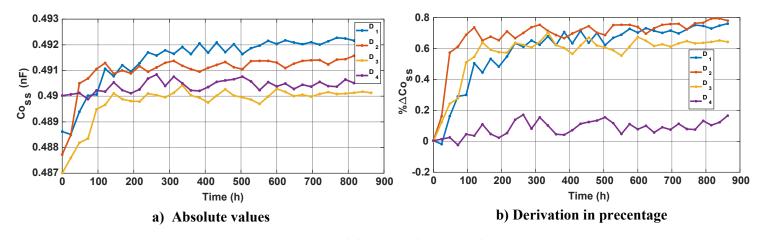

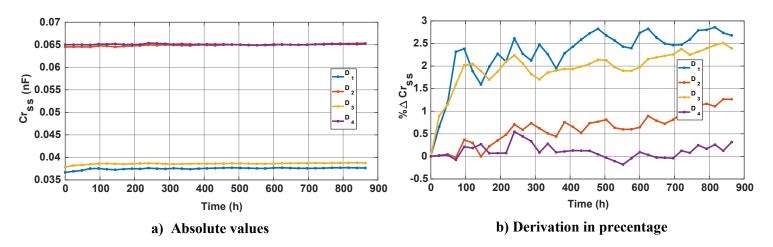

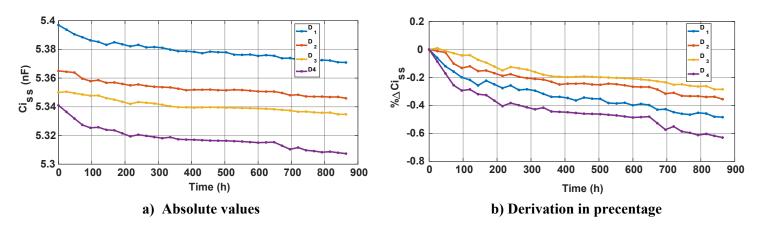

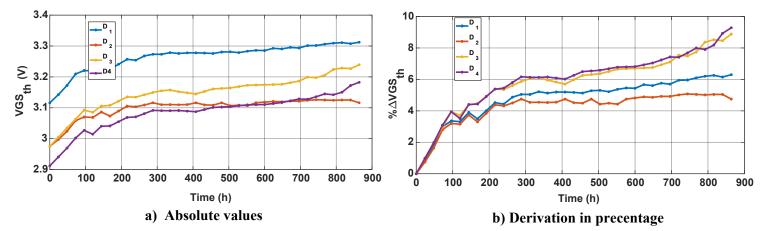

| 5.4. Ageing tests results                                                      | 160     |

| 5.5. Conclusions                                                               | 165     |

| Chapter 6: In-situ condition monitoring system and IGBT accelerated ageing te  | sts 169 |

| 6.1. Introduction                                                              | 169     |

| 6.2. In-situ condition monitoring methodology                                  | 169     |

| 6.2.1. General methodology                                                     | 169     |

| 6.2.2. In-situ condition monitoring                                            | 171     |

| 6.2.2.1. Parameters calculation                                                | 171     |

| 6.2.2.2. TSEP measurement and calibration                                      | 174     |

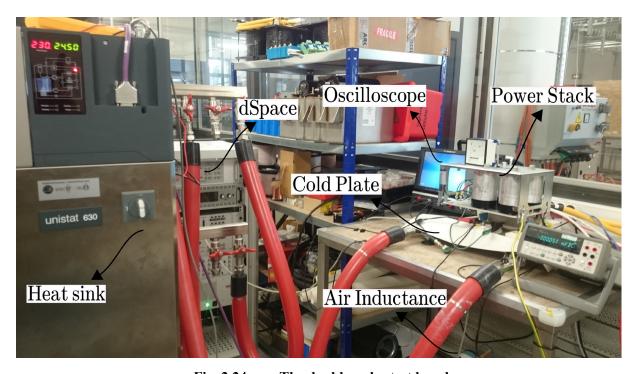

| 6.3. IGBT's test bench                                                         | 174     |

| 6.3.1. Power stack                                                             | 174     |

| 6.3.2. Measurement PCBs                                                        | 176     |

| 6.3.3. Control system and full test bench                                      | 176     |

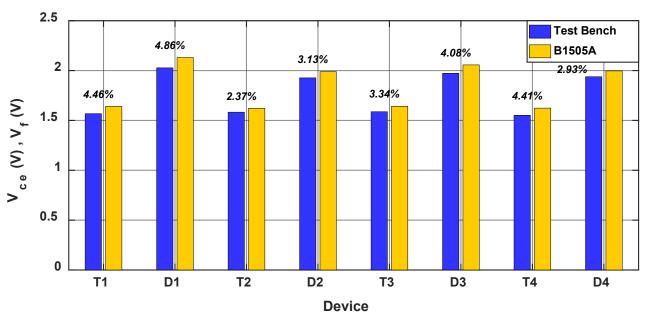

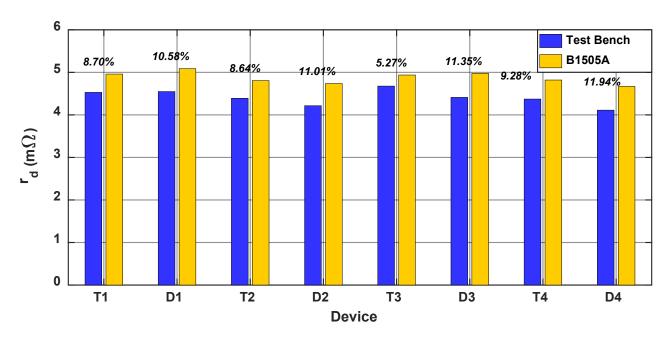

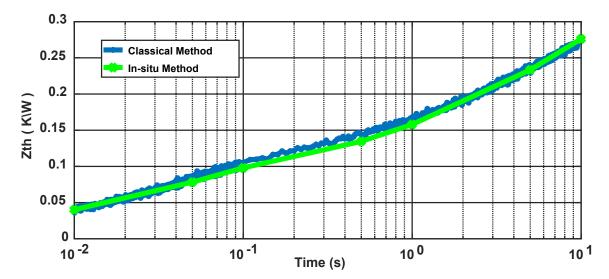

| 6.4. Validation of the in-situ condition monitoring system                     | 178     |

| 6.4.1. Validation of $V_{ce}$ , $V_f$ and $r_d$ measurements                   | 178     |

| 6.4.2. Validation of thermal impedance measurement                             | 179     |

| 6.5. Application of the accelerated ageing tests                               | 181     |

| 6.6. Implementation in a condition monitoring system of photovoltaic inverters | 183     |

| 6.7. Conclusions                                                               | 185     |

| Conclusion and Perspectives                                                    | 188     |

| References                                                                     | 192     |

# **List of Figures**

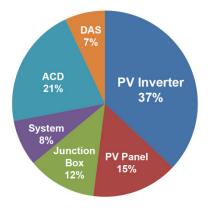

| Fig. 1:   | Unscheduled maintenance events in PV system                                        | 29     |

|-----------|------------------------------------------------------------------------------------|--------|

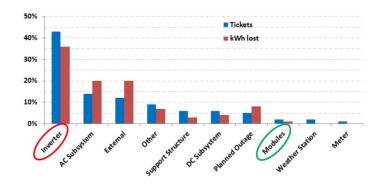

| Fig. 2:   | Frequency (%) of failure occurrences and associated energy losses                  |        |

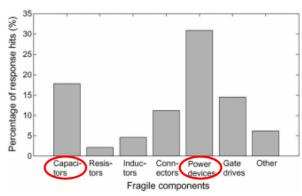

| Fig. 3:   | Percentage of failure occurrences                                                  |        |

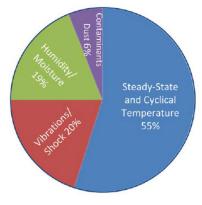

| Fig. 4:   | Source of stress distribution                                                      | 30     |

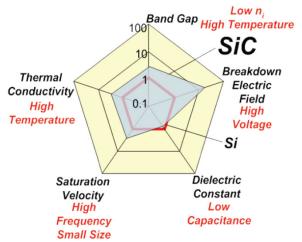

| Fig. 5:   | Diagram illustrating relative magnitudes of five properties of SiC relatively to S | i31    |

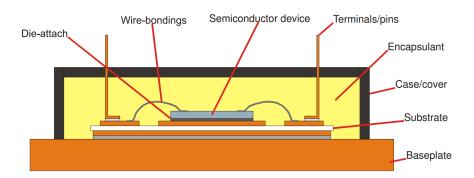

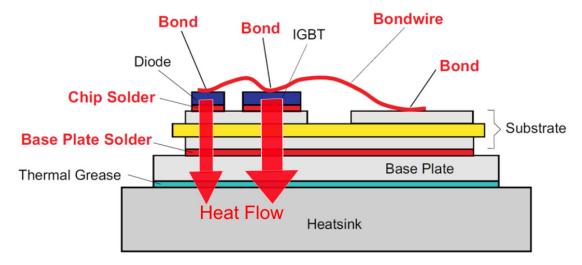

| Fig. 1.1: | Typical power electronics package structure                                        | 35     |

| Fig. 1.2: | Equivalent circuit of IGBT                                                         |        |

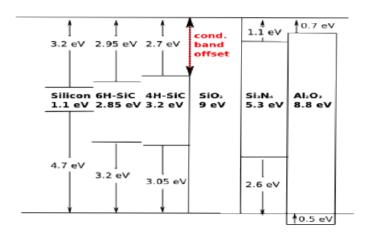

| Fig. 1.3: |                                                                                    |        |

| Fig. 1.4: | <b>.,</b>                                                                          |        |

| Fig. 1.5: |                                                                                    |        |

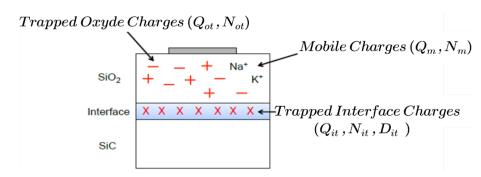

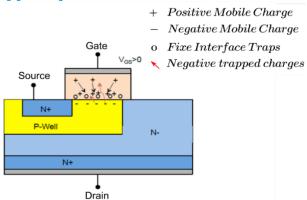

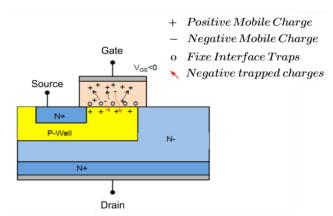

| Fig. 1.6: | Diagram of the charges in the MOSFET when a positive gate-source volta             | ige is |

| applied   | 39                                                                                 |        |

| Fig. 1.7: | Diagram of the charges in the MOSFET when a negative gate-source volta             | ige is |

| applied   | 39                                                                                 |        |

| Fig. 1.8: |                                                                                    |        |

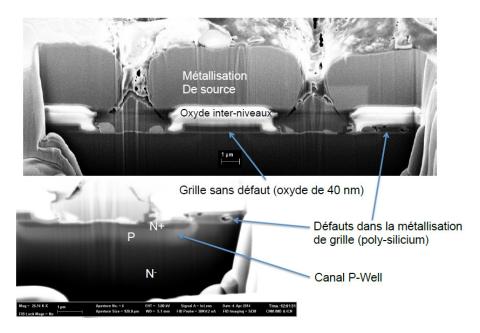

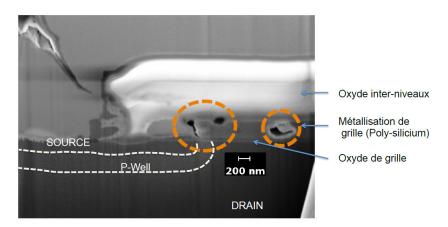

| Fig. 1.9: | SEM image of the gate's cracks                                                     | 40     |

| Fig. 1.10 |                                                                                    |        |

| Fig. 1.11 |                                                                                    |        |

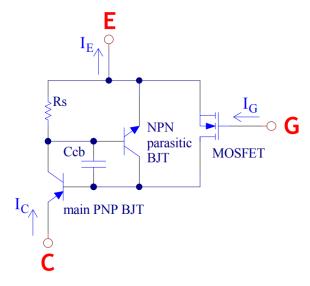

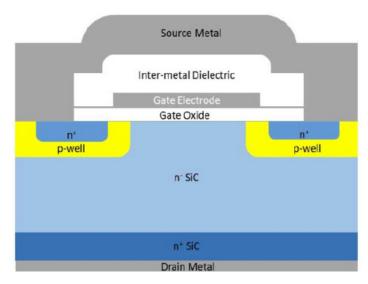

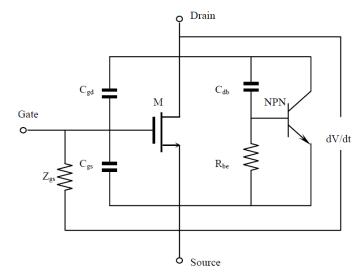

| Fig. 1.12 | Equivalent circuit of a power MOSFET                                               | 42     |

| Fig. 1.13 | : Destroyed MOSFET due to activation of the parasitic BJT                          | 42     |

| Fig. 1.14 | : SEB of MOSFET                                                                    | 43     |

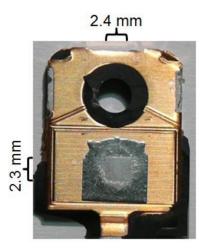

| Fig. 1.15 | : Failed SiC MOSFET power module due to body diode switching failure               | 44     |

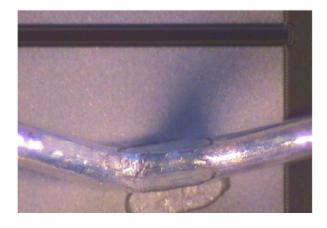

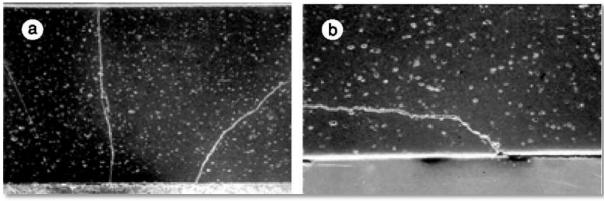

| Fig. 1.16 | Bond wire lift off (optical image)                                                 | 45     |

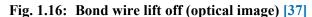

| Fig. 1.17 | ': Bond wire lift off (SEM image, x40)                                             | 45     |

| Fig. 1.1  | 8: Visualization of degradation effects inside the DUT by means of a Scar          | nning  |

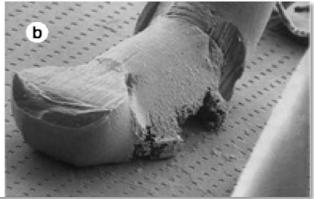

| Electron  | Microscope (SEM)                                                                   | 45     |

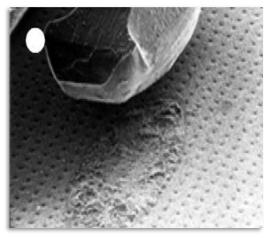

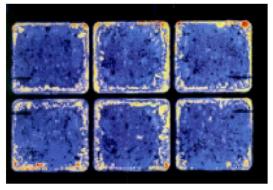

| Fig. 1.19 | 2: Aluminum metallization reconstruction                                           | 46     |

| Fig. 1.20 | Example of bond wire corrosion                                                     | 47     |

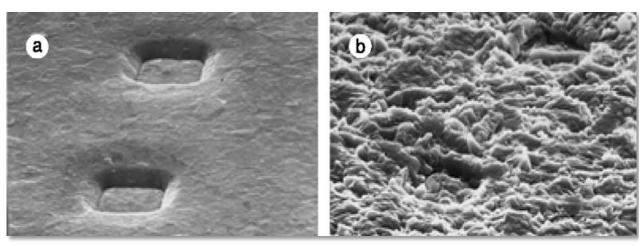

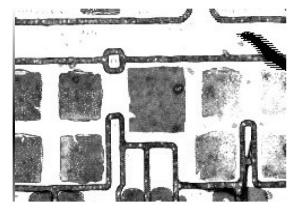

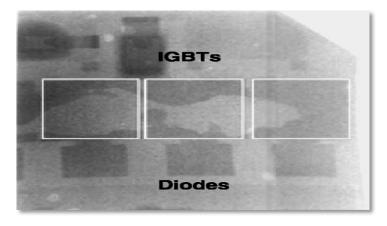

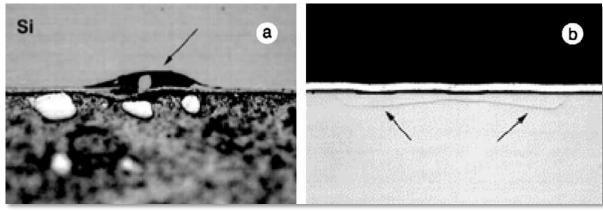

| Fig. 1.21 | : Chip solder fatigue caused by power cycling test                                 | 47     |

| Fig. 1.22 | 2: 34 mm module with torn off DBC (light-colored areas show solder fatigue)        | 48     |

| Fig. 1.23 | : AlN-module with copper baseplate after 16,000 cycles ( $\Delta Tc = 50 K$ )      | 48     |

| Fig. 1.24 | : X-ray microscopy image of an IGBT module showing a large void immedia            | iately |

|           | ree IGBT chips (0.8)                                                               |        |

|           | Example of silicon chip brittle cracking                                           |        |

|           | Example of substrate brittle cracking                                              |        |

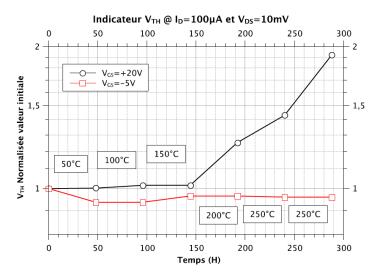

|           | : Derivation of the normalized threshold voltage for a positive and negative       |        |

|           | age                                                                                |        |

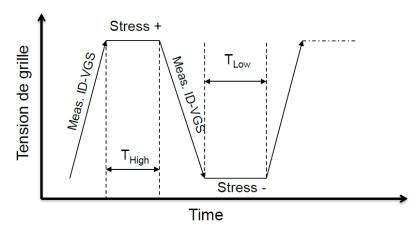

|           | : HTGB test configuration, representing the gate voltage as a function of time     |        |

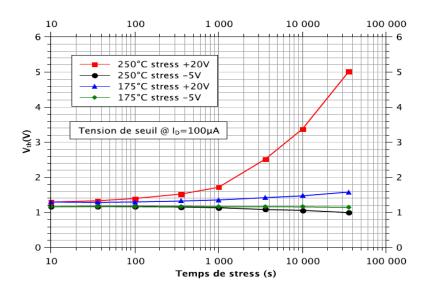

|           | : Threshold voltage evolution as a function of incrementing stress time            |        |

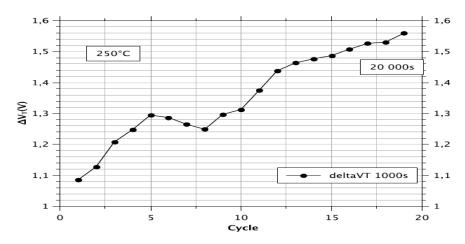

|           | : Threshold voltage's difference as a function of cycles' number                   |        |

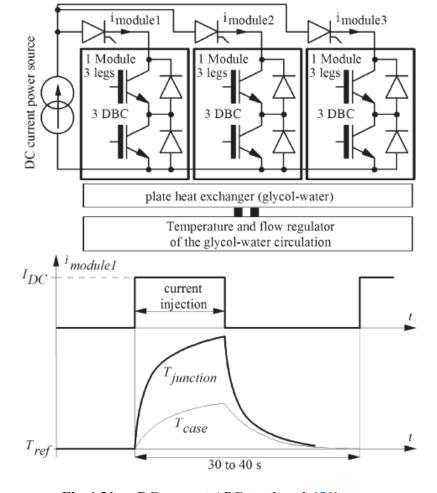

|           | : DC current APC test bench                                                        |        |

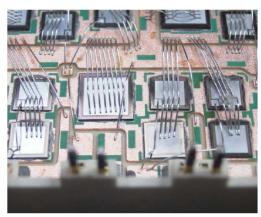

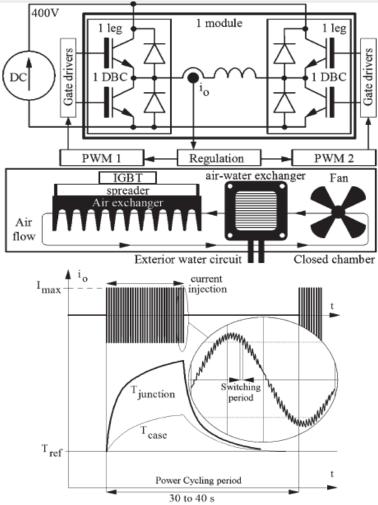

|           | Elementary block of the PWM test bench                                             |        |

|           | : Three phase back-to-back inverters test circuit                                  |        |

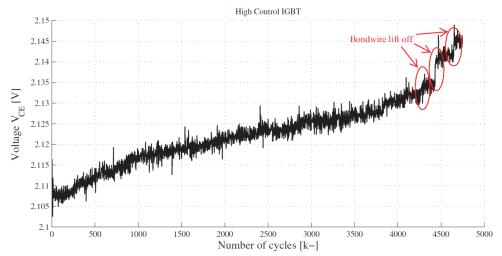

|           | : Measured <i>Vce</i> for IGBT                                                     |        |

|              | Evolution of Vce and Rth during APC test of ECONOPACK power module                           |     |

|--------------|----------------------------------------------------------------------------------------------|-----|

| -            | K                                                                                            |     |

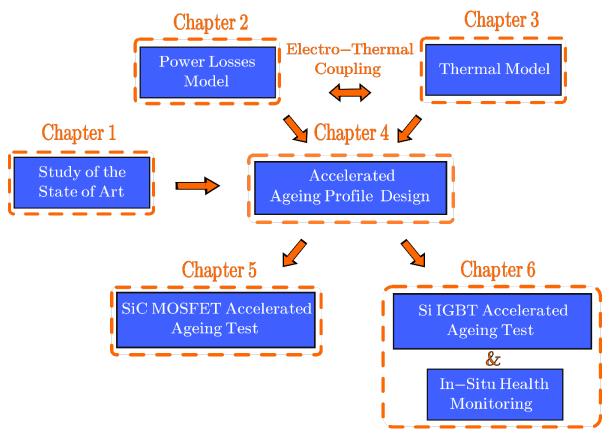

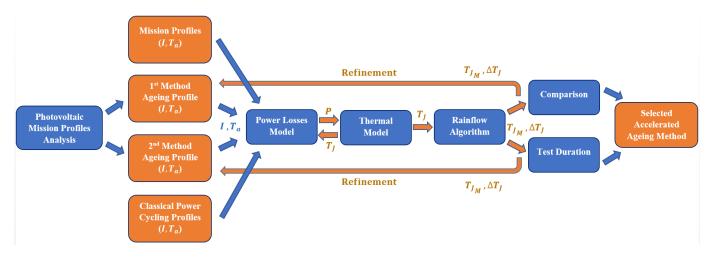

| Fig. 1.36:   | Global approach of the study                                                                 | 65  |

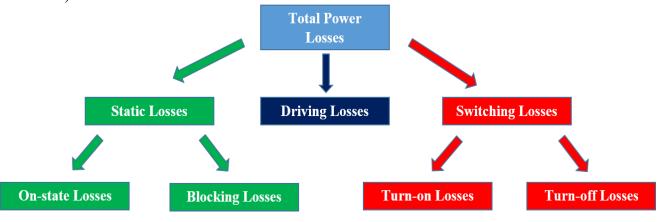

| Fig. 2.1:    | Types of power losses in IGBTs and MOSFETs                                                   | 67  |

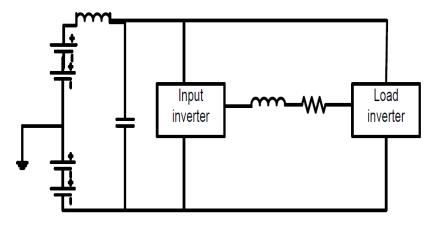

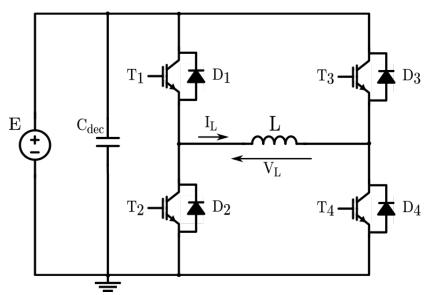

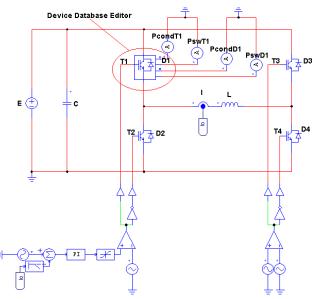

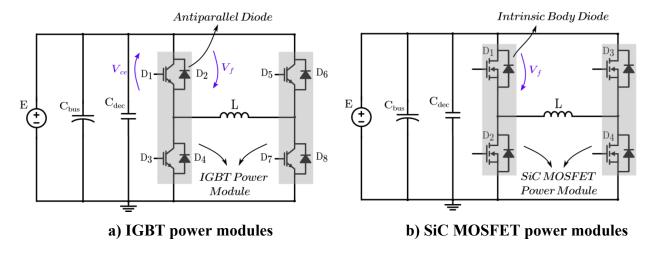

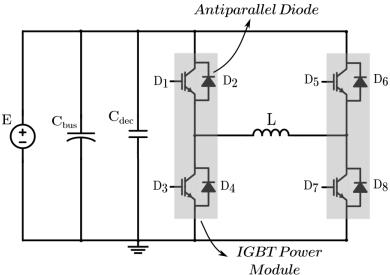

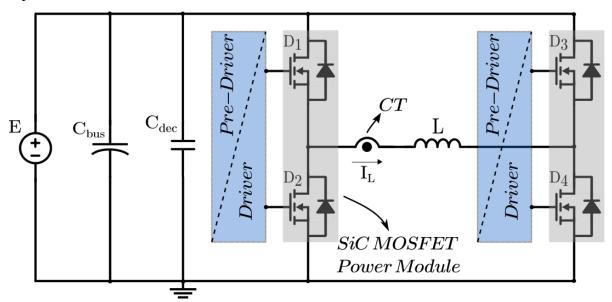

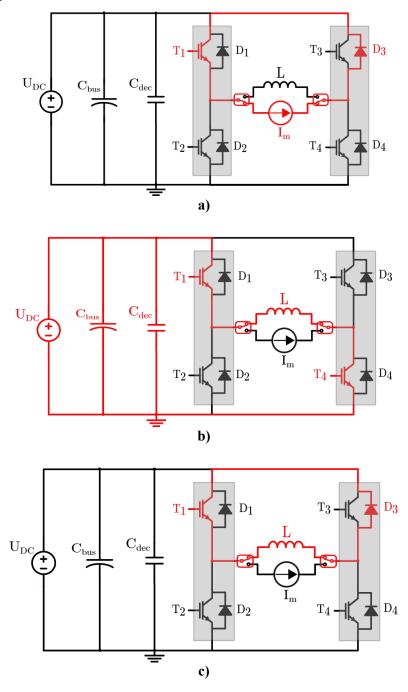

| Fig. 2.2:    | PWM two-level DC/AC voltage inverter in back-to-back configuration                           | 68  |

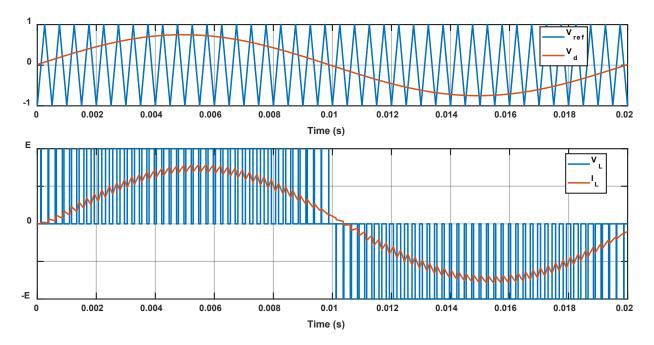

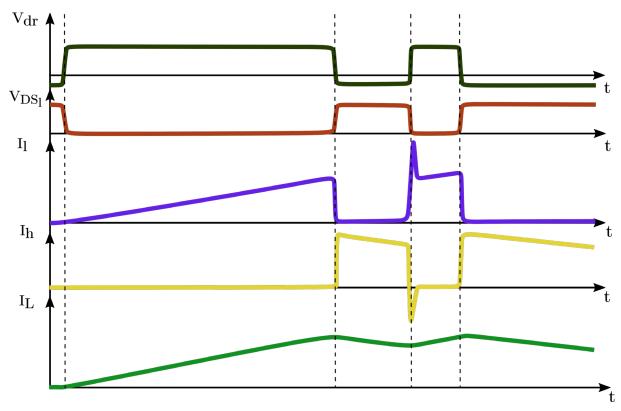

| Fig. 2.3:    | Pulse pattern generation / Load voltage and current                                          | 69  |

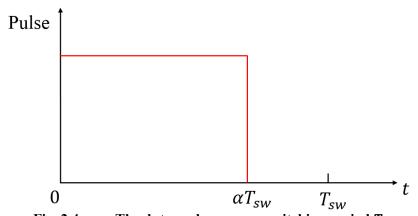

| Fig. 2.4:    | The duty cycle $\alpha$ over a switching period $Tsw$                                        | 69  |

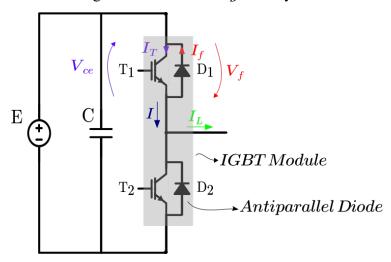

| Fig. 2.5:    | IGBT phase-leg                                                                               |     |

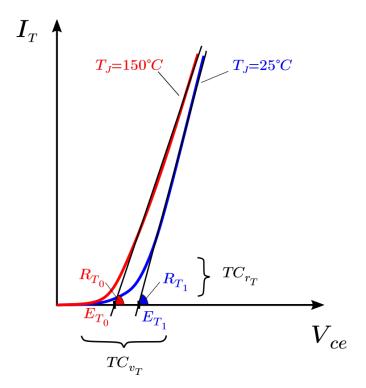

| Fig. 2.6:    | Approximation of on-state characteristic using substitutional straight lines,                | and |

| extracting ' | TCvT and TCrT                                                                                |     |

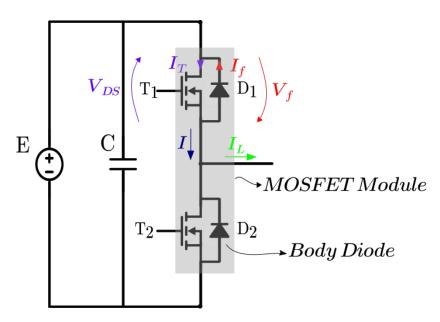

| Fig. 2.7:    | MOSFET module without antiparallel diodes                                                    |     |

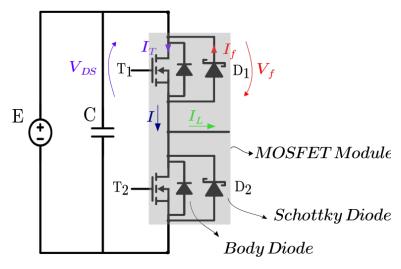

| Fig. 2.8:    | MOSFET module with antiparallel Schottky diodes                                              |     |

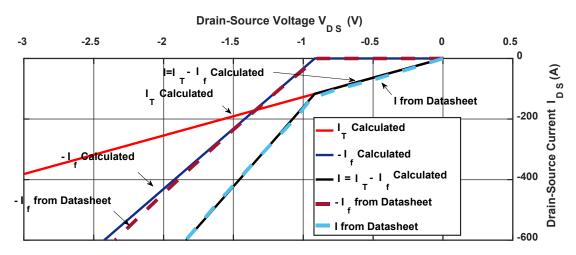

|              | Total current I, current in the transistor IT and current in the diode If,                   |     |

|              | f the drain-source voltage <i>VDS</i> from the manufacturer's datasheet                      |     |

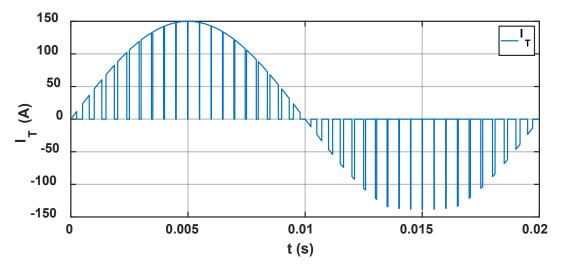

| _            | Current IT in the transistor as a function of time                                           |     |

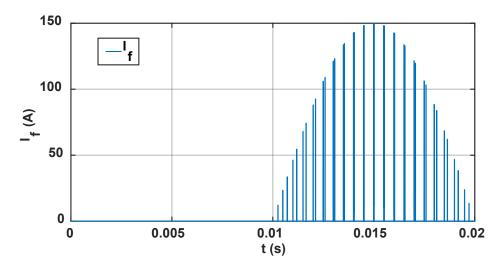

|              | Current If in the diode as a function of time                                                |     |

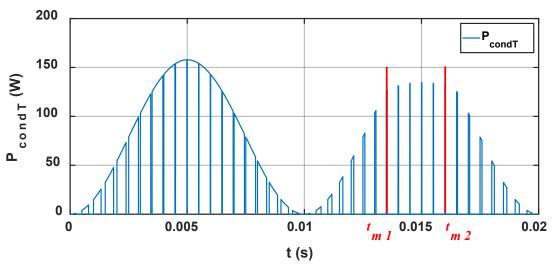

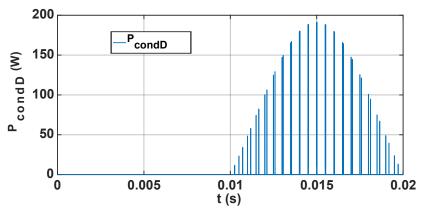

| -            | Conduction losses of the MOSFET on <i>Tout</i>                                               |     |

| _            | Conduction losses of the Schottky diode                                                      |     |

|              | Conduction losses of the Schottky diode (highlight on Fig. 2.13)                             |     |

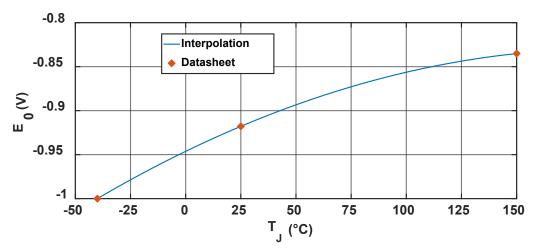

| _            | Diode's threshold voltage as a function of the junction temperature, issued from             |     |

|              | and from interpolation respectively                                                          |     |

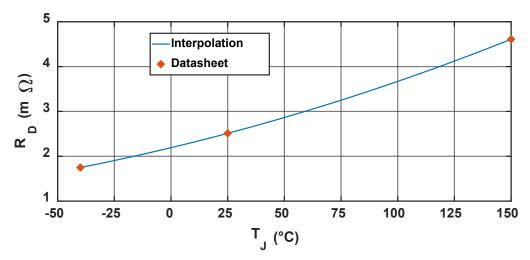

| _            | Diode's internal resistance as a function of the junction temperature, issued to             |     |

|              | eet and from interpolation respectively                                                      |     |

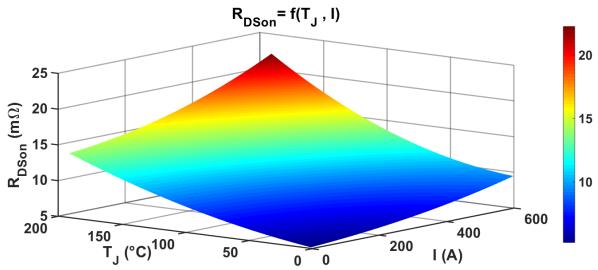

|              | On-state resistance of the MOSFET as a function of both the junction temperature             |     |

|              | rent                                                                                         |     |

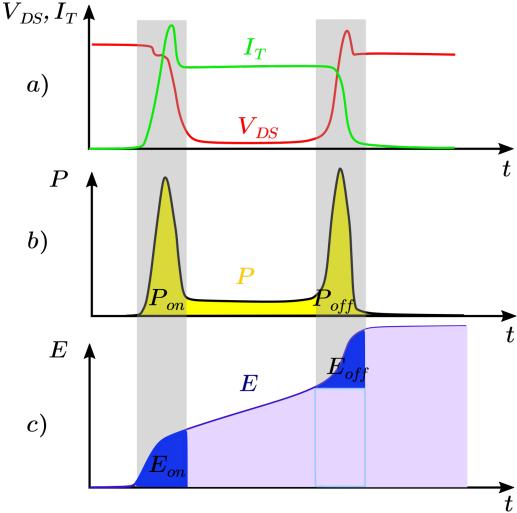

| _            | Switching Operation                                                                          |     |

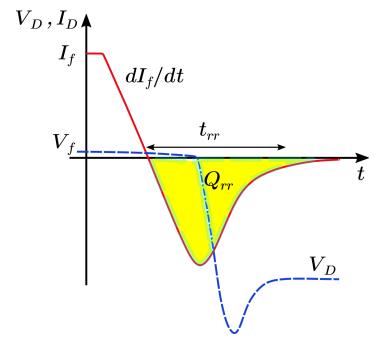

|              | The diode's reverse recovery energy                                                          |     |

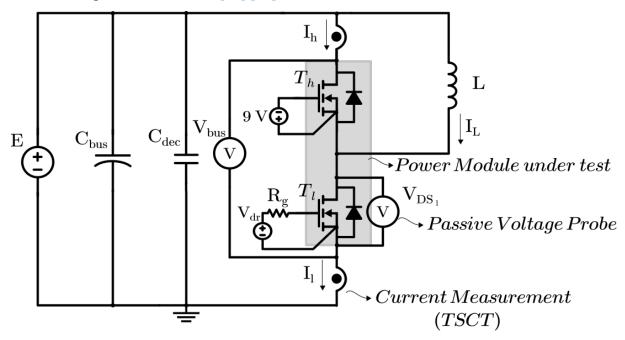

|              | The double pulse test's electrical circuit                                                   |     |

|              | The adjusted possive voltage probe                                                           |     |

| _            | The adjusted passive voltage probe  The used TSCT                                            |     |

| _            | The double pulse test bench                                                                  |     |

| _            | Highlight on the double pulse test bench                                                     |     |

|              | Control and monitoring of the test bench                                                     |     |

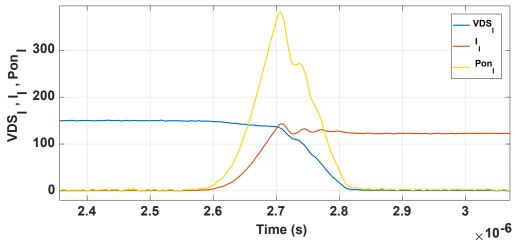

|              | The waveforms of <i>VDSl</i> , <i>Il</i> and <i>Ponl</i> as a function of time               |     |

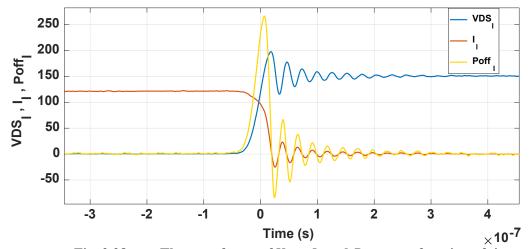

|              | The waveforms of VDSl, It and Poff l as a function of time                                   |     |

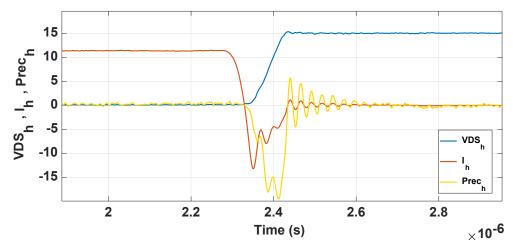

|              | The waveforms of <i>VDSt</i> , <i>It</i> and <i>Prech</i> as a function of time              |     |

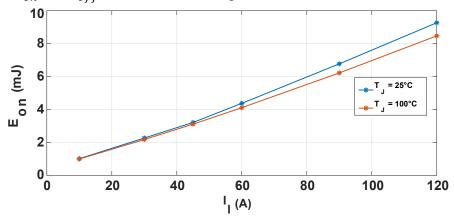

| _            | The turn-on energy losses as a function of the low side current ( $Eon = f$ )                |     |

|              | $5^{\circ}C$ and $100^{\circ}C$                                                              |     |

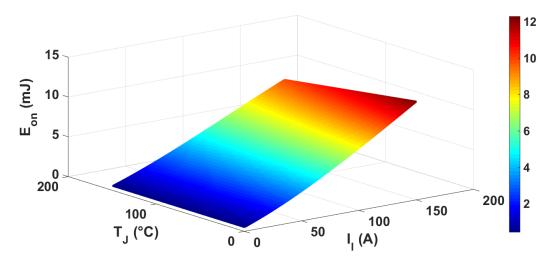

|              | The turn-on losses as a function of the low side current and the junc                        |     |

| _            | The term on rosses as a ranction of the row side eartest and the junction $E(Eo = f(Il, T])$ |     |

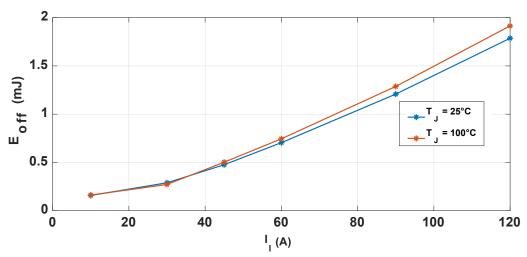

|              | The turn-off energy losses as a function of the low side current ( $Eoff = f$ )              |     |

|              | $5^{\circ}C$ and $100^{\circ}C$                                                              |     |

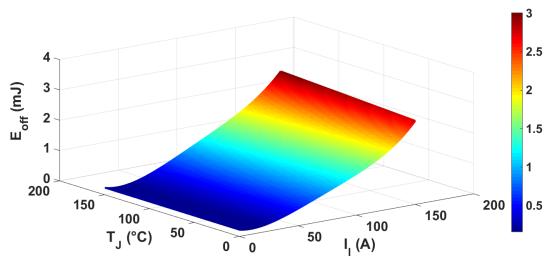

| •            | The turn-off losses as a function of the low side current and the junc                       |     |

|              | The tarm of rosses as a range of the lew state eartern and the junction $E(E) = E(E)$        |     |

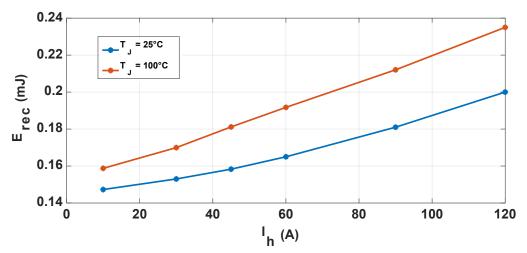

|              | The reverse recovery energy losses as a function of the high side current ( <i>Ere</i>       |     |

|              | $TI = 25^{\circ}C$ and $100^{\circ}C$                                                        |     |

|              | Switching power losses of the MOSFET on <i>Tout</i>                                          |     |

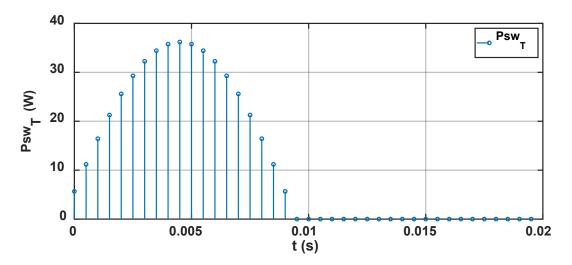

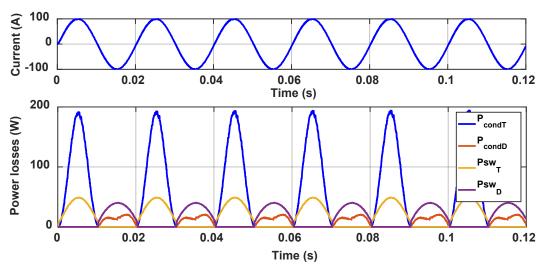

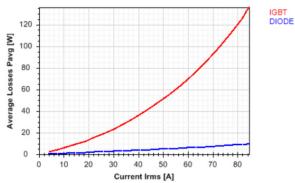

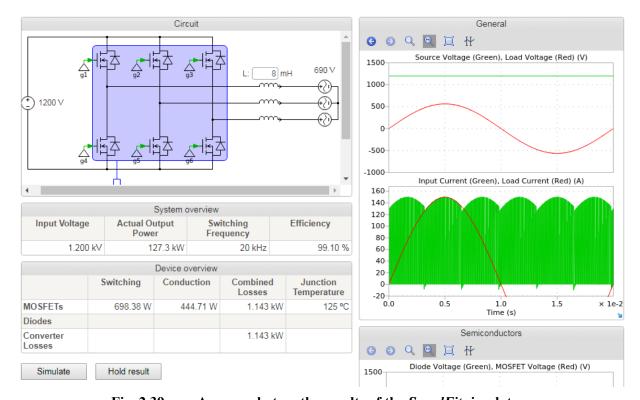

| Fig. 2.36:    | The simulation of the DC/AC inverter with <i>PSIM</i>                                   | . 92 |

|---------------|-----------------------------------------------------------------------------------------|------|

| Fig. 2.37:    | The estimated power losses with <i>PSIM</i>                                             | . 92 |

|               | The estimated power losses with <i>IPOSIM</i>                                           |      |

| -             | A screenshot on the results of the <i>SpeedFit</i> simulator                            |      |

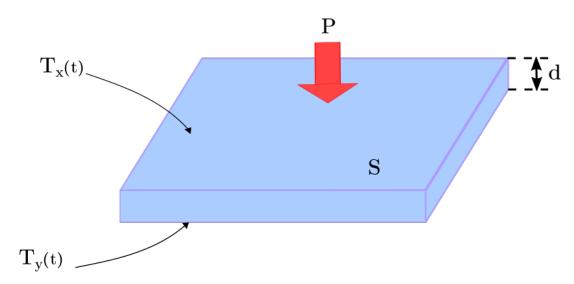

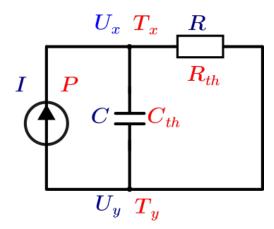

| Fig. 3.1:     | Heat conduction through a given material                                                | . 98 |

| Fig. 3.2:     | Equivalent electrical and thermal circuits                                              | . 99 |

| Fig. 3.3:     | Heat flow from the junction down towards the heat sink                                  | 100  |

| Fig. 3.4:     | Cauer network equivalent circuit                                                        |      |

| Fig. 3.5:     | Foster network equivalent circuit.                                                      |      |

| Fig. 3.6:     | Concept of the Overlap-Add method                                                       | 106  |

| Fig. 3.7:     | A single power pulse                                                                    |      |

| Fig. 3.8:     | Power losses' mission profile with the corresponding temperature variations             | 108  |

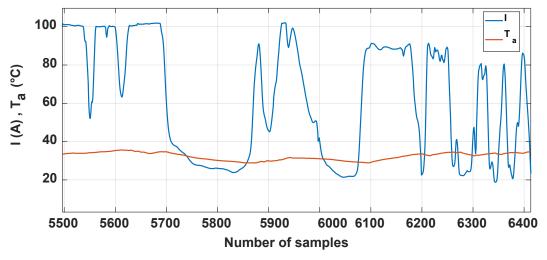

| Fig. 3.9:     | Current and ambient temperature mission profiles, used to compare the differ            |      |

| methods p     | erformance                                                                              | 109  |

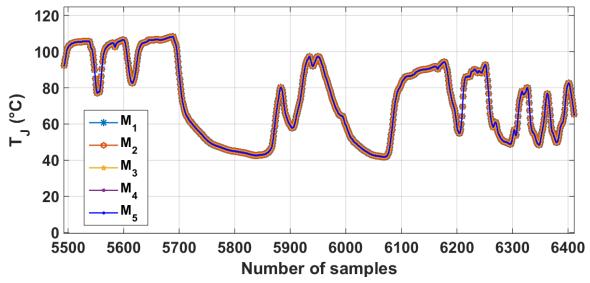

| Fig. 3.10:    | Estimated junction temperature, corresponding to the current's profile of Fig. 110      | 3.9  |

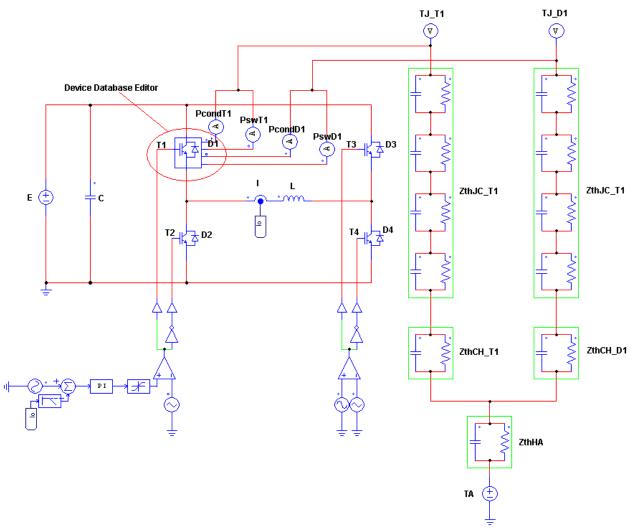

| Fig. 3.11:    | Estimating the semiconductors' junction temperature with <i>PSIM</i>                    | 111  |

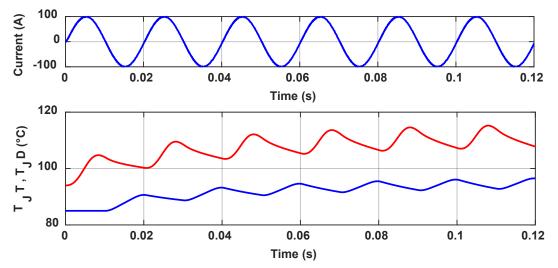

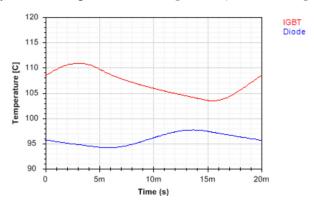

| Fig. 3.12:    | Example of the junction temperature estimation with <i>PSIM</i>                         | 111  |

| Fig. 3.13:    | An example of the junction temperature estimation on <i>Tout</i> with <i>IPOSIM</i>     | 112  |

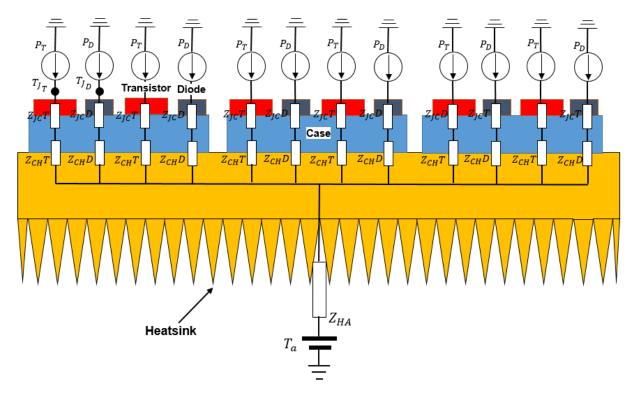

| Fig. 3.14:    | Equivalent Foster circuit of the full system                                            | 113  |

| Fig. 3.15:    | Two-level single-phase DC/AC inverters                                                  | 115  |

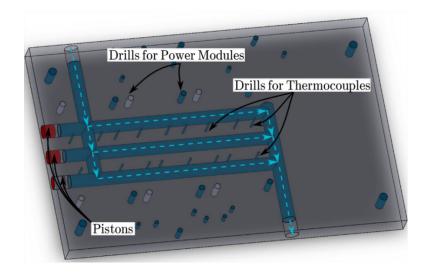

| Fig. 3.16:    | 3D geometry of the cold plates with the drilled holes for inserting                     | the  |

| thermocou     | ples                                                                                    | 116  |

| Fig. 3.17:    | Insertion of the thermocouples under the center of the chips                            | 116  |

| Fig. 3.18:    | IGBT's collector-emitter voltage $Vce$ and diode's forward voltage $Vf$ a               | ıs a |

| function of   | f the junction temperature, in the case of the IGBT power modules                       | 117  |

| Fig. 3.19:    | MOSFET body diode's forward voltage $Vf$ as a function of the junct                     | tion |

| -             | re in the case of SiC MOSFET power module                                               |      |

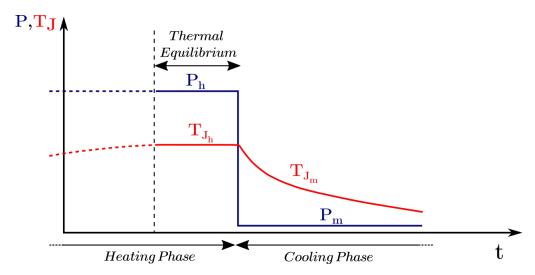

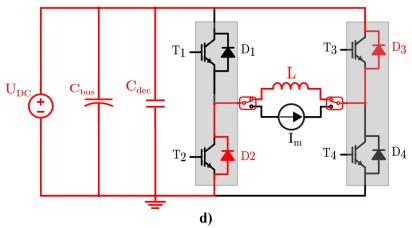

|               | Power losses and junction temperature represented as a function of time dur             |      |

|               | d cooling phases                                                                        |      |

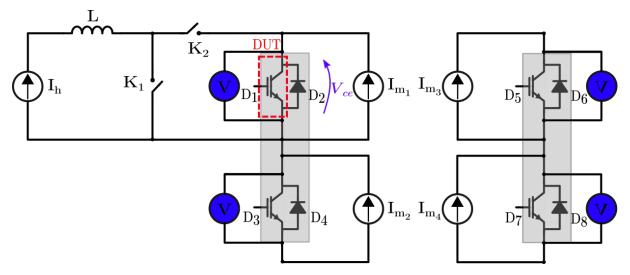

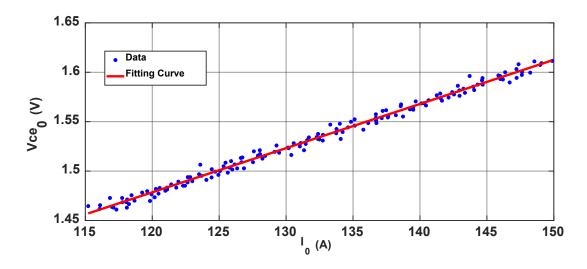

| -             | Simplified electrical circuit used for the thermal impedances measurement               |      |

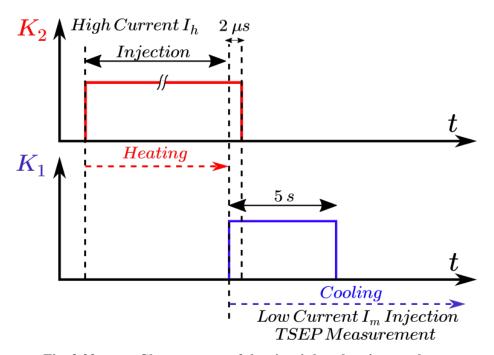

| _             | Chronograms of the circuit breakers' control                                            |      |

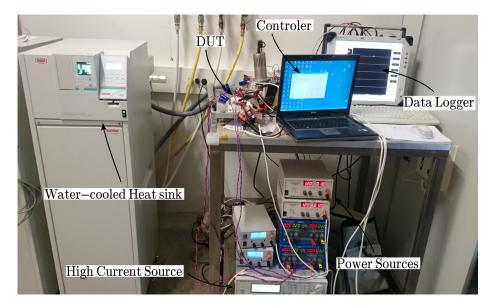

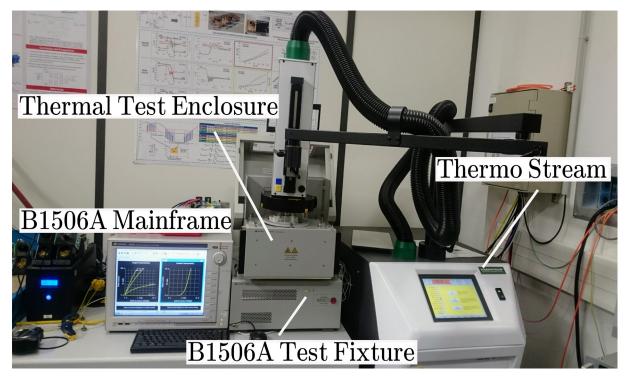

| _             | Thermal impedances measurement's test bench.                                            |      |

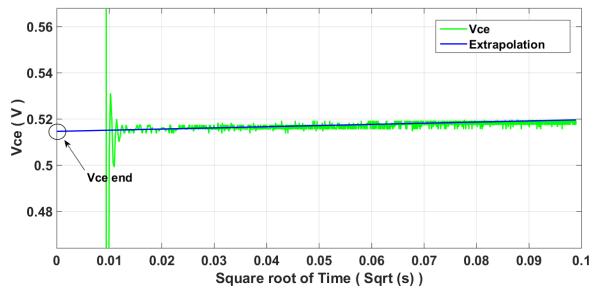

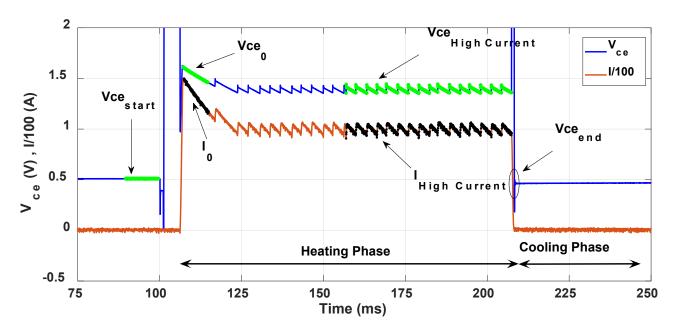

| -             | Linear extrapolation of <i>Vce</i> represented as a function of the square root of time |      |

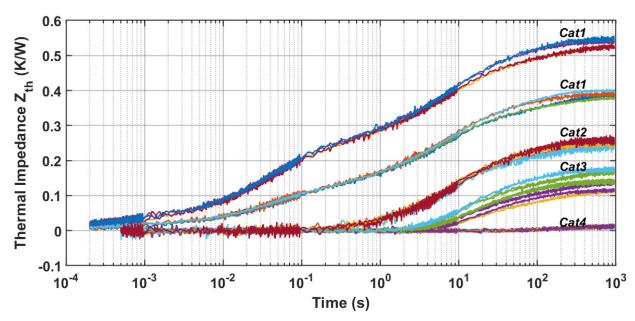

|               | Measured thermal impedances in the case of the IGBT inverter                            |      |

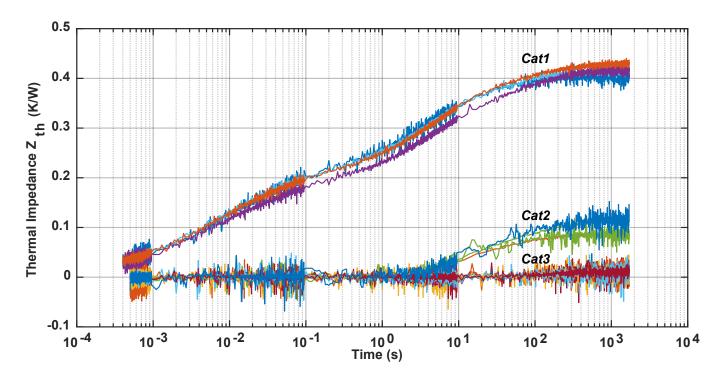

|               | Measured thermal impedances in the case of the SiC MOSFET inverter                      |      |

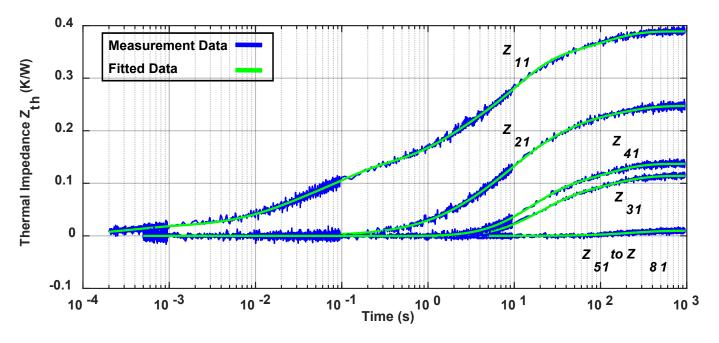

| Fig. 3.27:    | Fitting the thermal impedances for device $D_1$ in the case of the IGBT inverter        | 122  |

| Fig. 4.1:     | Full approach of the study                                                              |      |

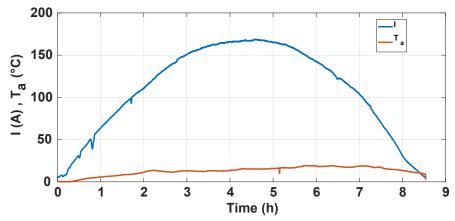

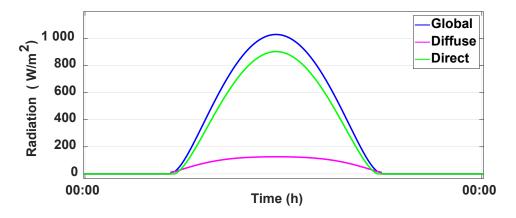

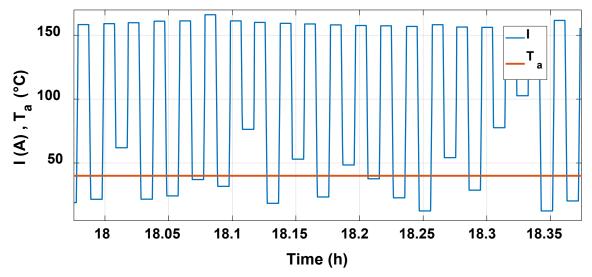

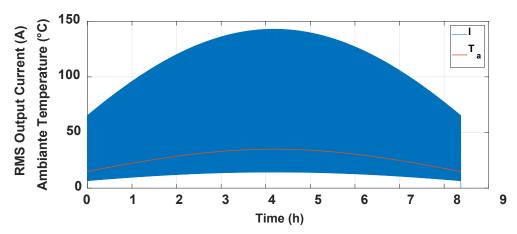

| Fig. 4.2:     | I and Ta mission profiles over a clear sky day                                          |      |

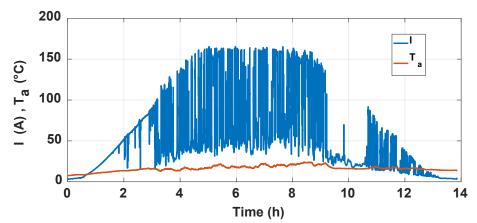

| Fig. 4.3:     | I and Ta mission profiles over a cloudy day                                             |      |

| Fig. 4.4:     | Highlight on several current variations from Fig. 4.3                                   |      |

| Fig. 4.5:     | Solar radiation over one day                                                            |      |

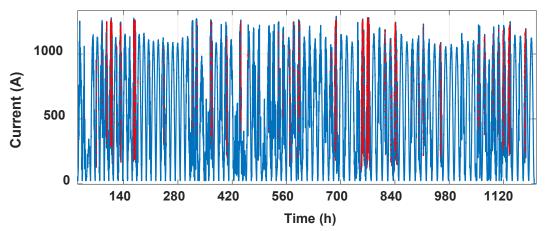

| Fig. 4.6:     | Extraction of current's considerable variations                                         |      |

| Fig. 4.7:     | Highlight on several variations from Fig. 4.6                                           |      |

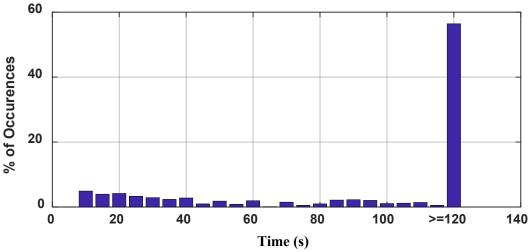

| Fig. 4.8:     | Histogram of occurrences (in percentage) of the delays between two consecur-            |      |

| big variation | ons of the current                                                                      | 131  |

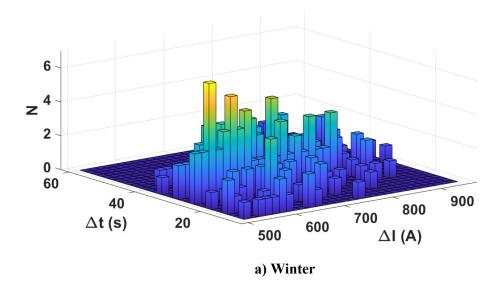

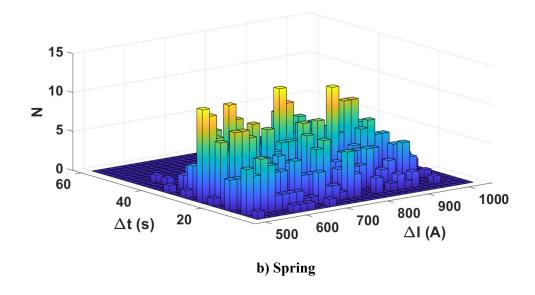

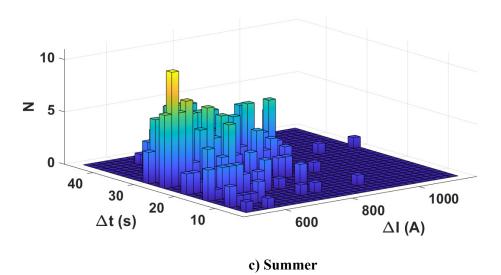

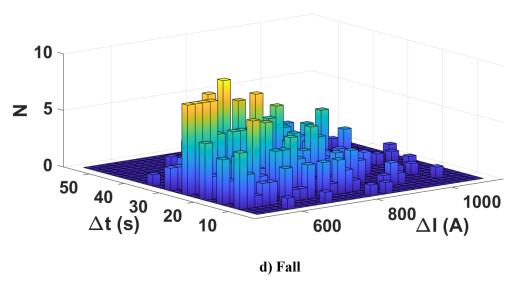

| Fig. 4.9:   | Histograms representing the number of occurrences of the current's variatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns as a |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| function of | f their duration and amplitude                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132     |

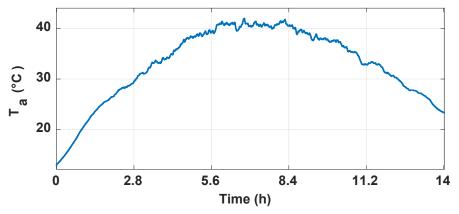

| Fig. 4.10:  | Ambient temperature profile over one day                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 133     |

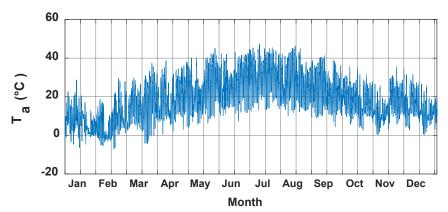

| Fig. 4.11:  | Ambient temperature profile over year 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 133     |

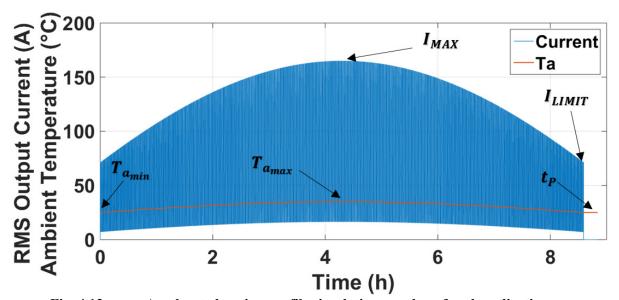

| Fig. 4.12:  | Accelerated ageing profile simulating one day of real application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 134     |

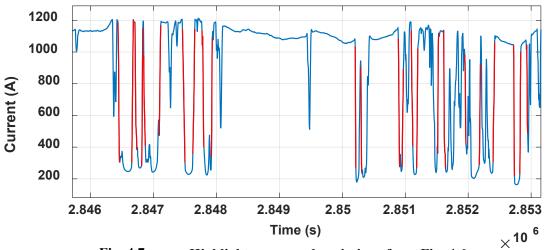

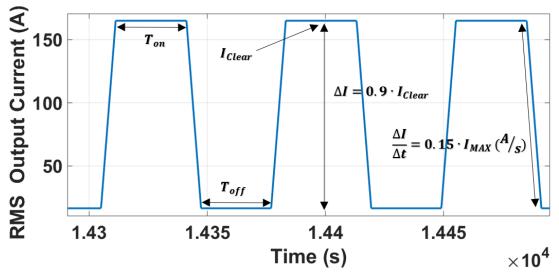

|             | Highlight on several current's variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

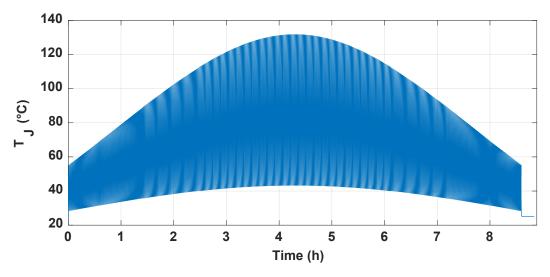

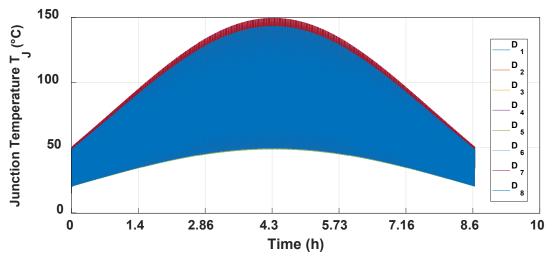

|             | MOSFET junction temperature's profile during the accelerated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

|             | ng one day)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

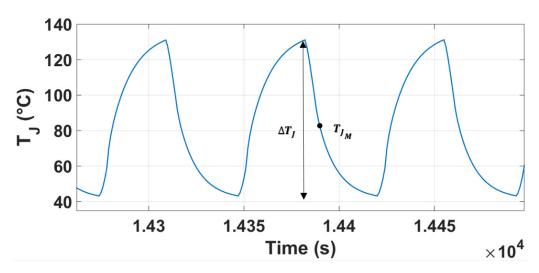

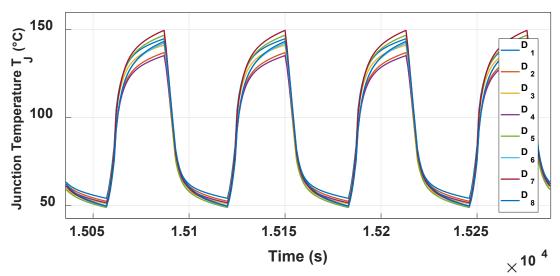

| Fig. 4.15:  | Highlight on several junction temperature variations from Fig. 4.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 136     |

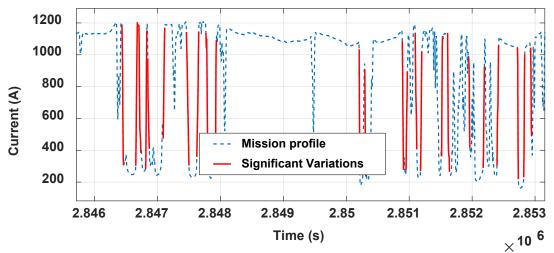

| -           | Extraction of the significant variations from the current's profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

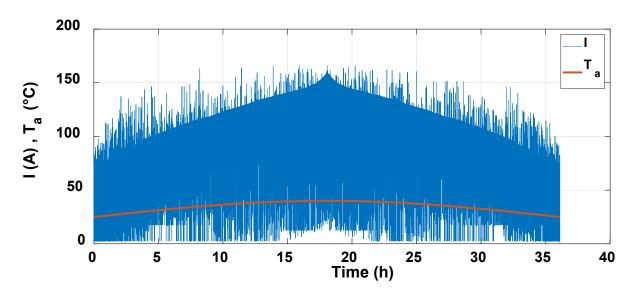

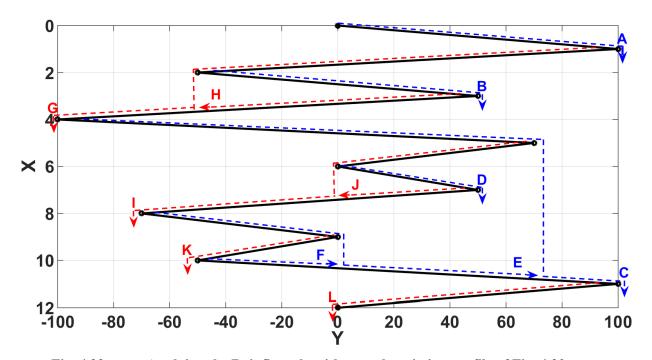

|             | 2 <sup>nd</sup> ageing profile accumulating all the significant variations occurring ov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| year        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

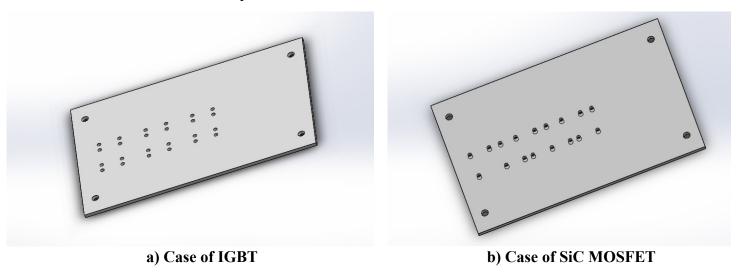

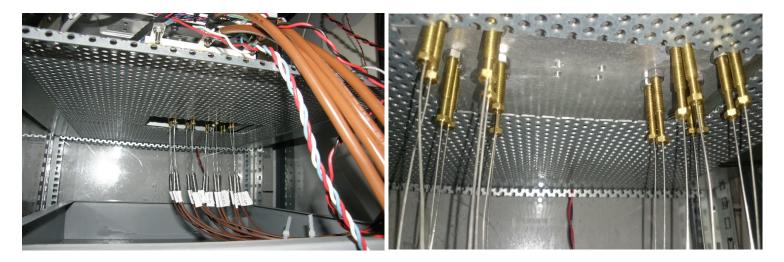

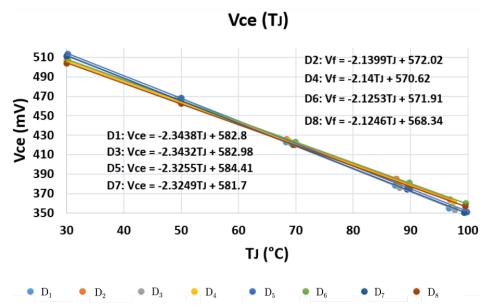

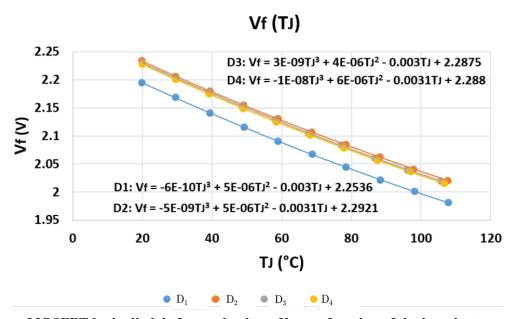

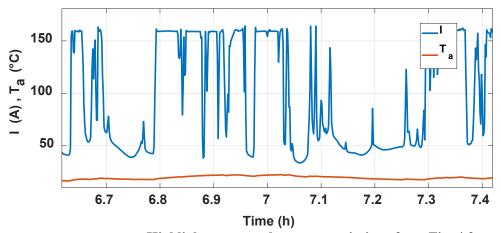

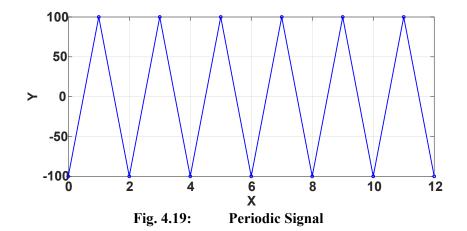

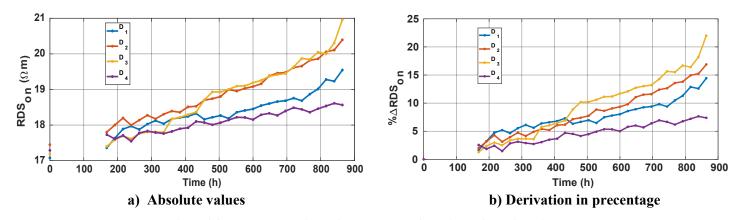

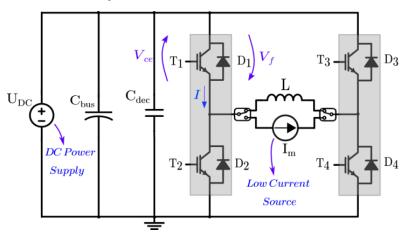

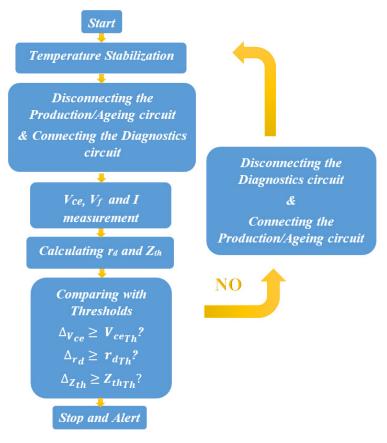

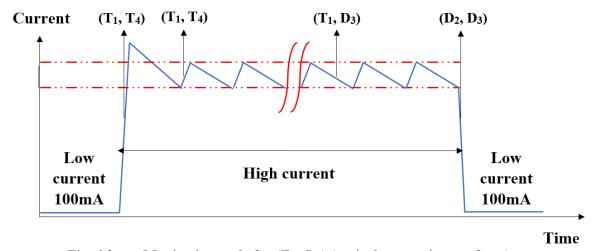

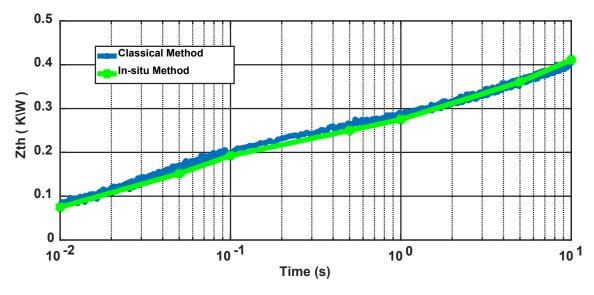

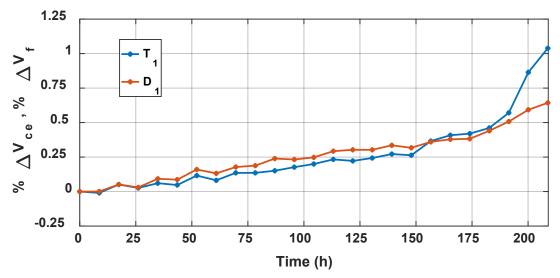

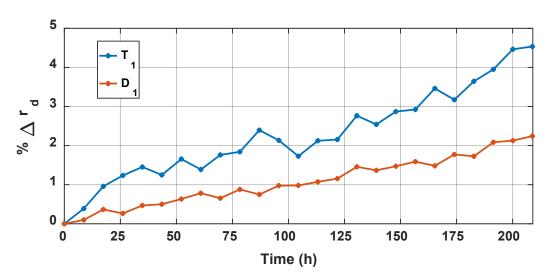

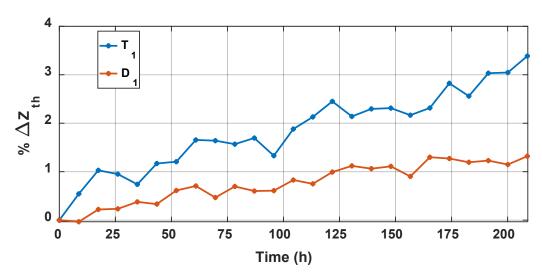

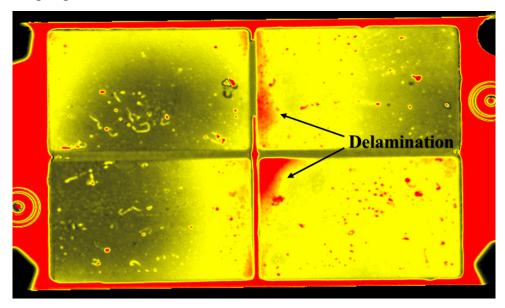

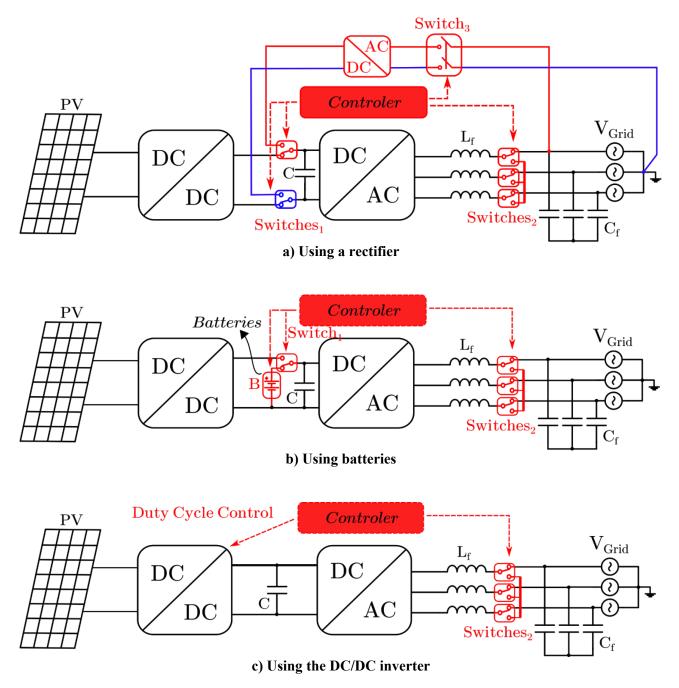

| Fig. 4.18:  | Highlight on several current variations from the profile in Fig. 4.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138     |