# Représentation dynamique de la liste des copies pour le passage à l'échelle des protocoles de cohérence de cache Julie Dumas

#### ▶ To cite this version:

Julie Dumas. Représentation dynamique de la liste des copies pour le passage à l'échelle des protocoles de cohérence de cache. Architectures Matérielles [cs.AR]. Université Grenoble Alpes, 2017. Français. NNT: 2017GREAM093. tel-01879032

# HAL Id: tel-01879032 https://theses.hal.science/tel-01879032

Submitted on 21 Sep 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ DE GRENOBLE

Spécialité : **Informatique** Arrêté ministériel : 25 mai 2016

Présentée par

## Julie DUMAS

Thèse dirigée par Frédéric PÉTROT

préparée au sein du laboratoire TIMA et au CEA-Leti et de l'École Doctorale Mathématiques, Sciences et Technologies de l'In-formatique

# Représentation dynamique de la liste des copies pour le passage à l'échelle des protocoles de cohérence de cache

Thèse soutenue publiquement le **13 décembre 2017** devant le jury composé de :

M. Florent de Dinechin

INSA Lyon/CITI, Président

M. Daniel Etiemble

Université Paris Sud/LRI, Rapporteur

M. Gilles Sassatelli

CNRS/Université Montpellier 2/LIRMM, Rapporteur

M. Ouentin Meunier

UMPC/LIP6, Examinateur

M. Frédéric Pétrot

TIMA, Directeur de thèse

M. Éric Guthmuller

CEA-Leti, Co-Encadrant de thèse

# Résumé

Le problème du passage à l'échelle des protocoles de cohérence de caches qui se pose pour les machines parallèles se pose maintenant aussi sur puce, suite à l'émergence des architectures *manycores*. Il existe deux classes de protocoles : ceux basés sur l'espionnage et ceux utilisant un répertoire. Les protocoles basés sur l'espionnage, qui doivent transmettre à tous les caches les informations de cohérence, engendrent un nombre important de messages dont peu sont effectivement utiles. En revanche, les protocoles avec répertoires visent à n'envoyer des messages qu'aux caches qui en ont besoin. L'implémentation la plus évidente utilise un champ de bits complet dont la taille dépend uniquement du nombre de cœurs. Ce champ de bits représente la liste des copies. Pour passer à l'échelle, un protocole doit émettre un nombre raisonnable de messages de cohérence et limiter le matériel utilisé pour la cohérence et en particulier pour la liste des copies.

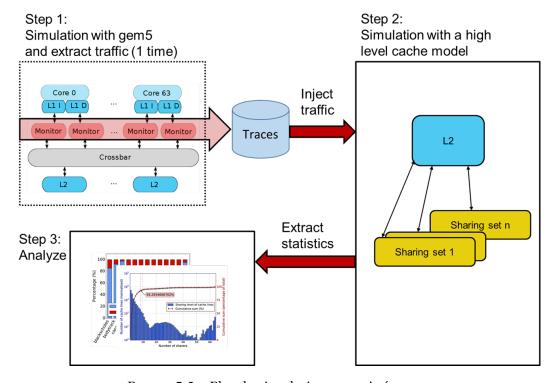

Afin d'évaluer et de comparer les protocoles et leurs représentations de la liste des copies, nous proposons tout d'abord une méthode de simulation basée sur l'injection de traces dans un modèle de cache à haut niveau. Cette méthode permet d'effectuer rapidement l'exploration architecturale des protocoles.

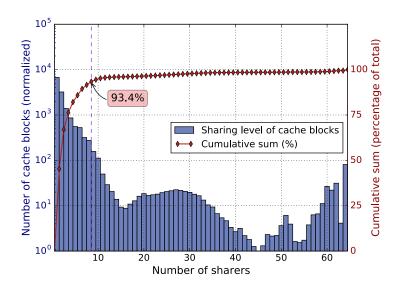

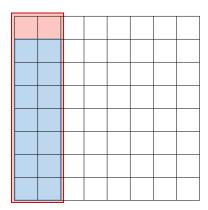

Nous proposons également une nouvelle représentation dynamique de la liste des copies pour le passage à l'échelle des protocoles de cohérence de caches. Pour une architecture à 64 cœurs, 93% des lignes de cache sont partagées par au maximum 8 cœurs, sachant par ailleurs que le système d'exploitation cherche à placer les tâches communicantes proches les unes des autres. Notre représentation dynamique de la liste des copies tire parti de ces deux observations en utilisant un champ de bits pour un sous-ensemble des copies et une liste chaînée. Le champ de bits correspond à un rectangle à l'intérieur duquel la liste des copies est exacte. La position et la forme de ce rectangle évoluent au cours de la durée de vie des applications. Plusieurs algorithmes pour le placement du rectangle cohérent sont proposés et évalués. Pour finir, nous effectuons une comparaison avec les représentations de la liste des copies de l'état de l'art.

#### **ABSTRACT**

Cache coherence protocol scalability problem for parallel architecture is also a problem for on chip architecture, following the emergence of manycores architectures. There are two protocol classes: snooping and directory-based. Protocols based on snooping, which send coherence information to all caches, generate a lot of messages whose few are useful. On the other hand, directory-based protocols send messages only to caches which need them. The most obvious implementation uses a full bit vector whose size depends only on the number of cores. This bit vector represents the sharing set. To scale, a coherence protocol must produce a reasonable number of messages and limit hardware ressources used by the coherence and in particular for the sharing set.

To evaluate and compare protocols and their sharing set, we first propose a method based on trace injection in a high-level cache model. This method enables a very fast architectural exploration of cache coherence protocols.

We also propose a new dynamic sharing set for cache coherence protocols, which is scalable. With 64 cores, 93% of cache blocks are shared by up to 8 cores. Futhermore, knowing that the operating system looks to place communicating tasks close to each other. Our dynamic sharing set takes advantage from these two observations by using a bit vector for a subset of copies and a linked list. The bit vector corresponds to a rectangle which stores the exact sharing set. The position and shape of this rectangle evolve over application's lifetime. Several algorithms for coherent rectangle placement are proposed and evaluated. Finally, we make a comparison with sharing sets from the state of the art.

#### REMERCIEMENTS

Je voudrais tout d'abord remercier mon directeur de thèse, Frédéric Pétrot, pour sa disponibilité et son implication en particulier lors des phases de rédaction. Je tiens à remercier mon encadrant au CEA, Éric Guthmuller, pour son aide lors du développement de PyCCExplorer, ses relectures, sa patience et surtout sa disponibilité. Je les remercie également d'avoir toujours fait en sorte de ne pas se contredire, et ainsi d'avoir eu un encadrement cohérent.

Je tiens également à remercier les membres de mon jury. Tout d'abord, Daniel Etiemble et Gilles Sassatelli qui ont accepté d'être mes rapporteurs. Je remercie également Florent de Dinechin et Quentin Meunier qui ont accepté de participer à mon jury de thèse. Je les remercie pour les échanges que nous avons pu avoir sur mes travaux de thèse.

Je souhaite également remercier l'ensemble du laboratoire LISAN pour leur accueil et en particulier Fabien Clermidy puis Jerôme Martin chefs du laboratoire au cours de ma thèse. Je remercie en particulier les autres doctorants que j'ai croisés au cours de ma thèse : Vincent, Florent, Maxime (les deux), Alex, Andréa, Réda, Thomas, Jimmy (et les repas du jeudi), Camille, Simon (et ses cannelés) et surtout Soundous. Je tiens à remercie particulièrement César Fuguet Tortolero pour son aide et ses conseils tout au long de ma thèse. Je remercie également Christian Bernard pour son intérêt à mes travaux. Je souhaite également remercier les responsables scientifiques : Edith Beigné, Marc Belleville et Pascal Vivet pour leurs conseils.

Je voudrais également remercier les membres de l'équipe SLS du laboratoire TIMA avec qui j'ai pu échanger et en particulier Hela avec qui j'ai pu partager mes difficultés avec gem5.

Je remercie également tous les professeurs avec qui j'ai pu intervenir à l'Ensimag : Olivier Muller, Claire Maiza, Matthieu Moy, Stéphane Mancini, François Broquedis, Frédéric Pétrot, Matthieu Chabanas, Sébastien Viardot pour leur soutien et leurs conseils en particulier durant les derniers mois de ma thèse.

Je souhaiterais remercie mes amis du conservatoire et de l'harmonie Echo des Balmes pour m'avoir permis de faire de la musique tout au long de ma thèse, même lorsque je n'avais pas beaucoup de temps. Je remercie également Lorraine de m'avoir soutenue pendant la rédaction. Je souhaite remercier Yannick, pour les chocolats chauds et le festival

# Table des matières

| Ta              | ble d  | les figures                                                                | xi |  |

|-----------------|--------|----------------------------------------------------------------------------|----|--|

| Li              | ste de | es tableaux                                                                | xv |  |

| 1               | Intr   | roduction                                                                  | 1  |  |

| 2 Problématique |        |                                                                            |    |  |

|                 | 2.1    | Architectures manycores                                                    | 3  |  |

|                 |        | 2.1.1 Modèle mémoire                                                       | 3  |  |

|                 |        | 2.1.2 Hiérarchie mémoire                                                   | 5  |  |

|                 | 2.2    | Caches et cohérence des caches dans les architectures manycores            | 6  |  |

|                 |        | 2.2.1 Architecture des caches                                              | 6  |  |

|                 |        | 2.2.2 Cohérence des caches                                                 | 7  |  |

|                 | 2.3    | Représentation de la liste des copies                                      | 10 |  |

|                 | 2.4    | Caractéristiques des applications parallèles                               | 12 |  |

|                 | 2.5    | Évaluation des représentations de la liste des copies                      | 13 |  |

|                 | 2.6    | Conclusion                                                                 | 14 |  |

| 3               | Coh    | érence des caches dans une architecture <i>manycore</i> à mémoire partagée | 15 |  |

|                 | 3.1    | Protocoles basés sur l'espionnage                                          | 15 |  |

|                 |        | 3.1.1 <i>Flexible snooping</i>                                             | 16 |  |

|                 |        | 3.1.2 In-Network Coherence Filtering                                       | 17 |  |

|                 | 3.2    | Protocoles avec répertoire limité                                          | 18 |  |

|                 |        | 3.2.1 Ackwise                                                              | 18 |  |

|                 |        | 3.2.2 Coarse bit-vector directory                                          | 19 |  |

|                 |        | 3.2.3 Virtualisation des CIDs                                              | 19 |  |

|                 | 3.3    | Protocoles de cohérence de caches dynamiques                               | 20 |  |

|                 |        | 3.3.1 Liste chaînée                                                        | 20 |  |

|                 |        | 3.3.2 Champ de bits limité                                                 | 21 |  |

|                 |        | 3.3.3 Sponge directory                                                     | 22 |  |

|                 |        | 3.3.4 SPACE                                                                | 23 |  |

|                 |        |                                                                            |    |  |

|   | 3.4 | Autres  | s propositions                                                             | 24 |

|---|-----|---------|----------------------------------------------------------------------------|----|

|   |     | 3.4.1   | Scalable Interface Coherence                                               | 24 |

|   |     | 3.4.2   | In-Network Cache Coherence                                                 | 24 |

|   |     | 3.4.3   | Classifications des données                                                | 25 |

|   |     | 3.4.4   | Fenêtres temporelles                                                       | 26 |

|   | 3.5 | Concl   | usion                                                                      | 27 |

| 4 | Rep | résenta | ation dynamique de la liste des copies                                     | 29 |

|   | 4.1 | Préser  | ntation du concept du protocole DCC                                        | 29 |

|   | 4.2 | Représ  | sentation du répertoire du protocole <i>Dynamic Coherent Cluster</i> (DCC) | 31 |

|   |     | 4.2.1   | Entrée du répertoire                                                       | 31 |

|   |     | 4.2.2   | Liste chaînée                                                              | 32 |

|   |     | 4.2.3   | Exemple d'entrée du répertoire DCC                                         | 32 |

|   |     | 4.2.4   | Coût matériel du répertoire                                                | 33 |

|   | 4.3 | Algori  | thmes de placement du rectangle cohérent                                   | 33 |

|   |     | 4.3.1   | Algorithme idéal                                                           | 34 |

|   |     | 4.3.2   | Algorithme <b>premier touché</b>                                           |    |

|   |     | 4.3.3   | Algorithme <b>combinatoire</b>                                             | 38 |

|   | 4.4 | Détail  | s de l'algorithme <b>combinatoire</b>                                      | 39 |

|   |     | 4.4.1   | Comportement de l'algorithme <b>combinatoire</b>                           | 40 |

|   |     | 4.4.2   | Évaluation théorique du coût matériel                                      | 43 |

|   | 4.5 | Concl   | usion                                                                      | 45 |

| 5 | Mét | hode d' | 'évaluation de la représentation de la liste des copies                    | 47 |

|   | 5.1 | Métho   | des de simulation existantes                                               | 47 |

|   |     | 5.1.1   | Simulations par interprétation d'instructions                              | 48 |

|   |     | 5.1.2   | Simulations basées sur l'injection de traces                               | 50 |

|   | 5.2 | Flot de | e simulation                                                               | 51 |

|   | 5.3 | Extrac  | tion des requêtes d'accès mémoire                                          | 52 |

|   |     | 5.3.1   | Choix des paramètres de gem5                                               | 52 |

|   |     | 5.3.2   | Modifications apportées à gem5                                             | 53 |

|   |     | 5.3.3   | Choix des applications                                                     | 53 |

|   |     | 5.3.4   | Simulation et extraction du trafic                                         | 54 |

|   | 5.4 | PyCCI   | Explorer : un simulateur haut niveau pour la cohérence de caches .         | 55 |

|   |     | 5.4.1   | Architecture logicielle                                                    | 56 |

|   | 5.5 | Choix   | des métriques et instrumentations du simulateur                            | 59 |

|   |     | 5.5.1   | Latence d'accès aux données                                                | 59 |

|   |     | 5.5.2   | Trafic induit par la cohérence de caches                                   | 60 |

|   |     | 5.5.3   | Évaluation du nombre de messages de diffusion                              | 60 |

|   | 5.6  | Concl   | usion     |                                                                                                            | 60 |

|---|------|---------|-----------|------------------------------------------------------------------------------------------------------------|----|

| 6 | Éval | luation | de l'infl | uence de la représentation de la liste des copies                                                          | 63 |

|   | 6.1  | Expér   | imentatio | ons avec le simulateur PyCCExplorer                                                                        | 63 |

|   |      | 6.1.1   | Implém    | entation dans le simulateur                                                                                | 64 |

|   |      |         | 6.1.1.1   | Protocole basé sur l'espionnage (snoop)                                                                    | 64 |

|   |      |         | 6.1.1.2   | Répertoire avec champ de bits complet (bit-vector)                                                         | 64 |

|   |      |         | 6.1.1.3   | Répertoire Ackwise                                                                                         | 65 |

|   |      |         | 6.1.1.4   | Répertoire utilisant une liste chaînée                                                                     | 65 |

|   |      | 6.1.2   | Explora   | tion architecturale avec PyCCExplorer                                                                      | 66 |

|   |      |         | 6.1.2.1   | Exploration architecturale pour Ackwise                                                                    | 66 |

|   |      |         | 6.1.2.2   | Exploration architecturale du protocole basé sur une liste                                                 | 67 |

|   |      | 612     | Classom   | chaînée                                                                                                    | 67 |

|   |      | 6.1.3   |           | nent des représentations de la liste des copies                                                            | 70 |

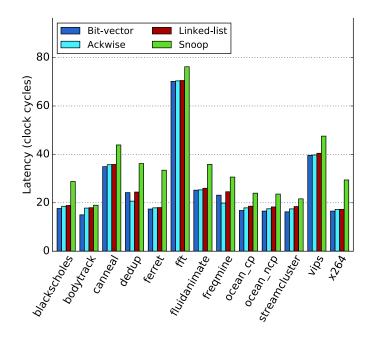

|   |      |         | 6.1.3.1   | Latence                                                                                                    | 70 |

|   |      | (1.4    | 6.1.3.2   |                                                                                                            | 74 |

|   |      | 6.1.4   |           | on du simulateur PyCCExplorer                                                                              | 76 |

|   |      |         | 6.1.4.1   | Comparaison entre PyCCExplorer et gem5 concernant l'évaluation de la représentation de la liste des copies | 76 |

|   |      |         | 6.1.4.2   | Comparaison des résultats à ceux d'autres travaux                                                          | 77 |

|   |      |         | 6.1.4.3   | Complexité de PyCCExplorer                                                                                 | 78 |

|   | 6.2  | Évalu   | ation du  | protocole DCC avec PyCCExplorer et implémentation                                                          |    |

|   |      | matér   | ielle     |                                                                                                            | 79 |

|   |      | 6.2.1   | Simulat   | ion avec PyCCExplorer                                                                                      | 79 |

|   |      |         | 6.2.1.1   | Environnement de simulation                                                                                | 79 |

|   |      |         | 6.2.1.2   | Étude des paramètres du protocole                                                                          | 80 |

|   |      |         | 6.2.1.3   | Comparaison des représentations de la liste des copies .                                                   | 83 |

|   |      |         | 6.2.1.4   | Conclusion sur l'ensemble des métriques                                                                    | 89 |

|   |      | 6.2.2   | Implém    | entation matérielle du protocole DCC                                                                       | 89 |

|   |      |         | 6.2.2.1   | Paramètres de synthèse                                                                                     | 89 |

|   |      |         | 6.2.2.2   | Fréquence de fonctionnement                                                                                | 90 |

|   |      |         | 6.2.2.3   | Surface du bloc <i>tiling</i>                                                                              | 90 |

|   | 6.3  | Concl   | usion     |                                                                                                            | 91 |

| 7 | Trav | vaux fu | turs      |                                                                                                            | 95 |

|   | 7.1  | Améli   | iorations | à apporter à PyCCExplorer                                                                                  | 95 |

|   |      | 7.1.1   | Simulat   | ion d'architecture avec plus de 64 cœurs                                                                   | 95 |

|   |      | 7.1.2   | Ajout d'  | 'autres topologies de réseau                                                                               | 95 |

|   |      | 7.1.3   | Ajout d'  | 'autres représentations de la liste des copies                                                             | 95 |

## TABLE DES MATIÈRES

|    |             | 7.1.4   | Ajout de méthodes décentralisées                                  | 96  |

|----|-------------|---------|-------------------------------------------------------------------|-----|

|    | 7.2         | Limite  | es des simulations du protocole DCC                               | 96  |

|    |             | 7.2.1   | Simulation des applications avec l'initialisation                 | 96  |

|    |             | 7.2.2   | Simulation sans le placement optimal des cœurs                    | 96  |

|    |             | 7.2.3   | Simulation avec d'autres architectures                            | 97  |

|    | 7.3         | Pistes  | de recherche autour du protocole DCC                              | 97  |

|    |             | 7.3.1   | Choix du keeper                                                   | 97  |

|    |             | 7.3.2   | Intégration du bloc <i>tiling</i> dans une architecture           | 97  |

|    |             | 7.3.3   | Ajouter un tas partagé pour mémoriser les rectangles de cohérence | 97  |

| 8  | Con         | clusior | <b>1</b>                                                          | 101 |

| A  | Algo        | orithm  | e de placement des tâches                                         | 107 |

|    | <b>A.</b> 1 | Préser  | ntation de l'algorithme de recuit simulé                          | 107 |

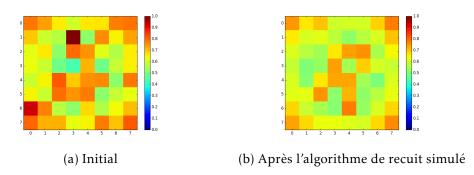

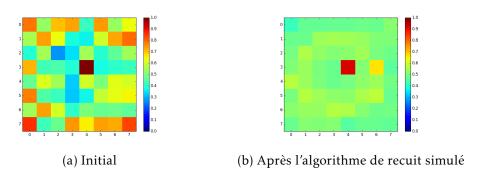

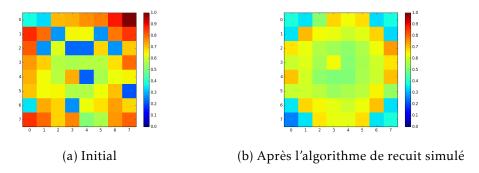

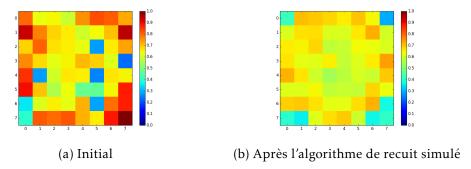

|    | A.2         | Placer  | ment des caches sur la grille avant et après l'algorithme         | 109 |

| Pu | ıblica      | ations  | 1                                                                 | 113 |

| Bi | bliog       | raphie  | -                                                                 | 115 |

# Table des figures

| 2.1  | Architecture à passage de messages                                                                                                                      | 4   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Architecture à mémoire partagée                                                                                                                         | 4   |

| 2.3  | Pyramide des différents types de mémoire                                                                                                                | 5   |

| 2.4  | Exemple avec 4 cœurs partageant des données                                                                                                             | 8   |

| 2.5  | Protocole de cohérence de caches basé sur l'espionnage                                                                                                  | 8   |

| 2.6  | Protocole de cohérence de caches basé sur un répertoire                                                                                                 | 9   |

| 2.7  | Machine à états finis pour un protocole de type MESI                                                                                                    | 10  |

| 2.8  | Format d'entrée dans un répertoire avec la liste des copies                                                                                             | 11  |

| 2.9  | Exemple de liste des copies représentée avec un champ de bits complet .                                                                                 | 11  |

| 2.10 | Nombre de lignes de cache partagées par n cœurs                                                                                                         | 12  |

| 3.1  | Trois types de communication dans un réseau en anneau                                                                                                   | 16  |

| 3.2  | INCF : exemple d'architecture avec des filtres au niveau des routeurs                                                                                   | 17  |

| 3.3  | Répertoire du protocole Ackwise                                                                                                                         | 18  |

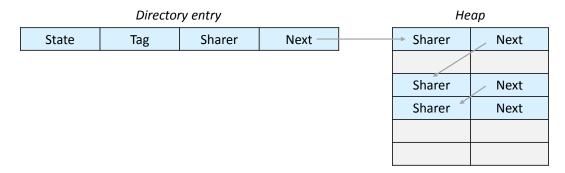

| 3.4  | Représentation de la liste des copies basée sur une liste chaînée                                                                                       | 20  |

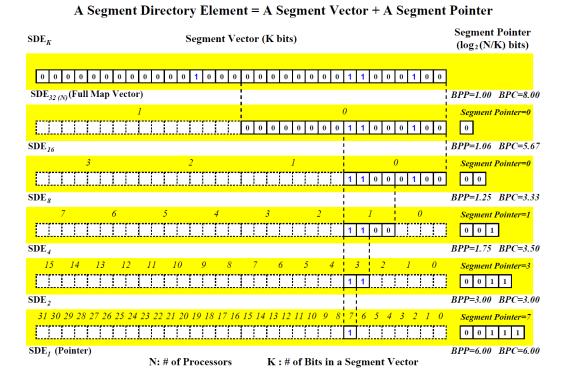

| 3.5  | Structure du répertoire utilisant des segments                                                                                                          | 21  |

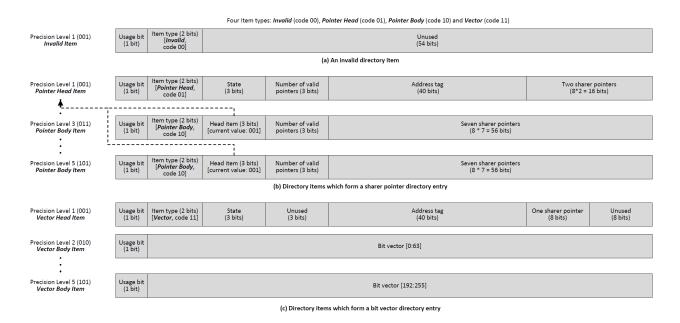

| 3.6  | Formats des entrées de <i>Sponge directory</i>                                                                                                          | 22  |

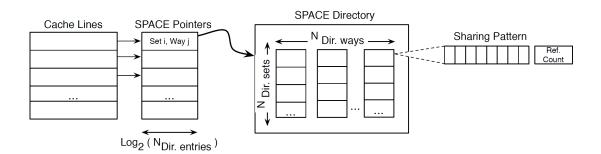

| 3.7  | Répertoire SPACE                                                                                                                                        | 23  |

| 3.8  | Création de l'arbre de cohérence du protocole INCC                                                                                                      | 25  |

| 3.9  | Répertoire du protocole INCC                                                                                                                            | 25  |

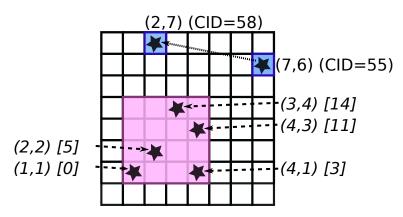

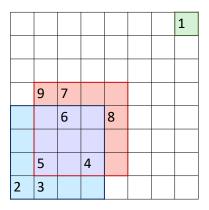

| 4.1  | Principe de DCC : les étoiles représentent les copies, les coordonnées                                                                                  |     |

|      | (x,y) sont dans un plan 2D dont l'origine est le coin en bas à gauche de la grille, et les valeurs entre crochets représentent la position du cœur dans |     |

|      | le rectangle                                                                                                                                            | 30  |

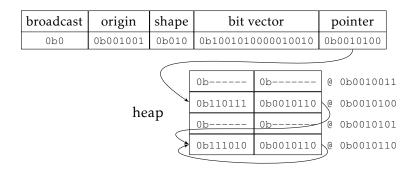

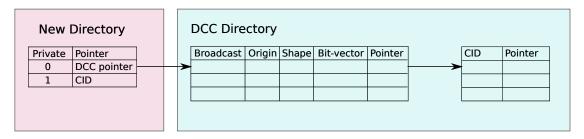

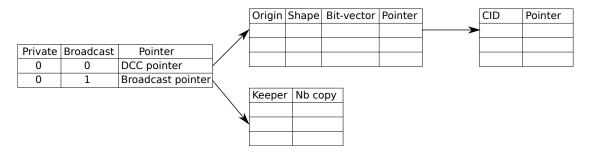

| 4.2  | Entrée du répertoire DCC                                                                                                                                | 31  |

| 4.3  | Exemple d'entrée du répertoire DCC avec le tas                                                                                                          | 32  |

| 4.4  | Exemple de rectangle englobant un rectangle de taille inférieure                                                                                        | 34  |

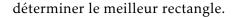

| 4.5  | Nombre de rectangles d'origine et de forme différentes en fonction de                                                                                   | J 1 |

| 2.0  | l'aire du rectangle pour 64, 256 et 1024 cœurs                                                                                                          | 35  |

|      |                                                                                                                                                         |     |

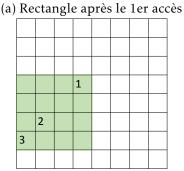

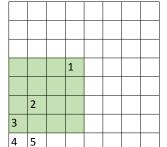

| 4.6  | Évolution du rectangle de cohérence après chaque accès avec l'algorithme              |    |

|------|---------------------------------------------------------------------------------------|----|

|      | premier touché                                                                        | 36 |

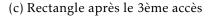

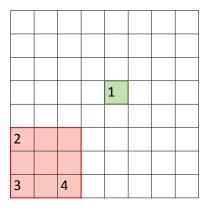

| 4.7  | Exemple de choix de rectangle <b>premier touché</b> en vert, <b>idéal</b> en rouge    | 37 |

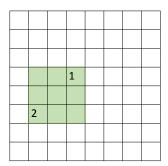

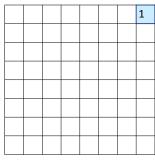

| 4.8  | Évolution du rectangle de cohérence après chaque accès avec l'algorithme              |    |

|      | combinatoire                                                                          | 39 |

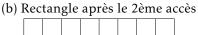

| 4.9  | Exemple de choix de rectangle <b>premier touché</b> en vert, <b>idéal</b> en rouge et |    |

|      | combinatoire en bleu                                                                  | 39 |

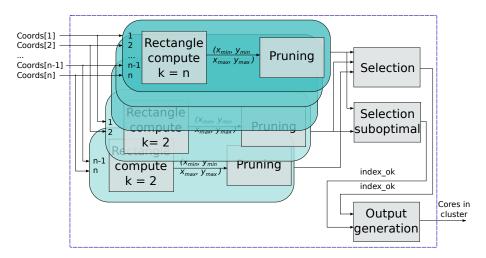

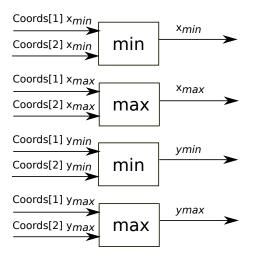

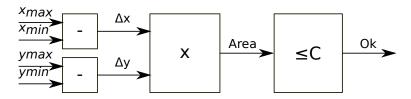

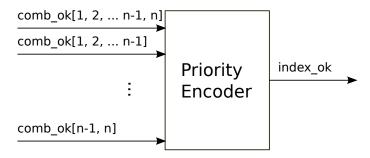

| 4.10 | Bloc <i>tiling</i> pour la recherche du rectangle de cohérence                        | 40 |

| 4.11 | Bloc de calcul des rectangles pour la combinaison [1, 2]                              | 42 |

| 4.12 | Bloc d'élagage pour une combinaison de copies                                         | 42 |

| 4.13 | Bloc de sélection implémenté avec un encodeur de priorité                             | 43 |

| 5.1  | Compromis entre temps de simulation et précision pour les différents                  |    |

|      | modes de gem5 extrait de [BGOS12]                                                     | 49 |

| 5.2  | Flot de simulation en trois étapes                                                    | 51 |

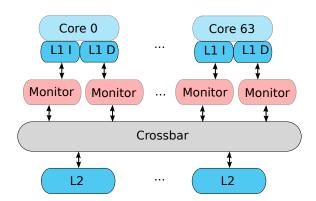

| 5.3  | Architecture simulée sur gem5 avec l'ajout des moniteurs                              | 53 |

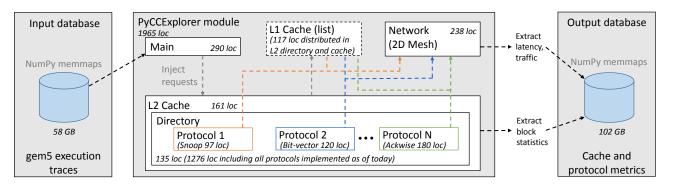

| 5.4  | Architecture logicielle de PyCCExplorer                                               | 56 |

| 6.1  | Latence moyenne relative à Ackwise avec un seuil de 5 pour plusieurs                  |    |

|      | valeurs de seuil                                                                      | 67 |

| 6.2  | Pourcentage de lignes de cache en mode diffusion avec un tas infini pour              |    |

|      | la représentation basée sur une liste chaînée                                         | 68 |

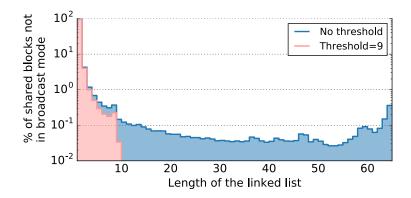

| 6.3  | Pourcentage des lignes qui ne sont pas en mode diffusion pour chaque                  |    |

|      | taille de liste chaînée                                                               | 68 |

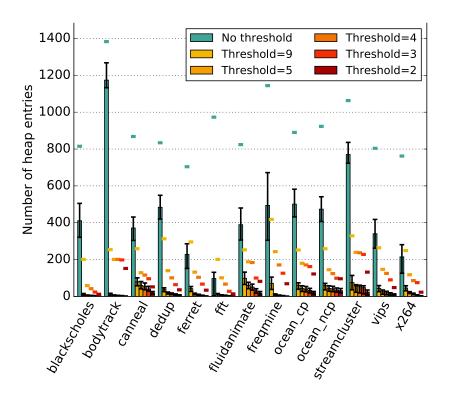

| 6.4  | Nombre d'entrées du tas utilisées pour la représentation avec une liste               |    |

|      | chaînée (avec un tas infini)                                                          | 69 |

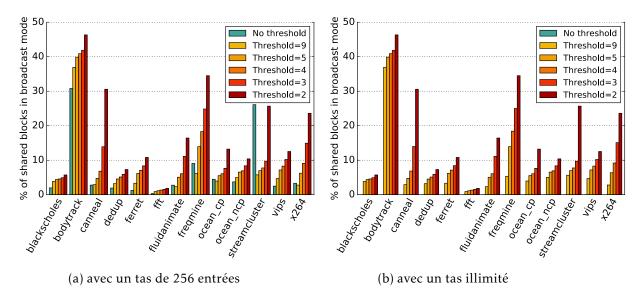

| 6.5  | Pourcentage de lignes de cache en mode diffusion pour la représentation               |    |

|      | de la liste des copies avec et sans limite sur la taille du tas                       | 70 |

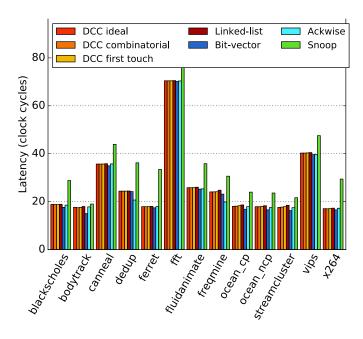

| 6.6  | Latence moyenne en nombre de cycles                                                   | 71 |

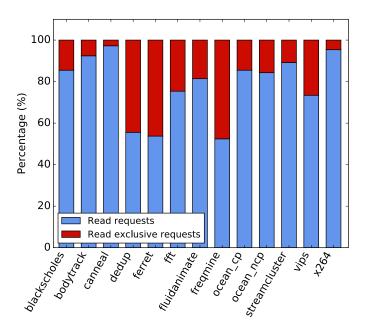

| 6.7  | Répartition des requêtes de lecture et de lecture exclusive                           | 72 |

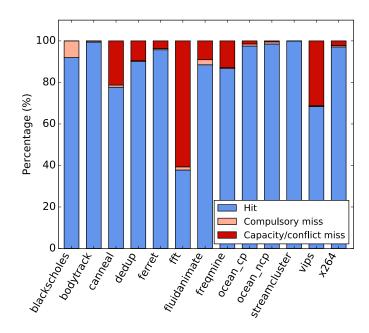

| 6.8  | Répartition du taux de succès/défaut de cache au niveau du Level Two (L2)             | 73 |

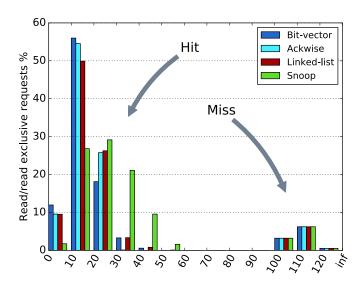

| 6.9  | Moyenne de la répartition de la latence des requêtes de lecture et de                 |    |

|      | lecture exclusive pour l'ensemble des applications                                    | 73 |

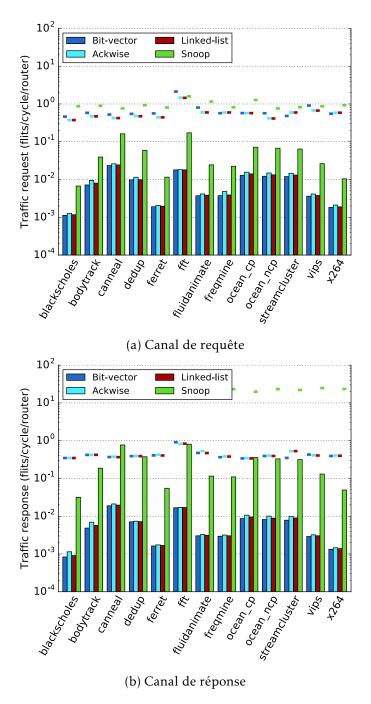

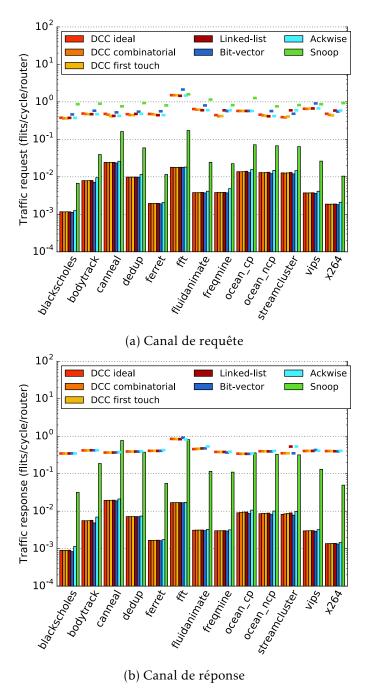

| 6.10 | Moyenne et maximum du trafic pour Ackwise, champ de bits, liste chaînée               |    |

|      | et espionnage                                                                         | 75 |

| 6.11 | Pourcentage des requêtes incohérentes en entrée de PyCCExplorer et                    |    |

|      | provenant de gem5                                                                     | 77 |

| 6.12 | Moyenne de l'utilisation du rectangle de cohérence avec le protocole DCC              |    |

|      | idéal pour les copies partagées                                                       | 80 |

| 6.13       | Pourcentage des lignes de cache en mode diffusion avec le protocole DCC   |     |

|------------|---------------------------------------------------------------------------|-----|

|            | idéal et un tas illimité                                                  | 82  |

| 6.14       | Nombre d'entrées du tas utilisées pour mémoriser la liste chaînée de DCC  | 82  |

| 6.15       | Moyenne de la latence en nombre de cycles                                 | 84  |

| 6.16       | Moyenne et maximum du trafic                                              | 85  |

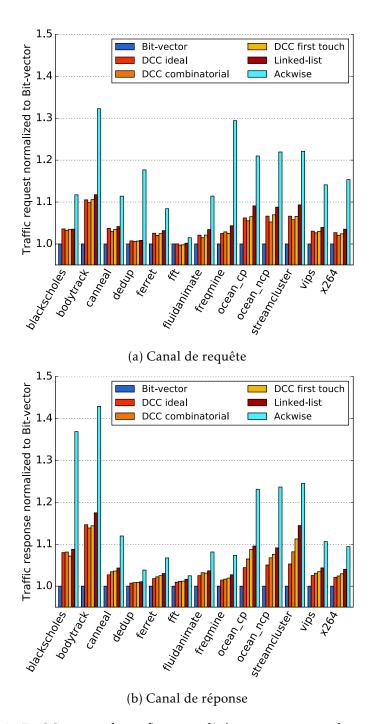

| 6.17       | Moyenne du trafic normalisé par rapport au champ de bits                  | 86  |

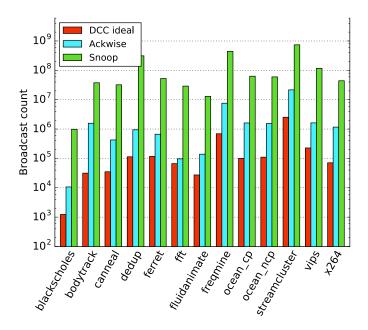

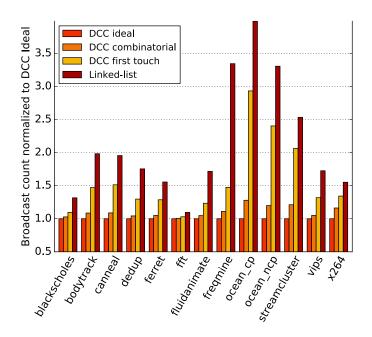

| 6.18       | Nombre de messages envoyés en diffusion                                   | 88  |

| 6.19       | Nombre de messages envoyés en diffusion normalisé par rapport à DCC       |     |

|            | idéal                                                                     | 88  |

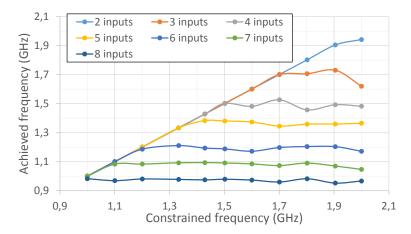

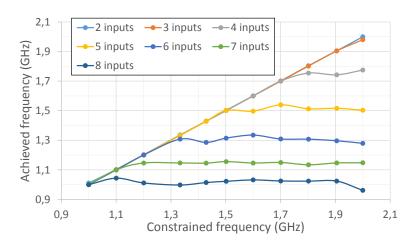

| 6.20       | Fréquence de fonctionnement du bloc tiling avec des multiplications       | 90  |

| 6.21       | Fréquence de fonctionnement du bloc tiling avec des Look-Up Table (LUT)s  | 91  |

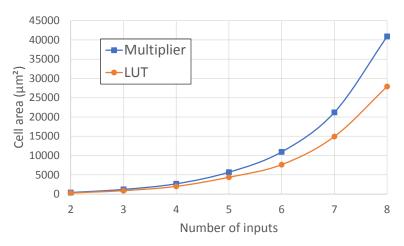

| 6.22       | Surface du bloc tiling à la fréquence maximale de fonctionnement en       |     |

|            | fonction du nombre d'entrées                                              | 91  |

| <b>7</b> 1 |                                                                           |     |

| 7.1        | Répertoire DCC avec ajout d'un niveau d'indirection selon si la ligne est | 0.0 |

| 7.0        | privée ou partagée                                                        | 98  |

| 7.2        | Répertoire DCC avec ajout d'un niveau d'indirection selon le mode de la   | 0.0 |

|            | ligne                                                                     | 98  |

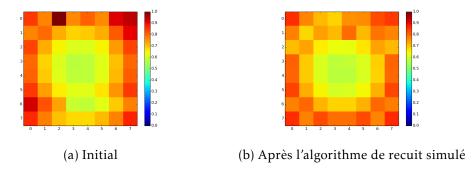

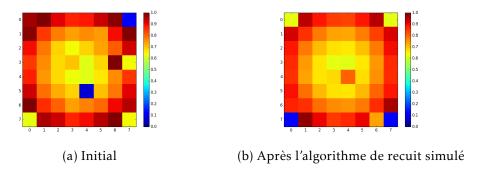

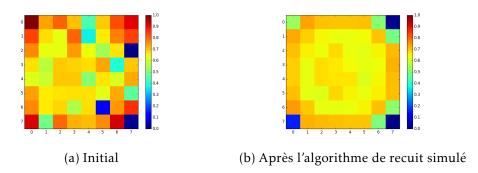

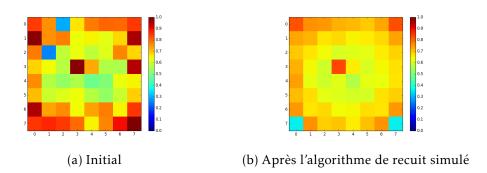

| A.1        | Placement des caches avant et après l'algorithme pour blackscholes . 1    | 109 |

| A.2        | Placement des caches avant et après l'algorithme pour bodytrack 1         | 109 |

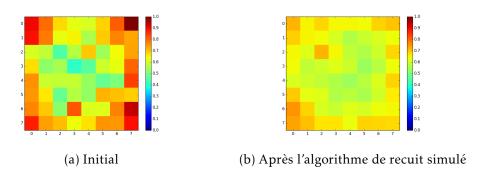

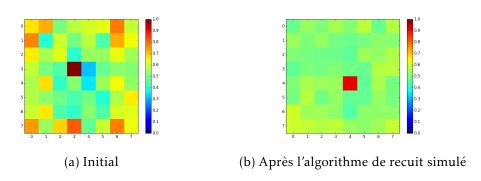

| A.3        | Placement des caches avant et après l'algorithme pour canneal             | 110 |

| A.4        | Placement des caches avant et après l'algorithme pour dedup               | 110 |

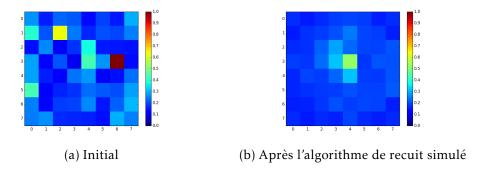

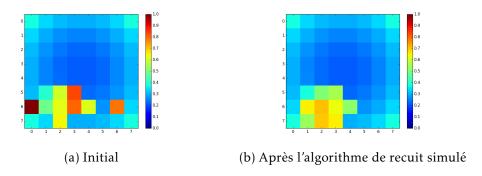

| A.5        | Placement des caches avant et après l'algorithme pour ferret 1            | 110 |

| A.6        | Placement des caches avant et après l'algorithme pour fft                 | 110 |

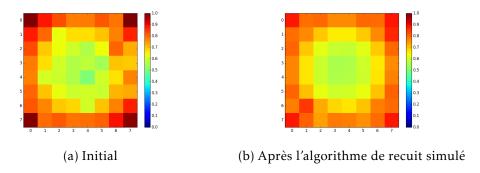

| A.7        | Placement des caches avant et après l'algorithme pour fluidanimate . 1    | 111 |

| A.8        | Placement des caches avant et après l'algorithme pour frequine 1          | 111 |

| A.9        | Placement des caches avant et après l'algorithme pour ocean_cp 1          | 111 |

| A.10       | Placement des caches avant et après l'algorithme pour ocean_ncp 1         | 111 |

| A.11       | Placement des caches avant et après l'algorithme pour streamcluster       | 112 |

| A.12       | Placement des caches avant et après l'algorithme de recuit pour vips 1    | 112 |

| A.13       | Placement des caches avant et après l'algorithme pour x264                | 112 |

# Liste des tableaux

| 5.1 | Paramètres du simulateur gem5                                          | 52 |

|-----|------------------------------------------------------------------------|----|

| 5.2 | Liste des applications                                                 | 54 |

| 5.3 | Temps d'exécution de certaines applications PARSEC et Splash2 sur gem5 | 55 |

| 6.1 | Comparaisons des représentations de la liste des copies                | 89 |

### CHAPITRE 1: INTRODUCTION

Bien que dans son rapport de 2015, l'International Technology Roadmap for Semiconductors (ITRS) prédise la fin de la diminution de la taille des transistors en 2021 [Cou16], d'autres technologies d'intégration, par exemple la 3D, ou encore la photonique intégrée, sont des candidates sérieuses pour continuer d'augmenter la puissance de calcul des ordinateurs, principalement en augmentant le nombre de cœurs interconnectés et en leur adjoignant de la mémoire locale.

En revanche, et même si des progrès notables ont été faits également du coté de la mémoire de masse, ses temps d'accès et débits restent loin de ceux que l'on peut obtenir sur une puce, et le resteront encore durablement à cause des technologies employées pour assurer un faible coût de fabrication. C'est pourquoi les machines actuelles utilisent une hiérarchie mémoire avec des mémoires rapides mais de faible capacité proche des unités de calcul et, plus on s'éloigne, plus la latence augmente mais la capacité augmente également. Aujourd'hui de nombreuses équipes travaillent à améliorer les performances des mémoires.

Par ailleurs, pour répondre aux besoins en calcul de plus en plus grands, la solution généralement admise est de découper les problèmes en plusieurs sous-problèmes et d'effectuer chaque calcul correspondant à un sous-problème sur un processeur différent. Le modèle de programmation sous-jacent le plus largement utilisé reste celui d'une mémoire partagée entre les différentes tâches logicielles, indépendamment des processeurs sur lesquels elles s'exécutent. En conséquence, la mémoire doit être hiérarchisée, c'est-à-dire que les parties les plus utiles de la mémoire de masse doivent être copiées dans des mémoires rapides proches des processeurs appelées « caches », pour satisfaire les besoins en performance à un coût raisonnable.

Les données présentes dans les caches sont donc des copies des données présentes dans la mémoire de masse. Ces copies induisent une difficulté connue depuis toujours sur les machines parallèles à mémoire partagée : la nécessité d'assurer la cohérence des caches. En effet, si une donnée copiée est modifiée localement, il faut que les processeurs qui possèdent une autre copie de cette donnée soient, avant qu'ils utilisent la dite donnée, avertis de cette modification, pour garantir qu'un prochain accès à leur propre copie contiendra bien la valeur attendue de la donnée. Ce problème possède des solutions efficaces mais dont le passage à l'échelle reste un objet d'étude avec l'augmentation du nombre de cœurs sur puce.

La difficulté du passage à l'échelle peut être abordée sous de multiples angles, allant de l'optimisation de la machine à états abstraite du protocole à l'organisation de la

hiérarchie mémoire autour de réseau sur puce avec des opérations plus avancées et effectuées au sein même du réseau d'interconnexion. Celui que nous choisissons dans cette thèse est plus modeste, et porte sur un point très particulier qui est un frein pratique important au passage à l'échelle : la représentation de la liste des processeurs possédant une copie d'une ligne de mémoire dans leur cache. Ce point, qui pourrait paraître anecdotique est en fait un problème très concret qui amène à un besoin démesuré en mémoire, de l'ordre de grandeur de celle utilisée par le cache de dernier niveau si l'on utilise des approches naïves.

#### Plan de la thèse

Dans le chapitre 2, nous exposons les problématiques de cette thèse liées à la cohérence de caches et plus particulièrement la représentation de la liste des copies de ces protocoles dans les architectures *manycores*.

Dans le chapitre 3, nous présentons un état de l'art sur les différents protocoles de cohérence de caches et les différentes représentations de la liste des copies. Nous nous intéressons principalement aux différentes représentations de la liste des copies pour les protocoles de cohérence avec un répertoire.

Le chapitre 4 présente notre représentation de la liste des copies que nous nommons DCC. Dans ce chapitre nous présentons le principe de DCC ainsi que ses différentes variantes.

Dans le chapitre 5, nous nous intéressons aux méthodes de simulation pour l'évaluation de la représentation de la liste des copies. Pour cela, nous présentons un rapide état de l'art des méthodes de simulation puis nous exposons notre méthode basée sur le simulateur PyCCExplorer que nous avons développé dans cette thèse.

Le chapitre 6 se focalise sur l'évaluation de l'influence de la représentation de la liste des copies. Pour cela, nous présentons les expérimentations faites avec PyCCExplorer ainsi que la validation de notre méthodologie de simulation. Nous nous intéressons également à l'évaluation de notre protocole DCC à l'aide de PyCCExplorer, puis nous présentons les résultats de synthèse obtenus lors de l'implémentation matérielle du protocole DCC.

Le chapitre 7 présente les pistes d'améliorations et les travaux futurs à mener dans la continuité des travaux de cette thèse.

Enfin, le chapitre 8 conclut cette thèse en répondant aux questions posées précédemment dans le chapitre 2.

# Chapitre 2: Problématique

#### Sommaire

| 2.1 | Architectures manycores                                           |  |  |  |

|-----|-------------------------------------------------------------------|--|--|--|

|     | 2.1.1 Modèle mémoire                                              |  |  |  |

|     | 2.1.2 Hiérarchie mémoire                                          |  |  |  |

| 2.2 | Caches et cohérence des caches dans les architectures manycores 6 |  |  |  |

|     | 2.2.1 Architecture des caches 6                                   |  |  |  |

|     | 2.2.2 Cohérence des caches                                        |  |  |  |

| 2.3 | Représentation de la liste des copies                             |  |  |  |

| 2.4 | Caractéristiques des applications parallèles                      |  |  |  |

| 2.5 | Évaluation des représentations de la liste des copies             |  |  |  |

| 2.6 | Conclusion                                                        |  |  |  |

Les progrès dans les technologies d'intégration et la diminution de la taille des transistors permettent aujourd'hui d'intégrer plusieurs centaines de cœurs sur un même circuit tout en limitant la consommation énergétique. En contrepartie, des difficultés particulières liées aux communications sont inhérentes à ce type d'architecture. En effet, lorsque le problème à résoudre est divisé en plusieurs sous-problèmes, les cœurs qui effectuent chacun une partie du problème ont besoin de se synchroniser et de partager les mêmes données.

## 2.1 Architectures manycores

Dans le cadre de cette thèse, nous nous intéressons aux architectures composées de plusieurs dizaines de cœurs que l'on qualifie d'architectures manycores. Les architectures manycores peuvent être composées uniquement de processeurs généraux de type Central Processing Unit (CPU) ou de plusieurs types d'unités de calcul, par exemple de CPUs ainsi que des cœurs spécialisés tel que des Graphics Processing Unit (GPU). Dans le premier cas, on parle d'architecture homogène alors que dans le deuxième cas, on qualifie ce genre d'architecture d'hétérogène. Dans le cadre de cette thèse, nous nous sommes focalisés sur les architectures homogènes.

#### 2.1.1 Modèle mémoire

Les architectures *manycores* peuvent être classifiées selon leur type de modèle mémoire. Dans les architectures dites «à passage de messages», les processeurs utilisent des

messages pour communiquer. Sur chacun des processeurs, une instance d'un système d'exploitation est exécutée et tous les processeurs disposent également de leur propre mémoire à laquelle eux seuls possèdent le droit d'accès en lecture/écriture.

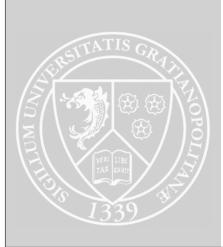

FIGURE 2.1 – Architecture à passage de messages

La figure 2.1 représente ce type d'architecture avec 4 CPUs et leur mémoire privée. Les CPUs communiquent entre eux à l'aide d'un bus de communication. Lorsque deux processus s'exécutant sur deux CPUs veulent communiquer, ils utilisent des messages de lecture ou d'écriture qui sont envoyés via le bus de communication. Lors de la réception d'un message, le CPU doit faire une suite particulière d'instructions permettant de l'écrire ou de le lire dans sa mémoire privée. Cette opération est faite à l'aide du système d'exploitation, ainsi ce type d'architecture nécessite un support de ce dernier et par conséquent s'appuie sur le logiciel.

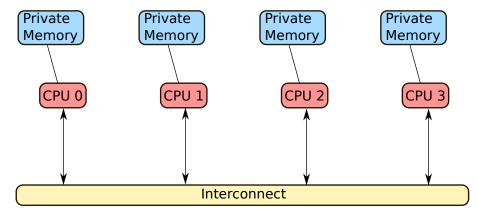

FIGURE 2.2 – Architecture à mémoire partagée

Dans les architectures à mémoire partagée, les processeurs ont accès à une mémoire en commun, comme le montre la figure 2.2. Cette fois, il existe une seule instance du système d'exploitation pour tous les processeurs et ils partagent la même mémoire. Pour s'échanger des données, les processeurs vont écrire et lire la mémoire partagée à l'aide de leurs instructions élémentaires d'accès à la mémoire. Ce type d'architecture s'appuie sur un support matériel pour l'accès à cette mémoire partagée.

Dans cette thèse, nous allons nous focaliser sur les machines *manycores* homogènes à mémoire partagée.

#### 2.1.2 Hiérarchie mémoire

Les architectures *manycores* sont composées de plusieurs CPUs et de plusieurs mémoires afin de ranger les résultats des calculs. Les technologies de fabrication des mémoires ont des caractéristiques de taille, débit et latence très différentes, ce qui a historiquement déterminé la manière même de concevoir un ordinateur. Plus les mémoires sont proches des unités de calcul (c'est-à-dire des cœurs) plus elles sont petites et rapides. Au contraire, plus elles sont éloignées du processeur, plus elles sont lentes mais elles possèdent une capacité de stockage généralement plus grande.

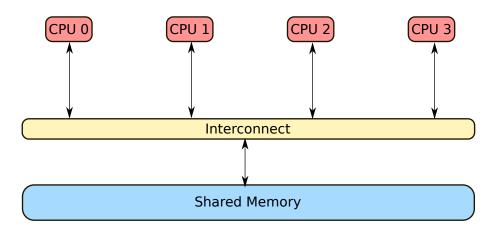

FIGURE 2.3 – Pyramide des différents types de mémoire

La figure 2.3 nous montre une pyramide qui représente une hiérarchie mémoire. À la base de la pyramide se trouvent les mémoires de type disque dur. Ces mémoires offrent une grande capacité (plusieurs tera-octets) mais elles sont particulièrement lentes. Actuellement, les *Solid-State Disk* (SSD) ont un débit de lecture qui peut atteindre 3 Go/s pour une latence de l'ordre de 0,1 ms. Les disques durs classiques ont une latence moyenne de 4,2 ms.

À l'étage supérieur se trouve la mémoire centrale ou principale. Cette mémoire permet de mémoriser une partie des données présentes dans le disque dur. Ces données sont copiées dans la mémoire principale lorsque le système d'exploitation souhaite y accéder. On utilise pour cela des mémoires de type *Dynamic Random Access Memory* (DRAM) qui ont une capacité de stockage de l'ordre de quelques giga-octets (aujourd'hui on trouve facilement des DRAM de 8 Go et bien plus) et elles ont un débit de lecture théorique jusqu'à 25 Go/s et une fréquence maximale de 3,2 GHz pour les DDR4 les plus rapides avec un contrôleur 64 bits.

Pour réduire la latence d'accès aux données, les processeurs utilisent des mémoires plus rapides que la mémoire principale que l'on appelle des caches [Smi82]. Les caches

possèdent une partie des données présentes dans la mémoire principale. Dans les architectures *manycores*, on retrouve plusieurs niveaux de cache. Plus le niveau est élevé, plus ce cache est loin des processeurs, mais dans ce cas il dispose d'une capacité plus grande qu'un cache proche d'un processeur. On accède aux données contenues dans les caches en quelques cycles, selon le niveau du cache. Pour un cœur, il existe le plus souvent deux caches de premier niveau *Level One* (L1), l'un pour les instructions et l'autre pour les données. Au-dessous, les caches de niveau 2 (L2) peuvent être :

- privés : seulement un cœur peut accéder à ce cache,

- partagés : plusieurs cœurs (mais pas forcément tous) peuvent accéder aux données de ce cache.

Enfin, au sommet de la pyramide, on retrouve les registres. Les unités de calcul utilisent les registres pour effectuer leurs calculs. Selon le type d'architecture les registres ont une taille de 32 ou 64 bits et ils sont accédés en un cycle du processeur.

Dans la pratique, lorsqu'un cœur souhaite lire une donnée, il envoie une requête de lecture à son cache. Si le cache possède la donnée, alors il y a *hit* dans le cache, sinon on parle de *miss*. Si le cache ne dispose pas de la donnée, il fait une requête au niveau supérieur de la hiérarchie mémoire jusqu'à ce que la requête arrive à un étage où se trouve la donnée. Lorsque la réponse est envoyée, elle traverse elle aussi les différents étages de la pyramide, et chaque étage peut mémoriser cette donnée. Par exemple, pour les caches, cela dépend de la politique d'inclusivité. Si un cache L2 est inclusif, alors toutes les données présentes dans les caches L1 le sont aussi dans le cache L2. Il faut donc dimensionner la taille du cache L2 afin qu'il puisse contenir les données mémorisées dans les caches L1. En effet, si le cache L2 est plein, alors il faut évincer une ligne de cache du L2, ce qui engendre l'éviction des données également dans les caches L1.

# 2.2 Caches et cohérence des caches dans les architectures manycores

Nous avons vu que les architectures étaient composées de plusieurs types de mémoires. Dans cette partie, nous allons nous focaliser sur les caches qui sont les plus petites mémoires en dehors des registres des processeurs. Au cours d'une exécution d'un programme, il existe un principe de localité temporelle : lorsqu'une donnée est accédée, il y a de fortes chances qu'elle soit de nouveau accédée dans un futur plus ou moins proche. Les caches permettent de ranger les données déjà accédées dans une mémoire proche des cœurs qui les utilisent, ce qui permet de réduire la latence d'accès.

#### 2.2.1 Architecture des caches

Quel que soit le niveau d'un cache, ce dernier est organisé de la même manière. Il est structuré sous la forme d'agrégations de lignes de cache. Les lignes de cache ont une taille fixe et permettent de mémoriser des données présentes à des adresses mémoires consécutives. Une ligne de cache contient donc plusieurs mots mémoire. Le choix de mémoriser plusieurs mots en un seul bloc a été fait en s'appuyant sur le principe de localité spatiale. En effet, lorsque l'on exécute l'instruction i, il y a de fortes chances que

l'instruction suivante à exécuter soit l'instruction  $\mathbf{i}+\mathbf{1}$ . Pour les données, si l'on est en train de lire une donnée comme un tableau à l'instant  $\mathbf{t}$ , à l'instant  $\mathbf{t}+\mathbf{1}$  il y a une forte probabilité que l'on accède à la suite du tableau qui est rangée en mémoire à l'adresse suivante. En augmentant la granularité lors des requêtes auprès de la mémoire principale, le nombre de messages échangés entre les caches et avec la mémoire principale diminue, en particulier lorsque l'on travaille sur des données proches.

Pour faire correspondre une adresse physique à un emplacement dans un cache, il existe plusieurs stratégies possibles :

**les caches à correspondance directe :** chaque adresse mémoire correspond à un seul emplacement dans le cache.

**les caches totalement associatifs :** les données peuvent être rangées n'importe où dans le cache.

**les caches associatifs par ensemble :** une adresse mémoire correspond à un ensemble d'emplacements et la donnée est rangée dans l'une des lignes réservées à cet ensemble.

Chacun de ces types possède des avantages et des inconvénients. Le calcul de l'entrée pour un cache à correspondance directe est facile à réaliser, il s'agit de l'adresse mémoire modulo la taille du cache. En revanche, si plusieurs données importantes pour le programme correspondent à la même ligne, elles vont se gêner en s'évinçant l'une l'autre à chaque accès, et ce même lorsque d'autres lignes du cache sont libres.

Les caches totalement associatifs n'ont pas ce problème, car une donnée peut être rangée dans n'importe quelle case. En revanche, il n'existe pas de fonction simple pour savoir à quel endroit est rangé une donnée. Il faut donc tester toutes les entrées pour trouver où se trouve la ligne de cache qui nous intéresse.

Pour remédier à ce problème, les caches associatifs par ensemble combinent les avantages de chacun de ces deux types. Le cache est divisé en plusieurs ensembles, eux-mêmes composés de plusieurs voies. Ainsi, une donnée peut être rangée dans l'une des voies d'un ensemble donné. Le calcul de l'entrée correspond donc à l'adresse modulo le nombre d'ensembles, puis il faut tester chacune des voies de l'ensemble afin de trouver la ligne de cache à laquelle on souhaite accéder.

#### 2.2.2 Cohérence des caches

Dans le cadre de nos travaux, nous nous intéressons aux architectures *manycores* à mémoire partagée et cohérente. Lorsque l'on exécute un calcul sur plusieurs cœurs, ces derniers peuvent lire et écrire les mêmes données. Or lorsque qu'une machine utilise des caches, les cœurs font des requêtes seulement à leur cache et si ces derniers possèdent la donnée dans leur mémoire interne, ils répondent à la requête sans repasser par la mémoire principale.

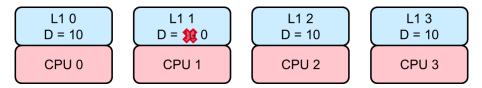

La figure 2.4 montre un exemple avec quatre cœurs et leurs caches L1. Tous les caches L1 possèdent la donnée **D** qui vaut 10. Lorsque le cœur 1 change la valeur de **D**, son cache L1 est mis à jour. Sans communication entre les caches L1, la valeur de **D** est différente selon le cache. En effet, dans cet exemple, **D** vaut 0 dans le cache L1 1 et 10

FIGURE 2.4 – Exemple avec 4 cœurs partageant des données

dans les autres caches L1. Il faut donc mettre en place un mécanisme de communication pour éviter qu'un tel problème se pose. Ce problème est connu sous le nom de cohérence de caches.

La gestion de la cohérence des caches peut être faite en logiciel ou en matériel. Dans le cas d'une gestion logicielle, le programmeur doit lui même invalider les lignes de cache avant qu'un cœur en modifie la valeur. Lorsque la cohérence des caches est gérée au niveau matériel, celle-ci nécessite du matériel supplémentaire mais l'écriture du logiciel n'est plus impactée. Dans le cadre de cette thèse, nous nous intéressons à la cohérence de caches effectuée de manière matérielle.

Il existe deux catégories de protocole de cohérence de caches matériel : ceux basés sur l'espionnage (*snoop*) et ceux basés sur un répertoire (*directory based*).

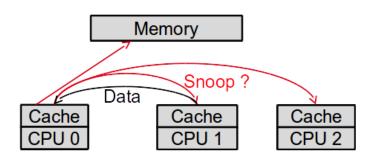

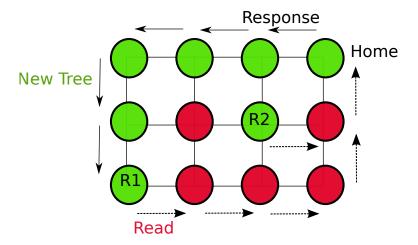

FIGURE 2.5 – Protocole de cohérence de caches basé sur l'espionnage

Dans le cas des protocoles de type espionnage, un cœur envoie un message de diffusion (*broadcast*) à tous les cœurs lorsqu'il veut accéder à une donnée, comme le montre la figure 2.5. Ce type de protocole passe difficilement à l'échelle car plus le nombre de cœurs, augmente plus le nombre de messages pour la cohérence sur le réseau augmente.

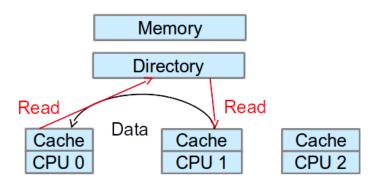

Le deuxième type de protocole de cohérence de caches utilise un répertoire comme sur la figure 2.6. Lorsqu'un cœur veut accéder à une donnée, il en fait la requête à un répertoire centralisé au niveau du cache de dernier niveau qui, lui, connaît la liste de tous les caches qui contiennent cette donnée. On appelle cette liste la liste des copies. La représentation la plus simple de la liste des copies est un champ de bits de la taille du nombre de cache L1, ce qui correspond aux nombres de cœurs lorsqu'il n'y a pas de séparation des caches d'instructions et de données. Quand un bit est à 1, cela signifie

FIGURE 2.6 – Protocole de cohérence de caches basé sur un répertoire

que ce cache contient la donnée. Cette solution permet de générer seulement le nombre de messages nécessaires. En revanche, l'implémentation la plus triviale de ce type de protocole passe difficilement à l'échelle à cause du coût de stockage du répertoire qui peut atteindre la taille des données mémorisées.

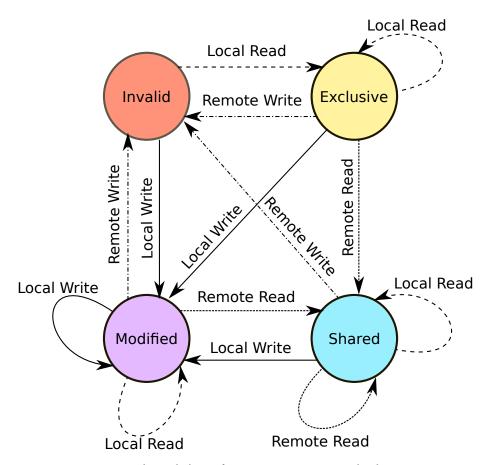

Le répertoire doit aussi contenir des informations sur l'état de la ligne de cache et en particulier l'état dans lequel est la machine à états du protocole de haut niveau. L'un des protocoles de haut niveau le plus utilisé est le protocole *Modified*, *Exclusive*, *Shared*, *Invalid* (MESI), dont les états stables, par opposition aux états transitoires qui eux sont le reflet de l'implémentation, sont les suivants :

*Modified*: la ligne a été modifiée et ce cache contient la donnée la plus à jour, par contre la mémoire principale n'est pas à jour;

*Exclusive*: la ligne de cache contient la donnée la plus à jour, tout comme la mémoire principale, en revanche aucun autre cache ne possède cette donnée;

**Shared:** la ligne de cache contient la donnée la plus à jour mais on ne sait pas si d'autres caches l'ont en mémoire. De plus, on ne sait pas si la mémoire principale est à jour;

*Invalid* : la ligne de cache n'est pas valide, c'est-à-dire qu'elle ne contient pas de données.

L'ensemble de ces états permet de savoir où se trouve la donnée la plus à jour. On peut ainsi savoir à l'éviction de la ligne de cache si les données doivent être mises à jour dans le niveau supérieur de la hiérarchie mémoire. Lorsque la ligne a été modifiée et qu'une demande d'écriture ou de lecture arrive d'un autre cache, il faut mettre à jour la mémoire principale en envoyant un message d'écriture différée (*write-back*).

La figure 2.7 montre les différentes transitions pour passer d'un état à un autre. Sur cette figure, on remarque qu'il existe quatre types de transitions :

Local Read: accès en lecture du même cache;

Remote Read: accès en lecture d'un autre cache;

Local Write: accès en écriture du même cache;

FIGURE 2.7 – Machine à états finis pour un protocole de type MESI

Remote Write: accès en écriture d'un autre cache.

Le protocole *Modified, Owned, Exclusive, Shared, Invalid* (MOESI) est une amélioration du protocole MESI où l'état *Owned* est ajouté. Lorsque la ligne de cache est dans cet état, cette ligne contient la donnée la plus à jour mais d'autres caches peuvent aussi avoir cette donnée et la mémoire principale n'est pas à jour. Cet état permet d'ajouter un état entre l'état *shared* et *modified*, c'est-à-dire lorsque la mémoire principale doit être mise à jour. Ainsi, lorsqu'une donnée a été modifiée et qu'un autre cœur souhaite lire cette donnée, le cache qui a modifié cette donnée peut satisfaire la requête sans envoyer un message d'écriture différée à la mémoire principale. Ce nouvel état permet de limiter les messages à la mémoire principale.

## 2.3 Représentation de la liste des copies

Dans le cas des protocoles de cohérence de caches avec un répertoire, la taille de chaque entrée dans le répertoire dépend essentiellement de la représentation de la liste des copies. En effet, comme le montre la figure 2.8, chaque entrée du répertoire comporte plusieurs informations :

Tag: l'identifiant de l'adresse physique de la ligne de cache;

**State :** l'état de la ligne de cache selon le protocole de haut niveau choisi (M, O, E, S ou I dans le cas du MOESI par exemple);

**Sharers**: la liste des caches qui possèdent cette ligne (c'est-à-dire la liste des copies).

| Tag State Sharers |

|-------------------|

|-------------------|

FIGURE 2.8 – Format d'entrée dans un répertoire avec la liste des copies

Parmi toutes ces informations, seule la représentation de la liste des copies évolue en fonction du nombre de cœurs dans le système. Ainsi, lorsque le nombre de cœurs augmente, le coût de la liste des copies augmente également, ce qui constitue un frein au passage à l'échelle des protocoles avec un répertoire. En effet, pour une ligne de cache de 64 octets (soit 16 mots de 32 bits), la taille du champ de bits nécessaire pour 1024 cœurs est deux fois plus importante que la taille nécessaire aux données elles-mêmes. Pour résoudre ce problème, on pourrait augmenter la taille des lignes de cache, mais cela augmente le nombre de données rapatriées dans le cache et potentiellement non utilisées, ainsi que le nombre de faux partages. On parle de faux partage quand plusieurs cœurs accèdent à des données différentes mais qui se trouvent dans la même ligne de cache. Par exemple, un cœur co accède au deuxième mot de la ligne de cache et un autre cœur c1 accède au sixième mot de la ligne de cache, cette ligne sera donc partagée entre c0 et c1 alors qu'ils n'utilisent pas les mêmes données. Plus on augmente la taille de la ligne de cache, plus on augmente le nombre de faux partages. Ce n'est donc pas une solution et c'est pourquoi plusieurs travaux de recherche s'intéressent à réduire la taille de la représentation de la liste des copies.

| Directory sha | aring list |      |                 |       |

|---------------|------------|------|-----------------|-------|

| L1 0          | L1 1       | L1 2 | L1 3            |       |

| 1 (           | 0          | 1    | 0               |       |

| 1             | 1          | 1    | 0               |       |

|               |            |      |                 |       |

| L1 0          | L1         | 1    | <b>▲</b> ● L1 2 | L1 3  |

| CPU 0         | CPU        | J 1  | CPU 2           | CPU 3 |

FIGURE 2.9 – Exemple de liste des copies représentée avec un champ de bits complet

La figure 2.9 montre un exemple d'une liste des copies représentée par un champ de bits. Dans cet exemple, la donnée représentée par un cercle bleu est présente dans les caches L1 des cœurs 0, 1 et 2. Les bits 0, 1 et 2 du champ de bits sont donc mis à 1 alors que le bit 3 vaut 0. La donnée représentée par un triangle rouge est présente dans les caches 0 et 2. On peut lire cette même information dans la liste des copies.

Dans la cadre de cette thèse, nous allons tenter de répondre à la question suivante : Quelles sont les représentations de la liste des copies qui permettent de réduire la taille du répertoire des protocoles de cohérence de caches?

## 2.4 Caractéristiques des applications parallèles

Dans les architectures à mémoire partagée, les tâches des applications parallèles communiquent entre elles à l'aide de données partagées même si la plupart des données sont privées comme le montre la figure 2.10.

FIGURE 2.10 – Nombre de lignes de cache partagées par n cœurs

Sur cette figure, l'histogramme représente le nombre de lignes de cache partagées par n cœurs, pour n compris entre 1 et 64. Cette figure correspond à la moyenne du nombre de lignes de cache partagées pour 13 applications provenant de SPLASH 2 [WOT+95] et PARSEC [BKSL08], applications parallèles de référence pour l'évaluation des architectures manycores. On remarque que 93,4% des lignes de cache sont partagées par au maximum 8 cœurs pour une architecture de 64 cœurs. On note également que pratiquement la moitié des lignes de cache sont privées et ce pour la durée de vie de l'application. Cette figure a été obtenue en analysant le nombre de cœurs différents ayant accédé à chaque donnée tout au long de la durée de vie de l'application. Ce choix permet d'obtenir une borne supérieure du nombre de copies et ainsi ne pas être dépendant de la taille des caches. En effet, au cours de la durée de vie de l'application, le nombre de copies peut fortement évoluer.

En partant de ces observations, une question légitime se pose : **Peut-on exploiter les** caractéristiques dynamiques des applications pour trouver une représentation plus compacte de la liste des copies?

#### 2.5 Évaluation des représentations de la liste des copies

Nous venons de voir que les protocoles de cohérence de caches ont des difficultés à passer à l'échelle pour les architectures *manycores*. Au cours du développement des nouveaux protocoles de cohérence de caches, les architectes peuvent utiliser différentes stratégies pour leur permettre d'évaluer les performances de leur protocole, allant des approches analytiques à gros grain [JF96] à la simulation.

Dans cette thèse, nous nous intéressons aux techniques de simulation pour des architectures *manycores*. Afin d'évaluer les performances des protocoles, les architectes peuvent utiliser des simulateurs plus ou moins précis. Plus le simulateur est précis, plus la description du protocole doit l'être, et donc le temps de développement d'un protocole augmente. De même, plus la description du protocole est détaillée, plus on augmente le temps de simulation.

Il existe un nombre important de simulateurs et gem5 [BBB+11], qui permet de simuler des architectures multiprocesseurs au niveau système, est l'un des plus utilisés par les architectes. Dans le cas du simulateur gem5, le temps de simulation nécessaire au boot d'un Linux sur 64 cœurs Alpha est de 20 minutes.

Si l'on ajoute de la précision en utilisant par exemple SystemCASS [Sys], un simulateur basé sur SystemC, il faut 14 minutes pour démarrer linux avec un seul cœur, plusieurs heures pour une plateforme avec 4 cœurs et plus de 3 jours avec 16 cœurs. Le temps de simulation augmente plus rapidement que linéairement avec le nombre de cœurs, ce qui rend la simulation d'une architecture *manycore* trop lente pour être exécutée dans un temps raisonnable.

Une simulation du système complet décrit au niveau *Register Transaction Level* (RTL) n'est pas possible pour une architecture *manycore* car cela est encore plus lent qu'avec les simulations basées sur SystemC. Par contre, si l'on dispose d'un modèle RTL et d'un émulateur, l'émulation est une solution viable car rapide. Avec un émulateur, le RTL doit être synthétisé puis le design est chargé sur l'émulateur. Pour l'exécution, l'émulateur dispose de matériel dédié (principalement de la logique reconfigurable) qui permet de reproduire le comportement du RTL. En revanche, pour de l'exploration architecturale, il faut développer chacun des modèles au niveau RTL, ce qui n'est pas négligeable en temps de développement.

Les architectes doivent donc trouver le bon compromis entre précision et temps (développement et exécution). Pour cela, nous pouvons par exemple ne modéliser qu'une partie de l'architecture et nous concentrer sur une modélisation fine des caches, du protocole de cohérence, et du réseau. Une autre solution est de modéliser une partie du système avec un niveau d'abstraction plus élevé et ainsi modéliser seulement les états stables. Dans ce cas, on ne pourra pas prouver que la proposition est stable, sans deadlock. Par contre, cette solution permet de fixer la borne maximale des performances atteignables. Ainsi, l'évaluation du protocole ne correspond pas à l'évalution d'une implémentation matérielle mais bien des capacités du protocole en supposant que l'on peut atteindre les conditions optimales.

Dans cette thèse, nous allons essayer de répondre à la question suivante : Comment peut-on évaluer un protocole de cohérence de caches et plus particulièrement

#### la représentation de la liste des copies pour une architecture manycore?

#### 2.6 Conclusion

Tout au long de ce chapitre nous avons soulevé plusieurs problèmes autour des protocoles de cohérence de caches et de leur simulation. Nous avons également défini un certains nombre d'hypothèses sur le type des architectures utilisées. Ces hypothèses sont les suivantes :

- nous considérons les architectures manycores à mémoire partagée;

- nous nous intéressons seulement aux protocoles de cohérence de caches matériels. Dans notre étude nous avons considéré que :

- les caches ont une politique d'écriture différée;

- le protocole de cache de haut niveau est de type MOESI.

Ce sont des propriétés nécessaires pour la simulation, mais nos travaux peuvent être appliqués à des caches dont l'écriture se fait après chaque modification (*write-through*) ou à un autre type de protocole de cache de haut niveau.

En partant de ces hypothèses et de nos considérations, les questions auxquelles nous allons tenter de répondre sont les suivantes :

- Quelles sont les représentations de la liste des copies qui permettent de réduire la taille du répertoire des protocoles de cohérence de caches?

- Comment peut-on évaluer un protocole de cohérence de caches et plus particulièrement la représentation de la liste des copies pour une architecture manycore?

- Peut-on exploiter les caractéristiques dynamiques des applications pour trouver une représentation plus compacte de la liste des copies?

Les prochains chapitres de ce document ont pour but de répondre aux différentes questions énoncées ci-dessus.

# Chapitre 3: Cohérence des caches dans une architecture manycore à mémoire partagée

| Sommaire |                                              |                                |    |  |

|----------|----------------------------------------------|--------------------------------|----|--|

| 3.1      | Proto                                        | coles basés sur l'espionnage   | 15 |  |

|          | 3.1.1                                        | Flexible snooping              | 16 |  |

|          | 3.1.2                                        | In-Network Coherence Filtering | 17 |  |

| 3.2      | Protocoles avec répertoire limité            |                                |    |  |

|          | 3.2.1                                        | Ackwise                        | 18 |  |

|          | 3.2.2                                        | Coarse bit-vector directory    | 19 |  |

|          | 3.2.3                                        | Virtualisation des CIDs        | 19 |  |

| 3.3      | Protocoles de cohérence de caches dynamiques |                                |    |  |

|          | 3.3.1                                        | Liste chaînée                  | 20 |  |

|          | 3.3.2                                        | Champ de bits limité           | 21 |  |

|          | 3.3.3                                        | Sponge directory               | 22 |  |

|          | 3.3.4                                        | SPACE                          | 23 |  |

| 3.4      | Autre                                        | s propositions                 | 24 |  |

|          | 3.4.1                                        | Scalable Interface Coherence   | 24 |  |

|          | 3.4.2                                        | In-Network Cache Coherence     | 24 |  |

|          | 3.4.3                                        | Classifications des données    | 25 |  |

|          | 3.4.4                                        | Fenêtres temporelles           | 26 |  |

| 3.5      | Concl                                        | usion                          | 27 |  |

Nous avons vu dans la problématique (chapitre 2) qu'il existe deux classes de protocoles de cohérence de caches : ceux basés sur l'espionnage et ceux utilisant un répertoire. Seuls ces derniers possèdent une liste des copies. Néanmoins, ces deux classes tendent à se rejoindre avec d'un côté l'ajout de filtres pour limiter la délivrance de messages à tous les cœurs dans le cas des protocoles basés sur l'espionnage et de l'autre côté une représentation moins précise de la liste des copies pour les protocoles utilisant un répertoire.

## 3.1 Protocoles basés sur l'espionnage

Parmi les protocoles basés sur l'espionnage, on observe que des filtres sont de plus en plus utilisés afin de réduire le nombre de messages. Ces filtres permettent également de diminuer la latence car les requêtes ne doivent plus attendre les réponses de l'ensemble des cœurs.

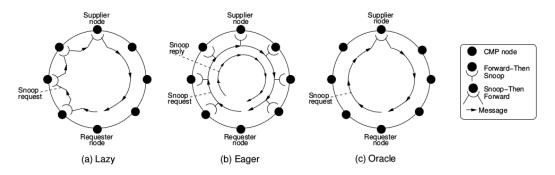

#### 3.1.1 Flexible snooping

Dans flexible snooping [SST06] les auteurs proposent d'ajouter des prédicteurs afin de se rapprocher de la solution optimale du point de vue de la latence. Dans leur exemple, le réseau a une topologie en anneau. La figure 3.1 montre trois types de communication. Dans le cas lazy, à chaque nœud le cache est interrogé, et lorsqu'il ne possède pas la donnée, la requête est transférée au cache suivant. Lorsque la donnée est présente, la réponse est envoyée au demandeur sans interroger les autres caches. La latence dépend donc de la distance sur l'anneau entre le demandeur et le premier cache possédant la donnée. Néanmoins, la topologie du réseau étant un anneau, la réponse doit traverser l'ensemble des nœuds suivants avant de revenir au demandeur mais ces nœuds ne sont pas interrogés, ils transfèrent simplement la requête au nœud suivant. Dans l'exemple eager, lorsqu'un nœud recoit une requête, il la transfère au nœud suivant puis il interroge son cache. Tous les caches qui disposent de la donnée répondent à la requête. Cette solution permet de réduire la latence, car la requête est transférée directement. Néanmoins, tous les caches sont interrogés pour chaque requête et le nombre de messages générés est plus élevé. Enfin, le troisième type de communication oracle montre la solution idéale que les auteurs souhaitent atteindre. Dans ce cas, la requête est transférée directement au nœud dont le cache possède la donnée et seulement ce cache est interrogé. Cette solution permet de minimiser la latence d'accès aux données. Dans flexible snooping, le choix du type de traitement à effectuer à chaque nœud est fait à l'aide d'un prédicteur. Ce dernier permet de choisir si la requête est traitée avant d'être transférée, si elle est transférée puis traitée ou si elle est simplement transférée.

FIGURE 3.1 – Trois types de communication dans un réseau en anneau

Cette proposition est basée sur une topologie en anneau, et lorsqu'on utilise cette topologie, un nœud communique seulement avec ses deux voisins. Lorsqu'un nœud reçoit une requête, il la transfère seulement à son autre voisin. Ainsi, la requête passe par tous les nœuds avant de revenir à l'émetteur. Lorsqu'on utilise un réseau de type grille 2D, la requête ne passe pas nécessairement par tous les nœuds. Lorsque l'on souhaite envoyer un message à tous les autres nœuds (messages de diffusion), la requête peut être dupliquée afin de parcourir l'ensemble des nœuds plus rapidement. Les messages de diffusion doivent être limités lorsqu'on utilise un réseau de type grille car ils saturent rapidement le réseau. Ainsi, la proposition *flexible snooping* ne peut pas être appliquée à ce type de topologie qui est largement répandue dans les architectures *manycores*.

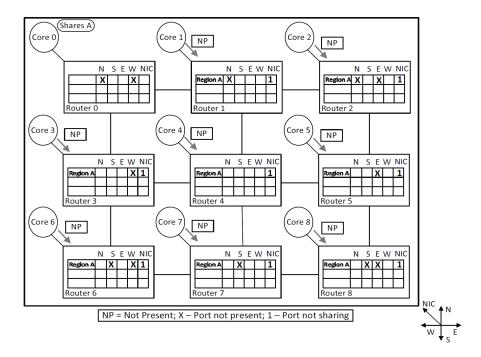

#### 3.1.2 In-Network Coherence Filtering

Les auteurs de *In-Network Coherence Filtering* [APJ09a] proposent d'ajouter des filtres au niveau des routeurs. Pour cela, les filtres maintiennent une table pour savoir si la donnée est partagée par au minimum un nœud dans chacune des directions. Ainsi lorsqu'un message est reçu, le routeur sait vers quelle direction il peut diffuser le message. Afin de limiter la taille des filtres, les auteurs proposent de maintenir les informations de cohérence au niveau d'une région, c'est-à-dire de plusieurs lignes de cache consécutives.

FIGURE 3.2 – INCF: exemple d'architecture avec des filtres au niveau des routeurs

La figure 3.2 montre un exemple avec 9 cœurs où le cœur 0 partage la région A. On remarque qu'il existe une entrée pour la région dans chaque filtre. De plus, on remarque que seuls les liens menant vers le cœur 0 avec un algorithme de routage XY sont activés. Cette solution permet de limiter les messages diffusés sur le réseau, mais les expérimentations ont été faites avec seulement 16 cœurs. Lorsqu'on augmente le nombre de nœuds dans le réseau, il faut augmenter la taille des tables au niveau de chaque routeur. De plus, lorsqu'on augmente la taille du réseau, les liens actifs pour chaque région augmentent et ainsi le nombre de messages diffusés augmente. Ces deux raisons font que ce protocole passe difficilement à l'échelle des *manycores*.

En l'état actuel des choses, et malgré l'ajout de filtres, les protocoles de cohérence de caches basés sur l'espionnage ne permettent pas de passer à l'échelle des *many-cores* [SHW11].

# 3.2 Protocoles avec répertoire limité

Pour les protocoles de cohérence de caches utilisant un répertoire, la taille de ce dernier est un frein au passage à l'échelle à cause de la représentation de la liste des copies. Une solution pour limiter cette taille est d'utiliser un répertoire imprécis, tout en garantissant *a minima* que tous les caches concernés par un message le recevront.

#### 3.2.1 Ackwise

Le protocole Ackwise proposé par Kurian  $et~al.~[{\rm KMP}^+10]$  limite le nombre de copies (c'est-à-dire le nombre de caches L1 qui possèdent la donnée). Pour cela, le protocole possède deux modes : le premier dans lequel le répertoire contient la liste des copies exacte et le deuxième où les messages de cohérence sont envoyés en diffusion. Lorsque le nombre de copies est inférieur ou égal à k, toutes les copies peuvent être mémorisées dans le répertoire.

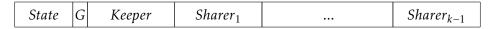

Figure 3.3 – Répertoire du protocole Ackwise

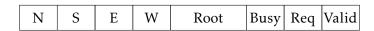

Le répertoire utilisé par Ackwise est présenté dans la figure 3.3 et contient les informations suivantes :

**State :** ces premiers bits sont nécessaires pour mémoriser l'état de la machine à états du protocole MOESI;

**G** (*Global*): ce bit est égal à 1 lorsque le mode diffusion est activé et 0 sinon, ce qui correspond au mode précis;

**Keeper:** ce champ est utilisé pour mémoriser le *Core ID* (CID) dont le cache est responsable de la cohérence;

**Sharers**: ces champs servent à mémoriser les identifiants des caches contenant les copies. Chaque champ peut contenir un seul CID.

Le *keeper* est le cache responsable de la cohérence, c'est lui qui répond aux requêtes de lecture. Au-dessus de k copies, il n'y a pas plus de place dans le répertoire, on utilise alors des messages de diffusion. Pour éviter de saturer le réseau avec ce type de messages, le champ  $Sharer_k$  est utilisé pour mémoriser un compteur du nombre de copies. Ainsi, seuls les caches L1 qui disposent de la donnée répondent à la requête, et le répertoire attend seulement ce nombre de réponses. Le nombre de champs pour mémoriser les copies dans le répertoire est fixé lors de l'implémentation et correspond au seuil k.

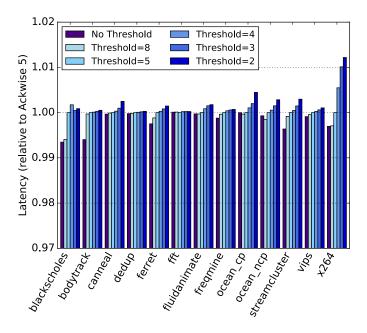

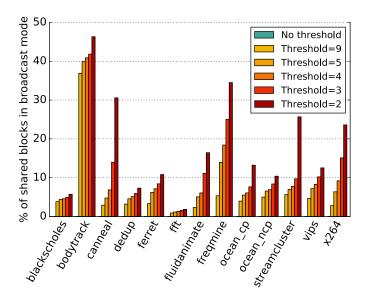

Dans leur article, les auteurs évaluent les performances d'Ackwise pour plusieurs valeurs de k comprises entre 2 et 64. Plus le seuil est élevé, plus les performances sont proches du protocole avec un répertoire exact mais le coût matériel est élevé. En effet, le coût matériel nécessaire pour mémoriser la liste des copies correspond au nombre de bits pour encoder le CID multiplié par le seuil k. Ainsi, pour réduire la taille du répertoire, il faut trouver un compromis entre performance et quantité de ressources. Pour cela les auteurs proposent de fixer un seuil bas, de l'ordre de quelques copies

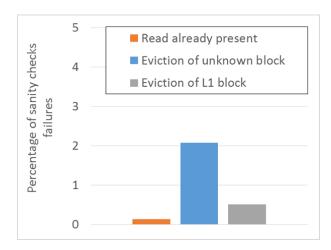

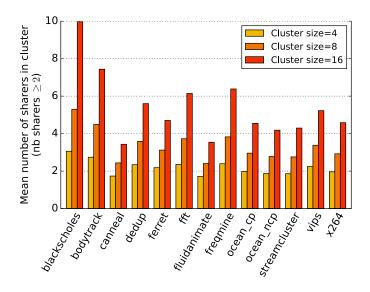

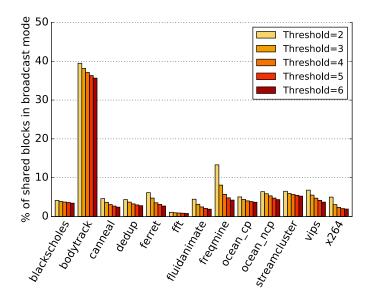

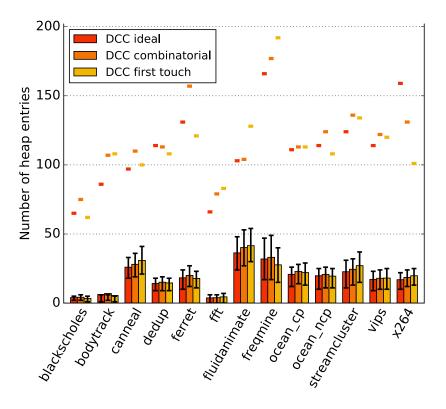

(inférieur à 8).