## Distributed runtime system with global address space and software cache coherence for a data-flow task model

François Gindraud

## ▶ To cite this version:

François Gindraud. Distributed runtime system with global address space and software cache coherence for a data-flow task model. Data Structures and Algorithms [cs.DS]. Université Grenoble Alpes, 2018. English. NNT: 2018GREAM001. tel-01891061

## HAL Id: tel-01891061 https://theses.hal.science/tel-01891061

Submitted on 9 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique

Arrêté ministèriel : 25 mai 2016

Présentée par

## François Gindraud

Thèse dirigée par Fabrice Rastello et co-encadrée par Albert Cohen

préparée au sein du Laboratoire d'Informatique de Grenoble dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

# Système distribué à adressage global et cohérence logicielle pour l'exécution d'un modèle de tâche à flot de données

Thése soutenue publiquement le **11 janvier 2018**, devant le jury composé de :

## **Madame Christine Morin**

Directeur de Recherche, Inria, Président

#### Monsieur Fabrice Rastello

Directeur de Recherche, Inria, Directeur de thèse

#### **Monsieur Albert Cohen**

Directeur de Recherche, Inria, Co-Encadrant de thèse

#### Monsieur Lawrence Rauchwerger

Full Professor, Texas A&M University, Rapporteur

## Monsieur Mikel Luján

Royal Society University Research Fellow, University of Manchester, Rapporteur

#### Monsieur Francesco Zappa Nardelli

Directeur de Recherche, Inria, Examinateur

#### Monsieur Frédéric Desprez

Directeur de Recherche, Inria, Examinateur

#### Monsieur Pierre Guironnet de Massas

Ingénieur, Kalray, Examinateur

#### Abstract

Distributed systems are widely used in HPC (*High Performance Computing*). Owing to rising energy concerns, some chip manufacturers moved from multi-core CPUs to MPSoC (*Multi-Processor System on Chip*), which includes a distributed system on one chip.

However distributed systems – with distributed memories – are hard to program compared to more friendly shared memory systems. A family of solutions called DSM (Distributed Shared Memory) systems has been developed to simplify the programming of distributed systems. DSM systems include NUMA architectures, PGAS languages, and distributed task runtimes. The common strategy of these systems is to create a global address space of some kind, and automate network transfers on accesses to global objects. DSM systems usually differ in their interfaces, capabilities, semantics on global objects, implementation levels (hardware / software), ...

This thesis presents a new software DSM system called Givy. The motivation of Givy is to execute programs modeled as dynamic task graphs with data-flow dependencies on MPSoC architectures (MPPA). Contrary to many software DSM, the global address space of Givy is indexed by real pointers: raw C pointers are made global to the distributed system. Givy global objects are memory blocks returned by malloc(). Data is replicated across nodes, and all these copies are managed by a software cache coherence protocol called Owner Writable Memory. This protocol can relocate coherence metadata, and thus should help execute irregular applications efficiently. The programming model cuts the program into tasks which are annotated with memory accesses, and created dynamically. Memory annotations are used to drive coherence requests, and provide useful information for scheduling and load-balancing.

The first contribution of this thesis is the overall design of the Givy runtime. A second contribution is the formalization of the Owner Writable Memory coherence protocol. A third contribution is its translation in a model checker language (*Cubicle*), and correctness validation attempts. The last contribution is the detailed allocator subsystem implementation: the choice of real pointers for global references requires a tight integration between memory allocator and coherence protocol.

#### Résumé

Les architectures distribuées sont fréquemment utilisées pour le calcul haute performance (HPC). Afin de réduire la consommation énergétique, certains fabricants de processeurs sont passés d'architectures multi-cœurs en mémoire partagée aux MPSoC. Les MPSoC (*Multi-Processor System On Chip*) sont des architectures incluant un système distribué dans une puce.

La programmation des architectures distribuées est plus difficile que pour les systèmes à mémoire partagée, principalement à cause de la nature distribuée de la mémoire. Une famille d'outils nommée DSM (Distributed Shared Memory) a été développée pour simplifier la programmation des architectures distribuées. Cette famille inclut les architectures NUMA, les langages PGAS, et les supports d'exécution distribués pour graphes de tâches. La stratégie utilisée par les DSM est de créer un espace d'adressage global pour les objets du programme, et de faire automatiquement les transferts réseaux nécessaires lorsque ces objets sont utilisés. Les systèmes DSM sont très variés, que ce soit par l'interface fournie, les fonctionnalités, la sémantique autour des objets globalement adressables, le type de support (matériel ou logiciel), ...

Cette thèse présente un nouveau système DSM à support logiciel appelé Givy. Le but de Givy est d'exécuter sur des MPSoC (MPPA) des programmes sous la forme de graphes de tâches dynamiques, avec des dépendances de flot de données (data-flow). L'espace d'adressage global (GAS) de Givy est indexé par des vrais pointeurs, contrairement à de nombreux autres systèmes DSM à support logiciel : les pointeurs bruts du langage C sont valides sur tout le système distribué. Dans Givy, les objets globaux sont les blocs de mémoire fournis par malloc(). Ces blocs sont répliqués entre les nœuds du système distribué, et sont gérés par un protocole de cohérence de cache logiciel nommé Owner Writable Memory. Le protocole est capable de déplacer ses propres métadonnées, ce qui devrait permettre l'exécution efficace de programmes irréguliers. Le modèle de programmation impose de découper le programme en tâches créées dynamiquement et annotées par leurs accès mémoire. Ces annotations sont utilisées pour générer les requêtes au protocole de cohérence, ainsi que pour fournir des informations à l'ordonnanceur de tâche (spatial et temporel).

Le premier résultat de cette thèse est l'organisation globale de Givy. Une deuxième contribution est la formalisation du protocole Owner Writable Memory. Le troisième résultat est la traduction de cette formalisation dans le langage d'un model checker (Cubicle), et les essais de validation du protocole. Le dernier résultat est la réalisation et explication détaillée du sous-système d'allocation mémoire : le choix de pointeurs bruts en tant qu'index globaux nécessite une intégration forte entre l'allocateur mémoire et le protocole de cohérence de cache.

# Contents

| Abstract |       |                                           |                 |

|----------|-------|-------------------------------------------|-----------------|

| Ré       | ésum  | é                                         | iv              |

| Co       | onten | ats                                       | $\mathbf{v}$    |

| 1        | Intr  | oduction                                  | 1               |

|          | 1.1   | High Performance Computing                | 1               |

|          |       | 1.1.1 Hardware Performance                | 1               |

|          |       | 1.1.2 Shared Memory vs Distributed Memory | 5               |

|          | 1.2   | Distributed Shared Memory                 | 7               |

|          |       | 1.2.1 Classification                      | 8               |

|          |       | 1.2.2 Families                            | 10              |

|          | 1.3   | Givy                                      | 13              |

|          | 1.4   | Outline & Contributions                   | 15              |

| 2        | Dun   | atime                                     | 17              |

| 4        | 2.1   | Virtual Memory                            | 17              |

|          | 2.1   | 2.1.1 Common Uses                         | 17              |

|          |       | 2.1.1 Common Oses                         | 19              |

|          |       | 2.1.2 Implementation                      | 19              |

|          |       | 2.1.4 In Givy                             | 20              |

|          | 2.2   | Givy                                      | $\frac{20}{20}$ |

|          | 2.2   | 2.2.1 Task                                | $\frac{20}{20}$ |

|          |       | 2.2.1 Task                                | $\frac{20}{22}$ |

|          |       | 2.2.3 Allocator                           | 26              |

|          |       | 2.2.4 Coherence Protocol                  | $\frac{20}{27}$ |

|          | 2.3   | Implementation                            | $\frac{27}{27}$ |

|          | 2.3   | 2.3.1 Version 1                           | $\frac{27}{27}$ |

|          |       | 2.3.2 Version 2                           | 28              |

|          |       | 2.3.3 Network                             | $\frac{20}{29}$ |

|          | 2.4   | Extensions                                | $\frac{29}{30}$ |

|          | 2.4   | 2.4.1 Region Split / Merge                | 30              |

|          |       | 2.4.1 Region Split / Nierge               | $30 \\ 31$      |

|          |       | 2.4.2 Region Set                          | 31              |

|          |       | 2.4.4 Stack and Globals Support           | $\frac{31}{32}$ |

|          |       | 2.4.4 Stack and Globals Support           | 32<br>32        |

|   | 2.5                   | State   | of the Art                          | 32        |  |  |  |

|---|-----------------------|---------|-------------------------------------|-----------|--|--|--|

| 3 | Coherence Protocol 37 |         |                                     |           |  |  |  |

|   | 3.1                   | Forma   | lization Flavors                    | 37        |  |  |  |

|   |                       | 3.1.1   | Operational                         | 37        |  |  |  |

|   |                       | 3.1.2   | Axiomatic                           | 38        |  |  |  |

|   | 3.2                   | Cache   | Coherence Protocols 101             | 40        |  |  |  |

|   |                       | 3.2.1   | VI                                  | 41        |  |  |  |

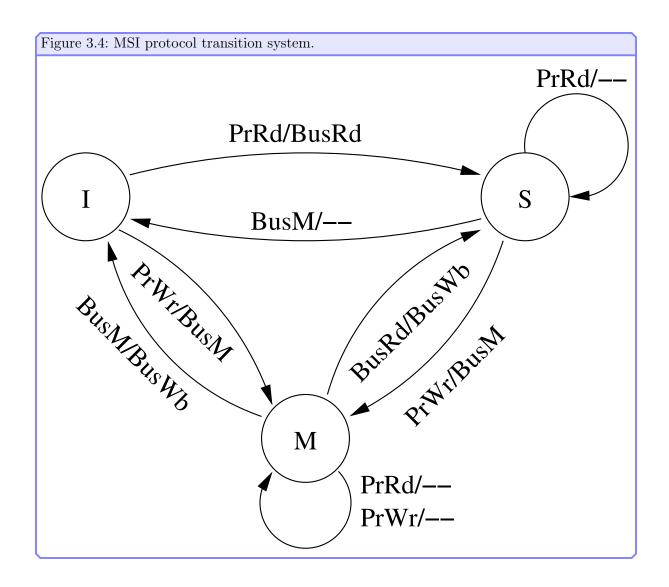

|   |                       | 3.2.2   | MSI - Snooping                      | 42        |  |  |  |

|   |                       | 3.2.3   | MSI - Directory                     | 44        |  |  |  |

|   |                       | 3.2.4   | MSI - Distributed                   | 44        |  |  |  |

|   | 3.3                   |         | Coherence Protocol                  | 44        |  |  |  |

|   | ა.ა                   | 3.3.1   |                                     | 45        |  |  |  |

|   |                       |         | Formal Model                        |           |  |  |  |

|   |                       | 3.3.2   | Discussion and Extensions           | 51        |  |  |  |

| 4 | Mei                   |         | Allocator                           | <b>53</b> |  |  |  |

|   | 4.1                   | Memor   | ry Allocation                       | 53        |  |  |  |

|   |                       | 4.1.1   | API                                 | 54        |  |  |  |

|   |                       | 4.1.2   | Performance Criteria And Trade-offs | 56        |  |  |  |

|   |                       | 4.1.3   | Classic Allocator Structures        | 57        |  |  |  |

|   | 4.2                   | Global  | l Address Space Management          | 59        |  |  |  |

|   | 4.3                   |         | tors – State of the Art             | 61        |  |  |  |

|   | 4.4                   |         | tor V1                              | 62        |  |  |  |

|   |                       | 4.4.1   | Page Mapper                         | 63        |  |  |  |

|   |                       | 4.4.2   | Page Mapper Base                    | 64        |  |  |  |

|   |                       | 4.4.3   | Page Mapper Fixed                   | 64        |  |  |  |

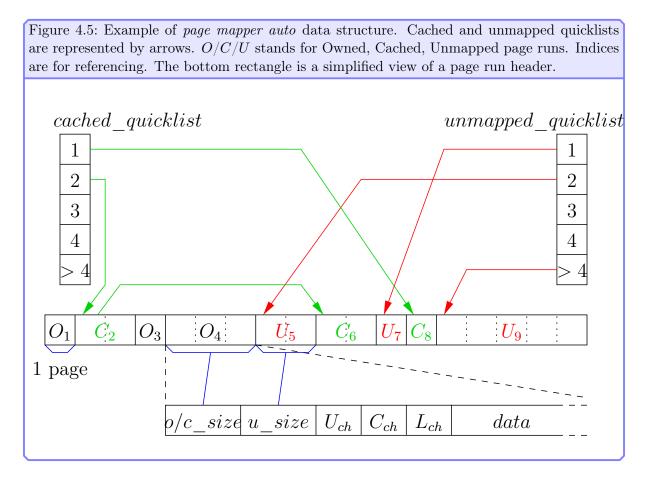

|   |                       | 4.4.4   | Page Mapper Auto                    | 66        |  |  |  |

|   |                       | 4.4.4   |                                     | 68        |  |  |  |

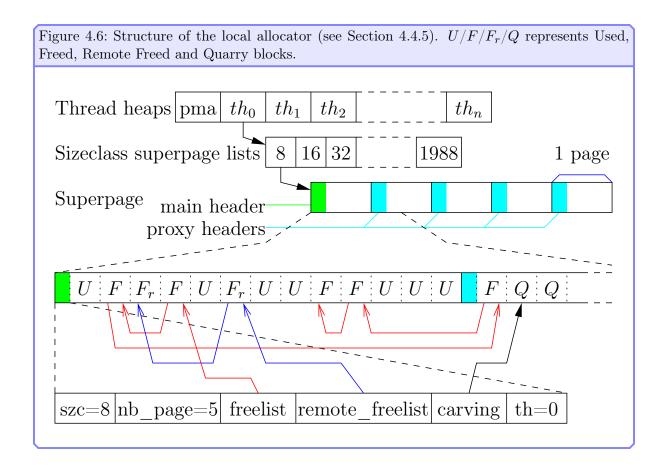

|   |                       |         | Local Allocator                     |           |  |  |  |

|   |                       | 4.4.6   | Proxy Allocator                     | 70        |  |  |  |

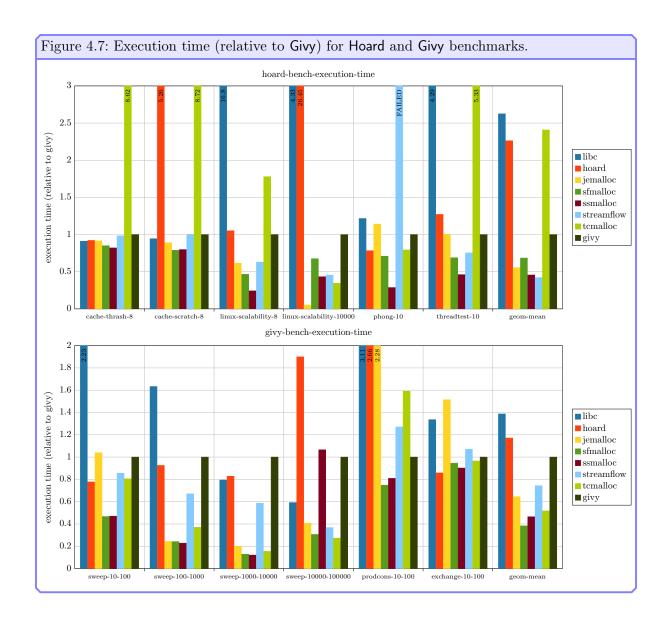

|   |                       | 4.4.7   | Measurements                        | 70        |  |  |  |

|   |                       | 4.4.8   | Proxy Allocator Performance         | 74        |  |  |  |

|   |                       | 4.4.9   | Conclusion                          | 77        |  |  |  |

|   | 4.5                   | Alloca  | tor V2                              | 77        |  |  |  |

|   |                       | 4.5.1   | Basic Allocator Structure           | 77        |  |  |  |

|   |                       | 4.5.2   | GAS Memory Management               | 79        |  |  |  |

|   |                       | 4.5.3   | GAS Coherence Metadata              | 79        |  |  |  |

|   |                       | 4.5.4   | Conclusion                          | 80        |  |  |  |

| 5 | Cor                   | rectnes | ee                                  | 81        |  |  |  |

| U | 5.1                   |         | le                                  | 81        |  |  |  |

|   | 0.1                   | 5.1.1   |                                     | 81        |  |  |  |

|   |                       |         | Description                         |           |  |  |  |

|   |                       | 5.1.2   | Modeling                            | 83        |  |  |  |

|   | <b>-</b> -            | 5.1.3   | Conclusion                          | 89        |  |  |  |

|   | 5.2                   |         | d Memory Data Structures            | 90        |  |  |  |

|   |                       | 5.2.1   | C11 / C++11 Memory Model            | 91        |  |  |  |

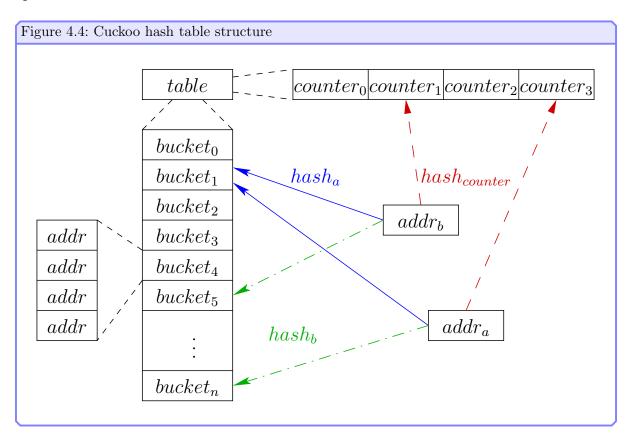

|   |                       | 5.2.2   | Cuckoo Hash Table                   | 92        |  |  |  |

| 6 Conclusion     | 97  |

|------------------|-----|

| List of Figures  | 101 |

| List of Listings | 103 |

| Bibliography     | 105 |

# Chapter 1

## Introduction

This chapter presents an overview of the challenges of high performance computing. It quickly describes the concept of Givy from a user point of view. It also places Givy into the current family of solutions to the HPC challenges.

## 1.1 High Performance Computing

## 1.1.1 Hardware Performance

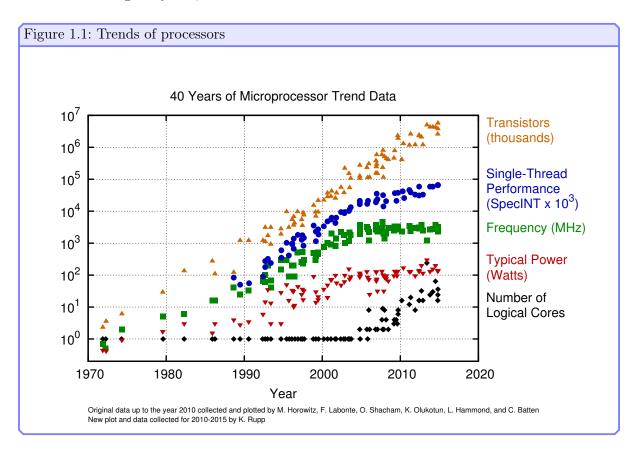

Processor frequencies have stagnated since around 2005. And *Moore's law* may start to fail after holding for years, as transistors starts to reach the size of a few atoms.

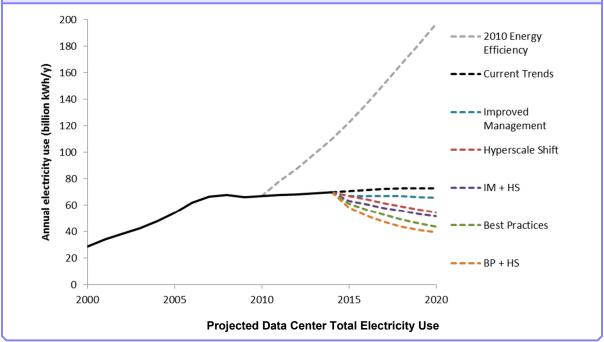

During this period, processor vendors were still able to increase performance. But they couldn't increase the frequency. It would have added more and more constraints on chip design (keeping the clock signal coherent across the chip). It also would have increased energy consumption and dissipation. A low consumption is becoming increasingly important with the presence of smartphones and other battery powered embedded devices. And as computing is now using a significant percentage of the world energy expenditures, this is also important for the environment. Heat dissipation is also a problem, as data centers today spend a lot of energy in cooling systems.

Figure 1.2: Estimations of the energy consumption of US datacenters. Estimates include energy used for servers, storage, network equipment, and infrastructure in all U.S. data centers. The solid line represents historical estimates from 2000-2014 and the dashed lines represent five projection scenarios through 2020.

Instead, processor vendors used the increased transistor density to put more transistors on each chip. They increased single processor performance by adding more complexity to the processor internal structures. It includes: more *cache* storage (to reduce time spent waiting for data), deeper *instruction pipelines* (which increases instruction throughput but not latency), smarter *branch prediction* (to reduce branching impact on pipeline latency). And they also added parallelism, in the form of *vector instructions*, and by adding multiple cores on each chip.

The total available computing power has indeed increased. But being able to use it is now very difficult, as you must consider and play along with all the processor complex structures. In addition to that, memory speeds have been slow compared to processor improvements. So another big problem of today is to bring enough data to the processor. If the data to be processed does not arrive in time, the processor will stall and wait for it, wasting computing power. The *cache* memory is used to store a subset of the whole system memory with a low latency processor access. Thus keeping the processor fed with data requires a good cache management.

The advent of multi-core processors did not help with the memory and cache problem. Most of them use the *shared memory* model, in which they all access the same memory. This means that memory and cache throughput must be divided between the cores. In some cases increased parallelism can lead to worse performance due to memory and synchronization contention. In addition to that, memory and the caches must be kept *coherent* between the processor cores. Today's processors have up to 3 hierarchical levels of cache, some of them shared between some cores, and some private to cores. This means that keeping the performance *and* the memory correctness is very difficult, and a trade-off.

In addition to the evolution of single core processor to multi-core processors, other computing design have gained popularity. Most of them use the huge amount of available transistors to provide performance in their own way. They all present a different API from single core processors.

**GPU** GPUs (*Graphics Processing Unit*) started as accelerators for video game screen rendering. They have gained more flexibility over the years (see the name GPGPU, for *General Purpose GPU*).

Contrary to multi-core processors, they have high parallelism, and contain hundreds or thousand of small computing units. These units have a small instruction set. They are grouped in groups which will execute the same code on different data (like a huge vector instruction). Memory accesses are carefully categorized, between regular ones and irregular, and each will use a different caching system.

This hardware design is extremely efficient for executing the same operation on a large input set, like computing pixel color for each pixel of a screen. Today they are also able to execute more irregular computations with limited control flow, but lose some efficiency. A lot of current research is being done to relax the control flow constraints without hurting performance too much.

GPUs are still considered accelerators. So they are controlled from another processor that manages memory transfers and start computations. Current GPU are programmable with a small DSL (domain specific language), and require the use of a specific API for control. Some recent GPUs allow a limited *shared memory* model through *virtual memory mapping*.

Computational Memory (C-RAM) C-RAM (Computational Memory, also called near-memory computing or processor-in-memory) is a recent alternative to classic processor-centric designs. Instead of improving the memory system around processing units (like in multi-core CPUs and GPUs), they add numerous small processing cores in the memory fabric. They share many similarities with GPU: similar to huge vector instructions, require external control with a specific API, huge number of small basic cores. They can be more efficient than GPUs (especially energy-wise), as there is no need to move the data in specific caches. However they add constraints due to memory geometry and data placement (memory banks, virtual memory, shared access with the controller CPU to memory).

**FPGA** FPGA (*Field Programmable Gate Array*) are programmable logic circuits. The huge amount of transistors is used to create a grid of programmable wires, wire con-

nections, and logic circuit units. A specific circuit can be designed and programmed on the chip. This is a cheaper and modifiable alternative to ASICs (Application-Specific Integrated Circuit), but provides less speed than them.

Again, they are often used as an accelerator, and require a specific API if linked a host machine for data transfer and control. Programming them requires designing a circuit using hardware description languages (VHDL) or higher level tools. As with hardware design, they are adapted to very regular code (fixed memory usage, static data structures). Some act as a programmable logic glue and integrate specific units in the grid, like memory banks, small processor cores, or specific computing units.

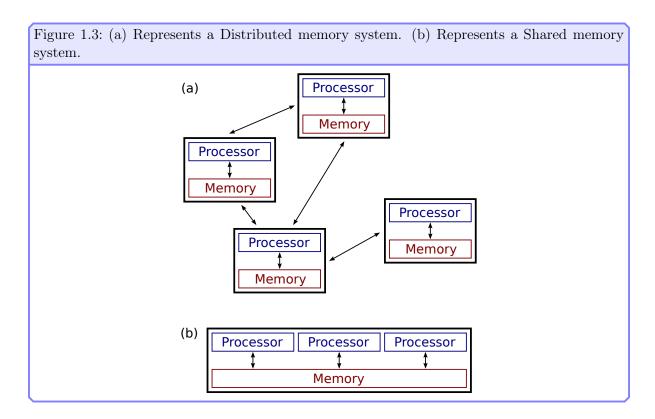

**Distributed Systems** Distributed systems are built by taking multiple *nodes*, and liking them by a network connection. Each node is a computer by itself, with an addressable memory, and computing elements (multi-core processor, sometimes coupled with a GPU): see Fig. 1.3.

These systems are usually built to increase the computing power when a single multicore processor is not enough. Having independent distributed memories instead of a single shared memory makes hardware design easier and scales better. However they are very difficult to program, due to the presence of multiple addressable memories (one on each node). Data transfers between nodes must be performed manually (network transfers), and computation split between nodes (scheduling & synchronization problems).

Distributed systems include *grid computing clusters* and *super-computers*. Grid computing can be made from consumer grade hardware, while super computers use more specific hardware (especially for the network layer). Distributed systems are wide spread in HPC (High Performance Computing), because they scale well and because the API

of individual nodes are similar to that of well known multi-core processors (contrary to GPU, FPGA, or C-RAM).

There are many tools and frameworks trying to ease the programming of distributed systems. This thesis describes a new tool called Givy, in the family of the DSM (*Distributed Shared Memory*) systems (see Section 1.2).

MPSoC Distributed systems have started to be used in an embedded context due to energy concerns. Maintaining the coherence of shared memory costs energy, which is saved if memories are separate like in a distributed system. It is also easier to use energy-saving strategies like DVFS (*Dynamic Voltage Frequency Scaling*) or partial shutdown of cores in a distributed system (the nodes are not synchronous).

Thus companies have started to develop MPSoC (Multi-Processor System on Chip) [70], which includes a complete distributed system in one chip. These MPSoC form a middle ground between GPUs (high parallelism, but basic cores) and multi-core CPUs (low parallelism, complex cores). They have roughly the same properties as distributed systems, but are smaller: very small memories, slower cores.

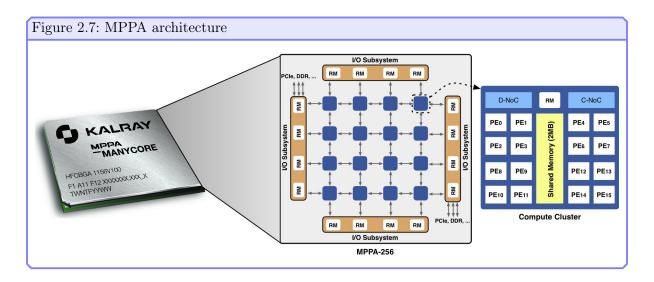

Early MPSoC like RAW [67] had proper distributed memories without hardware coherence. More recent chips such as Tile-GX [10] or the Intel Xeon Phi [5] use a network internally, but local memories are hidden and act as caches (non addressable). This thesis was initially focused on a recent chip develop by the Kalray company [6], named the MPPA [33, 32]. The MPPA has 16 homogeneous nodes each with a 2MB addressable memory and 16 homogeneous cores (+1 for management). It also has virtual memory support (see Section 2.1) on each node. It is thus a proper distributed system on a chip, with the additional constraint of very low node memory.

## 1.1.2 Shared Memory vs Distributed Memory

In this section we will discuss further the differences between shared and distributed memory. A summary of the key differences is listed in Fig. 1.4.

| gure 1.4: Summary of properties of distributed and shared memories. |                |                |  |  |

|---------------------------------------------------------------------|----------------|----------------|--|--|

| Property                                                            | Shared         | Distributed    |  |  |

| Addressing                                                          | global (void*) | local to nodes |  |  |

| Data transfer                                                       | automatic      | manual         |  |  |

| Programmer use                                                      | "easy"         | hard           |  |  |

| Hardware complexity                                                 | hard           | easy           |  |  |

| Energy consumption                                                  | high           | low            |  |  |

| Scaling                                                             | hard           | easy           |  |  |

| Scannig                                                             | Hard           | Сазу           |  |  |

Addressing A shared memory is easier to program, as all cores share the same address space. It means that every program object has a single reference that is valid for all cores (a pointer in the C language). Objects can be linked together through these references, forming complex structures like graphs. And these structures can be understood as is by all cores without the need for any translation.

In a distributed system, each node has its exclusive *address space* (its node-local memory). A program object only exists one node. It can be copied to other nodes, or interact with other nodes by reacting to network messages. But it cannot be accessed directly like a pointer could be dereferenced in shared memory. Classic algorithmic structures like graphs or trees are very difficult to create without global references.

Data Transfer Transferring data between nodes in a distributed memory system is manual and cumbersome (example in Listing 1.1). Data must be transferred through the network, which require actions by both sender and receiver. The sender must know the destination, and package the data from its address space to a format that the network can handle (serialization). The receiver must also know how to handle the incoming message: how to put its data in its own address space (deserialization), and where to put it. This can be done by a blocking call (recv() in the example), or other techniques like non blocking calls or RDMA (see Section 2.3.3). Although a lot of frameworks like MPI [37] simplify this, a data transfer is a complex operation that requires careful coordination between nodes.

```

Listing 1.1: Data transfer in distributed memory

{    // Node 1

int fd = connection_to_node2 ();

int data [42];

produce_data(data);

send (fd, data, 42 * sizeof (int));

}

{    // Node 2

int fd = connection_to_node1 ();

int data [42];

receive (fd, data, 42 * sizeof (int));

use_data (data);

}

```

In shared memory, transfers are mostly automatic, as in Listing 1.2. A piece of data doesn't need to be translated to any intermediate format, and has a global reference that both threads can use. As soon as data is written by produce\_data(), it will automatically be "transferred" to other threads. To make these transfers predictable, synchronization primitives must be used (like pthread\_barrier\_wait() in the example). pthread\_barrier\_wait() blocks until both threads have reach their calls, and ensures that all data has been transferred before returning. Other synchronization primitives exist: mutexes, atomics (see Section 5.2.1), memory barriers.

Cache Coherence Protocol If the shared memory system has a *true* shared memory, all writes to memory would be instantaneously visible (transferred) to any other threads. However, most shared memory processors use multiple levels of caches, with the first level being usually private to each core. In this case, how are new memory writes automatically "transferred" to other cores (and their caches)?

```

Listing 1.2: Data transfer in shared memory (naive example)

pthread_barrier_t barrier;

int data[42];

{ // Thread 1

produce_data (data);

pthread_barrier_wait (&barrier);

}

{ // Thread 2

pthread_barrier_wait (&barrier);

use_data (data);

}

```

Caches are kept synchronized through a cache coherence protocol. Caches can communicate on the chip, and notify other caches of new writes, to let them get the new values instead of using their stale stored values. The protocol describes how they communicate. It creates a semantic of when data is transferred, which is called memory model (see Section 5.2.1). Memory barriers – special processor instructions – are used to flush caches and force propagation of values.

This automatic notification and transfer system does not come with zero cost. It is much more complicated to design than distributed memories (protocol implementation, communication lines between caches). The communications between caches cost a lot of energy, and are difficult to scale to a high number of cores. Even with all these challenges, hardware manufacturers continue to provide shared memory, as it is so convenient for programmers [47].

## 1.2 Distributed Shared Memory

**Definition** The idea of DSM (*Distributed Shared Memory*) systems is to provide a programming model close to shared memory on top of a distributed memory hardware. DSM systems come with a wide variety of implementation choices, making them sometimes difficult to differentiate from a big hardware cache system. In this thesis, we define DSM systems as systems which:

- provide a shared-memory-like abstraction to programmers: global addressing, and global accesses;

- are built on top of a distributed memory system: addressable local memories, user visible network.

This definition excludes classic hardware caches from DSM systems, as they have non-addressable private memories (caches), and hidden networks (communication lines between caches). This also excludes chips like the Intel Xeon Phi [5], which has an internal hidden network that is used to create a distributed L2 abstraction. Most DSM systems are implemented with software, but not all (see NUMA systems, Section 1.2.2).

**DSM vs MPI/OpenMP** Like shared memory systems, a DSM will somewhat automate data transfers between distributed memories. Compared to a manually perfectly optimized message passing program implementation, a DSM will likely make unnecessary transfers and be far from optimal. The rules guiding the data transfers (memory model and coherence protocol) will over-approximate the data transfers needed (as underapproximating leads to a correctness problem).

But DSM are used to let programmers be more productive: using the DSM is easier, with a fast development cycle. Finding a perfect message passing solution can take years for expert programmers. And this perfect solution will likely include classic concepts like caching data. While it needs to be reinvented with message passing, DSM often already use it internally.

Another advantage of DSM are portability. Assuming DSM developers ported it to multiple platforms, programs using the DSM will be easier to port to these platforms. Message passing solutions are more dependent on machine features.

DSM can also hide the underlying architecture. On classic computing clusters made from multi-core nodes, traditional approaches use MPI [37] for inter-node communication, and OpenMP [31, 56] for multi-core management. While this is usable, it lets programmer handle difficult question like which cores can use the message passing system, under which synchronization scheme, or how to avoid dead-locks between the two... DSM usually have to solve these questions internally, moving the difficulty from application programmers to the DSM programmers.

**DSM vs Hardware Coherence** A software DSM will usually react slower than a completely hardware coherence system. However it is at a higher level of abstraction, and can use a wider range of information to optimize data transfers. For example, software DSMs can know the transferred object size, know if an object is node-local or globally shared, etc. Hardware implementation often use a "one size fits all" strategy, with fixed granularity, and will try to infer intent from the access pattern, which is harder. DSM can also be adapted faster and at lower cost than hardware.

#### 1.2.1 Classification

In this section we will try to classify the variety of DSM systems.

**Support Level** The *support level* is the entity (or group of entities) that implement the DSM mechanisms:

- Hardware: data transfers are managed completely by hardware; mostly NUMA systems (Section 1.2.2);

- Compiler: data transfers are hidden by language features, compiled to data transfers calls (or API calls);

- Library: data transfers are managed by a library (function calls).

Hardware support is the least portable, as you need the specific hardware to make the program work. However it is also the most transparent, as it will likely behave like a big multi-core CPU (NUMA systems). It is close to a hardware cache system, and share its flaws. It is often combined with a software API for high level operations (often an optimized implementation of MPI [7]).

Compiler strategies are often combined with a library one. The compiler will generate data transfer by adding calls to the library API. User programs must be programmed in the specific language.

Library support is the most portable and can fit in a existing language. However, users will have to add library calls manually.

**Data References** To support a shared-memory-like abstraction, the DSM system must provide a kind of *global reference*. These references are associated to a *global address space* (GAS). References can come in different types:

- Real pointer: a plain C pointer (void\*), which can be used as is (mostly found in NUMA);

- Fake pointer type: a small type that requires translation before accessing the data (often a combination of node id and a local C pointer);

- Index / key in a table: global data looks like a table or array, and is accessed through a global key;

- Object: global data is defined as objects, which have methods calls for interaction.

**Data Granularity** The DSM system must handle piece of data of different sizes. Data granularity describes how the DSM will handle these different sizes:

- Fixed granularity: a size is chosen (cache line size, or page size), and the DSM operates on chunks of this size;

- Constant after creation: the DSM operates on the piece of data as a unit, but it cannot be resized;

- Dynamic: the DSM operates on the piece of data as a unit, and it can grow or shrink.

Fixed granularity is simple, but cannot adapt to the size of global objects. Objects smaller than the granularity size will generate bigger data transfers than necessary, and may suffer for *false sharing* if multiple objects are in the same chunk. Objects bigger than the granularity size may be transferred piece by piece instead of using one long transfer that can be optimized.

Data Management and Access DSM can manage access to global data in two ways:

- Replication and caching: the DSM maintains multiple copies of the data object on multiple nodes;

- Remote access: only one node maintains a copy, and other nodes request temporary copies of the data from it every time.

The difference between the two access models is not always clear cut, as in most case the remote node must copy the data in its own virtual address space before accessing it. NUMA machines tend to rely on their fast hardware and use remote access: the data might be reloaded many times. Some low level GAS frameworks (like ARMCI [52]) tend to get a local copy of remote data, modify it, and push it back: this is still remote access as the temporary buffer is not kept coherent with remote data. Replication DSM will internally manage the local copy, and ensure it is kept up to date before every access.

**Execution Model** Our last important criteria for categorization is what execution model is supported by the DSM system:

- Threaded: the program is a set of concurrent threads;

- Task graph: the parallel program is described as a set of tasks, linked by value flow and dependencies;

A message passing program is usually tied to the threaded model, with blocking network calls, and heavy ordering and coordination. Old DSM approaches [15] automated the network transfers but kept the threaded model. NUMA architectures also work under this model as they try to look like a multi-core machine.

Most of the recent DSM work instead uses the task graph method. Programs are described as a set of tasks (inputs, outputs, and processing code). These tasks inputs and outputs are linked, and the links represents value flow. The task graph is then executed according to these links (dependencies). Tasks not transitively dependent may be executed concurrently.

The task model requires a heavier run-time support than a classic threaded one. However, it is able to hide network transfers (or memory access) latency by executing other ready tasks while it moves data. These models are attractive, but are less programmer friendly as they are less structured than the threaded model.

Threaded models cannot easily move computation units between nodes, so they can lose efficiency if the computation is imbalanced between nodes. Task graph models can move the already split computation units (tasks) easily between nodes. However they have to manage the *scheduling*, i.e. choosing where and when tasks are executed. Although some systems choose the scheduling at compile time [68], most will choose it at run-time. A run-time scheduler must carefully balance the quality of the schedule and the overhead cost of the scheduling algorithm.

For both models, the program must split his work into a number of units that is adapted to the target machine number of processing units. Too few big units will under-utilize the machine, and too many small units will loose efficiency in too much synchronization. Thus even if the task graph model looks "independent" from the machine, part of the graph generation must be able to scale according to the machine parallelism too.

#### 1.2.2 Families

A DSM could be created with any set of the previously shown properties. However, over time DSM systems have formed a few big families.

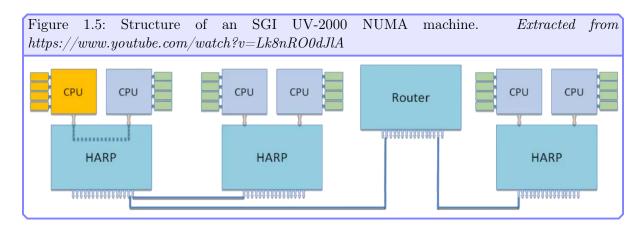

**NUMA Systems** NUMA (*Non-Uniform Memory Access*) systems (Fig. 1.5) have special hardware to track memory accesses and generate network transfers if the data is remote. This hardware may be located in the CPU, in the cache hierarchy (cache coherent NUMA, or ccNUMA), in its off-chip memory system (a.k.a. chipset), and/or in the network interfaces.

NUMA systems allow to use unmodified shared memory programs. However, if programs can be ported without effort, the performance cannot. If no special care is given to the memory layout of the program, false sharing may occur. Due to low or absence of data replication, data is best created on the node that will access it the most. Reductions should use temporary per-node accumulators values on separate DSM chunks. Thus performance still requires heavy tuning [38]. To alleviate some of the problems due to the rigid nature of hardware, most NUMA hardware vendor also implement optimized message passing libraries [7].

The Software NUMA systems are a sub family of NUMA. These DSM systems have a NUMA like behavior, but they detect memory accesses through the virtual memory system (Section 2.1). They do not require specific hardware and can be used in any system with virtual memory. However they suffer from a high fixed granularity, at the page level (usually 4KB). Examples include Treadmarks [15], and a DSM system for the MPPA at Kalray.

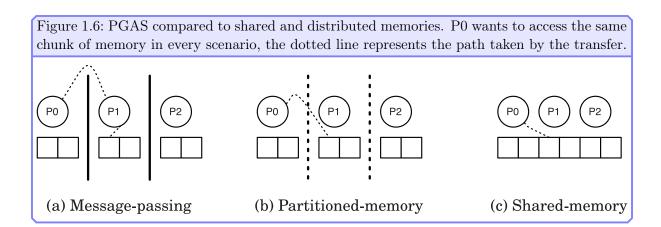

**PGAS Languages** The PGAS (*Partitioned Global Address Space*) language DSM family contains over a dozen different DSM systems (see [34] for a detailed overview).

PGAS sits between the shared and distributed models. It creates a global address space that can be accessed by all nodes, but it also keeps a *node-local* memory (see Fig. 1.6). Memory accesses in local and global memories use different constructs, so the distinction is visible to the programmer. This distinction is supposed to let the programmer be aware of the cost of accessing global memories, and avoid careless use like what could happen in a NUMA machine. Most PGAS languages try to use RDMA (Section 2.3.3) for remote accesses, as it does not require actions by the remote node (hence the dotted line avoids P1 in the figure).

Listing 1.3 shows some excerpts from UPC [26], a PGAS programming language. By our classification, UPC is a Compiler + Library, Threaded, Constant after creation granularity, Fake Pointer approach. UPC is a super-set of the C language, and it adds

a shared storage-specifier keyword to place variables in the global address space. It is supported by a run-time library, and the UPC compiler will automatically generate library calls when shared variables are accessed. Pointers into the GAS are fake pointers hidden by the compiler.

```

Listing 1.3: Example of UPC constructs

int a[16]; // local variable

shared int b[16]; // GAS variable

shared [4] int c[16]; // with explicit layout

b[3] += 42; // generates communication code

upc_memcpy(b, c, 16 * sizeof (int)); // GAS version of memcpy

shared int * gas_ptr; // fake pointer (node, virtual addr, phase)

```

A downside to these approaches is that the notion of a local memory is usually tied to a threaded model. This distinction between local and global memory also requires different libraries. In UPC, part of the C standard library has been duplicated into a GAS version (example: upc\_memcpy).

Other PGAS languages include X10 [28], CoArray Fortran [55], Global Arrays [53], or Chapel [27]. They are usually based on libraries like ARMCI [52] or GasNet [24] which handle the system setup for the global address space.

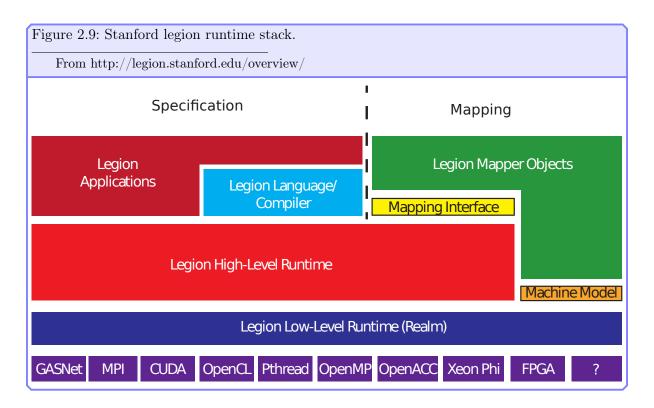

**Distributed Task Run-times** Another family consists of the task graph DSM runtimes. Examples include Stanford Legion [20], Intel Concurrent Collections (CnC) [25], StarSs [60] or Grappa [50].

Task DSM systems are based on a Task execution model, and most take the form of a library. StarSs uses OpenMP-like annotations with pragmas, and Legion can be either through its library or with a small language with a compiler pass. The library based ones require to fit the data to their structures with specific types, and often use index / key addressing, or fake pointers. Functions calls must be made to access piece of data in these tables, and they are used to detect accesses and make the necessary memory transfers.

The different run-times will be examined in more detail in Section 2.5.

**Distributed Objects** For completeness, we must mention the family of distributed object systems. In these DSM systems, objects are created and referenced in a global naming space. Interaction with these objects can be performed through methods, which will transfer arguments and retrieve results as needed. This family includes the CORBA standard [2], and the more recent trend of web APIs.

## 1.3 Givy

In this thesis, we wanted to develop a new DSM solution, which is called Givy. The initial motivation behind Givy was to build a DSM run-time to efficiently execute irregular parallel applications on MPSoC architectures. We also wanted to require as little program modification as possible. The Kalray MPPA was our main primary target, but we also support x86 clusters.

According to the previous classification, Givy is a Library support, Real pointer, Constant after creation granularity, Replication and Task based DSM system.

Having real C pointers (T\*) as global references is rare in software DSMs and more often found in NUMA strategies. In Givy, we provide an unmodified data interface for the user. They do not have to rewrite pointer based data structures to fit the DSM like in other software DSMs, as pointers are valid in the global address space. However, currently only heap data is in the GAS (data and pointers in the space managed by malloc()/free() and derivatives); stack and static data are not supported. This restriction is necessary as we need to have knowledge and control of the layout of program data. To control heap pointer values, we also require that the target architecture has virtual memory.

Using Givy still requires modifying the program, as we need to cut it into tasks. There is no way to bypass this modification if we want to balance irregular computations dynamically. Cutting the program into tasks gives a benefit: tasks inputs (function arguments) can be used to detect memory accesses.

Execution Model Givy programs are built following a dynamic data-flow execution model. A data-flow application is a dynamically built and unfolded graph of run-to-completion tasks with explicit data dependencies. Tasks are created at run-time by predecessors, and their dependencies are explicitly set by older tasks. When all dependencies are fulfilled and its data is available locally, a task may execute (non preemptively) and then its local resources be deallocated. Tasks are one-shot (they are destroyed after use) and cannot be interrupted (thus all accessed data must be visible in the input argument list).

Tasks arguments may be simple values (passed by value) or mutable memory regions. These regions are referenced through raw pointers. Each task accessing a region needs to specify the access mode, read-only (const T\*) or read-write (T\*). We require that the task graph corresponding to the target data-flow application is data-race free with respect to these memory regions. Extensions will allow some racy code patterns to be supported.

To execute such applications on distributed systems, the run-time system must be extended to deal with distributed memory. All memory references (regions) are placed in a global address space, so they can be accessed from any node. The run-time can perform

load balancing by migrating tasks either between cores or nodes. Each time a task will be executed, Givy will transfer the required data (input memory regions, and task frame with arguments) to its execution node. The global memory regions are replicated across nodes, and managed by a *software cache coherence protocol*.

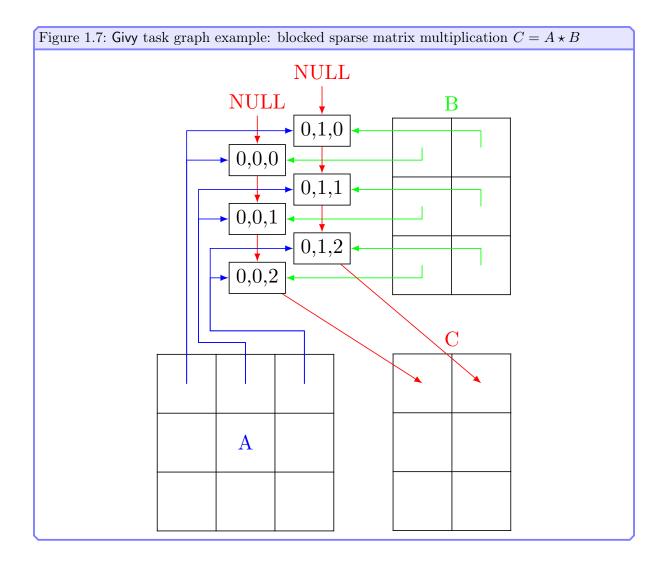

**Sparse Matrix Multiplication** Let us consider the blocked-sparse matrix multiplication  $C = A \times B$  as a motivating (dynamic) application. Sparse linear algebra is interesting because it is irregular, and use pointer indirections to sub blocks. An excerpt of C code describes a possible Givy task implementation in Listing 1.4, and Fig. 1.7 illustrates the shape of task dependencies.

```

Listing 1.4: Givy example: blocked sparse matrix multiplication C = A \star B

typedef double* Matrix; // NULL <=> full of zeroes

Matrix A[M][K] = {...}, B[K][N] = {...}, C[M][N] = {NULL};

// ...

// will perform C[i][j] += A[i][k] * B[k][j]

void mm_chunk(TASK next_chunk, const double *a,

const double *b, double *c)

{

if (a != NULL && b != NULL) {

if (c == NULL) { c = calloc(MATRIX_CHUNK_SIZE); }

c += a * b; // dense matmul like cblas_gemm

}

// forward c value to the next mm_chunk task

TASK_SET_ARG(next_chunk, c, 3 /* arg_pos=3 */);

}

// ...

// spawn all tasks (creates a chain of task for each i, j)

for (int i = 0; i < M; i++) {

for (int j = 0; j < N; j++) {

TASK next = gather_result_instance;

for (int k = K - 1; k \ge 0; k--)

next = TASK_SPAWN(mm_chunk, next, A[i][k], B[k][j], UNDEF);

}

}

```

Function mm\_chunk is instantiated as  $M \times N \times K$  tasks that perform the individual block dense matrix multiplication. Arguments a and b of each task are fixed at task creation as they do not change. Argument c represents C[i][j] which starts at NULL but might be allocated during execution to store a non-zero sub-matrix. So all tasks using C[i][j] are ordered as a chain and forward the current c to the next task in chain (pointed to by next\_chunk, fixed at spawn). Forwarding the argument with TASK\_SET\_ARG also unlocks the next task which enters the scheduler as it now has all its arguments.

When the task is scheduled to run on a specific node, we check that each region argument is available in the requested access mode by reading the coherence meta-data. If this is not the case, we send the coherence requests on the network, and put the task

on wait and execute other tasks. When all coherence requests have been completed, the task can run.

## 1.4 Outline & Contributions

This thesis presents four contributions to the design of a new DSM. The first contribution is the design of Givy, a run-time that fulfills the following criteria: Library support, Real pointer, Constant after creation granularity, Replication and Task based. The second contribution is a formal design of a coherence protocol and its integration with the run-time. The third contribution is the translation of the formal protocol into a model checker language. The fourth contribution is a partial implementation of Givy. It mainly consists of a memory allocator that: allows GAS-level malloc(); provides support for replicated regions. The implementation is not complete enough to test performance of the whole Givy runtime system. Only partial performance evaluation of the memory allocator has been done.

The rest of the manuscript falls into the following four chapters before concluding. Chapter 2 describes the run-time design. Chapter 3 describes the cache coherence proto col formal model. Chapter 4 describes the implementation of the memory allocator. Chapter 5 describes the validation attempts of the coherence protocol with a model checker and discusses the correctness of the low-level concurrent implementation.

# Chapter 2

## Runtime

This chapter describes the overall design of Givy. Givy relies heavily on *virtual memory* and a *network layer*. Section 2.1 and Section 2.3.3 discuss these two concepts before diving into the details of Givy in Section 2.2. Section 2.5 compares Givy to other task run-times.

**Region** In the following chapters, a *region* is a dynamically allocated buffer that is managed by the coherence protocol in Givy.

**Core** A processor core, a single threaded computing unit. Each core has a worker thread that can execute tasks.

**Node** A node contains a memory (and its own address space), a processor with one or more cores that share the node memory, a network interface. The coherence mechanisms manage regions between node's memory spaces.

**Target architecture** Givy targets a system made of multiple nodes that can communicate through a network.

## 2.1 Virtual Memory

This section describes what is virtual memory, along with some hardware / OS details that are relevant to Givy.

Most general purpose CPU cores today have virtual memory support. When using virtual memory, two address spaces exists: virtual addresses used in program space, and physical addresses in computer memory. These address spaces may have different shapes, so an address translation step is needed before any memory access, from the virtual address to the physical one. The translation table is not required to be complete: if the virtual address is not found, the access will fail.

### 2.1.1 Common Uses

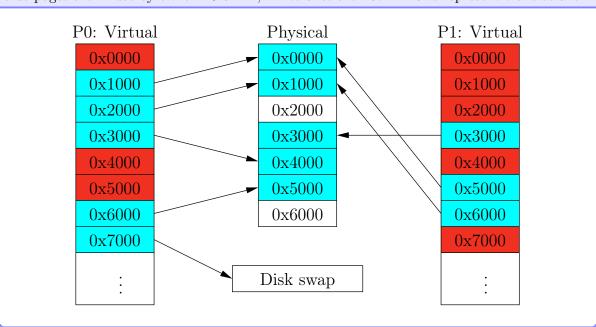

Most operating systems have exclusive control over the virtual memory system. They use it for many purposes: abstracting physical memory, security, disk swapping, error detection, memory sharing between processes, etc. Fig. 2.1 illustrates some of these, in a small system with two processes P0 and P1.

Figure 2.1: Example of a virtual memory layout for two processes P0 and P1. Virtual memory: light blue pages are mapped (usable), red ones unmapped (unusable). Physical memory: light blue pages are in use by either P0 or P1, white ones are not. Arrows represent translations.

Error detection Memory accesses without any translation entry generate errors. So there is a high chance that a bogus memory access will fall outside the set of current translations. Operating systems will catch the resulting error and stop the process (segmentation fault). Most operating systems always leave no translations for address 0x0 (NULL ) to ensure that an access to NULL fails.

**Physical memory abstraction** The physical memory is not always contiguous, and may contain holes. Virtual memory can hide these holes by using a contiguous virtual space translation scheme.

**Disk swapping** Virtual memory can be used to simulate a huge memory, even if the physical memory is small. If the program working set is too big to fit the physical memory, some of it is stored away in slower storage devices. In consumer computers, this is called *disk swapping*, as the hard drive is used to store data from the RAM.

With virtual memory, stored data is marked as *available* even if it is not in the physical memory (see address 0x7000 of P0 in Fig. 2.1). Stored data has a special tag in the translation table. When accessed, the operating system can retrieve the data from storage, place it in physical memory, and complete the memory access as if nothing happened.

**Security** Virtual memory provides security by placing each process in a sandbox (with respect to memory accesses). Operating systems will create one translation table (and thus one virtual address space) per process. As long as this table does not contain translations to other processes or OS memory, the current process is completely isolated

in memory. For example, in Fig. 2.1, address 0x3000 refers to different physical memory in P0 and P1.

Sharing memory between processes Multiple translation tables can point to the same physical memory addresses, like physical 0x0000 and 0x1000 in Fig. 2.1. A common use case is read-only shared data, like binary code of libraries used by both processes. Another use case is when processes explicitly request to share some memory.

## 2.1.2 Implementation

Virtual memory support is a team work between the hardware and the operating system. The operating system stores the set of virtual-to-physical address translations in a structure called *page table* [40]. Each memory access must be intercepted, and its address translated using the table before accessing the physical memory.

In order to prevent too much overhead, the translation is performed by a hardware unit called *Memory Management Unit* (MMU). The MMU only translates the upper bits of the memory address: translation is done at a coarse granularity. A page is a set of addresses with the same upper bits relevant for the architecture MMU. On x86 the page size is fixed at 4KB. On the MPPA it is a configurable power of two starting at 4KB. This coarse granularity prevents the page table data structure from taking too much memory space (less entries for the same amount of mapped memory).

To speed up the translation even more, most MMUs use a translation cache called Translation Lookaside Buffer (TLB). This cache stores a few entries from the page table, and must be kept in sync with it by the operating system (TLB flush on table modifications). A TLB cache miss is called a page fault. It will usually trigger an interrupt, and let operating system code determine the missing translation. A bogus access (like NULL) will be detected by the operating system, and transformed into a segmentation fault. Modern TLB can use multiple cache levels, or more often provide multiple page sizes to better support high memory usage (4KB / 2MB / 1GB pages on x86). Carefully using the higher page sizes can prevent slowdowns due to TLB saturation, but require careful memory placement (aligning virtual memory to the higher page size).

MMU also implement memory access protection. Each page has access mode flags (read / write / executable), that are compared to the accessing instruction and will trigger a segmentation fault if a mismatch happen.

Most operating systems nowadays lazily allocate physical pages to virtual mappings. Creating virtual memory in the OS will just create some page table entries. A physical page will be associated to a virtual page only when it is first accessed (first page fault).

#### 2.1.3 Posix API

The first (and now deprecated) way to manipulate virtual memory was the brk() system call. It was used to extend or shrink a linear contiguous program heap. It lacks flexibility, and will easily lead to fragmentation, and thus most modern memory allocators avoid using it (except the libc one).

The preferred way to create / destroy virtual memory chunks is by using the mmap()/munmap() system calls. mmap() primary use is to create a virtual memory mapping that is backed by a unix file descriptor: the memory will be filled with the resource data as needed by the operating system. Memory allocators create anonymous mappings (without any file descriptor) using the MAP\_ANONYMOUS flag: the memory is just a chunk of contiguous virtual memory pages freely usable. As we focus on memory allocation, in the remainder of this thesis mmap() is always used in the anonymous mode.

Some other system calls like madvise() and mprotect() can manipulate the created mapping flags and provide optimization hints to the operating system. However, there is no way to access the page table directly.

## 2.1.4 In Givy

Due to the use of raw C pointer as GAS addresses, C pointers must be carefully chosen to prevent collisions. Thus memory objects must be created at specific places in memory. Givy uses the virtual memory for this purpose, by implementing a malloc() that returns correctly placed pointers.

## 2.2 Givy

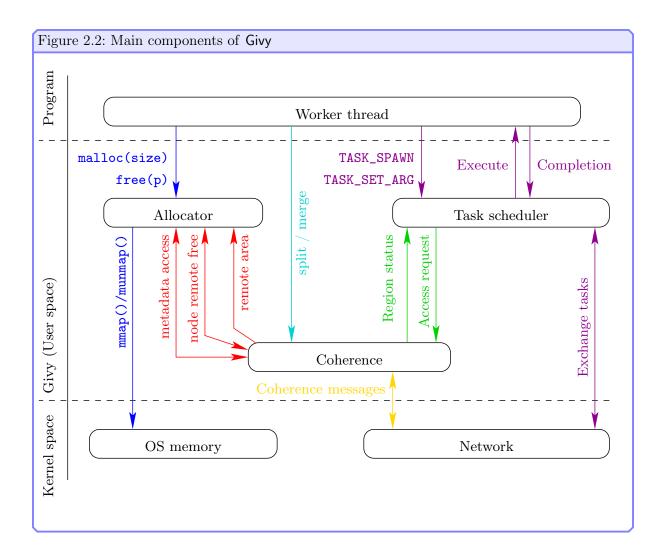

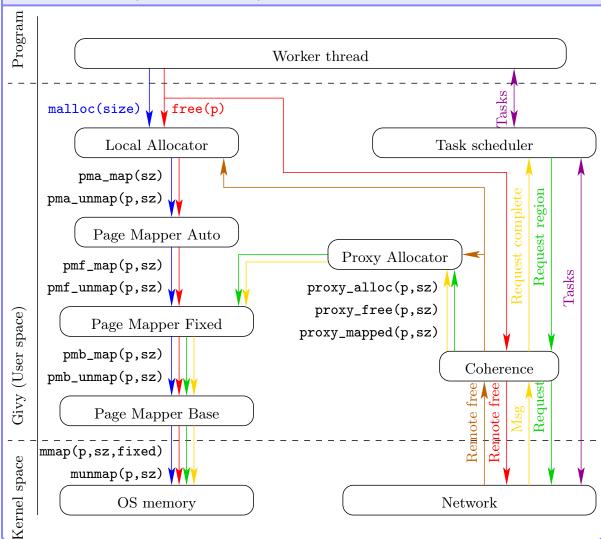

The Givy run-time contains 3 main components: a memory allocator, a cache coherence subsystem, and a task scheduler. These components interact with each other, with the operating system (system calls) and with worker threads (Givy calls). A summary of interactions can be found in Fig. 2.2.

As the run-time has not been completed, part of this section may describe my thoughts about how to implement the feature rather than an actual implementation. The Section 2.3 describes what has been implemented precisely.

#### 2.2.1 Task

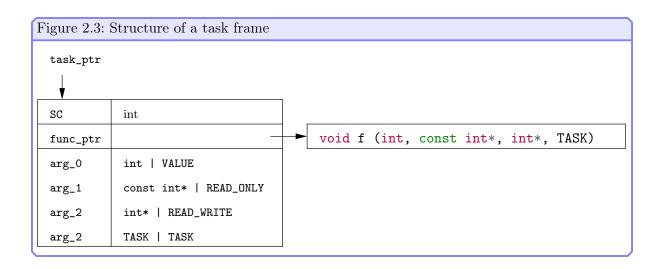

We start with the most basic component of the runtime: a single task. In Givy, a task is a *closure* built around a C function. In other words, it is a C function, with a set of argument values that can be used to call the function, and also some metadata for the runtime.

Implementation wise, a task is represented by a *task frame*. A *task frame* is an instance of a C structure filled with task data. An example is given in Fig. 2.3, for a fictional function f. The most basic part of the task frame is a pointer to function f, to be able to call it when executing the task. In Givy task frames are dynamically allocated for each task, and are thus *memory regions*. The TASK pseudo-type is a pointer to the corresponding task frame, which is a unique identifier for the task due to our real pointer GAS choice.

The task frame contains storage space for each function argument. The primitive TASK\_SET\_ARG will locate the task frame and fill these argument values. Each argument is also annotated with a flag that determine its kind. A VALUE flag indicates a trivial type that should just be copied. A READ\_ONLY or READ\_WRITE flag indicates a memory region, i.e. a memory buffer that is managed by the coherence protocol. The access mode

determines which mechanism to trigger in the coherence protocol. Lastly, the TASK flag indicates that the value is a task handle (internally, this is a region with a special access mode).

The SC field is called *synchronization counter*. This field represents the number of dependencies that a task is still waiting for, before being able to run. It is initialized to some positive integer at task frame creation. It can be decremented, and when it reaches 0 the task is now eligible to be run. TASK\_SPAWN will initialize the SC to the number of undefined arguments left in the task frame. TASK\_SET\_ARG will decrement the SC on each call, and thus make the task able to run when it reaches 0.

Task frames do not store link to neighbors in the task graph. They only store SC as dependency information. The dependency information is contained in the task code, by calling task\_tdec on the right tasks.

The TASK\_SPAWN / TASK\_SET\_ARG is a simplified API for the sake of presentation. Givy is designed more as a run-time target for higher level task computing systems (like OpenMP[31] or OpenStream [61]) than a user level run-time. Its actual API is lower level, and can trivially implement the simplified one:

| <pre>task* task_create(int sc, ArgInfo info[])</pre>        | Creates task frame |

|-------------------------------------------------------------|--------------------|

| <pre>void task_set_arg(task* t, ArgInfo arg, T value)</pre> | Only sets argument |

| <pre>void task_dec(task* t)</pre>                           | Decrements SC      |

In particular, SC is decoupled from the number of argument, and can be used to represent additional dependencies that could be difficult to represent through arguments.

In terms of implementation complexity, TASK\_SPAWN (and task\_create) are simple because they just create a local region and sets some values. TASK\_SET\_ARG, implemented by task\_set\_arg and task\_tdec is much more complex as it might need to access a task frame on remote nodes. They use a special mode of the cache coherence to do that efficiently. They are described in Section 3.3.2.

## 2.2.2 Scheduling

The next part of Fig. 2.2 to describe is the scheduler component. The scheduler is in charge of executing the tasks at the right time, place, and context.

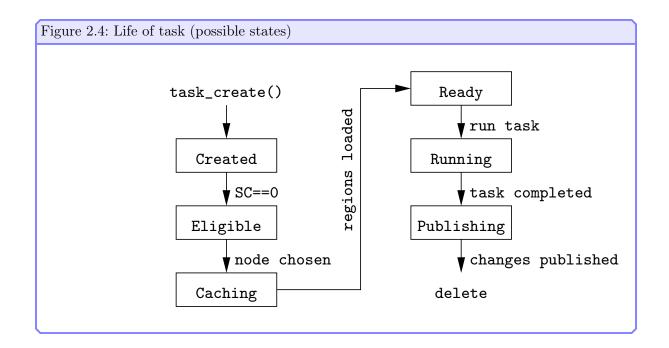

A task, from its creation to its destruction, goes through different states. The set of states is given in Fig. 2.4, along with the transition conditions. A task is represented by its task frame, which is a memory region. Thus the task – its task frame – is *owned* by a node at any time (see Chapter 3 for details).

**Life of a task** A newly created task is in the Created state. It stays in this state until the synchronization counter arrives to 0. A created task is owned by the node which called task\_create, and ownership does not change while in this state. Thus task\_set\_arg requests must be forwarded to the owner node if it is called from remote nodes.

When a task has all its dependencies resolved (SC equal to 0), it moves to the Eligible

state. In this state the task could be executed (all arguments known), but we need to chose a node to run it, and potentially load some remote regions on the node. While in this state, the task can be moved between nodes for load balancing (ownership can change).

At some point, a node will decide to execute an eligible task, and move it to the Caching state. In this state (and all states that follow), the task is committed to this node and *ownership cannot change*. If the task has memory regions as arguments, the node must use the coherence system to retrieve remote regions locally before executing the task. The scheduler will send coherence requests upon entering the caching state, and wait for answers.

When all regions are locally available, the task goes to the Ready state. This state indicates that the task can be executed immediately (all arguments are locally available). It stays in this state until it is scheduled to run on one of the node cores.

When a task is scheduled on a core and starts running, it goes into the Running state. A task cannot be interrupted, so it will lock the core until completion. While executing, a task can use API calls like task\_create, task\_set\_arg and task\_tdec. task\_tdec are registered and their execution delayed until the end of the next state.

At the end of execution, a task goes into the Publishing state. In this state, it must publish the changes made to the program state to every node. Changes include task state (arguments and SC) and modifications to regions (send invalidations in the coherence protocol). To ensure correctness, dependent tasks are not notified (task\_tdec) until region modifications are published. After all publishing operations have been performed, the task is destroyed and the task frame deleted.

A formal presentation of this state transition system is available in Chapter 3 as part of the coherence protocol formalization.

**Scheduling implementation** The first role of a scheduling system is to execute tasks according to their dependencies. The formal correctness of this system is discussed

in Chapter 5. Intuitively, if a task enters the running state then all arguments are available locally (coherence), and have been computed beforehand (synchronization counter). Correctness requires that dependencies given by the user are correct, and that there is no data race. Incorrect dependencies might let a task run without all its argument computed. Data races (writes in parallel with others accesses) might trigger invalidations of the remote regions copies used by a running task.

The current design of Givy has two load-balancing steps. The first one operates between nodes: each node has a queue of eligible tasks, and can exchange eligible tasks with other nodes. The second one operates between the cores of a node: each core has a queue of ready tasks, and can exchange ready tasks with other cores. In both cases, the basic strategy used is work stealing [23], which consists of stealing a bunch of tasks from a random partner when our queue is empty. Work stealing is a simple yet effective strategy, and often outperforms more complex strategies.

Ready task load balancing can use shared memory work stealing, for which very efficient algorithm already exists. Eligible task load balancing implements work stealing by sending *steal requests* to other nodes.

In the context of Givy, eligible task load balancing can be smarter than pure work stealing. Using information from the coherence and allocator system, we can selectively push some tasks to other nodes:

- if we do not have fresh copies of the required remote regions, and know that another node has them

- if we do not have enough memory left to locally load the required regions (embedded context)

- have too much tasks in our queue (tasks that created a lot of new tasks)

We could also think of defining scheduling policies for tasks, for example to help spreading the computation evenly when creating a lot of new tasks.

As an optimization, some of the tasks states can be bypassed if the task already fulfills the conditions. For example, a newly created task with all arguments already locally available can be run immediately. Bypassing queues is useful to reduce latency of execution, especially if few tasks are alive (and we need few cores to compute). However, if a sufficient number of tasks are waiting, some should be put into queues so that more nodes / cores can be used for the computation.

In our scheduling system, tasks (task frames) are not always referenced globally by the run-time. Instead their references are passed through the different structures

until deletion:

| diffit deletion. |                                              |  |  |

|------------------|----------------------------------------------|--|--|

| Created          | referenced by argument producer tasks (user) |  |  |

| Eligible         | eligible node queues (runtime)               |  |  |

| Caching          | referenced by caching requests (runtime)     |  |  |

| Ready            | ready core queues (runtime)                  |  |  |

| Running          | referenced by worker thread (runtime)        |  |  |

| Publishing       | referenced by publishing requests            |  |  |

| Finished         | deleted                                      |  |  |

No garbage collection of tasks is provided; a created task must be executed. Task cancellation is not provided yet. Cancelling a task could be done if it is still in created state, and all tasks referencing it are updated, but semantics of such operation would not be simple.

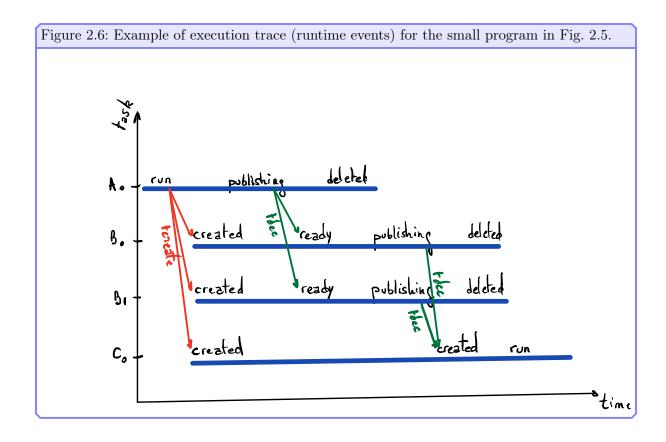

Figure 2.5: Example of a small task graph. A, B and C are task models (functions that describe tasks).  $A_0$ ,  $B_0 / B_1$  are task instances created from their models.

| A()                                                  | B(task d,int i) | $A_0$       |  |

|------------------------------------------------------|-----------------|-------------|--|

| $b0 = task\_create(B, 1);$ $b1 = task\_create(B, 1)$ |                 |             |  |

| $c0 = task\_create(C, 2)$                            | task_dec(d)     | $B_0$ $B_1$ |  |

| task_set_arg(b0, 0, c0); task_set_arg(b0, 1, 43)     |                 |             |  |

| task_set_arg(b1, 0, c0); task_set_arg(b1, 1, -36)    | C()             | $C_0$       |  |

| task_dec(b0)                                         |                 |             |  |

| task_dec(b1)                                         |                 |             |  |

**Example** Fig. 2.5 illustrates how to define a small task graph (on the right) using Givy runtime primitives (on the left). In this example, we will do a *fork-join* construct, which is creating parallel tasks doing the same job with different arguments, and then waiting for all to complete. Here task B is the operation to parallelism, with a dummy integer argument. Task A is the fork task; it will create all B tasks, gives them arguments, and uses a task\_tdec to let them start computing. C task is the join, which does not actually do anything because the join will be handled by the run-time. We want to outline that to perform task\_tdec on C, B tasks must have a reference to C. This is made possible as A creates both B0, B1 and C and can forward reference to C to B tasks.

Fig. 2.6 shows us some steps of a possible computation, starting with a A task created by an ancestor.

#### 2.2.3 Allocator

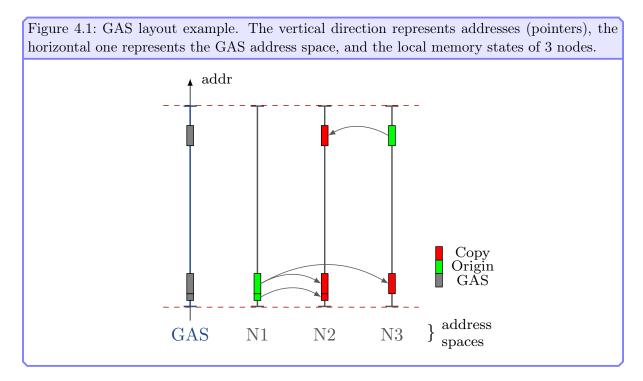

The memory allocator component is used to manage the global address space. In the current Givy system, heap data is in the GAS, thus malloc() allocates blocks in the GAS, and the raw pointers it returns are GAS references. So the malloc() implementation is responsible for managing the GAS memory, both at a node-local level as a normal allocator, but also at the GAS level. The allocator subsystem of Givy is described in more details in Chapter 4.

The GAS is defined as an interval of addresses in virtual memory. Virtual memory allow us to use the same addresses on every node, assuming we create the right mappings. At any given time, each node is only required to map the part of the GAS that is locally used by tasks. Thus Givy can process a huge data set even if physical memories are small, by spreading computations (and data requirements) to multiple nodes: each node only needs to load a small part of the data set.

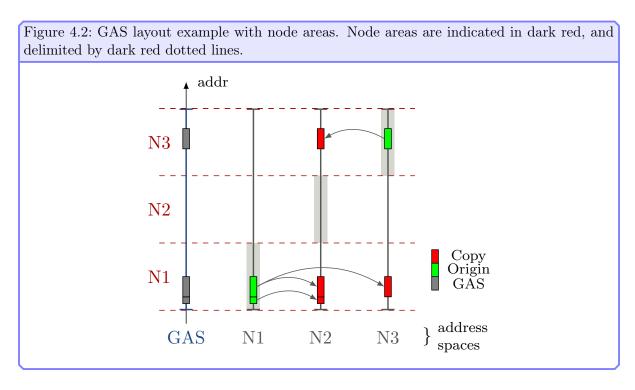

As classic memory allocators, the Givy allocator must manage the state of virtual memory. However it must coordinate its instances between nodes, to avoid *collisions* (allocating overlapping blocks). In Givy, this is done by giving a exclusive area of the GAS to each node (Section 4.2 and Fig. 4.2). Each node allocator will exclusively allocate and deallocate from its own area. This allocator also manages virtual memory associated to remote areas (areas given to other nodes).

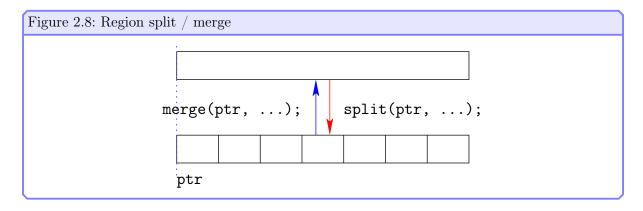

The allocator subsystem works closely with the coherence subsystem (red arrows in Fig. 2.2). Management of the *remote areas* is driven by coherence requests (such as request to load a memory region allocated at another node). As **free()** is a GAS operation, it may trigger coherence requests to free copies on other nodes. Lastly, the

allocator is responsible for placing, and providing access to coherence meta-data for each memory region.

#### 2.2.4 Coherence Protocol

The last critical component of Givy is the coherence protocol. It is a piece of event-driven code that maintains a coherence between the multiple node copies of a region. It relies on the memory allocator for managing the node-local address space. It requires meta-data to be associated to each region: this is also handled by the memory allocator. Coherence is achieved by exchanging network messages between nodes, which are described formally in Chapter 3.

## 2.3 Implementation

#### 2.3.1 Version 1

Originally, Givy was targeted for the MPPA architecture (see Fig. 2.7), which was being developed at the Kalray company. This architecture contains 16 nodes of 16 cores each (and one additional management core), with everything integrated on a single chip. This target added two important constraints to the run-time: it needed to fit into the 2MB memory available on each core; using the C language as C++ support was not a priority.

Thus the first version of the run-time was written in C. This version was entirely composed of the version 1 of the Givy allocator (Section 4.4). The version 1 of the allocator was designed heavily around the small footprint constraint, with simple slower structures to reduce code and meta-data size. It did not handle the coherence meta-data placement; meta-data was placed inline with the data.

An interesting problem is to generate the task frame structures for each function. In C there is no clean way to achieve this, so those structures would have required an external generator (small C compiler, or letting the higher level run-time handle the generation).

The version 1 run-time (or just allocator) was never tested completely on the MPPA as software support for virtual memory manipulation was not available at that time. Only the cuckoo hash table of the Page Mapper Fixed that used MPPA-specific atomics (the MPPA memory model is weaker than the weakest C11 atomic model, relaxed) was tested on the MPPA. For the published paper [39], the run-time was tested on x86 using mmap(). Work stopped on the version 1 shortly after to give rise to the version 2 described below.

### 2.3.2 Version 2

The version 2 of Givy is a new implementation in C++. To speed up development, it was decided to work on x86 while keeping the MPPA in mind. C++ was chosen instead of C: the later version of MPPA added support to C++ compilation; also C++ allows greater refactoring and reuse of structures in case they needed to be scaled to the MPPA 2MB.

The current version 2 of the protocol contains the version 2 of the allocator (Section 4.5), a basic network layer, and a partial implementation of the coherence protocol. The version 2 of the allocator has a more modular and advanced structure, and can store meta-data on demand for regions.

Compared to the C version 1, in C++ we could generate the task frame types using advanced template constructions. While this is somewhat automatic and stays within the language (no external code generator), this would have lead to unreadable code and difficult maintenance.

An interesting problem is the virtual address placement of the GAS. The chosen virtual address interval must be available on all process taking part to the GAS. Currently Givy chooses a hard-coded address interval far in the address space, which seems to be free from interference even under *Address Space Layout Randomization* (ASLR). GASnet [24] tries multiple intervals using heuristics in order to reduce the risk of GAS initialization failure. It would ultimately be better to use similar strategies for GAS placement.

```

Listing 2.1: Interesting C++ constructions

constexpr T f (void) {...} // compile-time executable function constexpr T v = f (); // compile-time generated value

T * p = new (addr) T (args...); // placement new

BoundUint<N> n; // uint8_t, uint16_t, uint32_t...

// Curiously Recurring Template Pattern (CRTP)

template<typename T> struct Link {

Link * prev; Link * next;

T & access_struct (void) { return static_cast<T&> (*this); }

};

class ChainableStruct : public Link<ChainableStruct> {

int blah;

...

};

```

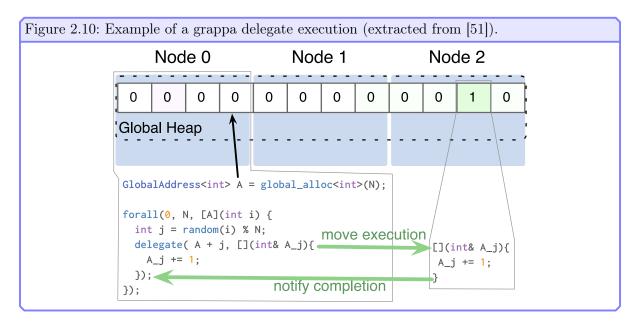

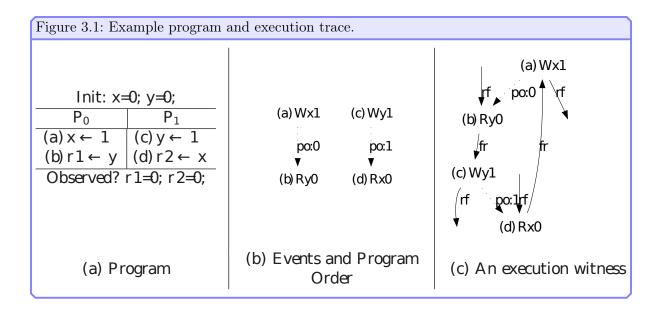

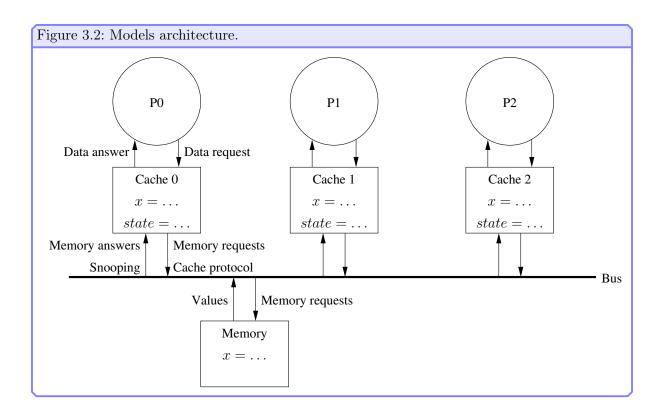

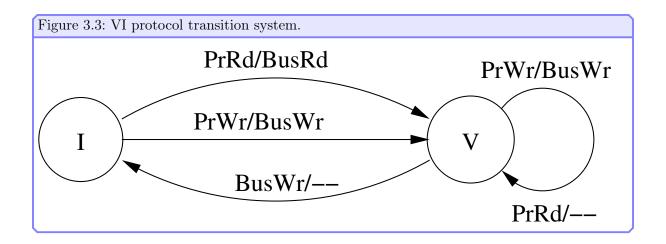

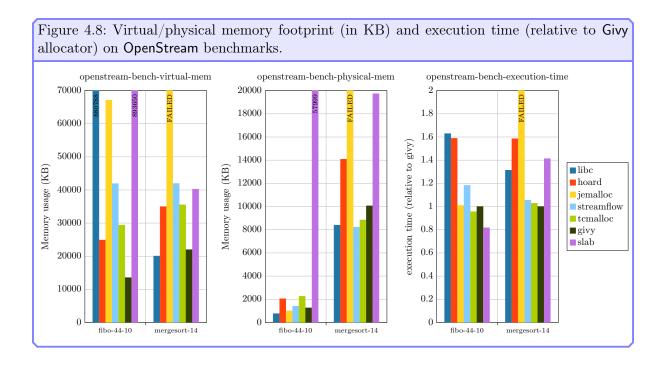

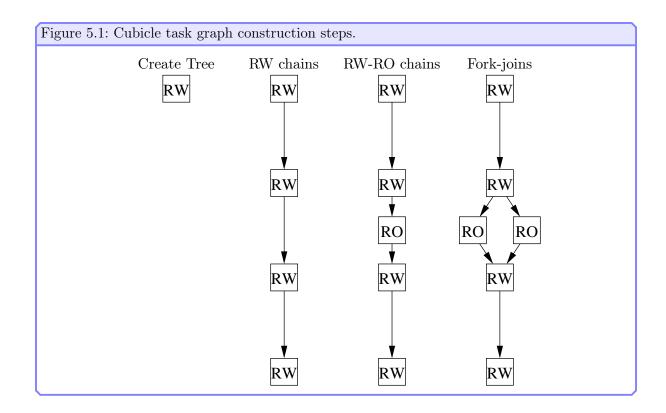

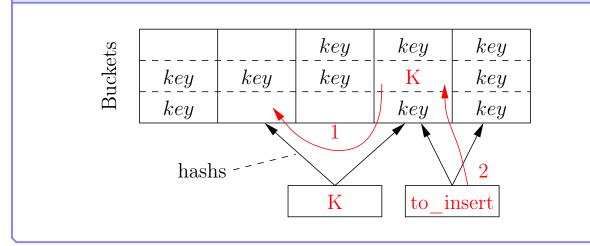

C++ features The C++ language is very large and offers a lot of different programming paradigms, with some having run-time overhead. Using C++14 with templates