#### Nouvelle Approche Globale par Composants AADL pour le Développement des Systèmes Adaptatifs de Contrôle Industriel

Farid Adaili

#### ▶ To cite this version:

Farid Adaili. Nouvelle Approche Globale par Composants AADL pour le Développement des Systèmes Adaptatifs de Contrôle Industriel. Informatique [cs]. Ecole Polytechnique de Tunisie, 2017. Français. NNT: . tel-01925172

#### HAL Id: tel-01925172 https://theses.hal.science/tel-01925172

Submitted on 16 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### ÉCOLE POLYTECHNIQUE DE TUNISIE, TUNISIE CONSERVATOIRE NATIONAL DES ARTS ET MÉTIERS, FRANCE

École Doctorale : École Doctorale Sciences Appliquées

Laboratoires: LISI/INSAT, Tunisie et CEDRIC/CNAM, France

#### THÈSE DE DOCTORAT

présentée par : Farid ADAILI

soutenue le: 04 Mars 2017

pour obtenir le grade de : Docteur de l'École Polytechnique de Tunisie

Spécialité : Électronique et Technologie de L'Information et de la Communication

## Nouvelle Approche Globale par Composants AADL pour le Développement des Systèmes Adaptatifs de Contrôle Industriel

#### THÈSE dirigée par

M. Mohamed KHALGUI Mme. Samia BOUZEFRANE

Mme. Olfa MOSBAHI

RAPPORTEURS

M. Mohamed ABID

M. Alain PLANTEC

**EXAMINATEURS**

M. Nicolas TREVES Mme. Maryline CHETTO

M. Laurent GEORGE

MdC/HDR, INSAT, Tunisie

$MdC/HDR,\ CNAM,\ France\ (Co-encadrante)$

MA, INSAT, Tunisie (Co-encadrante)

Prof, ENIS, Université de Sfax, Tunisie

Prof, Université de Bretagne Occidentale, France

Prof. CNAM, France

Prof. Université de Nantes, France

Prof, ESIEE, Paris Est marne la vallée, France

#### Remerciements

Il est toujours délicat de remercier l'ensemble des personnes qui ont contribué à l'aboutissement de mes travaux de recherche. Que ceux qui ne sont pas mentionnés ne m'en tiennent pas rigueur.

Je tiens tout d'abord à remercier mon directeur de thèse Monsieur Mohamed KHAL-GUI, Maître de Conférences/HDR à INSAT Tunisie et ma Co-Encadrante Madame Samia BOUZEFRANE, Maître de Conférences/HDR au CNAM France, qui ont su canaliser mes travaux de recherches doctorales, l'aide et les conseils qu'ils n'ont jamais cessés de me donner m'ont été d'une valeur inestimable, ce dont je leur suis très reconnaissant.

Mes très sincères remerciements à ma Co-encadrante Madame **Olfa MOSBAHI**, pour toute l'attention qu'elle m'a portée, sa disponibilité et son soutien inconditionnel au cours de ces années de recherches. Merci infiniment Madame OLFA.

Je remercie M. Mohamed ABID, professeur à ENIS-Sfax Tunisie et M. Alain PLAN-TEC, professeur à l'Université de Brest pour avoir accepté d'être les rapporteurs de ce mémoire. Les remarques pertinentes qu'ils ont émis ont permis de le consolider.

Je remercie également Mme. Maryline CHETTO, Professeur à l'Université de Nantes, M. Laurent GEORGE, Professeur à ESIEE, Paris Est marne la vallée, M. Nicolas TRÊVES, Professeur au CNAM-Paris pour l'intérêt qu'ils ont porté à mes travaux et pour avoir accepté de faire partie du jury de ma soutenance de thèse.

Je remercie également tous les membres du laboratoire LISI-INSAT pour leur accueil et leur disponibilité, surtout le directeur Monsieur **Moncef GASMI**. Mes collègues et chers amis surtout Aymen GAMMOUDI, Med Oussama BEN SALEM... Ils n'ont jamais cessé de m'encourager et de m'apporter du support.

Je remercie également tous les membres du Laboratoire CEDRIC-CNAM qui m'ont accueilli et qui m'ont permis de m'épanouir dans mes recherches et pour leur sympathie et leur bonne humeur. Ils ont contribué à une atmosphère propice pour travailler et se sentir bien.

Je n'oublie pas non plus tous mes amis.

Enfin, merci du fond du cœur à toute ma famille ainsi qu'à tous mes amis pour leur soutien inestimable et les bons moments partagés.

#### Glossaire

- --I: Interface

- $M_p$ : Ensemble des méthodes

- $P_{\Sigma} \subseteq I$  : Interfaces d'entrées

- $R_{\Sigma} \subseteq I$ : Interfaces de sorties

- $\beta_{\Sigma}$  : les méthodes qui interagissent avec les interfaces du composant

- -CS: Un composant selon

- $--\Theta$ : l'ensemble des signatures du composant

- ---AX: l'ensemble des axiomes du composant

- ---B: l'ensemble des comportements atomiques du composant

- $--(GL,\oplus)$ : Un monoïde commutatif

- COM: Component Object Model

- DCOM: Distributed Component Object Model

- -JB: Composant JavaBeans

- *ADL* : Langage de Description d'Architecture

- ACME: Architecture Description Interchange Language

- EADLs: Executable Architecture Definition Language

- POSET : Partial Ordered event Sets

- AADL: Architecture Analysis and Design Language

- ---RA2DL: Reconfigurable AADL

- SAE : Society of Automotive Engineers

- WCET: Worst Case Execution Time

- $TR^2E$ : Temps-Réel Réparties Embarqués

- *IMA*: Integrated Modular Avionics

- --TPN: Time Petri Net

- --BF: Blocs Fonctionnels

- FSM : Machine à États Finis

- ---SCI : Systèmes de Contrôles Industriels

- *IEM* : Input Event Module

- IEDB : Input Event Data Base

- -DM: Data Module

- *DDB* : Data Data Base

- ALDB: Algorithms Data Base

- *OEM* : Output Event Module

- -AL: Niveau Architecture

- -CL: Niveau Composition

- --DL: Niveau Données

- $--\beta$ : Module Contrôlé de RA2DL

- ---R: Module de Contrôle de RA2DL

- $\Psi_{RA2DL}$ : Ensemble de tous les algorithmes de RA2DL

- $\xi_{RA2DL}$ : Sous-ensemble des algorithmes

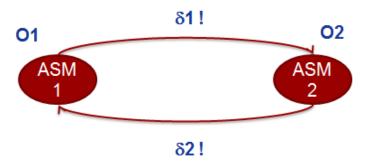

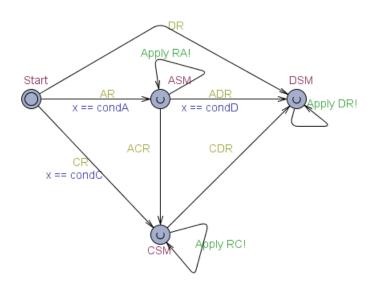

- ---ASM: Architecture State Machine

- $-S_{AL}$ : État dans ASM

- $S_{AL}^i$ : Un état particulier dans un niveau architectural

- O: Ensemble de n états dans  $S_{AL}$

- $\delta$ : Fonction de transition au niveau architecture

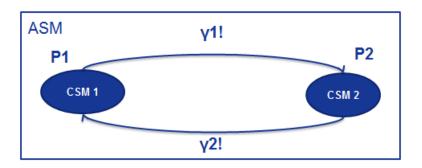

- CSM: Composition State Machine

- $-S_{CL}$ : État dans CSM

- $S_{CL}^{j}$  : Un état particulier dans un niveau composition

- $\Gamma(\delta_{RA2DL})$  : Ensembles des modèles d'exécutions des algorithmes

- P: Ensemble de m états dans  $\mathbf{S}_{CL}$

- $\gamma$ : Fonction de transition au niveau composition

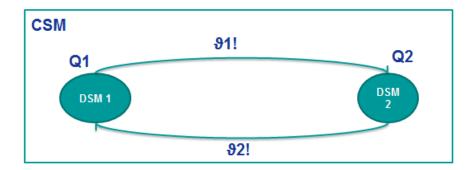

- DSM : Data State Machine

- $-S_{DL}$ : État dans DSM

- $-- S^k_{DL}$ : Un état particulier dans un niveau données

- Q: Ensemble de k états dans  $\mathbf{S}_{DL}$

- $\vartheta$ : Fonction de transition au niveau données

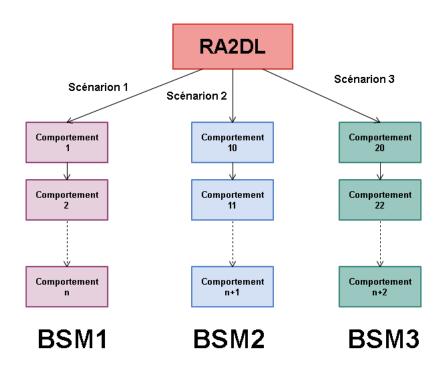

- BSM: Behavior State Machine

- RA: Reconfiguration Architecture

- --- CondA: Condition de passage à ASM

- RC: Reconfiguration Composition

- CondC: Condition de passage à CSM

- RD: Reconfiguration Données

- CondD: Condition de passage à DSM

- $flex_R$  : Seuil de flexibilité donné par un expert

- --Flex(RA2DL): Équation de la flexibilité

- $R_{exe}^i$ : Scénario de reconfiguration i accepté

- $R^i$ : Totalité des scénarios de reconfigurations

- AlgFlex : Algorithme de calcule de flexibilité

- MR: Middleware de reconfiguration

- -RT: Jeton de reconfiguration

- -RF: Flux de reconfigurations

- --DA: Adresse du composant RA2DL

- -V: Variable binaire

- PF : Facteur de priorité

- IRF : Port d'entrées

- --ORF: Port de sorties

- --EC: Contrôleur d'exécution

- -ST: Jeton de synchronisation

- -S: Sémaphore

- *CM* : Coordination Matrix

- $Reconfiguration_{ia,ja,ka}^a$ : Ensemble des scénarios de reconfigurations

- ia: Reconfiguration au niveau architecture

- ja: Reconfiguration au niveau composition

- ka: Reconfiguration au niveau données

- *id\_pool* : Identifiant de RA2DL-Pool

- *UT* : Table des utilisateurs

- *id\_user* : Identifiant d'utilisateur

- password\_user :Mot de passe d'utilisateur

- service\_user : Services réservées au utilisateur

- -RT: Table de reconfigurations

- $id\_reconf$ : Identifiant de reconfiguration

- $-id_RA2DL$ : Identifiant d'un composant RA2DL

- --ST: Table de sécurité

- privilege\_user : Privilèges des utilisateurs

- AAA: Authentication, Authorization et Accounting

- S: Services offerts par les composants RA2DL

- $M_{sc}$ : les droits de chaque paire (S et C)

- TCTL: Timed Compotational Tree Logic

- ---BMS: Body-Monitoring System

- ---M: impulsions envoyé par le Radar

- -N: Objets détectés par le Radar

- $--O_j$ : Un objet détecté

- $r_i$ : Direction

- $-d_i$ : Distance

- $--s_i$ : Surface

- C : Paramètre du Radar

- $--H_{-}Res$ : Haute résolution

- L\_Res: Faible résolution

- condition\_weather : Condition climatique

- --  $wind\_speed$ : Vitesse du vent

- $--M1,\,M2:$  Moteur 2 et Moteur 2

- $EV\_T1,\, EV\_T2:$  Thread 1 et Thread 2

- ci: Variable d'envoi des paquets

- Pi: Paquet numéro i

- Se : Taille du paquet à l'envoi

- Sr : Taille du paquet à la réception

- $--(S_f)$ : Fréquence d'envoi du paquet

#### Résumé

Cette thèse de doctorat propose une approche globale intitulée RA2DL pour le développement d'une architecture embarquée, logicielle et matérielle reconfigurable pour les systèmes de contrôle industriels à base de composants AADL. La reconfiguration est une opération souvent utile permettant la modification des composants AADL logiciels et matériels afin de les adapter dynamiquement à leur environnement d'exécution. Dans cette thèse, nous définissons des composants dynamiques et flexibles intitulés RA2DL à partir des composants statiques AADL qui peuvent encoder plusieurs comportements relatifs à plusieurs scénarios de reconfiguration d'une facon dynamique. Un scénario de reconfiguration est défini comme une opération dynamique et automatique permettant l'ajoutsuppression-mise à jour des algorithmes/ ports d'un composant donné. Dans ce cadre, un composant RA2DL sera la superposition de plusieurs sous-composants de même nature mais avec différentes reconfigurations ou caractéristiques au niveau des interfaces ou des implémentations. Nous modélisons cette approche à l'aide des automates temporisés pour spécifier les comportements des nouveaux composants R2ADL d'un système donné selon trois niveaux : architecture, composition et données. A l'aide du modèle checker UPPAAL, la vérification de cette approche est nécessaire pour la validation des différents scénarios de reconfiguration et notamment en ce qui concerne la vérification des propriétés temporelles, et en particulier les propriétés d'atteignabilité et de vivacité avec la logique TCTL. Une extension sera étudiée aussi pour le cas des systèmes distribués qui doivent garantir une cohérence de reconfiguration synchrone entre des composants RA2DL distribués. Notre étude portera également sur une contribution garantissant la sécurité de reconfiguration de RA2DL qui s'articule sur le concept du Pool. Enfin, nous présentons l'implémentation ainsi que la simulation des études des cas reconfigurables avec RA2DL pour montrer

l'applicabilité de l'approche proposée.

**Mots clés :** Approche par composant, Système de contrôle industriel, Système temps-réel embarqué, Reconfiguration, AADL, RA2DL, Modélisation, Vérification, Sécurité, Synchronisation, Simulation.

#### Abstract

This thesis focuses on a global approach named RA2DL that we propose for the development of embedded architecture, reconfigurable hardware and software for industrial control systems based on AADL components. The reconfiguration is a useful operation for changing the AADL software and hardware components to adapt dynamically to the execution environment. We define a new form of dynamic and flexible components called RA2DL from static components AADL which can encode several behaviors in multiple reconfiguration scenarios dynamically. A reconfiguration scenario is defined as a dynamic and automatic operation allowing the add-remove-update algorithms / ports for a given component. In this context, a RA2DL component will be the superposition of several subcomponents of the same type but with different characteristics or reconfigurations at the interfaces or implementations levels. We model this approach by using timed automata to specify the behavior of new R2ADL components of a given system on three levels: architecture, composition and data. Using the model checker UPPAAL, the verification of this approach is necessary for the validation of different reconfiguration scenarios especially regarding verification of temporal properties, and particularly the reachability and liveness properties with logic TCTL. An extension will also be investigated in the case of distributed systems that need to ensure coherence of synchronous reconfiguration between distributed RA2DL components. Our study will also include a contribution ensuring security in RA2DL which is based on the concept of the Pool. Finally, we present the implementation and simulation of reconfigurable cases studies with RA2DL to show the applicability of the proposed approach.

**Keywords:** Component-based approach, Industrial control system, Real-time embedded system, Reconfiguration, AADL, RA2DL, Modeling, Verification, Security, Synchronization, Simulation.

## Table des matières

| 1                       | Int | roduction Générale                                                      | 31 |

|-------------------------|-----|-------------------------------------------------------------------------|----|

| 1 Introduction Générale |     |                                                                         |    |

|                         | 1.1 | Rappels des concepts fondamentaux                                       | 33 |

|                         | 1.2 | Problématique                                                           | 36 |

|                         |     | 1.2.1 Détection des besoins de reconfiguration                          | 37 |

|                         |     | 1.2.2 Vérification formelle du comportement                             | 37 |

|                         |     | 1.2.3 Communication et synchronisation des composants reconfigurables . | 38 |

|                         |     | 1.2.4 Sécurité des composants reconfigurables                           | 38 |

|                         | 1.3 | Contraintes de Reconfiguration                                          | 39 |

|                         | 1.4 | Objectif et approche                                                    | 40 |

|                         |     | 1.4.1 Objectif                                                          | 40 |

|                         |     | 1.4.2 Approche Proposée                                                 | 40 |

|                         | 1.5 | Organisation du Manuscrit                                               | 43 |

|                         |     |                                                                         |    |

| II                      | Ét  | at de l'art                                                             | 45 |

| 2                       | Éta | t de l'Art                                                              | 47 |

|                         | 2.1 | Introduction                                                            | 47 |

|                         | 2.2 | Système de Contrôle Industriel                                          | 48 |

| 2.3 | Ingéni | erie Dirigée par les Modèles et la Validation         | 49 |

|-----|--------|-------------------------------------------------------|----|

|     | 2.3.1  | Ingénierie Dirigée par les Modèles                    | 49 |

|     | 2.3.2  | Vérification et Validation                            | 51 |

|     | 2.3.3  | Exemples de reconfigurations et IDM                   | 52 |

| 2.4 | Appro  | oches par Composants                                  | 54 |

|     | 2.4.1  | Concept du Composant                                  | 54 |

|     | 2.4.2  | Composants des systèmes embarqués                     | 57 |

|     | 2.4.3  | Composant On-line                                     | 59 |

|     | 2.4.4  | Composant Off-line                                    | 61 |

|     | 2.4.5  | Sécurité des Approches par Composants                 | 69 |

|     | 2.4.6  | Vérification Formelle par Model-Checking              | 70 |

|     | 2.4.7  | Synthèse                                              | 73 |

| 2.5 | Langa  | ge de Description et d'Analyse d'Architectures (AADL) | 73 |

|     | 2.5.1  | Principes du Langage                                  | 73 |

|     | 2.5.2  | Définition des Composants AADL                        | 74 |

|     | 2.5.3  | Structure Interne des Composants AADL                 | 76 |

|     | 2.5.4  | Ports d'interface                                     | 77 |

|     | 2.5.5  | Outils AADL Existants                                 | 78 |

|     | 2.5.6  | Annexe d'AADL                                         | 80 |

|     | 2.5.7  | L'annexe de gestion des erreurs en AADL               | 80 |

|     | 2.5.8  | Les Modes et les transitions de mode en AADL          | 81 |

|     | 2.5.9  | Discussion                                            | 82 |

| 2.6 | Métho  | odes de Reconfigurations Existantes                   | 85 |

|     | 2.6.1  | Définition                                            | 85 |

|     | 2.6.2  | Reconfiguration Statique                              | 86 |

|   |      | 2.6.3   | Reconfiguration Dynamique                                                 | 87  |

|---|------|---------|---------------------------------------------------------------------------|-----|

|   |      | 2.6.4   | Reconfiguration Automatique des Systèmes Temps-Réels Embarqués            | 88  |

|   |      | 2.6.5   | Synthèse                                                                  | 89  |

|   | 2.7  | Limite  | es des Solutions Existantes                                               | 90  |

|   |      | 2.7.1   | Inadéquation avec les Systèmes de Contrôle Industriel $\ \ldots \ \ldots$ | 90  |

|   |      | 2.7.2   | Reconfiguration Locale du Composant                                       | 91  |

|   | 2.8  | Synthe  | èse                                                                       | 92  |

|   | 2.9  | Conclu  | usion                                                                     | 93  |

|   |      |         |                                                                           |     |

| Π | I C  | Contrib | outions                                                                   | 95  |

| 3 | Pro  | mière   | ${f Contribution: RA2DL: Nouveau\ Composant\ AADL\ Reconfi-}$             | _   |

| J | gura |         | Contribution : ItAZDE : Ivouveau Composant AADE Itecom-                   | 97  |

|   | 3.1  | Introd  | uction                                                                    | 97  |

|   | 3.2  | Forme   | s de Reconfigurations                                                     | 98  |

|   |      | 3.2.1   | Reconfiguration d'Architecture                                            | 98  |

|   |      | 3.2.2   | Reconfiguration de Structure (Composition)                                | 99  |

|   |      | 3.2.3   | Reconfiguration de Données                                                | 100 |

|   | 3.3  | Archit  | ecture de RA2DL                                                           | 100 |

|   |      | 3.3.1   | Module d'Entrée des Événements (IEM)                                      | 100 |

|   |      | 3.3.2   | Module des Données (DM)                                                   | 101 |

|   |      | 3.3.3   | Module des Algorithmes (ALM)                                              | 101 |

|   |      | 3.3.4   | Module de Sortie des Événements (OEM)                                     | 102 |

|   | 3.4  | Forma   | disation de RA2DL                                                         | 102 |

|   |      | 3.4.1   | Niveau Architectural (AL)                                                 | 103 |

|   |      | 3.4.2   | Niveau Composition (CL)                                                   | 104 |

|   |     | 3.4.3   | Niveau de Données (DL)                                       | . 105 |

|---|-----|---------|--------------------------------------------------------------|-------|

|   |     | 3.4.4   | Comportement de RA2DL                                        | . 105 |

|   | 3.5 | Modél   | lisation de RA2DL                                            | . 106 |

|   | 3.6 | Flexib  | vilité de RA2DL                                              | . 109 |

|   | 3.7 | Exem    | ple                                                          | . 110 |

|   | 3.8 | Concl   | usion                                                        | . 112 |

| 4 | Cor | ıtribut | ion 2 : Nouveau concept : Réseau des Composants RA2DL        | 115   |

|   | 4.1 | Introd  | luction                                                      | . 115 |

|   | 4.2 | Résea   | u de RA2DL                                                   | . 116 |

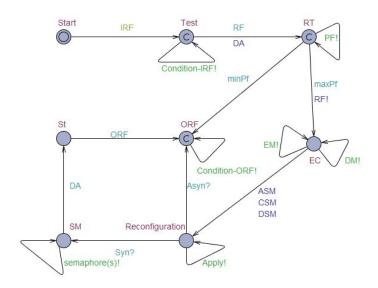

|   | 4.3 | Modèl   | le d'Exécution d'un RA2DL                                    | . 117 |

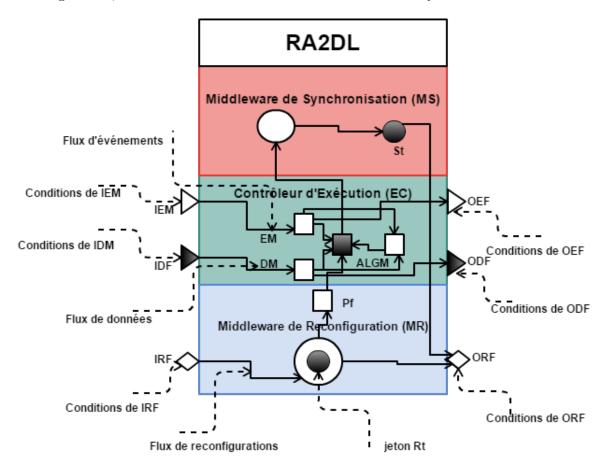

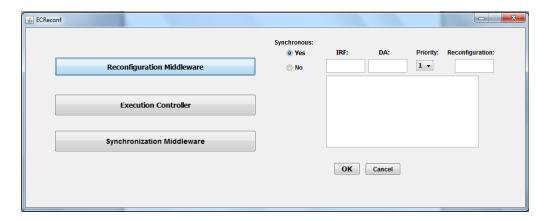

|   |     | 4.3.1   | Couche 1 : Middleware de Reconfiguration $\dots \dots \dots$ | . 118 |

|   |     | 4.3.2   | Couche 2 : Contrôleur d'Exécution                            | . 119 |

|   |     | 4.3.3   | Couche 3 : Middleware de Synchronisation                     | . 120 |

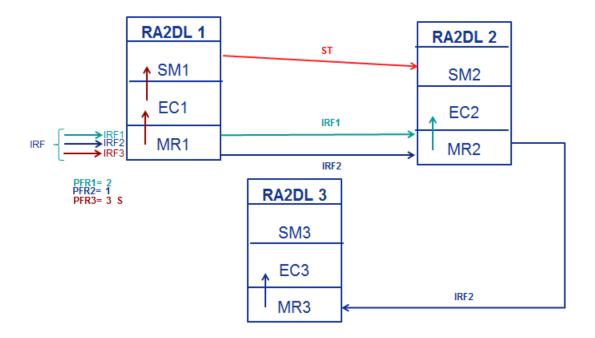

|   | 4.4 | Modèl   | le d'Exécution pour les Architectures RA2DL Distribuées      | . 120 |

|   |     | 4.4.1   | Définition                                                   | . 121 |

|   |     | 4.4.2   | Architecture RA2DL Distribuée                                | . 121 |

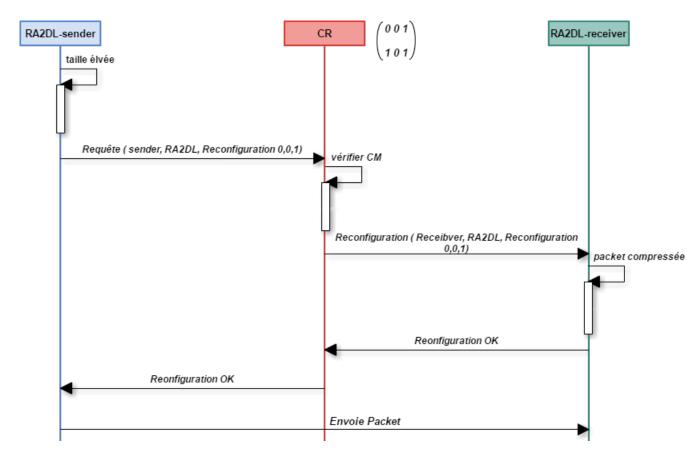

|   |     | 4.4.3   | Coordination Entre les Composants RA2DL Distribués           | . 123 |

|   | 4.5 | Modél   | lisation d'un Réseau de RA2DL                                | . 124 |

|   |     | 4.5.1   | Modélisation du Modèle d'Exécution                           | . 124 |

|   |     | 4.5.2   | Modélisation de la Coordination Entre les Composants RA2DL   | . 125 |

|   | 4.6 | Exem    | ple                                                          | . 126 |

|   | 4.7 | Concl   | usion                                                        | . 128 |

| 5 | Cor | ıtribut | ion 3 : RA2DL-Pool : Nouvelle Approche pour la Sécurisatio   | n     |

|   | du  | Compo   | osant RA2DL                                                  | 129   |

|   | 5.1 | Introd  | luction                                                      | . 129 |

|    | 5.2        | RA2D    | L-Pool : Nouvelle Extension pour la Sécurité du Composant RA2DL | 130 |

|----|------------|---------|-----------------------------------------------------------------|-----|

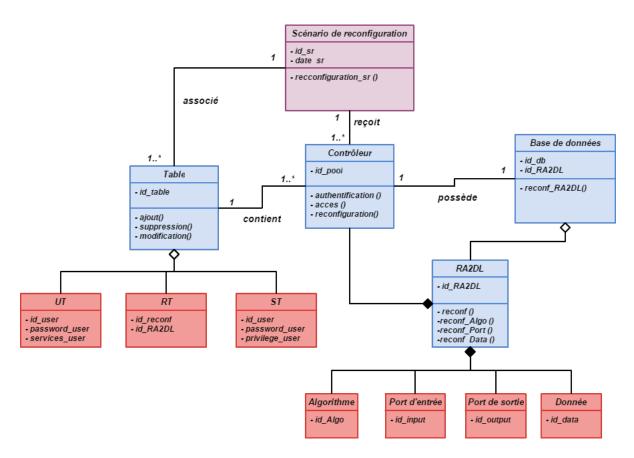

|    |            | 5.2.1   | Définition de RA2DL-Pool                                        | 130 |

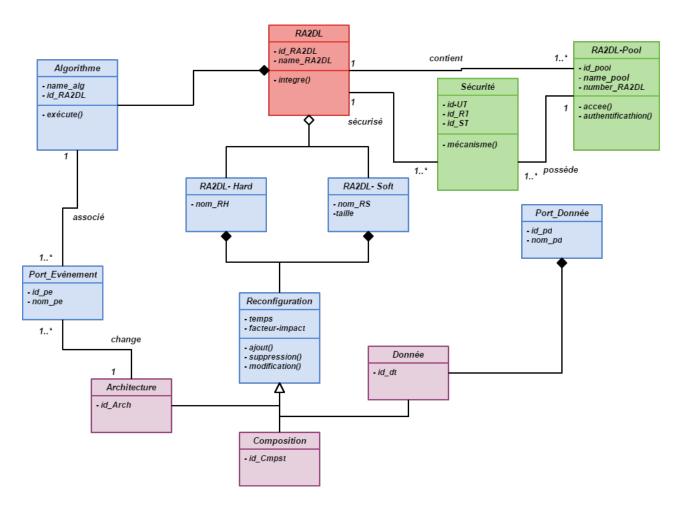

|    |            | 5.2.2   | Architecture de RA2DL-Pool                                      | 131 |

|    |            | 5.2.3   | Architecture Sécurisée à Base de RA2DL-Pool                     | 133 |

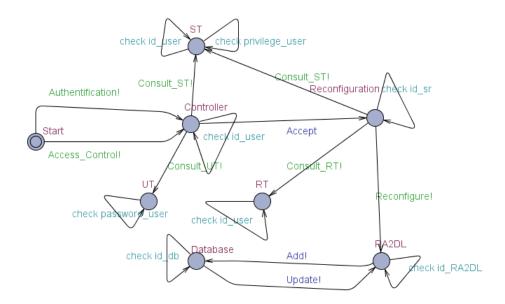

|    | 5.3        | Mécar   | nismes de Sécurité de RA2DL                                     | 133 |

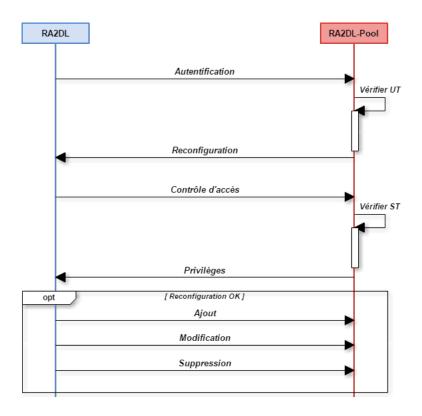

|    |            | 5.3.1   | Mécanisme d'Authentification                                    | 135 |

|    |            | 5.3.2   | Mécanisme de Contrôle d'Accès                                   | 136 |

|    | 5.4        | Modél   | lisation de RA2DL-Pool                                          | 136 |

|    | 5.5        | Conclu  | usion                                                           | 139 |

| 6  | Étu        | de de   | Cas et Expérimentation                                          | 141 |

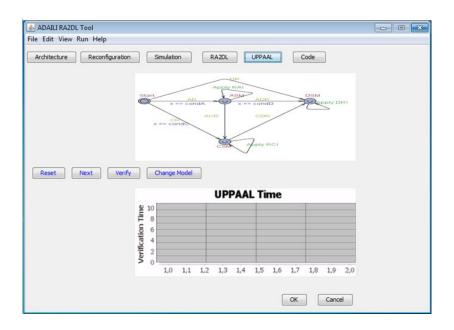

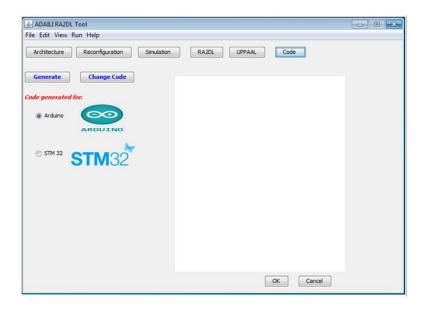

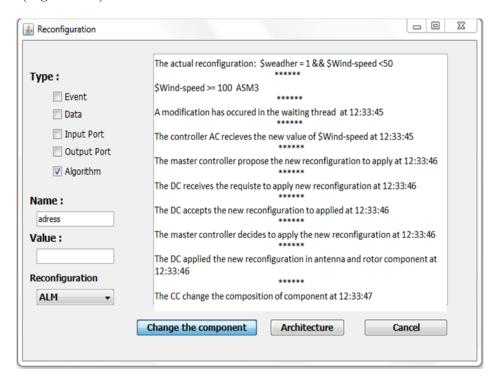

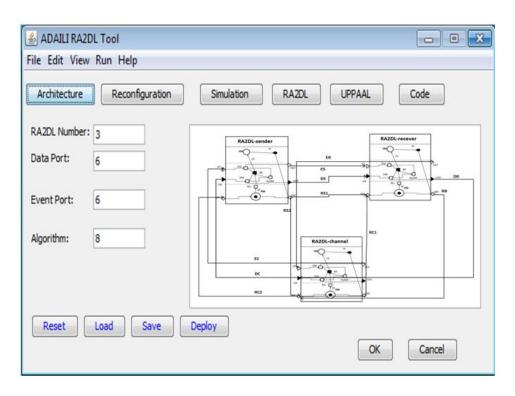

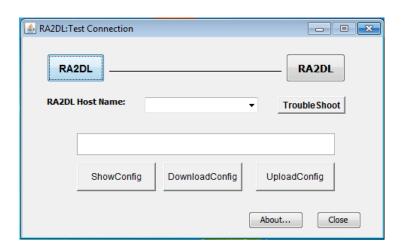

|    |            | 6.0.1   | Outil RA2DL-Tool                                                | 142 |

|    | 6.1        | Étude   | s de Cas                                                        | 146 |

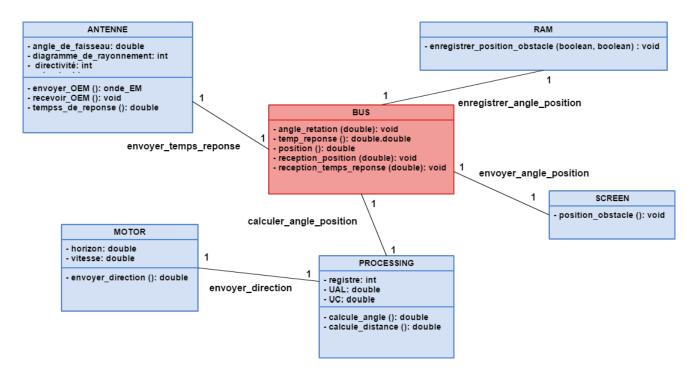

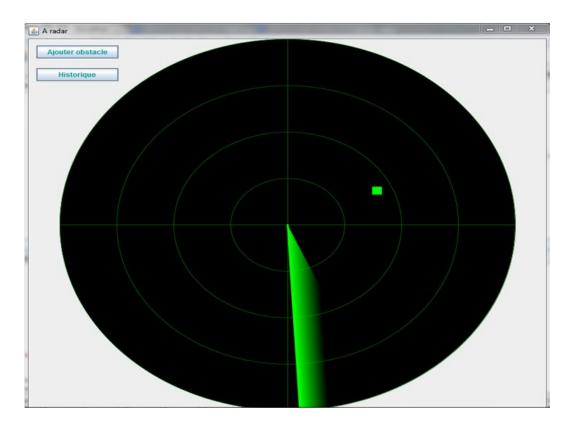

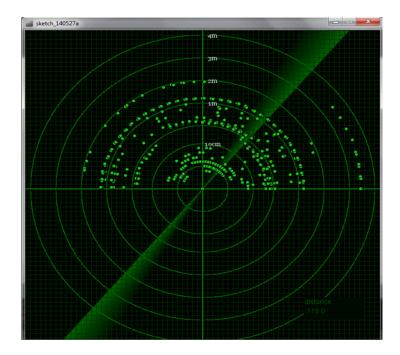

|    |            | 6.1.1   | Système Radar                                                   | 146 |

|    |            | 6.1.2   | IEEE 802.11 Wireless LAN                                        | 157 |

|    |            | 6.1.3   | Système de surveillance du corps                                | 165 |

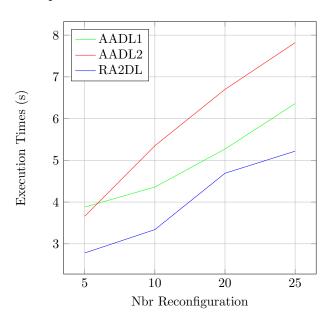

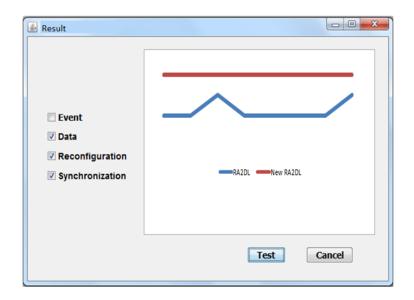

|    | 6.2        | Évalua  | ation de RA2DL et synthèse                                      | 169 |

|    |            | 6.2.1   | Évaluation de RA2DL                                             | 169 |

|    |            | 6.2.2   | Synthèse                                                        | 173 |

| IJ | 7 <b>C</b> | Conclu  | sion et perspectives                                            | 177 |

| 7  | Cor        | nclusio | n et perspectives                                               | 179 |

|    | 7.1        | Contri  | ibutions                                                        | 179 |

|    | 7.2        | Synth   | èse                                                             | 181 |

|    | 7 9        | Dangna  | pativos                                                         | 100 |

|       |     | `        |   |

|-------|-----|----------|---|

| TABLE | DES | MATIERES | ١ |

Bibliographie 183

## Liste des tableaux

| 2.1 | Compositions des composants AADL                             |

|-----|--------------------------------------------------------------|

| 2.2 | Comparaison entre les solutions de reconfiguration d'AADL 85 |

| 2.3 | Comparaison entre les méthodes de reconfigurations           |

| 3.1 | Scénarios de reconfigurations                                |

| 4.1 | Information du jeton                                         |

| 5.1 | Méthodes de RA2DL-Pool                                       |

| 5.2 | Résultat de vérification de RA2DL-Pool                       |

| 6.1 | Résultats de vérifications des propriétés du radar           |

| 6.2 | Informations du jeton                                        |

| 6.3 | Résultat de la vérification du réseau                        |

| 6.4 | Exemple d'exécution                                          |

## Table des figures

| 1.1 | Méthodologie RA2DL                    |

|-----|---------------------------------------|

| 2.1 | Processus de l'approche IDM           |

| 2.2 | Modèle du composant proposé           |

| 2.3 | Changement de modes avec Meta-H       |

| 2.4 | Cycle d'utilisation du model-checking |

| 2.5 | Composants logiciels d'AADL           |

| 2.6 | Composants Matériels d'AADL           |

| 2.7 | Composant système d'AADL              |

| 2.8 | Ports d'AADL                          |

| 3.1 | Architecture du composant RA2DL       |

| 3.2 | Niveau Architecture                   |

| 3.3 | Niveau Composition                    |

| 3.4 | Niveau Données                        |

| 3.5 | Comportement de RA2DL                 |

| 3.6 | Modélisation de RA2DL                 |

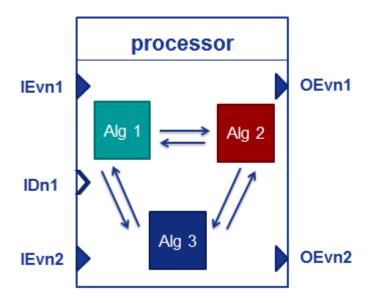

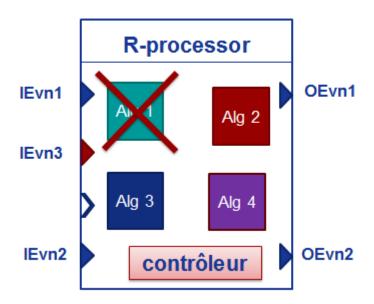

| 3.7 | Composant processor                   |

| 3.8 | Composant R-processor                 |

| 4.1 | Modèle d'exécution de RA2DL           |

#### TABLE DES FIGURES

| 4.2  | Matrice de coordination                                     |

|------|-------------------------------------------------------------|

| 4.3  | Coordination entre RA2DL <sub>1</sub> et RA2DL <sub>2</sub> |

| 4.4  | Modélisation d'un modèle d'exécution de RA2DL               |

| 4.5  | Modélisation de la coordination entre RA2DL                 |

| 4.6  | Exemple d'application distribuée                            |

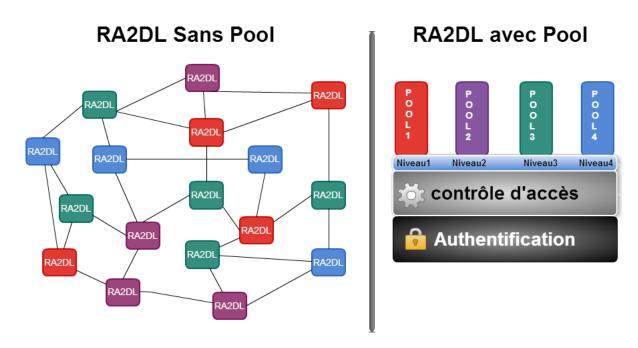

| 5.1  | RA2DL avec et sans Pool                                     |

| 5.2  | Diagramme de classe de RA2DL-Pool                           |

| 5.3  | Architecture sécurisée à base de RA2DL-Pool                 |

| 5.4  | Diagramme de séquence du mécanisme d'authentification       |

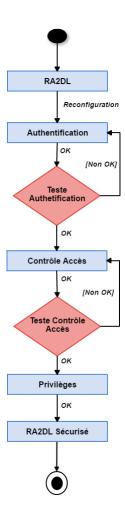

| 5.5  | Diagramme d'activité de deux mécanismes                     |

| 5.6  | Modélisation de RA2DL-Pool                                  |

| 6.1  | Architecture globale de RA2DL-Tool                          |

| 6.2  | Interface de vérification de RA2DL-Tool                     |

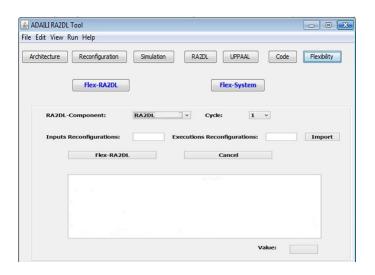

| 6.3  | Interface de calcul de la flexibilité                       |

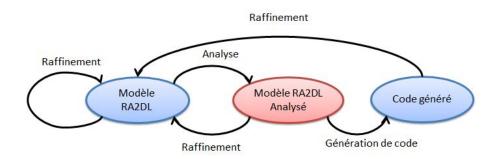

| 6.4  | Processus de génération de code évolutif                    |

| 6.5  | Génération de code du RA2DL                                 |

| 6.6  | Diagramme de classes du radar                               |

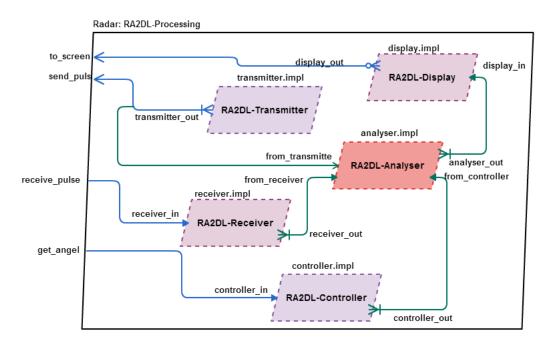

| 6.7  | Composants logiciels du système Radar                       |

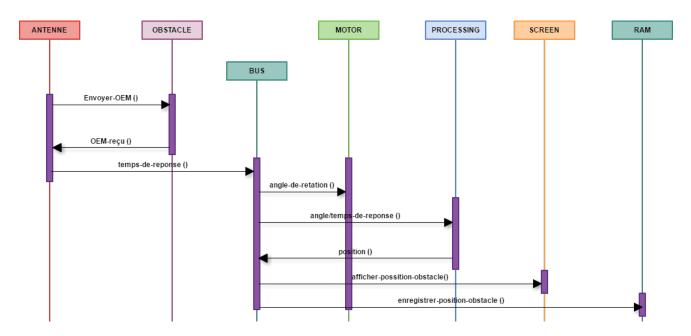

| 6.8  | Diagramme de séquence du système radar                      |

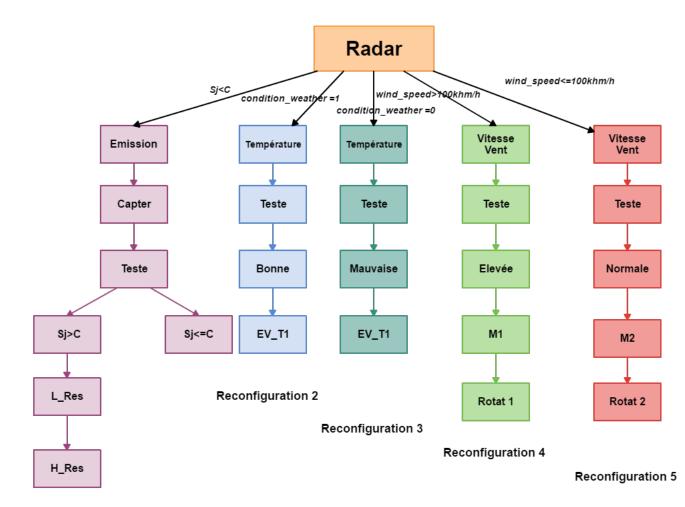

| 6.9  | Comportement du radar                                       |

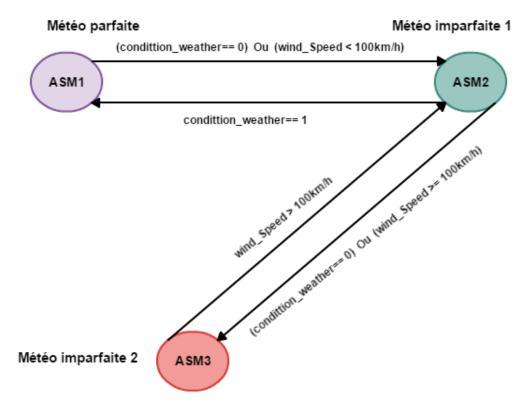

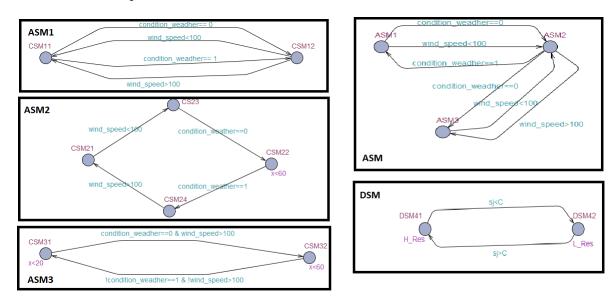

| 6.10 | Automate d'architecture du radar                            |

| 6.11 | Automate de composition de l'architecture ASM1              |

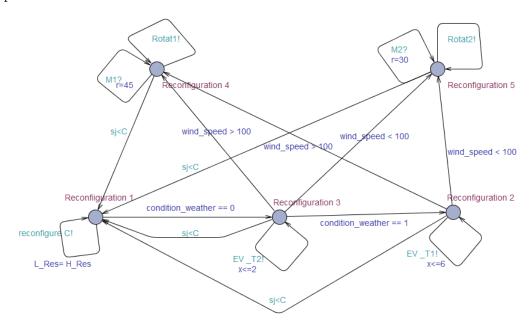

| 6.12 | Modélisation du module contrôleur                           |

| 6.13 | Modélisation du module contrôlé                             |

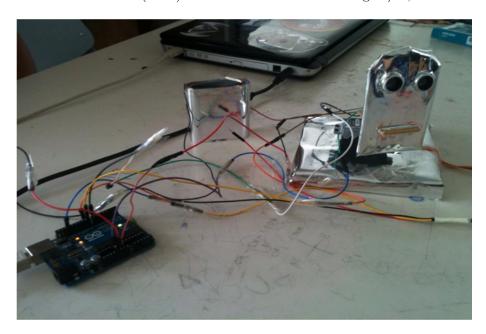

| 6.14 | Implémentation du système radar                             |

#### TABLE DES FIGURES

| 6.15 | Exemple de reconfiguration                                               |

|------|--------------------------------------------------------------------------|

| 6.16 | Interface de l'écran d'affichage                                         |

| 6.17 | Composants RA2DL du réseau de capteurs sans fil                          |

| 6.18 | Coordination entre RA2DL-sender et RA2DL-receiver                        |

| 6.19 | Interface du modèle d'exécution                                          |

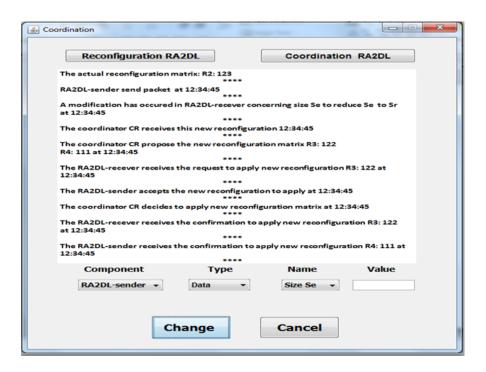

| 6.20 | Exemple de coordination et de reconfiguration                            |

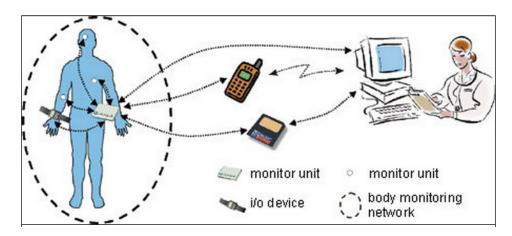

| 6.21 | Système de surveillance du corps [Bie02]                                 |

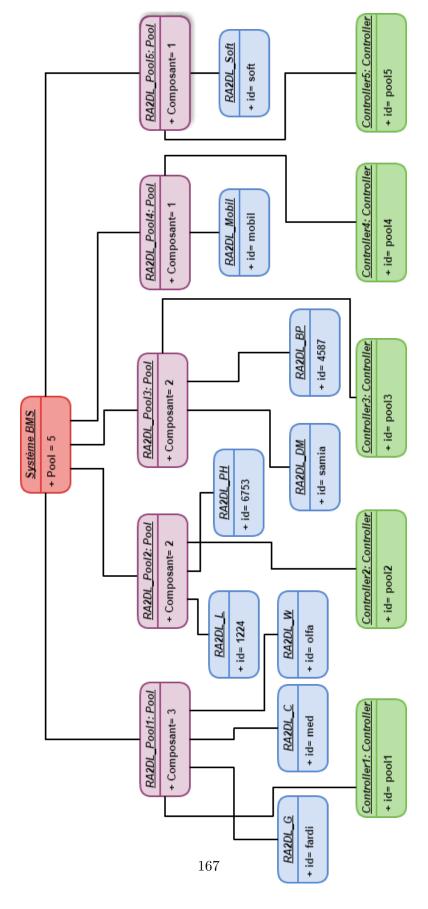

| 6.22 | Diagramme d'objet du système BMS                                         |

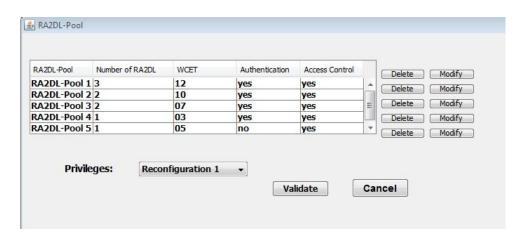

| 6.23 | RA2DL -Pool du système BMS                                               |

| 6.24 | Test de mécanisme d'authentification                                     |

| 6.25 | Objets détectés du système radar                                         |

| 6.26 | Comparaison des temps d'exécution entre (RA2DL) et (AADL1 et AADL2). 171 |

| 6.27 | Résultat de la simulation du modèle d'exécution de RA2DL 172             |

| 6.28 | Évaluation du temps de RA2DL sans et avec Pool du système BMS 173        |

# Première partie Introduction Générale

#### Chapitre 1

### Introduction Générale

#### 1.1 Rappels des concepts fondamentaux

Dans un premier temps, nous rappelons les principaux concepts de bases qui seront utilisés dans le cadre de cette thèse et les spécificités de chaque concept. Puis, nous nous focalisons sur la problématique de la reconfiguration soumise à des ensembles des contraintes. Ensuite, nous exposons la solution proposée et nous présentons les objectifs adaptées à la résolution de cette problématique.

Les systèmes embarqués : Ce sont des systèmes électroniques et informatiques intégrant à la fois des composants logiciels et matériels, sont souvent utilisés en raison de la diversité de leurs modes d'usage : Les systèmes avioniques intègrent des sous-systèmes électroniques comme les systèmes de navigation, radars, les systèmes de génération et de distribution électrique, etc. Les systèmes de télécommunications utilisent de nombreux systèmes embarqués des commutateurs téléphoniques aux téléphones mobiles. Les réseaux informatiques utilisent également des routeurs basés sur des contrôleurs embarqués et des ponts de réseau pour acheminer les données. La miniaturisation des composants logiciels, matériels et l'accroissement de la puissance de calcul dans les domaines de l'industrie sont aujourd'hui concernés par cette révolution technologique.

Composant: Dans le cadre de notre travail, nous nous basons sur la technologie intitulé "Composant" pour répondre aux besoins de cette révolution. En effet, plusieurs travaux de recherche sur l'approche par composant visent le développement des nouveaux types ou modèles de composants pour développer des systèmes ou des applications inté-

grants des composants. Ces composants sont très utiles car ils s'adaptent aux différents changements des besoins tels que la consommation d'énergie, la fiabilité, la performance et l'occupation physique, etc. Ces changements sont souvent en relation avec les environnements de fonctionnement et les révolutions du système : par exemple, changer le mode d'exécution ou minimiser la performance d'un composant. Le composant devrait modifier ses comportements d'une façon automatique au moment d'exécution pour répondre aux changements des caractéristiques de son environnement de l'exécution. Nous prenons les exemples de l'occurrence d'une panne matérielle ou logicielle, un scénario de reconfiguration, une modification de l'architecture et un changement du mode d'exécution qui obligent d'adapter le comportement d'un composant.

Modélisation des composants logiciels: Les travaux de recherche sur les systèmes embarqués visent le développement de modèles, de langages et d'outils pour la conception de systèmes embarqués. Ces derniers sont construits de manière modulaire à partir de composants. Jusqu'alors, les composants avaient été envisagés comme une décomposition structurelle du système à concevoir. Le défi actuel est de prendre en compte d'autres types de spécifications comme les spécifications structurelles et fonctionnelles. Les systèmes embarqués sont à la fois soumis à des contraintes de capacités (mémoire, bande passante), et à des exigences non fonctionnelles (exécution sous contraintes de temps réel). L'objectif principal dans ce domaine est d'étudier des modèles formels permettant de décrire ces systèmes et leurs contraintes (conception, spécification), de les construire (programmation, simulation, synthèse, exécution), et de les analyser (validation, vérification).

Composant AADL: (Architecture Analysis and Design Language) Standardisé par la sociétie SAE (International Society of Automotive Engineers) en 2004 [FG12] pour l'analyse et de description d'architecture des systèmes, qui est destiné à l'industrie des systèmes embarqués. AADL décrit plusieurs composants qui modélisent une partie du système. Certains composants sont matériels (bus, processor, memory ...), d'autres logiciels (process, thread, subprogram, ...). AADL fournit une description sous forme de texte, XML et graphique pour décrire des architectures matérielles et logicielles.

Automates temporisés : Introduits par Alur et Dill dans [AD94], constituent un modèle classique dont la sémantique s'exprime en terme de système de transitions tem-

porisé. Ils sont formés d'une structure de contrôle finie et manipulent un ensemble fini de variables réelles appelées horloges pour spécifier les contraintes de temps.

Logiques temporelles: Ces logiques ont été proposées pour la spécification des systèmes réactifs, pour la première fois en 1977 par Amir Pnueli [Pnu77]. Ce sont des formalismes adaptés pour énoncer des propriétés faisant intervenir la notion d'ordonnancement dans le temps, par exemple: un radar envoie un signal à la détection d'un objet.

**UPPAAL**: Un outil permet d'analyser des systèmes formés d'une collection d'automates temporisés qui communiquent par des variables entières partagées et des synchronisations par messages. Les automates temporisés d'Uppaal sont une variante des automates temporisés d'Alur et Dill [AD94]. En plus des horloges, les automates d'Uppaal manipulent des variables entières bornées. Les transitions de ces automates sont étiquetées par des gardes, des remises à zéro, des mises à jour de certaines variables entières et des étiquettes de synchronisation m? et m! où m est un canal.

Reconfiguration dynamique: De nos jours, l'un des défis les plus importants est le compromis entre la performance et la réponse rapide aux changements du marché et aux besoins des clients. L'une des directions les plus prometteuses pour résoudre ces problèmes est la reconfiguration dynamique. La reconfiguration dynamique. Cette fonctionnalité se réfère au processus de modification de la structure et du comportement du système au cours de son exécution. Être reconfigurable est important afin de réagir rapidement à l'évolution des besoins soudains et imprévisibles avec un coût et un risque minimum.

Les exigences des systèmes de contrôle industriels ont progressé de plus en plus en termes de flexibilité et d'agilité. En fait, les systèmes statiques sont conçus pour garder la même structure et le même comportement tout au long de leur existence. Sinon, ces systèmes n'ont pas la capacité de répondre à un événement externe. Ces systèmes ne peuvent pas faire face aux conditions fluctuantes qui touchent leur environnement d'exécution comme des pannes de machines, les changements d'objectifs, l'intégration d'une nouvelle machine, la modification de la demande de l'utilisateur, etc. L'une des solutions pour répondre à ces exigences est de rendre ces systèmes capables de s'adapter dynamiquement à l'environnement et à utiliser cette capacité d'adaptation afin de réduire leurs coûts et améliorer leur performance sans perturbations. En fait, selon l'état de leurs environ-

### 1.2. PROBLÉMATIQUE

nements, les systèmes de contrôle industriels peuvent chercher rapidement et de manière rentable la nouvelle configuration et la mise en œuvre de la reconfiguration sans être mis hors ligne. Il s'avère donc nécessaire de recourir à une méthode pertinente et rigoureuse pour modéliser ces systèmes afin de tenir compte de leur caractère reconfigurable, de leur conception et à être en mesure de maintenir leur cohérence au cours de leur évolution. La reconfiguration est le changement du comportement du système pour l'adapter à son environnement. Il existe deux types de reconfiguration : matérielle qui correspond à l'activation et la désactivation d'un composant du système et logicielle qui correspond à l'ajout ou la suppression des tâches.

Dans ce contexte, nous nous intéressons à améliorer les performances et réduire les coûts au niveau des systèmes embarqués à base de composants à travers leur adaptation au changement de leurs environnements. Ce changement est bien la reconfiguration que nous visons à l'implémenter au niveau d'un composant AADL qui se fait selon trois niveaux : architecturale, composition et données. Un système reconfigurable est modélisé à un moment donné par un ensemble de tâches. La reconfiguration architecturale engendre un ensemble de modifications sur l'architecture du système par l'ajout, la suppression des tâches ou l'arrêt et la reprise de l'exécution d'autres. La reconfiguration de composition permet la modification de la composition des tâches pour une architecture donnée. La reconfiguration des données modifie les valeurs des variables pour une composition donnée.

Dans ce chapitre introductif, nous présentons le contexte général de notre étude, nous synthétisons les problématiques posées dans cette thèse ainsi que les contraintes. Nous détaillerons les solutions et les objectifs de notre approche que nous exposerons dans la suite de ce mémoire.

## 1.2 Problématique

De nos jours, un des problèmes majeurs pour adapter dynamiquement des systèmes de contrôle industriel pour les rendre reconfigurables est la reconfiguration de son architecture applicative construite par des composants logiciels interagissant avec une architecture matérielle qui représente le support d'exécution construit par des composants matériels

### 1.2. PROBLÉMATIQUE

communicants entre eux. Nous regroupons ici les problèmes que posent la reconfiguration du système de contrôle industriel selon quatre axes complémentaires, à savoir : la détection des besoins de reconfiguration d'un système de contrôle industriel à base des composants, la mise en oeuvre et l'application des scénarios de reconfigurations, la vérification et l'analyse formelle du comportement d'un système reconfigurable après chaque reconfiguration, la coordination et la synchronisation entre les composants reconfigurables au niveau d'une architecture distribuée, et enfin le problème de sécurité des composants reconfigurables.

### 1.2.1 Détection des besoins de reconfiguration

Un premier problème concernant la reconfiguration dynamique des systèmes de contrôle industriel à base des composants est représenté au niveau de la reconfiguration de ces composants localement, qui consiste à détecter d'une part les conditions imprévisibles du changement de l'environnement à l'exécution de ces composants qui nécessitent des reconfigurations du composant, et d'autre part de s'assurer que le composant concerné est dans un état qui permet d'appliquer la reconfiguration demandée de façon sûre et automatique sans perturber l'exécution du système.

Par exemple : suite à une panne d'un capteur d'un système radar, il faut détecter les besoins de reconfiguration comme le changement climatique ou l'augmentation de vitesse du vent afin de proposer des scénarios de reconfigurations qui ne violent pas le fonctionnement du capteur. Puis la mise en oeuvre des mécanismes de reconfiguration.

### 1.2.2 Vérification formelle du comportement

La reconfiguration est dédiée essentiellement à la modification du comportement interne qui complique considérablement l'exécution du système ou du composant et qui permet la perturbation de son fonctionnement qui touche essentiellement son architecture, sa structure et ses données. En effet, il est nécessaire de suspendre certains algorithmes du système pour leur permettre de se reconfigurer. Si ces algorithmes sont modifiés par la reconfiguration, on ne peut les suspendre qu'une fois qu'ils ont fourni leurs résultats; sans quoi il est probable que le comportement du système devient incohérent. Nous appelons architecture flexible, l'architecture qui supporte les actions de la reconfiguration.

### 1.2. PROBLÉMATIQUE

Cette dernière permet de réaliser la reconfiguration de façon sûre et automatique. Nous devrons également nous intéresser aux problèmes que pose la vérification du comportement après chaque reconfiguration. Nous devrons également proposer une méthode d'analyse et vérifié le comportement du système reconfigurable, afin de vérifier que les scénarios de reconfigurations vérifient un certain nombre de propriétés.

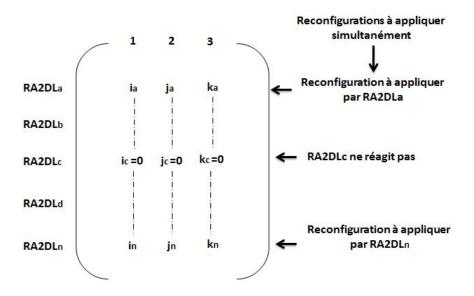

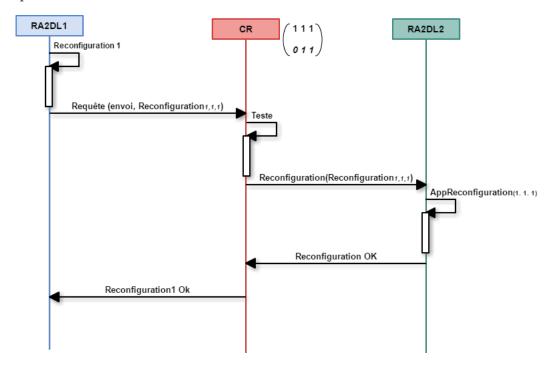

#### 1.2.3 Communication et synchronisation des composants reconfigurables

Le troisième problème réside au niveau de la coordination et la communication entre les composants reconfigurables. Au-delà de la mise en œuvre pratique des reconfigurations fiables des composants, et comment garantir la cohérence des reconfigurations dans une architecture distribuée à base des composants reconfigurable automatiquement, nous devons également proposer un protocole de coordination dans le cas où les reconfigurations sont synchrones afin de reconfigurer globalement le système. Une matrice de coordination est proposée qui permet la gestion de la coordination et la synchronisation d'une façon sûre afin de vérifier certaines propriétés de sûreté de cohérence, coordination correcte et ne viole pas l'aspect fonctionnel du système.

### 1.2.4 Sécurité des composants reconfigurables

Un système reconfigurable est ouvert à toutes formes d'attaques extérieures et des utilisations malveillantes dans le contexte d'un réseau ouvert se traduisant par une modification ou dysfonctionnement illégale. Par exemple, un scénario de reconfiguration peut être utilisé pour attaquer le système ou un composant. Au-delà de la mise en oeuvre pratique d'une sécurisation fiable du système pour garantir un niveau très élevé de sécurité, nous devrons également proposer une méthode pour sécuriser le système ou ses composants.

Ces différents problèmes seront fortement raffinés lorsque nous présenterons l'étude détaillée des besoins auquel nous allons répondre (Partie 2).

### 1.3 Contraintes de Reconfiguration

La reconfiguration matérielle et logicielle du système [LCD<sup>+</sup>00] peut être contrainte par des propriétés architecturales, de flexibilité, de ressources et de sécurité, etc. Elle est également contrainte d'assurer la performance requise par le système reconfigurable. Parmi les contraintes de reconfiguration, nous pouvons citer les suivantes :

- La reconfiguration du système repose elle-même sur l'ensemble des reconfigurations de ses composants et les possibilités de coordination et de synchronisation fournies. Cette reconfiguration doit, en particulier, garantir le respect des contraintes fonctionnelles, temporelles et opérationnelles. La question qui se pose est alors, comment peut-on effectuer la reconfiguration d'un système à base des composants par l'adaptation de ces comportements au moment de l'exécution, et plus particulièrement, comment reconfigurer un de ses composants (matériels ou logiciels) en respectant toutes les contraintes du cahier des charges?

- La reconfiguration des composants est dynamique et se fait d'une manière automatique pendant l'exécution du système. Les composants concernés par les reconfigurations peuvent être implicitement construits lors de fonctionnement du système (On-line) [CE00], ou des composants déjà spécifiés dès la conception et avant la mise en marche du système (Off-line) [The04]. La question qui se pose est donc, comment trouver un bon compromis entre les composants on-line et off-line?

- La reconfiguration des composants rend l'exécution du système un peu délicate vue la synchronisation et la cooridnation entre ces composants reconfigurables [MLCR08]. En effet, plusieurs incompatibilités peuvent apparaître entre les scénarios de reconfigurations et les règles de contrôle d'exécution. A titre d'exemple, nous pouvons citer la possibilité de deux scénarios de reconfigurations contradictoires qui apparaissent au même temps, un pour changer les constantes ou les variables d'un tel algorithme d'un composant et l'autre pour supprimer le même algorithme.

- Un autre problème concernant la reconfiguration dynamique des systèmes à base de composants consiste à sécuriser des activités de reconfiguration [BDF<sup>+</sup>11]. Cela concerne d'une part les composants concernés par les scénarios de reconfiguration, et d'autre part

le système qui dois reste fonctionnel et dans un état qui permet de mettre en œuvre l'adaptation de ses comportements.

### 1.4 Objectif et approche

### 1.4.1 Objectif

L'objectif général de notre travail de thèse est d'améliorer la productivité des systèmes de contrôles industriels qui sont équipés de composants matériels et logiciels en vue de les rendre reconfigurables et adaptatifs aux changements de leur environnent d'exécutions, en termes de qualité et de productivité. Nous devrons donc automatiser la reconfiguration et la production de ses composants composites. Pour améliorer la qualité de la production, nous nous appuierons sur des techniques de reconfiguration dynamique et automatique des composants de type AADL du système, ainsi que sur l'utilisation de protocoles propres à la mise en œuvre de coordination entre les composants du système dans une architecture distribuée. Pour améliorer la sécurité du système, nous utiliserons des techniques de sécurisation automatique des composants reconfigurables. Pour vérifier la qualité de notre approche, nous utiliserons des techniques de vérification formelle.

### 1.4.2 Approche Proposée

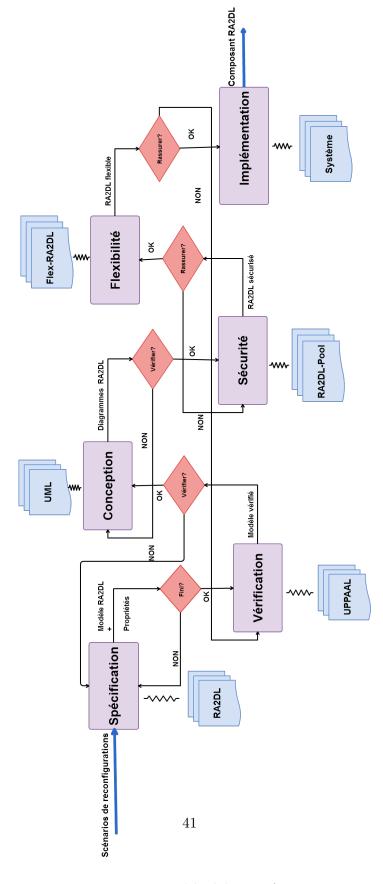

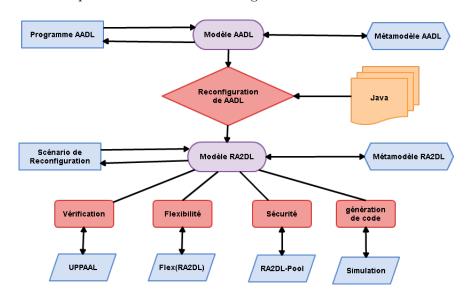

La solution envisagée par cette thèse s'attache à décrire une méthodologie globale représentée dans la Figure 1.1 qui repose sur six étapes : la spécification, la vérification, la conception, la sécurité, la flexibilité et l'implémentation, nous énumérons les détails de chaque étape ci-après pour le développement d'un système de contrôle industriel reconfigurable. Nous nous plaçons plus particulièrement dans le cadre des systèmes embarqués utilisant les approches par composants. Nous nous appuyons pour cela sur les travaux menés autour des composants AADL afin de proposer un composant AADL reconfigurable intitulé **RA2DL**.

FIGURE 1.1 – Méthodologie RA2DL.

#### 1.4.2.1 Spécification du composant RA2DL

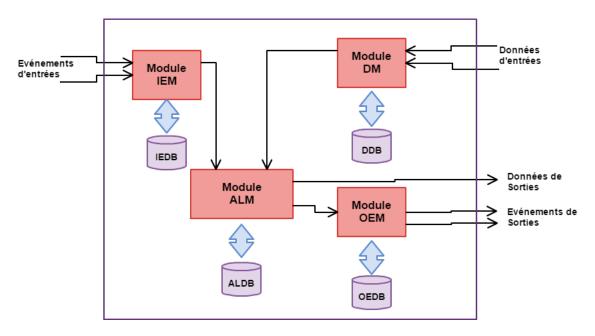

La première étape consiste à spécifier les caractéristiques locales du nouveau composant RA2DL. D'abord, nous regroupons les formes de reconfiguration en trois modes : architecturales, compositions (structures) et données. Ensuite, nous proposons une nouvelle architecture qui s'adapte aux trois formes de reconfigurations, c'est une architecture flexible répartie en quatre modules fondamentaux. Le premier module est dédié aux événements d'entrées, le deuxième est consacré aux algorithmes internes du composant, le troisième est réservé pour les événements de sorties et le quatrième dédie pour les données du composant. Enfin, nous formalisons les comportements de RA2DL en tenant compte ces trois formes de reconfigurations [AMKB15b] [AMKB15c].

#### 1.4.2.2 Vérification du composant RA2DL

La deuxième étape concerne la vérification des propriétés de sûreté, de vivacité, d'atteignabilité, de sécurité, etc. de RA2DL, en utilisant le modèle checker UPPAAL [Mer01] basé sur les automates temporisés pour la modélisation des composants et la logique TCTL (Timed Compotational Tree Logic) [ACD90] pour vérifier les propriétés de comportement, de synchronisation et de la sécurité de RA2DL. [AMKB15a].

### 1.4.2.3 Conception du composant RA2DL

La troisième étape consiste à représenter l'ensemble des besoins fonctionnels et non fonctionnels de RA2DL au niveau de la conception. Il s'agit de créer une représentation simplifiée par un modèle et un méta-modèle du composant RA2DL en utilisant le langage de modélisation unifié (UML) afin de montrer les vues statiques et dynamiques de RA2DL par un ensemble de diagrammes.

### 1.4.2.4 Sécurité du composant RA2DL

La quatrième partie est consacrée à la sécurisation du composant RA2DL. Nous proposons dans ce contexte une méthode qui s'articule autour de la notion du *Pool*, qui est un conteneur représenté par une super-classe qui vise à regrouper des composants RA2DL

selon un facteur de similarité afin d'affecter les différentes politiques ou des mécanismes de sécurité selon le niveau de sensibilité de ces composants [AMKB16].

#### 1.4.2.5 Flexibilité du composant RA2DL

La cinquième étape est dédiée aux mesures de la flexibilité de RA2DL, qui est un facteur crucial qui permet de calculer les taux d'acceptation de scénarios de reconfiguration. Ce facteur est comparé à un seuil  $flex_R$  donné par un expert. Pour mesurer la flexibilité d'un tel composant RA2DL, nous proposons une approche intitulée Flex-RA2DL qui s'appuie sur un algorithme AlgFlex dans le but de calculer cette flexibilité.

### 1.4.2.6 Implémentation du composant RA2DL

La sixième étape est réservée à l'implémentation du composant RA2DL, par la mise en œuvre de l'ensemble de ses modules sur une carte Arduino et la réalisation d'un outil complet intitulé RA2DL - Tool qui réalise toutes ces fonctions de la spécification à l'implémentation finale. L'application de notre approche est testée sur trois études de cas concrètes afin d'en valider les performances et montré l'applicabilité de notre approche dans le domaine de l'industrie.

### 1.5 Organisation du Manuscrit

Le manuscrit de thèse est organisé en sept chapitres structurés comme suit :

- Chapitre 2 : dresse un état de l'art sur l'approche par composant (l'approche online et off-line) et l'ingénierie dirigée par les modèles *IDM*. Après la définition du système de contrôle industriel, nous décrivons une étude détaillée du langage AADL et comment un composant de ce langage peut être exploité pour appliquer la reconfiguration locale au niveau du composant. Nous exposons les méthodes de reconfigurations statiques et dynamiques existantes nous détalions dans ce cadre les méthodes de la reconfiguration automatique des systèmes temps-Réels embarqués. Nous discutons aussi les limites des solutions existantes afin de synthétiser toutes ces approches.

- Chapitre 3 : comporte la première contribution de notre thèse représentée par une

approche qui analyse la reconfiguration d'un composant AADL et la transformation en un composant RA2DL. Cette approche vise à étudier les formes de reconfigurations possibles s'appliquant au RA2DL afin de proposer une architecture flexible. Nous proposons la formalisation du composant RA2DL avec ces comportement, la modélisation de RA2DL avec des automates temporisés et le calcul du facteur de flexibilité de RA2DL. Avant de conclure nous illustrons un exemple simple pour montre le passage d'un composant AADL à un composant RA2DL reconfigurable.

- Chapitre 4 : présente des extensions possibles à un composant RA2DL pour faciliter son exécution dans une architecture distribuée pour garantir une cohérence avec des reconfigurations synchrones. Nous étudions également c'est quoi un réseau des composants RA2DL au niveau d'une application distribuée avec la proposition et la modélisation d'un modèle d'exécution et d'un réseau de RA2DL distribué. Un simple exemple sera mis en place pour comprendre les contributions de ce chapitre.

- Chapitre 5 : propose une approche de sécurisation du composant RA2DL. Cette approche tient compte du groupement des composants RA2DL dans un conteneur intitulé RA2DL Pool en fournissant deux mécanismes de sécurité pour chaque Pool: authentification et contrôle d'accès.

- Chapitre 6 : consacré à l'implémentation du composant RA2DL. Le composant s'appuie sur un outil RA2DL Tool pour simuler l'exécution et les fonctionnalités de reconfigurations de la spécification à l'implémentation de RA2DL. Pour montrer les variétés d'applications, nous présentons trois études de cas sur lesquelles nous appliquons les contributions inventées au niveau de cette thèse. Nous montrons en particulier l'utilité et les gains de l'approche de reconfiguration proposée d'AADL par des évaluations statistiques.

- Chapitre 7 : nous concluons la thèse par un récapitulatif des contributions et des discussions avec des perspectives et des extensions possibles pour montrer l'utilité de notre approche dans nos futurs travaux de recherche.

Deuxième partie

État de l'art

# Chapitre 2

# État de l'Art

### 2.1 Introduction

Dans ce chapitre, nous présentons un état de l'art concernant l'ingénierie dirigée par les modèles et sur les approches par composants. Dans un premier temps nous définissons qu'est-ce-qu'un système de contrôle industriel et c'est quoi la différence entre un système de contrôle industriel et les systèmes temps-réels embarqués? Par la suite, nous citons des travaux d'ordre général sur les composants et nous abordons les types des composants On-line et Off-line ainsi que la sécurité de l'approche par composants. Ensuite, nous présentons un état de l'art sur le langage de description et d'analyse d'architecture (AADL) avec lequel nous avons restreint notre champ d'étude, nous donnons un panorama des principes d'AADL et les catégories de ses composants. Enfin, avant de conclure, nous présentons l'état de l'art dans le domaine de reconfiguration et plus particulièrement dans les systèmes temps-réels embarqués. Tout naturellement nous commençons par décrire les méthodes de reconfigurations statiques, par la suite, nous donnons les différentes méthodes de reconfigurations dynamiques, nous exposons aussi les méthodes de reconfigurations automatiques des systèmes temps-réels comme la reconfiguration mono-processeur et multi-processeurs. Notre contribution se situe dans la lignée de la reconfiguration automatique et dynamique des approches par composants. L'objectif est de construire un composant reconfigurable pour une application à base des composants distribuée, et de l'enrichir jusqu'à obtenir une application totalement reconfigurable.

Les principales contributions de cette thèse portent sur la reconfiguration des compo-

sants AADL matériels ou logiciels. Ces composants sont connectés entre eux pour former une architecture distribuée. Une description AADL consiste en un ensemble de déclarations de composants qui peuvent être instanciées pour former la modélisation d'une architecture du système global. AADL est particulièrement intéressant car il est orienté vers le développement d'applications par des composants et illustre donc bien la réponse à un besoin exprimé pour la reconfiguration par composant ou un réseau de composants soumis à des contraintes de fiabilité forte. En revanche, AADL définit les moyens de liaison entre les spécifications de ces composants et l'expression du comportement des différents composants.

### 2.2 Système de Contrôle Industriel

Dans cette section, nous présentons quelques définitions pour faire la différence entre un système embarqué, un système temps-réel et un système de contrôle industriel.

Système embarqué. Selon la définition de Wayne Wolf dans [Wol08] « Un système embarqué est défini comme un système électronique et informatique autonome, souvent temps réel, spécialisé dans une tâche bien précise. » Le terme désigne aussi bien (i) le matériel informatique représenté par certains périphériques qui sont essentiellement un processeur dédie au calcul et le contrôle de l'ensemble du système, des capteurs et des actionneurs et (ii) le logiciel utilisé constitue l'ensemble des programmes décrits dans un langage spécifique. Les ressources de ce système sont limitées. Cette limitation est également de niveau spatial à cause de l'encombrement réduit et de niveau énergétique à cause de la consommation restreinte.

Système temps-réel. Un système temps-réel (STR) est tout système qui doit respecter des contraintes essentiellement temporelles, l'exactitude des applications ne dépend pas seulement des résultats d'exécutions mais elle est liée aussi au facteur temps durant lequel ce résultat est produit. Dans ce cas, si les contraintes temporelles de l'application ne sont pas respectées, alors le système peut sebir des défaillances. Les contraintes temporelles sont divisées en deux types [Ngo08]: (i) contraintes strictes: à chaque occurrence d'une tache, on associe une échéance que le système doit impérativement respecter. Sans respect de ces

contraintes strictes, le système peut avoir des conséquences catastrophiques. (ii) contraintes relatives : le système se compose de tâches ayant des échéances, comme dans le cas des systèmes à contraintes strictes. Cependant, une violation d'une contrainte temporelle est tolérable et a un impact sur la qualité de service que l'on cherche à minimiser.

Système de contrôle industriel. Le système de contrôle industriel (SCI) fortement évolué ces dernières années est un système qui réunit un ensemble d'activités de types techniques et technologiques destinées essentiellement à l'automatisation des procédés et de systèmes de production industrielle. Les systèmes de contrôle industriel sont des réseaux de commande et de contrôle conçus pour soutenir les processus industriels. Ces systèmes sont utilisés pour surveiller et contrôler divers processus et opérations, tels que la distribution de gaz et d'électricité, l'eau, le raffinage du pétrole et le transport ferroviaire.

### 2.3 Ingénierie Dirigée par les Modèles et la Validation

Nous exposons dans cette section l'intérêt de l'ingénierie dirigée par les modèles IDM pour tirer profit de certains aspects : IDM en faveur de la qualité et de l'adéquation des ateliers produits par rapport au besoin, mais aussi pour couvrir le plus largement possible les besoins en termes de vérification et de validation.

### 2.3.1 Ingénierie Dirigée par les Modèles

L'ingénierie dirigée par les modèles IDM (en anglais, MDE : Model Driven Engineering) est un concept qui désigne la généralisation de l'approche MDA (Model Driven Architecture) [Sch06] et la séparation ente les spécifications fonctionnelles d'un système structuré en modèles et les spécifications de son implémentation sur une plate-forme donnée. Les avantages de l'IDM sont très nombreux dans la communauté des systèmes informatiques tels que :

- Une meilleure maîtrise de la complexité croissante des systèmes informatiques et leur réutilisation.

- La réalisation du même modèle sur plusieurs plates-formes grâce à des projections standardisées,

- L'indépendance vis à vis des évolutions technologiques,

- L'interopérabilité des applications tout en permettant l'évolution des plates-formes et techniques,

- La mise en œuvre de l'IDM est entièrement basée sur les modèles et leur transformation.

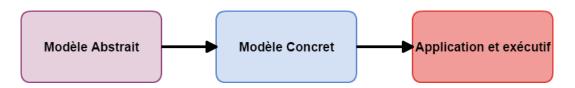

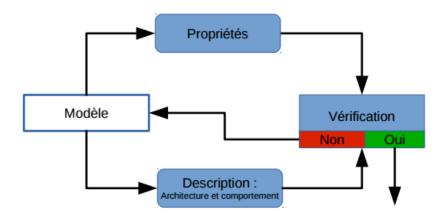

L'approche IDM consiste à manipuler différents modèles de l'application, depuis une description abstraite jusqu'à une représentation correspondant à l'implémentation effective du système. Le processus IDM se décompose en trois étapes, représenté par la Figure 2.1:

Figure 2.1 – Processus de l'approche IDM.

- Modèle Abstrait : ce modèle est raffiné afin d'ajouter différentes informations non fonctionnelles demeurant indépendantes de la plateforme d'exécution qui sera effectivement utilisée telle que la gestion de la sécurité,

- Modèle Concret : ce modèle prend en compte les spécifications propres à la plateforme d'exécution, il peut être également raffiné afin de prendre en compte différents paramètres liés à l'environnement d'exécution,

- Application et exécutif : le modèle concret est ensuite utilisé pour générer une application exécutable basée sur les spécifications à partir desquelles le modèle abstrait est construit.

L'IDM propose une démarche intégrée permettant de rassembler tous les éléments pour la description d'une application. De cette façon, IDM vise la mise en place de différentes étapes de raffinement depuis la conception de l'application jusqu'à la production de code exécutable.

Dans le contexte de l'IDM, les modèles sont manipulés via l'utilisation de langages [Pla12]. C'est pourquoi un certain nombre de langages permettant cette description sont apparus et offrent à ce jour un certain nombre de fonctionnalités. La plupart des approches

guidées par des modèles se basent soit sur :

- UML (Unified Modeling Language) [MG00] c'est un langage de modélisation unifié à usage général avec des profils comme MARTE (Modeling and Analysis of Real-Time and Embedded) [Mal08],

- ADL (Architecture Description Language) [ZFZ10] c'est un langage de description d'architecture dédié à des domaines particuliers, il permet la modélisation d'une architecture conceptuelle d'un système logiciel et/ou matériel et fournit une syntaxe concrète et une structure générique (framework) conceptuelle pour caractériser les architectures. Parmi les ADLs, le langage d'analyse et de description d'architectures (Architecture Analysis and Design Language) AADL fournit une notation textuelle et graphique standardisée pour décrire des architectures matérielles et logicielles. Le succès d'AADL dans l'industrie est justifié par son support avancé à la fois pour la modélisation d'architectures reconfigurables et pour la conduite d'analyses. En particulier, le langage a été conçu pour être extensible afin de permettre des analyses qui ne sont pas réalisables avec le langage de base. Dans cette optique, une annexe au standard AADL a été définie ABS (Annex Behavior Specification) [BF+07] pour compléter les descriptions d'architecture avec du comportement,

- **BIP** (Behavior Interaction Priority)[BBS06] : c'est un langage spécifique pour répondre à des besoins particuliers de modélisation et d'analyse, par exemple Fractal [BCL+06] et Ptolemy [EJL+03].

#### 2.3.2 Vérification et Validation

L'enjeu technologique et scientifique est l'étude de méthodes et outils facilitant le développement rigoureux et à coût maîtrisé des systèmes embarqués. La vérification représente un souci majeur pour un grand nombre de systèmes embarqués. D'où l'importance de la validation de ces systèmes [DPDP11], c'est-à-dire test, vérification et certification. Il y a donc un besoin réel et pressant de développer des méthodes et outils efficaces pour la validation des systèmes embarqués. Car la moindre faille sera exploitée par des malveillants potentiels . Les définitions les plus adéquates selon [TDH+04], [Car02] et [Mac05] pour les termes de vérification et de validation sont :

- vérification : est un ensemble d'étapes qui permet d'assurer que les modèles sont correctement formés et développés selon les bonnes pratiques. Les pratiques à ce niveau peuvent être l'aboutissement d'un ensemble de techniques comme la technique de modélisation.

- validation : est un processus qui permet d'affirmer que le modèle est cohérent par rapport à son intention en termes de méthodes utilisées et de résultat obtenu ; le but ultime est d'obtenir un modèle efficace, c'est-à-dire un modèle qui adresse le bon problème, qui fournit des informations pertinentes sur le système modélisé et que le modèle est finalement réellement utilisé.

### 2.3.3 Exemples de reconfigurations et IDM

Dans cette sous-section, nous présentons des exemples les plus proches de notre contexte de travail et qui traitent principalement le développement des systèmes adaptables dans le cadre de l'ingénierie dirigée par les modèles.

#### 2.3.3.1 MADAM

MADAM (mobility and adaptation-enabling middleware) [FHS<sup>+</sup>06] est projet qui permet de fournir aux ingénieurs logiciels des moyens adéquats pour développer des applications mobiles adaptatives.

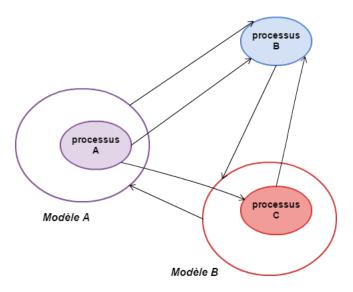

Avec MADAM, le modèle du système est une composition des composants types. Chaque composant type peut être atomique ou composite. Pour chaque composant type, plusieurs implémentations peuvent être définies. Pour distinguer entre les alternatives d'implémentations d'un composant dans les modèles d'architecture de MADAM, ils annotent des composants avec des propriétés (properties). Les propriétés sont étroitement liées à des éléments de contexte. De cette façon, ils représentent les dépendances entre les implémentations de composants et leurs contextes. Ces dépendances sont représentées sur des propriétés indicatrices de fonctions (property predictor functions), ces propriétés attribuent des valeurs constantes aux propriétés du composant type afin de faire la liaison entre les implémentations du composant et les éléments du contexte d'adaptation, cf. figure 3.1. Le middleware automatise la dérivation d'une variante d'un contexte spécifique à l'exécution,

c.-à-d. les configurations sont calculées en cours d'exécution.

MADAM met l'accent sur tous les éléments de l'adaptabilité des systèmes, notamment : le contexte, la variabilité, le comportement adaptatif du système par rapport à son environnement. Cependant, la modélisation des opérations de reconfiguration, les caractéristiques temporelles du système et l'analyse temporelle du système pour son comportement adaptatif ne sont pas traitées dans le projet MADAM.

#### 2.3.3.2 DiVA

DiVA (Dynamic Variability in complex Adaptive systems) [FDB<sup>+</sup>08] traite la notion de l'adaptabilité des systèmes dans une approche IDM en focalisant sur un traitement efficace du nombre de configurations possibles, qui peut croître de façon exponentielle avec chaque nouvelle dimension de variabilité. Dans cette approche on modélise : le contexte, la variabilité, le comportement adaptatif du système par rapport à son environnement. Cependant, la modélisation : des opérations de reconfiguration, les caractéristiques temporelles du système et l'analyse temporelles du système pour son comportement adaptatif, restent des points ouverts non traités dans le projet DiVA.

#### 2.3.3.3 CEA-Frame

CEA-Frame (Construction and Execution of Adaptable applications) [LSO+07] une approche dédiée pour la construction et l'exécution des applications reconfigurables qui offre principalement :

- 1- Des méthodes de spécification des variantes d'une application en combinant les techniques d'IDM et la modélisation orientée aspect.

- 2- Un mappage pour générer les éléments du système liés à la plateforme à partir de spécifications indépendant de la plateforme.

CEA-Frame présente une partie pour l'instanciation et l'exécution de ses applications. En conclusion, cette approche modélise le contexte, la variabilité du système et son comportement adaptatif, mais ne modélise pas les opérations de reconfiguration et ne prends pas en compte l'influence de ces opérations sur les caractéristiques temporelles du système.

Dans cette section nous avons présenté des travaux autour du développement des systèmes adaptables dans le cadre de l'IDM. Ces travaux ne traitent pas le cas des systèmes de contrôles industriels dans le cadre de l'IDM.

l'IDM de nos jours, ne cesse de faire face à des applications de plus en plus complexes qui doivent évoluer rapidement, à moindre frais ainsi que dans des courts délais. Et ce en répondant aux exigences croissantes des utilisateurs et au nombre grandissant de fonctionnalités à intégrer jusqu'à l'obtention du produit final. Pour aider les développeurs à suivre cette évolution, de nouvelles techniques de construction de logiciels destinées à faire face à ces contraintes ont vu le jour. C'est le cas de l'approche par composants, qui vise à faciliter le développement d'applications à partir de l'assemblage de briques logicielles/matérielles prédéfinies appelées composants. Nous expliquons dans la section suivante les intérêts des approches par composants.

### 2.4 Approches par Composants

Il est incontestable que le développement des applications à base de composants est devenue la norme depuis une vingtaine d'années. Nous présentons dans cette section les concepts de base des composants, puis nous dressons un état de l'art du domaine, nous décrivons les différents modèles à composant de type On-line (En ligne) et Off-line (Hors ligne). Ensuite, nous exposons les méthodes existants de sécurité des approches par composants. Enfin, nous concluons la section par une synthèse discute les limites de ces approches dans cette thèse pour mieux passionner notre approche.

### 2.4.1 Concept du Composant

De nos jours, il existe beaucoup de définitions dans la littérature du terme « composant ». Il est presque impossible de donner toutes ces définitions, mais nous nous essayons dans cette section de donner les définitions les plus utilisées par la communauté des systèmes embarqués.

Selon la définition de Larousse  $^1$  un composant est un « Élément standard utilisé dans

<sup>1.</sup> http://www.larousse.fr/dictionnaires/francais/composant/17736

la construction de produits industriels de série tels que machines, véhicules, circuits électriques et électroniques, appareils électroménagers, portes, fenêtres, etc. (En électronique, on distingue les composants passifs et les composants actifs) ».

Dans le rapport de Microsoft [Mic95], un composant est défini comme un fragment d'un logiciel qui est réutilisable, sous une forme binaire qui peut être lié avec d'autres composants provenant d'autres fournisseurs.

Szyperski dans [Szy02] définit un composant comme une unité de composition qui possède des interfaces contractualisées et un contexte de dépendance exprimé explicitement. Ensuite, il ajoute qu'un composant peut être déployé indépendamment.

Ivica Crnkovic dans son livre [Crn02] spécifie que chaque composant possède un ensemble d'interfaces permettant de décrire les connections possibles avec d'autres composants d'un système, ainsi qu'un code exécutable pouvant être associé au code d'autres composants.

Aoyoma dans [Aoy98], précise la différence entre le concept d'un composant et le concept d'un objet. Il considère qu'un composant devrait être capable de se connecter et de s'exécuter avec d'autres composants et/ou des frameworks, ce dernier peut être composé au moment de l'exécution sans compilation. De plus, il doit séparer l'interface de l'implémentation et cacher les détails de l'implémentation afin que les composants puissent être composés sans connaître les détails de l'implémentation.

Les caractéristiques principales servant à décrire un composant sont soulignées dans les définitions citées ci-dessous :

- Réutilisable : représente le principal objectif d'utilisation d'un composant. Il s'agit d'utiliser de nouveau le composant pour diverses applications,

- *Interaction*: désigne l'interaction et la communication entre les composants par l'intermédiaire de leurs interfaces.

Ivica Crnkovic dans [Crn04], définit deux types de composants pour les systèmes embarqués. Le premier réservé pour les petits systèmes non fonctionnels où l'interface du composant récapitule ses propriétés qui sont visibles de l'extérieur. Le deuxième type est dédié aux larges systèmes où les contraintes de ressources ne sont pas les principales préoccupations et la complexité et l'interopérabilité jouent un rôle beaucoup plus important.

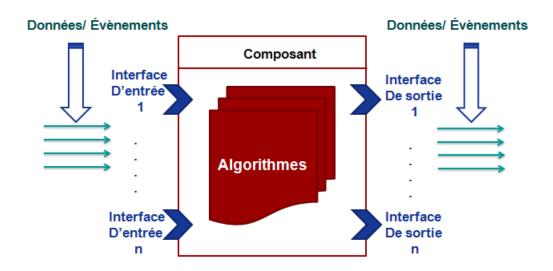

Dans notre thèse, nous définissons le modèle d'un composant (Figure 2.2) comme une boîte noire qui exécute un ensemble de fonctionnalités et qui est caractérisée par :

- Une implémentation : est présentée sous la forme des algorithmes intégrants des programmes exécutables qui supportent ses fonctionnalités et fournissent des services.

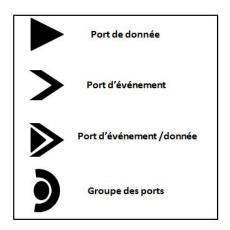

- Entrées/sorties : représentent les interfaces d'un composant, assurant les interactions avec d'autres composants de son environnement, ces interfaces possèdent deux types de ports, un pour les événements et l'autre pour les données.

FIGURE 2.2 – Modèle du composant proposé.

Il existe plusieurs types de formalisation de composants dans la littérature. Nous présentons ci-après quelques formalismes bien connus :

Les auteurs dans [MSKf05] ont formalisé un composant comme une unité qui fournit et demande des services à d'autres composants. Il offre les services aux autres composants par les interfaces de sortie et les demande par les interfaces d'entrée. Chaque interface notée I est associée à un port qui interagit avec un ensemble de méthodes noté  $M_p$ . La formalisation du composant est représentée comme suit :

$$\Sigma = (P_{\Sigma}, R_{\Sigma}, \beta_{\Sigma})$$

où,

- $P_{\Sigma} \subseteq I$ : Interfaces d'entrées,

- $R_{\Sigma} \subseteq I$ : Interfaces de sorties,

- $\beta_{\Sigma}: P_{\Sigma} \cup R_{\Sigma} \to M_p$ : les méthodes qui interagissent avec les interfaces du composant.

Un composant CS selon [Fil02] est formalisé de cette façon :

$$CS = (\Theta, AX)$$

où,

- $\Theta$  : représente l'ensemble des signatures du composant qui sont des interfaces d'entrées/sorties du composant,

- AX : désigne l'ensemble des axiomes du composant, qui sont des formules décrivant l'ensemble de ses comportements.

Sifakis dans [Sif05], donne une formalisation algébrique d'un composant  ${\cal CA}$  comme suit :

$$CA = (\mathbf{B}, GL, \oplus, \cong)$$

où,

- B : représente l'ensemble des comportements atomiques du composant,

- $(GL, \oplus)$ : représente un monoïde commutatif,

- $\textbf{-}\cong :$  est compatible avec la propriété de séparation structure-comportement.

Dans toutes les formalisations des composants citées auparavant, la spécification de la reconfiguration d'un composant n'est pas prise en compte. En effet, le changement des modes des composants n'est pas suffisamment formalisé pour spécifier une telle reconfiguration. De ce fait, il n'est pas possible de formaliser tous les comportements d'un composant reconfigurable en utilisant ces formalisations.

### 2.4.2 Composants des systèmes embarqués

Plusieurs travaux orientés composants dans le domaine des systèmes embarqués ont été conçus pour gérer la progression et la portabilité du code entre les différents systèmes. Il existe des propositions généralistes, ainsi que des implémentations pour des systèmes embarquées spécifiques. Tels que :

- Koala: C'est un modèle d'un composant développé essentiellement pour programmer les logiciels embarquées avec Philips [VOvdLKM00]. Dans Koala, les auteurs ont cherché à séparer le code métier de la configuration spécifique à la plate-forme. Ainsi, les développeurs du code métier encapsulent le code dans des composants et ne font aucune hypothèse sur les configurations dans lesquelles leurs composants sont utilisés. De même, les concepteurs de la configuration ne sont pas autorisés à changer le fonctionnement interne d'un composant Koala en fonction des spécificités de la plate-forme.

L'implémentation de Koala a été faite en langage C. La plupart des connexions entre les composants sont statiques et connues au moment de la configuration. Mais, malheureusement, Philips ne fournit pas l'accès au code source des composants logiciels de ses plates-formes.

- TAO : C'est un modèle d'un composant implémenté par CORBA [SLM98], dédie essentiellement pour les systèmes temps réel. Dans l'objectif de fournir un canevas qui contrôle les politiques et les mécanismes utilisés par CORBA en assurant un ordonnancement adapté.

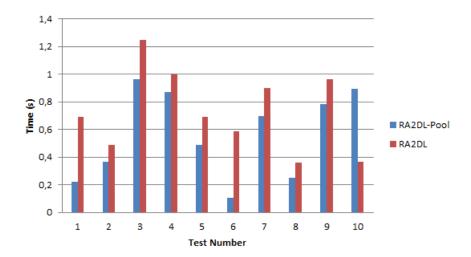

Le modèle à composants CORBA a été optimisé pour assurer le bon fonctionnement sur des systèmes sur puce. Les optimisations cherchent à réduire l'empreinte mémoire et le temps d'exécution. En particulier, les améliorations portent sur la diminution de la taille des structures de composants, principalement sur la réduction de code des talons et des squelettes, ainsi que sur des optimisations du compilateur.